#### Technical University of Denmark

#### High Performance Low Cost Digitally Controlled Power Conversion Technology

Jakobsen, Lars Tønnes; Andersen, Michael A. E.; Thomsen, Ole Cornelius; Niemann, Hans Henrik; Tøttrup, Peter

Publication date: 2008

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Jakobsen, L. T., Andersen, M. A. E., Thomsen, O. C., Niemann, H. H., & Tøttrup, P. (2008). High Performance Low Cost Digitally Controlled Power Conversion Technology.

#### DTU Library Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Lars T. Jakobsen

# High Performance Low Cost Digitally Controlled Power Conversion Technology

Innovation PhD thesis, December 2007

**DTU Electrical Engineering** Department of Electrical Engineering

## 1 Abstract

Digital control of switch-mode power supplies and converters has within the last decade evolved from being an academic subject to an emerging market in the power electronics industry. This development has been pushed mainly by the computer industry that is looking towards digital power management in order to reduce the power consumption of servers and datacenters.

The work presented in this thesis includes digital control methods for switch-mode converters implemented in microcontrollers, digital signal controllers and field programmable gate arrays.

Microcontrollers are cheap devices that can be used for real-time control of switch-mode converters. Software design in the assembly language of the microcontroller is important because of the limited resources of the microcontroller. Microcontrollers are best suited for power electronics applications with low bandwidth requirements because the execution time of the software algorithm that realises the digital control law will constitute a considerable delay in the control loop.

Digital signal controllers are powerful devices capable of performing arithmetic functions much faster than a microcontroller can. Digital signal controllers are well suited for digital control schemes involving multiple control loops such as digital control of a switch-mode power supply with several converter stages.

Customised digital control solutions implemented in application specific integrated circuits are the best solution for high bandwidth digital control of non-isolated DC-DC converters. A customised digital control solution for a voltage mode control scheme should include a digital pulse width modulator which can generate a pulse width modulated signal with high switching frequency and high resolution, a digital compensator with a short execution time and an analogue to digital converter with a short sampling time.

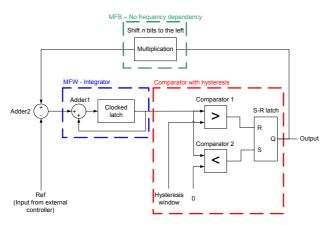

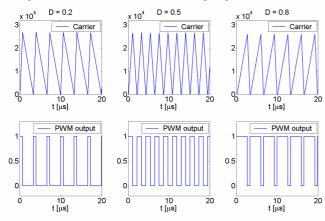

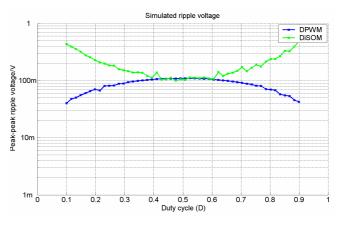

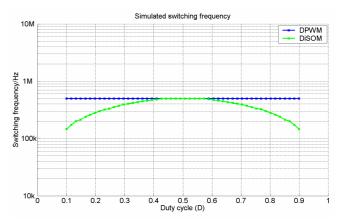

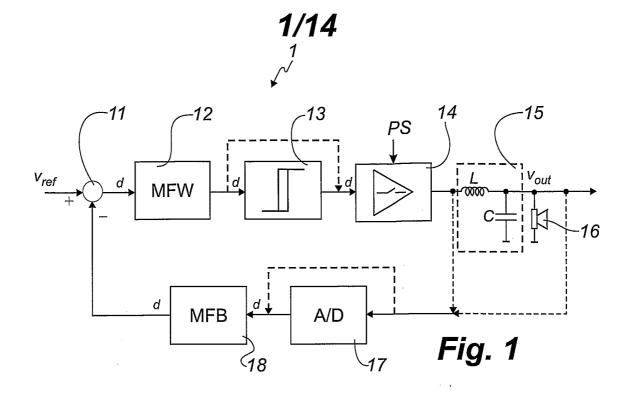

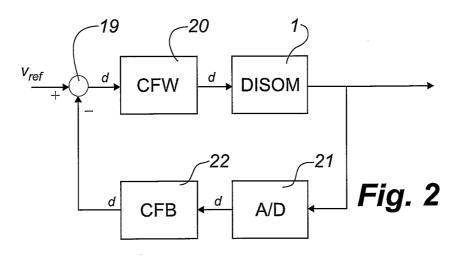

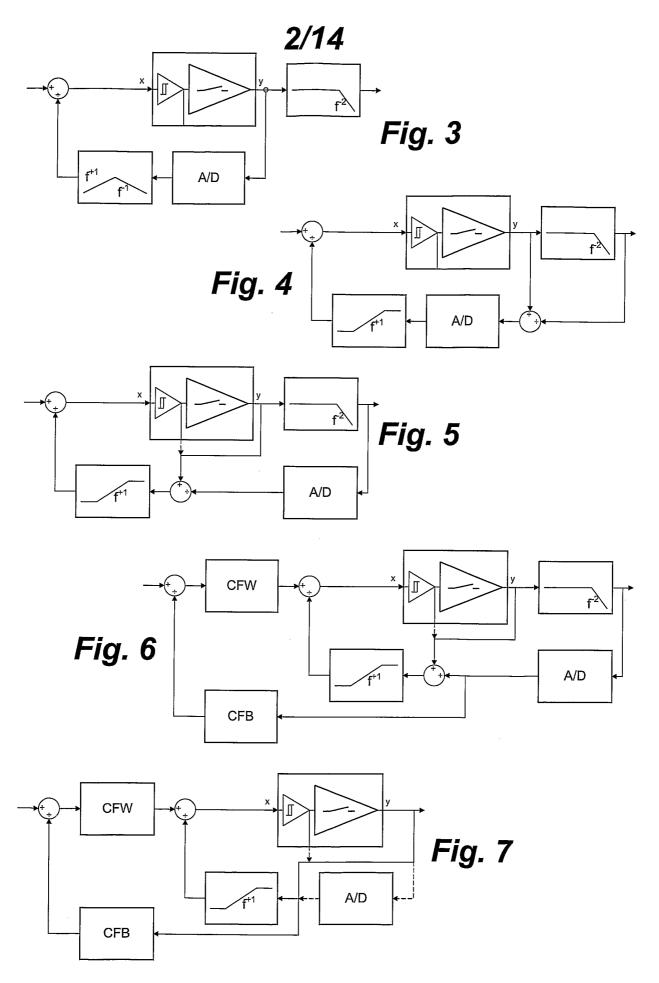

A digital self-oscillating modulator is proposed in the present thesis. The modulator is a free-running modulator which operates without an external carrier signal.

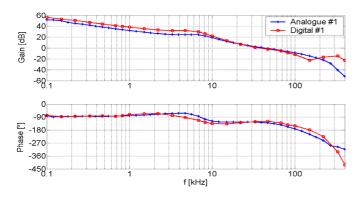

Customised digital control solutions offers the best performance for non-isolated DC-DC converters. The best digital control solution presented in this thesis, which was implemented with the digital self-oscillating modulator, performs comparable to common analogue control IC solutions. It is however possible to achieve an even better performance with an analogue control circuit built with separate analogue components.

## 2 Resumé på dansk

Digital regulering af switch-mode strømforsyninger og konvertere har indenfor de sidste ti år udviklet sig fra at være et videnskabeligt emne til et spirende marked i effektelektronikindustrien. Denne udvikling er hovedsageligt blevet skabt af computerindustrien, der ser digital power management som en måde at reducere strømforbruget i servere og datacentre.

Arbejdet, der præsenteres i denne afhandling, omhandler digitale reguleringsmetoder for switch-mode konvertere implementeret med microcontrollere, digitale signal controllere og field programmable gate arrays.

Microcontrollere er billige enheder, som kan benyttes til realtids regulering af switchmode konvertere. Softwaredesign i microcontrollerens eget assemblersprog er vigtigt på grund af microcontrollerens begrænsede ressourcer. Microcontrollere er bedst egnede til effektelektronikapplikationer med behov for lav båndbredde, fordi eksekveringstiden for software-algoritmen der realiserer den digitale regulering, vil udgøre en betragtelig forsinkelse i reguleringssløjfen.

Digitale signal controllere er hurtige enheder, som er i stand til at udføre aritmetiske beregninger hurtigere end en microcontroller. Digitale signal controllere er velegnede til reguleringssystemer med adskillige reguleringssløjfer såsom digital regulering af en switch-mode strømforsyning med flere konvertertrin.

Specielt udviklede digitale reguleringssystemer implementeret i 'application specific integrated circuits' er den bedste løsning til digital regulering af uisolerede DC-DC konvertere med høj båndbredde. Et specielt udviklet digitalt reguleringssystem med spændingsstyring bør omfatte en digital pulsbredde modulator med høj opløsning, en digital kompensator med kort eksekveringstid og en analog til digital konverter med kort måletid.

En digital selvsvingende modulator bliver introduceret i denne afhandling. Modulatoren er en fritløbende modulator, som fungerer uden et eksternt bærebølge signal.

Specielt udviklede digitale reguleringssystemer leverer den bedst mulige ydeevne til DC-DC konvertere. Det bedste digitale reguleringssytem beskrevet i denne afhandling, som er implementeret med en digital selvsvingende modulator, har en ydelse, der er sammenlignelig med almindelige analoge IC-løsninger. Det er imidlertid muligt at opnå en endnu bedre ydelse med et analogt reguleringssystem opbygget med separate komponenter.

## **3** Contents

| 1                           | Abstr                                                                 | act                                                                   | 1     |

|-----------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-------|

| 2                           | Resumé på dansk                                                       |                                                                       |       |

| 3                           | Contents                                                              |                                                                       |       |

| 4                           | Acknowledgements                                                      |                                                                       |       |

| 5                           | List of abbreviations                                                 |                                                                       |       |

| 6                           | Introduction                                                          |                                                                       |       |

| 7 State-of-the-art Analysis |                                                                       |                                                                       |       |

|                             | 7.1 I                                                                 | Digital PWM modulators                                                | 15    |

|                             | 7.1.1                                                                 | Dithering                                                             | 17    |

|                             | 7.1.2                                                                 | Hybrid DPWM modulators                                                | 18    |

|                             | 7.1.3                                                                 | Sigma-Delta DPWM modulators                                           | 21    |

|                             | 7.1.4                                                                 | Other DPWM techniques                                                 | 22    |

|                             | 7.2                                                                   | Digital control methods                                               | 25    |

|                             | 7.2.1                                                                 | Mixed Signal Control                                                  | 25    |

|                             | 7.2.2                                                                 | Digital Voltage Mode Control                                          | 27    |

|                             | 7.2.3                                                                 | Digital Current Mode Control                                          | 29    |

|                             | 7.2.4                                                                 | Non-linear Control                                                    | 31    |

|                             | 7.3                                                                   | Digital Hardware Implementations                                      | 33    |

|                             | 7.3.1                                                                 | Microcontrollers                                                      | 33    |

|                             | 7.3.2                                                                 | Digital Signal Processors/Controllers (DSPs/DSCs)                     | 35    |

|                             | 7.3.3                                                                 | Field Programmable Arrays / Custom ICs                                | 37    |

| 8                           | Micro                                                                 | ocontrollers in Power Electronics Converters                          | 43    |

|                             |                                                                       | Microcontroller definition                                            | 43    |

|                             | 8.2                                                                   | Software design for real-time control of switch-mode converters       | 45    |

|                             | 8.2.1                                                                 | Software reuse and development time                                   | 52    |

|                             | 8.3                                                                   | Microcontrollers and power electronics applications                   | 53    |

|                             | 8.3.1                                                                 | Non-isolated DC-DC converters                                         | 53    |

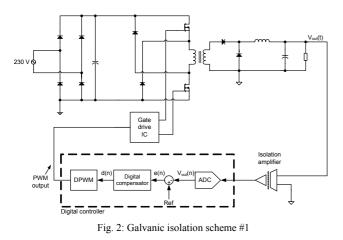

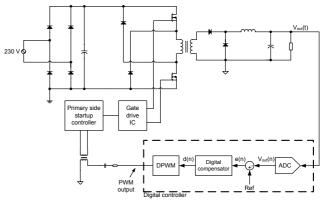

|                             | 8.3.2                                                                 | Offline converter with galvanic isolation                             | 56    |

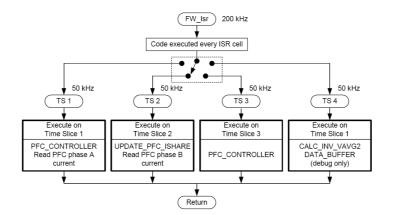

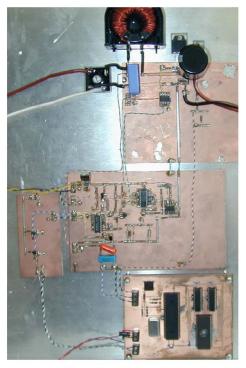

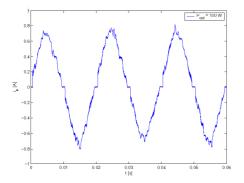

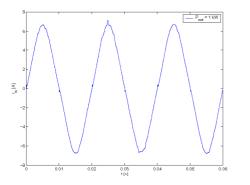

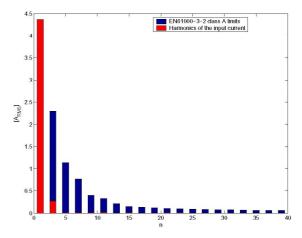

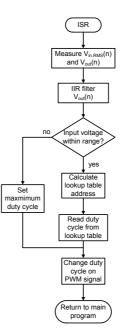

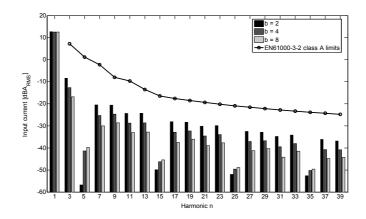

|                             | 8.3.3                                                                 | Boost converter with Power Factor Correction                          | 58    |

|                             | 8.4                                                                   | Conclusions and recommendations – The future of microcontrollers in j | power |

| el                          | ectronics                                                             | ·                                                                     | 60    |

| 9                           | Digital Signal Controllers/Processors in Power Electronics Converters |                                                                       |       |

| 9. | 1 DSC definition and devices                                                | 63  |  |  |

|----|-----------------------------------------------------------------------------|-----|--|--|

| 9. | 2 Applications and performance                                              | 65  |  |  |

|    | 9.2.1 Single-loop digital control of switch-mode converters                 | 65  |  |  |

|    | 9.2.2 Multi-loop digital control of switch-mode converters                  | 66  |  |  |

| 9. | 3 Conclusion                                                                | 69  |  |  |

| 10 | Customised Digital Control Solutions                                        | 71  |  |  |

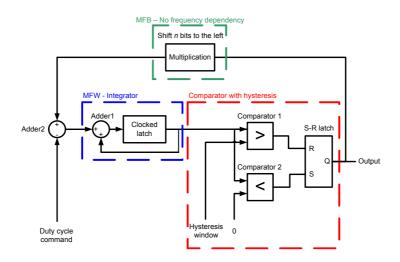

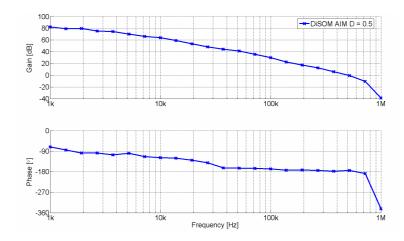

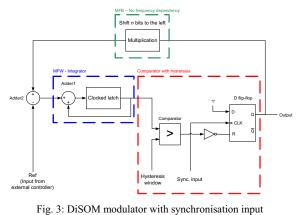

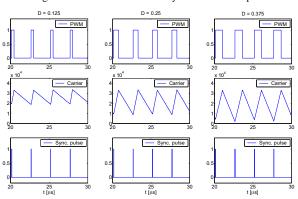

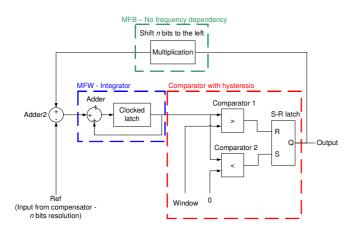

| 10 | 0.1 DiSOM – Digital Self-Oscillating Modulator                              | 71  |  |  |

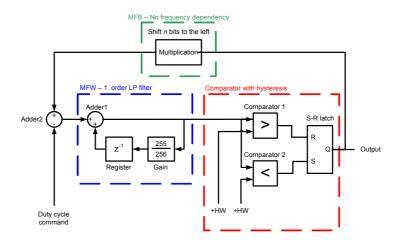

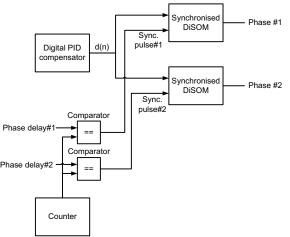

|    | 10.1.1 Fixed switching frequency operation in the DiSOM                     | 79  |  |  |

| 10 | D.2 Digital compensator implementation in ASICs                             | 81  |  |  |

| 10 | 0.3 Analogue to Digital Converters for High Performance Digital Control ICs | 84  |  |  |

|    | 10.3.1 Non-linear ADCs                                                      | 86  |  |  |

| 10 | 0.4 Interleaved Buck converter with efficiency improving control scheme     | 87  |  |  |

| 10 | 0.5 Conclusion - Digital versus Analogue Control                            | 89  |  |  |

| 11 | Conclusions                                                                 | 91  |  |  |

| 12 | Suggestions for future work                                                 | 95  |  |  |

| 13 | References                                                                  | 97  |  |  |

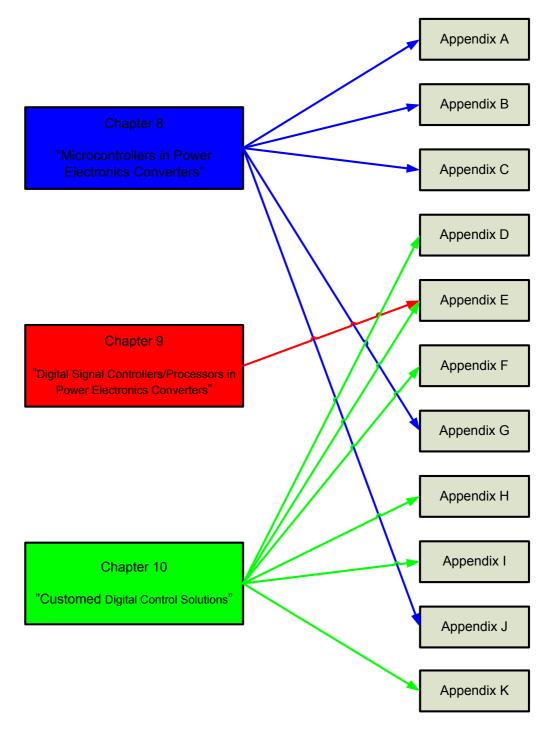

| 14 | Cross reference for chapters and appendices                                 | 105 |  |  |

| 15 | Appendix A – Publication by L. T. Jakobsen et al.                           | 107 |  |  |

| 16 | 16 Appendix B – Publication by L. T. Jakobsen et al                         |     |  |  |

| 17 | 17 Appendix C – Publication by L. T. Jakobsen et al                         |     |  |  |

| 18 | Appendix D – Publication by L. T. Jakobsen et al                            |     |  |  |

| 19 | Appendix E – Publication by L. T. Jakobsen et al                            | 147 |  |  |

| 20 | Appendix F – Publication by L. T. Jakobsen et al.                           | 157 |  |  |

| 21 | Appendix G – Publication by L. T. Jakobsen et al.                           | 165 |  |  |

| 22 | Appendix H – Publication by L. T. Jakobsen et al                            |     |  |  |

| 23 | Appendix I – Publication by L. T. Jakobsen et al                            |     |  |  |

| 24 | Appendix J – Paper draft by L. T. Jakobsen et al                            |     |  |  |

| 25 | 5 Appendix K – Patent application WO2007/098766A22                          |     |  |  |

## 4 Acknowledgements

The present PhD thesis could never have been written without the support of my family and my colleagues at the Technical University of Denmark.

My mother deserves the place of honour because she has always patiently listened to me complain about my technical and personal problems. I want to express my gratitude for her support and belief in me through good and hard times. I also want to thank my sister for always being there to discuss my problems and to tell me that I was not the only PhD candidate who doubted if he was capable of achieving the PhD degree.

I want to thank my supervisor Professor Michael Andersen for giving me the possibility to pursue the PhD degree as a member of the Power Electronics Group at the Technical University of Denmark and his constant support and help. I would likewise like to thank the Technical University of Denmark for the Innovation PhD scholarship that has funded my studies.

Industrial PhD Mikkel Høyerby and I have had many interesting discussions about both analogue and digital control and power electronics in general. These discussions have been a great inspiration and help to me and I want to express my appreciation to Mikkel Høyerby.

I would like to thank my other colleagues in the Power Electronics Group for creating a pleasant working environment and for their readiness to be of help to me at all times.

## 5 List of abbreviations

| ADC    | Analogue to Digital Converter                     |

|--------|---------------------------------------------------|

| AIM    | Astable Integrating Modulator                     |

| ALU    | Arithmetic Logic Unit                             |

| ASIC   | Application Specific Integrated Circuit           |

| BOM    | Bill of Materials                                 |

| CMC    | Current Mode Control                              |

| CMOS   | Complementary Metal Oxide Semiconductor           |

| CPU    | Central Processing Unit                           |

| D-FF   | Data Flip-Flop                                    |

| DAC    | Digital to Analogue Converter                     |

| DLL    | Delay Locked Loop                                 |

| DPWM   | Digital Pulse Width Modulator                     |

| DSC    | Digital Signal Controller                         |

| DSP    | Digital Signal Processor                          |

| FIFO   | First-In First-Out                                |

| FIR    | Finite Impulse Response                           |

| FPGA   | Field Programmable Gate Array                     |

| HDL    | Hardware Description Language                     |

| IC     | Integrated Circuit                                |

| IIR    | Infinite Impulse Response                         |

| ISR    | Interrupt Service Routine                         |

| KSPS   | Kilo-Samples-Per-Second                           |

| LTI    | Linear Time Invariant                             |

| MAC    | Multiplier/Accumulator                            |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| MSPS   | Mega-Samples-Per-Second                           |

| OCC    | One Cycle Control                                 |

| PFC    | Power Factor Correction                           |

| PID    | Proportional-Integral-Derivative                  |

| PLL    | Phase Locked Loop                                 |

| PWM    | Pulse Width Modulation                            |

| ROM  | Read Only Memory               |

|------|--------------------------------|

| SAR  | Successive Approximation ADC   |

| SMPS | Switch-Mode Power Supply       |

| TDM  | Time Division Multiplexing     |

| UPS  | Uninterruptible Power Supplies |

| VCO  | Voltage Controlled Oscillator  |

| VMC  | Voltage Mode Control           |

| VRM  | Voltage Regulator Module       |

|      |                                |

## 6 Introduction

Digital control of power electronics is a very broad definition which covers subjects ranging from the control of a non-isolated Buck converter delivering a few watts of power to the control of an inverter in a 5 Megawatt wind turbine. The specifications and performance criteria are very different for the Buck converter and the inverter and it is therefore impossible to make a general definition of what is meant by high performance and low cost.

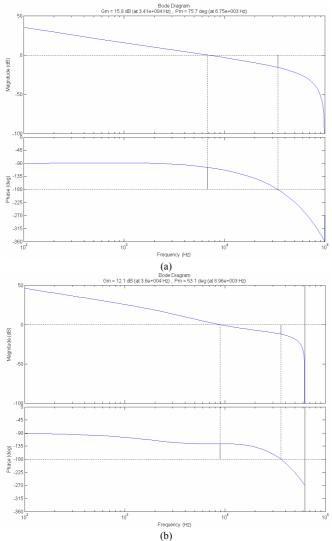

The purpose of this thesis is to investigate digital control solutions for switch-mode power converters in the power range from 10W up to 1kW. High performance is in thesis defined as accurate control of the output voltage and high control loop bandwidth. The digital control schemes presented in this thesis are the results of three years of research of the PhD project entitled "High Performance Low Cost Digitally Controlled Power Conversion Technology". The main body of the work relates to digital control of nonisolated DC-DC converters, but experiments within digital control of AC-DC converters have also been carried out.

The PhD project has been part of the Innovation PhD programme at the Technical University of Denmark which is new programme that has been started as an experiment. The purpose of the Innovation PhD programme is to educate candidates with a scientific PhD degree and knowledge of high-tech innovation and the business aspects of their area of research.

The work towards the Innovation PhD degree has encompassed market analysis of the power electronics market and specifically the market for digital control ICs. The market analysis has been used to write a business plan for a start-up company based on one of the ideas generated during the three year PhD project.

Because the project has been an Innovation PhD project the focus of the research has been on development of practical hardware and software solutions rather than theoretical analysis of the interaction between the digital control hardware and the switch-mode converter.

The advancements made in digital control of switch-mode power converters over the last few years have primarily been driven by the needs of the computer industry. The power consumption of both PCs and servers has increased as a result of the development of faster CPUs etc. The need for digital power management to supervise and control the power supplies in a server has given a boost to the research in high performance digital control methods for both DC/DC and AC/DC converters. Digital control of switch-mode power supplies and converters is not directly related to digital power management but it makes sense to combine the two in new products if digital power management is a requirement.

Analogue control of switch-mode converters has been developed over the last 35-40 years and has reached a very high level of performance. At the beginning of the PhD project existing digital control methods could not deliver performance that was anywhere near as good as the performance of analogue control methods. One of the aims of the project was therefore to come up with a new digital control method that was capable of delivering performance equal to the performance of state-of-the-art analogue control and at a competitive price.

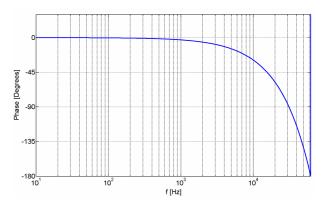

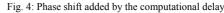

The biggest difference between analogue and digital control is that there is almost no delay in the analogue control loop. Digital control implementations have inherent delays in the analogue to digital converter that is sampling the output voltage and/or the inductor current and the digital controller core performing the calculations necessary to compute the duty cycle of the PWM signal controlling the converter. There will always be a delay regardless of the choice of hardware for the digital controller, but the choice of hardware has a huge impact on how long the delay is. The final converter performance is strongly determined by the delay as will be shown throughout the thesis.

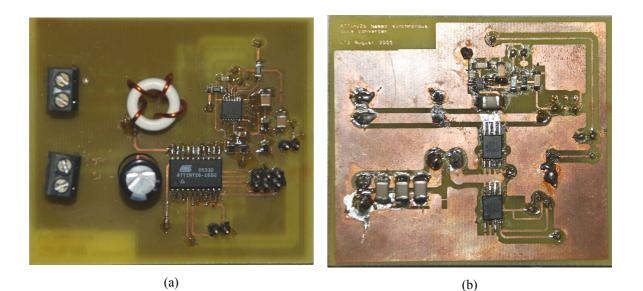

The PhD project has included work with low cost microcontrollers, Digital Signal Controllers (DSCs) and Field Programmable Gate Arrays (FPGAs).

In the beginning of the three year period the work focussed on digital control with microcontrollers, specifically 8-bit microcontrollers with a small number of I/O ports and an internal bus-width of 8 bit. The reason for choosing 8-bit microcontrollers as the subject of research was that academic research up to the year 2004 had for the most part been focussed on DSC implementations and it was thought that microcontrollers might represent a viable low cost alternative.

In order to obtain high performance digital control the software algorithms performing the control law was optimized with regards to minimizing the execution time of the algorithm. Experiments were performed with pure voltage mode control and mixed signal control schemes which combines the microcontroller with analogue control circuitry to improve system performance.

The next step was to investigate the limitations of state-of-the-art DSCs. It was quickly found that even though a DSC can perform computations faster than a microcontroller due to higher clock frequency and an on-chip hardware multiplier/accumulator module it is still not fast enough to deliver control loop performance comparable to existing analogue solutions.

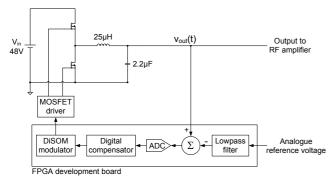

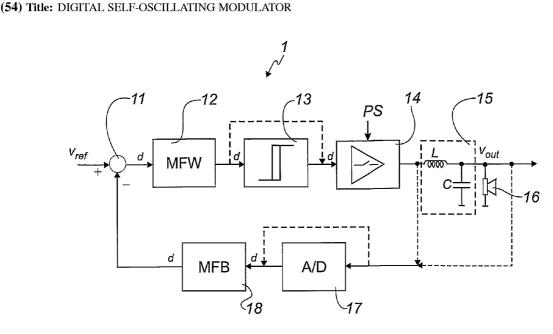

Customised digital control solutions implemented in an FPGA have been developed and tested in the second half of the PhD project. The work was divided into the development of VHDL implementations of a digital PID compensator with short computation time and low complexity and a complete controller implementation with a digital PWM modulator and the digital compensator. The author of this thesis and his supervisor has proposed a new Digital Self-Oscillating Modulator (DiSOM) that has been filed as a patent application.

The thesis describes some general properties of the digital controls method that have been researched in the PhD project. The thesis is supported by eleven appendices which is to be considered as an integral part of the thesis. The appendices comprise a number of papers published at international conferences and the patent application previously mentioned. The appendices describe some of the details of the different digital control methods that have been researched. It is recommended that the reader reads the appendices that are mentioned in a chapter of the thesis before the reading the chapter. Chapter 14 on page 105 shows which appendices should be read before each chapter.

## 7 State-of-the-art Analysis

Digital control technology for switch-mode power converters has evolved from mainly a research topic at universities to play an increasingly important role in the electronics industry. The progress achieved through university research and product development in the industry is indeed impressing and has shown that there definitely is a future for digital control of switch-mode power supplies.

The purpose of this chapter is to give an overview of the most important technologies that have been described in recently published scientific papers, patent applications and patents. There will also be some references to datasheets and user manual for specific products to highlight which technologies have actually made it through to the power electronics market.

The State-of-the-art analysis is divided into three main subjects, digital Pulse Width Modulators (DPWMs), digital control methods for power converters and digital hardware implementations.

The DPWM has proven to be of great importance in the design of digitally controlled power converters both in terms of the accuracy and speed of the digital controller.

The digital control methods will be extended to include mixed signal controllers since they incorporate some digital control elements and in some cases present very promising results.

The purpose of the State-of-the-art analysis is to describe different solutions, but not to compare them. The analysis will to some extent try to pinpoint the advantages and disadvantages of each solution, but the description be somewhat biased by the perception of the author since the specifics of the practical implementations are not always known.

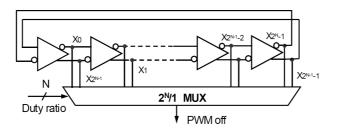

## 7.1 Digital PWM modulators

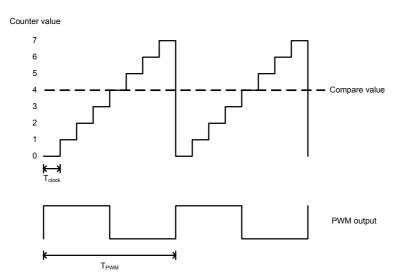

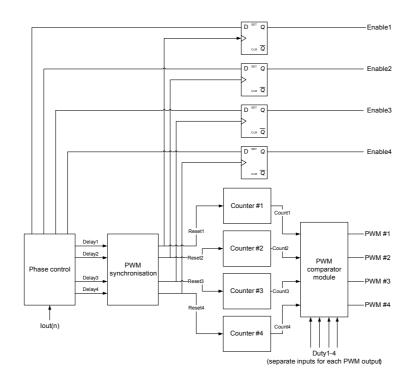

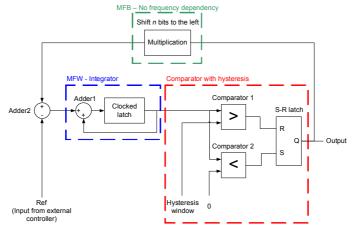

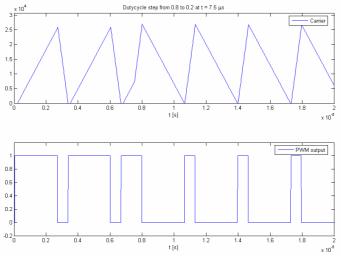

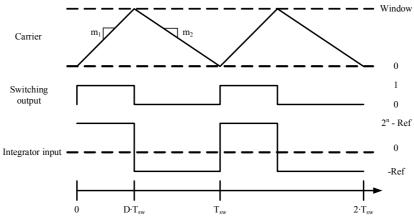

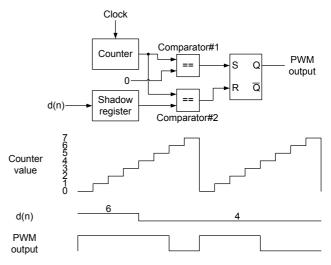

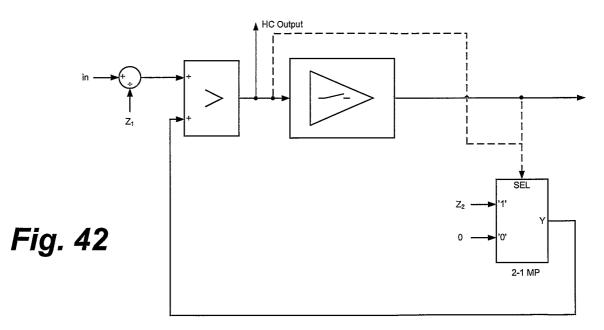

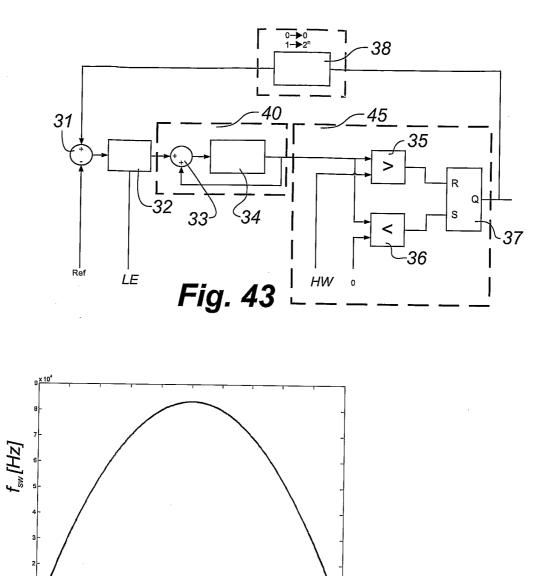

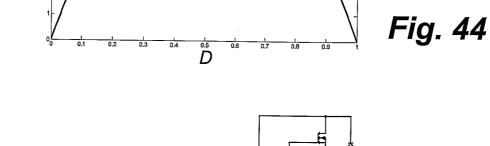

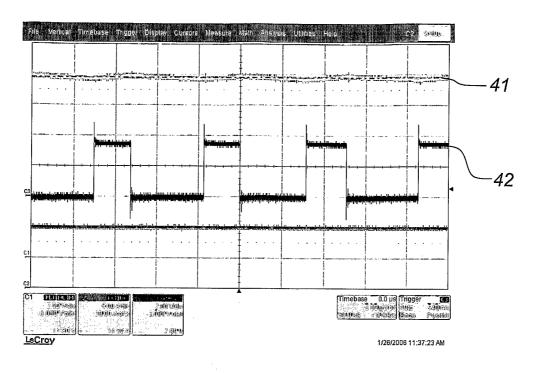

Digital PWM modulation is extremely important in modern digital control techniques for switch-mode power converters and especially DC/DC converters. The tendency is that the switching frequency used in power converters is increasing in order to reduce the size of capacitors and magnetic components in the converter. The use of higher switching frequencies has been made possible by advances made in MOSFET technology over the last decade. It is therefore important to be able to generate PWM signals with high switching frequencies digitally in order for digital control to be a viable alternative to analogue control. The most common DPWM is based on a counter clocked by a high frequency digital clock and a digital comparator. Fig. 7-1 shows the basic operation of a counter based PWM modulator. The counter based DPWM emulates a typical analogue PWM circuit where a triangular or sawtooth voltage is compared to a control signal that determines the duty cycle. The sawtooth voltage is emulated by a counter, which counts from zero to a preset value, which determines the PWM frequency,  $f_{sw}$ . If the counter value is smaller than the compare value, which can be changed by the digital control law such as a digital PID compensator, the PWM output is high, and if the counter value is larger than or equal to the compare value the PWM output is low.

The described implementation of a counter based DPWM generator is commonly used in a large number of microcontrollers and Digital Signal Controllers (DSCs) available from a number of manufacturers.

Fig. 7-1 Operation of a basic counter based DPWM

The DPWM modulator can be considered as a 1-bit D/A converter, which converts the digital control signal into an analogue signal. The effective resolution of the DPWM is determined by the clock frequency and the PWM frequency (see equation 7.1).

DPWM resolution =

$$\log_2\left(\frac{f_{sw}}{f_{clock}}\right)$$

(7.1)

The DPWM resolution is of great importance in modern switch-mode converters, because the demands for high accuracy of the output voltage regulation are increasing. The

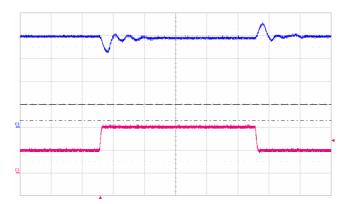

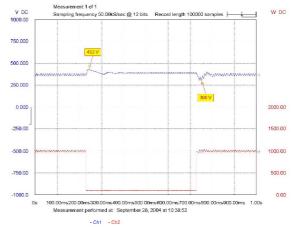

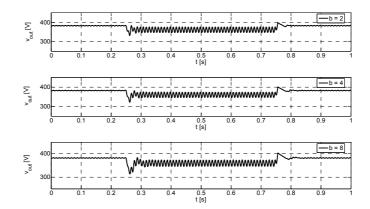

phenomena of *limit cycling* on the converter output voltage occurs if the DPWM resolution is too low [1,2]. Fig. 7-2 shows an illustration of what limit cycling is. Limit cycling results in a periodic oscillation on the output voltage at a frequency lower than the switching frequency.

In most modern day applications the basic counter based DPWM will not have the required resolution unless it is clocked at several GHz, which is virtually impossible to realise. If for instance a 1 MHz PWM signal with 12 bits of resolution were to be generated by a counter based DPWM block, the clock frequency would have to be 4.096 GHz.

One of the main areas of research within digital control of switch-mode converters in the last 6-7 years has been how to improve the DPWM resolution without operating at clock frequencies in the GHz range. In the following sub-sections, the most important methods to improve DPWM resolution will be briefly described.

Fig. 7-2 Illustration of limit cycling in a digitally controlled switch-mode converter (a) DPWM resolution is lower than ADC resolution resulting in limit cycling on the output voltage (b) DPWM resolution is higher than ADC resolution resulting in a steady output voltage [1]

#### 7.1.1 Dithering

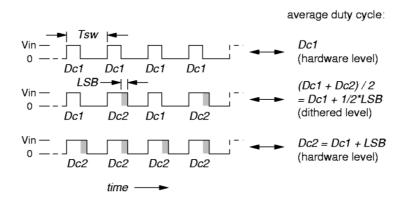

The simplest way to increase the effective resolution of a counter based DPWM is by adding dithering to the duty cycle command for the counter based DPWM. The principle of dithering (see Fig. 7-3) is to change the duty cycle by the smallest possible change, i.e.

by changing the least significant bit (LSB) of the duty cycle command to the DPWM modulator in a periodic manner. It is thereby possible to set the average duty cycle of the PWM signal in increments smaller than the change achieved by changing the LSB of the duty cycle command. By letting the dithering algorithm run over several PWM periods the effective resolution of the dithered PWM signal can be increased. If for example the PWM resolution must be increased by three bits the dithering algorithm would run over eight PWM periods. The dithering process will add sub-harmonic ripple currents and voltages in the switch-mode converter during steady state conditions, because the duty cycle command is periodically changed at a frequency lower than the switching frequency. The extra ripple voltage added by the dithering process will generally be smaller than the limit cycling oscillation that would occur without the use of dithering.

Fig. 7-3 Principle of dithering [1]

The disadvantage of the dithering process is that the sub-harmonic ripple introduced at the output voltage increases to an unacceptable level if the increase in resolution added by dithering is larger than 4-5 bits. The sub-harmonic ripple voltage will for a large increase in effective resolution get so large that the A/D converter (ADC) that samples the output will register the ripple and cause limit cycling in spite of the dithering process.

There are several ways of implementing dithering in a digital controller IC, which will not be described in detail. Dithering is included in several digital control ICs that are available on the market at the time this thesis was written [3-5].

#### 7.1.2 Hybrid DPWM modulators

A DPWM modulator based on a ring oscillator consisting of a number of delay elements, e.g. an inverter cell, can be implemented without the use of an external clock signal. The ring oscillator generates the PWM frequency automatically, and the minimum time step that the duty cycle can be adjusted in is equal to the propagation delay of one delay element. The disadvantage of the ring oscillator DPWM module is that it requires a large number of delay elements, thus requiring a large chip area in an IC implementation.

The hybrid DPWM modulator is basically composed of a small ring oscillator and a counter, which is clocked by the ring oscillator [6]. The oscillating frequency of the ring oscillator is higher than the switching frequency, and the counter is used to divide the oscillating frequency down to the switching frequency. The ratio between the oscillating and switching frequencies is typically low and the counter has a low number of bits. The counter sets the PWM frequency and determines the duty cycle in coarse steps. The exact point of transition from high to low for the duty cycle is determined by the delay line of the ring oscillator.

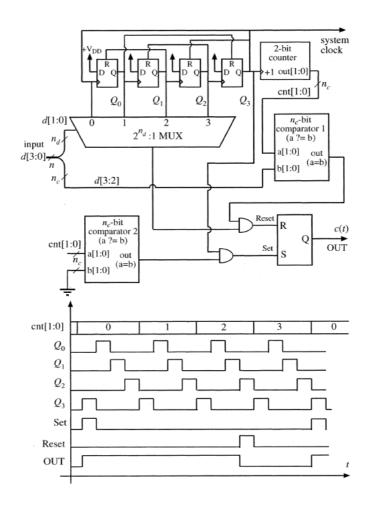

Fig. 7-4 shows a block diagram of a 4-bit hybrid DPWM modulator. The ring oscillator is composed of the four D Flip-Flops (D-FF) at the top of the block diagram. Comparator 2 is used to set the PWM frequency by dividing the system clock, i.e. the signal  $Q_3$  from the ring oscillator, by four. The output of comparator 2 in conjunction with  $Q_3$  is used to set PWM output on the S-R latch. Comparator 1 and the multiplexer (MUX) determine the duty cycle, where comparator 1 compares the counter output with the two most significant bits of the duty cycle command, d[3:2]. The two least significant bits of the duty cycle command, d[1:0], selects one of the four inputs to the MUX ( $Q_0$ ,  $Q_1$ ,  $Q_2$  or  $Q_3$ ) as the second input to the AND gate controlling the reset input of the S-R latch.

Since the four Q signals are shifted in time because of the propagation delay of the D-FFs it is possible to control the negative transition of the PWM output in steps that are equal to one quarter of the period time of the system clock. The delay line can be extended to a larger number of delays to be able to adjust the duty cycle in finer time steps, thereby increasing the effective resolution. Reference 6 reports a delay line based DPWM modulator with a switching frequency of 1 MHz with a ring oscillator frequency of 8 MHz. The counter is a 3-bit counter and the delay line adds 5 bits of resolution to make the effective DPWM resolution 8 bits.

The duty cycle can be adjusted in time steps equal to the propagation delay of one D-FF. In the basic configuration shown in Fig. 7-4 the propagation delay needs to be exactly equal to one fourth of the time period of the system clock. Otherwise the relationship between the duty cycle and the duty cycle command will not be a linear function.

Mass production of the delay line based DPWM will not allow tuning of the propagation delay to an acceptable level. CMOS process variations and temperature dependency is unavoidable and the design of the DPWM modulator will not meet the requirements for linearity in its basic form. To achieve linear operation a digital delay locked loop (DLL) can be added, which tunes the number of delay elements in the delay line [7]. The effective resolution of the DPWM will in this case vary with temperature and CMOS process variations, but the overall performance will most likely be better than for the basic delay line based DPWM.

If several PWM signals have to be generated by delay line based DPWM modules, the CMOS area that will be taken up by the DPWM block will be quite large. The reason is that it is necessary to have a delay line for each PWM signal that is generated. The number of multiplexers and comparators will also increase. Reference 8 proposes a structure in which one multiplexer and one comparator is time shared between several PWM modules. The idea is that it will always be known, which PWM signal is the next to change state, and the multiplexer and comparator can be assigned to the correct PWM output by a simple logic block. The idea is intended for implementation in a Field Programmable Gate Array (FPGA), but it is equally applicable to IC integration.

Fig. 7-4 Schematic and timing diagram for a delay line based DPWM modulator [6]

Texas Instruments have introduced a high resolution DPWM module in several Digital Signal Controllers (DSCs) and Application Specific Integrated Circuit (ASIC) products that is similar to the hybrid DPWM [9]. The Texas Instruments DPWM module runs of an external clock, which is typically 100 MHz. A delay line that receives the clock signal as input is used to increase the DPWM resolution in the same manner as in the hybrid DPWM. The number of delay elements in the delay line can be tuned so that the total delay matches one clock period in order to achieve linear operation of the DPWM. The delay line is not used as a ring oscillator, but it simply generates a number of positive edges shifted in time relative to the clock pulse.

Extensions of the hybrid DPWM modulator for multiphase interleaved Buck converters have been proposed in reference [10] and [11]. The main purpose of the proposed multiphase hybrid DPWMs is to simplify the design in order to reduce the complexity and implementation size of the modulator. Both of the proposed multiphase modulators use time sharing of a single delay line for all PWM outputs instead of having one delay line for each output. The disadvantage of the proposed modulators is that the duty cycle of each phase will be the same, which does not enable the digital control scheme to include active current sharing.

#### 7.1.3 Sigma-Delta DPWM modulators

Sigma-Delta modulator techniques have been used in both Analogue to Digital and Digital to Analogue converters and are well described in literature. In audio applications the Sigma-Delta modulator relies on over-sampling and extensive digital filtering to achieve very high DPWM resolution and a large signal-to-noise ratio. In practical applications of digital control of DC/DC converters both price and power consumption is of importance, and a simpler implementation of the Sigma-Delta modulator is necessary.

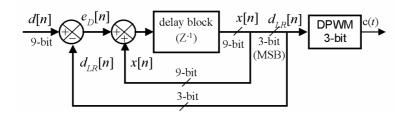

Fig. 7-5 shows an example of a Sigma-Delta DPWM modulator designed for low power portable applications. The modulator consists of a 3-bit counter based DPWM and a digital filter that turns a 9-bit duty cycle command into a 3-bit command for the counter based DPWM. The digital filter shapes the 3-bit signal in such a way that the average value is equal to the 9-bit input signal. The filter will generate some high frequency noise with a wide spectrum, which the DC/DC converter output filter will have to attenuate so as not to disturb the load on the output of the converter. The noise power spectrum will be attenuated at low frequencies and increase at higher frequencies. The noise power

spectrum is dependent on the switching frequency and the update rate of the duty cycle command d[n].

The Sigma-Delta DPWM modulator works best for switching frequencies in the MHz range, because the noise power will be low at lower frequencies, thereby allowing the DC/DC converter output filter to effectively attenuate the quantisation noise generated by the Sigma-Delta modulator.

Fig. 7-5 Block diagram of multi-bit Sigma-Delta DPWM [12]

The effective resolution is a function of the number of PWM periods over which the digital filter averages the 3-bit duty cycle command for the counter based DPWM and of the resolution of the counter based DPWM.

One important disadvantage of the Sigma-Delta modulator is that it requires a number of PWM periods to average the duty cycle command in order to achieve high DPWM resolution. It will be necessary to sample the output voltage with a sampling frequency that is an integer multiple of the PWM frequency to take advantage of the Sigma-Delta modulator's high resolution. The lower sampling frequency limits the achievable control loop bandwidth thereby resulting in a slower dynamic response of the DC-DC converter than for other DPWM technologies. Reference 12 therefore proposes a dual sampling compensator that samples with a low sampling frequency during steady state conditions and increases the sampling frequency if the error signal exceeds a certain preset limit.

Sigma-Delta modulators for DC-DC converters have been proposed in a number of scientific papers [12,13], but at the time of writing the present thesis no commercial controller ICs utilize the technology.

## 7.1.4 Other DPWM techniques

Apart from the three main types of digital PWM modulators with high duty cycle resolution several other DPWM modulators have been proposed in scientific papers [14-16]. Common for these solutions are that they are the work of researchers from a single

university and that they have not yet been used in the industry. For this reason the different solutions will only be briefly described.

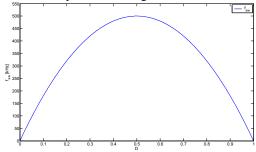

Reference 14 proposes a DPWM modulator with either fixed ON- or OFF-time. In the case of fixed ON-time the PWM resolution is increased for small duty cycle values and converges towards the resolution of a basic counter based DPWM for duty cycles close to unity. This is a desirable characteristic in Voltage Regulator Modules (VRM) that typically operate at a duty cycle around 0.1. In some applications it can be a disadvantage that the switching frequency varies with duty cycle, but in Point of Load Converters (POLs) and VRMs it is generally acceptable because the duty cycle variations are small during steady state operation. Reference 14 describes a combination of a constant frequency/constant ON-time modulator that achieves improved resolution with only small variations in the switching frequency. This type of modulator can be used if constant switching frequency is an important design parameter.

In reference 15 the digital carrier signal is generated with two high frequency clock signals operating with two different frequencies. The modulation technique is doubleedged PWM modulation where the two slopes of the digital carrier signal are clocked by the two different clock signals. Thus, the positive slope is controlled by the first clock and the negative slope by the second clock. The PWM resolution is in this case determined by the difference in frequency between the two clocks. The smaller the difference in frequency between the two clocks. The smaller the difference in frequency between the two clocks signals the higher the DPWM resolution. The authors of reference 15 propose that one clock signal is generated by a crystal oscillator and the second clock signal is generated by Phase Locked Loop (PLL) clocked by the crystal oscillator.

Reference 16 presents a way to increase PWM resolution in digital control systems implemented in an FPGA. The idea is to utilize the DLL that is included in many modern FPGAs. The DLL is in many cases able to create phase shifted versions of the internal clock, typically shifted by 90, 180 and 270 degrees. The additional transitions of the phase shifted clocks can be used to control the transition of the PWM signal thereby increasing the PWM resolution. The practical implementation is similar to the implementation of the PWM transitions of the PWM where a counter is used to control the coarse positioning of the PWM transitions and the delay line is used to control the exact position of the edge. In this case a

digital circuit utilizing the phase shifted clock signals generated by the PLL replaces the delay line.

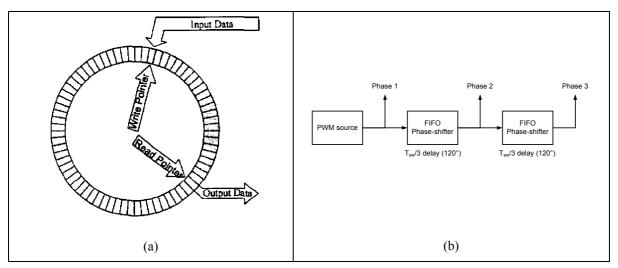

In section 7.1.2 two hybrid DPWM modulators for interleaved converters were briefly mentioned. These methods only applied to hybrid DPWM modulators, but other DPWM schemes can also be used to control interleaved converters. The simplest method for generating interleaved PWM signals is to generate one master signal. That signal is delayed by a fraction of the PWM period to generate the phase shifted PWM signal. One way to generate the delay is to configure a First-In-First-Out (FIFO) register as a ring buffer (see Fig. 7-6a). The ring buffer has two pointers; one to point to the address where new data is written and one to point to the address where the data is read. The FIFO is clocked by a high frequency clock and shifts the contents of the ring buffer one position for every clock cycle. By adjusting the read address of the ring buffer it is possible to adjust the delay of the PWM signal from input to output. Reference 17 proposes to cascade a number of FIFO phase-shifters (see Fig. 7-6b) to generate multiple phase shifted signals. The delay of each phase-shifter should be equal to 360/n degrees, where the integer *n* is the number of phases in the interleaved converter. The practical implementation in ref. 17 utilizes a FIFO IC from Texas Instruments and the control loop can be either analogue or digital because it simply feeds a PWM signal to the FIFO phase-shifters.

Fig. 7-6 FIFO based multiphase PWM generation [17](a) FIFO configured as a ring buffer (b) 3-phase PWM module with FIFO Phase-shifters

The use of FIFOs to generate phase shifted PWM signals from a single signal is straightforward but it does present a drawback in modern power electronics namely that

each phase gets exactly the same duty cycle. It is increasingly important to be able make slight adjustments in the duty cycle of each phase in an interleaved VRM module to ensure symmetrical phase currents. Variations in MOSFET ON resistance, inductor series resistance and different PCB layout for each phase can result in asymmetrical phase currents in an interleaved Buck converter. To achieve symmetrical current sharing it is necessary to adjust the duty cycle of each phase individually, which is not possible with the FIFO design proposed in reference 17.

## 7.2 Digital control methods

Digital control for a switch-mode power converter can be implemented in a number of different ways. The last five years of academic research have covered a large number of different digital control methods and it will not be possible to describe every solution in detail here. The subject has therefore been divided into four main groups which will be described generally in addition to one or two examples of practical implementations for each group.

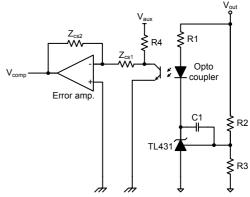

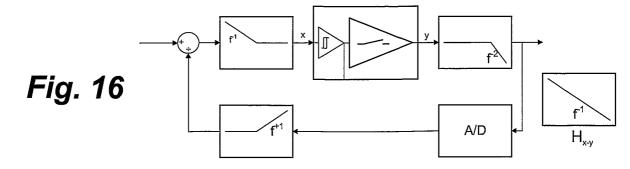

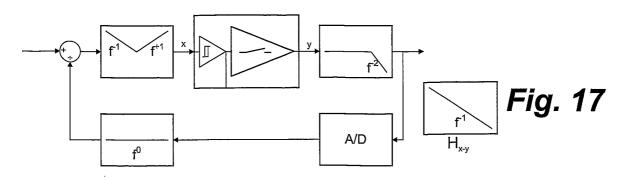

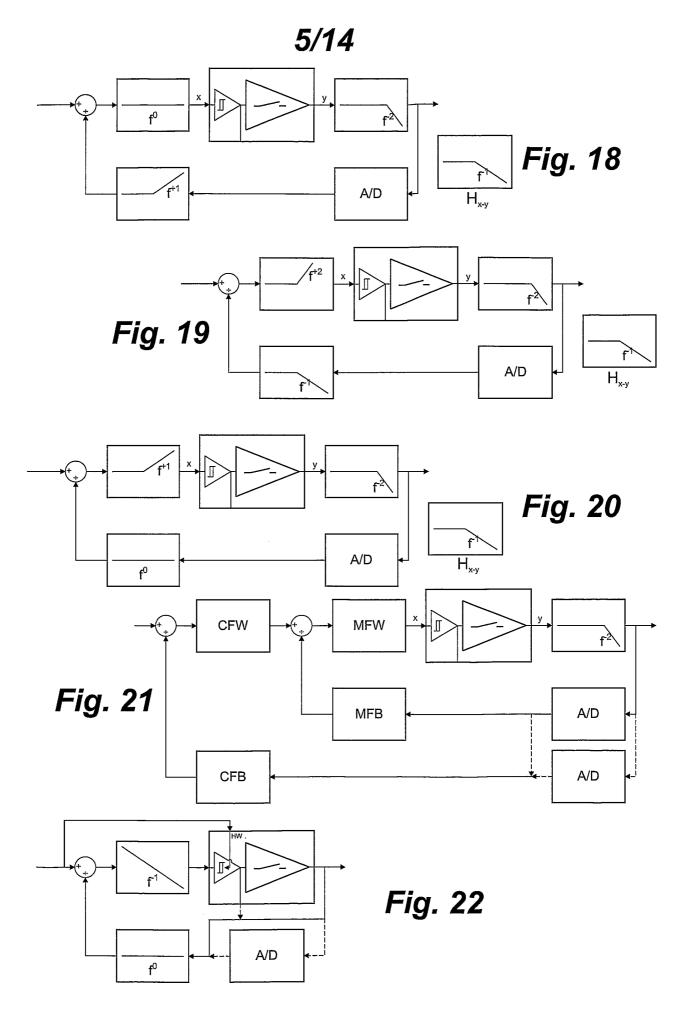

### 7.2.1 Mixed Signal Control

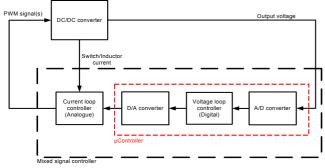

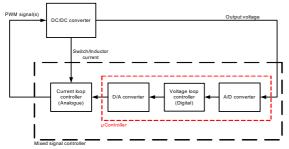

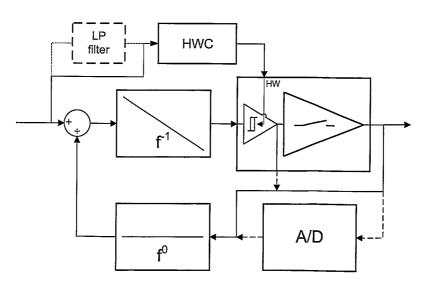

As the name suggests mixed signal control is not a purely digital control method. It involves combining analogue and digital control methods, typically with the purpose of reducing the complexity of the digital control system but also in order to improve system performance. The main idea is to remove the generation of the PWM signal from the digital domain and into the analogue domain, thereby removing the problem of limit cycling encountered in digital PWM generation due to poor resolution in the DPWM modulator.

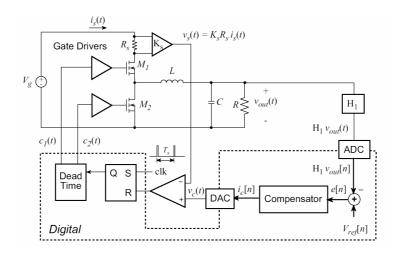

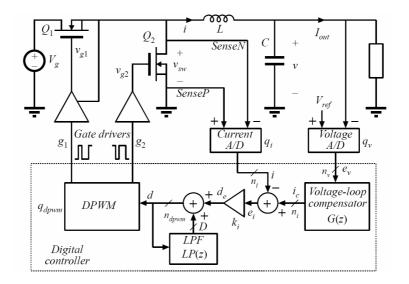

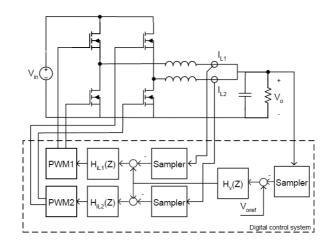

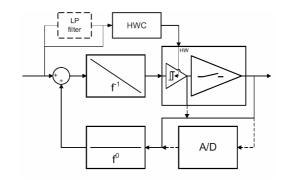

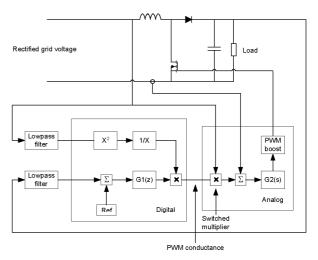

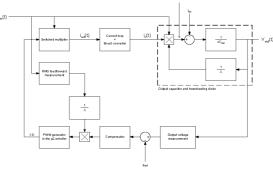

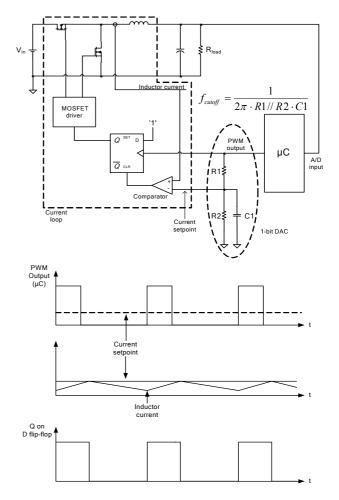

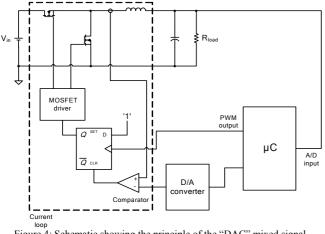

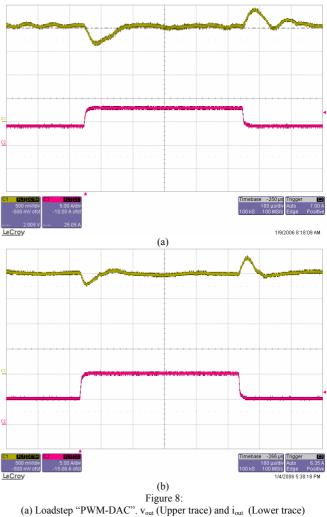

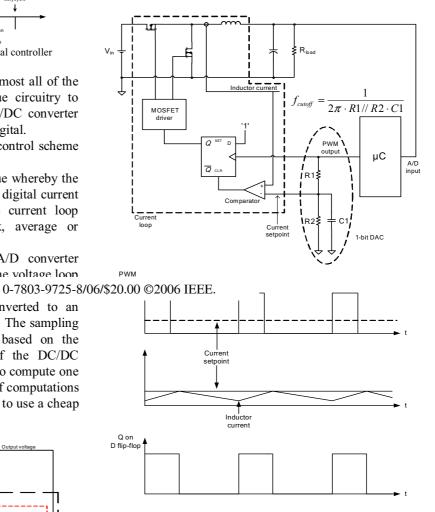

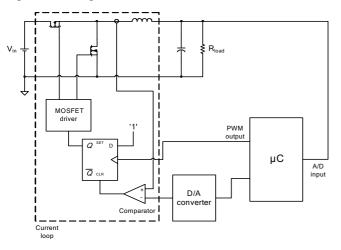

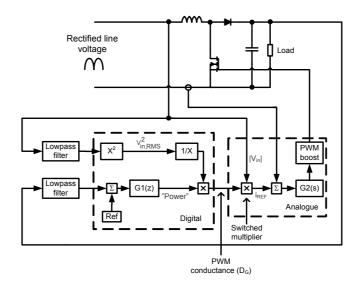

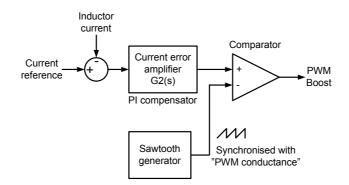

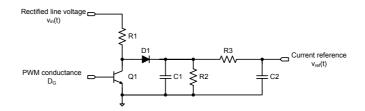

The most common mixed signal control method is a dual loop control system involving an analogue current control loop and a digital voltage control loop [18-20]. The current loop controls the inductor current in a typical switch-mode power converter, and it can be implemented as peak current mode control (see Fig. 7-7) [18], average current mode control [19] or some other current control scheme, e.g. hysteretic current mode control or one cycle control (OCC) [20].

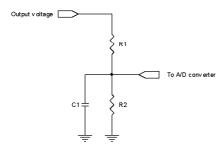

The benefit of implementing the current control loop with analogue circuitry is reduced limit cycling on the output voltage and a more simple digital control implementation. The problem of limit cycling is reduced because the analogue current loop theoretically has infinite PWM resolution as it has no clock to determine when the PWM signal can change from high to low or vice versa. The digital voltage loop is sampling the output voltage with an ADC and is calculating a reference value for the current loop. The current reference is converted into an analogue reference voltage by a Digital to Aanalogue Converter (DAC). The voltage loop will typically have a relatively simple control law such as a digital PID compensator.

Because the digital part of the controller only needs to sample the output voltage to implement a current mode control scheme it is possible to use a cheap A/D converter. The number of calculations that needs to be performed by the digital controller is also reduced since the current loop is analogue instead of digital.

Fig. 7-7 Typical mixed signal control scheme for a DC/DC converter [18]

Mixed signal controllers of the above-mentioned type have been proposed for virtually any type of application that switch-mode power converters are used in. The application range spans from Power Factor Correction circuits to low power DC/DC converters for Point of Load applications.

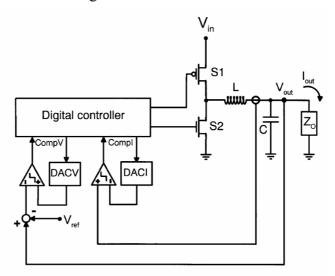

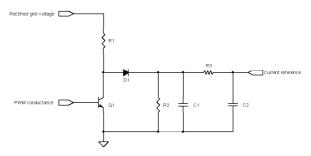

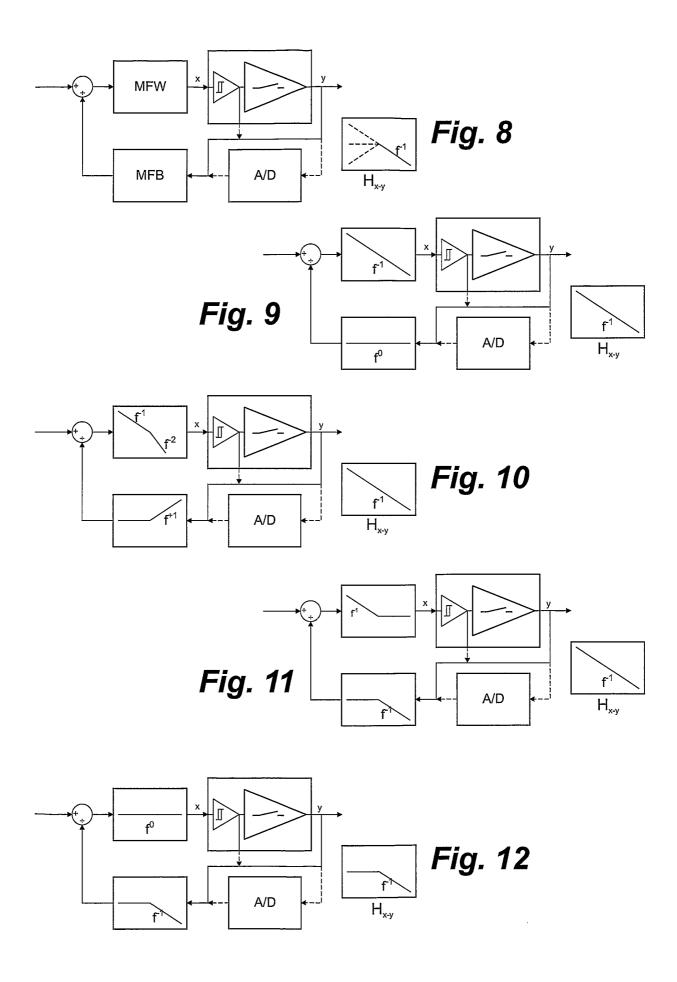

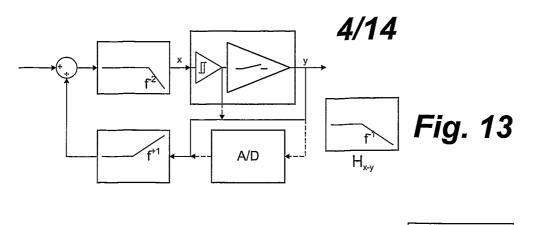

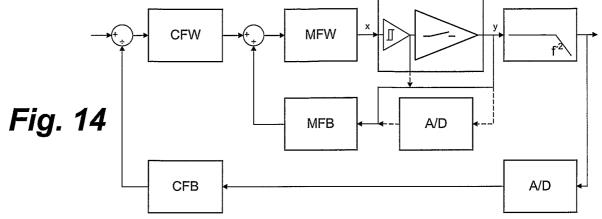

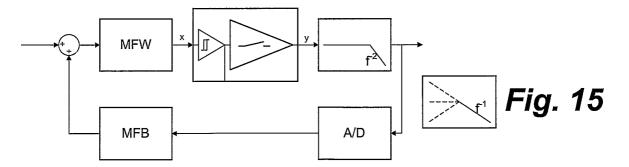

Other mixed signal control methods have been proposed with very different implementations and design criteria. One of the more interesting ideas is to change the system configuration dramatically so that sampling the output voltage and/or inductor current is avoided. An example of this is given in reference [21] (see Fig. 7-8), where the control method is built around two DACs that generate analogue reference voltages for the inductor current and output voltage error respectively. The current reference is a constant voltage whereas the voltage reference is a DC voltage superimposed by a ramp. The two MOSFETs, S1 and S2, are controlled by a very simple logic block that takes the two comparator outputs CompV and CompI as inputs. The digital logic is asynchronous in nature thus allowing the MOSFETs to be turned on and off at the exact instant the

comparator outputs change. The control method is referred to as synchronous/asynchronous because the control of the DACs is synchronous and the control of the MOSFETs is asynchronous. The same idea can be extended to pure voltage mode control and has been demonstrated on different converter topologies [22-24].

Other mixed signal control schemes have been proposed for special applications such as DC-DC converters with multiple outputs sharing a single inductor [25-27]. These methods differ in their implementation and the purpose of the design, but common to them is that the control scheme utilizes mixed signal methods.

Fig. 7-8 Mixed signal control scheme without an ADC [21]

## 7.2.2 Digital Voltage Mode Control

Digital voltage mode control is the simplest form of digital control for a switch-mode power converter. The main application for digital voltage mode control is non-isolated DC-DC converters, primarily VRMs and general purpose POLs.

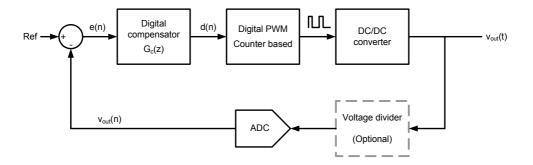

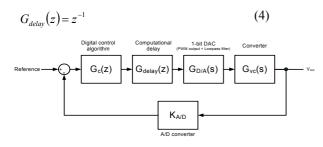

In this section digital voltage mode control is defined as a control system that samples the output voltage and based on that calculates the new duty command for the digital PWM module (see Fig. 7-9). All control schemes described in this section are based on linear control laws (for non-linear control methods see section 7.2.4).

Fig. 7-9 Block diagram for a basic VMC control scheme for a DC/DC converter

The most common voltage mode control scheme is to implement the compensator  $G_c(z)$  as a PID controller emulating the most common analogue control scheme [28-32]. The digital PID compensator has a transfer function, which is typically defined in the z-domain by equation 7.2. There are some slight differences in the definition of the transfer function for digital PID compensator, where some papers add one or two extra poles at high frequencies.

$$G_{c}(z) = \frac{b_{0} + b_{1} \cdot z^{-1} + b_{2} \cdot z^{-2}}{1 - z^{-1}}$$

(7.2)

The implementation of the voltage mode control scheme in references [28] to [32] differs in the type of digital hardware and ADC that is used, but the basic control scheme is the same.

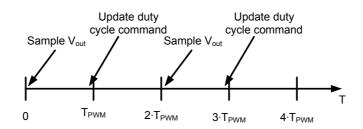

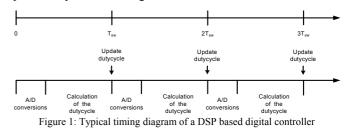

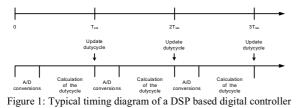

The sampling frequency of the ADC has a large impact on the control loop bandwidth of the digitally controlled DC/DC converter. Traditionally the sampling frequency is equal to the switching frequency of the DC/DC converter and the output voltage is sampled at the beginning of each PWM period. The digital controller calculates the new duty cycle and updates the duty cycle command for the DPWM modulator at the beginning of the next PWM period. The limitation in sampling frequency and the delay caused by the traditional sampling scheme will limit the control loop bandwidth that can be achieved for a given converter.

To increase the control loop bandwidth it has been proposed to sample the output voltage at a faster rate than the switching frequency [31-34]. In multiphase converters the sampling frequency can be equal to the switching frequency of each phase multiplied by the number of phases in the converter, since the duty cycle can be updated for the individual phases at the beginning of the switching period of every phase.

Other implementations of digital voltage mode control can be found in references [35] through [39].

#### 7.2.3 Digital Current Mode Control

Digital current mode control is a dual loop control scheme which samples both the output voltage and the inductor current. The voltage loop calculates a reference current for the current loop and the current loop calculates the duty cycle command to achieve the correct inductor current. Digital current mode control can be implemented in a number ways, e.g. peak or average current mode control, depending on how the inductor current is sampled [40]. Reference 40 gives an overview of predictive current mode control techniques. The idea of predictive current mode control is that the digital controller predicts what the duty cycle should be in the following PWM period in order to obtain a certain inductor current at the end of the following PWM period. Almost every digital current in one switching cycle, but it can only change the duty cycle in the following switching cycle. Fig. 7-10 shows a schematic of a typical implementation of a predictive current mode control scheme.

Predictive digital current mode control is most often implemented as average current mode control [41-49]. The digital controller samples the average inductor by sampling the current in the middle of either the ON- or OFF-time of the PWM signal controlling the switch-mode converter [41]. In that way the digital controller can sample the average current without sampling the current at a much higher rate than the switching frequency. Another advantage of the proposed sampling scheme is that there will be no switching noise on the current measurement since the ADC samples the current in the middle of either the ON- or OFF-period.

Fig. 7-10 Digital current mode control implementation [48]

Predictive current mode control has been implemented in Digital Signal Processors (DSPs), FPGAs and custom designed ICs. The most common approach is to use a DSP because the DSP is easy to program and it has a number of A/D inputs, which makes it possible to sample both the output voltage and inductor current [41-46]. The current loop is most often realised with a PI- or PID-compensator and the voltage loop as a PI-controller. The number of calculations that must be performed to implement the current loop will in many cases limit the switching frequency that it is possible to achieve for a certain DSP. The limitation is a result of the sampling point of the ADC sampling the current is moving in time as described above. As a result of this the time the DSP has to calculate the new duty cycle command varies with the duty cycle of the PWM signal, which means that a certain minimum calculation time must be allowed in order for the digital controller to complete the calculations. That can easily achieved by reducing the switching frequency. The switching frequency for predictive current control schemes implemented in a DSP are reported up to 200 kHz, which makes it suitable for Power Factor Correction (PFC) applications and high power DC/DC converters.

If the predictive current mode control scheme is implemented in an FPGA or an Application Specific Integrated Circuit (ASIC) the switching frequency can be increased. It is, however, questionable whether the digital current mode control is better than voltage mode control for DC/DC converters with very high switching frequencies, since the predictive current mode control scheme is basically an average current mode control scheme. The current loop in average current mode control typically has a bandwidth that is 5 to 10 times lower than the switching frequency. The requirements for converters operating at high switching frequencies is typically high control loop bandwidth for the output voltage and generally it will therefore be a better choice to use a pure voltage mode control scheme.

Predictive current control methods calculates the duty cycle command based on the sampled current and the parameters of the switch-mode converter, such as the inductor size and input voltage. The predictive current control scheme will therefore only be operating optimally when the actual converter parameters match the parameters used in the design of the control law. A simplified digital current mode control technique has been proposed in references 50 and 51. This technique alleviates some of the problems related to predictive

current mode control as described above. The control scheme is very simple with a proportional compensator in the current loop and can be used in both peak and average current mode control. Because of the simple structure of the control scheme it can also be used to control DC-DC converters with high switching frequency.

A derivation of an OCC control scheme for the inductor current is to use a very fast ADC, which samples the inductor current at a much faster rate than the switching frequency and digitally integrates the sampled current [52]. The PWM signal is generated by comparing the integrated inductor current with a digital current reference which is calculated by the voltage loop. If the integrated inductor current is smaller than the current reference the PWM signal is high. Once the sampled current is equal to the reference the PWM signal is set to low. The integrator is reset to zero at the beginning of each switching period. The control scheme just described is a quite expensive solution since it needs an ADC that samples the current at 20 Million Samples Per Second (MSPS) to control a converter with a switching frequency of just 50 kHz.

## 7.2.4 Non-linear Control

Digital control of switch-mode converters with linear control methods will generally not be able to achieve as high a control bandwidth as can be achieved with analogue control. The main reason is that the sampling frequency of the digital controller is equal to the switching frequency and the delays of the digital implementation.

One way to improve the transient response is through non-linear control techniques. Non-linear control is in this context defined as a control scheme where the control law changes as a function of the controlled parameter, e.g. the output voltage error. Non-linear control is therefore a very broad definition that includes a number of different implementations.

The fastest way to detect a change in the load current is to measure the output capacitor current, since a change in load current will be immediately reflected in the capacitor current. Measuring the capacitor current is however impracticable in high performance DC/DC converters since a small sense resistor is typically inserted in series with the capacitor, which will increase the output voltage ripple and power losses in the converter. Instead of measuring the capacitor current it is possible to estimate it by sampling the output voltage at a faster rate than the switching frequency and integrating the sampled output voltage error [53]. Alternatively the capacitor current can be estimated by

connecting an LCR-network in parallel with the capacitor, which has a characteristic impedance that is similar to the characteristic impedance of the capacitor, and measuring the current in LCR-network [55]. Once the capacitor current estimator has detected the load current change, the next step is to apply a sequence of PWM signals that restores the output voltage to the steady state value set by the voltage reference.

Reference 53 proposes the Proximate Time-Optimal Digital (PTOD) control scheme, which uses switching surface analysis to reach the steady state output voltage in the shortest time possible. The implementation of the PTOD scheme is a simple state machine that takes over the generation of the PWM signal from a linear PID compensator combined with a DPWM block. The implementation of PTOD scheme is so simple that it can easily be added to any linear control scheme and the performance of the DC/DC converter is dramatically increased during transient load conditions. The only drawback is that the output voltage needs to be sampled at a very high frequency to be able to estimate the capacitor current accurately.

Another way of achieving that the output voltage is returned to its steady state condition in the shortest possible time and with the least overshoot is by changing the control law if the output voltage error exceeds a preset limit [54]. The non-linear control scheme is designed for a Buck converter and the idea is to set the PWM signal to '1' if the output voltage is lower than the lower boundary. The period of time the PWM signal is high is calculated based on an estimation of the output current. Next the PWM signal is set to '0' for the period of time that is required to return the output voltage to its steady state value. This non-linear control requires a large number of computations to find the correct ONand OFF-times to achieve the optimal response to a step change in the load current.

During the transient condition the non-linear control scheme of reference 55 switches from linear voltage mode control to hysteretic current control for the estimated capacitor current. The control scheme requires that the estimated capacitor current is sampled at a very fast rate to achieve precise hysteretic control of the capacitor current.

The transient response of multiphase interleaved DC/DC converters can be improved by saturating the PWM signals of all phases to either '0' or '1' if the output exceeds an upper or lower threshold error voltage respectively [56]. Once the output voltage is within the threshold voltage the control scheme returns to interleaved operation and the linear control law resumes control of the duty cycle command.

A different approach to non-linear control is to let a PID compensator operate with a variable gain, which depends on the magnitude of the output voltage error [57]. The larger the output voltage error is, the larger is the gain of the PID compensator. The choice of compensator gain may theoretically result in an unstable system for a large output voltage error but because the error will converge towards zero the system will be stable in practice.

## 7.3 Digital Hardware Implementations

Cost and performance of a digital controller for a switch-mode power converter is greatly influenced by the choice of digital hardware used to implement the digital controller. This section aims to give a short description of the three main types of digital hardware used in digital control of switch-mode converters and mention some of the advantages and limitations of the different solutions.

### 7.3.1 Microcontrollers

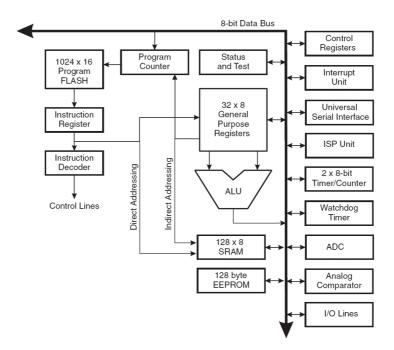

Microcontrollers have been around for several decades and have been used in almost any kind of industrial and consumer electronics. The term microcontroller has been used to describe anything from simple 8-bit controllers with few I/O ports to large 32-bit processors with many I/O ports, and advanced features such as a hardware multiplier for faster calculations. A microcontroller is in this thesis defined as a low cost digital controller with an 8- or 16-bit databus including features such as PWM outputs and A/D converters. The clock frequency of this type of devices is typically lower than or equal to 40 MHz, which limits the number of calculations that can be performed in the software algorithm that performs the control law for the switch-mode converter. The DPWM module in microcontrollers of this class is in general counter based with no extra features to enhance the DPWM resolution.

Microcontrollers can also be used to add extra functionality to switch-mode power supplies with an analogue control circuit [58-59]. In this case the microcontroller does not perform any real-time control of the output voltage or the inductor current, but it is used to supervise and act as controller on a system level. The microcontroller can also be used to add features such as current sharing between converters connected in parallel and to set an external voltage reference for the power supply [58].

The microcontroller adds functionality that could be added with analogue circuitry as well, but it would be more difficult to do so with analogue circuitry.

The microcontroller is reprogrammable, which makes it possible to change the functionality without having to change the hardware design.

The microcontroller can additionally be used to improve system performance by introducing a precise reference to the analogue control circuit [59] thus enhancing system performance. In reference 59 the microcontroller supplies a perfect sine wave reference for the current loop of a PFC to ensure low input current distortion.

None of the above-mentioned features, which can be added with a microcontroller, are included in the definition digital control, but they are examples of how microcontrollers are most often used in power electronics.

Actual real-time digital control of switch-mode power converters have been implemented in microcontrollers with varying results [19, 60-62]. Reference 60 describes a digital voltage mode controller implemented in a microcontroller from Microchip. The control law is a PID compensator implemented with gains that can only be selected as powers of 2. The time it takes to complete the computations necessary to implement the PID compensator is between 18 and 28 µs and the sampling frequency is limited to 20 kHz for a converter with a switching frequency of 78 kHz. Because of the poor adjustability of the PID compensator coefficients and the low sampling frequency, the transient response of the Buck converter tested in the reference is not especially fast. Another issue concerning the design of a voltage mode control scheme in a microcontroller is the low DPWM resolution due to the low clock frequency, which can cause limit cycling.

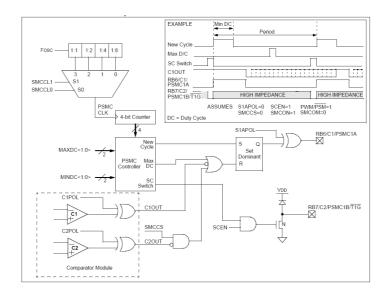

References 19, 61 and 62 present different mixed-signal controls schemes based on a microcontroller and some simple analogue hardware. The microcontroller used in all three designs is the PIC16C782 from Microchip [63], which includes a Programmable Switch Mode Controller (PSMC). The PSMC (see Fig. 7-11) includes two comparators, which can be used to compare the inductor current with the current reference, which can be set by an 8-bit DAC that is also included in the PIC16C782. The switching frequency can take on values equal to the clock frequency divided by powers of 2. The maximum and minimum duty cycle that the PSMC can generate is programmable by two 2-bit registers.

Fig. 7-11 PIC16C782 Programmable Switch Mode Controller [63]

The voltage loop of the mixed signal control scheme is implemented in software in the PIC16C782 and the sampling frequency ranges from 31 to 52 kHz in the cited references. The control laws, which are either a PI compensator [19, 61] or a Fuzzy Logic control law, have been implemented with 8 bit accuracy and all multiplications are performed by bit shifting.

Due to the low sampling frequency and the poor adjustability of the PI compensator or Fuzzy Logic control law the microcontroller based solutions published this far are only suitable for low bandwidth applications.

#### 7.3.2 Digital Signal Processors/Controllers (DSPs/DSCs)

Digital Signal Processors have been used to control power electronics for many years. Typical applications have been motor drives, uninterruptible power supplies and other power converters connected to the utility grid.

Common for these applications is that the cost of the DSP is only a fraction of the total cost and the complexity of the control algorithm is so complex that it requires a large number of calculations. The DSP will typically be quite expensive compared to the total cost of the power supply for most offline SMPSs and DC/DC power supplies.

First of all it is important to define what is understood by a DSP and why the term digital signal controller (DSC) is more appropriate for the kind of device used in digital control of switch-mode power converters.

A DSP is traditionally a component designed to perform a large number of arithmetic operations in a very short time. Typical applications for DSPs have been signal processing in audio and audio/visual applications implementing finite impulse response (FIR) filters and infinite impulse response (IIR) filters.

Filter algorithms depend on two types of mathematical operations, multiplication and addition, and the DSP is designed to perform the filter algorithm effectively. A multiplier/accumulator (MAC) module that can perform one multiplication and one addition in a single clock cycle is therefore an integral part of the DSP. The DSP also has large data and program memory areas to enable advanced filter algorithms.

The traditional DSP is very good at running filter algorithms for high order digital filters, but it lacks other features such as logic operations to compare numbers or single bits. DSPs typically do not include an ADC module, which has to be added as an external component.

The DSC on the other hand is a hybrid between a microcontroller and a DSP. In many cases the DSC also includes a MAC module, but in some devices it only has a dedicated hardware multiplier module that can perform a multiplication in one or two clock cycles. Furthermore the DSC includes other features like a full set of logic operations and in most cases several timers to support multiple PWM outputs and high performance ADCs. Different manufacturers of DSCs target different applications and the term DSC covers quite a large range of devices. A few examples of typical AC/DC and DC/DC converters controlled by a DSP or DSC will be described to give an idea of what the strength of the DSP/DSC is.

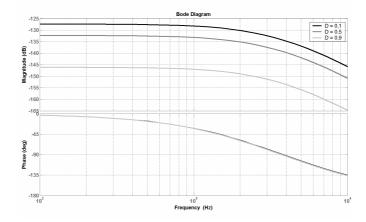

The DSP/DSC is well suited for control schemes including several loops, e.g. a current and a voltage loop, and perhaps extra signal processing to enhance system performance. A good example of that is a digital control scheme for a PFC with high control loop bandwidth [41]. The control scheme includes a current and a voltage loop plus an additional comb filter that attenuates the output voltage ripple in the output voltage feedback path. The comb filter has an order of 41 in this example and it is only practicable to implement a filter of that order in a DSP. Another example of a digital control scheme for a PFC implemented in a DSP is reference 44.

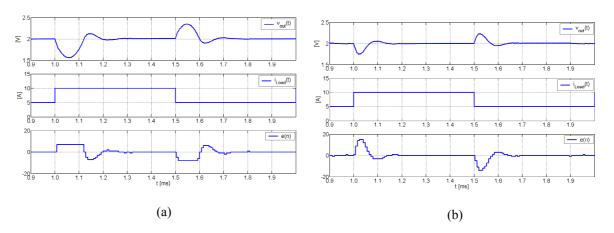

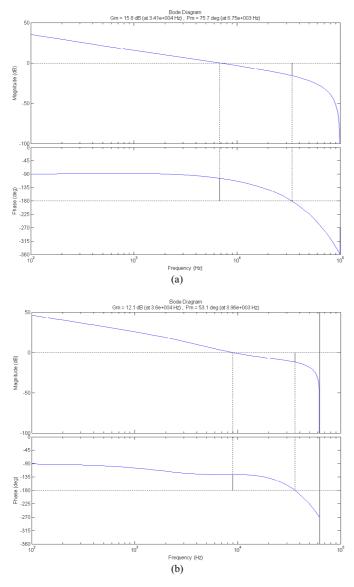

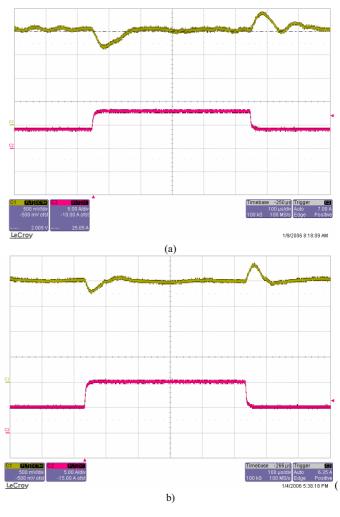

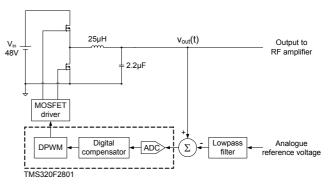

A simple voltage mode control scheme for a DC/DC Buck converter, which is based on a DSC, is described in reference 28. The advantage of using the DSC, which in this case is a DSC from the TMS320F280x family from Texas Instruments, is that it runs at a much higher clock frequency than a typical microcontroller and also that a MAC module is part of the DSC. The MAC module combined with the high clock frequency allows the DSC to sample the output voltage at the same rate as the converter is switching, i.e. 250 kHz in reference [28], which makes it possible to achieve higher control loop bandwidth and faster transient response than what is possible with a microcontroller. It should however be noted that the DSC is capable of much more than controlling a single Buck converter and that it is therefore an expensive solution in this kind of application.

#### 7.3.3 Field Programmable Arrays / Custom ICs

Both microcontrollers and DSCs are general purpose digital devices that can be used in a number of applications. Some of those devices have been designed with switch-mode converters as the primary application, but not for a specific converter topology or converter application. It follows from this that the manufacturer of a power supply almost certainly buys a device that can perform more operations than what is necessary in a specific product. The result is that the cost of the power supply is higher than strictly necessary.

Customised digital control ICs are increasingly popular in both academic research and the industry because they can offer a solution that is targeted for a specific application. The number of solutions that have been presented in scientific papers and introduced by semiconductor manufacturers is quite large and the solutions are very diverse. The subject is therefore divided into selected groups of solutions to highlight some of the trends.

Solutions programmed in FPGAs are included in this description because FPGA implementations presented in papers are used to show a new control method that should be implemented in an IC if the control method was to be sold commercially. FPGAs are good for prototyping but they are too big and expensive to be considered for use in low cost switch-mode power supplies.

#### 7.3.3.1 PID compensator implementations

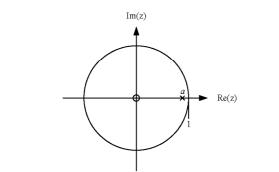

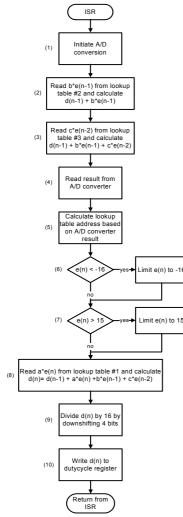

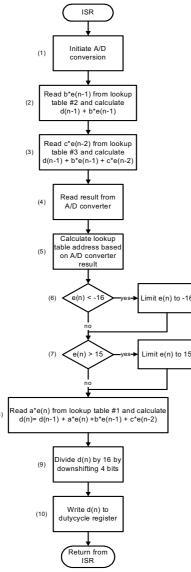

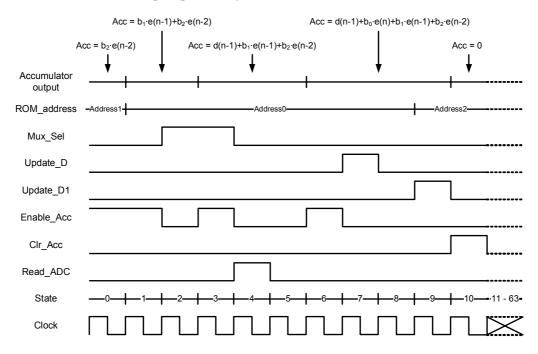

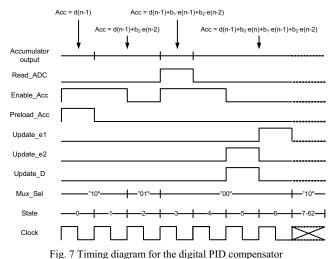

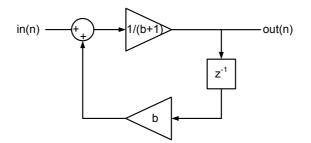

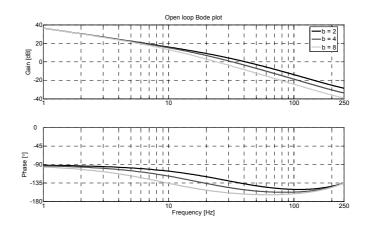

The digital PID compensator is the most common control law used in digital control for switch-mode converters. The digital PID compensator is actually an IIR filter and can be represented by the general difference equation 7.3.

$$d(n) = a_1 \cdot d(n-1) + \dots + a_i \cdot d(n-i) + b_0 \cdot e(n) + b_1 \cdot e(n-1) + b_j \cdot e(n-j)$$

(7.3)

where *d* is the duty cycle command for the DPWM, *e* is the error signal, *n* is the current sample number and *i* and *j* represents the number of poles and zeroes of the IIR filter. For the typical PID compensator (see equation 7.2) *i* is equal to 1 and *j* is equal to 2.

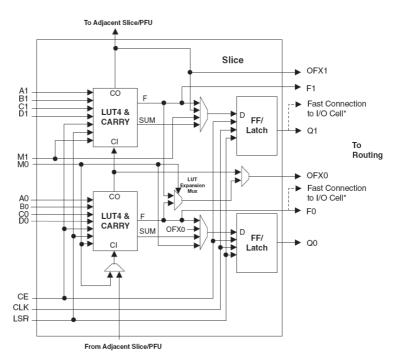

In a DSP/DSC the difference equation is solved with the MAC module, which performs the necessary multiplications and additions and the same method can be used in a custom IC [64-65]. Reference 64 presents a fixed-point 16-bit DSP core that is custom designed for digital control of switch-mode converters. Unlike a general purpose DSP/DSC the customised DSP core has a very limited instruction set (less than 30 instructions) which makes it a much simpler task to program the control algorithm. The DSP core has a  $16 \times 16$  bit hardware multiplier and a 32-bit ALU to perform the MAC operations. The gate count of the custom designed DSP core is small because of the limited instruction set thus reducing the physical size and power consumption.

An even simpler DSP core have been described in reference 65 to further reduce the size and cost of the digital control IC. That design utilizes an asymmetrical hardware multiplier with different word-lengths for the two inputs. The idea is that one of the input signals to the multiplier can be represented by a small number of bits, e.g. the error signal, whereas the other signal, e.g. the coefficient  $b_n$ , must be represented with a higher number of bits. The complexity and thereby the physical size of the hardware multiplier is reduced by reducing the number of bits of one input and ultimately the cost of the digital control IC is reduced.

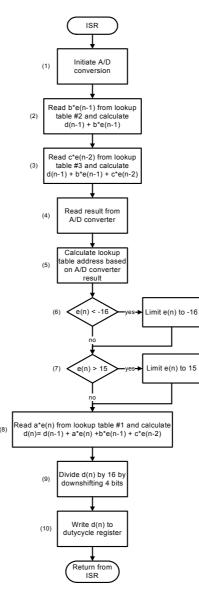

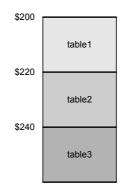

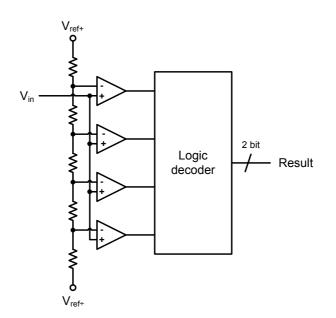

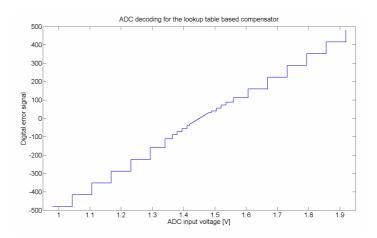

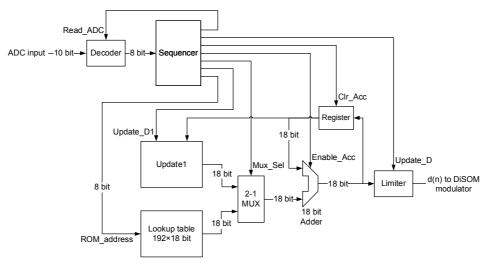

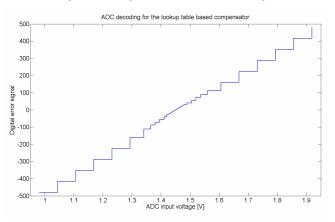

The lookup table based design is an alternative to the MAC based DSP core just described [66]. Instead of using a hardware multiplier block, which can be a quite large and expensive block in an IC design, the results of all possible multiplications can be calculated in advance and stored in a lookup table. The result of the multiplication of any error value and corresponding compensator coefficient can be read from memory during the calculation of the difference equation defining the PID compensator. The amount of memory that is allocated for the lookup table depends on the number of error values, which is determined by the ADC resolution and the required word-length for the compensator coefficients. The implementation of flash memory in an IC may be more expensive than having a larger amount of digital logic, e.g. a hardware multiplier, and there will be a trade-off that needs to taken into consideration when choosing which solution to use. A more critical issue in connection with the lookup table based design is that it is much harder to change the compensator coefficients solution to use flash methods and the registers storing the complete lookup table has to be updated rather than just a few registers storing the compensator coefficients.

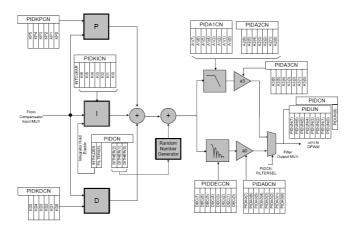

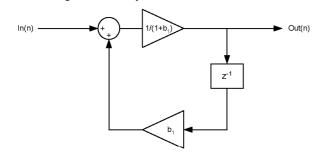

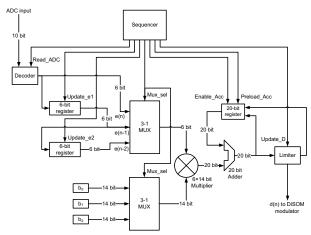

A third way of realising a PID compensator is to split the compensator transfer function into three terms, i.e. a proportional (P), an integral (I) and a derivative (D) term, that are solved separately and in parallel as shown in Fig. 7-12 [67]. The time it takes to compute the new duty cycle command is very short in this PID compensator implementation because the three terms are computed simultaneously.

Fig. 7-12 PID compensator wit separate P, I and D terms [67]

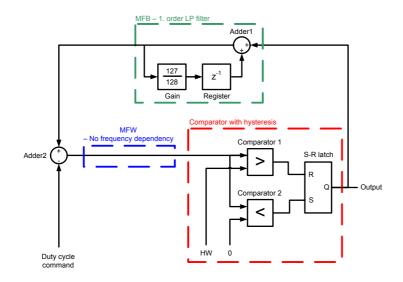

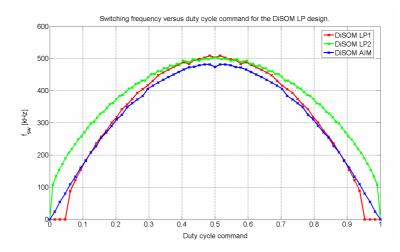

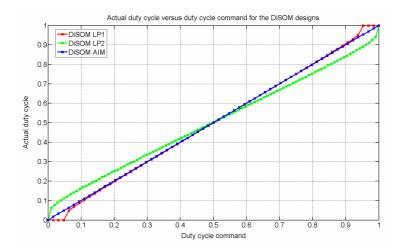

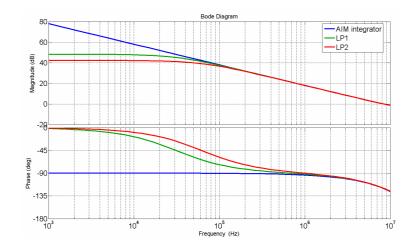

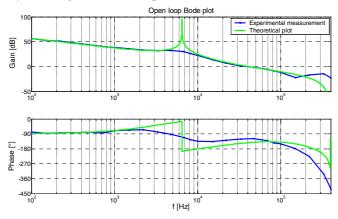

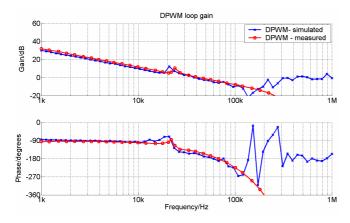

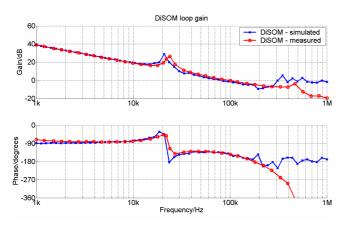

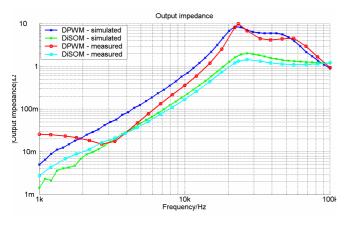

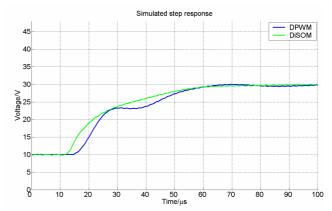

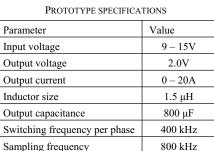

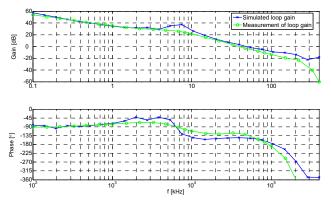

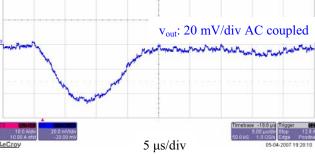

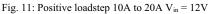

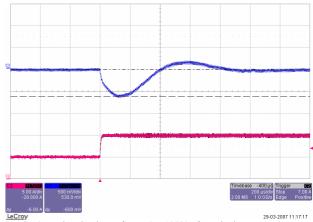

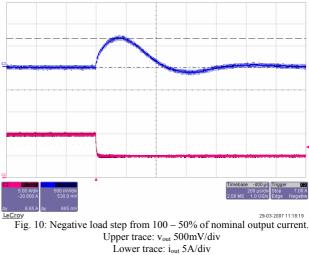

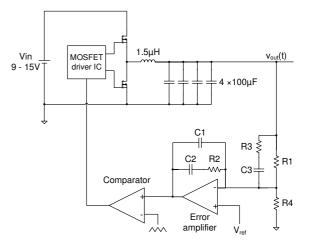

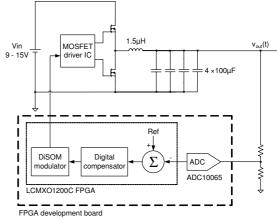

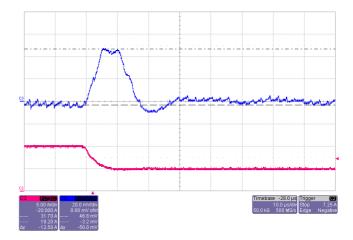

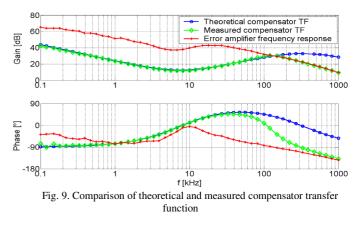

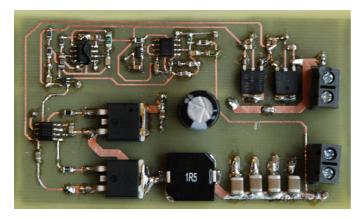

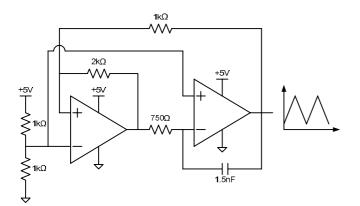

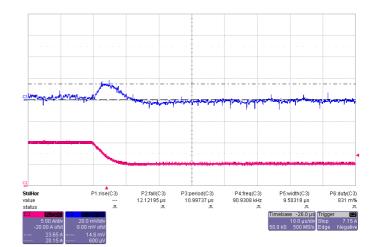

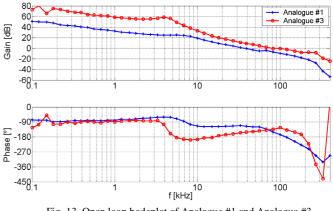

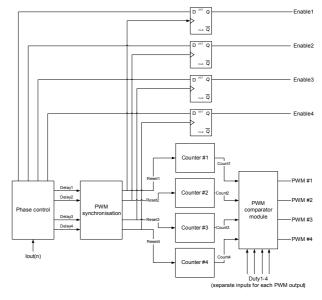

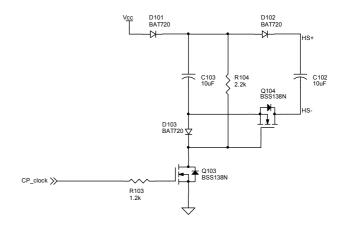

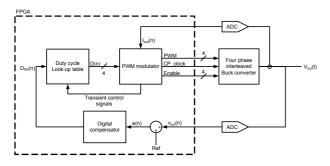

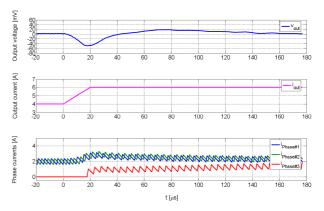

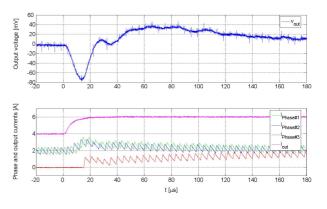

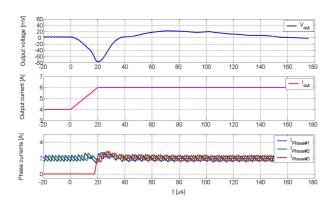

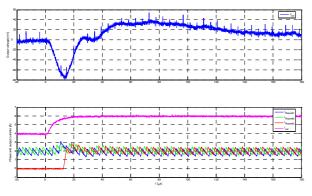

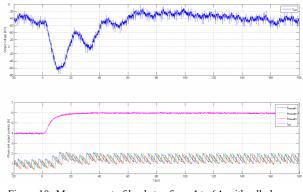

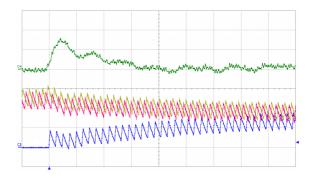

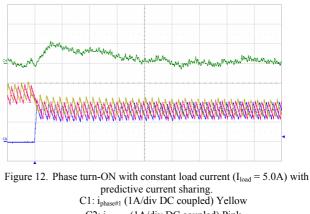

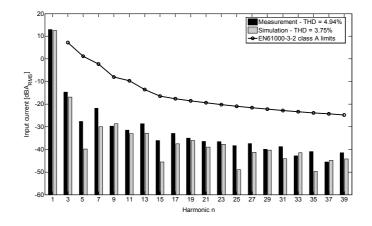

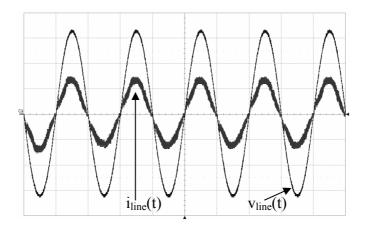

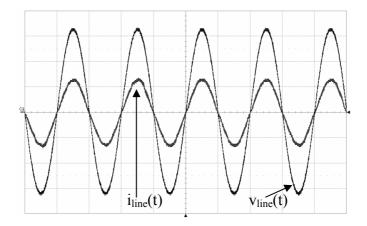

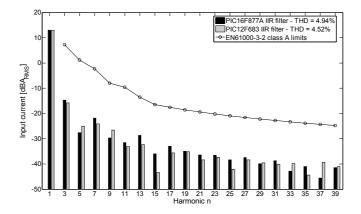

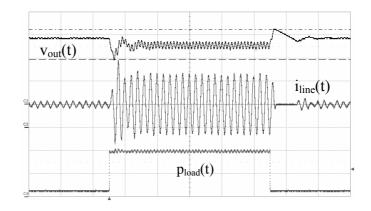

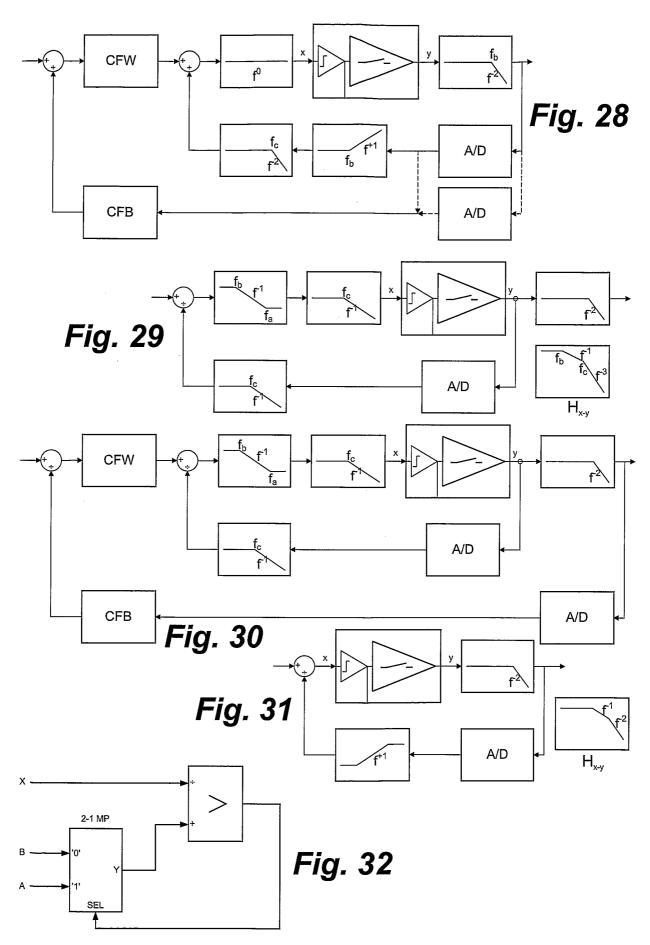

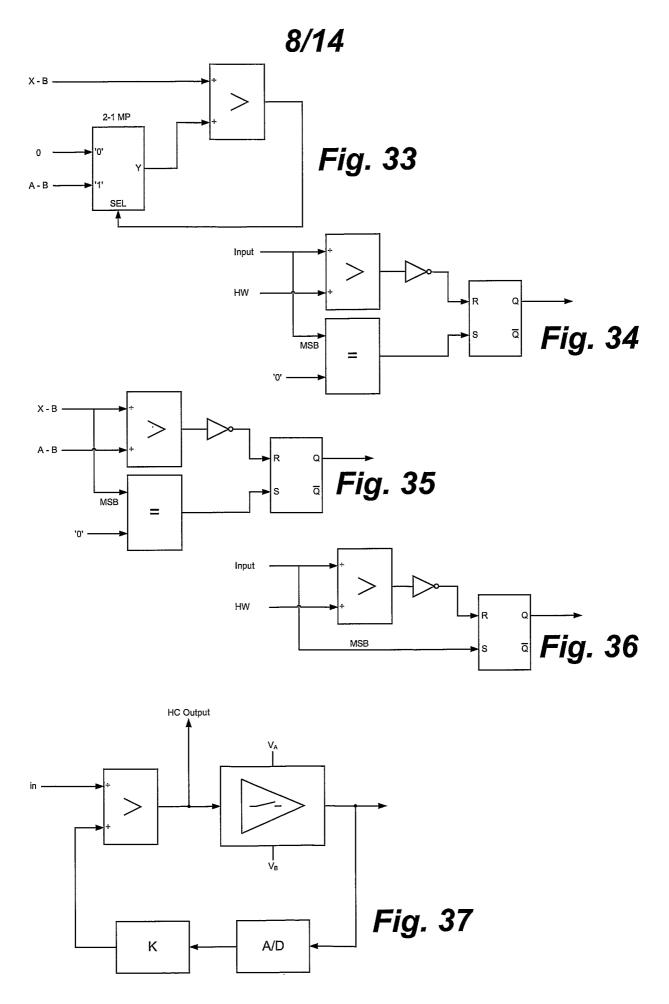

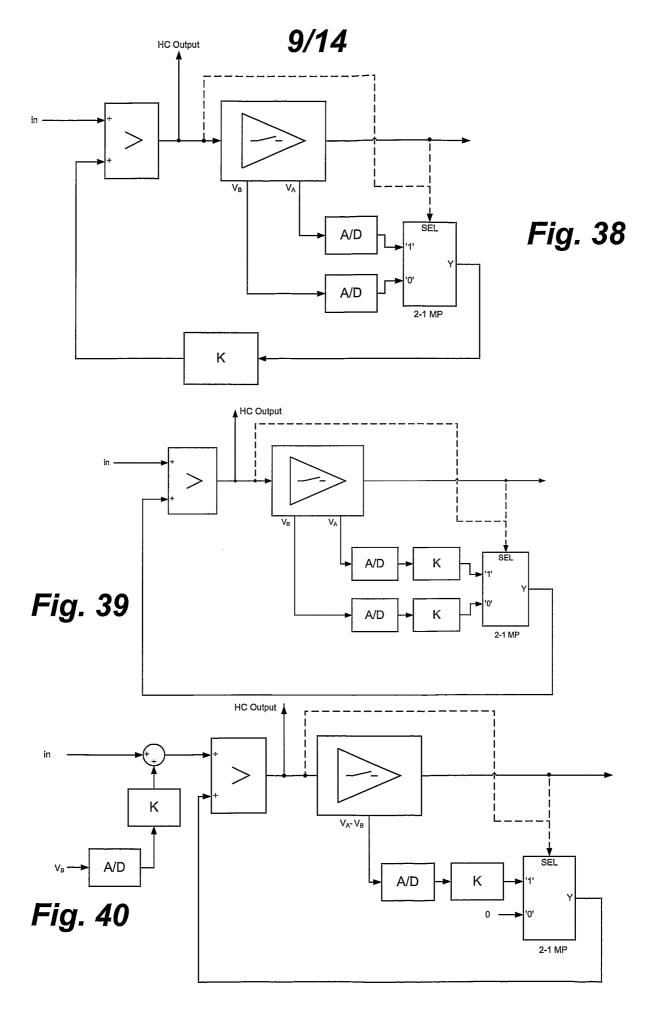

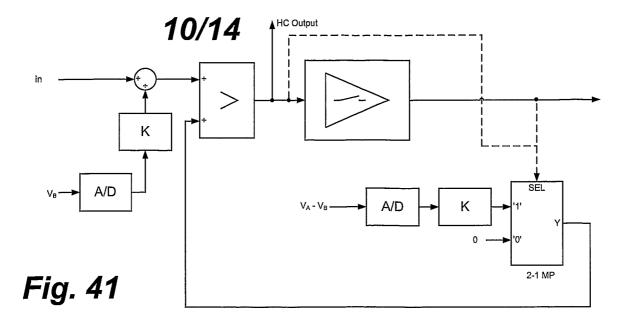

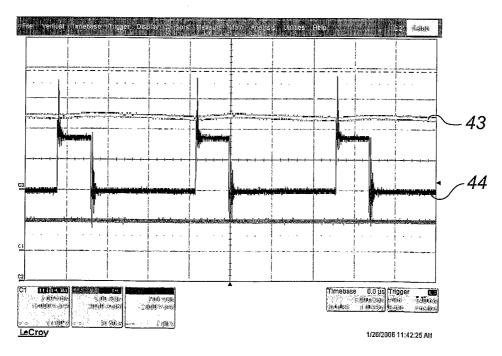

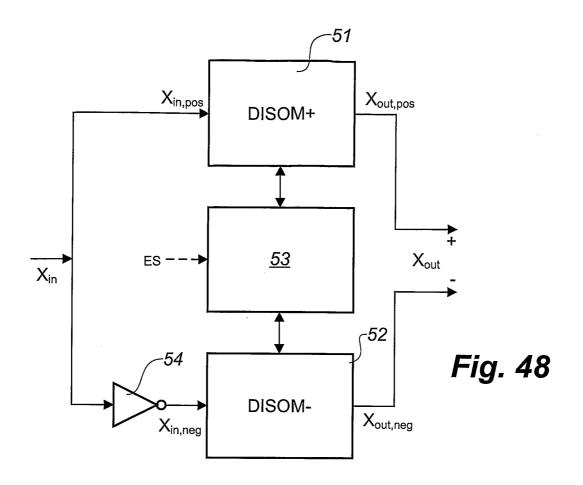

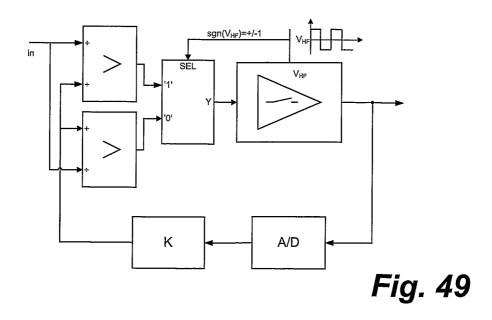

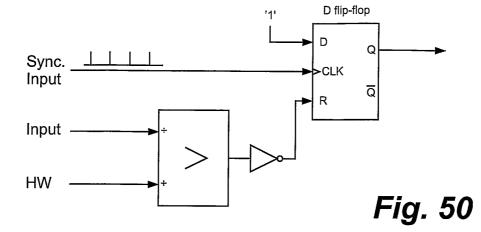

#### 7.3.3.2 Multimode controller ICs