brought to you by I CORE

### Technical University of Denmark

### Language-based Security for VHDL

Tolstrup, Terkel Kristian; Nielson, Hanne Riis; Nielson, Flemming

Publication date: 2007

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Tolstrup, T. K., Nielson, H. R., & Nielson, F. (2007). Language-based Security for VHDL. (IMM-PHD; No. 174).

### DTU Library

Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Language-based Security for VHDL

Terkel K. Tolstrup

Kongens Lyngby 2006 IMM-PHD-2006-174

Technical University of Denmark Informatics and Mathematical Modelling Building 321, DK-2800 Kongens Lyngby, Denmark Phone +45 45253351, Fax +45 45882673 reception@imm.dtu.dk

IMM-PHD: ISSN 0909-3192

# Summary

The need for reliable performance of computerised systems is well-known, yet the security verification of hardware systems is often none-existing or applied in an ad-hoc manner. To overcome this issue, standards such as the *Common Criteria* has been successful in listing points of attention for a thorough investigation of a system. Hence in this thesis it is investigated how language-based security techniques can be adapted and applied to hardware specifications. The focus of the investigation is on the information flow security that is required by the standard. Information flow security provides a strong notion of end-to-end security in computing systems. However sometimes the policies for information flow security are limited in their expressive power, and this complicates the matter of specifying policies even for simple systems. These limitations often become apparent in contexts where confidential information is released under specific conditions.

This thesis presents a novel policy language for expressing permissible information flow using expressive constraints on the execution traces for programs. Based on the policy language a security property is proposed and shown to be a generalised intransitive non-interference condition. The security property is defined on a fragment of the hardware description language VHDL that is suitable for implementing the *Advanced Encryption Standard* algorithm.

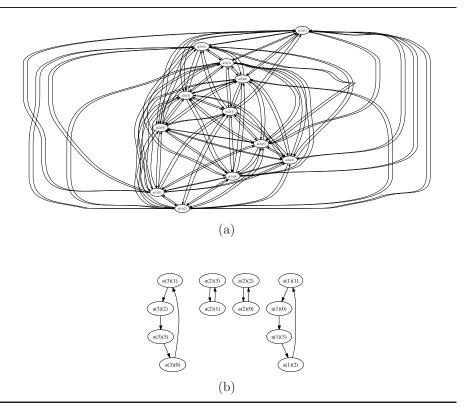

The means to verify the property is provided in the terms of a static information flow analysis. The goal of the analysis is to identify the entire information flow through the VHDL program. The result of the analysis is presented as a non-transitive directed graph that connects those nodes (representing either variables or signals) where an information flow might occur. The approach is compared to traditional approaches and shown to allow for a greater precision.

Practical implementations of embedded systems are vulnerable to side channel attacks. In particular timing channels have had a great impact on the security

verification of algorithms for cryptography. In order to address this another security property stating the absence of timing channels is presented. Again, verification is provided by a static analysis, that identifies the timing behaviour of a program. This analysis consists of a type system that identifies the delay between when a value enters the system and when it leaves it again. Programs accepted by our analysis are shown to have no timing channels.

# Resumé

Vigtigheden af pålidelig opførsel i computersystemer er velkendt, men stadigvæk bliver sikkerhedsverifikation af hardware-systemer ofte ikke udført, eller verifikationen bliver udført på en ustruktureret facon. For at overkomme dette problem, har standarder som Common Criteria været succesfulde ved at fremhæve vigtige punkter for en fuldstændig undersøgelse af et system. Derfor vil denne afhandling undersøge, hvorledes teknikker inden for sprog-baseret sikkerhed kan tilpasses og anvendes på hardware specifikationer. Fokus i denne undersøgelse vil være på information flow sikkerhed som det kræves af standarden. Information flow sikkerhed giver en stærk opfattelse af ende-til-ende sikkerhed i et computersystem. Imidlertid sker det, at politiker for information flow sikkerhed opgaven omkring at angive en politik for endda simple systemer. Disse begrænsninger bliver ofte fremhævet af systemer, hvor hemmelige oplysninger bliver frigivet ved opfyldelse af klare krav.

Denne afhandling præsenterer et nyt sprog for politiker, der muliggør at udtrykke information flow, der bliver tilladt under angivne krav til eksekveringssekvensen ved afvikling af programmet. Baseret på sproget for politikerne foreslås en sikkerhedsegenskab, som vises at generaliserer intransitiv non-interference egenskaben. Sikkerhedsegenskaben defineres på et fragment af hardware beskrivelses sproget VHDL, der er tilstrækkeligt til at implementere en Advanced Encryption Standard algoritme.

En information flow analyse defineres efterfølgende. Målet med analysen er at identificere, hvorledes information flyder gennem hele VHDL programmet. Resultatet af analysen er en intransitiv orienteret graf, der forbinder de knuder (repræsenterende enten variable eller signaler), hvor informationen eventuelt kan flyde. Denne tilgang sammenlignes med traditionelle metoder og vises at muliggøre en analyse med større præcision.

Virkelige implementationer af indlejrede systemer er sårbare over for angreb gennem side channels. Specielt har side channels stor indflydelse på sikkerhedsverifikationen af kryptografiskealgoritmer. Derfor foreslås en sikkerhedsegenskab, der angiver, hvornår et system er fri for timing channels. En statisk analyse til at identificere den tidsmæssige opførsel af et program bliver også præsenteret. Analysen består af et type system, der identificerer forsinkelser, mellem at en værdi kommer ind i systemet, og indtil den forlader systemer igen. Det bevises at programmer, der accepteres af analysen, ikke indeholder timing channels.

# **Preface**

Whether you take the doughnut hole as a blank space or as an entity unto itself is a purely metaphysical question and does not affect the taste of the doughnut one bit

— Haruki Murakami

This thesis was prepared at the department for Informatics and Mathematical Modelling, Technical University of Denmark in partial fulfillment of the requirements for acquiring the Ph.D. degree in engineering. The Ph.D. study has been carried out under the supervision of Professor Hanne Riis Nielson and Professor Flemming Nielson.

### Acknowledgements

I would like to thank my supervisors Hanne Riis Nielson and Flemming Nielson for continuous support and guidance. Furthermore I would like to thank them as well as the rest of the LBT Group, Han Gao, Christoffer Rosenkilde Nielsen, Henrik Pilegaard, Christian W. Probst and Ye Zhang for providing an inspiring and motivating working environment. Further gratitude must go to Henrik Pilegaard for enduring countless discussions, arguments and three years of sharing an office with me. I would to thank René Rydhof Hansen for numerous discussions and working together with me on [TNH06], likewise thanks go to Sebatian Nanz for comments and suggestions.

For my visit at the Universität des Saarlandes, Saarbrücken, Germany, I would like to thank Reinhard Wilhelm for providing me with everything I needed during the three month I visited, and for always discussing, commenting and motivating my work on timing channels. Thanks go to Stephan Thesing for

discussions and suggestions and to Jörg Bauer for comments, proof reading and never allowing me a boring weekend.

I would like to thank Andrei Sabelfeld for allowing me to visit him at Chalmers during September 2005, for helping me with numerous issues - work related and otherwise - and for being a inspiration, even after my return to Lyngby. Thanks also go to David Sands, Aslan Askarov and Daniel Hedin for welcoming me to the ProSec group, and for having daily discussions that have helped me shape an understanding and intuition for bisimulations as security properties.

Finally I would like to thank my family, friends and in particular my wife for unlimited patience, support and love, without which I could not have finished this thesis.

Lyngby, October 2006

Terkel K. Tolstrup

# **Contents**

| $\mathbf{S}$ | ımm             | ary                                   | i   |

|--------------|-----------------|---------------------------------------|-----|

| $\mathbf{R}$ | $\mathbf{esum}$ | é                                     | iii |

| Pı           | refac           | е                                     | v   |

| 1            | Intr            | roduction                             | 1   |

|              | 1.1             | Main thesis                           | 4   |

|              | 1.2             | Overview                              | 5   |

|              | 1.3             | Contributions                         | 5   |

| <b>2</b>     | VH              | DL                                    | 7   |

|              | 2.1             | CoreVHDL                              | 8   |

|              | 2.2             | Semantics                             | 12  |

|              | 2.3             | Properties of the Semantics           | 20  |

|              | 2.4             | Example: Advanced Encryption Standard | 21  |

| <b>(</b> | CONTENTS |

|----------|----------|

|          |          |

|   | 2.5  | Discussion and Related Work            | 23  |

|---|------|----------------------------------------|-----|

| 3 | Sec  | urity Policies                         | 29  |

|   | 3.1  | Locality-based security policies       | 31  |

|   | 3.2  | History-based Release                  | 36  |

|   | 3.3  | Transitive Security Policies           | 41  |

|   | 3.4  | Discussion                             | 44  |

| 4 | Info | ormation Flow Analysis                 | 49  |

|   | 4.1  | Local dependencies in CoreVHDL         | 50  |

|   | 4.2  | Soundness                              | 53  |

|   | 4.3  | History-based Release                  | 62  |

|   | 4.4  | Discussion                             | 71  |

| 5 | Rea  | aching Definitions Analysis            | 73  |

|   | 5.1  | Analysing CoreVHDL                     | 74  |

|   | 5.2  | Global dependencies                    | 81  |

|   | 5.3  | Analysing Advanced Encryption Standard | 86  |

|   | 5.4  | Discussion                             | 87  |

| 6 | Tin  | ning Leaks                             | 89  |

|   | 6.1  | COREVHDL with Timing Behaviours        | 91  |

|   | 6.2  | Absence of Timing Leaks                | 97  |

|   | 6.3  | Execution Path Analysis                | 102 |

| CONTENTS | xi |

|----------|----|

| '-       |    |

|   | 6.4 | Soundness                              |

|---|-----|----------------------------------------|

|   | 6.5 | Analysing Advanced Encryption Standard |

|   | 6.6 | Discussion of practical issues         |

|   | 6.7 | Summary                                |

|   |     |                                        |

| 7 | Con | clusion 131                            |

|   | 7.1 | Final remarks                          |

xii CONTENTS

### CHAPTER 1

# Introduction

There is something to be learned from a rainstorm. When meeting with a sudden shower, you try not to get wet and run quickly along the road. But doing such things as passing under the eaves of houses, you still get wet. When you are resolved from the beginning, you will not be perplexed, though you still get the same soaking. This understanding extends to everything.

— Yamamoto Tsunetomo

Every individual comes into contact with over a hundred embedded computer systems every day [Mat04]. Many exist in our homes and many more operate the commonplace items in the world around us. They are now common in households through cameras, televisions, video players, refrigerators, lawn sprinkler systems, and many other items. They are in the world around us controlling our street lighting, door openers, intruder alert systems, product theft security, speed cameras, and much more. Furthermore several embedded systems perform safety critical operations where malfunction might cause the loss of human lives, for example in pacemakers, steering aid for cars and fly-by-wire systems for airplanes.

Every day additional functionality are added to existing systems and new systems are integrated into more devices. In fact the growth in the complexity of embedded systems is said to be exponential, commonly referred to as Moore's law, that state that the number of transistors in a integrated circuit is doubled every 18 months. At the same time the size and price of the circuit is halved. According to [MED04] the electronics industry totalled a \$800 billion market in 2003. The main threat identified in [SEM03] to the growth of this market is the

2 Introduction

cost connected to the design of systems. The fact that about 60% to 70% of the total development time of a circuit is spent on simulation [MED02] makes it of great concern.

The concept of security for these systems is traditionally very low because the designer has always been able to depend on the physical security of an enclosed box. However, as more of the "boxes" are connected together networks come into being and opportunities for access and malfunction, whether through poor design, unforeseen circumstances, or foul play, become possible. Their security is at risk in many cases, much of it due to "security through obscurity". The simulation phase of the development cycle is rarely concerned with verifying security properties. Instead the focus is on validating the behaviour of the system on "standard" well-formed input, to make sure that the required functionality is implemented. However the security of systems is often compromised because of non-standard input, that might be the result of unforeseen usage of the system or hostile behaviour.

The need for reliable performance of computerised systems is well-known, yet the ad-hoc design of systems that become increasingly complex makes documenting and verifying security properties hard. Therefore to document the verification of a number of well-known security properties (e.g. authenticity, confidentiality and integrity) standards and frameworks have been proposed. In this thesis the focus will be on the Common Criteria [CC98] standard proposed and maintained by the International Standard Organization (ISO). The Common Criteria supersedes the Trusted Computer System Evaluation Criteria (TCSEC) [DOD85], the Information Technology Security Evaluation Criteria (ITSEC) [ITS91] and the Canadian Trusted Computer Product Evaluation Criteria (CTCPEC). The Common Criteria standard greatly benefits from being an internationally accepted standard, e.g. the United Nations have chosen the standard for the documentation of the security of systems used by the military of member countries.

The Common Criteria standard is a collection of objectives describing security properties for all kinds of systems, descriptions of assurances to match each objective and assurance levels that define the kind of methods used to provide the assurances. When documenting a system's security the designer needs to identify a set of reasonable objectives with respect to the setting and usage of the system. Based on these objectives assurances need to be given and documented. Each assurance is given within a level specifying the manner of the verification. Assurances given in the lower levels need to document details on the requirements for the system and the tests performed (for example by simulation) to ensure that the system behaves accordingly. Assurances in the higher levels require that formal methods are applied to verify the system.

In contrast to simulation, formal methods can be exhaustive, even for complex systems with infinitely many states, as they deal with proving the correctness of a system. One could prove the correctness of a system in the same fashion as theorems are proved. This would demand much time and effort. Hence assistance from automated *theorem provers* could aid the designers or evaluators. Still, the amount of expertise and knowledge required often result in only core functions of real-life systems being verified.

Another option is to validate the behaviour of the system by performing an exhaustive search on all possible input, *model checking* does so. However this approach might suffer from the complexity of systems, commonly referred to as the state explosion problem. Therefore many approaches based on model checking rely on techniques for reducing the state space, heuristics and randomisation. These techniques have shown to be powerful in finding flaws, but in general they are not suitable for proving the absence of flaws. However this would be a main goal for assuring a Common Criteria objective.

Therefore important properties of the formal methods assisting in the verification of Common Criteria assurances would have to be

Automatic: Demands a minimum of effort from the designer

Correctness: Guarantees that verification implies assurance

Efficient: Handles the complexity of realistic systems

Exhaustiveness: Must cover all executions on all input

To fulfill these properties we use static program analysis [NNH99]. Static program analysis benefits from being developed within well-founded frameworks with clear guidelines for their implementation, resulting in tools that are automatic and exhaustive. The limitation of static program analysis is that one is forced to sacrifice precision in return for efficiency. Precision is lost due to using abstractions of the analysed system. Still analyses can be designed to perform well on real-life systems, being both efficient and sufficiently precise. To achieve the correctness of the method it is therefore important that all abstractions introduced in the analysis still allow us to verify programs that fulfill the desired objectives.

4 Introduction

#### 1.1 Main thesis

The main thesis of this report is therefore to show that static program analyses can be designed and implemented, such that they result in tools that can automatically and efficiently verify specifications of integrated circuits and give exhaustive and correct assurances of Common Criteria objectives.

For this purpose we consider the objectives Information flow control policy (FDP\_IFC) and Information flow control functions (FDP\_IFF) from the Common Criteria standard, that deal with the confidentiality of information manipulated by the system. In this thesis the flow of information through a system is viewed as a directed graph and the definition of information flow policies is based on this view. This is contrary to much of the literature available in the field on information flow security (see [SM03a] for references). The traditional view is that information can be divided into hierarchical levels. This matches the intuition of military systems where information is labelled with security annotations such as Top Secret, Confidential and Unclassified. In the more general setting of multiple systems participating in collaborative transactions (e.g. online shopping, tax auditing and service oriented computing) a natural underlying hierarchical order is not always apparent. Hence in this thesis we will investigate the usage of graph-based policies for information flow security.

The flow of information is verified by a set of analyses dealing with different facets; first an analysis verifying the flow of information due to *control*- and *data-flow* during execution of the program and second an analysis that deals with covert channels introduced by differences in the timing behaviour of the system. Together, these analyses will give a large part of the assurance for a system needed when making the Common Criteria evaluation document.

Another main goal is that the designed analyses validate specifications of integrated circuits directly, rather than analysing on a process calculi, thereby forcing the developers to translate the system, and possibly introducing flaws in the process. The presented analyses are all specified on a fragment of VHSIC<sup>1</sup> Hardware Description Language (VHDL). The fragment will be referred to as COREVHDL and is expressive enough to deal with specifications of integrated circuits not designed for verification purposes.

<sup>&</sup>lt;sup>1</sup>Very High Speed Integrated Circuit

1.2 Overview 5

#### 1.2 Overview

In the following chapters the investigation of information flow security in the hardware setting is investigated. First the semantical model for COREVHDL is defined in Chapter 2, which allows us to formalise the semantical meaning of the Locality-based security policies in Chapter 3. Chapter 3 also proposes a generalised non-interference property, named History-based Release, that permits information flows based on the execution history of the involved principals. Chapter 4 presents an Information Flow analysis that allows for the automatic verification of hardware specifications. The analysis is extended in Chapter 5 by a Reaching Definitions analysis, which tracks the control flow in the program. In Chapter 6 timing leaks in integrated circuits are investigated. A security property for the absence of timing leaks in a COREVHDL specification is proposed and an automated analysis for verifying programs is presented.

During the investigations presented is this thesis much of the work has been inspired by a real communications system sought to be verified within the Common Criteria. The communications system was developed by the Danish company Maersk Data Defence, as a contractor for the military sector. The presented analyses were successful in verifying the available parts of the system that were previously verified by a paper-and-pencil approach. Unfortunately due to contractual obligations the system can not be discussed in this thesis. Instead we will continuously consider a reference implementation of the Advanced Encryption Standard (AES) [WBRF00]. This implementation will be a running example aiding in illustrating the techniques presented in the chapters.

#### 1.3 Contributions

The main contributions of this thesis are:

Chapter 2 presents a detailed semantical model of VHDL. In particular, practical issues of the semantics for VHDL is treated formally in accordance with state-or-the-art simulators. These issues are previously neglected or formalised in an incorrect manner, i.e. with respect to the VHDL standard [IEE01]. Parts of this contribution has previously been published in [TNN05] and [TN06].

Chapter 3 investigates the usage of graph based security policies for information flow security. Furthermore the policies are extended with a notion of localities and execution history that results in a generalised non-

6 Introduction

interference property, History-based Release. Parts of the graph based policies for information flow was originally published in [TNN05], while parts of the locality-based policies and the history-based release property for the process calculi *Klaim* [BBN<sup>+</sup>03] was published in [TNH06].

- Chapter 4 presents the automated analysis of a VHDL subset for information flow security. Especially the treatment of synchronisation in VHDL leads to novel results. Furthermore the automated analysis for programs that comply with the History-based Release property. Parts of these contributions have previously been published in [TNN05, TNH06].

- Chapter 5 motivates the need for *control flow* sensitive analyses for information flow security. The chapter presents a Reaching Definitions analysis, and discusses previously published approaches to static analysers for VHDL. The Reaching Definitions analysis was first published in [TNN05].

- Chapter 6 considers timing leaks in hardware specifications. A novel property for the absence of timing leaks is presented together with an automated analysis for verification of systems. The property is the first of its kind that supports the composition with generalised non-interference properties. Parts of the work was first published in [TN06].

Furthermore nontrivial extensions and additions have been necessary to complete the work presented in this thesis. In particular the work presented in this thesis removes several simplifications made on the hardware setting in the published papers.

## CHAPTER 2

# **VHDL**

The difference between virtuality and life is very simple. In a construct you know everything is being run by an all-powerful machine. Reality doesn't offer this assurance, so it's very easy to develop the mistaken impression that you're in control.

— Richard K. Morgan

Very High Speed Integrated Circuit Hardware Description Language, commonly referred to as VHSIC Hardware Description Language or VHDL, is one of the most widely used hardware description languages. Development was initiated in 1981 under a research programme initiated by the US Department of Defense to accommodate the rising need for documenting integrated circuits. Hence early on VHDL focussed on describing the behaviour of hardware in a manner that allowed specifications to be decomposed hierarchically while providing a well-defined interface for composing elements. With the details available in a VHDL description the possibility of simulating specifications became apparent. This possibility of simulating hardware descriptions before synthesising the circuit had great impact, as it severely cut the development cost and time, and therefore participated in shaping a new hardware design methodology. Finally, tools for automatic synthesis of descriptions were developed. During the mid-1980s all rights to the language definition were given to IEEE, who standardised the language as IEEE standard 1076-1987 [IEE87].

A problem not solved in the original standard was that of an electrical signal's driving strength. This is a result of not only having the pure boolean values

true and false in digital hardware design, but also having the possibility of e.g. turning off a signal in the synthesised circuit. The IEEE standard 1164-1993 [IEE93a] introduced the multi-valued logic std\_logic, not only including values for driving strengths but also an unknown value (primarily for simulation purposes). The VHDL standard was revised accordingly [IEE93b] while taking other issues into account as well, such as making the syntax more consistent and introducing more logical operators. Like all other IEEE standards the VHDL standard is revised every five years to ensure an ongoing relevance to the industry. The most recent revision is IEEE standard 1164-2001 [IEE01].

In this thesis we will focus on a subset of the latest revision. The subset is identified around the main concepts in *register transfer level* (RTL) VHDL, the interpretation of which common language simulators and synthesisers should agree on [IEC05]. The subset will be referred to as COREVHDL and is presented in Section 2.1. Furthermore we will discuss some of the language constructs left out, and their pre-compilation into the COREVHDL subset.

In order to reason about VHDL descriptions we first need to define their semantics. The semantics will be a cornerstone in the techniques presented later. Hence defining the semantics is the main goal of this chapter. The rest of the chapter will be structured as follows; the semantics is presented in Section 2.2. Section 2.4 presents the running example to be used throughout the thesis, which is based on an implementation of the *Advanced Encryption Standard*. Finally we discuss related work in Section 2.5.

#### 2.1 CoreVHDL

Prior to the introduction of VHDL most hardware was documented in an adhoc manner. Hence with the introduction of VHDL it was important to have a description language with a well-defined syntax and semantics. The original syntax of VHDL was essentially a subset of the Ada programming language, where special constructs were added to handle the parallelism inherent in hardware design. A central issue in hardware design is the behaviour of the underlying circuit, which the hardware description should document with enough precision to allow simulation and automatic synthesis. However, since VHDL is primarily developed for documenting hardware, only a subset of the language can be simulated and synthesised automatically. While many simulators often support larger subsets their simulations are only required to agree on the Register Transfer Level subset [IEC05]. Thus our investigation is limited to a subset of RTL VHDL to give some assurance of compliance with tools for synthesis.

2.1 CoreVHDL 9

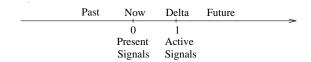

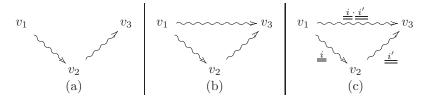

Figure 2.1: The representation of abstract time in the signal store.

A VHDL description may contain a mixture of behavioural and structural specifications. A behavioural specification describes the functionality in much the same way as a program in a traditional programming language. A structural specification describes how structures are connected into a more complex architecture. For a specification to be synthesizable the behaviour of the program must be completely specified, i.e. all parts of the VHDL specification must be given by a behavioural specification or the specifications used in the structural specification are all present either as library structures or constructed of smaller behavioural specifications.

COREVHDL is a fragment of RTL VHDL that concentrates on the behavioural specification of models. A program in COREVHDL consists of *entities* and *architectures*, uniquely identified by indices  $i_e, i_a \in Id$ . An entity describes a component's interface to the environment. An architecture comprises the behavioural or structural specification of an entity.

An entity specifies a set of signals referred to as ports  $(prt \in Prt)$ , each port is represented by a signal  $(s \in Sig)$  used for reference in the specification of the architecture; furthermore a notion of the intended usage of the signal is specified by the keywords in and out determining if the signals value can be altered or read by the environment, and the type of the signal's value.

An architecture model is specified by a family of concurrent statements  $(css \in Css)$  running in parallel; mainly processes, here the index  $i_p \in Id$  is a unique identifier in a finite set of process identifiers  $(I_p \subseteq_{fin} Id)$ . Each process has a statement  $(ss \in Stmt)$  as body and may use logical values  $(m \in LVal)$ , local variables  $(x \in Var)$  as well as signals  $(s \in Sig, S \subseteq_{fin} Sig)$ . When accessing variables and signals we always refer to their present value and when we assign to variables it is always the present value that is modified. However, when assigning to a signal its present value is not modified, rather its so-called active value is modified; this representation of signal's values, as illustrated in Figure 2.1, is used to take care of the physical aspect of propagating an electrical current through a system, the time consumed by the propagation is usually called a delta-delay. The wait statements are synchronisation points, where the active values of signals are used to determine the new present values that will

```

pgm \in Pgm

programs

pgm

ent \mid arch \mid pgm_1 \ pgm_2

ent \in Ent

entities

entity i_e is port(prt); end i_e;

ent

prt \in Prt

ports

::= s: in type \mid s: out type \mid prt_1; prt_2

prt

type \in Type

types

type

::=

std_logic

arch \in Arch

architectures

arch

::= architecture i_a of i_e is begin css; end i_a;

css \in Css

concurrent statements

css

::= i_p : process \ decl; \ begin \ ss; \ end \ process \ i_p

\mid i_b : \mathtt{block} \ decl; \ \mathtt{begin} \ css; \ \mathtt{end} \ \mathtt{block} \ i_b

\mid css_1 \parallel css_2

decl \in Decl

declarations

decl

::= variable x:type:=e

| signal s:type:=e

| decl_1; decl_2 |

ss \in Stmt

statements

::= null |ss_1;ss_2| if e then ss_1 else ss_2

ss

|x := e | s \le e

| wait on S until e

e \in Exp

expressions

m \mid op^u e \mid e_1 op^b e_2 \mid x \mid s

```

Figure 2.2: The subset CoreVHDL of VHDL.

be common to all processes. This will be further discussed in Section 2.2.

Concurrent statements could also be block statements that allow local signal declarations for the use of internal communication between processes declared within the block. The index  $i_b \in Id$  is a unique identifier in a finite set of block identifiers  $(I_b \subseteq_{fin} Id)$ . The scope of the local signals declared by a block definition is the concurrent statements specified inside the block.

2.1 CoreVHDL

Since VHDL describe digital hardware we are concerned with the details of electrical signals, and it is therefore necessary to include types to represent digitally encoded values. We consider logical values (LVal) of the standard logic type  $std\_logic$ , that includes traditional boolean values as well as values for electrical properties.

The formal syntax is given in Figure 2.2. In VHDL it is allowed to omit components of wait statements. Writing FS(e) for the free signals in e, the effect of 'on FS(e)' may be obtained by omitting the 'on S' component, and the effect of 'until true' may be obtained by omitting the 'until e' component. (In other words, the default values of S and e are FS(e) and true, respectively.) Semantically, S is the set of signals waited on, i.e. at least one of the signals of S must have a new active value, and e is a condition on the resulting present values that must be fulfilled, in order to leave the wait statement.

The syntax does not include any loops. In general the loops in VHDL can not be synthesised, as the synthesising tool needs to produce timing guarantees on finishing the loop. Instead, looping behaviour is obtained using processes and iterator signals. However, loops aid in making high-level specifications succinct. Hence in Section 2.1.1 we discuss the unrolling of loops during pre-compilation.

In CoreVHDL the notion of signals is simplified with respect to full VHDL and does not allow references further ahead in time than the following *delta-cycle*. This correspond to the choice made in RTL VHDL and not only simplifies the analysis but also simplifies the definition of the semantics: Of the many accounts to be found in the literature [Goo95, TE01] we have found the one of [TE01] to best correspond to our practical experiments, based on test programs simulated with the ModelSim SE 5.7d VHDL simulator [Men03]. Even with this restriction CoreVHDL is sufficiently expressive to deal with the programs of the AES implementation.

### 2.1.1 Pre-compiling RTL VHDL to CoreVHDL

The CoreVHDL subset of RTL VHDL is restricted in its expressiveness. Here we discuss some commonly used syntactical constructs and their pre-compilation to CoreVHDL. The following operations are performed right after a RTL VHDL specification has been parsed.

**Hierarchy flattening** The VHDL standard [IEE01] describe how the hierarchical structure of a specification can be flattened. The pre-compiler instantiates

all the modules and in-line functions. This enables us to handle structural specifications by flattening them to elaborate behavioural specifications.

**Concurrent Assignment** Signal assignment can be performed as a concurrent statement, this corresponds to a process that is sensitive to the *free signals* in the right-hand side expression and that has the same assignment inside [Ash02].

Loop unrolling Loops are also allowed at the level of concurrent statements, these are commonly used to produce a multitude of processes with similar behaviour. Furthermore loops can be applied within processes, with semantics similar to that of imperative languages, see e.g. [NN92]. If the specification is synthesizable all loops need to result in a finite execution [IEC05]. Hence when considering synthesizable specifications loops are unrolled.

Scalarisation of vectors Following the approach presented in [SV00] vectors are scalarized and replace the new signals named like the vector and postfixed with the index, this is possible as only statically defined vectors are available in RTL VHDL [IEC05].

#### 2.2 Semantics

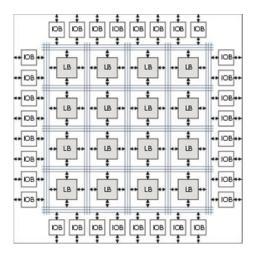

Before we can define the semantics for COREVHDL we need to understand how integrated circuits work. Most tools for synthesising circuits from VHDL descriptions support the configuration of *Field Programmable Gate Arrays* (FPGA). A FPGA consist of Logical Blocks (LB) and Input/Output Blocks (IOB), the structure is illustrated in Figure 2.3. The blocks are connected by wires, that in switch points can be interconnected or not. The synthesising step of the hardware design methodology is to decide the configuration of the switch points, thus giving the paths between LBs and IOBs. IOBs are the interface to the environment. The IOBs can also connect an outgoing wire to an incoming wire.

One important aspect of the synthesis step is that signals are mapped down to the wires connecting LBs and IOBs. It is also important to observe that the FPGA does not *execute* the VHDL specification, but instead provides a layout of the switches. The value of each signal will therefore be carried to and from the LB on different wires. In VHDL this is captured by dividing the values of signals into an active value and an present value, these match the from and to

2.2 Semantics 13

Figure 2.3: The structure of a FPGA.

wire, respectively. The time spent on stabilising and propagating the electrical current over the gates is called a *delta-delay*.

Another important aspect is that the integrated circuit does not *stop* working or otherwise end, in fact whenever the input is modified the new currents are propagated through the FPGA until it has stabilised again. To capture this behaviour when simulating hardware specifications we consider a *simulation cycle* as consisting of two phases:

- the signal update phase, and

- the process execution phase

In the signal update phase, simulation time is advanced to the time of the next scheduled active value, then all active values are applied to the corresponding signals. This may cause events to occur. In the process execution phase, all processes that wait on these events are resumed and executed until again suspended at wait statements. The simulation cycle is then repeated.

The main idea when defining the semantics for COREVHDL programs is therefore to execute each process by itself until a synchronisation point is reached (i.e. a wait statement). When all processes of the program have reached a synchronisation point synchronisation is handled, while taking care of the resolution of signals in case a signal has been assigned different values by the processes. This

synchronisation will leave the processes in a state where they are ready either to continue execution by themselves or wait for the next synchronisation.

**Basic semantic domains** The syntax of programs in COREVHDL is limited to statements operating on a state of logical values. These logical values are defined as  $v \in LVal = \{\text{'U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-'}\}$  where the values indicate the properties

| ſ | 'U' | Uninitialised | 'X' | Forcing Unknown | '0' | Forcing zero |

|---|-----|---------------|-----|-----------------|-----|--------------|

|   | '1' | Forcing one   | 'Z' | High Impedance  | 'W' | Weak Unknown |

|   | L'  | Weak zero     | 'H' | Weak one        | ,_, | Don't care   |

these logical values capture the behaviour of an electrical system better than traditional boolean values. Hence they have been included in the VHDL standard from the second revision [IEE93b], see [Ash02] for further details. We have a function mapping logicals in the syntax to logical values in the semantics  $\mathcal{L}: LVal \rightarrow Value$ .

Constructed semantic domains CoreVHDL includes local variables and signals. The values of the local variables are stored in a local state, which is a mapping from variable names to logical values.

$$\sigma \in State = (Var \rightarrow Value)$$

The idea is that we have a local state for each process, keeping track of assignments to local variables encountered in the execution of the process so far.

For communication between the processes we have signals, the values of which are stored in local states. The processes communicate by synchronising the signals of their local signal state with other processes.

$$\varphi \in Signals = (Sig \rightarrow (\{0,1\} \hookrightarrow Value))$$

The value assigned to a signal is available after the following synchronisation, therefore we keep the present value of a signal s in  $\varphi$  s 0. In  $\varphi$  s 1 we store the assigned value, meaning that it is available in the following delta-cycle. Each signal state has a time line for each signal. Values in the past are not used and therefore forgotten by the semantics; in COREVHDL it is not possible to assign values to signals further into the future than one delta-cycle.

2.2 Semantics 15

```

\mathcal{E}[\![m]\!] \langle \sigma, \varphi \rangle \qquad = \qquad \mathcal{L}[\![m]\!]

\mathcal{E}[\![x]\!] \langle \sigma, \varphi \rangle \qquad = \qquad \sigma \ x

\mathcal{E}[\![s]\!] \langle \sigma, \varphi \rangle \qquad = \qquad \varphi \ s \ 0

\mathcal{E}[\![op^u \ e]\!] \langle \sigma, \varphi \rangle \qquad = \qquad \frac{\varphi \ s \ 0}{op^u \ v} \qquad \text{where } \mathcal{E}[\![e]\!] \langle \sigma, \varphi \rangle = v

\text{and } \overline{op^u \ v} \ \text{defined}

\mathcal{E}[\![e_1 \ op^b \ e_2]\!] \langle \sigma, \varphi \rangle \qquad = \qquad v_1 \ \overline{op^b} \ v_2 \qquad \text{where } \mathcal{E}[\![e_1]\!] \langle \sigma, \varphi \rangle = v_1

\text{and } \mathcal{E}[\![e_2]\!] \langle \sigma, \varphi \rangle = v_2

\text{and } v_1 \ \overline{op^b} \ v_2 \ \text{defined}

```

Table 2.1: Semantics of Expressions

All signals have a present value, so  $\varphi$  s 0 is defined for all s. Not all signals need to be *active* meaning they have a new value waiting in the following delta-cycle, i.e.  $\varphi$  s 1 need not be defined. Hence we use  $\{0,1\} \hookrightarrow Value$  in the definition of the signal state to indicate that it is a partial function.

The semantics handles expressions following the ideas of [NN92]. For expressions

$$\mathcal{E}: Exp \rightarrow (State \times Signals \hookrightarrow Value)$$

evaluates the expression. The function is defined in Table 2.1. Note that for signals we use the current value of the signal, i.e.  $\varphi$  s 0.

#### 2.2.1 Statements

The semantics of statements and concurrent statements are specified by transition systems, more precisely by structural operational semantics [Plo04]. For statements we shall use configurations of the form:

$$\langle ss', \sigma, \varphi \rangle \in Stmt' \times State \times Signals$$

Here Stmt' refers to the statements from the syntactical category Stmt with an additional statement (final) indicating that a final configuration has been reached. Therefore the transition relation for statements has the form:

$$\langle ss, \sigma, \varphi \rangle \Rightarrow \langle ss', \sigma', \varphi' \rangle$$

which specifies one step of computation. The transition relation is specified in Table 2.2 and briefly commented upon below.

```

[Local Variable Assignment]:

\langle x := e, \sigma, \varphi \rangle \Rightarrow \langle \mathtt{final}, \sigma[x \mapsto v], \varphi \rangle

where \mathcal{E}[e]\langle \sigma, \varphi \rangle = v

[Signal Assignment]:

\langle s <= e, \sigma, \varphi \rangle \Rightarrow \langle \mathtt{final}, \sigma, \varphi^{[1]}[s \mapsto v] \rangle

where \mathcal{E}[e]\langle \sigma, \varphi \rangle = v

[Skip] :

\langle \text{null}, \sigma, \varphi \rangle \Rightarrow \langle \text{final}, \sigma, \varphi \rangle

[Composition]:

\frac{\langle ss_1, \sigma, \varphi \rangle \Rightarrow \langle ss'_1, \sigma', \varphi' \rangle}{\langle ss_1; ss_2, \sigma, \varphi \rangle \Rightarrow \langle ss'_1; ss_2, \sigma', \varphi' \rangle}

where ss'_1 \in Stmt

\frac{\langle ss_1, \sigma, \varphi \rangle \Rightarrow \langle \text{final}, \sigma', \varphi' \rangle}{\langle ss_1; ss_2, \sigma, \varphi \rangle \Rightarrow \langle ss_2, \sigma', \varphi' \rangle}

[Conditional]:

\langle \text{if } e \text{ then } ss_1 \text{ else } ss_2, \varphi \rangle \Rightarrow \langle ss_1, \sigma, \varphi \rangle

if \mathcal{E}[e]\langle \sigma, \varphi \rangle = '1'

\langle \text{if } e \text{ then } ss_1 \text{ else } ss_2, \varphi \rangle \Rightarrow \langle ss_2, \sigma, \varphi \rangle

if \mathcal{E}[e]\langle \sigma, \varphi \rangle = 0

```

Table 2.2: Statements

An assignment to a signal is defined as an update to the value at the delta-time, i.e.  $\varphi$  s 1. We use the notation  $\varphi^{[i]}[s \mapsto v]$  to mean  $\varphi[s \mapsto \varphi(s)[i \mapsto v]]$ .

Because the wait statement is in fact a synchronisation point of the processes it is handled in Section 2.2.2, along with the handling of the concurrent processes.

#### 2.2.2 Concurrent Statements

The semantics of concurrent statements handles the concurrent processes and the synchronisations of a CoreVHDL program. The transition system for concurrent statements has configurations of the form:

$$||_{i \in I} \langle css'_i, \sigma_i, \varphi_i \rangle$$

2.2 Semantics 17

for  $I \subseteq_{\text{fin}} Id$  and  $css'_i \in Css'$ ,  $\sigma_i \in State$ ,  $\varphi_i \in Signals$  for all  $i \in Id$ . Thus each process has a local variable and signal state. Here Css' refers to the concurrent statements from the syntactical category Css with the additional option of statement from the category Stmt preceding a concurrent statement. This allows for a succinct semantics for process statements.

The initial configuration of a CoreVHDL program is:

$$\|_{i \in I} \ \langle i : \mathtt{process} \ decl_i; \ \mathtt{begin} \ ss_i; \ \mathtt{end} \ \mathtt{process} \ i, \sigma_i^0, \varphi_i^0

angle$$

The  $i^{\text{th}}$  process uses an initial state for signals defined by the semantics for declarations of signals. If no initial value is specified the following are used:

$\sigma_i^0$  x = 'U' and  $\varphi_i^0$  s 0 = 'U' for all signals used in the process  $ss_i$ .  $\varphi_i^0$  s 1 is undef for all signals used in the process  $ss_i$ .

The transition relation for concurrent statements has the form:

$$||_{i \in I} \langle css'_i, \sigma_i, \varphi_i \rangle \Longrightarrow ||_{i \in I} \langle css'_i, \sigma'_i, \varphi'_i \rangle$$

which specifies one step of computation.

The transition relation is specified in Table 2.3 and explained below.

As mentioned, the idea when defining the semantics of programs in COREVHDL is that we execute processes locally until they have all arrived at a wait statement; this is reflected in the rule [Handle non-waiting processes (H)].

When all processes are ready to execute a wait statement we perform a synchronisation covered by the rule [Active signals (A)]. If a signal waited for is active, the processes waiting for that signal may proceed; this is expressed using the predicate  $active(\varphi)$  defined by

$$active(\varphi) \equiv \exists s \exists v : \varphi \ s \ 1 = v$$

The delta-delayed values of signals will be synchronised for all processes and in order to do this we use a resolution function  $f_s$  of the form:

$$f_s: multiset(Value) \rightarrow Value$$

Thus  $f_s$  combines the *multi-set* of values assigned to a signal into one value that then will be the new (unique) value of the signal. VHDL allow a resolution function to be specified in a syntax much like that of a process. We assume that

```

\begin{array}{c} (\operatorname{Handle\ non-waiting\ processes\ }(\mathbf{H})]: \\ & \langle ss_j, \sigma_j, \varphi_j \rangle \Rightarrow \langle ss_j', \sigma_j', \varphi_j' \rangle \\ \hline & \|_{i \in I \cup \{j\}} \ \langle ss_i; css_i, \sigma_i, \varphi_i \rangle \Longrightarrow \|_{i \in I \cup \{j\}} \ \langle ss_i'; css_i, \sigma_i', \varphi_i' \rangle \\ \\ & \text{where } ss_i' = ss_i \wedge \sigma_i' = \sigma_i \wedge \varphi_i' = \varphi_i \text{ for all } i \neq j. \\ \hline & \langle ss_j, \sigma_j, \varphi_j \rangle \Rightarrow \langle \operatorname{final}, \sigma_j', \varphi_j' \rangle \\ \hline & \|_{i \in I \cup \{j\}} \ \langle ss_i; css_i, \sigma_i, \varphi_i \rangle \Longrightarrow \|_{i \in I \cup \{j\}} \ \langle css_i', \sigma_i', \varphi_i' \rangle \\ \\ & \text{where } css_i' = css_i \text{ for all } i = j \text{ and } \\ & css_i' = ss_i; css_i \wedge \sigma_i' = \sigma_i \wedge \varphi_i' = \varphi_i \text{ for all } i \neq j. \\ \hline [\mathbf{Active\ signals\ }(\mathbf{A})]: \\ & \|_{i \in I} \ \langle \text{wait\ on\ } S_i \text{ untill\ } e_i; css_i, \sigma_i, \varphi_i \rangle \Longrightarrow \|_{i \in I} \ \langle css_i', \sigma_i, \varphi_i' \rangle \\ & \text{where} \\ & \varphi_i' \text{ s } 0 = \begin{cases} f_s \{ \mathcal{U}(\varphi_k, s) \mid k \in I \} \} & \text{if } \exists j \in I. \ \varphi_j \text{ s } 1 \text{ is defined } \\ & \text{otherwise, } \varphi_i \text{ s } 0 = v \end{cases} \\ & \varphi_i' \text{ s } 1 = undef \\ & css_i' = \begin{cases} css_i & \text{if } ((\exists s \in S_i, \varphi_i \text{ s } 0 \neq \varphi_i' \text{ s } 0) \\ & \wedge \mathcal{E}[e_i][\langle \sigma_i, \varphi_i' \rangle = i' 1') \end{cases} \\ & \text{wait\ on\ } S_i \text{ untill\ } b_i; css_i \text{ otherwise} \end{cases} \\ [\mathbf{Processes\ }(\mathbf{P})]: \\ & \|_{i \in I} \ \langle i: \text{ process\ } decl_i; \text{ begin\ } ss_i; \text{ end\ process\ } i, \sigma_i, \varphi_i \rangle \Longrightarrow \\ & \|_{i \in I} \ \langle ss_i; i: \text{ process\ } decl_i; \text{ begin\ } ss_i; \text{ end\ process\ } i, \sigma_i, \varphi_i \rangle \end{cases}

```

Table 2.3: Concurrent statements

all signals handled in resolution functions are in the argument of the function. The resolution function is applied to the active values of a signal, however if a signal is not active in a local signal state of a process the present value is used instead. We introduce the function

$$\mathcal{U}(\varphi_i, s) = \begin{cases} v & \text{if } \varphi_i \ s \ 1 = v \\ v & \text{otherwise, } \varphi_i \ s \ 0 = v \end{cases}$$

to determine whether the active value or the present value is used.

The VHDL standard [IEE01] defines a resolution function for the type std\_logic called resolve. The function is applied on a list of values for the signal. If the function is passed an empty list, it returns the value 'Z'. If there is only one driving value, the function returns that value unchanged. Otherwise, the func-

2.2 Semantics 19

|     |     |     |     |     | 'Z' |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 'U' |

| 'X' | 'U' | 'X' |

|     |     |     |     |     | '0' |     |     |     |     |

| '1' | 'U' | 'X' | 'X' | '1' | '1' | '1' | '1' | '1' | 'X' |

| 'Z' | 'U' | 'X' | '0' | '1' | 'Z' | 'W' | 'L' | 'H' | 'X' |

|     |     |     |     |     | W'  |     |     |     |     |

|     |     |     |     |     | 'L' |     |     |     |     |

| 'H' | 'U' | 'X' | ′0′ | '1' | 'H' | 'W' | 'W' | 'H' | 'X' |

| '_' | 'U' | 'X' |

Table 2.4: Resolution table rt

tion uses a resolution table to resolve driving values

resolve

$$\{s_1, s_2, \dots, s_n\} = rt(s_1, rt(s_2, rt(\dots, s_n) \dots))$$

where the resolution table rt is defined in Table 2.4.

Notice that even though a signal, which a wait statement is waiting for becomes active, it is not enough to guarantee that it proceeds with its execution. This is because we have the side condition 'until e'. This is reflected in the definition of the statement  $css'_i$  of the next configuration. Notice that the state of local variables is unchanged.

Recall that it is the intention to repeat the statement  $ss_i$  indefinitely in a process declaration i: process  $decl_i$ ; begin  $ss_i$ ; end process i, this is reflected in the rule [Processes (P)].

In the following chapters we will investigate security policies and mechanisms that dynamically change due to constraints on the history of execution. Therefore we will now define an execution trace. The point of interest is that specific executions take place prior to releasing specific information. Hence the semantics are annotated with the identifier of the process that gets to evaluate part of its body. Thus we write

$$||_{i \in I} \langle ss_i; css_i, \sigma_i, \varphi_i \rangle \stackrel{i}{\Longrightarrow} ||_{i \in I} \langle ss'_i; css_i, \sigma'_i, \varphi'_i \rangle$$

when an evaluation step with the rule [Handle non-waiting processes (H)] evaluated one step of process i. As a result an execution trace is then defined as the transitive reflexive closure of the semantics, and we write

$$\|i \in I \langle ss_i; css_i, \sigma_i, \varphi_i \rangle \stackrel{\omega}{\Longrightarrow}^* \|i \in I \langle ss_i'; css_i, \sigma_i', \varphi_i' \rangle$$

where  $\omega$  is a string of identifiers.

#### 2.2.3 Architectures

The Semantics for architectures basically initialises the local variable and signal stores for each process. As no actual evaluation is taking place when handling the architectures, we merely consider specifications where the variable and signal declarations are stripped. Hence no further formal definitions are considered.

### 2.3 Properties of the Semantics

In this section we will state properties of the Semantics that will aid us in establishing correctness results of the analyses presented in later Chapters. One property of the Semantics is that the execution of a statement  $ss_1$  is not influenced by the statement following.

**Lemma 2.1** If

$$\langle ss_1, \sigma, \varphi \rangle \Rightarrow^k \langle final, \sigma', \varphi' \rangle$$

then  $\langle ss_1; ss_2, \sigma, \varphi \rangle \Rightarrow^k \langle ss_2, \sigma', \varphi' \rangle$ .

**Proof.** The proof proceeds by induction in the length of the derivation sequence. If k = 0 the result holds vacuously. For the induction step we assume that the lemma holds for  $k \le k_0$  and we shall prove it for  $k_0 + 1$ . So assume that

$$\langle ss_1, \sigma, \varphi \rangle \Rightarrow^{k_0+1} \langle \text{final}, \sigma', \varphi' \rangle$$

hence the derivation sequence can be written

$$\langle ss_1, \sigma, \varphi \rangle \Rightarrow \gamma \Rightarrow^{k_0} \langle \text{final}, \sigma', \varphi' \rangle$$

for some configuration  $\gamma$ . Now we know that the rule [Composition] was used to obtain

$$\langle ss_1, \sigma, \varphi \rangle \Rightarrow \gamma$$

Hence we consider the two cases, first the case where statement  $ss_1$  evaluates to  $ss'_1$  in one step

$$\frac{\langle ss_1, \sigma, \varphi \rangle \Rightarrow \langle ss'_1, \sigma'', \varphi'' \rangle}{\langle ss_1; ss_2, \sigma, \varphi \rangle \Rightarrow \langle ss'_1; ss_2, \sigma'', \varphi'' \rangle}$$

and get

$$\langle ss_1; ss_2, \sigma, \varphi \rangle \Rightarrow \langle ss'_1; ss_2, \sigma'', \varphi'' \rangle \Rightarrow^{k_0} \langle ss_2, \sigma', \varphi' \rangle$$

and we can apply the induction hypothesis on the derivation sequence

$$\langle ss_1'; ss_2, \sigma'', \varphi'' \rangle \Rightarrow^{k_0} \langle ss_2, \sigma', \varphi' \rangle$$

The second case is when  $ss_1$  finish evaluation in one step

$$\frac{\langle ss_1, \sigma, \varphi \rangle \Rightarrow \langle \text{final}, \sigma'', \varphi'' \rangle}{\langle ss_1; ss_2, \sigma, \varphi \rangle \Rightarrow \langle ss_2, \sigma'', \varphi'' \rangle}$$

where the result follows immediately.

### 2.4 Example: Advanced Encryption Standard

The techniques presented in this thesis will be applied to the standard implementation of the Advanced Encryption Standard [WBRF00]. We shall consider the pipelined 128 bit version of the NSA Advanced Encryption Standard implementation of the algorithm. As the specification is rather substantial, and large parts are merely concerned with control signals and registers, we will present two subprograms, which will be used to illustrate the presented analyses.

The 128 bit version of the algorithm works on blocks of 128 bit, that are encrypted through 10 rounds. Each round consists of 4 stages that substitute, shift, mix and add a *round key* to the block, respectively. Decryption is done by reversing the order of the inverse stages in each round.

The first subprogram is the shift function that is part of an encryption or decryption round.

```

-- iteration no. 1

temp(0) := a(1)(1);

temp(1) := a(1)(2);

temp(2) := a(1)(3);

temp(3) := a(1)(0);

a(1)(0) := temp(0);

```

22 VHDL

```

a(1)(1) := temp(1);

a(1)(2) := temp(2);

a(1)(3) := temp(3);

-- iteration no. 2

temp(0) := a(2)(2);

temp(1) := a(2)(3);

temp(2) := a(2)(0);

temp(3) := a(2)(1);

a(2)(0) := temp(0);

a(2)(1) := temp(1);

a(2)(2) := temp(2);

a(2)(3) := temp(3);

-- iteration no. 3

temp(0) := a(3)(3);

temp(1) := a(3)(0);

temp(2) := a(3)(1);

temp(3) := a(3)(2);

a(3)(0) := temp(0);

a(3)(1) := temp(1);

a(3)(2) := temp(2);

a(3)(3) := temp(3);

```

The second subprogram is the process that determines the control flow of round blocks, and decides whether the key is added before or after the 10 rounds. This is the difference between the encryption and the decryption algorithms. The implementation considered performs either encryption or decryption depending on the value of the incoming signal ALG\_ENC. For encryption this is done before the first round instead.

```

POST_ADD_KEY <= ALG_KEY_10;

POST_ADD: process begin

b(0)(0) := FINAL_OUT_REG(0)(0) xor POST_ADD_KEY(0)(0);

b(0)(1) := FINAL_OUT_REG(0)(1) xor POST_ADD_KEY(0)(1);

b(0)(2) := FINAL_OUT_REG(0)(2) xor POST_ADD_KEY(0)(2);

b(0)(3) := FINAL_OUT_REG(0)(3) xor POST_ADD_KEY(0)(3);

b(1)(0) := FINAL_OUT_REG(1)(0) xor POST_ADD_KEY(1)(0);</pre>

```

```

b(1)(1) := FINAL_OUT_REG(1)(1) xor POST_ADD_KEY(1)(1);

b(1)(2) := FINAL_OUT_REG(1)(2) xor POST_ADD_KEY(1)(2);

b(1)(3) := FINAL_OUT_REG(1)(3) xor POST_ADD_KEY(1)(3);

b(2)(0) := FINAL_OUT_REG(2)(0) xor POST_ADD_KEY(2)(0);

b(2)(1) := FINAL_OUT_REG(2)(1) xor POST_ADD_KEY(2)(1);

b(2)(2) := FINAL_OUT_REG(2)(2) xor POST_ADD_KEY(2)(2);

b(2)(3) := FINAL_OUT_REG(2)(3) xor POST_ADD_KEY(2)(3);

b(3)(0) := FINAL_OUT_REG(3)(0) xor POST_ADD_KEY(3)(0);

b(3)(1) := FINAL_OUT_REG(3)(1) xor POST_ADD_KEY(3)(1);

b(3)(2) := FINAL_OUT_REG(3)(2) xor POST_ADD_KEY(3)(2);

b(3)(3) := FINAL_OUT_REG(3)(3) xor POST_ADD_KEY(3)(3);

POST_OUT_INT <= b;

end process POST_ADD;

ALG_DATA_LAST <= POST_OUT_INT when ALG_ENC = '0' else

FINAL_OUT;

```

#### 2.5 Discussion and Related Work

In this thesis focus will be on VHDL. However, other hardware description languages exists. The most predominant alternative to VHDL is the Verilog Hardware Description Language [IEE95]. The choice of VHDL was made because of the wide acceptance and support of the language in the industry. Still the common foundation of hardware description languages should allow for a fairly straightforward adaption of the techniques presented in the following chapters to other languages.

Another alternative might be the system description language SystemC [IEE05]. The SystemC language provides a greater freedom of expressiveness as it consists of libraries and macros for C++, hence allowing the C++ language facilities to be used in hardware descriptions. However, when synthesising designs, the procedure is normally to compile the SystemC descriptions to VHDL, where further development might be necessary. Therefore the analyses presented in this thesis can be applied at the VHDL level, to achieve similar results for SystemC specifications.

24 VHDL

#### 2.5.1 Semantics for VHDL

There exists alternative definitions of semantics for VHDL. In the following we will discuss these and argue for some of the choices, that make our semantics differ from others. The reason for these differences is primarily the ambiguity and complexity of the IEEE standard [IEE01], which allows for varying interpretations. To validate the choices made we therefore focus on the specification of synthesising RTL VHDL [IEC05] and the ModelSim SE 5.7d VHDL simulator [Men03].

The semantics presented in this chapter is based on the structural operational semantics presented by Goossens [Goo95], which aims to formalise the simulation algorithm described in the original VHDL standard [IEE87]. Thirunarayan and Ewing [TE01] extended this semantics to comply with the 1993 standard. The presented semantics is very close to these approaches, but still there are two issues that we address differently. First the progression of time at synchronisation points that update the present values of signals was erroneously formalised. Thirunarayan and Ewing points out the problem in their paper [TE01], however they correction does not solve the issue, but instead introduces a copying of the active value of signals whenever no processes can continue past their synchronisation points. Thereafter a process might mistakenly observe the signal as being active twice. Thirunarayan has acknowledged this issue and agreed to the solution presented in this thesis [Thi03].

The second issue has to do with the resolution of signals. In [Goo95, TE01] the resolution function is applied only on the active values of signals. However there is no distinction between the active and the present value in hardware and hence the resolution function should in fact be applied on both. This observation is supported by [Ash02] and ModelSim simulations of test specifications.

There are other alternatives. Many leave out important issues in the hardware model, such as

"For simplicity, delta-delayed signal assignments are not treated." [BFK94], which allows Breuer et al. to define a *clean* semantics of VHDL. Van Tassel [vT93] makes similar simplification to the considered subset of VHDL. These semantics do not match the understanding of hardware design investigated in this thesis.

Van Tassel [vT93] embeds the semantics of a VHDL subset in HOL, in this manner allowing for proof assistance. In the same line of research Russinoff [Rus95] defines the semantics of a simple hardware description language, which is similar to a subset of VHDL, in Boyer-Moore logic. Another approach that defines the semantics of VHDL in a logical language (i.e. ACL) is [RBG00].

These embeddings into proof assistants aid the formal verification of VHDL specifications.

Several hardware description languages are focused completely on finite state machines, such as Esterel [Est05]. In fact most VHDL specification were focused on describing globally synchronous specifications, that can be mapped to finite state machines. This is still one of its primary usages. Hence much work has been done on compiling VHDL descriptions into finite state machines, see e.g. [BLPV94, DB93, DB95].

Hymans [Hym02] defines a semantics that is based on Goossens' [Goo95] approach. The considered subset of VHDL is very close to the one at hand. The main differences is that Hymans introduces functions for random number generation to the language. These are not present in VHDL and are not synthesizable. Hymans' reason for introducing them is to accommodate verification of systems. Hence only a *test bench* process would use the functions. The semantics, however, has been modified to not include resolution of active signals. Instead Hymans utilises a global state that allows signal assignments to overwrite each other. This forces Hymans to assume that each signal is only assigned to in one process.

To verify that the presented definition of the semantics is accurate several test specifications were made that support or reject design choices in the semantics. The test specifications were simulated with the ModelSim simulator [Men03]. Although this does not provide any formal guarantee, it does allow us to debug the formal specifications. Below we report on two of the example specifications and the results of simulation them.

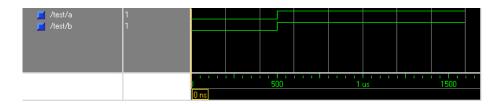

Waiting on signals In the semantics of programs the condition for allowing a process to continue execution after waiting for a signal is limited to signals that have actually changed value. I.e. using the definition of active signals is not sufficient to determine if processes continue execution in the rule [Active signals (A)]. We see from the below described program that we need the condition  $\exists s \in S_i$ .  $\varphi_i$  s  $0 \neq \varphi_i'$  s 0.

To illustrate this decision in the semantics we present a program, consisting of two processes. One process will continue to set the value of a signal to a constant value. The second process will wait on the signal set by the first process, and when allowed to continue execution it will alter another signal. This allows us to detect that the process is not halted while waiting on the signal. The signal CLK is a clock signal set by the simulator. It is inverted with a frequency of 500 ns.

26 VHDL

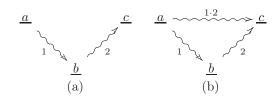

Figure 2.4: Result of simulating the program.

The result of simulating the program with the ModelSim SE 5.7d VHDL simulator is presented in Figure 2.4. Since the value of the signal B only changes once, namely after 500 ns and not again after 1000 ns or 1500 ns, we observe that the second process can not continue execution at the wait statement even though the first process sets an active value for the signal A.

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity test is

signal CLK : in STD_LOGIC;

end test;

architecture model of test is

signal A : STD_LOGIC := '0';

signal B : STD_LOGIC := '0';

begin

process begin

wait on CLK;

A <= '1';

end process;

process begin

wait on A;

B \le not B;

end process;

end test;

```

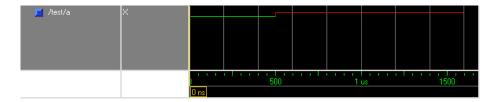

**Resolution off signals** In the semantics of programs it is specified how signals are resolved with a resolution function. Different test programs have been

Figure 2.5: Result of simulating the program.

simulated and the behaviour corresponds to the resolution function specified in [Ash02].

The simulated programs are of a form similar to the program presented below. The program consists of two processes running in parallel, each of them setting the value of the signal A. When the processes synchronise at the wait statements the resolution of the signal is performed. By altering the values assigned to A each entry in the resolution table can be tested. As above the signal CLK is a clock signal set by the simulator. It is inverted with a frequency of 500 ns.

The result of simulating the test program is presented in Figure 2.5.

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity test is

signal CLK : in STD_LOGIC;

end test;

architecture model of test is

signal A : STD_LOGIC := '0';

begin

process begin

wait on CLK;

A <= '1';

end process;

process begin

wait on CLK;

A <= '0';

end process;

end model;

```

28 VHDL

# **Security Policies**

The only thing necessary for the triumph of evil is for good men to do nothing.

— Edmund Burke

Security verification of a system is divided into two parts; a security policy and a security mechanism. The security policy is a high-level specification of the security properties that the given system should possess; typically it consists of statements describing goals of the security verification. These goals should be driven by our understanding of threats rather than how the system is implemented. Hence a policy might express goals regarding the access to objects or how information flows through the system. On the other hand the security mechanism enforces the security properties on the given system. In this chapter we investigate security policies for information flow. Security mechanisms matching the security policies are investigated in Chapter 4 and 5.

The concept of security policies came from the military sector. The first security policy model, Bell-LaPadula [BL73], was developed in 1973 to formalise the U.S. Department of Defense multilevel security policy. The model describes a set of access control rules through security labels on resources and clearances for users. Informally said, the model protects the confidentiality of information through a hierarchy of security levels. A user can not read information from levels higher than the users own, no read up, and the user can not write information to lower levels, no write down. This model became the standard military approach when evaluating systems, according to the U.S. Department of Defense "Orange

Book" [DOD85]. However for general usage the model has proved to be too restrictive, in particular due to it relying on dynamic security mechanisms that have problems with enforcing the policy in the presence of *implicit* flows. Here we make the distinction between *explicit* and *implicit* information flows; where explicit information flows are statements that directly affects one resource by reading another resource, e.g.

$$x := y$$

where the value of y is copied to x. An implicit flow occurs in connection with statements that alter the *control flow* of the program based on reading a resource, e.g.

$$y := 0$$

; if x then  $y := 1$  else null

where the value of x will determine which branch will be taken and finally the value of y. Observe that the implicit flow occur even when  $x \neq true$  as the attacker may observe that the value of y is 0.

Due to these issues investigation began on policies and mechanisms for preserving confidentiality in a system. On one hand Denning and Denning [Den76, DD77 developed static mechanisms for verifying the security of a system, while on the other hand Lampson [Lam73] and later Cohen [Coh77, Coh78] investigated notions for the confinement problem and strong secrecy. Goguen and Meseguer [GM82, GM84] introduced the security property, non-interference, that has later become the most influential property of information flow policies. Informally, non-interference means that an attacker of the system, who can view low confidentiality information, is not permitted to observe any differences after two executions of a program that only differ on its confidential inputs. Another weaker property, non-deducibility, was proposed by Sutherland [Sut86]. It was the first nondeterministic version of non-interference. It is weaker than non-interference as it allows the two executions of the program to modify the observable part of the resources as long as no connection between confidential information and resulting low confidentiality information can be made with complete certainty. The non-deducibility property has no practical usage, since a guarantee that allows the attacker to determine a secret with 99% probability is no better than no guarantee.

At about the same time Kemmerer [Kem82, Kem02] presented the *shared resource matrix methodology* aimed at identifying *covert channels* in *real* systems. The method is centred around the notion of a *resource matrix*, which is a matrix where the rows represent the resources available in the considered system and the columns represent the actions (referred to as primitives). Each field in the matrix state the access right for the action on the resource. In this model there are two access rights, *read* and *modify*. The resource matrix model allows

the security analyst to abstract on the resources and actions, and hence include resources such as the process scheduler and the system clock, while grouping actions into processes and programs. The strength of the shared resource matrix approach is verifying real systems, which has been illustrated in several cases (e.g. [HKMY86, KT96]). One drawback of the approach is that it does not formalise a security property, instead it aims at identifying information flows (and more generally covert channels). Thus if no leaks occur we are left without any guarantees.

In this chapter we aim to combine the expressive power of the security policies in the shared resource matrix approach with the strong end-to-end guarantee of non-interference. Arguments regarding the inapplicability of noninterference in the setting of many real systems have been raised [RMMG01]. One approach that has been relatively successful in dealing with this issue is introducing trusted components that are allowed to break the security policies, often referred to as intransitive noninterference [HY86, Rus92, RG99]. The proposed policies and security property incorporate a notion of intransitive noninterference and extend it with constraints on the execution history of the program. Previously security policies for access control based on execution history [AF03, BN04, BDF05] have been investigated and shown to provide a natural approach to specifying security policies. Furthermore the proposed policies and security property must be placed within the setting of hardware descriptions. For this purpose we build on the semantics presented in Chapter 2.

## 3.1 Locality-based security policies

To protect confidentiality within a system, it is important to control how information flows so that secret information is prevented from being released on unintended channels. The allowed flow of information in a system is specified in a security policy. In this section we present a policy language based on graphs. Here vertices represent security domains, describing the resources available in the program. A security domain is related to sets of resources available in the considered system.

This model allows for the granularity of the mapping from resources to security domains to be very fine-grained. For example we can introduce a security domain for each resource. For improved precision we could partition the usage of a resource into lifetime periods and introduce a domain for each, hence having more than one security domain for each resource used in the program. This would allow us to abstract from e.g. reuse of limited resources in the implementation, instead of introducing new gates for each lifetime period of a signal, and

thereby potentially increasing the size of the gate layout quadratically [HS06].

In our setting the variables and signals are our resources, hence they are related to security domains. This allows us to reason about groups of resources together, as well as singling out specific resources and isolate these in their own security domains. The security policies therefore focus on the information flow between intended domains of resources. Consequently we assume that variables and signals can be uniquely mapped to security domains.

**Definition 3.1** (Security Domains) For a given program we have a mapping from variables and signals  $Var \cup Sig$  to security domains V

$$\underline{\cdot}: Var \cup Sig \rightarrow V$$

We write  $\underline{x}$  and  $\underline{s}$  for the security domain of the variable x and signal s, respectively.

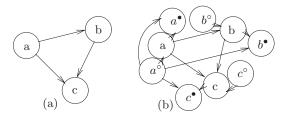

As stated above the security policies are based on graphs. Therefore the edges specify permitted flows of information. Information flow between resources can be restricted subject to fulfilment of constraints with respect to certain events taking place prior to the flow. Formally we propose the following definition of security policies.

**Definition 3.2** (Locality-based security policies) A security policy is a labelled graph  $G = (V, \lambda)$ , consisting of a set of vertices V representing security domains and a total function  $\lambda$  mapping pairs of vertices to labels  $\lambda : V \times V \to \Delta$ . We define  $\mathbb{G}$  to be the set of policies. The structure,  $\Delta$ , of labels is defined below.

In a flow graph the set of vertices V represent security domains. A security domain indicates the usage of a resource in the system. The edges in the flow graph describe the allowed information flow between resources. Hence an edge from the vertex for security domain  $v_1$  to the vertex for security domain  $v_2$  indicates that information is allowed to flow between the resources in these domains subject to the label attached to the edge.

The edges are labelled with constraints that the program must fulfill in order for the flow of information to be permitted. These constraints will include restrictions with respect to localities in the program. Hence we will consider local flows permitted in specific processes or blocks. Each process and block is uniquely referenced by identifiers Id that we map to security localities.

**Definition 3.3** (Security Localities) For a given program we have a mapping

from identifiers Id to security localities L

$$\underline{\cdot}: Id \rightarrow L$$