Technical University of Denmark

### De-embedding and Modelling of pnp SiGe HBTs

Hadziabdic, Dzenan; Jiang, Chenhui; Johansen, Tom Keinicke; Fischer, G.G.; Heinemann, B.; Krozer, Viktor *Published in:*

Proceedings of the 2nd European Microwave Integrated Circuits Conference

Link to article, DOI: 10.1109/EMICC.2007.4412682

Publication date: 2007

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Hadziabdic, D., Jiang, C., Johansen, T. K., Fischer, G. G., Heinemann, B., & Krozer, V. (2007). De-embedding and Modelling of pnp SiGe HBTs. In Proceedings of the 2nd European Microwave Integrated Circuits Conference (pp. 195-198). IEEE. DOI: 10.1109/EMICC.2007.4412682

## DTU Library Technical Information Center of Denmark

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# De-embedding and Modelling of pnp SiGe HBTs

D. Hadziabdic<sup>1</sup>, C. Jiang<sup>1</sup>, T. K. Johansen<sup>1</sup>, G.G. Fischer<sup>2</sup>, and B. Heinemann<sup>2</sup>, V. Krozer<sup>1</sup>

<sup>1</sup> ElectroScience, Oersted-DTU, Technical University of Denmark

Oersteds Plads 348, 2800 Kgs. Lyngby, Denmark

<sup>1</sup>dh@oersted.dtu.dk

$^{2}IHP$

Im Technologiepark 25, D-15236 Frankfurt (Oder), Germany <sup>2</sup>gerhard.fischer@ihp-microelectronics.com

Abstract— In this work we present a direct parameter extraction procedure for SiGe pnp heterojunction bipolar transistor (HBT) large-signal and small-signal models. Test structure parasitics are removed from the measured small-signal parameters using an open-short de-embedding technique, improved to account for the distributed nature of the interconnect lines. Good agreement is achieved between the small-signal model of the HBT and the measurements. Parameters for the large-signal VBIC model are extracted based on multi-bias small-signal model extraction, leading to consistency between measured and modeled  $f_T$ .

#### I. INTRODUCTION

A complementary BiCMOS (CBiCMOS) technology is a promising approach to achieve low voltage supply, low power consumption and high speed simultaneously in millimetrewave applications. The main challenge to develop such a process is to integrate high performance pnp transistors in a BiCMOS technology. IHP's 0.25  $\mu$ m SiGe:C CBiCMOS process offers a successful combination of npn HBTs with  $f_T/f_{max}$  of 170/170GHz and pnp HBTs with  $f_T/f_{max}$  of 90/120GHz (drawn emitter area: 0.22×0.84  $\mu$ m<sup>2</sup>) [1].

Successful circuit design using this technology requires accurate circuit models for both transistor types. Modelling of npn SiGe HBT devices has been a wide area of research [3]-[5]. In this paper, we focus on the modelling of the pnp HBTs.

An accurate de-embedding of the test structure parasitics is firstly implemented to improve HBT model accuracy. Hereafter, the de-embedded measurement results are applied for a direct parameter extraction of the small-signal equivalent circuit parameters. The model is verified by comparison of the simulated and measured results up to 49 GHz. The smallsignal model is utilized for parameter extraction for the largesignal VBIC95 model. The VBIC95 model [6] includes several advantages compared to the SPICE Gummel-Poon model: improved Early-effect modelling, quasi saturation, substrate and oxide parasitics, avalanche-multiplication and self-heating behaviour – all of which are important for accurate modelling of modern SiGe HBTs.

Finally, the VBIC model is experimentally verified against the measurements.

#### II. DE-EMBEDDING OF THE TEST STRUCTURE

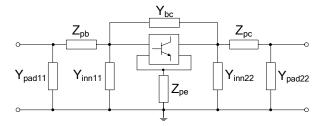

A three-step de-embedding method reported in [2] is employed to remove the contribution of the test structure parasitics. This method is further developed here to account for the distribution of the interconnect lines of the test structure. The equivalent circuit for the test structure including the transistor is shown in Fig. 1. Elements  $Y_{innxx}$  and  $Y_{padxx}$ , model the distributed coupling of the interconnect lines and the pads to the ground. Coupling between the pads through the substrate is negligible due to the presence of the ground shield.  $Y_{bc}$  is therefore assumed to be the only transmission element in the open structure. Two loading admittances of the two respective pads together with the corresponding interconnect lines are represented as the elements of the admittance matrix  $Y_{line}$ , as

$$Y_{line} = \begin{bmatrix} Y_{open11} + Y_{open21} & 0\\ 0 & Y_{open22} + Y_{open12} \end{bmatrix}$$

(1)

where  $Y_{openxx}$  are measured admittance matrix elements of the open standard. An empirical factor *n* is introduced to divide the  $Y_{line}$ , into  $Y_{pad}$  and  $Y_{inn}$  admittance matrices as

$$Y_{pad} = Y_{line} \cdot n ; \qquad Y_{inn} = Y_{line} \cdot (1-n) , \qquad (2)$$

where contribution of series impedances  $Z_{pb}$  and  $Z_{pc}$  to  $Y_{line}$  at low frequencies is assumed to be negligible. Series impedance elements,  $Z_{pb}$ ,  $Z_{pc}$  and  $Z_{pe}$ , are extracted as

$$Z_p = \left(Y_{short} - Y_{pad}\right)^{-1} \tag{3}$$

$$Z_{pe} = Z_{p12} \tag{4}$$

$$Z_{pb} = (Z_{p11} - Z_{p21}) \cdot n_{shift}$$

(5)

$$Z_{pc} = \left( Z_{p22} - Z_{p12} \right) / n_{shift}$$

(6)

where  $Y_{short}$  is the admittance matrix of the short standard measurement, and  $n_{shift}$  is introduced to correct a deembedding error, as will be explained later.

Fig. 1 Equivalent circuit model for the HBT test structure

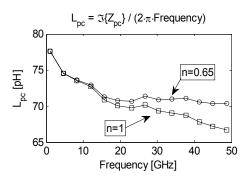

The factor *n* in (2) is found from the frequency dependence of the inductive part of  $Z_{pb}$  and  $Z_{pc}$ , which both can be modelled as a series-connected inductor and resistor. As shown in Fig. 2,  $L_{pc}$  is nearly frequency independent when *n*=0.65, meaning that only ~65% of  $Y_{line}$  admittance is due to the physical pad. Reduced frequency dependence is correspondingly observed in the extracted small-signal equivalent circuit element values of the HBT discussed.

Fig. 2 Extracted inductances of the interconnect line on the collector side

## III. EXTRACTION OF THE SMALL-SIGNAL EQUIVALENT CIRCUIT PARAMETERS

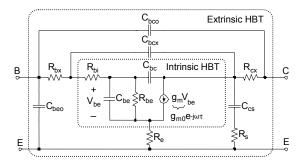

The small-signal equivalent circuit for the pnp SiGe HBT is shown in Fig. 3 [3]. The bias dependent intrinsic part describes the active device, while the extrinsic part represents the device parasitics.

Fig. 3 Small-signal equivalent circuit of a SiGe HBT biased in forward active mode operation

#### A. Oxide Capacitances

The total base-emitter and base-collector capacitances,  $C_{in}$  and  $C_{fb}$ , have been extracted from the Y-parameters of an HBT biased in the cut-off mode operation [3]. They are modelled in VBIC as sums of the fixed oxide capacitances and bias dependent junction capacitances,

$$C_{in} = C_{beo} + \underbrace{\frac{C_{be}}{C_{je}}}_{\left(1 - \frac{V_{be}}{P_e}\right)^{M_e}}; \quad C_{fb} = C_{bco} + \underbrace{\frac{C_{bc} + C_{bcx}}{C_{jc} + C_{jep}}}_{\left(1 - \frac{V_{bc}}{P_c}\right)^{M_c}}$$

(7)

respectively, where  $C_{je}$  and  $C_{jc}$  are zero-bias depletion capacitances,  $P_e$  and  $P_c$  are built-in potentials and  $M_e$  and  $M_c$ are grading terms of the two respective junctions.  $C_{bcx}$  is the extrinsic base-collector zero-bias depletion capacitance. The parameters are extracted by fitting the two curves,  $(C_{fb}-C_{bco})$ vs.  $(1-V_{bc}/P_c)$  and  $(C_{in}-C_{beo})$  vs.  $(1-V_{be}/P_e)$  respectively, to straight lines in double logarithmic plots [4].

#### B. Fixed Access Resistances and Inductances

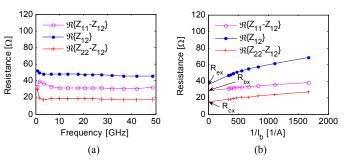

HBTs in saturation can be represented by a simple Tnetwork of resistors corresponding to access resistances  $R_{bx}$ ,  $R_{cx}$ , and  $R_e$  in Fig. 3. These resistors are found from the deembedded Z-parameters at these bias conditions after removal of the fixed oxide capacitances as

$$R_{bx} = \Re\{Z_{11} - Z_{12}\}$$

(8)

$$R_e = \Re\{Z_{12}\} \tag{9}$$

$$R_{cx} = \Re \{ Z_{22} - Z_{12} \}.$$

(10)

The values of these resistors in deep saturation ( $I_B=3mA$ ) are not varying with frequency, as depicted from Fig. 4(a), over a large frequency range. The fixed resistances are found from extrapolation of the values in (8) at large base currents as shown in Fig. 4(b).

Fig. 4 (a) Extracted values of equations (8)-(10) at  $I_{\rm B}$ =3mA and  $I_{\rm E}$ = $I_{\rm C}$ =1.5mA. (b) Determination of  $R_{bx}$ ,  $R_{cx}$ , and  $R_e$  from extrapolation of the Z-parameters.

Total access inductances of base and collector can be extracted as in (8)-(10) by using the imaginary part of the impedances. Negative collector inductance and relatively large base inductance are derived using this procedure. This indicates that the probes in the measurement setup could have been slightly shifted towards the collector side compared to the probe location in the short standard measurements. Adding 4 *pH* to the collector inductance and subtracting the same from the base inductance would balance both inductances. This error is compensated by the factor  $n_{shij}$ =1.06 in (5) and (6), since the compensating inductance corresponds to ~6% of the inductance of the access lines. After the compensation, the two access inductances have become negligibly small, 1.5 *pH*, and have therefore been omitted from the equivalent circuit.

### C. Substrate Parasitics

After the oxide capacitances and the fixed resistances in base and collector have been removed, the elements of the parasitic substrate transistor can be extracted through the Yparameters of HBTs in cut-off mode operation [3]. Neglecting the  $R_e$  in Fig. 3, the substrate resistance  $R_s$  and the collectorsubstrate capacitance  $C_{cs}$  have been extracted as

$$R_{s} = \Re\left(\frac{1}{Y_{22} + Y_{12}}\right); \qquad \omega C_{cs} = -\left\{\Im\left(\frac{1}{Y_{22} + Y_{12}}\right)\right\}^{-1}.$$

(11)

The extracted  $C_{cs}$  is fitted to the usual depletion capacitance expression, excluding the oxide capacitance term and using the corresponding VBIC parameters,  $M_s$ ,  $P_s$  and  $C_{jcp}$ .

#### D. Hybrid- $\pi$ Equivalent Circuit Modelling

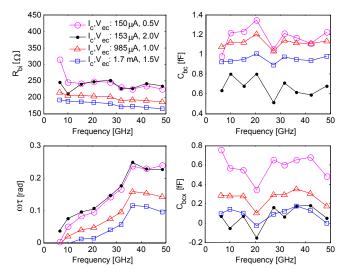

The intrinsic HBT shown in Fig. 3 exhibits the well-known hybrid- $\pi$  topology. The elements are extracted analytically from Y-parameters after removing the extrinsic part of the HBT except  $C_{bcx}$  using the method reported in [5]. Some extracted elements vs. frequency are shown in Fig. 5.

Fig. 5 Frequency dependence of the extracted elements for the hybrid- $\pi$  circuit at four bias points

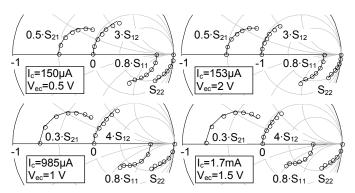

Fig. 6 Measured (o) and modelled (-) s-parameters in frequency range 0-49 GHz for the two parallel-connected HBTs biased in forward active region.

TABLE 1 EXTRACTED SMALL-SIGNAL MODEL ELEMENT VALUES

| Fixed elements |               |                        |                 |                |                |  |  |  |  |

|----------------|---------------|------------------------|-----------------|----------------|----------------|--|--|--|--|

| Cbco           | Cbeo          | <b>R</b> <sub>bx</sub> | R <sub>ex</sub> | R <sub>e</sub> | R <sub>s</sub> |  |  |  |  |

| [ <b>fF</b> ]  | [ <b>f</b> F] | [Ω]                    | [Ω]             | [Ω]            | $[\Omega]$     |  |  |  |  |

| 2.4            | 1.75          | 29                     | 14.6            | 36             | 500            |  |  |  |  |

| I [m A]                                      | Bias dependent elements |                        |                         |                         |           |                         |                          |                         |  |

|----------------------------------------------|-------------------------|------------------------|-------------------------|-------------------------|-----------|-------------------------|--------------------------|-------------------------|--|

| I <sub>c</sub> [mA]<br>/ V <sub>ec</sub> [V] | C <sub>cs</sub><br>[fF] | R <sub>bi</sub><br>[Ω] | g <sub>m0</sub><br>[ms] | C <sub>bc</sub><br>[fF] | τ<br>[ps] | C <sub>be</sub><br>[fF] | C <sub>bcx</sub><br>[fF] | R <sub>be</sub><br>[kΩ] |  |

| 0.15/0.5                                     | 2.1                     | 230                    | 5.2                     | 0.97                    | 0.53      | 10                      | 0.70                     | 21                      |  |

| 0.153/2                                      | 1.8                     | 231                    | 5.5                     | 0.41                    | 0.58      | 9.6                     | 0.25                     | 8.8                     |  |

| 0.985 /1                                     | 1.9                     | 190                    | 28                      | 0.88                    | 0.07      | 39                      | 0.31                     | 0.72                    |  |

| 1.7/1.5                                      | 1.8                     | 170                    | 48                      | 0.71                    | 0         | 70                      | 0.1                      | 0.25                    |  |

Comparison between the measured and the small-signal modelled S-parameters is shown in Fig. 6. Excellent agreement under various bias conditions is achieved in a wide frequency range. Simulated curves in Fig. 6 are based on extracted element values listed in Table 1.

#### IV. PARAMETER EXTRACTION FOR VBIC MODEL

Some of the extracted small-signal element values, like oxide capacitances, access resistances and parasitic substrate resistance have been directly used as parameters of the large-signal VBIC model. Collector-base depletion capacitance term in (7) at zero-bias is partitioned into  $C_{jc}$  and  $C_{jep}$  using the extracted  $C_{bc'}/C_{bcx}$  ratio of ~7 at the peak cut-off frequency. Partitioning of the total base current of the reverse Gummel-plot into intrinsic base-collector current  $I_{bc}$ , and parasitic base-emitter current  $I_{bep}$  is based upon the same ratio.

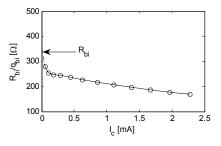

The extracted values for the intrinsic base resistance plotted versus collector current are shown in Fig. 7. The base resistance in the VBIC model is modulated by the normalized base charge  $q_b$ . The value extrapolated at the zero-current is used as  $R_{bi}$  in the VBIC model since  $q_b$  approaches unity there.

Fig. 7 Extracted intrinsic base resistance versus collector current at  $V_{ec}$ =1.5 V.

From the average slope of the  $\omega\tau$  plot in the Fig. 5 it appears that the extracted excess phase delay  $\tau$  falls with increasing collector current. The reason is that the basecollector reverse voltage and hence the collector depletion width, which contribute to the total transit time, decrease. Since the excess phase delay in the VBIC model is independent on the bias, an average value of 0.4 ps is used for the excess phase delay parameter  $T_d$ . Such a low value for the excess phase delay has only little impact on the small-signal behaviour well below the cut-off frequency  $f_T$ .

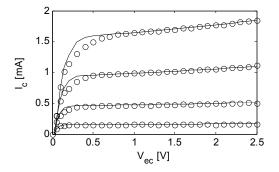

Quasi-saturation-parameters,  $R_{ci}$ , Gamma,  $V_0$  and  $H_{rcf}$ , are found by fitting the collector current  $I_c$  versus emittercollector voltage  $V_{ec}$  curves, as shown in Fig. 8. The resulting value of  $R_{ci}$  was 95  $\Omega$ .

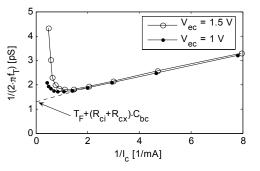

Subsequently, the forward transit time parameter  $T_F$ , which describes the hole transport through the base region and the collector depletion region, is estimated by extrapolation of the plot of the measured forward transit time vs. inverse collector current as illustrated in Fig. 9. The  $(R_{cx}+R_{ci})\cdot C_{bc}$  term accounts for a contribution from the parasitic collector resistance.

Fig. 8 Measured (o) and modelled (-) output characteristics at the base-emitter voltage swept from -0.85 to -1V in 50 mV steps

Fig. 9 Measured transit time vs. inverse collector current at two emitter-collector voltages  $V_{ec}$ .

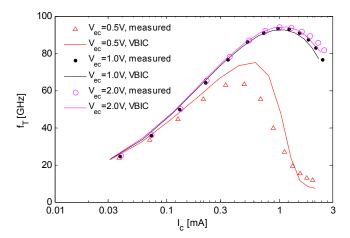

Finally, the parameters  $X_{tf}$ ,  $V_{tf}$ ,  $I_{tf}$  and  $Q_{tf}$ , which determine the transit time bias dependence, are determined from the  $f_T$  - $I_C$  curves shown in Fig. 10. Behaviour of the collector-base heterojunction was not captured by the VBIC with a high accuracy. Using an  $R_{cl}=200\Omega$  in the parameter extraction would have yielded a remarkably better fit of the output characteristics in the quasi-saturation region as well as of the  $f_T$  -  $I_C$  curve at  $V_{ec}=0.5V$ . This resistance is however much larger than expected from the layer properties of the structure.

Fig. 10 Measured and modelled bias dependency of the cut-off frequency

#### V. CONCLUSIONS

This work focuses on modelling of high performance SiGe pnp HBT devices. Parasitics of the test structure are deembedded taking into account distributed impedance of the interconnect lines. A de-embedding error resulting from the probe positioning inaccuracies is corrected. The elements of the small-signal equivalent circuit of the HBT are analytically extracted leading to an excellent agreement between the model and the measurements. The small-signal model has also shown to be beneficial for extraction of the VBIC model parameters. It was not possible to accurately model the transistor action in quasi-saturation, while simultaneously keeping the physical meaning of the VBIC parameters.

#### REFERENCES

- B. Heinemann, R. Barth, D. Knoll, H. Rucker, B. Tillack, and W. Winkler, *High-Performance BiCMOS Technologies without Epitaxially-Buried Subcollectors and Deep Trenches*, Semiconductor Science and Technology, issue 1, S153-S157, 2007

- [2] H. Cho and D. E. Burk, A Three-Step Method for the De-Embedding of High-Frequency S-Parameter Measurement, IEEE Trans. Electron Devices, Vol. 38(6): 1371-1375, June 1991.

- [3] T. K. Johansen, J. Vidkjær, and V. Krozer, Substrate Effects in SiGe HBT Modeling, in Proc. GAAS2003, Oct 2003, pp. 445-448.

- [4] T. K. Johansen, J. Vidkjær, and V. Krozer, Consistent Large-Signal Modeling of SiGe HBT Devices, in Proc. GAAS2004, pp. 423-426.

- [5] B.-S. Kim, C. Park, I.–H. Park, W.-S. Nah, and Y.-J. Yoon, Analytic Determination of Hybrid π Equivalent Circuit Parameters of SiGe HBTs Using Admittance Equations, in Asia-Pacific Microwave Conference 2002 pp. 466-469.

- [6] C. C. McAndrew et al., "VBIC95, the Vertical Bipolar Inter-Company Model," *IEEE Journal of Solid-State Circuits*, Vol. 31, Issue 10, pp. 1476-1483, Oct. 1996.