### Behavioral Synthesis of Asynchronous Circuits

Ph.D. thesis by Sune Fallgaard Nielsen

Computer Science and Technology Informatics and Mathematical Modelling Technical University of Denmark

This dissertation is submitted to Informatics and Mathematical Modeling at the Technical University of Denmark in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

The work has been supervised by Associate Professor Jens Sparsø and Professor Jan Madsen.

Kgs. Lyngby, December 31, 2004

Sune Fallgaard Nielsen

<u>ii</u>

## Resumé

Denne afhandling presenterer en metode for behavioral syntese af asynkrone kredsløb. Målet er at tilvejebringe et syntese flow, som udnytter og overfører metoder fra synkrone kredsløb til asynkrone kredsløb. Ideen er at flytte den synkrone behavioral syntese abstration ind i det asynkrone handshake domæne ved hjælp af en beregnings model, som ligner den synkrone datavej og kontrolenheds struktur, men som er fuldstændig asynkron.

Denne model indeholder muligheden for at isolerer enkelte eller alle beregningselementer ved at låse deres respektive inputs og outputs når beregningselementer er inaktivt. Dette reducerer unødvendig skifteaktivitet i de enkelte beregningselementer og derved energiforbruget af hele kredsløbet. En samling af behavioral syntese algoritmer er blevet udviklet, som tillader designeren at foretage design space exploration bestemt af både power- og udførelsestids-krav. Datavej og kontrol arkitekturen bliver derefter udtrykt i Balsa-sproget, og syntaks styret oversættelse anvendes til at konstrurere det tilhørende asynkrone handshake kredsløb (og evt. endeligt et layout).

# Abstract

This thesis presents a method for behavioral synthesis of asynchronous circuits, which aims at providing a synthesis flow which uses and tranfers methods from synchronous circuits to asynchronous circuits. We move the synchronous behavioral synthesis abstraction into the asynchronous handshake domain by introducing a computation model, which resembles the synchronous datapath and control architecture, but which is completely asynchronous. The model contains the possibility for isolating some or all of the functional units by locking their respective inputs and outputs while the functional unit is idle. This reduces unnecessary switching activity in the individual functional units and therefore the energy consumption of the entire circuit. A collection of behavioral synthesis algoritms have been developed allowing the designer to perform time and power constrained design space exploration. The datapath and control architecture is then expressed in the Balsa-language, and using syntax directed compilation a corresponding handshake circuit implementation (and eventually a layout) is produced.

# Acknowledgments

Many people have helped me to arrive at this point, all of whom I am grateful to.

# Contents

| 1        | Introduction   |                        |                                                                           |  |  |  |

|----------|----------------|------------------------|---------------------------------------------------------------------------|--|--|--|

|          | 1.1            | From                   | synchronous to asynchronous behavioral synthesis $\ldots \ldots \ldots 3$ |  |  |  |

|          | 1.2            | Thesis                 | outline and readers guide                                                 |  |  |  |

| <b>2</b> | Bac            | kgrou                  | nd 9                                                                      |  |  |  |

|          | 2.1            | $\operatorname{Synth}$ | esis flow and CDFG format                                                 |  |  |  |

|          | 2.2            | Behav                  | ioral synthesis                                                           |  |  |  |

|          |                | 2.2.1                  | ASAP and ALAP                                                             |  |  |  |

|          | 2.3            | Async                  | hronous circuit design                                                    |  |  |  |

| 3        | $\mathbf{Rel}$ | ated V                 | Vork 21                                                                   |  |  |  |

|          | 3.1            | Low p                  | ower behavioral synthesis, an overview                                    |  |  |  |

|          |                | 3.1.1                  | Lower bounds on switching activity                                        |  |  |  |

|          |                | 3.1.2                  | Reducing switching activity of functional units                           |  |  |  |

|          |                | 3.1.3                  | Reducing switching activity at CDFG level                                 |  |  |  |

|          |                | 3.1.4                  | Memory allocation for low-power                                           |  |  |  |

|          |                | 3.1.5                  | Interconnect design for low-power                                         |  |  |  |

|          | 3.2            | Async                  | hronous behavioral synthesis, an overview                                 |  |  |  |

|          | 3.3            | Async                  | hronous logic synthesis                                                   |  |  |  |

|          | 3.4            | Async                  | hronous behavioral synthesis                                              |  |  |  |

|          |                | 3.4.1                  | Partitioned controllers                                                   |  |  |  |

|          |                | 3.4.2                  | syntax-directed synthesis                                                 |  |  |  |

|          |                | 3.4.3                  | Synthesis of Asynchronous Circuits                                        |  |  |  |

|          |                | 3.4.4                  | Desynchronization                                                         |  |  |  |

|          |                | 3.4.5                  | Variable length time-slot behavioral synthesis                            |  |  |  |

|          | 3.5            | Summ                   | ary                                                                       |  |  |  |

| 4 | Behavioral Synthesis for Asynchronous Circuits |                                                                     |     |  |  |  |

|---|------------------------------------------------|---------------------------------------------------------------------|-----|--|--|--|

|   | 4.1                                            | From synchronous to asynchronous behavioral synthesis               | 39  |  |  |  |

|   | 4.2                                            | Asynchronous behavioral synthesis                                   | 45  |  |  |  |

|   | 4.3                                            | Datapath synthesis                                                  | 47  |  |  |  |

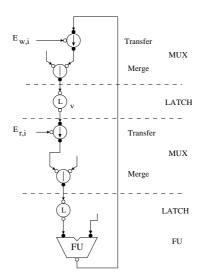

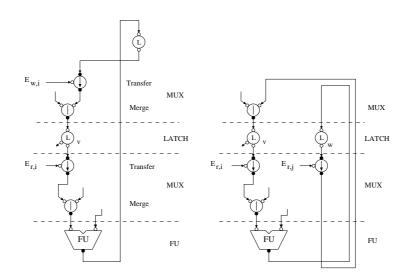

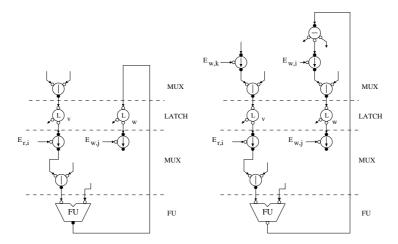

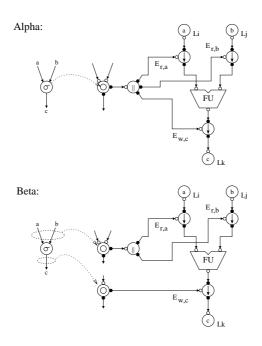

|   |                                                | 4.3.1 Datapath with out input/output FU latches (alpha)             | 48  |  |  |  |

|   |                                                | 4.3.2 Datapath with input/output FU latches (beta)                  | 51  |  |  |  |

|   |                                                | 4.3.3 Datapath with mixed input/output FU latches (gamma)           | 54  |  |  |  |

|   | 4.4                                            | Summary                                                             | 56  |  |  |  |

| 5 | Implementation in Balsa 57                     |                                                                     |     |  |  |  |

|   | $5.1^{-1}$                                     | Program structure                                                   | 57  |  |  |  |

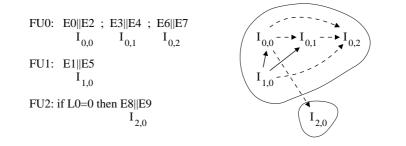

|   | 5.2                                            | Events: using functional units                                      | 60  |  |  |  |

|   | 5.3                                            | Implementing a schedule                                             | 61  |  |  |  |

|   | 5.4                                            | Implementing the architecture                                       | 63  |  |  |  |

|   | 5.5                                            | Optimizations                                                       | 67  |  |  |  |

|   | 5.6                                            | Summary                                                             | 70  |  |  |  |

| 6 | Alg                                            | orithms for Behavioral Synthesis                                    | 73  |  |  |  |

|   | 6.1                                            | Power-aware scheduling                                              | 74  |  |  |  |

|   |                                                | 6.1.1 Problem formulation                                           | 75  |  |  |  |

|   |                                                | 6.1.2 Power heuristic scheduling                                    | 75  |  |  |  |

|   |                                                | 6.1.3 Power and time constrained synthesis                          | 77  |  |  |  |

|   | 6.2                                            | Implementing synchronous power aware schedules in asynchronous cir- |     |  |  |  |

|   |                                                | cuits                                                               | 81  |  |  |  |

|   | 6.3                                            | Simulated annealing and evolutionary algorithm                      | 82  |  |  |  |

|   |                                                | 6.3.1 Problem formulation                                           | 82  |  |  |  |

|   |                                                | 6.3.2 Representation and feasibility                                | 84  |  |  |  |

|   |                                                | 6.3.3 Simulated annealing                                           | 85  |  |  |  |

|   |                                                | 6.3.4 Evolutionary algorithm                                        | 86  |  |  |  |

|   | 6.4                                            | Control data flow graph synthesis                                   | 88  |  |  |  |

|   | 6.5                                            | Summary                                                             | 92  |  |  |  |

| 7 | $\mathbf{Res}$                                 | ults                                                                | 93  |  |  |  |

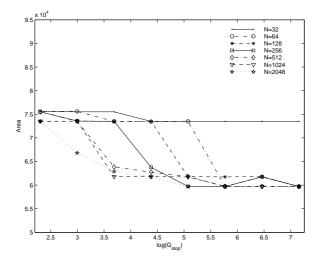

|   | 7.1                                            | Results for power aware scheduling                                  | 94  |  |  |  |

|   | 7.2                                            |                                                                     | 96  |  |  |  |

|   | 7.3                                            | Results for asynchronous behavioral synthesis                       | 99  |  |  |  |

|   |                                                | 7.3.1 GCD                                                           | 101 |  |  |  |

|   |                                                | 7.3.2 Benchmarks                                                    | 102 |  |  |  |

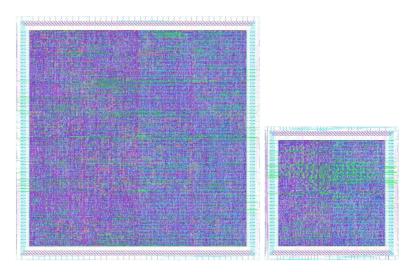

|   |                                                | 7.3.3 Layout results                                                |     |  |  |  |

|   | 7.4                                            | Summary                                                             | 105 |  |  |  |

| 8 | Con                                            | clusion                                                             | 109 |  |  |  |

|   | 8.1                                            | Advantages of the approach                                          |     |  |  |  |

|   | 8.2                                            | Perspective on the approach                                         |     |  |  |  |

|   | 8.3                                            | Future directions                                                   |     |  |  |  |

x

Bibliography

113

xi

### CHAPTER 1

## Introduction

Today, a wide range of dedicated real-time applications are emerging. Examples of these are the next generation of mobile phones, smart-cards and more futureristic applications as e-identification, e-payment, e-key systems etc. For such portable wire-less applications power is a limited resource because of restrictions in battery size or because power is extracted from the environment (light, magnetic fields or heat etc.). Furthermore, to meet the extreme size and weight requirements the entire system (input/output transducers, analog circuitry, futuristic-circuitry, power supply and the digital system, consisting of digital hardware and software) is implemented onto one single chip ("System on Chip").

The focus of this research is the hardware part of the digital system, which operates under the following difficult characteristics:

- **Data Processing** The applications are reactive in nature with data arriving in bursts with long periods of waiting. In-between bursts ultra low-power operation is required, while during bursts heavy computation, such as encryption for secure data transmission, is required.

- **Response Time** For some applications the time to respond to an external event is crucial as otherwise data will be irrevocably lost, requiring a close to zero transition time from sleep mode into full-speed operation.

- **Power Supply** For battery-less applications external power is provided spuriously by the environment and stored internally on large storage capacitors leading to a very limited power supply often of poor quality.

- Noise Level The presence of on-chip analog and RF-circuitry sets severe restrictions

for the electric-noise and electromagnetic-emission of the digital circuit such as not to disrupt input/output-interfacing or RF-communication.

Asynchronous design offers several advantages, compared to synchronous design, for the design of these intelligent circuits. The asynchronous design methodology specifically targets low-power operation (power is only used when processing) and the self-timed nature leads to an immediate response time. Furthermore asynchronous circuits are inherently insensitive (and thus robust) to variations in temperature, process parameters and supply voltage. The latter can be used advantageously since, if the circuit has access to external power, the supply voltage can be decreased allowing for ultra low-power operation. Finally, the asynchronous nature of the switching activity causes the electromagnetic and electric noise contributions to evenly distribute across the frequency spectrum (equivalent to white noise). This reduces spikes in the spectrum down to a level which allows co-existence with analog and RF-circuitry. Typically only critical subparts (with respect to operating characteristics) of the digital system will be implemented asynchronously and the remaining part synchronously.

Currently, the lack of synthesis methods and tools which are capable of directly synthesizing a working asynchronous circuit from a high-level specification makes the design of large systems a tedious effort involving more design work than designing a corresponding synchronous circuit. The majority of existing synthesis tools in this area are low-level and dedicated to the generation of control circuitry [24, 40, 71, 86, 92]. A few high-level synthesis tools exist, among those the Tangram silicon compiler developed by Philips Research Labs and the somewhat similar public domain version BALSA from Manchester University. These tools use special asynchronous hardware description languages dedicated to asynchronous design, that does not fit well into existing VHDL/SystemC based design flows and CAD-tools. Furthermore, the supported synthesis process, syntax-directed compilation, is characterized by a one-to-one correspondence between specification and implementation.

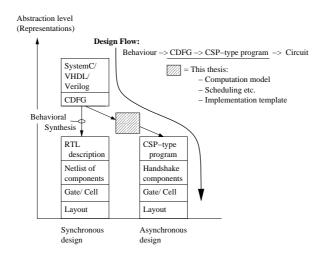

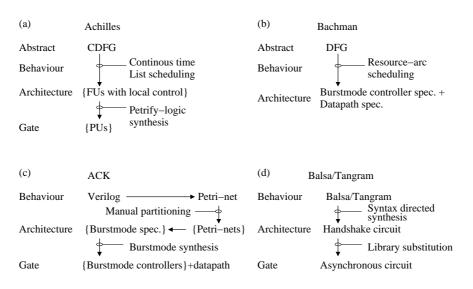

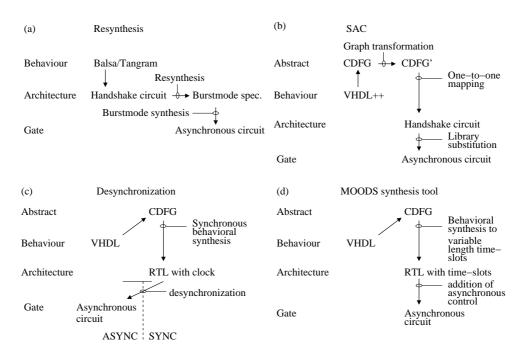

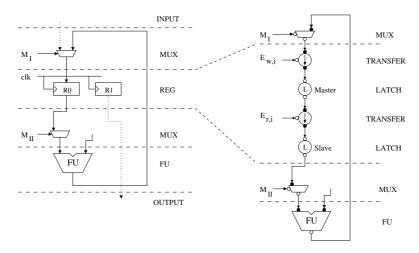

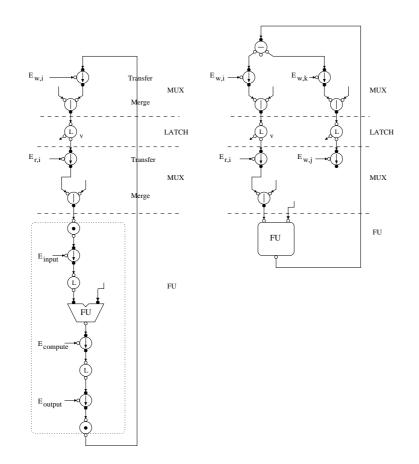

Let us begin by looking into the current status of synthesis flows of synchronous and asynchronous circuits as illustrated by Figure 1.1. Synthesis of synchronous circuits, which is illustrated in the left column of Figure 1.1, has succeeded in raising the level of abstraction to that of specifying circuits at the behavioral level. From a behavioral description in a language like VHDL, Verilog or System-C some intermediate representation is extracted – often a control data flow graph (CDFG). From the CDFG the classic synthesis tasks [67] of scheduling, allocation, and binding is performed resulting in a RTL level circuit description which is then synthesized into gate-level circuits and eventually a layout.

Synthesis of asynchronous circuits is illustrated in the right column of Figure 1.1. It is less mature and several somewhat different approaches is being pursued. The most influential of the available synthesis tools fall in two categories: (i) synthesis of large-scale RTL level circuits based on syntax-directed compilation from CSP-like languages: Tangram [11, 100], OCCAM [17], Balsa [8], ACK [59] and TAST [85], and (ii) synthesis of small-scale sequential control circuits [26, 41]. The tools that perform syntax directed compilation target a library of so-called handshake components.

Figure 1.1: Existing synchronous and asynchronous design flows and the design flow addressed in this thesis.

The handshake components can be designed using in principle any of the sequential control circuit synthesis tools. The syntax-directed compilation approach is radically different from the behavioral synthesis flow used by designers of synchronous circuits; the compiler merely performs a one-to-one mapping of the program text into a corresponding circuit structure. Although syntax-directed compilation does allow the designer to work at a relatively high level it does not provide any optimizations; "what you program is what you get". In some situations this can be considered an advantage but in general it puts more burden on the designer: exploring alternative implementations requires actually programming these, whereas in a traditional synchronous synthesis flow, the designer can quickly and easily experiment with different constraints and goals and in this way create alternative implementations from the same program text.

It is interesting to note that the internal representation of circuit behavior used in synchronous behavioral synthesis is actually based on an asynchronous model of a control dataflow graph (CDFG), i.e., a dependency graph expressing the controland data-flow of the application. This naturally raises the question: Is it possible to apply the transformations and optimizations used in synchronous synthesis for asynchronous design as well?

# 1.1 From synchronous to asynchronous behavioral synthesis

A central idea in this thesis is to construct a computation model which allows us to use the transformations and optimizations used in synchronous synthesis directly in

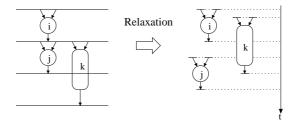

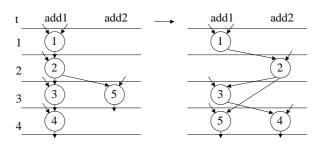

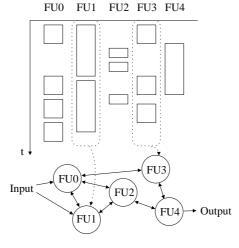

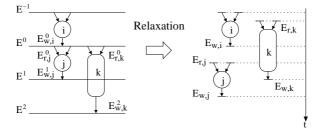

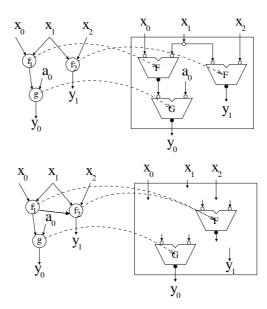

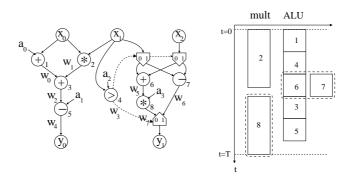

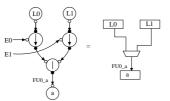

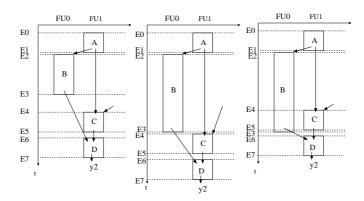

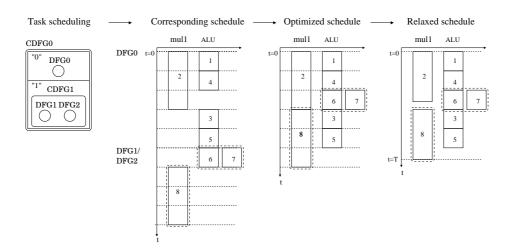

Figure 1.2: Relaxing synchronous synthesis (left) into the asynchronous handshake domain (right).

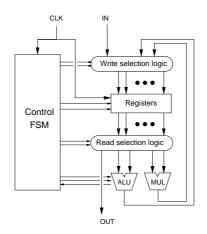

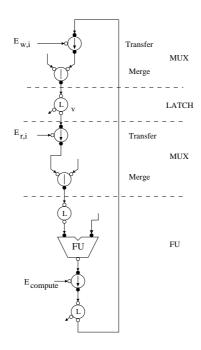

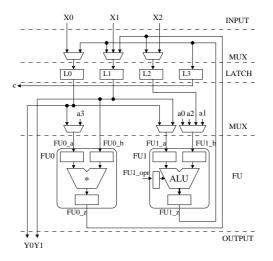

Figure 1.3: The synchronous computation model.

asynchronous design, without introducing any restrictions and at the same time use the transformations and optimizations developed for continuous time in one and the same model.

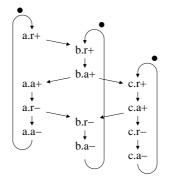

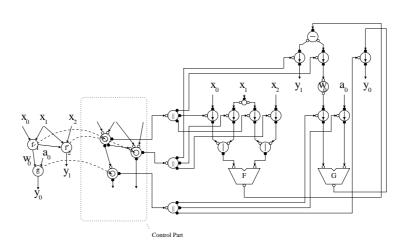

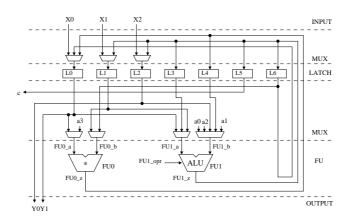

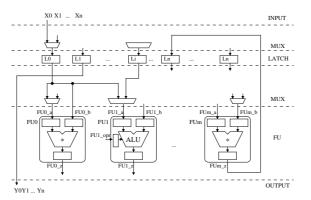

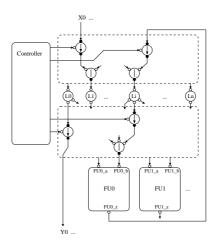

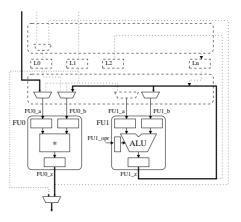

The target for synchronous behavioral synthesis is a hardware architecture consisting of a datapath which is able to perform a set of operations, and a controller which controls the execution sequence of these operations in order to perform a given application, as shown in Figure 1.3 A key issue in behavioral synthesis is to reuse hardware resources for the different operations in order to minimize area, and to explore possible parallelism by executing several hardware resources concurrently in order to increase performance.

All the traditional techniques of behavioral synthesis: Scheduling, Allocation and Binding are in synchronous circuits centered around a central synchronization event, determined by the global clock. This synchronization event determines (i) the beginning for executing an operation (ii) writing the result of an operation.

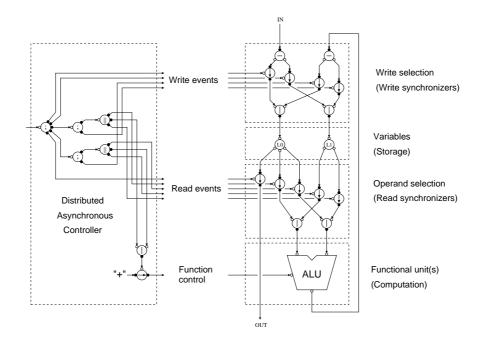

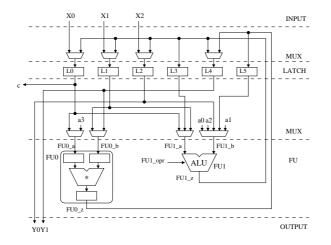

If we make these synchronization events local and controlled by the controller, we can create a hardware architecture consisting of a datapath and a controller, as

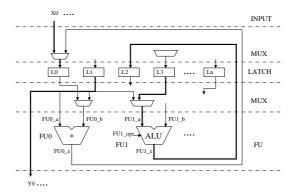

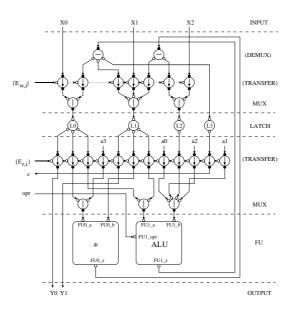

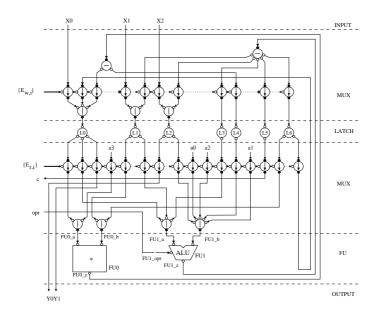

Figure 1.4: Computation model in the asynchronous handshake domain, where the labeling refers to the role the handshake components play in our model.

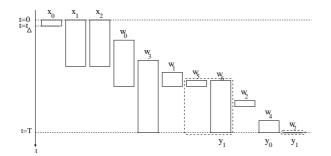

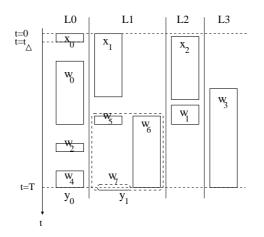

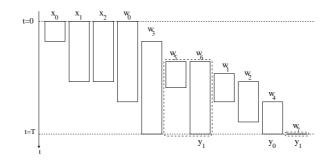

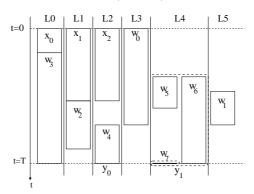

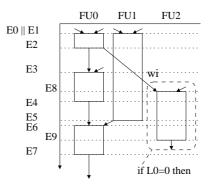

shown in Figure 1.4. It resembles the synchronous architecture but it is completely asynchronous. This computation model relaxes the strict ordering of the synchronous circuit and the synchronous schedule 1.2 (left) into the continuous time domain, the schedule for the asynchronous circuit 1.2 (right).

This idea allows us to use any of, but not restricted to, the many synchronous behavioral synthesis techniques to obtain a hardware architecture (datapath and controller) and then to implement this architecture using asynchronous circuit techniques.

In our work we use Balsa as a back-end. The datapath and control parts obtained from the front-end behavioral synthesis are described using a set of Balsa templates and then synthesized into handshake components and ultimately into a layout. In this way we take advantage of the fact that Balsa performs a one-to-one mapping thus allowing us to express the intended implementation at a relatively high level.

The parallism in CSP, and CSP-like languages, are centered around a parallel operator, that allows the computation to fork into parallel operations. However the construct also require all of these parallel operations to finish at the same time or have to wait until the slowest operation finishes. Therefore no new operations can begin, thus limiting the schedules that can be implemented. The implementation templates presented in this thesis is not restricted by this limitation. We utilize the CSP language constructs in an unconventional way, such that any continous schedule can be implemented.

Using this synthesis flow we have produced layouts for a couple of benchmarks and we report on the area, speed and power figures for these circuits. By building on top of syntax-directed compilation, our synthesis approach works entirely in the domain of handshake channels and handshake components. This has a number of significant implications: Firstly it enables the use of a synthesis flow which is surprisingly similar to that used in synchronous design tools, and secondly it avoids altogether the complex problem of specifying and synthesizing a controller. Our work is not in any way restricted to the use of Balsa or other syntax-directed methods, the used approach serves as a practical demonstration of how to use the developed methods and techniques.

For the behavioral synthesis part we have developed the following algorithm suite:

- (i) Power aware synchronous synthesis algorithm. This algorithm is a clique heuristic algorithm operating with a time and maximum power per time constraint. This is useful for applications having a power limit e.g. given by the maximum power delivered by a solar panel.

- (ii) Evolutionary synchronous synthesis algorithm and a simulated annealing synchronous synthesis algorithm. These are meta-heuristic algorithms operating with a maximum time constraint.

- (iii) Simulated Annealing task level algorithm for handling the conditional parts of the CDFG. This last algorithm has not been implemented but the method is outlined.

These algorithms all operate in discrete time using time-slots. After the final schedule has been obtained it is relaxed into an asynchronous schedule, keeping the order of execution events as a relative ordering.

The contribution of this thesis is the addition of behavioral synthesis to asynchronous circuit design in the form of automatic resource sharing and constraint based design space exploration. In particular our contributions are: (1) an abstract event based computation model, (2) synthesis algorithms for scheduling, allocation and binding and (3) target implementation specifications. The thesis publications are [74, 75, 93].

#### 1.2 Thesis outline and readers guide

This thesis is organized as follows:

- Chapter 1 Introduction Introduces this work, presents our contributions and shows this outline of the thesis.

- Chapter 2 Background Briefly introduces the ideas behind behavioral synthesis, CDFGs and asynchronous circuits.

- Chapter 3 Related Work Gives a survey of related work.

- Chapter 4 Behavioral Synthesis for Asynchronous Circuits Presents the concept which allows us to adapt the techniques from synchronous behavioral synthesis into behavioral synthesis of asynchronous design and describes details of datapath design.

- Chapter 5 Implementation in Balsa The use of the Balsa-language to generate our circuits is presented in this chapter.

- Chapter 6 Algorithms for Behavioral Synthesis The algorithms developed for behavioral synthesis used to generate the circuits are presented in this chapter.

- Chapter 7 Results The area, speed and power figures for our layouts are presented and discussed.

- Chapter 8 Conclusion contains the conclusion of the thesis and presents directions for future work.

As a reading guide, the reader who is familiar with asynchronous circuit design and behavioral synthesis and not interested in related work can skip chapter 2 Background and chapter 3 Related Work, and proceed directly to chapters 4 Behavioral Synthesis for Asynchronous Circuits, 5 Implementation in Balsa and 6 Algorithms for Behavioral Synthesis which presents the main contribution of this thesis. More specifically the underlying concepts of this work are introduced in 4 Behavioral Synthesis for Asynchronous Circuits. The circuit implementation details and Balsa-templates used to design the asynchronous circuits in the result section are presented in chapter 5 Implementation in Balsa. For the reader with an algorithmic interest chapter 6 Algorithms for Behavioral Synthesis presents the behavioral synthesis algorithms developed in this research. Finally, the reader is encouraged to read chapter 7 Results which explains and discusses the results.

### Снарте 2

# Background

This thesis brings together the domains of both behavioral synthesis and asynchronous circuit design. In order to be able to better understand the work presented in this thesis, this chapter will give an introduction to some of the concepts and ideas of these domains. The reader should not consider this to be a complete reference, nor to be a tutorial.

### 2.1 Synthesis flow and CDFG format

A CDFG captures only the control and data dependencies that are inherent in the computation. In this way it is not biased towards a certain implementation.

In this section we introduce the CDFG format and an example CDFG which will be used throughout in this thesis to illustrate the synthesis flow. The focus of the thesis is on the synthesis of asynchronous circuitry *given* a CDFG. The process of extracting the CDFG from a behavioral specification in some hardware description language is well understood. It is an integral part of existing synchronous synthesis systems, and it is not addressed in this thesis.

To illustrate the source code for our running example we will use the Balsalanguage [7, 8, 6], augmented with a multiplication operator, as the Balsa language does not yet include a multiplication operator. The aim in this thesis is not to advocate the use of Balsa, it should merely be seen as an illustration and in principle most hardware description languages could be used. For asynchronous circuit design it is convenient if the language includes channel communication primitives and statement level concurrency, and it is encouraging to see that such features are being included,

```

import [balsa.types.basic]

type word is 16 bits

procedure example(input X0,X1,X2:word;

output Y0, Y1:word) is

variable x0,x1,x2,y1,y0:word

constant a0= 255

constant a1= 255

constant a2= 255

constant a3= 255

begin

loop

XO \to xO || X1 \to x1 || X2 \to x2;

y0 := (((a0+x0)+(x0*x1)) - a1 as word) ||

if x1>a2 then

y1 := (a3*(x1+x2) as word)

else

y1:=(x1-x2 \text{ as word})

end ;

YO<-yO || Y1<-y1

end

end

```

Figure 2.1: An example Balsa description.

or at least proposed for inclusion in, such languages as System-C and System-Verilog and an additional package for adding such features to System-C is proposed in [13].

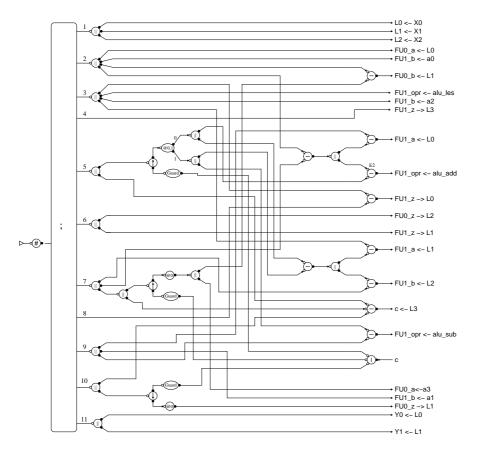

The intended synthesis flow involves the following steps: From the Balsa code the CDFG is exacted. The CDFG is then subject to the synthesis steps explained in this thesis and the resulting circuit structure (datapath and control) is expressed as a Balsa program. The final step of the synthesis flow is then to compile the Balsa program into a netlist of handshake components and to produce a standard cell implementation.

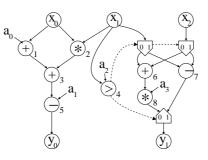

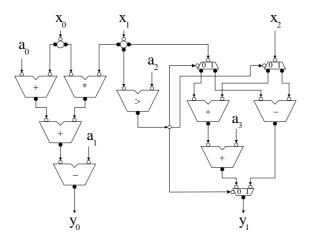

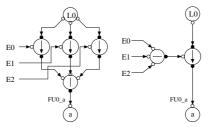

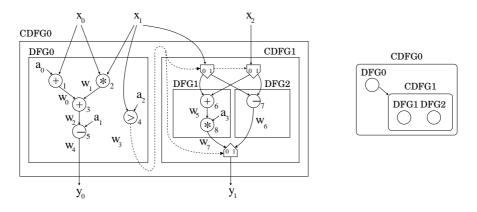

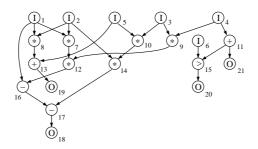

Figure 2.1 shows our example asynchronous component specified in Balsa and Figure 2.2 shows the corresponding CDFG which will serve as the running example in this paper. The elements of the CDFG and the structure are explained in the following. The CDFG is a 1-bounded colored Petri net – the colors representing data values. The edges in the CDFG contain places (like in a STG) and the nodes are Petri net transitions. A node can be an operator or can represent conditional sequencing as the example CDFG shows. For a more formal definition the reader is referred to [96, 33].

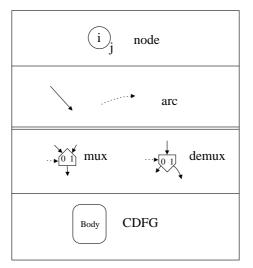

The basic elements in our CDFG are shown in Figure 2.3 and are as follows:

nodes Essential nodes represent atomic computations e.g. arithmetic operations as

Figure 2.2: The Control Data Flow Graph for our example.

addition. For firing a node, all inputs arcs need to have a data-token present. The i designates the operation the node performs and all nodes have a numbering j. This operation could also be the loading of data in and out of the circuit, in which case the name of the input/output is written inside the node. These nodes are called input/output nodes.

- **arcs** Represents the essential data dependencies which exist with in the computation or algorithm. The dotted arc is used to signify control arcs. There is no semantic difference between a data and control arc.

- There is a set of special nodes which needs explanation:

- **Control nodes** The mux and demux nodes are used to route data-tokens around in the CDFG. The mux node need a data-token on the control arc and then a data-token on the selected input arc to fire. The demux node only fires a data-token on the selected output.

- **Body** The body can be replaced by another CDFG and is not a fundamental component, rather it illustrates the hierarchical nature of the CDFG format. The input and output arcs of the CDFG are required to fit with the input and output arcs to the Body node.

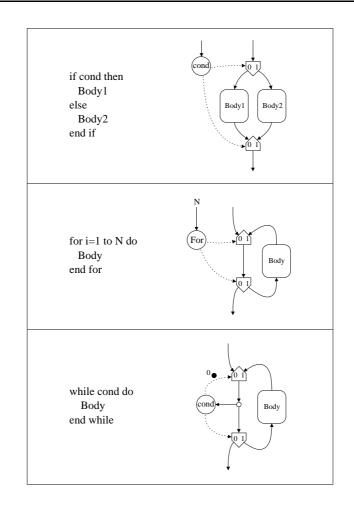

Using these fundamental nodes a sufficient set of algorithmic structures can be represented using the CDFGs. Figure 2.4 shows a set of basic algorithmic structures found in most languages and their corresponding CDFGs. Using these structures, the definition of the CDFGs nodes and our Balsa example in Figure 2.1 it is straightforward to arrive at the CDFG in Figure 2.2.

### 2.2 Behavioral synthesis

Behavioral synthesis is a refinement process in which a behavioral description of an algorithm is converted into a structural description, fulfilling a set of design constraints, and preserving the behavior of the algorithm [87, 67]. Each component

Figure 2.3: A minimum and, for most cases, sufficient set of Control Data Flow Graph elements.

in the structural description is in turn defined by its own (lower-level) behavioral description, for which a mapping to silicon hardware exists. The purpose of behavioral synthesis is two-fold: (i) Automate tedious parts of the design process and thus improve the turnaround time. (ii) To perform design space exploration.

Automating tedious parts of the design process is becoming increasingly important as designs increase in size and complexity, and the time alloted to construct the design becomes ever more tighter. Specifying the description of an algorithm at a higher level of abstraction allows a designer to focus on implementing an improved algorithm. It is well-known, that work put to use at a high-level of abstraction has a larger impact on the resulting performance characteristics, than work put to use at a lower-level of abstraction. Furthermore, the designer avoids spending time on details of the implementation e.g. transistor sizing, which of course has an impact on the performance but usually an order of magnitude less than improving the algorithm.

Design space exploration is also becoming increasingly important as modern systems are moving into System-on-Chip platforms where the design becomes part of a greater whole and thus needs to fit into certain specifications. This might mean that the maximal speed of the circuit is required if our circuit is part of the critical path of an entire system. But it might also be that requirements are low and thus there is no need to develop a large high-speed circuit.

The output from a high-level synthesis system usually consists of a datapath structure at the register-transfer level (RTL) or an equivalent description language, and a specification of a finite state machine to control the datapath. In our case we will use the Balsa language which will translate into a set of asynchronous handshake components for both the datapath and the ASFM. At the RT level or equivalent

Figure 2.4: Algorithm statements and corresponding CDFG structures.

level, a datapath is composed of a computational part (functional units e.g. ALUs, multipliers, and shifters etc.), storage units (registers, latches and memories) and interconnection units (e.g. busses, multiplexors and demultiplexors).

As previously discussed the first step is to extract a CDFG from the behavioral algorithm, part of this involves a series of compiler-like optimizations as code motion, dead code elimination, constant propagation, common subexpression elimination, and loop unrolling. Following this comes the core synthesis refinement process, of which there are two classes:

**Resource constrained behavioral synthesis** Here the goal is to find the fastest circuit given a set of resource constraints either in the form of a maximum allowable area for the circuit or a detailed description of the maximal number

and types of functional units and the maximum memory available to the circuit.

**Time constrained behavioral synthesis** Here the goal is to find the smallest circuit (computational area and memory) given a maximum execution time constraint.

In addition to these there is the power constraint which comes into play by adding to the two other constraints, reducing the solution space. In this thesis we will consider time and power constrained behavioral synthesis. The applications our research targets are performance-intensive parts of an algorithm which therefore require implementation in hardware, thus the constraints are often in the form of a time requirement or a dataprocessing frequency to which the smallest circuit needs to be found. However there is nothing preventing us from implementing resource and power constrained behavioral synthesis.

In general we distinguish between behavioral synthesis in continuous time and behavioral synthesis in discrete time, but in general both approaches involve the same three basic elements:

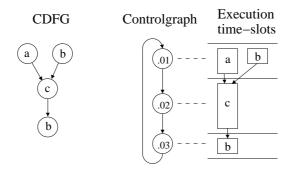

- **Scheduling** The operations in the CDFG need a start time. For continuous time this is an absolute time or a relative ordering of operations. In discrete time this denotes the start time-slot.

- **Allocation** A set of functional units needs to be allocated. The functional units are the machines on which the operations are executed.

- **Assignment** The operations need to be bound to a specific machine to avoid conflicts for parallel operations.

These elements are believed to be NP-hard problems and thus in general require heuristic approaches to find solutions. These three tasks are closely interrelated and should be solved simultaneously to arrive at an optimal solution. All the behavioral synthesis algorithms presented in this thesis do this. There are in principle three approaches to solve these problems:

- **Integer Linear Programming (ILP) formulations** which solve the problem for optimality but is only applicable for small problems.

- Heuristic methods that come in two flavors: constructive approaches and iterative refinement. There are many approaches for constructive scheduling, differing with regard to the selection criteria used to schedule the next operation. Heuristic approaches run efficiently for large designs, but does not produce optimal circuits.

- Meta-heuristic Algorithms which are capable of solving large ILP problems effectively, although heuristically.

Besides these fundamental elements of behavioral synthesis there are elements that involve finding the minimum amount of memory for the specific schedule, allocation

Figure 2.5: Four phase bundled data push handshake protocol.

and assignment, as well as finding the best routing (the minimal set of multiplexing) of data between the functional units. All of these elements of behavioral synthesis and datapath synthesis will be elaborated further in their respective chapters.

#### 2.2.1 ASAP and ALAP

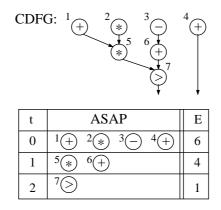

Now, before trying to minimize the silicon area, we first want to know if, given the CDFG and the time constraint T, a feasible schedule can be constructed at all? (using unlimited silicon area). Fortunately, there is a polynomial algorithm,  $\mathcal{O}(n^2)$ , which can give us that answer:

**ASAP** (As Soon As Possible) Augment the CDFG with a source node which has directed arcs to all the input nodes. Set  $S_{source} = 0$  for the source node. Then finding the  $S_i$  for all other nodes  $v_i$  ( $\sigma_i$ ) becomes a matter of finding the longest path from the source to that node. (Using the fastest FU for the job).

If  $S_{target} \leq T$  for the target node, it is possible to construct a feasible schedule. Furthermore  $S_i$  is the earliest time an operator  $\sigma_i$  can be scheduled (again allowing for unlimited silicon area). The same algorithm can be applied "backwards":

**ALAP (As Late As Possible)** Augment the CDFG with a sink node which has directed arcs from all the output nodes. Set  $L_{target} = T$  for the target node. Then finding the  $L_i$  for all other nodes  $v_i$  ( $\sigma_i$ ) becomes a matter of finding the longest path from that node to the target. (Using the fastest FU for the job).

And the time-interval  $S_i \ldots L_i$  specifies the scheduling time interval in which the operator  $\sigma_i$  can be scheduled, given the time constraint T and thus bounds the solution space, in which we are going to search for the optimal solution.

#### 2.3 Asynchronous circuit design

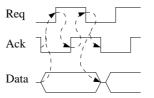

In this section we discuss some of the properties of the asynchronous circuit design style used in this thesis. As the word asynchronous indicates, an asynchronous circuit does not have a global synchronization event in the form of a clock, but rather is locally synchronized. In this thesis we use four-phase bundled data handshake protocol as component synchronization protocol. This means a signal contains a 1

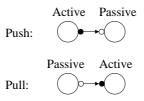

Figure 2.6: Two types of channel communications: push and pull. Data flows from left to right on the channels.

bit request and a 1 bit acknowledge wire additional to the data wires. One example of this the four-phase bundled data push early handshake protocol as illustrated by Figure 2.5. In this protocol the master controls the request and data signals and the slave controls the acknowledge, this also means data is transmitted from the master to the slave. The protocol operates by the master raising the request when the slave is ready to process data, indicated by the acknowledge being low, and the data signals are valid. The slave sees this and reads the data. When data has been read the slave acknowledges this by raising the acknowledge signal. The master then lowers the request signal, removes data and starts preparing for the next transmission. When the slave is ready for the next data the acknowledge signal is lowered. The choice of the four-phase bundled data protocol is an arbitrary choice, our method can be implemented with use of any handshake protocol.

There are two types of channels: push and pull. In a push channel data flows from master to slave and in a pull channel data flows from slave to master. In general the terms master and slave are not used, instead the terms active and passive are used to designate the controlling part of a channel communication and graphically this is illustrated by either a filled (active) or non-filled circle (passive) at the source or destination of a channel, as illustrated on Figure 2.6. The source and destination i.e. the direction of the dataflow is illustrated by the arrow on the channel line.

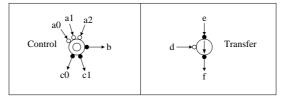

The asynchronous circuits designed in this thesis are built from a set of asynchronous building blocks called handshake components. As the name implies these components communicate using the handshake protocols. These components are independent components, usually designed using input/output-mode or Muller-C style [92]. All components operate using the same protocol, in this way one could consider this type of asynchronous circuit design as object oriented hardware design. Asynchronous circuits and the circuits presented in this thesis are built from handshake components which implements the equivalent RTL operations as latching data, multiplexing data, addition etc. Each of these handshake components has its own local asynchronous control to ensure proper asynchronous functionality and to handle the asynchronous handshake communication protocol [92]. Besides these asynchronous handshake components which have their equivalent RTL counter parts, there are the demerge/demux components which handle "datawire-forks".

Asynchronous handshake components where all outputs are active and all inputs are passive are push-style; components where all outputs are passive and all inputs

Figure 2.7: A minimum and, for most cases, sufficient set of handshake components.

are active are of pull-type; if all ports are passive the component is of passive-type; if all inputs are active the component is of active-type; others are of "mixed"-type.

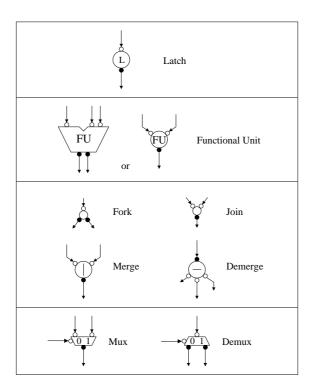

The basic set of building blocks are illustrated in Figure 2.7 in their push-form, where applicable, and can be divided into four groups:

- Latches Data is stored in latches and could be considered the variables of the circuit. Furthermore with one active input or output they implement the handshaking and support the token flow. In their push form a data write and data read always alternate. In their passive form they operate as the variables of the circuit where the surroundings can write and read data independently and to/from multiple sources and destinations.

- **Functional Units** These are the asynchronous equivalents of combinatorial circuits. We will primarily use the symbol on the left, but some tools will generate the right symbol. In their push form the operation is as follows: First all inputs have to be ready, then compute the functions and distribute the results on the respective outputs. The functional units should be considered transparent from a handshaking point of view, but also versions with input/output latches will be considered.

Figure 2.8: Handshake component extension.

- **Unconditional flow control** These components are used to handle parallelism and to merge/split data streams, which are mutually exclusive. The key here is that there is no external control of the data flow. For data streams which are not mutually exclusive either the following group of components have to be used or an arbiter needs to be inserted in front of the component. The merge in shown in the push-form and the demerge is shown in pull-form, which are their only form.

- **Conditional flow control** The MUX and DEMUX components are used to select among several inputs or routing the input to one of several outputs and thus conditionally control the dataflow in the asynchronous circuits.

The functional units in their memory form could by them selves be a network of asynchronous handshake components implementing the function, thus introducing hierarchy into the circuit.

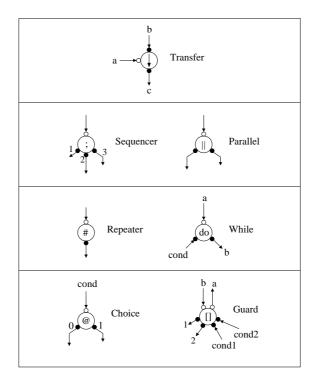

We will need an additional set of asynchronous building blocks to build the asynchronous circuit we desire, these are shown in Figure 2.8 and are all used to build more advanced control circuitry. The groups of handshake components are:

Transfer The transfer component is an active component used to control computa-

tion. When activated on input channel a the transfer component moves data from channel b to channel c.

- **Unconditional control** Here there are two components: The sequencer which for each activation executes a sequence, in order, of sub-operations, before completing the input handshake. The parallel executes all sub-operations in parallel and all have to complete before completing the input handshake.

- **Repetition** Infinite repetition is handled by the repeater, which sends an infinite number of activations to its outputs and never completes its input handshake. The while component implements conditional repetition and operates in the following way: Upon activation on input a, the while component inputs condition *cond* and if true output b is activated and the while components repeats this behavior by inputing the next condition *cond*. This continues until *cond* is false then the while component completes its handshake with a.

- **Conditional control** The choice component implements a binary choice by selecting on the input "cond" if equal to zero the "0" channel is activated otherwise the "1" channel is activated. The Guard components is used for implementing multiple selections or guards. Here the component have two selections and operates as follows: when a is activated the Guard component inputs all its conditions, here *cond*1 and *cond*2. The conditions have to be mutually exclusive. If any of the conditions where true the number is returned on a otherwise zero is returned. When b is activated with a positive data value, it is used to activate the operations, here either 1 or 2. The Guard component can have as many selections as required.

Of these components the transfer plays is most important for this research, as it plays the role of event synchronizer; controlling the computation and is the component connecting the control dominant part of the asynchronous handshake network with the data dominant part of the asynchronous handshake network. Transfer components degenerate to simple wire connections containing no logic.

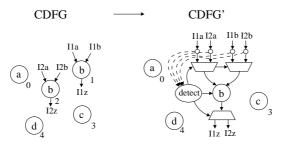

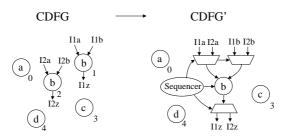

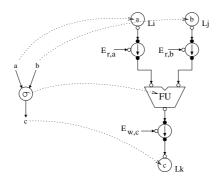

As mentioned in the introduction, there is an apparent resemblance between a circuit designed by a network of handshake protocols and the CDFG describing the behavior of the same circuit. This suggests a simple one-to-one synthesis approach where the CDFG is directly mapped into an asynchronous circuit, as shown in Figure 2.9. Such an approach was more extensively pursued in [73] and is further discussed in the following chapter.

Figure 2.9: Our example designed as an asynchronous circuit using hands hake components.

### Chapter 3

## **Related Work**

This chapter has two purposes: (i) To present an overview of recent advances in research in behavioral synthesis of low-power synchronous circuits and (ii) to present and compare related work with respect to behavioral synthesis of asynchronous circuits. In doing so, the desirable abilities and requirements for an asynchronous behavioral synthesis approach are uncovered.

#### 3.1 Low power behavioral synthesis, an overview

In CMOS circuits, there are two primary sources of power dissipation [72]: (i) Static dissipation originating from leakage current. (ii) Dynamic dissipation originating from switching transient (short-circuit) current and from charging of load capacitance. The total power dissipation becomes:

$$P_{avg} = P_{switching} + P_{short-circuit} + P_{leakage}$$

$$(3.1)$$

Of these components the first is the most dominant and is given by:

$$P_{switching} = \langle \alpha_{0 \to 1} \rangle_t C_l V_{dd}^2 \tag{3.2}$$

Where  $V_{dd}$  is the supply voltage and  $\langle \alpha_{0\to 1} \rangle_t$  is the average number of switching per time unit, that a node with capacitance  $C_l$  will make a power consuming transition  $(0 \to 1)$ . For a synchronous circuit  $\langle \alpha_{0\to 1} \rangle_t = \alpha_{0\to 1} f_{clk}$ , where  $\alpha_{0\to 1}$  is the average number of times the node switches per clock cycle and  $f_{clk}$  is the clock frequency. It is well-known that resource sharing destroys correlation between inputs and the computation and therefore increases the power consumption of the circuit. Furthermore, there is usually an overhead associated with resource sharing which will lead to a larger power dissipation. On the other-hand reducing the area of the circuit leads to a reduction of  $C_l$  which reduces the power consumption. For future deep submicron technologies leakage power will become more dominant. Therefore as leakage current is proportional to area, resource sharing has the potential to reduce leakage power dissipation. But as resource sharing also have an impact on on-off times for functional units and therefore leads to longer activation times which counters this effect.

There are three dominant approaches for behavioral synthesis targeting reduced dynamic power dissipation:

- Low-power behavioral synthesis [44, 19, 57, 61, 94, 69, 70, 84, 45, 89] through arranging the computation such that the internal switching activity is minimized: P ~ ⟨α<sub>0→1</sub>⟩<sub>t</sub>. The design goal is to find min(⟨α<sub>0→1</sub>⟩<sub>t</sub>).

- Low power behavioral synthesis through voltage scaling [55, 27, 10, 80]. Usually low-power designs operate at voltage-levels just above  $2|V_t|$ , thus the benefit from voltage scaling lies in speeding up a few critical computations at a power penalty, which is then more than canceled by choosing slower low power functional units at non-critical places in the circuit.

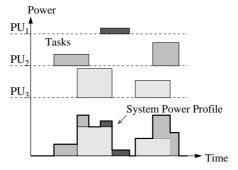

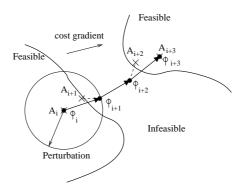

- Power aware behavioral synthesis [102, 5, 1] characterizes methods which targets the generation of a specific power profile of the circuit. The goal is usually a uniform flat power profile below a certain power maximum which corresponds to a hard constraint (e.g. maximum power delivered by a solar-panel). The majority of these algorithms are either based on meta-heuristic algorithms, or two-step algorithms, where in step one a traditional time constrained schedule is constructed and in step two the schedule is made "power-aware".

Usually there is an area penalty associated with these low-power techniques compared to non-low-power techniques and the different methods have different tradeoffs between area and power.

In the following sections we focus on the first of these approaches. There are many ways to minimize  $\langle \alpha_{0\to 1} \rangle_t$ , but the most dominant are those methods which exploit correlations in input-data as well as in the computation. This body of work can be divided into five groups which we will present in the following. The first group focuses on providing accurate lower bounds on power consumption for use in synthesis. The second group focuses on scheduling, allocation and assignment reducing the switching activity of the functional units, which is the largest contributor to power dissipation. The third group focuses on reducing switching activity at the CDFG level. The fourth group focuses on proper register allocation for low power. And finally the last group of papers focuses on reducing the power consumption of the interconnect binding functional units and registers together and the impact this has on scheduling, allocation and assignment. In the following we will present a non-exhaustive list of synthesis methods.

### 3.1.1 Lower bounds on switching activity

In order to find optimal solutions through exhaustive search based methods as branch and bound, it is necessary to bound the solution space using a polynomial approach. This is also useful for measuring optimality of heuristic approaches as the optimal solution is bounded by the heuristic solution and the lower bound. A branch and bound algorithm traces a decision tree whose leafs represent all possible solutions. Given a best solution found during execution of the branch and bound algorithm, a subtree can be pruned if a lower bound estimate of the best solution from the sub-tree yields a larger cost.

In [57, 94] the switching activity metric is defined as the Hamming distance of consecutive input vectors to functional units. Let  $w_{ij}$  define the power cost for the variables *i* and for each operation type *j* present in the DFG. This is computed based on a representative set of input vectors to the circuit. The central idea is to formulate the low power binding problem with resource constraints as a graph problem by defining an arc-labeled directed graph. The optimization problem is then to cover all nodes with exactly *m* (node disjoint) cycles with minimum total cost under the constraint that each cycle contains exactly one backward arc. The total cost is the sum of the arc weights of all cycles. Each cycle of a solution to this problem represents one resource, while the nodes of a cycle are the operations bound to it. The authors prove that the following ILP problem provides a lower bound on the low power binding problem with *m* resources:

$$z = \min \sum_{i,j=1}^{n} w_{ij} x_{ij} \tag{3.3}$$

subject to

$$\sum_{\substack{j=1\\i=1}}^{n} x_i j = 1 \quad i = 1, ..., n$$

$$\sum_{\substack{i=1\\i=j}}^{n} x_i j = 1 \quad j = 1, ..., n$$

$$\sum_{\substack{i>j\\i>j}}^{i>j} x_i j = m$$

(3.4)

with  $x_i j$  integer. In this formulation it is not guaranteed that precedence constraints, specifying operation a has to start after operation b, are fulfilled, hence a solution of the ILP problem delivers only a lower bound on the switching activity. Furthermore, the problem is a relaxation of the optimization problem as there are no constraints forcing each cycle to have exactly one backward arc. Instead of solving the ILP problem, a polynomial time bounded approach is proposed which approximates the ILP problem based on Lagrangian relaxation.

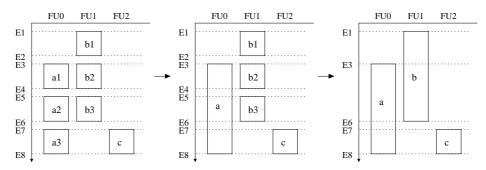

Figure 3.1: Optimizing schedule (from left to right) for reuse of input variables and reduction of switched capacitance. Operation 3 and 5 uses the same result from 2 in successive steps.

### 3.1.2 Reducing switching activity of functional units

The reduction of switching activity of functional units can be accomplished by scheduling operations such as to increase the correlation of the data presented to the functional unit. The first step in this direction is to observe that the average switching activity of any functional unit is significantly reduced if one of the operands remains unchanged [69, 70]. As operands are usually reused more than once in computations on the same type of functional unit, there is a basis for grouping operands together in the scheduling and binding process. The central idea is to group reusable operands together on the same particular functional unit and to execute these in successive time-slots/operation-groups. The idea is shown in Figure 3.1. In [69, 70] this is accomplished by extending the List-scheduling [67] to a Low Power List-scheduling by adding more heuristics. The traditional List-scheduling operates by having a priority queue of all ready operations determined by urgency, more precisely the difference the ASAP-ALAP interval. In the Low Power List-scheduling operation that share operands are grouped into operand-sharing sets. Once an operation has been scheduled, the other operations in the group are moved up to top priority and are scheduled successively, until an operation outside the set gets urgency zero, which is then set for immediate execution.

The next step is to generalize this observation into scheduling operations such as to increase the correlation between consecutive inputs to a functional unit [89, 45].

Again the list-scheduling heuristic can be modified to include this data correlation [89] and to operate by, besides the set of operations  $U_k$  where all predecessors have been scheduled, maintaining the set of most lately scheduled operations for each functional unit  $L_k$ . At any point the algorithm tries to schedule the operations that consume less power. By scheduling operations in this way there are more candidates in the ready set when power hungry operations are scheduled. For evaluation of the priority for the scheduling a power metric is used. Multiplexer power is no considered in this scheme. Let  $c_j$  be the switched capacitance from scheduling operation j on functional unit k where operation i was executed previously  $i \in L_k$ . If the operation is commutative, then operand swapping is tried to find the smallest switched capacitance. This information is stored for register binding.  $c_j$  is normalized with respect to the total switched capacitance of all operators in  $U_k$  of same type. The cost of the candidates are set to:

$$priority = \omega c_i + (1 - \omega) t_i^L \tag{3.5}$$

where  $t_j^L$  is the ALAP time of operation j relative to the average ALAP time of candidates in  $U_k$  of the same type. Parameter  $\omega$  is the weight given to relate power importance to meet time-deadline importance.

The Force-Directed scheduling method can also be modified for low power synthesis [45]. The algorithm models the switched capacitance of an sequence of two consecutive operands to a functional unit as the spring constant k and the probability of selecting the corresponding sequence is modeled as the displacement x, in the force equation F = kx. Thus, a force is associated with each feasible combination of forces which is used to make a power-optimal scheduling decision. This metric is then used in the Force-Directed scheduling method [77] to solve the behavioral synthesis problem for low power digital circuits.

The low power binding problem for a finite set of functional units having a single instance type/single-architecture can be formulated as a min-cost flow problem [31]. This problem is solvable, unlike the generalized low power binding problem functional units having multiple architectures which is an ILP problem. In [31] two polynomial algorithms are presented to heuristicly solve the ILP problem. The first graph-based method iteratively utilizes the single-architecture flow formulation for architecture and then chooses the least power consuming assignment from the set of candidates. Afterwards, the possible unassigned operations are assigned through a node coverage algorithms that follows another flow formulation. The node coverage algorithm runs iteratively until all operations are covered. The second technique assigns the operations to the functional units of multiple architectures in incremental steps similar to the left-edge algorithm.

There are many other methods for addressing the low power synthesis problem [84, 61, 44] these methods involve specifying the problem as auction based non-cooperative finite game, iterative optimizations and constraint logic programming.

### 3.1.3 Reducing switching activity at CDFG level

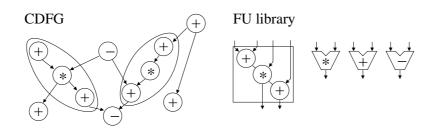

A different more radical approach is to design complex custom low-power functional units such as FFTs and filters and use these as buildings blocks for the circuit in addition to simple functional units as adders and multipliers [60]. This requires for the synthesis approach to be able to map groups of operators on these custom functional units, as shown in Figure 3.2. The method also provides techniques for resynthesis of the functional units to match the constraints and techniques for mapping multiple behaviors onto the same complex functional unit. The meta-heuristic approach used for the design space exploration is based on finding a sequence of incremental moves where only the last move has to generate an improvement in the cost function (the intermediate steps are allowed to move to unoptimal state-space solutions). The sets

Figure 3.2: Finding groups of operations in the CDFG to match the low-power functional units in the library.

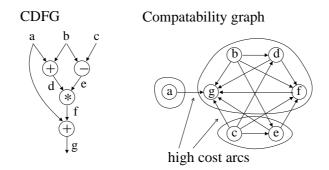

Figure 3.3: Generating the compatibility graph and performing a minimum cost clique-partitioning, asumming the shown arcs have a high switching capacitance cost.

of moves are: i) Simple and complex functional units are replaced by new modules from the library. ii) Complex modules are resynthesized. iii) Simple operations are combined into complex operations. vi) operations are split in to two separate operations. A Tabu-search [43] mechanism ensures solutions are not repeatedly traversed, this method is know as the variable depth search.

Addressing the low power synthesis problem directly at the CDFG level has the potential for large power savings [81, 82]. The proposed CDFG-transformation techniques involve: i) Reducing the total number of operations to be performed by common sub-expressions elimination, loop merging and distributivity. ii) Reduction of spurious switching transitions due to finite propagation delays from one logic block to the next (dynamic hazards). These extra transitions are a complex function of logic depth, input pattern and skew. To minimize these unwanted transitions, signal path balancing and logic depth reduction is handled. The sequence of optimization moves are handled by the use of a heuristic/probabilistic search algorithm.

### 3.1.4 Memory allocation for low-power

The goal here is to find the appropriate number of registers and the associated binding to minimize power consumption in the registers.

The register binding problem can be formulated as a minimum cost clique covering problem [19]. The power consumption is computed based on statistical information derived from assumptions on probabilistic input distributions. The power dissipation model is based on the Hamming distance and the capacitance of the registers are modeled as a fixed load for a given library. The paper [19] defines the compatibility graph G(V, A) as the graph where the nodes are variable intervals and the directed arcs A between two variables if their variable life times are non-overlapping and end-life-time of the source variable is less than the start-life-time of the target. Each arc represents a possible assignment and carries the switched capacitance difference between the two variables. The register assignment problem is then formulated as a minimum cost clique partitioning problem of that graph. They show that the unoriented compatibility graph for the data values in a scheduled dataflow graph without cycles and branches (a DFG fragment) is a comparability graph (or transitively orientable graph) which is a perfect graph. This is a useful property as clique partitioning problems can be solved in polynomial time for perfect graphs, through a max-cost flow reformulation of the problem, giving the minimum total power consumption on the registers in the circuit.

The memory allocation for low-power problem can also be formulated as a network flow problem [18]. This work focuses on solving the problem of rapidly resolving the problem to optimality for an incremental change of the schedule for use in low power scheduling methods. This is a two-step process: i) A max-flow computation involving a valid flow solution while retaining the previous solution as much as possible and ii) a min-cost computation which incrementally refines the found flow solution, using the concept of finding a negative cost cycle in the residual graph for the flow.

### 3.1.5 Interconnect design for low-power

One way to reduce the switching activity in the interconnect connecting registers to the functional units is to isolate/signal guard parts of the interconnect [110]. For interconnect, in this case built by a multiplexing network, it is not justifiable to insert latches through-out the routing network, when compared to the power overhead introduced by such a method. In addition to make use of data-correlations, it is proposed to freeze the inputs of the multiplexors to a fixed (hardwired) value, denoted the filler value. The probabilities for the different switching characteristics are computed by simulating the CDFG in which the binding and scheduling information is back-annotated. The algorithm for computing the filler values is a simple polynomial algorithm running through computing the most probable value. The power reduction of the interconnect is then built into an iterative behavioral synthesis algorithm for scheduling and binding to find the optimal low-power circuit. The meta-heuristic approach used for this is based on finding a sequence of moves where only the last move has to generate an improvement in the cost function (the intermediate steps are allowed to move to unoptimal state-space solutions), a tabu-search mechanism ensures solutions are not repeatedly traversed.

For bus-based micro architectures, reduction of switching activity can be accom-

plished in two ways [29, 30, 28]: (i) Through multiplexing the signals onto the buses in the correct order. (ii) And choosing the optimal set of busses and their connection between functional units and registers. For design of the buses, the average signal switching activity for all nodes in, and inputs to, the CDFG are computed by repeated simulation using a representative set of input vectors. Using this data the switching activity matrix  $SA_{ij}^k$ , for successive data transmissions  $i \to j$  for bus k, for a given bus configuration is computed and the lowest energy is selected. Simulated annealing is used to handle the complete synthesis process including bus configuration design.

## 3.2 Asynchronous behavioral synthesis, an overview

Synthesis of asynchronous circuits falls mainly in two categories: (i) synthesis of small-scale sequential control circuits [26, 41, 106] and, (ii) synthesis of large-scale circuits based on syntax-directed compilation from CSP-like languages: Tangram [11, 100], OCCAM [17], Balsa [8, 36] and ACK [59]. Several tools exist (in the public domain) in these areas, and these tools have been used to design industrial scale circuits.

Synthesis methods for generating small-scale sequential control circuits are lowlevel logic synthesis methods for the design of asynchronous logic, the asynchronous equivalent to synchronous control logic synthesis. syntax-directed synthesis is a line of high-level synthesis where there is a one-to-one correspondence between the highlevel programming language specifying the circuit and the circuit itself.

Besides those two main lines of research there are a number of other attempts. One of the most promising is desynchronization [14, 25] which relies on synchronous behavioral synthesis and then in the low-level logic synthesis phase substitutes the clock and the synchronization with asynchronous handshaking and control.

We illustrate the design flows of the different synthesis methods currently developed for asynchronous circuit design and indicate the different levels of abstraction in the synthesis process. The position inside each level is unimportant and does not signify any further degree of abstraction. The levels of abstraction are:

- **Abstract** This is the level where the behavior is expressed only by essential operations and their essential dependencies.

- **Behavior** The level where the behavior is specified in the form of a programming language and as such may contain restrictions in expression form, which may correspond to non-essential behavior.

- **Architecture** In this level the behavior is specified by architectural information consisting of larger-scale components implementing a predefined behavior.

- **Gate/Logic** At this level the behavior is expressed in the form of an architectural design built by logic gates.

- **Physical** This level represents behavior in physical form either as a layout or as a physical model of a layout.

Not all details will be indicated in the figures describing the different synthesis flows, only those which are of special nature or original to the method in question.

In the following we present a non-exhaustive list of synthesis methods, grouped together as to how their synthesis flows relates to each other.

## 3.3 Asynchronous logic synthesis

Asynchronous logic synthesis is the building method behind asynchronous synthesis as these methods are used to generate the asynchronous logic. This area has been and still is, the focus of a majority of the research in asynchronous circuit synthesis. Asynchronous logic synthesis can largely be divided into two groups: (i) Synthesis of small-scale sequential input/output-mode control circuits or handshake components [26, 41, 107, 108]. This is usually done through tools like Petrify [24, 26]. The behavior of the asynchronous circuit together with its environment is specified using a 1-bounded 1 color petri-net called a Signal Transition Graph (STG). The approach is limed by the NP-hardness of the synthesis problem with several improvements implemented through: Reducing the search space using heuristics [76]. Series of local graph transformations [91]. Furthermore the problem contains the important subproblem of consistent state coding (CSC), which is also the subject for extensive research [63, 65]. The design of GasP circuits [35, 97] fall under the same category of logic synthesis but employ a different handshake protocol.

The other group is synthesis of larger-scale controllers operating in fundamental mode/Burst mode [40, 41, 107, 108, 109]. These are race-free asynchronous combinatorial circuits with restrictions on both type of operation and the timing of how the environment interacts with the circuit. This synthesis problem is likewise an NP-hard problem which limits the size of the controllers possible to synthesize, but usually larger circuits than for the input/output-mode circuits can be synthesized. Again heuristics are employed to improve on the method [9, 98].

Theseus logic has developed a Synopsys back-end. Here the low-level logic synthesis of control and datapath is implemented using a NCL logic-synthesis leading to an asynchronous circuit. The tool is integrated into Synopsys through the use of special libraries and compile commands [38, 90].

## 3.4 Asynchronous behavioral synthesis

A number of papers have presented work on behavioral synthesis of asynchronous circuits from DFG or CDFG representations, but they are surprisingly few and they have a different and/or more limited scope [3, 4, 22, 23, 54]. The first paper limits itself to DFGs and focus mostly on a synthesis algorithm and its runtime. The remaining papers address synthesis from a CDFG representation and they target solutions where a centralized controller or a distributed structure of controllers are specified at the level of individual signal transitions (in the form of signal transition graphs or burst-mode state graphs).

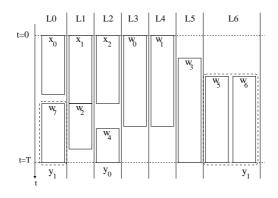

Figure 3.4: Synthesis flow for Achilles, the Bachman approach, ACK and Balsa/Tangram

The synthesis tool Achilles [4, 22, 23] and the synthesis tool by Bachman et al. [3] both represent "pure" asynchronous behavioral synthesis.

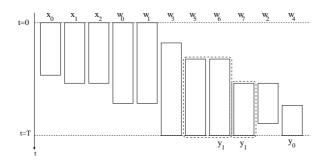

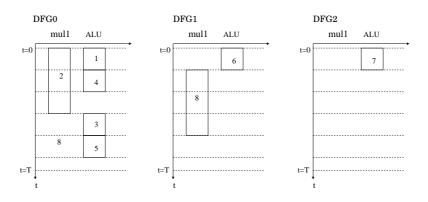

Achilles starts from a control data flow graph and uses a modified list-scheduling to generate a schedule in continuous time. The target architecture is a set of independent machines corresponding to each of the functional units in the circuit, as illustrated on Figure 3.5. Each independent FU then implements the appropriate part of the schedule, has its own memory and handles communication with the other FUs. Using this method, there is a possible communication overhead and memory overhead when comparing to a method using a single controller and datapath. The controller of each FU is specified as a Petri-net and synthesized using Petrify. The complete synthesis flow is illustrated in Figure 3.4 (a).

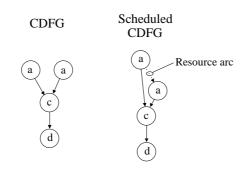

The synthesis tool by Bachman, utilizes a method designated as resource-edge scheduling, which is a form of scheduling where the additional ordering imposed by scheduling is represented as additional graph-dependencies added to the data flow graph, as illustrated in Figure 3.6. It is unclear from their work whether the starting point is a DFG or if they have included DFG extraction from VHDL/Verilog. The synthesis flow is illustrated in Figure 3.4 (b). The focus in their work is on architectural scheduling and series of algorithms have been developed, including scheduling and a continuous left-edge algorithm with the target architecture being a central controller and datapath. They primarily address the runtime and complexity of the developed algorithms.

Figure 3.5: Connection between the continuous schedule and the assignment to the asynchronous architecture for Achilles.

### **3.4.1** Partitioned controllers

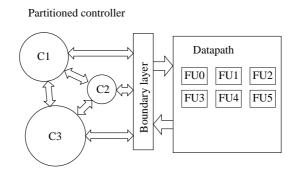

Asynchronous Circuit Kompiler (ACK) [48, 59] is a high-level synthesis system, which is based upon a traditional circuit design style; consisting of a datapath and a centralized controller. The starting point is a CDFG from which a datapath (functional unit allocation) and a Petri-net describing the control of the datapath is extracted. No behavioral synthesis is involved in this extraction, except the source code could contain pragmas for e.g. sharing a common subexpression. The synthesis process could therefor be characterized as syntax-directed.

The size of the Petri-net prevents direct synthesis of the controller, as this is an NP-hard problem. Instead, it is proposed to divide the controller into a small set of controllers and methods are described for letting multiple controllers jointly control a single functional unit in the datapath, through a boundary layer, also responsible for sending data from the datapath to appropriate controller, as illustrated in Figure 3.7. Unlike Achilles, there is not a one-to-one correspondence between the FU and the controller partitioning. The partitioning of the Petri-net is left to the designer and no automated methods are presented in the work.

The set of manually partitioned Petri-nets are then automatically converted into a set of burst-mode specifications, which is then synthesized into burst-mode controllers. The synthesis of the datapath is handled through Synopsys. The complete synthesis flow is illustrated on Figure 3.4 (c).

Several other approaches employ similar techniques with shared controllers and look into automated methods for partitioning controller into manageable sizes [54, 104, 105].

Figure 3.6: Behavioral synthesis mechanism for the synthesis tool developed developed by Bachman.

Figure 3.7: Control and Datapath architecture for ACK.

### 3.4.2 syntax-directed synthesis

Balsa [7, 8, 36], Tangram [11, 12, 100, 101] and OCCAM [17] are CSP type languages specifically designed for synthesis of large scale asynchronous circuits. They employ syntax-directed synthesis into a set of predefined asynchronous handshake components. Both tools are well developed, supported and have been used to design industry scale circuits. The controller consists of a distributed net of handshake components and likewise for the datapath. The flow is illustrated in Figure 3.4 (d).

The syntax-directed compilation approach is radically different from the behavioral synthesis flow used by designers of synchronous circuits. Firstly, syntax-directed compilation is based on a non-standard language, and secondly, and more important, the compiler merely performs a one-to-one mapping of the program text into a corresponding circuit. Although syntax-directed compilation does allow the designer to work at a relatively high level it does not provide any optimizations; "what you program is what you get". In some situations this can be considered an advantage but it also puts more burden on the designer: exploring alternative implementations requires actually programming these, whereas in a traditional synchronous synthesis flow, the designer can quickly and easily experiment with different constraints and

Figure 3.8: Synthesis flow for Resynthesis, SAC, Desynchronization and the MOODS tool.

goals and in this way create alternative implementations from the same program text.

The tools support logic optimization to some degree i.e. in the form of Peep-hole optimizations. These are optimizations where groups of handshake components when placed together in a certain way are replaced by one larger handshake component thus reducing the control logic.

To further improve on this, the resynthesis [20] approach is pushing this even further by grouping parts of the components related to operators in the datapath and re-synthesize the control logic using burst-mode circuits. The flow follows the balsaflow until the point where the circuit is described by a set of handshake components, these are then resynthesized. The flow is illustrated in Figure 3.8 (a).

The TAST tool [85] is pursuing the same direction but is instead synthesizing the controller from the specification, avoiding the handshake components completely and using a traditional control/datapath architecture. Advances in STG to asynchronous circuit synthesis has allowed this to be used for larger circuits and thus becomes more attractive. The starting point is a VHDL description, from which the Petrinet-specification and datapath is derived. The TAST tool is currently not available in the public domain.

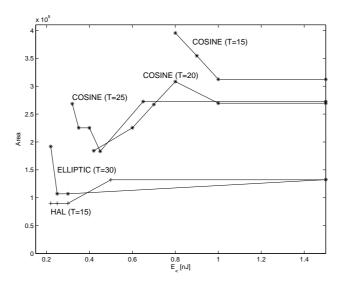

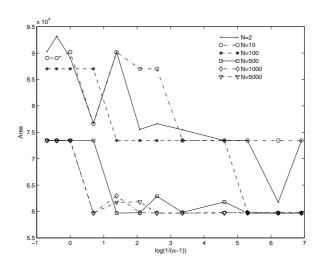

Blunno [15] targets the generation of micro-pipelines directly from a Verilog specification and [62] generates delay insensitive circuits from graph-theoretic specifications, but again there is a one-to-one correspondence between a specification and the resulting circuit.