#### Technical University of Denmark

## Traffic analysis and signal processing in optical packet switched networks

Fjelde, Tina; Dittmann, Lars; Stubkjær, Kristian

Publication date: 2002

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Fjelde, T., Dittmann, L., & Stubkjær, K. (2002). Traffic analysis and signal processing in optical packet switched networks.

### DTU Library

Technical Information Center of Denmark

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Traffic analysis and signal processing in optical packet switched networks

Tina Fjelde

Ph.D. Thesis October 2001

Research Center COM Technical University of Denmark

# Acknowledgements

I would like to start out by thanking my supervisors Lars Dittmann and Kristian Stubkjær. Kristian Stubkjær is acknowledged for considering me for the Ph.D. degree and thus giving me the chance to work in a very inspiring research area. I would like to thank Lars Dittmann for functioning as my main supervisor after I joined the Networking Competence Area and for inspiring me to broaden my horizons to what is outside the narrow scope of optics.

I would also like to give my thanks to Søren Lykke Danielsen, Carsten Jørgensen and Benny Mikkelsen for inspiring me to pursue the Ph.D. degree.

Moreover, I would like to acknowledge my colleagues Allan Kloch, David Wolfson and Peter Bukhave Hansen, and later Mads Lønstrup Nielsen and Henrik Wessing for the joint efforts we have made for hours upon end in the laboratory.

Furthermore, my other colleagues in the Networking- and Systems group, Henrik Christiansen, Michael Berger, Brian Mortensen, Henrik Poulsen, Anders Clausen, Fenghai Liu and Leif Oxenløwe are thanked for good collaboration and fruitful discussions. Moreover, I am grateful to my "officemates" Jesper Bo Jensen, Emmanuel Limal and Mads Lønstrup Nielsen (in chronological order) for putting up with my occasional chitchat.

Special thanks are extended to Alcatel Opto+ for supplying state-of-the-art devices for the experiments. Furthermore, all partners in the European IST project DAVID are acknowledged for a fruitful collaboration.

Finally, I would like to express my sincere thanks to Michael Berger and Mads Lønstrup Nielsen for proofreading and commenting on this thesis.

Kgs. Lyngby, Denmark October 1, 2001 Tina Fjelde

# List of acronyms

1R Reamplification

2R Reamplification + Reshaping

3R Reamplification + Reshaping + Retiming

ACTS Advanced Communications Technologies and Services

BER Bit Error Rate

BRF BiRefringent Fibre

CoS Class of Service

CW Continuous Wave

DAVID Data And Voice Integration over DWDM

DISC Delayed-Interference Signal Converter

DCF Dispersion Compensating Fibre

DFB Distributed Feed-Back (laser)

DFG Difference-Frequency Generation

DOMO Dual-Order MOde

DWDM Dense WDM

EA Electro Absorption (modulator)

EDFA Erbium-Doped Fibre Amplifier

EMPLS Electrical MPLS FDL Fibre Delay-Line

FEC Forward Equivalence Class

FEC Forward Error Correction

FIFO First-In-First-Out

FPGA Field Programmable Gate Array

FWHM Full Width Half Maximum

FWM Four-Wave Mixing

GC-SOA Gain-Clamped SOA

HOL Head-Of-Line (blocking)

IDS Input Data Signal

IETF Internet Engineering Task Force

IP In-Phase (operation)

IP Internet Protocol

IPDR Input Power Dynamic RangeISSR Input Signal Rejection RatioIST Information Society Technologies

List of acronyms iii

IWC Interferometric Wavelength Converter KEOPS KEys to Optical Packet Switching

LAN Local Area Network

LDP Label Distribution Protocol

LSP Label-Switched Path

LSR Label-Switched Router

MAC Media Access Control

MAN Metropolitan Area Network

MEMS Micro Electro-Mechanical Systems

MI Michelson Interferometer

MMI Multi-Mode Interference (coupler)

MPLS Multi-Protocol Label Switching

MPλS Multi-Protocol Lambda Switching

MZI Mach-Zehnder Interferometer

NOLM Nonlinear Optical Loop Mirror

NRZ Non-Return-to-Zero

OC Optical Channel

O/E/O Optical-to-Electrical-to-Optical (conversion)

OMPLS Optical MPLS

OOP Out-Of-Phase

OPADM Optical Packet Add-Drop Multiplexer

OPR Optical Packet Router

OPRN Optical Packet Ring Node

OSNR Optical Signal-to-Noise Ratio

OSPF Open Shortest Path First

OTDM Optical Time-Division Multiplexing

OXC Optical Cross-Connect

PLR Packet Loss Ratio

PRBS PseudoRandom Bit Sequence

QoS Quality of Service

RAM Random Access Memory

RZ Return-to-Zero

SDH Synchronous Digital Hierarchy

SDM Space-Division Multiplexing

SLALOM Semiconductor Laser Amplifier Loop Optical Mirror

SNR Signal-to-Noise Ratio

iv List of acronyms

SM Single-Mode

SMF Single-Mode Fibre

SOA Semiconductor Optical Amplifier

TDM Time-Division Multiplexing

TOAD Terahertz Optical Asymmetric Demultiplexer TOWC Tuneable Optical Wavelength Converter

UNI Ultrafast Nonlinear Interferometer

WAN Wide Area Network

WDM Wavelength Division Multiplexing

XGM Cross-Gain Modulation

XOR eXclusive-OR

XPM Cross-Phase Modulation

List of acronyms

#### Abstract

This thesis focuses on functionalities that are important for the realisation of future all-optical packet switched networks, and which may be implemented using the interferometric wavelength converter. The European IST research project DAVID, with the aim of demonstrating the feasibility of a Tbit/s optical packet switched network exploiting the best of optics and electronics, is used as a thread throughout the thesis.

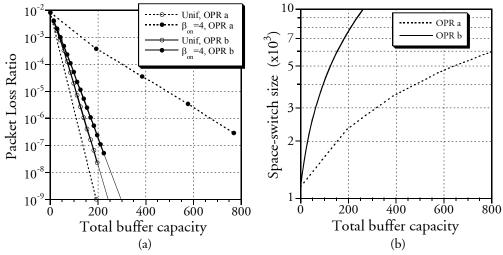

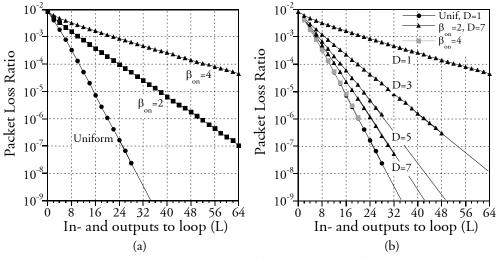

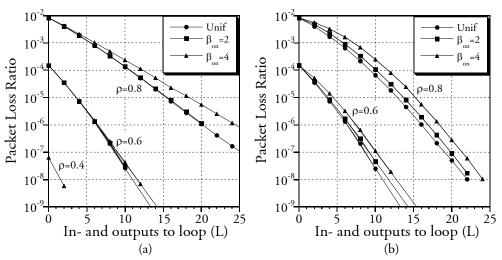

An overview of the DAVID network architecture is given, focusing on the MAN and WAN architecture as well as the MPLS-based network hierarchy. Subsequently, the traffic performance of the DAVID core optical packet router, which exploits wavelength conversion and fibre delay-line buffers for contention resolution, is analysed using a numerical model developed for that purpose. The robustness of the shared recirculating loop buffer with respect to bursty traffic is demonstrated and compared with a standard fibre delay-line based output buffer. Moreover, the effectiveness of the recirculating loop is demonstrated through a 55% reduction in the switching fabric size enabled by a small reduction in the offered load per input channel from 0.8 to 0.6.

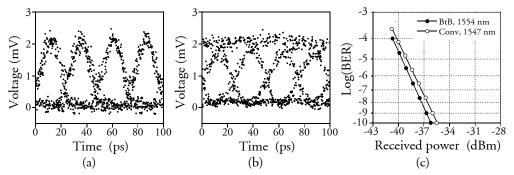

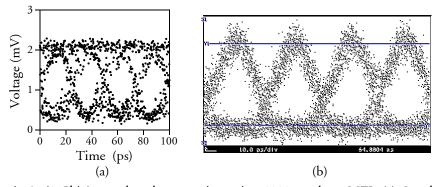

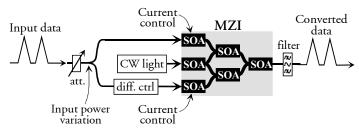

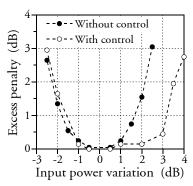

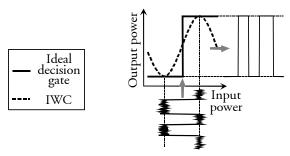

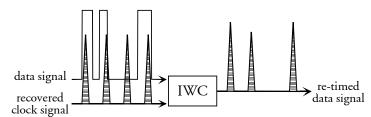

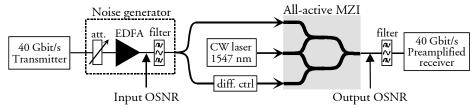

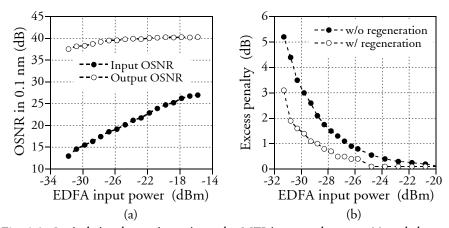

Different techniques for interferometric wavelength conversion are discussed and the performance of the IWC is analysed experimentally based on the all-active Mach-Zehnder and Michelson interferometer. Wavelength independence over the entire C-band is verified and wavelength conversion at up to 40 Gbit/s using the differential control scheme is demonstrated with a 0.6 dB penalty. Moreover, using a novel device denoted the DOMO MZI, co-propagational conversion to the same wavelength, an important functionality for practical networks, is demonstrated at 10 Gbit/s with a 2.4 dB penalty. Finally, a novel conversion scheme involving the injection of an additional clock signal into the IWC is presented. Results show very good transmission capabilities combined with a high-speed response.

It is argued that signal regeneration is an inherent attribute of the IWC employed as a wavelength converter due to the sinusoidal transfer function. This is verified experimentally at 40 Gbit/s on an input signal degraded by noise. Moreover, conversion to a 40 GHz clock signal, which enables re-timing, is demonstrated with a power penalty of 0.5 dB. The excellent regenerative capabilities of the novel conversion scheme are verified at 10 Gbit/s with a 4 dB improvement in receiver sensitivity. Finally, regeneration without wavelength conversion is demonstrated at 40 Gbit/s in an MZI with a 2.5 dB improvement. Additionally, the IWC's capabilities for simultaneous time-division de(multiplexing) and wavelength conversion are demonstrated experimentally for 40 to 10 Gbit/s demultiplexing and 2x10 to 20 Gbit/s multiplexing.

Abstract vii

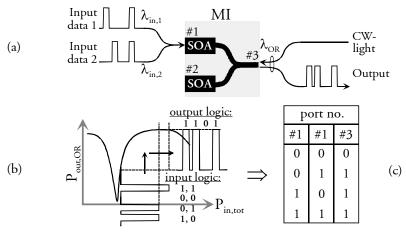

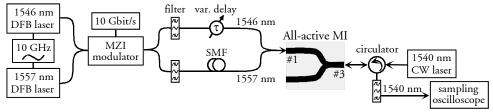

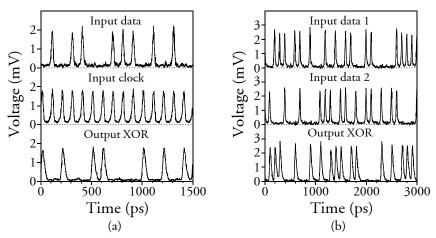

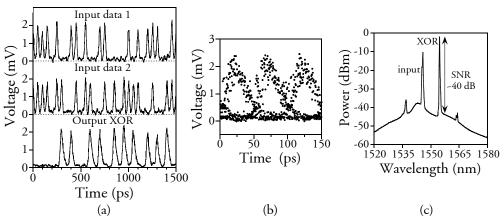

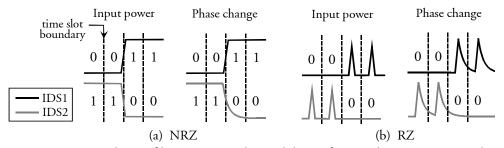

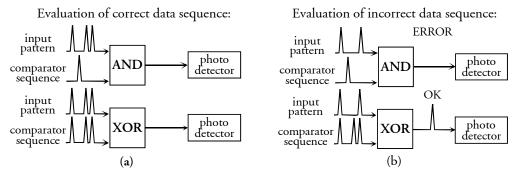

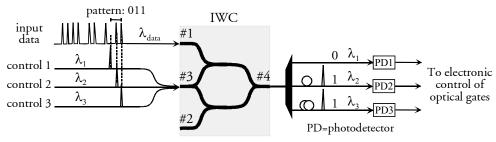

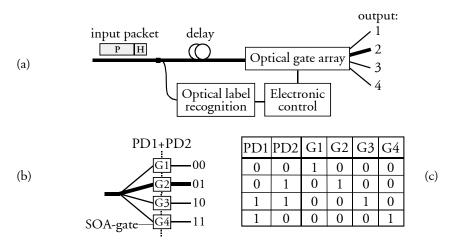

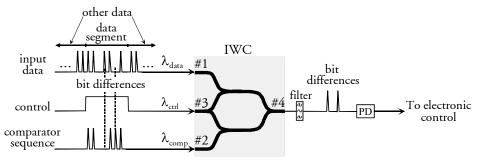

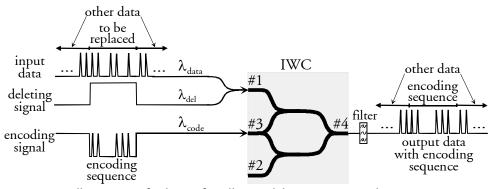

Lastly, the IWC's capabilities as an optical logic gate for enabling more complex signal processing are demonstrated and four applications hereof are discussed. Logic OR and AND are verified in full at 10 Gbit/s using PRBS sequences coupled into an MI. Moreover, logic XOR is demonstrated in an MZI at 10 and 20 Gbit/s with good results. Using an MI, the excellent performance of a novel scheme for MPLS label swapping exploiting logic XOR is demonstrated at 10 Gbit/s with a negligible 0.4 dB penalty. Finally, three novel schemes are described, involving all-optical pattern recognition by bit-wise sampling at multiple wavelengths, optical identification of bit differences in data segments through a combination of logic XOR and AND, and all-optical bit sequence replacement through logic OR and AND. The schemes enable important signal processing functionalities in packet switched networks to be implemented all-optically in a simple and cost-effective manner, and can be implemented using a single IWC.

## Resumé (in Danish)

Denne afhandling fokuserer på funktionaliteter, der er vigtige for realisering af fremtidens fuldt-optiske pakkekoblede netværk, og som kan implementeres ved hjælp af interferometriske bølgelængdekonvertere. Det europæiske IST forskningsprojekt DAVID, som har til formål at demonstrere gennemførligheden af et Tbit/s optisk pakkekoblet netværk, der udnytter det bedste af optikken og elektronikken, er benyttet som rød tråd gennem afhandlingen.

En oversigt over DAVID netværksarkitekturen, der fokuserer på MAN og WAN arkitekturen såvel som det MPLS-baseret netværkshierarki, er givet. Herefter er trafik-ydeevnen for den optiske pakkeruter i DAVID kernenetværket, som udnytter bølgelængdekonvertering og fiber forsinkelseslinier til konfliktløsning, analyseret ved hjælp af en numerisk model udviklet til formålet. Hårdførheden af den delte recirkulerende loop buffer med hensyn til bursty trafik er demonstreret og sammenlignet med en standard fiberforsinkelseslinie-baseret udgangsbuffer. Ydermere er effektiviteten af den recirkulerende loop demonstreret ved en 55% reduktion i switch-størrelsen, muliggjort ved en lille reduktion i trafikbelastningen per indgangskanal fra 0.8 til 0.6.

Forskellige teknikker til interferometrisk bølgelængdekonvertering er diskuteret og ydeevnen af IWC'en er analyseret eksperimentelt baseret på det fuldt-aktive Mach-Zehnder og Michelson interferometer. Bølgelængdeuafhængigheden over hele C-båndet er verificeret, og bølgelængdekonvertering ved op til 40 Gbit/s ved benyttelse af den differentielle kontrolmetode er demonstreret med en 0.6 dB følsomhedsforringelse. Ydermere, ved benyttelse af en ny komponent med betegnelsen DOMO MZI, er konvertering til samme bølgelængde med bølgeudbredelse i samme retning demonstreret ved 10 Gbit/s med en 2.4 dB følsomhedsforringelse. Denne funktionalitet er vigtig for implementering af praktiske optiske netværk. Slutteligt er en ny konverteringsmetode, der involverer kobling af et ekstra kloksignal ind i IWC'en, præsenteret. Resultater viser gode transmissionsegenskaber samt et hurtigt respons.

Det er argumenteret at signal regenerering er et medfødt attribut for IWC'en anvendt som en bølgelængdekonverter på grund af den sinusformede overføringskarakteristik. Dette er verificeret eksperimentelt ved 40 Gbit/s på et indgangssignal der er degraderet af støj, og konvertering til et 40 GHz kloksignal, som muliggør klok-genoprettelse, er demonstreret med en følsomhedsforringelse på 0.5 dB. De gode regenereringsegenskaber af den nye konverteringsmetode er verificeret ved 10 Gbit/s med en 4 dB følsomhedsforbedring. Slutteligt er regenerering uden bølgelængdekonvertering demonstreret ved 40 Gbit/s i en MZI med en 2.5 dB forbedring. Ydermere er IWC'ens anvendelse til samtidig tids-de(multipleksning) og bølgelængdekonvertering demonstreret experimentelt for 40 til 10 Gbit/s

Resumé

demultipleksning og 2x10 to 20 Gbit/s multipleksning.

Slutteligt er IWC'ens evner som optisk logisk kontakt til at muliggøre mere kompleks signalprocessering blevet demonstreret, og fire applikationer af dette er diskuteret. Logisk OR og AND er fuldt verificeret ved 10 Gbit/s ved hjælp af PRBS sekvenser koblet ind i en MI. Ydermere er logisk XOR demonstreret i en MZI ved 10 og 20 Gbit/s med gode resultater. Ved anvendelse af en MI er den gode præstation af en ny metode til MPLS label swapping, der udnytter logisk XOR, blevet demonstreret ved 10 Gbit/s med en negligibel 0.4 dB følsomhedsforringelse. Tre nye metoder er blevet beskrevet til fuldt-optisk mønstergenkendelse ved bitvis sampling ved multiple bølgelængder, optisk identifikation af bitforskelle i datasegmenter gennem en kombination af logisk XOR og AND, og fuldt-optisk bitsekvenserstatning gennem logisk OR og AND. Metoderne muliggør fuldt-optisk implementation af vigtige signalprocesseringsfunktionaliteter i pakkekoblede netværk på en simpel måde, og kan implementers i en enkelt IWC.

# Table of contents

|    | Acknowledgements                                                 | i    |

|----|------------------------------------------------------------------|------|

|    | List of acronyms                                                 | ii   |

|    | Abstract                                                         | vi   |

|    | Resumé (in Danish)                                               | viii |

| 1. | Introduction                                                     | 1    |

| 2. | Implementation of optical packet-switched networks: a case study | 6    |

|    | 2.1 Objectives of the IST project DAVID                          | 7    |

|    | 2.2 Overview of the DAVID network architecture                   | 7    |

|    | 2.2.1 The metro network (MAN)                                    | 8    |

|    | 2.2.2 The core network (WAN)                                     | 11   |

|    | 2.2.3 The DAVID network hierarchy                                | 13   |

|    | 2.3 Summary                                                      | 17   |

| 3. | The traffic performance of an optical packet router              | 19   |

|    | 3.1 The pros and cons of the optical packet router               | 20   |

|    | 3.2 Comparison of optical packet router architectures            | 21   |

|    | 3.2.1 Description of architectures                               | 22   |

|    | 3.2.2 Component count and basic traffic performance              | 24   |

|    | 3.3 The DAVID optical packet router                              | 28   |

|    | 3.3.1 General traffic model overview                             | 28   |

|    | 3.3.2 Description of packet scheduling algorithm                 | 30   |

|    | 3.3.3 Traffic performance                                        | 33   |

|    | 3.4 Summary                                                      | 37   |

| 4. | Interferometric wavelength conversion                            | 39   |

|    | 4.1 System requirements to wavelength converters                 | 40   |

|    | 4.2 Different techniques for wavelength conversion               | 40   |

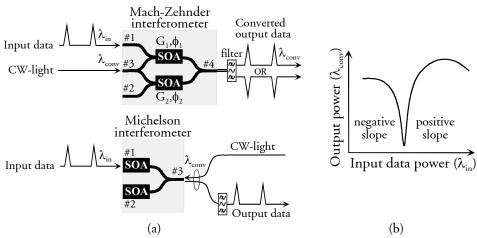

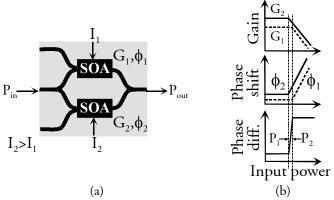

|    | 4.3 Standard wavelength conversion by cross-phase modulation     | 48   |

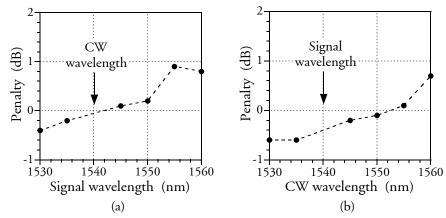

|    | 4.3.1 Wavelength dependency of the MI at 10 Gbit/s               | 48   |

|    | 4.3.2 20 Gbit/s wavelength conversion using an MZI               | 49   |

|    | 4.4 High-speed interferometric wavelength conversion using       |      |

|    | the differential control scheme                                  | 52   |

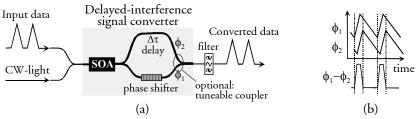

|    | 4.4.1 The principle of the differential control scheme           | 52   |

|    | 4.4.2 40 Gbit/s differential wavelength conversion in an MZI     | 54   |

|    | 4.4.3 Scheme for increased input-power dynamic range             | 56   |

|    | 4.5 The dual-order mode Mach-Zehnder wavelength converter        | 58   |

|    | 4.6. Novel scheme for interferometric wavelength conversion      | 63   |

Table of contents xi

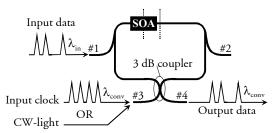

|    | 4.6.1 Principle of operation                                     | 63  |

|----|------------------------------------------------------------------|-----|

|    | 4.6.2 Speed performance and transmission properties              | 64  |

|    | 4.7 Summary                                                      | 68  |

| 5. | Simple signal processing using IWCs                              | 69  |

|    | 5.1 All-optical regeneration                                     | 69  |

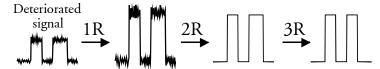

|    | 5.1.1 Introduction to all-optical regeneration                   | 70  |

|    | 5.1.2 Simultaneous regeneration and wavelength conversion        | 72  |

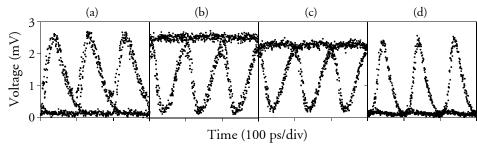

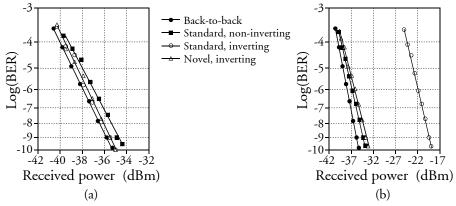

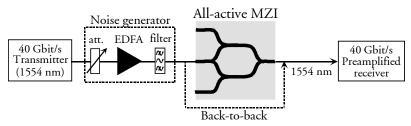

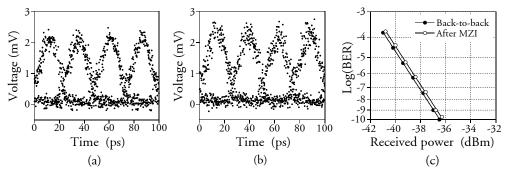

|    | 5.1.2.1 2R regeneration at 40 Gbit/s in an all-active MZI        | 72  |

|    | 5.1.2.2 3R regeneration at 40 Gbit/s in an all-active MZI        | 74  |

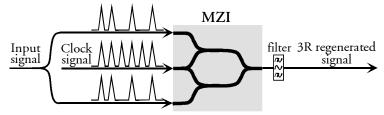

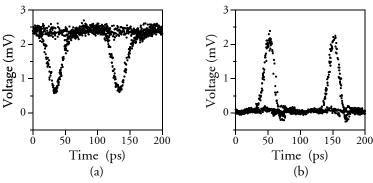

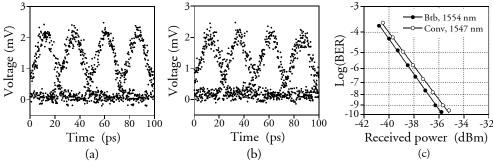

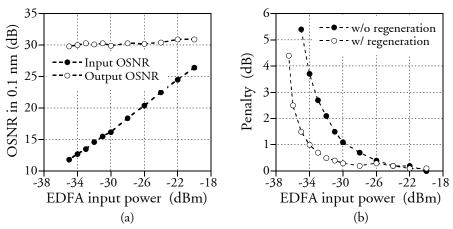

|    | 5.1.2.3 Regenerative capabilities of the novel conversion scheme | 77  |

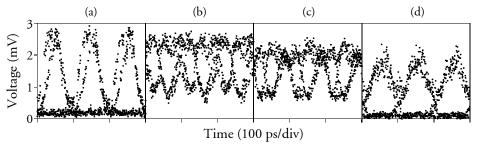

|    | 5.1.3 2R regeneration without wavelength conversion              |     |

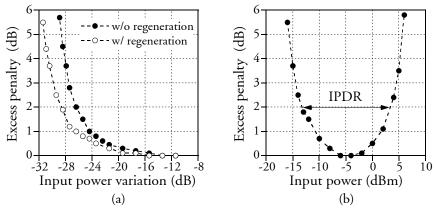

|    | using the pass-through scheme                                    | 78  |

|    | 5.1.3.1 Operating principle of the pass-through scheme           | 78  |

|    | 5.1.3.2 2R regeneration at 40 Gbit/s in an all-active MZI        | 79  |

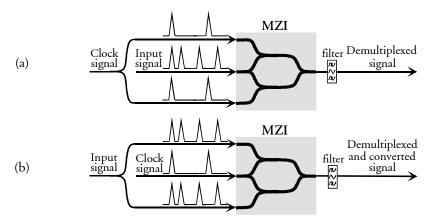

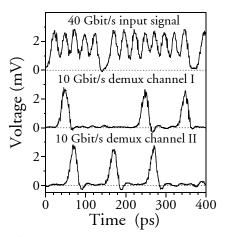

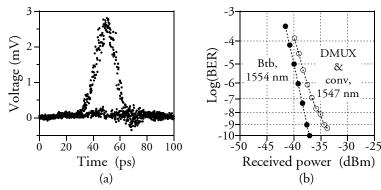

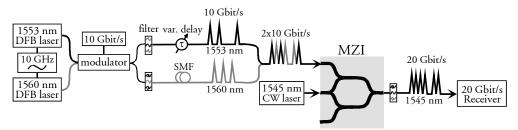

|    | 5.2 Simultaneous (de)multiplexing and wavelength conversion      | 81  |

|    | 5.2.1 All-optical time division demultiplexing                   | 81  |

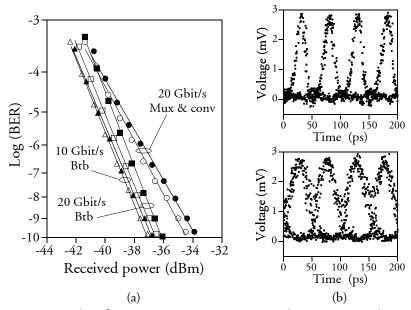

|    | 5.2.2 All-optical time division multiplexing                     | 84  |

|    | 5.3 Summary                                                      | 87  |

| 6. | All-optical logic and its applications                           | 89  |

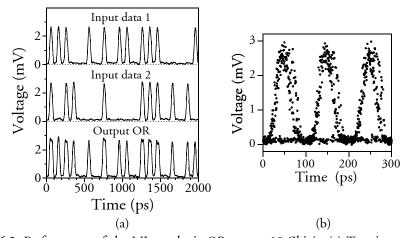

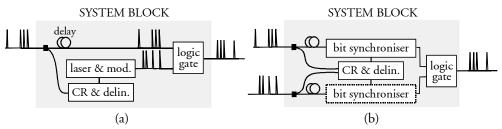

|    | 6.1 Boolean logic using IWCs                                     | 90  |

|    | 6.1.1 Logic OR                                                   | 90  |

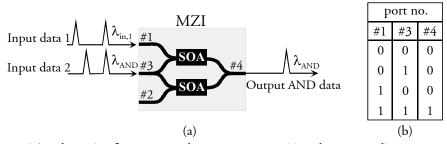

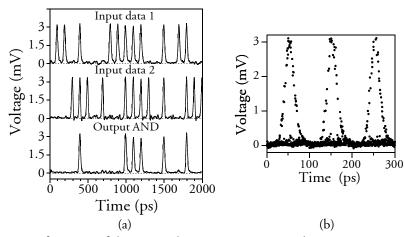

|    | 6.1.2 Logic AND                                                  | 93  |

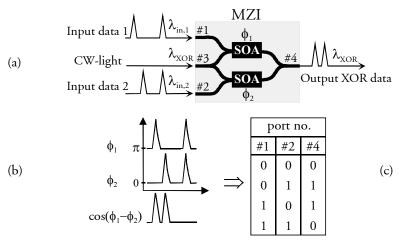

|    | 6.1.3 Logic XOR                                                  | 94  |

|    | 6.2 Applications of all-optical logic in a network perspective   | 99  |

|    | 6.2.1 All-optical MPLS label swapping                            | 100 |

|    | 6.2.2 All-optical pattern recognition by bitwise sampling        |     |

|    | at multiple wavelengths                                          | 104 |

|    | 6.2.3 Optical identification of bit differences in data segments | 108 |

|    | 6.2.4 All-optical bit sequence replacement                       | 110 |

|    | 6.3 Summary                                                      | 112 |

| 7. | Conclusion                                                       | 114 |

|    | Ph.D. publications and patents                                   | 118 |

|    | References                                                       | 122 |

|    |                                                                  |     |

# Chapter 1

#### Introduction

More sweeping job cuts for struggling Lucent:

As part of its second phase of restructuring, Lucent Technologies is to slash 15,000-20,000 additional jobs.<sup>1</sup>

At the time of writing, headlines like the one cited above are an everyday occurrence. What went wrong to prompt such a reversal of fortune for the communications industry since the boom in the late 1990's?

Obviously, tele- and datacommunications are closely related to the Internet, why the exponential growth of the Internet in the late 1990's spurred an explosion in requirements for bandwidth, and therefore in high-speed networking equipment and solutions. When the dot-com bubble burst in the spring of 2000 because the revenue potential could not keep up with the immense market expectations, the telecom and optical communications industry was also affected significantly. According to the magazine Fibre Systems Europe [1], most industry analysts agree that the service providers are to blame for the slowdown in the industry. Previously, service providers were spending large sums on new fibre infrastructure and network upgrades in order to keep pace with the growth in the Internet. Thus, optical vendors were forced to build up inventory in order to avoid losing sales. With the burst of the dot-com bubble, network expansion is not a priority, why service providers have turned to rationalisation of their business model, while waiting for the advent of next-generation networks. This reduction in capital expenditure on network infrastructure has affected the whole optical supply chain, which is left with a stockpile of depreciating hardware. As a consequence of this, many companies are announcing massive job cuts in order to minimise costs in the short term.

Fortunately, the future is not unconditionally dark for the optical communications industry. According to [1], the current downturn should instead be seen as a change of direction. Both analysts and component vendors agree that future investments should be placed in companies that will pave the way for next-generation optical networks. Here, innovation as well as product maturity is required to lower the cost and increase the flexibility of the networks.

So, what exactly does the term "next-generation optical network" cover? The development of the EDFA (erbium doped fibre amplifier) in the 1980's and its commercialisation by 1990 enabled the exploitation of optical amplification for

\_

<sup>&</sup>lt;sup>1</sup> Fibre Systems online news week 30, 2001 (http://news.fibers.org).

2 1. Introduction

increasing the repeater spacing and wavelength-division multiplexing (WDM) enabled an increase in capacity. Since then, optics has had a major role in communications networks [2]. Until now, the optical domain has been used solely for transport, while switching and more complex signal processing have been performed in the electronic domain. However, as the bit rate is increased, power-consumption and size issues make optical solutions increasingly attractive [3]. With the recent commercialisation of the micro-electro-mechanical systems (MEMS) technology for space switching [4] (e.g., employing tiny mirrors to reflect incoming light to the switch node to the appropriate outlet), all-optical networks, that route data entirely in the optical domain, are forthcoming [5].

It is envisaged that the first all-optical networks will be based on wavelength routing optical cross-connects (OXCs) employing MEMS-based switches with ms-level reconfiguration time. Most likely, Multiprotocol Lambda Switching (MPλS) will be used to set up circuits associated with optical wavelength channels [6,7].

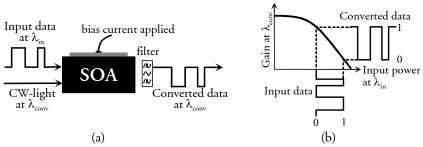

Although a feasible solution for optical space switching is the first step towards alloptical networks, widespread application of all-optical networks requires that the practical network size is not limited through the choice of optics rather than electronics. This means that the optical network should be flexible as well as scaleable in size. Among the key components to enable this are optical wavelength converters and 3R regenerators. Wavelength conversion enables flexibility through wavelength re-use because wavelength allocation can be done on a local instead of global scale, thus allowing more efficient bandwidth usage [8,9]. Among the prime candidates for all-optical wavelength conversion is the interferometric wavelength converter (IWC), which exploits the principle of cross-phase modulation (XPM) [10-12,Pub2,Pub4,Pub12]. In order to enable large-scale optical networks and longhaul transmission, it is critical to ensure that the signal quality is maintained from source to destination. For this, optical 3R regeneration is necessary, which, apart from re-amplification, comprises correction for noise and nonlinear distortion (reshaping) as well as ensuring that each pulse maintains its correct time position in the sequence (re-timing) [13-16,Pub1,Pub5,Pub17].

As optics matures, optical packet switching will most likely replace circuit switching due to the high degree of bandwidth utilisation and flexibility that it allows [17]. Also for packet switching, wavelength conversion is an important functionality, as it can be used to improve the traffic performance and reduce the required buffer capacity [18,19]. A likely scenario on the medium term is however still that processing of data packet overhead will be performed in the electrical domain, while the payload is switched transparently without O/E/O-conversion [20]. On the longer term, it may however be envisaged that increasingly complex signal processing functionalities can with advantage be implemented in the optical domain. For this purpose, all-optical logic gates will be key components. Using IWCs, Boolean functions such as logic

1. Introduction 3

NOT, AND, OR and XOR have been demonstrated within recent years [21,22,Pub10,Pub11]. Moreover, practical applications of optical logic gates for such different purposes as generation of PRBS<sup>2</sup> sequences [23], MPLS<sup>3</sup> label swapping [Pub20] and parity checking [24] have been demonstrated.

This thesis contains modelling as well as experimental work that is important for the implementation of optical networks in general and packet switched networks in particular. The work is partially linked to the ongoing European IST<sup>4</sup> project DAVID (Data And Voice Integration over DWDM), for which the aim is to exploit an optimal combination of electronics and optics to demonstrate the feasibility of a high-capacity optical packet switched network. The DAVID project will also function as the main thread between the different topics that are discussed in this thesis. Firstly, a general overview of the DAVID network concept will be given. Based on this discussion, the traffic performance of the DAVID core optical packet router (OPR) is analysed through simulations. Wavelength converters are key components in enabling the excellent traffic performance of the DAVID OPR. Following this line, a detailed experimental investigation of interferometric wavelength converters will be given, as well as comparison of the most attractive wavelength conversion schemes. As mentioned previously, 3R regeneration is an important factor for optical networks. In this thesis, experimental results demonstrating the IWC's capability for regeneration will also be given. Finally, taking the concept of optical networks a step further, more exotic applications of the IWC for time-division multiplexing and demultiplexing as well as optical logic will be experimentally verified. Finally, some novel schemes relying on optical logic for more complex data processing that are of interest in packet switched networks will be described. More specifically, the contents of this thesis is as follows:

In Chapter 2 the implementation of optical packet switched networks will be described using the DAVID project as a case study. Here, the MAN (Metropolitan Area Network) and WAN (Wide Area Network) architecture will be described. Finally, a description will be given of the DAVID network hierarchy, which exploits MPLS to create a unified switching/routing approach that links all network levels together.

In Chapter 3 the focus will be on the traffic performance of the DAVID core OPR, which exploits a recirculating loop for buffering. Firstly, a general comparison of the optical component count and traffic performance will be made with a generic packet switch using optical output buffering. Subsequently, the model used for the simulations will be discussed, whereupon a closer examination of the packet loss rate of the DAVID OPR will be given, using the parameters for switch size, etc. set within

<sup>&</sup>lt;sup>2</sup> PRBS: PseudoRandom Bit Sequence

<sup>&</sup>lt;sup>3</sup> MPLS: MultiProtocol Label Switching

<sup>&</sup>lt;sup>4</sup> IST: Information Society Technologies

1. Introduction

the DAVID project. Here, the effect of the size of the loop buffer and the packet arrival distribution will be discussed.

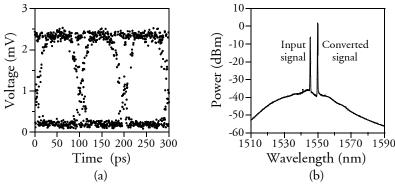

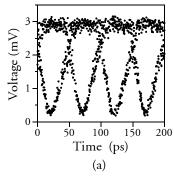

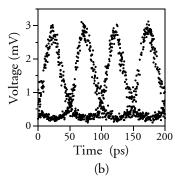

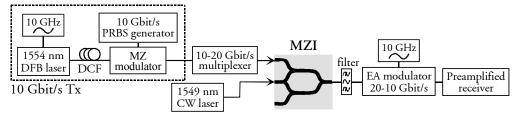

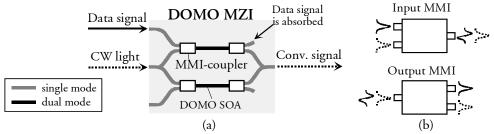

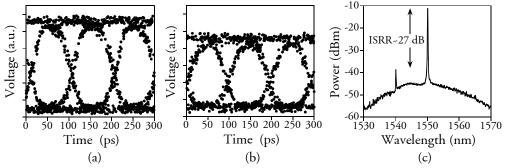

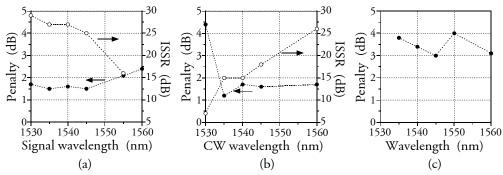

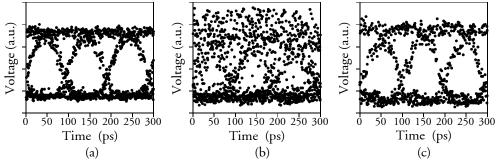

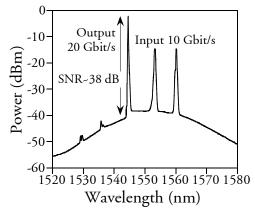

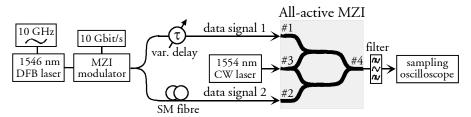

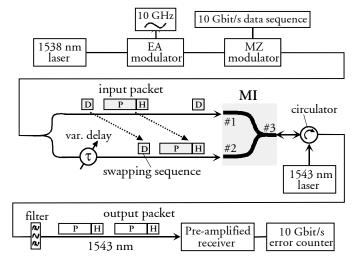

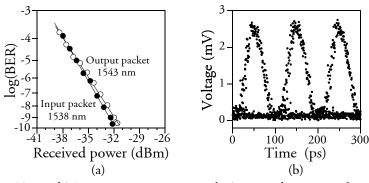

Chapter 4 gives the system requirements to optical wavelength converters and discusses some different technologies for wavelength conversion. Here, the focus is mainly on a comparison of the principle of operation, as well as advantages and disadvantages of techniques for interferometric SOA-based wavelength conversion. After some basic experimental results at 10 Gbit/s achieved with the integrated allactive Michelson interferometer (MI), conversion at up to 40 Gbit/s is presented using the all-active Mach-Zehnder interferometer (MZI). Subsequently, the Dual-Order Mode (DOMO) wavelength converter, which allows co-propagative conversion to the same wavelength through mode separation, is described, and results are given for conversion up to 20 Gbit/s. Finally, a novel conversion scheme, which enables a high-speed response combined with good transmission properties, is described, and a experimental comparison is made with standard wavelength conversion. The results shown in Fig. 4.8 and 4.15 were obtained with Mads Lønstrup Nielsen (COM), Allan Kloch (formerly COM) and Henrik Wessing (COM). The work in Sections 4.3.2 and 4.4 was carried out together with David Wolfson, Allan Kloch and Peter Bukhave Hansen, all formerly with COM, while the remainder of the experimental results were obtained with Allan Kloch and David Wolfson.

In Chapter 5, the principle of signal re-shaping and re-timing in an IWC is described. Following this, experimental results for simultaneous wavelength conversion and 2R regeneration at 40 Gbit/s are demonstrated. Subsequently, the principle of re-timing through conversion to a clock signal is given, and results are shown at 40 Gbit/s. Following this, the regenerative capabilities of the novel conversion scheme are demonstrated at 10 Gbit/s and the operating principle and 40 Gbit/s experimental results are shown for the pass-through scheme, which enables signal re-shaping in an IWC without wavelength conversion. Finally, the focus turns to application of the MZI for optical time-division demultiplexing and multiplexing. Firstly, results will be shown for simultaneous 40 to 10 Gbit/s demultiplexing and wavelength conversion, whereupon 2x10 to 20 Gbit/s multiplexing will be demonstrated. The work in Sections 5.1.2 and 5.1.3, with the exception of Section 5.1.2.3, was made together with David Wolfson, Allan Kloch and Peter Bukhave Hansen, while the remainder was done in collaboration with David Wolfson and Allan Kloch.

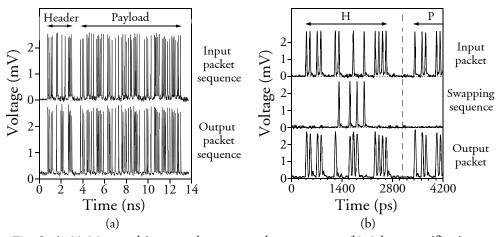

The topic of Chapter 6 is all-optical logic and its applications. The principle of operation and implementation-specifics, that should be paid attention to, are discussed. Moreover, experimental results are given for logic OR and AND at 10 Gbit/s using an MI and logic XOR at up to 20 Gbit/s using an MZI. Subsequently, a novel scheme for MPLS label-swapping exploiting logic XOR is

1. Introduction 5

described and the scheme is verified at 10 Gbit/s. Finally, three novel schemes for complex signal processing are presented, which exploit the IWC for multiple simultaneous logic operations. The first is applicable for all-optical pattern recognition, the second for identification of bit differences in data segments, and the third scheme enables all-optical bit sequence replacement. The experimental work in this chapter has been done in collaboration with Allan Kloch and David Wolfson. Chapter 7 concludes the thesis.

# Chapter 2

# Implementation of optical packetswitched networks: a case study

With the broad use of WDM as the transport technology in commercial networks, an important step has been taken in meeting the increasing demands for bandwidth within the last years. To cope with this evolution, the capacity and functionality of electronic IP (Internet Protocol) routers are also increasing dramatically, although technological breakthroughs are still required [3]. Due to issues of cost, power-consumption and physical size, other alternatives to electronic IP routers are being widely investigated; first optical layer cross-connects, e.g., based on the MEMS technology [4], that will increase capacity in current SDH<sup>5</sup> networks, are being developed [5]. An IETF<sup>6</sup> proposal is under study, involving exploitation of this OXC technology to enable the transport of IP traffic directly over a WDM infrastructure with the aid of MPλS<sup>7</sup> to set up circuits, or label-switched paths (LSPs), associated with optical wavelength channels [6,7].

In the meantime, several research projects worldwide, and especially in Europe, have investigated techniques for optical packet switching, which has the advantage of increased network flexibility and a larger degree of granularity (i.e., packets instead of wavelengths) than the circuit-switched technology that MP\LambdaS offers. This granularity increase enables an efficient reduction in the required network capacity, and thus a potential reduction in the connect cost for users, thanks to a better sharing of the physical resources. This is, however, at the expense of added complexity, both with respect to optical technology as well as electronic control.

In the European ACTS<sup>8</sup> project KEOPS (Keys to Optical Packet Switching), the feasibility of optical packet switching in the core network was studied intensely, with the focus on optical implementations of the required processing functionalities, e.g., for temporal synchronisation of packets, regeneration, switching, etc. [25,26]. However, very little attention was paid to the interoperability between optics and electronics and implementation of the required control electronics. As an extension of the KEOPS project, the IST project DAVID was started in the Summer 2000.

In this chapter, the implementation of an optical packet switched network will be discussed using the DAVID project as a case study. In Section 2.1, the objectives of the DAVID project will be discussed, whereupon a general overview of the DAVID

<sup>&</sup>lt;sup>5</sup> SDH: Synchronous Digital Hierarchy

<sup>&</sup>lt;sup>6</sup> IETF: Internet Engineering Task Force

<sup>&</sup>lt;sup>7</sup> The concept of MPλS will be discussed in more detail in Section 2.2.3.

<sup>8</sup> ACTS: Advanced Communications Technologies and Services

network architecture will be given in Section 2.2. Finally, a summary will be given in Section 2.3. It should be noted that, as the DAVID project is still running, some of the elements discussed in this chapter may be subject to change as the research project evolves.

## 2.1 Objectives of the IST project DAVID

As mentioned in the introduction to this chapter, the goal of the KEOPS project was mainly to demonstrate that the processing functionalities required in a packet switched network could, to a large extent, be implemented in the optical domain. Very little consideration was paid to integration in a practical network and interoperability between optics and electronics.

The objective of the DAVID project [27] is to exploit the experience gained, e.g., through the KEOPS project to develop a packet-over-WDM network concept that is feasible on a medium term. Both the network traffic properties and management will be taken into account, and the focus will both be on the metro and backbone level. Solutions exploiting both optics and electronics are investigated to find the optimum combination that will realise a multi-Tbit/s capacity; optics are introduced in order to offer a high capacity, while electronics are introduced in order to ease complex signal processing and enable buffering on longer time scales. Furthermore, in order to cope with the convergence in the transport of voice, data and multimedia applications that is seen in commercial networks today, several classes of service will be developed and service differentiation will be investigated. By the end of the project in 2003, a test-bed will be assembled to demonstrate the DAVID solution for metro-core network implementation and integration, as well as interfacing to the client layer.

#### 2.2 Overview of the DAVID network architecture

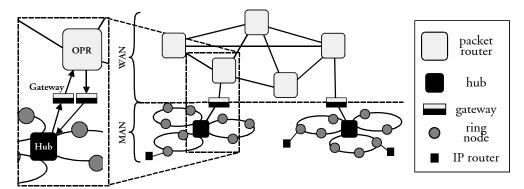

In Fig. 2.1 is shown a schematic of the DAVID network architecture, consisting of a metropolitan part (MAN) and a backbone part (WAN) [28,29]. The complete DAVID network forms an optical transport network that is able to carry (among other things) IP traffic. Both the MAN and the WAN operate in a packet switched mode in order to exploit the network capacity as much as possible. As indicated, the MAN consists of optical packet rings interconnecting optical packet ring nodes (OPRN), with several such rings interconnected through a Hub. The Hub will also provide access to the WAN through a gateway interface. The WAN consists of optical packet routers forming a mesh network. Some of the OPRs function as edge routers that are directly coupled to the MAN and handle add- and drop-traffic from and to the metro network, respectively, while others function as core routers that only handle transit traffic within the core network. Connection points for client traffic are provided in the MAN through connection of IP routers to the MAN ring nodes.

Fig. 2.1: General overview of the DAVID network. To the left a portion of the schematic is shown in an expanded version, and to the right is shown a key to the elements in the figure.

#### 2.2.1 The metro network (MAN)

As mentioned, the DAVID metro network consists of several unidirectional optical physical rings that are interconnected in a star-topology by a Hub. On each fibre, a fixed number of wavelengths are available through the use of WDM. Logical rings (from now on simply denoted rings) can either be physically separated on different fibres, or be obtained by partitioning the optical bandwidth into subsets of wavelengths. Nodes belonging to the same logical ring access the same set of shared resources. All the nodes on a ring can transmit and receive on any wavelength used in that ring. Ring resources are shared by the nodes of the MAN using a statistical time/wavelength/space-division scheme. This is done in the following manner:

- Each wavelength is time-slotted (TDM) with a slot duration of  $\sim 0.5-1 \,\mu s^9$

- Several slots are simultaneously transmitted through WDM

- Rings can be disjoint in space, i.e., on different physical fibres (SDM)

Time slots are aligned on all wavelengths of the same ring so that a multi-slot, consisting of all wavelengths on a logical ring, is available to each node in each time slot. The Hub handles slot alignment among different metro rings.

One of the wavelengths in each multi-slot is dedicated to control and management. This slot, which references data slots in the same multi-slot<sup>10</sup>, can be read and written by each node independently of transmission/reception of data in the other slots of the multi-slot. Ring-to-ring transmission is controlled by a MAC (Media Access Control) protocol and performed via the Hub on a time-slot basis through

$<sup>^{9}</sup>$  The value in the demonstrator is set to 0.5  $\mu$ s, while the exact value for the concept is to be determined.

<sup>&</sup>lt;sup>10</sup> Thus, the addition of a delay is required in each node to process and modify information in the control slot.

dynamic (input ring, output ring) permutation allocation. At any time, all wavelengths in the multi-slot are devoted to transmission to a specific destination ring, identified by a label in the control slot. A ring node may use any wavelength to reach a specific node in the destination ring.

In the MAN, collisions (multiple transmission in the same time slot) and receiver contentions (the number of packets destined for the same node simultaneously exceeds receiver capacity) are avoided at each source node through employment of a MAC protocol [28]. This is done by monitoring the state of the incoming multi-slot and giving priority to in-transit traffic, i.e., traffic not bound for that specific node. Collisions are avoided by prohibiting transmission of packets in a busy time slot, while contentions are avoided by prohibiting packet transmission to a given destination node if its capacity limit (i.e., number of receivers) is already met. It should be noted that contentions may also occur at the Hub. These are avoided by defining the Hub as a space-switch and running a proper slot scheduling algorithm.

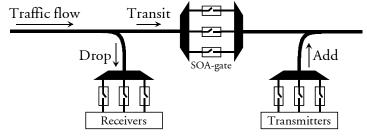

Each ring node is basically composed of two parts: an optical and an electronic part. The optical part, denoted the Optical Packet Add/Drop Multiplexer (OPADM), consists of a transit-, add- and drop part, as shown in Fig. 2.2. The traffic flows from left to right. At the input, a fraction of the WDM signal is tapped off for the drop part. The wavelengths are demultiplexed, whereupon an array of SOA-gates selects the packets to be dropped. These are detected by using a receiver-block, and the rest of the signal is transmitted on to the transit part. Here, an array of SOA-gates placed between a demultiplexer and a multiplexer functions as a fast wavelength selector, which erases packets that are terminated in the node, and allows the rest to pass. The advantage of this configuration is that it allows broadcasting, if desired. At the OPADM output, packets are added to the ring through an array of (tuneable) transmitters followed by a multiplexer. Note that the SOAs placed at the transmitter output are not mandatory; they may or may not be inserted depending on the on/off ratio of the lasers in the transmitter-block in order to prevent excessive cross-talk that degrades the signal quality.

Fig. 2.2: Schematic of the optical part of the MAN ring node (OPADM).

<sup>&</sup>lt;sup>11</sup> On-off ratio: ratio between output power when the laser is turned on and when it is turned off.

The electronic part of the ring node is used to interface to the client layer. It consists of an aggregation (reassembly) stage to create higher bit rate fixed-size data units from variable size packets (and vice-versa), a load-balancing stage to distribute the packets evenly on the available logical rings, and a queuing stage in which packets are grouped and stored per destination ring. The electronic interface also controls the MAC protocol and takes care of packet insertion onto the ring in a free slot.

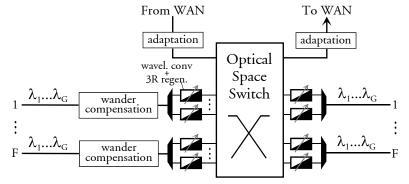

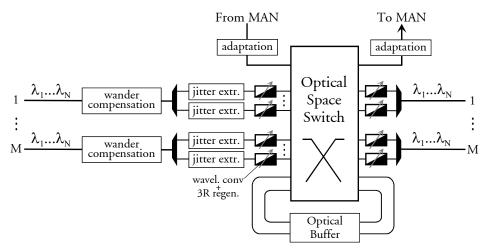

The role of the Hub is to switch packets between metro rings and between the MAN and the WAN. A schematic of the Hub, which is all-optical, is shown in Fig. 2.3. Finand output ports, each carrying G wavelengths, are dedicated to traffic coming from and going to the metro rings. Furthermore, a number of ports are dedicated to traffic coming from or going to the WAN. In order to prepare the traffic exchange between the MAN and the WAN, electronic format adaptation is performed (in the Gateway, c.f., Fig. 2.1). This will be discussed in more detail in Section 2.2.3. At the metro input interfaces, wander compensation (i.e., coarse, slow packet synchronisation) is performed in the WDM domain in order to align packets from the rings to the local frame clock of the Hub and to enable switching in a synchronous manner within the Hub. This synchronisation is required to compensate for slow delay variations due to, e.g., temperature fluctuations in the network. The exact configuration of the MAN wander compensator is, unlike the one in the WAN that will be discussed in Section 2.2.2, not decided yet. However, because the constraints are more relaxed in the MAN than the WAN, the wander compensator will be simpler, as will be discussed in Section 2.2.2. At the output of the wander compensators, wavelength conversion and 3R regeneration<sup>12</sup> are performed simultaneously through the use of SOA-based interferometers, which will be described in more detail in Chapters 4 and 5. Wavelength conversion is necessary to relax the constraints on the ring nodes and ease the slot scheduling in the MAN. 3R regeneration is employed in order to ensure a good signal quality. At the output of the space-switching fabric, which will be described in Section 2.2.2, wavelength conversion and 3R regeneration are performed

Fig. 2.3: Schematic of the Hub.

<sup>12 3</sup>R regeneration: Re-amplification + Re-shaping + Re-timing.

again to prepare for subsequent transmission. It can be noted that an advantage of having wavelength conversion both at the input and output of the switching fabric is that it allows complete decoupling between the wavelengths used internally in the Hub and the wavelengths used externally in the network. This may relax the requirements to the optical component count in the switching fabric, depending on the chosen configuration as discussed in Section 2.2.2.

#### 2.2.2 The core network (WAN)

As mentioned previously, the WAN consists of optical packet routers forming a mesh network. The structure of the core OPR [30], which is shown in Fig. 2.4, is much like the Hub as seen in Fig. 2.3. For the OPR, M in- and output ports, each carrying N wavelengths, are dedicated to transit traffic within the WAN. Furthermore, if the OPR is an edge router, a number of ports are dedicated to addand drop traffic coming from or going to the MAN Hub, respectively. Finally, a number of ports are dedicated to packet contention resolution through the use of an optical fibre-delay line (FDL) recirculating loop buffer. The mode of operation and traffic performance of the optical buffer will be discussed in more detail in Chapter 3. In addition to the WDM wander compensation blocks, the OPR also contains single-channel jitter extraction blocks, which enable synchronisation to the local clock of the OPR by compensating for packet-by-packet jitter introduced when cascading many core nodes. This jitter occurs because exact matching of the lengths of different optical paths within a core node is impossible. As packets in the MAN only traverse one node, namely the Hub, the jitter extraction blocks are not necessary in the metro network. The OPR packet synchronisation unit is described in detail in [31]: the WDM wander compensator consists of two identical blocks that are switched between, so that each block services alternate packets. Each block

Fig. 2.4: Schematic of the WAN optical packet router [30].

consists of a cascade of 11 slow switches with FDLs of different lengths, exponentially distributed, placed in between. The jitter extractor, which has a resolution of 5 ns, consists of an array of four SOAs and FDLs of different lengths placed in between a 1:4 splitter and a 4:1 combiner, thus enabling fast packet-by-packet alignment. It should be mentioned that precise dispersion management is done on the transmission links, meaning that dispersion compensation is not performed as part of the synchronisation unit.

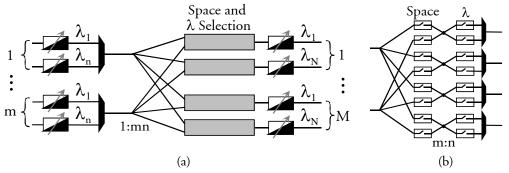

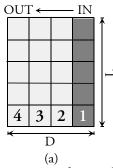

In Fig. 2.5a is shown a schematic of the optical switching fabric employed in the Hub and OPR. Note that, for completeness, the input and output wavelength converters are also shown in the figure. At the input to the switching fabric, packets arrive at mn (=MN) different input streams. Subsequent wavelength conversion and multiplexing band the mn input streams into m internal WDM groups, each carrying n wavelength channels. The m WDM groups are split out to mn SOA-based spaceand wavelength selection blocks that enable fully non-blocking switching. These blocks can, e.g., be implemented as shown in Fig. 2.5b using two sets of SOA arrays separated by mxn star couplers. The first set of SOAs selects a group of wavelengths coming from one of the switching fabric inputs, while the second set of SOAs in conjunction with the following multiplexers select a specific wavelength. Thus, at the output of each space- and wavelength selection block, a single packet within each time slot has been selected. This configuration has been chosen, among other things, because it allows both point-to-point connection as well as multicasting. Moreover, as very fast wavelength selection (ns-level) is not currently possible using tuneable filters, why the scheme using SOAs in conjunction with multiplexers must be employed. Following the space- and wavelength selection blocks, wavelength converters convert the wavelength to prepare for the following transmission, while 3R regeneration is performed to compensate for signal distortion caused in the optical switching fabric (in analogy to the Hub). Note that (m,n), used internally in the switching fabric, can be different from (M,N), which refers to the external fibres/wavelengths to the OPR. The (m,n) wavelength banding is performed to reduce the optical component count in the space- and wavelength selection blocks to a minimum, which for symmetry reasons is obtained for m=n (see Fig. 2.5b). In the DAVID project, the goal with respect to throughput in the WAN is 2.56 Tbit/s for each OPR. The bit rate is set to 10 Gbit/s, thus giving a maximum-size switching fabric of 256x256. The throughput of 2.56 Tbit/s is enabled through the use of 32 wavelengths per fibre, meaning (M,N)=(8,32). However, internally in the switching fabric (m,n)=(16,16) is used to reduce the optical component count, as discussed. The electronic control and header processing performed in the core OPRs is closely related to the switching/routing approach that is adopted in the DAVID project. This topic is discussed in Section 2.2.3.

Fig. 2.5: (a) Optical switching fabric in the Hub and OPR. (b) One possible implementation of space and wavelength selection blocks (shown with interconnection shuffle at input) [30].

### 2.2.3 The DAVID network hierarchy

The DAVID network concept covers a whole range of networking levels from the metro network to the optical backbone network. Within DAVID, Multiprotocol Label Switching is used to create a unified switching/routing approach covering all network levels including the MAN. This affects the functionalities included, e.g., in the interface (Gateway) between the MAN and the WAN and electronic control of the WAN OPR. In this section the concept of MPLS will be discussed briefly, and the hierarchical MPLS approach used in the DAVID project will be described. Furthermore, the affect this has on the functionalities implemented in the MAN-WAN gateway and the header processing performed in the OPRs is also discussed.

Historically, MPLS was the result of a convergence of a number of "IP switching" schemes or techniques that used ATM (Asynchronous Transfer Mode) hardware to speed up the forwarding of IP packets (see [32,33] for an overview). In order to standardise the different IP switching schemes, the MPLS working group was founded in the Internet Engineering Task Force (IETF) in 1997 [34]. This working group has since then been working on a common technology for IP switching that is independent of the underlying transport layer.

In a traditional IP network, an IP packet is stored and forwarded in each router it passes based on a longest-prefix match processing of the global destination address. However, due to the unsystematic relation between the IP address and destination, this table look-up is rather cumbersome. In IP/MPLS networks [35], the IP table look-up is replaced by simple and fast label switching: the IP control plane, with its flexibility and scalability is preserved, but extended with the MPLS functionality. In contrast to regular IP, MPLS is a connection-oriented protocol that works by setting up unidirectional label-switched paths. As will be explained below, this has important consequences with respect to, e.g., traffic engineering.

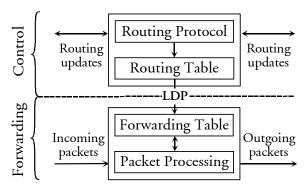

#### Control and forwarding:

Network-layer routing can be divided into two basic components, namely control and forwarding [32,33]. The relationship between the routing and forwarding components in MPLS is illustrated in Fig. 2.6. The control component employs standard routing protocols (e.g., OSPF (Open Shortest Path First) [36]) to exchange information with other routers, and based on routing algorithms, it uses LDP (Label Distribution Protocol) to build up and maintain a forwarding table based on the routing information. The forwarding component has the task of processing incoming packets, examining the headers and making forwarding decisions based on the forwarding table.

Fig. 2.6: Relationship between routing and forwarding components in MPLS.

#### Forwarding based on FEC and label swapping:

An IP header contains considerably more information than is needed to choose the next hop towards a packet's destination. Choosing the next hop can be thought of as a composition of two sub-functions [37]. The first is to partition the entire set of all possible packets so that a router can forward a finite number of subsets, or Forward Equivalence Classes (FECs). From a forwarding point-of-view, packets belonging to the same subset are indistinguishable: they are treated by the router in the same way. The second sub-function performed by the forwarding component is to map each FEC to a next hop.

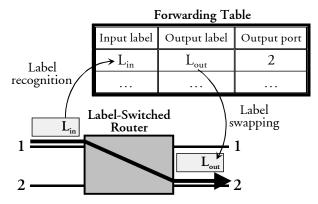

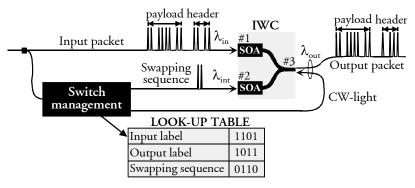

In MPLS the assignment of a particular packet to a specific FEC is done only once, as the packet enters the MPLS network at the co-called ingress label-switched router (LSR). The FEC, to which a packet is assigned, is encoded as a short, fixed length value, called a label. When a packet is forwarded to its next hop, the label is sent along with it. At subsequent hops, there is no further analysis of the packet's network layer header: only the attached label needs to be examined. This label-processing that is performed in each LSR is denoted label swapping, as illustrated in Fig. 2.7: a packet carrying the label  $L_{in}$  arrives at an LSR. This label is recognised and subsequently used as an index in the forwarding table (i.e., look-up table) that

specifies the next hop and the new label to use. When forwarding the packet to the next hop (located at output port #2 in the figure), the old label is replaced with the new label,  $L_{out}$ , which is processed at the next LSR upon arrival. This replacement of an old label with a new label is called label swapping. It can be mentioned that both label recognition and label swapping can be performed all-optically; Sections 6.2.1 and 6.2.2 describe some novel schemes to perform these functionalities in a simple manner by using a single SOA-based interferometer as a logic gate. Finally, at the node where the packet leaves the MPLS network (the so-called egress node), the label will be stripped off, reducing the packet to the format it entered the MPLS domain in (e.g., an IP packet): this is called label popping.

Fig. 2.7: The principle of label swapping in an MPLS network. In the LSR, the input label,  $L_{in}$ , in a packet is recognised and subsequently processed in a forwarding table. It is replaced by a new label,  $L_{out}$ , and the packet is forwarded to port #2.

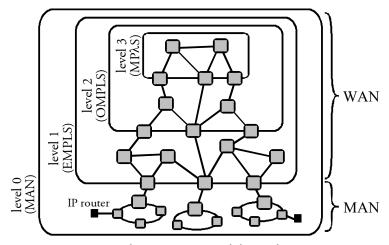

Within the DAVID project, it has been decided that in order to ensure that the WAN is both flexible and future-proof, it should be structured in a manner that can handle various bit-rates, different levels of aggregation and functionality. From the MAN access to the core of the WAN the throughput of nodes increases and the granularity decreases. Close to the MAN, to cope with a lower level of aggregation and limited throughput compared to the core WAN, one solution is to consider electronic routers that can provide the required flexibility and the capacity. Then, going more deeply in the core of the backbone, optical switching nodes can provide a higher capacity as well as flexibility by employing a medium level of aggregation combined with the granularity of the optical packet. Finally, in the high levels of the WAN, one can imagine that the level of aggregation is sufficient to allocate dynamic wavelength paths. This view of the network enables definition of a hierarchical DAVID network architecture, as shown in Fig. 2.8. Within each level of the hierarchy, MPLS is used. As indicated, within level 1 electrical MPLS (EMPLS) is employed, level 2 uses optical MPLS (OMPLS) and level 3 uses MP\LambdaS. In this connection, it should be noted that the terms mentioned here are not standardised; they originate within the DAVID project.

An MPLS-like networking concept is used within each level of the DAVID WAN hierarchy because of the scalability of MPLS, its support of Quality of Service (QoS) at the network level, and because MPLS provides the tools for traffic engineering in the network: with MPLS one can set up explicit routes through the network to optimise the usage of available network resources, or to create distinct paths for different QoS classes. Moreover, MPLS supports the formation of hierarchies, which is beneficial for the DAVID concept. Each hierarchical level in Fig. 2.8 can be described as follows [38]:

- Level 0: The MAN- as discussed in Section 2.2.1, the WDM dimension is used to establish a virtual topology, which is modified within the duration of a packet. At any time, the virtual topology within the MAN is controlled by the MAC protocol.

- Level 1: The EMPLS level is composed of packet routers that perform electrical switching of packets (i.e., O/E/O conversion is performed), including label swapping. In DAVID, the EMPLS level is used at the periphery of the hierarchical WAN where the capacity of electronic routers is sufficient. Moreover, it acts as an adaptation level, which performs traffic aggregation [38] and advanced label processing between the MAN and the OMPLS level. Thus, the functionalities implemented by the EMPLS level are concentrated in the MAN-WAN Gateway, as shown in Fig. 2.1. These functions are not yet feasible within the optical domain, mainly because the required sophisticated buffering schemes can only be implemented in electronics. This is discussed in more detail in Chapter 3.

- Level 2: At the OMPLS level, the packet payload is switched transparently within the optical packet routers as a means to enable higher throughput nodes (higher bit rates and more wavelengths). Packet forwarding is based on a look-up table, and the wavelength dimension is used to resolve contention, as far as possible. This is done by employing different wavelengths for packets bound simultaneously for the same output fibre. The OMPLS level uses optical packet forwarding to achieve a very high throughput. However, the functionality of optical packet switches is rather limited, why, in order to reach a high throughput, the granularity of the optical packets must be larger than the granularity used at the EMPLS level. The required packet duration is, among other things, dictated by the header processing time and the reconfiguration time needed by the optical switches. This has been studied extensively in connection with, e.g., the KEOPS project [39].

Level 3: If a larger extent of aggregation is beneficial than the OMPLS level can provide, an addition lambda-switched level may be the best solution. The MPλS level switches at the wavelength level with the wavelength assignment being performed by the MPLS control plane functions. Another use of the MPλS level could be in connection with service differentiation, where a specific lambda-switched path is set up for a service class requiring a superior QoS. It should be noted that the OPR architecture shown in Fig. 2.4 and Fig. 2.5 can support MPλS by allowing the set-up of dedicated circuits, meaning that the specific path through the optical switch is not reconfigured on a packet-by-packet basis. On this level, the MPLS label is equivalent to a specific wavelength, meaning that label swapping is equivalent to wavelength conversion. This means that alloptical wavelength conversion, which is the topic of Chapter 4, is a critical factor for the implementation of optical MPλS.

Practical implementation of the MPLS hierarchy is enabled by allowing packets to carry a number of labels, organised as a last-in first-out stack, denoted a label stack [37]. Each level in the hierarchy is associated with one label in the stack, and the packet is processed based on the top-level label at that moment. At the ingress to each level, a new label is pushed onto the stack, and at the egress, the label used within that specific hierarchical domain is popped off again.

Fig. 2.8: The DAVID network hierarchy [38].

## 2.3 Summary

In this chapter, the implementation of an optical packet-switched network has been discussed, using the European research project DAVID as a case study. It has been argued that optical packet switching is advantageous for implementing packet-over-WDM due to the flexibility, scalability and high level of granularity is offers.

The DAVID network, which includes both a metro and core part, has been discussed. The metro network consists of rings exploiting WDM that interconnect optical packet ring nodes. A central Hub exploiting a MAC protocol takes care of the access control. A MAN-WAN Gateway performs the interfacing, which includes traffic shaping and aggregation, between the two network layers. Finally, in the core network a mesh topology interconnects optical packet routers that exploit WDM in conjunction with wavelength conversion as well as an optical fibre delay-line buffer for contention resolution.

The overall DAVID network concept is hierarchical, and employs MPLS in order to exploit the advantages of, e.g., traffic engineering and aggregation. A description of the different levels in the DAVID hierarchy has been given and the different levels involving electrical MPLS, optical MPLS as well as MP\LS have been related to the DAVID network architecture.

# Chapter 3

# The traffic performance of an optical packet router

When dimensioning a packet switched network, there are two major aspects that need to be taken into account in order to ensure that information can be transferred from source to destination with an acceptable result and cost. Firstly, the physical performance of the network must be good, meaning that the data can be transmitted with a level of distortion (i.e., signal quality) that is acceptable for the operator/user. This may typically involve a required bit error rate (BER) at the receiver in the order of 10<sup>-12</sup>-10<sup>-15</sup>. This good signal quality is ensured through careful planning and design of the physical structure of the network, and will in today's commercial networks mean dispersion mapping, calculation of the end-to-end power budget, repeater spacing, etc. Secondly, the end-to-end traffic performance, which covers aspects relating to quality of service, must be acceptable. This means limiting the packet loss ratio (PLR)<sup>13</sup> to the order of 10<sup>-6</sup>-10<sup>-10</sup>, strongly depending on application. Furthermore, the end-to-end delay should be bounded. This factor is especially critical in the case of real-time traffic (e.g., telephony), where a delay of more than 25 ms [40] may degrade the quality. The network should be dimensioned to ensure an acceptable traffic performance for a well-defined offered traffic load. Again, the exact value required will vary, but a good design choice may be in the ~0.8 range. This high value is chosen in order to ensure that the bandwidth utilisation is kept high and the PLR reasonably low. Often the requirement of a high traffic load in conjunction with reasonable PLR will be difficult to meet in practice, especially under bursty traffic conditions, why careful dimensioning of the network switch nodes and traffic shaping will be necessary.

In this chapter the traffic performance of optical packet routers in core networks will be discussed, with the focus on minimising the PLR while keeping the component count and physical implementation feasible. In Section 3.1, the restraints placed on the packet router implementation due to limitations in optics will be discussed. Subsequently, two generic implementations of OPRs, relying on output and shared buffering, will be given and the traffic performance will be compared. Finally, in Section 3.3.3, a more in-depth analysis will be given of the traffic performance of the DAVID OPR, which was described in Chapter 2. The analysis will be based on a packet scheduling algorithm developed as a contribution to the DAVID project.

<sup>&</sup>lt;sup>13</sup> The packet loss ratio is defined as the ratio between data packets lost due to congestion/overload and the total number of packets transmitted.

## 3.1 The pros and cons of the optical packet router

Within the last years, much research has been devoted to the investigation of packet routers/switches implemented in the optical domain [17,25,26,41]. One of the major advantages of all-optical packet routers, as opposed to electronic routers involving O/E/O-conversion, is that scaling of the switch capacity can be achieved cost-effectively. Electronic IP/MPLS routers are now reaching capacities in the sub-Tbit/s throughput range with 10 Gbit/s line cards. However, reaching multi-Tbit/s throughput requires extensive parallelism and complex interconnection, which, although feasible, is not likely to be cost-effective [17]. Furthermore, power consumption and size are likely to be critical factors for the implementation of high-capacity electrical packet routers [3].

Thus, the advantage of all-optical high-capacity packet routers seems obvious; because the payload is switched transparently using, e.g., optical gates, complexity and power consumption is less dependent on bit rate. However, conversion to the electrical domain enables the exploitation of some very attractive features, which, as yet, are not practically feasible in the optical domain. One functionality that is quite complex, and therefore currently only feasible in the electrical domain is header processing, which, e.g., involves address recognition and -modification in data packets. Although much research is devoted to the optical implementation of these functionalities, as will be discussed in Chapter 6, the technology has not yet reached maturity, why pure optical packet switching is still years away. For medium-term network scenarios an opto-electronic approach where optical packet routers use electronic control and header processing is more realistic. This is also the scheme used in the DAVID research project, as discussed in Chapter 2. Packet switching requires a packet buffer memory in order to resolve contention between packets arriving simultaneously at the switch node input destined for the same output. This contention resolution is performed by delaying one packet with respect to the other, combined with wavelength conversion for handling wavelength blocking (wavelength conversion will be discussed in Chapter 4). An optical buffer would be desirable in order to preserve a high capacity all-optical data path. However, optical memory is at this time at a rather primitive stage, why it is necessary to resort to fibre delay-lines for packet storage. In general, the packet loss ratio is reduced when the delay-line length is increased. However, even small optical delay-line buffers with delays up to, e.g., ~20 time slots require long fibre spans in the range of ~4 km<sup>14</sup>. This is problematic due to issues such as cost, physical size and temperature

$<sup>^{14}</sup>$  A packet time duration of 1  $\mu$ s is assumed, corresponding to a length of 200 m. Packet durations in the range ~0.5-1.5  $\mu$ s are deemed to be optimal for applications in WANs. For example in the European ACTS project KEOPS, a packet duration of ~1.65  $\mu$ s was chosen [25], while a packet duration of 1  $\mu$ s is tentatively chosen in the DAVID project.

stabilisation. In contrast, an electronic RAM for storage of hundreds of thousands of packets is easily implemented and the storage time can be chosen freely. Thus, the implementation of optical packet routers requires careful dimensioning of the optical buffer in order to ensure that the required traffic performance is achieved without compromising the practical implementation. This is the topic of the remainder of this chapter.

## 3.2 Comparison of optical packet router architectures

There exist three basic types of buffering schemes in electronic packet switch architectures that can also be implemented in the optical domain, namely input- and output queuing and shared loop-back buffering. With input queuing, a separate buffer is placed on each input of the switch and in the simplest case of first-in-firstout (FIFO) queuing, packets arriving at the inputs are forwarded to the correct output in turn. With output queuing, a buffer is placed at each output of the switch, and arriving packets are forwarded to the correct output before being buffered. In the electrical domain, there exists a trade-off between input and output queuing. For traditional input queuing, the throughput is limited<sup>15</sup> because a packet can be held up by another packet ahead of it in line that is destined for a different output. This phenomenon, known as head-of-line (HOL) blocking, is, however, not a problem nowadays due to the introduction of Virtual Output Queuing (VOQ), where each input buffer is divided into separate logical queues for each output [42], thus avoiding HOL. Unfortunately, VOQ requires a rather complex scheduling algorithm, why alternatives to strict VOQ are attractive. These issues do not exist for output queuing with which there, however, exists a problem of internal speed-up because several packets destined for the same output may arrive simultaneously. Thus, the processing speed in the electrical output buffer must be K times the external line rate if there are K input ports to the switch. This means that, in practice, a combination of VOQ and output queuing is used for electronic buffers [43], thus exploiting the advantages of each scheme.

An optical buffer is constructed using fibre delay-lines, why the problem associated with speed-up for output queuing is nonexistent. For this reason output queuing is advantageous to input queuing in all respects in the optical domain.

The third buffering scheme is shared buffering, in which the memory is pooled and shared completely between all outputs. This sharing allows a reduction in the total amount of buffering, however at the expense of a larger switching fabric, as will be seen in Section 3.2.2. Another potential problem with completely shared buffering is

<sup>&</sup>lt;sup>15</sup> Assuming FIFO queuing and independent, identically distributed arrival processes with destinations uniformly distributed over all outputs, the throughput is limited to  $(2-\sqrt{2})\approx58.6\%$  [44].

that one heavily loaded output might monopolise use of the shared buffer, thus adversely affecting the performance of the other outputs [45]. This can, however, be prevented with an appropriately designed buffer scheduling algorithm.

## 3.2.1 Description of architectures

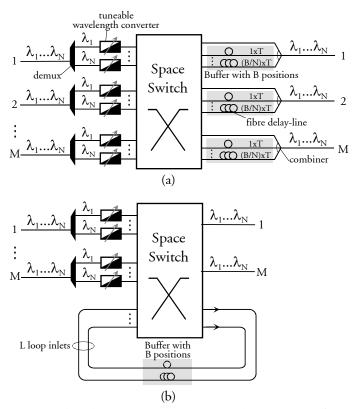

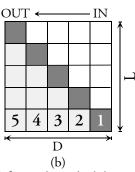

Based on the discussion given above, output and shared buffering are the two alternatives to be considered for optical packet switching. In Fig. 3.1 below are shown two generic optical packet router architectures relying on output buffering (Fig. 3.1a) and shared buffering (Fig. 3.1b), respectively. Both exploit WDM in conjunction with wavelength conversion for contention resolution. Note that the specific OPR architectures shown in Fig. 3.1 have been chosen as similar as possible in order for a fair comparison of the performance and space-switch size to be made in this section.

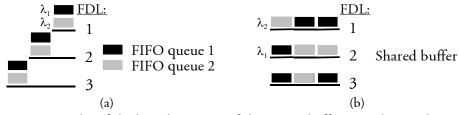

The architecture in Fig. 3.1a, denoted OPR a, has been proposed in the KEOPS project [18], wherein the traffic performance of optical packet switches using output buffering was investigated. The architecture, which has M in- and output ports, each carrying N wavelengths, can be divided into three main blocks: 1) The input section, where packets arriving at each inlet on the N fixed wavelengths  $\lambda_1$ - $\lambda_N$  are separated through demultiplexing, and tuneable optical wavelength converters change the wavelength of each incoming packet to address free space in the N different queues made available by the FDLs at each output. 2) The space switch, which is used to access the correct output as well as FDL, and therefore the proper delay. 3) Packet buffers that are realised by FDLs. As seen from the figure, the space switch has the size MNxM(B/N+1), where B is the number of packet positions in each output buffer and B/N is the number of fibre delay-lines. In the simplest case, the buffer is denoted degenerate<sup>16</sup> and consists of FDLs with length increments corresponding to one packet duration, i.e., the FDL has a length of one time slot, the second a length of two time slots, etc., and the last delay-line has a length of B/N=D time slots. Logically, each output buffer functions as a set of N FIFO queues, as illustrated schematically in Fig. 3.2a. Here, an example is given where the number of wavelengths, N, is two and the number of FDLs, D, is three. As indicated, this means that, by exploiting WDM, the buffer can store six packets simultaneously in two logical FIFO queues. Note that this means that temporal synchronisation of packets at the same wavelength in different FDLs is not allowed, as this will result in contention at the output.

<sup>&</sup>lt;sup>16</sup> A non-degenerate FDL buffer will have delay-line length increments that are not equal to one timeslot. Often an exponential increment is used. As shown in [46] this may result in a good traffic performance with the use of fewer FDLs, however at the expense of an increased length, more complex packet scheduling and a larger probability of the packet sequence integrity being violated.

In Fig. 3.1b is shown an OPR architecture (denoted OPR b), which relies on a recirculating loop to implement the optical buffer. An architecture, which logically functions as the one shown here, has been proposed as part of the DAVID project (see Fig. 2.4). As in Fig. 3.1a, the architecture has M in- and output ports for transit or add/drop traffic, each carrying N wavelength channels. Furthermore, L in- and outlets to the switching fabric are allocated to a recirculating loop buffer, which is shared by all outlets. After demultiplexing, tuneable wavelength converters are used to address a free output wavelength channel at the desired outlet. Alternatively, in case of contention the wavelength converters may be used to address free wavelengths in the recirculating loop, depending on the loop structure. This will be discussed in more detail later. The space switch, having the size (MN+L)x(M+L), is used to access the correct output port and wavelength channel or, in case of contention, the correct recirculating loop inlet. Note that wavelength converters are not placed at the loop outlets. This choice is made in order to allow a better comparison of the two architectures, as neither architecture allows full flexibility with respect to output wavelength as they are shown in Fig. 3.1; the output wavelength is partially determined by the queuing situation at hand. Regarding the

Fig. 3.1: Generic optical packet router architectures exploiting WDM for contention resolution. (a) Output buffering using fibre delay-lines. (b) Shared buffering using a recirculating loop.

structure of the recirculating loop, many different scenarios are possible. The simplest one is the fixed size loop, where all L inlets lead to the same delay D, thus enabling buffering of up to B=LD packets simultaneously. This structure can be implemented, e.g., by employing just one fibre in the loop with L wavelengths and adding a demultiplexer and a multiplexer at the in- and output of the loop, respectively. Alternatively, L different fibres can be used with the same length, thus avoiding the use of costly (de)multiplexers but at the expense of a more bulky design. In both cases, the traffic performance of the loop buffer will be the same.

In Fig. 3.2b is shown the logical structure of the fixed size recirculating loop buffer in the case of L=3 fibres with length D=3 time slots, each carrying one wavelength per time slot, but exploiting two different wavelengths internally. As indicated, unlike the output queuing in Fig. 3.2a, the shared buffer does not forbid temporal overlap of packets at the same wavelength in different FDLs if they are destined for different output ports. The packet scheduling algorithm, which will be described in more detail in Section 3.2.2, ensures that packets exiting the loop simultaneously destined for the same output port will be wavelength converted to different wavelengths before buffering.

Fig. 3.2: Examples of the logical structure of the output buffer (a) and recirculating shared buffer (b) in Fig. 3.1a and b, respectively.

## 3.2.2 Component count and basic traffic performance

The same logical OPR architecture can be implemented physically in numerous ways. For example, the switching fabric within the logical architecture shown in Fig. 3.1b, which is used in the DAVID project, can be implemented in its simplest form by splitting out to an array of (MN+L)x(M+L) SOA gates [18] and subsequent combining, or it can be implemented as shown in Fig. 2.5. This configuration is chosen to ensure a good physical performance, as discussed in Section 2.2.2. The same is the case for the architecture in Fig. 3.1a.

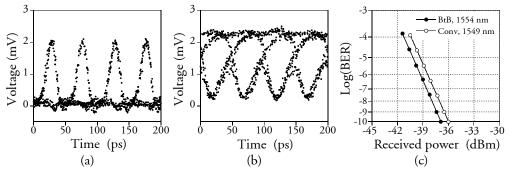

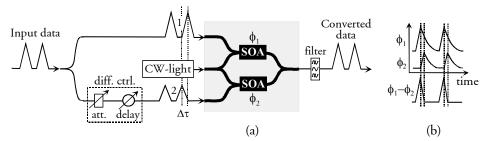

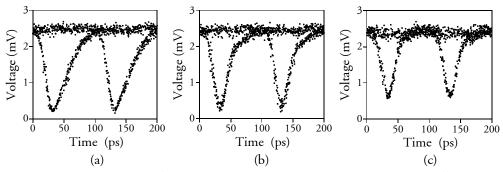

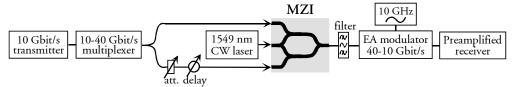

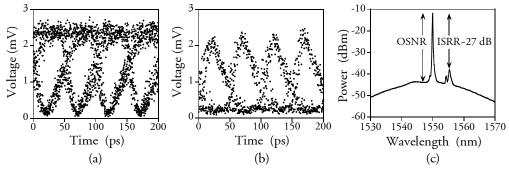

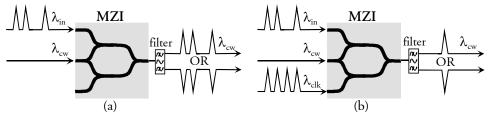

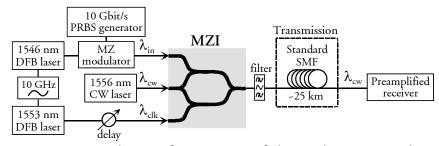

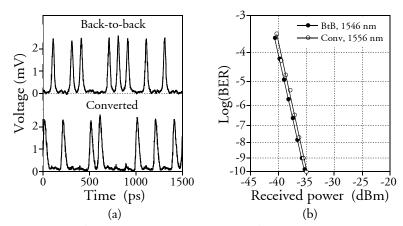

In this section a comparison of the component count of the two architectures in Fig. 3.1 will be given, assuming the most simple physical implementation of the architectures, which, as discussed above, may involve the employment of an SOA gate array with a size corresponding to the size of the space-switching fabric. This choice is made in order to ensure a fair comparison of the two architectures, as mentioned previously. Assuming that the space-switching fabric is implemented as discussed