# VLSI IMPLEMENTATION OF LOW POWER RECONFIGURABLE MIMO DETECTOR

A Thesis

by

### RAJBALLAV DASH

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

December 2009

Major Subject: Computer Engineering

# VLSI IMPLEMENTATION OF LOW POWER RECONFIGURABLE MIMO DETECTOR

A Thesis

by

### RAJBALLAV DASH

### Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

Approved by:

| Chair of Committee, | Gwan S. Choi          |

|---------------------|-----------------------|

| Committee Members,  | Peng Li               |

|                     | Duncan M.H. Walker    |

| Head of Department, | Costas N. Georghiades |

December 2009

Major Subject: Computer Engineering

#### ABSTRACT

VLSI Implementation of Low Power Reconfigurable MIMO Detector. (December 2009) Rajballav Dash, B.Tech., National Institute of Technology Rourkela Chair of Advisory Committee: Dr. Gwan S. Choi

Multiple Input Multiple Output (MIMO) systems are a key technology for next generation high speed wireless communication standards like 802.11n, WiMax etc. MIMO enables spatial multiplexing to increase channel bandwidth which requires the use of multiple antennas in the receiver and transmitter side. The increase in bandwidth comes at the cost of high silicon complexity of MIMO detectors which result, due to the intricate algorithms required for the separation of these spatially multiplexed streams. Previous implementations of MIMO detector have mainly dealt with the issue of complexity reduction, latency minimization and throughput enhancement. Although, these detectors have successfully mapped algorithms to relatively simpler circuits but still, latency and throughput of these systems need further improvements to meet standard requirements. Additionally, most of these implementations don't deal with the requirements of reconfigurability of the detector to multiple modulation schemes and different antennae configurations. This necessary requirement provides another dimension to the implementation of MIMO detector and adds to the implementation complexity.

This thesis focuses on the efficient VLSI implementation of the MIMO detector with an emphasis on performance and re-configurability to different modulation schemes. MIMO decoding in our detector is based on the fixed sphere decoding algorithm which has been simplified for an effective VLSI implementation without considerably degrading the near optimal bit error rate performance. The regularity of the architecture makes it suitable for a highly parallel and pipelined implementation. The decoder has intrinsic traits for dynamic re-configurability to different modulation and encoding schemes. This detector architecture can be easily tuned for high/low performance requirements with slight degradation/improvement in Bit Error Rate (BER) depending on needs of the overlying application. Additionally, various architectural optimizations like pipelining, parallel processing, hardware scheduling, dynamic voltage and frequency scaling have been explored to improve the performance, energy requirements and re-configurability of the design. Dedicated to family and friends

A special dedication to my newly born niece Ashwanita

#### ACKNOWLEDGEMENTS

First, I would like to thank my advisor, Dr. Gwan Choi for his encouragement and support during the duration of my research and my committee members, Dr. Peng Li, and Dr. Hank Walker for their feedback. A special thanks to my friend and colleague, Pankaj Bhagawat who provided valuable philosophical and technical inputs during the course of my research work. I also take this opportunity to thank Dr. Sunil Khatri whose words of advice have been a great influence.

Thanks to my family for their tremendous belief in me. A final note of thanks to all my friends at Texas A&M University and outside, who have kept me entertained and motivated during my stay here at the university.

## **TABLE OF CONTENTS**

| ABSTRA  | СТ                                                  | iii |

|---------|-----------------------------------------------------|-----|

| DEDICA  | ΓΙΟΝ                                                | v   |

| ACKNOW  | VLEDGEMENTS                                         | vi  |

| TABLE C | OF CONTENTS                                         | vii |

| LIST OF | FIGURES                                             | ix  |

| LIST OF | TABLES                                              | xi  |

| 1. INTR | ODUCTION                                            | 1   |

| 1.1     | MIMO Systems: An Overview                           | 2   |

| 1.2     | 2 Implementation Challenge of MIMO Detector         | 3   |

| 1.3     | 3 Current Generation MIMO Systems                   | 4   |

| 1.4     | 4 Contributions                                     | 7   |

| 1.5     | 5 Thesis Outline                                    | 10  |

| 2. BACK | GROUND OF MIMO DETECTION                            | 11  |

| 2.1     | System Model and Processing Stages                  | 11  |

| 2.2     | 2 Maximum-Likelihood Detection and Sphere Decoding  | 17  |

| 2.3     | 3 Analysis Criteria for VLSI Implementation         | 21  |

| 2.4     | Discussion of Implementation/Simulation Methodology | 23  |

| 3. FPGA | IMPLEMENTATION OF RECONFIGURABLE MIMO DETECTOR.     | 25  |

| 3.1     | Fixed Sphere Decoding and COSIC                     | 25  |

| 3.2     |                                                     | 29  |

| 3.3     |                                                     | 35  |

| 3.4     | Summary of Results and Conclusion                   | 37  |

| 4. ARCH | IITECTURAL SPACE EXPLORATION OF RECONFIGURABLE      |     |

| MIMO    | DETECTOR FOR IEEE 802.11n                           | 38  |

| 4.1     | Architectural Flexibilities in FSD Implementation   | 41  |

| 4.2     | 2 High Level Architectural Space Exploration        | 42  |

| 4.3     | B Details of the MIMO Detection VLSI Architecture   | 49  |

# Page

|             | 4.4     | ASIC Implementation Results                      | 51 |

|-------------|---------|--------------------------------------------------|----|

|             | 4.5     | Results, Summary and Conclusion                  | 52 |

| ~           |         | AWER RECOVERED AND END OF DETECTOR FOR REAL TRUE |    |

| Э.          |         | OWER RECONFIGURABLE MIMO DETECTOR FOR REAL-TIME  |    |

|             | MOBIL   | E APPLICATIONS                                   | 53 |

|             |         |                                                  |    |

|             | 5.1     | Circuit Power Estimation and Reduction           | 56 |

|             | 5.2     | DVFS Based Low Power Decoder Architecture        | 58 |

|             | 5.3     | Implementation Results                           | 66 |

|             | 5.4     | Results, Summary and Conclusions                 | 69 |

|             |         |                                                  |    |

| 6.          | SUMM    | ARY, CONCLUSIONS AND FUTURE WORK                 | 71 |

|             |         |                                                  |    |

| RF          | EFERENC | CES                                              | 73 |

| <b>X</b> 71 | Τ 4     |                                                  | 70 |

| ٧I          | IA      |                                                  | 79 |

# LIST OF FIGURES

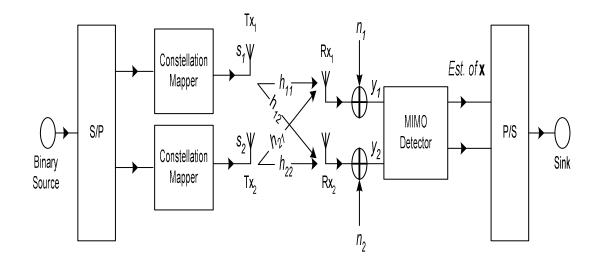

| Figure 2.1  | Example of a 2x2 MIMO Communication System with Channel Matrix                                                     | 14 |

|-------------|--------------------------------------------------------------------------------------------------------------------|----|

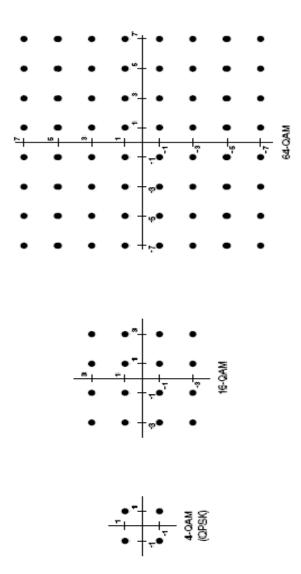

| Figure 2.2  | Constellation Point for QPSK, 16-QAM, 64-QAM Modulation Schemes                                                    | 15 |

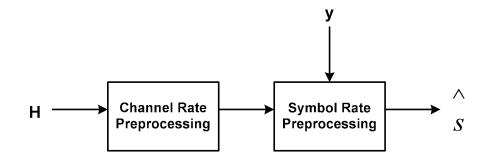

| Figure 2.3  | Processing Stages in General MIMO Detector                                                                         | 16 |

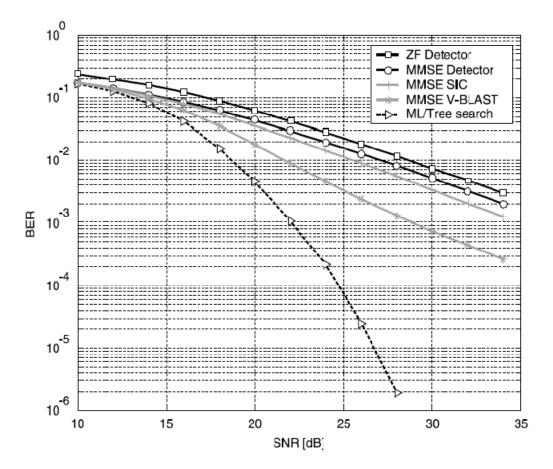

| Figure 2.4  | BER Performance of MIMO Detection Algorithms [4]                                                                   | 16 |

| Figure 2.5  | Example of ML Solution for 2x2 BPSK Systems                                                                        | 17 |

| Figure 2.6  | Example of Sphere Criterion and Tree Pruning                                                                       | 20 |

| Figure 2.7  | Computation of PD in Each Level of the SD Tree                                                                     | 20 |

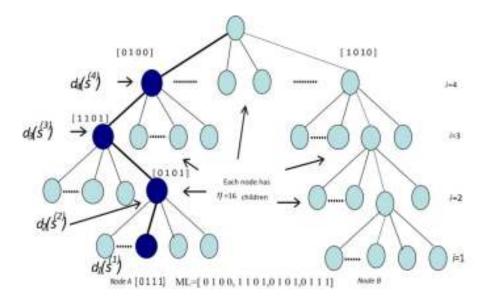

| Figure 3.1  | Example of (3, 2, 1, 1) FSD Ordering in [19]                                                                       | 27 |

| Figure 3.2  | Tree Structure of COSIC Algorithm                                                                                  | 27 |

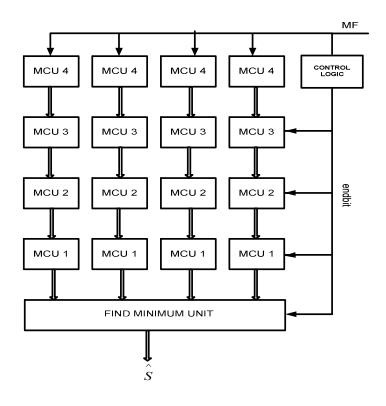

| Figure 3.3  | Data Path Parallelism and Control Structures                                                                       | 28 |

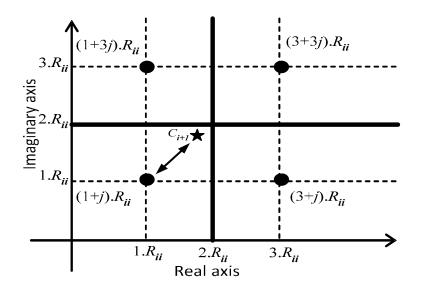

| Figure 3.4  | Example of Slicing Operation for 16-QAM                                                                            | 30 |

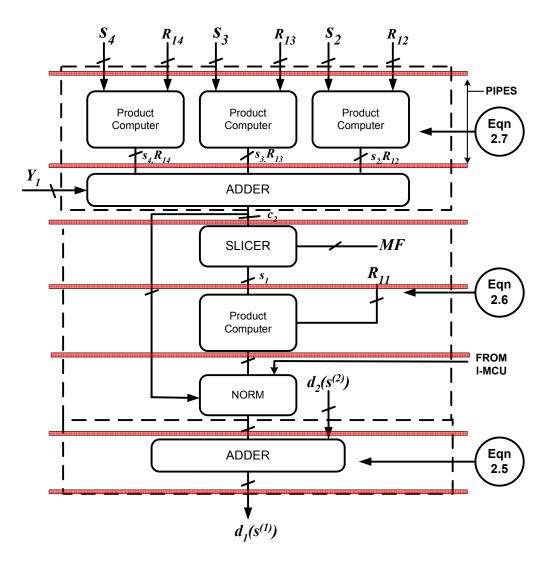

| Figure 3.5  | Metric Computation Unit of Level 1                                                                                 | 31 |

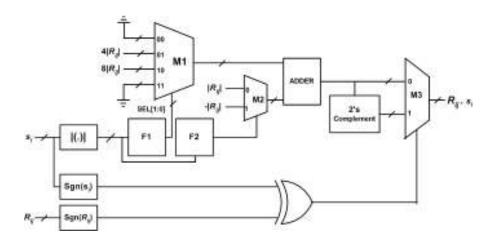

| Figure 3.6  | Product Computer Unit Using Shift and Add                                                                          | 32 |

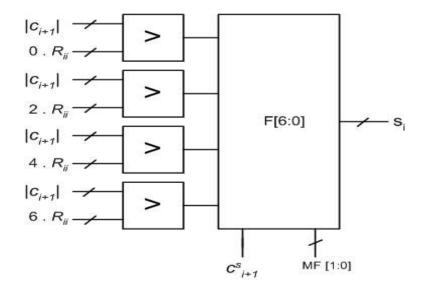

| Figure 3.7  | Slicer Logic which Performs Slicing Operation                                                                      | 32 |

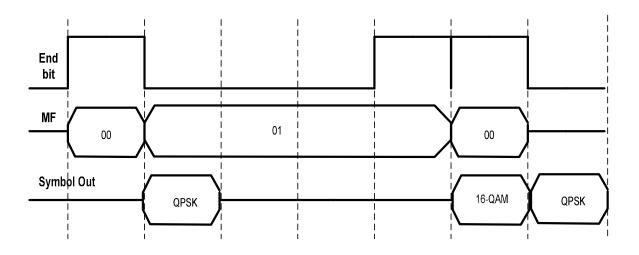

| Figure 3.8  | Output and Control Waveform                                                                                        | 33 |

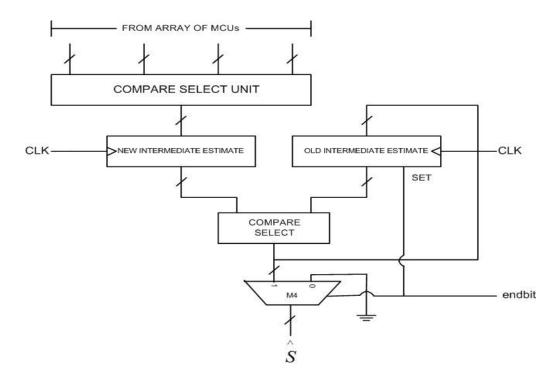

| Figure 3.9  | Find-Minimum Unit to Pick Minimum PD                                                                               | 33 |

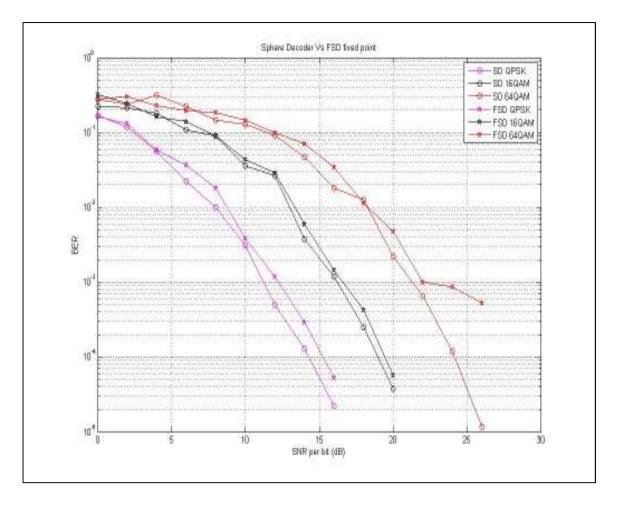

| Figure 3.10 | BER Performance Curve for SD (Floating Point/L2 Norm) vs<br>Implemented COSIC Algorithm with (Fixed-Point/L1 Norm) | 36 |

| Figure 4.1  | Tree Structure of FSD with COSIC Modification for 4x4 MIMO                                                         | 40 |

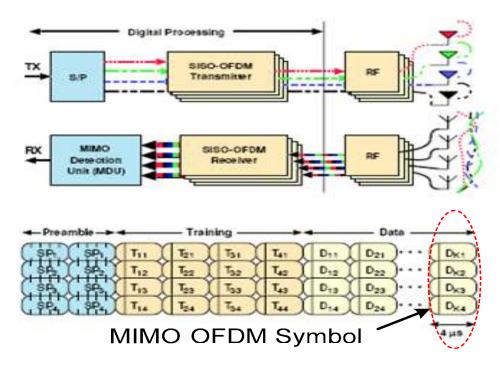

| Figure 4.2  | Packet Structure of IEEE 802.11n Systems                    | 40 |

|-------------|-------------------------------------------------------------|----|

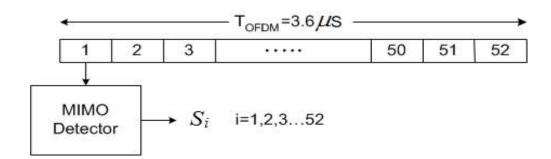

| Figure 4.3  | MIMO Detection Interface Timing as Required in IEEE 802.11n | 42 |

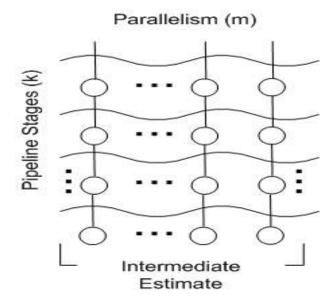

| Figure 4.4  | High Level Architecture of COSIC Based MIMO Detection       | 42 |

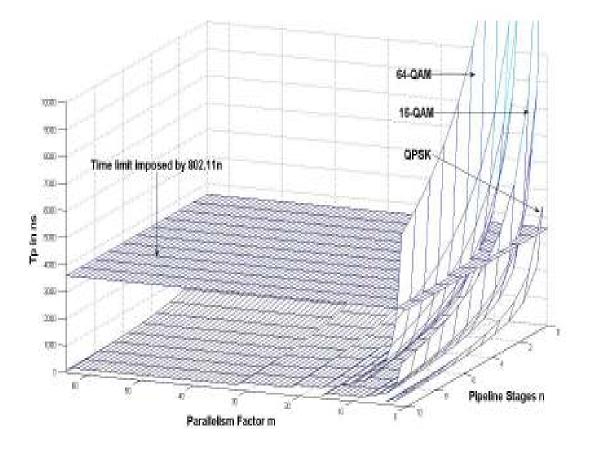

| Figure 4.5  | T <sub>p</sub> vs. (m, k) Constraint Due to 802.11n         | 44 |

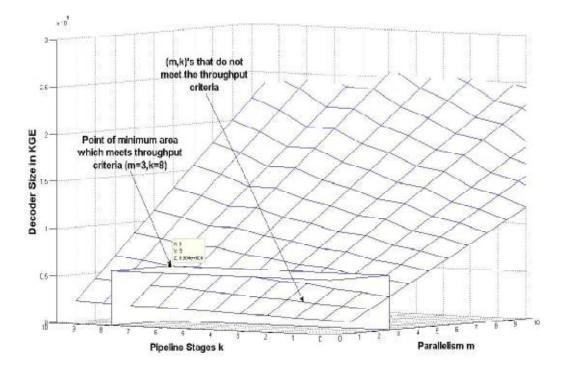

| Figure 4.6  | Area vs. T <sub>p</sub> for 64-QAM                          | 45 |

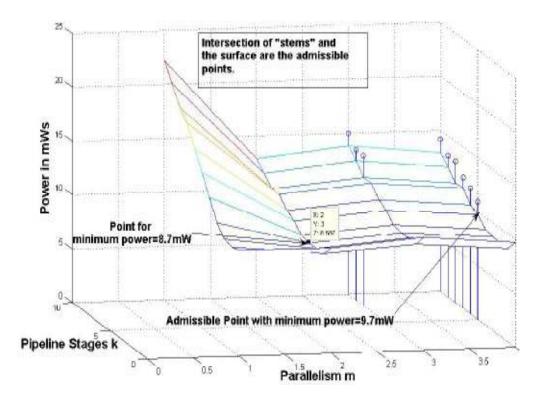

| Figure 4.7  | Aggregate Power vs. <i>m</i> , <i>k</i>                     | 46 |

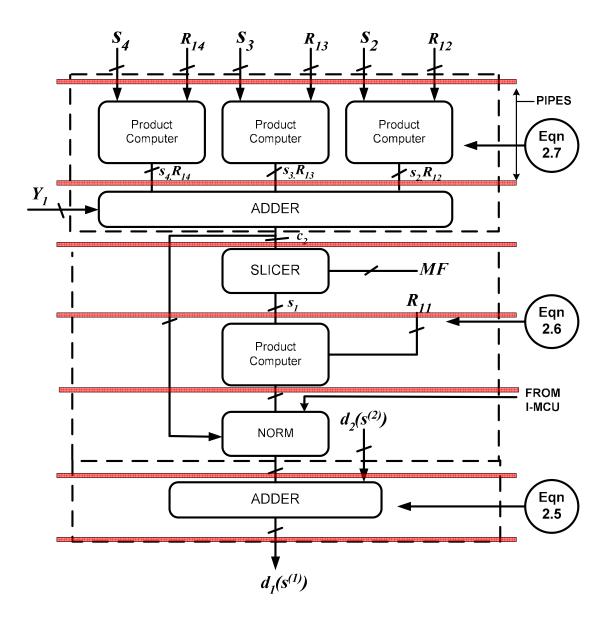

| Figure 4.8  | MCU Architecture of Level 1 in MIMO Detector                | 47 |

| Figure 5.1  | Decoding Iterations Verses Modulation Scheme                | 54 |

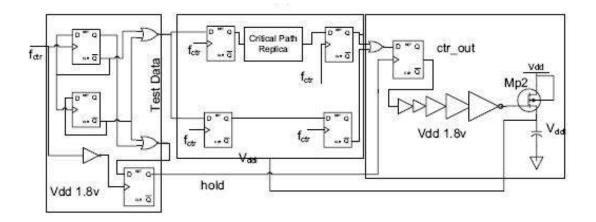

| Figure 5.2  | Frequency Controller Unit for DVFS                          | 57 |

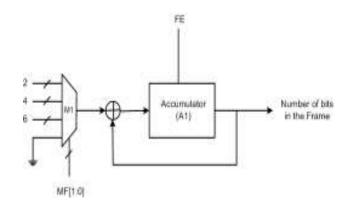

| Figure 5.3  | Bit Computer Unit                                           | 58 |

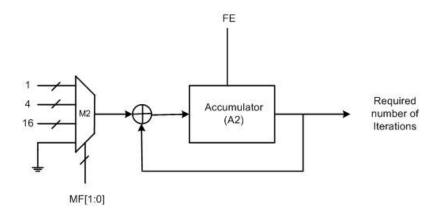

| Figure 5.4  | Iteration Computer Unit                                     | 59 |

| Figure 5.5  | Buck Converter Circuit for Voltage Regulation               | 61 |

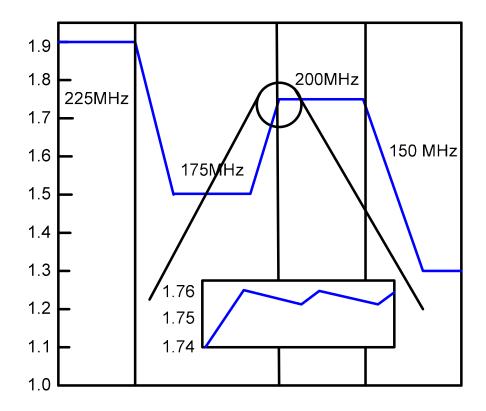

| Figure 5.6  | Voltage Output of the Voltage Controller                    | 62 |

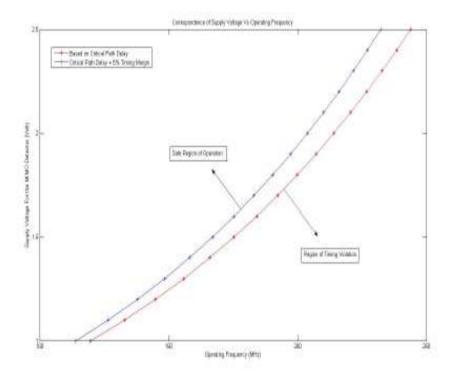

| Figure 5.7  | Voltage Supply Requirement with Different Frequency         | 63 |

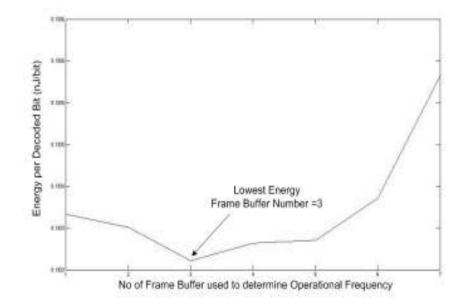

| Figure 5.8  | Number of Frame Buffer Verses Energy per Decoded Bit        | 64 |

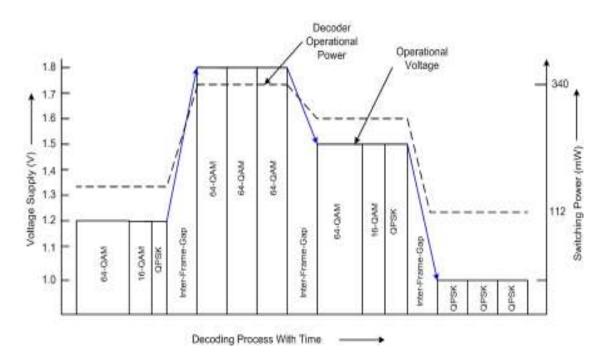

| Figure 5.9  | Frame-Wise Dynamic Voltage/Power Profiles                   | 66 |

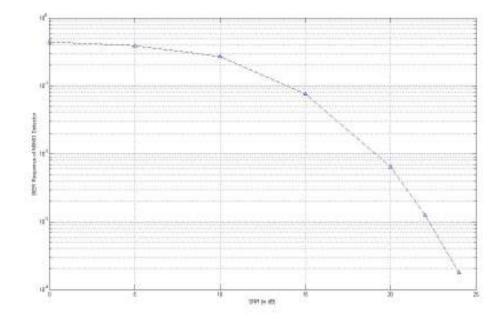

| Figure 5.10 | BER Response of the Presented DVFS Based MIMO Detector      | 67 |

### LIST OF TABLES

| Table 3.1 | Comparison of Reconfigurable Architectures            | 34 |

|-----------|-------------------------------------------------------|----|

| Table 3.2 | FPGA Implementation Results                           | 35 |

| Table 4.1 | Comparison of Performance with Existing Architectures | 49 |

| Table 4.3 | ASIC Implementation Details                           | 50 |

| Table 5.1 | ASIC Implementation Details and Comparison            | 68 |

#### **1. INTRODUCTION**

The need for ubiquitous communication has made wireless communication one of the most important segments for technological growth. The huge success of portable devices like cell phones, personal digital assistants (PDAs), smart phones, net books etc provide ample evidence to the importance of wireless communication in the consumer market. This has led to the need for evolving wireless standards in order to cater to the increasing demands of the consumer market. The wireless communication market has slowly transitioned from being predominantly used for voice communication to widespread surge in data usage, video downloads, and multimedia messaging which enhances the need of high bandwidth wireless links [1]. In order to cater to these high bandwidth applications, the wireless standards put in place a range of specifications which should be met in order to provide quality support to end users. Hence, the evolution of standards and systems is driven by the emergence of new applications which continue to require better quality of service (QoS) and higher data rates and by the need to support the growing number of users. This vast user base creates bandwidth limitations, affects service costs and also influences the QoS.

A number of factors affect the quality and capacity of wireless communications systems. The scarcity of available bandwidth for wireless communication combined with the increasing demand for higher data rates puts an ever increasing demand for high

This thesis follows the style of *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*.

speed communication systems. As increasing the spectrum available for wireless communication is not a viable solution, therefore utilizing the spectrum optimally with increased spectral efficiency is the key. This impairment is countered by improved communication systems which use advanced algorithms and efficient VLSI architectures to offer higher data rates and the required QoS.

#### 1.1 MIMO Systems: An Overview

Multiple-input multiple-output (MIMO) systems [2] use multiple antennas at both the transmitter and at the receiver to allow for spatial multiplexing to increase channel bandwidth. This technology is believed to enable the increase in channel bandwidth efficiency in future generation wireless systems to cater to the growing number of users. MIMO Technology enables the use of higher number of antennas which essentially allows for higher spectral efficiency compared to single-input singleoutput (SISO) systems with single antenna at transmitter and receiver. The major advantages of MIMO are due to the following gain factors [3]:

- 1. Array gain: Multiple antenna at the receiver side helps in picking up a larger percentage of transmitted power from the transmitter which fundamentally increases the range of the communication system and helps in suppressing interference from other sources.

- Diversity gain: Multiple receivers give us more information about the variations in the channel also called fading. This information allows us to better isolate signal component from noise thus increasing link-reliability and QoS.

3. Multiplexing gain: With multiple antennas at transmitter and receiver, multiplexed data streams can be transmitted together which allows for a linear increase in spectral efficiency and peak data rates in the same frequency band. The number of multiplexed data streams is limited by the number of antennas at the receiver and transmitter side.

A tradeoff exists between the above mentioned gains, as maximizing each of them requires different transmission schemes. The ability of MIMO technology although with the aforementioned tradeoffs, to provide these enormous gains has led to the use of MIMO in various wireless standards like UMTS, 3G, IEEE 802.11n WLAN and IEEE 802.16 WMAN among many others. Thus, MIMO technology theoretically offers significant increases in data throughput and link range without additional bandwidth or transmit power.

#### **1.2 Implementation Challenge of MIMO Detector**

Realizing the theoretical capacity boost of MIMO technology is only possible with the use of complex signal processing at the transmitter side & receiver side as compared to present day SISO systems. Spatially multiplexing the data streams in the transmit side requires more processing before the transmit stage in order to ease the decoding process. Also, a serial data stream needs to be pushed into a Serial Input Parallel Output (SIPO) buffer to be transmitted by multiple antennas. On the receiver side, these spatially multiplexed data streams needs to be separated by extremely complex signal processing techniques. Most of the MIMO detection techniques should cancel the interference of successive channels while keeping all the other advantages associated with MIMO systems. The complexity of transmitter and receiver increases rapidly at a far higher rate than the increase in spectral efficiency with the increase in number of antennas. Sometimes owing to the complex signal processing required at the receiver and transmitter, the gains of linear spectral efficiency is more than countered by a higher than linear increase in decoder complexity, even with the most basic processing algorithms. In order to fully exploit the advantages of multi-antenna systems, algorithms with even higher complexity is needed. Implementing these complex algorithms in an efficient VLSI architecture on silicon is an extremely crucial design challenge. However, for the successful implementation and widespread use of MIMO systems highly integrated and affordable implementations of the MIMO detector is of paramount importance.

#### **1.3 Current Generation MIMO Systems**

MIMO detector is the most complex unit of the MIMO Communication system. When spatial multiplexing is used at the transmit side, MIMO detectors task is to separate the spatially multiplexed data streams at the receiver side. Earlier most of the comparisons of MIMO detectors used to be on the basis of the complexity analysis of the signal processing algorithms. This complexity analysis does not relate to the silicon complexity of the decoder itself although they are a good metric for analyzing the complexity of the decoding process. These analysis show that MIMO systems from 2~6 antennas are practical from communication standpoint. Hence, case analysis with successively increasing number of antennas in communication system doesn't give us any significant information which would help in understanding feasibility of MIMO

implementation. Another method used to do analysis and algorithm optimization for complexity reduction was with the use of digital signal processor (DSP) which has custom functions for signal processing applications. However, the throughput achieved through DSP implementations along with implementations on other software programmable processing architectures is not sufficient to meet the requirements of next generation wireless standards owing to computational overheads associated with programmable logic. The analysis of algorithm efficiency done using programmable logic proved to be considerably different from dedicated communication circuits. For this reason, many algorithms which promised to be low power and computationally efficient in DSP architectures turned out to be ill suited for application specific integrated circuits (ASICs). Hence, a need for dedicated VLSI architectures for MIMO decoding was necessary for successful and efficient implementation. Recently, there has been quite some work relating to the actual VLSI implementations of MIMO algorithms and of complete MIMO systems. The few presented algorithms and designs provide initial reference points for the silicon complexity of MIMO detectors and illustrate suitable hardware architectures. Still till date, implementations of MIMO systems are band limited due to decoder performance rather than by wireless channel capacity. The authors, provide a comprehensive comparison of the true silicon complexity of different detection schemes and the associated performance tradeoffs and VLSI architectures based on actual VLSI implementations. VLSI implementations of various signal processing algorithms for MIMO detection in [4], further deals with the exploration of the design space that is available on the algorithmic and architectural level for the ASIC

implementation of low-complexity hard-decision MIMO detection for spatial multiplexing. A hardware implementation perspective was presented and results for various algorithms were compared. Here is a brief summary of the VLSI implementations of the following algorithms:

- 1. Linear and Successive Interference Cancellation (SIC) Detection: With proper implementation strategies SIC algorithms are less costly to implement in terms of silicon area than completely linear detectors. In [4] and [5], a linear detection architecture is presented which achieves nearly hundred percent hardware utilization, low decoding latency and higher throughput. Optimizations for matrix inversion and matrix decomposition are considered to enhance the performance of these architectures. In particular different architectural and circuit-level tradeoffs are discussed for the implementation of QR decomposition.

- 2. Exhaustive Search Maximum Likelihood: It is shown how this algorithm which achieves optimum bit error rate performance, but with a complexity that grows exponentially in rate, can still be implemented economically for higher throughput [6]. The reasons for this are a number of lossless (in terms of bit error rate) algebraic transformations and an optimized VLSI architecture.

- 3. Iterative tree-search algorithms: Tree-search algorithms mostly refer to Sphere Decoding and K-Best decoding in terms of MIMO detection although other less known search strategies are prevalent as well. VLSI implementation of the K-Best algorithm is described for a 4 × 4 system with 16-QAM modulation which achieves a high throughput compared to other implementations [7]. Additionally,

in [8] a one-node-per-cycle VLSI implementation of Sphere Decoding is presented. The implementation is shown to operate directly on complex-valued constellation points without the use of costly transcendental functions in [9]. A new modified-norm implementation is introduced in [10] easing computational complexity in norm computation.

In the past, most of these implementations dealt on the issue of simplifying signal processing algorithms for reducing computational complexity, achieving higher throughput and reducing latency of MIMO systems. Although these are important metric for commercial use, but another important factor is the usability of the architecture over different modulation schemes, across different antenna configurations, support for soft output detection which enables its use with FEC decoders for better BER performance.

#### **1.4 Contributions**

In this thesis, we explore the design space that is available on the architectural level for the ASIC implementation of low-complexity hard decision MIMO detection for spatial multiplexing. Algorithm was chosen on the basis of re-configurability to various modulation schemes, hardware reuse, enhanced throughput and lower silicon complexity. VLSI architecture has been developed for an iterative tree search decoder based on a special case of fixed sphere decoding algorithm for MIMO detection called COSIC algorithm. Various architectural optimization techniques and transformation was explored to improve the performance of the implementation. Performance improvement in terms of silicon complexity, operating power and throughput were considered. The VLSI implementation results are insightful from an implementation standpoint as they

provide the right metric in deciding the impact of the underlying algorithm and the associated architectural transformations used for design optimization. Here is a summary of all the contributions in this thesis:

- 1. Dynamic Reconfigurability in MIMO Detection: Most of the MIMO detector implementations don't deal with the issue of adaptive modulation schemes supported by numerous wireless applications and standards. The proposed detector architecture [11] uses a modified form of FSD algorithm which ensures constant throughput for a particular modulation scheme. Finite state machine (FSM) based control logic has been developed around the FSD implementation which uses modulation data to reconfigure the decoder to various modulation schemes like QPSK, 16-QAM and 64-QAM modulation schemes for 4x4 MIMO systems. The detector architecture can be further fine-grained pipelined to achieve higher throughput [12] without any scheduling complexity. The proposed architecture is highly suitable for the next generation wireless standards because of its flexibility, reduced computational complexity and higher throughput.

- 2. Design Space Exploration of Runtime Reconfigurable MIMO Detector for IEEE 802.11n: The focus here is on wireless systems based on 802.11n standard. In particular; extensive architectural space exploration was done to address the issues of power consumption, area, and re-configurability between different modes of operation while meeting the standards throughput requirement. Ultimately, two optimized designs [13] that target low area and low

power respectively was proposed. This detector will also support on the fly reconfigurability for QPSK, 16-QAM and 64-QAM modulation schemes. This architecture delivers close to optimal Maximum Likelihood (ML) BER performance with no reconfiguration latency, leading to uninterrupted detection of MIMO symbols. This will clearly present an example of the tradeoff limits of the design and the extent of tune-ability of the architecture based on various target applications.

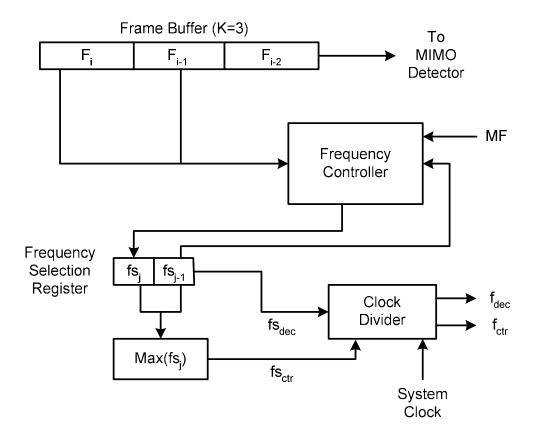

3. Low Power Reconfigurable MIMO Detector for Real-Time Mobile Applications: In this design we target two major issues: lower energy consumption based on a DVFS to exploit the re-configurability of the architecture to different modulation schemes with lower complexity and fixed throughput of detector across different modulation schemes which is ideal for real-time multi-media applications. The decoder uses optimal voltage and frequency while processing buffered data frames resulting in significant energy gains suitable for portable devices. This technique of varying voltage and frequency is called dynamic voltage and frequency scaling (DVFS) [14]. The DVFS frequency controller calculates the number of bits and decoding iterations required to process frames, and based on this information sets the operating frequency of the detector. A voltage regulator [15] is used to generate the appropriate voltage for that particular frequency. The choice is made in such a way so as to decode each frame, within a fixed time period irrespective of modulation scheme. Thereby, making available the output of each frame

synchronized to the fixed rate at which the data is consumed in real-time application interface like 802.11n. This detector delivers quasi-optimal BER performance with no reconfiguration latency which guarantees the necessary Quality of Service (QoS) with uninterrupted processing of MIMO symbols.

#### **1.5 Thesis Outline**

In section 2 of this thesis, the MIMO system model is described. The section also lists the performance criteria which constitute the basis for the development and evaluation of algorithms and VLSI architectures. It also introduces the available algorithm choices for MIMO detection, together with their corresponding complexity scaling behavior. We also discuss the reasoning behind the choice of algorithm for our implementations. In section 3, the implementation of the reconfigurable sphere decoder is discussed. Details are presented as to how the COSIC algorithm is modified for reconfigurability to various modulation schemes. In section 4, we see an architectural exploration of the hard detector aimed at IEEE 802.11n. We explore aspects such as parallel processing and pipelining such that an optimal detector based on throughput, area and power can be designed. Here we also present two designs, one optimized for power and other optimized for area. Section 5 deals with a scheduling algorithm presented for the reconfigurable detector such that it can use voltage and frequency optimally such that the working power envelope can be further squeezed. Section 6 wraps up the thesis with discussions on possible future work in MIMO, summary and conclusions.

#### 2. BACKGROUND OF MIMO DETECTION

This section will provide a detailed background of MIMO system model, processing stages, and the various algorithms used for MIMO detection. The choice of algorithm is very important for any VLSI implementation. This section will provide a brief summary of the advantages and disadvantages of each algorithm and its associated implementation.

#### 2.1 System Model and Processing Stages

Wideband MIMO communication systems can be reduced to a set of narrowband MIMO systems with proper modulation techniques such as OFDM or with proper equalization. As narrowband system model are much simpler, therefore it is straightforward to derive corresponding receivers for wideband MIMO communication systems based on the narrowband model. Also, the results and analysis derived from narrowband system model can be easily extendible to a wide range of communication scenarios and to provide a common basis for the comparison of different algorithms. Let us say the number of transmit antennas is given by  $M_T$  and the number of receive antennas is given by  $M_R$ . The example MIMO system shown in Figure 2.1 has  $M_T=2$  and M<sub>R</sub>=2. This system model can be extended for higher number of antennas. As we are only concerned about spatial multiplexing to enhance channel efficiency, we also assume  $M_R \ge M_T$ . Here binary source generates a sequence of information bits that is required to be transmitted over a wireless link. These bits are encoded by a FEC encoder (such as LDPC, Turbo codes, Convolution Codes). The encoded bit sequence (x) is then modulated onto symbols (s1, s2 etc.) and sent to the transmitter, symbols from each

transmitter undergoes independent gains ( $h_{11}$ ,  $h_{12}$  etc.) before reaching the receiver. Hence,  $Rx_1$  receives  $s_1h_{11} + s_2h_{21}$ , and  $Rx_2$  receives  $s_1h_{12} + s_2h_{22}$ . Signals at  $Rx_1$  and  $Rx_2$  are further corrupted by noise ( $n_1$ ,  $n_2$ ). Obviously the big problem with this is that the receiver sees a combination of what was transmitted from both transmit antennas plus noise. The MIMO detector attempts to compute the estimate  $\hat{s}$  of the most likely transmitted symbol sequence [ $s_1$ ,  $s_2$ ], and de-modulates  $\hat{s}$  to give out the estimate of the encoded bit sequence (it is assumed that the gains  $h_{11}$ ;  $h_{12}$  etc are known at the receiver through the channel estimation stage which happens during preprocessing). These bits are then fed to the FEC decoder to get back the bits generated by the binary source.

**Transmitter:** With spatial multiplexing, the modulation in the transmitter corresponds to choosing the entries of the transmitted signal vector **s** independently from a set of constellation points  $\Omega$  as shown in Figure 2.2, according to the data to be transmitted, so that  $\mathbf{s} \in \Omega^{M_T}$ . The set  $\Omega$  is defined by the modulation scheme for which a rectangular QAM modulation with  $Q = |\Omega|$  bits per complex-valued scalar symbol and with Gray encoding is usually assumed. The rate of the corresponding MIMO system with  $M_T$ transmit antennas in spatial multiplexing mode is then given by  $R = M_T \log_2 Q$  bits per channel use (bpcu). In all the sections discussed in this thesis, the corresponding constellation points are defined on an odd integer grid according to  $\Omega = \{(1 + 2a) + j(1 + 2b)\}$  with  $a, b \in Z$  as shown in Figure 2.2. For a fair comparison which is independent of the number of transmit antennas and of the modulation scheme, the signal vector **s** is normalized before transmission in such a way that the average transmitted power is one (i.e.,  $E \{ ||\mathbf{s}||^2 \} = 1$ ). **MIMO Channel:** The equivalent baseband model of the MIMO wireless channel that yields the  $M_R$ -dimensional received vector **y** is given by the following input-output relation

$$\mathbf{y} = \mathbf{H}\mathbf{s} + \mathbf{n}.\tag{2.1}$$

The  $M_R$ -dimensional vector **n** models the thermal noise as independent identically distributed (i.i.d.) circular symmetric (proper) complex Gaussian with zero mean and variance  $\sigma^2$  per complex dimension ( $E\{nn^H\} = \sigma^2 I$ ). The  $M_R \times M_T$  dimensional matrix H represents the complex-valued channel gains between each transmit and each receive antenna as discussed previously. For the simulations in the following sections, an i.i.d. Rayleigh fading channel model without correlation is assumed. Hence, the entries of H are chosen independently as zero mean proper complex Gaussian random variables with variance one per complex dimension. The SNR is defined in accordance with [3] as the ratio between the total transmitted power, which has been normalized to one, and the variance of the thermal noise according to

$$SNR = 1/\sigma^2 \tag{2.2}$$

**Receiver:** The  $M_R$  antennas at the receiver pick up the received signal vector y. Taking into account that the variance of the channel gains have unit variance, the *average* received signal-to-noise ratio (over channel realizations) per received antenna is immediately given by the SNR. The task of the MIMO detector at the receiver is to obtain the best possible estimate of the transmitted signal vector **s** based on the received vector **y**. Coherent modulation which is assumed in this thesis also requires that the receiver is provided with an estimate  $\hat{H}$  of the channel H. Such an estimate is usually

obtained during a separate training phase during preprocessing. Hence, broadly speaking MIMO processing can be split into two stages channel-rate and symbol-rate processing as illustrated in Figure 2.3. *Channel-rate processing* is often also referred to as *preprocessing*. The term comprises all operations that need to be carried out only when the channel estimate changes which happens when the system changes from one environment to another. *Symbol-rate processing* comprises all those operations that need to be carried out for each received symbol in order to estimate the transmitted vector symbol. We shall refer to this part of the receiver as the *detection unit*. Under low mobility scenarios when the channel doesn't change much, it is safe to assume that the channel remains same over a large number of symbols and hence, plays a less critical role in determining throughput of a general MIMO communication system. However, in high-mobility scenarios, under stringent latency constraints, or in wide-band MIMO

Figure 2.1: Example of a 2x2 MIMO Communication System with Channel Matrix

Figure 2.2: Constellation Point for QPSK, 16-QAM, 64-QAM Modulation Schemes

systems with frequency selective fading it is still justified, to consider the channel-rate processing complexity separate from the symbol-rate processing, as the frequency of the operation and the performance requirements are dictated by a completely different set of system parameters.

Figure 2.3: Processing Stages in General MIMO Detector

Figure 2.4: BER Performance of MIMO Detection Algorithms [4]

#### 2.2 Maximum-Likelihood Detection and Sphere Decoding

As discussed earlier, there are many MIMO detection algorithms with different tradeoffs intrinsically embedded in each of them. A comparative study of the BER performance of

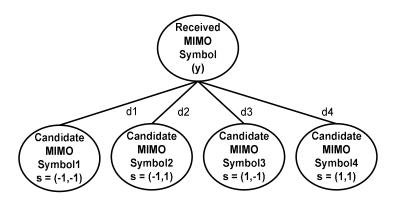

ML Solution = Min (d1, d2, d3, d4) Figure 2.5: Example of ML Solution for 2x2 BPSK Systems

different algorithms is given in Figure 2.4. It shows a significantly higher BER performance of the Maximum-Likelihood (ML) detection algorithm than linear detection (ZF, MMSE) and Successive Interference Cancellation (SIC) algorithms. Along with its higher BER performance, ML detection algorithms as we will see in this section can be simplified for effective VLSI implementation.

The baseband system model for a MIMO system with  $M_T$  transmit and  $M_R$  receive antennas can be expressed as in (2.1) where **s** is  $M_T \ge 1$  transmitted vector or vector symbol, **n** is  $M_R \ge 1$  zero mean complex Gaussian noise vector, and H is  $M_T \ge M_R$  dimensional complex matrix. The (i, j)<sup>th</sup> element,  $h_{ij}$ , of the matrix H denotes the

complex channel gain from the j<sup>th</sup> transmit antenna to the i<sup>th</sup> receive antenna. In all our discussions, we assume  $M_T = M_R = 4$  unless specified otherwise. The objective of ML detection is to search for a MIMO symbol over the entire set of possible MIMO symbols and find a set with minimum distance which in hard detection MIMO is taken as the most likely solution candidate. Therefore the objective of ML based MIMO detection to compute an estimate  $\hat{s}$  of s such that:

$$\widehat{s} = \arg \min_{s \in \Omega^{M_{T}}} ||y - Hs||^{2}$$

=arg min<sub>s \in \Omega^{M\_{T}}</sub> d(s) with d(s) = ||y - Hs||^{2} (2.3)

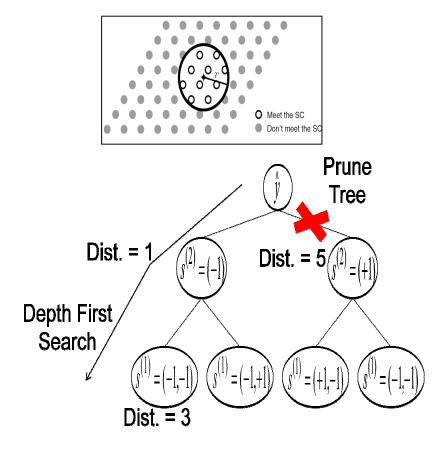

where  $\Omega$  is set of complex entries from the QAM constellation as shown in Figure 2.2 and  $\eta$  is the cardinality of the set. As previously discussed straightforward approach to solving (2.3) is an exhaustive search over all possible candidate vector symbols as shown in Figure 2.5. However, since the number of possible solutions grows exponentially with M<sub>T</sub>, the implementation of an exhaustive search becomes impractical as M<sub>T</sub> increases. For example, in case of a 4x4 MIMO system with 16-QAM modulation an exhaustive search would require the evaluation of 65536 candidate vector symbols. As can be seen in [4], ML detection can be mapped to an Iterative Tree Search Problem which eases the search process. In each level of the tree, we compute a Partial Distance (PD) of each symbol from the set of QAM symbols in which we are searching. In this way, for 4x4 MIMO system we will have a tree of depth equal to four as we will have to detect four symbols at the receiver. The breadth of this tree depends on the value  $\eta$  for a  $\eta$ -ary modulation scheme. For modulation schemes which have more spectral efficiency like 16-QAM and 64-QAM we have to search for the ML solution in a tree of depth 4 and breadth 16, 64 respectively which is highly inefficient for hardware implementation. One way to circumvent the exhaustive search is to evaluate only a small subset of all the possible vectors. The objective of sphere decoding is to prune this tree with a radius update technique (as shown in Figure 2.6) such that the BER performance is not degraded but less number of nodes are processed. For effectively searching through this tree we need QR based preprocessing. This technique transforms the channel matrix (H) into a unitary matrix (Q) and upper triangular matrix (R):  $\mathbf{H} = \mathbf{QR}$ . Hence, the cost function given by (2.3) can be rewritten as,

$$d(s) = ||y - Hs||^{2} = ||\hat{y} - Rs||^{2}, \text{ and } \hat{y} = Q^{H}y$$

(2.4)

where, R is an upper triangular matrix, and  $Q^{H}$  is the Hermitian of a unitary matrix Q. Vector  $\hat{y}$  as defined by (2.4) is the unconstrained zero forcing solution. The fact that R is upper-triangular ensures that each term in the summation depends only on the current level decision, as well as the history of the path to reach that level in the tree. Note that distance in (2.4) can now be rewritten to form summation across each transmit antenna.

$$\mathbf{d}_{i}(\mathbf{s}^{(i)}) = \mathbf{d}_{i+1}(\mathbf{s}^{(i+1)}) + |\mathbf{e}_{i}(\mathbf{s}^{(i)})|^{2}$$

(2.5)

$$|\mathbf{e}_{i}(\mathbf{s}^{(i)})|^{2} = |\mathbf{c}_{i+1}(\mathbf{s}^{(i+1)}) - \mathbf{R}_{ii} \cdot \mathbf{s}_{i}|^{2}$$

(2.6)

$$\mathbf{c}_{i+1}(\mathbf{s}^{(i+1)}) = \hat{\mathbf{y}}_i - \sum_{j=i+1}^{M_T} \mathbf{R}_{ij} \cdot \mathbf{s}_j$$

(2.7)

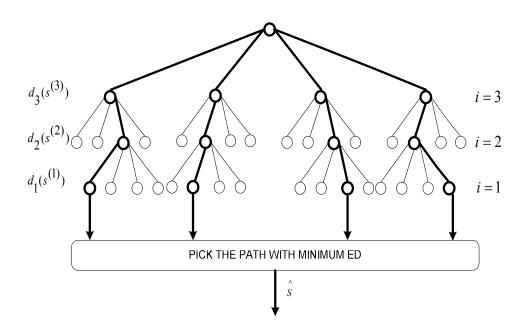

The quantity  $d_i(s^{(i)})$  is called the cumulative metric. The quantity  $|e_i(s^{(i)})|^2$  is called the incremental metric. The vector in (2.4)-(2.6) denotes a partial vector symbol candidate. This term  $d_i(s^{(i)})$  for i > 1 is called PD which was discussed earlier and Distance (D) for i=1. Because the PD's depend only on  $s^{(i+1)}$ , they can be associated with corresponding nodes in  $\eta$ -ary tree with  $M_T$  levels. For a 4x4 system, the equation for computation of each PD can be seen in Figure 2.7. As we can see, for a particular level of the tree the

Figure 2.6: Example of Sphere Criterion and Tree Pruning

$$d_{4}\left(\mathbf{s}^{(4)}\right) = \|\hat{y}_{4} - R_{44}.s_{4}\|^{2}$$

$$d_{3}\left(\mathbf{s}^{(3)}\right) = d_{4}\left(\mathbf{s}^{(4)}\right) + \|\hat{y}_{3} - R_{34}.s_{4} - R_{33}.s_{3}\|^{2}$$

$$d_{2}\left(\mathbf{s}^{(2)}\right) = d_{3}\left(\mathbf{s}^{(3)}\right) + \|\hat{y}_{2} - R_{24}.s_{4} - R_{23}.s_{3} - R_{22}.s_{2}\|^{2}$$

$$d_{1}\left(\mathbf{s}^{(1)}\right) = d_{2}\left(\mathbf{s}^{(2)}\right) + \|\hat{y}_{1} - R_{12}.s_{2} - R_{13}.s_{3} - R_{14}.s_{4} - R_{11}.s_{1}\|^{2}$$

Figure 2.7: Computation of PD in Each Level of the SD Tree

computation of its PD depends on its own level and with the previously detected levels only. Also, noticeable is the fact that total distance of each leaf node (candidate MIMO symbol) is an additive sum of PDs at each level of the tree. Hence, PDs can be considered as an incremental distance at each level of the tree. Alternatively, the computation of the terms  $d_i(s^{(i)})$  can be interpreted as a traversal of the tree from the root node to the leaf corresponding to **s**. Note that i = 1 correspond to leaf nodes. The estimate can now be obtained by searching the leaf with smallest D and returning the path from the top level ( $i = M_T$ ) to that leaf node which will give  $\hat{s}$ . The PD's and D's in (2.4) are equivalently referred to as the node's metric in the sequel.

#### 2.3 Analysis Criteria for VLSI Implementations

Once the system level aspects and requirements are understood, one can start with the development of low-complexity MIMO receivers. The available design space comprises of a variety of algorithms choices each of which provides opportunities for further optimizations on both algorithm and VLSI architecture level. At the same time, these choices and optimizations often entail tradeoffs between silicon area, throughput and BER performance which need to be balanced by the designer. Hence, joint consideration of both algorithm and implementation aspects are crucial for achieving efficient, low-complexity implementations.

**BER Performance:** The quality of a MIMO detection algorithm and of its associated implementation can be assessed by its BER performance which is obtained from fixed-point computer simulations as corresponding analytical expressions are often not available or do not include non-idealities caused by implementation tradeoffs.

*Diversity Gain:* Diversity gain describes the behavior of an algorithm in the limit of high SNR, and the diversity order corresponds directly to the slope of the BER curve.

*Error Floor:* In practical systems, the additive thermal noise term  $\mathbf{n}$  in the channel model in equation (2.1) does not accurately model the overall noise in an end-to-end system. Instead, other noise sources whose power does not degrade with increasing SNR also contribute to the effective overall noise power. At high SNR, these constant terms become the dominant factors and the BER curve shows an error floor.

*Complexity Order of Algorithm:* The complexity order of the MIMO detection algorithm provides description of the scaling behavior of its complexity in one or more design parameters in the limit of infinity. A complexity order of O(n2) for example specifies that the fastest growing term in the expression for the corresponding complexity is quadratic in *n*.

*VLSI Implementation Complexity:* The *computational complexity* describes the complexity of an algorithm in terms of number of costly operations. However, in practice, the notion of what kind of operation qualifies as costly differs widely depending on the underlying implementation technology. VLSI implementations allow for replacing sequences of basic operations by much more efficient single-cycle custom composite operations and additional hardware resources can be allocated for parallel execution of more frequent or more time consuming operations. Thus, it is important to identify the complexity defining operations with a basic VLSI architecture in mind and to count the associated efforts individually. Such careful counting of operations (with VLSI architecture and the associated memory requirement) provides reasonable means

for the comparison of similar algorithms which call for similar underlying architectures and for assessing the impact of corresponding optimizations.

*Silicon Complexity:* Unfortunately, even smart ways of counting the number of operations tend to fail, when comparing fundamentally different algorithms or when attempting to accurately predict the capabilities of a final VLSI implementation. Moreover, counting of operations does not immediately provide information about the design tradeoffs between throughput and silicon area, as data dependencies, memory access bottlenecks and other potential impairments are not captured. The true silicon (or implementation) complexity of an algorithm is given by the area and the throughput or delay that is achieved with a particular VLSI architecture.

#### 2.4 Discussion of Implementation/Simulation Methodology

As mentioned previously, the BER results are obtained from computer simulations based on the MIMO channel shown in Figure 2.1. This model is valid in rich scattering environments with sufficient spacing between the antennas on the order of one wavelength. The simulation results presented in this thesis assume perfect channel knowledge at the receiver, effectively setting  $\hat{H}$ =H, so that channel estimation and detection can be separated. All the BER results in this thesis are generated for a 4×4 MIMO system with the simulation setup and scaling values of noise for specific SNRs computed as described in [17]. Different architectures are explored with support for various modulation schemes and ideas presented can be easily extrapolated for different antenna configurations. The main motivation behind choosing  $M_T$  = 4 is the fact that four antennas already provide a considerable capacity improvement that is likely to cover the

needs for next generation wireless systems. Moreover, from a practical perspective, mounting more than four antennas with an appropriate distance with approximately one wavelength apart on a portable device appears difficult. In terms of the modulation scheme, it is also important to note that practical systems will employ adaptive modulation, predominantly using QPSK to 16-QAM for outdoor scenarios and QPSK to 64-QAM for indoor scenarios due to which algorithmic/architectural re-configurability to different modulation schemes are an important design criterion. Fixed point simulations were considered for finding design tradeoff with respect to BER and complexity. All the simulations for the algorithmic level exploration were done in bit accurate and cycle accurate code in MATLAB which is a good approximation of the implementation scenario. Once the fixed point accuracy and tolerance was verified, RTL was written in Verilog HDL to describe the functionality of the MIMO detector. RTL was verified using the same test points that were used for verification of the simulation model in MATLAB. RTL synthesis was done in Synopsys Design Compiler and postsynthesis simulations using cell libraries from Nangate 45nm PDK was done in Verilog XL. Cadence Silicon Encounter was used for the automated Place and Route of the design. All the results presented in this thesis are based on back annotated delays from cell libraries and delays from wire models. For the FPGA implementation, Xilinx integrated development environment was used for synthesis, timing closure and place and route.

#### **3. FPGA IMPLEMENTATION OF RECONFIGURABLE MIMO DETECTOR**

In this section, a reconfigurable architecture for MIMO detection and its FPGA implementation is presented based on a variant of the Sphere Decoding Algorithm discussed in Section 2.2. The design objective is to be able to reconfigure on the fly which is one of the prime requirements for future wireless standard. The previously discussed algorithms/architectures in Section 1.3 are relatively expensive from a reconfigurability viewpoint. From the few re-configurable MIMO detectors that have been reported till date, one implementation [18] uses VBLAST based detection scheme that incurs significant BER degradation and an expensive Processor based Control Unit. On the contrary, we use a variant of the Fixed-Throughput Sphere Decoding Algorithm (FSD) [19] with modifications which is provided in [20] for our implementation. Many of the challenges discussed in previous sections have been addressed. Also, it can be implemented in a highly parallel and pipelined manner, has fixed throughput for a given modulation scheme, delivers quasi-ML BER performance and achieves on the fly reconfiguration. This detector supports on the fly re-configurability for QPSK, 16-QAM and 64-QAM modulation schemes with quasi-ML performance. The control logic has minimal complexity and is highly integrated with the data flow.

#### **3.1 Fixed Sphere Decoding and COSIC**

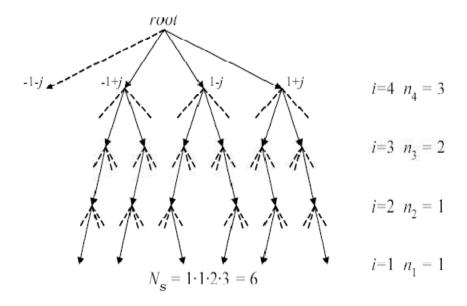

From an implementation point of view, the sphere decoding has two main drawbacks. Firstly, the detector complexity depends on the noise level and the channel conditions and, secondly, the sequential nature of the search limits the performance and the level of parallelism of a hardware implementation of the algorithm. A new fixedcomplexity sphere decoder (FSD) [19] is proposed to overcome those two problems by searching, independently of the noise level, over only a fixed number of lattice points H.s (2.1), generated by a subset of symbols around the received symbol. The FSD assigns a fixed number of candidates, n<sub>i</sub>, to be searched per level independent of the initial radius. This can be explained as follows: whereas in the first level,  $i = M_T$ , more candidates need to be considered due to interference from the other levels, the decisionfeedback equalization (DFE) performed on y<sub>i</sub> and the increase in value of diagonal in later level reduces the number of candidates that need to be considered in the last levels. The total number of candidates whose Euclidean distance is calculated is, therefore,  $N_s$ = $\sum_{i=1}^{M_T} n_i$ , where simulations show that quasi-ML performance is achieved with N<sub>S</sub> <<  $\eta^{M_{T}}$ . The n<sub>i</sub> candidates on each level i are selected according to increasing distance to y<sub>i</sub>, following the SE enumeration [21]. Figure 3.1 shows a hypothetical subset S in a 4x4system with 4-QAM modulation where the number of points per level  $n_s = (n_1; n_2; n_3;$  $n_4$ )<sup>T</sup> = (1; 1; 2; 3)<sup>T</sup>. In each level i, the  $n_i$  closest points to  $y_i$  are considered as components of the subset S. A trade-off exists between the complexity and the performance of the FSD. If more candidates are searched, the performance will be closer to that of the original SD but the required computational power will increase. That makes the FSD suitable for reconfigurable architectures where the number of candidates can be made adaptive depending on the MIMO channel conditions. The main problem with FSD ordering is its iterative preprocessing stages to find out the number of branches that should be selected at each level which has large computational complexity.

Figure 3.1: Example of (3, 2, 1, 1) FSD Ordering in [19]

Figure 3.2: Tree Structure of COSIC Algorithm

This makes implementation of FSD tougher. In [20], a simple technique based on FSD is presented which performs near to Optimal in BER performance but has reduced complexity. Figure 3.2 shows the COSIC ordering technique in 4x4 system with QPSK modulation where the number of points per level  $n_s = (n_1; n_2; n_3; n_4)^T = (1; 1; 1; 4)^T$ . In COSIC, at the first stage  $\eta$  candidate solutions of the tree are considered and then in successive levels one the best solution candidate is considered as shown in Figure 3.2. This algorithm degrades slightly in BER performance as compared to the FSD algorithm but compensates in terms of reduced complexity which helps in VLSI implementation.

Figure 3.3: Data Path Parallelism and Control Structures

**Simplified Norm Computation:** The Euclidean norm or  $1^2$  norm which needs to be computed at each level in (2.6) involves a squaring operation which requires multipliers. Multipliers are in general expensive in terms of hardware cost. In [9] it has been shown that the use of simplified norms leads to significant reduction in hardware cost with some BER degradation. In our design we have replaced the  $1^2$  norm in (2.6) by  $1^1$  norm. The  $1^1$  norm approximation for is given by:

$$\mathbf{d}_{i}(\mathbf{s}^{(i)}) = \mathbf{d}_{i+1}(\mathbf{s}^{(i+1)}) + |\operatorname{Re}\{\mathbf{e}_{i}(\mathbf{s}^{(i)})\}| + |\operatorname{Im}\{\mathbf{e}_{i}(\mathbf{s}^{(i)})\}|$$

(3.1)

where Re{} and Im{} denote real and imaginary parts respectively. The use of  $l^1$  norm causes the BER to degrade only by about 0.4dB-0.5dB [9].

#### **3.2 Reconfigurable Sphere Decoder Architecture**

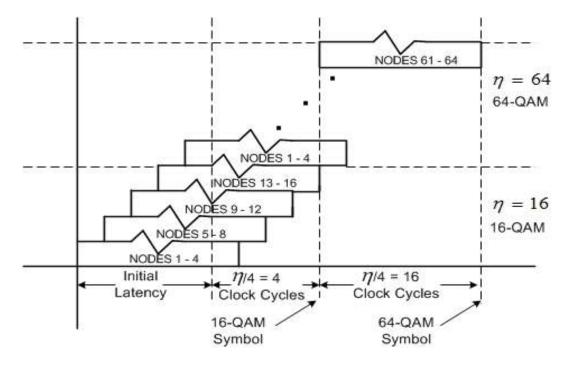

Figure 3.3 shows the high level architecture of our decoder. The choice of 4-way parallelism was made because the smallest constellation supported on our decoder is QPSK (which has four symbols,  $\eta$ =4). If this architecture is pipelined with *m* stages then it has an initial latency of *m*+  $\eta$ /4 clock cycles. Note that the FSD tree has  $\eta$  paths for a  $\eta$ -ary modulation scheme. Hence, the proposed architecture takes  $\eta$ /4 clock cycle to detect a  $\eta$ -ary modulated MIMO symbol. At each level of the FSD tree (Figure 3.2) we need to compute the d<sub>i</sub>(s<sup>(i)</sup>) metrics using (2.5)-(2.7). Each of these equations are computed by a Metric Computation Unit (MCU). The best child node at each level is picked using a slicing operation shown in Figure 3.4. Figure 3.5 shows the structure of the MCU at level-1 which is the lowest level in the tree. The upper box in the Figure 3.5 evaluates (2.7). Note that there is no need to implement the product terms in (2.7) using a multiplier. This product can be achieved by shift and add operation as shown in Figure

3.6, because the QAM constellation points only take on a finite number of integer values (e.g. in 16-QAM scheme the real and imaginary part of s<sub>j</sub>  $\varepsilon$  {-3, -1, 1, 3}). The block named slicer as shown in Figure 3.7 picks the nearest QAM symbol to c<sub>i+1</sub> as shown in Figure 3.4. The slicing operation involves independently comparing real and imaginary parts of c<sub>i+1</sub> with appropriate decision thresholds. The decision thresholds are given by (- $(\sqrt{\eta} - 2) + 2j)$  R<sub>ii</sub>, where j is an integer such that  $0 \le j \le (\sqrt{\eta} - 2)$ ). Our decoder configures the slicer based on Modulation Format bits (MF), which indicates the modulation scheme of the current MIMO symbol. The control unit of our design is a simple FSM which takes in MF [1:0] (00 => QPSK, 01 => 16-QAM, and 10 => 64-QAM) and generates a signal '*Endbit*' every ( $\eta$ /4) clock cycle. This signal indicates the completion of decoding one MIMO symbol.

Figure 3.4: Example of Slicing Operation for 16-QAM

Figure 3.5: Metric Computation Unit of Level 1

The waveforms in Figure 3.7 show the relation of the control signals with respect to the MIMO symbol. The design of the control unit is independent of number of parallel processing units m and pipelines k, this implies that very little redesign effort is required

in case one wants to achieve very high throughput by increasing m (subject to latency constraint) as we will see in the next section.

Figure 3.6: Product Computer Unit Using Shift and Add

Figure 3.7: Slicer Logic which Performs Slicing Operation

Figure 3.8: Output and Control Waveform

Figure 3.9: Find-Minimum Unit to Pick Minimum PD

The parallelism factor can also be increased (with corresponding changes in the control logic) to further increase the throughput. Figure 3.6 and Figure 3.7 shows the product computer and slicing unit used in our MCU. Figure 3.8 shows the underlying control signals generated to configure between different modulation schemes. Endbit is generated based on MF which is the detector input. Endbit is used to the minimum metric computed by the detector. Figure 3.9 shows the Find-Min unit which is required for hard decision of the MIMO symbol based on the computed distances.

#### **TABLE 3.1**

#### **Comparison of Reconfigurable Architectures**

| Ref    | QPSK | 16-QAM | 64-QAM | Dynamic     | BER         |

|--------|------|--------|--------|-------------|-------------|

|        |      |        |        | ReconFigure |             |

| [17]   | No   | Yes    | No     | No          | Quasi-ML    |

| [19]   | No   | Yes    | No     | No          | Quasi-ML    |

| [9]    | No   | Yes    | No     | No          | ML          |

| [16]   | No   | Yes    | No     | No          | Quasi-ML    |

| [22]   | Yes  | Yes    | Yes    | Yes         | Sub-Optimal |

| [23]   | No   | Yes    | No     | No          | Quasi-ML    |

| [This] | Yes  | Yes    | Yes    | Yes         | Quasi-ML    |

#### **3.3 FPGA Implementation Results**

The known previous reconfigurable architectures are either non-dynamic [18] or uses on-chip processors [22] to achieve re-configurability which is unsuitable for ASIC

#### **TABLE 3.2**

#### **FPGA Implementation Results**

| Target FPGA Device          | xc4vfx60 (Xilinx Virtex-4) |  |  |

|-----------------------------|----------------------------|--|--|

| Number of 4 Input LUTs      | 10745 (Utilization: 21%)   |  |  |

| Number of Slice Flip flops  | 845 (Utilization: 1%)      |  |  |

| Multipliers                 | None                       |  |  |

| Maximum Frequency           | 35 MHz                     |  |  |

| Max Decoding Rate: QPSK     | 280 Mbps                   |  |  |

| Max Decoding Rate: 16-QAM   | 140 Mbps                   |  |  |

| Max Decoding Rate: 64-QAM   | 52.5 Mbps                  |  |  |

| Total equivalent gate count | 107, 458                   |  |  |

| Control Logic Overhead      | 0.3%                       |  |  |

implementation. Moreover, the algorithm used in aforementioned designs degrades BER performance. In contrast, our decoder as shown in Table 3.1 supports on the fly reconfiguration, has a very simple control unit, with the control signals tightly integrated

with the datapath. More importantly, the proposed decoder delivers close to ML BER performance as shown in Figure 3.10. The decoding data flow is uninterrupted throughout the operation resulting in continuous detection. MATLAB was used to simulate bit accurate model of the decoder. We chose eleven bit fixed point quantization while maintaining internal precision) for negligible BER degradation. Based on this bit accurate MATLAB model, detail hardware was developed. RTL coding and synthesis

Figure 3.10: BER Performance Curve for SD (Floating Point/L2 Norm) vs. Implemented

COSIC Algorithm with (Fixed-Point/L1 Norm)

was done using Verilog HDL and Xilinx ISE 8.1 Embedded Development Kit respectively. Xilinx Virtex-4 [xc4vfx60] device was used for mapping the synthesized netlist. Floor-planning, Place and Route (P&R) of the design was done using the integrated Xilinx Floor-planner and automatic P&R tool. The input test vectors were generated by the fixed-point MATLAB model. The hardware design was validated by carrying out simulations on these test vectors with the Post-P&R simulation model using ModelSim PE 6.3c. Table 3.2 shows the FPGA Implementation results for our architecture.

#### 3.4 Summary of Results and Conclusion

The system architecture and FPGA implementation of a reconfigurable sphere decoder for MIMO detection is presented in this section. The detector is dynamically reconfigurable for QPSK, 16-QAM and 64-QAM modulation schemes for 4x4 MIMO systems. The decoder was implemented on a Xilinx [xc4vfx60] device. The decoder gives an un-coded throughput of 280 Mbps, 140 Mbps, and 52.5 Mbps for QPSK, 16-QAM, and 64-QAM respectively. The detector is further pipeline-able to achieve higher throughput. The proposed architecture is highly suitable for the next generation wireless standards because of its flexibility, reduced computational complexity and higher throughput.

# 4. ARCHITECTURAL SPACE EXPLORATION OF RECONFIGURABLE MIMO DETECTOR FOR IEEE 802.11n

The main objective of this section is to present an architectural exploration study done on the MIMO detector architecture that was developed in Section 3. The architecture described in the previous section can be parallelized and pipelined owing to its systolic-like nature. This section shows the results of exploration of this design space by searching through the tradeoff of pipelines and parallelism with the throughput for IEEE 802.11n providing the bounds for the operating clock frequency. As we saw in previous sections, the choice of algorithm and architecture has a significant bearing on the final hardware complexity and re-configurability. Besides the BER performance of an algorithm, our architecture focuses on issues like pipelining, parallelism, and reconfigurability. The algorithm should be designed such that it lends to a highly pipelined and parallel architecture. Also, the algorithm/architecture should be amenable to dynamic reconfiguration with various modulation schemes which is a requirement of various wireless standards. Among the earliest algorithms used for signal detection for un-coded MIMO was VBLAST [24]. Although computationally efficient, VBLAST suffers from a substantial degradation of BER. Other approaches for MIMO detection as we discussed earlier are the Sphere Decoding (SD) algorithm [9], which is a Depth First Search (DFS) based algorithm, and the K-best algorithm which is a Breadth First Search (BFS) based algorithm [17]. SD algorithm provides optimal Maximum Likelihood (ML) BER performance, but it is unsuitable for parallel and pipelined implementation. Also SD algorithm converges to the optimal solution in random fashion [9] which makes it unfit for practical systems. On the other hand, K-best algorithm provides constant throughput with quasi-optimal BER performance but involves sorting operation making it difficult to design a parallel and pipelined architecture. We use the Fixed-Throughput Sphere Decoding Algorithm (FSD) [19] with a modification called COSIC [20] algorithm for our implementation. It can be implemented in a highly parallel and pipelined manner, has fixed throughput (for a given modulation scheme) as seen in our implementation described in Section 3. FSD with COSIC achieves a quasi-optimal BER performance as can be seen from [20]. Here, it is also shown that the BER performance comparison for FSD and COSIC for 4x4 MIMO 64-QAM modulation scheme are quasioptimal and close to optimal respectively. In this section, we focus on wireless systems specifically based on 802.11n standard. In particular we carry out extensive architectural space exploration to address the issues of power consumption, area, and reconfigurability between different modes of operation while meeting the standards throughput requirement. Ultimately, we come up with two designs that target low area and low power respectively. Our detector supports on the fly re-configurability for QPSK, 16-QAM and 64-QAM modulation schemes. The control logic has low complexity and is highly integrated with the data flow. It delivers quasi-ML BER performance with no reconfiguration latency, leading to uninterrupted detection of MIMO symbols.

Figure 4.1: Tree Structure of FSD with COSIC Modification for 4x4 MIMO

Figure 4.2: Packet Structure of IEEE 802.11n Systems

#### 4.1 Architectural Flexibilities in FSD Implementation

As we saw in Section 3, the FSD algorithm with COSIC ordering maps the sphere decoding algorithm to a tree structure given in Figure 4.1. In COSIC, we consider n nodes in the first level and the best node in the next three levels of the FSD tree. MCU architecture for node processing in the last level (Level 1) was shown in Figure 3.5. The COSIC ordering technique if directly implemented then each of the branches of tree can map to n parallel processing MCUs which is a full parallel implementation of the COSIC algorithm. On the other extreme, if we reuse the same computing logic for computing each node of the tree then it is a complete sequential implementation of the same. The COSIC implementation in Section 3 has MCU units for each level of the tree. The depth of this logic can be pipelined owing to its systolic-like structure. Each added pipelining stage increases latency but also enhances the throughput of the detector. Hence, we can compensate for the loss of throughput in a sequential implementation by increasing the number of pipeline in our COSIC based architecture. The other constraint which is of importance is forced by the high level application e.g. IEEE 802.11n. As we will see later, the application enforces a hard constraint on the throughput required in the MIMO system. Hence, this section of the thesis describes methods in which we can exploit our architecture developed in Section 3 in terms of the number of pipelines/parallel processing nodes needed to meet the throughput requirements while providing optimal performance in terms of power and area. We show two optimized designs in this section. On design is optimized for low area and the other optimized for low power. Both our optimized designs meet applications throughput constraints.

#### 4.2 High Level Architectural Space Exploration

This section begins with a brief discussion about the throughput limitations imposed by the 802.11n standard. We then develop a strategy to evaluate various architectural parameters that meet the requirements of the standard.

Figure 4.3: MIMO Detection Interface Timing as Required in IEEE 802.11n

Figure 4.4: High Level Architecture of COSIC Based MIMO Detection

#### 4.2.1 Requirements of the IEEE 802.11n standard

Figure 2.1 depicts a simplified MIMO-OFDM system. An IEEE 802.11n system and its associated processing stages and requirements are shown in Figure 4.2. In MIMO-OFDM systems such as IEEE 802.11n, OFDM is used to mitigate the affect of multi-path fading. There are 52 data tones (or subcarriers) to be processed at the receiver. Each tone carries a MIMO symbol; hence the detector has to process all 52 tones in stipulated time of  $3.6\mu s$  (as imposed by the standard). This fact is shown pictorially in Figure 4.3. All 52 data tones are modulated using same modulation scheme, thus the decoder does not have to switch between modes within an OFDM symbol. The decoder is essentially an array of processors arranged as shown in Figure 4.4. It can process *m* candidate vectors in parallel. Furthermore, each data path in the array can be pipelined into *k* parts. The problem is to find *m* and *k* such that power/area is minimized as much as possible subject to the throughput constraint. Since, the decoder is reconfigurable this optimization has to be over all the supported modes.

#### **4.2.2.** Throughput Planning

First we will establish the relationship between the time taken,  $T_p$ , to process 52 MIMO symbols with *m* and *k* for  $\eta = 4$ , 16, and 64. Since the COSIC tree has  $\eta$  candidate vectors to be evaluated (for an  $\eta$ -ary modulation scheme), it takes  $\eta/m$  clock cycles to detect an  $\eta$ -ary modulated MIMO symbol in steady state. Hence,  $T_p$  is given by (4.1).

$$T_p = 52. \ \eta/m \ . \ freq$$

(4.1)

Figure 4.5: T<sub>p</sub> vs. (m, k) Constraint Due to 802.11n

We assume that the critical delay of data-path after introducing k pipelines reduces to  $C_d/(k+1)$ . This assumption has been validated empirically for k=0 to 10, using Synopsys Design Compiler re-timing utility. Eqn. 4.1 thus becomes:

$$T_p = T_p = 52. \ \eta/m \cdot C_d/(k+1)$$

(4.2)

where the factor 52 corresponds to the number of tones,  $C_d$  is the combinational delay of the un-pipelined data-path. Since 802.11n requires that the processing on all 52 tones be over in 3600ns, Tp  $\leq$  3600ns. Using above discussed model in Figure 4.5, we show how

Figure 4.6: Area vs. T<sub>p</sub> for 64-QAM

Tp behaves in the architecture space (with *m*, *k*) for  $\eta = 4$ , 16 and 64. Figure 4.5 also shows the constraint imposed by the 802.11n standard on the maximum time allotted to process all MIMO symbols. Clearly, all the points above the constraint plane are unacceptable as they don't meet the throughput criteria. In practice we keep the constraint plane at 3000ns (rather than 3600ns), this is to accommodate 15-20% pessimism factor.

#### 4.2.3. Power, Delay and Area Estimation

The power consumed comprises mainly of the core power (due to switching/leakage of logic gates), and due to clock network. The technology mapped

Figure 4.7: Aggregate Power vs. m, k

verilog netlist is analyzed for core power using Synopsys Design/Power Compiler. The technology library used was a composite current source (typical) based 45nm library from Nangate. The power consumed due to clock depends on number of flops and the geometry of the clock network. The clock network was modeled as a symmetrical mesh; the global clock network power was estimated using HSPICE. The local power was estimated using capacitive load due to the number of flip-flops driven by the local clock buffer (buffers were sized appropriately). Synopsys Design Compiler was used to estimate the delay of the circuit (re-timed circuit depending on the number of pipeline stages). Area estimates were also provided by Design Compiler.

Figure 4.8: MCU Architecture of Level 1 in the MIMO Detector

#### 4.2.4 Architectural Exploration for Low Area

In this subsection we describe our exploration procedure for low area, based on (m, k) constrained to throughput requirements of 802.11n. Figure 4.4 shows the

exploration space with respect to m and k. The points below the constraint plane are called admissible points. Since 64-QAM is computationally most expensive, the admissible points for 64-QAM must be admissible for 16-QAM and QPSK. Hence, to find (m, k) for area optimized decoder we only need to meet throughput requirements for 64-QAM with minimum hardware. Figure 4.6 shows variation of area of the decoder with m and k. In particular m=3 and k=8 meets the throughput requirement with least area as shown in Figure 4.6.

#### 4.2.5 Architectural Exploration for Low Power

Exploring the same space for power is more complicated, because different modulation schemes have different power consumption profiles while achieving the required throughput. Power consumption has to be optimized over all modes of operation. This means we have to pick (m, k) such that the 'aggregate power'' is minimized. We define aggregate power as  $Pow_{agg} = Prob(QPSK) * Pow(QPSK)+$ Prob(16-QAM) \* Pow(16-QAM)+ Prob(64-QAM) \* Pow(64-QAM), where Prob(QPSK) is the probability of the decoder being reconfigured to process QPSK MIMO symbols, and Pow(QPSK) is the power consumed by it while processing a QPSK MIMO symbol etc. Since there is no apriori knowledge of the probabilities, we assume them to be equally likely i.e. Prob(QPSK)=Prob(16-QAM)=Prob(64-QAM)=1/3.  $Pow_{agg}$  is a function of (m, k) as shown in Figure 4.7. However the point corresponding to the least power, does not meet the throughput criteria. Figure 4.7 shows the points (using stems) that meet the throughput criteria. Hence, (m, k) needs to be searched among these points. Hence, in our power optimized design uses m=4 and k=5 as shown in Figure 4.7.

#### TABLE 4.1

|           | Supported | BER   | Area  | Power | Technology | Throughput |

|-----------|-----------|-------|-------|-------|------------|------------|

| Reference | Modes     |       | (KGE) | (mW)  | (nm)       | (Mbps)     |

| [9]       | 16-QAM    | Q-Opt | 50K   | 473   | 250        | 169        |

| [17]      | 16-QAM    | Q-Opt | 91K   | 626   | 350        | 52         |

| [25]      | QPSK      | Opt   | 685K  | N/A   | 180        | 28.8       |

| [11]      | 16-QAM    | Q-Opt | 175K  | 407   | 180        | 160        |

#### **Comparison of Performance with Existing Architectures**

#### 4.3 Details of the MIMO Detection VLSI Architecture

The Metric Computation Units (MCUs) computes  $d_i(s^{(i)})$  metrics using (2.5)-(2.7).

#### 4.3.1 MCU Architecture

The MCU computes equations (2.5)-(2.7) in that order. Figure 4.8 shows the detailed structure of a MCU with only combinational logic at level 1 (lowest level in tree, corresponding to i = 1). The upper dotted box in Figure 4.8 evaluates (2.7). There is no need to implement the product terms in (2.7) using a multiplier. This product can be implemented simply by shift and add operation, because the QAM constellation points only take on a finite number of integer values (e.g. in 16-QAM scheme the real and imaginary part of  $s_j \in \{-3, -1, 1, 3\}$ ). The middle dotted box implements (2.5); this box is primarily composed of two blocks: a Slicer, and a block for computing the norm. As

## TABLE 4.2

## **ASIC Implementation Details**

| Design Parameters             | Area         | Power        |  |

|-------------------------------|--------------|--------------|--|

|                               | Optimized    | Optimized    |  |

|                               | Design       | Design       |  |

| Target Technology Library     | Nangate 45nm | Nangate 45nm |  |

|                               | PDK          | PDK          |  |

| Pipeline Stages (k)           | 8            | 5            |  |

| Parallelism (m)               | 3            | 4            |  |

| Gate Equivalent               | 58.2K        | 67.7K        |  |

| Power Consumption             | 11.91mW      | 9.7mW        |  |

| Frequency: QPSK               | 38.8MHz      | 18MHz        |  |

| Frequency: 16-QAM             | 116.3MHz     | 71.8MHz      |  |

| Frequency: 64-QAM             | 426.6MHz     | 287.3MHz     |  |

| Throughput Requirement QPSK   | 115.6Mbps    | 115.6Mbps    |  |

| Throughput Achieved QPSK      | 155Mbps      | 144Mbps      |  |

| Throughput Requirement 16-QAM | 231.1Mbps    | 231.1Mbps    |  |

| Throughput Achieved 16-QAM    | 310.13Mbps   | 287.2Mbps    |  |

| Throughput Requirement 64-QAM | 346.7Mbps    | 346.7Mbps    |  |

| Throughput Achieved 64-QAM    | 465.38Mbps   | 430.95Mbps   |  |

'best' child (nodes with least  $|e_i|^2$ ) of these nodes thereafter. From (2.5) it can be easily seen that, in order to minimize  $|e_i|^2$ , we need to compute s<sub>i</sub> such that the distance between  $c_{i+1}$  and  $R_{ii}$ .s<sub>i</sub> is minimized. The slicer block picks the nearest scaled QAM symbol ( $R_{ii}$ , s<sub>i</sub>) to  $c_{i+1}$  as shown in Figure 4.8. This operation involves independently comparing real and imaginary parts of  $c_{i+1}$  with appropriate decision thresholds. For example, in Figure 4.8 the nearest scaled QAM symbol to  $c_{i+1}$  is (1+j). $R_{ii}$ , since real and imaginary parts of  $c_{i+1}$ are both less than 2 $R_{ii}$ . In general, the decision thresholds are given by (- ( $\sqrt{\eta}$  - 2) + 2j)  $R_{ii}$ , where j is an integer such that  $0 \le j \le (\sqrt{\eta} - 2)$ ). The decoder configures the slicer based on the MF bits (MF bits are essentially representative of η). The block named 'NORM' computes (2.6), this involves squaring operations, however, we use suboptimal norm in order to avoid multipliers as will be described next. Simplified 1<sup>1</sup> norm computation as shown earlier in Section 3 was also used instead of 1<sup>2</sup> norm to reduce the number of multipliers in the design. Each individual blocks in the design can be seen in Section 3.

#### **4.4 ASIC Implementation Results**

Table 4.1 shows the comparison between various existing designs (q-opt stands for quasi-optimal). In Table 4.2 we present implementation results of our two designs (area and power optimized) and where they stand with respect to the existing designs. MATLAB was used to simulate bit accurate model of the decoder. We chose eleven bit fixed point quantization (internal precision was maintained) for negligible BER degradation. Detailed hardware architecture was then developed. The RTL coding was done using Verilog HDL. Nangate 45nm CMOS predictive standard cell library was used for the design flow. Synopsys Design Compiler was used to synthesize the gate level net-list and retime the circuit. MATLAB generated test vectors that were used to validate the design.

#### 4.5 Results, Summary and Conclusion

Two designs for reconfigurable MIMO detector are presented in this section. First design pushes for least area, and the second one targets lower power consumption. The detector is dynamically reconfigurable for QPSK, 16-QAM and 64-QAM modulation schemes for 4x4 MIMO systems as was discussed in Section 3 as well. The proposed architecture is highly suitable for the IEEE 802.11n wireless standard because of its flexibility, and ability to meet the required throughput.

## 5. LOW POWER RECONFIGURABLE MIMO DETECTOR FOR REAL-TIME MOBILE APPLICATIONS