# LINEARITY AND NOISE IMPROVEMENT TECHNIQUES EMPLOYING LOW POWER IN ANALOG AND RF CIRCUITS AND SYSTEMS

### A Dissertation

by

### EHAB AHMED SOBHY TAWFIK ABDEL GHANY

Submitted to the Office of Graduate Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Approved by:

Chair of Committee, Sebastian Hoyos

Committee Members, Edgar Sanchez-Sinencio

Laszlo B. Kish

Mahmoud El-Halwagi

Department Head, Costas N. Georghiades

December 2012

Major Subject: Electrical Engineering

Copyright 2012 Ehab Ahmed Sobhy Tawfik Abdel Ghany

### ABSTRACT

The implementation of highly integrated multi-bands and multi-standards reconfigurable radio transceivers is one of the great challenges in the area of integrated circuit technology today. In addition the rapid market growth and high quality demands that require cheaper and smaller solutions, the technical requirements for the transceiver function of a typical wireless device are considerably multi-dimensional. The major key performance metrics facing RFIC designers are power dissipation, speed, noise, linearity, gain, and efficiency. Beside the difficulty of the circuit design due to the trade-offs and correlations that exist between these parameters, the situation becomes more and more challenging when dealing with multi-standard radio systems on a single chip and applications with different requirements on the radio software and hardware aiming at highly flexible dynamic spectrum access. In this dissertation, different solutions are proposed to improve the linearity, reduce the noise and power consumption in analog and RF circuits and systems.

A system level design digital approach is proposed to compensate the harmonic distortion components produced by transmitter circuits' nonlinearities. The approach relies on polyphase multipath scheme uses digital baseband phase rotation pre-distortion aiming at increasing harmonic cancellation and power consumption reduction over other reported techniques.

New low power design techniques to enhance the noise and linearity of the receiver front-end LNA are also presented. The two proposed LNAs are fully differential and have a common-gate capacitive cross-coupled topology. The proposed LNAs avoids the use of bulky inductors that leads to area and cost saving. Prototypes are implemented in IBM 90 nm CMOS technology for the two LNAs. The first LNA

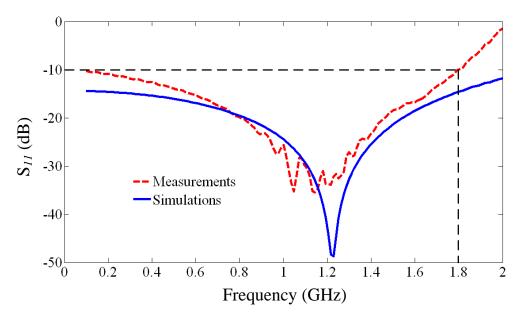

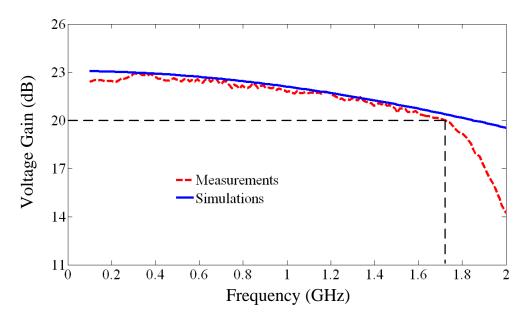

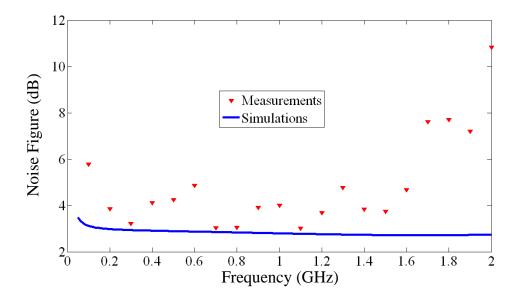

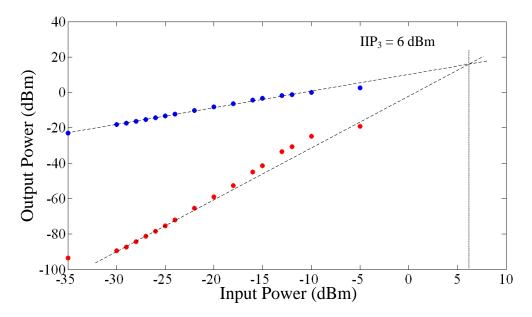

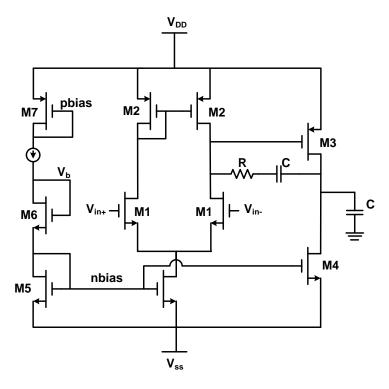

covers the frequency range of 100 MHz to 1.77 GHz consuming 2.8 mW from a 2 V supply. Measurements show a gain of 23 dB with a 3-dB bandwidth of 1.76 GHz. The minimum NF is 1.85 dB while the input return loss is greater than 10 dB across the entire band. The second LNA covers the frequency range of 100 MHz to 1.6 GHz. A 6 dBm third-order input intercept point, IIP3, is measured at the maximum gain frequency. The core consumes low power of 1.55 mW using a 1.8 V supply. The measured voltage gain is 15.5 dB with a 3-dB bandwidth of 1.6 GHz. The LNA has a minimum NF of 3 dB across the whole band while achieving an input return loss greater than 12 dB.

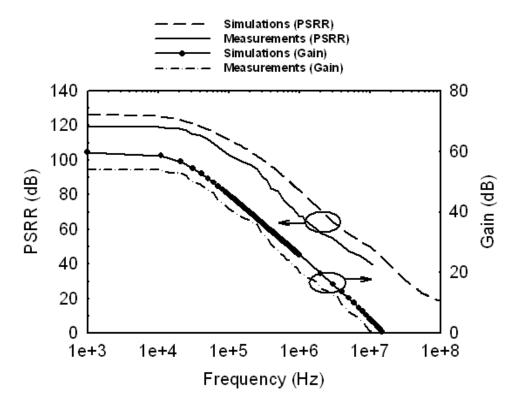

Finally, A CMOS single supply operational transconductance amplifier (OTA) is reported. It has high power supply rejection capabilities over the entire gain bandwidth (GBW). The OTA is fabricated on the AMI 0.5 um CMOS process. Measurements show power supply rejection ratio (PSRR) of 120 dB till 10 KHz. At 10 MHz, PSRR is 40 dB. The high performance PSRR is achieved using a high impedance current source and two noise reduction techniques. The OTA offers a very low current consumption of 25 uA from a 3.3 V supply.

# DEDICATION

To my great parents, my beloved sister, Maha, and my lovely wife, Salma.

### ACKNOWLEDGEMENTS

Before any one, I am thanking Allah the almighty for his blessing and mercy.

I am thankful to the members of my committee, Professor Sebastian Hoyos, the chair of the committee and my research advisor, Professor Edgar Sanchez-Sinencio, Professor Laszlo B. Kish, and Professor Mahmoud El-Halwagi, for their support, guidance, and helpful suggestions. Their guidance has served me well.

I wish to acknowledge all my colleagues, from the Analog Mixed Signal Center (AMSC) for their inspiring discussions and help. Special thanks to my friend and roommate, Ahmed Alaa Helmy. His friendship, assistance, and valuable discussions have meant more to me than I could ever express.

I would like to acknowledge my parents for their love that provided me with inspiration and support at each stage of my life. I owe them everything and wish I could show them just how much I love and appreciate them. I am also thankful to my sister, Maha, for her continuous support during this research work. I wish to thank my wife, Salma, for her encouragement during the last stage of my PhD. Her love and support allowed me to finish this journey. Finally, I would like to dedicate this work to all my family. I hope that this work makes you proud.

# TABLE OF CONTENTS

|    |                                 | P                                                             | age                                 |

|----|---------------------------------|---------------------------------------------------------------|-------------------------------------|

| AI | BSTR                            | ACT                                                           | ii                                  |

| DI | EDIC                            | ATION                                                         | iv                                  |

| A  | CKNO                            | DWLEDGEMENTS                                                  | V                                   |

| TA | ABLE                            | OF CONTENTS                                                   | vi                                  |

| LI | ST O                            | F FIGURES                                                     | viii                                |

| LI | ST O                            | F TABLES                                                      | xi                                  |

| 1. | INT                             | RODUCTION                                                     | 1                                   |

| 2. |                                 | ULTI-PHASE MULTI-PATH TECHNIQUE FOR DISTORTION CAN-<br>LATION | 4                                   |

|    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Introduction                                                  | 4<br>6<br>7<br>10<br>11<br>14<br>17 |

| 3. |                                 | LTIPLE FEEDBACK LOW POWER INDUCTORLESS WIDEBAND OS LNA        | 22                                  |

|    | 3.1<br>3.2<br>3.3               | Introduction                                                  | 22<br>24<br>26<br>27<br>29          |

|    |                                 | 3.3.1 Input impedance                                         | 29                                  |

|    |      | 3.3.2  | Stability                                       | 30 |

|----|------|--------|-------------------------------------------------|----|

|    |      | 3.3.3  | Noise analysis                                  | 32 |

|    | 3.4  | Circui | t design and measurement results                | 36 |

| 4. |      |        | VER INDUCTORLESS WIDEBAND COMMON GATE LNA       |    |

|    | WIT  | TH ENI | HANCED LINEARITY                                | 43 |

|    | 4.1  | Introd | luction                                         | 43 |

|    | 4.2  | Backg  | round                                           | 46 |

|    | 4.3  | Linear | rization techniques                             | 47 |

|    |      | 4.3.1  | Feedback                                        | 48 |

|    |      | 4.3.2  | Optimal biasing at sweet spot                   | 52 |

|    |      | 4.3.3  | Derivative superposition (DS)                   | 53 |

|    | 4.4  | Propo  | sed linear CGLNA                                | 54 |

|    |      | 4.4.1  | Input impedance and gain                        | 56 |

|    |      | 4.4.2  | Stability                                       | 57 |

|    |      | 4.4.3  | Noise analysis                                  | 58 |

|    |      | 4.4.4  | Linearity                                       | 60 |

|    | 4.5  | Circui | t design and measurement results                | 64 |

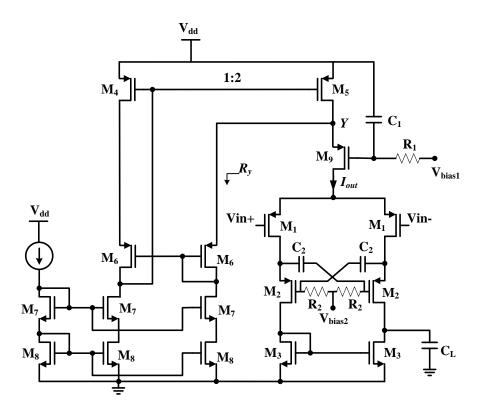

| 5. | HIG  | H-PSR  | R LOW-POWER SINGLE SUPPLY OTA                   | 70 |

|    | 5.1  | Introd | luction                                         | 70 |

|    | 5.2  |        | round                                           | 73 |

|    |      | 5.2.1  | Use of cascode transistor [51]                  | 73 |

|    |      | 5.2.2  | Use of Parallel path [52]                       | 74 |

|    |      | 5.2.3  | Use of ground referenced negative feedback [53] | 75 |

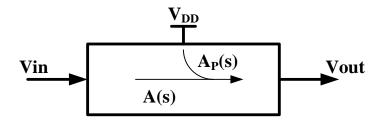

|    | 5.3  |        | sed system                                      | 76 |

|    | 5.4  | -      | rement result                                   | 78 |

| 6. | CON  |        | ION                                             | 80 |

| ٥. | 001  | ,0200  |                                                 |    |

| RI | EFER | ENCE   | S                                               | 82 |

# LIST OF FIGURES

| FIGUI | RE                                                                                                                                                                                                                  | Page  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

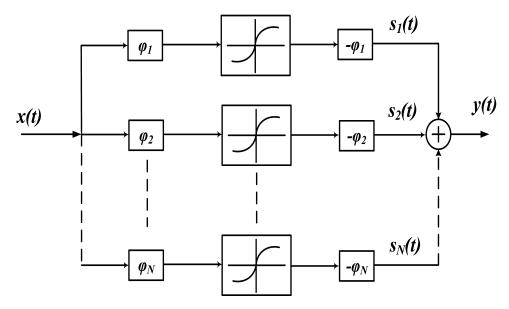

| 2.1   | Poly-phase multi-path technique proposed in [6]                                                                                                                                                                     | . 8   |

| 2.2   | Poly multi-path technique implemented with mixers that operate as wide-band phase shifters                                                                                                                          | . 8   |

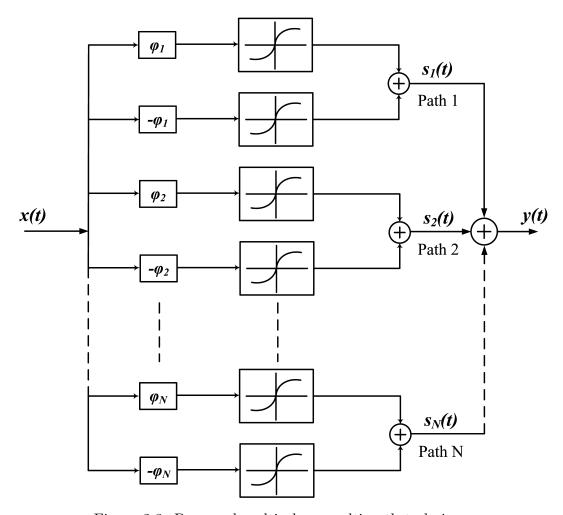

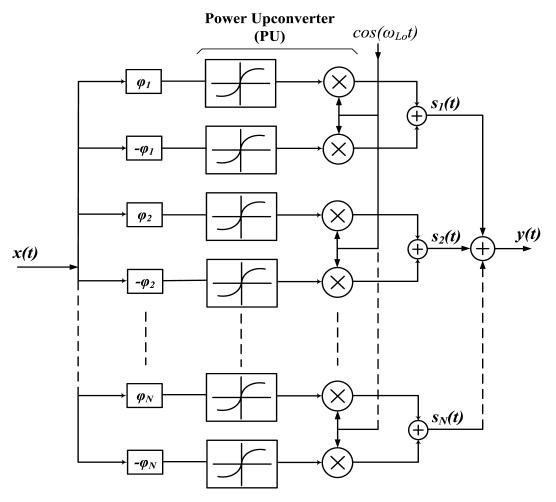

| 2.3   | Proposed multi-phase multi-path technique                                                                                                                                                                           | . 9   |

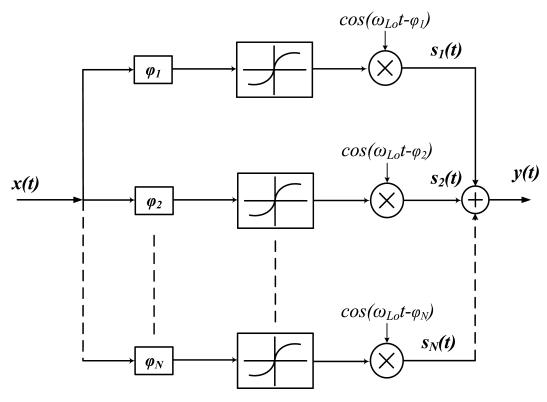

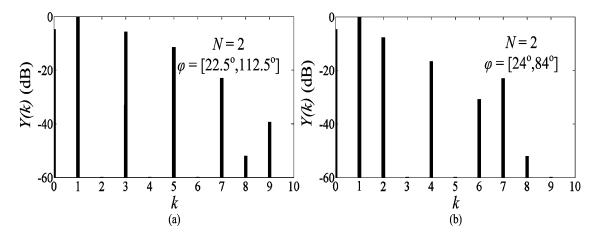

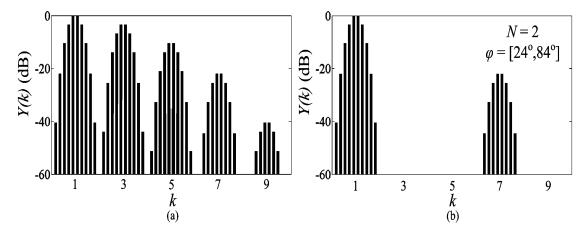

| 2.4   | Output spectrum of the proposed multi-phase scheme for a single-tone input. (a) $N=2$ and $\varphi=[22.5^o,112.5^o]$ . (b) $N=2$ and $\varphi=[24^o,84^o]$ . $a_k=[0,1,0.2,-1.6242,0.5,2.638,0.7,-4.284,0.8,6.954]$ | ]. 11 |

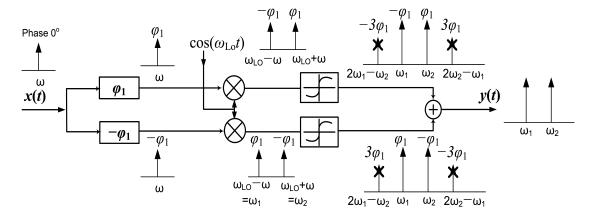

| 2.5   | Output spectrum for a two-tone input. (a) Without distortion cancellation. (b) Proposed multi-phase with $N=2$ and $\varphi=[24^o,84^o]$ . $a_k=[0,1,0,-1.6242,0,2.638,0,-4.284,0,6.954]$                           | . 13  |

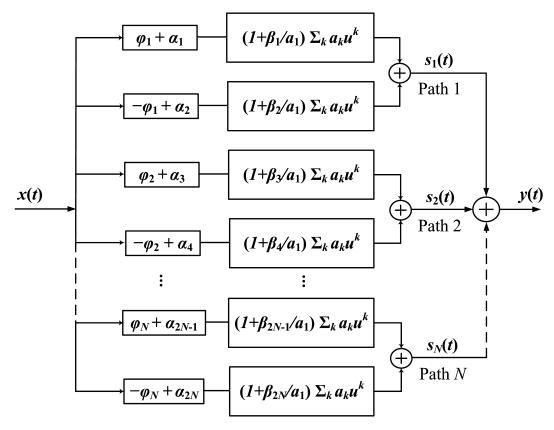

| 2.6   | Proposed multi-phase multi-path system with gain and phase mismatches included                                                                                                                                      | . 14  |

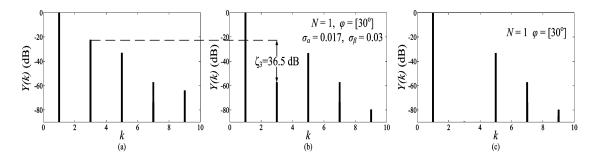

| 2.7   | Output spectrum for a single-tone input. (a) Without distortion cancellation. (b) Proposed multi-phase scheme with gain and phase mismatches. (c) Proposed multi-phase scheme without mismatches                    | . 16  |

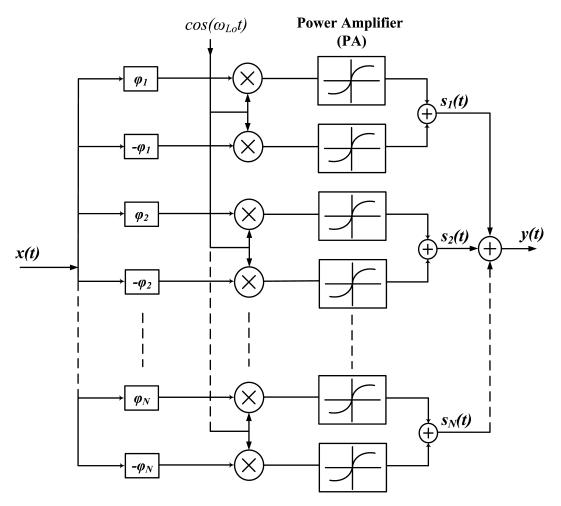

| 2.8   | Conventional transmitter architecture using current-output multi-PAs with the proposed digitally generated multi-phase technique                                                                                    | . 17  |

| 2.9   | Current-output power upconverter model with the proposed digitally generated multi-phase multi-path technique                                                                                                       | . 18  |

| 2.10  | Cancellation of the 3rd order nonlinearity in the signal side bands                                                                                                                                                 | . 20  |

| 2.11  | Comparison between the normalized output spectrum. (a) Without distortion cancellation. (b) With the proposed multi-phase technique.                                                                                | 20    |

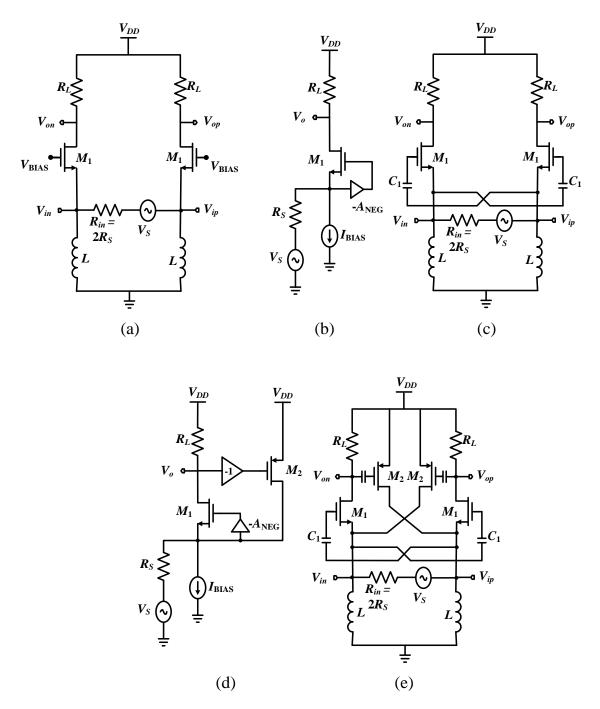

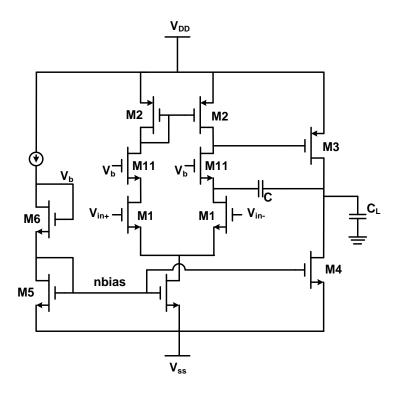

| 3.1   | Conventional differential CGLNA and low noise feedback techniques .                                                                                                                                                 | . 25  |

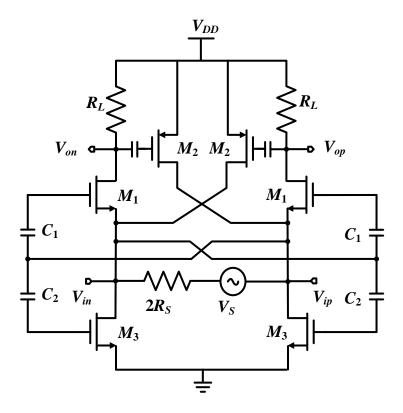

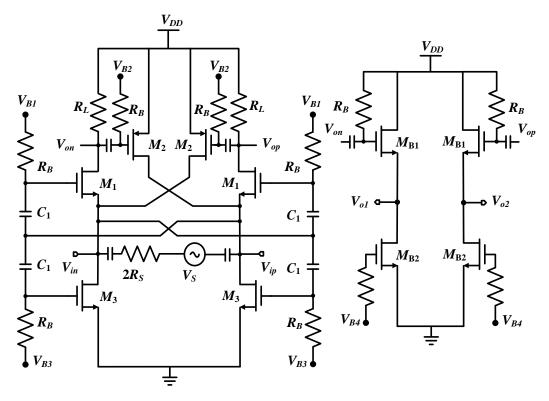

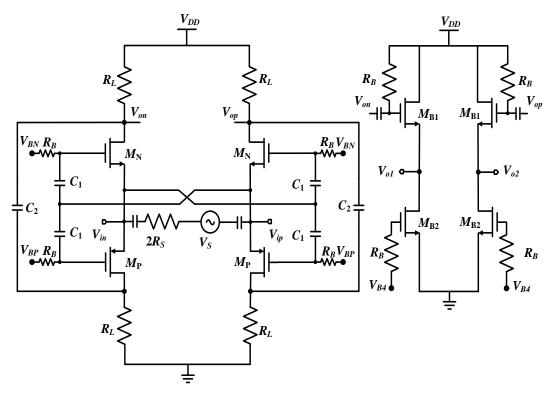

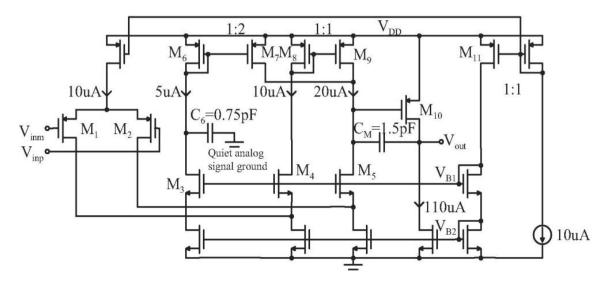

| 3.2   | Schematic of the proposed CGLNA (biasing circuit not shown)                                                                                                                                                         | 30    |

| 3.3   | Simplified single-ended CGLNA model                                                                                                                                                                                 | . 31  |

| 3.4   | Schematic of the proposed CGLNA showing noise sources                                                                                                                                                               | . 32  |

| 3.5  | Calculated noise figure versus the optimization parameter $\eta$ for the proposed CGLNA at $A_{POS}=0.35,R_L=650\Omega,\gamma=(4/3),{\rm and}\alpha=0.8$                                                                                                                                           | 35      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 3.6  | Schematic of the entire LNA with the output buffer                                                                                                                                                                                                                                                 | 37      |

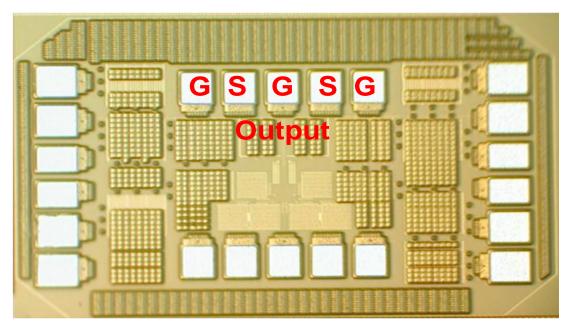

| 3.7  | Die photo of the proposed LNA                                                                                                                                                                                                                                                                      | 38      |

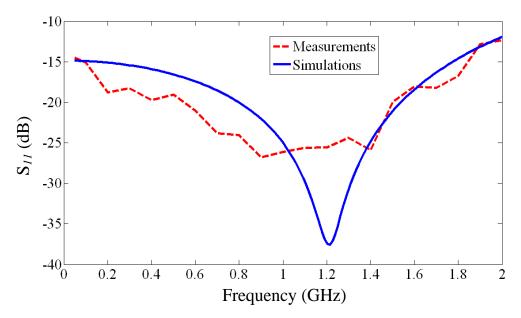

| 3.8  | Measured and simulated input matching versus RF input signal frequency                                                                                                                                                                                                                             | 40      |

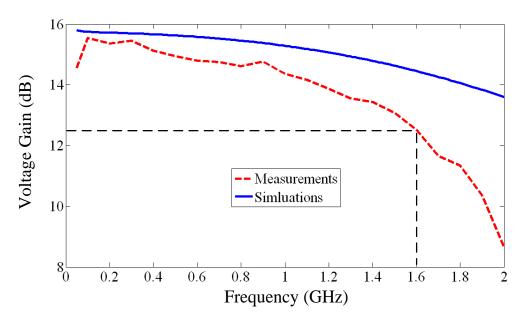

| 3.9  | Measured and simulated voltage gain versus RF input signal frequency                                                                                                                                                                                                                               | 40      |

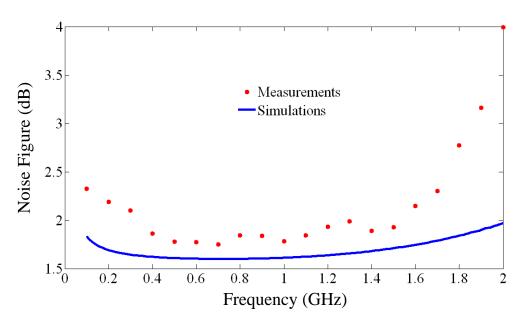

| 3.10 | Measured and simulated noise figure versus RF input signal frequency                                                                                                                                                                                                                               | 41      |

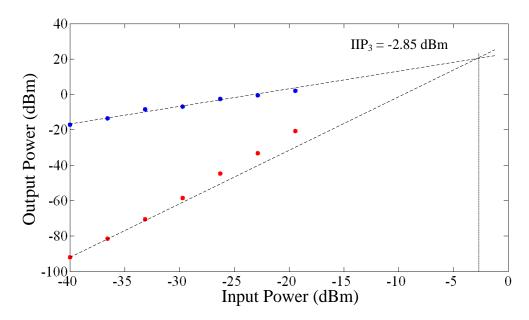

| 3.11 | Measured $IIP_3$ for the proposed CGLNA                                                                                                                                                                                                                                                            | 41      |

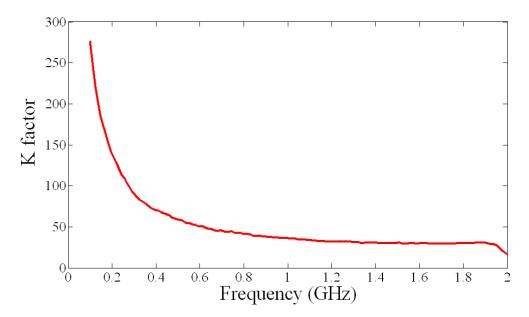

| 3.12 | Stability factor for the proposed CGLNA                                                                                                                                                                                                                                                            | 42      |

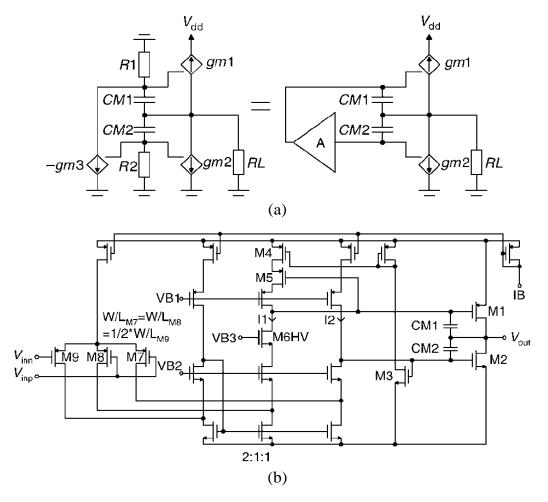

| 4.1  | Conventional and capacitor cross-coupled differential CGLNA                                                                                                                                                                                                                                        | 49      |

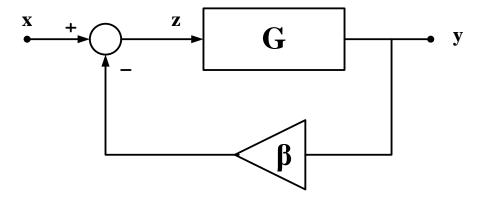

| 4.2  | Nonlinear amplifier is a negative feedback                                                                                                                                                                                                                                                         | 49      |

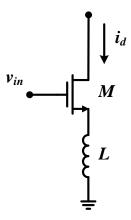

| 4.3  | Inductively source-degenerated LNA                                                                                                                                                                                                                                                                 | 51      |

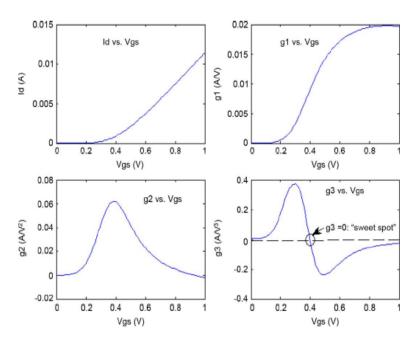

| 4.4  | NMOS transconductance characteristics [43]                                                                                                                                                                                                                                                         | 52      |

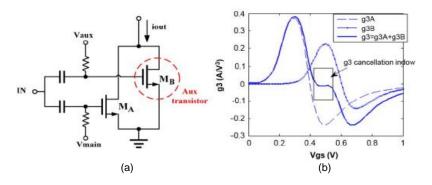

| 4.5  | (a) DS method (b) Third-order nonlinear coefficients [43]                                                                                                                                                                                                                                          | 53      |

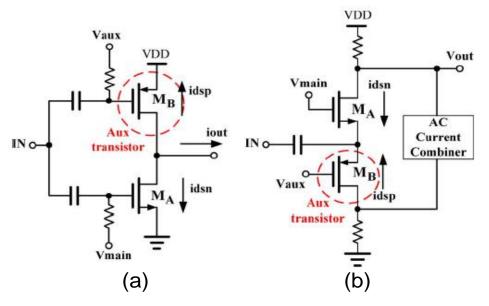

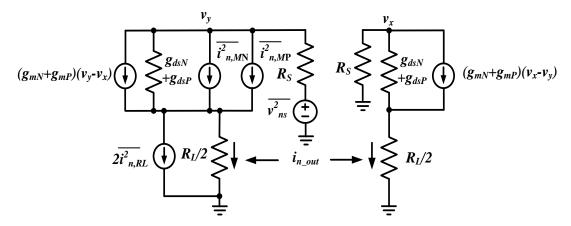

| 4.6  | Complementary DS (a) Common-source NMOS/PMOS [40] (b) Commongate NMOS/PMOS [41]                                                                                                                                                                                                                    | -<br>54 |

| 4.7  | Schematic of the proposed CGLNA (biasing circuit not shown)                                                                                                                                                                                                                                        | 55      |

| 4.8  | Simplified single-ended CGLNA model                                                                                                                                                                                                                                                                | 55      |

| 4.9  | Small signal model of the proposed CGLNA                                                                                                                                                                                                                                                           | 56      |

| 4.10 | Schematic of the proposed CGLNA showing noise sources                                                                                                                                                                                                                                              | 58      |

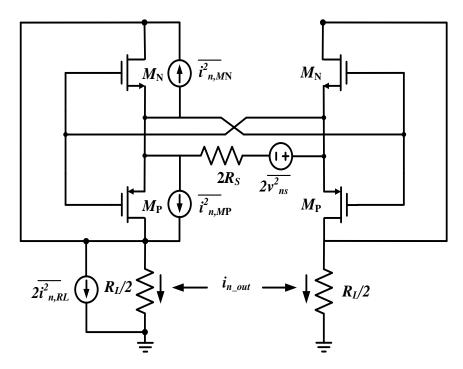

| 4.11 | Small signal model of the proposed CGLNA showing noise sources                                                                                                                                                                                                                                     | 59      |

| 4.12 | Common-gate schematic for distortion analysis (a) PMOS (b) NMOS (c) Complementary NMOS/PMOS DS                                                                                                                                                                                                     | 61      |

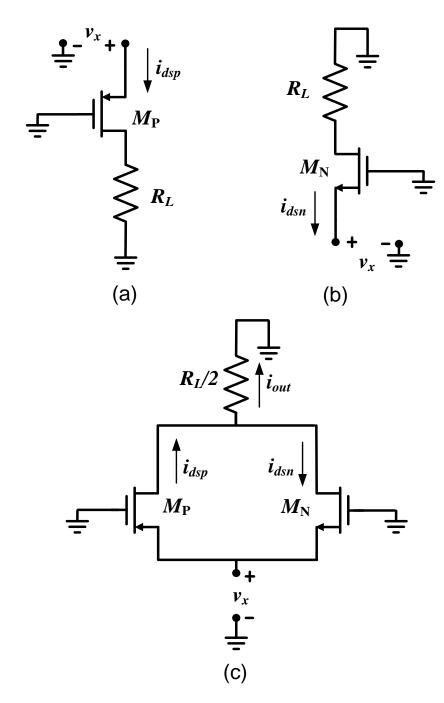

| 4.13 | Second/third-order nonlinear distortion coefficients of NMOS, PMOS, and total for complementary NMOS/PMOS as a function of the bias (IBM 90 nm CMOS process, $(\frac{W}{L})_{M_N} = \frac{44~\mu\text{m}}{0.1~\mu\text{m}}$ and $(\frac{W}{L})_{M_P} = \frac{100~\mu\text{m}}{0.1~\mu\text{m}}$ ). | 63      |

| 4.14 | Schematic of the entire LNA with the output buffer                                                                                                                                                                                                                                                 | 65      |

|      |                                                                                                                                                                                                                                                                                                    |         |

| 4.15 | Die photo of the proposed LNA                                                                        | 65 |

|------|------------------------------------------------------------------------------------------------------|----|

| 4.16 | Measured and simulated input matching versus RF input signal frequency                               | 67 |

| 4.17 | Measured and simulated voltage gain versus RF input signal frequency                                 | 68 |

| 4.18 | Measured and simulated noise figure versus RF input signal frequency                                 | 68 |

| 4.19 | Measured $IIP_3$ for the proposed CGLNA                                                              | 69 |

| 5.1  | Block Diagram of general electric circuit                                                            | 71 |

| 5.2  | Two Stage Miller Amplifier                                                                           | 72 |

| 5.3  | Cascode Compensation PSRR technique                                                                  | 73 |

| 5.4  | Parallel path using current mirror PSRR technique                                                    | 74 |

| 5.5  | (a) Small signal model of the output stage (b) Implementation of Class AB compensation for high PSRR | 75 |

| 5.6  | Proposed High PSRR single supply OTA                                                                 | 76 |

| 5.7  | Measured and simulated Gain and PSRR                                                                 | 78 |

# LIST OF TABLES

| TABL1 | E                                                                                       | Pa  | ge |

|-------|-----------------------------------------------------------------------------------------|-----|----|

| 2.1   | Comparison between the poly-phase technique in [6] and the proposed technique           |     | 21 |

| 3.1   | Comparison between different CGLNA configurations together with the proposed one        |     | 34 |

| 3.2   | Transistor aspect ratios for the LNA and buffer                                         | . ; | 37 |

| 3.3   | Performance summary of the proposed broadband LNA and comparison with the existing work |     | 42 |

| 4.1   | Transistor aspect ratios for the LNA and buffer                                         | . ( | 67 |

| 4.2   | Performance summary of the proposed broadband LNA and comparison with the existing work |     | 69 |

| 5.1   | The proposed high PSRR OTA performance and comparison                                   | . ' | 79 |

### 1. INTRODUCTION

Within the last two decades, Number of wireless standards for wireless communication has increased at a tremendous pace: Cellphones (GSM, EDGE, CDMA, W-CDMA,UMTS etc), communication networks (WIFI 802.11 a/b/g, bluetooth, WiMax, UWB etc), satellite services (GPS). The resulting crowded spectrum and the increase of users' demand for flexibility and mobility have pushed the evolution of transceivers compatible with as many different standards and frequency bands as possible. And since the sky has no limits, the progress in wireless communications never stops. A strong potential, in the last decade, has been directed to the idea on multi-bands, multi-standards on the same chip, which enables the user to access different communications wireless standards from single portable small device. Together these developments have imposed great challenges in the design of the wireless transceivers and puts tremendous efforts on RFIC designers to provide solutions and overcome problems especially with the rapid growth of CMOS technology into deep sub-micron.

The implementation of highly integrated multi-bands and multi-standards reconfigurable radio transceivers is one of the great challenges in the area of integrated circuit technology today. In addition the rapid market growth and high quality demands that require cheaper and smaller solutions, the technical requirements for the transceiver function of a typical wireless device are considerably multi-dimensional. The major key performance metrics facing RFIC designers are power dissipation, speed, noise, linearity, gain, and efficiency. Beside the difficulty of the circuit design due to the trade-offs and correlations that exist between these parameters, the situation becomes more and more challenging when dealing with multi-standard radio

systems on a single chip and applications with different requirements on the radio software and hardware aiming at highly flexible dynamic spectrum access.

From the RF transmitter point of view nonlinearity due to DACs, mixers, and power amplifiers (PA) creates spectral growth outside the signal band which interferes with adjacent channels. Also, the nonlinearity causes distortion within the signal band which increases the bit error rate after reception. Therefore, transmitter building blocks should be designed to meet both the linearity requirements and the desired transmit spectrum mask.

From the RF receiver point of view, the quality of a communication system is mainly influenced by the sensitivity of the receiver, which is defined as the minimum detectable signal the receiver can catch. A critical receiver stage is the first amplifier, low noise amplifier (LNA), that should have a low noise figure (NF) as well as sufficient gain to provide high sensitivity and also a high dynamic range. Dynamic range is set by the difference between linearity and sensitivity performance. Both metrics continue to become progressively challenging in many systems, for example, linearity requirements are becoming increasingly severe in many cases due to greater spectrum usage to avoid intermodulation products from strong signals. The third-order intermodulation products have substantial influence on the receiver performance. These undesired signals appear in a band close to the operating frequency and cause interference in the receiver system. In most cases intermodulation can be reduced by increasing the current through the active device however this will increase the power consumption which is an essential design factor to be reduced for of longer battery life and lower cost solutions.

Another important source of noise, beside the thermal and flicker noise coming from the circuit active and passive device, is the power supply noise which can significantly decrease the performance by reducing the dynamic range of the whole system especially, in high precision systems or if the circuits that are sensitive to supply noise are at the very beginning of the power supply/reference chain. Reducing the supply noise and having higher rejection is very essential and challenging in System-on-Chip (SOC) design of modern integrated circuits that have employed analog building blocks to be placed on the same die together with noisy digital circuitry.

In this dissertation, four different projects are presented that have proposed solutions to improve the linearity, reduce the noise and power consumption in analog and RF circuits and systems. The dissertation is organized as follows: Chapter 2 provides a system level design digital approach to compensate the harmonic distortion components produced by transmitter circuits' nonlinearities. The approach relies on polyphase multipath scheme uses digital baseband phase rotation pre-distortion aiming at increasing harmonic cancellation and power consumption reduction over other reported techniques. Chapters 3 and 4 provides new low power design techniques to enhance the noise and linearity of the receiver front-end LNA. Both proposed LNAs are fully differential and have a common-gate capacitive cross-coupled topology. The proposed LNAs avoids the use of bulky inductors that leads to area and cost saving. Prototypes are implemented in IBM 90 nm CMOS technology for the two LNAs. Circuit implementations are presented for the LNAs along with simulation results and measurements. In Chapter 5, a CMOS single supply operational transconductance amplifier (OTA), with high power supply rejection ratio (PSRR), is presented. A high output impedance current source and noise reduction techniques are used to improve of PSRR both at DC and at higher frequency up to the gain bandwidth (GBW) of the OTA, respectively. The presented OTA has a simple structure and it offers a very low current consumption compared to other reported structures. Chapter 6 concludes.

# 2. A MULTI-PHASE MULTI-PATH TECHNIQUE FOR DISTORTION CANCELLATION\*

Nonlinearities in transmitter circuits, such as power amplifiers (PAs), cause degradation in system performance and adjacent channel spectral growth interference. Poly-phase multi-path is considered among the techniques that can compensate the nonlinearities, creating a clean output spectrum. However, the poly-phase technique requires analog phase shifters which consume considerable power. Aiming at reducing the power consumption, this work presents a novel multi-phase multi-path technique with digital phase shifters. The technique is capable of canceling most of the harmonic and intermodulation products produced by a current-output nonlinear circuit to achieve the required linearity. The proposed system has advantages over existing poly-phase techniques in power consumption, accuracy, and flexibility. However, it lacks image rejection and local oscillator harmonic cancellation. Detailed analyses and simulations of the new technique are provided to show the effectiveness of the harmonic distortion cancellation.

#### 2.1 Introduction

In RF transmitters, nonlinearity due to DACs, mixers, and power amplifiers (PAs) creates spectral growth outside the signal band, which interferes with adjacent channels. Also, the nonlinearity causes distortion within the signal band, which increases the bit error rate after reception. Therefore, transmitter building blocks should be designed to meet both the linearity requirements and the desired transmit spectrum mask.

<sup>\*</sup>Part of this chapter is reprinted with permission from "A Multiphase Multipath Technique With Digital Phase Shifters for Harmonic Distortion Cancellation," by E. A. Sobhy and S. Hoyos, Dec. 2010. *IEEE Trans. Circuits Syst. II*, vol. 57, no. 12, pp. 921-925.

Cartesian feedback (CFB) [1, 2] is one of the methods to linearize an RF transmitter and enhance the spectral purity of nonlinear circuits. CFB is an analog solution that achieves high efficiency and shows robustness to process parameters, supply voltage, and junction temperature (PVT) variations, but has phase alignment limitations and stability issues [2]. Digital predistortion [3, 4, 5] is also a linearization solution. It is cost efficient but its accuracy is limited by the predistorter design and the degree it tracks the nonlinearity.

Another solution to cancel the distortion products is using the poly-phase multi-path technique [6, 7], in which the authors use several frequency-independent phase shifters in a multi-path topology. Two sets of phase shifters are used: one before and another after the nonlinear block to cancel the unwanted signal. The poly-phase multi-path technique significantly relaxes the requirements on the high quality bandpass LC filters used in conventional transmitters to remove the unwanted harmonics and sidebands. This makes the poly-phase circuits very attractive in multi-standards and cognitive radio transmitter architectures. In order not to increase the system complexity over a single path topology, the poly-phase technique is used with current-output nonlinear circuits [6], where the area and current are split into multi paths. In [6], a current-output power upconverter (PU) architecture is designed based on the poly-phase multi-path technique to produce a clean output spectrum. No RF filters are used at the output, aiming at software-defined radio applications. As reported in [6], the chip consumes 228 mW. A large portion of the consumed power, 156 mW, is used to realize the second set of phase shifters.

In this work, a novel multi-phase multi-path architecture is presented that no longer uses the analog phase shifters after the nonlinear block. Instead, these derotation phase shifters are moved to the digital front-end together with the original rotation phase shifters. This new digitally generated multi-phase topology has ad-

vantages over the architecture in [6] such as flexibility, power saving, and robustness to mismatches. These advantages come out at the cost of some signal loss, which can be minimized by proper choice of the digital phase shifts, double sideband transmission, and non-cancellation of the local oscillator (LO) harmonics that can be filtered out using a low quality bandpass filter. The Chapter is organized as follows. In Section 2, background on the poly-phase architecture in [6] is summarized. Section 3 covers the new proposed solution, showing the analyses and simulations for single and two-tone tests. In Section 4, mismatches between paths are considered. Applications are presented in Section 5.

## 2.2 Background

Fig. 2.1 shows the poly-phase multi-path technique presented in [6]. The input signal, at frequency  $\omega$ , is injected into N paths with matched nonlinear circuits. In each path, the signal undergoes equal phase rotation and de-rotation before and after the nonlinear circuit, respectively. The output spectrum of the nonlinear block has frequency components at  $\omega$  and also at multiples of  $\omega$  due to harmonic distortion. The phase shift vector  $\underline{\varphi} = [\varphi_1, \varphi_2, ..., \varphi_N]$  is chosen such that phases between paths are equidistant  $[\varphi_j = 360(j-1)/N, j=1,2,3...,N]$ . Choosing such a phase shift vector results in equal phases for the desired fundamental signals at the end of each path. Therefore, they are aligned to add up coherently. On the other hand, the undesired distortion components tend to cancel out after addition, except for the harmonics at  $(PN+1)\omega$ , where P=0,1,2,... In the case of two input tones at  $\omega_1$  and  $\omega_2$ , the nonlinear block not only generates harmonics of the two tones but also intermodulation products at  $m\omega_1 + n\omega_2$ , where m and n are negative and positive integers. Cancellation of the intermodulation products follows the same principle as canceling the harmonics. Once again, the intermodulations at m+n=PN+1,

where P = 0, 1, 2, ..., are not canceled by this scheme. This means that whatever the values of N and  $\varphi$  are, some intermodulation components are never canceled.

One of the challenges of the architecture in Fig. 2.1 is the phase shifter design after the nonlinear circuit, which is implemented in the analog domain, contrary to the first set of phase shifters, which is implemented in the digital domain [8]. Harmonics at the output of the nonlinear circuit require de-rotation by a constant phase over a wide band. The architecture in [6] implements the second set of phase shifters using mixers of identical LO frequencies with different phases, as shown in Fig. 2.2. These phases are generated by digital circuits (dividers and buffers) that consume 69% of the total chip power [6]. Also, mismatches between these phases affect the magnitude of canceled harmonics and intermodulations. Another point is that the poly-phase circuit in Fig. 2.2 cannot be used if the PA is implemented after the mixer because the de-rotation cannot be done before the nonlinear circuit. Therefore, this topology is restricted to using the PU architecture that combines the functionality of the PA and the upconversion mixer.

## 2.3 Proposed system

The proposed multi-phase multi-path circuit is shown in Fig. 2.3. The main idea is to implement both phase shifts (rotation and de-rotation) in the digital domain before the nonlinear block. The digitally rotated data is driven to multiple DACs to generate the multi-phase baseband signals. Moving the de-rotation phases to the digital domain requires proper choice of  $\underline{\varphi} = [\varphi_1, \varphi_2, ..., \varphi_N]$  to cancel the undesired distortion products. In such a way, the second set of analog phase shifters in [6] is avoided. As noted above, this would save 69% of the total power consumption in the implementation of [6]. Also, having full digital control on the shifters in the baseband leads to high accuracy in generating the phases. Hence, more immunity

Figure 2.1: Poly-phase multi-path technique proposed in [6].

Figure 2.2: Poly multi-path technique implemented with mixers that operate as wide-band phase shifters.

$\label{eq:Figure 2.3: Proposed multi-phase multi-path technique.}$

to mismatches is achieved. Moreover, the proposed technique can be applied to conventional transmitter architectures, where the mixer is followed by a current-ouput PA that is split into multi-PAs in the RF section, as will be shown in Section V. It is worth mentioning that the proposed technique is more suitable to be used with communication systems that use complex-valued constellations, such as QPSK, that have a double sideband spectrum. In contrast, the reported technique in [6] can be used for single sideband transmission because it is capable of canceling one of the LO sidebands. The following subsections show how to choose N and  $\underline{\varphi}$  in the proposed technique to cancel the harmonics and intermodulations.

Consider a sinusoidal baseband signal,  $x(t) = A\cos(\omega t)$ , applied to the proposed system in Fig. 2.3. Assume the nonlinear block has a memoryless characteristic given by  $w(t) = \sum_{k=0,1,2..} a_k u^k(t)$  where u(t) and w(t) are the input and output, respectively, and  $a_k$  is constant for all values of k. The signal,  $s_j(t)$ , at the end of path j, where j = 1, 2, 3, ...N, is given by

$$s_{j}(t) = \sum_{k} a_{k} A^{k} [\cos^{k}(\omega t + \varphi_{j}) + \cos^{k}(\omega t - \varphi_{j})]$$

$$= \sum_{k} b_{k} [\cos(k\omega t + k\varphi_{j}) + \cos(k\omega t - k\varphi_{j})]$$

$$= \sum_{k} 2b_{k} \cos(k\omega t) \cos(k\varphi_{j}). \tag{2.1}$$

where  $b_k$  depends on  $a_k$  and A for all values of k. After adding the signals at the end of each path, the output signal y(t) will be given as

$$y(t) = \sum_{k} \left[ 2b_k \cos(k\omega t) \sum_{j} \cos(k\varphi_j) \right]. \tag{2.2}$$

Figure 2.4: Output spectrum of the proposed multi-phase scheme for a single-tone input. (a) N=2 and  $\varphi=[22.5^o,112.5^o]$ . (b) N=2 and  $\varphi=[24^o,84^o]$ .  $a_k=[0,1,0.2,-1.6242,0.5,2.638,0.7,-4.284,0.8,6.954]$ .

From the above equation, each harmonic is multiplied by a factor  $\gamma_k = 2\sum_j \cos(k\varphi_j)$ . Canceling the kth harmonic requires choosing  $\underline{\varphi}$  such that  $\gamma_k$  is equal to zero except at k = 1, which corresponds to the desired signal component. For example, choosing N = 2 and  $\underline{\varphi} = [22.5^o, 112.5^o]$  results in  $\gamma_k = 0$  for k = 2, 4, 6. Thus, the 2nd, 4th, and 6th harmonics are canceled. Also, N = 2 and  $\underline{\varphi} = [24^o, 84^o]$  cancel the 3rd, 5th, 9th harmonics, and any harmonic  $k = 3^r 5^t$  for all non-negative r and t. To verify the previous analysis, simulations are done for the proposed system when a single-tone input is applied using ideal phase shifters and nonlinear circuits. The spectrum of the system output, Y(k), is plotted in Fig. 2.4, which illustrates the harmonic cancellation.

## 2.3.2 Two-tone test

In order to test the proposed architecture performance on intermodulation products, a two-tone input signal,  $x(t) = A_1 \cos(\omega_1 t) + A_1 \cos(\omega_2 t)$ , is applied. The signal at the end of path j is given by

$$s_{j}(t) = \sum_{k} 2[b_{k}\cos(k\omega_{1}t) + c_{k}\cos(k\omega_{2}t)]\cos(k\varphi_{j})$$

$$+ \sum_{m,n} 2d_{m,n}\cos[(m\omega_{1} + n\omega_{2})t]\cos[(m+n)\varphi_{j}].$$

(2.3)

where  $b_k$ ,  $c_k$ , and  $d_{m,n}$  depend on  $a_k$ ,  $A_1$ , and  $A_2$  for all non-negative integers k and positive or negative integers values of m and n. From the above equation, the output of the nonlinear circuit not only includes the harmonics of the input tones, but also contains the intermodulation products at  $\omega = m\omega_1 + n\omega_2$ . The system output signal y(t) is given by

$$y(t) = \sum_{k} \left\{ 2[b_k \cos(k\omega_1 t) + c_k \cos(k\omega_2 t)] \sum_{j} \cos(k\varphi_j) \right\}$$

$$+ \sum_{m,n} \left\{ 2d_{m,n} \cos[(m\omega_1 + n\omega_2)t] \sum_{j} \cos[(m+n)\varphi_j] \right\}$$

$$= \sum_{k} [b_k \cos(k\omega_1 t) + c_k \cos(k\omega_2 t)] \gamma_k$$

$$+ \sum_{m,n} d_{m,n} \cos[(m\omega_1 + n\omega_2)t] \gamma_{m,n}. \qquad (2.4)$$

Eqn. (2.4) shows that the same factor  $\gamma_k$  is multiplied by the intermodulation terms by replacing k with m+n. Therefore, if N and  $\underline{\varphi}$  are chosen to cancel the kth harmonic, the intermodulation products at  $m\omega_1 + n\omega_2$  with m+n=k are also canceled. Fig. 2.5 shows the simulation results of a two-tone test. Fully differential operation for the circuit model employed in the implementation is assumed to cancel the even nonlinearities. Fig. 2.5(a) shows the output spectrum without distortion cancella-

Figure 2.5: Output spectrum for a two-tone input. (a) Without distortion cancellation. (b) Proposed multi-phase with N=2 and  $\varphi=[24^o,84^o]$ .  $a_k=[0,1,0,-1.6242,0,2.638,0,-4.284,0,6.954]$ .

tion. Choosing N=2 and  $\underline{\varphi}=[24^o,84^o]$  cancels the harmonics and intermodulation products of k=m+n=3, 5, and 9 as shown in Fig. 2.5(b). Unfortunately, the intermodulation products at  $\omega=m\omega_1+n\omega_2$  with m+n=1 are not canceled. Specially important in RF applications, are the third-order intermodulation products  $(2\omega_1-\omega_2)$  and  $(2\omega_2-\omega_1)$ . Cancellation of this group would also cancel the fundamental desired signal at k=1, as explained in [6].

Note that the fundamental components at the output of each path in the proposed system do not add up in phase, which is an advantage in [6]. This attenuates the fundamental signal, which is multiplied by a factor  $\gamma_1$  according to (2.2) and (2.4), and degrades the amount of power that can be delivered to the output. To quantify this, in the above mentioned example where N=2 and  $\underline{\varphi}=[24^o,84^o]$ , the output fundamental signal is degraded by 5.8 dB. Fortunately, this degradation can be minimized by using another set of phase shifts,  $\underline{\varphi}=[12^o,48^o]$ , achieving the same performance. A loss of only 1.68 dB results in this case, which is acceptable and can be compensated by spending some extra transmission power.

Figure 2.6: Proposed multi-phase multi-path system with gain and phase mismatches included.

### 2.4 Mismatches

In the previous section, the analysis was based on ideal phase shifters and identical nonlinear blocks. Gain and phase mismatches certainly affect the magnitude of the canceled harmonics and intermodulation. In order to quantify the impact of mismatches, a phase error vector  $\underline{\alpha} = [\alpha_1, \alpha_2, \alpha_3, ..., \alpha_{2N}]$  and a gain error vector  $\underline{\beta} = [\beta_1, \beta_2, \beta_3, ..., \beta_{2N}]$  are introduced, as depicted in Fig. 2.6. As an example, we study the effect of mismatches on the proposed system when configured to cancel the third harmonic for a single-tone input  $x(t) = A\cos(\omega t)$ . The system uses one path  $(N = 1)^{\dagger}$  and  $\underline{\varphi} = [30^o]$ , which results in  $\gamma_3 = 0$  in the matched case. Considering

$<sup>^{\</sup>dagger}N=1$  means two subpaths with  $\varphi_1$  and  $-\varphi_1$  in the proposed technique, as indicated in Fig. 2.3

mismatches,  $\underline{\alpha} = [\alpha_1, \alpha_2]$  and  $\underline{\beta} = [\beta_1, \beta_2]$ , the output of the proposed system y(t) is given by

$$y(t) = \sum_{k} b_{k} \left[ \left( 1 + \frac{\beta_{1}}{a_{1}} \right) \cos(k\omega t + k\varphi + k\alpha_{1}) + \left( 1 + \frac{\beta_{2}}{a_{1}} \right) \cos(k\omega t - k\varphi + k\alpha_{2}) \right]$$

$$= \sum_{k} b_{k} \left[ I_{k} \cos(k\omega t) - Q_{k} \sin(k\omega t) \right]$$

(2.5)

where

$$I_{k} = \left(1 + \frac{\beta_{1}}{a_{1}}\right) \cos(k\varphi + k\alpha_{1})$$

$$+ \left(1 + \frac{\beta_{2}}{a_{1}}\right) \cos(-k\varphi + k\alpha_{2})$$

$$Q_{k} = \left(1 + \frac{\beta_{1}}{a_{1}}\right) \sin(k\varphi + k\alpha_{1})$$

$$+ \left(1 + \frac{\beta_{2}}{a_{1}}\right) \sin(-k\varphi + k\alpha_{2}).$$

(2.6)

In this case, the kth harmonic distortion  $HD_k$  is given by

$$HD_k = \frac{b_k^2 (I_k^2 + Q_k^2)}{b_1^2 (I_1^2 + Q_1^2)}. (2.8)$$

To quantify the effectiveness of the proposed multi-phase multi-path technique in the presence of mismatches, the improvement factor  $\zeta_k$  is defined as the ratio between the kth harmonic distortion when no multi-phase multi-path scheme is applied (only one nonlinear block is used) to the kth order harmonic distortion of the proposed multi-phase system output with mismatches, i.e.,

$$\zeta_k = \frac{b_k^2 / b_1^2}{H D_k}. (2.9)$$

Figure 2.7: Output spectrum for a single-tone input. (a) Without distortion cancellation. (b) Proposed multi-phase scheme with gain and phase mismatches. (c) Proposed multi-phase scheme without mismatches

$$\zeta_{3} = \frac{b_{3}^{2}/b_{1}^{2}}{HD_{3}} = \frac{I_{1}^{2} + Q_{1}^{2}}{I_{3}^{2} + Q_{3}^{2}}

= \frac{\left(1 + \frac{\beta_{1}}{a_{1}}\right)^{2} + \left(1 + \frac{\beta_{2}}{a_{1}}\right)^{2} + 2\left(1 + \frac{\beta_{1}}{a_{1}}\right)\left(1 + \frac{\beta_{2}}{a_{1}}\right)\cos(2\varphi + \alpha_{1} - \alpha_{2})}{\left(1 + \frac{\beta_{1}}{a_{1}}\right)^{2} + \left(1 + \frac{\beta_{2}}{a_{1}}\right)^{2} + 2\left(1 + \frac{\beta_{1}}{a_{1}}\right)\left(1 + \frac{\beta_{2}}{a_{1}}\right)\cos[6\varphi + 3(\alpha_{1} - \alpha_{2})]} (2.10)$$

In our example  $(N=1 \text{ and } \underline{\varphi}=[30^o])$ ,  $\zeta_3$  is given by (10) at the top of the next page. Simulations are done for the proposed system in Fig. 2.6. Fully differential operation is used to cancel the even harmonics. The standard deviation values of the phase and gain errors are chosen as in [9] ( $\sigma_{\alpha} = 0.017$  and  $\sigma_{\beta} = 0.03$ ). Fig. 2.7 shows the average system output spectrum over a thousand runs. Here,  $\gamma_3$  is shown to be 36.5 dB, which matches well with the analytical value derived in (2.10). The improvement factor can be generalized for any N and  $\underline{\varphi}$  chosen to cancel a group of harmonics as follows:

$$\zeta_k(N,\underline{\varphi}) = \frac{B}{C} \tag{2.11}$$

where B and C are given by (2.12) and (2.13) at the top of the next page, respectively.

All the previous analyses and results are valid for the intermodulation products

Figure 2.8: Conventional transmitter architecture using current-output multi-PAs with the proposed digitally generated multi-phase technique.

at  $\omega = m\omega_1 + n\omega_2$  by replacing k with m + n.

# 2.5 Applications

One of the limitations of the poly-phase multi-path technique reported in [6] is that it can only be used with the current-output PU architecture. Applying the technique on conventional transmitter architectures where the mixer is followed by the PA will not cancel the nonlinearities. This is because the nonlinearity block (PA) needs to be inserted between the phase shifters and the mixers for the poly-phase technique to work, as in Fig. 2.2. On the other hand, the proposed multi-phase

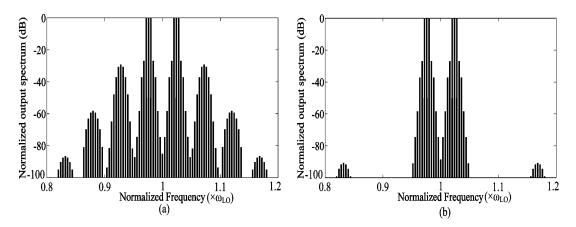

Figure 2.9: Current-output power upconverter model with the proposed digitally generated multi-phase multi-path technique.

technique can be applied to a current-output PA architecture that is split into multi-PAs, as shown in Figs. 2.8 and 2.9. However, it does not cancel the signal image and LO harmonics, which is an advantage in [6]. The proposed technique is capable of canceling the unwanted signals that fall in the LO sidebands, i.e., the signals at  $\omega_{LO} + k\omega_B$ , where  $\omega_{LO}$  is the LO frequency and  $\omega_B$  is the baseband signal frequency, are canceled for  $k \neq 1$  depending on N and  $\underline{\varphi}$ . This is clear in the system shown in Fig. 2.10 that uses  $\phi_1 = 30^\circ$  to cancel the 3rd order nonlinearity.

As an example, a multi-tone signal is applied to the systems shown in Fig. 2.8 and

$$B = \sum_{i=1}^{2N} \left( 1 + \frac{\beta_i}{a_1} \right)^2 + 2 \sum_{i=1}^{N} \left( 1 + \frac{\beta_{2i-1}}{a_1} \right) \left( 1 + \frac{\beta_{2i}}{a_1} \right) \cos(2\varphi_i + \alpha_{2i-1} - \alpha_{2i})$$

$$+ 2 \sum_{i=1}^{N-1} \sum_{j=i+1}^{N} \left[ \left( 1 + \frac{\beta_{2i-1}}{a_1} \right) \left( 1 + \frac{\beta_{2j-1}}{a_1} \right) \cos(\varphi_i - \varphi_j + \alpha_{2i-1} - \alpha_{2j-1}) \right]$$

$$+ \left( 1 + \frac{\beta_{2i}}{a_1} \right) \left( 1 + \frac{\beta_{2j}}{a_1} \right) \cos(-\varphi_i + \varphi_j + \alpha_{2i-1} - \alpha_{2j})$$

$$+ \left( 1 + \frac{\beta_{2i-1}}{a_1} \right) \left( 1 + \frac{\beta_{2j-1}}{a_1} \right) \cos(-\varphi_i - \varphi_j + \alpha_{2i-1} - \alpha_{2j})$$

$$+ \left( 1 + \frac{\beta_{2i}}{a_1} \right) \left( 1 + \frac{\beta_{2j-1}}{a_1} \right) \cos(-\varphi_i - \varphi_j + \alpha_{2i-1} - \alpha_{2j-1}) \right]$$

$$(2.12)$$

$$C = \sum_{i=1}^{2N} \left( 1 + \frac{\beta_i}{a_1} \right)^2 + 2 \sum_{i=1}^{N} \left( 1 + \frac{\beta_{2i-1}}{a_1} \right) \left( 1 + \frac{\beta_{2i}}{a_1} \right) \cos[k(2\varphi_i + \alpha_{2i-1} - \alpha_{2i})]$$

$$+ 2 \sum_{i=1}^{N-1} \sum_{j=i+1}^{N} \left[ \left( 1 + \frac{\beta_{2i-1}}{a_1} \right) \left( 1 + \frac{\beta_{2j-1}}{a_1} \right) \cos[k(\varphi_i - \varphi_j + \alpha_{2i-1} - \alpha_{2j-1})] \right]$$

$$+ \left( 1 + \frac{\beta_{2i}}{a_1} \right) \left( 1 + \frac{\beta_{2j}}{a_1} \right) \cos[k(-\varphi_i + \varphi_j + \alpha_{2i} - \alpha_{2j})]$$

$$+ \left( 1 + \frac{\beta_{2i-1}}{a_1} \right) \left( 1 + \frac{\beta_{2j-1}}{a_1} \right) \cos[k(-\varphi_i - \varphi_j + \alpha_{2i-1} - \alpha_{2j})]$$

$$+ \left( 1 + \frac{\beta_{2i}}{a_1} \right) \left( 1 + \frac{\beta_{2j-1}}{a_1} \right) \cos[k(-\varphi_i - \varphi_j + \alpha_{2i-1} - \alpha_{2j-1})] \right]$$

$$(2.13)$$

Fig. 2.9. Saleh's nonlinear AM-AM conversion model [10],  $w(t) = au(t)/[1 + bu^2(t)]$ , is used, where u(t) and w(t) are the input and output of the nonlinear block, respectively (a = 1.0536 and b = 0.0860). The maximum input signal amplitude is adjusted to be at the 1-dB compression point of the model.

Figure 2.10: Cancellation of the 3rd order nonlinearity in the signal side bands

Figure 2.11: Comparison between the normalized output spectrum. (a) Without distortion cancellation. (b) With the proposed multi-phase technique.

Table 2.1: Comparison between the poly-phase technique in [6] and the proposed technique

| Aspects of comparison                                  | [6] | Proposed |

|--------------------------------------------------------|-----|----------|

| Signal Harmonic Rejection                              | Yes | Yes      |

| Need Analog Phase Shifters                             | Yes | No       |

| Flexibility to different current-ouput PA Architecture | No  | Yes      |

| Fundamental Signal Alignment From Each Path            | Yes | No       |

| Third-Order Intermodulation Cancellation               | No  | No       |

| LO Harmonic Cancellation                               | Yes | No       |

| Signal Image Rejection                                 | Yes | No       |

Fig. 2.11 shows a comparison between the output spectrum without distortion cancellation and when the proposed technique is applied for N=2 and  $\underline{\varphi}=[12^o,48^o]$ . It is clear that the proposed technique can reduce the distortion that appears on the signal sidebands. This reduction significantly relaxes the requirements on the high-quality band-pass filter used in the transmitter output to remove the far LO harmonics. Therefore, the tunability of such filters will be easier, making the proposed multi-phase technique attractive to multi-standard transmitter architectures. Table 2.1 summarizes the trade-offs between the poly-phase technique in [6] and the proposed multi-phase multi-path technique with digital phase shifters.

# 3. MULTIPLE FEEDBACK LOW POWER INDUCTORLESS WIDEBAND CMOS LNA\*

A wideband low noise amplifier (LNA), which is a key block in the design of broadband receivers for multi-band wireless communication standards, is presented in this work. The LNA is a fully differential common-gate (CG) structure. It uses multiple feedback paths which add degrees of freedom in the choice of the LNA transconductance to reduce the noise figure (NF) and increase the amplification. The proposed LNA avoids the use of bulky inductors that leads to area and cost saving. A prototype is implemented in IBM 90 nm CMOS technology. It covers the frequency range of 100 MHz to 1.77 GHz. The core consumes 2.8 mW from a 2 V supply occupying an area of 0.03  $mm^2$ . Measurements show a gain of 23 dB with a 3-dB bandwidth of 1.76 GHz. The minimum NF is 1.85 dB while the average NF is 2 dB across the whole band. The LNA achieves a return loss greater than 10 dB across the entire band and a third-order input intercept point  $IIP_3$  of -2.85 dBm at the maximum gain frequency.

#### 3.1 Introduction

Multi-band multi-standard concepts have gained considerable interest in modern wireless communications systems [11, 12, 13, 14]. To support a wide set of communication standards and to accommodate different applications in a single device, broadband transceivers are essential and inevitably in demand. A wideband RF receiver front-end architecture constructed by one single path [15] provides lower cost, area,

<sup>\*</sup>Part of this chapter is reprinted with permission from "A 2.8-mW Sub-2-dB Noise-Figure Inductorless Wideband CMOS LNA Employing Multiple Feedback," by E. A. Sobhy, A. A. Helmy, S. Hoyos, K. Entesari, and E. Sanchez-Sinencio , Dec. 2011. *IEEE Trans. Microw. Theory Tech.*, vol. 59, no. 12, pp. 3154-3161.

and power consumption compared to the parallel-path architectures [16, 17]. Single path wideband concept can also accommodate emerging standards for cognitive radio applications, resulting in efficiency improvement in utilizing scarce spectrum resources.

One of the major challenges in wideband receivers is the design of a wide-band low-noise amplifier (LNA) that is shared among different standards. As the first block in the receiver chain, such an LNA should achieve good impedance matching, high and flat gain, and low noise figure (NF) across a wide frequency band. In addition, good linearity and low area and power consumption LNAs are required for high performance and low cost radios.

Recently, many wideband LNAs in CMOS technology have been reported, including distributed amplifiers [18] and resistive shunt feedback amplifiers [19, 20]. The former offers superior bandwidth in terms of high power consumption, large area, and deterioration of noise performance, which limits its widespread applications. The latter provides good broadband matching, noise, and gain, but it is hampered by greater power consumption, which makes them unattractive for low-power applications. Other implementations are inductor-based, such as L-degenerated broadband LNAs [21]. They have good performance in terms of NF and power consumption. However, the use of area consuming on-chip bulky inductors makes them unattractive for use in upcoming wireless low cost transceivers.

One of the wideband LNA topologies that has been widely investigated is the common-gate (CG) LNA. CG LNA is attractive compared to other topologies as it features wideband input impedance matching. Also, it offers good linearity, stability, and low power consumption. However, its main drawback is the relatively high NF [22]. This is due to the input matching condition, which restricts a certain value of transconductance to be used that leads to low gain and hence, high NF. Noise reduc-

tion techniques are used to overcome the disadvantage of the CG LNA configuration [22, 23, 24, 25, 26, 27]. Gain boosting scheme using negative feedback employing capacitive cross-coupling [22, 23], dual negative feedback [26], and positive-negative feedback [27] are applied to break the tradeoff between the input matching condition and the NF, which lead to simultaneous reduction in noise and power dissipation. However, reducing the noise figure below 2 dB is still challenging in CG LNAs.

In this work, a wideband differential CG LNA employing multiple feedback is proposed. It uses three feedbacks to add more flexibility in determining the  $g_m$  of the impedance matching device. This breaks the lower bound of the noise performance and leads to reduction in the noise figure and increase in the gain. To the best of the authors' knowledge, the proposed LNA achieves the lowest NF and highest gain among CG LNAs reported in the literature while consuming low power. It also avoids the use of bulky inductors resulting in considerable area and cost savings. The presented LNA covers frequency bands for Digital Video Broadcasting (DVB) at 450-850 MHz, Global System for Mobile communications (GSM) at 900 MHz, and Global Positioning System (GPS) at 1.2 and 1.5 GHz, providing a practical solution for multi-standard applications. The Chapter is organized as follows. In Section 2, existing noise reduction techniques for CG LNA using negative and positive feedbacks are discussed. Section 3 covers the proposed CG LNA, showing detailed analysis for the major LNA parameters. Finally, in Section 4, circuit implementation is presented along with simulation results and measurements.

## 3.2 Background

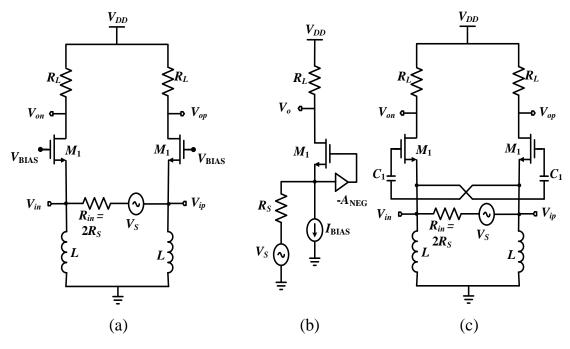

Fig. 3.1 (a) shows the differential configuration of the conventional CGLNA. In this circuit, the differential voltage gain,  $A_v = \frac{Vop-Von}{Vip-Vin}$ , and the differential input

Figure 3.1: Conventional differential CGLNA and low noise feedback techniques

impedance,  $R_{in}$ , are given by

$$A_v = g_{m1} R_L. \tag{3.1}$$

$$R_{in} = 2/g_{m1}. (3.2)$$

where  $g_{m1}$  is the transconductance of transistor  $M_1$ . Assuming perfect matching condition  $(R_{in} = 2R_S = 100\Omega)$ , the noise factor, F, is given by

$$F = 1 + \frac{\gamma}{\alpha} + \frac{4R_S}{R_L}.\tag{3.3}$$

where  $\gamma$  is the excess channel thermal noise coefficient, and  $\alpha$  is the ratio between  $g_{m1}$  and the zero-bias drain conductance,  $g_{do1}$ . The last term in (3.3) represents the noise contribution due to the load,  $R_L$ . Due to the power matching constraint, the CGLNA suffers a relatively high noise figure, NF. Noise reduction techniques are used to improve the NF of the CGLNA. In the following subsections, these techniques are briefly presented.

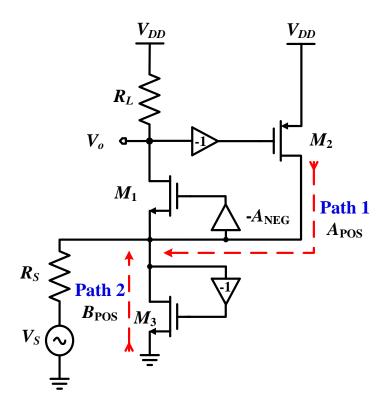

### 3.2.1 Negative feedback CGLNA employing capacitive cross-coupling

The idea to improve the noise performance of the CGLNA is based on introducing a decoupling mechanism between the input power matching condition and the NF. This is achieved by improving the effective transconductance and enhancing the gain. The single-ended model of the transconductance boosting structure is shown in Fig. 3.1 (b). The structure uses an inverting gain  $A_{NEG}$  that is inserted in the feedback between the gate and source terminals of  $M_1$ . The effective  $g_{m1}$  is boosted to  $g_{m1}(1 + A_{NEG})$  with input impedance matching of  $1/[g_{m1}(1 + A_{NEG})] = R_S =$

$50\Omega$ . This means smaller bias current, less channel noise from  $M_1$ , and consequently smaller noise contribution and power consumption. The noise factor, F, is then given by

$$F = 1 + \frac{\gamma}{(1 + A_{NEG})\alpha} + \frac{4R_S}{R_L}.$$

(3.4)

One possible way to implement the inverting gain,  $A_{NEG}$ , is to use cross-coupling capacitors,  $C_1$  as shown in the differential CGLNA topology in Fig. 3.1 (c) [22].  $A_{NEG}$  is approximately given by the capacitors ratio,  $(C_1 - C_{gs1})/(C_1 + C_{gs1})$ , where  $C_{gs1}$  is the gate-source capacitance of  $M_1$ . For  $C_1 >> C_{gs1}$ ,  $A_{NEG}$  is almost unity, which reduces  $A_v$ ,  $R_{in}$ , and F to the following

$$A_v = 2g_{m1}R_L. (3.5)$$

$$R_{in} = 2R_S = 1/q_{m1}. (3.6)$$

$$F = 1 + \frac{\gamma}{2\alpha} + \frac{4R_S}{R_I}.\tag{3.7}$$

Comparing to the conventional CGLNA, F is reduced and the effective transconductance is increased with reduction in power consumption.

#### 3.2.2 Positive-negative feedback CGLNA

The negative feedback CGLNA reduces the noise figure by the use of capacitive divider. Meanwhile, its transconductance,  $g_{m1}$  is restricted to 10 mS to satisfy the input power matching condition. Thus, this solution suffers from low gain. To alleviate the restriction of low  $g_{m1}$ , a positive feedback along with the negative

tive feedback is used in [27]. To increase the gain, the idea is to create a positive current feedback path through  $M_2$  as shown in the single-ended model in Fig. 3.1 (d). This feedback path increases the input impedance of the LNA to be equal to  $1/[g_{m1}(1+A_{NEG})(1-A_{POS})]$ , where  $A_{POS}=g_{m2}R_L$  is the positive feedback gain which varies from 0 to 1 for stability. In this way,  $g_{m1}$  can be chosen arbitrarily to values higher than 10 mS without restricting the input matching condition. For example, if  $A_{POS}$  is designed to be 0.5 and  $A_{NEG}=1$ , then  $g_{m1}=20$  mS for the 50 $\Omega$  input matching to be satisfied. Thus, the gain increases.

The fully differential positive-negative CGLNA in [27] is shown in Fig. 3.1 (e). Since the positive feedback loop provides degree of freedom in a way that the impedance matching does not fix the bias current, the current will be a design variable to improve the noise performance. Considering the thermal channel noise, under input matching condition, the noise factor is given by:

$$F = 1 + \frac{(1 - A_{POS})\gamma}{(1 + A_{NEG})\alpha} + g_{m2}R_S\frac{\gamma}{\alpha} + \frac{R_S}{R_L}(2 - A_{POS})^2.$$

(3.8)

For  $A_{NEG} = 1$  and  $A_{POS} = 0.5$ ,  $A_v$ ,  $R_{in}$ , and F are reduced to the following:

$$A_v = 2g_{m1}R_L. (3.9)$$

$$R_{in} = 2R_S = 2/g_{m1}. (3.10)$$

$$F = 1 + \frac{\gamma}{4\alpha} + g_{m2}R_S \frac{\gamma}{\alpha} + \frac{9R_S}{4R_L}.$$

(3.11)

The third term in (3.11) represents the noise due to  $M_2$ . The value of  $g_{m2}$  is chosen

to be small which translates to small noise contribution. Therefore, the positivenegative feedback CGLNA can achieve a lower NF than the negative feedback and conventional CGLNAs with higher gain. However, power consumption increases compared to negative feedback CGLNA.

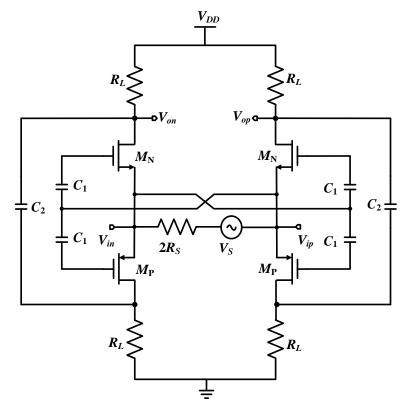

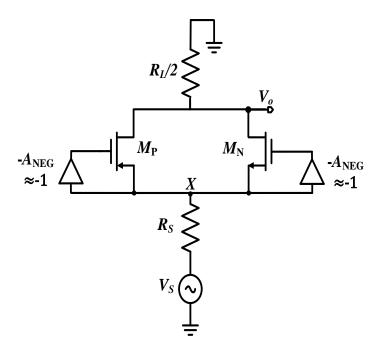

## 3.3 Proposed CGLNA

The idea of the proposed CGLNA is based on adding more degree of freedom on the impedance matching condition of the positive-negative feedback CGLNA in Fig. 3.1 (e). In this way, there will be more flexibility in choosing the optimum value of the LNA transconductance that achieves minimum noise figure. Fig. 3.2 shows the proposed CGLNA. The biasing inductors are replaced by current sources  $(M_3s)$ , that are capacitively cross-coupled using  $C_2$  ( $C_2 >> C_{gs3}$ ) [23]. As shown in the single-ended model in Fig. 3.3, the capacitively coupled transistor,  $M_3$ , creates another positive current feedback path beside the one created by  $M_2$ . Therefore, the output current of the LNA becomes the sum of the current provided by the source and those injected through  $M_2$  and  $M_3$ , making the current gain larger than unity.

## 3.3.1 Input impedance

The two current (shunt) positive feedback paths have the effect of increasing the CGLNA input impedance. Referring to Fig. 3.2, the input impedance is given by:

$$R_{in} = \frac{2}{g_{m1} (1 + A_{NEG}) (1 - A_{POS} - B_{POS})}$$

$$= \frac{2}{2g_{m1} (1 - A_{POS} - B_{POS})}$$

(3.12)

Figure 3.2: Schematic of the proposed CGLNA (biasing circuit not shown).

where  $A_{POS} = g_{m2}R_L$ ,  $B_{POS} = g_{m3}/2g_{m1}$ , and  $A_{Neg} = 1$ . Thus, the input matching condition is given by

$$2g_{m1}R_S(1 - A_{POS} - B_{POS}) = 1. (3.13)$$

From (3.13), two degrees of freedom,  $A_{POS}$  and  $B_{POS}$ , exist that allow arbitrary choice of  $g_{m1}$  achieving high gain and optimum minimum noise figure, as will be seen in the noise analysis.

The condition of stability is based on the approach of the return ratio, RR [25]. This approach is used to study the amplifier stability in the presence of multiple feedback loops and to model bidirectional paths between input and output. For the

Figure 3.3: Simplified single-ended CGLNA model.

Figure 3.4: Schematic of the proposed CGLNA showing noise sources.

proposed CGLNA, the RR has the following expression:

$$RR = \frac{-2g_{m1}R_S}{1 + 2g_{m1}R_S}(A_{POS} + B_{POS}). \tag{3.14}$$

The proposed CGLNA is stable if -1 < RR < 0 and this can be guaranteed by setting  $(A_{POS} + B_{POS}) < 1$  with a safe margin to take into account any process variation.

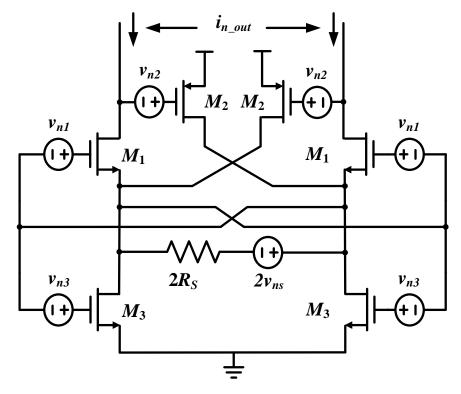

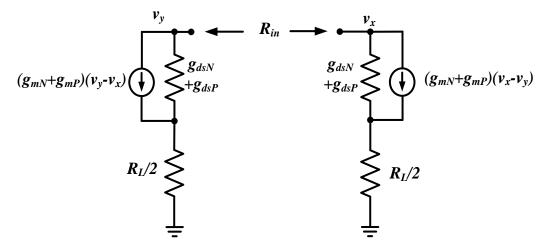

#### 3.3.3 Noise analysis

Fig. 3.4 shows a simplified model for the noise sources of the proposed CGLNA. The circuit noise performance is analyzed and its NF is computed assuming that the dominant noise sources are due to the thermal noise of the transistors and the load. The coupling capacitors,  $C_1$  and  $C_2$ , in Fig. 3.2 are replaced with short circuits

since they are much larger than the gate capacitance of the input transistors,  $M_1$ , and  $M_3$ , respectively. In this case, the noise due to the source resistance,  $v_{ns}$ , the thermal noise due to  $M_2$ ,  $v_{n2}$ , and that due to  $M_3$ ,  $v_{n3}$ , as shown in Fig. 3.2, create two equal and opposite noise currents in the output branches with magnitudes of  $g_{m1}v_{ns}/2$ ,  $g_{m1}g_{m2}R_sv_{n2}/2$ , and  $g_{m1}g_{m3}R_sv_{n3}/2$ , respectively. While the thermal noise due to  $M_1$ ,  $v_{n1}$ , creates two unequal output noise currents with differential value of  $g_{m1}(g_{m1}R_s-1)v_{n1}$ . The output differential current due to each noise source is given by:

$$\overline{i_{ns-out}^{2}} = 4kTR_{s}g_{m1}^{2}\Delta f.$$

$$\overline{i_{n1-out}^{2}} = 4kT\frac{\gamma_{1}}{\alpha}g_{m1}(g_{m1}R_{s}-1)^{2}\Delta f.$$

$$\overline{i_{n2-out}^{2}} = 4kT\frac{\gamma_{2}}{\alpha}g_{m2}(g_{m1}R_{s})^{2}\Delta f.$$

$$\overline{i_{n3-out}^{2}} = 4kT\frac{\gamma_{3}}{\alpha}g_{m3}(g_{m1}R_{s})^{2}\Delta f.$$

(3.15)

Assuming  $\gamma_1 = \gamma_2 = \gamma_3 = \gamma$ , the noise factor, F, is given by:

$$F = \frac{\overline{i_{ntotal-out}^2}}{\overline{i_{ns-out}^2}} = 1 + \frac{\gamma}{\alpha} \frac{(g_{m1}R_s - 1)^2}{g_{m1}R_s} + \frac{\gamma}{\alpha} g_{m2}R_s + \frac{\gamma}{\alpha} g_{m3}R_s + \frac{R_s}{R_L} \left(1 + \frac{1}{2g_{m1}R_s}\right)^2.$$

(3.16)

Note that the last term accounts for the noise contribution due to the load,  $R_L$ . Increasing the value of  $R_L$  relative to  $R_s$  reduces the load noise contribution to the overall noise figure. Under the input power matching condition, F reduces to

$$F = 1 + \frac{\gamma}{\alpha} \frac{(\eta - 1)^2}{\eta} + 2\frac{\gamma}{\alpha} \left(1 - A_{POS}\right) \eta$$

$$-\frac{\gamma}{\alpha} \left(1 - \frac{R_s}{R_L} A_{POS}\right) + \frac{R_s}{R_L} \left(1 + \frac{1}{2\eta}\right)^2. \tag{3.17}$$

Table 3.1: Comparison between different CGLNA configurations together with the proposed one

|                      | Convent.                                       | Negative                                        | Positive-Negative                                                | This work                                                         |

|----------------------|------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|

|                      | CGLNA                                          | feedback                                        | feedback CGLNA                                                   |                                                                   |

|                      |                                                | CGLNA                                           |                                                                  |                                                                   |

| Differential         | $\frac{2}{g_{m1}}$                             | $\frac{1}{g_{m1}}$                              | $\frac{1}{g_{m1}(1-A_{POS})}$                                    | $\frac{1}{g_{m1}(1-A_{POS})-g_{m3}/2}$                            |

| input                | gm1                                            | $gm_1$                                          | 9m1(1 11POS)                                                     | gm1(1 11POS) gm3/2                                                |

| impedance,           |                                                |                                                 |                                                                  |                                                                   |

| $R_{in}$             |                                                |                                                 |                                                                  |                                                                   |

| $g_{m1}$ for the in- | $\frac{1}{R_S}$                                | $\frac{1}{2R_S}$                                | $\frac{1}{2R_S(1-A_{POS})}$                                      | $\frac{1+g_{m3}R_S}{2R_S(1-A_{POS})}$                             |

| put matching         | 105                                            | 2103                                            | 2103(1 111 03)                                                   | 2103(1 11703)                                                     |

| $A_v$ at the in-     | $\frac{R_L}{R_S}$                              | $\frac{R_L}{R_S}$                               | $\frac{R_L}{R_S(1-A_{POS})}$                                     | $\frac{R_L(1+g_{m3}R_S)}{R_S(1-A_{POS})}$                         |

| put matching         |                                                | -                                               | 105(1 111905)                                                    | nts(1 npos)                                                       |

| NF at the in-        | $1 + \frac{\gamma}{\alpha} + \frac{4R_S}{R_L}$ | $1 + \frac{\gamma}{2\alpha} + \frac{4R_S}{R_L}$ | 1 +                                                              | 1 +                                                               |

| put matching         |                                                |                                                 | $\left(0.25 + \frac{0.5R_s}{R_L}\right) \frac{\gamma}{\alpha} +$ | $\left(0.06 + \frac{0.35R_s}{R_L}\right) \frac{\gamma}{\alpha} +$ |

|                      |                                                |                                                 | $\frac{\hat{9}R_S}{4R_L}$                                        | $3.11R_{\rm s}$                                                   |

| Percentage of        | _                                              | 28%                                             | 44.4%                                                            | $\frac{R_L}{53.4\%}$                                              |

| NF reduction         |                                                |                                                 |                                                                  |                                                                   |

| relative to the      |                                                |                                                 |                                                                  |                                                                   |

| conventional         |                                                |                                                 |                                                                  |                                                                   |

| CGLNA                |                                                |                                                 |                                                                  |                                                                   |

where  $\eta=g_{m1}R_s$  and  $A_{POS}$  are the optimization parameters used to determine the minimum noise factor for the proposed CGLNA. To find the optimum value of  $\eta$ ,  $\frac{dF}{d\eta}=0$ . As a result, for large  $R_L$ ,

$$\eta_{opt} = \frac{1}{\sqrt{3 - 2A_{POS}}}.$$

(3.18)

For small values of  $A_{POS}$ , (3.18) becomes:

$$\eta_{opt} = \frac{1}{\sqrt{3}} \left( 1 + \frac{A_{POS}}{3} \right). \tag{3.19}$$

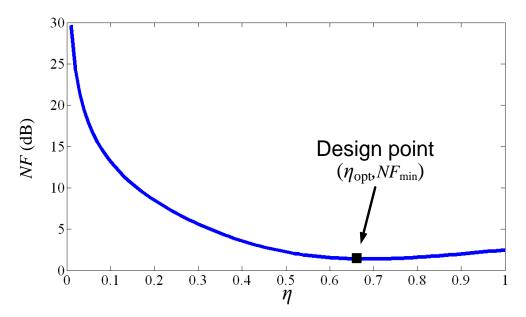

Figure 3.5: Calculated noise figure versus the optimization parameter  $\eta$  for the proposed CGLNA at  $A_{POS} = 0.35$ ,  $R_L = 650\Omega$ ,  $\gamma = (4/3)$ , and  $\alpha = 0.8$

Accordingly, the minimum noise factor,  $F_{min}$ , is given by:

$$F_{min} = 1 + 0.464 \frac{\gamma}{\alpha} - \frac{\gamma}{\alpha} \left( 1.155 - \frac{R_s}{R_L} \right) A_{POS} + \frac{R_s}{R_L} \left( 1.866 - 0.2886 A_{POS} \right)^2.$$

(3.20)

The negative sign for the third term in (3.20) plays an important role in reducing the proposed CGLNA noise factor. We can say that the combination of multiple feedbacks contributes to noise cancellation. As an example, for  $A_{POS} = 0.35$  to ensure stability,  $F_{min}$  is given by:

$$F_{min} = 1 + \left(0.06 + \frac{0.35R_s}{R_L}\right)\frac{\gamma}{\alpha} + \frac{3.11R_s}{R_L}.$$

(3.21)

Graphically, Fig. 3.5 shows the noise figure versus sweep of the optimization parameter  $\eta$ . As depicted, there is an optimum value  $\eta_{opt}$  to minimize the NF

which is confirmed by with the above analysis. In this design example, a minimum noise figure,  $NF_{min}$ , of 1.4 dB can be achieved for typical values of short-channel devices. Compared to the conventional CGLNA and other reported feedback based CGLNA topologies, the proposed CGLNA achieves the lowest NF with advantages of removing the bulky inductors and arbitrary choice of  $g_{m1}$  without restricting the input matching condition. Table 3.1 summarizes the main properties of the different CGLNA configurations together with the proposed one. The last line is showing the percentage of reduction in NF for each feedback method relative to the conventional CGLNA at at  $R_L = 650\Omega$ ,  $\gamma = (4/3)$ , and  $\alpha = 0.8$ . It can be shown that the proposed CGLNA can achieve the highest reduction among other toplogies.

### 3.4 Circuit design and measurement results

The proposed LNA with a voltage gain of 23 dB, 3-dB bandwidth of 1.76 GHz and a minimum noise figure of 1.85 dB over the band is implemented. A highly linear voltage buffer is used at the LNA output to drive the  $50\Omega$  load of the measuring equipment. Coupling capacitors are used between the LNA and the buffer to provide the buffer with separate DC bias. The gain and noise figure of the buffer are predetermined to de-embed their effect from the overall response to get the LNA response. The total schematic of the LNA with the buffer is shown in Fig. 3.6. Table 3.2 shows the transistor aspect ratios for the proposed LNA and buffer. In the layout implementation, the transistors are laid out with maximum number of fingers and close to minimum width per finger to minimize the effective series gate resistance, to reduce the signal loss and improve the noise figure specially for the input transistor,  $M_1$ . To reduce the effect of the flicker noise, the lengths of the transistors are increased. The coupling capacitors, employed in the design, are implemented using MIMCAP device supported by the IBM 90nm CMOS process which has a density

Figure 3.6: Schematic of the entire LNA with the output buffer

Table 3.2: Transistor aspect ratios for the LNA and buffer

| $(\frac{W}{L})_{M_1}$                            | $(\frac{W}{L})_{M_2}$             | $(\frac{W}{L})_{M_3}$                         | $(\frac{W}{L})_{M_{B1}}$           | $(\frac{W}{L})_{M_{B2}}$           |  |

|--------------------------------------------------|-----------------------------------|-----------------------------------------------|------------------------------------|------------------------------------|--|

| $\frac{75 \ \mu \text{m}}{0.175 \ \mu \text{m}}$ | $\frac{1.2 \ \mu m}{0.1 \ \mu m}$ | $\frac{6 \ \mu \text{m}}{0.3 \ \mu \text{m}}$ | $\frac{35 \ \mu m}{0.175 \ \mu m}$ | $\frac{50 \ \mu m}{0.175 \ \mu m}$ |  |

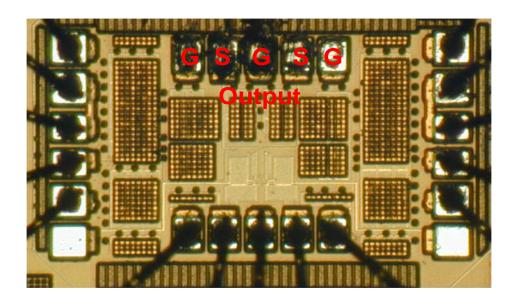

of 5.8 fF/ $\mu m^2$ . The biasing resistors are implemented using poly resistors. Fig. 3.7 shows a micrograph of the fabricated CGLNA/buffer with a chip size of 1mm×1mm (including the pads). The core LNA area is 0.03  $mm^2$

The core LNA consumes 1.4 mA from a 2 V supply while the buffer consumes 10 mA. The LNA is encapsulated in a micro leadframe (QFN) open package, where the DC biases and input RF signal are applied/monitored using an FR-4 printed circuit board (PCB). The output signal is monitored using a G-S-G-S-G differential probe. This measurement setup is used to evaluate the performance of the LNA

Figure 3.7: Die photo of the proposed LNA.