# University of Massachusetts Amherst ScholarWorks@UMass Amherst

Masters Theses 1911 - February 2014

2008

# A Process Variation Tolerant Self-Compensation Sense Amplifier Design

Aarti Choudhary University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/theses

Part of the Electrical and Computer Engineering Commons

Choudhary, Aarti, "A Process Variation Tolerant Self-Compensation Sense Amplifier Design" (2008). Masters Theses 1911 - February 2014.166.

Retrieved from https://scholarworks.umass.edu/theses/166

This thesis is brought to you for free and open access by ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses 1911 -February 2014 by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# PROCESS VARIATION TOLERANT SELF COMPENSATION SENSE AMPLIFIER DESIGN

A Thesis Presented by

AARTI CHOUDHARY

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

September 2008

Electrical and Computer Engineering

© Copyright by Aarti Choudhary 2008 All Rights Reserved

# PROCESS VARIATION TOLERANT SELF COMPENSATION SENSE AMPLIFIER DESIGN

A Thesis Presented by  $\label{eq:AARTI CHOUDHARY} \text{AARTI CHOUDHARY}$

| Approved as to style and content by | y:                           |

|-------------------------------------|------------------------------|

|                                     |                              |

| Sandip Kundu, Chair                 |                              |

|                                     |                              |

| Massimo V. Fischetti, Member        |                              |

|                                     |                              |

| Wayne P. Burleson, Member           |                              |

|                                     |                              |

|                                     | C.V. Hollot, Department Head |

Electrical and Computer Engineering

### ACKNOWLEDGMENTS

I am deeply indebted to my advisor, Professor Sandip Kundu for his constant encouragement and support throughout my graduate studies. His vast technical expertise and insight has given me an excellent background in the field of vlsi design. I would like to thank Professor Max Fischetti and Professor Wayne Burleson for their guidance and valuable feedback throughout my work. I have been fortunate to have worked with knowledgeable and friendly people at the VLSI Circuits and Systems laboratory at UMass. I am thankful to my family and my friends Vandita and Mayank for their constant encouragement at the time when it was needed the most

#### ABSTRACT

#### PROCESS VARIATION TOLERANT SELF COMPENSATION SENSE AMPLIFIER DESIGN

#### SEPTEMBER 2008

#### AARTI CHOUDHARY

M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Sandip Kundu

As we move under the aegis of the Moore's law, we have to deal with its darker side with problems like leakage and short channel effects. Once we go beyond 45nm regime process variations have emerged as a significant design concern as well. Also embedded memories are now very popular for both processor and ASIC designs. Embedded memories uses sense amplifier for fast sensing and typically, sense amplifiers uses pair of matched transistors in a positive feedback environment. A small difference in voltage level of applied input signals to these matched transistors is amplified and the resulting logic signals are latched. Intra die variation causes mismatch between the sense transistors that should ideally be identical structures. Yield loss due to device and process variations has never been so critical to cause failure in circuits. Due to growth in size of embedded SRAMs as well as usage of sense amplifier based signaling techniques, process variations in sense amplifiers leads to significant loss of yield for that we need to come up with process variation tolerant circuit styles and new devices. In this work impact of transistor mismatch due to process variations

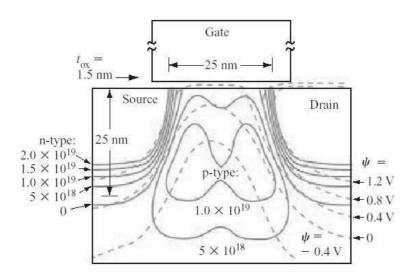

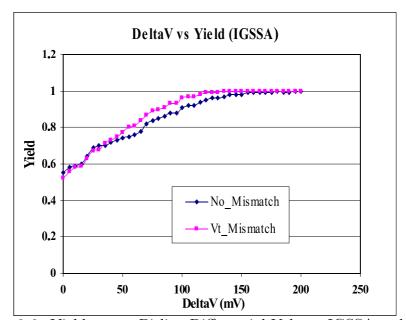

on sense amplifier is evaluated and this problem is stated. For the solution of the problem a novel self compensation scheme on sense amplifiers is presented on different technology nodes up to 32nm on conventional bulk MOSFET technology. Our results show that the self compensation technique in the conventional bulk MOSFET latch type sense amplifier not just gives improvement in the yield but also leads to improvement in performance for latch type sense amplifiers. Lithography related CD variations, fluctuations in dopant density, oxide thickness and parametric variations of devices are identified as a major challenge to the classical bulk type MOSFET. With the emerging nanoscale devices, SIA roadmap identifies FinFETs as a candidate for post-planar end-of-roadmap CMOS device. With current technology scaling issues and with conventional bulk type MOSFET on 32nm node our technique can easily be applied to Double Gate devices. In this work, we also develop the model of Double Gate MOSFET through 3D Device Simulator Damocles and TCAD simulator. We propose a FinFET based process variation tolerant sense amplifier design that exploits the back gate of FinFET devices for dynamic compensation against process variations. Results from statistical simulation show that the proposed dynamic compensation is highly effective in restoring yield at a level comparable to that of sense amplifiers without process variations. We created the 32nm double gate models generated from Damocles 3-D device simulations [25] and Taurus Device Simulator available commercially from Synopsys [47] and use them in the nominal latch type sense amplifier design and on the Independent Gate Self Compensation Sense Amplifier Design (IGSSA) to compare the yield and performance benefits of sense amplifier design on FinFET technology over the conventional bulk type CMOS based sense amplifier on 32nm technology node effective in restoring yield at a level comparable to that of sense amplifiers without process variations. We created the 32nm double gate models generated from Damocles 3-D device simulations [25] and Taurus Device Simulator available commercially from Synopsys [47] and use them in the nominal

latch type sense amplifier design and on the Independent Gate Self Compensation Sense Amplifier Design (IGSSA) to compare the yield and performance benefits of sense amplifier design on FinFET technology over the conventional bulk type CMOS based sense amplifier on 32nm technology node.

#### INTRODUCTION

Moore's law has been the key foundation and the driving force for breakthrough and evolution in the semiconductor industry. It has been serving the industry and academia marvelously since its evolution but as we continue to move in sub nanometer regime we have to deal with the darker side of the Moore's law [27] which comes from its fulfillment as by allowing nearly exponential increase in the device integration density and performance, it faces some major road blocks due to intrinsic physical limitation of the devices. One of the major barriers that the CMOS devices face at nanometer scale is increasing process parameter variations. Due to limitations of the fabrication process (e.g. sub-wavelength lithography and etching) and variation in the number of the dopants in the channel of short channel devices, device parameters such as length (L), width (W), oxide thickness ( $T_{ox}$ ), threshold voltage ( $V_T$ ) etc suffer large variations.

A 50 GHz microprocessor with 2 billion logic transistors using 22 nm drawn channel length (7 nm of effective channel length) devices operating at 250mV supply voltage by first half of the next decade - this is the expected roadmap should the scaling trends continue. Can we achieve this - maybe, maybe not!. To be able to even dream about such a processing system, it is important to be able to do predictive design. The old and easy way of designing for worst-case will not be adequate. It is important to accept that process variation is a reality and that one has to design circuits, with variations in mind.

Variations in the device parameters both systematic and random lead to loss in the parametric yield. The circuit yield loss due to process and device parameter variations has never been so critical and is getting some serious attention now. Moore's law

enabled us to integrate large memory blocks with logic circuits on a single chip, but this is also true that performance of the on-chip memory limits the speed and performance of the overall system. The key limiting factor is the increasing bit line capacitance, which results in increased time to develop bit line differential voltage.

For fast and power efficient memory design, both time and signal swing on the bit lines needs to be minimized. A sense amplifier is used to generate full rail output voltage using minimum bitline differential voltage or current making fast read write possible in memories. Designing high performance and robust sense amplifier is extremely important for designing SRAMS but with increasing parameter variations developing a robust, reliable and fast sense amplifier is becoming a task in itself. With each shrinking node it is important to accurately model the impact of device parameter variations at the circuit level and develop process tolerant design for sense amplifiers with improved performance and reduced impact of the leakage to reduce the gap between the CPUs and memories.

Proceeding in this direction we came up with the novel process variation tolerant Self Compensation Sense Amplifier (SSA) design on 32nm technology node on conventional bulk type CMOS technology. It demands only few additional transistors which compensates for the process variations since the single failing sense amplifier implicates the whole memory, there is one sense amplifier across each the column of the SRAM (128X8) so additional few transistors doesn't hurt the area overhead that much.

The trade off on added transistors in each sense amplifier in a column of SRAM to an improvement in the yield is definitely a solution to a problem. The fact that CMOS technology is at the cross-road today. Oxide scaling has halted due to gate leakage problem [40]. Changing oxide material provides an alternative solution for only 1-2 generations of technology [40]. Power density has become so high that power supply voltage must be scaled down which will require scaling of  $V_T$  which aggravates

the sub-threshold leakage problem. The ITRS predicts that static power dissipation per device will surpass the dynamic power dissipation by 2008. To reduce leakage while improving performance, ITRS predicts using strained silicon channels, ultra-thin single-gate FETs, and metallic gates. Two types of structure and materials changes must be considered. First, there are structures that allow a shorter channel length to be fabricated. Second, there are materials that enable higher performance for a given channel length. For the past few decades, new materials like strained silicon is used by IBM, Intel [17]. SOI based device structures incorporated by AMD, Honeywell, IBM has resulted in exponential growth of performance and integration density of silicon CMOS technology. One common condition for each innovation is that it was built on the advantages of existing ideas, without compromising the previous. Historically, the switch from metal gates to polysilicon gates, the switch from diffusion to ion implantation, and the incorporation of silicides were major changes that were difficult to implement, even though the transistor structure itself was little changed. Ultra thin body SOI FETs employ very thin silicon body to achieve better control of the channel by the gate and hence also gets advantage of reduced leakage and short channel effects [36].

Use of intrinsic or lightly doped body reduces threshold voltage  $(V_T)$  variations due to random dopant fluctuations and enhances the mobility of careers in the channel region and improvement in ON current. Researchers are exploring alternative technologies and this is a known notion that better scalability can be achieved by introduction of multiple gates at the other side of the body of each transistor resulting in a Double Gate (DG) SOI structure. CMOS device with a second gate for each device are referred to as 4-Terminal devices. In such technologies, one can choose to connect the back and front gates together or to control them separately while designing a circuit resulting in new circuit styles [36]. Connected back and front gates provides a simple way of mapping circuits designed in single gate technologies to double gates

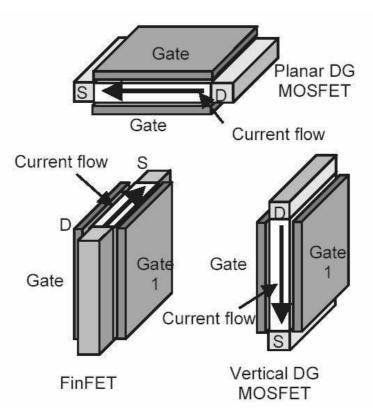

technologies. 3 Terminal configurations provide more ON current for transistors as well. On the other hand, independent gate control (4 Terminal configurations) can be used for designing new circuit styles. Back gate bias can be used to dynamically adjust the threshold voltage of the front gate to tune the power and performance requirement of a circuit. It can also be used for merging parallel transistors, the nature of these devices can be exploited to come up with new circuit styles. The three alternatives that are most widely considered for conventional MOSFET replacement are: planar device, vertical (pillar) device and the FinFETs.

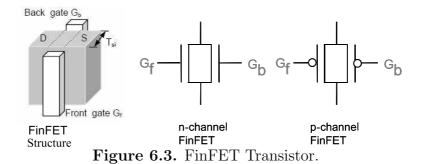

The FinFET technology is the most promising among the alternatives to conventional bulk CMOS [15]. FinFETs increase drive current through larger gate area while they reduce sub-threshold leakage through reduced channel doping. FinFETs have been successfully fabricated by multiple laboratories [20]. A FinFET is a vertical double gate device that is promising below 45nm technology [20, 34]. A double-gate FinFET structure offers additional configuration possibilities such as single channel or double-channel, whereby two gates create their own independent channels or one common channel. Similarly, the gates may be symmetric or asymmetric in terms of gate capacitance and current drive [19, 22]. FinFETs increase drive current through larger gate area while they reduce sub-threshold leakage through reduced channel doping. A FinFET is a vertical double gate device that is promising below 45nm technology [50] motivated by these considerations and feasibility for ease of manufacture and implementation, we chose FinFET to solve the yield problem. We propose Independent Gate Self Compensation Sense Amplifier Design (IGSSA), which is process variation tolerant self compensating FinFET based sense amplifier design.

### TABLE OF CONTENTS

|    |                                 |                                                                                                                                                                            | Page         |

|----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| A  | CKN                             | OWLEDGMENTS                                                                                                                                                                | v            |

| AI | BST]                            | RACT                                                                                                                                                                       | <b>vi</b>    |

| IN | TRO                             | DUCTION                                                                                                                                                                    | <b>i</b> x   |

| LI | ST (                            | F FIGURES                                                                                                                                                                  | xvi          |

| CI | HAP                             | $\Gamma 	ext{ER}$                                                                                                                                                          |              |

| 1. | INT                             | RODUCTION                                                                                                                                                                  | 1            |

|    | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Benefits of MOSFET Scaling Issues in Planar Bulk-Si MOSFET Scaling Process Induced Variations Thin-body MOSFETs Motivation and Road Maps  1.5.1 Motivation 1.5.2 Road Maps | 3<br>7<br>11 |

| 2. | SEN                             | SE AMPLIFIERS                                                                                                                                                              | 16           |

|    | 2.1<br>2.2                      | Voltage Mode Sense Amplifier                                                                                                                                               |              |

|    |                                 | 2.2.1 Current-Mirror Sense Amplifier (Conventional)                                                                                                                        | 25           |

| 3. | PR                              | OCESS VARIATIONS                                                                                                                                                           | 29           |

|    | 3.1<br>3.2<br>3.3               | Trends in Variability                                                                                                                                                      | 31           |

|           | 3.4        | Previo                           | ous Work to Combat Process Variations                                    | 33       |

|-----------|------------|----------------------------------|--------------------------------------------------------------------------|----------|

|           |            | 3.4.1<br>3.4.2                   | Supply Voltage                                                           |          |

|           | 3.5        | Impac                            | t of Mismatch on Sense Amplifiers                                        | 37       |

|           |            | 3.5.1<br>3.5.2<br>3.5.3          | Experimental Setup                                                       | 40       |

| 4.        |            |                                  | MPENSATION SENSE AMPLIFIER DESIGN ON CMOS TECHNOLOGY                     | 48       |

|           | 4.1        | Opera                            | tion                                                                     | 48       |

|           | 4.2<br>4.3 |                                  | t of Process Variations                                                  |          |

|           |            | 4.3.1<br>4.3.2<br>4.3.3          | The Operation of SSA                                                     | 53       |

| <b>5.</b> | МО         | DELII                            | NG OF DOUBLE GATE CMOS-DGFET                                             | 57       |

|           | 5.1<br>5.2 |                                  | e Scaling                                                                |          |

|           |            | 5.2.1<br>5.2.2<br>5.2.3          | Short-Channel Effects  Mobility Degradation  Dopant-Density Fluctuations | 59       |

|           | 5.3        | Propos                           | sed Structures                                                           | 61       |

|           |            | 5.3.1<br>5.3.2<br>5.3.3<br>5.3.4 | Doublegate Alternatives                                                  | 64<br>65 |

|           | 5.4<br>5.5 |                                  | T Fabrication                                                            |          |

|           |            | 5.5.1<br>5.5.2                   | Subthreshold Current                                                     |          |

|           | 5.6        | Const                            | agion.                                                                   | 71       |

|           |            |                                  |                                                                          |          |

| 6. | SEI | NSE AMPLIFIER DESIGN ON FINFET TECHNOLOGY                  | <b>7</b> 3 |

|----|-----|------------------------------------------------------------|------------|

|    | 6.1 | FinFET based Latch Sense Amplifier                         | . 74       |

|    | 6.2 | Working of FinFET based Latch Type Sense Amplifier         | . 75       |

|    | 6.3 | Impact of Process Variations in LSA                        | . 76       |

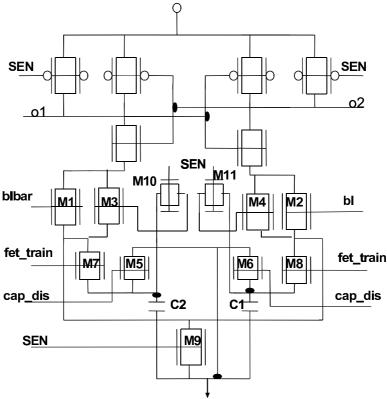

|    | 6.4 | Independent Gate Self Compensation Sense Amplifier (IGSSA) | . 77       |

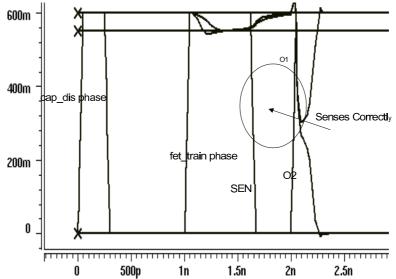

|    | 6.5 | IGSSA Operation                                            | . 79       |

|    | 6.6 | Impact of Process Variations in IGSSA                      | . 80       |

|    | 6.7 | Conclusions                                                | . 83       |

|    |     |                                                            |            |

| BI | BLI | OGRAPHY                                                    | 84         |

## LIST OF FIGURES

| re Pa                                                                                                                                                                                             | age  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1 Moore's law of scaling the number of transistors on a chip has been increasing exponentially                                                                                                    | 2    |

| 2 Device and interconnect (intra-die) variation trends                                                                                                                                            | 6    |

| 3 Technology Parameter Variations for next 12 yrs                                                                                                                                                 | 6    |

| Advanced transistor structures such as the UTB and the DG-MOSFET eliminate sub-surface leakage paths                                                                                              | 8    |

| Structure of the FinFET. $L_{eff}$ = physical gate length, $L_{gate}$ = drawn gate length, $T_{si}$ = silcon thickness, $T_{oxf}$ and $T_{oxb}$ are the front gate and back gate oxide thickness. | 9    |

| 6 Double Gate FinFET                                                                                                                                                                              | . 10 |

| 7 Basic 6T SRAM Cell                                                                                                                                                                              | . 12 |

| .1 Sense Amplifier across a rows of SRAM cells                                                                                                                                                    | . 17 |

| 2 Differential Senseamplifier                                                                                                                                                                     | . 18 |

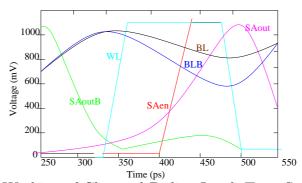

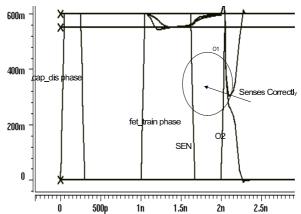

| 3 Sense Amplifier Operation                                                                                                                                                                       | . 20 |

| 4 Voltage Latch Type Sense Amplifier                                                                                                                                                              | . 21 |

| 5 Voltage Mode Latch Type Sense Amplifier                                                                                                                                                         | . 23 |

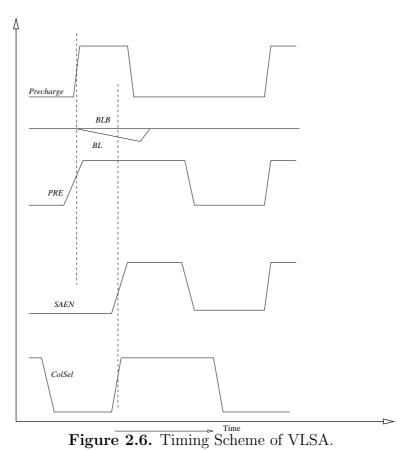

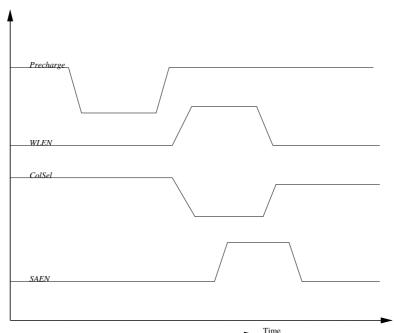

| 6 Timing Scheme of VLSA                                                                                                                                                                           | . 23 |

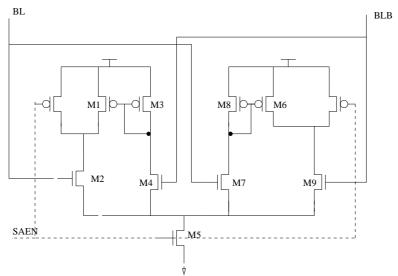

| 7 Conventional Mode Current Sense Amplifier                                                                                                                                                       | . 24 |

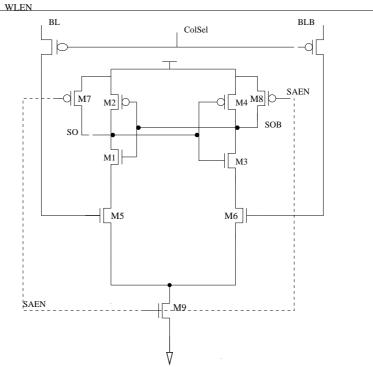

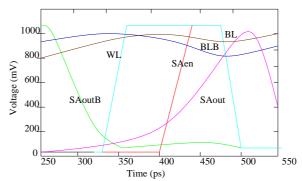

| 8 Voltage Mode Current Latch Type Sense Amplifier                                                                                                                                                 | . 26 |

| .9 Working of Voltage Mode Current Latch Type Sense Amplifier                                                                                                                                     | . 26 |

| 2.10 | Schematic of Clamped Bitline Latch Type Sense Amplifier                         |

|------|---------------------------------------------------------------------------------|

| 2.11 | Working of Clamped Bitline Latch Type Sense Amplifier                           |

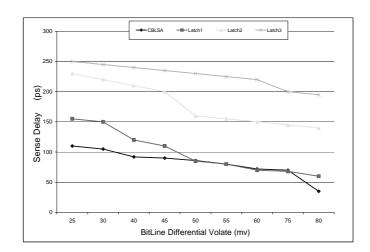

| 3.1  | Sense Delay versus Differential Voltage for different type of Sense Amplifier   |

| 3.2  | Sense Amplifier timing scheme                                                   |

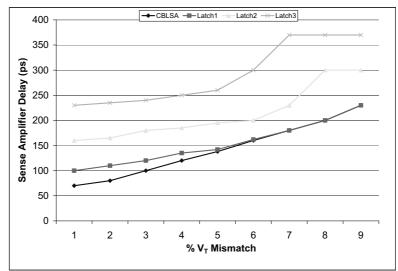

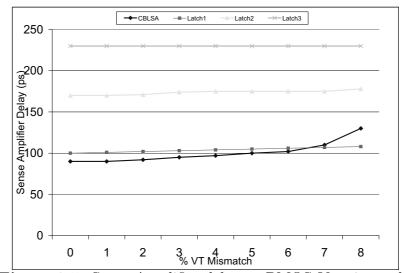

| 3.3  | Sense Amplifier delay vs NMOS $V_T$ mismatch                                    |

| 3.4  | Sense Amplifier delay vs NMOS channel length mismatch                           |

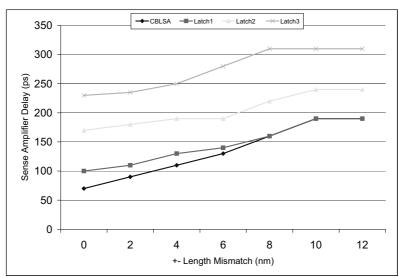

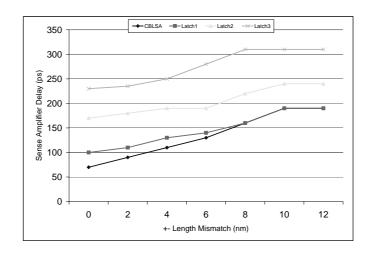

| 3.5  | Sense Amplifier delay vs PMOS $V_T$ mismatch                                    |

| 3.6  | Sense Amplifier delay vs PMOS channel length mismatch                           |

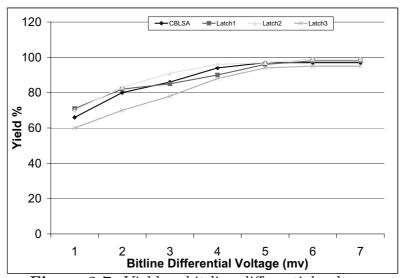

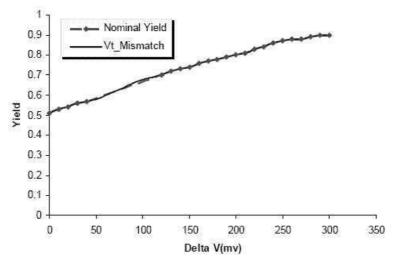

| 3.7  | Yield vs bit-line differential voltage                                          |

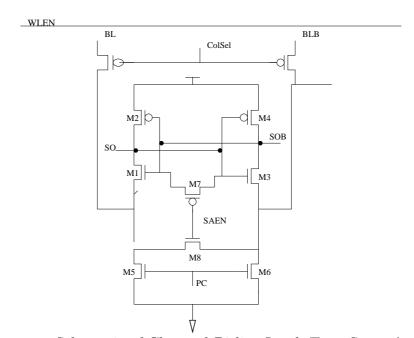

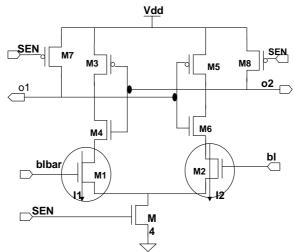

| 4.1  | Current Latch Voltage Mode Sense Amplifier scheme                               |

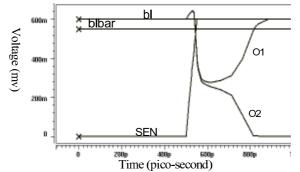

| 4.2  | Sense Amplifier Correct Operation                                               |

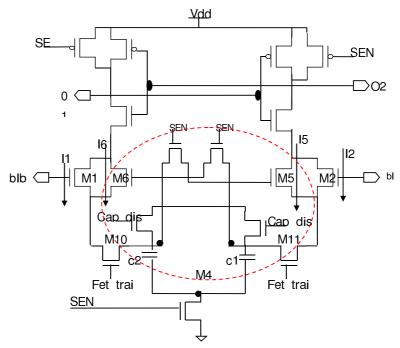

| 4.3  | Self Compensation Sense Amplifier Technique                                     |

| 4.4  | Self Compensation Sense Amplifier Correct Operation                             |

| 4.5  | Self Compensation Sense Amplifier Without FET_TRAIN Phase52                     |

| 4.6  | Yield vs Bitline Differential Voltage on 180nm                                  |

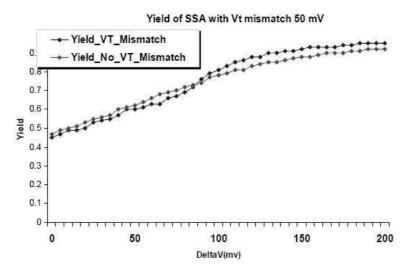

| 4.7  | Yield vs Bitline Differential Voltage on 32nm                                   |

| 4.8  | Yield vs Bitline Differential Voltage on 32nm with Vdd variation 54             |

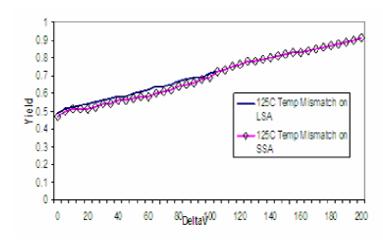

| 4.9  | Yield vs Bitline Differential Voltage on 32nm with Temp variation of $125^{o}C$ |

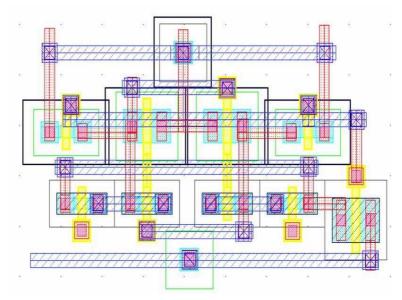

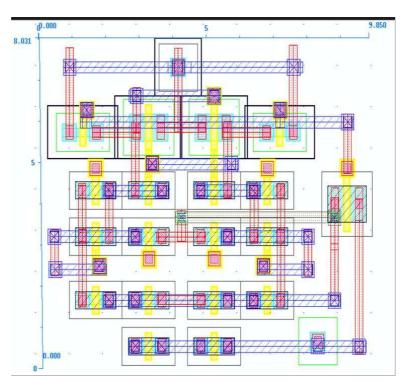

| 4.10 | Layout of nominal latch type sense amplifier                                    |

| 4 11 | Layout of self compensation latch type sense amplifier 56                       |

| 5.1 | The Superhalo doping profile has been shown to suppress DIBL through restoring some of the symmetry in electric potential that is lost as increased drain voltage tends to increase the drain depletion region and field lines. (Y. Taur - March/May 2002) 60 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

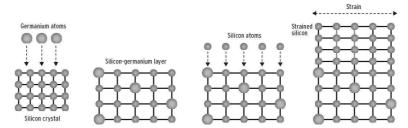

| 5.2 | Increasing mobility through straining the silicon lattice. As the silicon attaches to the larger germanium atoms, the spacing between atoms and therefore between potential collisions is increased.L. Geppert - Oct 2002                                     |

| 5.3 | Planar, Vertical and FinFET Architectures (M.Chan et all 2003)62                                                                                                                                                                                              |

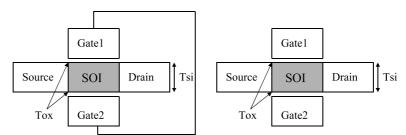

| 6.1 | FinFET with Tied or Independent Gates                                                                                                                                                                                                                         |

| 6.2 | Nominal Latch Type Sense Amplifier on FinFET Technology                                                                                                                                                                                                       |

| 6.3 | FinFET Transistor                                                                                                                                                                                                                                             |

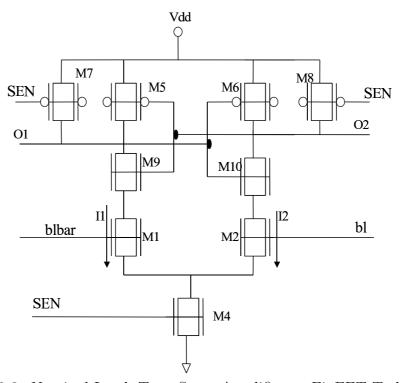

| 6.4 | Independent Gate Self Compensation Sense Amplifier Design (IGSSA)                                                                                                                                                                                             |

| 6.5 | IGSSA Waveforms for $V_T$ mismatch of 50 mV                                                                                                                                                                                                                   |

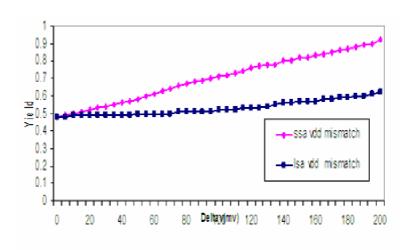

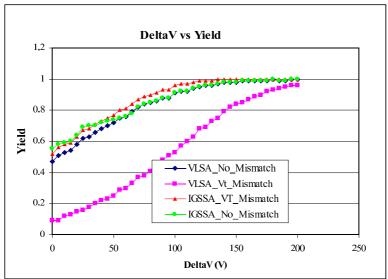

| 6.6 | Yield versus Bitline Differential Voltage IGSSA technique81                                                                                                                                                                                                   |

| 6.7 | Yield Comparison for two techniques nominal LSA and IGSSA82                                                                                                                                                                                                   |

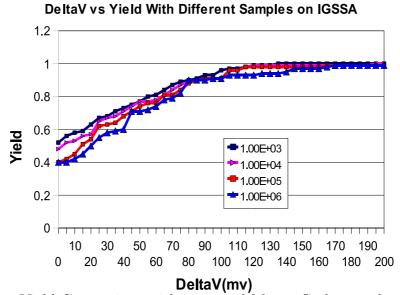

| 6.8 | Yield Comparison with increased Monte Carlo samples on IGSSA82                                                                                                                                                                                                |

#### CHAPTER 1

#### INTRODUCTION

This document is organized as follows, Chapter 1 presents the background and builds up the motivation on the basis of road-maps and where the trend of semiconductor industry is leading to. It point us to present known problems and possible solutions to those. It builds up the motivation as to why we chose the sense amplifier to solve the problem of process variations. Chapter 2 describes different types of sense amplifiers. Chapter 3 describes the impact of process variations and mismatch effects on the sense amplifier causing problems with yield and performance. Chapter-4 we propose the new self compensation sense amplifier (SSA) technique on one of the current mode latch type sense amplifier gives a comparison of this circuit with the existing current latch type sense amplifier. In Chapter 5 we describe the modeling of the double gate cmos its promises and challenges. Chapter 6 describes the Independent Gate Self Compensation Sense Amplifier design (IGSSA) on FinFET technology and we compare it with the SSA and nominal latch type sense amplifier. We generated our models through TCAD simulation from synopsys [47], and from DAMOCLES [25] 3D device simulation and used those in our sense amplifier depicting significant improvement in yield, performance and pvt variations.

#### 1.1 Benefits of MOSFET Scaling

Significant advances in silicon integrated circuit(IC) technology led by the continued miniaturized of the MOS transistor has enabled us increase in the computing power. The rapid progress in the semiconductor industry has been driven by im-

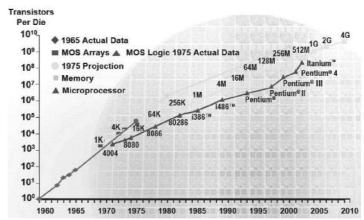

proved circuit performance and functionality together with reduced manufacturing costs. Since the 1960s MOS transistor have been shrinking 30% every three years, as predicted by Moore's law [27] shown in Figure 1.1.

**Figure 1.1.** Moore's law of scaling the number of transistors on a chip has been increasing exponentially.

While Moore's law only describes the rate of increase in transistor density, reduction of the physical MOS device dimensions has improved both circuit speed and density in the following ways:

a) Circuit operational frequency increases with a reduction in gate length,  $L_G$  as  $F_m ax = 1/L_G$ ; allowing faster circuits. b) Chip area decreases  $L_G^2$  enabling higher density and cheaper ICs. c) Switching power density is constant allowing lower power per function or more circuits at the same power.

Device scaling has been a relatively straightforward affair thus far, but physical limits are fast being approached, and new materials and device structures are needed to continue scaling trends.

#### 1.2 Issues in Planar Bulk-Si MOSFET Scaling

The planar bulk-silicon MOSFET has been the workhorse of the semiconductor industry over the last 40 years. However the scaling of the bulk MOSFETs becomes increasing difficult for the gate lengths below 20nm (sub-45nm half pitch technology node). As the gate length is reduced, the capacitive coupling of the channel potential to source and drain increase relative to the gate, leading to significantly degraded short channel effects (SCE). This manifests itself as a) increased off-state leakage b) threshold voltage ( $V_T$ ) roll-off,i.e. smaller  $V_T$  shorter gate lengths, and c) reduction of  $V_T$  with increasing drain bias due to a modulation of the source-channel potential barrier by the drain voltage, also called drain induced barrier lowering (DIBL).

In order to maintain the relatively strong gate control of the channel potential in bulk devices, various technological improvements such as ultra-thin gate dielectrics, ultra shallow source/drain junctions, halo implant and advance channel dopant profile engineering techniques such as super steep retrograde well have been necessary. Each of these technologies is now approaching fundamental limitations which may in turn, limit further scaling of device dimensions. Significant scaling difficulties have been encountered already and are expected to worsen in the next few years as the gate length  $(L_G)$  is projected to scale to well below 32nm [40]

With transistor scaling Vdd is also scaled down, However the threshold voltage,  $V_T$  cannot be scaled down significantly since the source/drain sub threshold leakage current Isdleak increase sharply with decreased  $V_T$  and it is important to keep Isdleak within tolerable limits because  $I_{dsat}$  depends on (Vdd- $V_T$ ), the scaling of Vdd tends to reduce  $I_{dsat}$  and hence make it difficult to improve the transistor. Short-channel effects (SCEs) such as drain induced barrier lowering [DIBL] are becoming very difficult to control as transistors are continuously scaled. This tends to lead to increased leakage current and reduces  $I_{dsat}$  and hence reduced transistor speed. Channel doping is becoming very large (both to set the threshold voltage correctly and to control SCEs),

leading to degradation in the mobility and to increased leakage current due to band to band tunneling.

Scaling of the gate dielectric equivalent thickness,  $T_{ox}$  is limited by gate leakage current. With scaling, random dopant fluctuations and line edge roughness can cause significant statistical variation in  $V_T$  and effective channel length  $L_{eff}$  [32].

In MOS devices, the gate dielectric thickness is single most important device dimension to enable device scaling and has also been the most aggressively scaled one. A thin gate dielectric increase capacitive coupling from gate to the channel, thereby reducing the source/drain influence on the channel. A larger gate capacitance also leads to a larger inversion charge density, or increased ON-state drive current. However gate dielectrics are already so thin that quantum mechanical direct tunneling through them results in significant gate leakage current below 20Å, The use of alternative high - K dielectric material can provide a small effective oxide thickness to maintain adequate gate control needed for  $L_G$  scaling while proving a large physical barrier to gate-oxide tunneling reducing gate leakage. Reduction of the source/drain extension junction depth directly decreases capacitive coupling of the drain to the channel, thus also reduces drain-induced short channel effect. Shallow source/drain to the channel formation required that low-energy ion implantation together with low thermal budget dopant activation to minimize dopant diffusion. The downside to this is the increase in the parasitic series resistance of the source and drain extension regions.

Raised source and drain technologies can alleviate the extrinsic resistance problem while maintaining shallow junctions. The contact resistance associated with the metallic contact to the source and drain regions is another source for parasitic series resistance and is expected to dominate total parasitic resistance of the device. In order to scale bulk-Si transistors, heavy body doping is also necessary to eliminate leakage path far from the gate dielectric interface and to increase back-gate (substrate) control of the body. For sub-100 nm gate length devices, a strong halo implant is generally used to suppress sub-surface leakage but this tends to increase the average channel doping in small  $L_G$  devices. However high channel doping concentration, reduce carrier mobility due to impurity scattering and increase transverse electric field, increase sub threshold slope, enhances band-to-band tunneling leakage and increase depletion and junction capacitances. These factors combine to significantly degrade devices performance.

In summary from device design point of view, in order to achieve good electrostatic integrity or good control of short channel effects (SCE), the gate dielectric thickness,  $T_{ox}$ , the source, drain junction depth,  $X_j$  and the channel depletion depth  $X_{DEP}$ , needs to be scaled down. The scale length for a bulk device  $\lambda_{BULK}$ , is an indication of how short  $L_G$  can be made before the SCE are excessive and is expressed in equation 1.1.

$$\lambda_{BULK} = 0.1(T_{OX}X_J X_{DEP}^2)^{1/3} \tag{1.1}$$

#### 1.3 Process Induced Variations

As the scale gets smaller, consistency of process control also decreases [39]. The semiconductor process cannot be perfectly controlled, which leads to statistical variation of many process variables. Several types of process variations can occur: line to line, batch to batch, wafer-to-wafer, die-to-die and intra die (within chip) [8, 30].

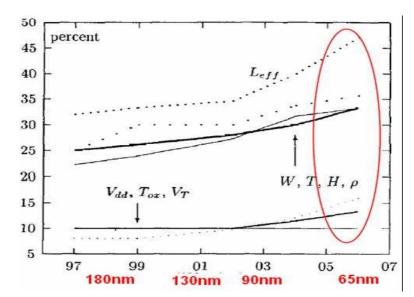

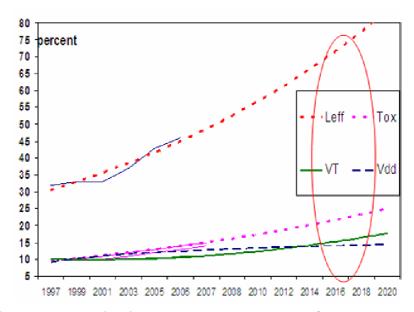

As per Sani Nassif [30] as shown in 1.2, there is 10% is  $V_T$  and 40% mismatch in the Leff.

If we extrapolate this graph as shown in 1.3for another 10 yrs, we see mismatch effect get even worse within a next decade.

Control of critical dimensions (CDs) in device and interconnects such as  $L_G$  in devices continues to be a difficult challenge, as the physical gate length is considerably smaller than the lithography printed line width [18, 8, 30]. In order to limit

Figure 1.2. Device and interconnect (intra-die) variation trends.

Figure 1.3. Technology Parameter Variations for next 12 yrs.

the impact of variations, the semiconductor industry is actually using slightly larger physical gate lengths than those specified in the ITRS, especially for memory applications. The slowing down on  $L_G$  scaling is now unavoidable in the future since the control of process variable does not track the scaling of minimum feature sizes. This is particular important for memory arrays, because if the desired degree of dimensional control were not achievable, design margins would need to be relaxed to achieve large functional memory arrays. While advanced process control can minimize systematic shifts in the CD the role of random variation arising from statistical dopant fluctuations and line edge roughness is expected to increase, so that variation will impact the overall power dissipation and performance [3]. Therefore, statistical treatment of random variation of circuits (statistical design) is becoming increasingly important. New transistor structures should have better immunity to process variations, and devices with tunable  $V_T$  are beneficial to counter any systematic shifts in transistor characteristics.

#### 1.4 Thin-body MOSFETs

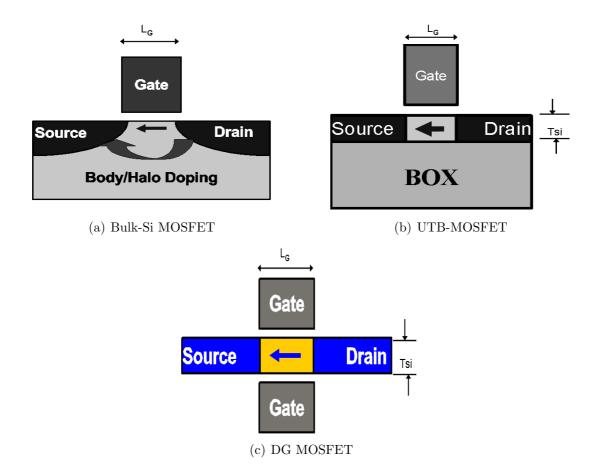

Figure 1.4 shows the transistor structures such as Ultra Thin Body (UTB) and the Double Gate MOSFET. They eliminate sub-surface leakage paths and extend scalability of Si CMOS technology. As the bulk MOSFET is scaled down, the control of short channel effects become increasingly difficult leading to increased sub threshold leakage current. This is because the source/drain influence over the channel potential becomes significant relative to the gate control. From equation 1.1, it is clear that if  $X_j$  and  $X_{DEP}$  can be reduced aggressively, it is possible to scale the MOSFET down to every small  $L_G$ . This is precisely what is done in the case of ultra-thin body (UTB) silicon on insulator (SOI) devices [5, 4]. Where  $X_j$  and  $X_{DEP}$  are physically limited to the thickness of an ultra-thin silicon film equation 1.1 qualitatively described the scaling behavior of UTB thus the scalability of MOS devices can be improved by using

Figure 1.4. Advanced transistor structures such as the UTB and the DG-MOSFET eliminate sub-surface leakage paths

an ultra thin silicon body such that all point in the silicon channel are close enough to the gate and well controlled by it, thereby eliminating sub-surface leakage currents [21]. The conventional fully depleted SOI MOSFET (with a thick body) is known to have worse short channel effects than bulk MOSFETs and partially depleted SOI MOSFETs [43]. Also partially depleted SOI (PDSOI) have the floating body effects [26].

Double Gate MOSFET has the best scalability, down to sub-10nm  $L_G$  devices [44, 16, 11]. The improved scalability of thin body devices makes them attractive for future generations of CMOS technology and so they have been included in the international technology road map for semiconductors (ITRS) [40].

UTB devices can be implemented in a straightforward manner as planar single gate fully depleted silicon on insulator (FDSOI) devices. While the planar double-gate device has been demonstrated [53], the fabrication of a planar double gate FET with a bottom gate that is aligned to the top gate and source/drain regions imposes numerous process challenges. Among all DG structures proposed so far, the FinFET is the most manufacturable because it eliminates the need for the bottom gate by rotating the channel by 90 and placing the gate electrodes on the two sidewall of the silicon fin [1, 34, 20, 15] Independent gate FinFETs in which the front and back-gate electrodes can be independently biased have been demonstrated as well [22, 37]. The front gate can be used to switch the device, whereas the back gate can be used to set the correct  $V_T$ . The back gate is as strong as front gate, and therefore the devices have degraded sub-threshold slope and transconductance due to capacitive division of the channel potential between the two gates [37].

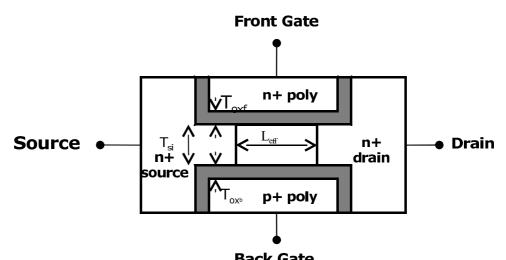

Figure 1.5 shows the top view of the FinFET devices. In this figure,  $L_{eff}$  = physical gate length,  $L_{gate}$  = drawn gate length,  $T_{si}$  = silcon thickness,  $T_{oxf}$  and  $T_{oxb}$  are the front gate and back gate oxide thickness

Figure 1.5. Structure of the FinFET.  $L_{eff}$  = physical gate length,  $L_{gate}$  = drawn gate length,  $T_{si}$  = silcon thickness,  $T_{oxf}$  and  $T_{oxb}$  are the front gate and back gate oxide thickness.

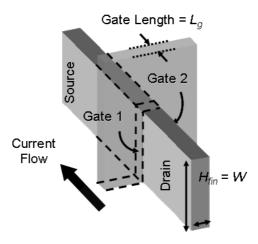

In this research work we have modeled the FinFET devices, it is explained elaborately in chapter-3. The planar FDSOI MOEFET can be extended to include a conducting electrode underneath the buried oxide (BOX) layer to form a second gate to control the channel from below. This ground plane or the back gate act as a second gate to shield the field penetration from the drain into the channel, and improves SCE. In a way it serve the role of the retrograde doping in a bulk MOSFET, by raising the body backside potential and by terminating drain electric fields shown in Figure 1.6

Figure 1.6. Double Gate FinFET.

In addition the, BOX eliminates source/drain-to-substrate depletion capacitance. In order to prevent electric field penetration through the BOX, the BOX layer should be thin. Another benefit of a thin BOX is the "back gate effect' similar to the "body effect' in bulk SI devices wherein the  $V_T$  can be tuned by the back-gate voltage. However the sub-threshold slope and the transconductance are degraded due to capacitive division of the channel potential between the front and the back-gate potentials. While the early FinFET devices were fabricated on SOI wafer, FinFETs on bulk-Si wafers have been demonstrated as well [1, 34, 20, 15].

Bulk FinFETs have the advantages of being potentially cheaper and can be easily integrated with conventional bulk-Si CMOS technology. Bulk FinFETs combine the benefits of good leakage and short channel effects controlled together with a cheaper manufacturing process, making them attractive for high density memory applications.

#### 1.5 Motivation and Road Maps

#### 1.5.1 Motivation

As CMOS technology progresses rapidly towards the nanometer regime, the integration level, performance and fabrication cost increase tremendously. Thus only high performance system chips design that integrate CPU (Central Processing Unit), DSP (Digital Signal Processing) processors or multimedia processors, memories, logic circuits analog circuits etc can afford the sub nanometer technology. Embedded memory has become a key component of any system and more practical than ever for at least two reasons. 1. Data processing and storage are the most primitive and basic components of the digital circuits. 2. Memory bandwidth is now one of the most serious bottlenecks to system performance.

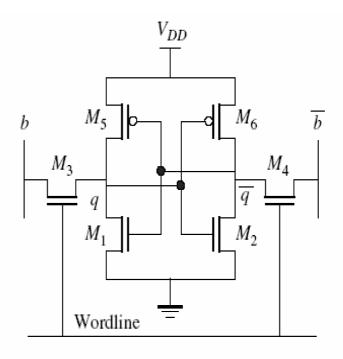

The speed gap between the MPUs and memory devices has been increased in the past decade and we have already hit the 'memory wall' [54]. The MPU speed has improved by a factor of 4 to 20 in the past decade. On the other hand, in spite of the exponential progress in storage capacity, minimum access time for each quadrupled storage capacity has improved only by a factor of two. Memory cell is the fundamental component of a memory system. The most important objective in the design of the memory cell is to minimize the size of the cell, which decreases the cost per bit, access time and power dissipation of the memory systems. Caches and other on chip memories requires very fast access time and also at the same time easy implementation. Both of these objectives are satisfied by SRAM Figure 1.7 shows the basic 6T SRAM cell.

Figure 1.7. Basic 6T SRAM Cell.

Since the size of the memory cell needs to be small most of the transistors are maintained close to minimum feature size of the process technology. One of the most critical circuits in the periphery of a memory is the sense amplifiers (SA). These circuits are strongly related to read access time of a memory, as they are used to retrieve the stored data in the memory array by amplifying small signal variations on the bit-line. The design of fast low-power and robust sense amplifier circuits is a challenge, due to the fact that in modern memory designs bit-lines exhibit significant capacitance, since there is higher number of cells per bit line, which sets limits in the sensing speed and introduces extra signal delays. Smaller the sense voltage, the faster the memory will be. The sense voltage also reduces power dissipation as the bit line can be restored to their default state as soon as a value has been sense and latched. If the sense transistors are perfectly matched, the lower limit on the sense voltage is set by the various noise margins and can be as low as 60-70 mV [38]. However

if the transistor mismatch the sense voltage must be increased to account for such mismatches, otherwise yield will suffer as the sense amplifier may show incorrect values [41]

Predicting and improving the design quality in terms of performance, yield and robustness are a central concern in designing sense amplifiers for use in SRAM cells. In a large embedded SRAM there may be many thousands of sense amplifiers and each one of them will have a very high yield requirement for the product to have a good overall yield in simple words "All units of one chip have to work in order to make the whole chip work".

A single failing sense amplifier implicates the whole memory but as CMOS IC technology becomes more and more advanced and Moore's law still governing the semiconductor industry, the control of process variations and manufacturing uncertainty becomes more and more critical. The sense amplifier performance degradation due to process variation and resulting yield loss is more pronounced than before [38]. It is important for the designer to be able to understand mismatch effects, since sensing should be done as fast as possible, subject to sensitivity constraints imposed by the parameter variations inherent in fabrication processes.

For low power application it is always desired to have low bit line differential voltage. The differential sense amplifiers are in general designed to be electrically and topologically symmetrical. Despite careful designing, small variations in parameters like threshold voltage and effective channel length due to process operating conditions [41, 41], lead to an input offset which affects the performance of the sense amplifier. The analysis of these variations provides a good understanding of the impact of device mismatches in differential sense amplifier. [42]. To guarantee reliability of the sense amplifiers either we have to come up with new process variation tolerant circuit styles, techniques or the replacement of conventional bulk type MOSFET and this is specially required for those circuits which rely on symmetry or matched transistors like sense

amplifier, srams, latches [7, 10, 29, 48] There has been lot of work done on similar lines which we will be discussing more in detail in chapter -2.

#### 1.5.2 Road Maps

To understand how Moore's law has run into trouble at 45 nm, we need to understand something about how CMOS transistors got evolved fulfilling Moore's law at every technology node. In an ironic twist of fate, the new CMOS transistor technology actually hearkens back to the earliest transistor implementations. When we make a layout through any VLSI design tools, we use the Mead-Conway design Rule: "Poly over silicon" produces a transistor The Mead-Conway rule was actually shorthand for a layer of poly-Si over an implied silicon dioxide insulator over a doped, over a Si substrate with implied source and drain, leads to a transistor being produced from photolithographic masks generated by VLSI CAD tool. Gorden Moore was trotted out to publicly proclaim: "The implementation of high-k and metal gate materials marks the biggest changes in transistor technology since the introduction of polysilicon gate transistors in the late 1960s"

Here Hafnium metal is used in the so-called high-k gate oxide layer, not the metal gate itself. The key issues at each technology node defined are usually the same. Each of these issues comes into play with different level of significance at each SIA node. In fact, it turn out that Moore's law has died many little deaths. The 2007 International Technology Roadmap for Semiconductors (ITRS) makes projections covering the next 15 years, through 2022 [40]. For the transistors these projections include the scaling of key parameters such as gate length, gate dielectric thickness, transistor leakage and drain saturation current, transistor speed performance, etc. In addition the ITRS assesses the main challenges to scaling MOSFETs, as well as the key technology innovations needed to overcome these challenges. The key target of ITRS scaling is to continue the historic 17 percent per year improvement in transistor performance, i.e.

in CV/I. This is important because the transistor performance improvement is critical components of the overall chip speed increase the scaling. The current mainstream transistor is planar bulk (or partially depleted silicon on insulator [PDSOI] which scales similarly to planar bulk). In order to help deal with scaling issues and to enable the targeted 17 percent per year transistor performance improvement while holding the leakage current to reasonable levels, a number of key technological innovations are necessary. The first of these is enhanced mobility due to applied strain, which was implemented in production in 2004, and has been continuously improved since then. This mobility enhancement allows increased  $I_{dsat}$  and is critical enabler for the desired transistor performance improvement. To continue to meet the targeted performance improvement, it is essential that the enhanced mobility be maintained as transistors are scaled. High K metal gate has already been incorporated, with AMD moved to Ultra thin body on 65nm technology. SIA road-map puts FinFETs as the prime candidate for post-planar CMOS device. FinFETs typically have un-doped, fully depleted channels because of the structure the electrostatic integrity and hence the ability to control SCEs are generally superior to planar bulk transistors. Furthermore the mobility should be superior because of the lack of doping. Finally because  $V_T$ is set by the work function of metal gate electrode random dopant fluctuations do not impact the statistical variability of  $V_T$  for these transistor types. Because of all these advantages the multiple-gate transistor will significantly improve scaling. Because SCEs increase notably, clearly the multiple gate transistor scales the best, while the Ultra thin Body Fully Depleted SOI scales in between the planar bulk and the multiple gates, which improve the electrostatic integrity and hence the control of SCEs with scaling. ITRS projects the ultimate MOSFET (for sub-15nm gate length transistors in the Road-map) is the multiple-gate transistors. Multiple parallel paths are envisioned, where for several years two or even all the three transistors types coexist.

#### CHAPTER 2

#### SENSE AMPLIFIERS

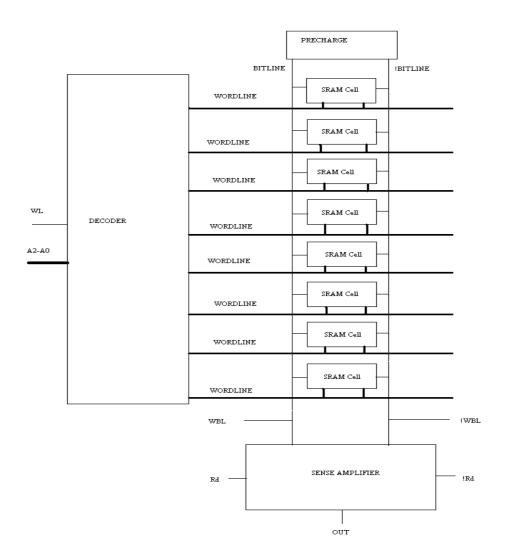

Sense Amplifier is the most critical circuits in the periphery of CMOS memory [23]. The performance of SA's strongly affects both memory access time, and overall memory power dissipation. As with other ICs today, CMOS memories are required to increase speed, improve capacity and maintain low power dissipation. These objectives are somewhat conflicting when it comes to sense amplifier in memories. With increased memory capacity usually comes increased bit line parasitic capacitance. This increased bit-line capacitance in turn slows down voltage sensing and makes bit-line capacitance swings energy expensive resulting in slower more energy hungry memories. Due to their great importance in memory performance sense amplifiers have become a very large class of circuits. Their main function is to sense or detect stored data from a read-selected memory cell. Figure 2.1 shows a typical position of sense amplifier in a column of memory cells.

Sense amplifiers are used to translate small differential voltage to a full logic signal that can be further used by digital logic. The need for increased memory capacity, higher speed, and lower power consumption has defined a new operating environment for future sense amplifiers. Below are the some of the effects of increased memory capacity and decreased supply voltage.

- 1) Increase in the number of memory cells per bit-line increases while as increase in the length of the bit-line increases

- 2) Decreasing memory-cell area to integrate more memory on a single chip reduces the current that is driving the now heavily loaded bit-line. This coupled with increased

Figure 2.1. Sense Amplifier across a rows of SRAM cells.

causes an even smaller voltage swing on the bit-line.

3) Decreased supply voltage results in smaller noise margins which in turn affect sense amplifier reliability. Shekhar Borkar from Intel suggests

"Sense amplifier are not tractable in future and will go away but not in memories"

Projections from the National Technology Roadmap for Semiconductors call for operating voltage of CMOS logic to drop by about a factor of 0.7 to 0.8 per generation to keep power dissipation in check. For the sense amplifier and other support circuit to work properly at reduced voltage requires scaling of the  $V_T$  of those devices. For a differential amplifier to sense correctly has a current mirror type of configurations as shown in Figure 2.2.

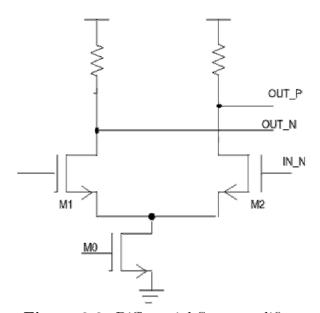

Figure 2.2. Differential Senseamplifier

For Sense amplifier to work in differential mode, M0, M1 and M2 should operate in Saturation Mode. The tail current should be  $I_{ref}=I_{DS}=\frac{k}{2}\frac{W}{L}(V_{GS}-V_T)^2$  For M0, M1 and M2 to remain in Saturation Vdd  $>V_{Tn}$  (in 0.18 um, a 0.25 V margin is typical)

At VDD < 1V scaling  $V_T$  leads to off current problems, such low  $V_T$  devices are not feasible in order to meet power requirements and reduce standby power post 45

nm technologies alternatively different sensing circuits may be developed for lower voltage operation.

Since SRAM requires balancing act between delay, area and power consumption. The circuit styles for the decoders and the sense amps, transistor sizing of these circuits, interconnect sizing and partitioning of the SRAM array can all be used as a tradeoff. With technology scaling the transistor mismatch doesn't scale, thus the delay of the output mux doesn't scale. The nonscaling of threshold mismatches with process scaling causes the signal swings in the bit line and data lines also not to scale, leading to an increase in the gate delay of the SRAM across technology generations. This delay increase for most of the SRAM organization can be mitigated by using more hierarchical designs for the bitline and data line path and using offset compensations scheme in sense amplifiers.

The sense amplifiers that are used in SRAM are mainly differential in nature. The differential sense amplifiers can distinguish smaller signals from noise due to their high common mode rejection ratio providing good reliability.

The differential sense amplifier is designed to be electrically balanced symmetric circuits. However due to process variations all the devices in the circuit does not have the same characteristics and this leads to variation in the design parameters if the circuit. The results of such variation in the device parameters are an offset voltage or current. An offset is a voltage or current difference which appears between the two output nodes, when an identical input voltage or bias circuit is applied at the inputs. This offset might affect the sensing delay or even the functionality of the circuit depending on the extent of process variation on each device. Therefore determining the worst case possibility of variation in each circuit is highly significant in the design of a sense amplifier. The offset voltage can be calculated as a function of the threshold voltages and dimensions of the transistors in the sense amplifier as shown in equation 2.1.

$$V_{OS} = f(V_T, I_D, W_i, L_i)$$

(2.1)

The following section discusses and analyzes different type of differential sense amplifier circuits. Especially latch type implementation due to their capability of positive feedback they are extensively used in memories [23, 52] This configuration makes possible to restore data in DRAM cells simply with increase in differential gain of the sense amplifier and reduces switching times and delays in the sense circuits thus has the benefit of fast speed and low power consumption, which makes them hot favorite for caches and low power embedded SRAMs [52, 23].

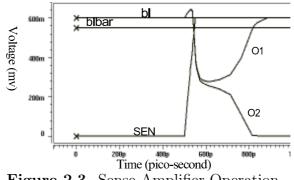

Figure 2.3. Sense Amplifier Operation.

To act as a sense amplifier, the cross coupled latch is initialized in its metastable point by equalizing bit-line and bit-linebar. Once a voltage difference is built over the two. The sense amplifier is enabled by raising 'SEN' [52]. Depending on the value of bit-line and bit-linebar the cross coupled pair traverses to one of its stable operation point as shown in the Figure 2.3.

Offset is particular and inherent to differential sense amplifiers, and it is the voltage or current difference which appears between the two output node potentials or between the two output currents, when an identical voltage or bias current is applied to the two inputs. The offset voltage or current has to be counteracted by the memory-cell generated signal for correct sense operations. Theoretically, differential sense amplifiers are electrically balanced symmetrical circuits. In practical implementa-

tions both the transistors and the passive elements have slight parameters differences inspite of the utmost design efforts to assure their symmetrization. These parameter difference and the resulting sense amplifier offsets are distributed spatially throughout the chips, wafer and lots and the signal generated by a memory cell has to act against and neutralize the appearing maximum offset before the sensing of the data signal could start. Thus, the offset limits the sensitivity i.e. the minimum data signal amplitude that the circuit can detect and it delays the effective start of data sensing. To improve both sensitivity and sensing speed the offsets should be kept small by minimizing the imbalances between the halves of differential sense circuit. Imbalances may results from the effects of process variations and can be mapped to non uniform variations in threshold voltage  $V_T$  gain factors, gain factors, load resistances, load capacitance which can be mapped to gate length variations.

## 2.1 Voltage Mode Sense Amplifier

Figure 2.4. Voltage Latch Type Sense Amplifier.

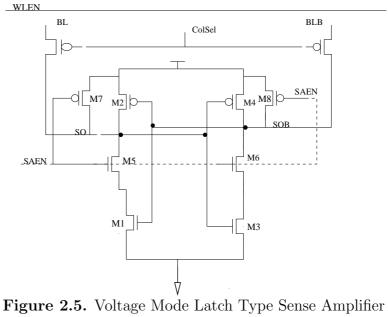

In conventional memories, voltage-mode sense amplifier is used that present a high input impedance to the bit-lines. This allows the sense amplifier to provide a high voltage gain with the use of simple circuits. The sense amplifier are designed with operating margins that constrain the minimum and maximum input signal amplitudes. The minimum input signal amplitude is necessary to provide reliable operation of the sense amplifier. To meet this constraint, a sufficient differential voltage in the bit-lines is allowed to develop before enabling the sense amplifier. The Voltage mode sense-amplifier also operates in two phases, in the pre-charge phase, the bit-lines and the sense-amp output are pre-charged high. SEN is pulled high for sensing the bitlines. The voltage mode sense amplifier requires differential discharging of the bit-line capacitance for sensing the voltage difference. It reacts after a certain amount of differential voltage is developed on the bit-line capacitance. Hence the time to develop a certain differential voltage to appear depends on the bit-line capacitance. Hence the time to develop a certain differential voltage will increase with the increase in the capacitance (i.e. number of cells in the column). The time to develop a certain differential voltage (for proper operation of sense-amplifier) will increase because of the increased leakage current and this problem will worsen with the coming technology generation. This section describes two differential voltage sense amplifiers cross-coupled inverter latch Figure 2.4 and 2.5 shows the typical Voltage Latch Type Sense Amplifier. Figure 2.6 shows the timing scheme of VLSA

# 2.2 Current Mode Sense Amplifier

In advanced memories the capacitances of the bitline is increasing due to technology scaling and the increasing number of cells attached to the column as shown in Figure 2.1. In such memories voltage mode cannot keep up to their performance thereby leading to the need for faster sensing techniques that are not affected by the bitline capacitance. Current mode sense amplifier are applied to reduce the sense circuit delays as they provide low common input/output impedences. The small input impedence presented to the bit-lines result in reduced voltage swings, cross-talk and

substrate currents. The current mode sense amplifier converts and amplifies a small current difference into CMOS voltage levels. This section describe different type of current mode sense amplifier and due to its inherent advantage of performance over voltage mode sense amplifier, we will demonstrate the compensation technique on the current mode sense amplifier both on Bulk CMOS technology and FinFET technology.

#### 2.2.1 Current-Mirror Sense Amplifier (Conventional)

The traditional form of the primitive current amplifier is the current mirror sense amplifier. In the current-mirror amplifier if the devices M1 and M2 are identical, then the bitline or input current I1 is the same as the readline or output current Io, because the gate-source voltage  $V_{GS}$  is common for both devices M1 and M2. If M1 and M2 differ only in their aspect ratios W/L otherwise they are identical. As shown in the Figure 2.7 [24] In this circuit, the gates of the two nMOS transistor M2 and

Figure 2.7. Conventional Mode Current Sense Amplifier

M9 are connected to the bit-lines. The substrate terminals are tied to their respective source terminals in order to remove substrate-bias effect. Notice that each bit-line is represented by a large parasitic capacitance. The nMOS transistor M5 is a long

channel device which acts as a current source for both branches, and is controlled by a SAEN signal. Before beginning of a "read" operation, the two bit lines (columns) are pulled up for equalization. The SAEN signal is low during this phase, so that the nMOS transistor M5 remains off. Since both M2 and M9 conduct source node is pulled up, and the output node of the amplifier also goes high. Therefore the output of the inverter is at a logic low level initially. Once a memory cell is selected for the "read" operation, the voltage on one of the complementary bit line will start to drop slightly. At the same time as the row selection signal, the SAEN signal driving M5 is also turned on if the stored data on the selected SRAM cell forces the bit line to decrease slightly, transistor M5 turns off, and the output voltage of the differential amplifier drop immediately.

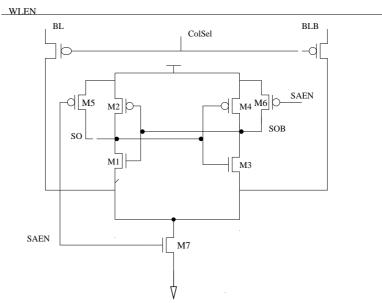

#### 2.2.2 Current Controlled Latch Sense Amplifier

Many sense amplifiers are activated simultaneously to achieve wide bandwidth, the current of sense amplifiers increases. Therefore power reduction in sense amplifiers is important to reduce the total power consumed in the memory. A current mirror sense amplifier is shown in Figure 2.7. It is easy to control and the speed of a current-mirror sense amplifier can be easily accelerated by increasing the operating current. Therefore memories frequently use this type of sense amplifier However, the static current flows through the pull down MOSFET connected to ground as long as SAEN is activated. To realize low-power and automatic power-saving scheme Kobayashi et all [23] came up with current controlled latch sense-amplifier shown in Figure 2.8.

In the read cycle, the data of memory cell appear as a small difference on the bit lines (BL and BLBAR) The gate of two NMOS's (M5 and M6) are connected to bit-line and bit-line bar. The current flow through M1 and M3 controls the serially connected latch circuit. A small difference between the current through M5 and M6 converts to a large output voltage, shown in Figure refLatch3.

Figure 2.8. Voltage Mode Current Latch Type Sense Amplifier.

Operation Latch Type Sense Amplifier (LSA) starts by turning on M9. After LSA is activated, the operation current ( $I_{sa}$ ) flows during the transition of output nodes. The current flow only during switching of inverters that compose the latch sense amplifier. The operating of LSA is shown in figures. It is difficult to control the latch timing, because of early latching often causes errors. A latch sense amplifier must start the sensing operation after the bit line are separated enough to sense, can be understood more clearly with the Figure 2.9 [52].

Figure 2.9. Working of Voltage Mode Current Latch Type Sense Amplifier.

#### 2.2.3 Clamped Bitline Sense Amplifier

Another type of current mode sense amplifier is Clamped Bitline Sense Amplifier (CBLSA), It is another current mode type of sense amplifier, which amplifies a small differential current between the bit-lines into a full rail-to-rail voltage. It requires an extra timing signal (equalize signal) for its operation. This presents a two fold problem: one is the routing overhead required for the equalize signal and the other is the generation of timing pulse for sensing every data bit. The CBLSA circuit has no provision for stopping the flow of static current, and hence dissipates power, even when there is no data activity on the interconnect. The CBLSA has an equalize transistor that keeps the voltage at outputs of the cross-coupled inverter at half- $V_dd$  will lead to continuous static power dissipation during the equalize period. Shown in Figure 2.10

Figure 2.10. Schematic of Clamped Bitline Latch Type Sense Amplifier.

The bit-lines in CBLSA are connected to a low impedance node, which is away from the sense amplifier output. The transistors M1, M2 and M3, M4 form the cross-

coupled inverters. Transistors M5 and M6 provide the low impedance termination. During the precharge phase transistor M8 equalizes the output node of the sense amplifier and the output nodes are precharged to Vdd. Transistors M5 and M6 are off during that time thereby preventing any static currents. During the read operation, transistors M5 and M6 are on and once a sufficient differential current is developed the SAEN signal is pulled low to enable the sense amplifier. The cross coupled inverter pair is enabled which converting and amplifying the difference in the currents in the two legs of the sense amplifier circuits.

The working on CBLSA is shown in Figure 2.11

Figure 2.11. Working of Clamped Bitline Latch Type Sense Amplifier.

## CHAPTER 3

## PROCESS VARIATIONS

Parameter variations have become increasingly important for microprocessor design. It occur for multiple reasons, including non-uniform ion implantation or photo resist exposure, or lack of uniformity in oxidation, diffusion or polishing. Variation between the production lines can occur because of different mask, stepper and the optics at each line. There can be variation between each exposed field on a wafer because of slight changes in the distance between wafers and the optics due to steppers or the wafer not being perfectly flat. Varying illumination and lens aberrations can lead to a large intra-field variation of effective channel length and speed. The process variation can cause the delays of wires and gates within a chip to vary. As a result, some chip may also operate correctly at slower speeds. In order to understand that we need to classify the type of variation and components of variations. The process variations in semiconductor devices can be classified into environmental variations and physical variations.

Environmental variation includes variation in power supply voltage, noise coupling among nets and temperature. Changes in supply voltage accounts for IR drop and Package Noise. Physical Variation are caused by processing and mask imperfections and reliability-related degradation.

As geometries shrink, the impact of process variations on interconnect reliability is expected to increase. Varying etch rates can modify the profile of wire crosssection. At the same time, the thickness of the metallic and dielectric layers can change over the die surface. As the degree of control of processing methods and techniques are not able to keep up with the degree of scaling in feature size, the manufacturing methods introduce variations. These variations are permanent and result from limitation in the fabrication process. As technology scales, the features size reduces thereby requiring a sophisticated fabrication process. All of these variations effects speed, power (primarily leakage) and yield.

## 3.1 Trends in Variability

The semiconductor process cannot be perfectly controlled, which leads to statistical variation of many process variables. Several types of process variations can occur: line to line, batch to batch, wafer-to-wafer, die-to-die and intra die. There can be variation between each exposed field on a wafer, because of slight changes in the distance between wafers and the optics, due to steppers or the wafer not being perfectly flat. Varying illumination and lens aberrations can lead to a large intra-field variation of effective channel length and speed.

Inter die variation is the difference in the value of a parameter across nominally identical die (whether those die are fabricated on same wafer, on different wafers or in different lots) and is typically accounted for in circuit design as a shift in the mean of some parameter values (e.g.  $V_T$  or wire width) equally across all devices or structures on any one chip. For purposes of circuit design it is usually assumed that each contribution or component in the inter die variation is due to different physical and independent sources, and it is usually sufficient to lump these contribution together into single effective die-to-die variation component with a single mean and variance and are modeled using worst case corners, substantially all of existing practical and theoretical work on yield analysis and maximization techniques are focused on intradie variation. Intra die variation or within die variation occurs spatially within a die, which are random and due to the semiconductor manufacturing process. These variations are classified into three categories which include devices variation, interconnect

variation and dynamic variations. Device variations are fluctuation in MOS parameters and include effective gate length  $(L_{eff})$ , Threshold voltage  $(V_T)$  Thickness of the gate oxide  $(T_{OX})$ , and the drain/source region parasitic resistance  $(R_{dsw})$ , effective gate length variation could arise due to masking difference and threshold variations occur due to dopant variations.

## 3.2 Source of Local Variation

The source affecting device and interconnect variation on a die are: Random Dopant fluctuations, Sub-Wavelength Lithography, Increased use of Chemical Mechanical Polishing Gate oxide thickness is critical but generally well controlled parameter variation tends to occur from one wafer to another.

As we scale the transistor further, physics based random variation in the threshold voltage due to random dopant fluctuations, and in the channel length due to line edge roughness, add random components of variability to the systematic layout silicon just mentioned. These variations play a significant part in sub threshold leakage and other important device performance metrics. This uncertainty is expected to continue as we scale our silicon devices to the level of atomic scaling, with oxides a few atoms thick and channels with countable numbers of dopant atoms. The rise in the inherent systematic and random non uniformity will have effects that are far-reaching in every aspect of design, manufacturing, test and overall reliability "The law of large number no longer applies". It's obvious that no single solution or advancement can solve this problem of process variation. We have to come up with ways with new devices and process variation tolerant technique both at the circuit level and architecture to solve our problem of process variations  $V_T$  is adjusted to desired level by implanting dopants (threshold implant) in the channel.

Every technology generated, transistor area reduces by half and number of dopant atoms in channel decreases exponentially. Dopant fluctuation results in: two transistors next to each other will have different  $V_T$  from one another due to random placement and concentration fluctuation of the dopant atoms.

Sub wavelength photolithography is the primary reason for line edge roughness and causes of variation in length and width. Lithography variation is one reason why poly is oriented in one direction and dummy cells are used in SRAM arrays.

For short channel MOSFET, variation in  $L_{eff}$  can cause further variation in  $V_T$  due to drain source charge sharing, halo implants are used these days to minimize this effect. As circuit designers we do not want parametric yield to have large impact on the final yield. The dilemma which we face today: Process and device variation data/model is not available until sufficient silicon has been processed most of the circuit blocks are designed before this data is available, so we need to come up with process variation tolerant techniques both at the architecture level and circuit level, there has been lot of efforts in the past [7, 48]. For dealing with these variations, numerous process technology, circuit and architectural solution have been proposed to combat variation. Designer verifies the circuit functionality and performance under the extreme conditions.

## 3.3 Traditional Approach: Worst Case Design

Traditionally, 5 different bins are defined by two letter acronyms describing the relative performance characteristics (T=typical, F= fast, S= slow) of nmos and pmos devices. There are differential spice models for fast, slow and typical nmos and pmos devices and they are generated in accordance with the maximum and minimum values of the saturation currents and threshold voltage of the transistors found on a sample chip. Using these models, the circuit/chip is simulated on spice.

MOS transistor dimensions and the threshold voltage are among the key parameters that control CMOS transistor's drive current. MOS circuits become extremely