## University of Massachusetts Amherst ScholarWorks@UMass Amherst

Masters Theses 1911 - February 2014

2011

# Design of an FPGA-based Array Formatter for Casa Phase-Tilt Radar System

Akilesh Krishnamurthy University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/theses

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

Krishnamurthy, Akilesh, "Design of an FPGA-based Array Formatter for Casa Phase-Tilt Radar System" (2011). Masters Theses 1911 -February 2014. 691.

Retrieved from https://scholarworks.umass.edu/theses/691

This thesis is brought to you for free and open access by ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses 1911 -February 2014 by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# DESIGN OF AN FPGA-BASED ARRAY FORMATTER FOR CASA PHASE-TILT RADAR SYSTEM

A Thesis Presented

by

AKILESH KRISHNAMURTHY

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

September 2011

Electrical and Computer Engineering

$\odot$  Copyright by AKILESH KRISHNAMURTHY 2011 All Rights Reserved

# DESIGN OF AN FPGA-BASED ARRAY FORMATTER FOR CASA PHASE-TILT RADAR SYSTEM

# A Thesis Presented $\label{eq:by} \mbox{\sc AKILESH KRISHNAMURTHY}$

| Approved as to style and content b | oy:                                                                   |

|------------------------------------|-----------------------------------------------------------------------|

|                                    |                                                                       |

| Russell G. Tessier, Chair          |                                                                       |

|                                    |                                                                       |

| Stephen Frasier, Member            |                                                                       |

|                                    |                                                                       |

| Joseph Bardin, Member              |                                                                       |

|                                    |                                                                       |

|                                    | C. V. Hollot, Department Chair<br>Electrical and Computer Engineering |

#### ACKNOWLEDGMENTS

I would first like to extend my deepest sense of gratitude to my parents and brother for their encouragement and support to pursue graduate studies at UMass Amherst.

I would like to thank my advisor, Professor Russell Tessier and Eric Knapp for giving me the wonderful opportunity to work in their research group. My thesis work would not have been possible without their constant motivation and guidance. I will forever be grateful for all the encouragement and continued support I received from them. I also wish to thank Professor Stephen Frasier and Professor Joseph Bardin for their helpful comments and feedback.

I would like to acknowledge the help and support of my lab mates Deepak Unnikrishnan and Vishwas Vijayendra, with whom I have shared numerous technical discussions and brainstorming sessions. Thanks to Arunachalam Annamalai for his help during the final phase of the project. Finally, I would like to thank all my friends in Amherst, the members of the Reconfigurable Computing Group, and CASA, who have made my stay here truly memorable.

#### ABSTRACT

## DESIGN OF AN FPGA-BASED ARRAY FORMATTER FOR CASA PHASE-TILT RADAR SYSTEM

#### SEPTEMBER 2011

# AKILESH KRISHNAMURTHY B.E., ANNA UNIVERSITY, INDIA M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Russell G. Tessier

Weather monitoring and forecasting systems have witnessed rapid advancement in recent years. However, one of the main challenges faced by these systems is poor coverage in lower atmospheric regions due to earth's curvature. The Engineering Research Center for the Collaborative Adaptive Sensing of the Atmosphere (CASA) has developed a dense network of small low-power radars to improve the coverage of weather sensing systems. Traditional, mechanically-scanned antennas used in these radars are now being replaced with high-performance electronically-scanned phased-arrays. Phased-Array radars, however, require large number of active microwave components to scan electronically in both the azimuth and elevation planes, thus significantly increasing the cost of the entire radar system. To address this issue, CASA has designed a "Phase-Tilt" radar, that scans electronically in azimuth and mechanically in elevation. One of the core components of this system is the Phased-Array controller or the Array Formatter. The Array Formatter is a Field Programmable

Gate Array (FPGA)-based master controller that translates user commands from a computer to control and timing signals for the radar system. The objective of this thesis is to design and test an FPGA-based Array Formatter for CASA's Phase-Tilt radar system.

# TABLE OF CONTENTS

|    |            |                                                    |                                                                                                                                                  | Pa | ıge                  |

|----|------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------|

| A  | CKN        | OWLI                                               | EDGMENTS                                                                                                                                         |    | iv                   |

| Al | BST        | RACT                                               | ٦                                                                                                                                                |    | $\mathbf{v}$         |

|    |            |                                                    |                                                                                                                                                  |    |                      |

| LI | ST (       | OF TA                                              | ABLES                                                                                                                                            |    | X                    |

| LI | ST (       | OF FIG                                             | GURES                                                                                                                                            |    | xi                   |

| CI | ΗΔΡ        | TER                                                |                                                                                                                                                  |    |                      |

|    |            |                                                    |                                                                                                                                                  |    |                      |

| 1. | INT        | RODU                                               | UCTION                                                                                                                                           |    | 1                    |

| 2. | BA         | CKGR                                               | ROUND                                                                                                                                            |    | 7                    |

|    | 2.1<br>2.2 |                                                    | Polarized Radars                                                                                                                                 |    |                      |

|    |            | 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4                   | Host Computer Sub-System                                                                                                                         |    | 11<br>13             |

|    | 2.3        | Phase-                                             | e-Tilt Modes of Operation                                                                                                                        |    | 15                   |

| 3. | AR         | RAY I                                              | FORMATTER BOARD                                                                                                                                  |    | <b>17</b>            |

|    | 3.1<br>3.2 | -                                                  | fications                                                                                                                                        |    |                      |

|    |            | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6 | Spartan-3E XC3S500E FPGA  Clocking Architecture  Expansion Connectors  External Memories  RS-232 Serial Ports  Ethernet Physical Layer Interface |    | 19<br>20<br>21<br>22 |

| 4. | MI         | CROB           | LAZE AN                | D EMBEDDED DEVELOPMENT KIT                                                        | . 24 |

|----|------------|----------------|------------------------|-----------------------------------------------------------------------------------|------|

|    | 4.1<br>4.2 |                |                        | Processor                                                                         |      |

|    |            | 4.2.1<br>4.2.2 |                        | tform Studio  Development Kit                                                     |      |

| 5. |            |                |                        | OCLOGY AND HARDWARE SYSTEM RE                                                     | . 26 |

|    | 5.1<br>5.2 | _              |                        | ogy                                                                               |      |

|    |            | 5.2.1          | Xilinx IP              | Cores                                                                             | 27   |

|    |            |                | 5.2.1.2 U<br>5.2.1.3 I | Memory Controllers  JART Core  Digital Clock Manager  First In First Out Memories | 28   |

|    |            | 5.2.2<br>5.2.3 |                        | eripheral (PF)erilog Modules                                                      |      |

|    |            |                | 5.2.3.2                | Γ/R Module Interface                                                              | 31   |

|    | 5.3        | T/R N          | Module FPC             | GA Architecture                                                                   | 33   |

| 6. | AR         | RAY I          | FORMAT                 | ΓER SOFTWARE                                                                      | . 36 |

|    | 6.1        | Bootin         | ng the Syste           | em                                                                                | 36   |

|    |            | 6.1.1          | Bootloade              | r                                                                                 | 36   |

|    | 6.2        | Micro          | Blaze Softw            | are Application                                                                   | 37   |

|    |            | 6.2.1          | Software I             | Functions                                                                         | 38   |

|    |            |                |                        | Jnicast Scheme                                                                    |      |

|    | 6.3        | Forma          | tter Data F            | Rates                                                                             | 45   |

| 7  | БТІ        | HFDN           | FT INTE                | REACE                                                                             | 40   |

|    | 7.1  |        | veight IP (lwIP)                     |      |  |  |

|----|------|--------|--------------------------------------|------|--|--|

|    | 7.2  |        |                                      |      |  |  |

|    | 7.3  | Comm   | unication Protocol                   | . 51 |  |  |

|    |      | 7.3.1  | Store Calibration Data               |      |  |  |

|    |      | 7.3.2  | Store Timing and Sequence Data       | . 53 |  |  |

| 8. | COI  | NCLU   | SIONS AND FUTURE WORK                | 55   |  |  |

|    | 8.1  |        | ısions                               |      |  |  |

|    | 8.2  | Future | Work                                 | . 55 |  |  |

|    |      |        |                                      |      |  |  |

| Al | PPEI | NDICE  | ES                                   |      |  |  |

| Α. | MIC  | CROBI  | LAZE SOFTWARE APPLICATION USER GUIDE | 56   |  |  |

|    |      |        | ORMATTER CUSTOM VERILOG MODULES      |      |  |  |

|    |      |        | ORMATTER BOARD USER MANUAL           |      |  |  |

| ΒI | BLIC | OGRA   | PHY                                  | 73   |  |  |

# LIST OF TABLES

| Table | Page                                                        |

|-------|-------------------------------------------------------------|

| 2.1   | Polarimetric pulsing sequences of dual-polarized radars     |

| 3.1   | Summary of Spartan-3E XC3S5000E FPGA Attributes             |

| 5.1   | Array Formatter Board ports                                 |

| 5.2   | Hardware utilization of the AFB FPGA                        |

| 6.1   | Host Computer commands for MicroBlaze software functions 45 |

| A.1   | PF software registers mapped to verilog module ports        |

# LIST OF FIGURES

| Figure | Page                                                                   |

|--------|------------------------------------------------------------------------|

| 1.1    | Modern radar system                                                    |

| 1.2    | Scanning ability of electronically-scanned phased-array radars $[5]$ 3 |

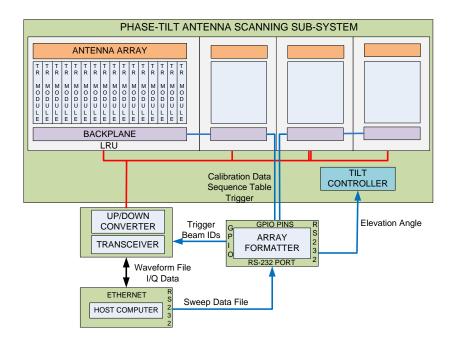

| 1.3    | Phase-Tilt radar system block diagram                                  |

| 1.4    | Phased-Array Controller/Formatter                                      |

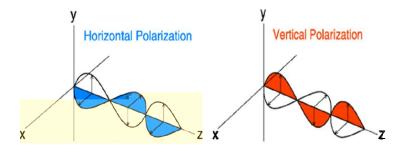

| 2.1    | Horizontal and vertical polarizations of radar signals [10] 8          |

| 2.2    | Phase-Tilt radar system architecture                                   |

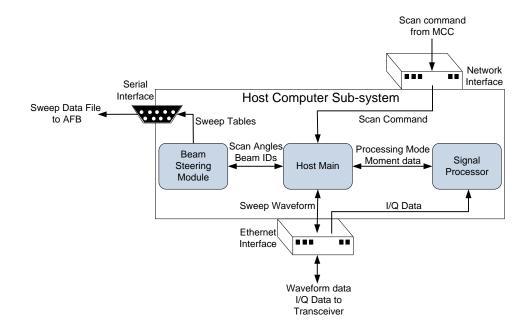

| 2.3    | Host Computer sub-system                                               |

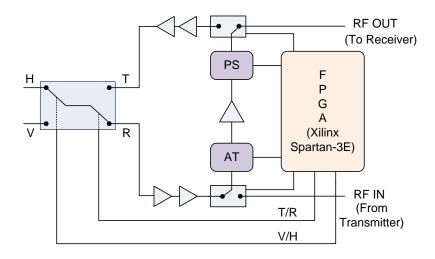

| 2.4    | T/R Module block diagram [11]                                          |

| 2.5    | Phase-Tilt antenna array                                               |

| 2.6    | Block diagram of the Array Formatter Board                             |

| 2.7    | Transceiver sub-system                                                 |

| 3.1    | Spartan-3E Starter Kit Board [25]                                      |

| 3.2    | Clock Regions, DCM sites, and I/O banks in the FPGA $\dots\dots 20$    |

| 3.3    | RS-232 serial ports                                                    |

| 3.4    | Ethernet PHY with RJ-45 connector [25]                                 |

| 5.1    | Array Formatter system architecture                                    |

| 5.2    | Serial data format                                                     |

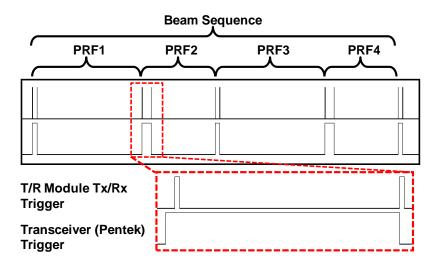

| 5.3    | Timing state machine trigger outputs                                   |

| 5.4 | T/R Module FPGA34                                                           |

|-----|-----------------------------------------------------------------------------|

| 5.5 | T/R Module memory bits                                                      |

| 5.6 | T/R Module sequence table bits                                              |

| 6.1 | Bootloader illustration                                                     |

| 6.2 | Data format for updating T/R Module memory                                  |

| 6.3 | Data format for writing port registers                                      |

| 6.4 | Data format for reading port registers                                      |

| 6.5 | Data format for writing address register                                    |

| 6.6 | Timing state machine output trigger plot                                    |

| 6.7 | Diagram showing the relative time periods during the radar operation phase  |

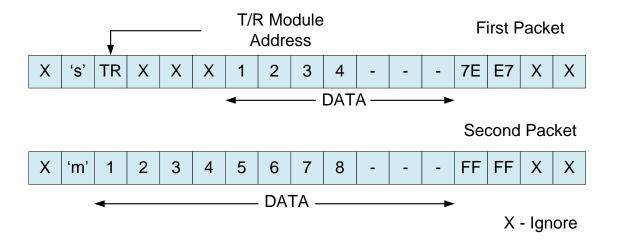

| 7.1 | Ethernet packets for Store Calibration Mode                                 |

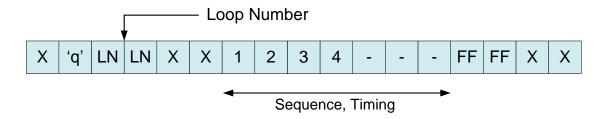

| 7.2 | Ethernet packet for Store Timing and Sequence Data54                        |

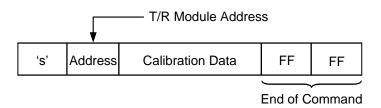

| A.1 | Host Computer data format for storing calibration data in Formatter         |

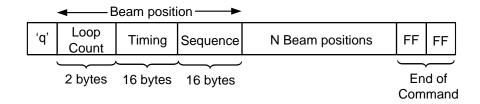

| A.2 | Host Computer data format for storing sequence table and timing information |

| A.3 | Laboratory setup to test AFB communication                                  |

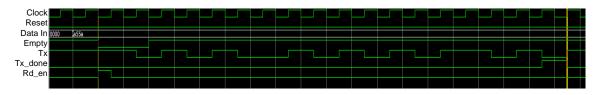

| B.1 | T/R Module transmitter waveform                                             |

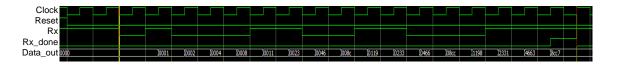

| B.2 | T/R Module receiver waveform                                                |

| В.3 | Timing state machine waveform                                               |

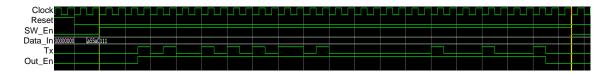

| B.4 | Transceiver interface transmitter waveform                                  |

| R 5 | Clock divider waveform 70                                                   |

#### CHAPTER 1

#### INTRODUCTION

State-of-the-art weather prediction systems rely on the use of advanced radar systems for efficient and accurate information. Radar systems study the quantity of interest by transmitting an electromagnetic signal in space and detecting the echoed signal received from the target [17]. The comparison of transmit and receive signals reveals crucial target information, such as location, size, etc. The process is repeated several times to increase the accuracy of the target information collected. Current radar systems are digitally controlled using modern computers and sophisticated data acquisition systems. A modern radar system typically consists of a computer, an antenna panel for transmitting and receiving signals, and a data acquisition system for processing digital and analog signals as shown in Figure 1.1. The Data Acquisition Systems consists of Analog to Digital Converters, analog and digital circuitry, and hardware support to perform complex signal processing algorithms. They also require several high-speed interfaces to communicate with different radar components.

Figure 1.1. Modern radar system

Radars used for atmospheric sensing gather critical weather-related information, that can be used for weather monitoring and forecasting. The information collected by

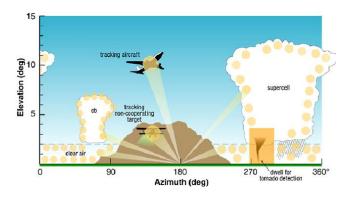

weather radars can detect hazardous weather events such as tornadoes. Traditionally, these radars have been mechanically controlled, in which the antenna panel is tilted by a motor controller [5]. A typical scanning cycle of mechanically-tilted weather radars is as follows: The radar is first tilted in the elevation plane, and samples a small region of the atmosphere by transmitting a beam of energy, and then listening to the received energy for a certain period of time. The radar is then moved in the azimuth plane, and this process is continued across multiple azimuth beam positions, until the radar completes a 360 degree scan in the azimuth plane. The radar then changes the elevation angle to perform another azimuth scan. In this way, many azimuth scans are performed to scan the entire region of interest in the atmosphere. Such radars typically consume several minutes to perform a full cycle scan in the atmosphere [5] [7]. Alternative scanning techniques have been explored in the past to address the limitations of mechanically-scanned systems. Phased-Arrays are an emerging breed of radars, that have received significant attention from the radar community by virtue of their fast scanning abilities [8]. They have an array of antennas fed by signals, whose relative phases are varied to produce radiation patterns in desired directions and cancel patterns in other directions.

Phased-Array radars can send multiple beams at the same time without tilting or moving the radar mechanically as shown in Figure 1.2 [5]. Current state-of-the-art two-dimensional phased-array antenna systems are capable of electronic beam steering in both the azimuth and elevation planes. Radio Frequency (RF) circuitry such as phase-shifters and attenuators facilitate electronic beam steering in these radars. Typical scanning rates of phased-arrays are in the order of seconds, thus delivering better scanning performance when compared to their mechanical counterparts [5]. The ability to "dwell" or repeatedly sense the same quantity of interest increases the accuracy of the data sampled by these radars. Also, the failure rate of phased-

arrays is much lower than that of mechanically-tilted radars, because of the absence of mechanical components like motor controllers [5] [7].

Figure 1.2. Scanning ability of electronically-scanned phased-array radars [5]

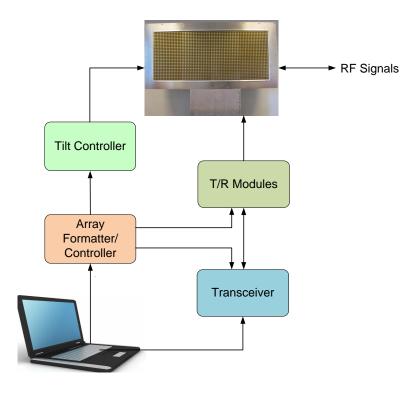

The electronically-scanned phased-array radars, however, suffer from two main limitations - (1) the high-cost of the active electronic circuitry behind the antenna array, and (2) the design of highly complex digital sub-systems to facilitate electronic beam steering. CASA has proposed to address these issues by designing a low-cost phased-array radar system called "Phase-Tilt" [8]. The Phase-Tilt radar scans electronically only in one dimension (azimuth), thereby, reducing the amount of active electronic circuitry behind the antenna array. Scanning in the elevation plane is performed mechanically using a tilt controller. The block diagram of the Phase-Tilt radar system is shown in Figure 1.3. The Phase-Tilt radar consists of the following sub-systems: Host Computer, Transceiver, Array Controller or Formatter, Tilt Controller, and the Phase-Tilt Antenna array [8]. The linear antenna array is a planar structure of  $64 \times 32$  passive antenna elements [14] [15]. The array consists of 64 columns; each column has 32 antennas. The antenna columns are controlled by active electronic circuits called Transmit/Receive Modules (T/R Modules). There are 64 T/R Modules for 64 antenna columns; a T/R Module controls the 32 antenna elements in the column. The tilt controller is used for tilting the antenna array in the elevation plane. The Transceiver sub-system receives the RF signals from the

Figure 1.3. Phase-Tilt radar system block diagram

antenna array and performs all the relevant signal processing tasks needed for post processing of weather data.

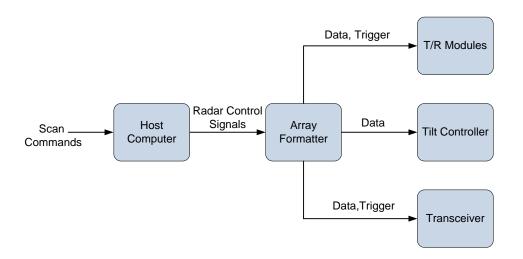

The master controller in this system is the Array Controller or the Formatter which controls and synchronizes the different radar sub-systems with high-speed control, trigger, and switch signals as shown in Figure 1.4. The Formatter interfaces the computer to all the radar sub-systems. User commands from the computer are broken down, interpreted, and translated by the Formatter to data and trigger signals. The aim of this thesis is to design an Array Formatter for CASA's Phase-Tilt radar system.

The functions of the Array Formatter are: storing and transferring data files, updating beam positions, sending timing and switch signals to trigger events, and sending control signals to control the different radar sub-systems. The Formatter is the gateway for the Host Computer to communicate with all the other radar sub-systems. The details of the roles of the Formatter are described in Chapter 2 and

Figure 1.4. Phased-Array Controller/Formatter

Chapter 6. A typical Array Formatter requires hardware resources such as microcontrollers or microprocessors for data acquisition and control, peripheral interfaces for communicating with radar sub-systems, and sufficient memory for storing data and timing information [16].

Field Programmable Gate Arrays (FPGA)-based radar controllers are used these days by virtue of their fine grained and course grained parallelism, and support for high-speed interfaces [9]. FPGAs also offer a high degree of flexibility at an affordable cost. In this project, we use a soft microprocessor-based system on the FPGA to implement an Array Formatter for CASA's Phase-Tilt radar system. A soft microprocessor is a microprocessor that is implemented in the FPGA fabric. The soft microprocessor is the central control agent in the Formatter design. This FPGA-based system will be the first prototype used as the Array Formatter for phased-array antenna systems.

The rest of the thesis document is organized as follows: Chapter 2 describes the CASA Phase-Tilt Radar System. The Array Formatter Board specifications and features are described in Chapter 3. Chapter 4 introduces the MicroBlaze soft processor by Xilinx and also the environment used to create the embedded system on the

FPGA. Chapter 5 outlines the design methodology adopted in this thesis work, and also the FPGA system architecture of the Array Formatter. The Array Formatter software has been discussed in Chapter 6. Chapter 7 describes the ethernet interface between the Array Formatter and the Host Computer in detail. Chapter 8 concludes the thesis with an overview of the future work.

#### CHAPTER 2

#### BACKGROUND

For several decades, weather sensing systems have relied on the use of long-range, high-power radars to sense the atmosphere. Conventional radars transmit high-power radar beams that traverse several hundreds of miles in space in a straight path. While the beam continues to travel along straight lines, the earth's surface beneath the beam begins to curve away [16]. Radars are affected by the earth's curvature that limits their range of scanning, and also their ability to cover the lower regions of the atmosphere. The Center for Collaborative Sensing of the Atmosphere (CASA), an Engineering Research Center established by the National Science Foundation, is developing a dense network of small low-power radars to overcome coverage gaps due to earth's curvature and complex terrains [16]. CASA radars are separated by a few tens of kilometers apart over a large area, which enables them to get high spatial and temporal resolution views even in the lower atmospheric regions. The Center has currently deployed a network of four mechanically-scanned radars in Oklahoma. The next step in the evolution of distributed radar systems is the use of solid-state electronics and low-cost, electronically-scanned phased-array radars.

The active electronic circuits used in current phased-arrays are the solid-state Transmit/Receive Modules [11]. The T/R Modules control the antenna array by varying the antenna parameters such as phase, amplitude, and electric field polarizations. While the phase and amplitude adjust the antenna beam positions, the electric field polarization of the received signal gives structural characteristics of the scattering target. The electric field polarization of an electromagnetic (EM) wave refers to

Figure 2.1. Horizontal and vertical polarizations of radar signals [10]

the locus of points of the electric field vector that lies in a plane perpendicular to the direction of propagation of the wave. Weather radars usually transmit radiations whose electric field vector lies either in the horizontal or vertical plane as shown in Figure 2.1 [10].

#### 2.1 Dual-Polarized Radars

Dual-polarized radars have the ability to transmit or receive signals in either polarization. The variable transmit and receive electric field polarizations in the signals allows dual-polarized radars to measure hydrometeor characteristics, such as shape, size, and differentiate thermodynamic phase [6]. This helps in determining rainfall rates, and sometimes discriminate between between liquid or ice phases of the hydrometeor [6]. A weather radar usually transmits in one polarization and receives in the other or same polarization depending on the scattering characteristics of the target. The radar follows a sequence of Transmit (T) and Receive (R) modes in either Horizontal (H) or Vertical (V) polarization to determine the information about the hydrometeor. There are four possible polarimetric combinations for a dual-polarized radar which are:

- 1. TH Transmit in Horizontal Polarization

- 2. RH Receive in Horizontal Polarization

#### 3. TV - Transmit in Vertical Polarization

#### 4. RV - Receive in Vertical Polarization

The science of radar polarimetry is the analysis of these transmit and receive electric field polarization combinations, also called the radar polarimetric pulsing sequence. The sequence can implement different radar functionalities such as "Single," "Cross," or "Alternate." In Single Polarization the radar transmits and receives signals in the same polarization for multiple cycles; a cycle is a pair of Transmit-Receive states of the radar. Alternate Polarization refers to alternating the polarization of the radar between consecutive cycles. Cross Polarization refers to transmitting and receiving signals in different polarizations within the same cycle. Table 2.1 shows sample polarimetric pulsing sequences implementing different functionalities in a dual-polarized radar [10].

Table 2.1. Polarimetric pulsing sequences of dual-polarized radars

| Cycle | Single  | Alternate | Cross   |

|-------|---------|-----------|---------|

| 1     | Т=Н К=Н | Т=Н К=Н   | T=H R=V |

| 2     | Т=Н К=Н | T=V R=V   | T=V R=H |

| 3     | Т=Н К=Н | Т=Н К=Н   | T=V R=H |

| 4     | Т=Н К=Н | T=V R=V   | T=H R=V |

### 2.2 Phase-Tilt System Overview

CASA has developed the X-band Phase-Tilt radar that operates at a frequency of 9.36 GHz in an effort to create a low-cost, electronically-scanned, dual-polarized, phased-array antenna scanning system. The Phase-Tilt radar system architecture is as shown in Figure 2.2.

The Phase-Tilt radar is used for distributed, collaborative, and adaptive sensing of the atmosphere. The radar is controlled by a central Meteorological Command and

Figure 2.2. Phase-Tilt radar system architecture

Control Agent (MCC). The user scan preferences are encoded in the MCC. Depending on the preferences of different users and the state of the atmosphere, the MCC creates a "scan task." A scan task is typically a sub-volume of the atmosphere which is of particular interest to the user. The MCC creates the necessary scan command from the task, and issues the command to each one of the radar Host Computers in the network.

The Host Computer controls its radar by translating the scan commands to control files and control structures. The computer uploads these files to the AFB, and then the AFB becomes the master controller which synchronizes the different sub-systems of the radar. The next few sections describe each sub-system in detail.

#### 2.2.1 Host Computer Sub-System

A block diagram of the Host Computer sub-system is shown in Figure 2.3. The Host Computer interfaces the human user to the rest of the system. In this project, the computer is interfaced with the Array Formatter and the Transceiver using the

Figure 2.3. Host Computer sub-system

RS-232 and Ethernet ports respectively. The waveform data file is uploaded by the computer to the Transceiver. The signal processing component of the host computer sub-system performs real-time signal processing of the digital I and Q data from the Transceiver. The Beam Steering Module in the system records the current and future beam locations, and also calculates the "sweep" data structure (a sweep is a sequence of azimuth beam positions) from the scan command created by the end user. The sweep data file is uploaded to the Formatter via the computer's RS-232 serial interface.

#### 2.2.2 Phase-Tilt Antenna Scanning Sub-system

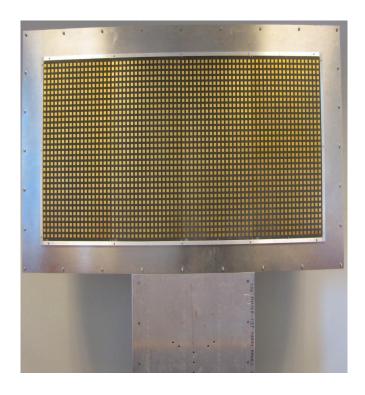

The Phase-Tilt antenna scanning sub-system consists of 64 T/R Modules, antenna elements, and a Mechanical Actuator or Tilt Controller as shown in Figure 2.2. A picture of the passive antenna array is shown in Figure 2.5. The antenna scanning sub-system consists of four Line Replaceable Units (LRUs). An LRU is a black box of components that can be easily replaced or replicated depending on the needs of

the application. Each LRU consists of  $0.25m \times 0.50m$  passive antenna array arranged as 16 columns and 32 rows, 16 T/R Modules that feed the 16 antenna columns, RF and DC power distribution backplane, and AC to DC power converters [14] [15]. The 64 T/R Modules are grouped into four LRUs. A T/R Module consists of three components: RF circuits, such as phase-shifters and attenuators, to set the amplitude and phase of the antenna columns, T/R and V/H switches to switch the the antenna columns between Transmit and Receive modes, and Vertical and Horizontal polarizations respectively, and an integrated Field Programmable Gate Array (FPGA) to control these circuits and interface with other radar components. The components of a T/R Module is shown in Figure 2.4 [11].

Figure 2.4. T/R Module block diagram [11]

The FPGA in the T/R Module has an internal memory, which is configured as a look-up table to store the amplitude and phase coefficients of the antenna column. The FPGA also maintains a sequence table which holds the address of the T/R Module memory. The sequence table is a data structure which contains the T/R Module states for the polarimetric pulsing sequence to be performed by the radar.

Figure 2.5. Phase-Tilt antenna array

#### 2.2.3 Array Formatter Board (AFB)

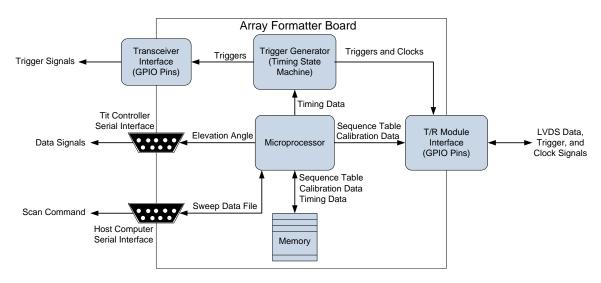

A block diagram of the AFB is shown in Figure 2.6. The Array Formatter assumes master control of the entire radar system. The FPGA-based Formatter provides the required control and timing signals for the radar, and interfaces the Host Computer with the antenna scanning sub-system. The sweep data file from the computer is broken down by the Formatter to create sequence tables. The sequence table is broadcast to all the 64 T/R Modules. All the T/R Modules switch between their states by triggers sent by the AFB's Timing State Machine (TSM). The TSM also triggers the Transceiver sub-system. The Formatter stores the calibration data in its memory, which contains the phase and amplitude coefficients for each of the 64 T/R Modules. The calibration data is conveyed to each T/R Module individually by the Formatter. The Tilt Controller is also controlled by the AFB to update the current and future elevation angles

The Formatter is interfaced to the T/R Modules and the Transceiver via its General Purpose I/O (GPIO) pins on-board, which is capable of sending Low-Voltage Differential Signals (LVDS) for fast communication. The Formatter also interfaces with the Tilt Controller via its second RS-232 port. The elevation angle of the Tilt Controller is adjusted before pulsing the radar.

Figure 2.6. Block diagram of the Array Formatter Board

#### 2.2.4 Transceiver Sub-system

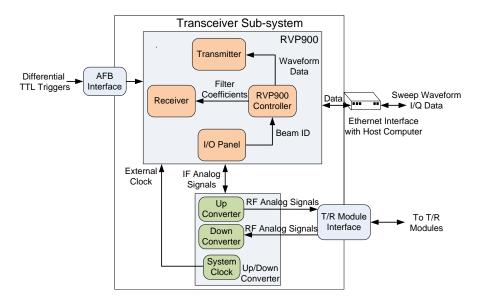

The Transceiver sub-system consists of a commercially available Vaisala's RVP900 system [18], and an up-down converter as shown in Figure 2.7. The RVP900 creates the transmit-modulated waveform, digitizes the received signal, and demodulates the digitized signal [8]. The three inputs feeding the RVP900 are an external clock, differential TTL signals, and gigabit Ethernet as shown in Figure 2.7. The AFB sends the differential input TTL signal as a trigger to the transceiver. The gigabit Ethernet is used for interfacing the RVP900 system with the computer that uploads the waveform table and downloads the I/Q data.

The up-down conversion system is made from commercial off-the-shelf components, such as amplifiers, oscillators, mixers, etc. The up-down converter system

converts the Intermediate Frequency (IF) analog signals to Radio Frequency (RF) analog signals when the radar is in transmit mode, and does the reverse conversion when the radar is in the receive mode. The reference clock in the up-down conversion system is used as the clock input for the RVP900 as shown in Figure 2.7.

Figure 2.7. Transceiver sub-system

### 2.3 Phase-Tilt Modes of Operation

The Phase-Tilt radar fundamentally operates in two modes - Initialization and Operation.

Initialization: Communication paths between each sub-system and component in the radar system are set up. Registers are reset, all amplifiers are turned off, and each sub-system has its own power up sequence to be performed during the initialization phase. A major part of the initialization process is spent in updating the T/R Module memory with calibration data (phase and amplitude coefficients). The calibration data from the Host Computer is conveyed to the T/R Modules via the Array Formatter Board. The AFB stores the calibration data in its memory and routes it to its T/R Module interface through its LVDS bus in a point to point (unicast)

data format. The addressed T/R Module echoes the message back to the Formatter Receiver, which verifies the correctness of the data transmitted. The error check enables correct loading of the T/R Module memory as initialization is an important step towards successful and reliable radar operation. The T/R Module memory is a look-up table that is indexed by the sequence table to populate the antenna columns with phase, amplitude, and polarization diversity during the radar operation mode. The Formatter updates the T/R Module memory periodically or whenever the system performance changes due to external parameters.

**Operation:** The scan command which is a sequence of azimuth beam positions is translated to appropriate sweep data files and then uploaded to the AFB memory by the computer system. Each azimuth beam position has an associated 8 polarization sequences (sequence table), the number of times the sequence is repeated (the loop count), the transmit pulse length, and the Pulse Repetition Time (PRT), which is the time elapsed between the beginning of one pulse to the beginning of the next pulse. The AFB first loads the elevation to the Tilt Controller, before broadcasting the sequence tables to all the T/R modules in a point to multipoint (broadcast) data format. The pulse length, loop count, and PRT are given as inputs to the TSM. Once all the T/R Module sequence tables have been updated, the Formatter starts the TSM to pulse the radar. One pass through the TSM steps the T/R Modules through the sequence table once, generating 4 pulses. The TSM repeats the sequence until the loop count decrements to zero. The loop count number is chosen by the user depending on the number of pulses needed for a particular beam location. Once the loop count decrements to zero, the Formatter reads the second beam position from its memory, and broadcasts the associated sequence to the T/R Modules, and the whole process repeats. When all the azimuth beam positions for a particular elevation angle are read out of the memory, the computer uploads the next scan command to the Formatter.

#### CHAPTER 3

#### ARRAY FORMATTER BOARD

This chapter describes the Array Formatter Board in detail. The specifications from a radar standpoint are listed below first, followed by the features of the board used for implementing and testing the Formatter design.

#### 3.1 Specifications

- 1. Support for real-time data acquisition and processing.

- 2. Support for high-speed and low-speed peripherals for communicating with different radar components.

- 3. Support for debug interfaces for the system development.

### 3.2 Array Formatter Board Features

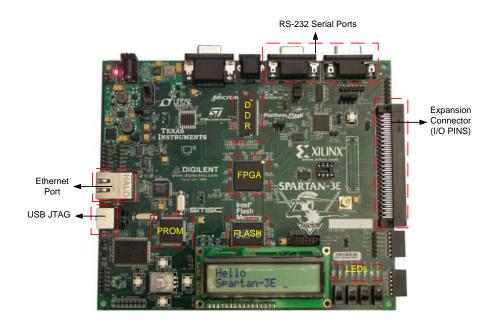

The Spartan-3E Starter Kit board by Xilinx [25] is used for designing and testing the Array Formatter. The Spartan-3E Starter Kit as shown in Figure 3.1, is a development board that can be used for various embedded processing applications, and includes many peripherals, such as memory controllers, general purpose I/Os, and bus interfaces.

Some of the key components of the board are Spartan-3E FPGA (XC3S500E), 50 MHz on-board oscillator, 16 MB Parallel Flash (FLASH), 64 MB DDR SDRAM (DDR), 4 MB Xilinx Serial Platform Flash PROM, two RS-232 Serial Ports, Ethernet 10/100 Phy, JTAG USB download, and expansion connectors for I/Os.

Figure 3.1. Spartan-3E Starter Kit Board [25]

The serial port is used for debugging and communicating with the computer. The other serial port is used for communicating with the Tilt Controller. The expansion I/O connector is used for interfacing the T/R Modules with the board. The 64 MB DDR SDRAM is used as the AFB memory that stores calibration data files, sequence tables, and also the timing information for the TSM. The DDR SDRAM is also used for executing the software application of the MicroBlaze processor, which is explained in chapter 6. 16 MB Parallel Flash is used to store the MicroBlaze software application. The 4 MB Serial Platform Flash PROM is used for storing the FPGA configuration file.

#### 3.2.1 Spartan-3E XC3S500E FPGA

The XC3S500E FPGA is a part of the Spartan-3E family of FPGAs by Xilinx. The Spartan-3E FPGA family architecture fundamentally consists of five programmable logic elements [24]:

Configurable Logic Blocks (CLBs) contain flexible LUTs that implement logic and memory. CLBs can implement a wide variety of functions and also store data.

Input/Output Blocks (IOBs) control the signal flow between the I/O pins and the internal logic. It supports a variety of signaling standards including Low Voltage Differential Signaling (LVDS) standards for high speed signaling. The Formatter communicates with the T/R Modules using the LVDS standard.

Block RAMS that can be used for data storage.

Multiplier Blocks can accept two 18-bit inputs to calculate the product.

**Digital Clock Managers (DCMs)** provide high quality self-calibrating clock signals, and digital solutions for delaying, phase-shifting, multiplying, and dividing the clock signals. DCMs are used for providing three different clock frequencies in the system as required by the MicroBlaze system, DDR SDRAM memory controller, and the T/R Module interface bus. The details of the clocking architecture are explained in section 3.2.2.

The summary of the XC3S500E FPGA attributes is given in Table 3.1.

Table 3.1. Summary of Spartan-3E XC3S5000E FPGA Attributes

| Feature               | Count  |

|-----------------------|--------|

| Total Gates           | 500K   |

| Total Cells           | 10,476 |

| Total CLBs            | 1,164  |

| Total Slices          | 4,656  |

| Distributed RAM Bits  | 73K    |

| Block RAM Bits        | 360K   |

| Dedicated Multipliers | 20     |

| Total DCMs            | 4      |

| User I/Os             | 232    |

#### 3.2.2 Clocking Architecture

The Spartan-3E Starter Kit board supports up to three clock sources:

1. An on-board 50 MHz clock oscillator.

- 2. External clock can be given via the SMA connector.

- 3. Optionally install an 8-pin DIP-style clock oscillator.

A 100 MHz external clock signal is supplied to the Formatter via the SMA connector on the board.

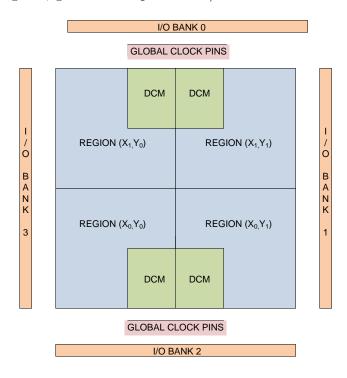

Appropriate I/O and clock regions are chosen for interfacing the FPGA with the external memories, external clock oscillator, and the I/O expansion header to avoid excessive delays in the clock path. There are four DCM sites available in the FPGA. The four clock regions, global clock pins and I/O banks are shown in Figure 3.2.

Figure 3.2. Clock Regions, DCM sites, and I/O banks in the FPGA

#### 3.2.3 Expansion Connectors

The Spartan-3E Starter Kit board has support for several expansion connectors for conveniently interfacing with other off-board components. There is support for three I/O expansion headers:

- 1. A Hirose 100-pin expansion connector with support for 43 FPGA user-I/O pins, including 15 LVDS I/O pins and 2 input only pins.

- 2. Three 6-pin peripheral module connections.

- 3. Landing pads for Agilent connector-less probes.

The Hirose 100-pin expansion connector is used for interfacing the T/R modules and the Transceiver. Data and clock signals in LVDS format are exchanged serially between the T/R Modules and the board.

#### 3.2.4 External Memories

The Spartan-3E Starter Kit board includes three external memory chips that are used in this project. The first is a 512Mbit ( $32M \times 16$ ) DDR SDRAM by Micron [12] with a 16-bit data interface. The DDR SDRAM chip is used for storing calibration data, sequence tables, timing information, and the loop count value. The microprocessor in the system also executes its software code from the DDR SDRAM. All the DDR SDRAM pins are connected to the I/O Bank 3 of the FPGA [25].

The second memory chip used in this project is a 16 MB Intel StrataFlash (Parallel Flash). The non-volatile Parallel Flash provides a number of options to the designers as listed below.

- 1. Support for storing a single FPGA configuration file.

- 2. Support for storing two different configuration files to switch dynamically between two FPGA configurations using the board's multi-boot feature.

- 3. Support for storing the microprocessor software code, and also shadows the code to the DDR SDRAM, from where it can be executed by the processor.

- 4. Support for storing any non-volatile data from the FPGA.

In this project, we use the Parallel Flash for storing the processor code, and also to shadow the code to the DDR SDRAM memory. The processor eventually executes from the DDR SDRAM and more details about this process are given in Chapter 6. The third memory chip used in this project is on-board 4 MB Xilinx XCF04S Serial Platform Flash PROM. In this project, the PROM is used to store the FPGA configuration file. The FPGA is configured from the PROM in the Master Serial configuration mode [25]. Details about this configuration mode can be found in [25].

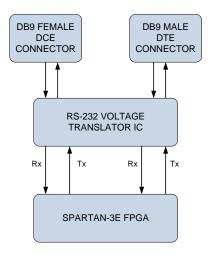

#### 3.2.5 RS-232 Serial Ports

The Spartan-3E Starter Kit board has two RS-232 serial ports: a male DB9 DTE connector and female DB9 DCE connector as shown in Figure 3.3. The DTE connector is used for interfacing the AFB with the Host Computer using a null modem serial cable. The DCE connector is used for interfacing the AFB with the mechanical actuator. The output voltage levels of the FPGA is in LVCMOS or LVTTL standards, which are converted to the RS-232 voltage standards by the voltage converter IC as shown in Figure 3.3. Likewise, when the FPGA receives serial data from either of the ports, the RS-232 voltage levels are converted back to LVCMOS standard by the voltage translator IC.

Figure 3.3. RS-232 serial ports

#### 3.2.6 Ethernet Physical Layer Interface

Figure 3.4. Ethernet PHY with RJ-45 connector [25]

The AFB also has support for an Ethernet physical layer to implement the standard Ethernet interface. The board includes a Standard Microsystems LAN83C185 10/100 Ethernet physical layer (PHY) interface and an RJ-45 connector as shown in Figure 3.4. All timing is controlled by the on-board 25 MHz crystal oscillator. The Ethernet interface is implemented in this work to enable high-speed communication between the Formatter and the Host Computer. This interface can replace the serial link to achieve a faster and more reliable communication channel. Details about the implementation of the ethernet interface are given in Chapter 7.

# CHAPTER 4

#### MICROBLAZE AND EMBEDDED DEVELOPMENT KIT

This chapter gives a brief overview of the MicroBlaze-soft processor by Xilinx and also the environment used to create the embedded system on the FPGA.

# 4.1 MicroBlaze Soft Processor

The central processing component of the AFB is a soft microprocessor by Xilinx called MicroBlaze. The XC3S500E Field Programmable Gate Array has support for MicroBlaze, which is completely reconfigurable and built by combining various logic cores inside the FPGA. The MicroBlaze processor is an embedded soft 32-bit RISC processor [20]. The processor has high-speed instruction and data buses to guarantee access to instructions and data simultaneously both on and off the chip.

MicroBlaze supports both general purpose and special purpose registers. The processor has a three stage pipeline and a 32-bit high speed bus [20]. Two of the bus interfaces supported by MicroBlaze that are used in this project are:

**Processor Local Bus (PLB):** A fully synchronous bus that gives access to processor peripherals.

Local Memory Bus (LMB): A high-speed bus that connects MicroBlaze to peripherals like Block RAMs for high-speed access.

# 4.2 Embedded Development Kit

The Xilinx Embedded Development Kit (EDK) is a design suite that helps in designing a complete embedded system [22]. The two main tools used in EDK are Xilinx Platform Studio and Software Development Kit.

#### 4.2.1 Xilinx Platform Studio

The Xilinx Platform Studio (XPS) facilitates the design of the hardware components of the embedded processor system on an FPGA. The tool provides a graphical user interface for interconnection of the various components of the system, such as processors, peripherals, and buses. Apart from the standard IP cores that are available in the IP catalog [19], the XPS allows the creation of custom peripherals that can be included in the system. The XPS uses IP Interface (IPIF) libraries to implement basic functionalities between processors and peripherals. These are optimized and parameterized to give a simplified Bus Protocol called IP Interconnect (IPIC) [22].

#### 4.2.2 Software Development Kit

The Xilinx Software Development Kit (SDK) provides an environment for developing embedded software applications. In essence, the SDK helps in developing software for the hardware system developed in XPS. A Software Platform is the lowest level of the software stack that includes all the drivers and libraries of the components of the embedded system. Many applications can share the same software platform. A standalone software platform is created to execute single threaded applications on a single processor system.

# CHAPTER 5

# DESIGN METHODOLOGY AND HARDWARE SYSTEM ARCHITECTURE

# 5.1 Design Methodology

The hardware components of the embedded system are designed using XPS and the software application is developed using SDK as explained in section 4.2. The software application is developed using C. The custom hardware logic in the FPGA is designed in Verilog, and the embedded system designed in EDK is instantiated as a module in the main Xilinx ISE project.

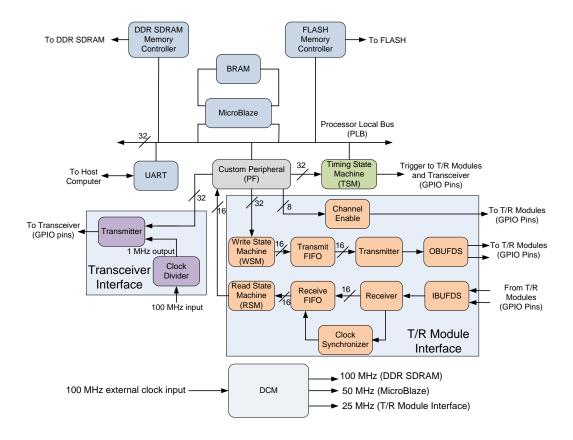

# 5.2 AFB FPGA Hardware System Architecture

The Array Formatter design is implemented on the Xilinx Spartan-3E FPGA and the system architecture is illustrated in Figure 5.1. The FPGA system architecture has the following key components:

- 1. MicroBlaze Processor.

- 2. Xilinx IP Cores such as UART, Digital Clock Managers, Memory Controllers, and FIFOs [19].

- 3. Custom Peripheral (PF)

- 4. Custom Verilog Modules (T/R Module Interface, Timing State Machine, and Transceiver Interface)

Details of the MicroBlaze soft processor have been described in section 4.1. The next few sub-sections describe the other components in the system.

Figure 5.1. Array Formatter system architecture

#### 5.2.1 Xilinx IP Cores

The Xilinx IP cores facilitate ease of design and integration into the system. This section describes the various IP blocks that have been used to design the system on the Formatter FPGA.

#### 5.2.1.1 Memory Controllers

Xilinx IP cores such as Multi-Port Memory Controller for the DDR SDRAM and the External Memory Controller for Flash are used for controlling the two external memory chips [19]. These two cores are attached to the Processor Local Bus (PLB) of the system.

# **5.2.1.2** UART Core

The Xilinx UART core is used for communicating with the Host Computer. It has an adjustable baud rate and experiments are conducted at a rate of 115 Kbps.

#### 5.2.1.3 Digital Clock Manager

The Digital Clock Managers are used to provide three different clock frequencies: 25 MHz, 50 MHz, and 100 MHz. The FPGA is triggered by an external 100 MHz clock oscillator, and the DCM generates three output frequencies: 25 MHz, 50 MHz, and 100 MHz. The MicroBlaze system runs at 50 MHz, while the T/R Module interface runs at 25 MHz to satisfy the serial bus load requirements connected to the T/R Modules, and the DDR SDRAM memory controller runs at 100 MHz as the operating frequency range of the memory chip is between 75 MHz and 133 MHz [12].

#### 5.2.1.4 First In First Out Memories

Xilinx FIFO cores are used in a system whenever data or control signals are exchanged between two different clock domains. Two FIFO cores (Transmit and Receive FIFOs) are used in this system to facilitate communication between the MicroBlaze processor and the T/R Module interface. The Transmit FIFO buffers the data to be transmitted to the T/R Modules. Likewise, the Receive FIFO holds the data received from the T/R Modules before being read out by the processor.

# 5.2.2 Custom Peripheral (PF)

The Custom Peripheral, called PF in this system, is added to facilitate communication between the processor and the rest of the custom hardware Verilog modules (T/R Module Interface, Transceiver Interface and Timing State Machine). These Verilog modules are described in the next section. In order to add a custom peripheral to the PLB of the MicroBlaze system, the "Create Custom Peripheral" wizard is used in Xilinx XPS [22]. This wizard also generates the necessary device drivers that

are used in developing the software application for the MicroBlaze processor. The processor communicates with PF by making use of PF's software accessible registers. In this work, the PF is configured to have 30 software accessible registers. These registers are mapped to the different ports of the custom Verilog modules, and are listed in table A.1 in Appendix A. In order to access this peripheral in software, the applications makes use of the APIs defined in PF's device driver. The software APIs used for accessing this peripheral are described in Appendix A. After creating this peripheral, the Xilinx PLB interface modules are automatically included in the HDL files of PF. These PLB interface modules take care of all bus transactions between the processor and the peripheral.

#### 5.2.3 Custom Verilog Modules

The custom Verilog modules in this system are used for communicating with the T/R Modules and the Transceiver. The three interfaces are described in the following sections.

#### 5.2.3.1 T/R Module Interface

The Array Formatter Board communicates with the T/R Modules to convey the sequence table information, update each T/R Module memory with calibration coefficients, and trigger the switching of T/R Modules during the operation mode of the Phase-Tilt radar.

The Transmitter and Receiver blocks are used for transferring data between the Formatter and T/R Modules. A similar pair of Transmitter and Receiver blocks is configured in the FPGA of the T/R Modules. The Transmitter block on either side is the master, which sends data and clock using the LVDS standards via the I/O pins on each board.

Two Finite State Machines [13] are implemented to control the Transmit and Receive FIFOs in this interface. The PF loads the Write State Machine (WSM) with a 32-bit data for the T/R Modules. The WSM then writes this data as two 16-bit words to the Transmit FIFO. The Transmitter module is a serial shift-out register that reads the 16-bit data from the Transmit FIFO, and sends the data serially as LVDS signals through the Xilinx OBUFDS (Output Buffer for Differential Signalling) primitive. Likewise, in the receive chain, the LVDS data signals from the T/R Modules are converted into a single ended signal by the Xilinx IBUFDS (Input Buffer for Differential Signalling) primitive. The Receiver module performs the conversion to a 16-bit data, and then writes it to the Receive FIFO. The Read State Machine (RSM), which is controlled by PF, reads the value out of the Receiver FIFO. The Receiver operates at 25 MHz and the Receiver FIFO operates at 50 MHz with a clock synchronizer between the two modules.

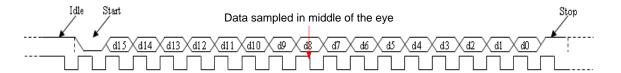

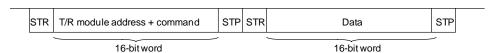

Serial Data Format: The serial data transferred between the Formatter and the T/R Modules follows a simple protocol, where the message is represented as 18 bits as shown in Figure 5.2. The message includes 1 start bit, 16 data bits, and 1 stop bit. The start bit, which is a zero, indicates the start of data transmission. This is followed by the 16-bit data to be transmitted. The transmission ends with the stop bit, which is a one. Data is sampled at the negative edge of the clock cycle, and the last clock is used to manage the data flow in the Receiver.

Figure 5.2. Serial data format

#### Channel Enable:

The array of sixty-four T/R Modules is arranged as two groups of 32 Modules each. Each group has its own channel through which data is transmitted to the Formatter. T/R Modules 1 to 32 are grouped to the left channel, while Modules 33 to 64 are

grouped to the right channel. The T/R Modules are configured in a way such that, the loaded calibration data words are echoed back to the Formatter during the radar initialization phase for error check. In order to enable one of the two channels during this phase, a channel enable module is implemented in the T/R Module interface of the Formatter's FPGA. This logic enables the left or right T/R Module channel, depending on its address. The channel enable module is also controlled by PF, and it gets the T/R Module address from one of the software accessible registers of PF.

#### 5.2.3.2 Timing State Machine (TSM)

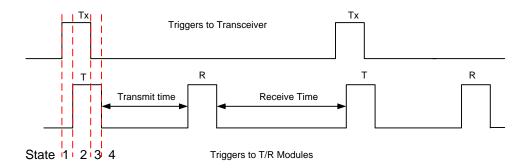

The TSM is implemented in the Formatter for triggering the T/R Modules and the Transceiver as explained in section 2.2. The pulse length, pulse repetition time, and Loop Count are read out from the DDR SDRAM memory by the MicroBlaze processor, and fed as inputs to the TSM for an azimuth beam position. The TSM goes through 32 states, and one iteration of the 32 states passes the T/R Modules through the sequence table once, thus generating 4 pulses. The 32 states are repeated for a particular beam location until the loop count decrements to zero. The Loop Count value determines the number of pulses needed by the Phase-Tilt radar in an azimuth beam position.

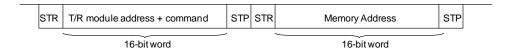

In order to pulse the radar, the TSM first sends a trigger to the Transceiver. This trigger switches the Transceiver to the Transmit state, which creates the output waveform. After a certain delay, the TSM triggers the T/R Modules to switch to the Transmit state. Once the Transmit time of the pulse elapses, the TSM triggers the T/R Modules to switch to the Receive state. The T/R Modules stay in this state until the Receive time elapses, and the TSM then triggers the Transceiver to start the next Transmit state. This sequence of triggers continues until the TSM Loop Count value decrements to zero. This corresponds to the Phase-Tilt radar transmitting a

fixed number of pulses in an azimuth beam position. The outputs of the TSM is shown in Figure 5.3.

Figure 5.3. Timing state machine trigger outputs

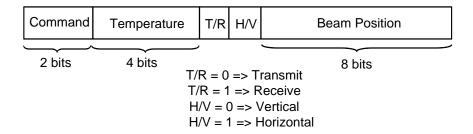

#### 5.2.3.3 Transceiver Interface

The Formatter communicates with the RVP900 Transceiver to convey the scan information before pulsing the radar. The Transceiver synchronizes the received radar data from the antenna panel with this scan information. This scan data contains information about the beam position and the polarization pulsing sequence performed by the radar.

The Transceiver interface consists of three lines: clock, enable signal, and a 32-bit serial data interface. The serial data interface is also another Transmitter, that shifts out a 32-bit data serially out through the GPIO pins on the board. The interface runs at 1 MHz, and hence, a clock divider is used to derive this clock rate from the external 100 MHz clock.

The implementation and verification of the custom Verilog modules are discussed in Appendix B. The AFB ports in these modules are used for communicating with the Phase-Tilt radar components. Except for clocks, all the data lines are sent serially. These ports are listed in Table 5.1.

The hardware utilization of the Spartan-3E FPGA for implementing the Array Formatter design is shown in Table 5.2.

**Table 5.1.** Array Formatter Board ports

| Port                          | Data Width | Data Rate or Frequency |

|-------------------------------|------------|------------------------|

| UART Transmit                 | 1          | 115 Kbps               |

| UART Receive                  | 1          | 115 Kbps               |

| T/R Module Interface Transmit | 1          | 25 MHz                 |

| T/R Module Interface Receive  | 1          | 25 MHz                 |

| T/R Module Interface Clock    | 1          | 25 MHz                 |

| Transceiver Interface Data    | 1          | 1 Mbps                 |

| Transceiver Interface Clock   | 1          | 1 MHz                  |

| TSM Trigger                   | 2          | Variable               |

Table 5.2. Hardware utilization of the AFB FPGA

| Logic Utilization | Used | Available | Percentage Utilization |

|-------------------|------|-----------|------------------------|

| Slices            | 3287 | 4656      | 70%                    |

| Flip Flops        | 3741 | 9312      | 40%                    |

| LUTs              | 3816 | 9312      | 40%                    |

| BRAMs             | 11   | 20        | 55%                    |

| DCMs              | 2    | 4         | 50%                    |

# 5.3 T/R Module FPGA Architecture

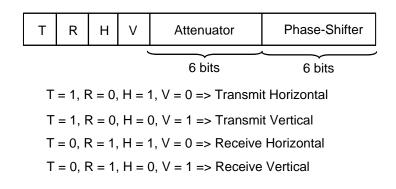

The T/R Module includes a Spartan-3E FPGA, which controls the RF components and the switches in the T/R Module. The architecture of the T/R Module FPGA is shown in Figure 5.4.

The FPGA has an on-chip memory module, which contains phase and amplitude coefficients (calibration data) for an antenna column. During the radar initialization phase, the memory of each T/R Module is preloaded with calibration data. The look-up table memory is 16 bits wide as shown in Figure 5.5, with 6 bits each for setting the attenuator and phase-shifter, and 4 bits for holding the information about T, R, H, and V states. The memory has 1K entries, and is divided into four segments for

Figure 5.4. T/R Module FPGA

the four T/R Module states (TH, TV, RH, RV). The set of calibration data for each T/R Module state corresponds to 256 different beam positions in an azimuth plane.

Figure 5.5. T/R Module memory bits

The FPGA also contains a sequence table that addresses the look-up table memory. The polarimetric pulsing sequence performed by the radar is determined by the eight entries in the sequence table. The sequence table, as shown in Figure 5.6, is 16 bits wide. The first two bits represent the mode. This instructs all the T/R Modules in the array to listen to the Array Formatter and update their sequence tables. The four temperature bits are latched by the temperature register in the T/R Module. These bits update the temperature of the on-board thermal sensor. The T/R and V/H bits select one of the four segments in the look-up table memory, which repre-

sents the T/R Module state. The eight beam position bits is used for selecting one of the 256 azimuth beam positions in the selected memory segment.

Figure 5.6. T/R Module sequence table bits

At the rising edge of the trigger pulse sent by the Array Formatter's TSM, the data in the memory that is addressed by the sequence table is latched by the port registers. The port registers are interfaced to the attenuators, phase-shifters, T/R and V/H switches to adjust the antenna column parameters. In this way, the T/R Module FPGA communicates with the Array Formatter and controls the operation of the Phase-Tilt radar.

#### CHAPTER 6

#### ARRAY FORMATTER SOFTWARE

This chapter describes the software application details of the Array Formatter that has been implemented and tested on the Spartan-3E FPGA.

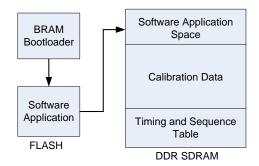

# 6.1 Booting the System

The Xilinx Spartan-3E FPGA features the ability to configure from the Xilinx PROM available on-board in the Master Serial configuration mode [25]. On power up, the initial configuration loads the FPGA with the hardware components along with the MicroBlaze software application which gets loaded into the Block RAM. The MicroBlaze processor executes the application from the Block RAM as soon as the FPGA is configured. The capacity of the Block RAM is 8 Kilo Byte because of the limited available hardware resources. Hence the software bootloader technique is used in this thesis work to execute the Formatter software application that is larger than 8 KB.

#### 6.1.1 Bootloader

A bootloader is a software piece of code that gets loaded along with the configuration bitstream while programming the PROM. The Intel Parallel Flash is used in this project to store the main software application code. The sequence of steps that take place during the bootloading operation is described below:

1. On power up, the FPGA gets configured by the PROM, and the processor executes the bootloader from the processor reset location.

- 2. Bootloader copies the image of the software code from the Parallel Flash to the DDR SDRAM as shown in Figure 6.1.

- 3. Processor executes the software code from the DDR SDRAM.

Figure 6.1. Bootloader illustration

The software application that is built from the project has the Executable and Linkable Format (ELF). ELF image files are generally not used for storing and bootloading as it increases the complexity of the bootloader code [21]. The ELF image is instead converted to SREC (Motorola S-record) format, which is one of the common bootloadable image formats, and hence, helps the process of bootloading. The concept of bootloading is shown in Figure 6.1.

# 6.2 MicroBlaze Software Application

The Array Formatter software application is developed in C. The Formatter prints the success of the bootloader process to the Host Computer, and then starts to execute the application code from the DDR SDRAM.

All peripheral device drivers are included in the code as header files. These files give access to the peripheral APIs. The drivers help users to treat the peripheral as a black box, and not deal with any complex bus transactions between the processor and the peripheral. For example, the user can instruct the MicroBlaze processor to write a 32-bit data to a specific address location in the DDR SDRAM, by calling the function

XIo\_Out32(Address, Data). The processor recognizes the address space of the DDR SDRAM between its base and high addresses. The DDR SDRAM chip is accessed as a memory-mapped I/O, and any memory read or write operation is specified within this address range. Similarly, all other peripherals are accessed as memory-mapped I/Os by the processor, and the device driver APIs are used to communicate with them in the software application. These APIs are described in Appendix A.

The Formatter has three communication interfaces on the chip that are implemented in Verilog. These are the T/R Module interface, Transceiver interface, and the TSM. The interfaces are port-mapped to the software accessible registers of the Custom Peripheral (PF). The registers are accessed in software by the APIs defined in the PF device driver. The PF is configured to have 30 software accessible registers, and these are mapped to all the three communication interfaces. For example, a software write to the T/R Module interface corresponds to writing a 32-bit data to the FIFO WSM. In order to write the data to the FIFO WSM, the processor writes into the PF register that corresponds to the input data port of the WSM. The processor then enables the FIFO WSM in software by setting the corresponding PF register to one. Likewise, the processor performs a software read operation from the T/R Module interface by first starting the FIFO RSM in software, and then reading the data from the output port of the RSM. The processor uses the corresponding PF registers that are mapped to the RSM enable and data output ports. These functions along with other software communication interfaces have been described in Appendix A.

#### 6.2.1 Software Functions

The MicroBlaze software functions can be grouped into two schemes: Unicast and Broadcast schemes. The Unicast scheme corresponds to the Phase-Tilt radar initialization mode, where the calibration data is loaded in the AFB's memory, and then routed to the corresponding T/R Modules. The Broadcast scheme, on the other

hand, is associated with the radar operation mode. In this scheme, the sequence table and timing information for multiple beam positions in an azimuth plane are loaded in the memory. The processor then reads them out from the memory, and writes to the T/R Module interface and the TSM respectively.

The MicroBlaze application program begins in a while loop that makes a call to access the UART receive buffers for the Host Computer command. The program enters a case statement that calls the different software functions depending on the 8-bit command decoded by the processor. If the command is 'z' or "exit," the application sets the command flag to 1. The application while loop terminates when the command flag is set to 1. The MicroBlaze software functions are explained below:

#### 6.2.1.1 Unicast Scheme

In the unicast scheme, the Formatter addresses each T/R Module individually, and waits for the T/R Modules to echo the words back for error check. The Formatter enables the left or right channel of the T/R Modules to transmit data. The left channel is enabled if the Formatter receives data from T/R Modules 1 to 32, and the right channel is enabled for T/R Modules 33 to 64. The following are the five MicroBlaze software functions under the Unicast scheme.

#### **Store Calibration Data:**

If the command decoded by the Formatter is 's,' the store calibration data function is executed by the processor. The T/R Module calibration coefficients are stored in the Formatter's DDR SDRAM memory segment. The Formatter's memory is divided into segments of 4 KB to store the T/R Module calibration data. The steps taken by the MicroBlaze processor to implement this function in software is given below:

- 1. Receive T/R Module address as the next byte of data.

- 2. Calculate the DDR memory segment address for the T/R Module.

- 3. Calibration data are then formatted as 32-bit words by concatenating four consecutive 8-bit words from the UART receiver.

- 4. Store 32-bit words in memory, until the of command (0xFFFF) is received.

#### Transmit Calibration Data:

If the command decoded by the Formatter is 'f,' the application enters the "Transmit Calibration Data" function. The calibration data that is stored in DDR SDRAM is transmitted to the T/R Module Interface by loading each data word into the WSM. This function is used for loading the T/R Module look-up table memory with calibration data. A 16-bit command is created and transmitted by the Formatter. This command instructs the addressed T/R Module to update its memory with calibration data. The steps taken by the Formatter to implement the function are explained below:

- 1. Receive T/R module address and calculate the DDR memory segment address.

- 2. Create the command for the addressed T/R module to update its memory and write to the WSM.

- 3. Enable one of the T/R Module channels to receive the echoed data.

- 4. Read all the calibration data from DDR SDRAM for the addressed Module, and write to the WSM.

- 5. Wait until all words are read back from the RSM.

The data format for updating the T/R Module look-up table memory is shown in Figure 6.2. The Formatter creates and transmits the command for updating the T/R Module memory. The command is followed by another word that indicates the total number of data words, "N." This is followed by the "N" data words that are written into the T/R Module memory.

Figure 6.2. Data format for updating T/R Module memory

#### Write T/R Module Port Registers:

If the Host Computer command is 'p,' the application enters the "Write T/R Module Port Registers" function. The steps are explained below for this mode of operation.

- 1. Receive T/R module address and the port register data from the Host Computer.

- 2. Create the command for the addressed T/R Module to update port registers, and then write the command and data to the T/R Module interface (WSM).

- 3. Enable one of the T/R Module channels to receive the echoed data.

- 4. Wait until the two 16-bit words (command and data) are read out from the RSM.

On receiving the data and command from the Formatter, the T/R Module FPGA bypasses the look up table memory to set the antenna column parameters directly into the port registers. The data format for communicating with a T/R Module during this mode of operation is shown in Figure 6.3. The first 16-bit word addresses the T/R Module, and also has the command for loading the port registers. The second word is the port registers data.

Figure 6.3. Data format for writing port registers

#### Read T/R Module Port Registers:

This function is executed when the Host Computer command is 'r.' The computer sends the command to instruct the Formatter to read from a T/R Module port registers. The steps for this mode are listed below.

- 1. Get T/R module address.

- 2. Create command to access the port registers for the addressed T/R Module, and then write the command to the WSM.

- 3. Enable one of the T/R Module channels to receive data.

- 4. Wait until the two 16-bit words (command and data) are read from the RSM.

The data format for communicating with the T/R Modules is shown in Figure 6.4. Only one 16-bit word is sent to the T/R Module, which contains both the command and the T/R Module address. Two 16-bit words are received by the Formatter, which contains both the T/R Module command and the 16-bit data from the port registers.

Figure 6.4. Data format for reading port registers

#### Write T/R Module Address Register:

The MicroBlaze processor executes this function on receiving command 'a' from the Host Computer. The purpose of this software function is to write the T/R Module port registers with the data contained in the addressed memory location of the T/R Module look-up table memory. The following are the set of steps:

1. Get T/R module address.

- 2. Create command for the T/R Module, and then write the command and T/R Module memory address to the WSM.

- 3. Enable one of the T/R Module channels to receive data.

- 4. Wait until the two 16-bit words (command and data) are read from the RSM.

The Formatter first addresses a T/R Module, and then addresses the location in the Module's look-up table memory. The data contained in the addressed memory location is loaded in the port registers of the T/R Module. The data format between the Formatter and the T/R Module for this function is shown in Figure 6.5.

Figure 6.5. Data format for writing address register

#### 6.2.1.2 Broadcast Scheme

In the Broadcast scheme, the Formatter first stores the sequences and timing-related information in its memory, and then writes these data to the T/R Module interface and the TSM. The sequence table serves as the address bits for the memory look-up table in the T/R Module as shown in Figure 5.4. For each T/R Module in the antenna array, the set of amplitude, phase, T/R, and H/V values contained in the memory are loaded into the corresponding port registers at the rising edge of the trigger pulses generated by the Formatter's TSM. The T/R Module port registers are interfaced to the attenuators, phase-shifters, and the T/R and V/H switches. There are two software functions in the Broadcast scheme. The first function stores the data in the DDR SDRAM. The second function writes the data to the WSM of the T/R Module interface, and then starts the TSM.

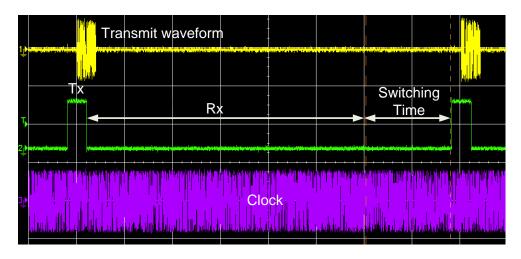

#### Store Timing and Sequence Data:

If the command from the Host Computer is 'q,' the processor executes the "Store Timing and Sequence Data" function. A scan command is a set of azimuth beam position for a fixed elevation angle. Each azimuth beam position consists of Sequence Tables, Timing Information (PRT, Pulse length), and the Loop Count as explained in section 2.3. The Formatter stores the scan command in its memory. The sequence of steps is explained below.

- 1. Receive two 8-bit words from the computer, and create the 16-bit Loop Count variable of the TSM. Store Loop Count variable in memory as a 32-bit word.

- 2. Receive sixteen 8-bit words, and create four 32-bit words for the TSM timing registers. Store the four timing register values in memory.

- 3. Repeat step 2 for storing sequence table information as four 32-bit words in memory.

- 4. Repeat steps 1,2, and 3 for multiple beam positions until the Loop Count variable is received as 0xFFFF (end of command).

#### Begin:

The "Begin" function is executed by the processor when it receives the character 'b' from the computer as the command. This function corresponds to the radar operation mode. Sequence and timing related information from the memory are read out by the Formatter and appropriate actions are taken as explained below.

- Read sequence table data out from the memory and write to the WSM of the T/R Module interface.

- 2. Create the 32-bit scan information for the Transceiver, and send the data to the Transceiver interface.

- 3. Read timing information and Loop Count variable from the memory, and load these information to the TSM.

- 4. Steps 1 to 3 are repeated for the other beam positions until all the sequence and timing information in memory have been read out to complete one scan in the azimuth plane.

Table 6.1. Host Computer commands for MicroBlaze software functions

| MicroBlaze Software Function      | Scheme    | Command |