### **University of Massachusetts Amherst** ScholarWorks@UMass Amherst

Masters Theses 1911 - February 2014

2011

## Functional Verification of Arithmetic Circuits using Linear Algebra Methods

Mohamed Basith Abdul Ameer Abdul Kader University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/theses

Part of the Electrical and Computer Engineering Commons

Ameer Abdul Kader, Mohamed Basith Abdul, "Functional Verification of Arithmetic Circuits using Linear Algebra Methods" (2011). Masters Theses 1911 - February 2014. 657.

Retrieved from https://scholarworks.umass.edu/theses/657

This thesis is brought to you for free and open access by ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses 1911 -February 2014 by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

### FUNCTIONAL VERIFICATION OF ARITHMETIC CIRCUITS USING LINEAR ALGEBRA METHODS

#### A Thesis Presented

by

MOHAMED ABDUL BASITH AMEER ABDUL KADER

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

September 2011

Electrical and Computer Engineering

$\odot$  Copyright by Mohamed Abdul Basith Ameer Abdul Kader 2011 All Rights Reserved

### FUNCTIONAL VERIFICATION OF ARITHMETIC CIRCUITS USING LINEAR ALGEBRA METHODS

#### A Thesis Presented

by

### MOHAMED ABDUL BASITH AMEER ABDUL KADER

| Approved as to style and content by: |                                        |

|--------------------------------------|----------------------------------------|

|                                      |                                        |

| Maciej Ciesielski, Chair             |                                        |

|                                      |                                        |

| Israel Koren, Member                 |                                        |

|                                      |                                        |

| Eric Polizzi, Member                 |                                        |

|                                      |                                        |

|                                      | Christopher V. Hollot, Department Head |

Electrical and Computer Engineering

#### ACKNOWLEDGMENTS

I am grateful to the Almighty for his mercy and blessings. I would like to thank Professor Maciej Ciesielski who has been so inspiring as a guide and advisor and for providing unwavering and immeasurable support throughout the course of my research work. I would like to thank him for giving me this opportunity and for pushing me to perform to the best of my abilities. I am indebted to Dr.André Rossi, of Université de Bretagne-Sud, Lorient, France, who helped us develop the mathematical formulation and provided us with the necessary software, developed specifically for the project. I would also like to thank all my friends, room-mates and colleagues, especially my peers in the VLSI-CAD Lab, for their unconditional help and support.

#### ABSTRACT

### FUNCTIONAL VERIFICATION OF ARITHMETIC CIRCUITS USING LINEAR ALGEBRA METHODS

#### SEPTEMBER 2011

MOHAMED ABDUL BASITH AMEER ABDUL KADER

B.E., ANNA UNIVERSITY, INDIA

M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Maciej Ciesielski

This thesis describes an efficient method for speeding up functional verification of arithmetic circuits namely linear network such as wallace trees, counters using linear algebra techniques. The circuit is represented as a network of half adders, full adders and inverters, and modeled as a system of linear equations. The proof of functional correctness of the design is obtained by computing its algebraic signature using standard linear programming (LP) solver and comparing it with the reference signature provided by the designer. Initial experimental results and comparison with Satisfiability Modulo Theorem (SMT) solvers show that the method is efficient, scalable and applicable to complex arithmetic designs, including large multipliers. It is intended to provide a new front end theory/engine to enhance SMT solvers.

vi

### TABLE OF CONTENTS

|    |                          | Page                                                  |

|----|--------------------------|-------------------------------------------------------|

| A  | CKN                      | OWLEDGMENTS v                                         |

| AI | BST]                     | RACT                                                  |

| тт | om o                     | NE MADIEC                                             |

| LI | <b>51</b> (              | 0F TABLES ix                                          |

| LI | ST (                     | of figures x                                          |

| CF | HAP                      | $\Gamma \mathrm{ER}$                                  |

| 1. | INT                      | RODUCTION 1                                           |

|    | 1.1                      | Formal Verification                                   |

|    |                          | 1.1.1Equivalence Checking31.1.2Boolean Satisfiablity3 |

|    |                          | 1.1.3 Model Checking                                  |

|    |                          | 1.1.4 Automatic Test Pattern Generation               |

|    | 1.2                      | Motivation                                            |

| 2. | PR                       | EVIOUS WORK 8                                         |

|    | 2.1<br>2.2<br>2.3<br>2.4 | Binary Decision Diagrams (BDDs)                       |

|    | 2.5                      | Arithmetic Bit-Level (ABL)                            |

|    | 2.6<br>2.7               | Satisfiability Modulo Theories (SMT)                  |

| 3. | ALC                      | GEBRAIC MODELING OF ARITHMETIC NETWORKS 22            |

|    | 3.1                      | Arithmetic Network                                    |

| 4.           | MATHEMATICAL FORMULATION OF FUNCTIONAL VERIFICATION PROBLEM |                                                                                               |            |

|--------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------|

|              | 4.1<br>4.2<br>4.3                                           | Mathematical Formulation                                                                      | 32         |

| <b>5</b> .   | TH                                                          | EOREMS AND BOOLEAN MODELS                                                                     | 39         |

|              | 5.1<br>5.2<br>5.3<br>5.4                                    | Theorems Imposing Binary Constraints Deriving Boolean Constraints Verifying Incorrect Designs | 44         |

| 6.           | SAT                                                         | TISFIABILITY MODULO THEORY (SMT)                                                              | 62         |

|              | 6.1<br>6.2                                                  | Introduction to SMT                                                                           | -          |

|              |                                                             | 6.2.1 MathSAT         6.2.2 Yices         6.2.3 Z3                                            | 64         |

|              | 6.3<br>6.4                                                  | Relation of the Proposed Verification Method to SMT Techniques Comparison with SMT solvers    |            |

| 7.           | AN                                                          | ALYSIS OF RESULTS                                                                             | 68         |

|              | 7.1<br>7.2<br>7.3                                           | Functional Verification System                                                                | 68         |

|              |                                                             | 7.3.1Carry Look-Ahead Adder7.3.2Ripple Carry Adder7.3.3Parallel Prefix Adder                  | 71         |

|              | 7.4                                                         | Multipliers                                                                                   | 73         |

| 8.           | CO                                                          | NCLUSIONS AND FUTURE WORK                                                                     | <b>7</b> 8 |

| $\mathbf{A}$ | PPE:                                                        | NDIX: FUNCTIONAL VERIFICATION FLOW                                                            | 82         |

| ВІ           | BLI                                                         | OGRAPHY                                                                                       | 90         |

### LIST OF TABLES

| ble Pag                                                                                                                                                              | ge |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1 Truth table for full-adder circuit in Figure 5.2(a)4                                                                                                             | 46 |

| 6.1 Comparison with SMT solvers (without Boolean constraints, $RE \neq \phi$ ). (MO = out of memory 4GB, TO = timeout after 1800sec)                                 | 66 |

| 6.2 Comparison with SMT solvers (with Boolean constraints, $RE = \phi$ ) 6                                                                                           | 67 |

| 7.1 CPU runtime for computing algebraic signature for $n$ -bit carry look ahead adder with basic logic gates $(RE = \phi)$                                           | 71 |

| 7.2 CPU runtime for computing algebraic signature for $n$ -bit ripple carry adder in structured form (composed of full adders) ( $RE = \phi$ )                       | 71 |

| 7.3 CPU runtime for computing algebraic signature for $n$ -bit ripple carry adder with gate level implementation $(RE \neq \phi)$                                    | 72 |

| 7.4 CPU runtime for computing algebraic signature for $n$ -bit integer multipliers without additional constraints $(RE \neq \phi)$                                   | 75 |

| 7.5 CPU runtime for computing algebraic signature for $n$ -bit integer multipliers with additional constraints propagated in the network $(RE = \phi)$               | 76 |

| 7.6 CPU runtime for computing algebraic signature for $n$ -bit integer Booth-encoded multipliers with additional constraints propagated in the network $(RE = \phi)$ | 76 |

| A.1 Options available in the multiplier generator                                                                                                                    | 83 |

### LIST OF FIGURES

| Figure                                                                                                                                                                             | Page       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.1 Formal verification flow                                                                                                                                                       | 2          |

| 1.2 An example of SAT                                                                                                                                                              | 4          |

| 1.3 Model Checking                                                                                                                                                                 | 5          |

| 2.1 Two equivalent expressions having the same BDD. (a) $F = a'bc + abc + ab'c$ ; (b) $G = ac + bc$                                                                                | 9          |

| 2.2 Application of BDD to SAT                                                                                                                                                      | 10         |

| 2.3 Binary Moment Diagrams: (a) The moment decompositio (b) BMD for binary encoded integer $X = 4x_2 + 2x_1 + *BMD$ for $X = [x_2 \ x_1 \ x_0]$                                    | $x_0; (c)$ |

| 2.4 *BMD representation for Boolean operators: a) NOT: $x' =$ AND: $x \wedge y = x \cdot y$ ; c) OR: $x \vee y = x + y - xy$ ; d) XOR $x \oplus y = x + y - 2xy$                   | :          |

| 2.5 RTL verification using canonical TED representation: (a), Functionally equivalent RTL modules; (c) The isomorphore for the two designs                                         | phic TED   |

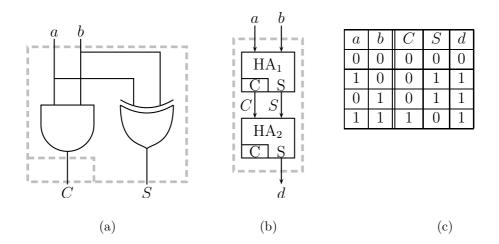

| 3.1 Logic-level Half-adder, $\operatorname{HA}(a,b)$                                                                                                                               | 23         |

| 3.2 Modeling of logic gates using half-adders: (a) $S = XOR(a, b)$ $C = AND(a, b)$ of half-adder; (b) OR gate $d = C + S$ detection two half-adders; (c) truth table for $C, S, d$ | rived from |

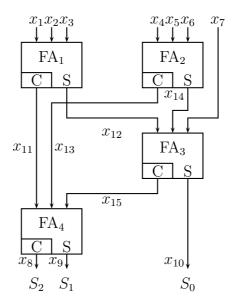

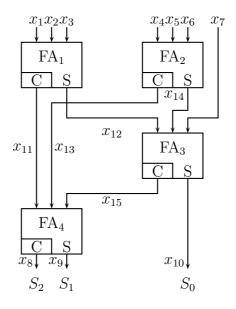

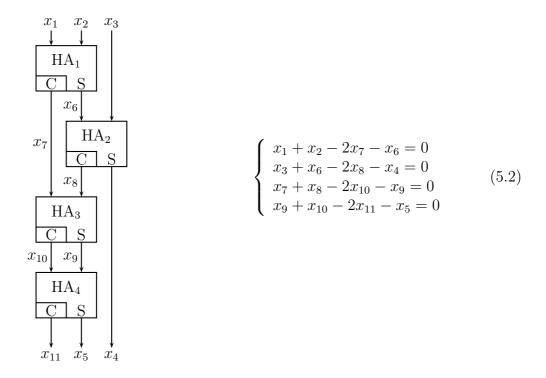

| 3.3 Arithmetic network of a 7-3 counter                                                                                                                                            | 25         |

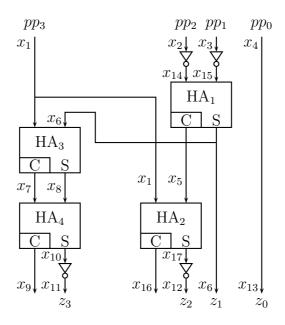

| 4.1 Signed $2 \times 2$ multiplier network                                                                                                                                         | 35         |

| 5.1 Arithmetic network of a (7.3) counter                                                                                                                                          | <i>1</i> 1 |

| 5.2 | Configuration in Netlist45                                                                       |

|-----|--------------------------------------------------------------------------------------------------|

| 5.3 | Full Adder symbol : $x_1 + x_2 + x_3 = 2x_5 + x_4 \dots 47$                                      |

| 5.4 | Signed $2 \times 2$ multiplier network                                                           |

| 5.5 | Signed $3 \times 3$ multiplier network                                                           |

| 5.6 | BDD of a signed $3 \times 3$ multiplier network                                                  |

| 5.7 | Gate level implementation of parallel prefix adder (courtesy of [52])                            |

| 5.8 | Parallel Prefix Adder network                                                                    |

| 5.9 | Incorrect signed $2 \times 2$ multiplier network with signals $x_5$ and $x_6$ incorrectly routed |

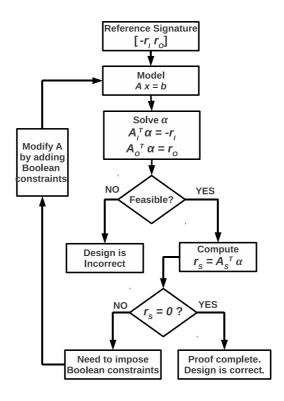

| 7.1 | Flowchart of the functional verification system                                                  |

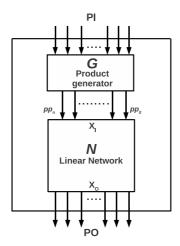

| 7.2 | Deriving inputs for multiplier networks                                                          |

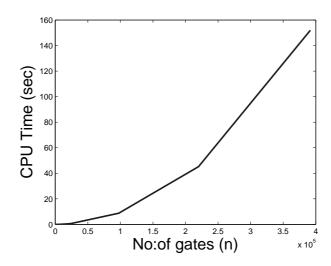

| 7.3 | Computational complexity of our approach                                                         |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Formal Verification

With the increasing size and complexity of integrated circuits (IC) and systems on chip (SoC), design verification has quickly become a dominating factor of the overall design flow. In today's designs over 75% of the entire design effort and cost is devoted to verification, making it the most challenging and expensive part of the overall design process. Of particular importance (and difficulty) is verification of arithmetic datapaths and their components, such as multipliers. Checking for functional correctness of arithmetic circuits and datapaths remains a major concern in IC and SoC design flows.

In early stages of CAD for synthesis and verification, simulation was a predominant technique for design verification. Simulation is based on computing the output values for a sequence of input patterns, and as such is an exhaustive technique. Its success depends on computing response to all input patterns and hence there is every possibility that there might be design errors which may never get identified during logic simulation. Also, as the size and complexity of the design grows, the number of input pattern grows exponentially which makes it impossible to verify the overall design using logic simulation. These drawbacks have led to the development of Formal Verification techniques which are based on proving global mathematical properties of the design rather than simulating circuit responses for a particular input sequence.

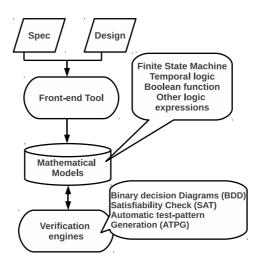

The most promising approach to verification of arithmetic designs is formal verification, which proves functional correctness of a design using mathematical logic and formal reasoning instead of simulation. Various techniques for functional verification, such as Binary Decision Diagrams (BDDs), Boolean satisfiability checking (SAT) methods, model checking, property checking, and equivalence verification, have been used as a proof process. An overview of a formal verification flow is shown in Figure 1.1

Figure 1.1. Formal verification flow.

As shown in Figure 1.1, in formal verification environment the specification and design description are first converted into mathematical models. These models include finite state machines, temporal logic, Boolean functions and other logic expressions. The mathematical models are then verified using different canonical representations, satisfiability checks and automatic test-pattern generation techniques. Unlike logic simulation, which requires exhaustive check of design responses to all possible input combinations, formal methods use mathematical models of the design to prove its properties and functionality.

#### 1.1.1 Equivalence Checking

Equivalence Checking or Equivalence Verification is concerned with verifying whether two designs are equivalent or not. Equivalence checking can be applied to two designs at the same design level or at different design levels. Based on the type of equivalence definition, equivalence checking can be applied to either combinational parts of the design or to the sequential part. Today, combinational designs as large as having 10 million gates can be efficiently verified by contemporary equivalence verification tools with the notable exception for complex arithmetic circuits.

A number of canonical graph-based representations are used to solve equivalence checking for combinational designs. They include decision diagrams such as Binary Decision Diagrams (BDDs) [6] and their many variants, Binary Moment Diagrams (BMDs) [7], Taylor Expansion Diagrams (TEDs) [11] and others. Since BDDs and BMDs cannot efficiently represent abstract designs, Taylor Expansion Diagrams (TEDs) and Finite-field Decision Diagrams (FFDDs) were introduced. These are extensions of BDDs and BMDs with input and output represented as symbolic variables. The difference between the two classes of diagrams lies in the arithmetic representation of data; TEDs use integer arithmetic, whereas FFDDs use finite field arithmetic. They also differ in the type of decomposition used; TEDs use Taylor series expansion whereas FFDDs use multi-valued Galois field (GF) decomposition. These canonical representations are reviewed in the next chapter.

#### 1.1.2 Boolean Satisfiablity

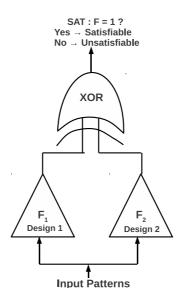

Boolean Satisfiability (SAT) [20] is a constraint satisfaction problem that appears in computer-aided design of VLSI circuits and in Artificial Intelligence. Given function  $\phi$ , SAT checks for a variable assignment for which function  $\phi$  is true. If there exists such an assignment of variables then  $\phi$  is satisfiable, else it is unsatisfiable. Despite the fact that Boolean Satisfiability is NP-complete, SAT is used in many

real world problems including test pattern generation, equivalence checking, testing, logic synthesis, logic simulation and others. Most SAT solvers use Conjunctive Normal Forms (CNFs). The goal is to prove that there are no input patterns for which the outputs of the two designs differ. This can be solved by connecting the outputs through a "miter", F, that includes an XOR gate as shown in Figure. 1.2. If the output of a miter F = 1 is satisfiable, the two designs are different, and the SAT solver provides an example of input patterns(counter-proof) for which  $F_1 \neq F_2$ . Otherwise, such constructed SAT problem is Unsatisfiable (unSAT), in which case the designs are equivalent. In summary, the equivalence problem is reduced to proving Unsatisfiability of such a structure.

Figure 1.2. An example of SAT.

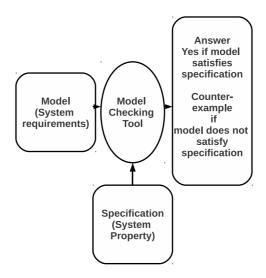

#### 1.1.3 Model Checking

Model Checking [8], or Property Checking, is a technique which determines whether the design satisfies the properties given in its specification. A model checking tool accepts system requirement (model) and a property (specification) to ensure that the model and the property are satisfied. The model checking tool returns "true" if

the model satisfies the property, otherwise it returns a counter-example. The idea of providing a counter-example is to detail the reason for the property not being satisfied by the model. Thus by analyzing the counter-example the source of error can be found and rectified and the model can be tried again. This repetitive process of checking if a given property is satisfied and generating counter-example ensures that several properties are satisfied giving confidence in the correctness of the design. Over the years, model checking has undergone remarkable improvement owing to the improvement in SAT techniques [20]. The basic idea of model checking approach is illustrated in Figure 1.3

Figure 1.3. Model Checking.

#### 1.1.4 Automatic Test Pattern Generation

Automatic Test Pattern Generation (ATPG) [10] is a technique of generating test vectors as stimulus for testing the circuits for manufacturing faults. Manufacturing faults are physical defects in the circuit generated during manufacturing process, which result in incorrect operation of the circuit. The faults led to the circuit sig-

nals being permanently stuck at either logical 0 or 1. Several efficient algorithms have been developed for stuck-at faults detection using Boolean reasoning. Thus using Automatic Test Pattern Generation techniques, powerful formal verification techniques can be formed. Automatic test pattern generation is often used in conjunction with SAT.

#### 1.2 Motivation

Unlike gate-level logic designs, which can be handled using Boolean methods, arithmetic designs require treatment on higher abstraction levels. Techniques based on decision diagrams or SAT solvers that work at the circuit and logic level are not scalable for complex arithmetic systems as they require "bit-blasting", i.e., flattening of the entire design into bit-level netlists. Some of the recent approaches to verification use Satisfiability Modulo Theories (SMT) and symbolic algebra methods, but they suffer from lack of adequate models that can harness the inherent bit-level nature of complex arithmetic designs.

The work described in this thesis aims at overcoming some of these limitations. It presents a novel approach to perform functional verification of arithmetic circuits, which combines algebraic description of the arithmetic design with the bit-level details, using linear algebra techniques. The proof of correctness is obtained by modeling the arithmetic circuit as a network of half adders and full adders and computing an algebraic signature of the circuit using a standard LP solver. The computed signature is then compared with the reference signature (golden model) provided by the designer to determine if the design is correct. The computation of the algebraic signature is very fast and scalable as it is based on a simple manipulation of a set of linear equations without finding variable assignments (typical of SAT approaches) and without imposing integer constraints on its variables. In addition to functional verification and property checking, the method can be used to extract circuit behav-

ior from its structural description by computing its input signature. The proposed technique can be used in conjunction with, or as one of the SMT engines (theories) to enhance capabilities of the current SMT solvers.

#### CHAPTER 2

#### PREVIOUS WORK

Several methods have been proposed to check an arithmetic circuit against its specification at a higher level of abstraction. Different variants of canonical graph-based representations have been proposed, including Binary Decision Diagrams (BDDs) [6] or their variants such as Multiplicative Power Hybrid Decision Diagrams (\*PHDDs) [9], Hybrid Decision Diagrams (HDDs) [12], etc. These representations are commonly referred to as Decision Diagrams. Decision diagram is a graph based structure where the nodes of the graph represent the variables and the edges represent the decomposition of the function with respect to the individual variables.

An important feature of decision diagrams is canonicity, meaning that the representation of a function with such a diagram is unique. Two combinational circuits can be checked for equivalency by simply checking if their decision diagrams are isomorphic. In practice, the decision diagrams for the two functions are built in the same manager, so the test for isomorphism reduces to checking if the two functions point to the same root of the diagram.

More advanced methods include Binary Moment Diagrams (BMDs) [7] and Taylor Expansion Diagrams (TEDs) [11] that attempted to represent the design at higher levels of abstraction. The next section reviews the different canonical diagram representations.

#### 2.1 Binary Decision Diagrams (BDDs)

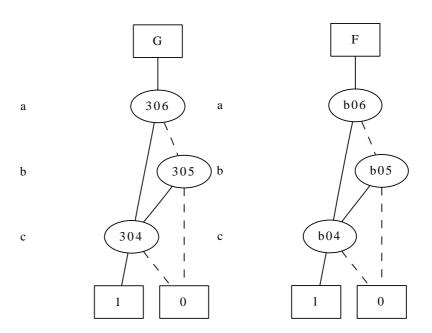

The most commonly used decision diagram representation is Binary Decision Diagram (BDD). [6] BDD is a canonical representation of Boolean functions represented as a directed acyclic graph. It provides a more compact representation than truth-tables, Sum of Products (SOPs) form, or Conjunctive Normal Forms (CNFs) for most of the Boolean functions used in the area of VLSI design. BDDs are based on the Shannon function decomposition, where the function is decomposed into two co-factors  $f_x = 0$  and  $f_{\overline{x}} = 1$ . Individual paths lead to taking a decision x=0 or x=1, hence the name "decision diagrams". Efficient algorithms exist to represent Boolean functions as BDDs. BDDs represent Boolean functions and logic circuits at bit-level and are used to verify bit-level designs, such as control and random logic. They are extensively used in verification and logic synthesis but also in satisfiability and testing. Bryant [6] proposed an algorithm to reduce ordered BDDs, known as Reduced Ordered BDDs (ROBDDs). This form is irredundant, canonical and minimal.

**Figure 2.1.** Two equivalent expressions having the same BDD. (a) F = a'bc + abc + ab'c; (b) G = ac + bc

An example of use of BDD in equivalence checking is shown in Figure 2.1. The two function F and G are equivalent and hence their BDDs are identical (for the same ordering of variables).

Another application of BDDs is in solving Boolean Satisfiability (SAT), illustrated in Figure 2.2 with a BDD for F = a(b+c). In-order to find a satisfiability solution for F = 1(0) one needs to find a path from the root of the BDD to terminal node 1 (0). In this case the paths ab or ab'c provide a satisfiability solution, i.e., a = b = 1 or b = 0, a = c = 1 satisfies F = 1.

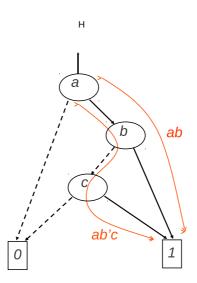

Figure 2.2. Application of BDD to SAT.

BDDs have emerged as data structure of choice in logic synthesis, SAT, and Boolean logic representation, but their application to verification of arithmetic circuits is limited. In general, solutions based on bit-level decision diagrams suffer from high computational complexity due to exponential growth of the BDD size for complex arithmetic circuits such as multipliers. For example, a BDD for  $14 \times 14$  multiplier

cannot be built in a typical modern computer due to large memory size required by its data structure. Recognizing this weakness, researchers turned to other canonical forms, such as BMDs, TEDs, and others capable of representing designs at higher levels of abstraction than a bit-level.

#### 2.2 Binary Moment Diagrams (BMDs)

Another form of canonical graph-based diagrams that are more applicable to arithmetic functions than BDDs are Binary Moment Diagrams (BMDs) introduced by Bryant [7]. BMDs are based on moment decomposition principle that treat arithmetic functions as linear functions with Boolean input and integer output. BMDs are used in verifying arithmetic designs with bit-level inputs and integer outputs.

BMDs use modified Shannon's expansion, where the Boolean variable is treated as a binary (0,1) integer variable. The complement of x is modeled as  $\overline{x} = 1 - x$  and the terms of the expansion are regrouped as

$$f(x) = (1-x) \cdot f_{\overline{x}} + x \cdot f_x = f_{\overline{x}} + x \cdot (f_x - f_{\overline{x}}) = f_{\overline{x}} + x \cdot f_{\Delta x}$$

Here "·", "+" and "-" denote multiplication, addition and subtraction, respectively. The above decomposition is termed as moment decomposition where  $f_{\overline{x}}$  is the constant moment, and  $(f_{\Delta x} = f_x - f_{\overline{x}})$  is the linear moment. Thus, a Boolean function f is treated as a linear function in x, with  $f_{\overline{x}}$  as the constant term, and  $f_{\Delta x}$  as the linear coefficient of f, the partial derivative of f with respect to f. This transformation relies on the fact that the variable f is still Boolean, i.e., it evaluates to either 0 or 1.

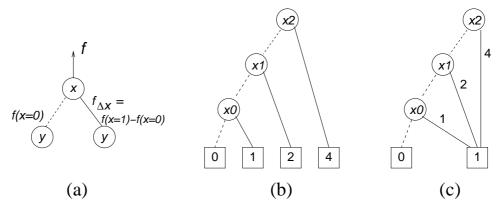

Each node of a BMD represents a function based on its moment decomposition, as shown in Figure 2.3(a). The two edges coming from a node represent the constant moment (shown in dashed lines) and the first moment (shown in solid lines) of the

**Figure 2.3.** Binary Moment Diagrams: (a) The moment decomposition principle; (b) BMD for binary encoded integer  $X = 4x_2 + 2x_1 + x_0$ ; (c) \*BMD for  $X = [x_2 \ x_1 \ x_0]$ .

function with respect to the decomposing variable. The BMD representation of the unsigned integer  $X = 4x_2 + 2x_1 + x_0$  encoded with n = 3 bits is shown in Figure 2.3(b). The three constants at the terminal nodes of the BMD can be moved to the edges and represented as edge-weights, as shown in Figure 2.3(c). This diagram is known as multiplicative binary moment diagram or \*BMD. There are two major features that differentiate \*BMDs from decision diagrams.

- BMDs are not decision diagrams since they are based on the moment decompositions and not on the bit-wise Shannon expansion.

- BMDs are multiplicative diagrams, i.e., each path from the root to the terminal node is a product of the variables labeling the nodes and edge weights along the path. As such, they are not applicable to SAT.

In addition to integer word-level functions, a \*BMD can be used to represent Boolean logic. The equations used to model Boolean logic are as follows:

$$NOT: \quad x' = (1-x) \tag{2.1}$$

$$AND: x \wedge y = x \cdot y$$

(2.2)

$$OR: \quad x \lor y = \quad x + y - x \cdot y \tag{2.3}$$

$$XOR: x \oplus y = x + y - 2x \cdot y$$

(2.4)

**Figure 2.4.** \*BMD representation for Boolean operators: a) NOT: x' = (1 - x); b) AND:  $x \wedge y = x \cdot y$ ; c) OR:  $x \vee y = x + y - xy$ ; d) XOR:  $x \oplus y = x + y - 2xy$ .

Figure 2.4 shows BMD representations for these basic Boolean operators [7]. In the diagrams, x and y are Boolean variables represented by binary variables, and + and + represent algebraic operators of ADD and MULT, respectively. The resulting functions are 0,1 integer functions.

In principle, a word-level BMD can efficiently represent integer multiplication, since its size grows linearly with the size of the multiplier's input. However, BMDs require word-level information about the design, which is usually not available or is hard to extract from optimized bit-level implementation. Also, an integer (word-level) output of a BMD cannot be split into individual bits, which severely limits its application to arithmetic, bit-level verification. Another limitation is that BMDs cannot be used for solving SAT problems since they are multiplicative diagrams, i.e., the weights combine multiplicatively along the path from the terminal node to the root. Solving integer-valued SAT problem in this structure is similar to solving integer factorization problem which is known to be hard.

### 2.3 Taylor Expansion Diagrams (TEDs)

To address some of the limitations of BMDs and BDDs, and in particular the need for a more abstract representation of designs with arithmetic components, another type of diagram, Taylor Expansion Diagram (TED), has been introduced [11]. TEDs are based on Taylor series expansion of polynomial representation of the computations expressed by the design. TED representation maps word-level inputs into word-level outputs and represents the infinite precision computation as polynomial. TEDs can be used in verification of designs at behavioural and algorithmic levels, such as datapath and signal processing systems, due to their power of abstraction, canonicity and compactness. The computations in such designs are expressed as polynomials and represented with TEDs, with memory requirements orders of magnitude smaller than those of other representations. TEDs can also be used to transform the initial functional representation into a structural representation, such as data-flow graphs (DFG), which makes them applicable to behavioural and high-level synthesis.

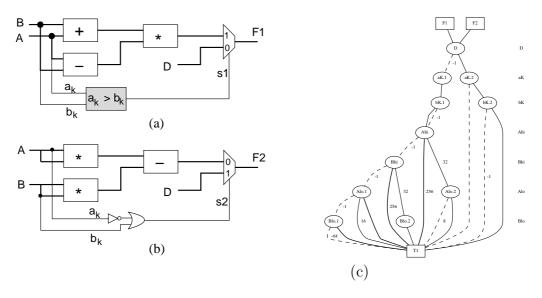

Construction of a TED for an RTL design starts with building trivial TEDs for its primary inputs. Partial expansion of the word-level input signals is often necessary when one or more bits from any of the input signals fan out to other parts of the design. This is the case in the designs shown in Fig. 2.5 (a) and (b), where bits  $a_k = A[k]$  and  $b_k = B[k]$  are derived from word-level variables A and B. In this case, the word-level variables must be decomposed into several word-level variables with shorter bit-widths.

**Figure 2.5.** RTL verification using canonical TED representation: (a), (b) Functionally equivalent RTL modules; (c) The isomorphic TED for the two designs.

Once all the abstracted primary inputs are represented by their TEDs, Taylor Expansion Diagrams can be constructed for all the components of the design. TEDs for the primary outputs are then generated by systematically composing the constituent TEDs in the topological order, from the primary inputs to the primary outputs. For example, to compute A + B in Fig. 2.5 (a) and (b), the ADD operator is applied to functions A and B (each represented in terms of their abstracted components). The subtract operation, A - B, is computed by first multiplying B with a constant -1 and adding the result to the TED of A. The multipliers are constructed from their respective inputs using the MULT operator, and so on. To generate a TED for the output of the multiplexors, the Boolean functions  $s_1$  and  $s_2$  first need to be constructed as TEDs. Finally, the TEDs for the primary outputs are generated using the MUX operator with the respective inputs. As a result of such a series of composition operations, the outputs of the TED represent multi-variate polynomials in terms of the primary inputs of the design.

After having constructed the respective ordered, reduced, and normalized Taylor Expansion Diagram for each design, the test for functional equivalence is performed by checking for isomorphism of the resulting graphs. In fact, the TED-based verification is similar to that using BDDs and BMDs: the generation of the TEDs for the two designs under verification takes place in the same TED manager; when the two functions are equivalent, both functions point to the same root of the common TED, shown in Fig. 2.5(c).

It should be noted that the arithmetic operations in these designs assume that no overflow is produced by any of the intermediate signal. That is, functions F1 and F2 are functionally equivalent under an *infinite precision* computation model. This limitation is a natural consequence of the design representation on the abstract level, where notion of the individual bits is not available. The major limitation is

that TEDs cannot express individual output bits (eg; sign) as function of word-level inputs. Splitting of signals is a problem as well.

### 2.4 Symbolic Algebra

Computations encountered in behavioural design specifications such as digital signal and image processing designs, digital filter designs, and designs that employ complex transformations, such as DCT, DFT, WHT, etc. can be represented in terms of polynomials. For the purpose of component mapping, polynomial models of high level design specifications have been used in behavioural synthesis in [32, 33, 26]. For each component (operator), a polynomial representation is created and the polynomials are matched by comparing their co-efficients. However, for large multivariate polynomials, comparing and storing large matrices becomes inefficient.

Commercial symbolic algebra tools, such as Maple [40], Mathematica [41], and MatLab [43], use advanced symbolic algebra methods to perform efficient manipulation of mathematical expressions, including fast multiplication, factorization, etc. These tools have also been used for the purpose of polynomial mapping, namely, to perform simplification modulo polynomial as in [26]. However, despite the unquestionable effectiveness of these methods for classical mathematical applications, they are less effective in modeling of large scale digital circuits and systems, and in particular in polynomial verification. For example, symbolic algebra tools offered by Mathematica and alike cannot unequivocally determine the *equivalence* of two polynomials. The equivalence is checked by subjecting each polynomial to a series of *expand* operations and comparing the coefficients of the two polynomials ordered lexicographically.

Recently, a number of computer symbolic algebra methods have been applied to model RTL designs with arithmetic components as polynomial expressions, mostly for equivalence checking. A polynomial abstraction technique based on the fundamental theorem of algebra has been proposed in [27]. This abstract model preserves the control and data properties of the original system and can be verified via symbolic model checking. Some of the newer approaches combine symbolic computation methods with the relational modeling techniques from Kleene algebra [17],[50]. In [51] both the data path and the control part of the design are encoded using polynomials, and the verification is performed in a generalized bounded model checking style.

A concept of polynomial functions over finite integer rings has been introduced in [30] to perform equivalence verification of arithmetic data-paths with fixed bitwidth. Similar to BMDs, its applicability to verification of arithmetic circuits is limited as it relies on a word-level representation of the datapaths, which is often not available. An attempt to address modular datapath verification and optimization problem is discussed in [1]. It uses Horner expansion diagram (HED) to reduce and prove equivalence of portions of datapaths modeled as polynomials over finite integer rings. This work is limited to relatively small DSP designs, such as filters, that can be represented as polynomials of higher degree. It basically suffers from the same problem as TED. An approach to verification of bit-level implementations using theory of Grobner basis over fields has been proposed by [47] and adopted by others [31, 49]. These methods are very complex and limited to small polynomials.

Kalla [31] proposed a method of equivalence checking of two polynomials implemented in n-bit representation by checking if the difference between the two expressions is a "vanishing polynomial", i.e., if it reduces to 0 modulo n. This method, however, relies on a complicated theory of Grobner basis and requires the use of symbolic algebra systems such as Maple. Furthermore, the "vanishing polynomial" method cannot be easily used to compare two complex arithmetic designs expressed on arithmetic Boolean level and with logic gates.

A technique based on term rewriting was proposed [46] for RTL equivalence checking, using a database of rewrite rules for typical multiplier implementation schemes.

However, the method cannot be automated for non-standard implementations. Automated techniques for extracting arithmetic bit level information from gate level netlists has been proposed in the context of equivalence checking [45] and debugging [29].

#### 2.5 Arithmetic Bit-Level (ABL)

Automated techniques for extracting arithmetic bit level information from gate level netlists has been proposed in the context of equivalence checking [45] and debugging [29]. In [45, 49] a gate level network of an addition circuit (a basic component of the multiplier) is modeled as a network of half adders, called arithmetic bit-level (ABL) network, and a heuristic ABL normalization was added to enable their comparison [48]. Since ABL representation is not unique, a heuristic ABL normalization was proposed to enable their comparison [48]. Basically, the ABL description of addition networks and bit-wise multiplication is transformed into a reduced normal form, using commutative and distributive laws. Such normalization process enables structural similarities between the design under verification and the specification given as a property, which simplifies job for standard equivalence checkers. In [49] ABL normalization is combined with the techniques of computer algebra to produce a set of equivalent "variety subset problems". ABL components are modeled by polynomials over unique ring, and the normal forms are computed w.r.t. the Grobner basis over rings  $\mathbb{Z}/2^n$  using modern computer algebra algorithms. ABL descriptions can be also derived from the gate-level implementations using Red-Muller decomposition techniques, but they yield unduly large polynomials of high degree. All these methods are computationally intensive and are not scalable to large designs.

A simplified version of this technique has been recently presented by the same group [25], replacing expensive Grobner base computation by direct generation of polynomials representing individual output bits in terms of the primary inputs. How-

ever, no general method for deriving such (potentially very large) polynomials and comparing them in a systematic way against the specification has been proposed.

A high-level multiplier description language has been introduced in [18] to model a wide range of common implementations at a structural (gate-level) and arithmetic level. The correctness of the created model is established by bit-level transformations matching the model against a standard multiplication specification. The model is also translated into a gate level netlist to be compared with the implementation using standard equivalence checker. The method relies on a large amount of structural similarity between the two models that enables the use of standard equivalence checkers.

It is important to emphasize that this approach relies on the existence of structural similarities, which is common in standard equivalence checkers in industry. However, a pair of designs to be checked for equivalence are often structurally different. For example, word-level signals at the output of first level boxes (Add, Sub in Figure 2.5 (a) and \*,\* in (b)) look structurally similar, but are not equivalent (A + B, A - B) vs  $A^2, B^2$ . This makes a verification tool that relies on such similarity difficult. This can be illustrated with a pair of designs in Figure 2.5. In contrast, no assumption is made in our work about structural similarity; instead, the formal proof for functional equivalence is provided using mathematical model and specifically, standard linear algebra.

### 2.6 Satisfiability Modulo Theories (SMT)

Another direction of research into design verification investigates Satisfiability Modulo Theory (SMT) solvers. Satisfiability Modulo Theories (SMTs) solve formal properties at higher level than Boolean functions. SMT is a generalization of Boolean SAT, in which the binary variables are replaced by predicates or binary-valued functions of non-binary variables. These predicates may come from a variety of under-

lying theories. SMT solvers combine Boolean SAT with specialized solvers for some well-defined theories, such as Boolean logic, linear arithmetic, theory of equality of uninterrupted functions, theory of bit-vectors, theory of arrays and list structures and others [4] [19]. SMTs can enrich Conjunctive Normal Form (CNF) with linear constraints, arrays, all-difference constraints, uninterpreted functions, etc. SMT solvers use the same engine as SAT, but integrates theory reasoning and Boolean reasoning. Despite great advances of SAT solvers in verification, notably in property checking, their applicability to functional verification of highly-optimized custom datapath implementation remains limited [49].

Some of the SMT solvers for quantified free linear arithmetic include MathSAT [37], YICES [38], Z3 [39], and for non-linear arithmetic ABSolver [3] and iSAT [36]. New SMT solvers are developed continually, including those to efficiently solve linear inequalities in integer domain (Mistral) [16]. Our work is related to this topic but tackles the problem in a way that does not require solving a decision problem or finding a satisfying assignment for the integer variables.

### 2.7 Summary

In summary:

- Standard verification techniques based on <u>decision diagrams</u> and Boolean SAT are unable to handle arithmetic functions efficiently, especially multipliers.

- <u>ILP methods</u> are ineffective, as they inevitably require finding satisfying assignments for all *integer* or *binary* variables. Such a process is known to be computationally prohibitive for large designs.

- Current <u>symbolic algebra</u> methods are limited to relatively small designs that can be represented as polynomials. Advanced methods based on Grobner theory are very complex, and efficient algorithms for solving the associated verification problem are not readily available.

• Standard industry practice that performs functional verification by bringing the implementation and specification to a common level (typically gate-level) and using equivalence checking, relies on <u>structural similarity</u> between the two designs, which is often absent. The same is true for current ABL methods reviewed here.

In contrast, in this thesis no assumption is made about internal structural similarity between the implementation (arithmetic circuit) and the specification (its intended function). In fact, the specification is given just as a simple linear expression that relates word-level output to bit-level inputs. Such a specification can be trivially derived for all the known arithmetic designs, such as different adders, simple and recoded multipliers, etc. The only requirement is that the design is arithmetic, combinational, and the designer knows its intended function.

In this work, the functional verification is solved using standard *linear algebra* techniques. In contrast to the existing ILP methods it does not require solving an ILP problem. Instead, the computation is based on a simple manipulation of a set of linear equations, similar to Gaussian elimination, without performing variable assignments (typical of SAT approach) and without imposing integer constraints on its variables. This method can be used to enhance capabilities of current SMT solvers by integrating it as one of the SMT engines (theories).

Thus it can be seen that verification of arithmetic designs remains an unsolved problem and that it could be solved only at the level that incorporates Boolean (bit) level view of the design.

#### CHAPTER 3

# ALGEBRAIC MODELING OF ARITHMETIC NETWORKS

#### 3.1 Arithmetic Network

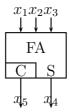

It has been shown that any arithmetic circuit can be expressed as a network of half-adders (HA), full-adders (FA) and basic logic gates (XOR, AND, OR, and INV) [45]. For this reason, in this work we will refer to such a representation as an arithmetic network, and we will use the terms circuit and network interchangeably. Furthermore, logic gates can also be converted to a simple combination of HA or FA circuits [49]. As a result, any arithmetic circuit can be expressed solely in terms of HA, FA and inverters. For the purpose of this work, an arithmetic network is represented as a directed graph G = (V, E), where V is a set of vertices and E is a set of directed edges. Vertex  $v \in V$  models an arithmetic operator (HA, FA) or inverter. An edge  $e \in E$  represents an electrical signal connecting two vertices. Each signal in the network is represented by a variable  $x_k$ .

Each arithmetic or logic operator is modeled with a set of linear equations that involves variables representing its input and output signals. For example, a half-adder (HA) with binary inputs a, b, binary outputs S (sum) and C (carry out), is modeled as

$$a+b=2C+S (3.1)$$

Similarly, a full adder (FA) with binary inputs a, b,  $c_{in}$ , binary outputs S and C is modeled as

$$a + b + c_{in} = 2C + S (3.2)$$

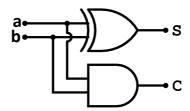

Figure 3.1. Logic-level Half-adder, HA(a, b)

Logic gates can be similarly represented by algebraic equations by deriving their functions from a half adder. This can be seen from Figure 3.1 of a logic-level half adder circuit. Specifically, XOR(a, b) is simply a sum output, S, of the half adder HA(a, b), and the AND(a, b) is the carry-out output, C, of HA(a, b).

The OR gate, d = OR(a, b), can be similarly derived (using deMorgan's law) from the carry out (AND) output of the HA by inverting its inputs and outputs:

$$(1-a) + (1-b) = 2(1-d) + S (3.3)$$

Or, equivalently

$$a + b = 2d - S \tag{3.4}$$

Combining this equation with the equation (3.1) for HA gives C + S = d. As a result, an OR(a, b) gate can be modeled with the following equations involving two half adders:

$$\begin{cases} a+b=2C+S\\ C+S=d \end{cases}$$

(3.5)

Figure 3.2 shows HA model for the basic logic gates, AND, OR and XOR. The correctness of the equations can be verified with the truth table provided in the figure.

**Figure 3.2.** Modeling of logic gates using half-adders: (a) S = XOR(a, b), C = AND(a, b) of half-adder; (b) OR gate d = C + S derived from two half-adders; (c) truth table for C, S, d.

Finally, the inverter gate y = INV(x) can be trivially modeled by the following equation: x + y = 1.

#### 3.2 Mathematical Model of Arithmetic Network

The functionality of an arithmetic network composed of HA, FA and INV nodes can be represented by a system of linear equations whose variables are inputs  $x_I$ , outputs  $x_O$  and internal signals  $x_S$ . There is one equation for each HA, FA, XOR gate or AND gate (3.1) and (3.2), and a pair of equations (3.5) for an OR gate.

**Example 1.** Figure 3.3 represents a 7-3 counter, composed of full adders.

The following equations can be derived for this network using the FA model described above.

$$\begin{cases} x_1 + x_2 + x_3 - 2x_{11} - x_{12} = 0 \\ x_4 + x_5 + x_6 - 2x_{13} - x_{14} = 0 \\ x_{12} + x_{14} + x_7 - 2x_{15} - x_{10} = 0 \\ x_{11} + x_{13} + x_{15} - 2x_8 - x_9 = 0 \end{cases}$$

(3.6)

Mathematically, we can represent it as:

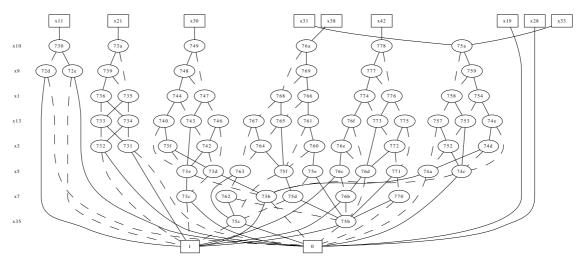

Figure 3.3. Arithmetic network of a 7-3 counter.

$$A x = b (3.7)$$

where A is an  $m \times n$  constraint matrix, x is an n-vector representing the signals and b is a constant vector. For the 7-3 counter, we have:

We now describe a method to represent such a network by a single *algebraic sig*nature expression that can be used to verify the circuit against its intended function.

First, we introduce the concept of a *Reference Signature*, which provides the expected relationship between primary inputs and outputs of the arithmetic circuit, and serves as a "golden model" of the circuit.

**Definition 3.2.1.** The Input Signature, or  $Sig_I(N)$ , of an arithmetic circuit, N, is a linear combination of primary input variables that represents the integer function computed by the circuit.

**Example 2.** For a 7-3 counter,  $N_{7-3}$ , with inputs  $\{x_1, x_2, x_3, x_4, x_5, x_6, x_7\}$ , the input signature is given by:

$$Sig_I(N_{7-3}) = x_1 + x_2 + x_3 + x_4 + x_5 + x_6 + x_7$$

(3.8)

**Example 3.** For a *n*-bit binary adder,  $N_A$ , with inputs  $\{a_0, b_0, \dots, a_{n-1}, b_{n-1}\}$ , the input signature is given by:

$$Sig_I(N_A) = \sum_{i=0}^{n-1} 2^i a_i + \sum_{i=0}^{n-1} 2^i b_i$$

**Example 4.** Consider a 2-bit unsigned multiplier,  $N_{M2}$ , with inputs  $\{a_0, b_0, a_1, b_1\}$ . Since the multiplier is a non-linear circuit, we first need to convert its primary inputs into new variables called partial product terms,  $pp_I$  as follows:

$$A \cdot B = (2a_1 + a_0) \cdot (2b_1 + b_0)$$

$$= 4a_1b_1 + 2a_1b_0 + 2a_0b_1 + a_0b_0$$

$$= 4pp_3 + 2pp_2 + 2pp_1 + pp_0$$

$$(3.9)$$

The variables  $pp_i$  become primary inputs to our multiplier and the input signature is given by:

$$Sig_I(N_{M2}) = 4pp_3 + 2pp_2 + 2pp_1 + pp_0 (3.10)$$

Mathematically, Input Signature,  $Sig_I(N)$ , can be represented as:

$$Sig_I(N) = r_I^T x_I$$

Where  $r_I$  is a input signature vector and  $x_I$  is a set of primary inputs.

**Example 5.** In the case of a 2-bit unsigned multiplier, we have:

$$r_{I}^{T} x_{I} = [4 \ 2 \ 2 \ 1] \left[ egin{array}{c} x_{1} \\ x_{2} \\ x_{3} \\ x_{4} \end{array} \right]$$

Where  $x_1 = pp_3$ ,  $x_2 = pp_2$ ,  $x_3 = pp_1$  and  $x_4 = pp_0$ .

**Definition 3.2.2.** The **Output Signature**, or  $Sig_O(N)$ , of an arithmetic circuit, N, is defined as a linear combination of the primary output signals that represent the n-bit encoding of the output word computed by the circuit.

**Example 6.** For a 7-3 counter,  $N_{7-3}$ , with outputs  $\{x_8, x_9, x_{10}\}$ , the output signature is given by:

$$Sig_O(N_{7-3}) = 4x_8 + 2x_9 + x_{10} (3.11)$$

**Example 7.** For a *n*-bit binary adder,  $N_A$ , with outputs  $\{C, S_{n-1}, S_{n-2}, \cdots, S_0\}$ , the output signature is given by:

$$Sig_O(N_A) = 2^n \cdot C + \sum_{i=0}^{n-1} 2^i \cdot S_i$$

**Example 8.** For a 2-bit unsigned multiplier,  $N_{M2}$ , with outputs  $\{z_3, z_2, z_1, z_0\}$ , the output signature is given by:

$$Sig_O(N_{M2}) = 8z_3 + 4z_2 + 2z_1 + z_0 (3.12)$$

In general, an output signature for any arithmetic circuit with n outputs  $S_i$  is represented as

$$Sig_O(N) = \sum_{i=0}^{n-1} 2^i S_i$$

Mathematically, Output Signature,  $Sig_O(N)$ , can be represented as:

$$Sig_O(N) = r_O^T x_O$$

Where  $r_O$  is a output signature vector and  $x_O$  is a set of primary outputs.

**Example 9.** In the case of a 2-bit unsigned multiplier, we have:

$$r_O^T x_O = [8 \ 4 \ 2 \ 1] \begin{bmatrix} z_3 \\ z_2 \\ z_1 \\ z_0 \end{bmatrix}$$

**Definition 3.2.3.** The **Reference Signature**, or Ref(N), of an arithmetic circuit is defined as the difference between its output signature and input signature and is given by:

$$Ref(N) = Sig_O - Sig_I$$

(3.13)

Mathematically in terms of input and output signature vectors, the Reference Signature, Ref(N) is defined as follows:

$$Ref(N) = \begin{bmatrix} -r_I \ r_O \end{bmatrix}^T \begin{bmatrix} x_I \\ x_O \end{bmatrix}$$

Where  $r_I$  is a input integer signature vector,  $r_O$  is an output integer signature vector,  $x_I$  is a set of primary inputs and  $x_O$  is a set of primary outputs.

**Example 10.** For the 7-3 counter example, with  $x_I = [x_1, \dots, x_7]$  and  $x_O = [x_8, x_9, x_{10}]$ , the reference signature, Ref(N), is given by:

$$Ref(N_{7-3}) = 4x_8 + 2x_9 + x_{10} - x_1 - x_2 - x_3 - x_4 - x_5 - x_6 - x_7$$

(3.14)

Or, equivalently as

$$[-r_I \ r_O]^T \begin{bmatrix} x_I \\ x_O \end{bmatrix} = [-1 \ -1 \ -1 \ -1 \ -1 \ -1 \ -1 \ 4 \ 2 \ 1] \begin{bmatrix} x_I \\ x_O \end{bmatrix}$$

Here the output signature corresponds to the 3-bit encoding of the output word, while the input signature is a sum of the input bits.

In our work an arithmetic network N will be similarly represented by its algebraic signature, Sig(N), and compared to the reference signature Ref(N). For the circuit to be functionally correct, its algebraic signature must match its reference signature, i.e.,

$$Sig(N) = Ref(N) \tag{3.15}$$

**Definition 3.2.4.** The Algebraic Signature, or Sig(N), of an arithmetic network N, is given by:

$$Sig(N) = r^T x$$

Where  $r = [r_I \ r_O \ r_S]$  is an integer signature vector and  $x = [x_I \ x_O \ x_S]^T$  is a set of variables representing signals.

Our goal is to compute an algebraic signature of a network as a means of proving its functionality expressed by the reference signature. This can be accomplished by setting up a linear system describing the arithmetic network and solving it using a linear programming (LP) solver described in next section.

#### CHAPTER 4

# MATHEMATICAL FORMULATION OF FUNCTIONAL VERIFICATION PROBLEM

This section describes the method for computing algebraic signature for arithmetic networks using linear algebra techniques and discusses the issue of signature matching.

#### 4.1 Mathematical Formulation

Let n be the total number of signals in the network, each represented by a variable  $x_k$ , and m be the number of linear equations in the system. The network is then represented in matrix form as

$$A x = b (4.1)$$

Where A is an  $m \times n$  matrix representing the network, x is an n-vector representing the signals, and b is a constant vector of size m.

The vector x of signal variables is further partitioned into a set of input signals  $x_I$ , output signals  $x_O$ , and internal signals  $x_S$ . Matrix A is similarly partitioned into submatrices  $A_I, A_O, A_S$ . Then, the system Ax = b can be written as:

$$A_I x_I + A_O x_O + A_S x_S = b$$

Where  $A_I$  is the matrix A restricted to the columns associated with primary input signals  $x_I$ ,  $A_O$  is the matrix A restricted to the columns of primary output signals  $x_O$  and  $A_S$  is the matrix A restricted to the columns of internal signals  $x_S$ .

For the 7-3 counter of Fig. 3.3,  $x^T = [x_1, \dots, x_{15}]$ , where  $x_I^T = [x_1, x_2, x_3, x_4, x_5, x_6, x_7]$ ,  $x_O^T = [x_8, x_9, x_{10}], x_S^T = [x_{11}, x_{12}, x_{13}, x_{14}, x_{15}], n = 15, m = 4 \text{ and } b = 0.$

Mathematical representation of the network is given as follows:

$$A = \begin{pmatrix} x_1 & x_2 & x_3 & x_4 & x_5 & x_6 & x_7 & | & x_8 & x_9 & x_{10} & | & x_{11} & x_{12} & x_{13} & x_{14} & x_{15} \\ 1 & 1 & 1 & 0 & 0 & 0 & 0 & | & 0 & 0 & | & -2 & -1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 0 & | & 0 & 0 & 0 & | & 0 & 0 & -2 & -1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 & | & 0 & 0 & -1 & | & 0 & 1 & 0 & 1 & -2 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & | & -2 & -1 & 0 & | & 1 & 0 & 1 & 0 & 1 \end{pmatrix} b = \begin{pmatrix} 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{pmatrix}$$

Given an arithmetic network, represented by A x = b, the system computes its algebraic signature vector  $r = [-r_I, r_O, r_S]$ , in an attempt to match the reference signature vector  $[-r_I, r_O]$ . This is done by combining the rows of A into a single algebraic signature  $Sig(N) = r^T x$ , by finding a linear combination  $\alpha$  of rows of A that produces  $r = [-r_I, r_O, r_S]$ . This operation is similar to a classical Gaussian elimination. Intuitively, since we want to eliminate all the internal signals from the algebraic signature, we want to have  $r_S = 0$ . By doing this, only primary input and output signals will be involved in the signature. It will be shown later that  $r_S = 0$  is sufficient but not a necessary condition for satisfying the reference signature.

Recalling that matrix A and variables x are partitioned into groups associated with inputs, outputs, and internal signals, the signature  $Sig(N) = r^T x$  for network N is obtained from a signature vector, r, computed as follows:

$$r = A^{T} \alpha \Leftrightarrow \begin{cases} A_{I}^{T} \alpha = -r_{I} \\ A_{O}^{T} \alpha = r_{O} \\ A_{S}^{T} \alpha = r_{S} \end{cases}$$

$$(4.2)$$

Here  $\alpha$  is a vector of integer coefficients (to be computed) that reduces linear equations defined by matrix A to the signature vector r. Vectors  $r_O$  and  $r_I$  are provided by the

user as part of the reference signature to be verified. Since the goal is to match the algebraic signature with the reference, we need to find vector  $\alpha$  such that

$$[A_I, A_O]^T \alpha = \begin{bmatrix} -r_I \\ r_O \end{bmatrix}$$

(4.3)

Such a computation can be done easily and efficiently using any linear programming (LP) system. The LP system solves these equations in terms of  $\alpha$  as a constraint satisfaction problem, with no objective function. Basically, searching for  $\alpha$  is searching for a linear combination of the rows of matrix A that results in the algebraic signature for the network. This is typically done using Simplex algorithm during the pre-solving phase of any LP system, which is fast and scalable.

Note that no integer constraints need to be imposed on variables x since we are solving for  $\alpha$  and not for x. This is the main difference between our approach and all the known approaches based on LP or ILP proposed so far, making this computation fast, efficient and highly scalable.

# 4.2 Computing the Signature

Given the network, described by A x = b, and its reference signature  $[-r_I, r_O] \begin{bmatrix} x_I \\ x_O \end{bmatrix}$ , its algebraic signature,  $r^T x$ , is computed with the following two-step approach. First we attempt to solve the system described by equations,

$$\begin{cases} A_I^T \alpha = -r_I \\ A_O^T \alpha = r_O \\ A_S^T \alpha = 0 \end{cases}$$

with given  $r_I$ ,  $r_O$  and with  $r_S$  forced to 0. If the solution to this system exists, there exists  $\alpha$  for which these equations hold, the reference signature is valid and the

circuit is proved to be correct. In this case resulting vector  $\alpha$  provides the desired linear combination of the rows of A that reduces it to the reference signature without any internal signals,  $x_S$ .

If the system is infeasible, we relax the constraint on  $r_S$  so that  $r_S$  is no longer required to be 0 and solve a reduced system in which  $r_S$  is allowed to take arbitrary value. We refer to this process as "Completing the Signature" (in terms of  $r_S$ ), i.e., we solve the following linear system for  $\alpha$  using standard LP solver:

$$\begin{cases}

A_I^T \alpha = -r_I \\

A_O^T \alpha = r_O

\end{cases}$$

(4.4)

Note that the vector  $r_S$  associated with internal variables  $x_S$  is not being used in the computation. If the system still has no solution, i.e, there is no linear combination of rows of A that will produce the algebraic signature that matches the reference signature vector  $[-r_I, r_O]$ , the circuit is incorrect. If the system has solution,  $\alpha$ , the signature vector  $r_S$  associated with the internal variables is computed as follows:

$$r_S = A_S^T \alpha$$

Ideally, we would like to have all the internal variables eliminated from the algebraic signature, i.e.,  $r_S = 0$ , as a condition for satisfying the reference signature. However, this may not always be possible with a basic system of equality constraints, A x = b, and additional constraints of Boolean nature may need to be imposed. This issue, and the consequences of non-zero  $r_S$ , will be illustrated by the following examples.

Let us revisit the 7-3 counter circuit described by equation (3.6) with the reference signature given by equation (3.14). Its input and output reference signature vectors are given by:

$$r_I^T = \begin{bmatrix} -1 & -1 & -1 & -1 & -1 & -1 \\ T_O^T = \begin{bmatrix} 4 & 2 & 1 \end{bmatrix}$$

According to our procedure, we first force  $r_S$  to zero and compute  $\alpha$  using the following relationship:

$$[A_I, A_O, A_S] \alpha = \begin{bmatrix} -r_I \\ r_O \\ 0 \end{bmatrix}$$

The system has the following solution:

$$\alpha^T = [-1 \ -1 \ -1 \ -2]$$

Subsequently, the following signature is computed for this system:

$$Sig(N_{7-3}) = r^T x = -x_1 - x_2 - x_3 - x_4 - x_5 - x_6 - x_7 + 4x_8 + 2x_9 + x_{10}.$$

The internal signals  $x_S = [x_{11}, x_{12}, x_{13}, x_{14}, x_{15}]$  have been completely eliminated, so that the computed signature matches the reference signature and the design is considered correct.

## 4.3 Residual Expression

An interesting question arises, what if the computed signature Sig(N), in addition to the reference signature, contains an expression associated with the internal signals, i.e., if  $r_S \neq 0$ . We refer to such an expression as a *Residual Expression*, denoted RE(N):

$$RE(N) = Sig(N) - Ref(N) = r_S^T x_S$$

(4.5)

Does the existence of a non-empty residual expression,  $RE(N) \neq \emptyset$  imply that the system does not satisfy the reference signature and the design is incorrect? It turns out that it is not necessarily the case, and that  $r_S = 0$  is a sufficient but not a necessary condition for the circuit to be correct. It will be shown in Chapter 5 that as long

as RE(N) evaluates to zero for all values of internal signal variables  $x_S$  produced by the network, the network signature will match the reference signature and the design will be correct. This case is illustrated with the following example.

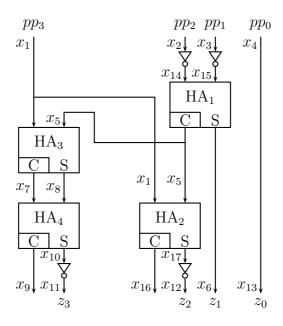

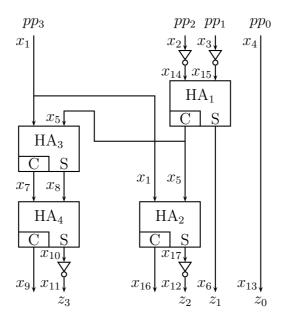

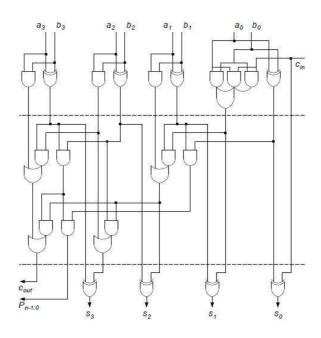

**Example 1:** Consider a signed  $2\times 2$  multiplier network,  $N_{M2}$ , shown in Figure 4.1.

Figure 4.1. Signed  $2 \times 2$  multiplier network.

The network is described by the following equations:

$$\begin{cases} x_{14} + x_{15} - x_6 - 2x_5 = 0 \\ x_1 + x_5 - x_{17} - 2x_{16} = 0 \\ x_7 + x_8 - x_{10} - 2x_9 = 0 \\ x_1 + x_5 - x_8 - 2x_7 = 0 \\ x_2 + x_{14} = 1 \\ x_3 + x_{15} = 1 \\ x_4 - x_{13} = 0 \\ x_{17} + x_{12} = 1 \\ x_{10} + x_{11} = 1 \end{cases}$$

$$(4.6)$$

or, equivalently in matrix A x = b with:

Here  $x_1 = pp_3$ ,  $x_2 = pp_2$ ,  $x_3 = pp_1$ ,  $x_4 = pp_0$  and  $x_{11} = z_3$ ,  $x_{12} = z_2$ ,  $x_6 = z_1$ ,  $x_{13} = z_0$ . The combination of HA<sub>3</sub> and HA<sub>4</sub> models an OR gate (see equation 3.5) that appears in this network. Inputs to the network are partial product terms  $\{pp_0, pp_1, pp_2, pp_3\}$ , generated by a partial product generator module, from the actual inputs of the multiplier,  $a_1, a_0, b_1, b_0$ . Hence, the expected input signature,  $Sig_I(N_{M2})$ , for the network is:

$$Sig_I(N_{M2}) = (-2a_1 + a_0)(-2b_1 + b_0)$$

$$= 4a_1b_1 - 2a_1b_0 - 2a_0b_1 + a_0b_0$$

$$= 4pp_3 - 2pp_2 - 2pp_1 + pp_0$$

$$(4.7)$$

The output signature is obtained directly from the encoding of the output bits,  $Sig_O(N_{M2}) = -8z_3 + 4z_2 + 2z_1 + z_0$ , so the reference signature for this design is:

$$[r_O, -r_I]^T \begin{bmatrix} x_O \\ x_I \end{bmatrix} = Ref(N_{M2}) = -8z_3 + 4z_2 + 2z_1 + z_0 - 4pp_3 + 2pp_2 + 2pp_1 - pp_0$$

In order to compute an algebraic signature, first we try to solve the system for  $\alpha$  by forcing  $r_S$  to zero using the following relationship:

$$A^T \alpha = \begin{bmatrix} -r_I \\ r_O \\ 0 \end{bmatrix}$$

In this case there is no feasible solution to the system. Therefore, we try to complete the signature in-terms of  $r_S$ . Subsequently we must consider  $r_S$  to be a free signal and find  $\alpha$  using the following relationship:

$$[A_I, A_O]^T \alpha = \begin{bmatrix} -r_I \\ r_O \end{bmatrix}$$

This system has a solution,  $\alpha^T = \begin{bmatrix} -2 & -4 & -8 & 0 & -8 & 4 & 1 & 2 & 2 \end{bmatrix}$  and the corresponding algebraic signature computed by the system is:

$$Sig(N_{M2}) = -4pp_3 + 2pp_2 + 2pp_1 - pp_0 - 8z_3 + 4z_2 + 2z_1 + z_0$$

$$+8x_7 + 4x_8 - 8x_{10} + 4x_{17}$$

$$(4.8)$$

In this case  $Sig(N) - Ref(N) \neq \emptyset$ , and has a residual expression,

$$RE(N_{M2}) = r_S^T x_S = -8x_7 - 4x_8 + 8x_{10} - 4x_{17}$$

associated with the internal signals. Does this mean that our system does not satisfy the reference signature and the design is incorrect? It turns out that this expression actually evaluates to zero with the help of additional constraints, to be discussed in the next section.

In summary, we have seen two cases:

• When  $r_S = 0$ , all the internal signals are automatically eliminated from the input/output relationship

• When  $r_S \neq 0$ , some internal signals. are present but the residual expression can be reduced to zero for all values of the internal variables that can be produced by the system which will be discussed in the next section.

#### CHAPTER 5

#### THEOREMS AND BOOLEAN MODELS

In this section we will present a set of theorems that govern our approach to functional verification of arithmetic circuits. In the following, the circuit is considered correct if it satisfies the functionality expressed by the reference signature i.e., if its algebraic signature matches the reference signature. We also discuss the need for additional constraints to properly model the inherent Boolean nature of arithmetic circuits.

#### 5.1 Theorems

**Theorem 5.1.1.** Given an arithmetic circuit N represented by A = b with reference signature  $Ref(N) = [-r_I, r_O]^T \begin{bmatrix} x_I \\ x_O \end{bmatrix}$ , the circuit is incorrect if there is no solution to equation,

$$[A_I, A_O]^T \alpha = \begin{bmatrix} -r_I \\ r_O \end{bmatrix}$$

*Proof.* The lack of solution to this equation indicates that the coefficients associated with the input and output variables do not match those of the reference signature. Hence the circuit does not satisfy the reference signature and by definition it is in-correct.

The remaining theorems consider the case when the computed algebraic signature contains residual expression, RE(N). We distinguish two cases:

- When there is no residual expression  $(RE = \phi)$  in the algebraic signature, i.e. when  $r_S = 0$ ; and

- When RE(N) is not empty  $(r_S \neq 0)$  but  $RE(N) = r_S^T x_S$  evaluates to zero for all possible values of internal variables  $x_S$  produced by the circuit.

**Theorem 5.1.2.** Given an arithmetic circuit N represented by A = b with reference signature  $Ref(N) = [-r_I, r_O]^T \begin{bmatrix} x_I \\ x_O \end{bmatrix}$ , the circuit is correct if its computed algebraic signature matches exactly the reference signature and contains no residual expression RE(N), i.e.,  $r_S = 0$ . That is  $RE(N) = \phi$  is a sufficient condition for the arithmetic circuit to be correct.

*Proof.* By definition, the Residual Expression, RE(N), is the difference between its algebraic signature  $(r^T x)$  and reference signature,  $[-r_I, r_O]^T \begin{bmatrix} x_I \\ x_O \end{bmatrix}$ , that is

$$RE(N) = r^T x - [-r_I, r_O]^T \begin{bmatrix} x_I \\ x_O \end{bmatrix}$$

Since

$$r^T \ x = [-r_I, r_O, r_S]^T \begin{bmatrix} x_I \\ x_O \\ x_S \end{bmatrix}$$

We have

$$RE(N) = [-r_I, r_O, r_S]^T \begin{bmatrix} x_I \\ x_O \\ x_S \end{bmatrix} - [-r_I, r_O]^T \begin{bmatrix} x_I \\ x_O \end{bmatrix} = r_S^T x_S$$

If the circuit has no residual expression,  $RE(N) = \phi$ , then

$$RE(N) = r_S^T x_S = 0$$

which implies that  $r_S = 0$ . That is, no internal signal variables are involved in the signature and hence the algebraic and reference signatures match indicating that the circuit is correct.

**Example:** To illustrate this case, consider again a (7-3) counter in Figure 5.1.

Figure 5.1. Arithmetic network of a (7-3) counter.

The network has the following sets of variables,  $x_I^T = [x_1, x_2, x_3, x_4, x_5, x_6, x_7]$ ,  $x_O^T = [x_8, x_9, x_{10}], x_S^T = [x_{11}, x_{12}, x_{13}, x_{14}, x_{15}]$  and can be described by a set of linear equations 3.6, repeated here for reference.

$$\begin{cases} x_1 + x_2 + x_3 - 2x_{11} - x_{12} = 0 \\ x_4 + x_5 + x_6 - 2x_{13} - x_{14} = 0 \\ x_{12} + x_{14} + x_7 - 2x_{15} - x_{10} = 0 \\ x_{11} + x_{13} + x_{15} - 2x_8 - x_9 = 0 \end{cases}$$

The reference signature is given by:

$$Ref(N) = 4x_8 + 2x_9 + x_{10} - (x_1 + x_2 + x_3 + x_4 + x_5 + x_6 + x_7)$$

(5.1)

ans reference signature vectors are given by:

$$-r_I^T = [1 \ 1 \ 1 \ 1 \ 1 \ 1 \ 1]$$

$$r_O^T = [4 \ 2 \ 1]$$

Computation of the signature using the linear system

$$[A_I, A_O, A_S]^T \alpha = \begin{bmatrix} -r_I \\ r_O \\ 0 \end{bmatrix}$$

gives the following solution:

$$\alpha^T = [-1 \ -1 \ -1 \ -2]$$

That is, there exists a linear combination  $\alpha$  of rows of A whose sum reduces to a reference signature without any internal signals  $(r_S = 0)$ . The resulting algebraic signature is:

$$r^T x = 4x_8 + 2x_9 + x_{10} - x_1 - x_2 - x_3 - x_4 - x_5 - x_6 - x_7$$

The signature is identical with the reference signature of Equation 5.1 and does not contain any of the internal signals,  $x_s$ , i.e.,  $r_s = 0$ . Hence the design is correct.

A stronger, necessary and sufficient condition for circuit correctness is that RE(N) = 0, i.e., when a possibly non-empty  $RE(N) = r_S^T x_S$ , with  $r_S \neq 0$ , evaluates to zero for

all possible values of  $x_S$  generated by the circuit. The fact that  $RE(N) \neq \phi$  does not necessarily mean that the circuit is *incorrect*. The numerical value of RE(N) must be proved to be zero.

**Theorem 5.1.3.** Given an arithmetic circuit N represented by A = b with reference signature  $Ref(N) = [-r_I, r_O]^T \begin{bmatrix} x_I \\ x_O \end{bmatrix}$ , the circuit is correct iff  $RE(N) = r_S^T x_S = 0$  i.e., it evaluates to zero for all the values of  $x_S$  produced by the network.

*Proof.* As previously shown, the residual expression RE(N) can be written as

$$RE(N) = [-r_I, r_O, r_S]^T \begin{bmatrix} x_I \\ x_O \\ x_S \end{bmatrix} - [-r_I, r_O]^T \begin{bmatrix} x_I \\ x_O \end{bmatrix} = r_S^T x_S$$

If the circuit has non-empty residual expression, the vector  $r_S \neq 0$  and the only way RE(N) can evaluate to zero is that the linear combination of variables  $x_S$  evaluates to zero. If this is the case, RE(N) = 0 and Sig(N) = Ref(N). If the residual expression evaluates to zero for all values of  $x_S$ , then  $RE(N) = r_S^T x_S = 0$  and Sig(N) = Ref(N), i.e., the circuit is correct.

Now, let's assume that the circuit is correct, and show that it implies that RE(N) = 0. Again, recall that Sig(N) - Ref(N) = RE(N). If the circuit is correct, then Sig(N) = Ref(N) and RE(N) = 0

Note that Theorem 5.1.3 expresses a more general case than the one stated in Theorem 5.1.2 for  $RE(N) = \phi$ . This is because  $RE(N) = r_S^T x_S = 0$  can be obtained by either having  $r_S = 0$  (empty RE(N)) or, for non-zero  $r_S$ , having the linear combination  $r_S^T x_S$  evaluate to zero. This theorem points out to an interesting difficulty in proving correctness of arithmetic circuit in cases where RE is non-empty. Additional constraints must be imposed on the circuit in an attempt to simplify linear equations or to prove RE = 0 directly.

The following section explains this issue.

### 5.2 Imposing Binary Constraints

Proving that RE = 0 for all the values of internal signals poses a new problem that requires additional insight into a binary nature of the network. This can be done by examining the circuit and deriving additional constraints, in form of Boolean invariants and assertions. Deriving such invariants is done routinely and efficiently by logic synthesis and verification tools, such as ABC [22, 5]. However, our initial experience shows that the problem may be simpler as it relates to a special class of designs, namely integer arithmetic circuits. These constraints are of binary nature and can be viewed as special cases of Boolean constraints needed to properly model the integer arithmetic semantic of the network. Our initial analysis shows that these constraints can be classified as follows:

- Structural constraints, caused by fanout of internal signals; these can be easily modeled as equality constraints on the corresponding signals (such as  $x_8 = x_{17}$  in Example 2);

- Boolean constants that can be propagated in the network, such as the C output of two half-adders connected in series (e.g., signal  $x_9$  in Example 2, Figure 4.1); and

- Binary constraints that may result from specific network configurations, such as internal signals of a gate-level implementation of a full-adder. In some cases, such as those for multipliers shown in Table 7.4, they can be derived relatively easily, but in general cases the problem may require more work.

# 5.3 Deriving Boolean Constraints

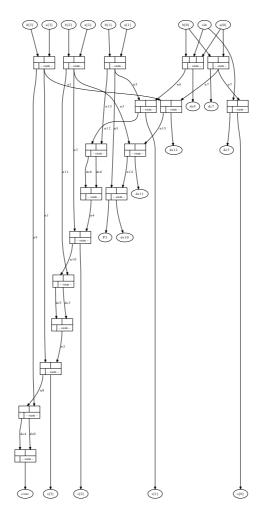

We first demonstrate how to derive Boolean constraints in a HA network shown in Figure 5.2. Such a network often appears in arithmetic circuits composed of wallace trees. We will show that this network represents a full adder (FA) circuit and will

Figure 5.2. Configuration in Netlist.

derive the constraints on some of the internal signals resulting from this configuration. This will provide important Boolean information necessary to correctly model arithmetic circuit as a system of algebraic equations.

First we prove that  $x_{11} = 0$ . The C and S outputs of a HA (in this case  $HA_3$ ) are never equal to 1 at the same time, i.e.,  $C \cdot S = 0$ . Since  $x_{11} = x_{10} \cdot x_9$ , we have  $x_{11} = 0$ . Hence, the equations 5.2 can be rewritten as