## Universitat Autònoma de Barcelona

# ESTUDIO DE UN KIT DE DISEÑO MIXTO CON SOFT-CORE MICROBLAZE E IP's, PARA EL CONTROL ESP, ASR Y ABS

Memoria del proyecto

de Ingeniería Técnica en

Informática de Sistemas

realizado per

Danilo Sanz Moreno

i dirigido per

Raúl Aragonés Ortiz

### Escola d'Enginyeria

Sabadell, Junio de 2010

## Índice

| Sec | cción                                        | Página |

|-----|----------------------------------------------|--------|

| 1.  | Introducción                                 | 6      |

|     | 1.1. Tipología y palabras clave              | 6      |

|     | 1.2. Descripción                             | 6      |

|     | 1.3. Estructura de la memoria                | 7      |

|     | 1.4. Definiciones, acrónimos y abreviaciones | 8      |

|     | 1.5. Objetivos                               | 10     |

| 2.  | Estudio de viabilidad                        | 12     |

|     | 2.1. Marco del proyecto                      | 12     |

|     | 2.1.1. Contexto                              | 12     |

|     | 2.1.2. Frenado antibloqueo                   | 13     |

|     | 2.1.3. El control de tracción                | 14     |

|     | 2.1.4. Control de estabilidad                | 15     |

|     | 2.1.5. Disponibilidad en el mercado          | 17     |

|     | 2.2. Partes interesadas                      | 19     |

|     | 2.2.1. Intereses ( Stakeholders )            | 19     |

|     | 2.2.2. Perfiles de usuario                   | 20     |

|     | 2.2.3. Project Team                          | 20     |

|     | 2.3. Fases del proyecto y planificación      | 21     |

|     | 2.3.1. Fases del proyecto                    | 21     |

|     | 2.3.2. Planificación                         | 21     |

|     | 2.4. Descripción del sistema                 | 23     |

|     | 2.5. Metodología de desarrollo               | 23     |

3.

| 2.6 | . Entor   | no de prototipado         | 24 |

|-----|-----------|---------------------------|----|

|     | 2.6.1.    | Descripción               | 24 |

|     | 2.6.2.    | EI FPGA                   | 26 |

|     | 2.6.3.    | SystemOnChip PSoC         | 27 |

|     | 2.6.4.    | Memoria flash serie       | 29 |

|     | 2.6.5.    | Memoria flash paralelo    | 30 |

|     | 2.6.6.    | Sensor de temperatura     | 31 |

| 2.7 | '. Perifé | éricos                    | 32 |

|     | 2.7.1.    | Acelerómetro              | 32 |

|     | 2.7.2.    | Sensor óptico             | 34 |

| 2.8 | . Estad   | o del arte                | 35 |

|     | 2.8.1.    | El microprocesador        | 35 |

|     | 2.8.2.    | El Bus                    | 39 |

|     | 2.8.3.    | Sistema operativo         | 41 |

| 2.9 | . Entor   | no de desarrollo software | 42 |

|     | 2.9.1.    | Xilinx EDK                | 42 |

|     | 2.9.2.    | Cypress PsoC Designer     | 42 |

|     | 2.9.3.    | CypressPsoc Programmer    | 43 |

|     | 2.9.4.    | Avnet Programming Utility | 43 |

|     | 2.9.5.    | Microsoft Visual C#       | 43 |

| 2.1 | .0.       | Coste del sistema         | 43 |

| 2.1 | .1.       | Evaluación de riesgos     | 45 |

|     | 2.11.1    | . Lista de riesgos        | 45 |

|     | 2.11.2    | . Catalogación de riesgos | 45 |

|     | 2.11.3    | . Plan de contingencia    | 46 |

| 2.1 | .2.       | Conclusiones              | 46 |

| Dis | seño de   | el sistema                | 47 |

|    | 3.1. Introd | ducción                           | 47 |

|----|-------------|-----------------------------------|----|

|    | 3.2. Comp   | onentes principales de Microblaze | 47 |

|    | 3.3. El mé  | todo Execute in Place             | 48 |

|    | 3.4. Los IP | Core's                            | 49 |

|    | 3.5. Prueb  | as de rendimiento                 | 50 |

|    | 3.5.1.      | Dhrystone                         | 50 |

|    | 3.5.2.      | Whetstone                         | 51 |

|    | 3.6. Concl  | usiones                           | 52 |

| 4. | Implemen    | tación                            | 52 |

|    | 4.1. Medi   | da de la temperatura              | 53 |

|    | 4.1.1.      | Obtención de los datos            | 53 |

|    | 4.1.2.      | Programación                      | 55 |

|    | 4.2. IPCor  | e acel2axis                       | 57 |

|    | 4.2.1.      | Lectura pulso activo              | 57 |

|    | 4.2.2.      | Demodulación de ancho de pulso    | 58 |

|    | 4.2.3.      | Cálculo de la aceleración         | 59 |

|    | 4.2.4.      | Mapeado de puertos                | 60 |

|    | 4.2.5.      | Calibrado de acelerómetro         | 61 |

|    | 4.3. Senso  | or óptico                         | 61 |

|    | 4.3.1.      | Conversión de la entrada          | 61 |

|    | 4.3.2.      | Protocolo comunicación PSoC-FPGA  | 62 |

|    | 4.3.3.      | Mapeado de puertos                | 64 |

|    | 4.4. Progr  | ama MicroBlaze                    | 64 |

|    | 4.4.1.      | Envío a PC                        | 64 |

|    | 4.4.2.      | Cálculos tratados                 | 65 |

|    | 4.5. Aplica | ación para PC                     | 65 |

| 5. | Pruebas     |                                   | 67 |

Autor : Danilo Sanz Moreno Documento : Memoria final del proyecto

|    | 5.1. Introducción                      | 67 |

|----|----------------------------------------|----|

|    | 5.2. Pruebas del acelerómetro          | 67 |

|    | 5.3. Pruebas del sensor de temperatura | 68 |

|    | 5.4. Pruebas del sensor óptico         | 69 |

|    | 5.5. Pruebas del sistema global        | 70 |

| 6. | Conclusiones y futuras ampliaciones    | 71 |

|    | 6.1. Conclusiones                      | 71 |

|    | 6.2. Futuras Ampliaciones              | 72 |

| 7. | Bibliografía                           | 73 |

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 1. Introducción

### 1.1. Tipología y palabras clave

Tipología: Codiseño hardware/software

Palabras clave: PSoC<sup>(1)</sup>, FPGA<sup>(2)</sup>, Sensor, Codiseño hardware/software, C#

### 1.2. Descripción

Éste proyecto consiste en el estudio de una placa de prototipado mixta analógico-digital formada principalmente por un PSoC<sup>(1)</sup>, una FPGA<sup>(2)</sup> y memoria flash para determinar sus capacidades en sistemas de control ESP<sup>(3)</sup>, ASR<sup>(4)</sup> y ABS<sup>(5)</sup>.

El estudio se basa en concluir la lógica que se puede añadir al dispositivo para enfocarlo a unas aplicaciones que, a pesar de ser muy comunes en coches, está poco desarrollado en motocicletas y ciclomotores. Es por ello surge el interés de diseñar un sistema del más bajo coste posible para impulsar su desarrollo.

El valor final del estudio se encuentra en la comparación y el comentario de las opciones de configuración más adecuadas para, posteriormente, llevar a cabo la implementación de un sistema hardware que mida las principales variables necesarias para poder llevar su finalidad mediante la programación software.

- (1) FPGA ( Field Programmable Gate Array ) es un chip reprogramable que permite la implementación de circuitos hardware digitales por medio de conexiones entre bloques lógicos mediante su programación via software.

- (2) PSoC ( Programmable System On Chip ) es un microcontrolador reprogramable de la marca *Cypress* que como particularidad permite la implementación de determinadas funciones analógicas y digitales gracias a la incorporación de módulos prediseñados.

- (3) ESP ( *Electronic Stability Program* ) es un medio de seguridad que actúa sobre una de las ruedas del vehículo frenándola en casos de giro para evitar casos de pérdida de adherencia.

- (4) ASR ( Automatic Stability Control ) es un sistema de seguridad que corrige la situación de patinaje de una rueda desacelerándola o frenándola.

- (5) ABS ( Antilock Brake System ) es un dispositivo que actúa sobre los frenos haciendo que estos no bloqueen la rueda, ya que en ese caso pierden adherencia.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

1.3. Estructura de la memoria

Esta memoria se divide en ocho capítulos divididos cada uno de ellos en sub-apartados

correspondientes a la explicación llevada a cabo.

En el primer capítulo se hace una pequeña introducción donde se introduce al lector a los

objetivos del proyecto y el contexto que abarca.

El segundo capítulo se dedica a hacer un estudio de viabilidad. En este punto se estudia el

caso al que estará destinado el hardware final y la función de los componentes. Se explican

los componentes que se utilizarán y el estado del arte para determinar el sistema base.

El tercer capítulo corresponde al diseño, donde se explica el sistema base, su funcionamiento

y los elementos que contiene. También aquí se muestran los resultados de las pruebas de

rendimiento realizadas, y se compara con otras.

El quinto capítulo corresponde a la implementación del sistema, se explican todos los

elementos que interactúan y sus aspectos de programación más importante.

El sexto capítulo muestra los resultados de las pruebas de todas las implementaciones

llevadas a cabo.

En el séptimo punto corresponde a las conclusiones acerca del sistema y a las mejoras que se

le pueden hacer.

El octavo capítulo muestra la bibliografía consultada por el alumno.

7

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 1.4. Definiciones, acrónimos y abreviaciones

**AVNET xc3s400A Eval Board**: marca y modelo de la placa de prototipado estudiada.

Big-endian: Determina el orden de los bits en memoria, que se escriben en el orden natural.

**BlockRAM**: memoria formada por bloques lógicos reconfigurables embebidos en la FPGA.

Caché: Memoria de rápido acceso situada muy cerca del procesador.

**CLB:** Son las siglas de *Configurable Logic Block* y es cada uno de los bloques que contiene un FPGA en su interior para formar funciones.

**Cypress**: Fabricante de microcontroladores PSoC, en concreto, el modelo *CY8C24894* es el que se encuentra en la placa.

**g**: Unidad estándar de medida utilizada por acelerómetros, equivale a la unidad de la gravitación terrestre de 9.81 m/s<sup>2</sup> aproximadamente.

**Harvard**: Arquitectura en que se divide las instrucciones de los datos para ubicarlos en memorias diferentes. Es el método alternativo a la arquitectura Von Neumann.

**Interrupciones** : Sistema de procesamiento por el cual se interrumpe el flujo de ejecución del programa para atender la petición de un periférico de entrada/salida.

**IPCore (** *Intellectual Property Core* ) : Software prediseñado para su implementación en FPGA's u otros dispositivos programables, su punto fuerte es la portabilidad entre dispositivos y en muchas ocasiones la optimización de recursos de éstos.

**LUT :** Son las siglas de Logic-Up-Table, es un vector de memoria con valores predefinidos.

**Pipeline :** Sistema por el que al dividir una instrucción de procesamiento en varias etapas, varias instrucciones pueden estar ejecutándose al mismo tiempo cada una en su correspondiente etapa, de esta manera el número de etapas define el número de instrucciones que pueden estar ejecutándose simultáneamente.

**PSoC** ( *Programmable System On Chip* ) : Microcontrolador reprogramable de la marca *Cypress* que como particularidad permite la implementación de determinadas funciones analógicas y digitales.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

**RISC**: Son las siglas de *Reduced Instruction Set Computer* y es una característica de la arquitectura de microprocesador. En ésta las instrucciones son pequeñas y del mismo tamaño con lo que suele tomar menos tiempo de ejecución.

**SPARC** : Son las siglas de Schalable Processor Architecture, es una arquitectura RISC de carácter libre.

Spartan-3A XC3S400A: Familia y modelo del FPGA contenido en la placa objeto del estudio.

**System-On-Chip**: Tipo de microcontroladores que se diferencian a los habituales por permitir la reconfiguración sin estar sometidos a la dependencia de hardware que lleven alrededor.

Xilinx: Famoso fabricante de FPGA's, es el que desarrolla Spartan-3A.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 1.5. Objetivos

- O.1. Tener un estudio donde se analicen las opciones de implementación más provechosas para la FPGA y se elija la más adecuada.

- O.2. Implementar un sistema base embebido en la FPGA con las opciones escogidas.

- O.3. Realizar pruebas de rendimiento sobre el sistema de procesado implementado y hacer una comparativa con otros.

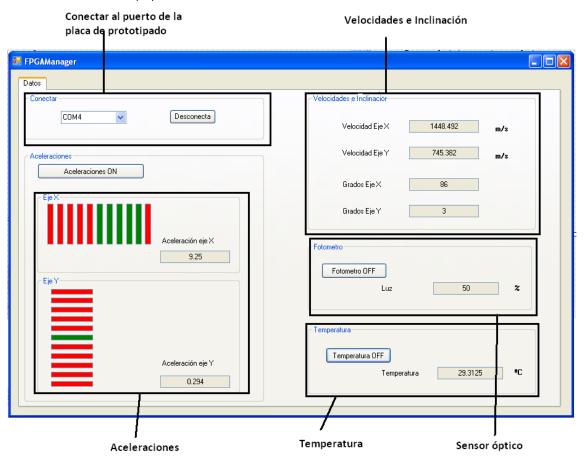

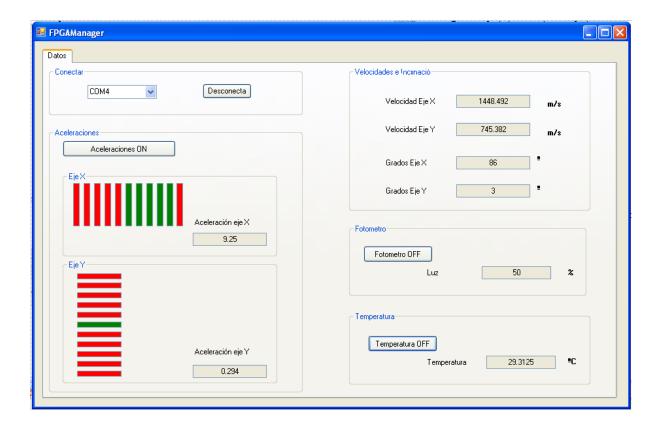

- O.4. Obtener un programa destinado a PC con el que se pueda interactuar con el dispositivo.

- O.5. Realizar la medida, el tratamiento y el envío a PC de datos referentes a la temperatura ambiente a través de un sensor de temperatura.

- O.6. Realizar un IPCore que nos permita obtener la aceleración a través de un acelerómetro. Estos datos deben ser tratados mediante cálculos para obtener velocidad, inclinación y enviarlos a PC.

- O.7. Estudiar e implementar el tratamiento de señales analógicas por el PSoC y enviarlas en formato digital a la FPGA, una vez aquí se podrán tratar junto al resto de datos.

Tabla 1.1: Prioridad de los objetivos

|            | Crítico | Prioritario | Secundario |

|------------|---------|-------------|------------|

| 01         | X       |             |            |

| 02         | X       |             |            |

| О3         | X       |             |            |

| 04         |         | Х           |            |

| <b>O</b> 5 |         | Х           |            |

| <b>O</b> 6 |         | Х           |            |

| 07         |         |             | Х          |

Autor : Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 1.6. Material entregado

- a) Un documento que contiene los detalles del estudio llevado a cabo.

- b) Una aplicación diseñada para PC que permite visualizar los datos recibidos del hardware programado.

- c) Un cd que contiene los archivos fuentes, los proyectos y los ejecutables con las instrucciones a seguir.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2. Estudio de viabilidad

### 2.1. Marco del proyecto

Este apartado introduce al lector a los sistemas a los que se pretende enfocar el hardware y explica su funcionamiento, justificando en todos los casos la forma en que se podría tratar con los componentes utilizados.

#### 2.1.1. Contexto

Desde hace años nos encontramos en los automóviles sistemas de seguridad pasiva basados en el antibloqueo de frenos, el control de tracción y el control de estabilidad. En las motocicletas estos sistemas son novedosos y no están muy estandarizados debido a su precio y a que en la mayoría de ocasiones ni siquiera se dispone como equipamiento adicional.

Para llevar a cabo estos sistemas se requiere realizar medidas de velocidad en las ruedas. Aunque estas medidas se pueden limitar únicamente a la velocidad de la rueda para conocer la desaceleración, se pueden complementar con un acelerómetro de dos ejes y un sensor de temperatura. De esta manera el acelerómetro puede medir el ángulo del manillar con un eje y la inclinación lateral de la motocicleta con el otro, mientras, el sensor de temperatura se destina a detectar el sobrecalentamiento del disco de freno.

El complemento a este proyecto sería un tratamiento de las señales que permita actuar frenando ligeramente la rueda.

Lo que se pretende es montar un hardware que quizás se pueda implementar para llevar a cabo aplicaciones de este calibre. Para tal fin se dispone de una placa de prototipado que puede albergar sistemas basados en microprocesadores sintetizables, combinados con los IPCores necesarios, para el tratado de las señales externas. Además, ésta dispone de un SystemOnChip PSoC incorporado que permite el tratado de señales de Entrada/Salida tanto analógicas como digitales. De este modo surge un interés por conocer las capacidades que pueda tener el kit en este ámbito. Además de la placa, el acelerómetro y el sensor de temperatura se dispone de un sensor óptico que se encargaría de medir la velocidad de la rueda.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2.1.2. Frenado antibloqueo

El ABS o sistema de frenos antibloqueo se basa en la detección del bloqueo, lo cual produce que el neumático se deslice en el asfalto. Para tratar el problema se dispone el sensor óptico y el sensor de temperatura.

### Bloqueo de ruedas

El método antibloqueo que se puede tratar a partir de este proyecto es la detección de un sobrecalentamiento de los discos de frenos y una desaceleración muy brusca de las ruedas, con lo cual la rueda está a punto de quedar bloqueada.

Para obtener la desaceleración de la ruedas se utiliza el foto-sensor, con el que se puede calcular la velocidad angular de la rueda y la aceleración, teniendo en cuenta que la aceleración es el diferencial de velocidad respecto al tiempo. El sensor de temperatura situado cerca del disco de frenos nos debe aproximar la temperatura del disco de frenos. En caso de calentarse en exceso, también se soltaría el freno momentáneamente para que el disco pueda recuperar su temperatura.

El hecho de contemplar la temperatura como una variable supone un avance en estas aplicaciones, ya que hasta el momento ningún sistema ABS ha incorporado la medición térmica.

### Análisis

Tabla 2.1: Actuadores ABS

| Elementos<br>actuadores | Acelerómetro | Sensor óptico                                                          | Sensor de<br>temperatura                   |

|-------------------------|--------------|------------------------------------------------------------------------|--------------------------------------------|

| Bloqueo de frenos.      | No.          | Sí, para obtener la<br>velocidad de giro y<br>sacar la desaceleración. | Sí, para conocer la temperatura del disco. |

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2.1.3. El control de tracción

El ASR o control de tracción es un sistema que protege el vehículo frente el patinaje de una rueda. Este caso es especial en aceleraciones o frenadas y, a diferencia del ESP descrito más abajo, el ASR está enfocado únicamente a los casos de pérdida de adherencia de las ruedas. Estos casos pueden darse debidos a una aceleración o bien en una frenada. Para ello utiliza los mismos mecanismos que el ABS y su actuación es la de desacelerar el vehículo o la de frenar una de las ruedas.

#### Actuación en aceleración

El primer caso a tratar es la pérdida de tracción de una rueda debido a una aceleración. Hay que destacar que todas las motos a nivel comercial son de tracción trasera y que una aceleración, en determinadas condiciones del asfalto y atmosféricas, puede provocar que la rueda trasera pierda adherencia y patine.

El tratamiento de este problema pasaría por la medida de la diferencia de velocidad angular o tangencial de cada rueda, resuelta mediante el tiempo entre cada lectura del fotosensor, conociendo los dientes o agujeros del disco exactos que corresponden a una vuelta de la rueda.

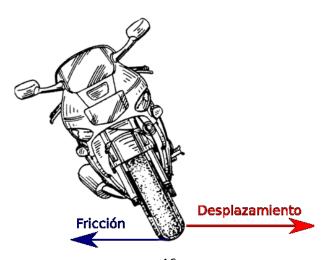

Figura 1.1: Descripción velocidades angulares

En esta situación se produciría que wA sería mayor que wB, con lo que se frenaría el disco trasero gradualmente a la diferencia entre wA-wB.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### Actuación en el frenado

El segundo caso es la pérdida de tracción durante una frenada. En esta situación la motocicleta derrapa ligeramente en una de las dos ruedas debido a la diferencia de desaceleración entre ellas. Este sistema detectaría el patinaje de la misma forma que en el caso de la aceleración, por medio del diferencial de velocidad angular entre ambas ruedas, dado el caso se deberá reducir la frenada en la rueda que gira más rápido.

#### Análisis

Tabla 2.2: Actuadores ASR

| Elementos<br>actuadores   | Acelerómetro | Sensor óptico                                                  | Sensor de<br>temperatura                         |

|---------------------------|--------------|----------------------------------------------------------------|--------------------------------------------------|

| Actuación en aceleración  | No.          | Sí, para velocidad de giro<br>en rueda delantera y<br>trasera. | Sí, para conocer la temperatura del disco.       |

| Actuación en e<br>frenado | el No        | Sí, para velocidad de giro<br>en rueda delantera y<br>trasera. | Sí, para conocer la<br>temperatura del<br>disco. |

### 2.1.4. Control de estabilidad

El ESP (Electronic Stability Program), también llamado ESC (Electronic Stability Control), es un dispositivo de seguridad incorporado en vehículos de tracción que actúa durante los virajes, evitando que una de las ruedas derrape y se desestabilice.

La implementación del control del ESP en motocicletas pasa principalmente por controlar tres aspectos básicos que son los siguientes:

- La aceleración tangencial al giro no corresponde con la aceleración de la rueda delantera girada determinando el ángulo de giro del manillar.

- El ángulo de inclinación de la motocicleta respecto a la posición vertical no corresponde con el ángulo de giro del manillar ni la velocidad.

- La velocidad de giro de las ruedas no corresponde.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### Diferencia de aceleración tangencial/tangencial

En este caso el factor determinante es conocer el ángulo de giro del manillar. La actuación en esta situación sería frenar la rueda delantera hasta el punto en que corresponda con la aceleración tangencial.

Para hacer la medición del ángulo del manillar se podría utilizar uno de los ejes del acelerómetro, para conocer la velocidad tangencial se utilizaría el sensor óptico que proporcionaría la aceleración de la rueda trasera, y para conocer la aceleración angular el sensor óptico en la rueda delantera.

### Diferencia entre inclinación y giro del manillar

Es esta situación es necesario contemplar la velocidad de la motocicleta ya que a mayor velocidad es menos decisiva esta diferencia. A velocidades altas es necesario tomar la curva inclinando la motocicleta mucho más que el manillar y al revés. Este caso es debido a que un giro de manillar a mucha velocidad desviará la base de la motocicleta al interior de la curva mientras las zonas más alejadas tienden a ir hacia delante por su propia inercia. Por lo tanto, a velocidades altas, la inclinación de la motocicleta al lado que gira contrarresta esa inercia. Además ayuda a girar, dado que la fuerza de fricción hacia el centro de la curva contrarresta la tendencia que tienen las ruedas a desplazarse al exterior.

Para resolver esta situación se deberá concluir la función que nos determina un giro correcto en función de las tres variables comentadas. En el caso que la función determine un giro excesivo se frenarían ambas ruedas para intentar recuperar el equilibrio.

Figura 2.2: Fuerzas presentes en la inclinación

Autor: Danilo Sanz Moreno

Documento : Memoria final del proyecto

### Diferencia de giro entre ruedas

Para controlar la estabilidad de la moto en una curva también se hace uso del sistema de control de tracción por el que ambas ruedas tienen que llevar una velocidad angular equivalente. Para este caso se frenará la rueda que gire más rápido para evitar el patinaje.

### Análisis

Tabla 2.3: Actuadores ESP

| Elementos<br>actuadores                           | Acelerómetro                                                             | Sensor óptico                                                                                             | Sensor de temperatura                         |

|---------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Diferencia<br>aceleración angular<br>y tangencial | Sí, para conocer<br>giro del manillar.                                   | Sí, para velocidad de giro en rueda delantera y velocidad tangencial con velocidad de giro rueda trasera. | ·                                             |

| Diferencia<br>inclinación y giro del<br>manillar  | Sí, para obtener inclinación lateral de motocicleta y giro del manillar. | Sí, para conocer la<br>velocidad de la<br>motocicleta.                                                    | Sí, para conocer la temperatura del disco.    |

| Diferencia de giro<br>entre ruedas                | No                                                                       | Sí, determinar la velocidad angular de cada rueda.                                                        | Sí, para conocer<br>temperatura del<br>disco. |

### 2.1.5. Disponibilidad en el mercado

El sistema ABS hace más de diez años que se empezó a integrar en motocicletas. Aunque a simple vista cuesta reconocer el sistema ABS, este destaca por ser un poco más grande que los sistemas de frenos habituales (ver figura 2.3).

Autor: Danilo Sanz Moreno

Documento : Memoria final del proyecto

Figura 2.3: Frenos ABS

Sobre los sistemas ESC- ABS disponibles actualmente cabe decir que funcionan mediante un sensor electromagnético y unas placas que al cruzar entre los sensores producen que exista o no corriente. Los resultados obtenidos son mucho mejores de los que se podría obtener con un sensor óptico en el que el polvo o la suciedad son suficientes para eliminar el paso de fotones entre el emisor y el receptor.

Figura 2.4: ESP-ABS de BMW

Autor : Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2.2. Partes interesadas

### 2.2.1. Intereses (Stakeholders)

Tabla 2.4: Stakeholders

| Nombre              | Descripción                     | Responsabilidad                                                                                                                           |

|---------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Raúl Aragonés Ortiz | Director de proyecto            | Aprobación del proyecto. Participa en su definición y hace el seguimiento. Supervisa el trabajo hecho por el alumno y evalúa el proyecto. |

| Danilo Sanz Moreno  | Alumno responsable del proyecto | Realización del proyecto.<br>Definición de requisitos y<br>funcionalidades.                                                               |

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2.2.2. Perfiles de usuario

El proyecto que se realiza no dispone de usuarios específicos dado que es un sistema autónomo. En cualquier caso existen grandes posibilidades de ampliación dado que el sistema hardware final no está suficientemente explotado y existe la posibilidad de la implementación de los algoritmos de control mediante el tratamiento de las señales captadas.

Tabla 2.5: Perfiles de usuario

| Perfil                                                 | Responsabilidad                                                                                                                         |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Ingeniero o diseñador hardware/software                | Explotación del estudio para la implementación en dispositivos semejantes y prever la viabilidad de otro proyectos.                     |

|                                                        | Partiendo de la aplicación obtenida, ampliar el sistema con nuevas funcionalidades y algoritmos para su implementación en la vida real. |

| Empresa dedicada al sector de seguridad en automóviles | Uso del dispositivo medidor para la implementación de sistemas de frenado.                                                              |

### 2.2.3. Project Team

Tabla 2.6: Project Team

| Nombre              | Descripción                     | Responsabilidad                                                                                                                                                                                            |

|---------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Raúl Aragonés Ortiz | Director de proyecto y tutor.   | Define, planifica y sigue el proyecto.<br>Supervisa el trabajo hecho por el alumno.                                                                                                                        |

| Danilo Sanz Moreno  | Alumno responsable del proyecto | Colabora con el director de proyecto en el estudio de viabilidad y la planificación.  Desarrolla la investigación que requiere y en la que se basa el proyecto. Implementa las funcionalidades requeridas. |

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2.3. Fases del proyecto y planificación

### 2.3.1. Fases del proyecto

El proyecto se ha estructurado en 7 etapas diferentes que se detallan a continuación:

1º etapa: Familiarización con la placa y documentación sobre los componentes.

2ª etapa: Decisión y estudio de la implementación de microprocesador y bus en la FPGA.

3ª etapa: Estudio sobre la implementación de sistemas operativos con soporte para el microprocesador escogido.

3º etapa: Diseño del sistema hardware base.

4º etapa: Estudio e implementación de la lectura de la temperatura.

5ª etapa: Desarrollo del software con interfaz gráfica para PC de interacción con el dispositivo.

6º etapa: Diseño e implementación del IPCore para el tratamiento de la aceleración.

7º etapa: Diseño e implementación del sistema de tratado de señal analógica en el PSoC y un IPCore en FPGA para recibir datos del PSoC.

### 2.3.2. Planificación

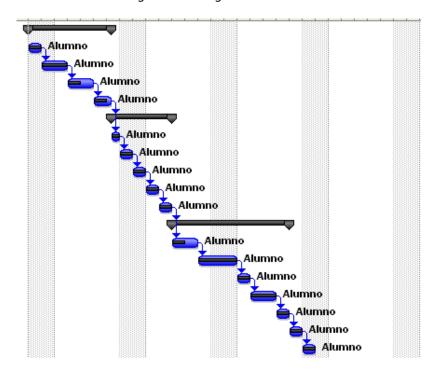

Las etapas del proyecto se han dividido según la relación de la memoria, que a su vez determina los seguimientos que se han ido haciendo.

Autor : Danilo Sanz Moreno

Documento: Memoria final del proyecto

Figura 2.6: Tabla de tareas

| Nombre de tarea                         | Duración<br>prevista | redecesora: | Duración real |

|-----------------------------------------|----------------------|-------------|---------------|

| ⊟ Estudio de viabilidad                 | 120 horas            |             | 117 horas     |

| Familiarización con la placa            | 20 horas             |             | 18 horas      |

| Estudio Leon-3-AMBA                     | 40 horas             | 2           | 45 horas      |

| Estudio e implementación MicroBlaze-PL  | 40 horas             | 3           | 31 horas      |

| Estudio e implementación kernel         | 20 horas             | 4           | 23 horas      |

| ⊡ Diseño                                | 65 horas             | 5           | 63 horas      |

| Estudio componentes de MicroBlaze       | 15 horas             | 5           | 14 horas      |

| Estudio e Implementación ExecuteInPlace | 15 horas             | 7           | 16 horas      |

| Estudio y adaptación pruebas de rendim  | 20 horas             | 8           | 18 horas      |

| Implementación pruebas de rendimiento   | 10 horas             | 9           | 8 horas       |

| Estudio IPCore's                        | 5 horas              | 10          | 7 horas       |

| ⊡ Implementación                        | 175 horas            | 11          | 192 horas     |

| Lectura de temperatura                  | 30 horas             | 11          | 33 horas      |

| Implementación del IPCore acel2axis     | 50 horas             | 13          | 50 horas      |

| Implementación sensor optico            | 30 horas             | 14          | 30 horas      |

| Implementación Programa MicroBlaze      | 35 horas             | 15          | 39 horas      |

| Diseño e implementación aplicación PC   | 30 horas             | 16          | 40 horas      |

| Pruebas                                 | 30 horas             | 17          | 30 horas      |

| Documentación del proyecto              | 30 horas             | 18          | 30 horas      |

| Total horas                             | 420 horas            | 19          | 420 horas     |

Figura 2.7: Diagrama de Gantt

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2.4. Descripción del sistema

El sistema final obtendrá los datos de los sensores y hará cálculos para poder visualizarlos en PC. La placa deberá encender unos led's que lleva integrados para la medición dinámica de una variable, también actuará en función de unos botones que lleva.

En la aplicación de PC debe existir la posibilidad de pedir o no los datos.

Figura 2.7. Esquema del sistema

### 2.5. Metodología de desarrollo

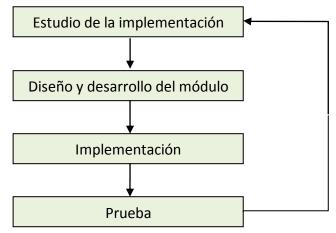

La metodología de desarrollo usada en todo el proyecto ha sido el modelo clásico ya que se trata de un proyecto con personal reducido que no permite un desarrollo más elaborado por los posibles riesgos de fracaso que puedan haber.

Figura 2.8: Metodología de desarrollo

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2.6. Entorno de prototipado

### 2.6.1. Descripción

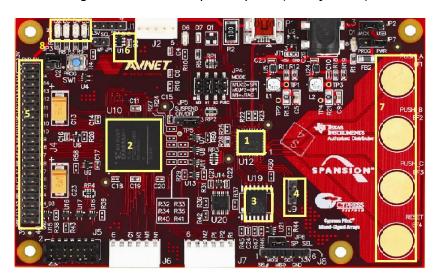

Para la realización de este proyecto se trabaja sobre el kit *AVNET Spartan-3A Evaluation Board* que trabaja a un voltaje de 3.3 Volts.

La placa se compone principalmente por un FPGA, un PSoC, puertos de entrada/salida y memorias flash.

Acerca de la memoria se ha de decir que el dispositivo lleva incorporados dos chips: uno de ellos es memoria de acceso serie síncrona de 16 MegaBytes compartida por el FPGA y PSoC, y la otra es de 16 líneas de datos en paralelo de 4 MegaBytes, accesible únicamente por la FPGA.

Además la placa cuenta con todos los puertos necesarios dedicados a reprogramación y reseteado.

El puerto USB se reconoce en el PC como si de un puerto serie se tratara dado que viene controlado por un módulo USB-UART en el PSoC. La velocidad a la que trabaja este UART es de 115.800 bits/segundo, y se ha de mantener la misma configuración para programar/comunicar el dispositivo.

Figura 2.9. Placa de prototipado (vista frontal)

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

Figura 2.10: Placa de prototipado (vista trasera)

Partiendo de la figura 2.6 podemos distinguir los principales componentes de la placa de prototipado:

- 1. Cypress PSoC CY8C24894-24LFXI

- 2. FPGA Xilinx Spartan-3A 400 ft256

- 3. La memoria Flash serie Spansion S25FL128P.

- 4. Pines de entrada/salida mapeados en el PSoC en los puertos P0\_1, P0\_3 y P0\_5 de arriba hacia abajo

- 5. Pines de entrada/salida mapeados en la FPGA en los que se indican sus puertos en el misma placa y en los esquemáticos.

- 6. Sensor de temperatura Texas Instruments TMP100 conectado a PSoC y FPGA.

- 7. Botones sensitivos al tacto *CapSense* de Cypress.

- 8. 4 LED's de salida conectados directamente al FPGA.

- 9. Memoria flash paralela Spansion S29GL032N.

En los siguientes apartados se describen los componentes más importantes.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2.6.2. El FPGA

El FPGA es un dispositivo de los llamados SoC (*SystemOnChip*) . SystemOnChip quiere decir que a diferencia de las placas de evaluación de microcontroladores habituales, en los que toda la programación ha de estar adaptada al diseño inicial de la placa de evaluación, este se puede programar incorporando elementos hardware para obtener diseños más completos.

### Introducción

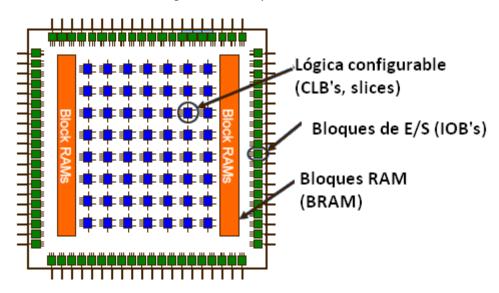

La estructura interna de una FPGA es una matriz de conexiones separadas por bloques, encontrándose los más cercanos al exterior los de entrada/salida y memoria RAM y en el núcleo los slices o CLB's (Cell logic blocks), compuestos de Flip-Flops y LUT's con un determinado número de entradas ( 4 en nuestro modelo ).

Figura 2.11: Esquema FPGA

Una vez que realizamos el proceso de co-diseño hardware/software se deben generar las netlist del diseño, que forma el bloque con los elementos, y a continuación el sintetizado que adapta el diseño al modelo de FPGA.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

• La familia Spartan-3A

La familia de FPGA Spartan-3A se corresponde con la serie de FPGA's de bajo coste de la marca Xilinx. El modelo que contiene la placa de prototipado contiene 400 mil puertas lógicas distribuidas en 7168 slices o CLB's. También dispone de 360 mil BlockRAMbits, es

decir, hasta 45 KBytes de memoria que se puede utilizar como BlockRAM.

Esta familia de FPGA está optimizada para lógica de entrada/salida disponiendo de más

bloques para interactuar con el exterior que otros modelos de la serie.

Las señales de reloj disponibles para utilizar con el chip FPGA son tres, uno de ellos es de un generador de onda cuadrada MAXIM que funciona a 16 MHz y se encuentra mapeado en el

pin C10, y los otro dos provienen del PSoC, uno es de 12 MHz que viene desde el puerto

P2[6] de PSoC al pin N9 de la FPGA y el otro es de 32 MHz que llega desde el P3[7] al T7.

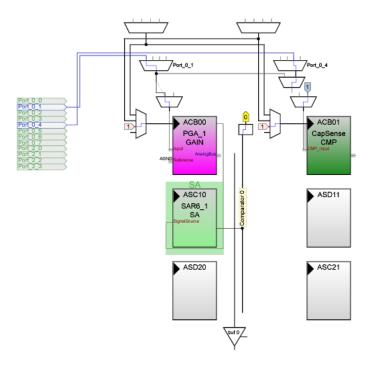

2.6.3. SystemOnChip PSoC

El PSoC es un microcontrolador SystemOnChip reprogramable de la marca Cypress. A

diferencia de la FPGA, éste se reprograma mediante módulos analógicos y digitales que se interconectan a unos bloques para tal propósito. Esto hace que sea fácil adaptar a múltiples

diseños y propósitos.

La cantidad de bloques lógicos disponibles para diseñar el sistema periférico dependen del

modelo de PsoC que vayamos a programar, en nuestro caso existen 4 bloques digitales y 4

analógicos.

Hay que comentar que existen dos tipos de bloques digitales, tenemos los BB que son

Building Blocks y los CB Comunication Blocks. La diferencia entre ellos es que los

Comunication Blocks son los únicos que pueden disponer bloques de comunicaciones para

I2C, SPI, UART.

De bloques analógicos también distinguimos dos tipos, los CT (Continuous Time) se

componen de circuitos amplificadores y los SC (Switch Capacitor) que están formados por

circuitos con capacidades conmutadas.

27

Autor: Danilo Sanz Moreno

Documento : Memoria final del proyecto

**DIGITAL BLOCKS** PORT 7 BB CB PROGRAMMABLE ROUTING AND INTERCONNECT MAC PORT 6 DECIMATOR PORT 5 M8C CPU CORE CB BB POR AND LVD SYSTEM RESETS PORT 4 NTERNAL VOLTAGE REFERENCE PORT 3 ANALOG BLOCKS INTERRUPT CONTROLLER PORT 2 СТ SC PORT 1 SC 24-MHz OSCILLATOR SC SC PORT 0

Figura 2.12: Esquema PSoC

MICROCONTROLADOR

**BLOQUES REPROGRAMABLES**

**ENTRADA/SALIDA**

Además de lo dicho, el PsoC es reprogramable dinámicamente, es decir que podemos montar más de un diseño en bloques y que respondiendo a determinados eventos pasemos de tener un diseño cargado a otro sin que el consumo de bloques lógicos se acumule.

En el PSoC de la placa incluye un programa inicial compuesto por dos diseños diferentes. Uno de ellos responde a la configuración *USBUart* el cual hace que la conexión USB sea tratada como una conexión UART y es la configuración que se usa en la comunicación PC-placa. Las otra configuración es la *SPIconfig* que se carga al configurar la memoria SPI.

Existen once señales que comunican el PSoC con la FPGA (ver figura 2.13).

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

Figura 2.13: Señales PSoC-FPGA

| F1          | PSOC_P2_1  |

|-------------|------------|

| H1          | PSOC_P2_73 |

| G2          | PSOC P2 3  |

| H3          | PSOC P2 5  |

| J1          | PSOC P0 4  |

| J2          | PSOC_P4_6  |

| L2          | PSOC P5 3  |

| L1          | PSOC P5 7  |

| M3          | PSOC P5 4  |

| M4          | PSOC P5 6  |

| $\sqrt{N3}$ | PSOC_P7_0  |

|             |            |

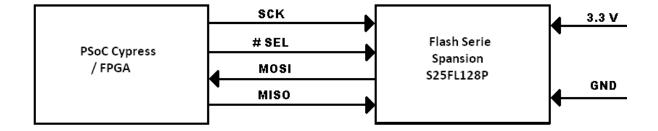

### 2.6.4. Memoria flash serie

La memoria flash serie incluida es de 16 MB (128 Mbits), esta memoria utiliza el protocolo SPI y puede ser accesible o bien por el PsoC o por la FPGA. Funciona a 4 MHz de frecuencia de reloj que viene determinada por la configuración del módulo SPIconfig configurado en el PSoC, por lo que entrega 1 bit cada 250 nanosegundos. En este tipo de memoria la limitación viene dada por la capacidad de transferencia.

El protocolo SPI se trata de un protocolo serie síncrono entre periféricos. Es full-dúplex lo que permite comunicación bidireccional.

El funcionamiento de este protocolo depende de una señal maestra *SCK* que lleva la señal de reloj (proporcionada por el PsoC), una de activación de transferencia *#SEL*, y dos de datos: una *MOSI* (master-output slave-input) que entrega el esclavo al master y otra *MISO* (master-input slave-output) para salida de datos.

Figura 2.14: Memoria flash serie

Autor : Danilo Sanz Moreno

Documento: Memoria final del proyecto

### 2.6.5. Memoria flash paralelo

La otra memoria flash es de comunicación paralela con 16 líneas de datos. Es una memoria asíncrona con una latencia de 90 ns en el tiempo de acceso y 15 ns en el de escritura. Dispone de 22 líneas de direcciones para direccionar los 4 MegaBytes y tiene una mayor velocidad y menor latencia que la memoria serie, es por ello que se le busca la utilidad como memoria ROM de programa.

Tabla 2.7: Señales Memoria flash paralela

| Señal              | Nº de líneas | Utilidad                                          |  |

|--------------------|--------------|---------------------------------------------------|--|

| Data               | 16           | Envío de datos a leer/escribir                    |  |

| Address            | 22           | Dirección de memoria a leer/escribir              |  |

| CE (Chip Enable)   | 1            | Habilitación del dispositivo para operar          |  |

| WE (Write Enable)  | 1            | Junto a CE, operación de escritura                |  |

| RE (Read Enable)   | 1            | Junto a CE, operación de lectura                  |  |

| Reset              | 1            | Borrar memoria                                    |  |

| OE (Output Enable) | 1            | Habilitar salida                                  |  |

| RY/BY (Ready/Busy) | 1            | Indica memoria preparada a 0 o ocupada si es 1    |  |

| Byte               | 1            | Transferencia es en modo 1 byte a 0 o 2 bytes a 1 |  |

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

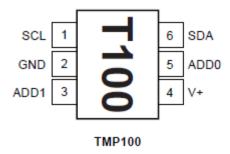

### 2.6.6. Sensor de temperatura

La placa incluye un sensor de temperatura Texas Instruments TMP100 que conecta con la FPGA y el PSoC por medio del protocolo I2C. Este sensor mide temperaturas en un rango de -55 a 125 °C con un máximo de error absoluto de ±3°.

Figura 2.15: Sensor de temperatura

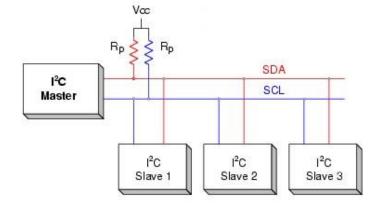

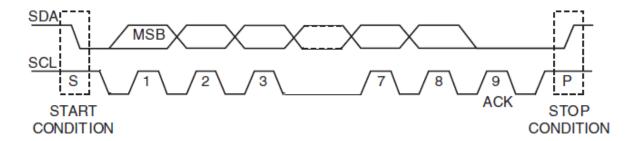

El I2C es un bus que consta de dos señales básicas, la *SCL* (Serial Clock) para el señal de reloj y la *SDA* (Serial Data) para transportar los datos. Dos resistencias *pull-up* dejan el bus a '1' cuando no existe ninguna transferencia.

El protocolo de funcionamiento de este bus es muy parecido al protocolo serie. Durante cada transferencia existe un dispositivo maestro que genera la señal de reloj, en nuestro caso es el microprocesador y otro esclavo, que en nuestro caso es el sensor de temperatura, con una dirección de de siete bits que proporciona el fabricante (*0x48* para *TMP100* con un solo dispositivo conectado).

Figura 2.16. Esquema protocolo I<sup>2</sup>C

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

Para iniciar la transferencia, el maestro crea una situación de *START* antes de la comunicación y una situación de *STOP* al acabar de enviar datos.

Figura 2.17. Señales protocolo I<sup>2</sup>C

La señal de START se define con un flanco de bajada en SDA mientras SCL está a '1' y la de stop es el paso contrario, un cambio a '0' con el señal SCL a '1'. Las transmisiones son de 8 bits consecutivos con uno final de confirmación.

### 2.7. Periféricos

### 2.7.1. Acelerómetro

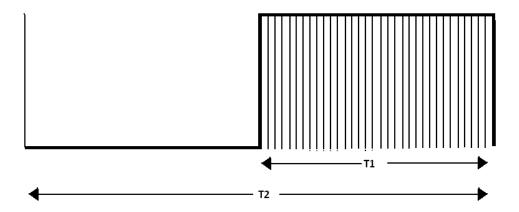

Para la medida de inclinación se dispone de un acelerómetro analógico/digital Analog Devices ADXL202JE de dos ejes y con un rango de  $\pm 2~g$ 's. Éste se encuentra encastado a una placa de evaluación ADXL202EB. La aceleración se traduce en función del ancho de pulso activo de una señal cuadrada, de la cual, la frecuencia viene determinada por una resistencia conectada a dicha placa.

La señal se muestra activa un 50% aproximadamente del periodo si la aceleración es de 0 g's, aumentando o disminuyendo en función de un 12.5% por g aproximadamente, dependiendo del voltaje de entrada. De esta manera tenemos que el ancho de pulso será entre un 25% (-2g) y un 75% (+2g) aproximadamente del periodo.

Autor : Danilo Sanz Moreno

Documento: Memoria final del proyecto

Tabla 2.8: Relación Vin-DutyCycle Acelerómetro

| Vin | % Duty Cycle mínimo<br>por g | % Duty Cycle típico<br>por g | % Duty cycle máximo<br>per g |

|-----|------------------------------|------------------------------|------------------------------|

| 5 V | 10.5                         | 12.5                         | 14.5                         |

| 3 V | 9                            | 11                           | 13                           |

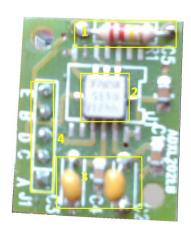

Figura 2.18. Vista acelerómetro

La resistencia (1 en la figura) es de 220 k $\Omega$ , esto quiere decir que la señal cuadrada tendrá un periodo de 2ms aproximadamente siguiendo la tabla 2.9, esto se traduce en una frecuencia de aproximadamente 500 Hz.

Tabla 2.9: Relación R<sub>SET</sub>- Periódo Acelerómetro

| Periodo T2 | Resistencia R <sub>SET</sub> |

|------------|------------------------------|

| 1 ms       | 124 kΩ                       |

| 2 ms       | 248 kΩ                       |

| 5 ms       | 620 kΩ                       |

| 10 ms      | 1.24 ΜΩ                      |

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

El acelerómetro dispone de 3 entradas, una de autotest (E en la figura 2.13) conectada a 0 Volts, otra de V+ (A en la figura 2.13) para conectar un voltaje entre 3V y 5V y la de tierra(E en la figura 2.13) a 0 V. También incorpora dos salidas X (C) e Y (D) conectados con los pines de la FPGA A13 y C13 para obtener los datos. El cálculo de la aceleración viene determinado por la siguiente ecuación:

Aceleración (en g's) = ( Duty Cycle – Duty Cycle at 0g )/Duty Cycle por g

### 2.7.2. Sensor óptico

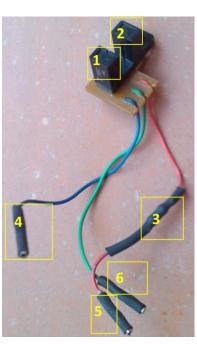

Figura 2.19: Vista Sensor Óptico

El sensor óptico está formado un diodo fotoemisor y un fotoreceptor.

• El fotoemisor (1 en la figura 2.14) no es más que es un led que emite luz infraroja que viene determinado en el periférico por el símbolo indicado en la figura 2.15. Es operativo a 1.6 Volts por lo que se ha añadido una resistencia de 100 k $\Omega$  (3 en la figura 2.14) con tal que produzca una diferencia de potencial de 1.7 Volts.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

Figura 2.20: Símbolo fotoemisor

Figura 2.21: Símbolo fotoreceptor

• El fotoreceptor (2 en figura 2.14) consiste en un fototransistor con el colector conectado a V+ (3 en la figura 2.14) y en el que la luz infrarroja actúa como corriente de base. En función de la luz infrarroja aplicada a la base pasará más o menos corriente ésta se entrega por el emisor y da la salida del circuito (4 en figura 2.14).

### 2.8. Estado del arte

En este apartado se describe el sistema que se ha incorporado al proyecto y el estudio llevado a cabo.

### 2.8.1. El microprocesador

Para el desarrollo de proyectos sobre FPGA's resulta mucho más cómodo incorporar un microprocesador, de este modo obtenemos más flexibilidad de uso y podemos realizar los cálculos necesarios por medio de programación en ensamblador o C. Estos microprocesadores se dividen en dos conjuntos: los hard-core y los soft-core.

### Microprocesadores hard-core

En las placas de prototipado de más alta gama se incorporan los denominados microprocesadores hard-core, éstos son microprocesadores físicos de silicio desarrollados por empresas dedicadas como comúnmente conocemos AMD o Intel.

Dado el avance tecnológico es posible incorporar hard-core's en FPGA's. Algunos modelos de las series Virtex incorporan microprocesadores PowerPC de IBM a una frecuencia que ronda los 550 MHz y configuraciones multi-core. Estos microprocesadores se encuentran mapeados dentro del chip de la misma forma que lo haría en una placa base con la ventaja

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

de poder incorporar IPCore's a su alrededor. Obtienen mejores resultados que los soft-cores ya que la lógica de construcción en FPGA's requiere latencias mayores y limita la frecuencia.

Nuestra placa de prototipado no dispone de ningún microprocesador hard-core por lo tanto se tendrá que acudir a buscar una solución soft-core.

### • Microprocesadores Soft-core

Los soft-core son microprocesadores IP-core sintetizables escritos en lenguajes de descripción hardware. El proceso de sintetización es el que se lleva a cabo para generar el archivo que define las conexiones internas del sistema y determina que se cumplan las limitaciones con la FPGA sobre el que se implementa. De este modo es parecido a la compilación de un programa software con la diferencia de que lo que se diseña es hardware.

### Leon

Leon es un microprocesador RISC de 32-bits con arquitectura SPARC V8, es ampliamente parametrizable y está escrito en VHDL. Fue desarrollado por la Agencia Europea Espacial (ESA) y actualmente se mantiene por el grupo Gaisler Research. La versión probada ha sido la Leon-3.

El microprocesador se distribuye como parte del conjunto GRLIB IP Library que se compone además de varios IP's de licencia libre para conectar sobre buses AMBA.

Existen dos versiones disponibles, una es la versión FT (*Fault-tolerant*) con tolerancia a fallos y comercial que se utiliza principalmente para aplicaciones espaciales, la otra es la versión estándar con la que se ha tratado en el proyecto. A continuación podemos ver sus principales características:

- Conjunto de instrucciones SPARC V8 con ordenación big-endian. Dispone de tres modos de direccionamiento: immediato, directo e indirecto. Incluye instrucciones MAC, multiplicación y división.

- Disponible la incorporación de unidades MAC hardware hasta de 32bits y divisores hardware.

- Soporte multi-core con una unidad despachadora de procesos.

Autor: Danilo Sanz Moreno

Documento : Memoria final del proyecto

Tratamiento de interrupciones.

• Varios tipos de unidades de cálculo para punto flotante FPU.

• Pipeline configurable de hasta 7 etapas.

• Caché de arquitectura Harvard de hasta 4 niveles configurable que pueden ir desde

1KB hasta 256 KB por vía, y hasta 4 vías.

Soporte de unidad de manejo de memoria para protección de zonas críticas de

sistemas operativos.

• Utiza el bus AMBA 2.0 ( Advanced Microcontroller Bus Architecture ) con soporte del

AHB.

Todo el conjunto, con todas las opciones activadas puede llegar a obtener un rendimiento de

hasta 1.4 DMIPS/MHz (ver 3.5) y puede llegar a funcionar a 125 MHz en FPGA's.

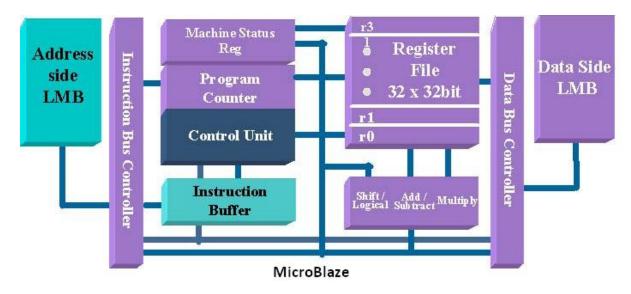

MicroBlaze

MicroBlaze es el microprocesador RISC sintetizable que Xilinx dispone para sus FPGA Spartan y Virtex. Es un microprocesador de 32-bit que usa el orden *big-endian*. La versión tratada de

MicroBlaze en este proyecto es la 7.2 y a continuación mostramos datos de su arquitectura.

Conjunto de instrucciones propio que se basa en instrucciones de 32 bits con 2 o 3

operandos.

32 registros de propósito general de 32-bits cada uno

Bus de procesador de 32-bit CoreConnect PLB.

• Bus de memoria BRAM LMB configurable en velocidad

Configuraciones de shifter hardware, divisores y multiplicadores

Cachés Harvard configurables de hasta 256 KB para datos y 256 KB instrucciones

Unidad de manejo de memoria.

Pipeline de 3 o 5 etapas.

• Tratamiento de interrupciones

Soporte multi-core

37

Autor : Danilo Sanz Moreno Documento : Memoria final del proyecto

• Soporte de múltiples sistemas operativos

Figura 2.22: Estructura interna MicroBlaze

#### Evaluación

Después de hacer varias pruebas y búsquedas de configuraciones de Leon-3 se determinó la dificultad de incorporar este microprocesador en la placa objeto.

Para probar el microprocesador Leon-3 se necesita un sistema operativo Linux en el PC y los archivos de *constraints* de la placa. Para parametrizar el sistema se utilizó un programa de interfaz gráfica llamado *xconfig*, para simularlo se usó el simulador vhdl Modelsim en línea de comandos.

Para compilar un programa *Holamundo* en C, desarrollado para Leon, se requirió instalar el paquete correspondiente al compilador GCC para Sparc.

Después de simular se decidió la implementación sobre la placa de prototipado y surgieron problemas relacionados de capacidad al sintetizar el Leon-3. Todo el proceso se realizó primeramente en una placa soportada y posteriormente con la nuestra. Dado que el proceso de sintetizado requería tiempos de espera de hasta 30 minutos y siempre daba saltaban errores por falta de espacio se decidió probar el procesador MicroBlaze que es más común y existe más documentación.

El sistema final dispondrá MicroBlaze con una configuración limitada a 32 KB de BRAM y 50 MHz utilizando el método *Execute in Place* (véase 3.2), para ello se requiere del software FDK de Xilinx.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

#### 2.8.2. El Bus

Otro de los elementos a determinar en el sistema es el bus de procesador que queremos utilizar. En este apartado se explican los buses utilizados por ambos y se desarrollan las opciones de implementación y funcionamiento de éstos.

#### **AMBA**

Es la arquitectura de bus con la que trabaja el soft-core Leon. Se desarrolló por la marca ARM y se trata de una arquitectura orientada a microcontroladores de altas prestaciones, la versión incluida en la *GRLIB* para el diseño de Leon-3 es el AMBA 2.0 de 32-bits.

En la versión 2.0 de AMBA se disponen de tres tipos de buses. Éstos son el ASB, APB y el AHB.

El APB es un bus orientado a periféricos de baja velocidad de reloj. La forma como este bus se incorpora al sistema es mediante el APBbride, que no es más que un IPCore que conecta con uno de los buses de alto rendimiento realizando la conversión de datos necesaria para la compatibilidad con los periféricos. La incorporación de buses dedicados a este propósito baja el consumo final del sistema.

El ASB es el bus de alta velocidad en la primera versión de AMBA. Su uso va destinado a transacciones entre el microprocesador y la memoria u otras que requieran de estas prestaciones. Este bus permite el envío consecutivo de instrucciones por medio del uso de un pipeline en el controlador.

El AHB es un nuevo bus de alto rendimiento incorporado en la versión AMBA 2.0. Soporta mayores frecuencias que ASB y configuraciones de 64 y hasta 128 bits.

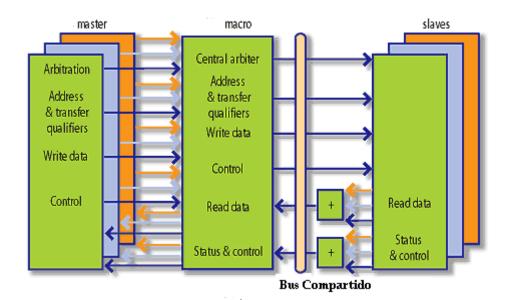

#### CoreConnect

CoreConnect es la arquitectura de buses para incorporación sobre MicroBlaze. Se compone de tres buses en que los más destacados son el PLB, un bus de alto rendimiento para elementos de memoria estandarizado entre los desarroladores de IPCore's, y el OPB, equivalente al APB de AMBA. En nuestro diseño final solo figura el bus PLB.

El PLB se trata de un bus síncrono configurado a 50 MHz que soporta lecturas y escrituras concurrentes con un direccionamiento hasta 32-bits. Tiene líneas independientes de control de lectura y escritura, y para proporcionar mayor rendimiento soporta el direccionamiento en multi-etapa (*pipeline*) con lo que el master puede pedir el bus mientras se ejecuta una

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

transacción. Existen 4 niveles de prioridad de acceso a este bus que se determinan con el señal de arbitraje que proporciona el master a la transacción

El controlador master incorpora las señales de control de lectura/escritura, las direcciones a leer o escribir, los datos a escribir y la prioridad de la transacción.

La zona macro del PLB incluye el arbitraje central para determinar la prioridad de la operación y los registros para las señales que recibe por los controladores maestro y esclavo.

Los controladores esclavos incluyen en la macro datos de lectura a través de las líneas de conexión (el bus) y los registros de estado y control.

Figura 2.23: Esquema PLB

#### Evaluación

Dado que el microprocesador escogido ha sido MicroBlaze y no disponemos de una gran cantidad de periféricos, la configuración escogida ha sido la de montar un bus PLB único para controlar todas las señales.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

#### 2.8.3. Sistema operativo

La última de las necesidades que presenta el proyecto es la de instalar un sistema operativo de tiempo real (RTOS) para poder añadir escalabilidad y comodidad al desarrollar el sistema. Las ventajas de la implementación de estos sistemas son múltiples, pero las más importantes van relacionadas con la posibilidad de creación de procesos y el control de zonas críticas.

El uso por el que se requiere un kernel es el de obtener tiempos inferiores al segundo, dado que éste proporciona una API con funciones para tal propósito.

A pesar de que existe una gran cantidad de sistemas operativos disponibles con soporte para MicroBlaze, propietarios y libres, se contempla la posibilidad de instalar unicamente UCLinux o Xilkernel, por ser dos de los más conocidos.

#### **UCLinux**

uCLinux es un sistema operativo basado en el kernel de Linux 2.6 en su última versión. Este sistema ha sido portado para microcontroladores que no disponen de unidad de gestión de memoria. El inconveniente de este sistema operativo es que necesita demasiada memoria RAM para datos, el sistema mínimo requiere más de 1 MB de datos cuando estamos limitados a 32 KB.

#### Xilkernel

Xilkernel es la otra opción como sistema operativo, está disponible únicamente para softcores MicroBlaze y hard-cores PowerPC. Se incluye en el EDK de Xilinx y está dotado de la POSIX API de C con lo que permite el multi-proceso, la planificación por prioridades, la intercomunicación de procesos, las opciones de sincronización y el manejo de interrupciones.

Este kernel ocupa apenas 9 KB de memoria y es altamente configurable mediante *Software Platform Settings* de EDK.

#### Elección

Aunque se han contemplado más sistemas operativos de los aquí descritos se optó directamente por implementar el Xilkernel. El motivo fue la gran cantidad de documentación que existe en torno a éste, sus bajos requisitos en el sistema y la no necesidad de compilar el código, encontrándose su implementación en forma de librería.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

2.9. Entorno de desarrollo software

A continuación se detallan las herramientas de desarrollo software para la programación del

sistema obtenido.

2.9.1. Xilinx EDK

El Xilinx EDK (Embedded development kit) es el entorno de desarrollo de Xilinx para sistemas embebidos que contiene herramientas, procesadores e IPCores prediseñados. La versión

utilizada es la 11.5 para Windows XP 32-bits que se incluye en el Design Suite 11.5 de Xilinx.

Se compone de dos entornos, el XPS (Xilinx Platform Studio) para el desarrollo de hardware y

el Xilinx SDK (Software development kit) para el desarrollo de software.

Aunque el entorno incorpora los archivos que dan soporte a las principales placas de

desarrollo, en nuestro caso se debe instalar previamente los archivos de conexionado al

exterior.

El EDK permite trabajar con los procesadores MicroBlaze y PowerPC e incorpora una parte

de los códigos fuente del soft-core MicroBlaze. Incluye también el código de los principales

buses y asistentes para su implementación, de la misma forma que una gran cantidad de

controladores IPCore para incorporar a nuestro diseño y un kernel parametrizable para

sistemas de tiempo real.

2.9.2. Cypress PsoC Designer

Es la herramienta para diseñar y crear el código que programaremos en el PsoC. La versión

utilizada ha sido el PsoC Designer 5.0. Esta herramienta nos permite escoger los User

Modules, ubicarlos en los bloques lógicos y programar el procesador en C o en Assembler.

Proporciona además los datasheets de los componentes donde indica su funcionamiento y la API

del componente, así como opciones de generación de datasheets del proyecto diseñado y la

programación del dispositivo sin necesidad de usar el PsoC programmer.

42

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

#### 2.9.3. CypressPsoc Programmer

Es la herramienta usada habitualmente para la programación del dispositivo. Para utilizarlo debemos instalar además los drivers de los PsoC que se proporcionan junto a la herramienta.

#### 2.9.4. Avnet Programming Utility

Esta herramienta sirve para descargar nuestros diseños de FPGA a la placa de evaluación. Permite programar directamente sobre la FPGA, sobre la memoria flash paralela y sobre la memoria flash serie escogiendo el puerto COM correspondiente a nuestro dispositivo y la velocidad a la que tengamos configurado el modulo USBUART del PsoC (115200 por defecto).

#### 2.9.5. Microsoft Visual C#

Es un entorno de desarrollo incorporado en la suite Visual Studio 2008. Se ha usado para hacer la aplicación con interfaz gráfica que se ejecutará en PC. Se trata de un lenguaje orientado a objetos para aplicaciones sobre la plataforma .NET 3 o superior de Microsoft.

#### 2.10. Coste del sistema

#### Costes de personal

• **Director de proyecto:** Horas dedicadas: 30

Coste/hora: 35 €

Coste total: 1050 €

| Título : Estudio de un kit de diseño mixto con so<br>Autor : Danilo Sanz Moreno<br>Documento : Memoria final del proyecto | oft-core MicroBlaze e IP's, para el control ESP, ASR y ABS |         |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------|

| • Alumno:                                                                                                                 | Horas dedicadas:                                           | 420     |

|                                                                                                                           | Coste/hora:                                                | 15€     |

|                                                                                                                           | Coste total:                                               | 6300€   |

| Coste total del persona                                                                                                   | ıl:                                                        | 7350 €  |

|                                                                                                                           |                                                            |         |

| Costes hardware                                                                                                           |                                                            |         |

| Placa de evaluación                                                                                                       | 49€                                                        |         |

| Circuito integrado A                                                                                                      | DXL202EB con acelerómetro ADXL202JE:                       | 24€     |

| • Emisor infrarojos:                                                                                                      |                                                            | 0.16€   |

| • Fototransistor:                                                                                                         |                                                            | 2.61€   |

| Coste total hardwa                                                                                                        | re:                                                        | 75.77 € |

|                                                                                                                           |                                                            |         |

|                                                                                                                           |                                                            |         |

| Costes software                                                                                                           |                                                            |         |

|                                                                                                                           | 1000=                                                      | 400.0   |

| Coste total software:        | 1113 € |

|------------------------------|--------|

| Avnet Evaluation Board       | 0€     |

| Xilinx Design Suite EDK      | 595€   |

| Microsoft Visual Studio 2008 | 329€   |

| Microsoft Office Word 2007   | 189€   |

8538.77 €

Coste total:

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

## 2.11. Evaluación de riesgos

#### 2.11.1. Lista de riesgos

**R1.Planificación temporal optimista:** estudio de viabilidad. No se acaba en la fecha prevista, aumentan los recursos.

**R2.Falta alguna tarea necesaria:** estudio de viabilidad. No se cumplen los objetivos del proyecto.

**R3.Cambio de requisitos:** estudio de viabilidad, análisis. Retraso en el resto de tareas.

**R4.Equipo del proyecto demasiado reducido:** estudio de viabilidad. Retraso en la finalización del proyecto, no se cumplen los objetivos del proyecto.

**R5.Herramientas de desarrollo inadecuadas:** implementación. Retraso en la finalización del proyecto, menos calidad.

**R6.Dificultad de acceder a los** *stakeholders:* estudio de viabilidad, estudio del dispositivo, diseño, pruebas... Faltan requisitos o son inadecuados, retrasos, insatisfacción usuarios.

**R7.No se hace correctamente la etapa de pruebas:** desarrollo, implantación. Falta de calidad, deficiencias en la puesta en marcha, insatisfacción usuarios, pérdidas económicas.

**R9.Abandono del proyecto antes de la finalización:** en cualquier fase. Pérdidas económicas, frustración.

**R10.Avería de recursos materiales:** en cualquier fase. Retraso del proyecto.

#### 2.11.2. Catalogación de riesgos

Tabla 2.10: Catalogación de riesgos

| Riesgo | Probabilidad | Impacto      |

|--------|--------------|--------------|

| R1     | Alta         | Crítico      |

| R2     | Alta         | Crítico      |

| R3     | Alta         | Marginal     |

| R4     | Alta         | Crítico      |

| R5     | Baja         | Crítico      |

| R6     | Baja         | Crítico      |

| R7     | Alta         | Crítico      |

| R8     | Media        | Crítico      |

| R9     | Media        | Catastrófica |

| R10    | Baja         | Crítico      |

Autor : Danilo Sanz Moreno

Documento: Memoria final del proyecto

## 2.11.3. Plan de contingencia

Tabla 2.11: Plan de contingencia

| Riesgo | Solución a adoptar                                                  |

|--------|---------------------------------------------------------------------|

| R1     | Aplazar alguna funcionalidad, afrontar posibles pérdidas.           |

| R2     | Revisar el estudio de viabilidad, modificar la planificación.       |

| R3     | Aplazar alguna funcionalidad, modificar planificación i             |

|        | presupuesto.                                                        |

| R4     | Pedir un aplazamiento.                                              |

| R5     | Mejorar la formación del equipo, prevenir herramientas              |

|        | alternativas, mejorar la calidad.                                   |

| R6     | Fijar un calendario de reuniones, mejorar el contacto con el jefe   |

|        | de proyecto.                                                        |

| R7     | Diseñar las pruebas con antelación, negociar contrato de            |

|        | mantenimiento, dar garantías.                                       |

| R8     | Revisar las normas, legislación y patentes. Consultar a un experto. |

| R9     | No tiene solución.                                                  |

| R10    | Prevenir la reposición de material de recambio.                     |

## 2.12. Conclusiones

Dado que se ha implementado el sistema hardware mínimo y a pesar de los riesgos encontrados deducimos que este proyecto es viable.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

## 3. Diseño del sistema

#### 3.1. Introducción

El sistema MicroBlaze con PLB montado en la placa de prototipado consiste en un microprocesador de 32-bits con multiplicador de enteros de 32 bits por hardware y una unidad de punto flotante. La frecuencia de reloj es de 50 MHz, el pipeline es de 3 etapas y la memoria BRAM es de 32 KB dado que MicroBlaze solo nos permite escoger BRAM en potencias de 2.

## 3.2. Componentes principales de Microblaze

Para poder trabajar cómodamente con el microprocesador MicroBlaze resulta esencial conocer algunos archivos de configuración y el significado que tienen. Estos archivos se pueden encontrar distribuidos en las carpetas que se crean con la realización del proyecto.

**System.mhs:** es el archivo que contiene la descripción del soft-core MicroBlaze y de las IP's. Se describen los IPCore's utilizados y la dirección base de estos. Es uno de los archivos a verificar en los errores hardware que nos puede reportar el sintetizador.

**System.mss:** Es el archivo que determina el sistema operativo utilizado, el compilador del microprocesador y el driver y versión utilizado para cada IPCore.

**Bitgen.ut:** Contiene parámetros de configuración utilizados a la hora de crear el archivo .bit. Estos parámetros determinan entre otras cosas la velocidad de reconfiguración del FPGA, el señal de reloj que determinará el inicio del proceso de configuración y el estado de los pines en el momento de configuración.

**Xparameters.h:** Contiene directivas de las direcciones de memoria donde se encuentran mapeados los IPCore. Se utiliza como cabecera de programa para no tener que escribir las direcciones de acceso a los IP's a mano.

**Systen.ucf:** Este archivo es el que usa el sintetizador para interconexionar los pines de la FPGA con los puertos de entrada y/o salida de cada IPCore.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

**Proyecto.ld:** Aquí se encuentra la configuración del proyecto software para ejecutar en la FPGA. Se describen los segmentos en los que se divide el programa y su ubicación, así como las direcciones de inicio de la memoria donde ubicaremos el software.

**Archivo.bit**: es el archivo final que se obtiene para descargar el diseño en placa. Este archivo lo podemos ubicar en la memoria serie o paralela en otro formato, estableciendo los *jumpers* para indicar que el archivo.bit se ha de buscar en una memoria o en otra cada vez que se resetee el sistema.

**Archivo.bin:** Es el formato de archivo para programar la memoria. En el caso de la conversión de archivo.bit a .bin los dos archivos dispondrán el mismo contenido pero distinto en formato.

**Executable.elf:** Es el archivo que contiene el ejecutable del programa codificado para MicroBlaze.

#### 3.3. El método Execute in Place

Dado que nuestro sistema MicroBlaze solo dispone de 32KB para código y datos. Este espacio es insuficiente para almacenar un programa medianamente grande. Es por ese motivo que se decide buscar la forma para que la memoria flash paralela se utilice como memoria para instrucciones.

Para realizar el proceso se requiere indicar en el archivo .ld que segmentos ubicaremos en memoria BRAM y que segmentos ubicaremos en memoria flash y a partir de que dirección, para tal motivo se determinan los segmentos de solo lectura .text, .init, .fini, .rodata, .sdata2 y .sbss2 que se pueden ubicar en la memoria flash, a posteriori de la compilación se han de generar estas partes en .bin con el comando:

```

mb-objcopy -O binary -j .text -j -init ... ./Proyecto/executable.elf

./Proyecto/Codigo.bin

```

El proceso posterior es actualizar el bitstream con el archivo .ld para poder indicar al hardware a partir de que posición de memoria se encuentra el código. Se generará un archivo .bit que habremos de portar a .bin con un script llamado make\_bpi\_image.bat que se encuentra en la carpeta FLASH\_BURN.

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

#### 3.4. Los IPCore's

Para añadir funcionalidades al procesador es necesario utilizar periféricos y memoria. Pues bien, los IPCore no son más que controladores que describen un comportamiento para periféricos y memoria.

Para el montaje de nuestro sistema encontramos que existen algunos IPCore's ya creados que se pueden implementar en nuestro sistema. Cada IPCore dispone de una API que podemos utilizar además de estar mapeados en una dirección de memoria con lo que podemos hacer accesos de lectura y escritura de datos sobre esa dirección en función del funcionamiento que tenga el IPCore. A continuación describiremos su cantidad y su función:

Tabla 3.1: IPCores del sistema

| IPCore            | Número | Dispositivo que<br>controla                                   | Función                                                            |

|-------------------|--------|---------------------------------------------------------------|--------------------------------------------------------------------|

| Microblaze        | 1      |                                                               | Microprocesador                                                    |

| lmb_v10           | 1      |                                                               | Bus que comunica MicroBlaze<br>y la memoria BRAM o<br>periféricos. |

| plb_v46           | 1      | bus de datos                                                  | IPCore que define el bus PLB.                                      |

| Imb_bram_if_cntrl | 2      | lmb_v10                                                       | Controlador de memoria<br>BRAM que conecta el bus con<br>ésta.     |

| xps_mch_emc       | 1      | Memoria flash paralela                                        | Controlador de memoria flash paralela                              |

| bram_block        | 1      | controlador de memoria<br>BRAM de datos y de<br>instrucciones | Bloque de memoria BRAM.                                            |

| xps_gpio          | 1      | Botones Cap Sense                                             | Controla los elementos de entrada/salida                           |

Autor: Danilo Sanz Moreno

Documento: Memoria final del proyecto

| IPCore          | Número | Dispositivo que controla | Función                                                                           |

|-----------------|--------|--------------------------|-----------------------------------------------------------------------------------|

| xps_iic         | 1      | Sensor de temperatura    | Incorpora el protocolo I2C<br>para control del TMP100                             |

| xps_intc        | 1      | Señales de interrupción  | Controlador de interrupciones                                                     |

| xps_timer       | 1      | Contador de ciclos       | Contador de ciclos de 32-bits                                                     |

| xps_uartlite    | 1      | Conexión serie con PSoC  | Controlador protocolo serie                                                       |

| clock_generator | 1      | Divisor de señal         | Genera una señal de reloj de<br>50 MHz a partir del reloj de<br>entrada de 16 MHz |

| proc_sys_reset  | 1      |                          | Restaura el sistema                                                               |

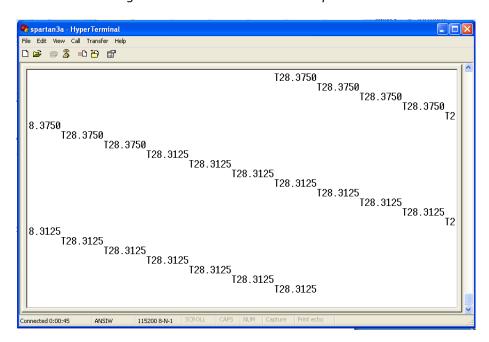

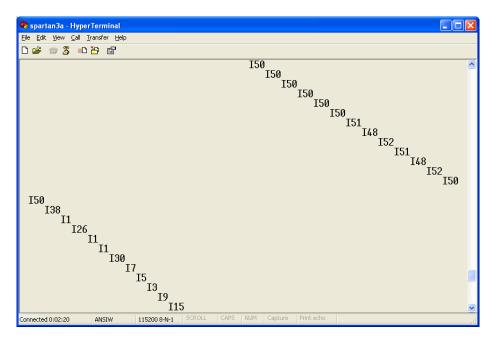

#### 3.5. Pruebas de rendimiento