## DISSERTATION FOR THE DEGREE DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE (SPECIALITY IN MICROELECTRONICS)

# PARALLEL POST-PROCESSING SOLUTION FOR GNSS-R INSTRUMENT

Ph.D Dissertation by

Guo Yi E-mail: guo@ieec.uab.es

CO-ADVISOR: Prof. Carles Ferrer

DEPARTMENT OF MICROELECTRONIC AND ELECTRONIC SYSTEM

UNIVERSITAT AUTÒNOMA DE BARCELONA (IEEC-UAB)

CO-ADVISOR: Prof. Antonio Rius

INSTITUT DE CIÈNCIES DE L'ESPAI (ICE-CSIC) INSTITUT D'ESTUDIS ESPACIALS DE CATALUNYA (IEEC)

Bellaterra, December, 2011

Department of Microelectronic and Electronic System Universitat Autònoma de Barcelona (UAB)

#### Universitat Autònoma de Barcelona (UAB) Department of Microelectronic and Electronic System

# PARALLEL POST-PROCESSING SOLUTION FOR GNSS-R INSTRUMENT

Dissertation presented to obtain the degree of Doctor of Philosophy in Computer Science (Speciality in Microelectronics)

**Author:** Guo Yi

**Directors:** Prof. Carles Ferrer and Prof. Antonio Rius

Prof. Carles Ferrer i Ramis, Professor from the Universitat Autònoma de Barcelona, Prof. Antonio Rius Jordán, Professor from Institut de ciències de l'espai (ICE-CSIC) and Institut d'Estudis Espacials de Catalunya (IEEC)

#### **CERTIFY:**

that the dissertation "Parallel Post-processing Solution for GNSS-R Instrument", presented by Ms. Guo Yi to obtain the degree of Doctor of Philosophy in Electrical Engineering, has been done under their direction at the Universitat Autònoma de Barcelona.

Barcelona, December, 2011

Prof. Carles Ferrer Prof. Antonio Rius

#### **Preface**

L-band signals transmitted by the Global Navigation Satellites Systems (GNSS) from its reflection off the Earth's surface allow for the inference of some of its geophysical properties. This concept is named GNSS-Reflectometry (GNSS-R), or PAassive Reflectometry and Interferometry System (PARIS).

The collected signals are processed by specialized GNSS-R receivers. This dissertation focusses on system design, which is primarily able to post-process the received GNSS-R data, with the purpose of reducing the sustained data throughput of the instrument, which is in the order of several Mbytes/sec. This amount of data poses very stringent requirements on GNSS-R designers .

In our study, we have taken as an example of GNSS-R receiver design, the GPS Open-Loop Differential Real Time Receiver (GOLD-RTR), which was designed, developed and built at the ICE (IEEC-CSIC). The problem that we faced could be stated thus: we have a system which produces 12.8 Mb/s in a sustained manner, and we need to reduce this rate by three orders of magnitude by applying suitable integration algorithms, to be discussed later.

The work towards my PhD has focused on one broad subject and applied this to the actual hardware design platform in order to study and address it. The subject was parallelism provision for the GNSS-R post-processing system, with special focus on the integration algorithms. The subject of parallelism provision is considered a multilayer problem, the most discussed issues are related to the task-level and memory-level design.

The Symmetric Multi-Leon3 On Linux (SMLOL) platform, was developed to address the timing issues for the GNSS-R application. This subject was the parallelism provision for the task-level system, with special focus on the conventional Symmetric MultiProcessing (SMP) scheme.

As a multi-task problem, we used to assess the computational load, system performance and infer the system bottlenecks. However the unbalanced workload in the hardware design (among processors, cache, memory and bus) can not be fundamentally resolved through software methodology.

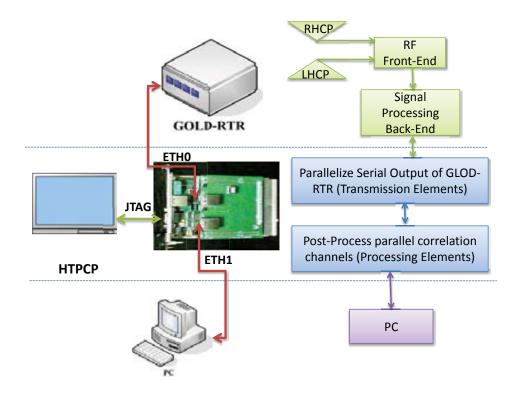

The Heterogeneous Transmission and Parallel Computing Platform (HTPCP) was later developed in order to balance the transmission and computing workload. This subject was the parallelism provision for the memory-level system. According to the simulations results arrived at by MPARM emulator, we built and optimized the memory hierarchy system, in order to remove the bus busy ratio and memory access time between cache and main memory.

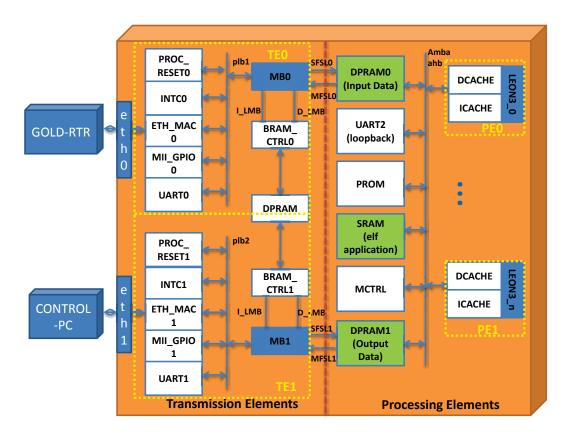

Moreover, dealing with the bus congestion issue, we implemented two types of element: Transmission Elements (TEs) and Processing Elements (PEs), as well as several interface designs: Massage Passing Interface (MPI) and Fast Simplex Link (FSL) in HTPCP.

The intended solution was to design, build and test a system with capacity to reduce the data flow three orders of magnitude by performing autonomous post-processing algorithms.

#### **Prefacio**

Las señales de banda trasmitidas por los sistemas de navegación global por satélite (GNSS, *Global Navigation Satellites Systems*) permiten averiguar algunas de las propiedades geofísicas de la Tierra al reflejarse en su superficie. Este concepto se llama reflectometría GNSS (GNSS-R) o sistema de interferometría y reflectometría pasivo (PARIS, *Passive Reflectometry and Interferometry System*).

Una serie de receptores GNSS-R especializados se encargan de procesar las señales recogidas. Esta tesis se centra en el diseño de dichos receptores, que permite principalmente procesar *a posteriori* los datos GNSS-R obtenidos, con el objetivo de reducir la tasa de transferencia de datos sostenida (*sustained data throughput*) del dispositivo, que es de alrededor de varios MB/s. Dicha cantidad de datos afecta enormemente al diseño de receptores GNSS-R.

En nuestro trabajo, hemos tomado como ejemplo de diseño de receptores GNSS-R el receptor GOLD-RTR (GPS *Open-Loop Differential Real Time Receiver*), diseñado, desarrollado y construido en el ICE (IEEC-CSIC). El problema al que nos enfrentamos es el siguiente: disponemos de un sistema que produce 12.8 Mb/s de forma sostenida y necesitamos reducir su magnitud tres veces mediante la aplicación de algoritmos de integración adecuados, que discutimos más adelante.

Las investigaciones realizadas durante mi doctorado, centradas en un tema muy amplio, las he aplicado al estudio y tratamiento de la plataforma de diseño del hardware correspondiente. El tema desarrollado fue el uso del paralelismo para el sistema de post-procesamiento GNSS-R, con especial atención a los algoritmos de integración. El tema del paralelismo se considera un aspecto problemático de múltiples dimensiones, siendo las más tratadas la del diseño de tareas y de memoria.

Se desarrolló una plataforma SMLOL (*Symmetric Multi-Leon3 On Linux*) para tratar los problemas de sincronización de la aplicación GNSS-R. Aquí se trató el uso del paralelismo para el sistema de tareas, con especial atención al esquema SMP (*Symmetric MultiProcessing*) convencional.

Como problema multitarea, evaluamos la carga computacional y el rendimiento del sistema y comprobamos las congestiones del sistema. Sin embargo, el desequilibrio en la carga de trabajo del diseño del hardware(en procesadores, memoria caché, memoria principal y buses) no se puede solucionar fundamentalmente mediante una metodología aplicada al software.

Posteriormente se desarrolló la plataforma HTPCP (Heterogeneous Transmission and Parallel Computing Platform) para equilibrar la carga de trabajo de transmisión y computacional. En este caso, se trató el uso del paralelismo con relación a la memoria del sistema. Según los resultados de simulación obtenidos con el emulador MPARM, construimos y optimizamos el sistema de jerarquía de memoria, para eliminar la tasa de ocupación del bus y el tiempo de acceso a la memoria entre la memoria caché y la memoria principal.

Asimismo, en relación con el problema de congestión en el bus, implementamos dos tipos de elementos: elementos de transmisión (TEs) y elementos de procesamiento (PEs), así como varios diseños de interfaces: interfaz MPI (*Massage Passing Interface*) e interfaz FSL (*Fast Simplex Link*) en HTPCP.

La solución deseada era diseñar, construir y probar un sistema con capacidad para reducir tres veces la magnitud del flujo de información mediante algoritmos de post-procesamiento autónomos.

|                                                    | To my parents and Lei,   |

|----------------------------------------------------|--------------------------|

|                                                    | To my son,               |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

| "Life is like a box of chocolate, you never know v | what you are gonna get." |

|                                                    | Movie Forrest Gump       |

|                                                    |                          |

|                                                    |                          |

|                                                    |                          |

## **Acknowledgments**

The work presented in this thesis could not have been done without the aids and supports of many people. Therefore I have a great honor to express my sincere gratitude to all.

I would first like to thank my supervisors Carles Ferrer and Antonio Rius for everything, of which I would like to highlight all the support and help they provided me throughout the entire Ph.D. as well as encouragement in every endeavor. They were a big motivating force behind this herculean task I finished in last couple of years. Second, I would like to thank the David Atienza for all the support during my stage in EPFL, and as well as for all the collaborative work.

On a personal note, I must thank all my friends in Barcelona but special thanks goes to Lena Kanellou, L. Andrés Cardona for their helps and encouragement. I would also like to acknowledge my debt to Serni Ribó, without his help and patient, I can not go through the system debugging phase alone. I also want to thank Josep Sanz and Fran Fabra, without their wisdom, I can not fix the problem of ethernet and the endianess, and finally get the optimized result. Last but not least, I would like to thank Estel Cardellach for all the support documents she has given to me.

Finally, I am indebted to my husband Jiang Lei and my parents for their unconditional support and continuous encouragement throughout my work.

Guo Yi Barcelona, November 18, 2011

### **List of Publications**

This dissertation is based on the following Fourteen papers, referred to in the text by letters (A-N).

- **A.** L. A. Cardona, J. Agrawal, Y. Guo, J. Oliver, C. Ferrer; "Performance-Area Improvement by Partial Reconfiguration for an Aerospace Remote Sensing Application", in *Proceedings of International Conference on ReConFigurable Computing and FPGAs*, Cancun, Mexico, November, 2011.

- **B.** Y. Guo, S. Ribó, J. Sanz, A. Rius, C. Ferrer; "HTPCP: Real-Time Post-Processing Solution for GNSS-R Instrument", in *Proceedings of 3rd Int.Colloquium on Scientific and Fundamental Aspects of the Galileo Programme*, Copenhagen, Denmark, August. 2011.

- C. Y. Guo, A. Rius, S. Ribó, C. Ferrer; "Heterogeneous Transmission and Parallel Computing Platform (HTPCP) for Remote Sensing Applications", in *Proceedings* of SPIE, Microtechnologies, Prague, Czech Republic, April. 2011.

- **D.** L. A. Cardona, Y. Guo, C. Ferrer; "Partial reconfiguration of a peripheral in an FPGA-based SoC to analyse performance-area behaviour ", in *Proceedings of SPIE, Microtechnologies*, Prague, Czech Republic, April. 2011.

- **E.** Y. Guo, A. Rius, S. Ribó, C. Ferrer; "On-board real-time parallel processing for GNSS-R Instrument GOLD-RTR", in *GNSSR-10 Workshop*, Barcelona, Spain, October 21-22, 2010.

- **F.** Y. Guo, D. Atienza, A. Rius, S. Ribó, C. Ferrer; "HTPCP:GNSS-R multi-channel correlation waveforms post-processing solution for GOLD-RTR Instrument", in *Proceedings of NASA/ESA Conf. on Adaptive Hardware and Systems (AHS-2010)*, Anaheim, CA, USA, pp. 157- 163, Jun. 2010.

- **G.** Y. Guo, D. Atienza, A. Rius, S. Ribó, C. Ferrer; "GNSS-R multi-channel correlation waveforms post-processing solution for GOLD-RTR Instrument" in *PHD FORUM of Design, Automation & Test in Europe (DATE-2010)*, Dresden, German March 15-18, 2010.

- **H.** Y. Guo, E. Kanellou, L. A. Cardona, A. Rius, and C. Ferrer; "Parallel workload analysis in SMP platform: a new modelling approach to infer the hardware efficiency for remote sensing application " in *Proceedings of SPIE, VLSI Circuits*"

- and Systems IV, Dresden, German vol. 7363, DOI: 10.1117/12.821549. May 2009.

- I. A. Garcia-Quinchía, Y. Guo, E. Martín, C. Ferrer; "A System-On-Chip (SOC) Platform to Integrated Inertial Navigation Systems & GPS " in *Proceedings of international Symposium on Industrial Electronics (ISIE 2009)*, Seúl-Corea July 5-8, 2009.

- **J.** C. Ferrer, Y. Guo, X. Wang, E. Kanellou; "Fault Tolerant NoCs architectures for aerospace applications" in *Forum on specification and Design Languages (FDL-2007): Workshop on System Design in Avionics & Space Industry*, Barcelona, Spain 18-20 of September 2007.

- **K.** Y. Guo, C. Ferrer; "IMS/GPS integration with a novel real-time system platform for inertial data estimation" in *IEEE International Conference on the Computer as a Tool (EUROCON-2007)*, Warsaw, Poland pp. 2503-2583, ISBN: 1-4244-0813-X September 9-12, 2007.

- **L.** Y. Guo, X. Fitó, C. Ferrer; "A novel real-time system platform development applied to an integrated inertial navigation system" in *Proceedings of the 15th IEEE Mediterranean Conference on Control and Automation (MED- 2007)*, Athens, Greece Paper T11-002,ISBN:978-960-254-664-2 June 27-29, 2007.

- **M.** X. Fitó, E. Kanellou, Y. Guo, C. Ferrer; "Designing an inertial measuring system using system-on-chip and sensor microsystems integration" in *Proceedings of the IEEE International Sysposium on Industrial Electronics Conference (ISIE 2006)*, Montreal, Quebec, Canada pp.3285-3263, ISBN: 1-4244-0497-5 July 9-13, 2006.

- N. X. Fitó, F. Lleixa, Y. Guo, C. Ferrer; "Microsystems and System-on-Chip Integration applied to Inertial Measuring System Development" in *Proceedings of the 9th IEEE International Workshop on Advanced Motion Control (AMC-2006)*, Istanbul, Turkey pp. 488-493, vol. 1 & 2, ISBN: 0-7803-9511-1 March 27-29, 2006.

## **Contents**

| Pı | refac | <b>e</b>                                              | i   |

|----|-------|-------------------------------------------------------|-----|

| Pı | refac | io                                                    | iii |

| A  | ckno  | wledgments                                            | vii |

| Li | st of | Publications                                          | ix  |

| Al | bbrev | viations xx                                           | iii |

| I  | Int   | roduction                                             | 1   |

|    | 1.1   | Motivation                                            | 2   |

|    | 1.2   | Objectives                                            | 2   |

|    | 1.3   | Document Structure and Context                        | 3   |

| II | Sta   | ate of the art                                        | 7   |

|    | 2.1   | Introduction                                          | 9   |

|    | 2.2   | GNSS-R Post-Processing Relevant Design                | 9   |

|    |       | 2.2.1 GNSS-R Scenario                                 | 10  |

|    |       | 2.2.2 GOLD-RTR Instrument                             | 12  |

|    |       | 2.2.3 Examples of GNSS-R Post-Processing Applications | 13  |

|    |       | 2.2.3.1 Altimetry                                     | 14  |

|    |       | 2.2.3.2 Ocean Wind and Roughness                      | 16  |

|    |       | 2.2.3.3 Ocean Permittivity                            | 18  |

|    |       | 2.2.3.4 Land and Hydrological Applications            | 18  |

|       |          | 2.2.3.5 Ice and Snow Applications                    | 19 |

|-------|----------|------------------------------------------------------|----|

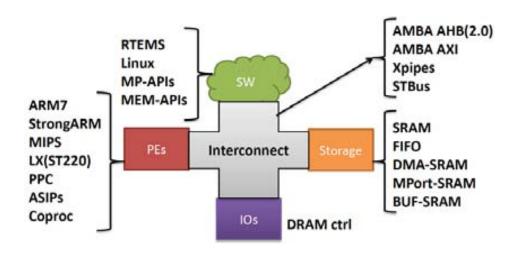

| 2.3   | B Parall | el System Design                                     | 20 |

|       | 2.3.1    | Parallel System                                      | 20 |

|       | 2.3.2    | Parallelism                                          | 23 |

|       | 2.3.3    | Parallel Architecture                                | 26 |

|       | 2.3.4    | Parallel Algorithm                                   | 28 |

|       | 2.3.5    | Parallel Programming Model                           | 29 |

|       |          |                                                      |    |

| III F | Parallel | System Design Based on SMLOL                         | 41 |

| 3.1   | Introd   | luction                                              | 43 |

| 3.2   | SMLC     | DL Platform Overview                                 | 43 |

|       | 3.2.1    | Board Review                                         | 44 |

|       | 3.2.2    | Setup Demonstration Platform                         | 45 |

|       | 3.2.3    | SMLOL Architecture                                   | 46 |

| 3.3   | 3 Hardy  | ware Design in Lower Layer                           | 47 |

|       | 3.3.1    | Configurable Processors and Development Tools        | 48 |

|       |          | 3.3.1.1 Processors Comparison                        | 48 |

|       |          | 3.3.1.2 Development Tools                            | 51 |

|       |          | 3.3.1.3 Performance Metrics                          | 52 |

|       | 3.3.2    | Endianess Design                                     | 53 |

|       | 3.3.3    | Memory Hierarchy Design                              | 54 |

| 3.4   | Softw    | are and OS Design in Higher Layer                    | 55 |

|       | 3.4.1    | Parallel Workload Analysis and Mathematical Modeling | 56 |

|       | 3.4.2    | The Post-Processing Code - Coherent/Incoherent       | 58 |

|       | 3.4.3    | Linux Embedded OS Analysis and Design                | 63 |

|       |          | 3.4.3.1 Compiler Requirement                         | 63 |

|       |          | 3.4.3.2 Linux Kernel Analysis                        | 64 |

|       |          | 3.4.3.3 CPU Configuration                            | 67 |

|       |          | 3.4.3.4 Ethernet Configuration                       | 67 |

|       | 3.4.4    | Multi-task Application and Timing Performance        | 70 |

|    | 3.5        | MPARM Simulation                                                 | 75         |

|----|------------|------------------------------------------------------------------|------------|

|    |            | 3.5.1 Tackle on the Bottleneck of SMLOL                          | 76         |

|    |            | 3.5.2 Simulation Results                                         | 76         |

|    | 3.6        | Summary                                                          | 78         |

|    |            |                                                                  |            |

| IV | <b>P</b> a | rallel System Design Based on HTPCP                              | <b>3</b> 5 |

|    | 4.1        | Introduction                                                     | 87         |

|    | 4.2        | HTPCP Architecture                                               | 87         |

|    | 4.3        | HTPCP Hardware Design                                            | 89         |

|    |            | 4.3.1 Transmission Elements                                      | 90         |

|    |            | 4.3.1.1 Operation Flow of TEs                                    | 91         |

|    |            | 4.3.1.2 Transmission Protocol and Frame                          | 92         |

|    |            | 4.3.1.3 TE/TE Interface Design - Massage Passing Interface (MPI) | 93         |

|    |            | 4.3.2 Processing Elements                                        | 94         |

|    |            | 4.3.2.1 Memory Hierarchy Design                                  | 95         |

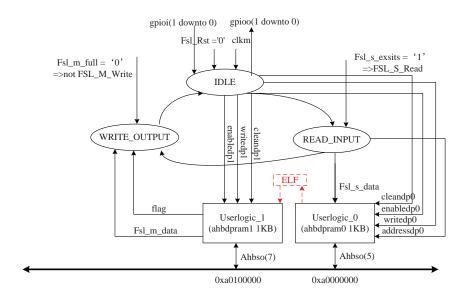

|    |            | 4.3.2.2 PE/TE Interface Design - FSL & GPIO                      | 98         |

|    |            | 4.3.3 Design Flow of HTPCP                                       | .01        |

|    |            | 4.3.3.1 LEON3 System                                             | .02        |

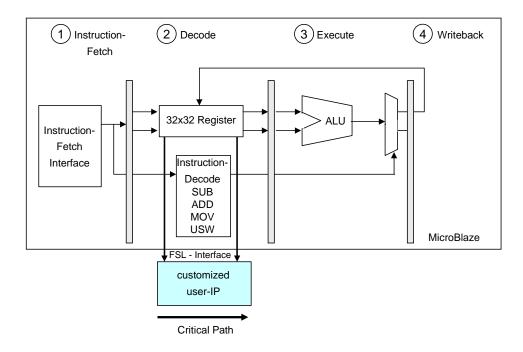

|    |            | 4.3.3.2 Microblaze System                                        | .06        |

|    |            | 4.3.3.3 LEON3 System and MB System Integration 1                 | 15         |

|    | 4.4        | Seven Software Routines                                          | 17         |

|    |            | 4.4.1 MPI Transmission between TEs                               | 20         |

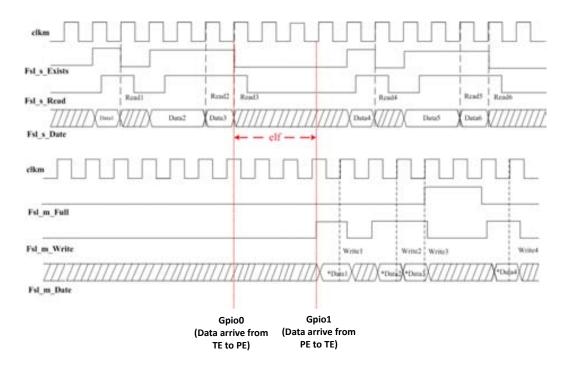

|    |            | 4.4.2 FSL Transmissions between PE and TE Design                 | 21         |

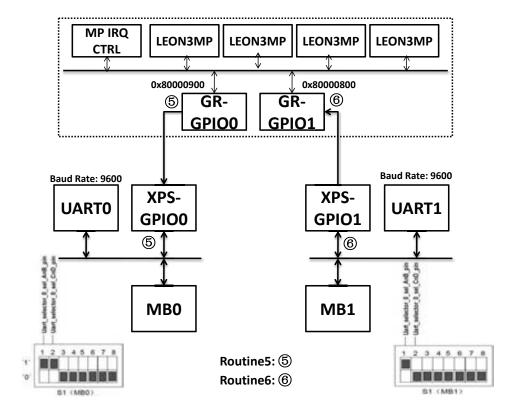

|    |            | 4.4.3 GPIO Connection between PE and TE                          | .23        |

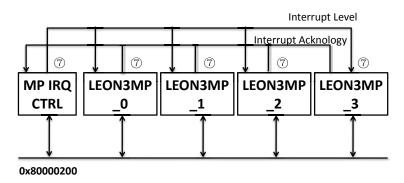

|    |            | 4.4.4 Multi-processor Interrupt Controller between PEs 1         | .27        |

|    | 4.5        | Summary                                                          | .28        |

|    |            |                                                                  |            |

| V  | GN         | SS-R Post-Processing Application and Implementation 13           | 33         |

|    | 5.1        | Introduction                                                     | .35        |

|    | 5.2        | Experiment Constrains                                            | .35        |

|            |      | 5.2.1 Hardware Design Constrains                                                  | . 136 |

|------------|------|-----------------------------------------------------------------------------------|-------|

|            |      | 5.2.2 GOLD-RTR Output Waveforms                                                   | . 138 |

|            |      | 5.2.3 Control PC Output Integrated Waveforms                                      | . 139 |

|            | 5.3  | Post-Processing Algorithms and Timing Parameters                                  | . 140 |

|            |      | 5.3.1 Data Reduction                                                              | . 141 |

|            |      | 5.3.2 Coherent Integration                                                        | . 142 |

|            |      | 5.3.3 Incoherent Integration                                                      | . 144 |

|            |      | 5.3.4 The Coherence Time $	au_{coh}$ and the Coherence Integration Time $T_{coh}$ | 144   |

|            |      | 5.3.5 Incoherence Integration Time $T_{incoh}$                                    | . 147 |

|            | 5.4  | Demonstration Architecture                                                        | . 147 |

|            |      | 5.4.1 The Black Box - HTPCP                                                       | . 148 |

|            |      | 5.4.2 MicroBlaze Processors                                                       | . 150 |

|            |      | 5.4.3 LEON3 Processors                                                            | . 151 |

|            | 5.5  | Campaign on Real Data                                                             | . 151 |

|            | 5.6  | Experiment Results                                                                | . 153 |

|            | 5.7  | Summary                                                                           | . 154 |

|            |      |                                                                                   |       |

| <b>V</b> ] | O    | verall Conclusions                                                                | 161   |

| Δ          | Inn  | ut Waveform Format                                                                | 165   |

|            | шр.  |                                                                                   | 100   |

| В          | Out  | put Waveform Format                                                               | 167   |

| C          | Soli | ution 1: Four LEON3 processors share one software routine.                        | 169   |

| •          | 501  | acion 1. 1 our 22010 processors share one software routine.                       | 100   |

| D          | Solu | ution 2: Four LEON3 cores work with four hardware routines.                       | 171   |

| E          | Solu | ution 3: Four LEON3 processors execute four software routines                     | in    |

|            |      | allel.                                                                            | 173   |

| F          | Con  | nmands from Control PC to HTPCP                                                   | 175   |

| C          | Cor  | nmands from GOLD-RTR to HTPCP                                                     | 177   |

| J          | COII | mmunus nom dom wiw to mil or                                                      | 1//   |

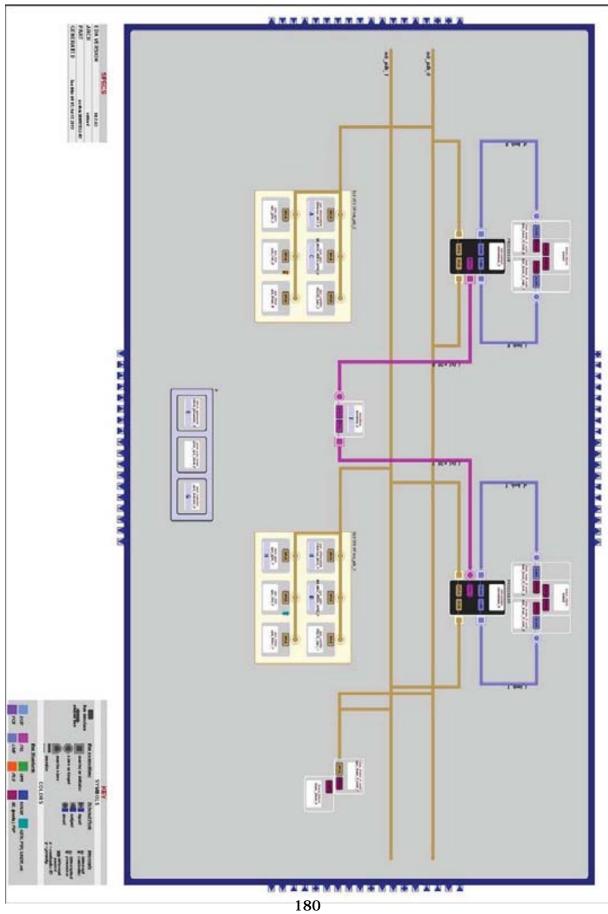

| H          | Blo  | ck Diagram of HTPCP in EDK                                                        | 179   |

## **List of Figures**

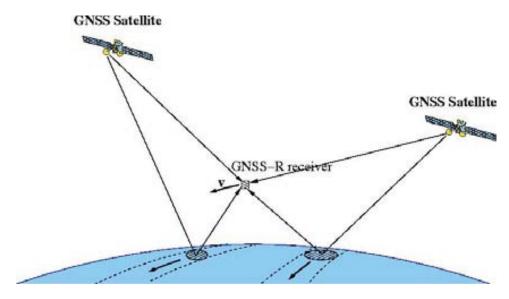

| 2.1  | GNSS-R scenario: GNSS signals reflected on the ocean surface are used to gather their properties like roughness or level. (Adapted from Nogués-Correig et al.[2])                                                                                      | 10 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

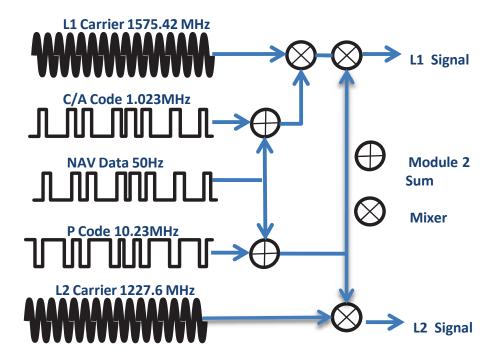

| 2.2  | GNSS-R TX signal model                                                                                                                                                                                                                                 | 11 |

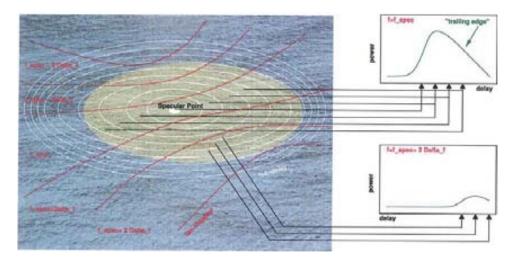

| 2.3  | The composition of all the DM-slices generates the Delay-Doppler Map (DDM). (Adapted from Cardellach et al. [5])                                                                                                                                       | 12 |

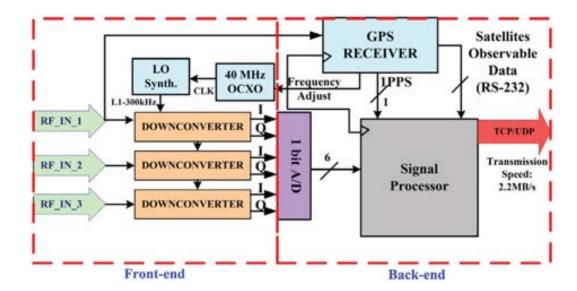

| 2.4  | Block diagram of GOLD-RTR instrument.(Adapted from Nogués-Correig et al.[2])                                                                                                                                                                           | 13 |

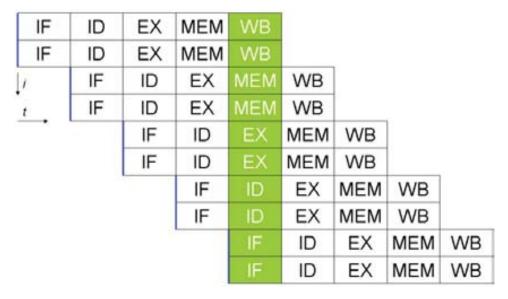

| 2.5  | Canonical five-stage pipeline in a RISC machine. (IF = Instruction Fetch, ID = Instruction Decode, EX = EXecute, MEM = Memory Access, WB = Write Back)                                                                                                 | 24 |

| 2.6  | A five-stage pipelined superscalar processor, capable of issuing two instructions per cycle. It can have two instructions in each stage of the pipeline, for a total of up to 10 instructions being simultaneously executed                            | 24 |

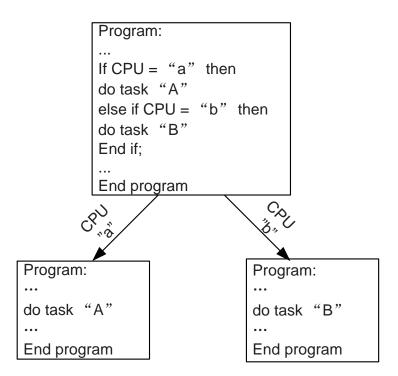

| 2.7  | Task-level parallelism                                                                                                                                                                                                                                 | 26 |

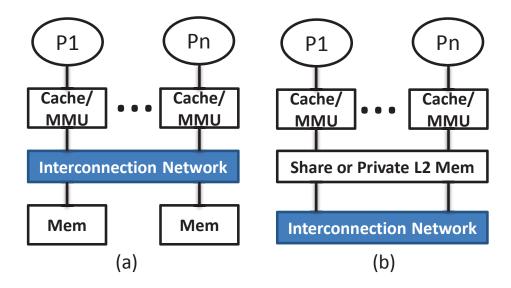

| 2.8  | Multiprocessing systems: a) The multiprocessor with local cache or Memory Management Unit (MMU), but shared memory by long interconnects; b) The multi-core processors with local cache or MMU, but private or shared L2 memory by short interconnects | 27 |

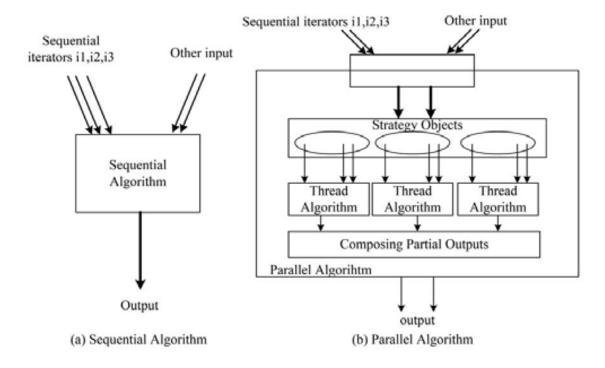

| 2.9  | Sequential algorithm vs parallel algorithm.                                                                                                                                                                                                            | 28 |

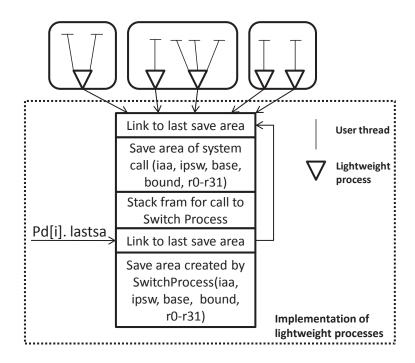

| 2.10 | Thread, process and OS                                                                                                                                                                                                                                 | 29 |

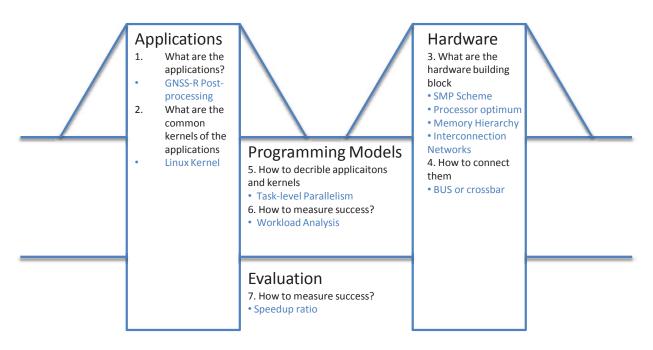

| 2.11 | A view from Berkeley: seven critical questions for 21st Century parallel computing. (Adapted from Krste Asanovic et al. [88])                                                                                                                          | 30 |

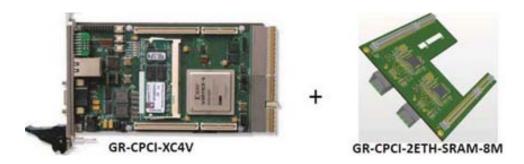

| 3.1  | GR-CPCI-2ETH-SRAM-8M board installed on GR-CPCI-XC4V board                                                                                                                                                                                             | 44 |

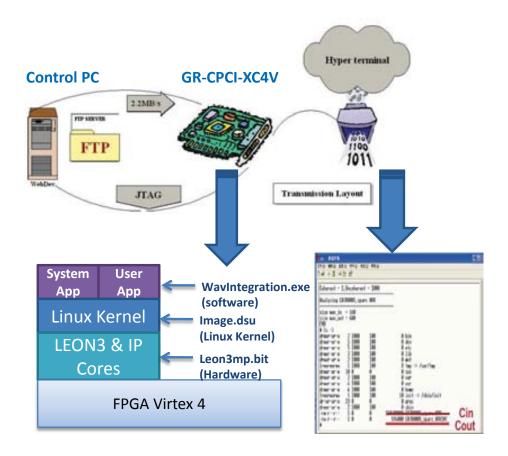

| 3.2  | SMLOL work schematic                                                                                                                                                                                                                                   | 45 |

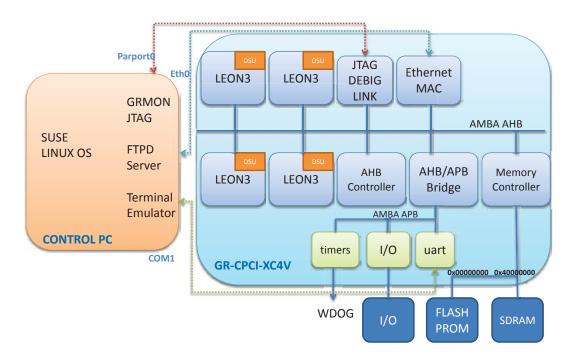

| 3.3  | SMLOL architecture                                                                                                                                                                                                                                     | 46 |

| 3.4  | Linux on SMP design flow                                                                                                                                                                                                                               | 47 |

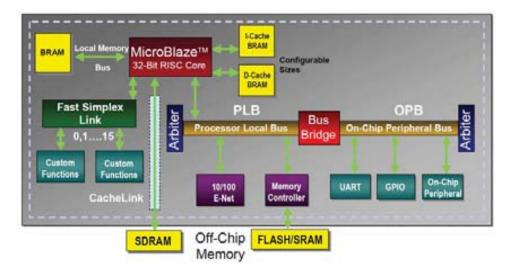

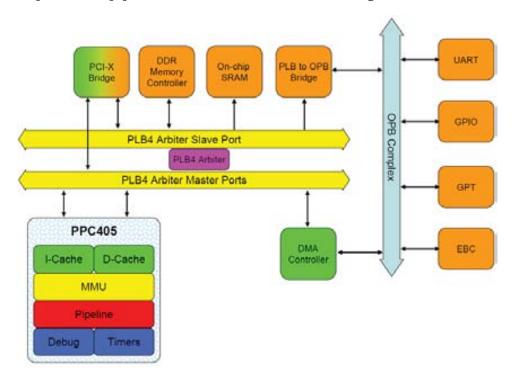

| 3.5 Microblaze architecture                                                                                                                                        | 48 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6 PowerPC 405 architecture                                                                                                                                       | 49 |

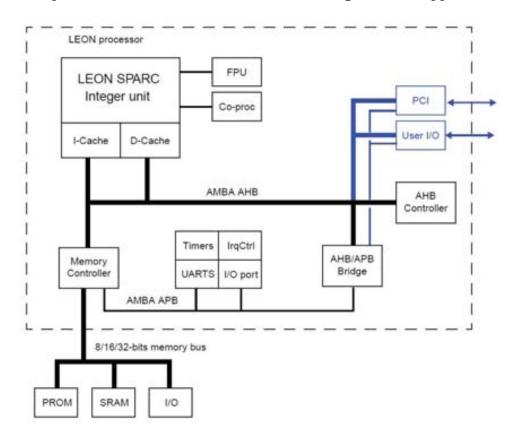

| 3.7 LEON3 architecture                                                                                                                                             | 50 |

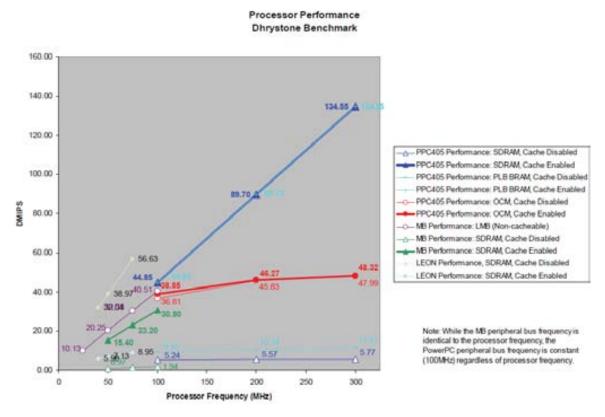

| 3.8 Dhrystone benchmark results on three types of processors. (Adapted from [SANDIA REPORT])                                                                       | 52 |

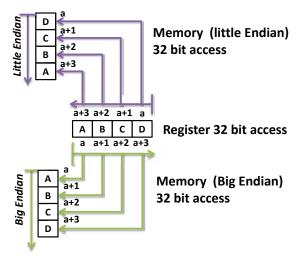

| 3.9 Little endian v.s. big endian                                                                                                                                  | 53 |

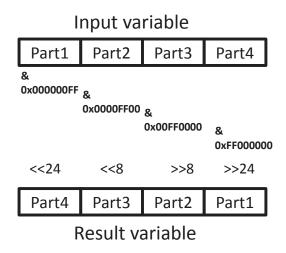

| 3.10 Byte rotate each input variable and assign to the result variable                                                                                             | 54 |

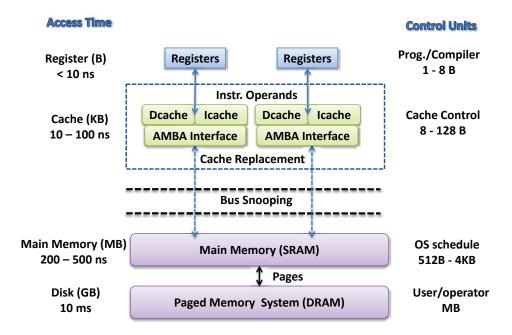

| 3.11 Memory hierachy design                                                                                                                                        | 55 |

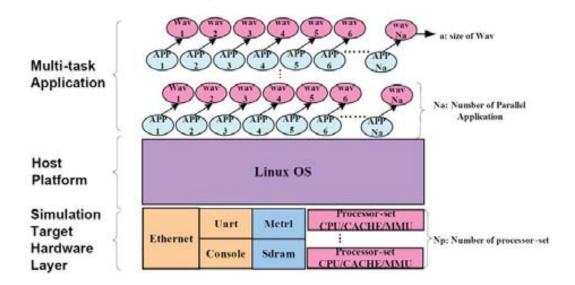

| 3.12 Multi-task application                                                                                                                                        | 56 |

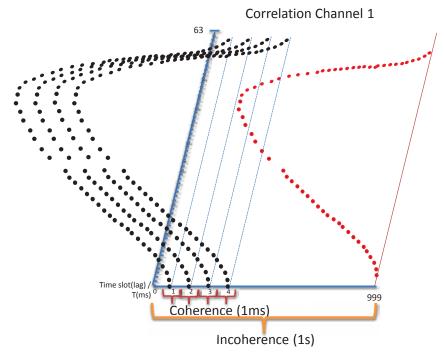

| 3.13 Coherent process input: Every 1s, get 1000 waveforms, 64 lag each, for each correlation channel, total 64000 complex values for each each correlation channel | 59 |

| 3.14Incoherent process output: Every 1s, get 64 integrated complex values for each correlation channel                                                             | 60 |

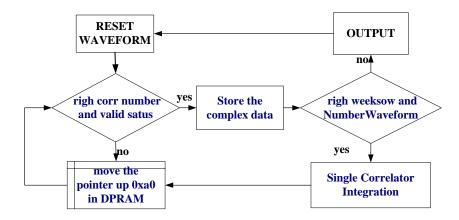

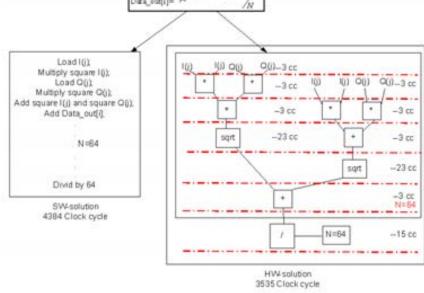

| 3.15 Design flow of Post-processing code.                                                                                                                          | 61 |

| 3.16 Software design versus hardware design.                                                                                                                       | 62 |

| 3.17The file system of the SNAPGEAR Linux                                                                                                                          | 64 |

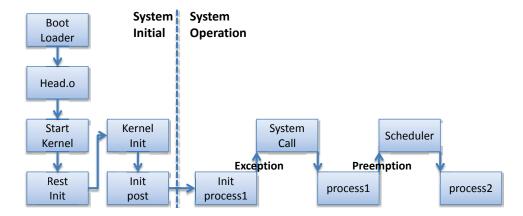

| 3.18Linux kernel initializes the process and incurs the latency                                                                                                    | 65 |

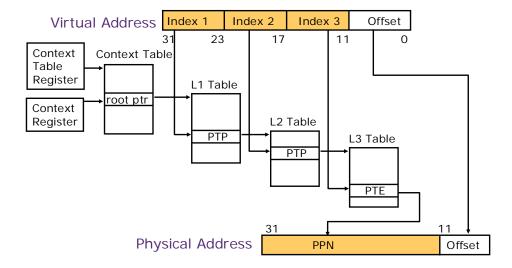

| 3.19 SRMMU virtual address and physical address mapping                                                                                                            | 66 |

| 3.20 "CPU info" description on SMLOL platform with 2/3/4 cores                                                                                                     | 67 |

| 3.21 Ethernet configuration                                                                                                                                        | 68 |

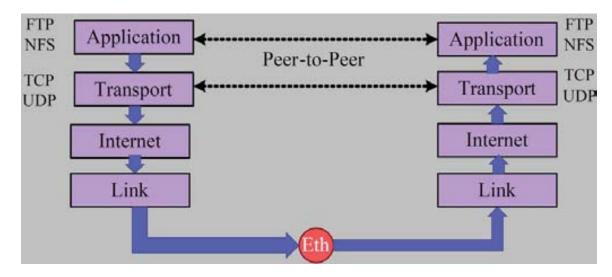

| 3.22 FTP and UDP protocol                                                                                                                                          | 69 |

| 3.23 FTP transmission time                                                                                                                                         | 69 |

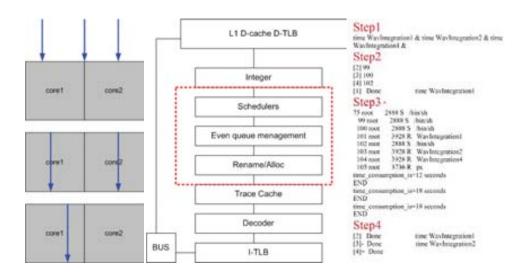

| 3.24 The scheduling of three parallel tasks execute in SMLOL with 2 cores                                                                                          | 70 |

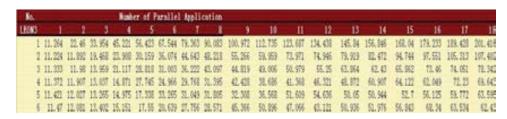

| 3.25 Execution time (s) of parallel application on SMLOL @ 60MHz                                                                                                   | 71 |

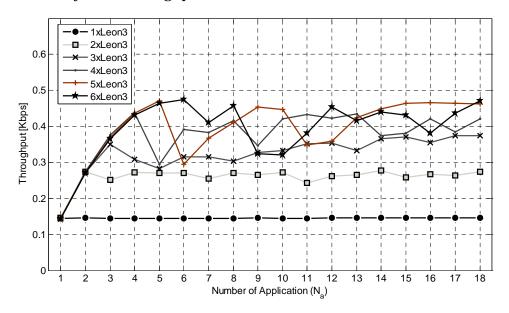

| 3.26 System throughput v.s. parallel applications at multi-core platforms                                                                                          | 73 |

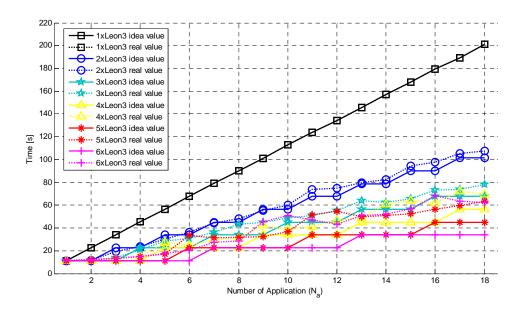

| 3.27 Execution time v.s. parallel applications at multi-core platforms                                                                                             | 74 |

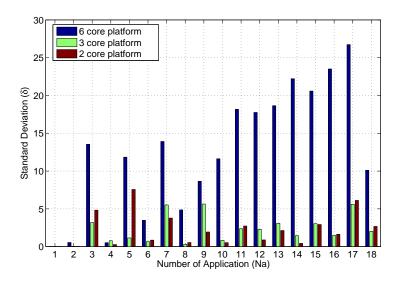

| 3.28 Standard deviation of the execution time with 2 core, 3 core and 6 core platforms                                                                             | 74 |

| 3.29MPARM scheme                                                                                                                                                   | 75 |

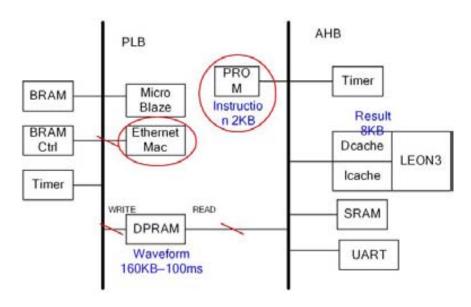

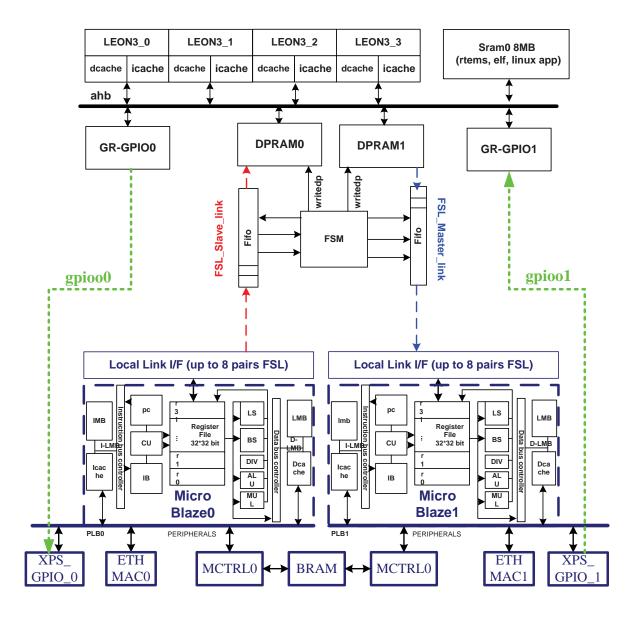

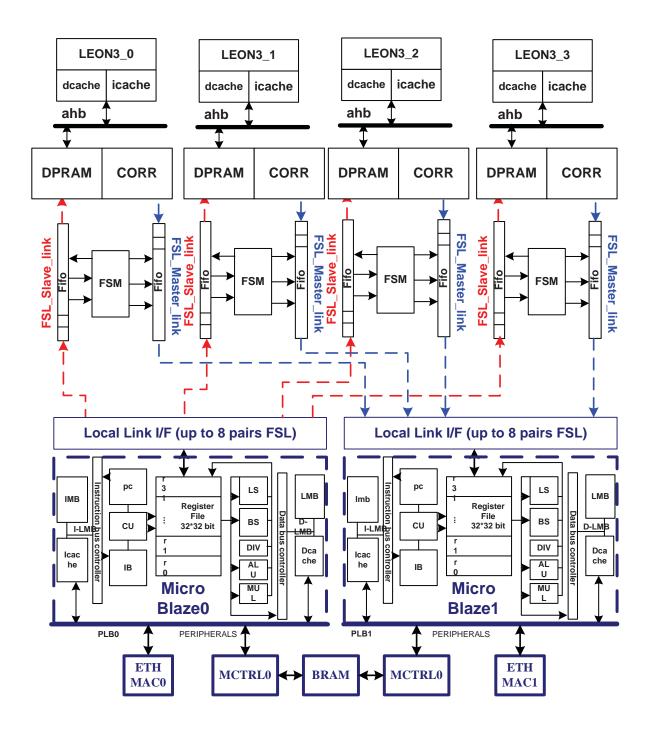

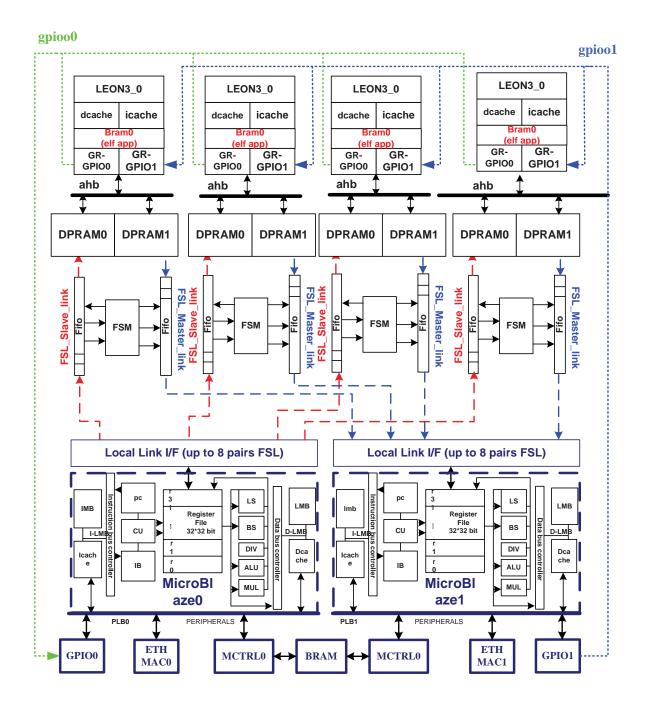

| 3.30MB and LEON3 dual-core architecture                                                                                                                            | 78 |

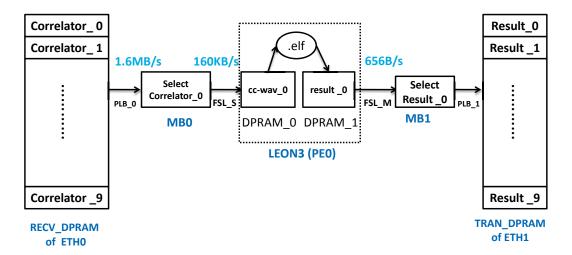

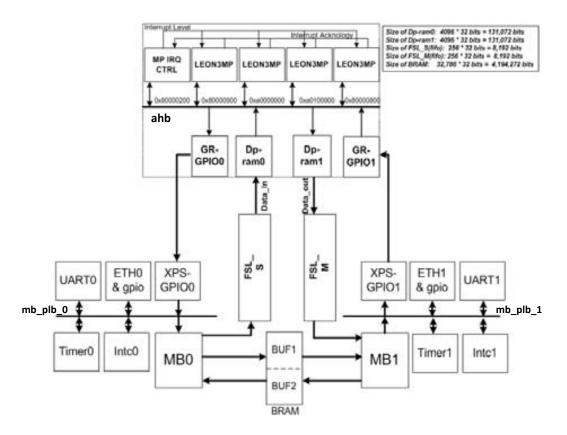

| 4.1 HTPCP block diagram.                                                                                                                                           | 88 |

| 4.2 Work schematic of GNSS-R application                                           | 89  |

|------------------------------------------------------------------------------------|-----|

| 4.3 Transmission diagram                                                           | 90  |

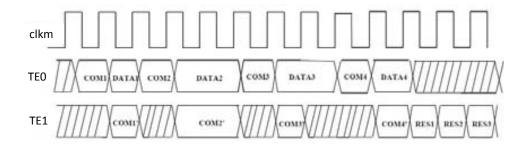

| 4.4 Operation flow of transmission elements (TE0 and TE1)                          | 91  |

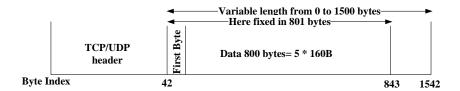

| 4.5 TCP/UDP package frame                                                          | 92  |

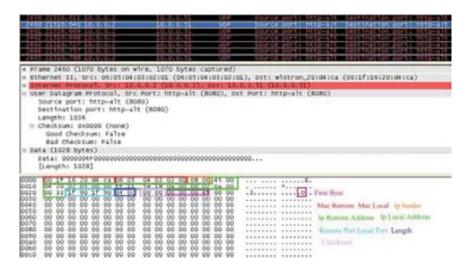

| 4.6 Transmission result in the wireshark                                           | 92  |

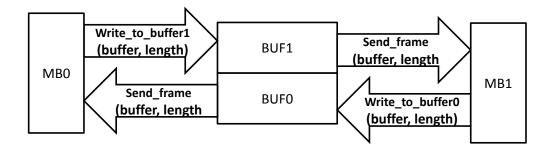

| 4.7 MPI transmission in HTPCP                                                      | 93  |

| 4.8 MPI sequence control                                                           | 93  |

| 4.9 The data path in PE design                                                     | 94  |

| 4.10 Memory hierarchy design in HTPCP                                              | 95  |

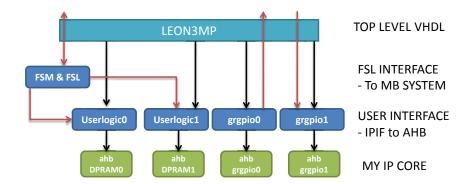

| 4.11 The Finite State Machine (FSM) design                                         | 99  |

| 4.12 Integrated a customized IP into MicroBlaze via the FSL interface              | 100 |

| 4.13 The sequence chart of HTPCP                                                   | 101 |

| 4.14 HTPCP design flow                                                             | 102 |

| 4.15 IP cores design in LEON3 system                                               | 102 |

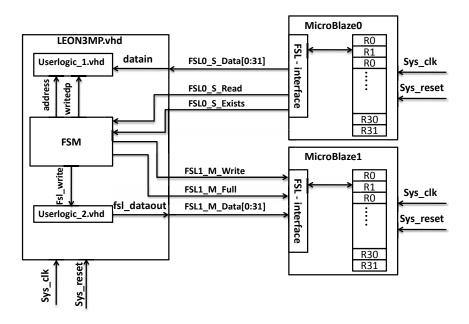

| 4.16 Two FSL links in leon3mp.vhd.                                                 | 103 |

| 4.17 FSM design with two FSL links                                                 | 104 |

| 4.18 IP cores design of Ahbdpram0 and Ahbdpram                                     | 104 |

| 4.19 Ahb ipif designs of Ahbdpram0 and Ahbdpram                                    | 105 |

| 4.20 IP cores design of grgpio0 and grgpio1                                        | 105 |

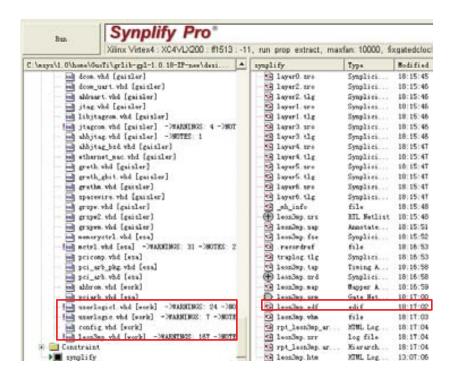

| 4.21 Compile LEON3 system by Synplify Pro                                          | 106 |

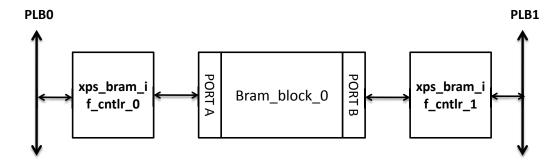

| 4.22 MPI design with one bram_block and two bram controllers                       | 109 |

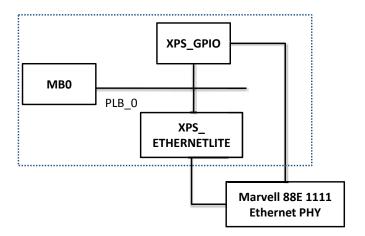

| 4.23 Xps_ethernetlite and xps_gpio block diagram                                   | 111 |

| 4.24 FSL detailed connections between LEON3 system and MB system                   | 115 |

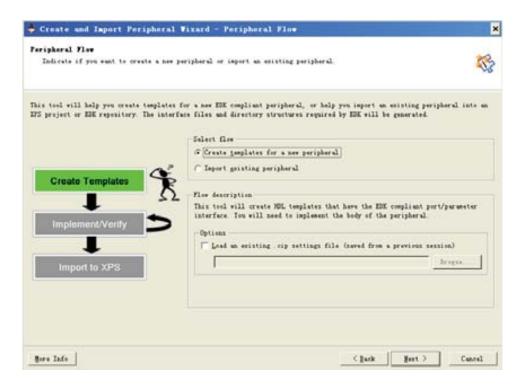

| 4.25 Create templates for a new peripheral                                         | 116 |

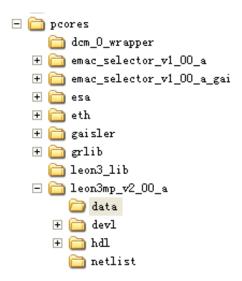

| 4.26 File structure of IP cores in LEON3 system                                    | 117 |

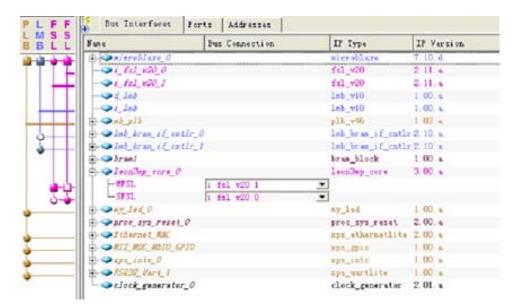

| 4.27 FSL connections between Microblaze_0 and leon3mp_core_0 in Xilinx XPS Project | 117 |

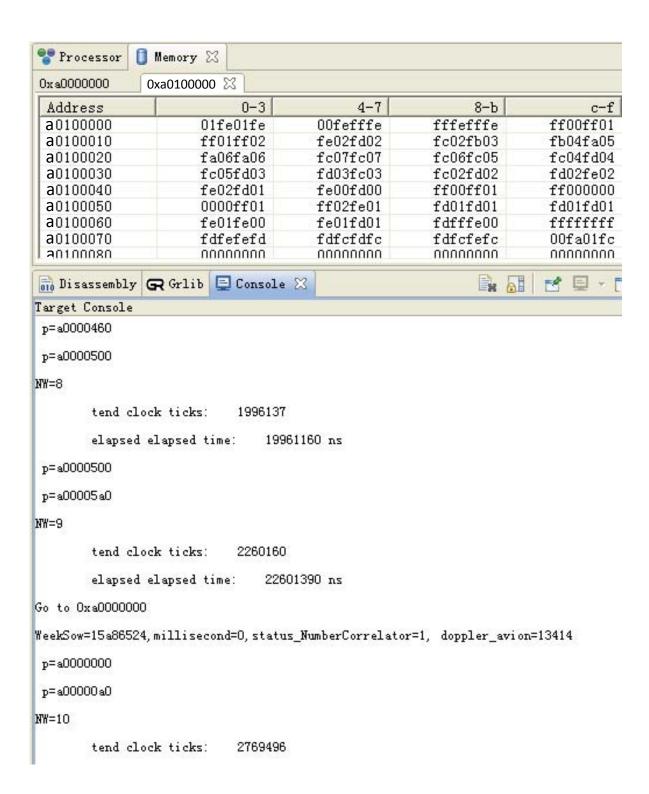

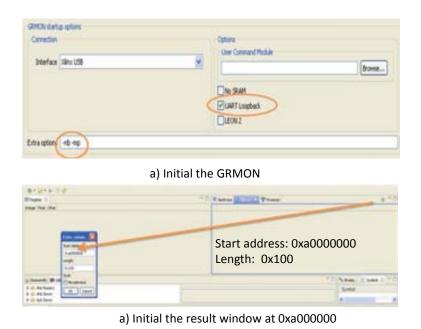

| 4.28 GRMON initialization at 0xa0000000 and 0xa0100000                             | 119 |

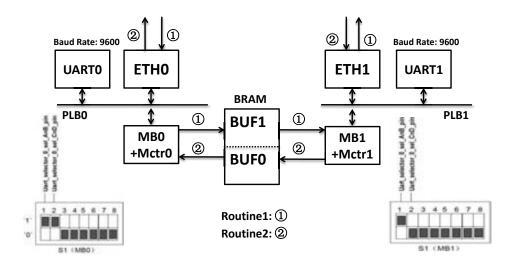

| 4.29 Routine 1 and Routine 2 diagram                                               | 120 |

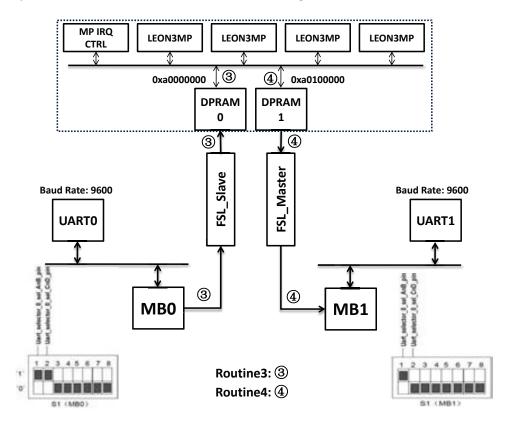

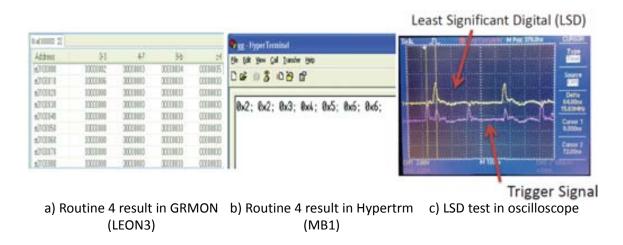

| 4.30 Routine 3 and Routine 4 diagram                                               | 121 |

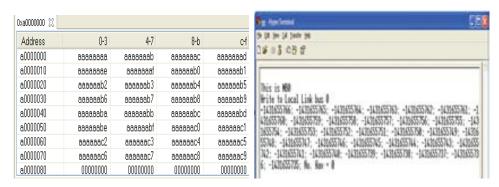

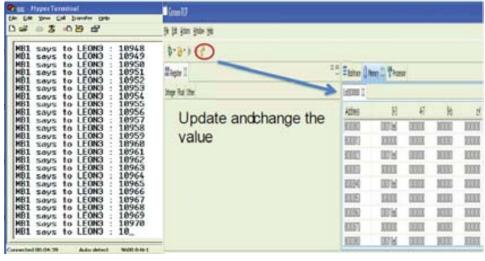

| 4.31 Routine 3 results in GRMON and Hypertrm                                       | 122 |

| 4.32 | Routine 4 results in GRMON and Hypertrm                                           | 123 |

|------|-----------------------------------------------------------------------------------|-----|

| 4.33 | Two software tests for Routine 4                                                  | 124 |

| 4.34 | Routine 5 and Routine 6 diagram                                                   | 125 |

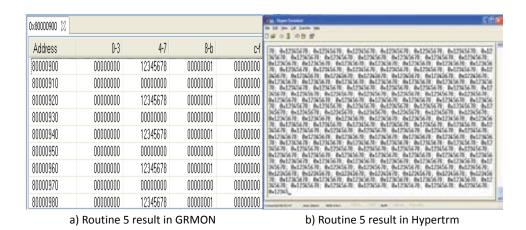

| 4.35 | Routine 5 results in GRMON and Hypertrm                                           | 126 |

| 4.36 | Routine 6 results in Hypertrm and GRMON                                           | 126 |

| 4.37 | Routine 7 diagram.                                                                | 127 |

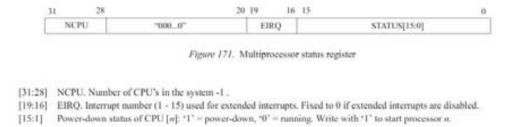

| 4.38 | Multiprocessor status register                                                    | 127 |

| 4.39 | Detect the CPU ID in C                                                            | 128 |

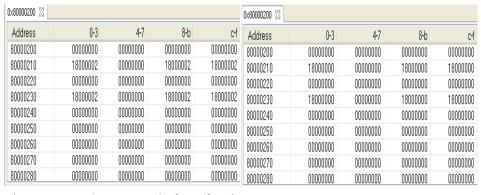

| 4.40 | Routine 7 results in GRMON                                                        | 128 |

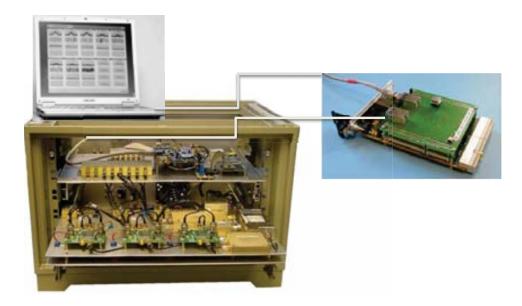

| 5.1  | GOLD-RTR instrument                                                               | 136 |

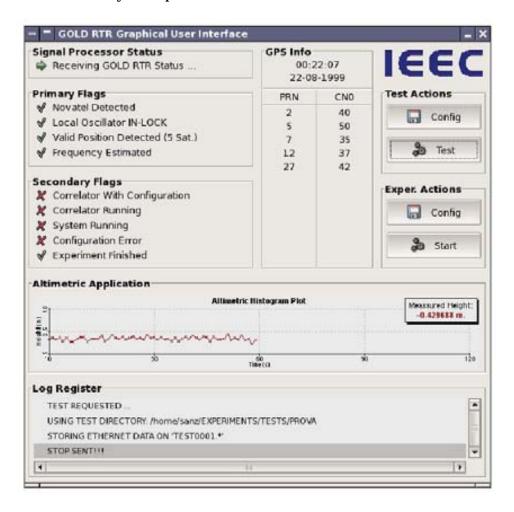

| 5.2  | The main window of the Control PC                                                 | 137 |

| 5.3  | The complete system                                                               | 138 |

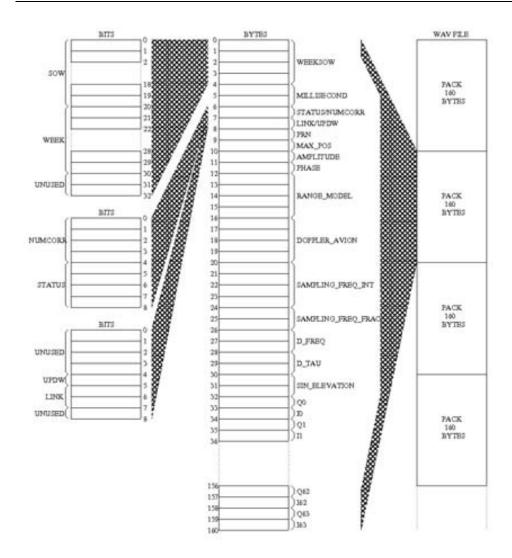

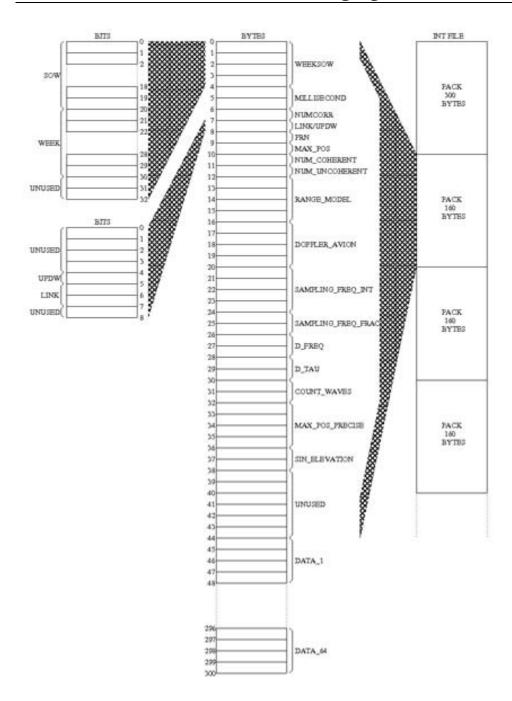

| 5.4  | The structure of the waveforms packet (160 bytes)                                 | 139 |

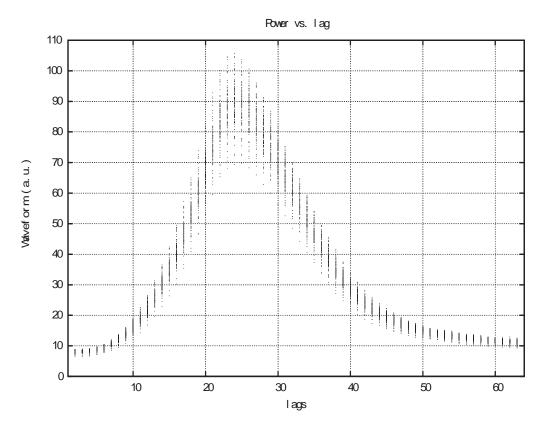

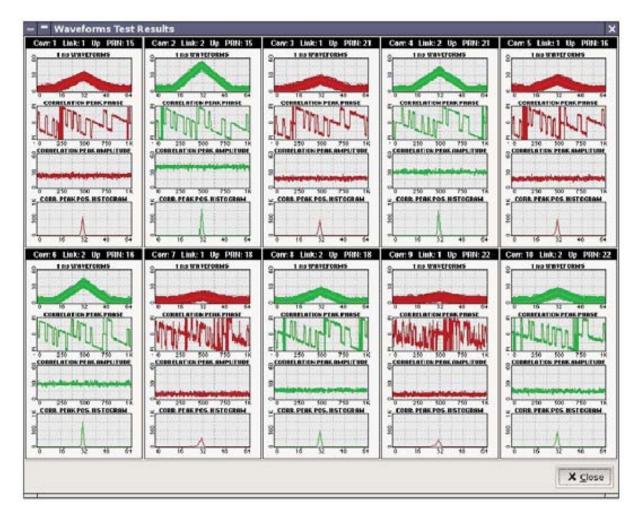

| 5.5  | The graphical representation of the GOLD-RTR output waveforms                     | 140 |

| 5.6  | The structure of the integrated waveforms packets (300 Bytes)                     | 141 |

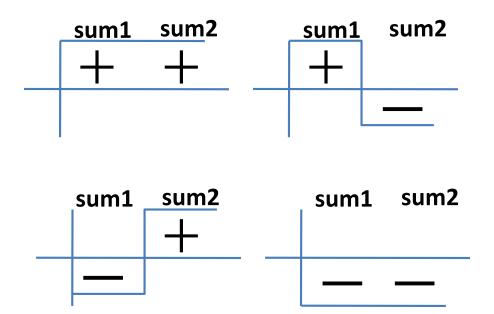

|      | Four cases occur with the sum of these two sets waveforms during the transit time | 144 |

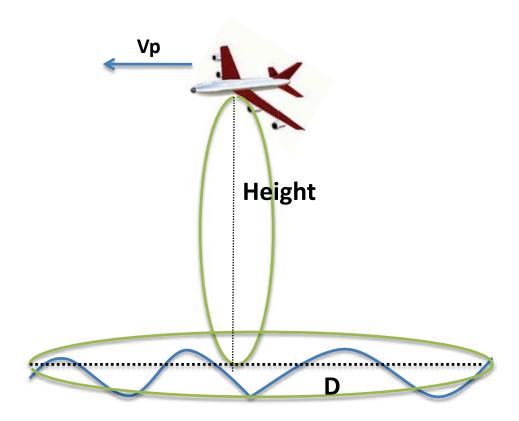

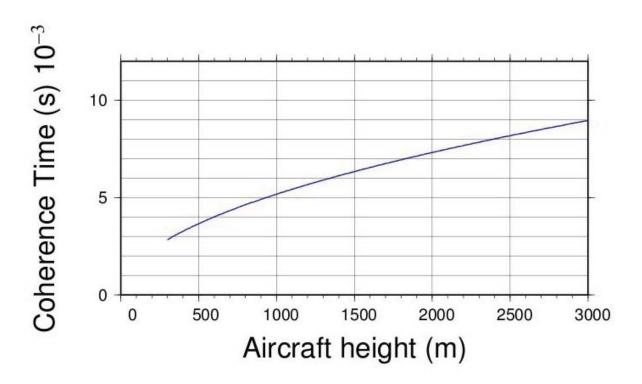

| 5.8  | Coherence time $	au_{coh}$ and coherence integration time $T_{coh}$               | 145 |

| 5.9  | Coherence time using the Van Citter-Zernike theorem                               | 146 |

| 5.10 | HTPCP demonstration diagram                                                       | 148 |

| 5.11 | The map of the experiment campaign CO10.(Adapted from Cardellach et al. [3])      | 152 |

## **List of Tables**

| 2.I         | List of the GNSS-R techniques identified in the literatures                                                         | 14  |

|-------------|---------------------------------------------------------------------------------------------------------------------|-----|

| 2.II        | Flynn's taxonomy.                                                                                                   | 29  |

| 2.III       | Comparison of OPENMP and POSIX                                                                                      | 30  |

| 3.I         | Three types of FPGAs comparison.                                                                                    | 45  |

| 3.II        | Hardware parameters in SMLOL design                                                                                 | 55  |

| 3.III       | Timing affections in parallel system                                                                                | 57  |

| 3.IV        | The impact on compiler optimization levels                                                                          | 64  |

| 3.V         | The impact on the cache migration cost                                                                              | 66  |

| 3.VI        | Three types of execution time (s)                                                                                   | 72  |

| 3.VI        | IThe speedup parameter for multi-processors                                                                         | 72  |

| 3.VI        | ISimulation results by MPARM                                                                                        | 76  |

| <b>4.</b> I | Solution1: memory hierarchy design summary                                                                          | 96  |

| 4.II        | Solution2: memory hierarchy design summary                                                                          | 97  |

| 4.III       | Solution3: memory hierarchy design summary                                                                          | 98  |

| 4.IV        | The optimized memory hierarchy design summery                                                                       | 98  |

| 4.V         | The cables and design tools are needed for the software routines                                                    | 118 |

| 4.VI        | The executable files location, the initial address, and the initial components of LEON3 system in seven SW routines | 118 |

| 4.VI        | ITest results of Routine 1 and 2                                                                                    | 121 |

| 4.VI        | ITest results of Routine 3                                                                                          | 123 |

| 4.IX        | Test results of Routine 4                                                                                           | 123 |

| 5.I         | Case study to illustrate the $\tau_{coh}$ and $T_{coh}$                                                             | 145 |

| 5.II        | The amount of data comparison between original system and complete system                                           | 149 |

| 5.III The ten execution results for experiment one | 153 |

|----------------------------------------------------|-----|

| 5.IV The minimum lost ratio of experiment one      | 153 |

| 5.V The maximum lost ratio of experiment one       | 154 |

| 5.VI The averages lost ratio of experiment one     | 154 |

| 5.VIIThe results of experiment two                 | 154 |

#### **Abbreviations**

ALU Arithmetic Logic Unit

AMBA Advanced Microcontroller Bus Architecture

API Application Programming Interface

ASIC Application Specific Integrated Circuit

BBD Black Box Definition

BRAM Block RAM

CC-WAV Cross-Correlation WAVeform CPU Central Processing Unit

Dcache Data Cache

DCM Digital Clock Manager

DCR Device Control Register

DDM Doppler Delay Map

DM Delay Map

DPRAM Dual-Port RAM

DRAM Dynamic Random Access Memory

DSP Digital Signal Processing

DSU Debug Support Unit

EDAC Error Detection and Correction EDK Embedded Development Kit ESA European Space Agency

FIFO First In First Out

FPGAs Field Programmable Gate Arrays

FPU Floating Point Unit

FSL Fast Simplex Link

FSM Finite State Machine

FTP File Transfer Protocol

GDB GNU DeBugger

GNSS Global Navigation Satellite System

GNSS-R Global Navigation Satellite System - Reflectometry GOLD-RTR GPS Open-Loop Differential Real-Time Receiver

GPS Global Positioning System

GUI Graphical User Interface

HDL Hardware Description Language

HTPCP Heterogeneous Transmission and Parallel Computing Platform

HW HardWare

ICACHE Instruction Cache

ILP Instruction-Level Parallelism

IP Internet Protocol

IPC Inter-Process Communication

JTAG Joint Test Action Group

LMB Local Memory Bus LUT LookUp Table MB MicroBlaze

MHS Microprocessor Hardware Specification

MII Media Independent Interface MMPs Massively Multi-Processing MMU Memory Management Unit

MPD Microprocessor Peripheral Definition

MPI Massage Passing Interface

MPs Multi-Processors

MPSOC Multi-Processors System-On-Chip

MSS Microprocessor Software Specification

NOC Network on Chip

NUMA Non-Uniform Memory Access time

OPB On-chip Peripheral Bus

OS Operation System

PAO Peripheral Analyze Order

PARIS Passive Reflectometry and Interferometry System

PC Personal Computer

PDF Probability Density Function

PEs Processing Elements

PLB Processor Local Bus

PM Processing Module

POPI POlarimetric Phase Interferometry

POSIX Portable Operating System Interface of Unix

PPC PowerPC

PPS Pulse-Per-Second PUs Processor Units

RAM Random Access Memory

RF Radio Frequency

RISC Reduced Instruction Set Computer

RMII Reduced Media Independent Interface

ROM Read-Only Memory

SCI Single Correlation Integration

SDRAM Synchronous Dynamic Random Access Memory

SDK Software Development Kit

SEU Single Event Upset

SMLOL Symmetric Multi Leon3 On Linux SMP Symmetric Multi-Processing

SNAPGEAR SnapGear's embedded Linux distribution

SOC System-On-Chip SOW Second Of Week SRAM Static Random Access Memory

SRMMU SPARC Reference MMU

SW SoftWare

TCP Transmission Control Protocol

TES Transmission Elements

TLP Thread-Level Parallelism

UART Universal Asynchronous Receiver/Transmitter

UDP User Datagram Protocol UMA Uniform Memory Access

UP Uni-Processor

UTP Unshielded Twisted Pair

XCL Xilinx Cache Link

XMP Xilinx Microprocessor Project

XPS Xilinx Platform Studio

# Part I Introduction

#### Introduction

The European Space Agency (ESA) proposed a method for extracting altimeter information from GPS signals reflected off the surface of the sea, called the Passive Reflectometry and Interferometry System (PARIS) in 1993 [1] or the GNSS-R scenario. There is a list of potential applications that has increased considerably since then, including the remote sensing of the state of the sea (surface roughness and its salinity), soil moisture levels, sea-ice characterization, and snow structures [2] which we review in Chapter 2. Because of the mostly non-coherent nature of the reflected signals, they cannot usually be tracked by standard GNSS receivers such as GPS, GLONASS, the future GALILEO and COMPASS. In order to conduct experimental work, a new instrument was designed by ICE (IEEC-CSIC) to compute and store the cross-correlation waveform (CC-WAV) in real time. This device is called the GPS Open-Loop Differential Real-Time Receiver (GOLD-RTR) [3]. Since 2005, this GNSS-R hardware receiver has been used in more than 42 campaign flights and in over 250 days of continuous ground-based observations.

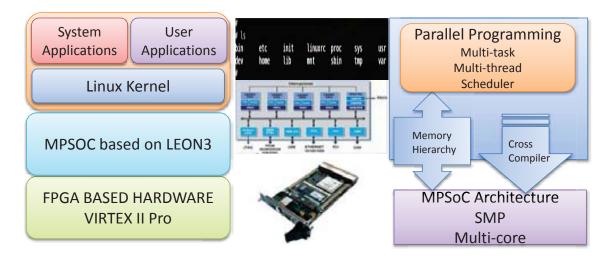

In order to meet the portable and timing requirements for airborne missions, using FPGA as a post-processing platform will be a new approach. FPGA is well suited to form a parallel architecture since it incorporates several soft-cores. Taking into account time-to-market issues and rapid prototype developments, a shared memory Symmetric Multiprocessing (SMP) mounted with embedded OS appears as the first option to explore as we review in Chapter 3. However, the bus-based SMP has limited scalability due to bus congestion and shared memory issues [4]. A new approach is necessary to analysis the parallelism system from the workload perspective, particularly to provide a new emulation framework for addressing situations where is a bottleneck in different layers of Multi-Processing System-On-Chip (MPSOC) design.

The importance of post-processing the recorded waveforms of GOLD-RTR is that it provides diversity to the post-processing algorithm, and thereby reduces the load for the instrument downlink. A novel parallel platform HTPCP is designed to permit leverage of the processing capability and transmission load and this is reviewed in Chapter 4. Moreover, with regard to the post-processing algorithm, Coherent/Incoherent integration is introduced in Chapter 5, combined with the real campaign data to verify the correctness of the HTPCP design in GNSS-R post-processing systems.

#### 1.1 Motivation

The aim of this PhD is to design a post-processing development board, where we can carry out a series of post-processing algorithms for the collected Cross-Correlation WAVforms (CC-WAVs) of the GOLD-RTR. With the development of SMP and NOC architecture, an on-board parallel processing system becomes possible. With sophisticated design tools, FPGA provides the perfect platform for interaction between software programs and hardware designs. For this reason we consider taking advantage of SMP especially in terms of its computing power, and of NOC especially in terms of its transmission power, and so minimize the shortcomings of each architecture, in order to develop a novel real-time post-processing system which can meet the actual bandwidth requirements of the GNSS-R application. In this way we hope to achieve a long term effective campaign and post-processing the CC-WAV in real time during that campaign.

The first challenge in this work is to achieve the system real-time processing features in the multi-processor hardware architecture design. This work will try to address the conflict between the intensive computational load and the transmission load in the SMP design.

The second challenge is the co-design process of the hardware and software. We attempt to find the system design bottlenecks by testing and analyzing the workload model at different levels. The chosen methodology for addressing this problem is the use of memory hierarchy designs and bus designs in order to leverage the workload between the computation and transmission systems. Basically the redesign of these two parts can solve the issues of bus congestion and memory allocation. Moreover, we provide a timing controller to monitor the timing of the input and output data.

Last but not least, in order to study the GNSS-R scenario, an incentive for working the post-processing algorithms for GNSS-R instrument is considered as a scientific experiment for the geophysical exploitation. One example, the Coherent/Incoherent Integration algorithm, has been studied as part of this PhD. This concept has been tested and proven for the future measurements of altimetry experiments, sea roughness caused by wind, soil moisture and sea ice etc..

#### 1.2 Objectives

The main objectives of this PhD are summarized as follows:

- Identify the timing constraints of the post-processing design of GOLD-RTR, emphasizing the basic scientific demonstration of a parallel system.

- Test and simulate the post-processing algorithm on SMP platforms, in order to find out the system bottlenecks in the architecture design.

- Develop the post-processing algorithms to realize a fine-grained parallelism application on the target board, i.e., HTPCP. Fill the gap between the processing time and the storage of the CC-WAV for GNSS-R applications.

- Develop a novel architecture, HTPCP, which has been proposed as a promising technique for GNSS-R post-processing systems, which could meet the realtime requirement and the diversity requirement of processing the scientific demonstrations.

- Verify the HTPCP with the real campaign experiment, in order to demonstrate the correctness of the system design.

The fundamental platform for the development of this thesis is the research project of National Space Plan (CICYT ESP2005-03310), the project entitled "ASAP: Altimetric and Scatterometric Applications of the PARIS Concept", which was developed by ICE (IEEC-CSIC) and INTA. The platform will be used for future campaigns of the GOLD-RTR Instrument.

#### 1.3 Document Structure and Context

This document reflects the line of my PhD research towards obtaining the doctorate. At the beginning of my doctorate course, the subject was decided by implementing the post-processing algorithm of GNSS-R application by FPGA. With the gradual deepening of the study, my research subjects constantly expanded from a general signal processing problem to a concrete multi-core processing, and finally reached a parallel system design. This document is not only the result of this project, but rather an experimental platform. It covers the HTPCP hardware design, post-processing algorithm design, laboratory readiness tests, and the aircraft campaign result experiments.

The rest of the thesis is organized as follows.

- Chapter II discusses the state of the art, focussing on setting out the latest situation in two fields: GNSS-Reflectometry (GNSS-R) technique and Parallel system development.

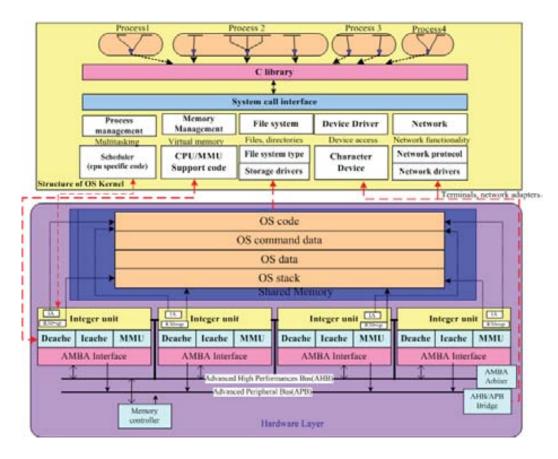

- Chapter III describes the parallel system based on the SMP scheme, namely the Symmetric Multi-LEON3 On Linux (SMLOL) platform, which is designed and analyzed to implement the post-processing algorithm over a task-level parallelism system. The in-depth analysis of timing performance is based on the MPARM emulator, in order to discover the bottleneck of the SMLOL platform. It provides a framework for applying the post-processing algorithm as well as testing its performance in a realistic scenario.

- Chapter IV focusses on the novel parallel platform, called HTPCP, which is presented in order to carry out the real time post-processing for GNSS-R

applications. Moreover, two problems are proposed and solved, 1) Parallelize the inherent serial output of the GOLD-RTR instrument and 2) Post-process the multi-channel (I and Q) correlators in parallel. The seven laboratory readiness tests demonstrate the correctness of the IP cores design in HTPCP.

- Chapter V presents two experiment results based on the real campaign environment in order to demonstrate the correct operation of the entire system (GOLD-RTR + HTPCP + Control PC). Moreover a detailed description of the post-processing algorithm coherent/incoherent integration is introduced, to deal with the data reduction and the data mass storage issues.

- Chapter VI concludes the thesis.

# **Bibliography**

- [1] M. Martín-Neria, "A passive reflectometry and interferometry system (paris):application to ocean altimetry," *ESA Journal*, vol. 17, no. 4, pp. 331–355, 1993.

- [2] E. Cardellach, F. Fabra, O. Nogués-Correig, S. Oliveras, S. Ribó, and A. Rius, "Gnss-r ground-based and airborne campaigns for ocean, land, ice and snow techniques: application to the gold-rtr datasets," RADIO SCIENCE, 2011.

- [3] O. Nogués-Correig, E. Cardellach-Galí, J. Sanz-Camderrós, and A. Rius, "A gps-reflections receiver that computes doppler-delay maps in real time," *IEEE Transactions on Geoscience and Remote sensing*, vol. 45, no. 1, pp. 156–174, 2007.

- [4] Y. Guo, L. Kanellou, A. C. Luis, A. Rius, and C. Ferrer, "Parallel workload analysis in smp platform: a new modelling approach to infer the hw efficiency for remote sensing application," in *Proceedings of of SPIE-VLSI Circuits and Systems IV (SPIE'09)*. Dresden, Germany: SPIE, May 2009.

# Part II State of the art

# State of the art

# 2.1 Introduction

This dissertation is based on the previous knowledge in two fields: GNSS-Reflectometry (GNSS-R) and parallel system design. This Chapter reviews the state of the art of both fields: a) the GNSS-R technique and b) the parallel system development. Here we cover the theoretical basis and technology development related with our project. The first category is described as the GNSS-R post-processing relevant design, it focuses on the implementation of the GNSS-R instrument and its performance for geophysical exploration. The second category is described as the parallel system design based on the basic principles of the parallel system design, and it focuses on the exploration of the parallel system, the definition of parallelism, parallel architecture, parallel algorithm and parallel programming model, in order to argue that they represent an important and distinct category of computer architectures.

# 2.2 GNSS-R Post-Processing Relevant Design

In this Section, we summarize the basic principles of the GNSS-R technique. We mainly focus on the GNSS-R scenario, GOLD-RTR instrument and GNSS-R post-process applications. It is organized as following:

- **The GNSS-R Scenario**, define the GPS transmission signal structure, frequency carriers, carrier modulation, cross-correlation function, and the physical significance of the reflected signal.

- **The GOLD-RTR Instrument**, briefly introduce the composition of the instrument and the work principle of GOLD-RTR.

- The GNSS-R Post-Process Applications, devoted on the description of the basic aspects involved in the technique of using GNSS signals reflected off the ocean surface to infer its physical properties.

#### 2.2.1 GNSS-R Scenario

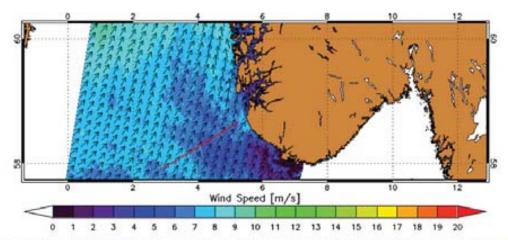

In 1993, the European Space Agency (ESA) proposed a method for extracting altimeter information from GPS signals after their reflection off the sea surface. This concept is created by the Passive Reflectometry and Interferometry System (PARIS) as passive multistatic radar to monitor mesoscale ocean altimetry [1]. This theoretical notion has turned into one of the most recent applications for the Global Navigation Satellite System (GNSS), which is the used of reflections for oceanographic remote sensing purposes. So far it mainly extends to the use of GPS signals combined with airborne receivers to form a type of bistatic radar. The idea is to capture both the GPS signals coming directly from the transmitting satellites and the ones that have been reflected off the ocean surface as shown in Fig.2.1. The delay between them can be used to determine aircraft altitude, and extract the ocean scattered signal information about wave height, wind speed and wind direction. These techniques allow further processing of the real-time computed 1-ms waveforms in a flight campaign over the ocean, ice, or ground, which can be used to obtain geophysical parameters such as sea level and tides, sea surface mean-square slopes, ice roughness and thickness, soil moisture and biomass, or future applications.

**Figure 2.1:** GNSS-R scenario: GNSS signals reflected on the ocean surface are used to gather their properties like roughness or level. (Adapted from Nogués-Correig et al.[2])

As shown in Fig.2.2, satellite transmissions occur using two different frequency carries, L1 = 1575.42 MHz and L2 = 1227.60 MHz, both obtained by multiplication of the fundamental frequency (10.23 MHz) with the factor 154 and 120, respectively. These frequencies are suitable for satellite transmissions because in this range both rain effects and galactic noise are minimized. The low Signal-to-Noise (SNR) L-band (L1 = 1575.42 MHz,  $\lambda$  = 0.1905 meter wavelength) electromagnetic field is transmitted by satellite orbiting at  $\sim$  20000 km altitude. The signals are transmitted at Right-Hand Circular Polarization (RHCP) continuously. A detailed description of the GPS can be found in Spilker et al. [3] or Misra and Enge et al. [4].

Figure 2.2: GNSS-R TX signal model.

The carriers modulate two types of codes, called C/A code (Coarse/Acquisition) and P code (Precise). The former is used for civil applications within the Standard Positioning Service (SPS). The latter allows access to the Precise Positioning Services (PPS), available for military purpose. These codes modulate the signal by introducing 180° phase-shifts. One of the codes is the navigation code, used to help real-time positioning. The other codes are designed to isolate the signal transmitted by one particular GPS space vehicle from the others received simultaneously which build up a Code Division Multiple Access (CDMA) scheme that spreads the band-width of the data signal and drops down its power spectral density. Each satellite accesses the transmission medium using its own pseudorandom sequence, and it can be distinguished and identified from the rest because it assigned sequences exhibits good cross-correlation properties with those of the other satellites.

These cross-correlation functions are also called waveforms, or delay maps (DM). A detailed description of cross-correlation functions can be found in Cardellach et al. [5], where we acquire the Fig.2.3 to describe the correlation function. As shown, it is an ideal triangle in amplitude units in direct propagation conditions (no reflection). The half-width of the triangle is the chip-length, which means the time interval for potential phase-shifts. For the C/A code, this is  $\sim 300$  meter. The delay of the signal is measured by either displacements of the peak of this triangle function (group delay), or more precisely by tracking the changes in the phase of the carrier. The ionospheric and lower atmospheric conditions, together with multi-path environment introduce some additional delays. When the signal reflected off the Earth surface is collected, (1) the polarization is mostly swapped, from RHCP to Left-Hand Circular Polarization (LHCP). This effect depends on the dielectric properties of the surface

**Figure 2.3:** The composition of all the DM-slices generates the Delay-Doppler Map (DDM). (Adapted from Cardellach et al. [5])

as well as geometry of the reflection; (2) the correlation function is distorted, since the diffuse scattering, the antenna collects signals reflected at the specular point as well as at other points within the surface, which add contributions to the cross-correlation function at longer delays than the specular one. The waveform is not a triangle function any more as shown in Fig.2.3, but the trailing edge decays at lower slope than the leading edge. Moreover, in certain dynamic conditions, the Doppler frequency suffered by the off-specular reflections differs significantly from the Doppler frequency at the specular point. These signals are then filtered out by the cross-correlations and coherent integration process. In those cases to retrieve the complete glistening zone, a set of cross-correlations must be performed at slightly different frequencies around the specular one, generating a Delay-Doppler Map (DDM). All these waveforms can be provided as a set of complex number (C-DM, C-DDM) given in amplitude-units, or non-coherently integrated in time to reduce the noise, given in power-units (P-DM, P-DDM).

#### 2.2.2 GOLD-RTR Instrument

The GOLD-RTR instrument [GOLD-RTR] is designed by the ICE (IEEC-CSIC). A detailed description of the GOLD-RTR can be found in [2]. Here we briefly introduce the composition of the instrument and the work principle of GOLD-RTR. As shown in Fig.2.4, the GOLD-RTR includes two parts: the RF front-end and the signal-processing back-end. The front-end is composed of three I and Q direct downconversion chains with their corresponding three antenna inputs. The local oscillator synthesizer that feeds them coherently with a common-tone down-shifted 300 KHz from L1 carrier. The system reference oscillator operates at 40 MHz, therefore, the data sample frequency is 40MHz. The back-end is composed of a one-bit A/D conversion stage that converts the three I and Q Base-Band pairs to digital and six comparators performing the sign extraction. After sampling, the bus of six

Figure 2.4: Block diagram of GOLD-RTR instrument.(Adapted from Nogués-Correig et al.[2])

base-band 1-bit signals is split into **ten** equal copies, which are input to the ten correlation channels. Each correlation channel contains 64 single-lag correlators in order to provide **64-lag** waveforms at **50 ns** spacing. The instrument has a set of 640 single-lag IQ correlators, grouped into ten 64-lag independent correlation channels that work simultaneously. The real-time signal processor computes the waveforms. A commercial GPS receiver card (Novatel) computes the navigation solution from antenna input 1. The GOLD-RTR communicates with Control PC through a full-duplex Ethernet link at 100 Mbps, using a standard Unshielded Twisted Pair (UTP) cable ended with RJ-45 connectors. An important issue is that the two down-looking antenna used to collect GPS reflected signals, and the up-looking antennas used to collect the GPS direct signals. The geometrical projection of such a baseline into the scattering direction enters, straightforward, as a relative phase between both LH and RH signals.

An important issue is that there is flexibility in the loaded signal models in order to force offset-values in delay or frequency, for both direct and reflected signals. All these features make it possible to assign different satellites to different channels, or to assign the same satellite to all the channels, but with slight differences in the frequency model to produce a Doppler/delay map (DDM), or DDM of two polarizations of a satellite signal, or other possible combinations.

# 2.2.3 Examples of GNSS-R Post-Processing Applications

Nowadays, there are many applications of the GNSS-R post-processing. These applications are applied to the different experiments, and the results put forward in the campaigns. Cardellach et al. [5] has concretely described and classified the GNSS-R applications. The GNSS-R applications tend to be classified according to the observed surface: (a) Ocean; (b) Land; and (c) Ice and Snow. Another classification

**Table 2.I:** List of the GNSS-R techniques identified in the literatures.

| Technique:                       | Bibliography:                                                                                                  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                  | GROUP-ALTIMETRY                                                                                                |

| Peak-Delay                       | Martín-Neira et al. [6] (2001)                                                                                 |

| Retracking                       | Lowe et al.[7] (2002); Ruffini et al. [8] (2004)                                                               |

| Peak-Derivative                  | Hajj and Zuffada et al. [9] (2003); Rius et al. [10] (2010)                                                    |

|                                  | PHASE-ALTIMETRY                                                                                                |

| Interferometric-beats            | Cardellach et al. [11] (2004); Helm et al. [12] (2004)                                                         |

| 5-Parameter DM Fit               | Treuhaft et al.[13](2001)                                                                                      |

| Separate Up/Down Channels        | Fabra et al. [14] (2011); Semmling et al. [15] (2011)                                                          |

|                                  | OCEAN ROUGHNESS                                                                                                |

| DM-fit                           | Garrison et al. [16] (2002); Cardellach et al. [17] (2003); Komjathy et al. [18] (2004)                        |

| Multiple-satellite DM-fit        | Komjathy et al. [18] (2004)                                                                                    |

| DDM-fit                          | Germain et al.[19](2004)                                                                                       |

| Trailing-edge                    | Zavorotny and Voronovich [20] (2000a), Garrison et al. [16] (2002)                                             |

| Delay and Doppler spread         | Elfouhaily et al.[21](2002)                                                                                    |

| Scatterometric-delay             | Nogués-Correig et al.[2](2007), Rius et al. [10](2010)                                                         |

| DDM Area/Volume                  | Marchan-Hernandez et al.[22](2008); Valencia et al.[23](2009)                                                  |

| Discrete-PDF                     | Cardellach and Rius et al.[24] (2008)                                                                          |

| Coherence-time                   | Soulat et al.[25](2004); Valencia et al.[26] (2010)                                                            |

|                                  | OCEAN PERMITTIVITY                                                                                             |

| Polarimetric-ratio               |                                                                                                                |

| POPI                             | Cardellach et al.[27](2006)                                                                                    |

|                                  | LAND                                                                                                           |

| Soil-moisture cross-polar        | Masters et al.[28](2004); Manandhar et al.[29](2006); Katzberg et al.[30] (2005); Cardellach et al. [31](2009) |

| Soil-moisture polarimetric-ratio | Zavorotny and Voronovich el at.[32](2000b), Zavorotny et al.[33](2003)                                         |

| Object-identification            | Lei-Chung et al.[34](2009)                                                                                     |

|                                  | SEA-ICE                                                                                                        |

| Permittivity by peak-power       | Komjathy et al.[35](2000); Belmonte et al.[36](2007)                                                           |

| 1st-year thickness VH-phase      | Zavorotny and Zuffada et al.[37](2002)                                                                         |

| Permittivity polarimetric ratio  |                                                                                                                |

| Permittivity POPI                | Cardellach et al.[27](2006), Cardellach et al [31](2009)                                                       |

| Sea-Ice roughness                | Belmonte et al.[36](2007)                                                                                      |

|                                  | SNOW                                                                                                           |

| Volumetric-scattering            | Wiehl et al.[38]                                                                                               |

regards the final product: (i) altimetry; (ii) roughness; (iii) permittivity parameters (such as temperature, salinity, or humidity), which determine the reflectivity level of the surface materials. Still, the observables used in the technique might also characterize the classification: (1) integrated power observables solely; or (2) high sampling complex correlation functions (amplitude and phase). Finally, we might need to distinguish between applications that require polarimetric or non-polarimetric observables. The data obtained in the experimental campaigns cover all the cases. Therefore, we focus on the applications that can be tested with the released data set, that is: applications of both integrated and complex-field observables, under categories (a) to (c), (i) to (iii), either polarimetric or not. Table 2.I summarizes the GNSS-R techniques and the reference literatures for each method.

#### **2.2.3.1** Altimetry

The altimetric techniques can in principle be applied to reflections off any surface, but their performance will depend on the signal-to-noise ratio of the scattering. Therefore, GNSS-R altimetry has only been conducted on strongly reflecting surfaces/geometries, such as waters and smooth ice, or land at near-surface receiver altitudes [39].

The altimetry aims to resolve the vertical distance between the receiver and the surface, and/or the vertical location of the specular point (with respect a reference ellipsoid/geoid). The observables to deal with are the distances between transmitter, receiver and/or surface. They can be given in the space-domain (called ranges) or in the time-domain (called delays). They are related to each other by the speed of light, and from here on we will call them range or delays indistinctly. Because the GNSS-R observations are bi-static, the way to relate the ranges with the surface level will depend on the geometry (incidence angle), as well as other systematic effects (atmospheric, instrumental, antennas set up, etc). Here we focus on the observable, that is, the altimetric range. The altimetric range is the distance traveled by the reflected signal with respect to the one traveled by the direct radio-link. When the range is measured through the delay of the code (delay of the correlation function), it tends to be called group-delay or pseudo-range. When the carrier-phase can be tracked, variations in the range can be monitored with much better precision, since an entire cycle corresponds to  $\lambda \sim 20$  cm change ( $\sim 0.5$  mm/carrier-phase degree). This latter approach is called *carrier-phase altimetry*.

#### Group-Delay Altimetry Observables

In a smooth-surface reflection event, the distance between the path traveled by the reflected signal and the path traveled by the direct link would simply correspond to the range between the peaks of the two correlation functions. Nevertheless, and since most reflections occur off rough surfaces, this approach cannot generally be used. Rius et al. [40] shows that variations in the delay of the reflected peak mostly account for changes in the surface roughness.

A few techniques have been used to identify the specular point delay in the waveform:

**Peak-Delay:** the altimetric range is taken as the peak-to-peak delay. This peak delay can be directly extracted by combining some fields provided in the data.

**Re-tracking:** which consists on fitting a theoretical model to the data. The best-fit model indicates the delay where the specular point lies.

**Peak-Derivative:** identifies the maximum of the derivative of the leading edge as the specular point delay. The peak-derivative delay can be directly extracted by combining some fields provided in the data.

# • Phase-Delay Altimetry Observables