# ΠΑΝΕΠΙΣΤΗΜΙΟ ΘΕΣΣΑΛΙΑΣ ΠΟΛΥΤΕΧΝΙΚΗ ΣΧΟΛΗ ΤΜΗΜΑ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ

Υλοποίηση και βελτιστοποίηση συνδυαστικού γραφοθεωρητικού αλγορίθμου για προσομοίωση πολύ μεγάλης κλίμακας γραμμικών κυκλωμάτων σε μαζικά παράλληλες αρχιτεκτονικές

Development and Optimization of a combinatorial multigrid algorithm for large scale circuit simulation on massively parallel architectures

Μεταπτυχιαμή Διατοιβή

Δημήτοιος Κ. Γαουφάλλου

Επιβλέποντες Καθηγητές: Νέο

Νέστως Ευμορφόπουλος Επίκουρος Καθηγητής

Γεώργιος Σταμούλης

Καθηγητής

Παναγιώτα Τσομπανοπούλου Επίκουρος Καθηγήτρια

Βόλος, Οκτώβριος 2015

## ΠΑΝΕΠΙΣΤΗΜΙΟ ΘΕΣΣΑΛΙΑΣ ΠΟΛΥΤΕΧΝΙΚΗ ΣΧΟΛΗ ΤΜΗΜΑ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ

Υλοποίηση και βελτιστοποίηση συνδυαστικού γραφοθεωρητικού αλγορίθμου για προσομοίωση πολύ μεγάλης κλίμακας γραμμικών κυκλωμάτων σε μαζικά παράλληλες αρχιτεκτονικές

## Μεταπτυχιακή Διατριβή

Δημήτριος Κ. Γαρυφάλλου

Επιβλέποντες: Νέστως Ευμορφόπουλος

Επίμουρος Καθηγητής

Γεώργιος Σταμούλης

$K\alpha\theta\eta\eta\eta\tau\dot{\eta}\varsigma$

Παναγιώτα Τσομπανοπούλου

Επίμουρος Καθηγήτρια

| Εγμοίθημε από την τοιμελή εξεταστική επιτροπή την 7η Οκτωβοίου 2015 |              |                      |  |  |

|---------------------------------------------------------------------|--------------|----------------------|--|--|

|                                                                     |              |                      |  |  |

| Ν. Ευμορφόπουλος                                                    | Γ. Σταμούλης | Π. Τσομπανοπούλου    |  |  |

| Επίμουρος Καθηγητής                                                 | Καθηγητής    | Επίμουρος Καθηγήτρια |  |  |

Μεταπτυχιακή Διατριβή για την απόκτηση του Μεταπτυχιακού διπλώματος Ειδίκευσης «Επιστήμη και Τεχνολογία Υπολογιστών, Τηλεπικοινωνιών και Δικτύων», στα πλαίσια του Προγράμματος Μεταπτυχιακών Σπουδών του Τμήματος Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών του Πανεπιστημίου Θεσσαλίας.

.....

Δημήτριος Γαρυφάλλου

Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Πανεπιστημίου Θεσσαλίας

Copyright © Dimitrios Garyfallou, 2015

Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας μεταπτυχιακής διατριβής, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της διατριβής για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

To my family and my friends  $\Sigma \tau \eta \nu \text{ οιμογένειά μου μαι στους φίλους μου}$

## Ευχαριστίες

Με την περάτωση της παρούσας μεταπτυχιακής διατριβής, θα ήθελα να ευχαριστήσω θερμά τους επιβλέποντές μου κ. Νέστορα Ευμορφόπουλο, κ. Γεώργιο Σταμούλη και κα Παναγιώτα Τσομπανοπούλου για την εμπιστοσύνη που επέδειξαν στο πρόσωπό μου με την ανάθεση του συγκεκριμένου θέματος, την άριστη συνεργασία και την συνεχή καθοδήγηση, η οποία διευκόλυνε την εκπόνηση της μεταπτυχιακής διατριβής μου.

Επίσης, θα ήθελα να ευχαριστήσω τους φίλους και συνεργάτες μου του Εργαστηρίου Ε5 για την υποστήριξη και την δημιουργία ενός ευχάριστου και δημιουργικού κλίματος και ιδιαίτερα τον Dr. Κωνσταντή Νταλούκα για τις εύστοχες υποδείξεις και την συνεχή στήριξή του.

Τέλος, οφείλω ένα μεγάλο ευχαριστώ στην οικογένειά μου και στους φίλους μου για την αμέριστη υποστήριξη και την ανεκτίμητη βοήθεια που μου παρείχαν τόσο κατά την διάρκεια των σπουδών μου όσο και κατά την εκπόνηση της μεταπτυχιακής μου διατριβής.

Δημήτριος Γαρυφάλλου

Βόλος, 2015

## **Contents**

| List of Tables                         | vi                  |

|----------------------------------------|---------------------|

| List of Figures                        | vii                 |

| List of Acronyms                       | viii                |

| Περίληψη                               | x                   |

| Abstract                               | xi                  |

| 1 Introduction                         | 1                   |

| 1.1 Motivation                         |                     |

| 1.2 Thesis Contribution                |                     |

| 1.3 Outline                            | 1                   |

| 2 Linear System Solution Methods       | 3                   |

| 2.1 Introduction                       | 3                   |

| 2.1.1 Sparsity Overview                | 3                   |

| 2.2 Overview of the Methods            | 4                   |

| 2.3 Stationary Methods                 | 5                   |

| 2.3.1 The Jacobi Method                | 5                   |

| 2.3.2 The Gauss-Seidel Method          | 6                   |

| 2.3.3 The Successive Overrelaxation    | n Method (SOR)7     |

| 2.4 Nonstationary Methods              | 8                   |

| 2.4.1 Generalized Minimal Residua      | ıl (GMRES)          |

| 2.4.2 Conjugate Gradient (CG)          | 9                   |

| 2.4.3 BiConjugate Gradient (BiCG       | <b>)</b> 10         |

| 2.5 Computational Aspects of the Me    | thods11             |

| 2.6 Multigrid Methods                  |                     |

| 3 Introduction to Preconditioners      | 13                  |

| 3.1 Introduction                       |                     |

| 3.2 Jacobi Preconditioner              | 14                  |

| 3.3 SSOR Preconditioner                | 14                  |

| 3.4 Incomplete Factorization Precond   | ditioners14         |

| 4 A Multigrid-Like SDD solver          | 17                  |

| 4.1 Support Theory for Preconditioning | ng 17               |

| 4.1.1 Electric Networks as Graphs      | - Support Basics 17 |

| 4.1.2 Steiner Preconditioners          |                     |

| 4.1.3 Predicting the performance o     | f solvers19         |

| 4.2 The Combinatorial Multigrid Solv   | zer                 |

| 4.2.1 Related work on SDD solvers      |                     |

| 4.2.2 SDD linear systems as graphs     | 3                   |

| 4.2.3 A graph decomposition algor      | ithm22              |

| 4.2.4 The Multigrid algorithm          |                     |

| 5 GPII Architecture and the CUDA Pro   | ogramming Model 25  |

Contents

| 5.1 Introduction                         | 25 |

|------------------------------------------|----|

| 5.2 Hardware Implementation              | 26 |

| 5.2.1 SIMT Architecture                  | 26 |

| 5.3 Device Memory Model                  | 27 |

| 5.3.1 Global Memory                      | 27 |

| 5.3.2 Local Memory                       | 28 |

| 5.3.3 Shared Memory                      | 28 |

| 5.3.4 Constant Memory                    | 28 |

| 5.3.5 Texture Memory                     | 29 |

| 5.4 The CUDA Programming Model           | 29 |

| 5.5 NVIDIA® TESLA <sup>TM</sup> C2075    | 30 |

| 5.5.1 Engine Specifications              | 31 |

| 5.5.2 Memory Specifications              | 31 |

| 6 Improving CMG solver performance       |    |

| 6.1 Introduction                         |    |

| 6.2 System Specifications and Benchmarks |    |

| 6.3 Implementation and Results           |    |

| 7 Conclusion                             | 39 |

| 7.1 Future Work                          | 39 |

| References                               | 41 |

## List of Tables

|     | Summary of Operations for Iteration i: " $a/b$ " $$ means " $lpha$ " multiplications with the trix and " $b$ "with its transpose, and storage requirements for the methods in iterat. |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | denotes the order of the matrix                                                                                                                                                       |    |

| 6.1 | Test platform specifications                                                                                                                                                          | 33 |

| 6.2 | IBM Power Grid Benchmarks for DC Analysis                                                                                                                                             | 33 |

| 6.3 | Matrix size and non-zero elements of the MNA arrays                                                                                                                                   | 34 |

| 6.4 | ISPD 2005/2006 Placement Benchmarks                                                                                                                                                   | 34 |

| 6.5 | CMG preconditioner-solve step runtime speedup                                                                                                                                         | 37 |

| 66  | PCG runtime sneedun                                                                                                                                                                   | 37 |

# List of Figures

| 2.1 | The Jacobi Method                                                     | 6          |

|-----|-----------------------------------------------------------------------|------------|

| 2.2 | The Gauss-Seidel Method                                               | 7          |

| 2.3 | The SOR Method                                                        | 8          |

| 2.4 | The Preconditioned GMRES(m) Method                                    | 9          |

| 2.5 | The Preconditioned Conjugate Gradient Method                          | 10         |

| 2.6 | The Preconditioned BiConjugate Gradient Method                        | 11         |

| 4.1 | A graph and its spanning tree - obtained by deleting the dashed edges | 18         |

| 4.2 | A graph and its Steiner preconditioner.                               | 19         |

|     | A bad clustering                                                      |            |

| 4.4 | Decompose Graph Algorithm                                             | 22         |

| 4.5 | Two-level Combinatorial Multigrid                                     | <b>2</b> 3 |

| 4.6 | Full Combinatorial Multigrid                                          | <b>2</b> 3 |

| 5.1 | How GPU Acceleration Works                                            | 25         |

| 5.2 | CPU vs GPU Architecture                                               | 26         |

| 5.3 | Memory Hierarchy                                                      | 27         |

| 5.4 | 2D Grid of Thread Blocks                                              | 30         |

|     | Fermi SM                                                              |            |

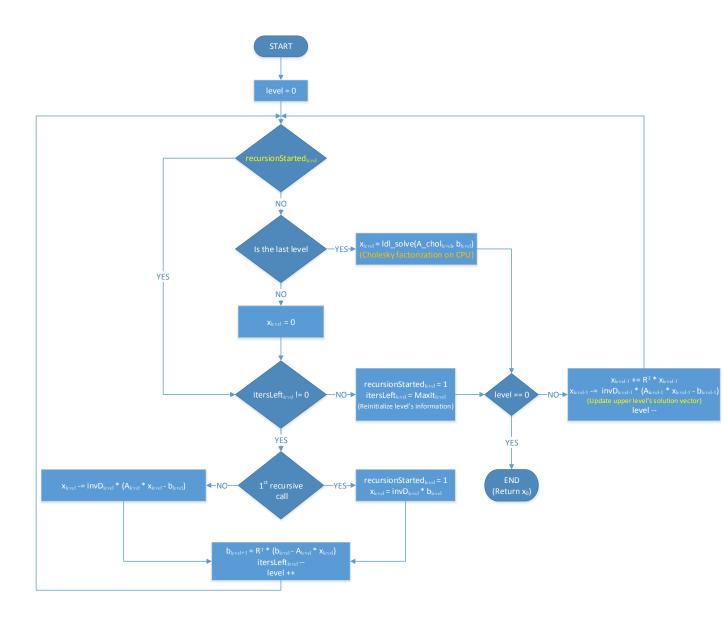

| 6.1 | CMG recursive flow                                                    | 35         |

| 62  | CMG iterative flow                                                    | 36         |

## List of Acronyms

AMG Algebraic Multigrid

**BiCG** BiConjugate Gradient

**CCS** Compressed Column Storage

**CG** Conjugate Gradient

**CMG** Combinatorial Multigrid

**COO** Coordinate

**CPU** Central Processing Unit

**CSR** Compressed Row Storage

**CUDA** Compute Unified Device Architecture

**DC** Direct Current

**DIA** Diagonal Format

**DRAM** Dynamic Random-Access Memory

**ECC** Error Checking & Correction

**EDA** Electronic Design Automation

**ELL** ELLPACK

**FLOPs** Floating-Point Operations Per second

GCC GNU Compiler Collection

**GMG** Geometric Multigrid

**GMRES** Generalized Minimal Residual

**GPGPU** General Purpose Graphics Processing Unit

**GPU** Graphics Processing Unit

**HPC** High Performance Computing

**HYB** Hybrid

**ICC** Intel C++ Compiler

**IBM** International Business Machines Corporation

IC Integrated Circuit

MG Multigrid

MNA Modified Nodal Analysis

**OP** Operating System

**NVCC** Nvidia CUDA Compiler

**PKT** Packet

**PCG** Preconditioned Conjugate Gradient

**SDD** Symmetric Diagonally Dominant

segSpMV Segmented Sparse Matrix Vector Multiplication

**SIMD** Single Instruction, Multiple Data

**SIMT** Single-Instruction Multiple-Thread

ix List of Acronyms

**SM** Streaming Multiprocessor

**SpMV** Sparse Matrix Vector Multiplication

**SOR** Successive Overrelaxation

**SSOR** Symmetric Successive Overrelaxation

**SPD** Symmetric Positive Definite

## Περίληψη

Η επίλυση γραμμικών συστημάτων της μορφής Ax = b, για συμμετρικούς πίνακες με κυρίαρχη διαγώνιο αποτελεί πρόβλημα θεμελιώδους θεωρητικής σημασίας καθώς επίσης χρησιμοποιείται σε αμέτρητες εφαρμογές στην αριθμητική ανάλυση, τη μηχανική και τις επιστήμες. Ο πρώτος αξιόπιστα αποδοτικός επιλυτής τέτοιων συστημάτων για γενικές και αυθαίρετα σταθμισμένες τοπολογίες, προτάθηκε μόλις πριν λίγα χρόνια και. Ο επιλυτής αυτός στηρίζεται στις αρχές της θεωρίας γράφων και επιτυγχάνει εξαιρετικά αποτελέσματα ενώ παράλληλα παρέχει ισχυρές εγγυήσεις για την ταχύτητα σύγκλισης.

Σκοπός μας είναι η επιτάχυνση της απόδοσης του συγκεκριμένου επιλυτή για συστήματα τα οποία εμφανίζονται στην προσομοίωση κυκλωμάτων πολύ μεγάλης κλίμακας. Οι πίνακες που εμφανίζονται σε αυτά τα μεγάλα συστήματα έχουν αραιή δομή με αποτέλεσμα οι μέθοδοι για τον αποδοτικό χειρισμό τους να είναι συχνά κρίσιμες για την επίδοση πολλών εφαρμογών συμπεριλαμβανομένης και της προσομοίωσης κυκλωμάτων. Ο συγκεκριμένος επιλυτής είναι βασισμένος σε μια από τις επαναληπτικές μεθόδους επίλυσης, η επιτάχυνσή των οποίων παραμένει πρόκληση για την επιστημονική κοινότητα. Στην παρούσα διατριβή μελετάμε τις επιπτώσεις υλοποίησης του γραφοθεωρητικού επιλυτή CMG σε μαζικά παράλληλες αρχιτεκτονικές (GPUs).

#### Λέξεις Κλειδιά:

Γραμμικά συστήματα, Προρυθμιστές, Μέθοδοι επίλυσης, Κάρτα Γραφικών, Προγραμματισμός Υψηλών Επιδόσεων

## **Abstract**

The solution of linear systems in the form Ax = b, on symmetric diagonal dominant matrices (SDDs) is a problem of fundamental theoretical importance but also one with a myriad of applications in numerical mathematics, engineering and science. The first reliably efficient SDD solver for general and arbitrary weighted topologies was first proposed in recent years. The solver is based on support theory principles and it achieves state of the art empirical results while providing robust guarantees on the speed of convergence.

Our purpose is to accelerate the performance of this solver for systems that occur in very large scale circuit simulation. Matrices that arise in those very large systems are sparse matrices, and as a result, methods for efficiently manipulating them are often crucial to the performance of many applications including circuit simulation. This solver is based on one of the iterative solution methods, which have proven to be of particular importance in computational science. This master thesis studies the implications of a CMG implementation on massively parallel architectures (GPUs).

#### **Keywords:**

Linear Systems, Preconditioners, Solution Methods, Graphics Processing Unit, High Performance Computing

## Chapter 1

## Introduction

#### 1.1 Motivation

Circuit simulation is a technique where a computer software is used to simulate the behavior of an electronic circuit or system, using mathematical models. New designs can be tested, evaluated and diagnosed without actually constructing the circuit or device. It is used across a wide spectrum of applications, ranging from integrated circuits(IC) and microelectronics to electrical power distribution networks and power electronics. Simulating a circuit's behavior before actually building it can greatly improve design efficiency by making faulty designs known as such, and providing insight into the behavior of electronics circuit designs. In particular, for integrated circuits, the tooling is expensive, breadboards are impractical, and probing the behavior of internal signals is extremely difficult. Therefore almost all integrated circuits design relies heavily on simulation.

#### 1.2 Thesis Contribution

The core of circuit simulation is based on the solution of linear systems in the form Ax = b. Those systems arise after the Modified Nodal Analysis. In Electrical Engineering, Modified Nodal Analysis or MNA is an extension of nodal analysis which not only determines the circuit's node voltages (as in classical nodal analysis), but also some branch currents [1]. Several algorithms are based on solving such sort of linear systems. The contribution of this thesis is the acceleration of the CMG solver for SDD systems that arise in circuit simulation.

Starting from a C implementation [2] of the algorithm, we ported the most time consuming part on a GPU with a view to improve the performance of the solution phase of the CMG solver. The current implementation is also based on the work have been done in my diploma thesis where we implemented a GPU kernel called segSpMV to accelerate CMG solver [3] [4]. The evaluation results showed that using our GPU implementation we can achieve CMG and PCG execution time speedups up to 10x and 5.7x over the sequential versions respectively.

For the implementation we have used the Compute Unified Device Architecture (CUDA) [5], which is an open-source programming and interfacing tool provided by NVIDIA. The GPU device used for the benchmarking is the NVIDIA® TESLA<sup>TM</sup> C2075 with 448 CUDA cores.

#### 1.3 Outline

In chapter 2 we give background material on the existing solution methods of linear systems. We begin with a review of what sparsity means and we describe the most useful sparse matrix storage. Then, we refer to stationary, nonstationary and multigrid methods.

In chapter 3 we review some basic notions of preconditioner matrices. We discuss about the importance of the preconditioning, how it is used and how it improves the convergence of the methods.

Chapter 4 provides some background material on support theory for graphs and describes the Steiner preconditioner. In the second section we give some background material on solvers and we present CMG.

In chapter 5 we present the GPU architecture and the CUDA programming model. Also, we mention the basic specifications of the NVIDIA® TESLA<sup>TM</sup> C2075.

#### 1. INTRODUCTION

In chapter 6 we present our attempt to improve the performance of CMG. Firstly, we make a brief introduction, we describe our workstation and we present our benchmarks. In the last section, we describe our implementation and we present the experimental evaluation results.

Finally, chapter 7 concludes the thesis and gives some future directions.

## Chapter 2

## **Linear System Solution Methods**

#### 2.1 Introduction

There are two broad categories of methods for solving linear equations of the form Ax = b when A is large and sparse: **direct** and **iterative**. While for some techniques such as direct solvers, we only provide brief descriptions, for iterative solvers, we go into more depth to describe the algorithms, since they are of interest to us here.

A direct method for solving the system of equations Ax = b is any method that produces the solution x after a finite number of operations. An example of a direct method is using Gaussian elimination to factor A into matrices L and U where L is lower triangular and U is upper triangular, then solving the triangular systems by forward and back substitution. Direct methods are typically preferred for dense linear systems. The problem with direct methods for sparse systems is that the amount of computational effort and storage required can be prohibitive [6].

An alternative to direct methods of solution are iterative methods, which involve the construction of a sequence  $\{x^{(i)}\}$  of approximations to the solution x, for which  $x^{(i)} \rightarrow x$ . Iterative methods for solving general, large sparse linear systems have been gaining popularity in many areas of scientific computing. Until recently, direct solution methods were often preferred to iterative methods in real applications because of their robustness and predictable behavior. However, a number of efficient iterative solvers were discovered and the increased need for solving very large linear systems triggered a noticeable and rapid shift toward iterative techniques in many applications [7]

In this master thesis we are interested only in iterative methods on sparse matrices. But before we analyze some of the most well-known, let's see what the term **sparse** refers to.

### 2.1.1 Sparsity Overview

Consider the solution of linear systems of the form

$$Ax = b, (2.1)$$

where A is an nxn matrix, and both x and b are nx1 vectors. Of special interest is the case where A is large and sparse. The term sparse above refers to the relative number of non-zeros in the matrix A. An nxn matrix A is considered to be sparse if A has only O(n) non-zero entries. In this case, the majority of the entries in the matrix are zeros, which do not have to be explicitly stored. An nxn dense matrix has  $\Omega(n^2)$  non-zeros. There are many ways of storing a sparse matrix. Whichever method is chosen, some form of compact data is required that avoids storing the numerically zero entries in the matrix. It needs to be simple and flexible so that it can be used in a wide range of matrix operations. This need is met by the primary data structure in CSparse<sup>1</sup>, a compressed-column matrix [8]. Some basic operations that operate on this data structure are matrix-vector multiplication, matrix-matrix multiplication, matrix addition, and transpose.

The simplest sparse matrix data structure is a list of the nonzero entries in arbitrary order. The list consists of two integer arrays i and j and one real array x of length equal to the number of entries in the matrix.

<sup>&</sup>lt;sup>1</sup>CSparse is a C library which implements a number of direct methods for sparse linear systems.

For example, the matrix [9]

$$A = \begin{bmatrix} 4.5 & 0 & 3.2 & 0 \\ 3.1 & 2.9 & 0 & 0.9 \\ 0 & 1.7 & 3.0 & 0 \\ 3.5 & 0.4 & 0 & 1.0 \end{bmatrix}$$

(2.2)

is presented in **zero-based triplet** form below. A zero-based data structure for an m-by-n matrix contains row and column indices in the range 0 to m-1 and n-1, respectively.

$$i = \{2, 1, 3, 0, 1, 3, 3, 1, 0, 2\}$$

$j = \{2, 0, 3, 2, 1, 0, 1, 3, 0, 2\}$

$x = \{2, 1, 3, 0, 1, 3, 3, 1, 0, 2\}$

The triplet form is simple to create but difficult to use in most sparse matrix algorithms. The **compressed-column storage** (CCS) is more useful and is used in almost all functions in CSparse. An m-by-n sparse matrix that can contain up to nzmax entries is represented with an integer array p of length n+1, an integer array i of length nzmax, and a real array i of length i[p[j+1]-1], and the corresponding numerical values are stored in i[p[j]] through i[p[j+1]-1], and the corresponding numerical values are stored in the same locations in i. The first entry i0 is always zero, and i1 is i2 in the number of actual entries in the matrix. The example matrix (2.2) is represented as

$$p = \{ 0, 3, 6, 8, 10 \}$$

$i = \{ 0, 1, 3, 1, 2, 3, 0, 2, 1, 3 \}$

$x = \{ 4.5, 3.1, 3.5, 2.9, 1.7, 0.4, 3.2, 3.0, 0.9, 1.0 \}$

One of the goals of dealing with sparse matrices is to make efficient use of the sparsity in order to minimize storage throughout the computations, as well as to minimize the required number of operations. Sparse linear systems are often solved using different computational techniques than those employed to solve dense systems.

There are many sparse matrices formats such as DIA, ELL, CSR, HYB, PKT and COO for both structure and unstructured matrices [28]. The Combinatorial Multigrid Solver is based on Compressed Column Storage (CCS) and as it is designed for symmetric matrices, we focus on the CSR format. It is easy to see that CSR is equal to CCS for symmetric matrices with the difference that we use row major storing-access.

### 2.2 Overview of the Methods

Below are short descriptions of each of the methods to be discussed, along with brief notes on the classification of the methods in terms of the class of matrices for which they are most appropriate. In later sections of this chapter more detailed descriptions of these methods are given [10].

#### • Stationary Methods

#### - Jacobi.

The Jacobi method is based on solving for every variable locally with respect to the other variables; one iteration of the method corresponds to solving for every variable once. The resulting method is easy to understand and implement, but convergence is slow.

#### - Gauss-Seidel

The Gauss-Seidel method is like the Jacobi method, except that it uses updated values as soon as they are available. In general, if the Jacobi method converges, the Gauss-Seidel method will converge faster than the Jacobi method, though still relatively slowly.

#### - SOR

Successive Overrelaxation (SOR) can be derived from the Gauss-Seidel method by introducing an extrapolation parameter  $\omega$ . For the optimal choice of  $\omega$ , SOR may converge faster than Gauss-Seidel by an order of magnitude.

#### • Nonstationary Methods

#### - Conjugate Gradient (CG).

The conjugate gradient method derives its name from the fact that it generates a sequence of conjugate (or orthogonal) vectors. These vectors are the residuals of the iterations. They are also the gradients of a quadratic functional, the minimization of which is equivalent to solving the linear system. Conjugate gradient (CG) is an extremely effective method when the coefficient matrix is symmetric positive definite (SPD), since storage for only a limited number of vectors is required.

#### - Generalized Minimal Residual (GMRES).

The Generalized Minimal Residual method computes a sequence of orthogonal vectors, and combines these through a least-squares solve and update. However, it requires storing the whole sequence, so that a large amount of storage is needed. For this reason, restarted versions of this method are used. In restarted versions, computation and storage costs are limited by specifying a fixed number of vectors to be generated. This method is useful for general nonsymmetric matrices.

#### - BiConjugate Gradient (BiCG).

The biconjugate gradient (BiCG) method generates two CG-like sequences of vectors, one based on a system with the original coefficient matrix A, and one on A<sup>T</sup>. Instead of orthogonalizing each sequence, they are made mutually orthogonal, or "bi-orthogonal". This method, like CG, uses limited storage. It is useful when the matrix is nonsymmetric and nonsingular; however, convergence may be irregular, and there is a possibility that the method will break down. BiCG requires a multiplication with the coefficient matrix and with its transpose at each iteration.

### 2.3 Stationary Methods

Iterative methods that can be expressed in the simple form

$$x^{(k)} = Bx^{(k-1)} + c, (2.3)$$

(where neither B nor c depend upon the iteration count k) are called stationary iterative methods. In this section, we present the three main stationary iterative methods: the Jacobi method, the Gauss-Seidel method and the Successive Overrelaxation (SOR) method.

### 2.3.1 The Jacobi Method

The Jacobi method is easily derived by examining each of the n equations in the linear system Ax = b in isolation. If in the i<sup>th</sup> equation

$$\sum_{j=1}^n \alpha_{i,j} x_j = b_i,$$

we solve for the value of  $x_i$  while assuming the other entries of x remain fixed, we obtain

$$x_i = \left(b_i - \sum_{j \neq i} \alpha_{i,j} x_j\right) / \alpha_{i,i} . \tag{2.4}$$

This suggests an iterative method defined by

$$x_i^{(k)} = \left(b_i - \sum_{j \neq i} \alpha_{i,j} \, x_j^{(k-1)}\right) / \alpha_{i,i} \tag{2.5}$$

which is the Jacobi method. Note that the order in which the equations are examined is irrelevant, since the Jacobi method treats them independently. For this reason, the Jacobi method is also known as the method of *simultaneous displacements*, since the updates could in principle be done simultaneously.

In matrix terms, the definition of the Jacobi method in (2.3) can be expressed as

$$x^{(k)} = D^{-1}(L+U)x^{(k-1)} + D^{-1}b, (2.6)$$

where the matrices D, -L and -U represent the diagonal, the strictly lower-triangular, and the strictly upper-triangular parts of A, respectively.

The pseudocode for the Jacobi method is given in below in Figure 2.1. Note that an auxiliary storage vector, x is used in the algorithm. It is not possible to update the vector x in place, since values from  $x^{(k-1)}$  are needed throughout the computation of  $x^{(k)}$

```

Choose an initial guess x^{(0)} to the solution x.

for k=1,2,\ldots

for i=1,2,\ldots,n

\bar{x}_i=0

for j=1,2,\ldots,i-1,i+1,\ldots,n

\bar{x}_i=\bar{x}_i+a_{i,j}x_j^{(k-1)}

end

\bar{x}_i=(b_i-\bar{x}_i)/a_{i,i}

end

x^{(k)}=\bar{x}

check convergence; continue if necessary end

```

Figure 2.1: The Jacobi Method

#### 2.3.2 The Gauss-Seidel Method

Consider again the linear equations (2.2). If we proceed as with the Jacobi Method, but now assume that the equations are examined one at a time in sequence, and the previously computed results are used as they are available, we obtain the Gauss-Seidel method pseudocode in Figure 2.2.

```

Choose an initial guess x^{(0)} to the solution x.

for k=1,2,\ldots

for i=1,2,\ldots,n

\sigma=0

for j=1,2,\ldots,i-1

\sigma=\sigma+a_{i,j}x_{j}^{(k)}

end

for j=i+1,\ldots,n

\sigma=\sigma+a_{i,j}x_{j}^{(k-1)}

end

x_{i}^{(k)}=(b_{i}-\sigma)/a_{i,i}

end

check convergence; continue if necessary end

```

Figure 2.2: The Gauss-Seidel Method

$$x_i^{(k)} = \left(b_i - \sum_{i>j} \alpha_{i,j} x_j^{(k)} - \sum_{j>i} \alpha_{i,j} x_j^{(k-1)}\right) / \alpha_{i,i}$$

(2.7)

Two important facts about the Gauss-Seidel method should be noted. First, the computations in (2.5) appear to be serial. Since each component of the new iterate depends upon all previously computed components, the updates cannot be done simultaneously as in the Jacobi method. Second, the new iterate  $x^{(k)}$  depends upon the order in which the equations are examined. The Gauss-Seidel method is sometimes called the method of successive displacements to indicate the dependence of the iterates on the ordering. If this ordering is changed, the components of the new iterate (and not just their order) will also change.

These two points are important because if *A* is sparse, the dependency of each component of the new iterate on previous components is not absolute. The presence of zeros in the matrix may remove the influence of some of the previous components. Using a judicious ordering of the equations, it may be possible to reduce such dependence, thus restoring the ability to make updates to groups of components in parallel. However, reordering the equations can affect the rate at which the Gauss-Seidel method converges. A poor choice of ordering can degrade the rate of convergence; a good choice can enhance the rate of convergence.

In matrix terms, the definition of the Gauss-Seidel method in (2.5) can be expressed as

$$x^{(k)} = (D - L)^{-1} (Ux^{(k-1)} + b)$$

(2.8)

As before D, -L and -U represent the diagonal, lower-triangular, and upper-triangular parts of A, respectively.

## 2.3.3 The Successive Overrelaxation Method (SOR)

The Successive Overrelaxation Method, or SOR, is devised by applying extrapolation to the Gauss-Seidel method. This extrapolation takes the form of a weighted average between the previous iterate and the computed Gauss-Seidel iterate successively for each component:

$$x_i^{(k)} = \omega \overline{x_i}^{(k)} + (1 - \omega) x_i^{(k-1)}.$$

(where  $\overline{x_i}$  denotes a Gauss-Seidel iterate, and  $\omega$  is the extrapolation factor). The idea is to choose a value for  $\omega$  that will accelerate the rate of convergence of the iterates to the solution.

In matrix terms, the successive overrelaxation (SOR) algorithm can be written as follows:

$$x^{(k)} = (D - \omega L)^{-1} (\omega U + (1 - \omega)D) x^{(k-1)} + \omega (D - \omega L)^{-1} b.$$

(2.9)

The pseudocode for the SOR algorithm is given above above in Figure 2.3.

```

Choose an initial guess x^{(0)} to the solution x.

for k=1,2,\ldots,n

\sigma=0

for j=1,2,\ldots,i-1

\sigma=\sigma+a_{i,j}x_j^{(k)}

end

for j=i+1,\ldots,n

\sigma=\sigma+a_{i,j}x_j^{(k-1)}

end

\sigma=(b_i-\sigma)/a_{i,i}

x_i^{(k)}=x_i^{(k-1)}+\omega(\sigma-x_i^{(k-1)})

end

check convergence; continue if necessary end

```

Figure 2.3: The SOR Method

### 2.4 Nonstationary Methods

Nonstationary methods differ from stationary methods in that the computations involve information that changes at each iteration. Typically, constants are computed by taking inner products of residuals or other vectors arising from the iterative method.

#### 2.4.1 Generalized Minimal Residual (GMRES)

The GMRES method generates a sequence of orthogonal vectors, but in the absence of symmetry this can no longer be done with short recurrences; instead, all previously computed vectors in the orthogonal sequence have to be retained. For this reason are used restarted versions of the method. GMRES algorithm has the property that residual norm  $\|b - Ax_i\|$  can be computed without the iterate having been formed. Thus, the expensive action of forming the iterate can be postponed until the residual norm is deemed small enough. The GMRES iterates are constructed as:

$$x^{i} = x^{0} + y_{1}u^{1} + \dots + y_{i}u^{i}, \tag{2.10}$$

The GMRES method retains orthogonality of the residuals by using long recurrences, at the cost of a larger storage demand.

The pseudocode for the restarted GMRES algorithm with preconditioner M is given in Figure 2.4.

```

x^{(0)} is an initial guess

for j = 1, 2, ....

Solve r from Mr = b - Ax^{(0)}

v^{(1)} = r/||r||_2

s := ||r||_2 e_1

for i = 1, 2, ..., m

Solve w from Mw = Av^{(i)}

for k = 1, ..., i

h_{k,i} = (w, v^{(k)})

w = w - h_{k,i}v^{(k)}

h_{i+1,i} = ||w||_2

v^{(i+1)} = w/h_{i+1,i}

apply J_1, ..., J_{i-1} on (h_{1,i}, ..., h_{i+1,i})

construct J_i, acting on ith and (i + 1)st component

of h_{.,i}, such that (i+1)st component of J_i h_{.,i} is 0

s := J_i s

if s(i+1) is small enough then (UPDATE(\tilde{x}, i) and quit)

end

UPDATE(\tilde{x}, m)

end

In this scheme UPDATE(\tilde{x}, i)

replaces the following computations:

Compute y as the solution of Hy = \tilde{s}, in which

the upper i \times i triangular part of H has h_{i,j} as

its elements (in least squares sense if H is singular),

\tilde{s} represents the first i components of s

\tilde{x} = x^{(0)} + y_1 v^{(1)} + y_2 v^{(2)} + ... + y_i v^{(i)}

s^{(i+1)} = ||b - A\tilde{x}||_2

if \tilde{x} is an accurate enough approximation then quit

else x^{(0)} = \tilde{x}

```

Figure 2.4: The Preconditioned GMRES(m) Method

## 2.4.2 Conjugate Gradient (CG)

The Conjugate Gradient method is an effective method for symmetric positive definite systems. It is the oldest and best known of the nonstationary methods discussed here. The method proceeds by generating vector sequences of iterates (*i.e.*, successive approximations to the solution), residuals corresponding to the iterates, and search directions used in updating the iterates and residuals. Although the length of these sequences can become large, only a small number of vectors needs to be kept in memory. In every iteration of the method, two inner products are performed in order to compute update scalars that are defined to make the sequences satisfy certain orthogonality conditions. On a symmetric positive definite linear system these conditions imply that the distance to the true solution is minimized in some norm.

The pseudocode for the Preconditioned Conjugate Gradient (PCG) Method is given below in Figure 2.5. It uses a preconditioner M; for M = I one obtains the unpreconditioned version of the Conjugate Gradient Algorithm.

```

Compute r^{(0)} = b - Ax^{(0)} for some initial guess x^{(0)} for i=1,2,\ldots solve Mz^{(i-1)} = r^{(i-1)} \rho_{i-1} = r^{(i-1)^T}z^{(i-1)} if i=1 p^{(1)} = z^{(0)} else \beta_{i-1} = \rho_{i-1}/\rho_{i-2} p^{(i)} = z^{(i-1)} + \beta_{i-1}p^{(i-1)} endif q^{(i)} = Ap^{(i)} \alpha_i = \rho_{i-1}/p^{(i)^T}q^{(i)} x^{(i)} = x^{(i-1)} + \alpha_i p^{(i)} r^{(i)} = r^{(i-1)} - \alpha_i q^{(i)} check convergence; continue if necessary end

```

Figure 2.5: The Preconditioned Conjugate Gradient Method

### 2.4.3 BiConjugate Gradient (BiCG)

The Conjugate Gradient method is not suitable for nonsymmetric systems because the residual vectors cannot be made orthogonal with short recurrences. The GMRES method retains orthogonality of the residuals by using long recurrences, at the cost of a larger storage demand. The BiConjugate Gradient method takes another approach, replacing the orthogonal sequence of residuals by two mutually orthogonal sequences, at the price of no longer providing a minimization.

The update relations for residuals in the Conjugate Gradient method are augmented in the BiConjugate Gradient method by relations that are similar but based on  $A^T$  instead of A. The pseudocode for the Preconditioned BiConjugate Gradient Method with preconditioner M is given in the top of the next page in Figure 2.6.

```

Compute r^{(0)} = b - Ax^{(0)} for some initial guess x^{(0)}.

Choose \tilde{r}^{(0)} (for example, \tilde{r}^{(0)} = r^{(0)}).

for i = 1, 2, ...

solve Mz^{(i-1)} = r^{(i-1)}

solve M^T \tilde{z}^{(i-1)} = \tilde{r}^{(i-1)}

\rho_{i-1} = z^{(i-1)^T} \tilde{r}^{(i-1)}

if \rho_{i-1} = 0, method fails

if i = 1

p^{(i)} = z^{(i-1)}

\tilde{p}^{(i)} = \tilde{z}^{(i-1)}

else

\begin{array}{l} \beta_{i-1} = \rho_{i-1}/\rho_{i-2} \\ p^{(i)} = z^{(i-1)} + \beta_{i-1}p^{(i-1)} \\ \tilde{p}^{(i)} = \tilde{z}^{(i-1)} + \beta_{i-1}\tilde{p}^{(i-1)} \end{array}

endif

q^{(i)} = Ap^{(i)}

\tilde{q}^{(i)} = \tilde{A}^T \tilde{p}^{(i)}

\alpha_i = \rho_{i-1}/\tilde{p}^{(i)^T} q^{(i)}

x^{(i)} = x^{(i-1)} + \alpha_i p^{(i)}

r^{(i)} = r^{(i-1)} - \alpha_i q^{(i)}

\tilde{r}^{(i)} = \tilde{r}^{(i-1)} - \alpha_i \tilde{q}^{(i)}

check convergence; continue if necessary

end

```

Figure 2.6: The Preconditioned BiConjugate Gradient Method

### 2.5 Computational Aspects of the Methods

Efficient solution of a linear system includes the selection of the proper choice of iterative method. However, to obtain good performance, consideration must also be given to the computational kernels of the method and how efficient they can be executed on the target architecture. The performance of direct methods, is largely that of the factorization of the matrix. However, this lower efficiency of execution does not imply anything about the total solution time for a given system. Furthermore, iterative methods are usually simpler to implement than direct methods, and since no full factorization has to be stored, they can handle much larger systems than direct methods. Table 2.1 lists the type of operations performed per iteration and the storage required for each method (without preconditioning).

| Method          | Inner<br>Product | SAXPY | Matrix-Vector<br>Product | Precond<br>Solve | Storage<br>Requirements |

|-----------------|------------------|-------|--------------------------|------------------|-------------------------|

| JACOBI          |                  |       | $1^{\alpha}$             |                  | Matrix + 3n             |

| Gauss<br>Seidel |                  | 1     | $1^{\alpha}$             |                  |                         |

| SOR             |                  | 1     | $1^{\alpha}$             |                  | Matrix + 2n             |

| GMRES           | i+1              | i+1   | 1                        | 1                | Matrix + (i+5)n         |

| CG              | 2                | 3     | 1                        | 1                | Matrix + 6n             |

| BiCG            | 5                | 5     | 1/1                      | 1/1              | Matrix + 10n            |

Table 2.1: Summary of Operations for Iteration i: " $\alpha/b$ " means " $\alpha$ " multiplications with the matrix and "b" with its transpose, and storage requirements for the methods in iteration i: n denotes the order of the matrix.

## 2.6 Multigrid Methods

Before closing this chapter we would like to discuss about the multigrid (MG) methods. MG methods in numerical analysis is defined as a group of algorithms for solving differential equations using a hierarchy of discretizations. They are an example of a class of techniques called multiresolution methods, very useful in problems exhibiting multiple scales of behavior. For example, many basic relaxation methods exhibit different rates of convergence for short-and long-wavelength components, suggesting these different scales be treated differently, as in a Fourier analysis approach to multigrid. MG methods can be used as solvers as well as preconditioners.

The main idea of MG is to accelerate the convergence of a basic iterative method by global correction from time to time, accomplished by solving a coarse problem<sup>2</sup>. This principle is similar to interpolation between coarser and finer grids. The typical application for multigrid is in the numerical solution of elliptic partial differential equations in two or more dimensions.

Multigrid can be applied in combination with any of the common discretization techniques.MG methods are among the fastest solution techniques known today. In contrast to other methods, multigrid methods are general in that they can treat arbitrary regions and boundary conditions. They do not depend on the separability of the equations or other special properties of the equation.

-

<sup>&</sup>lt;sup>2</sup> Coarse problem is an auxiliary system of equations used in an iterative method for the solution of a given larger system of equations. It is basically a version of the same problem at a lower resolution, retaining its essential characteristics, but with fewer variables.

## Chapter 3

## Introduction to Preconditioners

#### 3.1 Introduction

In chapter 2 we discussed about many iterative methods. The convergence rate of iterative methods depends on spectral properties of the coefficient matrix. Hence one may attempt to transform the linear system into one that is equivalent in the sense that it has the same solution, but that has more favorable spectral properties. A *preconditioner* is a matrix that effects such a transformation. For SPD systems, the rate of convergence of the conjugate gradient method depends on the distribution of the eigenvalues of A. The purpose of preconditioning is that the transformed matrix in question will have a smaller spectral condition number, and/or eigenvalues clustered around 1. For nonsymmetric problems the situation is more complicated, and the eigen-values may not describe the convergence of nonsymmetric matrix iterations like GMRES. On parallel machines there is a further tradeoff between the efficacy of a preconditioner in the classical sense, and its parallel efficiency. Many of the traditional preconditioners have a large sequential component.

If M is a nonsingular matrix that approximates A, then the linear system (3.1) has the same solution as (2.1) but must be significantly easier to solve.

$$M^{-1}Ax = M^{-1}b, (3.1)$$

$$AM^{-1}y = b, x = M^{-1}y (3.2)$$

$$M_1^{-1}AM_2^{-1}y = M_1^{-1}b, x = M_2^{-1}y$$

(3.3)

The system (3.1) is preconditioned from the left, (3.2) is preconditioned from the right. At (3.3) is performed split preconditioning where the preconditioner is M = M1M2.

Iterative algorithms such as the Conjugate Gradient method, converge to a solution using only matrix-vector products with A. It is well known that iterative algorithms suffer from slow convergence properties when the condition number of A,  $\kappa(A)$ , which is defined as the ration of the largest over the minimum eigenvalue of A, is large. What preconditioned iterative methods attempt to do is to remedy the problem by changing the linear system to  $M^{-1}Ax = M^{-1}b$ . In this case, the algorithms use matrix-vector products with A, and solve linear systems of the form My = z. So now the speed of convergence depends on the **condition number**  $\kappa(A, M)$ .

The condition number is defined as:

$$\kappa(A, M) = \max_{x} \frac{x^{T} A x}{x^{T} M x} \cdot \max_{x} \frac{x^{T} M x}{x^{T} A x}.$$

(3.4)

where x is taken to be outside the null space of A. There are two contradictory goals one has to deal in constructing a preconditioner M: (i) The linear systems in M must be easier than those in A to solve, (ii) The condition number must be small so it will minimize the number of iterations.

Historically, preconditioners were natural parts of the matrix A. We analyze some of the most well-known preconditioners below.

### 3.2 Jacobi Preconditioner

The simplest preconditioner consists of just the diagonal of the matrix

$$m_{i,j} = \begin{cases} \alpha_{i,i}, & \text{if } i = j \\ 0, & \text{otherwise} \end{cases}$$

This is known as the (point) Jacobi preconditioner.

For the model problem,  $\kappa(B^{-1}A) = O(n) = \kappa(A)$ , so the asymptotic rate of convergence is not improved with diagonal scaling. B in this case does not need to be factored. The storage required for the preconditioner is O(n) since it is a sparse matrix. And, the preconditioner system is very easy to solve, since it simply requires dividing each vector entry by the corresponding diagonal entry of B.

Even through the asymptotic rate of convergence is not improved, diagonal scaling can sometimes make the difference between convergence and non-convergence for an ill-conditioned matrix A. Moreover, diagonal scaling generally achieves some reduction in the number of iterations, and is so cheap to apply that it might as well be done.

#### 3.3 SSOR Preconditioner

Another example of a preconditioner is the SSOR preconditioner which like the Jacobi preconditioner, can be easily derived from the coefficient matrix without any work.

Assume we have a symmetric matrix A. If this matrix is decomposed as

$$A = D + L + L^T$$

in its diagonal, lower, and upper triangular part, the SSOR matrix is defined as

$$M = (D + L)D^{-1}(D + L)^{T}$$

or, parametrized by  $\omega$

$$M(\omega) = \frac{1}{2-\omega} \left(\frac{1}{\omega}D + L\right) \left(\frac{1}{\omega}D\right)^{-1} \left(\frac{1}{\omega}D + L\right)^{T}.$$

The SSOR matrix is given in factored form, so this preconditioner shares many properties of other factorization-based methods. For example, its suitability for vector processors or parallel architectures depends strongly on the ordering of the variables.

## 3.4 Incomplete Factorization Preconditioners

A broad class of preconditioners is based on incomplete factorizations of the coefficient matrix. We call a factorization incomplete if during the factorization process certain fill elements, nonzero elements in the factorization in positions where the original matrix had a zero, have been ignored. Such a preconditioner is then given in factored form M + LU with L lower and U upper triangular. The efficacy of the preconditioner depends on how well  $M^{-1}$  approximates  $A^{-1}$ .

When a sparse matrix is factored by Gaussian elimination, fill-in usually takes place. In that case, sparsity-preserving pivoting techniques can be used to reduce it. The triangular factors L and U of the coefficient matrix A are considerably less sparse than A.

Sparse direct methods are not considered viable for solving very large linear systems due to time and space limitations, however, by discarding part of the fill-in in the course of the factorization process, simple but powerful preconditioners can be obtained in the form M = LU where L and U are the incomplete (approximate) LU factors.

Summarizing, it can be said that existing solutions to the problem for incomplete factorization preconditioners for general SPD matrices follow one of two cases: simple inexpensive fixes that result in low quality preconditioners in terms of convergence rating, or sophisticated, expensive strategies that produce high quality preconditioners.

## Chapter 4

## A Multigrid-Like SDD solver

In this chapter we give some background material on support theory of preconditioning and we describe the CMG, the solver that we studied and tried to optimize. The CMG solver was proposed by I. Koutis and Gary Miller and is characterized by the form of the preconditioner [11] [12]. The first implementation was in MATLAB [13] and later it transformed into C code. The basis of our implementation is the C code of the CMG solver [2] [3].

### 4.1 Support Theory for Preconditioning

The main goal of the support theory is to provide techniques to bound the generalized eigenvalues and condition number for a matrix pencil (A, B) where B is a preconditioner for A. In this section we review fragments of support theory that are relevant to the design of the CMG. We refer the reader to [14] for an extensive explosion of support theory.

### 4.1.1 Electric Networks as Graphs – Support Basics

The cornerstone of combinatorial preconditioners is the following intuitive yet paradigm-shifting idea explicitly proposed by Vaidya [15]: A preconditioner for the Laplacian of a graph A should be the Laplacian of a simpler graph B, derived in a principled fashion from A.

There is a fairly well known analogy between graph Laplacians and resistive networks [16]. If G is seen as an electrical network with the resistance between nodes i and j being  $1/w_{i,j}$ , then in the equation Av = i, if vis the vector of voltages at the node, i is the vector of currents. Also, the quadratic form  $v^T Av = \sum_{i,j} w_{i,j} (v_i - v_j)^2$  expresses the **power dissipation** on G, given the node voltages v. In view of this, the construction of a good preconditioner B amounts to the construction of a simpler resistive network (for example by deleting some resistances) with an energy profile close to that of A.

The **support** of A by B, defined as  $\sigma(A/B) = max_v \frac{v^T A v}{v^T B v}$  is the number of copies of B that are needed to support the power dissipation in A, for all settings of voltages. The principal reason behind the introduction of the notion of support, is to express its local nature, captured by the Splitting Lemma.

**Lemma 4.1 (Splitting Lemma)** If  $A = \sum_{i=1}^{m} A_i$  and  $B = \sum_{i=1}^{m} B_i$  where  $A_i$ ,  $B_i$  are Laplacians, then  $\sigma(A, B) \leq \max_i \sigma(A_i, B_i)$

The Splitting Lemma allows us to bound the support of A by B, by splitting the power dissipation in A into small local pieces, and "supporting" them by also local pieces in B.

For example, in his work Vaidya proposed to take B as the maximal weight spanning tree of A. Then, it is easy to show that  $\sigma(B,A) \leq 1$ , intuitively because more resistances always dissipate more power. In order to bound  $\sigma(A,B)$ , the basic idea to let the  $A_i$  be edges on A(the ones not existing in B), and let  $B_i$  be the unique path in the tree that connects the two endpoints of  $A_i$ . Then one can bound separately each  $\sigma(A_i,B_i)$ . In fact, it can be shown that any edge in A that doesn't exist in B, can be supported only by the path  $B_i$ .

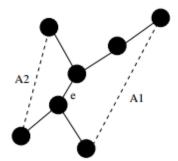

As an example, consider the example in Figure 4.1 of the two (dashed) edges *A1*, *A2* and their two paths in the spanning tree (solid) that share one edge "e".

In this example, the **dilation** of the mapping is equal to 3, i.e. the length of the longest of two paths. Also, as "e" is uses two times, we say that the **congestion** of the mapping is equal to 2. A core Lemma in Support Theory [14] [17] is that the support can be upper bounded by the product **congestion** \* **dilation**.

Figure 4.1: A graph and its spanning tree - obtained by deleting the dashed edges

#### 4.1.2 Steiner Preconditioners

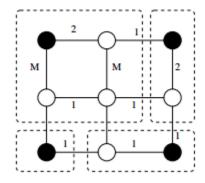

Steiner preconditioners, introduced in [18] and extended [19] introduce external nodes into preconditioners. The proposed preconditioner is based on a partitioning of the n vertices in V into m vertex disjoint clusters  $V_i$  For each  $V_i$ , the preconditioner contains a star graph  $S_i$  with leaves corresponding to the vertices in  $V_i$  rooted at a vertex  $r_i$ . The roots  $r_i$  are connected and form the **quotient** graph Q. This general setting is illustrated in Figure 4.2 at next page.

Let D' be the total degree of the leaves in the Steiner preconditioner S. Let the **restriction** R be an  $n \times m$  matrix, where R(i,j) = 1 if vertex i is in cluster j and 0 otherwise. Then, the Laplacian of S has n + m vertices, and the algebraic form

$$S = \begin{pmatrix} D' & -D'R \\ -R^TD' & Q + R^TD'R \end{pmatrix}. \tag{4.1}$$

A troublesome feature of the Steiner preconditioner S is the extra number of dimensions/vertices. Gremban and Miller [18] proposed that every time a system of the form Bz = y is solved in a usual preconditioned method, the system

$$S\begin{pmatrix} z \\ z' \end{pmatrix} = \begin{pmatrix} y \\ 0 \end{pmatrix}$$

should be solved instead, for a set of **don't care** variables z'. They also showed that the operation is equivalent to preconditioning with the dense matrix

$$B = D' - V(Q + D_Q)^{-1}V^T (4.2)$$

where V = D'R and  $D_Q = R^T D'R$ . The matrix B is called the Schur complement of S with respect to the elimination of the roots  $r_i$ . It is a well-known fact that B is also a Laplacian.

The analysis of the support  $\sigma(A/S)$ , is identical to that for the case of subgraph preconditioners. For example, going back to Figure 4.2 the edge (v1, v4) can only be supported by the path (v1, r1, v4), and the edge (v4, v7) only by the path (v4, r1, r2, v7). Similarly we can see the mappings from edges in A to paths in S for every edge in A. In the example, the **dilation** of the mapping is 3, and it can be seen that to minimize the **congestion**

on every edge of S (i.e. make it equal to 1), we need to take D' = D, where D are the total degrees of the nodes in A, and w(r1, r2) = w(v3, v5) + w(v4, v7). More generally, for two roots  $r_i, r_j$  we should have

$$w(r_i, r_j) = \sum_{i' \in V_i, j' \in V_j} w_{i,j}.$$

Under this construction, the algebraic form of the quotient Q can be seen to be  $Q = R^T A R$ .

In [19] it was shown that the support  $\sigma(S/A)$  reduces to bounding the support  $\sigma(Si, A[V_i])$ , for all i, where  $A[V_i]$  denotes the graph induced in A by the vertices  $V_i$ . The key behind bounding  $\sigma(Si, A[V_i])$  is called **conductance**. Let us give the definition of conductance.

**Definition 4.1** The conductance  $\Phi(A)$  of a graph A = (V, E, w) is defined as

$$\Phi(A) = min_{S \subseteq V} \frac{w(S, V - S)}{min(w(S), w(V - S))}$$

where W(S, V - S) denotes the total weight connecting the sets S and V - S, and where W(S) denotes the total weight incident to the vertices in S.

The main result of [19] is captured by the following Theorem.

Theorem 4.1 The support  $\sigma(S/A)$  is bounded by a constant c independent from n, if and only if for all i the conductance of the graph  $A^0[V_i]$  induced by the nodes in  $V_i$  augmented by the edges leaving  $V_i$  is bounded by a constant c'.

Figure 4.2: A graph and its Steiner preconditioner.

### 4.1.3 Predicting the performance of solvers

Theorem 4.1 doesn't give a way to pick clusters, but it does provide a way to avoid bad clustering. In recent work [20], Grady proposed a multigrid method where the construction of the "coarse" grid follows exactly the construction of the **quotient** graph in the previous section. Specifically, Grady's algorithm proposes a clustering such that every cluster contains exactly one pre-specified 'coarse' nodes. It then defines the restriction matrix R and he lets the coarse grid be  $Q = R^T A R$ , identically to the construction of the previous Section. The algorithm is iterated to construct a hierarchy of grids. The question then is whether the proposed clustering provides the guarantees that by Theorem 4.1 are necessary for the construction of a good Steiner preconditioner. The following Figure, is the Figure 2 of [20], with a choice of weights that force the depicted clustering.

*Figure 4.3: A bad clustering.*

Every cluster in Figure 4.3 contains exactly one black/coarse node. The problem with the clustering is that the top left cluster, has a very low conductance when  $M \gg 1$ . In general, in order to satisfy the requirement of the previous Theorem, there are cases where the clustering has to contain clusters with no coarse nodes in them. As we will discuss in later the behavior of the multigrid algorithm proposed in [20] is closely related to the quality of the Steiner preconditioner induced by the clustering. This implies that the multigrid of [20] can suffer bad convergence.

The canonical clustering in Grady's algorithm is very suitable for GPU implementations, when other solvers may be less suitable. This gives to it an advantage on this type of hardware. Even in the presence of a number of relatively bad clusters, it can be faster relative to a solver that uses better clusters. However the advantage is lost when the computed clusters cross a negative threshold in quality, a threshold that depends on several hardware-dependent factors. The value of Support Theory is evident in this case. Grady's algorithm can be instrumented with a very fast routine that measures the quality of the formed clusters and predicts its performance, and reverts to another solver when needed. One can also imagine hybrid clustering algorithms where the majority clusters are formed using the algorithm [20] and the 'sensitive' parts of the system are treated separately.

### 4.2 The Combinatorial Multigrid Solver

The present chapter describes the Combinatorial Multigrid Solver (CMG). At the beginning, we give a short review of multigrid solvers and then we describe the basic components of CMG.

#### 4.2.1 Related work on SDD solvers

Multigrid was originally conceived as a method to solve linear systems that are generated by the discretization of the Laplace (Poisson) equation over relatively nice domains [21]. The underlying geometry of the domain leads to a hierarchy of grids  $A = A_0, \ldots, A_d$  that look similar at different levels of detail; the picture that the word multigrid often invokes to mind is that of a tower of 2D grids, with sizes  $2^{d-i} \times 2^{d-i}$  for  $i = 0, \ldots, d$ . Its provably asymptotically optimal behavior for certain classes of problems soon lead to an effort, known as Algebraic Multigrid (AMG), to generalize its principles to arbitrary matrices. In contrast to classical Geometric Multigrid (GMG) where the hierarchy of grids is generated by the discretization process, AMG constructs the hierarchy of "coarse" grids/matrices based only on the algebraic information contained in the matrix. Various flavors of AMG, based on different heuristic coarsening strategies, have been proposed in the literature. AMG has been proven successful in solving more problems than GMG, though sometimes at the expense of robustness, a by-product of the limited theoretical understanding.

A solver with provable properties for arbitrary SDD matrices, perhaps the "holy grail" of the multigrid community, was discovered only recently. The path to it was Support Theory [14], a set of mathematical tools developed for the study of combinatorial subgraph preconditioners, originally introduced by Vaidya [15] [22]. It has been at the heart of the seminal work of Spielman and Teng [23] who proved that SDD systems can be solved in nearly-linear time. Koutis and Miller [24] proved that SDD matrices with planar connection topologies (e.g. 4-

connectivity in the image plane) can be solved asymptotically optimally, in O(n) time for n-dimensional matrices. The complexity of the Spielman and Teng solver was recently significantly improved by Koutis, Miller and Peng [25] [26], who described an O(mlogn) algorithm for the solution of general SDD systems with m non-zero entries.

It is fair to say that these theoretically described solvers are still impractical due to the large hidden constants, and the complicated nature of the underlying algorithms. Combinatorial Multigrid (CMG) [11] is a variant of multigrid that reconciles theory with practice. Similarly to AMG, CMG builds a hierarchy of matrices/graphs. The essential difference from AMG is that the hierarchy is constructed by viewing the matrix as a graph, and using the discrete geometry of the graph, for example notions like graph separators and expansion. It is, in a way, a hybrid of GMG and AMG, or a discrete-geometric MG. The re-introduction of geometry into the problem allows us to prove sufficient and necessary conditions for the construction of a good hierarchy and claim strong convergence guarantees for symmetric diagonally dominant (SDD) matrices based on recent progress in Steiner preconditioning [18] [19] [22].

### 4.2.2 SDD linear systems as graphs

In this subsection we discuss how SDD linear systems can be viewed entirely as graphs. Combinatorial preconditioning advocates a principled approach to the solution of linear systems. The core of CMG and all other solvers designed in the context of combinatorial preconditioning is in fact a solver for a special class of matrices, graph Laplacians. The **Laplacian** A of a graph G = (V, E, w) with positive weights, is defined by:

$$A_{i,j} = A_{j,i} = -w_{i,j} \wedge A_{i,i} = -\sum_{i \neq j} A_{i,j}$$

More general systems are solved via light-weight transformations to Laplacians. Consider for example the case where the matrix A has a number of positive off-diagonal entries, and the property  $A_{i,i} = \sum_{i \neq j} |A_{i,j}|$ . Positive off-diagonal entries have been a source of confusion for AMG solvers, and various heuristics have been proposed. Instead, CMG uses a reduction known as double-cover [18]. Let A = Ap + An + D, where D is the diagonal of A and Ap is the matrix consisting only of the positive off-diagonal entries of A. It is easy to verify that

$$Ax = b \iff \begin{pmatrix} D + A_n & -A_p \\ -A_n & D + A_n \end{pmatrix} \begin{pmatrix} x \\ -x \end{pmatrix} = \begin{pmatrix} b \\ -b \end{pmatrix}$$

In this way, the original system is reduced to a Laplacian system, while at most doubling the size. In practice it is possible to exploit the obvious symmetries of the new system, to solve it with an even smaller space and time overhead.

Matrices of the form  $A + D_e$ , where A is a Laplacian and  $D_e$  is a positive diagonal matrix have also been addressed in various ways by different AMG implementations. In CMG, we again reduce the system to a Laplacian. If  $d_e$  is the vector of the diagonal elements of D, we have

$$Ax = b \Leftrightarrow \begin{pmatrix} A + D_e & 0 & -d_e \\ 0 & A + D_e & -d_e \\ 0 & -d_e^T & \sum_i d_e(i) \end{pmatrix} \begin{pmatrix} x \\ -x \\ 0 \end{pmatrix} = \begin{pmatrix} b \\ -b \\ 0 \end{pmatrix}$$

Again it's possible to implement the reduction in a way that exploits the symmetry of the new system, and with a small space and time overhead work only implicitly with the new system.

A symmetric matrix A is called diagonally dominant (SDD), if  $A_{i,i} \ge \sum_{i \ne j} |A_{i,j}|$ . The two reductions above can reduce any SDD linear system to a Laplacian system. Symmetric positive definite matrices (SPD) with non-positive off-diagonals are known as M-matrices. It is well known that if A is an M-matrix, there is a positive diagonal matrix D such that A = DLD where

L is a Laplacian. Assuming D is known, an M-system can also be reduced to a Laplacian system via a simple change of variables. In many application D is given, or it can be recovered with some additional work [23].

There is a one-to-one correspondence between Laplacians and graphs, so we will be often using the terms interchangeably.

## 4.2.3 A graph decomposition algorithm

The crucial step for the construction of a good Steiner preconditioner is the computation of a group decomposition that satisfies, as best as possible, the requirements of Theorem 4.1. Before the presentation of the **Decompose-Graph** algorithm, that extends the ideas of [19], we need to introduce a couple of definitions. Let volG(v) denote the total weight incident to node v in graph G. The weighted degree of a vertex v is defined as the ratio

$$wd(v) = \frac{vol(v)}{max_{u \in N(v)}w(u, v)}$$

The average weighted degree of the graph is defines as

$$awd(G) = \left(\frac{1}{n}\right) \sum_{y \in N} wd(y).$$

#### Algorithm 7 Algorithm Decompose Graph.

- 1: Algorithm Decompose Graph

- 2:

- 3: Input: Graph A = (V, E, w)

- 4: Output: Disjoint Clusters  $V_i$  with  $V = \bigcup_i V_i$

- 5: Let  $W \subseteq V$  be the set of nodes satisfying  $wd(v) > \kappa \cdot awd(A)$ , for some constant  $\kappa > 4$ .

- 6: Form a forest graph F, by keeping the heaviest incident edge of v for each vertex  $v \in V$  in A.

- 7: For every vertex  $w \in W$  such that  $vol_T(w) < vol_G(w)/awd(A)$  remove from F the edge contributed by w in Step 2.

- 8: Decompose each tree T in F into vertex-disjoint trees of constant conductance.

Figure 4.4: Decompose Graph Algorithm

It is not very difficult to prove that the algorithm **Decompose-Graph** presented in Figure 4.4 produces a partitioning where the conductance of each cluster depends only on awd(A) and the constant  $\kappa$ . In fairly general sparse topologies that allow high degree nodes, awd(A) is constant and the number of clusters m returned by the algorithm is such that n/m > 2 (and in practice larger than 3 or 4).

#### 4.2.4 The Multigrid algorithm

In this subsection we outline the intuition behind Steiner preconditioners and multigrid. Details and proofs can be found in [22]. Algebraically, any of the classic preconditioned iterative methods, such as the Jacobi and Gauss-Seidel iteration, is nothing but a matrix S, which gets applied implicitly to the current error vector e, to produce a new error vector e' = Se. For example, in the Jacobi iteration we have  $S = (I - D^{-1}A)$ . This has the effect that it reduces effectively only part of the error in a given iterate, namely the components that lie in the low eigenspaces of S (usually referred to as high frequencies of A). The main idea behind a two-level multigrid is that the current smooth residual error r = b - Ax, can be used to calculate a correction  $R^T Q^{-1}Rr$ , where Q is a smaller graph and R is an  $m \times n$  restriction

operator. The correction is then added to the iterate x. The hope here is that for smooth residuals, the low-rank matrix  $R^TQ^{-1}Rr$  is a good approximation of  $A^{-1}$ . Algebraically, this correction is the application of the operator  $T = (I - R^TQ^{-1}RA)$  to the error vector  $\mathbf{e}$ . The choice of Q is most often not independent from that of  $\mathbf{R}$ , as the *Galerkin condition* is employed:

$$Q = RAR^T$$

The Galerkin condition ensures that T is a projection operator with respect to the A-inner product. Two level convergence proofs are then based on bounds on the angle between the subspace Null(P) and the high frequency subspace of S.

At a high level, the key idea behind CMG is that the provably small condition number  $\kappa(A, B)$  where B is given in expression 4.2, is equal to the condition number  $\kappa(\hat{A}, \hat{B})$  where  $\hat{A} = D^{-1/2}AD^{-1/2}$  and  $\hat{B} = D^{-1/2}BD^{-1/2}$ . This in turn implies a bound on the angle between the low frequency of  $\hat{A}$  and the high frequency of  $\hat{B}$  [19]. The latter subspace is  $Null(R^TD^{1/2})$ . This fact suggests to choose  $R^TD^{1/2}$  as the projection operator while performing relaxation with  $(I - \hat{A})$  on the system  $\hat{A}y = D^{-1/2}b$ , with  $y = D^{1/2}x$ . Combining everything, we get the following two-level algorithm in Figure 4.5.

```

Two-level Combinatorial Multigrid

Input: Laplacian A = (V, E, w), vector b, approximate solution x, n \times m restriction matrix R

Output: Updated solution x for Ax = b

1. D := diag(A); \hat{A} := D^{-1/2}AD^{-1/2};

2. z := (I - \hat{A})D^{1/2}x + D^{-1/2}b;

3. r := D^{-1/2}b - \hat{A}z; w := RD^{1/2}r;

4. Q := RAR^T; Solve Qy = w;

5. z := z + D^{1/2}R^Ty

6. x := D^{-1/2}((I - \hat{A})z + D^{-1/2}b)

```

Figure 4.5: Two-level Combinatorial Multigrid

The two-level algorithm can naturally be extended into a full multigrid algorithm, by recursively calling the algorithm when the solution to the system with Q is requested. This produces a hierarchy of graphs  $A = A_0, \ldots, A_d$ . The full multigrid algorithm we use, after simplifications in the algebra of the two-level scheme is as follows in Figure 4.6.

```

function x := CMG(A_i, b_i)

1. D := diag(A)

2. x := D^{-1}b

3. r_i := b_i - A_i(D^{-1}b)

4. b_{i+1} := Rr_i

5. z := CMG(A_{i+1}, b_{i+1})

6. for i = 1 to t_i - 1

7. r_{i+1} := b_{i+1} - A_{i+1}z

8. z := z + CMG(A_{i+1}, r_{i+1})

9. endfor

10. x := x + R^Tz

11. x := r_i - D^{-1}(A_ix - b)

```

Figure 4.6: Full Combinatorial Multigrid

If nnz(A) denotes the number of non-zero entries in matrix A, we pick

$$t_i = max\{ \left[ \frac{nnz(A_i)}{nnz(A_{i+1})} - 1 \right], 1\}$$

This choice for the number of recursive calls, combined with the fast geometric decrease of the matrix sizes, targets a geometric decrease in the total work per level, while optimizing the condition number.

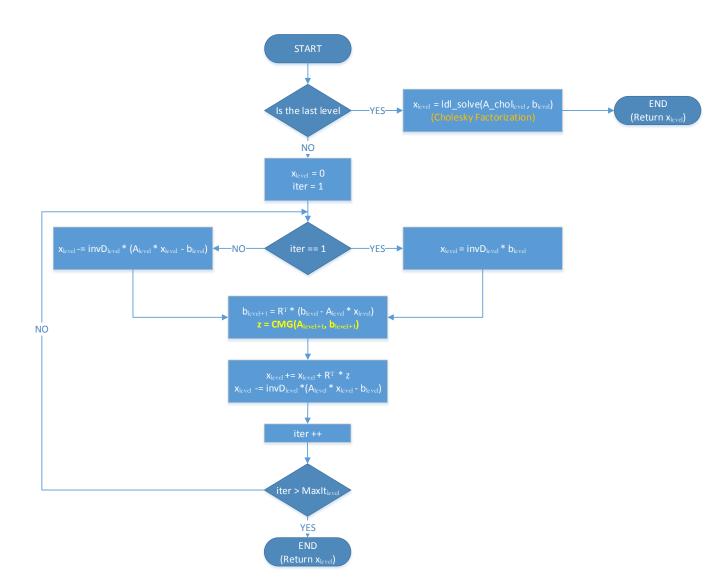

As we can see at the above Figure 4.6, the operation of sparse matrix-vector multiplication (SpMV) occurs in steps 3, 7 and 11 of the CMG algorithm. Those multiplications are the bottleneck in CMG solver and my diploma thesis [3] was only focused on solving those bottlenecks accelerating the time required for SpMV operations. The full Combinatorial Multigrid is executed in PCG method every time we have to solve  $Mz_{i-1} = r_{i-1}$  in preconditioner solve step. In this thesis we accelerate both the PCG and CMG solver by porting them on an Nvidia GPU. Details are given in Chapter 6.

# Chapter 5

# GPU Architecture and the CUDA Programming Model

#### 5.1 Introduction

General-Purpose Graphics Processing Unit (GPGPU) Computing only became practical and popular after ca. 2001, with the advent of both programmable shaders and floating point support on graphics processors. GPGPU computing is the use of a GPU together with a CPU to accelerate scientific, analytics, engineering, consumer, and enterprise applications.

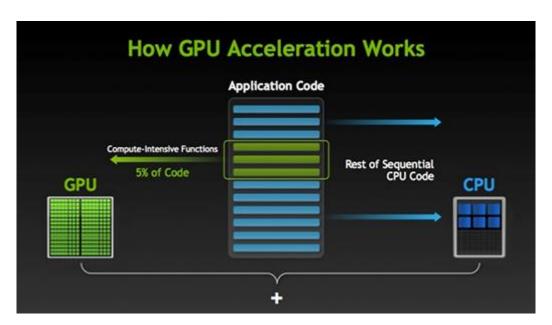

GPU-accelerated computing offers unprecedented application performance by offloading compute-intensive portions of the application to the GPU, while the remainder of the code still runs on the CPU as illustrated by Figure 5.1. From a user's perspective, applications simply run significantly faster.

Figure 5.1: How GPU Acceleration Works

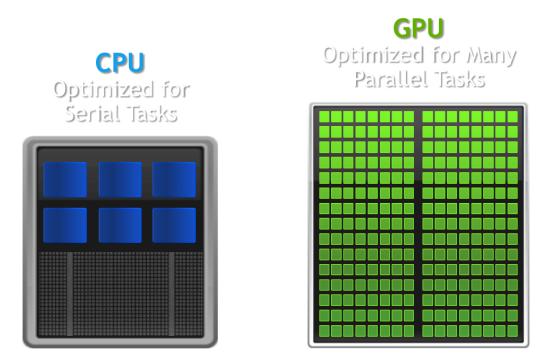

A simple way to understand the difference between a CPU and GPU is to compare how they process tasks. A CPU consists of a few cores optimized for sequential serial processing while a GPU has a massively parallel architecture consisting of thousands of smaller, more efficient cores designed for handling multiple tasks simultaneously as shown by Figure 5.2 at the top of following page.

Figure 5.2: CPU vs GPU Architecture

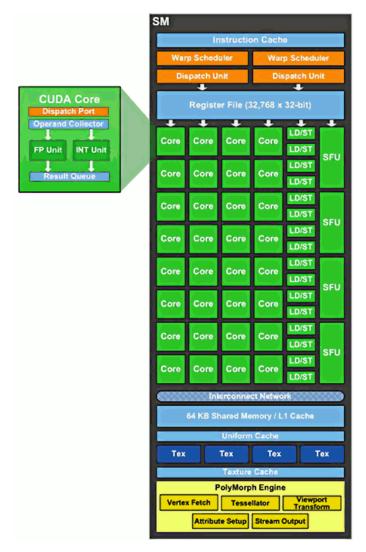

#### 5.2 Hardware Implementation

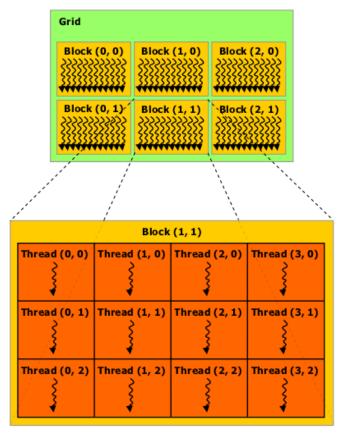

The NVIDIA GPU architecture is built around a scalable array of multithreaded Streaming Multiprocessors (SMs). When a program on the host CPU invokes a kernel grid, the blocks of the grid are enumerated and distributed to multiprocessors with available execution capacity. The threads of a thread block execute concurrently on one multiprocessor, and multiple thread blocks can execute concurrently on one multiprocessor. As thread blocks terminate, new blocks are launched on the vacated multiprocessors.

A multiprocessor is designed to execute hundreds of threads concurrently. To manage such a large amount of threads, it employs a unique architecture called SIMT (Single-Instruction, Multiple-Thread). The instructions are pipelined to leverage instruction-level parallelism within a single thread, as well as thread-level parallelism extensively through simultaneous hardware multithreading as detailed in Hardware Multithreading. Unlike CPU cores they are issued in order however and there is no branch prediction and no speculative execution.

#### 5.2.1 SIMT Architecture

The multiprocessor creates, manages, schedules, and executes threads in groups of 32 parallel threads called warps. Individual threads composing a warp start together at the same program address, but they have their own instruction address counter and register state and are therefore free to branch and execute independently. The term warp originates from weaving, the first parallel thread technology. A half-warp is either the first or second half of a warp. A quarter-warp is either the first, second, third, or fourth quarter of a warp.

When a multiprocessor is given one or more thread blocks to execute, it partitions them into warps and each warp gets scheduled by a warp scheduler for execution. The way a block is partitioned into warps is always the same; each warp contains threads of consecutive, increasing thread IDs with the first warp containing thread 0. Thread hierarchy, which describes how thread IDs relate to thread indices in the block, is described in a later section.

A warp executes one common instruction at a time, so full efficiency is realized when all 32 threads of a warp agree on their execution path. If threads of a warp diverge via a data-dependent conditional branch, the warp serially executes each branch path taken, disabling threads that are not on that path, and when all paths complete, the threads converge back to the same execution path. Branch divergence occurs only within a warp; different warps execute independently regardless of whether they are executing common or disjoint code paths.

The SIMT architecture is akin to SIMD (Single Instruction, Multiple Data) vector organizations in that a single instruction controls multiple processing elements. A key difference is that SIMD vector organizations expose the SIMD width to the software, whereas SIMT instructions specify the execution and branching behavior of a single thread. In contrast with SIMD vector machines, SIMT enables programmers to write thread-level parallel code for independent, scalar threads, as well as data-parallel code for coordinated threads. For the purposes of correctness, the programmer can essentially ignore the SIMT behavior; however, substantial performance improvements can be realized by taking care that the code seldom requires threads in a warp to diverge. In practice, this is analogous to the role of cache lines in traditional code: Cache line size can be safely ignored when designing for correctness but must be considered in the code structure when designing for peak performance. Vector architectures, on the other hand, require the software to coalesce loads into vectors and manage divergence manually.

## 5.3 Device Memory Model

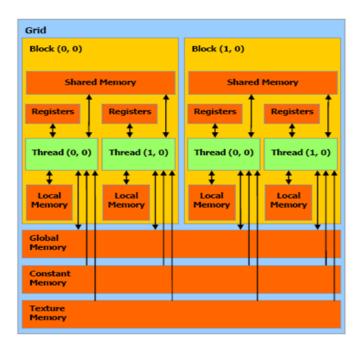

Threads may access data from multiple memory spaces during their execution as illustrated by Figure 5.3. Each thread has private local memory. Each thread block has shared memory visible to all threads of the block and with the same lifetime as the block. All threads have access to the same global memory.

There are also two additional read-only memory spaces accessible by all threads: the constant and texture memory spaces. The global, constant, and texture memory spaces are optimized for different memory usages. Those memory spaces are persistent across kernel launches by the same application. Texture memory also offers different addressing modes, as well as data filtering, for some specific data formats.

An instruction that accesses addressable memory (i.e., global, local, shared, constant, or texture memory) might need to be re-issued multiple times depending on the distribution of the memory addresses across the threads within the warp. How the distribution affects the instruction throughput this way is specific to each type of memory and described in the following sections. For example, for global memory, as a general rule, the more scattered the addresses are, the more reduced the throughput is.

Figure 5.3: Memory Hierarchy

#### 5.3.1 Global Memory

Global memory resides in device memory and device memory is accessed via 32-, 64-, or 128-byte memory transactions. These memory transactions must be naturally aligned: Only the 32-, 64-, or 128-byte segments of device memory that are aligned to their size (i.e., whose first address is a multiple of their size) can be read or written by memory transactions.