# Algorithms for Large-Scale Power Delivery Network Analysis on Massively Parallel Architectures

by

#### Konstantis Daloukas

Submitted to the Department of Electrical and Computer

Engineering

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical and Computer Engineering

at the

#### UNIVERSITY OF THESSALY

July 2014

©Konstantis Daloukas, 2014.

| Author       |                                                   |

|--------------|---------------------------------------------------|

|              | Konstantis Daloukas                               |

|              | Department of Electrical and Computer Engineering |

|              | July 4, 2014                                      |

|              |                                                   |

|              |                                                   |

| Certified by |                                                   |

| J            | Panagiota Tsompanopoulou                          |

|              | Assistant Professor                               |

|              | Thesis Supervisor                                 |

## Algorithms for Large-Scale Power Delivery Network Analysis on Massively Parallel Architectures

by

#### Konstantis Daloukas

Submitted to the Department of Electrical and Computer Engineering on July 4, 2014, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

#### Abstract

The on-chip power delivery network constitutes a vital subsystem of modern nanometer-scale integrated circuits, since it affects in a critical way the performance and correct operation of the devices. As technology scaling enters in the nanometer regime, there is an increasing need for accurate and efficient analysis of the power delivery network. The impact of first-order phenomena like IR drop or electromigration or second-order phenomena like Joule heating, that were neglected until recently, on the power delivery network, necessitates the existence of fast and accurate methodologies for electrical and thermal analysis of the power grid.

A typical power delivery network is modeled as an RLC network and its electrical or thermal analysis amounts at solving a linear system of equations. Due to the sheer size of contemporary power delivery networks (which comprise millions or billions of nodes), its analysis is a very challenging process, both in terms of computational and memory requirements. Parallel architectures that have recently appeared and provide a large amount of computational resources appear as the platform of choice for executing computationally demanding algorithms. However, most state-of-the-art algorithms for power grid analysis do not entail a large degree of parallelism and have excessive memory requirements, which makes their mapping onto parallel architectures difficult or even infeasible.

To this end, this dissertation proposes three new methodologies for analysis of large-scale power delivery networks found in contemporary integrated circuits. We present two algorithms for electrical analysis and one algorithm for combined electro-thermal analysis of the power delivery network. The novel characteristic of the proposed algorithms is the large degree of multi-level parallelism that they entail. As a results, they appear as ideal candidates for mapping onto parallel architectures. Our algorithms are able to greatly accelerate the simulation process, achieving up to two or three orders of magnitude speedup for power grid electrical analysis and one order of magnitude speedup for electro-thermal analysis, while at the same time scaling linearly with the number of power grid nodes.

## Αλγόριθμοι για Ανάλυση του Δικτύου Τροφοδοσίας Μεγάλης Κλίμακας Ολοκληρωμένων Κυκλωμάτων σε Μαζικά Παράλληλες Αρχιτεκτονικές

### Κωνσταντής Νταλούκας

### Περίληψη

Το δίκτυο τροφοδοσίας αποτελεί ένα ζωτικής σημασίας υποσύστημα στα μοντέρνα ολοκληρωμένα κυκλώματα, καθώς καθορίζει τη σωστή λειτουργία και την απόδοση του κυκλώματος. Λόγω της συνεχούς μείωσης της κλίμακας σχεδιασμού, υπάρχει μια αυξανόμενη ανάγκη για ακριβή και αποδοτική ανάλυση του δικτύου τροφοδοσίας. Ο αντίκτυπος των πρωτευόντων φαινομένων, όπως η πτώση τάσης ή η ηλεκτρομετανάστευση, αλλά και των δευτερευόντων φαινομένων, όπως η επίδραση του φαινομένου Joule heating στους αγωγούς, που δε λαμβάνονταν υπόψη μέχρι πρότινος, καθιστούν απαραίτητη την ύπαρξη κατάλληλων και αποδοτικών μεθοδολογιών για ηλεκτρική και θερμική ανάλυση του δικτύου τροφοδοσίας.

Ένα τυπικό δίκτυο τροφοδοσίας μοντελοποιείται ως ένα δίκτυο RLC και η ηλεκτρική και θερμική ανάλυσή του ανάγεται στην επίλυση ενός συστήματος γραμμικών εξισώσεων. Λόγω του μεγάλου μεγέθους των σύγχρονων δικτύων τροφοδοσίας (τα οποία περιλαμβάνουν εκατομμύρια ή δισεκατομμύρια κόμβους), η ανάλυσή τους είναι μια πολύ απαιτητική διαδικασία, τόσο από άποψη υπολογιστικής ισχύος όσο και από άποψη απαιτήσεων σε μνήμη. Οι παράλληλες αρχιτεκτονικές που έχουν εμφανιστεί πρόσφατα, προσφέρουν πολύ μεγάλη υπολογιστική ισχύ με αποτέλεσμα να εμφανίζονται ως η κατάλληλη πλατφόρμα για την εκτέλεση υπολογιστικά απαιτητικών αλγορίθμων. Ωστόσο, οι περισσότεροι αλγόριθμοι που χρησιμοποιούνται σήμερα στα περισσότερα εμπορικά εργαλεία για την ανάλυση του δικτύου τροφοδοσίας δεν εμπεριέχουν μεγάλο βαθμό παραλληλισμού και έχουν υπερβολικές απαιτήσεις μνήμης, γεγονός που καθιστά την υλοποίησή τους σε παράλληλες αρχιτεκτονικές ιδιαίτερα δύσκολη και σε αρκετές περιπτώσεις ανέφικτη.

Βάσει των παραπάνω, η παρούσα διατριβή προτείνει τρεις νέες μεθοδολογίες για την

ανάλυση των δικτύων τροφοδοσίας μεγάλης κλίμακας που εμπεριέχονται στα σύγχρονα ολοκληρωμένα κυκλώματα. Παρουσιάζονται δύο αλγόριθμοι για την ηλεκτρική ανάλυση και ένας αλγόριθμος για τη συνδυασμένη ηλεκτρο-θερμική ανάλυση του δικτύου τροφοδοσίας. Το νέο χαρακτηριστικό των προτεινόμενων αλγορίθμων είναι ο μεγάλος βαθμός παραλληλισμού σε πολλαπλά επίπεδα, ο οποίος τους καθιστά κατάλληλους για την υλοποίηση σε παράλληλες αρχιτεκτονικές. Οι προτεινόμενοι αλγόριθμοι επιταχύνουν σημαντικά τη διαδικασία προσομοίωσης, επιτυγχάνοντας έως και τρεις τάξεις μεγέθους επιτάχυνση για την ηλεκτρική ανάλυση και μία τάξη μεγέθους επιτάχυνση για την ηλεκτρο-θερμική ανάλυση, ενώ την ίδια στιγμή κλιμακώνουν γραμμικά με τον αριθμό των κόμβων στο δίκτυο τροφοδοσίας τόσο σε υπολογιστική πολυπλοκότητα όσο και σε απαιτήσεις σε μνήμη.

## Acknowledgements

As this long endeavor has reached its end, I would like to express my deep gratitude to a group of people who provided my with guidance, assistance, support, and encouragement. It is certain that without their help, I would not have been able to complete my dissertation.

First of all, I would like to express my sincere gratitude to my Ph.D. advisors, Professor Panagiota Tsompanopoulou, Professor Nestor Evmorfopoulos, and Professor George Stamoulis. Their guidance and support were the main reasons that most ideas presented in this dissertation have been accomplished. Their diligence, intelligence and wisdom have had great influence on my research development. Research directions, technical criticisms as well as valuable feedback from our office discussions brought me continuous sources of motivation and inspiration. Apart from being excellent scientists, they are also valuable collaborators and true supporters.

I would also like to thank my thesis committee members, Professor John Moondanos and Professor Christos Sotiriou from the University of Thessaly, as well as Professor Apostolos Dollas and Professor Dionisios Pnevmatikatos from the Technical University of Crete, for providing important feedback for my dissertation.

My sincere thanks to all my friends for their encouragement all these years. Especially, I would like to thank my friends from the Electronics Lab. Without their help, I would not have led such a fruitful and joyful life in the Department of Electrical and Computer Engineering. Particularly, I would like to thank my close friends, George, Michalis, and Babis for their constant support, help and valuable discussions. Also, many thanks to Mary, Lena, Maria, and Despoina for their continuous secretarial support.

During the academic years 2010-2013, my research had been partially funded by the Bodossaki Foundation in Greece. I really appreciate the opportunity of being a member of the Bodossaki Foundation scholars' family and the experience of participating in a large number of conferences that made my research more visible.

Also, I would like to thank Yorgos Koutsoyannopoulos and Sotiris Bantas from

Helic, Inc. for their guidance and financial support during the last year of my studies.

Finally, I appreciate so much the unconditional love, help, trust, and support from my family and Ioanna. There are no words that can express my gratitude and appreciation for all they have done for me. Without their patience and support, I would not have been able to finish my dissertation. The least I can do in recognition is to dedicate this dissertation to them.

To my family, Ioanna & my friends

| This doctoral thesis has been examined by a joint committee of the<br>Department of Electrical and Computer Engineering from the<br>University of Thessaly and the Department of Electronic and |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Computer Engineering from Technical University of Crete as follows:                                                                                                                             |

| Professor Panagiota Tsompanopoulou                                                                                                                                                              |

| Assistant Professor of Electrical and Computer Engineering University of Thessaly                                                                                                               |

| Professor Nestor Evmorfopoulos                                                                                                                                                                  |

| Member, Thesis Committee                                                                                                                                                                        |

| Assistant Professor of Electrical and Computer Engineering University of Thessaly                                                                                                               |

| Professor George Stamoulis                                                                                                                                                                      |

| Member, Thesis Committee<br>Professor of Electrical and Computer Engineering                                                                                                                    |

| University of Thessaly                                                                                                                                                                          |

| Professor Apostolos Dollas                                                                                                                                                                      |

| Member, Examination Committee                                                                                                                                                                   |

| Professor of Electronic and Computer Engineering Technical University of Crete                                                                                                                  |

| Professor John Moondanos                                                                                                                                                                        |

| Member, Examination Committee                                                                                                                                                                   |

| Professor of Electrical and Computer Engineering University of Thessaly                                                                                                                         |

| Professor Dionisios Pnevmatikatos                                                                                                                                                               |

| Professor of Electronic and Computer Engineering Technical University of Crete                                                                                                                  |

| Professor Christos Sotiriou                                                                                                                                                                     |

| Member, Examination Committee                                                                                                                                                                   |

| Professor of Electrical and Computer Engineering University of Thessaly                                                                                                                         |

## Contents

| A        | bstra            | nct                                          | 3  |

|----------|------------------|----------------------------------------------|----|

| П        | ερίλι            | ηψη                                          | 5  |

| Li       | ${f st}$ of      | Figures                                      | 17 |

| Li       | $\mathbf{st}$ of | Tables                                       | 19 |

| Li       | $\mathbf{st}$ of | Acronyms                                     | 21 |

| 1        | Intr             | roduction                                    | 23 |

|          | 1.1              | Background and Motivation                    | 23 |

|          | 1.2              | Contributions                                | 26 |

|          | 1.3              | Outline                                      | 27 |

| <b>2</b> | Par              | allel Computing Architectures                | 29 |

|          | 2.1              | Introduction                                 | 29 |

|          | 2.2              | Differences between CPUs and GPUs            | 31 |

|          |                  | 2.2.1 Concurrency in GPUs                    | 32 |

|          | 2.3              | GPU Programming - The CUDA Programming Model | 32 |

| 3        | Line             | ear System Solution Methods                  | 35 |

|          | 3.1              | Direct Methods                               | 36 |

|          | 3.2              | Iterative Methods                            | 39 |

|          |                  | 3.2.1 Conjugate Gradient Algorithm           | 40 |

|   |     | 3.2.2 Preconditioning                                            | 41 |

|---|-----|------------------------------------------------------------------|----|

|   | 3.3 | Solution of Linear Systems on Parallel                           |    |

|   |     | Architectures                                                    | 45 |

| 4 | Pov | ver Grid Electrical Simulation                                   | 47 |

|   | 4.1 | Power Grid Modeling                                              | 47 |

|   | 4.2 | Related Work                                                     | 51 |

|   | 4.3 | Fast Transform Solvers for Networks with                         |    |

|   |     | Special Structure                                                | 54 |

|   |     | 4.3.1 Fast Transform Solvers for 2D Networks                     | 54 |

|   |     | 4.3.2 Fast Transform Solvers for 3D Networks                     | 58 |

|   | 4.4 | Proposed Methodology for Power Grid                              |    |

|   |     | Analysis                                                         | 64 |

|   |     | 4.4.1 Preconditioner Construction and Storage                    | 64 |

|   |     | 4.4.2 Procedure Implementation and Opportunities for Parallelism | 72 |

|   | 4.5 | Experimental Results                                             | 75 |

|   |     | 4.5.1 Experimental Setup                                         | 75 |

|   |     | 4.5.2 Transient Analysis Results for the Industrial              |    |

|   |     | Benchmarks                                                       | 76 |

|   |     | 4.5.3 Transient Analysis Results for the Synthetic               |    |

|   |     | Benchmarks                                                       | 80 |

|   |     | 4.5.4 Scalability of FTCG and FTCG-3D                            | 82 |

|   |     | 4.5.5 Memory Efficiency                                          | 83 |

|   |     | 4.5.6 Efficiency Under Grid Irregularity                         | 84 |

| 5 | Pow | ver Grid Electro-Thermal Simulation                              | 87 |

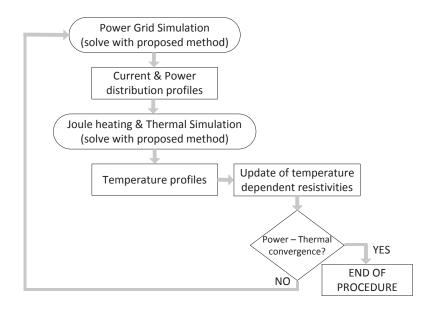

|   | 5.1 | Methodology Overview                                             | 89 |

|   | 5.2 | Fast Transform Solvers for Full 3D Networks                      | 92 |

|   | 5.3 | Proposed Approach for Electro-Thermal Analysis                   | 96 |

|   |     | 5.3.1 Procedure Implementation                                   | 98 |

|   | 5.4 | Experimental Evaluation                                          | 99 |

| 6                | Cor          | clusions and Future Directions | 103 |

|------------------|--------------|--------------------------------|-----|

|                  | 6.1          | Conclusions                    | 103 |

|                  | 6.2          | Future Directions              | 104 |

| $\mathbf{A}_{]}$ | ppen         | dix A: Mathematical Proofs     | 106 |

| Pι               | Publications |                                | 113 |

| $\mathbf{R}_{0}$ | efere        | nces                           | 115 |

## List of Figures

| 2-1 | Architecture of the NVIDIA Tesla K20 GPU                                 | 30 |

|-----|--------------------------------------------------------------------------|----|

| 2-2 | NVIDIA CUDA Thread Model                                                 | 33 |

| 4-1 | Example of a power delivery network with 3 horizontal and 3 vertical     |    |

|     | rails, along with its equivalent model for electrical analysis           | 48 |

| 4-2 | Example of a power delivery network with 3 horizontal and 3 vertical     |    |

|     | rails, along with the regular 2D and 3D grids used for preconditioning.  | 65 |

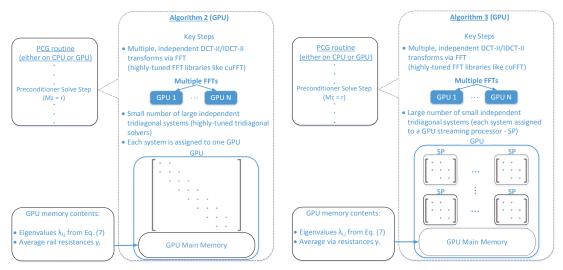

| 4-3 | The key steps for the application of the proposed preconditioners and    |    |

|     | their mapping onto the available GPUs                                    | 72 |

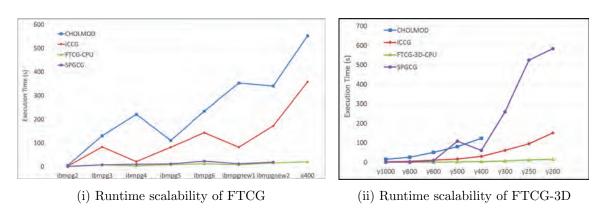

| 4-4 | Runtime scalability of FTCG and FTCG-3D on the set of the industrial $$  |    |

|     | benchmarks                                                               | 82 |

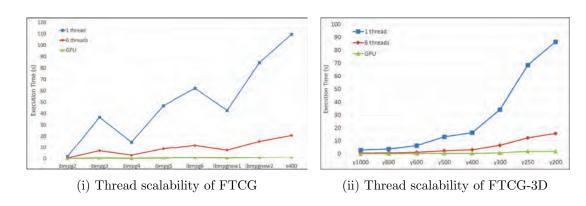

| 4-5 | Thread scalability of the 1-thread, 6-thread, and the GPU implementation | ns |

|     | of FTCG and FTCG-3D on the set of the industrial benchmarks              | 83 |

| 5-1 | Electrical-Thermal positive feedback simulation loop                     | 90 |

| 5-2 | Example of the thermal equivalent of the 3D power grid from Fig. 4-      |    |

|     | 1(i) that is used for preconditioning                                    | 98 |

## List of Tables

| 4.1 | Maximum and average voltage drop error when neglecting via resi-       |     |

|-----|------------------------------------------------------------------------|-----|

|     | stances in the analysis of a set of large-scale industrial power grid  |     |

|     | benchmarks                                                             | 69  |

| 4.2 | Circuit details and convergence results for electrical analysis of the |     |

|     | 2D benchmarks                                                          | 77  |

| 4.3 | Circuit details and convergence results for electrical analysis of the |     |

|     | 3D benchmarks                                                          | 78  |

| 4.4 | Runtime results of CHOLMOD, ICCG, SPGCG, and FTCG for electrical       | 1   |

|     | analysis of the 2D benchmarks                                          | 79  |

| 4.5 | Runtime results of CHOLMOD, ICCG, SPGCG, and FTCG for electrical       | 1   |

|     | analysis of the 3D benchmarks                                          | 79  |

| 4.6 | Memory requirements of FTCG, CHOLMOD, and ICCG                         | 84  |

| 4.7 | Results of FTCG-3D under varying grid irregularity                     | 85  |

| 5.1 | Runtime results of CHOLMOD, ICCG, and FTCG for electro-thermal         |     |

|     | analysis of the synthetic benchmarks                                   | 101 |

## List of Acronyms

**ALU** Arithmetic Logic Unit

**BiCG** Biconjugate Gradient Method

**CG** Conjugate Gradient

**CPU** Central Processing Unit

**CUDA** Compute Unified Device Architecture

**DCT** Discrete Cosine Transform

**FDM** Finite Difference Method

**FFT** Fast Fourier Transform

**FPGA** Field-Programmable Gate Arrays

GMRES Generalized Minimal Residual Method

**GPU** Graphics Processing Unit

IC Integrated Circuit

**IDCT** Inverse Discrete Cosine Transform

MIMD Multiple Instruction Multiple Data

MNA Modified Nodal Analysis

**ODE** Ordinary Differential Equation

**PCG** Preconditioned Conjugate Gradient

**SFU** Special Function Units

**SIMD** Single Instruction Multiple Data

**SIMT** Single Instruction Multiple Thread

SMX Streaming Multiprocessor

**SP** Streaming Processor

**SPD** Symmetric and Positive Definite

**TSV** Through Silicon Via

## Chapter 1

## Introduction

### 1.1 Background and Motivation

The relentless push for high-performance and low-power integrated circuits has been met by aggressive technology scaling, which enabled the integration of a vast number of devices on the same die but brought new problems and challenges to the surface. The on-chip power delivery network (power grid) constitutes a vital subsystem of modern nanometer-scale Integrated Circuits (ICs), since it affects in a critical way the performance and correct operation of the devices.

The major issues in the power delivery networks of contemporary circuits is voltage drop (or IR drop) and electromigration. Voltage drop is the decrease in the nominal value of the supply voltage of the chip that a device sees due to the finite resistance of interconnects and can severely affect the correct operation and the performance of the design. On the other hand, electromigration is the transport of material caused by the gradual movement of the ions in a conductor due to the momentum transfer between conducting electrons and diffusing metal atoms. Electromigration affects the reliability of the power grid and can even lead to disconnections, thus making a chip unusable.

As a result, in order to address these issues and to determine the quality of the supply voltage delivered to the devices, the designer has to perform static and dynamic simulation of the electrical circuit modeling the power grid. This has become a very challenging problem for contemporary ICs, since power grids encountered in these circuits are extremely large (comprising several thousands or millions of nodes) and very difficult to simulate efficiently (especially over multiple time-steps). Static (DC) or transient simulation refers to the process of computing the response of an electrical circuit to a constant or time-varying stimulus respectively. Since a power delivery network can be generally modeled as a linear RLC circuit, the process of DC or transient simulation of large-scale power grids amounts to solving very large (and sparse) linear systems of equations. The methods that have been proposed so far for tackling analysis of power delivery networks can be categorized as follows:

- Direct methods (based on matrix factorization) have been widely used in the past for solving the resulting linear systems arising in power grid analysis, mainly because of their robustness in most types of problems. They also have the property of reusability of factorization results in transient simulation with a fixed time-step. Unfortunately, these methods do not scale well with the dimension of the linear system, and become prohibitively expensive for circuits beyond a few thousand elements, in both execution time and memory requirements. In addition, a fixed time-step is almost never used in practice because it becomes very inefficient to constantly simulate during long intervals of low activity. All practical implementations of integration techniques for Ordinary Differential Equations (ODEs) employ a variable or adaptive time-step mechanism [9]. In those cases, the reusability of matrix factorization in direct methods ceases to exist.

- Iterative methods involve only inner products and matrix-vector products, and constitute a better alternative for large sparse linear systems in many respects, being more computationally- and memory-efficient. This holds even more so for modern nonstationary iterative methods which fall under the broad class of "Krylov-subspace" methods [31]. Iterative methods possess themselves a kind of reusability property for transient simulation, in that the solution at the

last time-step provides an excellent initial guess for the next time-step, thus making a properly implemented iterative method converge in a fairly small number of iterations. In fact, this property also holds in the case of a variable time-step, since the quality of the last solution as initial guess for the next solution is not affected. The above features make iterative methods much more suitable for DC and variable time-step transient analysis of large-scale linear circuits such as power distribution networks.

The main problem of iterative methods is their unpredictable rate of convergence which depends greatly on the properties (specifically the condition number) of the system matrix. A preconditioning mechanism, which transforms the linear system into one with more favorable properties, is essential to guarantee fast and robust convergence. However, the ideal preconditioner (one that approximates the system matrix well and is inexpensive to construct and apply) differs according to each particular problem and each different type of system matrix. That is why iterative methods have not reached the maturity of direct methods and have not yet gained widespread acceptance in linear circuit simulation. Although general-purpose preconditioners (such as incomplete factorizations or sparse approximate inverses) have been developed, they are not tuned to any particular simulation problems and cannot improve convergence by as much as specially-tailored preconditioners.

Another aspect of circuit simulation that has become very important recently is to uncover hidden opportunities for parallelism in its intermediate steps. This is essential for harnessing the potential of contemporary parallel architectures, such as multi-core processors and Graphics Processing Units (GPUs) in order to enable analysis for very-large scale power delivery networks. GPUs, in particular, are massively parallel architectures whose computational power is about 3.95 TFlops, greater by an order of magnitude than that of multi-core processors. As a result, they appear as a platform of choice for the efficient execution of computationally-intensive tasks such as power grid analysis and simulation.

Direct solution methods offer little room for parallelism as they are mainly based on backward and forward solution of triangular systems which do not entail large parallelism due to the dependencies that exist among the solution steps. On the contrary, Krylov-subspace iterative methods offer ample possibilities for parallelism that have been explored sufficiently well. However, the construction and application of the preconditioner is a very delicate part of parallelizing an iterative method because it is completely application-dependent (and traditional general-purpose preconditioners have very little room for parallelism). Unfortunately, there has been little systematic research for the development of parallel simulation algorithms, and more specifically algorithms for power grid analysis that can be mapped onto massively parallel architectures like GPUs. This can be attributed in part to the difficulty in parallelization of direct linear solution methods that have been mostly employed thus far. In addition, most sophisticated preconditioners that have been developed for power grid analysis have little room for parallelism. Thus, they cannot be mapped efficiently and take full advantage of the computational power of massively parallel architectures.

#### 1.2 Contributions

In order to address the limitations of the existing simulation techniques for power grid analysis, this research work presents a class of new parallel algorithms for efficient analysis of power delivery networks found in contemporary large-scale ICs as described below:

1. Two parallel algorithms for DC and transient electrical analysis of power delivery networks, FTCG and FTCG-3D. FTCG targets power delivery networks with negligible via resistances (near-2D structures), while FTCG-3D targets power delivery networks with significant via resistances. Both methods combine a preconditioned iterative method with two problem-specific and highly-parallel preconditioning algorithms. Both preconditioning algorithms take into account the structure of the underlying power grid in order to accelerate the convergence of the iterative method. In addition, their specialized structure allows applying a Fast Transform-based solver that utilizes Fast

Fourier Transform (FFT) for the solution of the necessary preconditioning step. The main characteristics of the application of a Fast Transform are the near-optimal operation complexity, as well as its inherent parallelism and low memory requirements, compared to a generic solver for linear systems. As a result, massively parallel architectures such as GPUs can be used to accelerate the simulation algorithm, while at the same time the application's memory demands render feasible the analysis of very large power grids on such architectures.

2. A parallel algorithm (ET-FTCG) for static combined electro-thermal analysis of power delivery networks. ET-FTCG combines FTCG for electrical analysis and an efficient preconditioning approach for thermal analysis and can efficiently tackle electro-thermal analysis of very large-scale power delivery networks by utilizing massively parallel architectures.

#### 1.3 Outline

The next chapters of the dissertation are organized as follows. Firstly, the relevant background information regarding parallel architectures are presented in Chapter 2. Then, in Chapter 3 we give the important background details behind direct and iterative linear system solution methods, preconditioning and porting of linear system solution algorithms onto parallel architectures. Chapter 4 describes the theory behind power grid electrical analysis and discusses the proposed algorithms for large-scale power grid analysis on massively parallel architectures. Following this chapter, we describe the details behind our proposed algorithm for electro-thermal analysis of the power delivery network in Chapter 5. The proposed algorithm combines one of the techniques described in Chapter 4 with a novel algorithm for thermal analysis of the power grid. Finally, Chapter 6 concludes the dissertation.

## Chapter 2

## Parallel Computing Architectures

#### 2.1 Introduction

During the last few years, we have witnessed a paradigm shift towards parallel computing. Technology advances have enabled the integration of multiple cores in a single die, thus enabling the development of a plethora of computation substrates for parallel, high performance, computing. In addition, the diminishing returns from the continuous technology scaling on single-core processors has forced researchers to start designing architectures that would incorporate more than one processors. Architectures such as homogeneous or heterogeneous multicore and manycore processors, and, more recently, GPUs have allowed the time- and power efficient execution of computationally intensive applications at a minimum expense.

Multi-core processors seek to maintain the execution speed of sequential programs as more cores are utilized. Starting from a small number of processors and owing to technology scaling, designers increased the number of cores at each semiconductor process generation. Each core comprises its own local cache and computational resources, while communication between different cores is achieved through means of high-speed interconnects. Although multi-core processors offer a significant amount of computational resources, they are mainly optimized for execution of sequential applications. As a result, porting of an application on a multi-core architecture is not a trivial process.

Figure 2-1: Architecture of the NVIDIA Tesla K20 GPU.

In contrast to multi-core architectures, massively parallel architectures (and their main representatives GPUs) comprise a large number of simpler computational cores, as they are focused on providing massive parallelism.

Fig. 2.1 depicts the architecture of the latest Tesla K20 GPUs accelerator from NVIDIA, which is a typical high-end GPUs. The smallest unit capable of performing parallel computations is the Streaming Multiprocessor (SMX), with the main difference between a low-end GPUs and a high-end GPUs of the same architecture being the number of SMXs inside the chip. In the case of Tesla K20 GPUs, each SMX unit is composed of 192 cores, also known as Streaming Processors (SPs). Its architecture was built for a maximum of 15 SMXs, giving a maximum of 2,880 cores. However in practice, some SMXs are deactivated in order to increase the yield.

The cores of a SMX are mainly optimized for calculations which means that there is no extra hardware devoted to sequential and control operations (e.g. branch prediction). They are 32-bit units that can perform basic integer and single precision (FP32) floating point arithmetic. In addition to the computation cores, there are 32 Special Function Unitss (SFUs) that perform special mathematical operations such as log, sqrt, sin and cos, among others. Each SMX has also 64 double precision

floating point units, known as FP64, and 32 LD/ST units (load / store) for writing and reading memory.

As far as the memory model of the GPU is concerned, GPUs such as the Tesla K20 implement a four-level memory hierarchy; (1)registers, (2) L1 cache, (3) L2 cache and (4) global memory. All levels, except for the global memory, reside in the GPU chip. The L2 cache is hardware-managed and it improves memory accesses on global memory. The L1 cache is software-managed (meaning that the programmer is responsible for managing its contents), there is one per SMX, and it can be as fast as the registers. Kepler and Fermi based GPUs have L1 caches of size 64KB that are split into 16KB of programmable shared memory and 48KB of automatic cache, or vice versa.

#### 2.2 Differences between CPUs and GPUs

Modern GPUs have evolved towards parallel processing, implementing the Multiple Instruction Multiple Data (MIMD) architecture. Most of their chip budget is reserved for control units and cache, leaving a small area for numerical computations. A Central Processing Unit (CPU) performs different tasks and advanced control and cache mechanisms is the only way to achieve a good performance level. On the other hand, GPUs have a Single Instruction Multiple Data (SIMD) architecture and the main goal of its architecture is to achieve high performance through massive parallelism. Contrary to the CPU, a GPU is mostly occupied by Arithmetic Logic Units (ALUs) and a minimal region is reserved for control and cache. Owing to their architecture, GPUs can achieve up to three orders of magnitude speedup over CPUs for algorithms that entail large degree of parallelism.

Although this difference in architecture makes GPUs much more restrictive than CPUs, a GPU is much more powerful if an algorithm is carefully designed for it. Contemporary GPU architectures such as NVIDIA's Fermi and Kepler have added a significant degree of flexibility by incorporating a L2 cache for handling irregular memory accesses and by improving the performance of atomic operations, even if

such flexibility is still far from the one found in CPUs. As a result, there is a tradeoff between flexibility and computing power. Actual CPUs struggle to maintain a balance between computing power and general purpose functionality. On the other hand, GPUs aim at massive parallel arithmetic computations.

#### 2.2.1 Concurrency in GPUs

Usually, the number of logical threads that a GPU application requires is larger than the available processing units in the GPU hardware. As a result, there must be an efficient way for thread management that will allow for efficient utilization of the GPU resources.

GPUs divide the number of threads into small groups that work in SIMD mode. For the NVIDIA GPUs, these groups are known as warps and each warp contains 32 threads. GPUs comprise efficient mechanisms for handling the entire space of computation in order to support concurrency. The number of threads that are running on the GPU corresponds to the number of processing units available. However, the maximum number of concurrent threads available is much higher. For example, the latest Tesla K40 GPU can process up to 2,880 threads in parallel, but can handle up to 30,720 concurrent threads. The thread scheduler is the hardware part that is responsible for deciding which warp of threads is ready for execution. It switches idle warps (e.g., warps that are waiting for a memory access) with warps ready for computation. This means that numerical computations and memory accesses are pipelined and the thread scheduler tries to maintain this pipeline full all the time and fully utilize the computational resources of the GPU.

## 2.3 GPU Programming - The CUDA Programming Model

With the advent of more sophisticated GPUs, the need for programmability became apparent in order to utilize their computation resources. The Compute Unified Device Architecture (CUDA) [2] programming model is a parallel computing

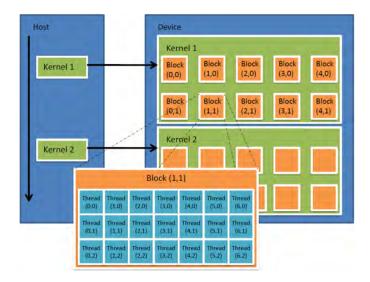

Figure 2-2: NVIDIA CUDA Thread Model.

platform and programming model created by NVIDIA and implemented by the GPUs that they produce. An application written in the CUDA programming model comprises the host and the device code. The host code executes on the CPU-side and contains the control-intensive part of the application. It is responsible for uploading the data to the GPU and orchestrating the execution of the device code. The host program can work in a synchronous or asynchronous manner, depending if the result from the GPU is needed for the next step of computation or not. When the device code has finished in the GPU, the result data is copied back from device to host.

On the other hand, the device code comprises a series of kernel functions (or kernels) that execute on the GPU and correspond to the computational intensive parts of the application. CUDA programmers typically use kernels for expressing parallelism at its finest granularity. Through the abstraction layer that is offered by the CUDA programming model, the programmer can design massively parallel algorithms independent of the number of physical processing units or the execution order of threads.

Upon execution of a kernel function, the programmer defines a logical geometry. This "geometry" of execution is described by a 3-level, 3D index space where all logical threads are organized. The space of computation is composed of a grid,

blocks and threads. An example of a two dimensional grid of computation depicted in Fig. 2-2. A grid is a discrete k-dimensional (with k=1,2,3) box type structure that defines the size and volume of the space of computation. Each element of the grid is a block and each block contains many spatially organized threads. A thread is assigned to every point in the k-dimensional space and corresponds to the execution of a particular instance of the kernel function. Each thread is described by a unique tuple of ids. Threads are organized into blocks, each having up to three dimensions (3D thread index within the block geometry). The overall computation can, in turn, be partitioned in blocks, also organized in a 3D space (3D block index within the global computation geometry). CUDA provides functionality for synchronization among threads that belong to the same block. On the other hand, blocks are completely independent on each other and can execute in parallel. Therefore, only threads that belong to the same block can communicate directly, through memory which is visible only inside the block.

## Chapter 3

## Linear System Solution Methods

In general, a linear system of equations is described by the following equation:

$$\mathbf{A}\mathbf{x} = \mathbf{b} \tag{3.1}$$

where  $\mathbf{A} \in \mathbb{R}^{n \times n}$  is an  $n \times n$  matrix of real numbers,  $\mathbf{b} \in \mathbb{R}^n$  is a vector of size n, and  $\mathbf{x} \in \mathbb{R}^n$  is an unknown solution of vector of size n that will be determined by a solution method. A solution for the linear system in (3.1) exists if the matrix  $\mathbf{A}$  is non-singular, which means that the inverse matrix  $\mathbf{A}^{-1}$  with  $\mathbf{A}\mathbf{A}^{-1} = \mathbf{I}$  exists. The solution methods for linear systems are classified as **direct** and **iterative**. Direct solution methods solve the above linear system in a predefined number of steps, which depends on the size n of the linear system. On the other hand, iterative solution methods determine an approximation of the exact solution to a predefined accuracy level.

Matrices arising in power grid analysis are very large (n can be in the order of millions or billions) and have two important features:

- The system matrix **A** is sparse, with less than 20 elements per each row, in principal. Had the system matrix been full, power grid analysis would be impractical due to both execution time and memory reasons.

- System matrix **A** is a Symmetric and Positive Definite (SPD) matrix. Symmetry

means  $\alpha_{ij} = \alpha_{ji}$ ,  $i, j = 0, 1, \dots, n-1$ , while positive definiteness means that

$$\mathbf{v}^T \mathbf{A} \mathbf{v} > 0$$

, for all vectors  $\mathbf{v}$

Symmetry and positive definiteness are two important properties of a matrix that allow utilization of more efficient direct or iterative methods for the solution of the corresponding system.

This chapter describes the general principles that sparse direct and iterative methods are based on and describes the state-of-the-art algorithms for solution of symmetric and positive-definite linear system of equations, namely the Cholesky decomposition and the Preconditioned Conjugate Gradients algorithms.

#### 3.1 Direct Methods

Direct solution methods solve the linear system in (3.1) in a predefined number of steps, which depends on the size of the linear system. They consist of two steps, namely a factorization step where the system matrix is decomposed into a number of factors, and the solution phase where the matrix factorization is used for the solution of the initial system.

LU factorization is the direct method used in general, non-symmetric matrices. It factors the system matrix in two factors, one lower- and one upper-triangular matrix  $\mathbf{A} = \mathbf{L}\mathbf{U}$ , and equation (3.1) is transformed into the following:

$$\mathbf{A}\mathbf{x} = \mathbf{b} \Rightarrow (\mathbf{L}\mathbf{U})\mathbf{x} = \mathbf{b} \Rightarrow \mathbf{L}(\mathbf{U}\mathbf{x}) = \mathbf{b}$$

where  $\mathbf{L}$  is a lower-triangular matrix while  $\mathbf{U}$  is an upper-triangular one. As a result, the original system is transformed into two equivalent systems and is solved into two steps as follows:

$$Ly = b$$

$$\mathbf{U}\mathbf{x} = \mathbf{y}$$

## **Algorithm 1** Factorization phase for the LU algorithm

```

for k = 0: n-2 do

for i = k: n-1 do

a(i,k) = a(i,k) / a(k,k)

for j = k+1: n-1 do

a(i,j) = a(i,j) - a(i,k) \cdot a(k,j)

end for

end for

end for

```

The advantage of breaking the original linear system into the above set is that each linear system requires the solution of a triangular system (forward substitution for the first system and backward substitution for the second one) which is a trivial computational process.

Algorithm 1 presents the pseudocode for the factorization phase of the LU algorithm, where the **L** and **U** factors are stored in place, while Algorithm 2 and Algorithm 3 present the pseudocode for the forward and backward substitution for the solution of the triangular systems. As we can observe, the factorization phase of the LU algorithm requires  $\frac{2n^3}{3}$  operations, rendering the decomposition phase a computationally demanding process with the increasing size of the system matrix.

On the other hand, if matrix  $\mathbf{A}$  is SPD, it allows for a special factorization and the Cholesky decomposition can be employed. Cholesky decomposition factors the system matrix into  $\mathbf{A} = \mathbf{L}\mathbf{L}^T$  and the original system is transformed into the

#### **Algorithm 2** Forward substitution for solution of a lower triangular system

```

\begin{aligned} & \textbf{for } i = 0 : n - 1 \ \textbf{do} \\ & y(i) = b(i); \\ & \textbf{for } j = 0 : i - 1 \ \textbf{do} \\ & y(i) -= L(i, j) * y(j); \\ & \textbf{end for} \\ & y(i) \neq L(i, i); \\ & \textbf{end for} \end{aligned}

```

### **Algorithm 3** Backward substitution for solution of an upper triangular system

```

egin{aligned} & 	extbf{for } i = n-1:0 \ 	extbf{do} \ & 	extbf{x}(i) = 	extbf{y}(i); \ & 	extbf{for } j = i+1:n-1 \ 	extbf{do} \ & 	extbf{x}(i) -= 	extbf{U}(i, j) * 	extbf{x}(j); \ & 	extbf{end for} \ & 	extbf{x}(i) \ /= 	extbf{U}(i, i); \ & 	extbf{end for} \end{aligned}

```

### Algorithm 4 Factorization phase for the Cholesky algorithm

```

\begin{array}{l} \textbf{for } i = 1: n-1 \ \textbf{do} \\ \textbf{for } j = 0: i \ \textbf{do} \\ \textbf{s} = 0 \\ \textbf{for } k = 0: j-1 \ \textbf{do} \\ \textbf{s} + = L[i * n + k] * L[j * n + k]; \\ \textbf{if } i = = j \ \textbf{then} \\ L[i * n + j] = \operatorname{sqrt}(A[i * n + i] - s) \\ \textbf{else} \\ L[i * n + j] = (1.0 \ / \ L[j * n + j] * (A[i * n + j] - s)); \\ \textbf{end if} \\ \textbf{end for} \\ \textbf{end for} \\ \textbf{end for} \\ \textbf{end for} \end{array}

```

following equivalent systems:

$$\mathbf{L}\mathbf{y} = \mathbf{b}$$

$\mathbf{L}^T\mathbf{x} = \mathbf{v}$

Algorithm 4 presents the pseudocode for the decomposition phase of Cholesky factorization. Again, after matrix factorization, the resulting linear systems are solved by employing Algorithm 2 and Algorithm 3. As we can observe, Cholesky factorization is more efficient than LU factorization, requiring  $\frac{n^3}{3}$  operations and half the amount of memory storage for saving the matrix factors.

The main advantages of direct methods are their robustness and the fact that once the factorization is completed, the solution of the linear system, even with multiple right hand side vectors, is a trivial process as long as the system matrix remains the same. However, direct methods present superlinear scaling both in

computational and memory requirements with the increasing size of the linear system, which rules them out for large-scale linear systems.

## 3.2 Iterative Methods

Iterative methods belong to the general category of relaxation methods. Starting with an initial solution guess, they provide a partial solution in each step which eventually converge to the desired solution, with a predefined accuracy level. Iterative methods can be categorized as follows:

• Stationary methods that solve a linear system with a matrix that approximates the original one through a series of steps that try to minimize the error of the result. The approximation matrix is usually a decomposition of the initial matrix that allows for more efficient solution. Among the most well-known stationary iterative methods is Jacobi, Gauss-Seidel, and Successive Over-Relaxation (SOR). If  $\mathbf{A} = \mathbf{D} + \mathbf{L} + \mathbf{U}$  is a decomposition of the system matrix in its diagonal ( $\mathbf{D}$ ), upper triangular ( $\mathbf{U}$ ), and lower triangular ( $\mathbf{L}$ ) parts, the approximation for each of the aforementioned iterative method is presented below:

- Jacobi:

$$\mathbf{x}^{(k+1)} = \mathbf{D}^{-1}(\mathbf{b} - \mathbf{R}\mathbf{x}^{(k)})$$

, where  $\mathbf{R} = \mathbf{U} + \mathbf{L}$ .

- Gauss-Seidel:

$$\mathbf{x}^{(k+1)} = \mathbf{L}_*^{-1}(\mathbf{b} - \mathbf{U}\mathbf{x}^{(k)})$$

, where  $\mathbf{L}_* = \mathbf{L} + \mathbf{D}$ .

- SOR:

$$\mathbf{x}^{(k+1)} = (\mathbf{D} + \omega \mathbf{L})^{-1} (\omega \mathbf{b} - (\omega \mathbf{U} + (\omega - 1)\mathbf{D})) \mathbf{x}^{(k)} = \mathbf{L}_w \mathbf{x}^{(k)} + \mathbf{c}$$

, where  $\mathbf{L}_w = -(\mathbf{D} + \omega \mathbf{L})^{-1} (\omega \mathbf{U} + (\omega - 1)\mathbf{D})$ ,  $\mathbf{c} = (\mathbf{D} + \omega \mathbf{L})^{-1} \omega \mathbf{b}$ , and  $0 < \omega < 2$ .

• Non-stationary (or Krylov-subspace) methods: They form a basis of the sequence of successive matrix powers times the initial residual, which is called the Krylov sequence. Then, the approximations to the solution are formed by minimizing the residual over the subspace formed. Typical examples of Krylov-subspace methods are the Conjugate Gradient (CG), the Generalized Minimal Residual Method (GMRES), and the Biconjugate Gradient Method (BiCG). The CG

method is applicable to SPD systems while GMRES and BiCG are applicable on non-symmetric problems.

We are mainly interested in SPD matrices as this is the type of matrices involved in linear systems arising from power grid analysis. In the next section we will provide a detailed description of the CG iterative method that is applicable on SPD linear systems.

## 3.2.1 Conjugate Gradient Algorithm

The CG method is the first Krylov-subspace iterative method that was developed for SPD matrices [31]. The idea behind the CG algorithm is based on the theory of global minimization and orthogonal polynomials. Through a number of iterations, the CG method aims to minimize the A-norm:

$$\parallel x_i - x \parallel^2_{\mathbf{A}} \equiv (x_i - x, \mathbf{A}(x_i - x))$$

for  $x_i$  that are in the Krylov subspace  $K_i(\mathbf{A}, r_0) \equiv \{r_0, \dots, \mathbf{A}^{i-1}r_0\}$ . The CG method approximates the solution of the linear system by computing a series of residual vectors, where in each step the current residual vector is orthogonal to the space of the previously generated residuals. At its final iteration, the solution vector approximates the real solution of the initial system in a predefined accuracy level.

Regarding the convergence rate of CG, it can be shown [4] that the required number of iterations (for a given initial guess and convergence tolerance) is bounded in terms of the spectral condition number  $\kappa_2(\mathbf{A}) = \|\mathbf{A}\|_2 \|\mathbf{A}^{-1}\|_2 \ge 1$  - specifically, it is  $\mathcal{O}(\sqrt{\kappa_2(\mathbf{A})})$ , which for SPD matrices becomes  $\kappa_2(\mathbf{A}) = \frac{\lambda_{max}(\mathbf{A})}{\lambda_{min}(\mathbf{A})}$  where  $\lambda_{max}(\mathbf{A})$ ,  $\lambda_{min}(\mathbf{A})$  are the maximum and minimum eigenvalues of  $\mathbf{A}$  respectively. This means that convergence of CG is fast when  $\kappa_2(\mathbf{A}) \simeq 1$  and slow when  $\kappa_2(\mathbf{A}) \gg 1$ .

The main drawback of iterative methods is the unknown number of steps that are required for convergence (convergence rate). The convergence rate of iterative methods depends on the spectral properties of the matrix  $\mathbf{A}$  of the linear system. In order to improve these properties, a mechanism that transforms the original matrix

to a matrix with more favorable properties is required. This process is known as preconditioning.

## 3.2.2 Preconditioning

Preconditioning is a technique that is used to transform the original linear system into one with more favorable spectral properties, and is essential to guarantee fast and robust convergence of an iterative method. In the case of linear systems involving SPD matrices, the rate of convergence of the conjugate gradient method depends on the distribution of the eigenvalues of **A**. Hopefully, the transformed (preconditioned) matrix will have a smaller spectral condition number, and/or eigenvalues clustered around 1. Nevertheless, a clustered spectrum (away from 0) often results in rapid convergence, particularly when the preconditioned matrix is close to normal. If **M** denotes the preconditioner matrix, then the following linear system (left preconditioned system) has the same solution with the system from (3.1) but is easier to solve:

$$\mathbf{M}^{-1}\mathbf{A}\mathbf{x} = \mathbf{b} \tag{3.2}$$

In the case of Krylov subspace methods like the CG algorithm, it is not necessary to form the preconditioned matrix  $\mathbf{M}^{-1}\mathbf{A}$  explicitly, as it would be too expensive and we would lose the sparsity of the matrix. Instead, matrix-vector products are required and a series of linear system solutions of the form:

$$\mathbf{Mz} = \mathbf{r} \tag{3.3}$$

Algorithm 5 describes the Preconditioned Conjugate Gradient (PCG) method for the solution of an SPD linear system  $\mathbf{A}\mathbf{x} = \mathbf{b}$ . As we can observe, PCG entails a large degree of parallelism as it comprises only matrix-vector and vector-vector products that make the method an ideal candidate for mapping onto parallel architectures. The preconditioner solve step  $\mathbf{M}\mathbf{z} = \mathbf{r}$  in every iteration (line 6) effectively modifies the CG algorithm to solve the system  $\mathbf{M}^{-1}\mathbf{A}\mathbf{x} = \mathbf{M}^{-1}\mathbf{b}$ , which has the same solution as the original one  $\mathbf{A}\mathbf{x} = \mathbf{b}$  [4]. In this case, the computationally demanding part of

## Algorithm 5 Preconditioned Conjugate Gradients

```

1: \mathbf{x} = \text{initial guess } \mathbf{x}^{(0)}

2: \mathbf{r} = \mathbf{b} - \mathbf{A}\mathbf{x}

3: iter = 0

4: repeat

iter = iter + 1

Solve Mz = r

(Preconditioner Solve Step)

6:

7:

\rho = \mathbf{r} \cdot \mathbf{z}

if iter == 1 then

9:

\mathbf{p} = \mathbf{z}

else

10:

\beta = \rho/\rho 1

11:

\mathbf{p} = \mathbf{z} + \beta \mathbf{p}

12:

end if

13:

14:

\rho 1 = \rho

15:

\mathbf{q} = \mathbf{A}\mathbf{p}

\alpha = \rho/(\mathbf{p} \cdot \mathbf{q})

16:

17:

\mathbf{x} = \mathbf{x} + \alpha \mathbf{p}

18:

\mathbf{r} = \mathbf{r} - \alpha \mathbf{q}

19: until convergence

```

the algorithm is the preconditioner solve step, which effectively receives the whole burden of the algorithm. In general, the condition number  $\kappa_2(\mathbf{A})$  and the number of iterations grows as a function of the matrix dimension N. If  $\mathbf{M}$  approximates  $\mathbf{A}$  in some way, then  $\mathbf{M}^{-1} \simeq \mathbf{A}^{-1}$  and  $\kappa_2(\mathbf{M}^{-1}\mathbf{A}) \simeq \kappa_2(\mathbf{I}) = 1$ , which makes the PCG converge quickly as the number of iterations become independent of the matrix dimension (i.e. they are bounded by a constant,  $\mathcal{O}(1)$ ). So the motivation behind preconditioning is to find a matrix  $\mathbf{M}$  with the following properties: 1) the convergence rate of the preconditioned system  $\mathbf{M}^{-1}\mathbf{A}\mathbf{x} = \mathbf{M}^{-1}\mathbf{b}$  is fast, and 2) a linear system involving  $\mathbf{M}$  (i.e.  $\mathbf{M}\mathbf{z} = \mathbf{r}$ ) can be solved much more efficiently (in  $\mathcal{O}(N)$  or slightly higher number of operations) than the original system involving  $\mathbf{A}$ , in which case the performance of PCG will be optimal or very close to optimal.

An additional salient feature for a preconditioner matrix is the degree of parallelism that the solution of the linear system  $\mathbf{Mz} = \mathbf{r}$  must entail. The last characteristic is quite significant in order allow for efficient mapping of the preconditioner solve step onto parallel architectures.

#### **Preconditioning Algorithms**

As was aforementioned, the preconditioner matrix  $\mathbf{M}$  must provide a good approximation to the system matrix  $\mathbf{A}$ . The optimal preconditioner matrix is  $\mathbf{M} = \mathbf{A}$ , where the product  $\mathbf{M}^{-1}\mathbf{A}$  has a condition number equal to 1. However, the preconditioner solve step requires solving the system  $\mathbf{M}\mathbf{x} = \mathbf{b}$ , which involves again the problem of the solution of a linear system with  $\mathbf{A}$  as a system matrix.

As we can deduce, finding an optimal preconditioner is not trivial. A large number of research approaches focused on developing general purpose preconditioners. Although such preconditioners can be used as black boxes without specific knowledge of the underlying problem, their efficacy in terms of the convergence rate for every problem is not guaranteed. On the other hand, problem-tailored preconditioners can provide a great acceleration of the convergence rate. However, developing such a preconditioner requires that the underlying problem has a special structure, which is not the case for most problems.

The simplest preconditioner is a diagonal matrix whose diagonal entries are identical to those of **A**. The preconditioner matrix is known as the diagonalor Jacobi preconditioner and its application requires inverting a diagonal matrix. Although inverting a diagonal matrix is a trivial process, the Jacobi preconditioner often offers mediocre results.

Another class of preconditioning algorithms are algorithms based on incomplete matrix factorizations. Incomplete LU preconditioning can be used in generic linear systems whereas Incomplete Cholesky preconditioning can be used in the case of an SPD system. Both are variants of the factorization methods (namely LU and Cholesky) that were described in Section 3.1. The Incomplete Cholesky algorithm creates a preconditioner matrix  $\mathbf{M} = \mathbf{L}\mathbf{L}^T$ , where  $\mathbf{L}$  is a lower triangular matrix. Its main difference with the Cholesky factorization is that little or no fill-ins are allowed in the  $\mathbf{L}$  factor. If no fill-ins are allowed,  $\mathbf{L}$  is restricted to have the same sparsity pattern as  $\mathbf{A}$  and all other elements are discarded. In this case, the solution of the preconditioner solve step  $\mathbf{M}\mathbf{z} = \mathbf{r} \Rightarrow \mathbf{L}\mathbf{L}^T\mathbf{z} = \mathbf{r}$  is computed with forward

and backward substitution. Unfortunately, the Incomplete Cholesky is not always a stable preconditioner.

The need for more elaborate preconditioning algorithms enforced researchers to deviate from the standard practice of incomplete factorizations and use more advanced techniques like Sparse Approximate Inverse or Multigrid preconditioners. Sparse Approximate Inverse (SPAI) preconditioners [8] compute a preconditioner matrix  $\mathbf{M} \approx \mathbf{A}^{-1}$  as the solution of the constrained minimization problem:

$$\min_{\mathbf{M} \in S} \| \mathbf{I} - \mathbf{A} \mathbf{M} \|_F$$

where S is a set of sparsity pattern and  $|||_F$  is the Frobenius norm of a matrix. The advantage of this method is that after construction, preconditioner's application (preconditioner solve step) requires only a matrix-vector multiplication as we already have  $\mathbf{M}^{-1}$ , making a Sparse Approximate Inverse preconditioner extremely efficient. However, the main problem with this type of preconditioners is that finding an appropriate sparsity pattern is not easy. An intuitive approach would be one to select the sparsity pattern of system matrix  $\mathbf{A}$ . However, this does not work well for complicated problems, as the preconditioner may require a larger number of non-zero elements in order to improve convergence.

On the other hand, multigrid algorithms [7] create a preconditioner by approximating the original matrix through a hierarchy of coarser matrices (or coarser grids). There are both geometric and algebraic approaches, with the latter taking advantage of the a-priori knowledge of the geometry of the underlying problem and the latter working solely on the system matrix. The main idea behind multigrid methods when used as preconditioners is to accelerate convergence of the iterative method by global correction from time to time. They are iterative methods on their own and consist of the following steps:

- Smoothing that aims at reducing high frequency errors, for example using a few iterations of the Gauss–Seidel method.

- Restriction, which is the downsampling of the residual error to a coarser grid.

• Interpolation (or prolongation), which interpolates (maps) the correction computed on a coarser grid into a finer grid.

The main advantage of multigrid is that it often scales linearly with the number of discrete nodes used, which means that it can solve these problems to a given accuracy in a number of operations that is proportional to the number of unknowns. However, its main drawbacks is that multigrid is an iterative method on its own and that the prolongation and restriction operators are not rigorously defined for every problem. As a result, they can tax the ability for convergence of an iterative method when used as preconditioning mechanisms.

# 3.3 Solution of Linear Systems on Parallel Architectures

With the advent of massively parallel architectures, there has been an increasing demand for linear system solution algorithms that could take advantage of the computational resources that the former offer. Research works [18] and [49] present a parallel implementation of the LU and the Cholesky factorization direct algorithms on a GPU. Authors in [18] reduce the problem to a series of rasterization problems and use appropriate data representations to match the blocked rasterization order and cache pre-fetch technology of a GPU. They exploit high spatial coherence between elementary row operations and use fast parallel data transfer techniques to move data on GPUs. In the same context, authors in [49] organize blocks of nodes of a sparse matrix in the supernode data structure for GPU and propose a queue-based approach for the generation and scheduling of GPU tasks with dense linear algebraic operations in order to accelerate factorization. The main problems with the aforementioned approaches is that they entail a small degree of parallelism both in the factorization and the solution phase. As a result, they are not good candidates for mapping onto a parallel architecture. In addition, their large memory demands can exceed the main memory available on a GPU, making their execution infeasible.

On the other hand, mapping an iterative method on a parallel architecture is a trivial process as both the matrix-vector and the vector-vector products entail a large degree of parallelism. The only delicate part is the preconditioner solve step, which is not amenable for mapping onto a parallel architecture if the solution of the preconditioner matrix M does not contain a large degree of parallelism. Incomplete factorization-based preconditioners require the construction of the preconditioner and the triangular solution steps. For both the Incomplete LU and the Incomplete Cholesky preconditioners, the factorization phase is amenable to porting on a parallel architecture. However, the triangular solution step exhibits a little degree of parallelism. As a result, in a parallel implementation that involves a GPU, the triangular solution step is performed at the CPU and the solution vector is transferred back to the GPU, which can greatly limit acceleration [23]. This is not the case for multigrid preconditioners that exhibit a large degree of parallelism, as the internal grid can be mapped on the computational grid of a GPU quite well. However, the drawbacks that were mentioned in Section 3.2.2 hinder its wide adoption as a parallel preconditioning method.

Based on the aforementioned observations, we can deduce that finding a preconditioner that will be able to accelerate convergence rate, while at the same time exhibit a large degree of parallelism is not trivial. The following chapters will describe three novel, extremely efficient and highly-parallel preconditioning approaches that in combination with an iterative method can enable analysis of very large-scale power delivery networks on massively parallel architectures.

## Chapter 4

## Power Grid Electrical Simulation

## 4.1 Power Grid Modeling

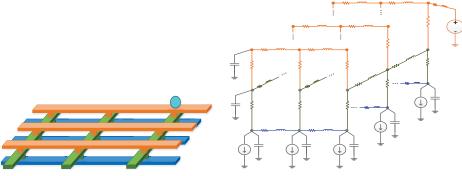

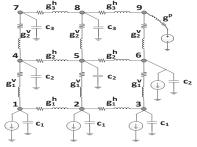

Power grid electrical simulation refers to the process of finding the response of the power delivery network when constant (DC analysis) or time-varying (transient analysis) sources are present. A power delivery network is a multi-layer network that comprises a number of metal lines, with alternating routing in horizontally and vertically directions. The lower-most metal layer connects the power delivery network with the logic gates, whereas the upper metal layer connects the network with the supply voltage. Each IC comprises two power delivery networks: one for the supply voltage (VDD network) and the other for the ground (GND network).

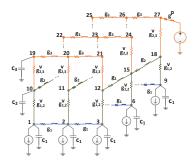

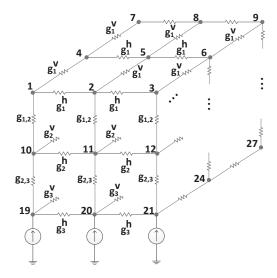

The typical model of a power grid is obtained by modeling each wire segment (between two contacts) as a resistance in series with an inductance, with capacitances to ground at both contact nodes. Each power bump is modeled as a voltage source while each logic gate is modeled as a current source. Fig. 4-1(i) depicts the geometry structure of a 3D power grid for the VDD supply with 3 layers and Fig. 4-1(ii) depicts its equivalent model for electrical analysis.

Let the electrical model of the power grid be composed of b composite R-L branches and N non-supply nodes. If we apply the Modified Nodal Analysis (MNA) method, we formulate the systems of linear equations (4.1) and (4.2), where the first is for DC and the second is for transient analysis:

- (i) Geometry structure of a 3D power grid with 3 layers. Vias represent connections between adjacent metal layers while the blue circle represents the solder bump.

- (ii) Equivalent model for electrical analysis

Figure 4-1: Example of a power delivery network with 3 horizontal and 3 vertical rails, along with its equivalent model for electrical analysis. The figure depicts only the VDD rails.

$$\mathbf{G}\mathbf{x} = \mathbf{e} \tag{4.1}$$

$$\tilde{\mathbf{G}}\mathbf{x}(t) + \tilde{\mathbf{C}}\dot{\mathbf{x}}(t) = \mathbf{e}(t) \tag{4.2}$$

where

$$ilde{\mathbf{G}} = \left[egin{array}{cc} \mathbf{0} & \mathbf{A}_{rl} \ -\mathbf{A}_{rl}^T & \mathbf{R}_b \end{array}

ight]$$

$$ilde{\mathbf{C}} = \left[ egin{array}{cc} \mathbf{C}_n & \mathbf{0} \ \mathbf{0} & \mathbf{L}_b \end{array}

ight]$$

$$\mathbf{x}(t) = \left[ egin{array}{c} \mathbf{v}_n(t) \ \mathbf{i}_b(t) \end{array}

ight]$$

$$\mathbf{e}(t) = \left[ egin{array}{c} \mathbf{e}_n(t) \\ \mathbf{0} \end{array}

ight]$$

In the systems described in (4.1) and (4.2),  $\mathbf{A}_{rl}$  is the  $N \times b$  incidence matrix of the

directed composite R-L branches (with elements  $a_{ij} = \pm 1$  or  $a_{ij} = 0$  depending on whether branch j leaves/enters or is not incident with node i),  $\mathbf{v}_n(t)$ ,  $\mathbf{i}_b(t)$  are the  $N \times 1$  and  $b \times 1$  vectors of node voltages and branch currents respectively,  $\mathbf{e}_n(t)$  is a  $N \times 1$  vector of excitations from independent sources at the nodes,  $\mathbf{C}_n$  is a  $N \times N$  diagonal matrix of the node capacitances, and  $\mathbf{R}_b$ ,  $\mathbf{L}_b$  are diagonal  $b \times b$  matrices of the resistances and self-inductances of the composite R-L branches.

The system from (4.2) represents a non-linear system of equations. Using the Backward-Euler approximation we obtain from (4.2) the following discretized system of linear algebraic equations:

$$(\tilde{\mathbf{G}} + \frac{\tilde{\mathbf{C}}}{h_k})\mathbf{x}(h_k) = \mathbf{e}(h_k) + \frac{\tilde{\mathbf{C}}}{h_k}\mathbf{x}(h_{k-1})$$

(4.3)

where  $h_k$ , k = 1,... is the chosen time-step that may in general vary during the analysis. By block-matrix operations on the above system we obtain the following system of coupled recursive equations [11]:

$$(\mathbf{A}_{rl}(\mathbf{R}_{b} + \frac{\mathbf{L}_{b}}{h_{k}})^{-1}\mathbf{A}_{rl}^{T} + \frac{\mathbf{C}_{n}}{h_{k}})\mathbf{v}_{n}(h_{k}) = \frac{\mathbf{C}_{n}}{h_{k}}\mathbf{v}_{n}(h_{k-1}) - (\mathbf{A}_{rl}(\mathbf{R}_{b} + \frac{\mathbf{L}_{b}}{h_{k}})^{-1}\frac{\mathbf{L}_{b}}{h_{k}}\mathbf{i}_{b}(h_{k-1}) + \mathbf{e}(h_{k})$$

$$(4.4i)$$

$$\mathbf{i}_{b}(h_{k}) = (\mathbf{R}_{b} + \frac{\mathbf{L}_{b}}{h_{k}})^{-1}\frac{\mathbf{L}_{b}}{h_{k}}\mathbf{i}_{b}(h_{k-1}) + (\mathbf{R}_{b} + \frac{\mathbf{L}_{b}}{h_{k}})^{-1}\mathbf{A}_{rl}^{T}\mathbf{v}_{n}(h_{k})$$

$$(4.4ii)$$

At each time-step  $h_k$  we have to solve the  $N \times N$  linear system (4.4i) with system matrix  $\mathbf{A} \equiv \mathbf{A}_{rl} (\mathbf{R}_b + \frac{\mathbf{L}_b}{h_k})^{-1} \mathbf{A}_{rl}^T + \frac{\mathbf{C}_n}{h_k}$  and then find branch currents from (4.4ii). If we neglect inductances and model the grid as an RC circuit, the system (4.4) reduces to the following system:

$$(\mathbf{A}_{rl}\mathbf{R}_b^{-1}\mathbf{A}_{rl}^T + \frac{\mathbf{C}_n}{h_k})\mathbf{v}_n(h_k) = \frac{\mathbf{C}_n}{h_k}\mathbf{v}_n(h_{k-1}) + \mathbf{e}(h_k)$$

(4.5)

In both DC and transient analysis, the system matrix can be shown to be an SPD matrix, which means that efficient direct or iterative methods such as the

Cholesky factorization or the method of PCG can be employed for its solution. However, the sheer size of power delivery networks from large-scale ICs mandates utilization of preconditioned iterative methods instead of direct methods due to the large computational and memory demands of the latter.

In addition, electrical simulation with variable time-step completely rules out direct methods as they require a matrix re-factorization each time the time-step is modified, thus increasing their computational demands especially for large-scale power delivery networks. In addition, a fixed time-step is almost never used in practice because it becomes very inefficient to constantly simulate during long intervals of low activity. All practical implementations of integration techniques for ODEs employ a variable or adaptive time-step mechanism [9]. In those cases, the reusability of matrix factorization in direct methods ceases to exist. This is true even for general-purpose preconditioning mechanisms that are based on matrix factorization (such as the Incomplete Cholesky) preconditioner that was described in Chapter 3. Although the computational demands of calculating the incomplete factorization are significantly lower than that for full factorization, this represents an additional overhead for the corresponding simulation algorithm.

As a result, finding a preconditioning mechanism that will be efficient for analysis with variable time-step both in terms of computational and memory demands is essential in order to allow for the wide adoption of iterative linear system solution algorithms. In addition, any preconditioning mechanism has to offer a significant degree of parallelism in order to allow for mapping onto parallel architectures.

Fortunately, as we will describe, matrices arising from power delivery networks can be well-approximated by preconditioners with special structure such that the number of iterations becomes bounded (or very slowly rising), while the preconditioned linear system  $\mathbf{Mz} = \mathbf{r}$  can be solved by applying a Fast Transform in a near-optimal number of operations in a sequential implementation, and even less operations in a parallel environment (owing to the large parallel potential of Fast Transforms as well as other parallelization opportunities).

## 4.2 Related Work

The growing need to simulate large power grids resulted to the design and development of a large number of power grid analysis methods. These methods can be categorized into methods that exploit special structures (such as specific patterns) of the power delivery network and methods that utilize simulation in order to analyze the behavior of the power delivery network. The former category includes algorithms that obtain approximated solutions for the power delivery network, e.g. algorithms that apply the idea of multigrid techniques for solving partial differential equations for power grid analysis [20] [48] [26], Fast Poisson solvers [32], methods based on analysis in the frequency domain [19], stochastic-based algorithms [28], or model order reduction techniques [37] [22]. Although these methods allow for fast analysis of a power delivery network, they lack the desired accuracy (which is very important for late design stage analysis), they do not scale well with the size of the power grid, and in their majority do not provide a large degree of parallelism. As a result, the latter category of algorithms has attracted a lot of interest due to the ability for accurate characterization of the static and dynamic behavior of the power delivery network. Methods that fall into the aforementioned category include methods that utilize direct and iterative solution algorithms.

Direct solution methods are proposed in [45] and [34] that utilize either the LU or the Cholesky decomposition. Although they are robust and achieve the most accurate results, they suffer from a super-linear increase in computational and memory demands with the problem size. In addition, they provide limited room for parallelism, and as a result, they cannot utilize the computational resources of massively parallel architectures.

The need for simulation methods with small memory footprint and efficient parallel execution has led many researchers to deviate from the standard practice of direct factorization methods and present more suitable iterative methods. Research works [11] and [33] have proposed iterative solvers for efficient simulation of power delivery networks. Power grid analysis was first formulated as a symmetric positive

definite system to be solved by PCG in [11], but the preconditioner used was the general-purpose (and inefficient for specialized applications) incomplete Cholesky. A different pattern-based preconditioner was proposed in [33], but it is very simple and heuristic and does not appear to reduce the number of iterations significantly.

Recently, parallel architectures have been utilized to accelerate power grid analysis. Authors in [34] have proposed domain decomposition as a parallel technique for analysis on multi-core architectures. GPUs are used in research approaches [32], [16], and [17] as parallel platforms that enable tackling power analysis of large-scale power networks. Authors in [17] propose multi-grid as a solution method for power grid analysis and they use multi-core and massively parallel Single Instruction Multiple Thread (SIMT) platforms to tackle power grid analysis, while authors in [32] formulate the traditional linear system as a special two-dimension Poisson equation and solve it using analytical expressions based on the FFT algorithm, with GPUs being used to further speed up the algorithm. However, both [32] and [17] only solve very regular grid structures with specialized techniques, which can limit their effectiveness for irregular power delivery networks that are found in late design stages. Instead, we propose to use such a regular structure as preconditioner in order to solve any practical (and possibly irregular) power delivery network.

Preconditioning has lately drawn attention as a method for efficiently tackling the analysis of large-scale and irregular power grid designs. Such a possibility is the topic of research works [16], [42], [25], and [41] for power grid analysis, and [29] in the context of IC thermal simulation. In [16] and [42], the preconditioning has been carried out by multigrid techniques. However, when used as preconditioner for iterative methods, multigrid is not very efficient because it is an iterative method by itself, and also solves a system approximately which can hinder the convergence of PCG. Moreover, some operations of multigrid are not always well-defined (e.g. mapping by interpolation from coarser to finer grids and back, and correction of solutions), and the construction of approximate matrices for all coarser grids is an expensive setup phase which has to be repeated every time the system is reconstructed in each time-step change during transient analysis. Our approaches