#### **UNIVERSITY OF THESSALY**

#### DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

**Master Thesis**

"Study of the effect of optimizations on OpenCL code when executed on different heterogeneous architectures"

**Authors**

**Theocharidis Konstantinos**

Kalogirou Christos

**Supervisor**

Antonopoulos Christos, Assistant Professor

Committee Members

Bellas Nikolaos, Associate Professor

Potamianos Gerasimos, Associate Professor

Volos, July, 2013

Πανεπιστήμιο Θεσσαλίας

Τμήμα Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών

Μεταπτυχιακή Διπλωματική Εργασία

"Μελέτη επίπτωσης βελτιστοποιήσεων σε κώδικα OpenCL κατά την εκτέλεση σε διαφορετικές ετερογενείς αρχιτεκτονικές"

<u>Συγγραφείς</u>

Θεοχαρίδης Κωνσταντίνος

Καλογήρου Χρήστος

Επιβλέπων Καθηγητής

Αντωνόπουλος Χρήστος, Επίκουρος Καθηγητής

Μέλη Επιτροπής

Μπέλλας Νικόλαος, Αναπληρωτής Καθηγητής

Ποταμιάνος Γεράσιμος, Αναπληρωτής Καθηγητής

Βόλος, Ιούλιος, 2013

#### <u>Ευχαριστίες</u>

Θα θέλαμε να ευχαριστήσουμε τους καθηγητές μας, κύριο Αντωνόπουλο Χρήστο, κύριο Μπέλλα Νικόλαο και κύριο Ποταμιάνο Γεράσιμο για τη στενή συνεργασία τους και τη βοήθειά τους. Επίσης θέλουμε να ευχαριστήσουμε τις οικογένειές μας και τους φίλους μας για τη στήριξή τους.

# Περίληψη

Η παρούσα διπλωματική εργασία μελετά την επίδραση διαφόρων βελτιστοποιήσεων σε κώδικα OpenCL πάνω σε διαφορετικές ετερογενείς αρχιτεκτονικές. Το ενδιαφέρον της επιστημονικής κοινότητας προς τις τελευταίες προέκυψε με τους περιορισμούς που έθεσε η κατανάλωση ισχύος και η παραγωγή θερμότητας, με την παύση της ισχύος του νόμου του Moore.

Αρχικά, ο παράλληλος προγραμματισμός επιτυγχάνονταν μέσω multi-core επεξεργαστών, many-core καρτών γραφικών, αλλά και άλλων επιταχυντών, όπως τα FPGAs. Το πρόβλημα που δημιουργήθηκε όμως ήταν ότι κάθε μία από αυτές τις αρχιτεκτονικές είχε το δικό της προγραμματιστικό μοντέλο και ο κώδικας χρειαζόταν να ξαναγραφεί για να είναι μεταφέρσιμος ανάμεσα στις αρχιτεκτονικές. Το γεγονός αυτό οδήγησε στην δημιουργία των ετερογενών συστημάτων και για αυτό το 2009, η Khronos έβγαλε το μοντέλο προγραμματισμού OpenCL. Το OpenCL εγγυάται πως ο ίδιος κώδικάς τρέχει ορθά σε όλες τις αρχιτεκτονικές, αλλά δεν μπορεί να εγγυηθεί τίποτα για την απόδοσή του. Συνεπώς, άρχισαν να διερευνούνται διάφορες τεχνικές βελτιστοποίησης οι οποίες να είναι ικανές να προσαρμόσουν την απόδοση μιας αρχιτεκτονικής σε αυτήν μιας άλλης.

Η προσπάθεια αυτή αποτέλεσε και το κίνητρο της εργασίας μας, στην οποία μελετούμε διάφορες βελτιστοποιήσεις και διάφορα υπολογιστικά πρότυπα εφαρμογών για να βρούμε συγκεκριμένα, ποιες τεχνικές βελτιστοποίησης ευνοούν ποια υπολογιστικά πρότυπα και μέσω ποιων αρχιτεκτονικών γίνεται κάτι τέτοιο. Ιδιαίτερη σημασία έχει το γεγονός ότι πέρα από τα πειραματικά αποτελέσματα που παρατίθενται, γίνεται ιδιαίτερη προσπάθεια στο να αιτιολογηθεί ο λόγος που αυτά προέκυψαν.

Οι τεχνικές βελτιστοποίησης οι οποίες εξετάστηκαν ήταν οι α) Geometry, b) Vectorization, c) Loops και d) Branches και οι εφαρμογές πάνω στις οποίες εξετάστηκαν ήταν οι lud, crc, needle, srad και bfs. Οι εφαρμογές αυτές αποτελούν μέρος των 13 Dwarfs του Berkeley. Οι αρχιτεκτονικές οι οποίες χρησιμοποιήθηκαν ήταν ένας Intel Xeon E5645, μία NVIDIA GeForce GTX480 και μία AMD Cayman.

## Abstract

This master thesis studies the effect of different optimizations on OpenCL code when executed on different heterogeneous architectures. The interest of scientific community towards the latter arose with the saturation of Moore's law. This happened as frequency scaling began to reach its limits due to physical constraints such as power consumption and heat generation.

Firstly, the parallel programming achieved via multi-core CPUs, many-core GPUs and other accelerator devices, like FPGAs. However, the problem was that each one of such architectures had its private programming model and the code needed to be rewritten so as to be portable among architectures. This fact led to the genesis of heterogeneous systems and for this reason, in 2009, the Khronos consortium introduced OpenCL, a programming standard which guarantees functional, but not performance portability among different architectures. Therefore, developers began to search for optimizations, whose implementation, can adapt the performance of one accelerator device to the same levels of another.

This searching stimulated our interest for this project, through which we evaluate various optimizations and computational patterns in order to reveal which specific optimization techniques benefit which certain computational patterns and on which certain architectures this happens. It is very important that the underlying cause-result relation, for optimizations and parametric choices improving or degrading the performance on a particular architecture, is also sought out.

The optimization techniques that examined were the a) *Geometry*, b) *Vectorization*, c) *Loops* and d) *Branches* and the applications on which they are applied were a subset of the 13 Berkeley dwarfs. These were the applications *lud*, *crc*, *needle*, *srad* and *bfs*. Last but not least, the architectural devices that used were an Intel Xeon E5645 CPU, an NVIDIA GeForce GTX480 GPU and an AMD Cayman GPU.

# Table of contents

| Chapter 1 8                                     | 3 |

|-------------------------------------------------|---|

| Introduction                                    | 3 |

| 1.1 Contributions                               | ) |

| 1.2 Thesis Outline                              | ) |

| Chapter 2 1                                     | l |

| Hardware Architectures                          | l |

| 2.1 Intel Xeon E5645                            | l |

| 2.2 NVIDIA GeForce GTX480                       | 2 |

| 2.3 AMD Cayman architecture                     | 5 |

| 2.4 Comparison of a GPU and a CPU               | ) |

| Chapter 3 21                                    | l |

| Basic Concepts of Parallel Computing and OpenCL | l |

| 3.1 Parallel Computing                          | l |

| 3.1.1 Flynn's Taxonomy                          | l |

| 3.1.2 Levels of Parallelism                     | 2 |

| 3.1.3 Processor Architectures                   | 2 |

| 3.2 Open Computing Language (OpenCL)            | 1 |

| 3.2.1 Platform Model                            | 1 |

| 3.2.2 Execution Model                           | 5 |

| 3.2.3 Memory Model                              | 7 |

| Chapter 4                                       | 3 |

| The 13 Dwarfs                                   | 3 |

| Chapter 5                                       | 1 |

| Related Work                                    | 1 |

| Chapter 6                                       | 1 |

| Analysis of optimizations on dwarf benchmarks   | 1 |

| 6.1 lud                                         | 5 |

| 6.1.1 Analysis of <i>lud_perimeter</i> kernel   | 5 |

| 6.1.1.1 Data Dependencies                       | 5 |

| 6.1.1.2 Basic code segment                      | 5 |

| 6.1.1.3 Optimization Efforts and Results               |  |

|--------------------------------------------------------|--|

| 6.1.2 Analysis of <i>lud_internal</i> kernel           |  |

| 6.1.2.1 Data Dependencies                              |  |

| 6.1.2.2 Basic code segment                             |  |

| 6.1.2.3 Optimization Efforts and Results               |  |

| 6.2 crc                                                |  |

| 6.2.1 Analysis of <i>compute</i> kernel                |  |

| 6.2.1.1 Data Dependencies                              |  |

| 6.2.1.2 Basic code segment                             |  |

| 6.2.1.3 Optimization Efforts and Results               |  |

| 6.2.1.3 Unfeasible Optimizations                       |  |

| 6.3 needle                                             |  |

| 6.3.1 Analysis of <i>needle_opencl_shared_1</i> kernel |  |

| 6.3.1.1 Data Dependencies                              |  |

| 6.3.1.2 Basic code segment                             |  |

| 6.3.1.3 Optimization Efforts and Results               |  |

| 6.3.1.4 Unfeasible Optimizations                       |  |

| 6.4 srad                                               |  |

| 6.4.1 Analysis of <i>srad_cuda_1</i> kernel            |  |

| 6.4.1.1 Data Dependencies                              |  |

| 6.4.1.2 Basic code segment                             |  |

| 6.4.1.3 Optimization Efforts and Results               |  |

| 6.4.1.3 Unfeasible Optimizations                       |  |

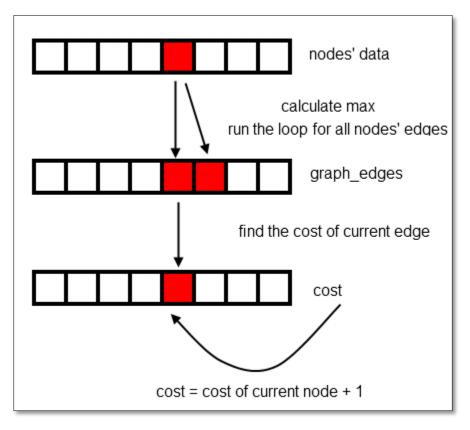

| 6.5 bfs                                                |  |

| 6.5.1 Analysis of <i>kernel1</i> kernel                |  |

| 6.5.1.1 Data Dependencies                              |  |

| 6.5.1.2 Basic code segment                             |  |

| 6.5.1.3 Optimization Efforts and Results               |  |

| Chapter 7                                              |  |

| Conclusion                                             |  |

| References                                             |  |

## **Chapter 1**

## Introduction

According to Moore's Law, the number of transistors on a chip roughly doubles every two years. This law has stayed valid over the years by cramming more and more transistors into the same core. As frequency scaling began to reach its limits due to physical constraints such as power consumption and heat generation, the area of chip, known as "Dark Silicon" [13], which can't be powered at the same time with the others due to power limitations, started to increase dramatically. It is characteristic that studies reveal that the amount of dark silicon in 22nm technology is around 20% and it predicts it will be more than 50% at 8nm. Therefore, the question is, what is the point in scaling down and increasing the number of transistors per chip if we can't use them? This question led the scientific community to focus on the idea of heterogeneous systems and parallel computing.

The many-core CPU system, such as that of Intel i7 processor technology and the many-core architectures that support general purpose programming on GPUs via appropriate programming models, such as the CUDA (Compute Unified Device Architecture) programming model of NVIDIA, are two fundamental paradigms that support parallelism. However, the interest for better performance and parallelism has now led to heterogeneous computing, involving CPUs and other highly parallel multi-core architectures, like GPUs and FPGAs. The aim of heterogeneous computing is to overcome the problem of dark silicon by exploiting with the best manner the accelerator devices that participate in the computation process. This can be done by assigning each task to the accelerator device that can execute it faster and more power efficiently in comparison with the others. This can be derived from the fact that some devices are more able to execute certain computational patterns than others and the verification of this observation is one of the motivations of this thesis.

Additionally, the arising problems of using different programming models on different architectures pose also for heterogeneous systems. Rewriting the code for each device limits the opportunities for remapping the code on a different architecture, therefore, in 2009, the Khronos [1] consortium introduced OpenCL [2], a programming standard which supports programs that execute across heterogeneous platforms including CPUs, GPUs, FPGAs and other accelerators. The key merit of OpenCL is that it allows programmers to write code which is at least functionally independent of the underlying architecture. It provides easy-to-use abstractions and a broad set of programming APIs which are based on the C language.

However, OpenCL guarantees functional portability but not performance portability. Though OpenCL compliant, each architecture is designed according to specifications decided by its manufacturer. This creates the problem of the same program exhibiting unpredictably different performance on hardware with similar technical capabilities. The hardware can be from different manufacturers or even different generations of the same model. Functional portability is necessary but ensuring performance portability is also essential from a developer's point of view.

If an application written in generic, platform independent OpenCL code, is not fast enough to be usable on a platform, then developers will prefer to program the application in the platform's native language or resort to platform-specific optimizations in OpenCL, which however, may limit both the functional and mainly the performance portability of the code. Nevertheless, the application might have to be written more than once for the application to work optimally on multiple platforms. As this adds to undue overhead for the developers, a more feasible solution will be to optimize the application individually for each platform. This method could be applied for exploring the OpenCL optimization space. Since programs are guaranteed to be portable, developers could tune an OpenCL program which was meant for one architecture and make it optimized for another without losing correctness.

Therefore, the goal of this thesis is to find out if there are specific standard optimizations which are good for specific computational patterns and architectures. Such optimizations could be applied automatically (maybe), alleviating the programmer from the burden of platform-specific optimizations and enhancing code portability. This can be achieved by taking a subset of the 13 OpenCL dwarfs of Berkeley [4] and apply on them a set of optimizations while they are executing on different architectures. Finally, an evaluation and analysis of these results aids in understanding one the respective architecture in more detail and also helps in interpreting which form of computational pattern is more suitable to be optimized for which accelerator device.

### **1.1 Contributions**

The main contribution of this thesis is identifying which optimization parameters prove beneficial or not for the Intel CPU, AMD GPU and NVIDIA GPU devices that used, taking into account the different computational and communicational patterns on which they are tested. Furthermore, one more contribution is the finding of which of the afore-mentioned optimizations can keep the performance portable among which devices.

Moreover, another significant contribution is that the underlying cause-result relation for optimizations and parametric choices improving or degrading the performance on a particular architecture is also sought out. The results of the experiments are analyzed to provide a deeper understanding of the underlying architecture and to realize the suitability of specific optimizations applying on specific computational patterns and architectural devices.

Additionally, along with the afore-mentioned contributions, further gains from this thesis are that the programmers working with OpenCL will have a better understanding of how to develop programs with optimal performance and that the identified parameters can be later incorporated into a compiler which will then automatically apply the specific optimizations based on the target architecture.

## **1.2 Thesis Outline**

This thesis is organized into seven chapters including this chapter. The organization is as follows:

- **<u>Chapter 2</u>**: Presents the hardware architectures that used for the experiments and analyzes the most fundamental architectural parts of them.

- **<u>Chapter 3</u>**: Gives a background perspective of the concepts and terminologies used throughout this thesis. Parallel computing and OpenCL are some of the concepts which are discussed.

- **<u>Chapter 4</u>**: Presents the 13 Dwarfs and explains in brief their characteristics discussing the scientific areas on which they are applied.

- <u>Chapter 5</u>: Discusses the related work. Prior work in exploration of optimization space, benchmarks used, etc., are presented in comparison to the work done in this thesis.

- **<u>Chapter 6</u>**: Presents the experimental results and analyzes the HW/SW interactions on each architecture resulting to the positive and negative effect of optimizations.

- <u>Chapter 7</u>: Concludes this thesis by presenting in detail the conclusions and take-home points and discussing directions of future work.

# **Chapter 2**

## **Hardware Architectures**

This chapter discusses in brief the hardware was used for the experiments. We focus on the characteristics that are more relevant to our study. They were a CPU and two GPUs, an Intel Xeon E5645, a NVIDIA GeForce GTX480 and an AMD Cayman.

### 2.1 Intel Xeon E5645

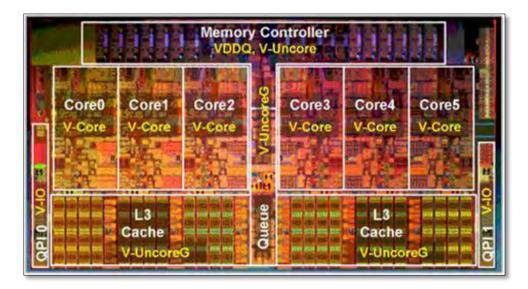

The CPU was used for the experiments belongs to Intel Xeon 5600 family and more specifically its name is Intel Xeon E5645 [9], [10]. Its architecture codename is Westmere and is built in 32nm. The following *Figure 2.1* shows how this processor is organized.

Figure 2.1: The die of the Intel Xeon E5645 [9]

The package contains six cores and each core can run two threads simultaneously if possible, using the Hyperthreading Technology. This means that a maximum number of twelve threads running simultaneously are feasible, if the two threads of a core do not have to share common resources of this core. Otherwise the maximum number of threads is six, one in each core. The standard frequency of the processor is at 2,4GHz but under heavy workload can reach the frequency of 2.67GHz. Also the package contains a Memory Controller with max memory capacity support of 288GB and max bandwidth of 32GB/s.

Like all modern processors, the E5645 has a cache memory with different levels. There are 3 levels of cache. The first level is separate for each core with a capacity of 32KB. The second one is also separate for each core with a capacity of 256KB. The third and last one is the biggest reaching the capacity of 12MB. As it is shown in the picture, is a big part of the chipset and is common for all processors. Its position on the die is crucial and is designed next to the cores for low latency access.

This processor like his predecessors embeds some instruction sets known as SSE. It provides the latest packages the SSE4.1 and SSE4.2 which are single instruction multiple data (SIMD) instructions. The SSE4.1 adds instructions that improve compiler vectorization and provides a hint that can improve memory throughput when reading from uncacheable WC memory type. The SSE4.2 provides a rich set of string and text processing capabilities that traditionally required many opcodes.

### 2.2 NVIDIA GeForce GTX480

Unlike a central processor, a graphic card processor has a totally different architecture. The graphic card that is presented is the NVIDIA GeForce GTX480 [11] using the Fermi architecture.

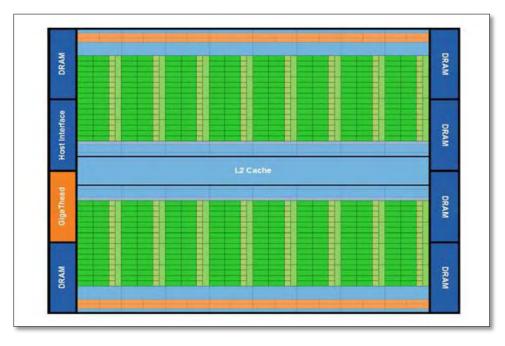

The block diagram of Fermi is shown in *Figure 2.2*. Fermi's lithography is in 40nm. A Fermi GPU contains 15 streaming multiprocessors of 32 CUDA cores each. Each multiprocessor can manage up to 1.536 threads meaning that we can have 23.040 threads in flight (1.536 threads \* 15 multiprocessors). These threads cannot run concurrently but it is useful to have so many threads in order to use another warp for computations when the current warp is accessing the memory. We can run concurrently up to 480 threads (32 CUDA cores \* 15 streaming multiprocessors).

Figure 2.2: Fermi's block diagram [11]

The GPU uses GDDR5 memory which is partitioned in six channels. Each channel's interface is 64 bit and the memory's interface is 384 bit. Fermi can support up to 6GB of GDDR5 RAM and GTX480 has 1536MB partitioned in six chipsets. The host interface is responsible for the connection of the CPU to the GPU via PCIe. The GigaThread global scheduler distributes thread blocks to SM thread schedulers.

The next level is called streaming multiprocessor (SM) and is organized like in <u>Figure 2.3</u>. Each multiprocessor has 32 CUDA cores designed to execute 32 instructions from a bundle of 32 threads, which NVIDIA calls a warp. The cores of a SM also share the registers, the caches, the local memory, and the load/store units (LDST) of their own SM. There are 16 LDST units in each multiprocessor allowing source and destination addresses to be calculated for sixteen threads per clock. The special function units (SFUs) handle complex math operations, such as square roots, reciprocals, sines, and cosines. Each SFU executes one instruction per thread, per clock.

|                                               |                      | Instruction Cach        |             |       |

|-----------------------------------------------|----------------------|-------------------------|-------------|-------|

|                                               | Warp Schedu          | uler                    | Warp Schedu | ler i |

|                                               | Dispatch Ur          | nit                     | Dispatch Un | a:-   |

|                                               | +                    |                         | *           |       |

|                                               |                      | Register File (4096 x 3 | (2-64)      |       |

|                                               | -                    | -                       | -           | -2-   |

|                                               | Core Core            | Core Core               | LD/ST       | SEU   |

|                                               | Core Core            | Gore Core               | LDIST       | Sru   |

| CUDA Core<br>Disaston For<br>Operand Calandar | Core Core            | Core Core               | LOST        | SEL   |

| FP Unit INT Unit                              | Core Core            | Core Core               | LDIST       | SFU   |

| Transit Count                                 | Core Core            | Core Core               | LD/ST       | SFU   |

|                                               | Core Core            | Core Core               | LDST        |       |

|                                               | Core Core Core LD.ST |                         | SFU         |       |

|                                               | Core Core            | Core Core               | LDST        |       |

|                                               | C                    | Interconnect Netwo      | ork,        |       |

|                                               | 64                   | KB Shared Memory / I    | L1 Cache    |       |

|                                               | E-                   | Uniform Cache           |             |       |

Figure 2.3: Fermi's SM [11]

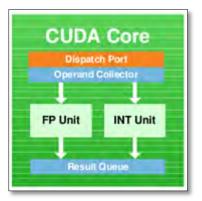

The smallest compute unit is called CUDA core and it is shown in <u>Figure 2.4</u>. It contains a pipelined floating-point unit (FPU), a pipelined integer arithmetic logic unit (ALU), some logic for dispatching instructions and operands to these units, and a queue for holding results. It does not have its own register file or L1 cache like CPUs. It does not even have a load or store unit to access memory. A CUDA core incorporates the new IEEE 754-2008 floating-point standard, providing the fused multiply-add (FMA) instruction for both single and double precision arithmetic, improving the over a multiply-add instruction (MAD) performance by doing a multiplication and addition with a single final rounding step.

Figure 2.4: Fermi's CUDA core [11]

The older GPU generations were designed for graphic applications and there was not a need for a high double precision performance. But HPC applications need double precision arithmetic. Fermi is designed specially to offer unprecedented performance in double precision. It can perform up to 16 double precision fused multiply-add operations per SM per clock.

Fermi also uses a model of dual-issue, as shown in <u>Figure 2.5</u>, to achieve peak hardware performance. Each SM features two warp schedules and two instruction dispatch units. This allows two warps of a SM to be executed concurrently. The schedulers select two warps and issue one instruction from each warp to sixteen cores of this warp. Warps execute independently and the schedulers do not need to check for dependencies from within the instruction stream. The dual-issue model can execute two integer instructions, two floating instructions, or a mix of integer, floating point, load, store and SFU instructions. However, double precision instructions do not support dual dispatch.

|      | Warp Scheduler            | Warp Scheduler            |

|------|---------------------------|---------------------------|

|      | Instruction Dispatch Unit | Instruction Dispatch Unit |

| 1    | Warp 8 instruction 11     | Warp 9 instruction 11     |

|      | Warp 2 instruction 42     | Warp 3 instruction 33     |

|      | Warp 14 instruction 95    | Warp 15 instruction 95    |

| time |                           | 1                         |

| -    | Warp 8 instruction 12     | Warp 9 instruction 12     |

|      | Warp 14 instruction 96    | Warp 3 instruction 34     |

| Ţ    | Warp 2 instruction 43     | Warp 15 instruction 96    |

Figure 2.5: The dual issue model [11]

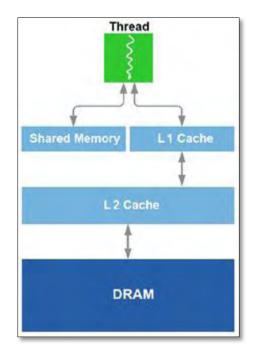

The more recent graphic cards have also different cache levels like processors because of the general purpose C or C++ programs they execute. Traditional GPU architectures support a read-only "load" path for texture operations and a write-only "export" path for pixel data output, an approach that is not appropriate for general purposes programs. The Fermi architecture addresses this challenge by implementing a single unified memory request path for loads and stores, with an L1 cache per SM multiprocessor and unified L2 cache that services all operations. The Fermi's memory hierarchy is shown in *Figure 2.6*.

The first level of Fermi consists of the Shared Memory and the L1 Cache and is shared by the CUDA cores of a multiprocessor but its multiprocessor has its own Shared Memory and L1 Cache. The total capacity of the first level is 64KB. It is configurable and the developer can choose either 16KB of Shared memory and 48KB of L1 Cache or 48KB of Shared memory and 16KB of L1 Cache.

The second level is the L2 Cache. The capacity of this level is 768KB, is shared by all the streaming multiprocessors and services all load, store and texture requests. L2 Cache shares data efficiently across the GPU. In the block diagram of Fermi it is seen that the L2 Cache is wisely put in the center of the chipset. The distance of the L2 Cache is the same for all the multiprocessors and at the same time is very close to them for low latency access.

Figure 2.6: Memory hierarchy of Fermi [11]

Fermi also offers faster atomic operations. Atomic memory operations are important in parallel computing. Fermi secures that atomic operations such as add, min, max and compare-and-swap are performed without the interruption by other threads. These atomic operations performance is up to 20x faster than the previous NVIDIA's generations due to a combination of more atomic units in hardware and the addition of L2 Cache.

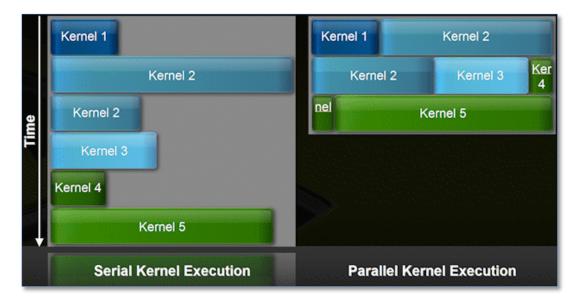

Another important improvement is the technology of the Gigathread Thread Scheduler. This scheduler is responsible for distributing blocks to various SMs. Fermi's scheduler provides greater thread throughput, dramatically faster context switching, concurrent kernel execution and improved thread block scheduling. Context switch is up to 10x faster than previous generation. The concurrent kernel execution is shown in *Figure 2.7*. This improvement allows small kernels of the same application to run concurrently in order to achieve a better GPU utilization.

Figure 2.7: Gigathread Thread Scheduler [11]

### 2.3 AMD Cayman architecture

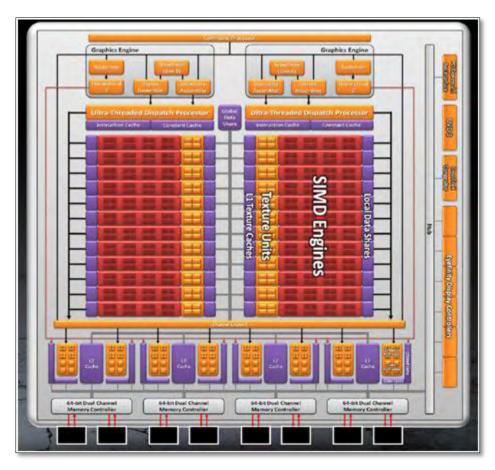

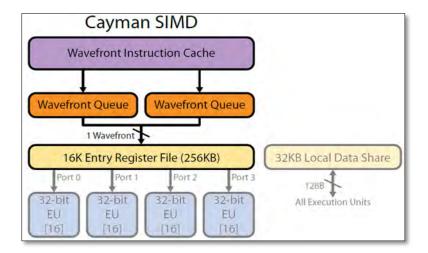

The second graphic card we used was an AMD Cayman [12] and its block diagram is shown in *Figure 2.8*. Cayman packs up in 24 cores, which AMD calls a "SIMD" and are tuned up to 0.88GHz and uses lithography of 40nm. Each core is a 16-wide SIMD processor and each SIMD lane is a 4-wide VLIW. So, there are totally 64 execution units in each core. NVIDIA calls a bundle of 32 threads a warp and these 32 threads must execute the same instruction per cycle. A Cayman has to execute the same instruction for 64 threads and AMD calls it a wavefront.

Each SIMD can have up to 8 work-groups in-flight. Each work-group is 1 or 4 wavefronts meaning the maximum number of wavefronts is 32 for a SIMD and when the dispatch processor schedules two wavefronts for execution in a SIMD, they will run to completion. However, the actual number of wavefronts will depend on the resources needed such as registers and local data share. Each SIMD has 16K registers which have to share between 1-32 wavefronts. These registers hold four 32-bit values, so it is critically important to hold data packed in 128-bit chunks.

Cayman includes two dispatch processors. They are responsible for managing the executing kernels and scheduling wavefronts onto the cores. Each dispatch processor is responsible for the half

of the SIMDs. Also each dispatch can launch 248 wavefronts in-flight. That means that we can have 496 wavefronts with 64 work-items each. So there can be 31.744 work-items in-flight across GPU at a given time.

Figure 2.8: Cayman's block diagram [12]

The Cayman's VLIWs have been fundamentally re-designed in order to match with general purpose workloads. *Fiqure 2.9* shows the new architecture of a SIMD. Cayman's VLIW enhances four pipelines the XYZW pipelines to handle all the operations. AMD's VLIW pipelines are a multi-precision, staggered design that can bypass results between the pipelines. The operations in a VLIW bundle can be independent like a 4-wide SIMD, but this is not necessary.

Figure 2.9: A Cayman's SIMD [12]

The VLIWs are statically scheduled. In contrast with NVIDIA's SM design which requires scheduling between the two issue ports. Fermi has to handle the contention for the shared load-store unit and the special function unit and also executing 64-bit instructions across both execution pipelines. AMD's approach burdens the compiler because it must find substantial instruction level parallelism (ILP) within each work-item. It is more difficult to achieve peak performance on AMD GPUs because static scheduling is less flexible.

One of the biggest problems when programming on GPUs is the bandwidth of the PCIe. Although Cayman uses PCIe2.1 and not PCIe3.0, has managed to achieve faster data transfers through PCIe. The predecessors were using two DMA controllers, each one controlled transfers in a single direction. The Cayman DMA controllers are both bidirectional, which increases the realizable bandwidth for the PCI-Express link.

Like the Fermi architecture Cayman has a similar memory hierarchy too. AMD makes extensive use of two explicitly addressed memory structures and separate read and write paths, each with specialized caches. It separates the write and read data paths for improving performance, but achieving coherence is very expensive.

The first level memory cache is in the SIMD and is called Local Data Share (LDS). It is 32KB and is exposed through the OpenCL and Direct Compute specifications, which require a 16KB and 32KB array. This level is shared only by the work-items of a work-group. LDS is a 32 way banked structure and includes bank conflict detection serializing the access to each bank. So, N accesses in the same bank means that the bandwidth will be reduced by a factor of N.

The second level memory is the Global Data Share (GDS). It is 64KB and is shared by the entire GPU. It is similar to LDS but it is used for the communication for an entire kernel and not a work-group. It is also 32 way banked structure and is not a part of a SIMD. It is a globally shared structure and available to each SIMD. The GDS is a structure that does not correspond to anything in the OpenCL or DirectCompute specification unlike the LDS.

Cayman also offers two levels of non-coherent texture caches which are read-only memories. AMD uses virtual memory addresses and the Texture Memory Unit (TMU) is responsible for translate these addresses for accessing the texture cache. The L1 cache memory is 8KB and is organized in 64B lines, so that aligned accesses in each quarter wavefront will target a single cache line. This can achieve a performance of 1.3TB/s.

Maximizing the bandwidth helps the GPUs to hit high performance. One of the keys for maximizing bandwidth is memory coalescing. Memory coalescing means grouping together aligned reads or writes that have good locality. Each coalesced memory access can use a single address and request, while moving many pieces of data. AMD uses two levels for exploiting locality. The first level is maximizing the utilization of each 128-bit register, which can hold four 32-bit data values. The second level of locality is coalescing together 4 different 16B accesses into a single cache line access.

The last level of cache memory is the L2 cache. The L2 cache is shared by all the SIMDs and is 512KB. The L2 is partitioned with a 64KB slice for each of the 8 GDDR5 memory channels. These slices can read a 64B line per cycle achieving a bandwidth of 450GB/s to the L1 caches and L2's intent is to exploit locality of data too.

Each memory channel uses a write combining cache that multiple writes are coalesced to a single cache line into one transaction. The WCCs also buffer up many writes so that they can be performed in a single batch and achieve maximum bandwidth. Simple stores can proceed from the WCC to the memory controllers. AMD uses the term FastPath for that. However, more complicated memory accesses go through additional hardware and require extra latency and bandwidth, along what AMD terms the CompletePath.

The highest level in memory hierarchy is the GDDR5 memory. The memory controllers are 64bits wide and drive two 32-bit GDDR5 channels. There are 8 channels for the communication with the graphics memory. The memory controller's intent is to maximize bandwidth via memory coalescences and write buffering.

### 2.4 Comparison of a GPU and a CPU

A GPU is similar to a CPU if they are considered as a compute device. But there are a lot of differences between their architectures.

The first difference is the way they like to execute instructions. A GPU emphasizes massively threaded throughput and SIMD performance, rather than the latency of a single instruction stream. A CPU is clocked very higher than a GPU and is good at executing the instructions single-threaded. The higher clock speed helps them to compensate for the lower number of cores. On the other hand a GPU is not efficient in a serial code.

The second difference lies in the control unit. Each core of a CPU has its own control unit and can run independently from the others, meaning that each core can execute different blocks of instructions at a given time. The cores of a GPU cannot do that. There is a control unit in each SM or SIMD. So, the cores of a SM or a SIMD have to execute the same instructions in parallel.

There is also a difference in caches. A CPU is designed to have many levels of cache memory and the last level has usually a big capacity. Since later years GPUs did not use caches, they started to use caches when it was found that they are useful for general purpose applications. Latest generations have also different levels of cache memory but they do not have so many levels as a CPU. Also they have smaller cache memories than CPUs and some GPU architectures, as the Cayman have read-only caches.

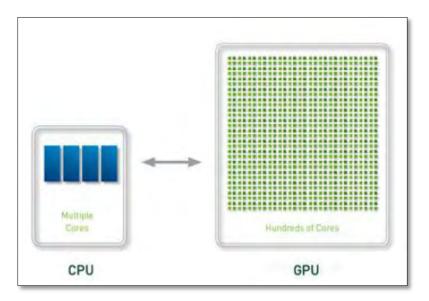

Another difference is that GPUs usually have vector processors which do not have advanced features such as branch prediction, and out of order execution. This enables GPUs to have much higher number of computational units (see *Figure 2.10*) due to the lesser complexity and the larger space available on the die. CPUs however have such advanced features since they are designed for general-purpose computation.

Last but not least, one very important difference between them is the context switching. On GPUs, thread context switching is implemented in hardware, which enables it to switch between thousands of threads very quickly. CPUs depend on the operating system to take care of context switching and this is much slower.

Figure 2.10: CPUs consist of a few number of cores (2 to 6), whereas GPUs consist of hundreds of cores

# **Chapter 3**

## **Basic Concepts of Parallel Computing and OpenCL**

### **3.1 Parallel Computing**

In this section, fundamentals of parallel computing will be presented.

Dual-core and quad-core processors on CPUs, general-purpose GPU computing and more recently, heterogeneous computing are the most basic forms of parallelism. In heterogeneous computing, tasks are executed in parallel on CPUs, GPUs, FPGAs and other devices obtaining unprecedented levels of performance.

#### 3.1.1 Flynn's Taxonomy

According to Flynn's taxonomy [3], architectures are classified based on the presence of single or multiple streams of instructions and data. There are four classifications as listed in the *Figure 3.1*. The descriptions are provided below.

**SISD:** An architecture in which a single processor executes a single instruction to operate on data stored in a single memory.

**SIMD:** An architecture in which multiple processing elements execute the same operation on multiple data simultaneously.

**MISD:** An architecture in which multiple processing elements perform different operations on the same data. This can be seen in a pipeline architecture where the same data moves along a pipeline and different operations are performed on it.

**MIMD:** An architecture in which different processing elements perform different operations on different pieces of data. The data can be stored in a shared memory or a distributed memory.

|               | Flynn's Taxonor    | ny                   |

|---------------|--------------------|----------------------|

|               | Single Instruction | Multiple Instruction |

| Single Data   | SISD               | MISD                 |

| Multiple Data | SIMD               | MIMD                 |

Figure 3.1: Flynn's Taxonomy classifies architectures into four categories based on the presence of single or multiple streams of instructions and data [3]

### 3.1.2 Levels of Parallelism

In this section, the three levels of parallelism are introduced, namely, instruction-level parallelism, task-level parallelism and data-level parallelism.

**Instruction-level Parallelism:** In instruction-level parallelism (ILP), more than one instruction is executed during a single clock cycle. Though the program to be executed might be following a sequential execution model, various micro-architectural techniques such as out-of-order execution or pipe-lining can be applied to exploit ILP.

**Task-level Parallelism:** In task-level parallelism, each processor executes a different thread or process on the same or different data. For e.g., in a dual core processor, two different cores can execute two different threads at the same time. If the threads are part of the same process, the data being worked upon can be the same. Task-parallelism emphasizes on distributing the process or thread across parallel processing nodes.

**Data-level Parallelism:** In data-level parallelism, each processor executes the same thread or process on different data. For e.g., adding two vectors can be done in a single clock cycle if there are as many processors as the number of additions to be performed. This model is in sync with the SIMD model. Data-parallelism emphasizes on distributing the data across parallel processing nodes.

### **3.1.3 Processor Architectures**

A multi-processor system, as its name suggests is a single computer system which has multiple processing nodes. Multi-processors can be classified based on their execution model. Various processor architectures which form the basis and are implemented in many of the current CPUs and GPUs are presented along with a discussion of their features and shortcomings.

**Vector processors:** In vector processors, there are multiple, pipelined functional units which has the capability to execute single instructions on vectors or arrays of data. All the functional units execute the instructions in lock-step fashion on the local data. According to Flynn's taxonomy, vector processors follow the SIMD model. Vector processors are very power-efficient as the units consist of simple execution units. There is no instruction checking done at runtime and no other complex features implemented in the processor. Taking the simplicity into account, the space required for the units on the die is also considerably smaller, thereby leading to higher number of units and more power efficiency.

**VLIW processors:** The VLIW architecture takes advantage of ILP, by executing multiple instructions in parallel but the difference being that the schedule of instructions is determined when the program is compiled. It has multiple execution units like vector processors, but it is capable of executing different instructions at the same time. The VLIW architecture is more power hungry than vector processors. Unlike super-scalar processors, the schedule of instructions is statically determined by the compiler, rather than by the processor.

**Super-scalar processors:** In super-scalar processors, multiple functional units are available on the processor so that multiple instructions can be executed per clock cycle. Data dependencies between instructions are dynamically checked at runtime for doing this. Super-scalar processors are different from multi-core processors where the redundant units are entire processors and parallelism is achieved by executing one thread per core. Though super-scalar processors process multiple data items in a single clock, they do not process multiple data items for a single instruction. Super-scalar processors are much more power-hungry than VLIW and vector processors due to their dynamic behavior. The units are more complex due to added functionalities such as out-of-order execution, branch prediction, etc.

**Multi-core processors:** Multi-core processors contain multiple independent cores on a single chip (also known as chip multiprocessor). Though the cores are independent, they do share some resources such as cache memories, main memory between them. Sharing cache memories aids in exhibiting task-parallelism where the cores can work on the same data simultaneously. In addition, implementing multiple functional units (such as ALUs) in a single core aids in data-parallelism. According to Flynn's taxonomy, it follows the MIMD model. Multi-core processors can implement super-scalar or vector architectures or even a hybrid of both for added performance benefits. Most real programs get maximum benefit with a mixture of both data-parallelism and task-parallelism. Most of the processors being manufactured now, try to support a combination of these configurations.

**Many-core processors:** Many-core processors are similar to multi-core processors but with a much higher number of cores. It is not required that all the cores have to be all on a single chip, but all the cores will be in a single processor package. They are designed for a higher degree of parallelism,

supporting advanced levels of scalability. Many-core processors follow the MIMD model. They usually consist of simpler elements such as vector processors, whereas multi-core processors usually consist of more complex elements such as super-scalar processors. Each core in many-core processor is simple, small, and independent from each other. Typically, a multi-core processor will have fewer cores (two to six) whereas many-core processors usually have 32 or more cores.

### 3.2 Open Computing Language (OpenCL)

OpenCL is an open industry standard maintained by the Khronos Group for writing programs that execute across heterogeneous computing devices such as CPUs, GPUs and other processors. The OpenCL framework provides a runtime system, libraries and a programming language which is an extension to the standard C language (based on C99). This helps programmers to develop portable general-purpose software which can take advantage of all the different platforms that support OpenCL.

The write once, run anywhere behavior of OpenCL is the one major property which sets it apart from other such languages for the GPU. During runtime, the OpenCL code is compiled just-intime for the particular architecture and hence the programmer needs not bother about which target architecture the program will be running on, as long as it supports OpenCL. OpenCL supports both data-parallel and task-parallel programming models, as well as the hybrid of them. Primarily driving the design is the data-parallel model. It also provides a broad set of programming APIs using which developers can query and identify the actual device capabilities and create efficient code.

### 3.2.1 Platform Model

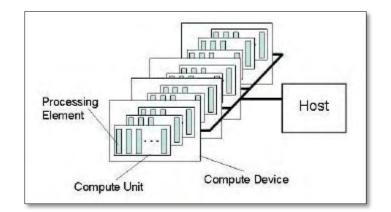

The OpenCL specification defines a platform as a host connected to multiple OpenCL devices which are composed of a number of compute units. Compute units can be further divided into a number of processing elements. <u>Figure 3.2</u> illustrates how all of these devices interact together. A brief description for each is provided below.

**Host:** A host usually consists of a CPU and is responsible for running the host application. The host application runs natively on the host and submits commands to the OpenCL device. The commands to be submitted are queued up in a data structure called the command queue which is then scheduled onto the device. Execution of kernels, reading and writing of memory objects are examples of some of the commands which are submitted.

**Devices:** A device can correspond to a multi-core CPU, a GPU, a FPGA, a APU etc. A single device is composed of a number of compute units, such as the individual cores in a multi-core CPU.

An aspect to be noted of this model is that, provided the host device also supports OpenCL, programmers can partition a program into serial code and parallel code which are best suited for the CPU and the GPU, respectively. Thereby, the execution can go back and forth between the devices making the best utilization of them.

Figure 3.2: The OpenCL Platform Model specifies a host which is usually a CPU connected to multiple OpenCL compute devices such as GPUs or APUs. The compute devices consist of a collection of compute units (cores) which are further composed of multiple processing elements [2]

### **3.2.2 Execution Model**

In this section, the OpenCL execution model is presented. Before talking further about the execution, the various terms used are introduced.

**Program:** An OpenCL program consists of one or more kernels and auxiliary functions which are used by the kernels. Programs are written in an OpenCL-C language. The language has extensions which are for e.g., specifying memory spaces and also additional keywords for specifying a function as a kernel function. The OpenCL compiler which is a part of the runtime compiles programs to create binaries which can be executed or saved for later loading.

**Kernel:** The kernel is a function in an OpenCL program that is executed on a device. The return types of kernels are always void as all inward and outward communication is done through the memory. All the necessary operations such as copying of memory objects, setting kernel arguments etc., required for the kernel execution are managed by the host application.

**Work-Item:** Instances of the kernel are executed in parallel on the compute units of the device. The same kernel code is executed by all the work items concurrently, but the specific path taken can vary based on the algorithm. Work-items are identified in two ways - one is by using a global ID and the second way is through a combination of a local ID and work-group ID, which will be explained in detail in the next segment.

**Work-Group:** As mentioned before, a collection of work-items are assigned for execution on a single compute unit. This collection of work-items is called as a work-group. When a kernel is enqueued for execution, two parameters pertaining to work-groups can be specified, which are the global work size and the local work size. The global work size is the total number of kernel instances or work-items that are to be started for computation, whereas the local work size is the number of work-items that are assigned to one work-group. So the number of work-groups will be always equal to the global work size divided by the local work size. If the local work size is not specified, then the OpenCL implementation will decide how to break down the global work-items into appropriate work-groups. In case there are more work-groups than the available number of compute units, the work-groups will be scheduled one by one on the compute units. A compute unit will always concurrently finish executing the work-items in one work-group before executing work-items from another work-group.

In OpenCL, the execution model is based on parallel execution of the kernel, with the process involving both the host and the compute device. The steps involved in kernel execution are listed in the *Fiqure 3.3*. The *Fiqure 3.4* shows how each of the steps presented in the *Fiqure 3.3* relate to the host and the compute device. Although the host is required for the initial setup of the execution process, the compute device executes the kernel independent of the host and the compute device to communicate is by copying data from the host memory to the device memory and vice versa. Debugging OpenCL programs are therefore quite difficult as the only way to ensure computation is done correctly is to copy the data back to the host and then verify the output.

| _   | 1. Device Setup                                     |

|-----|-----------------------------------------------------|

|     | Initialize platform                                 |

|     | Get devices and create command queue                |

|     | 2. Device and Host Buffer Setup                     |

|     | Create memory buffers on the host and device        |

| Cop | by input data from the host memory to device memory |

|     | 3. Kernel Initialization                            |

|     | Load kernel source code from file                   |

|     | Create program object and build the program         |

|     | 4. Kernel Execution                                 |

|     | Set kernel arguments                                |

|     | Execute the OpenCL kernel                           |

|     | 5. Output copying and Cleanup                       |

| Co  | ppy output data from device memory to host memory   |

|     | Delete all allocated objects                        |

Figure 3.3: The steps involved in an OpenCL kernel execution [2]

Figure 3.4: The interactions between the host and compute device for a kernel execution [2]

### 3.2.3 Memory Model

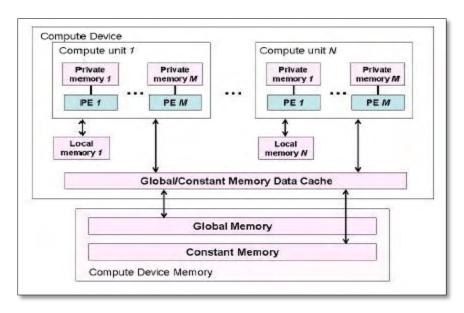

In this section, the memory model of OpenCL is presented. The memory in OpenCL devices is classified into five regions - global, constant, texture, local and private. The task of deciding the region to store data is solely up to the programmer. <u>Figure 3.5</u> shows the memory hierarchy as defined by OpenCL. A brief description of each of the memory regions is provided below.

Figure 3.5: The OpenCL Memory Model defines four regions of memory accessible to work-items while executing a kernel. The global memory in the compute device is accessible to the host also [2]

**Global Memory**: The global memory region is the main means of communication between the host and the device. The host can create read/write buffers on the global memory of the device using commands. It is accessible to all the work-items and a programmer can use the global address space qualifier in a kernel to denote that an object is to be stored in global memory. Though it is usually the largest space available on the device, the access latency is also much larger compared to the other regions.

**Constant Memory**: The constant memory is a part of the global memory, but the difference between them is that while the host can read and write into this region, the kernel has read-only access. The constant address space qualifier is used to denote that an object is to be placed in constant memory.

**Local Memory:** The local memory is named as such as it is the memory that is available only to a local work group. In other words, the local memory is made private to a compute unit. So the compute units local memory will be accessible to all the work-items that are part of the same work-group. The space available is much smaller, but has low latency compared to the global region. Using the local

memory, work-items in a work-group can share data among them quickly and synchronize their execution. The local address space qualifier is used to denote that an object is to be placed in local memory.

**Private Memory:** This memory region is accessible to only a single work-item. This is the fastest and the smallest memory that is available to a work-item. The private address space qualifier is used to denote that an object is to be placed in private memory.

## **Chapter 4**

## The 13 Dwarfs

The increasing proliferation of heterogeneous computing platforms presents the parallel computing community with the challenge of evaluating the efficacy of such parallel architectures, particularly given the diversity of hardware architectures and their associated (non-interoperable) programming environments.

OpenCL and 13 Dwarfs or OCD for short [4] is a benchmark suite that aims to provide a futureproof software methodology to enable the evaluation of hardware innovation across a variety of architectures. To this end, application kernels following computation and communication patterns are selected from the Berkeley 13 Dwarfs. The focus is on these because they offer a diverse set of patterns, each of which is relevant across a variety of domains. For example, the n-body method is relevant across physics, chemistry, and a variety of other domains.

Overall, it is believed that OpenCL and the 13 Dwarfs will provide a useful baseline for the evaluation of platforms and runtime systems across application domains. In the future, representative applications for each dwarf will be prepared hoping that in this way a set of implementations will be created which may be used to make generalizations about the higher-level patterns and the effectiveness of a given platform for executing a given pattern.

An indicative brief description of each of the 13 Berkeley dwarfs follows:

**Dense linear algebra:** Consists of dense matrix and vector operations. It has a high ratio of math-toload operations and a high degree of data interdependency between threads. *Application areas*: Linear Algebra (LAPACK, ATLAS), Data Mining (Streamcluster, K-means) **Sparse linear algebra:** Solves the same problem as dense linear algebra but has matrices with few non-zero entries. To reduce space and computation, such algorithms store and operate on a list of values and indices rather than proper matrices, resulting in more indirect memory accesses. <u>Application areas</u>: Finite Element Analysis, Partial Differential Equations

**Spectral methods:** Transform data from/to either a spatial or temporal domain. The execution profile is typically characterized by multiple stages of processing, where dependencies within a stage form a "butterfly" pattern of computation.

Application areas: Fluid Dynamics, Quantum Mechanics, Weather Prediction

**N-body methods:** Calculate interactions between many discrete points and are characterized by large numbers of independent calculations within a timestep, followed by all-to-all communication between timesteps.

Application areas: Molecular Modeling, Molecular Dynamics, Cosmology

*Structured grids*: Organize data in a regular multidimensional grid, where computation proceeds as a series of grid updates. For each grid update, all points are updated using values from a small neighborhood around each point. The neighborhood is normally implicit in the data and determined by the algorithm.

Application areas: Image Processing (SRAD), Physics Simulations (HotSpot)

**Unstructured grids:** Possess data structures, e.g., linked list of pointers that keep track of the location and neighborhood of points which are used to update the location. Like sparse linear algebra, updates typically involve multiple levels of memory reference indirection, as an update to any point requires first determining a list of neighboring points and then loading values from those neighboring points. <u>Application areas</u>: Computational Fluid Dynamics, Belief Propagation

**MapReduce:** Captures the repeated independent execution of a map function and results are aggregated at the end via a reduce function. No communication is required between processes in the map phase, but the reduce phase requires global communication.

Application areas: Distributed Searching, Sequence Alignment, Parallel Monte Carlo Simulations

**Combinational logic:** Exploits bit-level parallelism in order to achieve high throughput. Such a workload involves performing simple operations on very large amounts of data. <u>Application areas</u>: Encryption & Decryption, Hashing

**Graph traversal:** Visits and evaluates a number of objects in a graph. Such algorithms typically involve a significant amount of random memory access for indirect lookups. The bottleneck is generally due to access latency rather than access bandwidth.

Application areas: Searching, Sorting, Collision Detection

**Dynamic programming:** Solves a complex problem by solving a series of simpler subproblems. <u>Application areas</u>: Graph Problems (Floyd's All-Pairs shortest path, Bellman - Ford algorithm), Sequence Alignment (Needleman – Wunsch, Smith - Waterman)

**Backtrack & branch-and-bound:** Approaches generally search a very large search space to find a globally optimal solution. Because the search space is so large, an implicit method is needed to prune the search space to make this approach computationally tractable.

Application areas: Artificial Intelligence (N – Queens), Integer Linear Programming,

Boolean Satisfiability, Combinatorial Optimization

*Graphical models*: Map variables into nodes and conditional probabilities into edges, e.g., Bayesian networks.

<u>Application areas</u>: Computational Biology (Sequence homology search), Machine Learning (Hidden Markov Models), Embedded Computing (Viterbi decode)

*Finite state machines*: Capture a system whose behavior is defined by states, transitions defined by inputs and the current state, and events associated with transitions or states. These dwarf algorithms are highly dependent on conditional operations and interdependent data, which are also commonly found in graph traversal.

Application areas: Video Decoding, Parsing, Compression,

Data Mining  $\rightarrow$  Reverse Engineering the Brain

# **Chapter 5**

## **Related Work**

In this section some indicative related works will be presented about the performance portability of OpenCL on heterogeneous architectures.

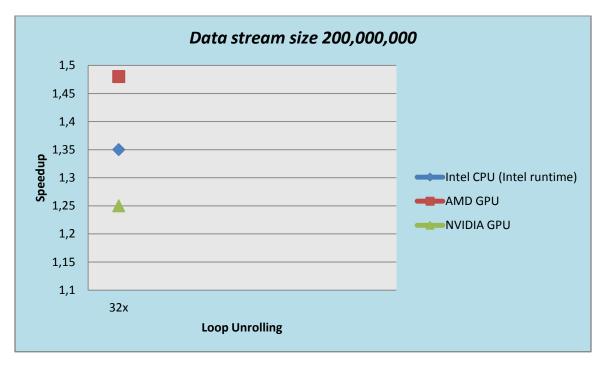

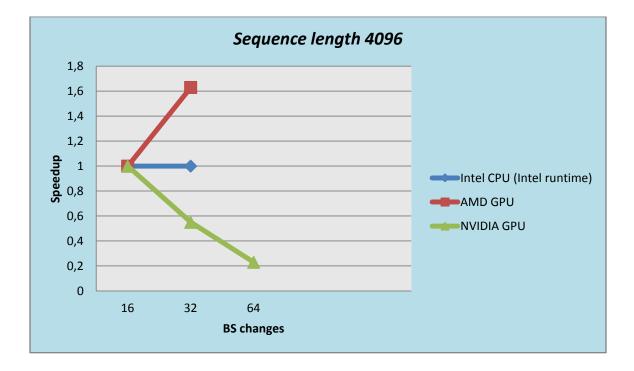

There are few publications that have studied the performance portability of OpenCL on heterogeneous architectures. In [5] Rul *et al.* have studied the performance portability of OpenCL. The study has been done on four different architectures, including an Intel Core i7 720 - QM (a 1.60 GHz quad-core), an NVIDIA Tesla c1060, an ATI FirePro V8700 and a Sony/Toshiba/IBM Cell Broadband Engine (Playstation 3). For the experiments, three Parboil benchmarks (cp, mri-fhd, mri-q) and three optimization parameters (loop unrolling, vectorization, number of threads in a thread block) were used.

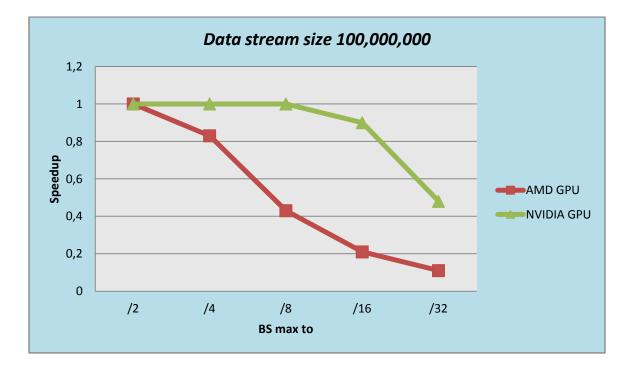

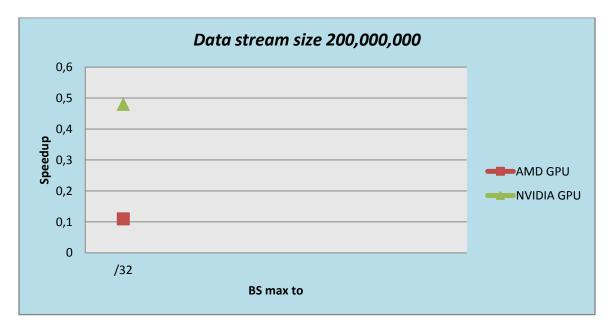

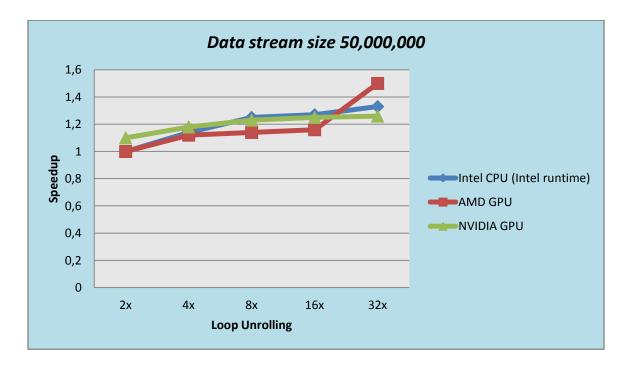

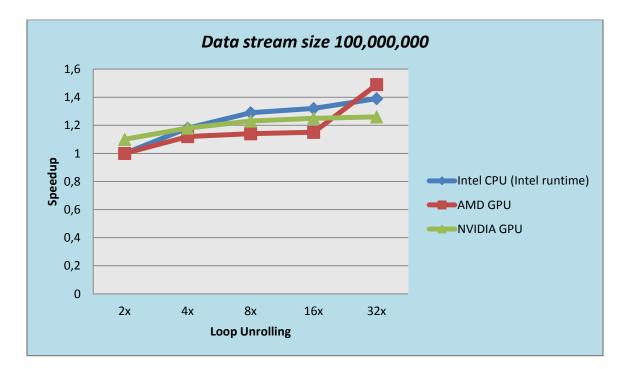

They found that when optimizing for CPUs, loop unrolling is not an important optimization for these kernels, but loop unrolling is crucial for good performance on Cell. For Tesla, the thread block size is the most important parameter, while big loop unrolling factor degrades performance on Tesla. Also, while the Tesla and FirePro respond largely similarly to the optimizations, the FirePro is much more sensitive to parameter values for the optimizations and it has different optimal parameter values than the Tesla. Furthermore, when adding vectorization, this degradation becomes even larger and the optimal unrolling factor becomes smaller.

They conclude that the impact of the optimizations varies hugely between architectures, confirming the need for architecture-specific optimization and that the OpenCL does not support performance portability. However, they have only observed the behavior of the benchmarks and have not looked into the causes for the behavior. In this thesis, this has been improved upon by explaining the rationality behind the behavior of the benchmarks for each architecture.

Another indicative work about the OpenCL portability and performance on software heterogeneous architectures is a master thesis [6]. In this survey, well-known image-processing algorithms (binarization, dct, convolution, sum, histogram) are evaluated on three different architectures (NVIDIA Fermi GTX 470, AMD Evergreen HD 5850, Intel Core Nehalem i7-930).

The author has shown that for GPUs the basic optimizations that are useful someone to implement on OpenCL code are the maximization of parallel execution, the memory access coalescing, the local memory usage and the loop unrolling. The architecture of the AMD GPU is comparable to the architecture of the NVIDIA GPU, but one significant optimization parameter that has extra the AMD is the VLIW packing. Efficient use of AMD GPU hardware requires that the kernel contains enough parallelism to fill all VLIW slots. This can be achieved in two ways, by loop unrolling or by

using explicit vector data types.

On the other side, this thesis states that for OpenCL to reach hardware efficient implementations on a CPU a different mapping as compared to the GPU implementations is required and some important optimization techniques are the maximization of parallel execution and the exploitation of cache hierarchy. The available parallelism on a CPU is limited to the width of the vector units inside a core multiplied by a relatively small number of cores, while for the cache hierarchy to improve the performance of a program, the program should contain spatial and/or temporal locality. Moreover, it is recommended that in order to improve the performance on an Intel CPU, one must avoid to use local memory and barrier synchronization instructions, offered by OpenCL. Local memory for CPUs is mapped onto a region of the global memory and it isn't low-latency, while the barrier synchronization is unnecessary if someone assigns one work-item per work-group in CPUs.

Generally, it is shown that OpenCL cannot guarantee performance portability, as the architectural philosophy gap between CPUs and GPUs is huge and an optimal implementation for a CPU performs very badly on GPUs. As an indicative example, for most of the algorithms tested, the Intel optimized implementations only launch one thread per Compute Unit, which results in heavy under-utilized Compute Units on the GPUs.

Finally, in one of the most promising works that was published recently [7], the performance of OpenCL programs is evaluated on out-of-order multi-core CPUs from the architectural perspective. In this paper, the authors evaluated various aspects of OpenCL programs, including scheduling overhead, instruction-level parallelism, data location, locality and vectorization, comparing OpenCL to conventional parallel programming models for CPUs such as OpenMP. Their study was performed on two different architectures (Intel(R) Xeon (R) CPU E5645, NVIDIA GeForce GTX 580) and for the experiments they used simple applications and Parboil benchmarks [8].

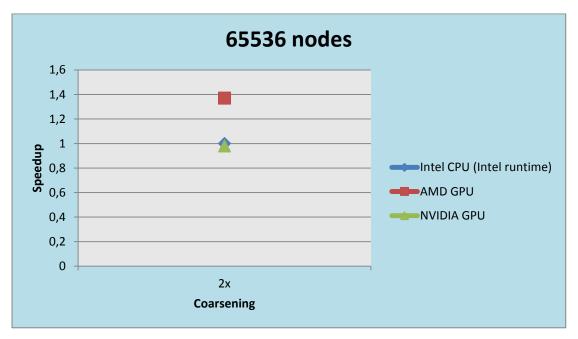

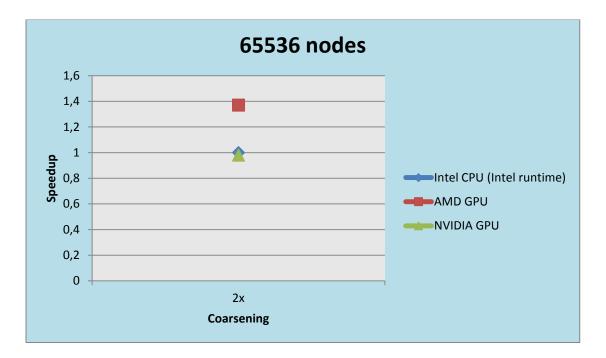

Key findings of their evaluation are that opting for a large work-group size and coarsening the granularity of work per work-item are helpful for better performance on CPUs, because each one of them causes the reduction of the total number of work-groups which entails reduction of total context-switches. Coarsening GPUs, this survey verifies that as expected, they have different optimization requirements compared with CPUs, as they need many work-groups to exploit the vast parallelism execution opportunities that their hardware offers. However, a small work-group size is also bad on GPUs, since it makes GPUs unable to launch many warps within a streaming multiprocessor, thus minimizing the opportunities to overlap computation with data accesses.

Moreover, they observed that the large ILP value helps performance on CPUs. For example, in the case of ILP = 1, the next instruction depends on the output of the previous instruction; but in the case of ILP = 2, there is an independent instruction between two dependent instructions. They showed that an increasing ILP benefits the CPUs, while it keeps the performance in about the same levels for GPUs. Another important finding is that adding affinity support to OpenCL may help performance in some cases, due to the fact that this can lead to fewer cache misses on the private caches of CPU processors. Last but not least, this survey shows that vectorization can improve the CPU performance, as the vectorized code would result to less thread creation compared to non-

vectorized code, since SIMD instructions can perform computation on more than one data item at the same time.

Generally, this paper shows that since OpenCL has the same background as CUDA, most OpenCL applications are written to better utilize thread level parallelism (TLP), which is a scheme that cannot be applied on CPUs since even when the TLP of the application is large, the physical TLP available on CPUs is limited by the number of CPU cores, so that the context switching overhead is much higher on CPUs than on GPUs, for which this overhead is negligible. However, considering the characteristics of CPU architectures, the OpenCL application can be optimized further for CPUs, and the programmer needs to consider these insights for portable performance.

## **Chapter 6**

## Analysis of optimizations on dwarf benchmarks

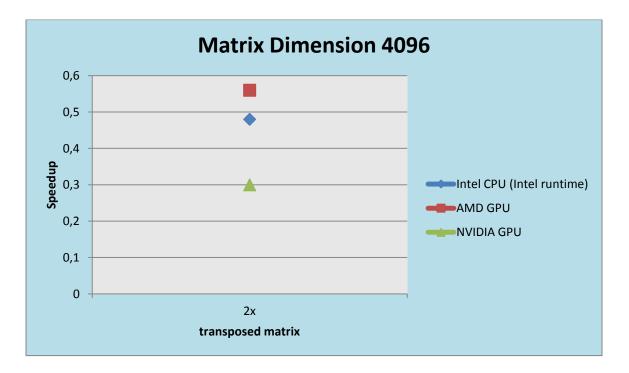

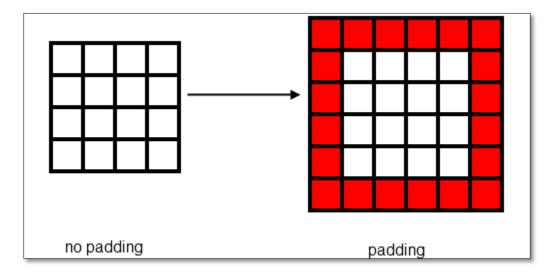

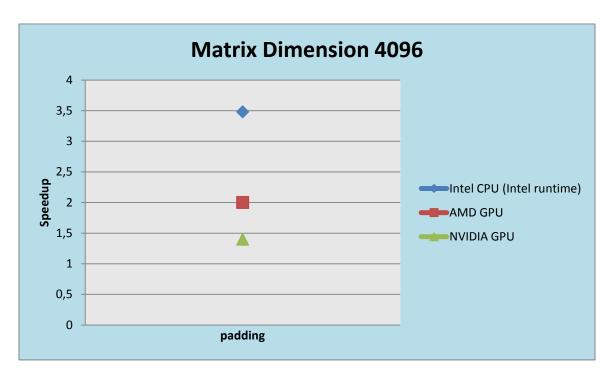

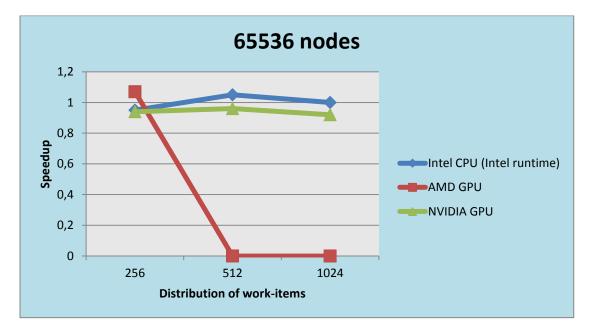

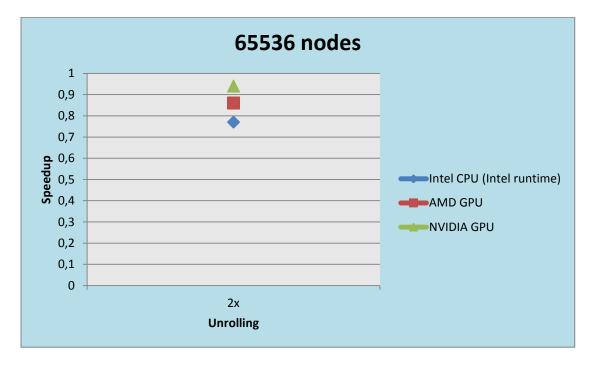

In this section we tested the optimizations *Geometry* (*Granularity*, *Geometry of work-items*), *Vectorization* (*Vector Types*), *Loops* (*Loop Unrolling*) and *Branches* (*Padding*) and the OpenCL Berkeley dwarfs on which they are evaluated are the applications *lud*, *crc*, *needle*, *srad* and *bfs*. Moreover, some important things referred about the cache memory and the cache lines, in the applications that the latter affect the performance. This happens in kernels that make use of local memory and we tried to find which computational patterns offer more cache hits and how data should be organized in memory for better performance.

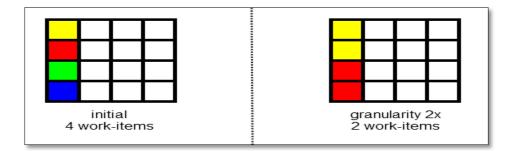

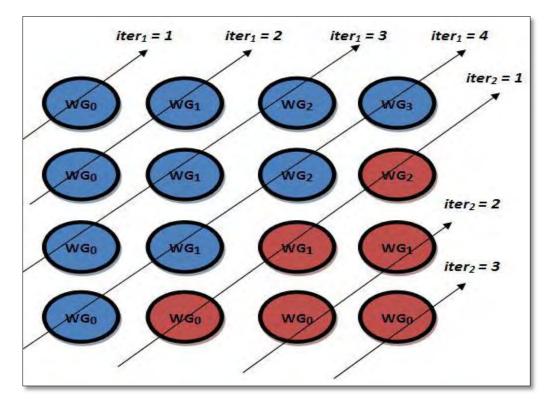

Geometry was the first optimization we tested. We separated it in two categories: granularity and Geometry of work-items. Testing granularity leads to the reduction of the number of work-items, but to the increment of the workload in each of them. This is expected to improve the performance of the CPU, because they are designed to execute many instructions per work-item and reduces the number of context switches, but it can be proved catastrophic for the GPUs. Changing the Geometry of work-items means that we keep the same number of the total work-items as the initial code, but the size of each work-group or grid is different. It is important to remember here, that except for the cases that our kernel is called iteratively, the work per work-item remains the same.

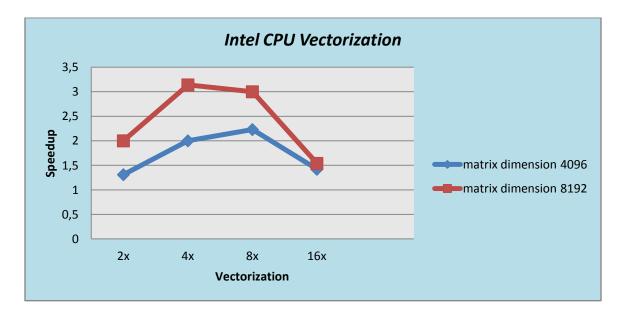

Vectorization is supported by architectures with vector type units such as the Intel CPU and the AMD GPU. The NVIDIA GPU can sometimes execute some instructions vectorized because of the double issue. In order to use vectorization, the data must be allocated on a consecutive memory area. We expect that if the vectorization can be applied on an application, it will give a speedup because it lets two or more instructions to be executed concurrently in the same clock cycle.

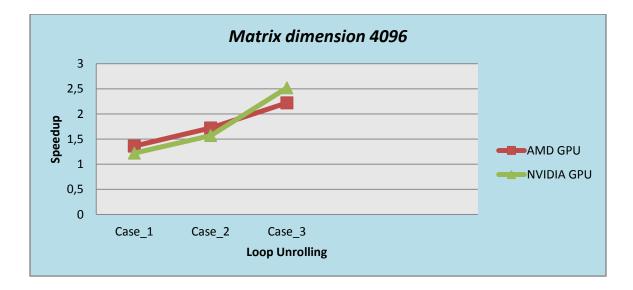

The loop unrolling is one of the most popular optimizations. It is supposed that can boost the performance because it can hide the cache misses, leads to better use of registers, or it can reschedule the instructions in the loop. Different steps in loop unrolling may give a totally different performance. Moreover, AMD GPU and Intel CPU are expected to take advantage of their ILP metric that support.

Last but not least, we inspected how the branches affect the performance. Branches can kill the performance of a GPU because of the divergencies but it can also affect the CPU. We tried to eliminate them to see the difference of the performance on the code.

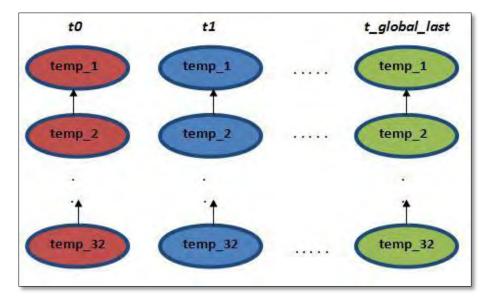

We must also mention that through an experimental study that we done in a set of our benchmarks, we found that the work-groups execute per core in Intel CPU and the work-items within them execute sequentially. Namely, each work-group is assigned to a core of Intel CPU and when it finishes its execution, a context switch happens in order another one to take place in this core.

### 6.1 lud

In LU Decomposition, a matrix is decomposed into a product of two matrices, a lower triangular and upper triangular matrix. Application *lud* belongs to the *dense linear algebra* category of dwarfs and comprises three kernels, the *lud\_diagonal*, *lud\_perimeter* and *lud\_internal*. The most time-consuming kernel is the *lud\_internal* and the *lud\_perimeter* follows. The time of *lud\_diagonal* is negligible and this kernel does not be considered in the analysis and implementation of this thesis.

### 6.1.1 Analysis of *lud\_perimeter* kernel

#### 6.1.1.1 Data Dependencies

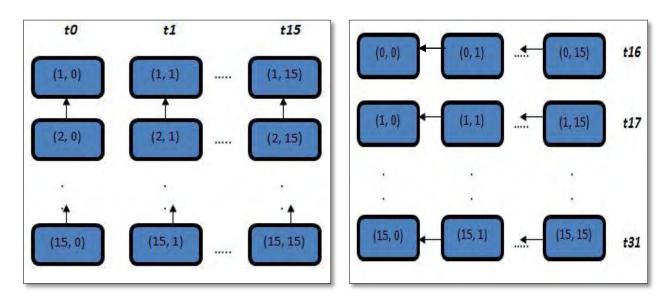

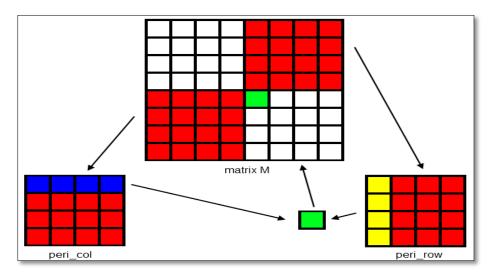

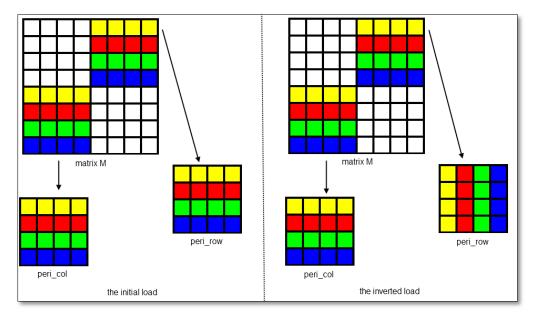

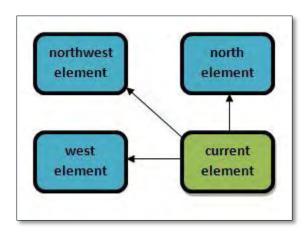

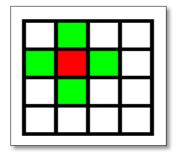

In *lud\_perimeter* kernel half of the work-items of each work-group fill the local, per workgroup *peri\_row* array, while the others fill the local, per work-group *peri\_col* array. Every work-item in both computations follows a form of computation which is similar to the *prefix\_sum* pattern. Namely, in every consecutive iteration more calculations are done per element per work-item compared to the previous iteration. *Figure 6.1* shows the way that the calculations are performed in this kernel.

Figure 6.1: The first image depicts the computation data dependencies of local, per work-group peri\_row array, where the second image depicts the respectives for local, per work-group peri\_col array

The local, per work-group *dia* array is used only for reading. Moreover, the BLOCK\_SIZE that is used in the original version of the code is 16 (as verified by the *Figure 6.1*), but the work-group size is 32 (2 \* BLOCK\_SIZE), so 16 work-items correspond to *peri\_row* and 16 work-items correspond to *peri\_col*. The BLOCK\_SIZE here is the TILE\_SIZE of *local memory*.

The arrays *peri\_row* and *peri\_col* are 2-dimensional BLOCK\_SIZE\*BLOCK\_SIZE size local, per work-group arrays. As can be inferred from the *Fiqure 6.1*, work-items 0 to 15 of *peri\_row* have vertical data dependencies on their private calculation data and as they don't have any dependencies among them, they are executed in parallel in each iteration. On the other hand, work-items 16 to 31 of *peri\_col* have horizontal data dependencies on their atomic computations and they are also executed in parallel in each iteration, since they do not need any synchronization points among them. Furthermore, we must mention that in *Figure 6.1*, the first row of *peri\_row* doesn't be included because it doesn't participate in computations.

Last but not least, we must mention that the *lud\_perimeter* kernel is executed iteratively. The number of work-groups decreases by one in each consecutive iteration and the work-group size remains constant in all kernel calls.

#### 6.1.1.2 Basic code segment

The time-consuming code segment of *lud\_perimeter* kernel on which our optimizations are applied, presented here in order to help one to realize better the form of communication and computation that exists.

```

If ( get_local_id(0) < BLOCK_SIZE ) {

idx = get_local_id(0);

for (i = 1, i < BLOCK_SIZE; i++) {

for (j = 0; j < i; j++)

peri_row[i][idx] -= dia[i][j] * peri_row[j][idx];

}

}

else {

idx = get_local_id(0) - BLOCK_SIZE;

for (i = 0; i < BLOCK_SIZE; i++) {

for (j = 0; j < i; j++)

peri_col[idx][i] -= peri_col[idx][j] * dia[j][i];

peri_col[idx][i] /= dia[i][i];

}

}</pre>

```

### 6.1.1.3 Optimization Efforts and Results

### 1) Execution Geometry

#### a) Granularity

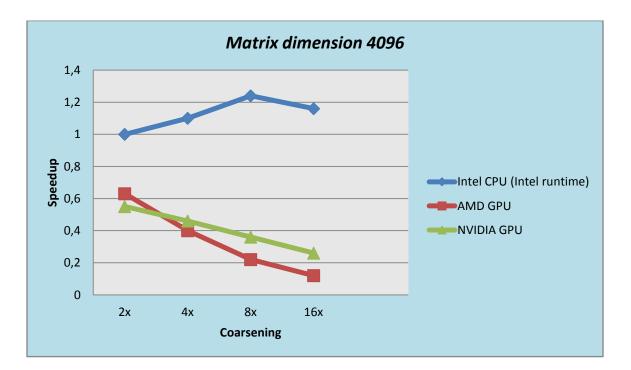

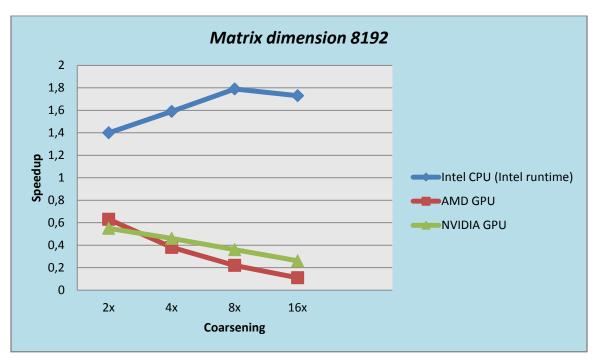

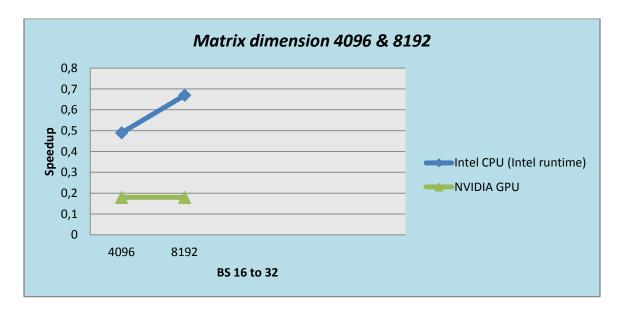

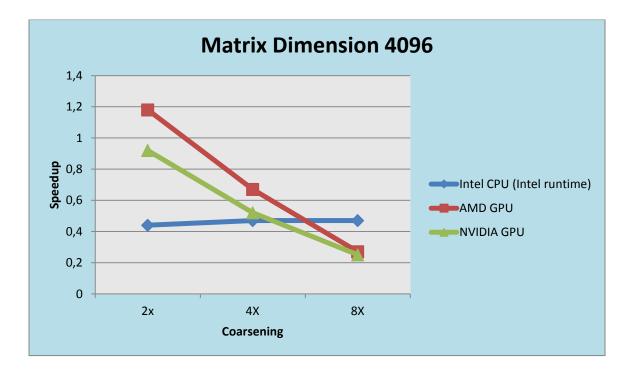

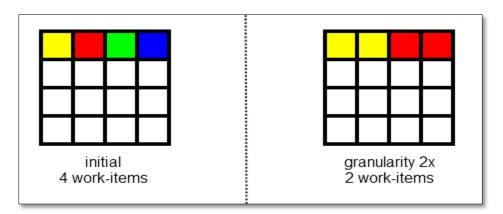

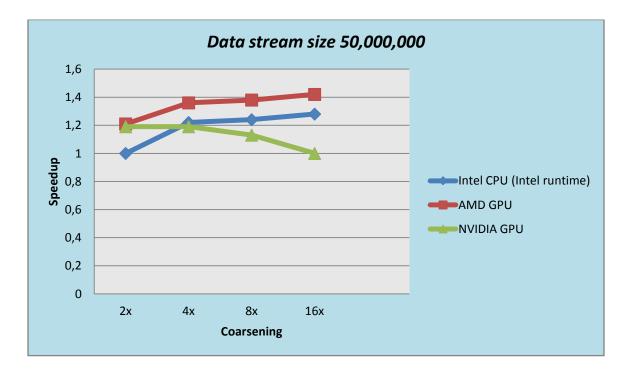

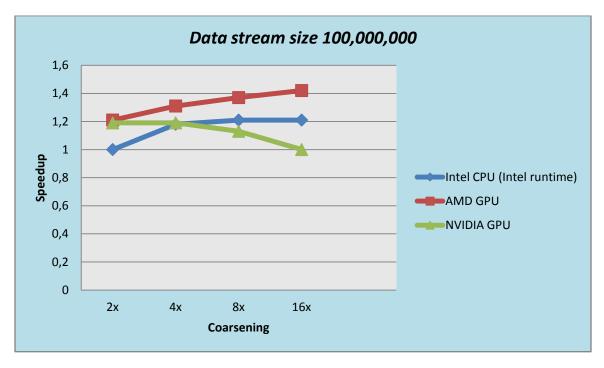

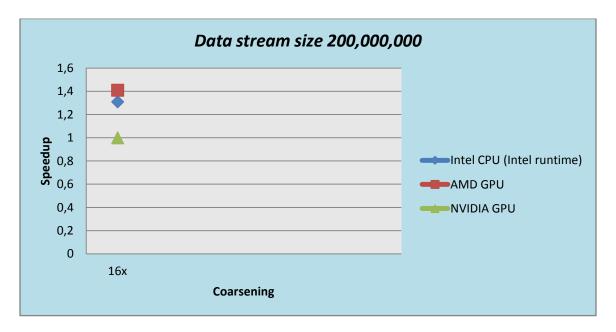

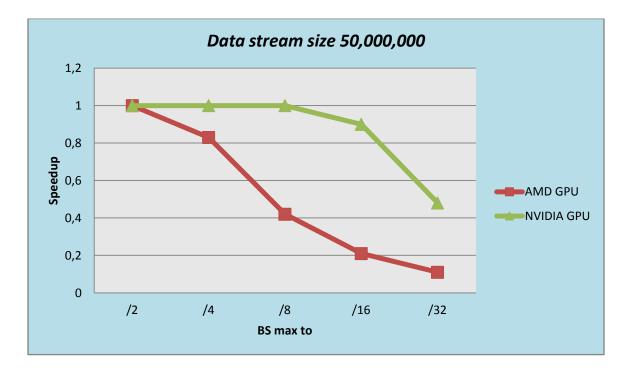

2x, 4x, 8x and 16x coarsening of the workload per work-item is tested. Larger coarsening per work-item is better for the Intel CPU, whereas it proves catastrophic for GPUs. In kernel *lud\_perimeter, 2x coarsening* means that the work-group size reduces from 32 to 16, while with *4x coarsening* it reduces from 32 to 8 and so on. Therefore, the work per work-item is gradually bigger along work-group size reduction.

Specifically, we use the <u>Figure 6.1</u> to explain it further. We choose the 4x coarsening case for that and the induction to other cases is similar. We have explained previously how the data dependencies of peri\_row and peri\_col arrays are per work-item. In 4x coarsening case, the workgroup size reduces from 32 to 8 and this means that 4 work-items per work-group are responsible for the computation of peri\_row and the other 4 are responsible for the computation of peri\_col. Namely, the work-item 0 of peri\_row array will get the summed work of work-items 0 to 3 of initial implementation, work-item 1 will get the summed work of work-items 4 to 7 and so on. In other words, in initial implementation during the first iteration, work-item 0 computes the element peri\_row[1][0], work-item 1 computes the element peri\_row[1][1] and so on. Instead, in 4x coarsening case during the first iteration, work-item 0 computes the elements peri\_row[1][0] to peri\_row[1][3], work-item 1 computes the elements peri\_row[1][4] to peri\_row[1][7] and so on. Therefore, it is obvious that the coarsening per work-item in 4x coarsening case, as related to peri\_row array, increases by 4 compared to initial implementation.

Additionally, similar is the situation for the computation of *peri\_col* array. However, the thing that deserves to mention here is the following. As the *Granularity* optimization leads usually to a form of data that it is feasible to be vectorized due to the consecutive memory locations that the data have, it is good when one applies that to take that into consideration. Observing the second image of *Figure* <u>6.1</u>, that of *peri\_col* case, we see that the coarsening here can be implemented per column and not per row, as in the case that happens in *peri\_row* array. This holds because the data dependencies per work-item have vertical form for *peri\_row* case, while they have horizontal form for *peri\_col* case. The problem is that the consecutive data per column cannot be vectorized, since they do not belong to successive memory locations. For example peri\_col[0][0] and peri\_col[1][0] elements belong to different memory locations. A solution to this is the transition of *peri\_col* array that gives the same computational pattern that *peri\_row* array has and the things that explained previously can exactly be applied in this case. Therefore, the coarsening per work-item is the same for *peri\_row* and *peri\_col* local, per work-group arrays and the *Vectorization* optimization (we will refer to that later in this section) can very effectively be implemented.

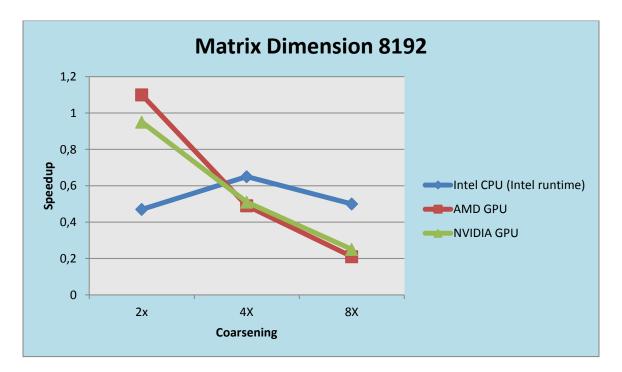

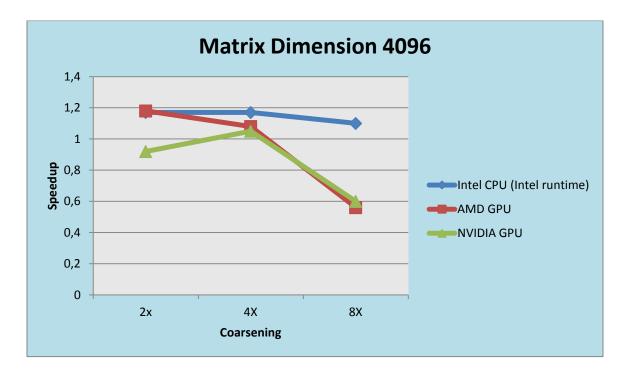

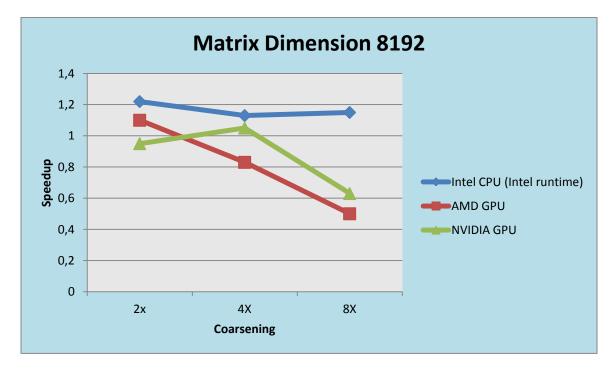

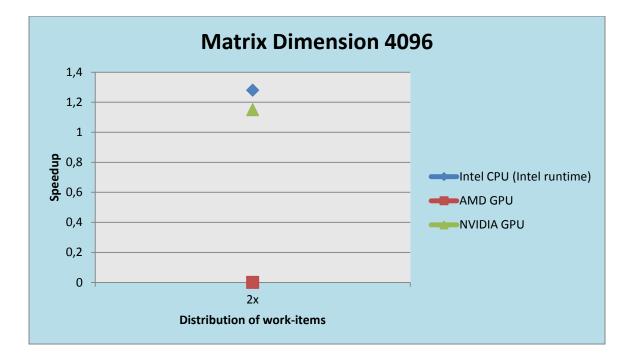

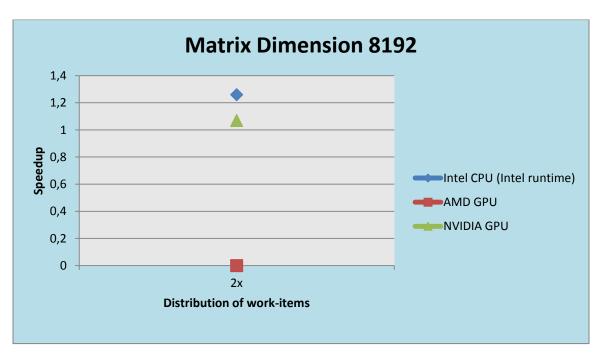

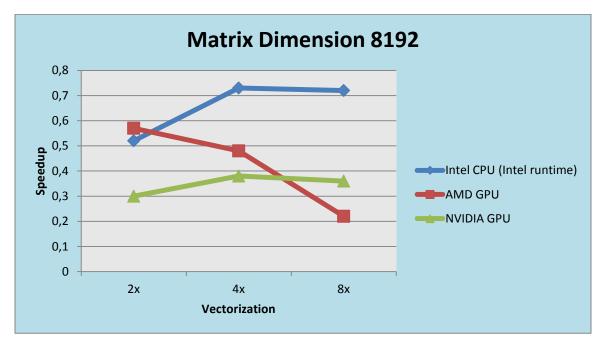

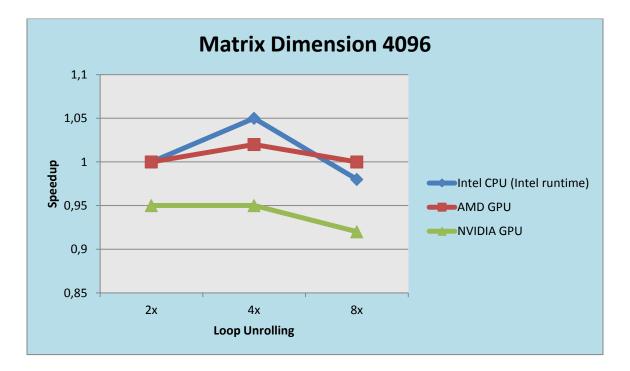

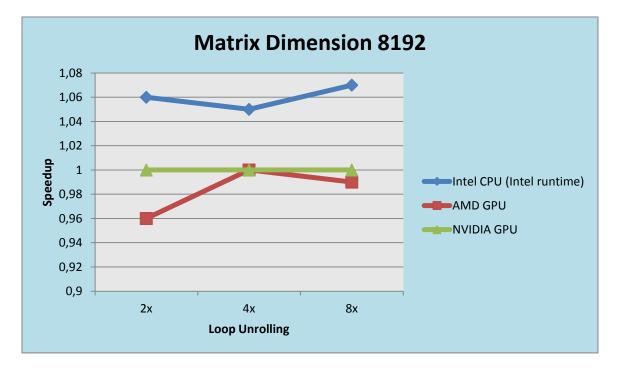

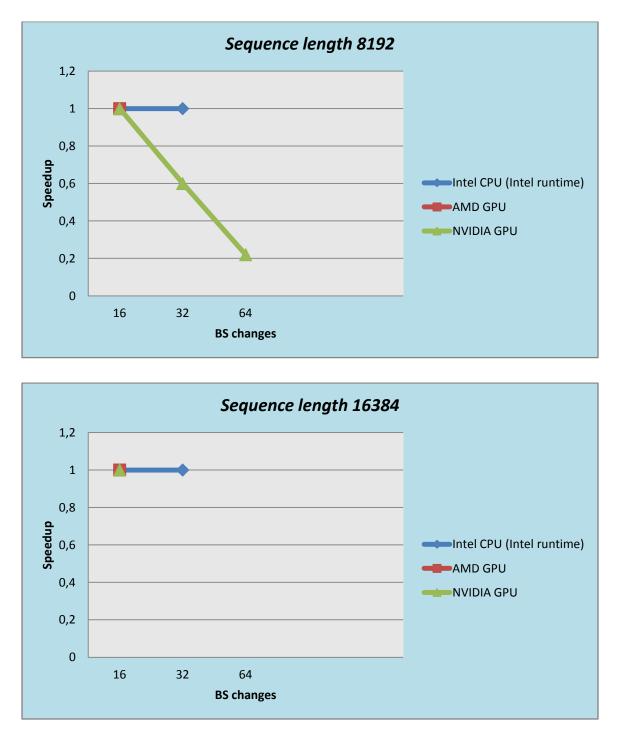

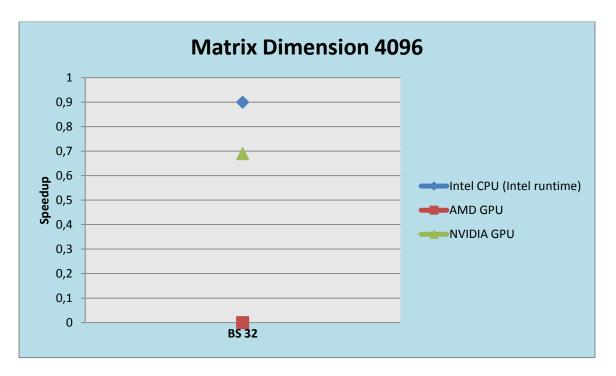

*Figure 6.2* and *Figure 6.3* depict the results for matrix dimension 4096 and 8192.

| Optimizations /<br>Devices (4096) | Intel CPU<br>(Intel runtime) | AMD GPU        | NVIDIA GPU     |

|-----------------------------------|------------------------------|----------------|----------------|

| Initial Code                      | 63,321,554 ns                | 110,547,551 ns | 30,023,648 ns  |

| 2x coarsening                     | 60,574,101 ns                | 174,268,240 ns | 55,017,120 ns  |

| 4x coarsening                     | 57,433,163 ns                | 279,506,877 ns | 65,330,656 ns  |

| 8x coarsening                     | 51,001,526 ns                | 495,125,112 ns | 83,164,480 ns  |

| 16x coarsening                    | 54,496,953 ns                | 925,336,786 ns | 116,684,256 ns |

| Optimizations /<br>Devices (4096) | Intel CPU<br>(Intel runtime) | AMD GPU | NVIDIA GPU |

|-----------------------------------|------------------------------|---------|------------|

| 2x coarsening                     | 1                            | 0.63    | 0.55       |

| 4x coarsening                     | 1.10                         | 0.40    | 0.46       |

| 8x coarsening                     | 1.24                         | 0.22    | 0.36       |

| 16x coarsening                    | 1.16                         | 0.12    | 0.26       |

| Optimizations /<br>Devices (8192) | Intel CPU<br>(Intel runtime) | AMD GPU                | NVIDIA GPU     |

|-----------------------------------|------------------------------|------------------------|----------------|

| Initial Code                      | 352,030,387 ns               | 4 <b>10,034,996</b> ns | 100,092,608 ns |

| 2x coarsening                     | 250,110,372 ns               | 653,036,769 ns         | 183,355,968 ns |

| 4x coarsening                     | 221,658,341 ns               | 1,065,818,329 ns       | 218,478,112 ns |

| 8x coarsening                     | 196,498,045 ns               | 1,901,088,454 ns       | 278,167,008 ns |

| 16x coarsening                    | 203,916,734 ns               | 3,571,183,673 ns       | 391,285,888 ns |

| Optimizations /<br>Devices (8192) | Intel CPU<br>(Intel runtime) | AMD GPU | NVIDIA GPU |

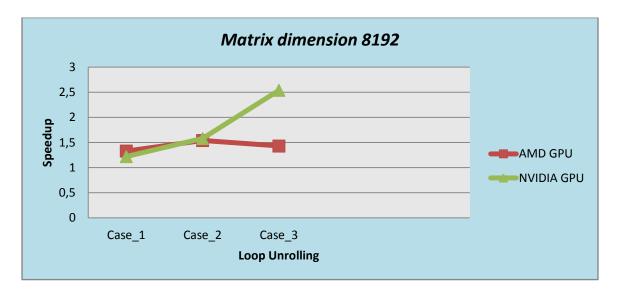

|-----------------------------------|------------------------------|---------|------------|