# A new distributed diffusion algorithm for dynamic load-balancing in parallel systems

Departament d'Informàtica Unitat d'Arquitectura d'Ordinadors i Sistemes Operatius

A thesis submitted by Ana Cortés Fité in fulfilment of the requirements for the degree of *Doctor per la Universitat Autònoma de Barcelona*.

Barcelona (Spain), September 2000

# A new distributed diffusion algorithm for dynamic load-balancing in parallel systems

Thesis submitted by Ana Cortés Fité in fulfilment of the requirements for the degree of Doctor per la Universitat Autònoma de Barcelona. This work has been developed in the Computer Science Department of the Universidad Autònoma de Barcelona and was advised by Dra. Ana Ripoll Aracil,

Bellaterra September, 2000

**Thesis Advisor**

Ana Ripoll Aracil

"... mami explica'm aquest conte."

#### **ACKNOWLEDGEMENTS**

A lot of people have made this work possible. I wish to express my sincere gratitude to them all for being there, for working with me and for helping me.

First of all I want to thank Ana Ripoll Aracil for being my advisor throughout this work, for her constant advice and never-ending encouragement. I have learned from her how to organise basic concepts and new ideas, and how to describe and transmit them with clarity.

I would like to express my gratitude to Emilio Luque for his suggestions at the outset of this work, as well as for his inestimable contribution to its development at certain critical moments.

My deepest thanks go to Miquel Angel Senar for his technical support and the clarity of his discussion of this work, and, particularly, for not being discouraged at my own discouragement, for bringing calm and good sense in moments of desperation and madness and, above all, for being there at all times. Without his support and affection this work would never have reached its conclusion.

Thanks to Ferran Cedó, member of the Department of Mathematics at the *Universitat Autònoma de Barcelona*, for his mathematical support in the formal detailed descriptions and analysis of this work.

To Tomàs Margalef for thinking of me at the very beginning of this work, and for getting me under starters' orders.

To Dani Franco and Indira Garcés for lending me the beta version of their network simulator in order to obtain "deadlock" free reliable communication times.

I would also like to thank María Serrano, Lola Reixachs, Eduardo César and Elisa Heymann for putting up with long talks with me without ever losing their patience.

Thanks to Josep Pons and Jaume Jo who have collaborated in the implementation of some of the programs related to this work.

Special thanks to Porfidio Hernández for his academic help during the period in which I was intensively preparing my lectures.

I am also grateful to the rest of my colleagues from the Computer Architecture and Operating Systems Group as well as to those who have passed through the Group during the gestation and preparation periods of this work, for their constant support and encouragement.

Last, but decidedly not least, I would like to thank my family for their support throughout this time, and especially my daughter Júlia who, without being aware of it, has given me the strength to cope with the work's tough final stage, and who has had to suffer in ignorance all of my many and various moods and frames of mind.

# Contents

| PREFACE                                                       | vii |

|---------------------------------------------------------------|-----|

| CHAPTER 1                                                     |     |

| THE DYNAMIC LOAD-BALANCING PROBLEM                            | 1   |

| 1.1 Introduction                                              | 3   |

| 1.2 KEY ISSUES IN THE LOAD-BALANCING PROCESS                  | 4   |

| 1.3 PROCESSOR LEVEL                                           | 5   |

| 1.3.1 Load Manager block                                      | 6   |

| 1.3.2 Load Balancing Algorithm block                          | 8   |

| Load Balancing Activation                                     | 8   |

| Work Transfer Calculation                                     |     |

| 1.3.3 Migration Manager block                                 | 10  |

| Load unit selection                                           |     |

| Load transfer                                                 |     |

| 1.4 SYSTEM LEVEL                                              |     |

| 1.4.1 Centralised                                             |     |

| 1.4.2 Totally distributed                                     |     |

| 1.4.3 Partially distributed                                   |     |

| 1.4.4 Synchronous versus asynchronous                         |     |

| 1.5 LOAD-BALANCING ALGORITHM TAXONOMY                         |     |

| 1.6 DYNAMIC LOAD-BALANCING STRATEGIES                         | 16  |

| 1.6.1 Randomised                                              | 17  |

| 1.6.2 Physical Optimisation                                   |     |

| 1.6.3 Diffusion                                               | 20  |

| 1.6.4 Dimension Exchange                                      | 22  |

| 1.6.5 Gradient Model                                          | 23  |

| 1.6.6 Minimum-direction                                       | 25  |

| 1.7 SOFTWARE FACILITIES FOR SUPPORTING DYNAMIC LOAD-BALANCING | 28  |

| 1.7.1 Architecture of Process-based LBS                       | 29  |

| 1.7.2 Design issues of a process migration mechanism          | 30  |

| Migration Initiation                                                      | 30 |

|---------------------------------------------------------------------------|----|

| State Capture                                                             | 30 |

| State Transfer                                                            |    |

| Process Restart                                                           | 32 |

| 1.7.3 Limitations of process migration mechanisms                         | 33 |

| 1.7.4 Examples of existing packages for supporting dynamic load balancing | 34 |

|                                                                           |    |

| •                                                                         |    |

| CHAPTER 2                                                                 |    |

| ·                                                                         |    |

| NEAREST-NEIGHBOUR LOAD-BALANCING METHODS                                  | 39 |

| 2.2 Basic notation and assumptions                                        | 41 |

| 2.3 ITERATIVE NEAREST-NEIGHBOUR LOAD BALANCING ALGORITHMS                 |    |

| 2.3.1 Algorithm convergence                                               |    |

| 2.3.2 Termination detection problem                                       |    |

| 2.4 ANALYSIS OF RELEVANT NEAREST-NEIGHBOURS LOAD BALANCING ALGORITHMS     |    |

| 2.4.1 The SID (Sender Initiated Diffusion) algorithm                      |    |

| 2.4.2 The GDE (Generalised Dimension Exchange) algorithm                  |    |

| 2.4.3 The AN (Average Neighbourhood) algorithm                            |    |

| 2.5 SUMMARY OF THIS CHAPTER                                               |    |

| 2.5 GOVINANT OF THIS CHAITER                                              |    |

|                                                                           |    |

|                                                                           |    |

| CILADTED 2                                                                |    |

| CHAPTER 3                                                                 |    |

| DASUD LOAD-BALANCING ALGORITHM                                            | 71 |

|                                                                           |    |

| 3.1 DASUD (DIFFUSION ALGORITHM SEARCHING UNBALANCED DOMAINS)'S MOTIVA     |    |

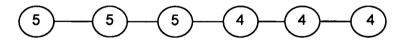

| 3.2 DESCRIPTION OF THE DASUD ALGORITHM                                    |    |

| 3.2.1 Description of the first stage of DASUD                             |    |

| 3.2.2 Description of the second stage of DASUD                            |    |

| Searching Unbalanced Domains (SUD) block                                  |    |

| Fine Load Distribution (FLD) block                                        |    |

| Sending Instruction Message (SIM) block                                   |    |

| Processing Instruction Messages (PIM) block                               | 81 |

| 3.3 AN EXAMPLE OF DASUD EXECUTION      | N                                      | 83  |

|----------------------------------------|----------------------------------------|-----|

| 3.4 DASUD'S COMPLEXITY                 |                                        | 86  |

| 3.5 DASUD'S CONVERGENCE                |                                        | 88  |

| 3.6 DASUD'S CONVERGENCE RATE           | ······································ | 98  |

| 3.7 PERFECT LOCAL BALANCE ACHIEVED     | BY DASUD                               | 99  |

| 3.8 GLOBAL BALANCE DEGREE ACHIEVE      | D BY DASUD                             | 101 |

| CHAPTER 4                              |                                        |     |

| COMPARATIVE STUDY OF N                 |                                        |     |

| BALANCING ALGORITHMS.                  |                                        | 103 |

| 4.1 SIMULATION FRAMEWORK               |                                        | 105 |

| 4.1.1 Interconnection Networks         |                                        | 107 |

| 4.1.2 Synthetic Load distributions     |                                        | 108 |

| 4.2 QUALITY METRICS                    |                                        | 111 |

| 4.3 STABILITY ANALYSIS                 |                                        | 112 |

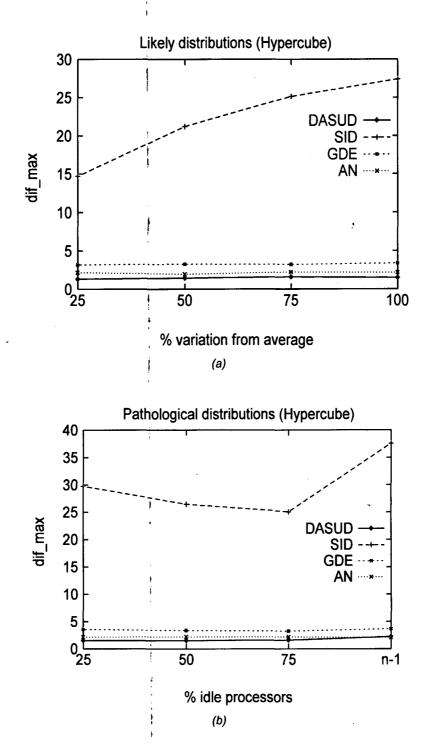

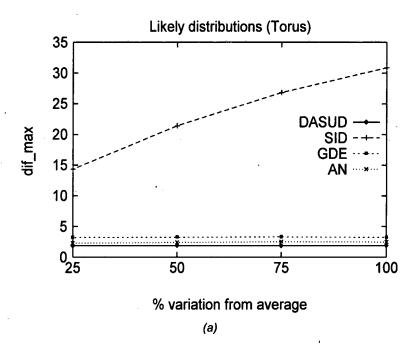

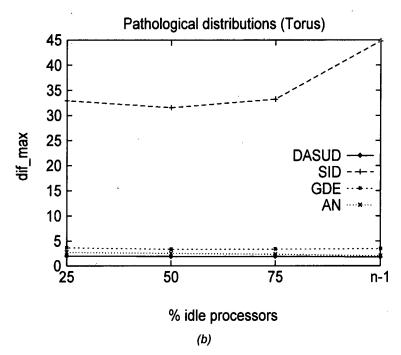

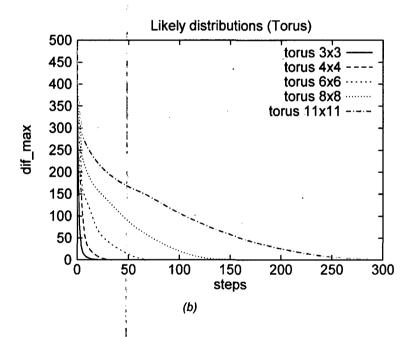

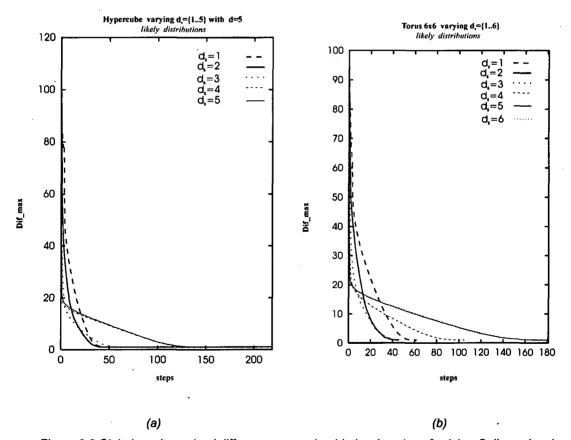

| 4.3.1 Influence of the initial load d  | istribution pattern in the dif_max     | 113 |

| 4.3.2 Influence of the system size in  | the dif_max                            | 116 |

| 4.3.3 Influence of the initial load d  | istribution shape in the dif_max       | 117 |

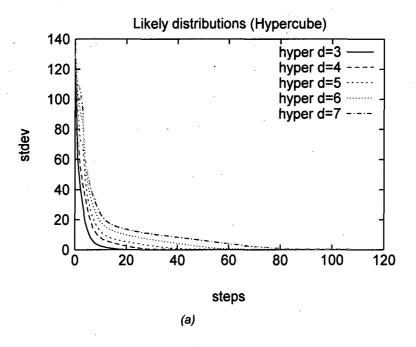

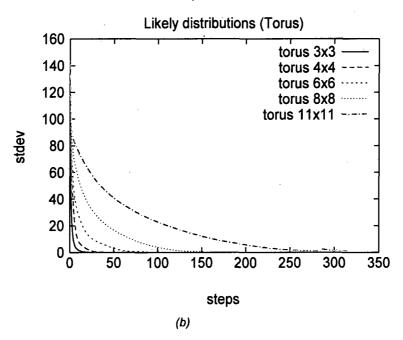

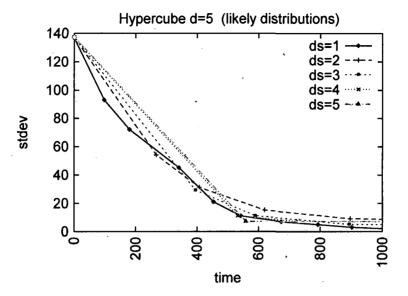

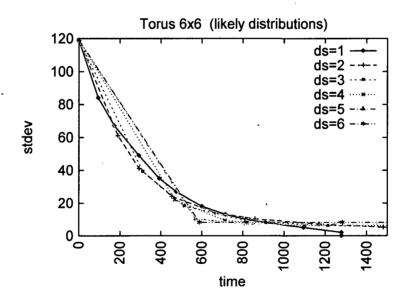

| 4.3.4 Influence of the initial load d  | istribution pattern in the $\sigma$    | 119 |

| 4.3.5 Influence of the system size in  | 1 the σ                                | 120 |

| 4.3.6 Influence of the initial load d  | istribution shape in the $\sigma$      | 122 |

| 4.3.7 Conclusions of the stability a   | nalysis                                | 122 |

| 4.4 EFFICIENCY ANALYSIS                |                                        | 124 |

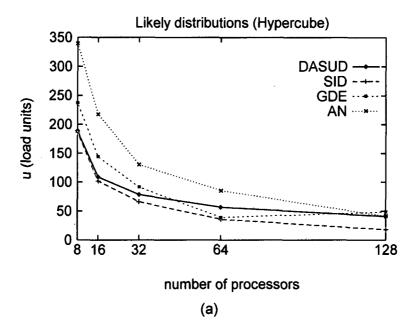

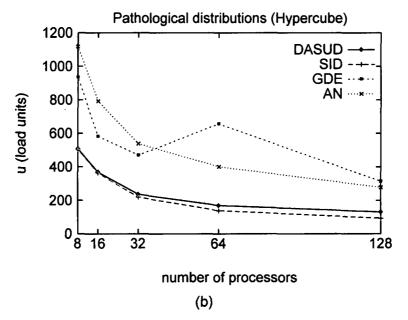

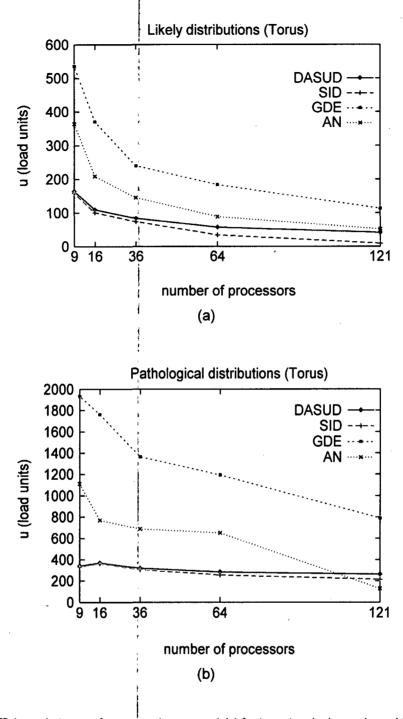

| 4.4.1 Influence of the initial load d  | istribution pattern in u               | 124 |

| 4.4.2 Influence of the system size in  | ı u                                    | 125 |

| 4.4.3 Influence of the initial load d  | istribution shape in u                 | 129 |

| 4.4.4 Influence of the initial load di | istribution pattern in steps           | 130 |

| 4.4.5 Influence of the system size in  | steps                                  | 131 |

| 4.4.6 Influence of the initial load di | istribution shape in steps             | 135 |

| 4.4.7 Conclusions of the efficiency    | analysis                               | 136 |

| 4.5 SUMMARY AND CONCLUSIONS OF THE     | E COMPARATIVE STUDY                    | 137 |

|                                        |                                        |     |

## **CHAPTER 5**

| SCALABILITY OF DASUD                                     | 139 |

|----------------------------------------------------------|-----|

| 5.1 Introduction                                         | 141 |

| 5.2 DASUD'S SCALABILITY WITH RESPECT TO THE PROBLEM SIZE | 142 |

| 5.3 DASUD'S SCALABILITY WITH RESPECT TO THE PROBLEM SIZE | 145 |

| 5.4 CONCLUSION ABOUT DASUD'S SCALABILITY                 | 150 |

| •                                                        |     |

| CHAPTER 6                                                |     |

| ENLARGING THE DOMAIN (D <sub>S</sub> -DASUD)             | 151 |

| 6.1 Introduction                                         | 153 |

| 6.2 EXTENDED SYSTEM MODEL                                | 154 |

| 6.3 METRICS                                              | 156 |

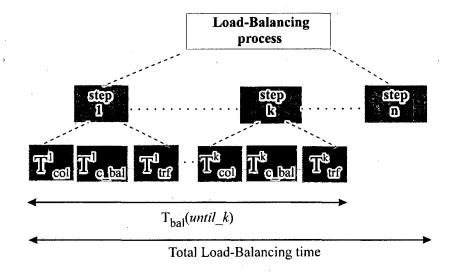

| 6.3.1 Communication periods                              | 157 |

| The information collection period ( $T_{col}^{s}$ )      | 159 |

| The transfer period ( $T_{trf}^{s}$ )                    | 159 |

| 6.3.2 Computational period ( $T^s_{c\_bal}$ )            | 159 |

| 6.3.3 Trade-off factor ( $t_off(k)$ )                    | 160 |

| 6.4 THE EXPERIMENTAL STUDY OF D <sub>S</sub> -DASUD      | 161 |

| 6.4.1 The best degree of final balance                   | 162 |

| 6.4.2 Greater unbalancing reduction                      | 170 |

| 6.5 CONCLUSIONS TO THIS CHAPTER                          | 174 |

| CHAPTER 7                                                |     |

| CONCLUSIONS AND FUTURE WORK                              | 177 |

| 7.1 CONCLUSIONS AND MAIN CONTRIBUTIONS                   | 179 |

| 7.2 CURRENT AND FUTURE WORK                              | 184 |

| •                                                        |     |

| REFERENCES                                               | 187 |

### APPENDIX A

| DASUD LOAD-BALANCING ALGORITHM: EXPERIMENTAL       |                  |  |  |

|----------------------------------------------------|------------------|--|--|

| AND THEORETICAL ANNEXES                            | A.1              |  |  |

| A.1 EXPERIMENTAL VALIDATION OF DASUD'S FINAL BALAN | CE DEGREEA.3     |  |  |

| A.2 EXPERIMENTAL VALIDATION OF DASUD'S CONVERGENCE | E RATE A.4       |  |  |

| A.3 A REALISTIC LOAD-BALANCING MODEL               | A.6              |  |  |

| APPENDIX B                                         |                  |  |  |

| COMPARATIVE STUDY OF NEAREST-NE                    | IGHBOUR LOAD-    |  |  |

| BALANCING ALGORITHMS: COMPLEME                     | NTARY TABLES B.1 |  |  |

| APPENDIX C                                         |                  |  |  |

| ENLARGING THE DOMAIN (ds-DASUD): C                 | COMPLEMENTARY    |  |  |

| FIGURES                                            | C.1              |  |  |

| APPENDIX D                                         |                  |  |  |

| ENLARGING THE DOMAIN (Ds-DASUD): 0                 | COMPLEMENTARY    |  |  |

| FIGURES AND TARIES                                 | D 1              |  |  |

#### **PREFACE**

Advances in hardware and software technologies have led to increased interest in the use of large-scale parallel and distributed systems for database, real-time, and large-scale scientific and commercial applications. The operating systems and management of the concurrent processes constitute integral parts of the parallel and distributed environments. One of the biggest issues in such a system is the development of effective techniques for the distribution of processes among processing elements to achieve some performance goal(s), such as minimising execution time, minimising communication delays, and/or maximising resource utilisation. Load-balancing is one of the most important problems which have to be solved in order to enable the efficient use of multiprocessor systems. Load-balancing aims at improving the performance of multiprocessor systems by equalising the computational load over all processors in the system since it is commonly agreed that equally balancing loads between all processors in the system directly leads to a minimisation of total execution time.

There are applications that can be partitioned into tasks with regular computation and communication patterns and, therefore, load-balancing algorithms can be used to assign computational tasks to processors before beginning the execution. This is called static load-balancing. However, there is an important and increasingly common class of scientific applications (such as particle/plasma simulations, parallel solvers for partial differential equations, numerical integration, N-body problem to name just a few) where the computational load associated with a particular processor may change over the course of a computation and cannot be estimated beforehand. For this class of non-uniform problems with unpredictable a priori computation and communication requirements, dynamic load-balancing algorithms are needed to efficiently distribute the computational load at run time on the multiprocessor system. This work is about dynamic load-balancing in message-passing parallel computers where, in general, a direct, point-to-point interconnection network is used for communication. Load-balancing is performed by transferring load from heavily to lightly loaded processors. For that purpose, a load-balancing

algorithm has to resolve the issues of *when* to invoke a balancing operation, *who* makes load-balancing decisions according to what information and *how* to manage load migrations between processors. We can find several answers to these questions which results in a wide set of load-balancing techniques.

A highly popular class of load-balancing strategies are nearest-neighbour approaches which are edge-local, that is, methods that can be implemented in a local manner by each processor consulting only its neighbours, thereby avoiding expensive global communication in distributed applications. The load moved along each edge is related to the gradient in the loads across it. These kinds of distributed load-balancing algorithms are appealingly simple and they degrade gracefully in the presence of asynchrony and faults. Most of these algorithms are implemented in an iterative way to achieve a global load balanced state and, therefore, they are referred to as iterative load-balancing algorithms. The load balance stems from successive approximations to a global optimal load distribution by only being concerned with local load movements. In the ideal case, a perfect state is achieved when all processors have the same load. These kinds of load-balancing algorithms are suited to appreciably decreasing large imbalances.

Most iterative load-balancing algorithms proposed in the literature consider an idealised version of the load-balancing problem in which the loads are treated as real numbers; therefore, loads can be split to arbitrary. However, in a more realistic setting of the problem, which covers medium and large grain parallelism, the loads (processes, data, threads) are not infinitely divisible and, as a consequence, they are treated as natural numbers. There are two categories of load-balancing algorithms that consider discrete load model. On the one hand, the load-balancing algorithms that were originally designed under the discrete load model assumption, and, on the other hand, the discrete adaptation of the idealised load-balancing algorithms by performing rounding operations. Iterative load-balancing algorithms using discrete load model produce situations in which a global load balance cannot be guaranteed when the load-balancing process terminates. Furthermore, the convergence analysis of these iterative load-balancing algorithms using discrete load model has not been explored in the literature.

We raised the issue of the development of a realistic iterative load-balancing algorithm which was able to solve the balancing problems of existent discrete load-balancing algorithms in an asynchronous fashion. One important goal in this work was to derive a rigorous mathematical description of the proposed algorithm, which allows us to analyse its convergence, as well as other formal aspects of the algorithm such as its complexity and convergence rate. The proposed algorithm called DASUD (Diffusion Algorithm Searching Unbalanced Domains) is noteworthy for its ability to detect locally unbalanced situations that are not detected by other algorithms and for always achieving the optimal local balance distribution

Once DASUD was fully described, we were interested in comparing our proposal to the most relevant load-balancing strategies within the same family, in order to evaluate the goodness of DASUD. For that purpose, we raised the need to develop a simulation environment in which to be able to simulate the whole load-balancing process for different iterative load-balancing algorithms under the same conditions. Parameters such as topology, load distributions, system size and problem size should be easily variable in order to analyse the influence of each of them on the behaviour of the simulated load-balancing algorithms.

By simulation we have compared our algorithm with three well-known nearest-neighbours load-balancing algorithms within the literature attending to two quality measurements: stability and efficiency. Stability measures the ability of the algorithm to coerce any initial load distribution into a global stable state as close to even as possible. Efficiency measures the time delay for arriving at the globally stable state. From the results we are able to conclude that DASUD exhibits the best trade-off between the degree of balance achieved and the time incurred to reach it.

#### This work is organised as follows:

The first chapter gives an overview of the dynamic load-balancing problem in parallel computing where the key issues that must be considered in this problem are described. Following this, a load-balancing algorithm taxonomy that illustrates how load distribution can be carried out is developed, and a simple description of the most relevant dynamic load-balancing strategies is included.

- The second chapter is focused on the nearest-neighbour load-balancing methods. Since this kind of load-balancing algorithms works in an iterative way, two important issues such as the algorithm convergence and its termination detection are discussed. Three relevant load-balancing algorithms from this category are described and analysed in detail.

- In chapter three the proposed dynamic load-balancing algorithm DASUD is described and analysed. DASUD's complexity is provided, as well as its convergence proof and upper bounds for the final balance degree and the number of balance iterations needed to achieve it.

- In chapter four the proposed load-balancing algorithm is compared by simulation to three of the most relevant load-balancing algorithms within the nearest-neighbour category that were described in chapter 2. The simulation framework has been designed including different interconnection networks as well as a wide range of system sizes. Moreover, the load distribution patterns simulated vary from situations which exhibit lightly unbalanced degree to highly unbalanced situations. The comparison has been carried out in terms of the unbalance degree reached by the algorithms and the time needed to achieve this final state.

- In chapter five the scalability of the proposed strategy is analysed in order to show the capacity of reacting similarly under different problem and system sizes.

- A question that ocurred to us during the evaluation of DASUD was: how would DASUD work if it was able to collect more load information than only that of its immediate neighbours?. For that purpose, in chapter six, an extended system model is provided. The influence of enlarging the domain into the time incurred in transferring messages beyond one link, and the extra computational cost

incurred by the extended version of DASUD ( $d_s$ -DASUD) has been also considered to evaluate which enlargement provides the best trade-off between balance improvement and the load-balancing time spent.

- Chapter seven summarises the main conclusions derived from this thesis, outlining, in addition, current and future work in this field.

- Finally, the complete bibliography is provided, and complementary tables and figures are included in four appendixes.

# Chapter 1

## The dynamic load-balancing problem

#### **Abstract**

This chapter gives an overview of the dynamic load-balancing problem in parallel computing where, firstly, the key issues that must be considered in this problem are described. Following this, a load-balancing algorithm taxonomy that illustrates how load distribution can be carried out is presented, as well as a simple description of the most relevant dynamic load-balancing strategies. Finally, environments and existing tools for supporting load-balancing are described.

#### 1.1 Introduction

When a parallel application is divided into a fixed number of processes (tasks) that are to be executed in parallel, each processor performs a certain amount of work. However, it may be that some processors will complete their tasks before others and become idle because the work is unevenly divided, or some processors operate faster than others, or both situations, Ideally, all the processors should be operating continuously on tasks that would lead to the minimum execution time. Achieving this goal by spreading the tasks evenly across the processors is called load-balancing. Load-balancing can be attempted statically before the execution of any process, or dynamically during the execution of the processes. Static loadbalancing is usually referred to as the mapping problem or scheduling problem. Dynamic load-balancing techniques assume little or no compile-time knowledge of the runtime parameters of the problem, such as task execution times or communication delays. These techniques are particularly useful in efficiently resolving applications that have unpredictable computational requirements or irregular communication patterns. Adaptive calculations, circuit simulations and VLSI design, N-body problems, parallel discrete event simulation, and data mining are just a few of those applications.

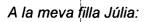

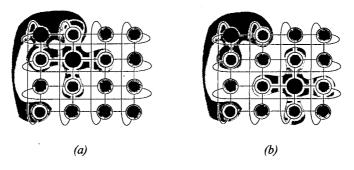

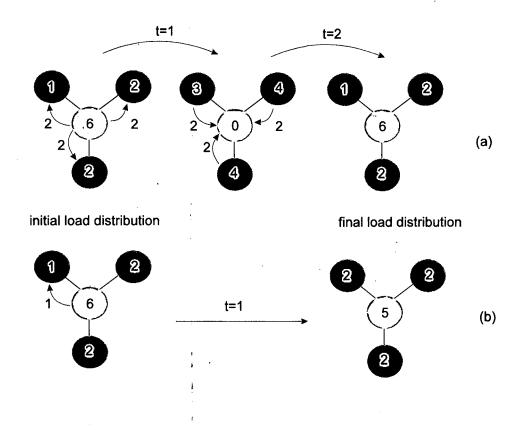

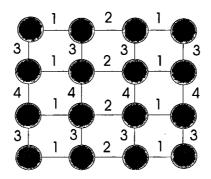

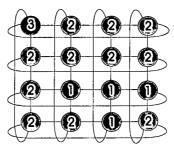

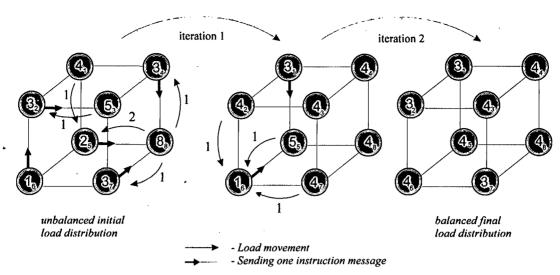

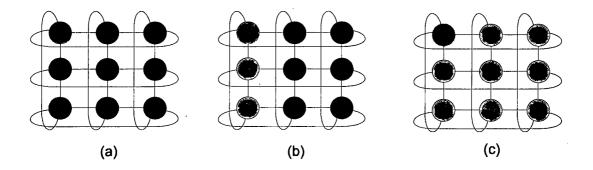

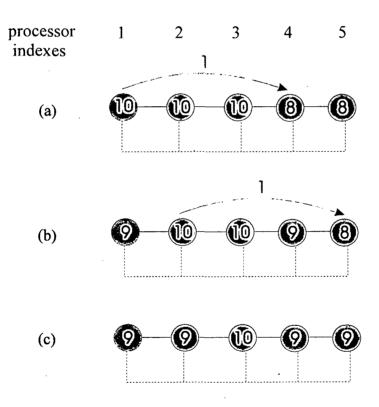

Dynamic load-balancing (DLB) is based on the redistribution of load among the processors during execution time, so that each processor would have the same or nearly the same amount of work to do. This redistribution is performed by transferring load units (data, threads, processes) from the heavily loaded processors to the lightly loaded processors with the aim of obtaining the highest possible execution speed. DLB and load sharing are used as interchangeable terms in the literature. While DLB views redistribution as the assigning of the processes among the processors, load sharing defines redistribution as the sharing of the system's processing power among the processes. The results of applying an ideal DLB algorithm to a 3x3 torus is shown in figure 1.1. The numbers inside the circles denote

In this context, both terms (process and tasks) are used indistinctly.

the load value of each processor. Initially, at time ( $t_0$ ) the load is unevenly distributed among the processors. The load becomes the same in all processors after executing an ideal DLB strategy (time  $t_0$ ).

Figure 1.1. Dynamic load-balancing process.

Every DLB strategy has to resolve the issues of when to invoke a balancing operation, who makes load-balancing decision according to what information and how to manage load migrations between processors. There has been much research on DLB strategies for distributed computing systems. However, on parallel computing systems, the DLB problem takes on different characteristics. First, parallel computers typically use a regular point-to-point interconnection network, instead of random network configuration. Second, the load imbalance in a distributed computer is due primarily to external task arrivals, whereas the load imbalance in a parallel computer is due to the uneven and unpredictable nature of tasks.

The advantage of dynamic load-balancing over static load-balancing is that the system need not be aware of the run-time behaviour of the applications before execution. Nevertheless, the major disadvantage of DLB schemes is the run-time overhead due to the load information transfer among processors, the execution of the load-balancing strategy, and the communication delays due to load relocation itself.

#### 1.2 Key issues in the Load-Balancing process

The design of a dynamic load-balancing algorithm requires resolving issues such as: who specifies the amount of load information made available to the decision-maker; who determines the condition under which a unit of load should be transferred; who identifies the destination processor of load to transfer; and how to

manage load migrations between processors, amongst other issues. Combining different answers to the above questions results in a large area of possible designs of load-balancing algorithms with widely varying characteristics. On the one hand, there are decisions which must be taken at processor level, and others that require a greater or lesser degree of co-ordination between different processors, so the latter become system-level decisions.

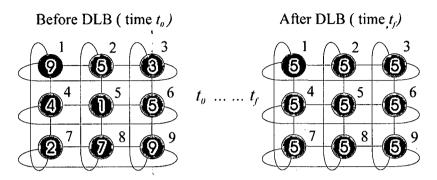

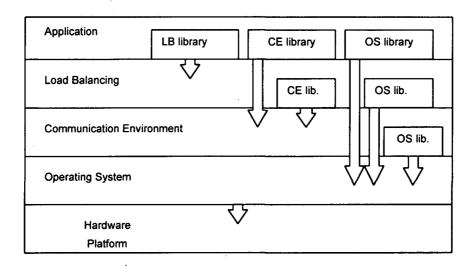

In order to be systematic in the description of all necessary decisions related to the load balancing process, we distinguish two different design points of view: the *processor* level point of view and the *system* level point of view (see figure 1.2). We refer to *processor level* when the load-balancing operations respond to decisions taken by a processor. Otherwise, we talk about *system level* when the decisions affect a group of processors. In the following sections, we outline the description of each one of these levels.

Figure 1.2. Load-balancing: two design points of view

#### 1.3 Processor level.

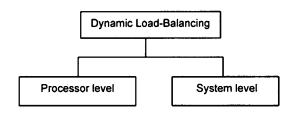

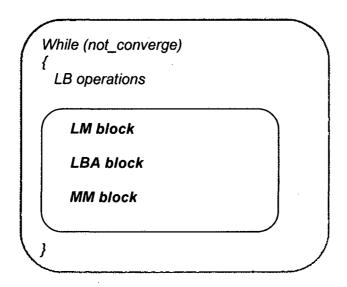

A processor which intervenes in the load-balancing process will execute computational operations both for applications tasks as well as for load-balancing operations. This section describes the load-balancing operations carried out at processor level and their design alternatives. In order to perform the load-balancing operations, a processor must allocate three functional blocks to effectively implement the load-balancing process: the Load Manager (LM), the Load-Balancing Algorithm (LBA) and the Migration Manager (MM), as shown in figure 1.3. The Load Manager block is the one related to all load-keeping issues. The Load-Balancing Algorithm block is related to the concrete specification of the load-balancing strategy. Finally, a Migration Manager block is needed in order to actually perform the load movements.

The processors, which incorporate each one of these three blocks, will be referred to as *running processors*.

Figure 1.3 Functional blocks that integrate the load-balancing process within a processor.

The next sections will discuss the implementation issues for each one of these blocks, as well as their co-operation.

#### 1.3.1 Load Manager block

One of the most important issues in the load-balancing process is to quantify the amount of load (data, threads or processes) of a given processor (load index). It is impossible to quantify exactly the execution time of the resident processes of a processor. Therefore, some measurable parameters should be used to determine the load index in a system such as the process sizes, the number of ready processes, the amount of data to be processed and so on. However, previous studies have shown that simple definitions such as the number of ready processes are particularly effective in quantifying the load index of a processor [Kun91].

The Load Manager block has the responsibility of updating the load information of the running processor, as well as gathering load information from a set of processors of the system (underlying domain). The time at which the load index of each processor is to be updated is known as the load evaluation instant. A non-negative variable (integer or real number), taking on a zero value if the processor is idle and taking on increasing positive values as the load increases, will be measured at this time according to the load unit definition [Fer87]. There must be a trade-off between the load gathering frequency and the ageing of the load information kept by the LM block, in order to avoid the use of obsolete values by the Load Balancing Algorithm block. This trade-off is captured in the following three load collection rules:

- On-demand: Processors collect the load information from each other whenever a load-balancing operation is about to begin or be initiated [Sta84][Zna91].

- Periodical: Processors periodically report their load information to others, regardless of whether the information is useful to others or not [Yua90][Kal88].

- On-state-change: Processors disseminate their load information whenever their state changes by a certain degree [Xu95] [Sal90].

The on-demand load-gathering method minimises the number communication messages, but postpones the collection of system-wide load information until the time when a load-balancing operation is to be initiated. Its main disadvantage is that it results in an extra delay for load-balancing operations. Typically, this category includes bidding methods, where underloaded processors ask for load information from other processors to choose the best partner in performing load-balancing [Sta84][Zna91]. Conversely, the periodic method allows processors in need of a balancing operation to initiate the operation based on maintained load information without delay. The problem with the periodical scheme is how to set the interval for information gathering. A short interval would incur heavy communication overheads, while a long interval would sacrifice the accuracy of the load information used in the load-balancing algorithm. A protocol to exchange load information periodically called LIEP (Load Information Exchange Protocol) was presented in [Yua90]. In that work processors were arranged into a logical hypercube with dimension d (the topology diameter). During each period of load information exchange, a processor invoked d rounds of load exchanges in such a way that a processor exchanged its load value with the directly connected processor in the inspected dimension. A way to optimise the load collection process is reported in [Kal88] where the methodology proposed consists of periodically piggy-backing the load information with regular messages. The on-state-changing rule is a compromise of the on-demand and periodic schemes. In [Sal90] an on-state-changing method is reported in order to include the advantages of both approaches. In this case, a processor sends a status message to its neighbours only if its own load has changed

by a certain value and an updated interval has elapsed since the last update. This reduces unnecessary frequent updates.

Nevertheless, how the LM block proceeds to collect and hold load information is not relevant to the Load Balancing Algorithm block. The information required by this block is limited to a set of non-negative numbers that represent the load index of each one of the processors belonging to the underlying domain. These values will be used subsequently to evaluate whether it is necessary to perform load movements or not and how these movements must be performed.

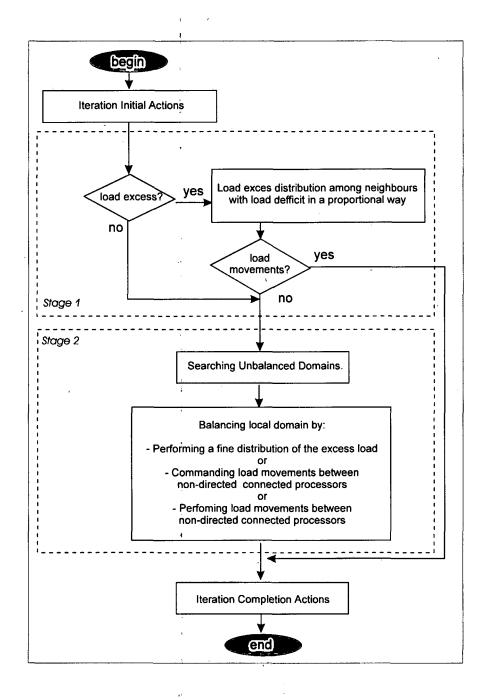

#### 1.3.2 Load Balancing Algorithm block

The Load Balancing Algorithm block uses the load information provided by the previous LM block in deciding if it is necessary or not to balance the load, source and destination processors of load movements, as well as the amount of load to be transferred. An LBA algorithm, can be divided into two phases: Load Balancing Activation and Work Transfer Calculation.

#### Load Balancing Activation

This phase uses the load information kept by the LM block to determine the presence of a load imbalance. The criterion used to evaluate whether a processor is balanced or not is known as *trigger condition* and is normally associated to a threshold value that can be defined as:

- Fixed threshold: one or several fixed values are used as criteria to determine whether a processor is an overloaded processor or not [Zho88] [Mun95].

- Adaptive threshold: the threshold values are evaluated during the execution of the load-balancing algorithm and their values are usually state dependent [Wil93][Xu93][Cor99c].

Usually, the election of fixed thresholds as trigger condition produces simple strategies where each processor compares its load index with a fixed threshold to determine whether a processor has load excess (overloaded) or not (underloaded). In applications where the total load is expected to remain fairly constant, the load

balancing would be undertaken only in those cases where the load index of some processor falls outside specified upper and lower thresholds [Mun95].

Another method that has been suggested for situations in which the total load is changing is to balance load if the difference between a processor's load and the local load average (i.e. the average load of a processor and its neighbors) exceeds some threshold [Cor99c][Wil93]. Another similar approach consists of setting the threshold value using the global load average instead of the local load average to determine the trigger condition at each processor [Xu93].

All running processors in the system will evaluate the trigger condition at the start of executing the load-balancing algorithm. However, not all the running processors will overcome their trigger condition. The processors whose trigger condition evaluation does not fail will be called *active processors*. We refer to sender-initiated (SI) approaches when active processors are the ones with load excess and we refer to received-initiated (RI) schemes, [Eag85][Wil93], when the underloaded processors will become the active processors by requesting load from their overloaded counterpart.

#### Work Transfer Calculation

This phase is concerned with devising an appropriate transfer strategy to correct the imbalance previously detected and measured. After determining that load-balancing is required, *source* and *destination* processor pairs are determined, as well as *how much work* should be transferred from one processor to another. The function used to determine the destination of load can be implemented using one of the following choices:

- Randomly: no information about the domain state of the underlying processor is needed and destination processors are chosen in a random fashion [Zho88].

- Fixed: decisions produced by the active processors are not state dependent. The quantity of load to be transferred from one processor to another is set a priori as a fixed value. [Xu97][Cyb89].

- Evaluated: the amount of load to be moved between processors is evaluated at run time following some predetermined function [Wil93][Cor99c]

#### 1.3.3 Migration Manager block

Finally, the last block is the Migration Manager (MM) block. This block receives as input the information generated by the Load Balancing Algorithm block, i.e., the destination processors and the amount of load that should be transferred to them. This block can be divided into two phases: *load unit selection* and *load transfer*, in order to differentiate between the way of choosing the individual load units to be transferred, and the physical transfer of those elements. Both phases are described below.

#### Load unit selection

Source processors *select* the most suitable *load units* (process, threads, data,...) which properly match with the load value to be moved. The quality of load-unit selection directly affects the ultimate quality of load-balancing. Sometimes, it may prove to be impossible to choose a group of load units whose associated load index corresponds exactly to the value that needs to be moved. The problem of selecting which load units to move is weakly NP-complete, since it is simply the subset sum problem. Fortunately, approximation algorithms exist which allow the subset sum problem to be solved to a specified non-zero accuracy in polynomial time [Pap94]. Before considering such an algorithm, it is important to note that other concerns may constrain load transfer options. In particular, we would like to avoid costly transfers of either large numbers of processes or large quantities of data unless absolutely necessary. We would also like to guide load selection to preserve, as best as possible, existing communication locality in the application. In general, we would like to associate a cost with the transfer of a given set of load units and then find the lowest cost set for a particular desired transfer.

#### Load transfer

This module should provide the appropriate mechanisms to correctly migrate several selected load units (which can be either processes, data or threads) to any destination processor. Data migration load-balancing systems support dynamic balancing through transparent data redistribution. Data migration mechanisms usually exhibit the lowest complexity amongst the three mechanisms as they only have to move data-systems based on thread migration support dynamic load balancing

through thread redistribution in multithreading environments. In such systems, a user application consists of a number of processes assigned to different processors and process encapsulates a certain number of threads that can created/destroyed dynamically. Transparent migration of threads implies the movement of the data and the computation state of a particular thread for one process located in a processor to another process located in a different processor. Process migration load-balancing systems support dynamic load balancing through transparent process redistribution in parallel and/or distributed computing environments. As in thread migration load-balancing systems, process migration implies the movement of the data and the computation state. However, process migration mechanisms exhibit the highest complexity as they must be aware of a huge amount of information. In the case of a process, the computation state is considerably more complex compared to the thread case and, moreover, application binaries must also be moved. In section 1.8, a more detailed description of the migration mechanisms provided by some load-balancing software packages is reported.

After having described the behaviour of each one of the blocks corresponding to one load-balancing operation, it is important to indicate that this decomposition in the load-balancing process in different modules allows us to experience in a plugand-play fashion with different implementations at each one of the above blocks, allowing the space of techniques to be more fully and readily explored. It is also possible to customise a load-balancing algorithm for a particular application by replacing some general methods with those specifically designed for a certain class of computations.

#### 1.4 System level

This level analyses which processors are involved in the load-balancing process and how their co-operation is carried out. Hence, the first decision that must be considered is the election of the set of running processors that participates in the load-balancing process. Depending on the number of processors belonging to this set we can distinguish between: *centralised*, *totally distributed* and *semi-distributed*

approaches. In totally distributed and semi-distributed schemes the load-balancing goal is obtained because load-balancing operations are concurrently executed in more than one processor as time goes by. In particular, when the load-balancing blocks are executed simultaneously in all running processors of the system, we are considering a *synchronous* implementation of the load-balancing process. Otherwise, the system works in an *asynchronous* way. The influence of each one of above characteristics in the load-balancing process will be discussed in next subsections.

#### 1.4.1 Centralised

Centralised load balancing strategies are characterised by the use of a dedicated processor for maintaining a global view of the system state and decision making. This processor is called central scheduler (or central job dispatcher). A central strategy can improve resource utilisation by having all the information of processors and it can achieve optimal performance by using sophisticated algorithms. It can also impose less overhead on the communication network by avoiding transfers of duplicate or inaccurate host state information. Global scheduling can also avoid task thrashing caused by contradictory load balancing decisions. However, centralised models have low reliability. If the central processor fails, the operation of the whole system can be corrupted. In addition, in large systems with high load fluctuation, the messages with load information can overload the interconnection structure around the central processor.

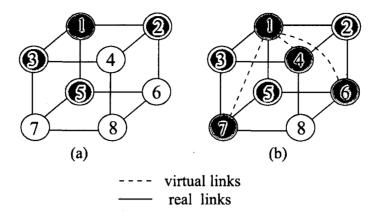

#### 1.4.2 Totally distributed

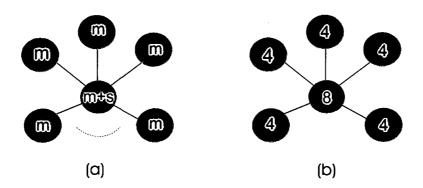

An alternative to centralised approaches is a *distributed* scheme, in which the load-balancing decisions are carried out by all the processors of the system. Load information exchanges are restricted to a local sphere of processors and load-balancing operations are also performed within this sphere or domain. Depending on the existing relationship between different domains, we can distinguish between *overlapped* domains or *non-overlapped* domains. In figure 1.4, the processors in red are chosen as the running processor. In this example, we consider the domain of a given processor as the processors directly connected to it. Therefore, with the blue and yellow colours we indicate the domains of each one of the running processor. In figure 1.4, a we can observe that there are some common processors between the

blue and the yellow domains. Hence, we refer to them as overlapped domains. Otherwise, we refer to non-overlapped domains (figure 1.4.b).

Figure 1.4. Overlapped domains (a) and non-overlapped domains (b).

When the domain includes a given processor and its immediate neighbours we refer to it as a *nearest–neighbour* approach. Nearest-neighbour load-balancing methods operate on the principle of reducing the load imbalance between each processor and its immediate neighbours with the aim of diffusing load through the system converging toward a system-wide balance. Otherwise, load-balancing strategies are categorised as *non-nearest-neighbour* approaches. Non-nearest-neighbour load- balancing alternatives work in a decentralised form by using local information, which is not restricted to immediate neighbours. Under this assumption the scope of the domain is extended to a large *radius* that may also include the neighbours' neighbours and so on.

Totally distributed approaches, in using local information, do not make such effective balance decisions as Centralised approaches, but, in contrast, they incur smaller synchronisation overheads.

#### 1.4.3 Partially distributed.

For large systems (more than 100 processors), neither centralised nor distributed strategies proved to be appropriate. Although centralised strategies have the potential of yielding optimal performance, they also have disadvantages that make them suitable only for small or moderate systems [Bau88]. On the other hand, distributed strategies have good scalability, but for large systems it is difficult to achieve a global optimum because the processors have a limited view of the global

system state. Partially distributed strategies (also called semi-distributed) were proposed as a trade-off between centralised and fully distributed mechanisms. The main idea is to divide the system into regions and thus split the load-balancing problem into subtasks. These strategies can be viewed at two levels: (i) load-balancing within a region and (ii) load-balancing among all the regions.

Different solutions can be devised for each level of the strategy. Each region is usually managed by a single master-processor using a centralised strategy and, at the level of the region, master-processors may (or may not) exchange aggregated information about their corresponding regions.

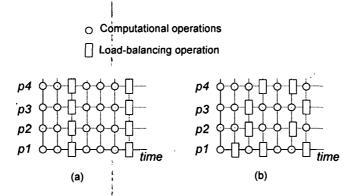

#### 1.4.4 Synchronous versus asynchronous

Taking into account the instant at which load-balancing operations are invoked, both totally and partially distributed strategies can be further subdivided into synchronous and asynchronous strategies. From this point of view, we talk about synchronous algorithms when all processors involved in load-balancing (running processors) carry out balancing operations at the same instant of time so that each processor cannot proceed with normal computation until the load migrations demanded by the current operations have been completed. Otherwise, if each running processor performs load-balancing operations regardless of what the other processors do, we refer to asynchronous approaches. Figure 1.5 shows these behaviours for a four processor system. Notice that the distinction between synchronous and asynchronous does not apply for centralised schemes due to the existence of only one running processor in the entire system.

Figure 1.5. Synchronous (a) and asynchronous (b) load-balancing operations.

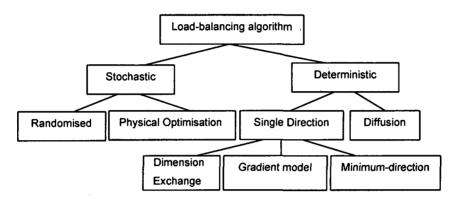

#### 1.5 Load-balancing algorithm taxonomy

Most of the load-balancing strategies proposed in the literature are focused basically on the development of approaches for solving the Load Balancing Algorithm block mentioned in section 1.3.2. In terms of the algorithmic method used by these strategies we can derive the taxonomy shown in figure 1.6. The main criteria in classifying these algorithms concerns the way in which load distribution is carried out.

Figure 1.6. Load-Balancing taxonomy in terms of algorithmic aspects from the processor level point of view.

In **Stochastic** methods, the load is redistributed in some randomised fashion, subject to the objective of load balancing. Stochastic load balancing methods attempt to drive the system into an equilibrium state with high probability. Two different approaches can be found: *Randomised* allocation and *Physical optimisation*.

Randomised allocation methods are very simple methods that do not use information about potential destination processors. A neighbour processor is selected at random and the process is transferred to that processor. No exchange of state information among the processors is required in deciding where to transfer a load unit. On the other hand, Stochastic algorithms, where physical optimisation is applied, are based on analogies with physical systems. They map the load-balancing problem onto some physical systems, and then solve the problem using simulation or techniques from theoretical or experimental physics. Physical optimisation algorithms offer a slightly more variety in the control of the randomness in the redistribution of load units. This control mechanism makes the process of load balancing less susceptible to being trapped in local optima and therefore these stochastic algorithms

are superior to other randomised approaches which could produce locally but not globally optimal results.

**Deterministic** methods proceed according to certain predefined strategies. These solutions are usually performed in an iterative form when the execution of the load-balancing algorithm is repeated more than once in a given processor, before restarting the execution of the user application [Xu94]. Deterministic methods can be classified into two categories according to the load distribution within the domain: *Diffusion* and *Single-direction*.

Firstly, in diffusion methods the load excess of an overloaded processor is simultaneously distributed amongst all processors of the underlying domain, following an iteration of the load-balancing algorithm. In contrast, in single-direction methods only one processor of the underlying domain can be chosen as destination processor after executing one iteration of the load-balancing algorithm. Single Direction methods are further classified according to how the destination processor is selected. When the direction of the closer lightly loaded processor is used as a selection criterion we refer to *Gradient Model*, and when the chosen processor is the least loaded processor of the underlying domain we talk about *Minimum-Direction* schemes. Techniques where all processors are considered one by one at each load-balancing iteration are called *Dimension Exchange* strategies.

We will now describe some of the most relevant strategies that appear in the literature.

#### 1.6 Dynamic load-balancing strategies

Following the taxonomy described in the previous paragraph, and bearing in mind the design characteristics outlined in section 1.4, we have constructed table 1.1, which draws together all published strategies, as far as we are aware. Particularly, in the case of processor level, the algorithmic aspects seen in section 1.5 are used. At each box of the table, the mnemonic for the strategy and its reference are given. Strategies indicated with a continuos line are not feasible or have not been proposed as far as the author knows. We now describe some of the strategies indicated in the table, starting with those classified in the randomised category.

|                                               |             |             |                       |                                   | Syste                                                                    | em Level View                                                                          |                                                     |                                                      |  |

|-----------------------------------------------|-------------|-------------|-----------------------|-----------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|--|

| Dynamic                                       |             | Centralised | Totally Distributed   |                                   | Semi-Distributed                                                         |                                                                                        |                                                     |                                                      |  |

|                                               |             |             |                       |                                   | Non-Nearest                                                              | Nearest-                                                                               | 7                                                   |                                                      |  |

| Load-Balancing                                |             |             | Neighbours            | Neighbours                        |                                                                          |                                                                                        |                                                     |                                                      |  |

|                                               | Stochastic  |             | Randomised            |                                   | Reservation [Eag85] RANDOM[Zho88] THRDL[Zho88] LOWEST[Zho88] MYPE[Yua90] |                                                                                        |                                                     |                                                      |  |

| Algorithmic Aspects from Processor Level View | Stock       | Physical    | Optimisation          | GTCA [Bau95]<br>CBLB[Bau95]       |                                                                          | SA.[Fox89]                                                                             | CSAM[Cha95]<br>MFAM [Cha95]                         |                                                      |  |

|                                               |             |             | Diffusion             | Multi-level-<br>Diffusion [Hor93] | NA [Sal90]<br>DDE [Wu96]<br>AN-n [Cor99c]                                | Diffusion [Cyb89][Boi90] SID,RID [Wil93] ATD [Wat98] AN [Cor99c] [Son94][Die99] [Hu99] | Membership-exc. [Eva94]<br>Joint-membership [Eva94] |                                                      |  |

|                                               | įį          |             | Dimension<br>Exchange |                                   | EDN [Cor99c]                                                             | DE [Cyb89] GDE [Xu97] DN [Cor99c] Graph-Colouring[Hos90]                               |                                                     |                                                      |  |

|                                               | Determinist | Determinist | Deterministic         | Single-direction                  | Gradient<br>Model                                                        |                                                                                        |                                                     | GM (Lin87)<br>B(Ber90)<br>X-GM (Lul91)<br>EG [Mun95] |  |

|                                               |             | iS          | Minimum-<br>direction | Central [Zho88]<br>LBC[Lin92]     | GLRM[Xu93]<br>GMLM [Xu93]                                                | CWN [Kai88]<br>ACWN [Shu89]<br>LLRM[Xu93]<br>LMLM [Xu93]                               | Sphere-like [Ahm91]<br>Hierch. Sched. [Dan97]       |                                                      |  |

Table 1.1 Load-Balancing techniques classified with respect to system level view and processor level view.

#### 1.6.1 Randomised

As we have seen, in randomised load-balancing algorithms, the destination processors for load transfer are chosen in a random fashion. Therefore, these kinds of algorithms use less system state information than deterministic algorithms. These algorithms use only local load information to make movement decisions. In such cases a threshold value is preset as a criterion in determining whether a processor must send out part of its load or not. Several randomised algorithms based on a threshold value  $(T_i)$  as a trigger condition (RANDOM, THRHLD,LOWEST) are

reported in [Zho88]. In the RANDOM algorithm when a processor detects that its local load is bigger that  $T_h$  a processor is randomly selected as a destination of load movements. Since all processor's are able to make load movement decisions, this algorithm is classified as a totally distributed and non-nearest-neighbours approach. THRHLD and LOWEST algorithms are similar to the RANDOM algorithm in the sense that they also select the destination processor in a random way. However, a number of randomly selected processors, up to a limit  $L_p$ , are inspected instead of selecting only one candidate. In the THRHLD algorithm, extra load is transferred to the first processor whose load is below the threshold value. In contrast, in the LOWEST algorithm a fixed number of processors  $(L_p)$  are polled and the most lightly loaded processor is selected as destination processor. A similar scheme is used in the MYPE algorithm [Yua90]. Instead of using only one threshold value, the MYPE algorithm uses two threshold values to determine the state of the underlying processor,  $N_u$  and  $N_i$ . A processor is overloaded when its load is higher than  $N_u$ . Underloaded processors are the ones whose load is lower than  $N_1$ . Otherwise, they refer to neuter processors. An overloaded processor randomly selects a number of processors (up to the a preset limit) whose load indexes are lower than  $N_{l_1}$  as potential receivers. Then a polling scheme is used to determine the final destination of the load. The load excess will be sent to the first processor whose current load is lower than  $N_i$ .

#### 1.6.2 Physical Optimisation

The most common physical optimization algorithm for the load-balancing problem is simulated annealing. Simulated annealing is a general and powerful technique for combinatorial optimization problems borrowed from crystal annealing, in statistical physics. Since simulated annealing is very expensive and one of the requirements for dynamic load balancing is yielding the result in limited time, two hybrid methods, combining statistical and deterministic approaches, are proposed in [Cha95]: the Clustering Simulated Annealing Model (CSAM) and the Mean Field Annealing Model (MFAM). They were proposed to allocate or reallocate tasks at run time, so that every processor in the system had a nearly equal execution load and load interprocessor communication was minimised. In these methods, the load balancing was activated on a specific processor called the local balancer. The local

balancer repeatedly activates the task allocation algorithm among a subset of processors. Each local balancer makes task allocation decisions for a group of four to nine processors. Groups are overlapped with each other, allowing tasks to be transferred through the whole system.

The CSAM combines a heuristic clustering algorithm (HCA) and the simulated annealing technique. The HCA generates clusters, where each cluster contains tasks which involve high intertask communication. Various task assignments (called system configurations) are generated from the HCA to provide clusters in various sizes that are suitable for the annealing process. During the annealing process, system configurations are updated by reassigning a cluster of tasks from one processor to another. The procedure of simulated annealing is used to either accept or reject a new configuration. The MFAM (Mean Field Annealing Model) was derived from modelling the distributed system as a large physical system in which load imbalance and communication costs causes the system to be in a state of non-equilibrium. Imbalance is balanced through a dynamic equation whose solution reduces the system imbalance. The dynamics of the MFAM are derived from Gibbs distribution. Initially all tasks have the same probability of being allocated in each processor. Several iterations of an annealing algorithm are carried out so that the system is brought to a situation where each process is assigned to only one processor. A major advantage of the MFAM is that computation of the annealing algorithm can be implemented in parallel. A similar load-balancing algorithm that uses simulated annealing technique is reported in [Fox89]

In addition to the simulating annealing technique, genetic algorithms constitute another optimisation method that has borrowed ideas from natural science and has also been adapted to dynamic load-balancing. Examples of genetic load-balancing algorithms can be found in [Bau95]. The first algorithm presented in the paper is Genetic Central Task Assigner (GCTA). It uses a genetic algorithm to perform entire load-balancing action. The second, Classifier-Based Load Balancer (CBLB), augments an existing load-balancing algorithm using a simple classifier system to tune the parameters of the algorithm.

#### 1.6.3 Diffusion

One simple method for dynamic load-balancing is for each overloaded processor to transfer a portion of its load to its underloaded neighbours with the aim of achieving a local load balance. Such methods correspond closely to simple iterative methods for the solution of diffusion problems; indeed, the surplus load can be interpreted as diffusing through the processors towards a steady balanced state. Diffusion algorithms assume that a processor is able to send and receive messages to/from all its neighbours simultaneously.

Corradi *et alter* propose a more precise definition of diffusive load-balancing strategies in [Cor99c]. In particular, they define an LB strategy as diffusive when:

- It is based on replicated load-balancing operations, each with the same behaviour and capable of autonomous activity;

- The LB goal is locally pursued: the scope of the action for each running processor is bound to a local area of the system (domain). Each running processor tries to balance the load of its domain as if it were the whole system, based only on the load information in its domain; and

- Each running processor's domain overlaps with the domain controlled by at least one other running processor and the unification of these domains achieves full coverage of the whole system.

Cybenko describes in [Cyb89] a simple diffusion algorithm where a processor *i* compares its load with all its immediate neighbours in order to determine which neighbouring processors have a load value smaller than the underlying processor's load. Such processors will be considered underloaded neighbour processors. Once underloaded neighbours are determined, the underlying processor will evaluate the load difference between itself and each one of its neighbours. Then, a fixed portion of the corresponding load difference is sent to each one of the underloaded neighbours. This strategy, as well as other strategies from the literature based on this, [Ber89][Die99][Hu99] were originally conceived under the assumption that load can be divided into arbitrary fractions, i.e., the load was treated as a non-negative real quantity. However, to cover medium and large grain parallelisms which are more realistic and more common in practical parallel computing environments, we must

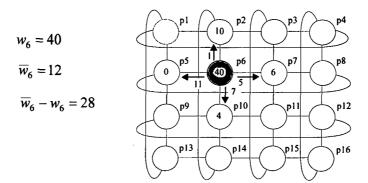

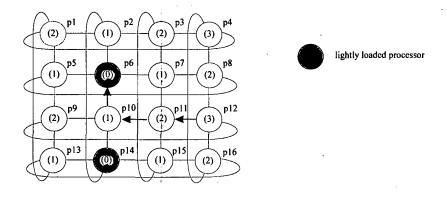

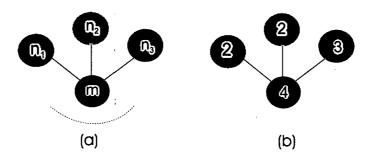

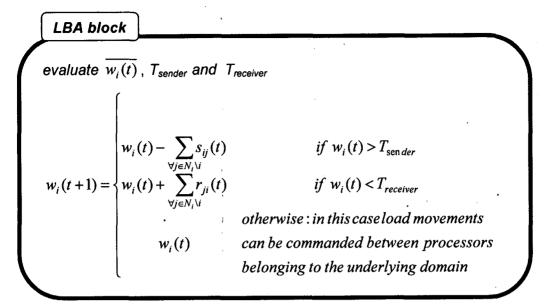

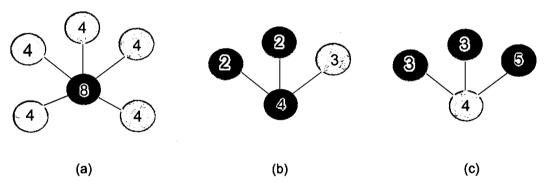

treat the loads of the processors as non-negative integers, as was carried out in [Cor99c][Son94][Wat98][Wil93]. A relevant strategy in this area is the SID (Sender Initiated Diffusion) algorithm [Wil93]. In this algorithm, each processor i has a load value equal to  $w_i$  and it evaluates its local load average  $(\overline{w}_i)$  to be used as a trigger condition. If the load of processor i is bigger than the load average of its domain, then it is an overloaded processor. Otherwise, the processor was referred to as underloaded. An overloaded processor distributes its excess load among its underloaded neighbours. A neighbour processor j of the underlying processor i, is a neighbour with deficit if its load is smaller than the load average of the underlying domain  $(\overline{w}_i > w_i)$ . Then, the surplus of a given processor i is distributed among its deficient neighbours in a proportional way. This strategy is classified as a senderinitiated scheme because the overloaded processors are the active processors. The same authors described a similar strategy called RID (Receiver Initiated Diffusion) which is based on the same idea as the SID algorithm, but using a receiver-initiated scheme to determine the processors which take load-movements decisions. An example of the behaviour of this algorithm is shown in figure 1.7. The number inside the nodes represents the load of the corresponding processor. Processor 6 has a load value equal to 40 ( $w_6 = 40$ ) and the load average within its domain is 12 ( $\overline{w}_6 = 12$ ). Therefore, the load excess of processor 6 is equal to 28 units of load. After applying the SID algorithm, processor 6 decides to move 1, 11, 5 and 7 load unit to processors 2, 5, 7 and 10 respectively. These load movements are denoted by the numbers behind the arrows.

Figure 1.7 An example of the execution of one iteration of the SID strategy in processor 6.

The reader can find more examples of deterministic diffusion load-balancing strategies in [Cor99c][Eva94][Hor93][Sal90][Wat98] and [Wu96].

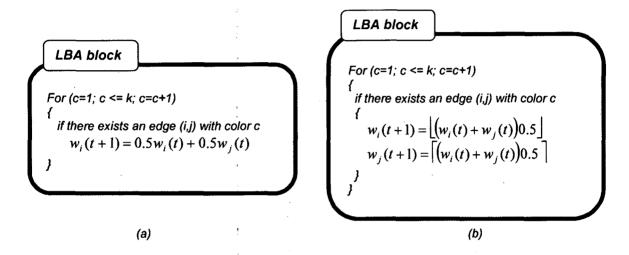

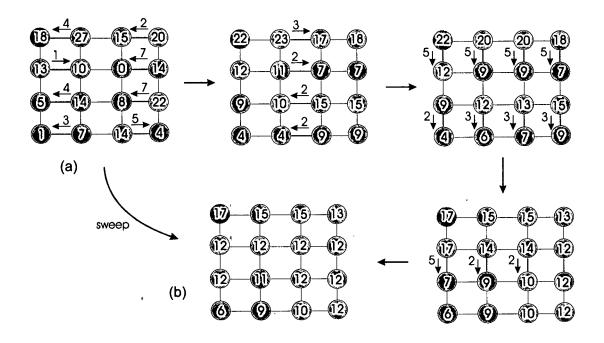

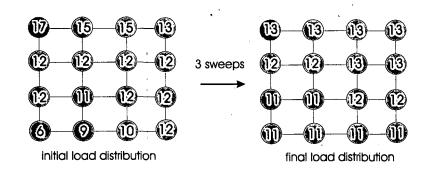

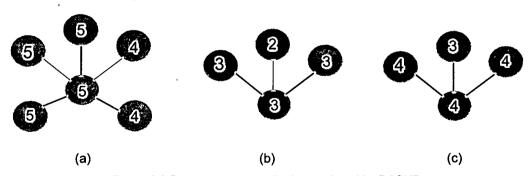

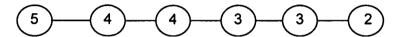

#### 1.6.4 Dimension Exchange

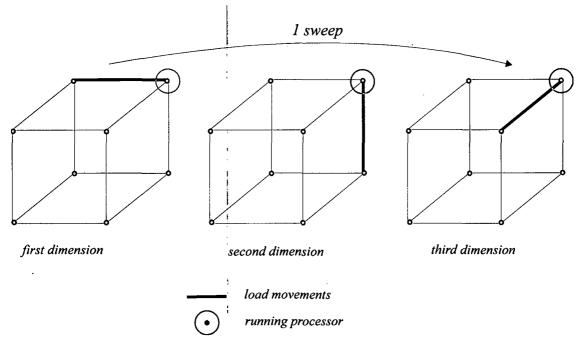

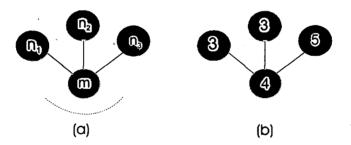

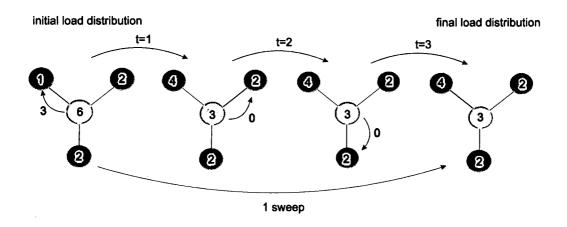

This load-balancing method was initially studied for hypercube topologies where processor neighbours are inspected by following each dimension of the hypercube. Thus, this is the origin of the dimension exchange (DE) name. Originally, in DE methods, the processors of a *k*-dimensional hypercube pair up with their neighbours in each dimension and exchange half the difference in their respective loads [Cyb89]. The load value of the underlying processor is updated at each neighbour inspection and the new value is considered for the next revision. Going through all the neighbours once consists of carrying out a "sweep" of the load-balancing algorithm. Such behaviour is shown in figure 1.8.

Figure 1.8 Load movements for DE methods in a 3-dimensional hypercube through three iterations of the load-balancing algorithm (1 sweep) in a running processor.

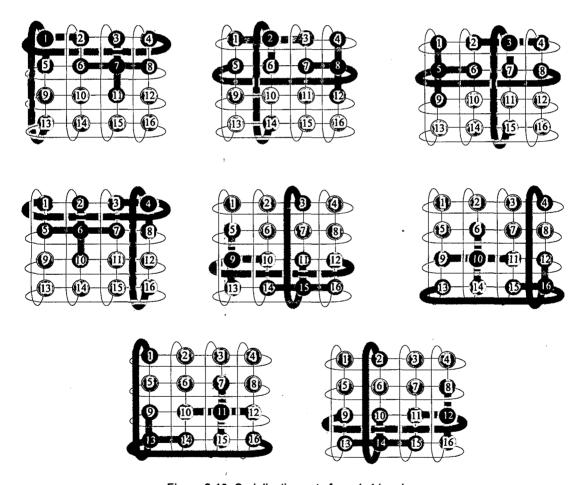

Xu et alter present in [Xu97] a generalisation of this technique for arbitrary topologies, which they call the GDE (Generalised Dimension Exchange) strategy. For arbitrary topologies the technique of edge colouring of undirected graphs (where each node of the graph identifies one processor of the system and the edges are the

links) is used to determine the number of dimensions and the dimension associated at each link. The links between neighbouring processors are minimally coloured so that no processor has two links of the same colour [Hos90]. Subsequently, a "dimension" is then defined as being the collection of all edges of the same colour. At each iteration, one particular colour/dimension is considered, and only processors on edges with this colour execute the dimension exchange procedure. The portion of load exchanged is a fixed value and is called the exchange parameter. This process is repeated until a balanced state is reached. The DE algorithm uses the same value of the exchange parameter for all topologies, while the GDE algorithm uses different values depending on the underlying topology.

The DN (Direct Neighbour) algorithm is a strategy based on the dimension exchange philosophy, which uses a discrete load model [Cor99c]. This strategy allows load exchange between two processors only directly connected by a physical link. A balancing action within a domain strives to balance the load of the two processors involved. In order to assure the convergence of this method, the running processors must synchronise amongst themselves in such a way that the running processors active in any given moment have non-overlapping domains. The same authors describe an extension to this algorithm, the EDN (Extended Direct Neighbour) algorithm, which works as a non-nearest neighbour strategy. This strategy allows a dynamic domain definition by moving load between direct neighbours, overcoming the neighbourhood limit through underloaded processors. Load reallocation stops when there are no more useful movements, i.e., a processor is reached whose load is minimal in its neighbourhood.

### 1.6.5 Gradient Model

With gradient-based methods, load is restricted to being transferred along the direction of the most lightly loaded processors. That is, an overloaded processor will send its excess load only to one neighbor processor at the end of one iteration of the load-balancing algorithm. Therefore, the main difference between the gradient model and the dimension exchanged scheme is that at each iteration the load information of the entire underlying domain is considered in deciding the destination processor, whilst in DE methods only one processor is considered at each iteration.

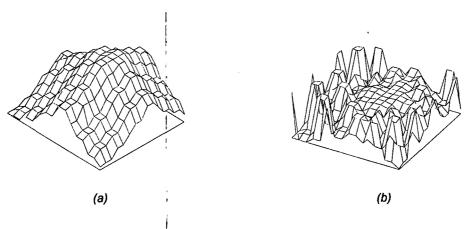

In the Gradient Model algorithm described in [Lin87] two-tiered load-balancing steps are employed. The first step is to let each individual processor determine its own loading condition: light, moderate or heavy. The second step consists of establishing a system-wide gradient surface to facilitate load migration. The gradient surface is represented by the aggregate of all proximities, where a proximity of a processor i is the minimum distance between the processor and a lightly loaded processor in the system. The 'gradient surface is approximated by a distributed measurement called the pressure surface, then the excessive load from heavily loaded processors is routed to the neighbour of the least pressure (proximity). The resulting effect is a form of relaxation where load migrating through the system is guided by the proximity gradient and gravitates towards underloaded processors. Figure 1.9 shows an example of a gradient surface in a 4x4 torus network where there are two lightly loaded processors (processors 2 and 10). The value between brackets (x) represents the pressure surface of each processor. Let us suppose that processor 12 is an overloaded processor (yellow colour). By following the proximities depicted in the figure, the load excess of processor 12 will be guided to be moved through the red links in order to achieve one of the two lightly loaded processors within the system (in this case processor 6).

1.9 The GM scheme on a 4x4 torus...

This basic gradient model has serious drawbacks. First, when a large portion of moderately loaded processors suddenly turns lightly loaded, the result is considerable commotion. Lüling *et alter* proposed an improved version of the GM algorithm to remedy this problem, the Extended Gradient Model (X-GM) [Lül91]. This

method adds a suction surface which is based on the (estimated) proximities of non-heavily-loaded processors to heavily-loaded processors. This information would cause load migration from heavily-loaded processors to nearby local minima which may be moderately-loaded processors. Since the system load changes dynamically, the proximity information kept by a processor may be considerably out-of-date. And finally, if there are only a few lightly-loaded processors in the system, more than one overloaded processor may emit some load toward the same underloaded processor. This "overflow" effect has the potential to transform underloaded processors into overloaded ones. The authors of [Mun95] propose another extension to the GM scheme, EG (Extended Gradient) mechanism, to overcome the problems mentioned. The EG mechanism is a two-phase strategy, where an overloaded processor confirms that a processor is still underloaded before transferring load to it, and then the underloaded processor is reserved in transferring the load.

### 1.6.6 Minimum-direction

The minimum-direction scheme is an alternative to dimension exchange methods and gradient model within the single-direction category of deterministic load-balancing algorithms. In the strategies based on this scheme, the running processor chooses the least loaded processor within its domain as the only destination of a load movement after executing the load-balancing algorithm once. Notice that, depending on the scope of the domain, the least loaded processor within the underlying domain may coincide with the least loaded processor in the whole system. Such a match is typically produced in centralised load-balancing systems where the running processors have access to the load of the entire system.

The LBC (Load-Balancing with a Central job dispatcher) strategy reported in [Lin92] makes load-balancing decisions based on global state information which is maintained by a central job dispatcher. Each processor sends a message to the central site whenever its state changes. Upon receiving a state-change message, the central dispatcher updates the load value kept in its memory accordingly. When a processor becomes underloaded, the state-change message is also used as a load request message. In response to this load request, the dispatcher consults the table where load values are kept, and the most loaded processor is chosen as load source.

Then this processor is notified to transfer some load to the requesting processor. The LBC strategy is a centralised algorithm because the central site guides all load movements. This strategy is also classified as a receiver-initiated method in the sense that the underloaded processors are the ones which start the load-balancing operations.

The CENTRAL algorithm described in [Zho88] is a centralised sender-initiated algorithm that works in a complementary form to the LBC strategy. When a processor detects that it is an overloaded processor, it notifies the *load information center* (LIC) about this fact by sending a message with its current load value. The LIC selects a processor with the lowest load value and informs the originating processor to send the extra load to the selected processor.

GLRM (Global Least Recently Migrated) and GMLM (Global Minimum Load Maintained) are two totally distributed non-nearest-neighbour strategies where the domain of each processor includes all processors in the system [Xu93]. Both GLRM and GMLM strategies use the global load average in the system as a threshold to determine whether a processor is overloaded or not. This threshold is computed at each processor using the load values received from the information collector (IC) processor. The IC processor has the responsibility of collecting the load of the entire system and broadcasting it to all processors. These actions will be performed on a time window basis. Once a processor is considered to be overloaded, a destination processor must be chosen. GLRM selects the destination processor by applying the last recently migrated discipline in a window time and the GMLM strategy determines the destination processor as the processor with minimum load value in the current time window. If the domain of each processor is restricted to the immediate neighbours, two nearest-neighbour strategies are easily derived from the two previous ones: LLRM (Local Least Recently Migrated) and LMLM (Local Minimum Load Maintained).

Another algorithm based on the minimum-direction scheme is the CWN (Contracting Within Neighbourhood) strategy [Kal88]. CWN is a totally distributed strategy where each processor only uses load information about its immediate

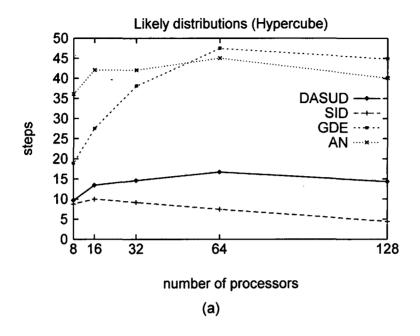

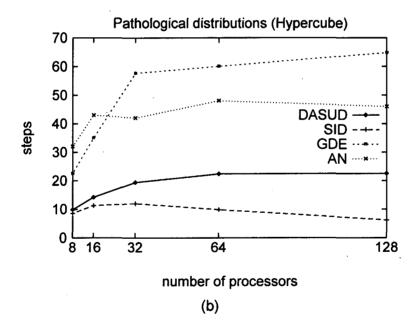

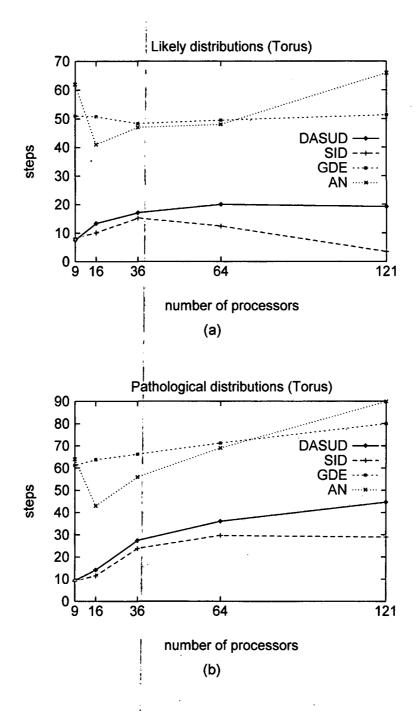

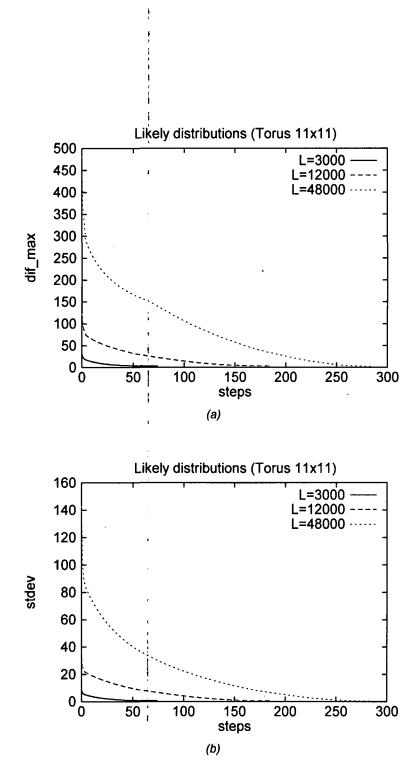

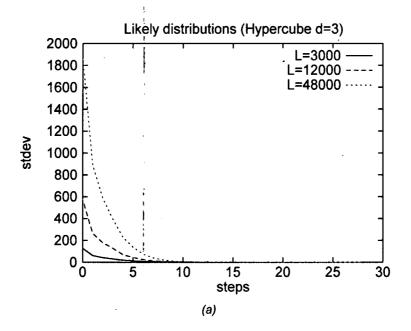

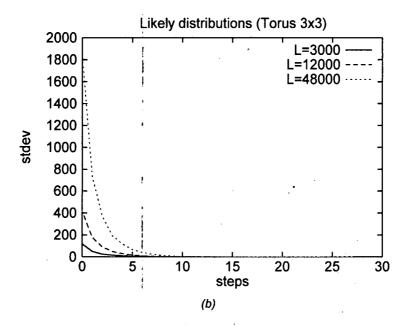

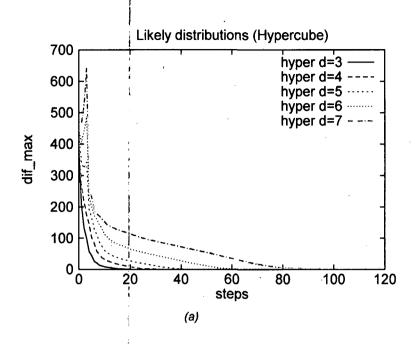

neighbours. A processor would migrate its excess load to the neighbour with the least load. A processor that receives some load keeps it for execution if it is most lightly loaded when compared with all its neighbours; otherwise, it forwards the load to its least loaded neighbour. This scheme has two parameters: the *radius*, i.e. the maximum distance a load unit is allowed to travel, and the *horizon*, i.e. the minimum distance a load unit is required to travel. If we allow these parameters to be tuneable at run-time, the algorithms become ACWN (Adaptive Contracting Within a Neighbourhood) [Shu89].