Algorithm and Hardware Co-design

for Learning On-a-chip

by

Zihan Xu

A Dissertation Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

Approved August 2017 by the Graduate Supervisory Committee:

Yu Cao, Chair Chaitali Chakrabarti Jae-sun Seo Shimeng Yu

ARIZONA STATE UNIVERSITY

December 2017

#### ABSTRACT

Machine learning technology has made a lot of incredible achievements in recent years. It has rivalled or exceeded human performance in many intellectual tasks including image recognition, face detection and the Go game. Many machine learning algorithms require huge amount of computation such as in multiplication of large matrices. As silicon technology has scaled to sub-14nm regime, simply scaling down the device cannot provide enough speed-up any more. New device technologies and system architectures are needed to improve the computing capacity. Designing specific hardware for machine learning is highly in demand. Efforts need to be made on a joint design and optimization of both hardware and algorithm.

For machine learning acceleration, traditional SRAM and DRAM based system suffer from low capacity, high latency, and high standby power. Instead, emerging memories, such as Phase Change Random Access Memory (PRAM), Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM), and Resistive Random Access Memory (RRAM), are promising candidates providing low standby power, high data density, fast access and excellent scalability. This dissertation proposes a hierarchical memory modeling framework and models PRAM and STT-MRAM in four different levels of abstraction. With the proposed models, various simulations are conducted to investigate the performance, optimization, variability, reliability, and scalability.

Emerging memory devices such as RRAM can work as a 2-D crosspoint array to speed up the multiplication and accumulation in machine learning algorithms. This dissertation proposes a new parallel programming scheme to achieve in-memory learning with RRAM crosspoint array. The programming circuitry is designed and simulated in TSMC 65nm technology showing 900X speedup for the dictionary learning task compared to the CPU performance.

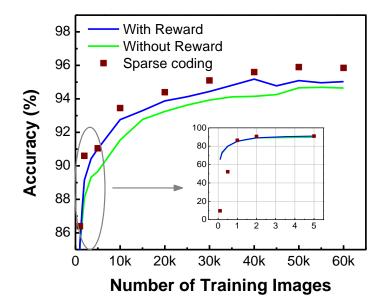

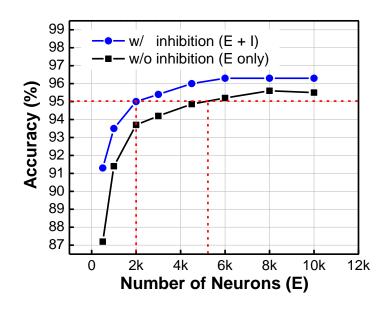

From the algorithm perspective, inspired by the high accuracy and low power of the brain, this dissertation proposes a bio-plausible feedforward inhibition spiking neural network with Spike-Rate-Dependent-Plasticity (SRDP) learning rule. It achieves more than 95% accuracy on the MNIST dataset, which is comparable to the sparse coding algorithm, but requires far fewer number of computations. The role of inhibition in this network is systematically studied and shown to improve the hardware efficiency in learning.

#### ACKNOWLEDGMENTS

Foremost, I would like to sincerely thank my advisor Dr. Yu Cao for the support of my Ph.D research. He has guided me the professional way to do research patiently. He has helped me solve difficult prolems in my research. His motivation and enthusiasm always inspire me to work harder and pursue the truth. His knowledge and vision has directed me towards a great career. I could not have imagined having a better advisor for my Ph.D study.

Besides my advisor, I would like to thank the reset of my dissertation committee: Dr. Chaitali Chakrabarti, Dr. Jae-sun Seo, and Dr. Shimeng Yu. They have helped me a lot through my projects with their professional knowledge and attitude. They have given me a broad view and experience of different research fields.

I also want to thank my fellows in Arizona State University for the help, discussion, and support: Dr. Chengen Yang, Dr. Ketul Sutaria, Dr. Naveen Suda, Dr. Jyothi Velamala, Dr. Saurabh Sinha, Pei An, Venkatesa Sarma Ravi, Abinash Mohanty, Devyani Patra, Srivatsava Gorthy, Xiaocong Du, Zheng Li, Shihui Yin, Deepak Kadetotad, Xiaoyang Mi, Pai-Yu Chen, Dr. Ligang Gao, Runchen Fang, Zhiwei Li, Rui Liu, Manqing Mao, Dr. Wenhao Chen, Dr. Binbin Lin, Ming Tu.

I would like to thank all the faculty and staff in Arizona State University for the great Electrical Engineering program.

Last but not the least, I want to thank my parents for their unreserved support throughout my life.

## TABLE OF CONTENTS

|      | 1 age                                                    |

|------|----------------------------------------------------------|

| LIST | OF TABLESvi                                              |

| LIST | OF FIGURES vii                                           |

| CHAI | PTER                                                     |

| 1    | INTRODUCTION 1                                           |

|      | 1.1 Background1                                          |

|      | 1.2 Contributions                                        |

| 2    | RELATED WORK                                             |

|      | 2.1 Machine Learning Algorithm Optimization8             |

|      | 2.2 Machine Learning Hardware Design10                   |

| 3    | EMERGING MEMORY MODELING 14                              |

|      | 3.1 Introduction                                         |

|      | 3.2 Phase Change Random Access Memory17                  |

|      | 3.3 Spin-Transfer Torque Magnetic Random Access Memory35 |

|      | 3.4 Review of Resistive Random Access Memory             |

| 4    | MACHINE LEARNING HARDWARE DESIGN                         |

|      | 4.1 Introduction                                         |

|      | 4.2 Parallel Programming Scheme and Circuit Design54     |

|      | 4.3 Simulation and Results                               |

| 5    | BIO-INSPIRED LEARNING ALGORITHM 63                       |

|      | 5.1 Introduction                                         |

| CHAPTER                                           | Page |

|---------------------------------------------------|------|

| 5.2 Feedforward Inhibition Spiking Neural Network | 68   |

| 5.3 Results and Discussion                        | 76   |

| 6 FUTURE WORK                                     |      |

| 7 CONCLUSION                                      |      |

| REFERENCES                                        |      |

# LIST OF TABLES

| Table |                                            | Page |

|-------|--------------------------------------------|------|

| 1.    | Parameters in the PRAM Circuit Level Model | 19   |

| 2.    | Material Properties in PRAM Model          | 22   |

| 3.    | PRAM Cell Simulation Parameters            | 29   |

| 4.    | Nominal Performance of 32nm SLC PRAM       | 32   |

| 5.    | Parameters in STT-MRAM Model               | 36   |

| 6.    | Models of Critical Points in STT-MRAM      | 39   |

| 7.    | Formulas for the RC Elements in SPICE      | 42   |

| 8.    | STT-MRAM Cell Simulation Parameters        | 45   |

| 9.    | Comparison of the Neural Network Models    | 93   |

| LIST OF FIGU |

|--------------|

|--------------|

| Figure | Page                                                                             |

|--------|----------------------------------------------------------------------------------|

| 3.1.   | PRAM Fundamental 15                                                              |

| 3.2.   | Magnetic Tunnel Junction Structure16                                             |

| 3.3.   | Hierarchical Memory Modeling Framework17                                         |

| 3.4.   | The FSM Models of PRAM                                                           |

| 3.5.   | The Equivalent Circuit Model of PRAM 19                                          |

| 3.6.   | 2D Structure of PRAM Cells in Raphael                                            |

| 3.7.   | Geometry Dependence of Fully Crystalline GST Resistance                          |

| 3.8.   | Geometry Dependent Electrical Resistance Model                                   |

| 3.9    | Compact Models of Thermal Parameters                                             |

| 3.10.  | The Iteration in Model Simulation                                                |

| 3.11.  | PRAM Model Validation                                                            |

| 3.12.  | Stuck-SET Model                                                                  |

| 3.13.  | PRAM Cell Structure                                                              |

| 3.14.  | State Transition Curve                                                           |

| 3.15.  | State Transition Curve in Nominal Condition with Different Pulse Width 31        |

| 3.16.  | Contribution of Different Variation Sources to Variability of R <sub>RESET</sub> |

| 3.17.  | RESET State Transition Curve with CW Variations                                  |

| 3.18.  | PRAM Write Power                                                                 |

| 3.19.  | Required RESET Current and Pulse Width with Given Resistance Margin 34           |

| 3.20.  | State Transition Curve with Stuck-SET Degradation                                |

| 3.21.  | An In-plane STT-MTJ is Programmed by a Current Pulse                             |

| Figure | Page                                                                            |

|--------|---------------------------------------------------------------------------------|

| 3.22.  | $d\theta/dt$ for Different <i>I</i> When $\theta$ Changes from 0° to 180°       |

| 3.23.  | STT-MTJ Model Validation                                                        |

| 3.24.  | The Regional RC Network for Dynamic SPICE Simulation                            |

| 3.25.  | The Switching Behavior under Different Pulse Widths                             |

| 3.26.  | The Matching in the Prediction of MTJ Resistance                                |

| 3.27.  | The Scaling of Critical Current                                                 |

| 3.28.  | STT-MRAM Cell Structure                                                         |

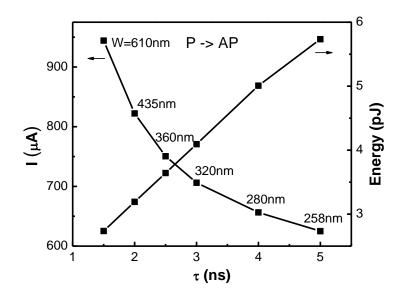

| 3.29.  | Programming Current and Energy of $P \rightarrow AP$ Switching                  |

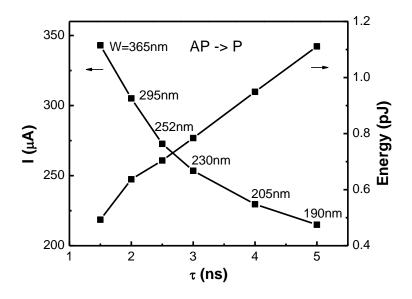

| 3.30   | Programming Current and Energy of $AP \rightarrow P$ Switching                  |

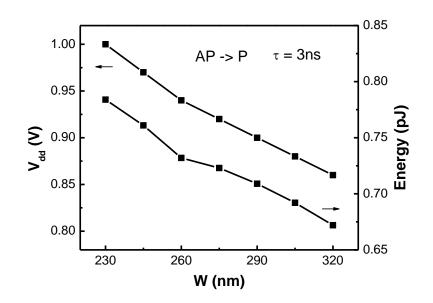

| 3.31.  | Supply Voltage and Energy vs. Transistor Sizes for $AP \rightarrow P$ Switching |

| 4.1.   | The Similarity of Programming a Biophysical Synapse and a RRAM Cell 52          |

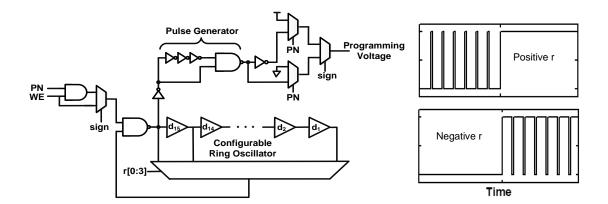

| 4.2.   | The Parallel Programming Scheme 55                                              |

| 4.3.   | Circuit Schematic to Generate the Programming Voltage Z 57                      |

| 4.4.   | Circuit Schematic to Generate the Programming Pulses of <i>r</i>                |

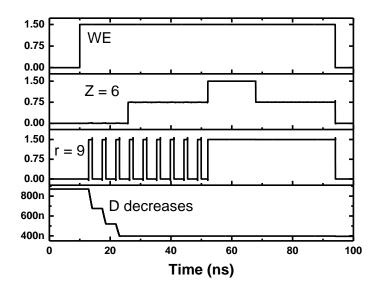

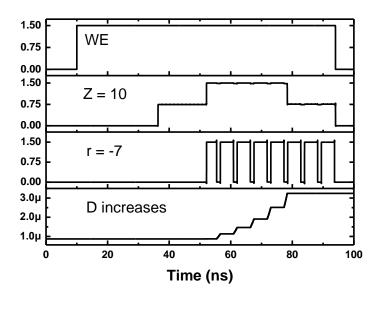

| 4.5.   | Timing Diagram of the Programming System                                        |

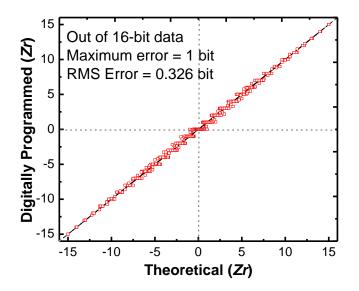

| 4.6.   | The Quantization Error of the Parallel Programming Method                       |

| 4.7.   | Demonstration of the Proposed Method in Updating the Dictionary 62              |

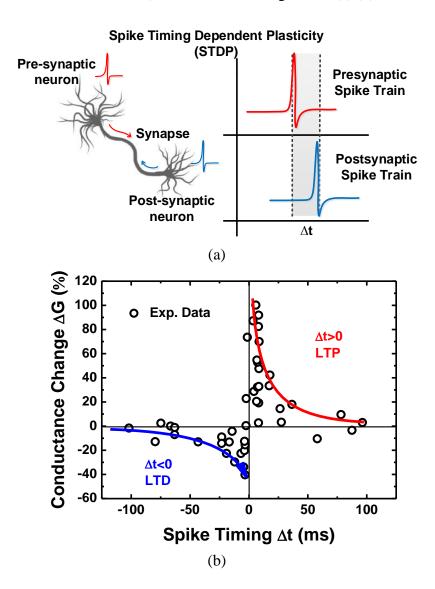

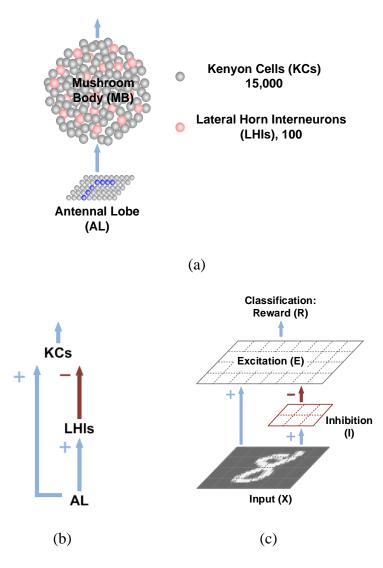

| 5.1.   | Feedforward Inhibition Motif                                                    |

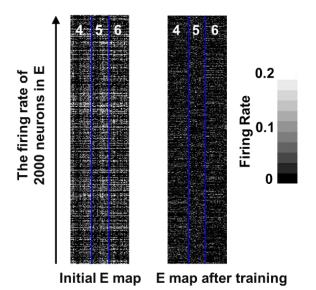

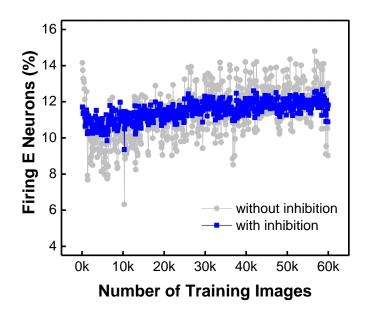

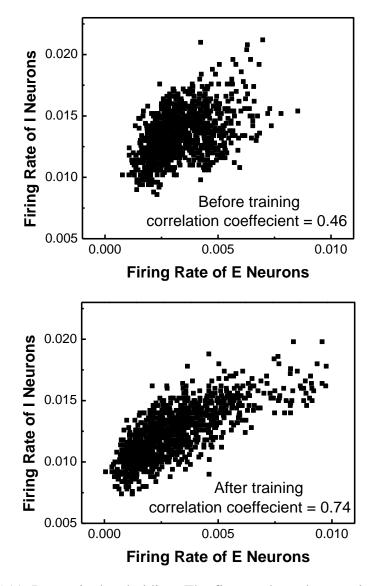

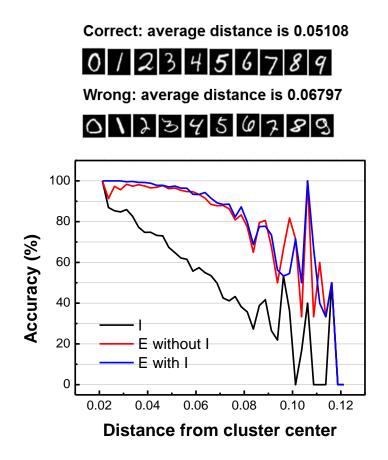

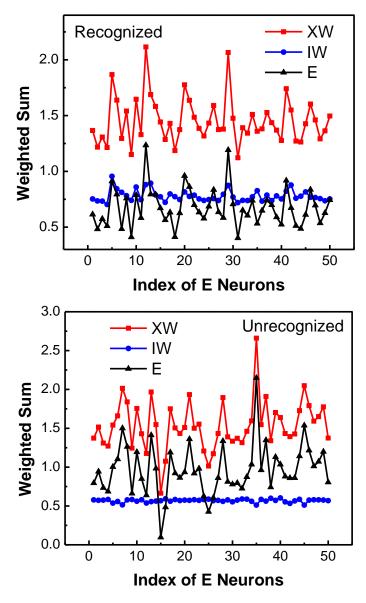

| 5.2.   | The Firing Map of Excitatory Neurons77                                          |

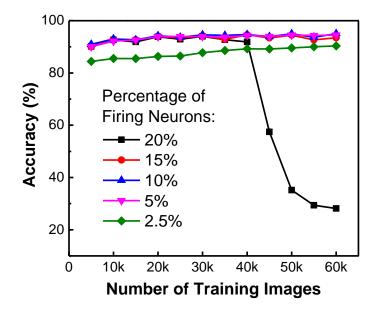

| 5.3.   | Testing Accuracy as a Function of the Number of Training Images                 |

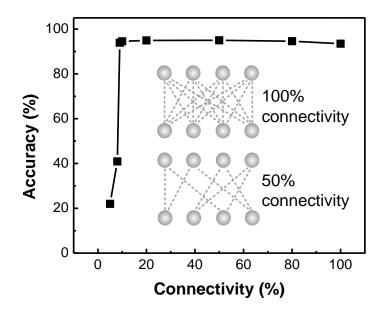

| 5.4.   | The Effect of Connectivity                                                      |

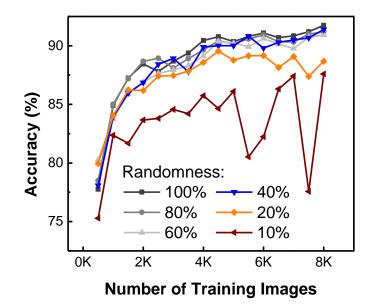

| 5.5.   | The Effect of Weight Randomization                                              |

| Figure | ]                                                                | Page |

|--------|------------------------------------------------------------------|------|

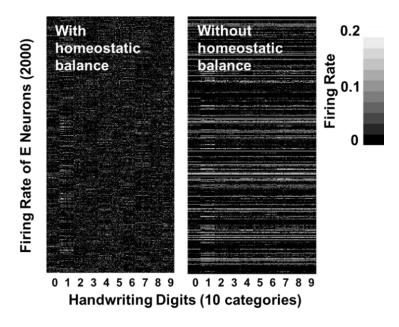

| 5.6.   | The Effect of Homeostatic Balance                                | 82   |

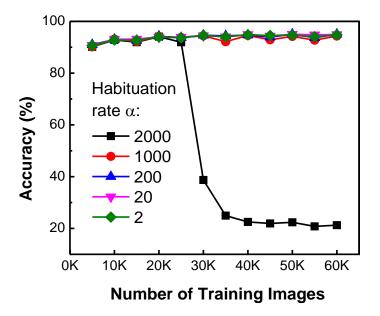

| 5.7.   | The Effect of Habituation Rate                                   | 83   |

| 5.8.   | The Effect of Sparsity                                           | 84   |

| 5.9.   | The Prediction Accuracy as a Function of the Number of E Neurons | 86   |

| 5.10.  | Thresholding                                                     | 88   |

| 5.11.  | Dynamic Thresholding                                             | 89   |

| 5.12.  | The Classification Results of the Inhibition Layer               | 91   |

| 5.13.  | The Total Weighed Sum of Input                                   | 92   |

### 1. Introduction

#### 1.1. Background

Machine learning technology, especially deep learning, has a lot of incredible achievements in recent years. Machine learning based products have been integrated into our daily life, such as spam filter for email, recommendation system on ecommerce websites, and automatic face detection when taking photos with the smart phones. It has also rivalled or exceeded human performance in many intellectual tasks including image recognition, face detection and the Go game. In the image recognition task of 1,000 categories (ImageNet Large Scale Visual Recognition Challenge), the state-of-the-art algorithm achieves 2.25% top-5 error rate (ILSVRC 2017), which is better than the human performance of 5.1% top-5 error rate (Karpathy 2014).

Machine learning is the science of getting computers to learn, without being explicitly programmed. The computers do not copy human's knowledge directly, but learn from data with human defined rules. Machine learning is a very broad concept, and this dissertation only focuses on neural networks. A deep neural network model usually needs to learn millions of parameters provided millions of data (LeCun et al. 2015, 521:436-444). Thus, machine learning algorithms require huge amount of computations and data movement.

The current success of machine learning can be attributed to three aspects. First, the computational capability of modern computers have been increasing rapidly. Especially the development of Graphics Processing Unit (GPU) makes large scale parallel computation possible and efficient (Raina et al. 2009, 873-880). And deep learning models, especially neural networks, are featured by highly parallel computation of matrix

multiplication and convolution. With GPUs, people can train a deep neural network much faster than before. This not only speeds up the developing and tuning cycle of the algorithms, but also makes high complexity models possible. Second, as Internet spreads all over the world, there are huge amount of data generated by everyone every day, such as articles, pictures and search history. These "big data" on the Internet can be easily accessed and collected. And large amount of data is crucial to the training of any machine learning algorithm. Third, new algorithms and techniques were proposed to improve learning when simply increasing the model complexity cannot improve the performance due to overfitting, e.g. regularization, dropout (Srivastava et al. 2014, 873-880), and residual learning (He et al. 2015). Due to the reasons above, the tremendous growth of machine learning depends on the development of both hardware and algorithm.

The demand for faster computing is increasing every day. The semiconductor hardware industry has been following Moore's law due to a variety of benefits of scaling (Moore 1965, Moore 1975). The number of transistors on a chip doubles every two years. The performance of a chip doubles every 18 months due to more and faster transistors. And the cost of chips becomes more affordable to more people. Although Moore's law came from Gordon Moore's observation rather than any scientific or engineering theory, it has been very successful for over 50 years. However, as the silicon technology has scaled to sub-14nm regime, simply scaling down the device cannot provide enough speed-up any more. New device technologies and system architectures are needed to improve the computing capacity and continue Moore's law. Moreover, specific hardware for machine learning acceleration is highly in demand.

Based on different applications of machine learning, there will be different specifications and hardware choices. Machine learning algorithms usually have two phases, the training phase and the inference phase. During training, the model computes the forward path and backward path to update the parameters. During inference, the model parameters are fixed, and the model only computes the forward path to get the output for a given input. Basically, training is to obtain the model while inference is to use the model. Thus, training requires more computing and memory accesses. Designing hardware for training is more challenging than inference. Also, the hardware for inference can be very specific to the model to achieve better performance, while the hardware for training needs to be more general since the model to be trained often changes. From the perspective of where the machine learning models are used, they can be used in cloud servers or on edge devices. In the cloud, complex deep learning models are used to do training or inference on "big data". Speed is important to shorten the model development cycle or reduce the query latency. On the edge, more and more machine learning applications like voice recognition, machine translation and personalized health care will be implemented on the mobile devices. Therefore, application in the cloud may prefer hardware optimized for high speed, while application on the edge may prefer hardware optimized for low power.

There are different hardware choices based on different specifications. CPU is good for light load due to its high frequency, low power and high flexibility. GPU is now widely used to train deep learning models, which is much faster than CPU due to its Single Instruction Multiple Data (SIMD) operation and high bandwidth memory. However, GPU is not yet specialized for machine learning and it consumes a lot of power. Recently, more attention is paid to design of Application Specific Integrated Circuit (ASIC) for machine learning (Misra 2016, 74:239-255). It has the promise to outperform GPU in terms of speed and power. But ASIC design usually needs a long design and verification cycle, and the software ecosystem needs to follow up quickly. Another great option is the Field Programmable Gate Array (FPGA) (Misra and Saha 2016, 74:239-255). The computing capacity and memory capacity of FPGAs are improving quickly. And the development cycle of FPGA is much shorter than ASIC. These features make FPGA an excellent choice for certain fast changing applications.

The above acceleration options are mostly based on parallel computation with SIMD. Most efforts are made to include more parallel Processing Elements (PE) and increase the memory bandwidth, so that the computing capacity and the data movement capacity are improved together. However, in these approaches, data storage and computing are separated. Data need to be transferred from memory to the registers in PE to be processed. Since it's quite possible to increase the number of parallel PEs to speed up computing, the memory bandwidth will eventually become the bottleneck. Therefore, a more advanced idea is to do the computing capability.

Learning on-a-chip requires not only hardware design and implementation, but also optimization of the algorithms to be easier to implement on hardware. One approach is to reduce the number of bits of data including parameters and variables. In the current computer system, data are usually represented by 32 bits, such as single-precision floating-point number and integer type. Many researches have shown that machine learning algorithms do not actually need 32-bit numbers (Gupta et al. 2015, Baldassi et al. 2016,

93:052313, Merolla et al. 2016). Reducing the number of bits will benefit computation, data movement and memory storage for hardware implementation.

Similarly in human brain, the basic elements, the neurons and synapses, do not have high numerical precision, but the brain has excellent performance and extreme low power in the cognitive tasks. It manages a variety of tasks with such a small volume. Thus biology and neuroscience provide motivation to improve the current learning algorithms and their hardware implementation efficiency.

#### 1.2. Contributions

As silicon technology scales down, traditional CMOS-based memory such as SRAM and DRAM will suffer from high standby power consumption. They may no longer be the technology of choice for machine learning acceleration. Instead, emerging memories, such as Phase Change Random Access Memory (PRAM) (Burr et al. 2010, 28:223-262, Wong et al. 2010, 98 :2201-2227), Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM) (Wang et al. 2008, 44:2479-2482, Sharad et al. 2012, 11:843-853), and Resistive Random Access Memory (RRAM) (Wong et al. 2012, 100:1951-1970, Jo et al. 2010, 10:1297-1301, Yu et al. 2013, 25:1774-1779), are promising candidates for the next generation non-volatile memory. They provide low standby power, high data density, fast access and excellent scalability. They are also very promising to be integrated into the machine learning chip with CMOS technology. More importantly, they have the potential to do computation. Therefore, they are great candidates in the machine learning hardware. Modeling of these emerging memory devices is essential to the design. This dissertation proposes a hierarchical memory modeling framework and models PRAM and STT-MRAM in four different levels of abstraction (Xu et al. 2012, Xu et al. 2013, Xu et al. 2014, 102:7681). With the proposed models, various simulations are conducted to investigate the performance, optimization, variability, reliability, and scalability of these two memories.

Emerging non-volatile memory devices such as RRAM can work as a 2-D crosspoint array, which is a promising structure for matrix-based machine learning algorithms. It can do parallel computation of multiplication and accumulation based on current-voltage relationship. Thus, it reduces the need for data movement since the computation happens in the memory itself. This architecture is different from the mainstream Von-Neumann architecture, and is more suitable for data intensive applications like machine learning algorithms. How to integrate the non-volatile memory array with the computing system is a very challenging problem. It requires proper circuit and system design to achieve high speed and low power. This dissertation proposes a new parallel programming scheme to achieve in-memory learning with RRAM crosspoint array (Xu et al. 2014, 41:126-133). Based on the scheme, the programming circuitry is designed and simulated in TSMC 65nm technology. The proposed parallel programming scheme can speed up the dictionary learning task significantly compared to the CPU.

Another approach to optimize the algorithms is to learn from the biological nervous system. Inspired by the brain, which has high accuracy, low power and high hardware efficiency, many learning models were developed with spiking neurons (Cao et al. 2015, 113:54-66, Diehl et al. 2015). This dissertation proposes a bio-plausible feedforward inhibition spiking neural network with Spike-Rate-Dependent-Plasticity (SRDP) learning rule (Xu et al. 2016, Xu et al. 2017). It achieves more than 95% accuracy on the standard benchmark MNIST dataset, which is comparable to the sparse coding algorithm, but needs

much less number of computations. The inhibition in this network plays an important role in improving the hardware efficiency of learning.

The rest of the dissertation is organized as follows. Chapter 2 reviews related works on machine learning algorithm optimization with low numerical precision, and machine learning hardware design including ASIC and FPGA. Chapter 3 focuses on emerging memory devices. Modeling and design exploration are conducted for Phase Change Random Access Memory (PRAM) and Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM). Resistive Random Access Memory (RRAM) is also reviewed in this chapter to be used in next chapter. Chapter 4 designs the new parallel programming circuitry for learning on an RRAM crosspoint array. In Chapter 5, existing learning algorithms are firstly reviewed, and a new bio-plausible learning algorithm of feedforward inhibition spiking neural network is proposed and demonstrated with the standard benchmark MNIST dataset. Finally, Chapter 6 proposes the future works and Chapter 7 concludes this dissertation.

## 2. Related Work

This chapter reviews related works on machine learning algorithm optimization with low numerical precision, and machine learning hardware design including ASIC, FPGA and emerging non-volatile memory array.

## 2.1. Machine Learning Algorithm Optimization

To optimize machine learning algorithms for hardware implementation, many efforts were spent on reducing the numerical precision due to its benefits to computation, data movement and memory storage. Many works focused on the training of models. Hollis et al. (1990, 2:363-373) studied the effects of precision constraints on the backpropagation in neural network training. Fixed point arithmetic was used in the analog circuits to implement the backpropagation. Holt et al. (1993, 42:281-290) theoretically analyzed the finite precision error of the computations in training Multi-Layer Perceptron (MLP) for hardware implementation. Plagianakos and Vrahatis (1999) used the differential evolution strategy to train neural networks of 3-bit integer weights on simple datasets. For more complex deep learning algorithms, Baldassi et al. (2016, 93:052313) did the theoretically analysis for the possibility that learning may need only few bits of synaptic precision.

Gupta et al. (2015) proposed the stochastic rounding method to train deep learning models with 16-bit fixed-point number. It achieved 25.4% testing error on CIFAR-10 dataset (Krizhevsky and Hinton 2009), which is very close to the floating-point model baseline. Gysel et al. (2016) managed to condense CaffeNet model to 8-bit fixed-point representation using quantization and fine-tuning method. Lin et al. (2016) further proposed 3 fine-tuning methods and did a systematical study. They studied the effect of

low precision weights and activations separately. They also showed different layers in the model have different effect of low precision on the accuracy.

More aggressively, there are many works trying to train neural networks with binary weights and activations. Baldassi (2009, 136:902-916) studied generalization learning in a perceptron with binary synapses. Kim and Smaragdis (2016) proposed the weight compression and noisy backpropagation method to train neural networks with binary weights and activations. They achieved 1.33% error rate on the MNIST dataset (LeCun et al. 1998, 86:2278-2324). Courbariaux has a series of three papers (Courbariaux et al. 2014, Courbariaux et al. 2015, Courbariaux et al. 2016) on the binary neural networks and studied the more difficult CIFAR-10 dataset. They used the method of propagating gradients through discretization and batch normalization in training, and achieved 9.9% error rate on CIFAR-10 dataset with the VGG model baseline (Simonyan and Zisserman 2014). Rastegari et al. (2016) proposed a new method to project the binary weights based on mathematical derivation and applied this on AlexNet (Krizhevsky 2012) on the more complex ImageNet dataset. Compared to the 80.2% top-5 accuracy of full-precision AlexNet, they achieved 69.2% accuracy with binary weight and binary activation model, and achieved 79.4% accuracy with binary weight only model. Zhou et al. (2016) studied various number of bits of weights and activations in the AlexNet model, and achieved 43.6% accuracy. Merolla et al. (2016) not only studied the weight binarization but also other nonlinear distortions during training. They showed that deep neural networks are robust to them with experiments on CIFAR-10 and ImageNet dataset. Stromatias et al. (2015) also showed the robustness of spiking deep belief networks to noise and reduced bit precision. With all these efforts above, the binary neural networks training can achieve the same

accuracy as the full-precision counterpart on some datasets, but still cannot compete on the complex ImageNet dataset. Li et al. (2016) proposed the ternary weight networks and applied on the ResNet (He et al. 2016). They showed 84.2% accuracy on ImageNet dataset compared to the 86.76% accuracy of the full-precision model. Other experiments also showed that the accuracy of the ternary weight networks is almost the same as the full-precision counterparts.

Besides the low precision models, Iandola et al. (2016) tried to reduce the size of neural networks for easier implementation on the embedded hardware. They proposed a small CNN architecture called SqueezeNet. It achieved AlexNet-level accuracy on ImageNet dataset with 50x fewer parameters. For inference purpose only, Han et al. (2015) proposed the deep compression method including pruning, trained quantization and Huffman coding. They managed to reduce the memory storage of VGG-16 model by 49X with no loss of accuracy.

#### 2.2. Machine Learning Hardware Design

Many efforts were made to design machine learning acceleration hardware including ASIC and FPGA. Chen et al. proposed a series of ASIC designs called "DianNao family" (Chen et al. 2016, 59:105-112, Chen et al. 2014, 49:269-284, Luo et al. 2017, 66:73-88, Du et al. 2015, 43:92-104). They specially emphasized the impact of the memory on machine learning accelerator design, performance and energy. Among the DianNao family, DaDianNao was designed for neural networks and achieved peak performance of 5585 giga operations per second (GOPS) with peak power of 15.97 W in 28 nm technology. This is a 450X speedup over GPU with 150X less energy comsumption. It applied loop tiling and SIMD to minimize the memory access. ShiDianNao was designed for

convolutional neural networks (CNN) and achieved 194 GOPS with 0.32 W in 65 nm technology. Since the storage size of convolution kernels is not very large, this design stored the parameters in SRAM rather than DRAM, thus saving a lot of time and energy in memory access. A group from MIT proposed an energy-efficient reconfigurable ASIC design for CNN (Chen et al. 2016, 52:127-138). The design adopted special dataflow according to the behavior of convolution thus maximized the data reuse. The chip implemented in 65 nm technology achieved 34.7 images per second of the five convolutional layers inference in AlexNet with power of 278 mW. Google recently revealed more details about their Tensor Processing Unit (TPU) (Jouppi et al. 2017). It achieved 180 tera floating point operations per second (TFLOPS) with 4 chips on the board. The 2D systolic array is adopted in matrix multiplication to improve the throughput.

Apart from these designs accelerating the arithmetic computations in neural networks, IBM designed the chip called TrueNorth implementing the spiking neural networks (Merolla et al. 2014, 345:668-673). They converted the convolutional neural network to the spiking version and implemented on the TrueNorth chip. They achieved more than 1000 images per second for inference.

To further speed up the inference, Han et al. (2016) designed an ASIC of efficient inference engine (EIE) on compressed deep neural networks as a follow-up work of the deep compression work. It achieved 102 GOPS on compressed models and 3 TOPS on uncompressed models.

There are also many works using FPGA as the machine learning accelerator. Farabet et al. (2011) designed a runtime reconfigurable dataflow processor and developed the compiler to map CNN algorithms on the hardware design. They demonstrated the street scene understanding application and achieved 160 peak GOPS with only 10 W power. Gokhale et al. (2014) designed a mobile coprocessor for CNN and achieved 240 GOPS. Zhang et al. (2015) used a roofline model to explore the design space of the computation throughput and memory bandwidth, and achieved 61.62 GFLOPS under 100 MHz working frequency for CNN. Suda et al. (2016) proposed a throughput-optimized OpenCL based design on FPGA for CNN. They achieved 136.5 GOPS for the convolution operation. Qiu et al. (2016) implemented VGG-16 model on FPGA using RTL design. The data precision is quantized to 8 bits and even 4 bits with only 0.4% accuracy loss. They achieved 187.8 GOPS for convolution and 137 GOPS for the full model. Ma et al. (2016) proposed a scalable and modular RTL compiler of CNN. They optimized the CNN operations in RTL and developed a compiler to map the CNN models to the RTL module. So, it integrates the flexibility of high level synthesis (HLS) and the finer level optimization of RTL. They achieved 114.5 GOPS for the AlexNet model. Wei et al. (2017) implemented the systolic array architecture on FPGA and achieved impressive 461 GFLOPS for floating point data type and 1.2 TOPS for 8-16 bits fixed point data. Besides the above efforts to reduce the data precision, there are a few works to implement the binary neural networks on FPGA utilizing the flexibility of FPGA (Nurvitadhi et al. 2016, Fraser et al. 2017, Zhao et al. 2017). They have achieved peak throughput from 207.8 GOPS up to 14.8 TOPS.

There are also some other works using the emerging non-volatile memory array. Park et al. (2012) firstly demonstrated the use of a 1k-bit RRAM crosspoint array to speed up machine learning algorithms. Garbin et al. (2014) proposed a spike-based implementation of CNN using binary RRAM devices and achieved 94% accuracy on MNIST dataset. Xia et al. (2015) did a thorough technological exploration RRAM

crosspoint array for matrix-vector multiplication. They studied the non-ideal factors of the device, variations, and parasitics, and analyzed how to achieve a better trade-off between performance, energy and reliability. Prezioso et al. (2015) did an experimental implementation of RRAM crosspoint array for a single layer perceptron. They demonstrated the training of the model on the RRAM crosspoint array and achieved a good classification result on a small task. Hu et al. (2016) developed the Dot-Product Engine with RRAM crosspoint array and showed 1,000X to 10,000X more speed-energy efficiency product than state-of-the-art ASIC design. Gokmen and Vlasov (2016, 10) applied stochastic computing and stochastic update rule on the RRAM crosspoint array. They achieved 98% accuracy on MNIST dataset by training a CNN model. A full update cycle of an array performed using 1 ns pulses can be completed in 20 ns with 0.28 W power. Chi et al. (2016) designed the entire system and software-hardware interface to use RRAM crosspoint array as matrix-vector multiplication accelerator called PRIME. It shows 1,596X to 73,237X speedup and 335X to 138,984X power consumption reduction over CPU.

## 3. Emerging Memory Modeling

In this chapter, a hierarchical framework is proposed for the emerging memory modeling. Phase Change Random Access Memory (PRAM) and Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM) are modeled explicitly. With the proposed compact models, early stage design benchmarking is performed for these two types of memory. In addition, Resistive Random Access Memory (RRAM) is reviewed for the completion of the scope and will be used in the later work.

#### 3.1. Introduction

As Silicon technology is scaling down toward the 10nm regime, CMOS-based memory devices such as SRAM and DRAM suffer from high standby power consumption, so that they may no longer be the technology of choice. Instead, emerging memories, such as Phase Change Random Access Memory (PRAM) and Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM), are promising candidates for the next generation non-volatile memory. They provide low standby power, high data density, fast access and excellent scalability. In the past decade, there has been significant research effort on engineering various types of memory device. Modeling of these memory devices including nominal performance and variability is highly demanded for design practice.

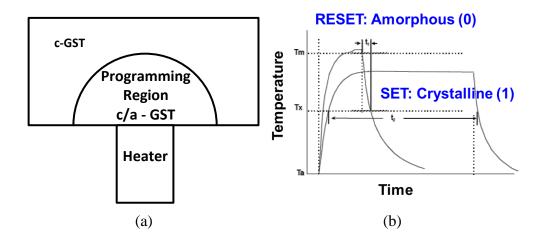

Phase Change Random Access Memory (PRAM) is one promising candidate for the next generation non-volatile memory. It has been shown to have excellent scalability, fast read access time, good data retention and high data density (Burr et al. 2010, 28:223-262, Wong et al. 2010, 98 :2201-2227). Figure 3.1 (a) shows the basic structure of PRAM. It consists of phase change material (chalcogenide alloy, Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST)) and a heater. The phase change material can switch between the amorphous phase with high electrical resistance (logic '0') and the crystalline phase with low electrical resistance (logic '1'). The phase is changed by increasing the temperature of phase change material with applied current pulse. To change the crystalline phase to amorphous phase, a current pulse with high amplitude and short duration is applied. To change the amorphous phase to crystalline phase, a lower and longer current pulse is applied. Figure 3.1 (b) shows the temperature profile in PRAM cell during these two switching periods. Additionally, by changing the current pulse profile, it is able to program PRAM to intermediate states continuously so that Multi-Level-Cell (MLC) is available for PRAM.

Figure 3.1. PRAM fundamental. (a) A basic PRAM cell structure. (b) Temperature profile of phase change material during programing.

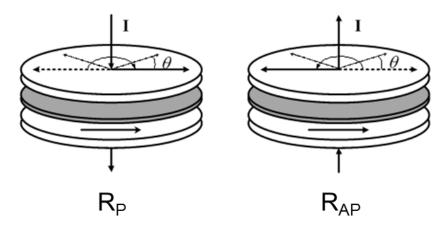

Besides PRAM, Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM) is another promising memory technology. It promises good combinations of high density, fast read and write access, low switching power, and non-volatile data storage (Wang et al. 2008, 44:2479-2482, Sharad et al. 2012, 11:843-853). STT-MTJ is based on Magnetic Tunnel Junction (MTJ). Figure 3.2 illustrates the basic structure of MTJ. Magnetic tunnel junction consists of two layers of ferromagnetic material separated by an

insulator layer. The magnetic orientation of one layer is fixed while the magnetic orientation of the other layer can be changed by application of current pulse through MTJ. The magnetic angle between these two layers (parallel (P) or anti-parallel (AP)) determines the resistance of MTJ. When a current is applied through the junction, the spin of the electrons is polarized by the fixed magnetic layer, and then transferred to the free layer to change the magnetic orientation.

Figure 3.2. Magnetic Tunnel Junction structure.

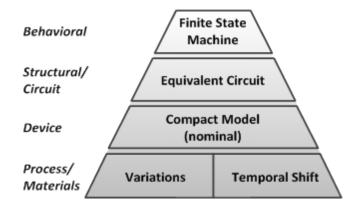

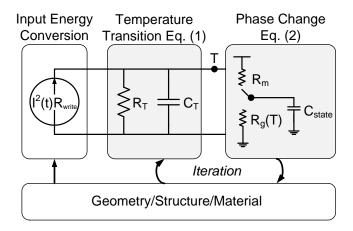

A good memory model should have the following features. (1) The model should be based on physical principle of the device for it to be trustable and tunable with technology evolution. (2) The model should capture various performance metrics of memory device including static and dynamic behavior, energy, speed, variability, reliability and scalability to support optimizations at multiple design levels (system level, circuit level, etc.). (3) The model should be easily implemented in SPICE with high simulation efficiency for co-design with CMOS devices. Hence, a hierarchical memory modeling framework is proposed, which is capable with all the features above. Figure 3.3 illustrates the proposed hierarchical memory modeling framework, which is general for all types of memory devices. It starts from the common behavioral model of a digital memory, the finite-state-machine (FSM), with electrical forces to control the program/erase/hold of the state. The FSM is then mapped to a structural model, using an equivalent circuit for SPICE simulation. This includes device-level models that can capture the underlying physical mechanisms of phase change and the dependence on material/structure parameters. The physical nature of device-level model further helps embed variability and reliability issues in the analysis. From top down to the bottom, one can develop the model layer by layer, from abstraction to details. It also helps us with memory design from a system perspective. From bottom up, one can do optimization for the memory from a device perspective. With such hierarchical approach, cross-layer analysis and the comparison of different memories in each hierarchy level are enabled. This will give us a better understanding of different types of memory and make heterogeneous design easier. PRAM and STT-MRAM are then modeled within such a framework.

Figure 3.3. Hierarchical memory modeling framework.

#### 3.2. Phase Change Random Access Memory

#### 3.2.1. PRAM Modeling

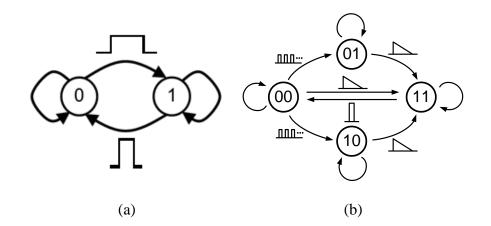

At behavior level, PRAM is modeled as the finite-state-machine in Figure 3.4. Since PRAM has both single-level cell (SLC) and multi-level cell (MLC) application, it has multiple FSMs. As shown in Figure 3.4 (a), SLC PRAM has two digital states, '0' and '1'. To RESET the cell from '1' to '0', a high and short current pulse is applied. To SET the cell from '0' to '1', a lower and longer current pulse is applied. Since PRAM needs large write energy, the data is read before write; if the initial state and the target state are the same, no writing is needed. Figure 3.4 (b) shows the FSM model for a 4 levels MLC PRAM (Bedeschi et al. 2009, 44:217-227). Here '00' is high resistance amorphous state, '11' is low resistance crystalline state, and '01' and '10' are the two intermediate states. To SET PRAM to '11' state from any other initial state, a ramping down SET pulse is applied. To RESET a '01' or '10' state to '00' state, it needs to SET to '11' first and then RESET. To write '01' or '10', it needs to RESET to '00' first and then program in a read and verify process using sequential short current pulses. With the FSM, one can easily figure out the transfer of states under a given current pulse.

Figure 3.4. The FSM models of PRAM. (The programming current waveform is illustrated.) (a) SLC (b) 4 levels MLC.

To map the FSM behavior into a circuit-level model for SPICE, an equivalent circuit model is introduced that captures each state transition in FSM. The input at this level is the initial state and the applied current pulse, and the output is the next state as well

as the energy and latency of each programming step. The circuit level model focuses on the physical procedure of state transition, and is shared by both SLC and MLC operations.

Figure 3.5. The equivalent circuit model of PRAM.

| Parameters         | Description                                     |

|--------------------|-------------------------------------------------|

| Ι                  | Input current amplitude                         |

| R <sub>write</sub> | Electrical resistance of PRAM cell during write |

| R <sub>T</sub>     | Thermal resistance of GST                       |

| CT                 | Thermal capacitance of GST                      |

| C <sub>state</sub> | Store the state of memory cell                  |

| R <sub>g</sub> (T) | Describe the crystallization of GST             |

Table 1. Parameters in the PRAM circuit level model.

Figure 3.5 gives the equivalent circuit model of PRAM, which consists of four parts, input energy conversion, temperature transition, phase change and geometry. Table 1 defines the parameters used at this level. The geometry block in Figure 3.5 describes the cross-sectional shape of a PRAM cell; the exact dimensions of each part are used to calculate electrical and thermal parameters. As the phase change of PRAM is based on heating, the input power is calculated by  $I^2R_{write}$  in the input energy conversion block. Since the crystalline GST has a very low resistivity,  $R_{write}$  is mainly the resistance of the metallic

heater (Itri et al. 2004). The energy conductance in PRAM is described by the energy conservation equation:

$$\int \left( I^2 R_{write} - \Delta T / R_T \right) dt = C_T \Delta T \tag{1}$$

where  $\Delta T$  is the temperature difference between the top electrode and the interface of GST and the heater. Equation (1) is modeled by the  $R_TC_T$  circuit in the temperature transition block (Figure 3.5), where  $R_T$  is the thermal resistance and  $C_T$  is the thermal capacitance (Kwong et al. 2008, Warren et al. 2008). The output node of this block indicates the temperature in the PRAM cell, which is further used in the phase change block. The phase change block consists of a capacitor  $C_{state}$  to indicate the state of the memory, a switch, a voltage source and resistors. The temperature evaluated by the temperature transition block is used to decide the switch position: when the temperature is higher than melting temperature (T>T<sub>m</sub>), the switch flips up and C<sub>state</sub> is charged by the voltage source, indicating the melting of GST. When the temperature is between the melting and annealing temperature (T<sub>a</sub><T<T<sub>m</sub>), the switch flips down and C<sub>state</sub> is discharged through R<sub>g</sub>, indicating the annealing of GST. The crystallization process is described by the Johnson-Mehl-Avrami (JMA) equation (Johnson and Mehl 1939, 135:416-458):

$$f = 1 - \exp\left(-\frac{t}{\tau(T)}\right) \tag{2}$$

where f is the fraction of the crystalized region, t is time, and  $\tau(T)$  is a temperature dependent time constant defined by:

$$\tau(T) = \begin{cases} R_m C_{state} & (T > T_m) \\ R_g(T) C_{state} = \tau_0 \exp\left(\frac{E_A}{k_B T}\right) & (T_a < T < T_m) \end{cases}$$

(3)

where  $E_A$  is the active energy of crystallization,  $k_B$  is Boltzmann constant and  $\tau_0$  is a constant. Therefore, the RC circuit models the exponentially phase change of PRAM and the voltage of  $C_{state}$  indicates the size of amorphous region, which corresponds to the memory state.

This abstracted level of PRAM model can be used to capture the nominal performance of single memory cell. The latency of write is defined as the time when the input current is applied to the end when the cell cools down. So, the latency can be obtained from the temperature transient curve by the circuit model. The energy of write is evaluated by  $I^2R_{write}t_{pulse}$ , where  $t_{pulse}$  is the time period of the input current pulse.

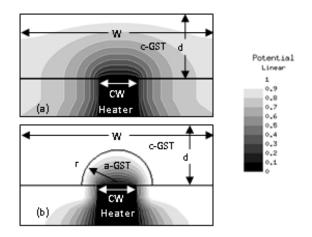

The device level model of PRAM predicts the parameters in the circuit model from cell geometry. It further paves a path to analyze the variability issues. TCAD simulators can be used to analyze the resistance change of PRAM, but with poor simulation efficiency. Thus, a geometry based compact model is necessary for design analysis. In this section, a geometry dependent resistance model is proposed for the mushroom cell PRAM (Wong 2010 98:2201-2227), which is one of the most common shapes of PRAM cell. Raphael 2D, a TCAD tool, is used to validate the model.

Figure 3.6 shows the 2D structure and the potential profile of a mushroom cell PRAM from Raphael 2D. The key dimensions of a mushroom cell are also specified in Figure 3.6: d is the thickness of GST, W is the width of the top contact, and CW is the width of the bottom contact between GST and the heater. It is assumed that the shape of the amorphous region is a hemisphere with radius r. These dimensions will determine the electrical resistance, thermal resistance and thermal capacitance of PRAM memory cell.

Table 2 summarizes the material properties that are used in this model (Li and Chan 2008, Li et al. 2008, 7:138-141).

Figure 3.6. 2D structure of PRAM cells in Raphael. (a) Fully crystalline state. (b) Fully amorphous state.

Table 2. Material properties in PRAM model (Li and Chan 2008, Li et al. 2008,

7:138-141).

| Material        | Electrical    | Thermal                         | Specific                         |

|-----------------|---------------|---------------------------------|----------------------------------|

|                 | resistivity p | conductivity $\kappa$           | Heat $c_0$                       |

|                 | (Ω·cm)        | $(W \cdot m^{-1} \cdot K^{-1})$ | $(J \cdot cm^{-3} \cdot K^{-1})$ |

| Crystalline GST | 0.0361        | 0.5                             | 1.25                             |

| Amorphous GST   | 33.33         | 0.2                             | 1.25                             |

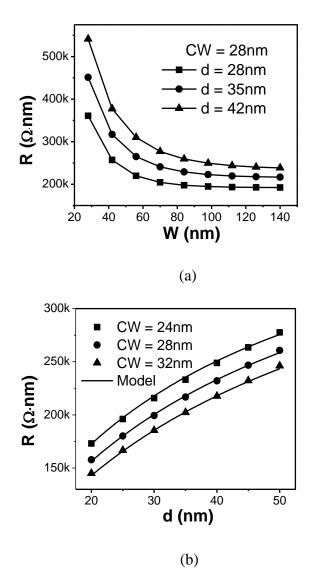

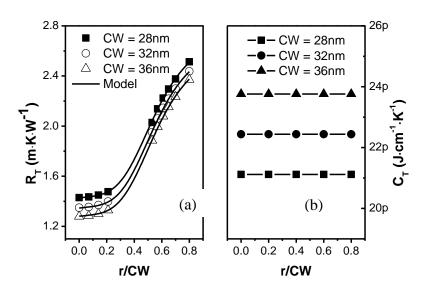

Figure 3.7 shows the dependence of the resistance of fully crystalline GST on W, CW and d. Figure 3.7 (a) shows the saturation of resistance with increasing W. Thus, our model only focuses on the case when W is large enough and does not affect the resistance. Since the two contacts of GST are of different size, we use an effective width to calculate the resistance as:

$$R = \rho_c \frac{d}{\alpha CW} \tag{4}$$

where the coefficient  $\alpha$  is the effective factor calculated as  $\alpha = 0.79 \text{*d/CW}+1.08$ . Figure 3.7 (b) validates the model for the crystalline resistance.

Figure 3.7. Geometry dependence of fully crystalline GST resistance. (a) Saturation of R with W increasing. (b) Fully crystalline resistance model vs. Raphael simulation results.

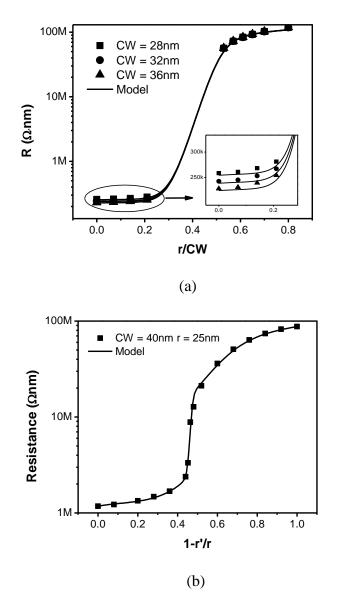

For the amorphous state, as shown in Figure 3.8 (a), the resistance primarily depends on r/CW, due to the large difference in the resistivity of amorphous GST and crystalline GST. When the mushroom fully covers the bottom contact (r/CW > 0.5), GST

shows a much higher resistance than that in the crystalline state. When the mushroom is very small, the resistance is low and does not change much with r/CW. The resistance changes dramatically when r/CW  $\approx$  0.5. We use a smoothing function to continuously model the resistance.

Figure 3.8. Geometry dependent electrical resistance model. (a) RESET (b) SET When the phase change material is changing from amorphous state to crystalline phase (SET), a smaller crystalline mushroom (with a radius of r') grows up inside the

original amorphous mushroom from the bottom contact. Figure 3.8 (b) shows the resistance change during this process. The difference in resistance value is due to the different resistivity for the two figures.

The thermal resistance of GST is modeled using a similar approach. The thermal resistance of full crystalline GST is calculated by:

$$R_T = \frac{d}{\kappa_c \alpha CW}$$

(5)

On the other side, since the difference in thermal conductivity of crystalline GST and amorphous GST is not as much as that of electrical resistivity, thermal resistance  $R_T$  does not change much with r/CW, as shown in Figure 3.9 (a). The thermal resistance also depends on d/CW in both crystalline state and amorphous state. Thermal capacitance  $C_T$ depends on d and CW because crystalline GST and amorphous GST have the same heat capacity, as shown in Figure 3.9 (b):

$$C_T = c_0 \alpha CWd/2 \tag{6}$$

Figure 3.9. Compact models of thermal parameters.

(b)

Figure 3.10. The iteration in model simulation significantly impacts the prediction of (a) temperature profile and (b) resistance transition.

With these geometry dependent resistance and capacitance models, the parameters in the circuit level model (Figure 3.5) can be obtained. Since  $R_T$  depends on the state of PRAM, which is represented by the size of the amorphous region, it changes during the SET process. Thus, it is important to iteratively simulate the heat and phase transition blocks (Figure 3.5) in order to accurately determine the temperature profile and the final resistance value, as shown in Figure 3.10.

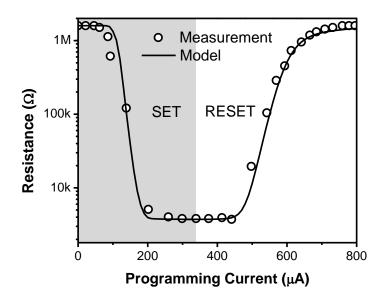

The resistance of a PRAM cell is predicted from the model with given initial geometry information and input current pulse, the geometry, and the material property. This model matches with experimental data from the paper of Lacaita et al. (2004) as shown in Figure 3.11. CW=68nm and d=119nm is used in this simulation.

Figure 3.11. R-I characteristics validated with experimental data from (Lacaita et al. 2004). CW=68nm and d=119nm.

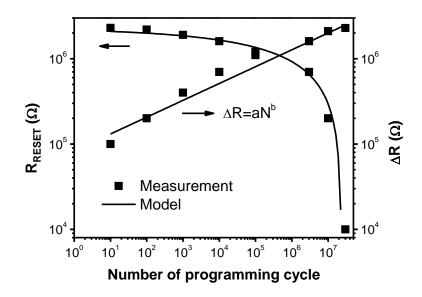

In the next level, process variation and material reliability are modeled. Since our device level model is geometry dependent, the impact of process variation can be easily simulated, which will be further discussed in Section III. There are two main reliability issues for PRAM, soft errors due to resistance drift and Stuck-SET failures. While error due to resistance drift can be recovered by the write process, Stuck-SET is hard error that is attributed to Ge depletion (Kim and Ahn 2005) or Ge contamination at the interface of GST and the heater. The resistance drop is modeled as

$$\Delta R = a N^{\nu} \tag{7}$$

where N is the number of programming cycles, a and b are fitting parameters as shown in Figure 3.12. In the circuit level, it is modeled by the degradation of the heating efficiency. In order to emulate this effect, the input energy  $I^2R_{write}$  is multiplied by a coefficient  $\lambda$ , which is less than 1 and is a function of N.

Figure 3.12. Stuck-SET model fitted with measured data from (Kim and Ahn 2005).

### 3.2.2 PRAM Design Exploration

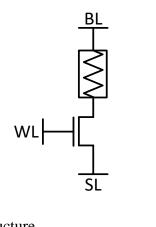

In this section, the performance of the proposed model is analyzed with respect to variability and reliability for the 32nm technology node. A new metric, State Transition Curve, is presented to capture the characteristics of PRAM for reliable design. PRAM employs 1T1R (1 transistor 1 resistor) structure as shown in Figure 3.13. BL, WL and SL correspond to bit line, word line and source line respectively. The models are incorporated into HSPICE using Verilog-A to simulate the shown structure. PTM 32nm HP (High Performance) MOSFET (Zhao and Yu, 2006, 53:2816-2823) is used for the simulation in

order to get high current for programming. Critical parameters of interest including their variations are listed in Table 3.

Figure 3.13. PRAM cell structure

|      | Parameter          | Value ( $\mu \pm 3\sigma$ ) |

|------|--------------------|-----------------------------|

|      | CW                 | 28 nm ±4%                   |

|      | d                  | 49 nm ±2%                   |

| PRAM | R <sub>SET</sub>   | 9 kΩ                        |

|      | R <sub>RESET</sub> | 3.6 MΩ                      |

|      | R <sub>write</sub> | 1 kΩ                        |

|      | $V_{dd}$           | 0.9 V                       |

| CMOS | $V_{th}$           | $494mV \pm 45mV$            |

|      | Length             | 28 nm                       |

Table 3. PRAM cell simulation parameters

For PRAM, State Transition Curve (STC) is a curve that describes resistance changes with programming current amplitude for a particular pulse width. Since the currents for SET and RESET are quite different, there are two sets of STC for PRAM. Figure 3.14 (a) shows the STC for SET and indicates the role of STC in reliable PRAM design. STC1 and STC2 show the characteristics of PRAM under nominal and variational condition respectively. The initial resistance is determined by the initial geometry of PRAM. The resistance transition is determined by the phase change model in Figure 3.5 and the geometry dependent resistance model in Figure 3.8. If the final resistance is a lot larger than the read threshold resistance, we can choose the current that achieves a successful write. However, such a choice may not be sufficient due to variability. STC2 in Figure 3.14 (a) represents incomplete state transition due to variation. If we still choose the same current, the write fails. But in MLC programming, intentional incomplete state transition is adopted by using sequential short current pulses as shown in Figure 3.14 (b). We can tune the current pulse to obtain the required resistance value. Figure 3.14 (b) shows that different magnitude of input current can achieve the same resistance with different number of current pulses. It consumes more energy for more programming steps (I<sub>1</sub>), but smaller resistance steps help more accurate MLC resistance control.

Figure 3.14. State Transition Curve of (a) SLC SET and (b) MLC SET.

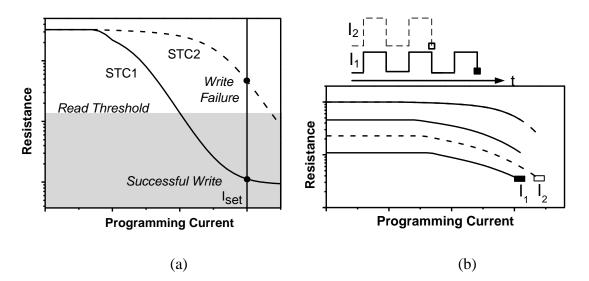

In this section, the performance of SLC PRAM cell is analyzed with proposed model and STC. We extract results under CMOS and GST process variation and temporal degradation. For nominal condition, STCs for different pulse width are presented in Figure 3.15. When t<sub>pulse</sub> increases, STCs shift left, so that smaller current is needed to get the same resistance. Thus, we can choose current and pulse width as listed in Table 4. The energy and latency performance of PRAM are also presented. The latency is obtained by the temperature transient curve, which is larger than the pulse width.

Figure 3.15. State Transition Curve in the nominal condition with different pulse width: (a) SET (b) RESET.

|                         | SET  | RESET |

|-------------------------|------|-------|

| Ι (μΑ)                  | 85   | 140   |

| t <sub>pulse</sub> (ns) | 100  | 40    |

| R (Ω)                   | 9.3k | 3.6M  |

| Energy (pJ)             | 0.72 | 0.78  |

| Latency (ns)            | 107  | 50    |

Table 4. Nominal performance of 32nm SLC PRAM.

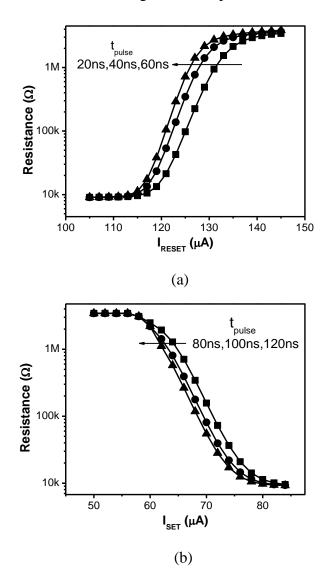

Figure 3.16. The contribution of different variation sources to the variability of  $R_{RESET}$ .

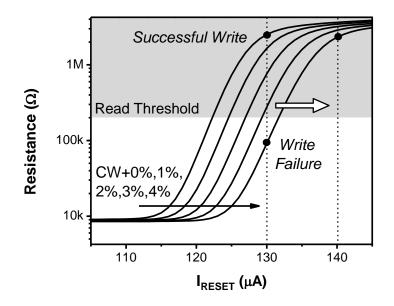

Next, the effect of variation is considered. Three variation sources are considered in this work:  $V_{th}$  of the transistor, CW and d as listed in Table 3. From the simulation, the variations of PRAM resistance ( $\Delta R_{SET}$  and  $\Delta R_{RESET}$ ) are obtained.  $\Delta R_{RESET}$  is much larger than  $\Delta R_{SET}$ . The contribution of the variation sources to  $\Delta R_{RESET}$  is shown in Figure 3.16. We see that CW is the critical variation source. Further, we analyze the impact of variation in CW on memory performance. Figure 3.17 shows how STC changes with CW. As CW increases, STC shifts right and  $R_{RESET}$  drops at a fixed I<sub>RESET</sub>. Under nominal CW, when I<sub>RESET</sub> = 130µA,  $R_{RESET}$  is much higher than read threshold indicating a successful write. For the same current, when CW experiences variation of +4%,  $R_{RESET}$  is below read threshold causing a write failure. However, if I<sub>RESET</sub> = 140µA, we always have a successful write under variation of CW. Therefore, this plot helps choose RESET current with a fixed pulse width to tolerate different CW variations.

Figure 3.17. RESET State Transition Curve is highly sensitive to CW variations  $(t_{pulse} = 40ns)$ .

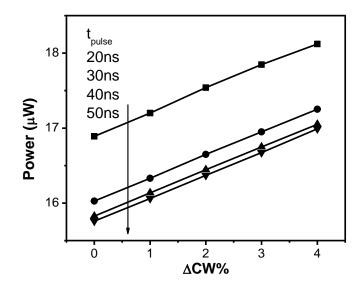

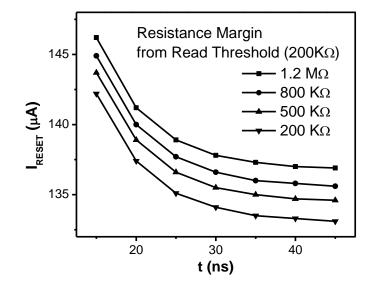

Figure 3.17 also shows that if we fix the margin from  $R_{RESET}$  to the read threshold resistance, we have to increase  $I_{RESET}$  with CW. For fixed resistance margin, the write power,  $I^2R_{write}$ , increases with CW as shown in Figure 3.18. In addition, the power goes up when we reduce the current pulse width since the required current is larger. Figure 3.19 shows the relation between required RESET current and pulse width for maintaining different resistance margins for successful writes. In order to achieve higher resistance margin, more current and time are needed resulting in higher power requirements.

Figure 3.18. Write power dramatically increases with larger CW variations, assuming a constant resistance value after write.

Figure 3.19. Required RESET current and pulse width with given resistance margin.

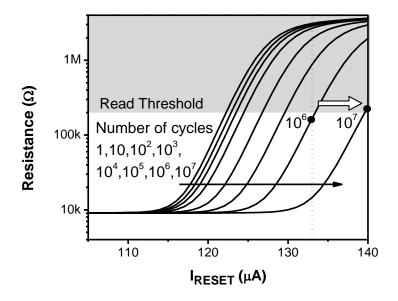

Finally, the impact of Stuck-SET on STC is simulated and the results are presented in Figure 3.20. The degradation increases as the number of cycles increases. If  $I_{RESET} =$

133 $\mu$ A, RESET resistance of PRAM drops below the read threshold after 10<sup>6</sup> cycles, which causes hard error. We can increase I<sub>RESET</sub> to 140 $\mu$ A to increase PRAM lifetime to 10<sup>7</sup> cycles.

Figure 3.20. State Transition Curve with Stuck-SET degradation.

## 3.3. Spin-Transfer Torque Magnetic Random Access Memory

### 3.3.1. STT-MRAM SPICE Model

Since STT-MTJ has only two stable states, STT-MRAM can only support SLC application. The FSM is the same as SLC PRAM as shown in Figure 3.4 (a).

The dynamics of the magnetic moment  $\vec{M}$  of the free layer in MTJ is defined by the LLG equation (Ralph and Stiles 2008, 320:1190-1216, Kammerer et al. 2010, 57:1408-1415):

$$\frac{d\dot{M}}{dt} = -\gamma \mu_0 \vec{M} \times \vec{H}_{eff} - \gamma \frac{2K}{M_s^2} \left(\vec{M} \cdot \vec{u}_{ea}\right) \cdot \left(\vec{M} \times \vec{u}_{ea}\right) + \frac{\alpha}{M_s} \vec{M} \times \frac{d\dot{M}}{dt} + \eta \frac{\mu_B I}{eV}$$

(8)

The terms (from left to right) represent the Zeeman torque, by both the local field and the thermal fluctuation field, the anisotropic torque, the damping torque, and the spintransfer torque, in which the efficiency ( $\eta$ ) depends on the current direction. Table 5 defines key model parameters (Lu et al 2007, 40:320-325, Faber et al. 2009).

| Saturation magnetization $(M_s)$                               | $M_{s0}\left[4\left(1-\frac{1}{4r_{ch}'-1}\right)\cdot\exp\left(-\frac{2S_{b}}{3R}\frac{1}{4r_{ch}'-1}\right)-3\right]$ |      |  |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|--|

| Effective magnetic field $(\tilde{H}_{eff})$                   | Intrinsic $\vec{H}$ +thermal fluctuation $\vec{H}_{f}$                                                                  |      |  |

| Gyromagnetic ratio (γ)                                         | Anisotropic const. (K) Damping const. (d                                                                                |      |  |

| $1.76 \times 10^{11} \text{ rad} \cdot \text{s}^{-1}/\text{T}$ | $1.13 \mathrm{x} 10^5 \mathrm{T} \cdot \mathrm{A/m}$                                                                    | 0.02 |  |

Table 5. Parameters on the geometry and materials.

The switching of the magnetic moment is the key dynamics in STT-MTJ. In general, it is a three dimensional movement: the Zeeman torque and the anisotropic torque contribute to the rotation in the plane perpendicular to the easy axis, indicated by an angle  $\varphi$ ; the damping torque and the spin-transfer torque dominate the switching in the easy plane, resulting in the change of  $\theta$ . Considering a realistic structure of STT-MTJ (Figure 3.21), the change of the magnetic moment can be separated into two planes and thus, the LLG equation reduced to two scalar equations of magnetic angle  $\varphi$  and  $\theta$ .

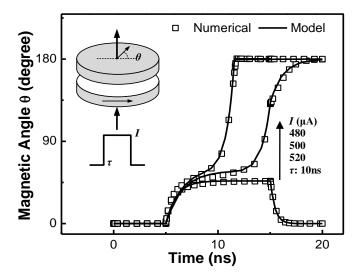

Figure 3.21. An in-plane STT-MTJ is programmed by a current pulse.

$$M_{s}\frac{d\varphi}{dt} = -\gamma\mu_{0}M_{s}H\sin\theta - 2\gamma K\sin\theta\cos\theta$$

(9)

$$M_s \frac{d\theta}{dt} = \alpha M_s \frac{d\varphi}{dt} + \eta \frac{\mu_B I}{eV}$$

(10)

Substituting  $d\varphi/dt$  from Equation (9) to Equation (10):

$$M_s \frac{d\theta}{dt} = -\alpha \gamma (\mu_0 M_s H \sin \theta + 2K \sin \theta \cos \theta) + \eta \frac{\mu_B I}{eV}$$

(11)

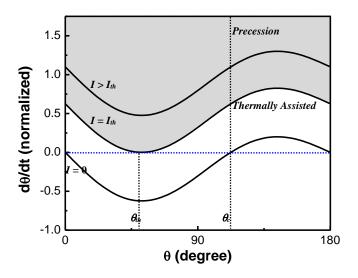

The scalar equation of Equation (11) is the foundation to analyze the switching dynamics of  $\theta$ . Based on Equation (11), Figure 3.22 plots  $d\theta/dt$  for different *I* when  $\theta$  changes from 0° to 180°. Some critical points are highlighted below in order to obtain the physical map for further model derivation:

Figure 3.22.  $d\theta/dt$  for different *I* when  $\theta$  changes from 0° to 180°.

Threshold current ( $I_{th}$ ): This concept separates two possible switching mechanisms in a STT-MTJ device, precession switching and thermally assisted switching. When  $I > I_{th}$ ,  $d\theta/dt$  is always > 0 (Figure 3.22) and thus, the magnetic angle is able to complete the switching with sufficient  $\tau$ . However, when  $I < I_{th}$ ,  $d\theta/dt$  may be < 0, requiring the assist of thermal fluctuation  $H_f$  to statistically switch STT-MTJ (Faber et al. 2009). As the thermal process takes a longer time and is not deterministic, today's STT-MTJ usually follows the precession switching.  $I_{th}$  can be solved from the minimum of  $d\theta/dt = 0$ , which is associated with the threshold angle  $\theta_{th}$  (Figure 3.22).

Critical angle ( $\theta_c$ ): This angle defines a critical value the magnetic moment has to reach at the end of the current pulse; if  $\theta$  at time =  $\tau$  is smaller than  $\theta_c$ , the damping torque may pull  $\theta_c$  back to 0° (Figure 3.21). As observed in Figure 3.22, when I = 0, there are three points to satisfy  $d\theta/dt = 0$ : 0° and 180° are two stable solutions, while  $\theta_c$  is a metastable point. This behavior is similar as that in a SRAM cell, and helps us develop the model of  $\theta_c$ .

Critical current ( $I_c$ ): Given the pulse width  $\tau$ ,  $I_c$  is the minimum current required to switch the magnetic angle from 0° to  $\theta_c$ .  $I > I_c$  ensures a successful precession switching. To solve  $I_c$ , Equation (11) is integrated from 0° to  $\theta_c$  for  $d\theta$ , and from 0 to  $\tau$  for dt. A compact solution is obtained (Table 6).  $I_c$  is proportional to the inverse of  $\tau$ , implying a tradeoff between speed and the writing power in design optimization.

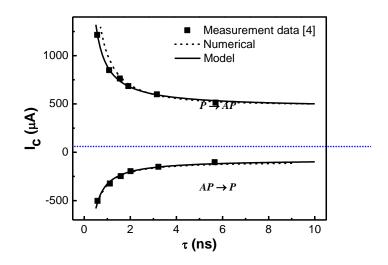

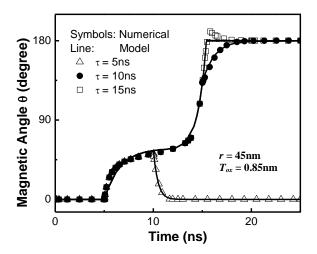

Table 6 summarizes the models for  $P \rightarrow AP$ , in standard international units. For  $AP \rightarrow P$ , the formulas remain the same, but with different coefficient values due to the different initial condition. The formulas in Table 6 have a clear root in physics, and are accurate in the precession switching. They are scalable with process and material parameters, supporting the development of the RC network. Figure 3.23 validates our model with the measurement data (Chun et al. 2013, 48:598-610). Due to the operation nature of STT-MTJ, it requires more current and energy to switch it from *P* to *AP* (Figure 3.23).

Table 6. Models of Critical Points in STT-MRAM.

| $	heta_{th}$ | $\cos^{-1}\left[\left(\sqrt{(\mu_0 M_s H)^2 + 32K^2} - \mu_0 M_s H\right) / (8K)\right]$       |

|--------------|------------------------------------------------------------------------------------------------|

| Ith          | $lpha\gamma(eV)/\eta\mu_{B}\cdot\left[\mu_{0}M_{s}H\sin\theta_{th}+K\sin(2\theta_{th})\right]$ |

| $\theta_c$   | $\cos^{-1}\left[-\mu_0 M_s H /(2K)\right]$                                                     |

| $I_c$        | $(\pi r^2) \cdot (2.1 \times 10^{-4} M_s / \tau + 0.34 M_s H + 4.26 \times 10^{10})$           |

Figure 3.23 Validation with published STT-MTJ data (Chun et al. 2013, 48:598-610). (r = 45nm,  $T_{ox} = 0.85nm$ )

The switching of the magnetic angle represents the write process of STT-MTJ. The read of the state is by characterizing the resistance of MTJ. When a read current is delivered to STT-MTJ, the resistance reaches a low value ( $R_P$ ) if the magnetic moments in both ferromagnetic layers are in parallel; otherwise a higher resistance ( $R_{AP}$ ) is detected. Coupled with the dynamic magnetization procedure in previous section, this property completes the operation of STT-MTJ.

The tunnel magneto-resistance (*TMR*) of MTJ is defined as  $(R_{AP}-R_P)/R_P$ . During the continuous switching of the magnetic angle, the change of MTJ resistance follows (Madec et al. 2010, 57:1416-1424):

$$R(\theta) = 2R_{p} \left( \frac{1 + TMR}{2 + TMR + TMR \cdot \cos \theta} \right)$$

(12)

The static values of  $R_{AP}$  and  $R_P$  are calculated from the tunneling current through  $T_{ox}$ . Equation (12) is used to model the dynamic resistance during the switching period. 3.3.2. STT-MRAM Compact Model

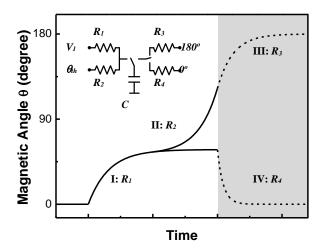

The details of the switching period are important for various design purpose, such as power and yield. In addition, design applications of STT-MTJ usually involve CMOS as the control device. For these reasons, compact model of STT-MTJ needs to be embedded into the SPICE simulator. Different from previous approach that directly implement the LLG equation through complex Verilog-A codes, this work also proposes a simple RC network that is physical, intuitive, and general.

Starting from the fundamental LLG equation (Equation (11)),  $\sin\theta$  can be approximated  $as\theta$ , 1, or  $-\theta$ , when  $\theta$  is close 0°, 90°, or 180°, respectively. A similar treatment can be applied to  $\cos\theta$ . By expanding  $\sin\theta$  and  $\cos\theta$  in this approach,  $d\theta/dt$  in Equation (11) is expressed as a linear function of  $\theta$ , and thus, the solution of the LLG equation is transferred as a passive RC network for SPICE simulation.

Based on this general principle, four distinct regions are recognized, easing the implementation. Figure 3.24 shows the network which supports transient SPICE simulations, with the output node representing  $\theta$ . *R*s are functions of those critical points in Table 6, and *C* is a constant, as derived below:

Figure 3.24. The regional RC network for dynamic SPICE simulation.

Region 1: This is at the beginning of the current pulse, when  $\theta$  is close to 0 and thus, sin $\theta \sim \theta$  and cos $\theta \sim 1$ . The damping torque resists the change of  $\theta$ , implying that the  $R_1C$ network is a negative feedback.  $V_1$ , which is a linear function of applied I, is charging the output node.

Region 2: As soon as  $\theta$  exceeds the threshold angle  $\theta_{th}$ ,  $\theta$  is close to 90° so that  $\sin \theta \sim 1$  and  $\cos \theta \sim 90^\circ - \theta$ . In this region,  $d^2\theta/dt^2$  becomes positive, as indicated in Figure 3.22. Such a fact suggests that the RC network is a positive feedback: the increase in  $\theta$  helps speed up the switching. Therefore, a negative resistance,  $R_2$ , is obtained from Equation (11), giving an exponential increase in the magnetic angle (Figure 3.24). If the current pulse stays long enough, the magnetic angle rapidly reaches 180°, as shown in Figure 3.21. However, if  $\tau$  is not long enough to complete the switching, two more regions are needed for time >  $\tau$ .

Region 3: If  $\theta > \theta_c$  when the current pulse ends, the damping torque helps finish the switching without *I*, as shown in Figs. 3.21. In this case, Equation (11) can be expanded around 180° to obtain  $R_3C$ . Region 4: Finally, if  $\theta < \theta_c$  when the current pulse ends, the damping torque overwhelms and pulls the magnetic angle back to the initial state, 0°. The switching fails, under the influence of *R*<sub>4</sub>*C*.

Table 7 summarizes all model parameters. They are in closed-form, derived from the LLG equation and parameters in Table 6. The proposed RC network is followed by the *TMR* model (Equation (12), in Verilog-A) to complete the simulation structure. Working together, they convert the magnetic angle to electrical resistance. As all parameter values are pre-solved before the simulation, this RC network is highly efficient in the SPICE environment.

| $V_1$                 | $\theta_{th} + a(I - I_{th})/(\pi r^2)$     |

|-----------------------|---------------------------------------------|

| $R_1$                 | $K_1(\mu_0 M_s H + 2K)/M_s$                 |

| $R_2$                 | $K_{2}[1-b(I-I_{th})/(\pi r^{2})]K/M_{s}$   |

| <i>R</i> <sub>3</sub> | $K_3(2K-\mu_0M_sH)$                         |

| $R_4$                 | $K_4 \left( \mu_0 M_s H + 2K \right) / M_s$ |

Table 7. Formulas for the RC Elements in SPICE.

The newly developed models are implemented into SPICE. Two simulation examples are presented in Figure 3.21 and Figure 3.23. Under the same assumptions of *I*, *r* and  $T_{ox}$ , Figure 3.25 further demonstrates the prediction under different pulse width  $\tau$ . As expected by the RC network in Figure 3.24, different RC components are activated, depending on the switching condition. The success of data writing is determined by both the magnitude and the duration of the current pulse. The proposed modeling and simulation method smoothly captures such a behavior for design exploration.

Figure 3.25. The switching behavior under different pulse widths.

Figure 3.26. The matching in the prediction of MTJ resistance.

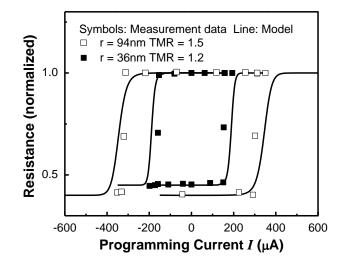

By combining the switching model and the *TMR* model together, the new solution generates the electrical property of STT-MTJ. Figure 3.26 validates this approach with the experimental data (Diao et al. 2007, 19:165209, Lin et al. 2009). For a STT-MTJ device, since  $P \rightarrow AP$  starts from  $\theta = 0^\circ$  but  $AP \rightarrow P$  starts from  $\theta = 180^\circ$ , these two switching paths experience different switching thresholds, as predicted by the LLG equation. This causes the hysteresis behavior in the resistance, which is well matched by our proposed models. In addition, the new compact model is general enough to describe the data from different processes, as demonstrated in Figure 3.26.

### 3.3.3. STT-MRAM Design Exploration

The STT-MRAM models are implemented into SPICE with Verilog-A. The effects of technology scaling and the design under reliability constraints are studied.

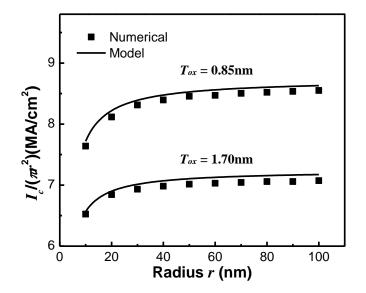

From the perspective of technology scaling, Figure 3.27 examines the minimum programming current, Ic, under shrinking of device feature size for fixed pulse width  $\tau$  = 5ns. The radius r impacts the density of Ic mainly through saturation magnetization (Ms in Table 5), which is a material property (Lu et al. 2007, 40:320-325). The density of Ic is sensitive to r only when the radius is smaller than 20 nm. On the contrary, Ic is highly sensitive to Tox, as Tox affects the intrinsic magnetic field in Equation (8). In addition, Tox has a strong influence on the resistance and the long-term reliability of the tunnel junction (Madec et al. 2010, 57:1416-1424). Therefore, process control of Tox is extremely important to STT-MTJ based memory design.

Figure 3.27. The scaling of critical current of STT-MTJ device.

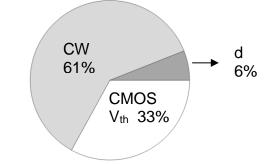

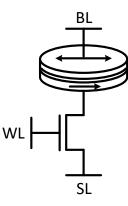

Then, we investigate the design optimization of a single cell STT-MRAM under reliability constraints. Similar to PRAM, STT-MRAM adopts 1T1MTJ structure, as shown in Figure 3.28. BL, WL and SL correspond to bit line, word line and source line respectively. We used the MTJ model parameters in Figure 3.23 and PTM HP transistor model in 45nm technology (Zhao and Yu, 2006, 53:2816-2823). Critical parameters of interest including their variations are listed in Table 8.

Figure 3.28. 1T1MTJ memory cell structure.

|      | Parameter       | Value ( $\mu \pm 3\sigma$ )       |

|------|-----------------|-----------------------------------|

| STT  | r               | $45 \text{ nm} \pm 1 \text{ nm}$  |

|      | T <sub>ox</sub> | 0.85 nm                           |

|      | R <sub>p</sub>  | 1 kΩ                              |

|      | $R_{ap}$        | 2 kΩ                              |

| CMOS | $V_{dd}$        | 1 V, 2.2 V                        |

|      | $V_{th}$        | $469 \text{ mV} \pm 5 \text{ mV}$ |

|      | Length          | 45 nm                             |

Table 8. STT-MRAM cell simulation parameters.

Due to the difference in required critical current for  $P \rightarrow AP$  and  $AP \rightarrow P$ switchings, a boosted voltage of 2.2V is applied for  $P \rightarrow AP$  while nominal Vdd of 1V is used for  $AP \rightarrow P$ . In the memory cell, process variation affects both MTJ and access transistor. We use the MTJ radius r and transistor threshold voltage Vth to represent the variation sources listed in Table 8. After embedding these variations into the nominal model, one million Monte Carlo simulations are run to show the yield under different programming conditions.

We calculated the bit error rate (BER) as the percentage of the simulations in which the angle  $\theta$  reaches 1800 from 0o and vice versa at the end of simulation time. To guarantee reliability constraint of block failure rate (BFR) of 10<sup>-8</sup>, all the current profiles described by the combination of current pulse amplitude (I) and width ( $\tau$ ), result in the same BER of 2x10<sup>-5</sup>. We set this BER constraint since BFR = 10<sup>-8</sup> of a 512-bit block can be achieved with ECC scheme BCH (t=2) that results in small hardware overhead (Yang et al. 2014, 76:133-147).

Programming current and cell energy consumption are generated for  $P \rightarrow AP$  and  $AP \rightarrow P$  with equal BER in Figure 3.29 and Figure 3.30, respectively. The energy is calculated by the integration of I\*Vdd for the duration of the pulse. It includes both STT-MTJ and transistor energy. We see for both  $P \rightarrow AP$  and  $AP \rightarrow P$  switchings, current pulse amplitude increases as current pulse width decreases, similar to the trend shown in Figure 3.23. However, under the BER =  $2x10^{-5}$  constraint, the required current amplitude is larger than the critical current amplitude. Correspondingly, required transistor size has to be increased to support the large current amplitude. On the other hand, programming energy increases as current pulse width increases because the decrease in current I is slower than the increase in  $\tau$ .

Figure 3.29. Programming current and energy of  $P \rightarrow AP$  switching. All points have  $2x10^{-5}$  BER.

Figure 3.30. Programming current and energy of  $AP \rightarrow P$  switching. All points have  $2x10^{-5}$  BER.

From Figure 3.29 and Figure 3.30, we see that  $P \rightarrow AP$  switching requires much larger current and transistor size in spite of boosted voltage supply (2.2V for  $P \rightarrow AP$  and

1V for AP → P). Therefore, the design constraints are set by those of P → AP. Using transistor sizes set by P → AP, AP → P switching will have much lower BER than  $2x10^{-5}$ , which is not needed and results in a waste of energy. So, we propose to reduce the supply voltage for AP → P switching to save energy.

Figure 3.31. Supply voltage and energy at different transistor sizes for  $AP \rightarrow P$  switching. All points have BER of  $2x10^{-5}$ .

Figure 3.31 shows different combinations of supply voltage (Vdd) and transistor width (W) to obtain the same BER of  $2x10^{-5}$  for  $\tau = 3$ ns. The energy decreases with lower Vdd and larger W since current amplitude almost remains the same. As shown in Figure 3.31, when the transistor size increases from 230nm to 320nm (required by P  $\rightarrow$  AP switching), required voltage decreases from 1V to 0.86V to achieve same BER. Thus, programming energy is reduced from 0.784pJ to 0.672pJ (14.3% decrease). However, if the two switchings have equal probability, this optimization causes only 2.3% overall energy reduction. If we make  $AP \rightarrow P$  switching more often by some coding techniques, more energy reduction can be achieved.

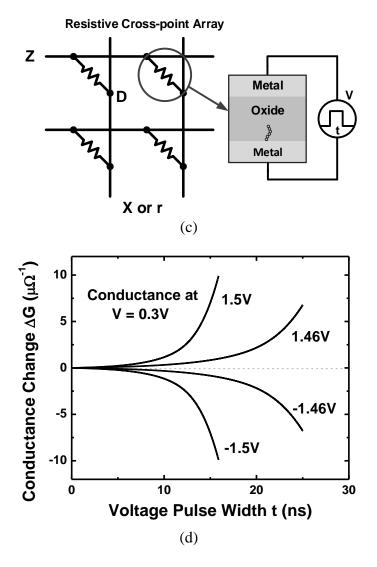

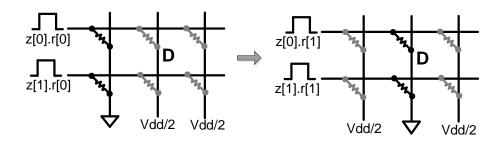

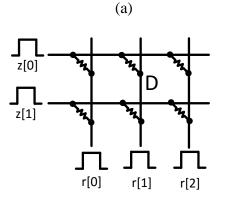

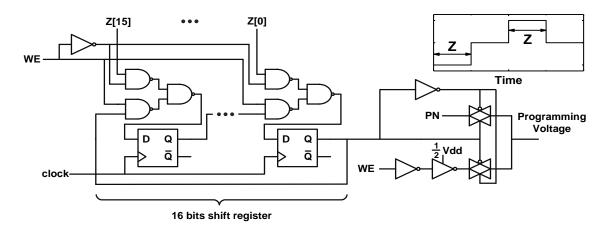

3.4. Review of Resistive Random Access Memory