# Contributions to the Design and Operation of a Multilevel-Active-Clamped Dc-Ac Grid-Connected Power Converter for Wind Energy Conversion Systems

Thesis submitted for the PhD Degree issued by the Universitat Politècnica de Catalunya, in its Electronic Engineering Program.

Luis Caballero Diaz

Thesis advisor: Dr. Sergio Busquets Monge Dr. Sergi Ratés Palau

June 2017

# Agradecimientos

Me gustaría dedicar estas líneas para agradecer a todas las personas que han hecho posible que esta tesis sea una realidad.

Primero de todo, muchas gracias a Sergio Busquets por la dirección de la tesis y tener siempre una idea o propuesta cuando el camino se complicaba.

Muchas gracias a Sergi Ratés, codirector de la tesis, por facilitarme el camino para el desarrollo de la tesis y mostrarse siempre dispuesto a intentar ayudarme.

Muchas gracias a Joan Nicolás, profesor del grupo GREP, por la impagable ayuda facilitada y la dedicación y entusiasmo mostrado durante el transcurso de la tesis.

Finalmente, agradecer el apoyo, confianza y cariño recibido por parte de mi familia, que ha sido incuantificable. Muchas gracias por darme todo el cariño que me habéis dado.

Todo ha sido mucho más fácil gracias a vosotros, muchas gracias.

# **CONTENTS**

| ABSTRACT        |                                                                      |

|-----------------|----------------------------------------------------------------------|

| Nomenclature    |                                                                      |

| CHAPTER 1. INTE | RODUCTION                                                            |

| 1.1. Wind Er    | nergy Overview                                                       |

| 1.2. Wind Er    | nergy Conversion System Configurations11                             |

| 1.2.1. C        | Constant-Speed WECS 12                                               |

| 1.2.2. D        | Doubly-Fed Induction Generator (DFIG) WECS                           |

| 1.2.3. F        | ull-Power Converter WECS                                             |

| 1.2.4. T        | rends in WECS Configuration14                                        |

| 1.3. Power C    | Converter Overview                                                   |

| 1.3.1. N        | Aultilevel Converter Concept                                         |

| 1.3.2. C        | Comparison of 2L versus 3L Power Converters 17                       |

| 1.3.3. N        | Aultilevel Converter Topologies                                      |

| 1.3.3.1.        | Cascaded H-Bridge Topology19                                         |

| 1.3.3.2.        | Flying Capacitor Topology20                                          |

| 1.3.3.3.        | Diode-Clamped Topology21                                             |

| 1.3.3.4.        | Recent ac-ac Multilevel Converter Topologies for WECS                |

| 1.3.3.          | 4.1. Three-Level H-Bridge (3L-HB) Topology 21                        |

| 1.3.3.          | 4.2. Five-Level H-Bridge (5L-HB) Topology 22                         |

| 1.3.3.          | 4.3. Three-Level NPC + Five-Level H-Bridge (3L-NPC + 5L-HB) Topology |

| 1.3.3.          | 4.4. Neutral Point Pilot (NPP) Topology24                            |

| 1.3.3.          | 4.5. Modular Multilevel Topology24                                   |

| 1.3                                      | .3.4.6. Active Neutral-Point-Clamped (ANPC) Topology2 | 25 |

|------------------------------------------|-------------------------------------------------------|----|

| 1.4. Power Converter Reliability in WECS |                                                       |    |

| 1.5. 3L-ANPC Operating Principle         |                                                       |    |

| 1.5.1.                                   | Active Loss Balancing [34]2                           | 28 |

| 1.5.2.                                   | Feed-Forward Loss Balancing [36]2                     | 29 |

| 1.5.3.                                   | Multilevel active-clamped operating principle [49]2   | 29 |

| 1.6. Thesis objective                    |                                                       |    |

| 1.7. Thesis outline                      |                                                       |    |

| CHAPTER 2. ENHANCED POWER DEVICE CONFIGURATION AND OPERATION OF A GRID-CONNECTED INVERTER FOR |  |  |

|-----------------------------------------------------------------------------------------------|--|--|

| WIND ENERGY CONVERSION SYSTEMS                                                                |  |  |

| 2.1. Introduction                                                                             |  |  |

| 2.2. 3L-ANPC Operating Principle                                                              |  |  |

| 2.3. Proposed 3L-ANPC Design Guidelines                                                       |  |  |

| 2.4. WECS Operating Points                                                                    |  |  |

| 2.5. Electro-Thermal Model                                                                    |  |  |

| 2.5.1. Power Loss Model                                                                       |  |  |

| 2.5.2. Thermal Model                                                                          |  |  |

| 2.6. Simulation Results                                                                       |  |  |

| 2.7. Conclusions                                                                              |  |  |

| CHAPTER 3. NOVEL COMMUTATION SEQUENCE TO SPLIT SWITCHING AND CONDUCTION LOSSES4 |  |

|---------------------------------------------------------------------------------|--|

| 3.1. Introduction                                                               |  |

| 3.2. 3L-ANPC Power Loss Distribution                                            |  |

| 3.3. Proposed Commutation Sequence                                              |  |

| 3.4. Simulation Results                                                         |  |

| 3.5. Conclusion | 60 |

|-----------------|----|

|-----------------|----|

| CHAPTER 4. EXPERIMENTAL VALIDATION                      |    |

|---------------------------------------------------------|----|

| 4.1. Introduction                                       | 61 |

| 4.2. Leg Prototypes and Leg Characterization Test Bench | 62 |

| 4.3. Leg Power Loss                                     | 69 |

| 4.4. Thermal Performance                                | 73 |

| 4.5. Silicon Area                                       | 83 |

| 4.6. Conclusions                                        | 86 |

| CHAPTER 5. HYBRID POWER DEVICE CONFIGURATION OF N-LEVEL ACTIVE-CLAMPED INVERTER F | or Wind |

|-----------------------------------------------------------------------------------|---------|

| ENERGY CONVERSION SYSTEMS                                                         | 89      |

| 5.1. Introduction                                                                 | 89      |

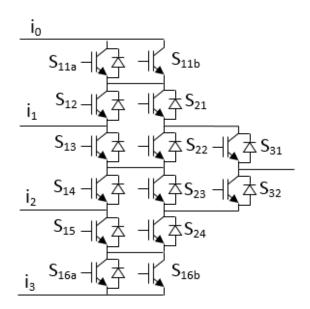

| 5.2. Multilevel Active-Clamped Topology and Basic Operating Principle             |         |

| 5.3. Hybrid Power Semiconductor Configuration                                     |         |

| 5.4. Enhanced Commutation Sequence                                                |         |

| 5.5. Simulation Results for a Four-Level Active-Clamped Inverter                  |         |

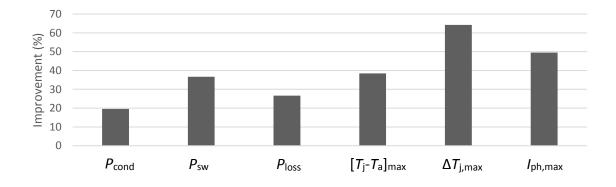

| 5.6. Conclusions                                                                  | 101     |

| CHAPTER 6. CONCLUSION              | 103   |

|------------------------------------|-------|

| 6.1. Contributions and Conclusions | . 103 |

| 6.2. Future Research Work          | . 104 |

| References |

|------------|

|------------|

# ABSTRACT

The demand of wind energy has considerably increased during the last decades. In order to fulfil this great energy demand, wind energy conversion systems (WECS) are designed to manage higher power ratings. Currently, the most attractive power converter topology in commercial WECS is the conventional two-level back-to-back voltage-source converter (2L-B2B). However, the 2L-B2B topology could have difficulties to achieve an acceptable performance with the available switching devices for the largest WECS, even though having the cost advantage. Instead, multilevel converters increase the power without increasing neither current nor blocking voltage of the power semiconductors, enabling a cost-effective design for the largest WECS using the available switching devices. Within the multilevel converters, the 3L-NPC topology offers high penetration in the market of large WECS. However, one of its major drawbacks is that the power loss is unevenly distributed among the switching devices. Therefore, the 3L-NPC output power capability is limited by the thermal performance of the most stressed switching device, which depends on the operating point. The 3L-ANPC topology was proposed in order to improve the power loss distribution among the power semiconductors. The 3L-ANPC provides a controllable path for the neutral current. Hence, the 3L-ANPC is able to offer certain freedom to distribute the power loss among the power semiconductors. As a consequence, and compared to the 3L-NPC, the thermal performance is more uniform and the output power capability increases. However, there is still room for improvement.

In light of the previous discussion, the proposed thesis defines enhanced design guidelines for the dc-ac grid-connected 3L-ANPC power converter, focused on improving its reliability and electrical performance, and following the trend of the current state of the art to define a feasible solution for the next generation of WECS. The thesis contributions are based on defining an enhanced power device configuration and a novel commutation sequence, avoiding concentrating both significant conduction and switching losses on a single power semiconductor device. This allows then selecting the most appropriate device for each converter position, which leads to a better converter efficiency and to a more uniform power loss distribution and thermal performance. This also leads to a higher converter power rating, and it is expected to improve the converter reliability.

# NOMENCLATURE

# Acronyms and Abbreviations

| ANPC   | Active neutral-point-clamped                      |

|--------|---------------------------------------------------|

| B2B    | Back-to-back                                      |

| DFIG   | Doubly-fed induction generator                    |

| HVDC   | High-voltage direct-current                       |

| IGBT   | Insulated-gate bipolar transistor                 |

| LUT    | Leg under test                                    |

| MAC    | Multilevel active-clamped                         |

| ММС    | Modular multilevel converter                      |

| MOSFET | Metal-oxide-semiconductor field-effect transistor |

| NPC    | Neutral-point-clamped                             |

| NPP    | Neutral-point-pilot                               |

| PMSG   | Permanent-magnet synchronous generator            |

| PWM    | Pulse-width modulation                            |

| rms    | Root mean square                                  |

| Si     | Silicon                                           |

| SiC    | Silicon Carbide                                   |

| WECS   | Wind energy conversion system                     |

| ZVS    | Zero Voltage Switching                            |

# Symbols

Topology parameters

| п                                        | Number of levels of the topology |

|------------------------------------------|----------------------------------|

| $\mathbf{i}_k$ ; $k \in \{1,2,\dots,n\}$ | Input terminals of the topology  |

# Time and Frequency

| t               | Time                |

|-----------------|---------------------|

| fn              | Grid frequency      |

| f <sub>sw</sub> | Switching frequency |

| T <sub>d</sub>  | Delay time          |

# Passives values

| R                | Resistance           |

|------------------|----------------------|

| R <sub>dis</sub> | Discharging resistor |

| L                | Inductance           |

| С                | Capacitance          |

# Voltage

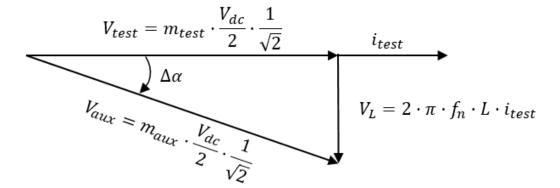

| V <sub>aux</sub>    | Auxiliary leg rms voltage with reference to the neutral point  |

|---------------------|----------------------------------------------------------------|

| V <sub>test</sub>   | Leg under test rms voltage with reference to the neutral point |

| $v_{C}$             | Capacitor voltage                                              |

| $V_{ m L}$          | Inductor rms voltage                                           |

| V <sub>l-n,pk</sub> | Phase-to-neutral peak voltage                                  |

| V <sub>dc</sub>     | dc-link voltage                                                |

4

| V <sub>CE</sub>     | IGBT collector-emitter voltage during on-state   |

|---------------------|--------------------------------------------------|

| $V_{ m F}$          | Diode forward voltage during on-state            |

| $\Delta V_{\rm dc}$ | Allowed transient dc-link capacitor over-voltage |

# Current

| i <sub>out</sub>    | Leg output current                                        |

|---------------------|-----------------------------------------------------------|

| i <sub>test</sub>   | Current of leg under test                                 |

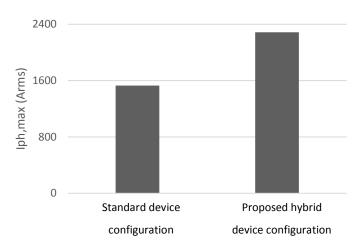

| I <sub>ph,max</sub> | Maximum inverter rms phase current for a maximum junction |

|                     | temperature                                               |

# Power

| P <sub>cond</sub> | Conduction power loss       |

|-------------------|-----------------------------|

| Pgen              | Generated active power      |

| P <sub>in</sub>   | Converter input power       |

| P <sub>leg</sub>  | Converter leg power loss    |

| P <sub>out</sub>  | Converter output power      |

| P <sub>sw</sub>   | Switching power loss        |

| P <sub>loss</sub> | Global converter power loss |

# Temperature

| $\Delta T_{j,\max}$ | Maximum device junction temperature variation |

|---------------------|-----------------------------------------------|

| T <sub>a</sub>      | Ambient temperature                           |

| T <sub>h</sub>      | Heatsink temperature                          |

| $[T_j - T_a]_{max}$ | Maximum device junction temperature increase above ambient |

|---------------------|------------------------------------------------------------|

|                     | temperature                                                |

| T <sub>j,T</sub>    | Junction temperature of switch T                           |

| T <sub>j,D</sub>    | Junction temperature of diode D                            |

Angle

| Δα | Phase shift between the voltage of leg under test and the voltage |

|----|-------------------------------------------------------------------|

|    | of auxiliary leg                                                  |

# Converter parameters

| т                | Modulation index ( $V_{l-n,pk}/V_{dc}/2$ ) |

|------------------|--------------------------------------------|

| m <sub>aux</sub> | Modulation index of auxiliary leg          |

| $m_{ m test}$    | Modulation index of leg under test         |

| pf               | Power factor                               |

| s <sub>T</sub>   | Control signal of switch T                 |

# Thermal impedance

| $Z_{\text{th}(j-c),T}$ | Junction-to-case thermal impedance of switch T |

|------------------------|------------------------------------------------|

| Z <sub>th(j-c),D</sub> | Junction-to-case thermal impedance of diode D  |

| $Z_{\rm th(c-h),T}$    | Case-to-heatsink thermal impedance of switch T |

| $Z_{\rm th(c-h),D}$    | Case-to-heatsink thermal impedance of diode D  |

| Z <sub>th(h-a)</sub>   | Heatsink-to-ambient thermal impedance          |

# Switching energy

| Esw_igbt              | Energy loss in one IGBT turn on and one turn off |

|-----------------------|--------------------------------------------------|

| E <sub>SW_DIODE</sub> | Energy loss in one diode turn off                |

# Weibull wind distribution

| С                | Weibull scale parameter                       |

|------------------|-----------------------------------------------|

| $f_{ m weibull}$ | Amount of time in per unit of each wind speed |

| k                | Weibull shape parameter                       |

| $v_{ m wind}$    | Wind speed                                    |

# CHAPTER 1

## INTRODUCTION

Abstract – This opening chapter presents a brief wind energy overview, detailing the most used wind energy conversion system (WECS) configurations and the evolution of power electronics in wind power. Then, the thesis objective is defined and the thesis outline is presented.

## 1.1. Wind Energy Overview

Wind turbines were invented some centuries ago but wind power did not play a significant role in that period [1]. In fact, the start of modern wind turbines was in 1957 by the pioneering and innovative Gedser wind turbine (200 kW) [2]. The Gedser wind turbine was working 11 years without any remarkable maintenance. Currently, it is located in the Danish Electricity Museum in Bjerringbro (Denmark).

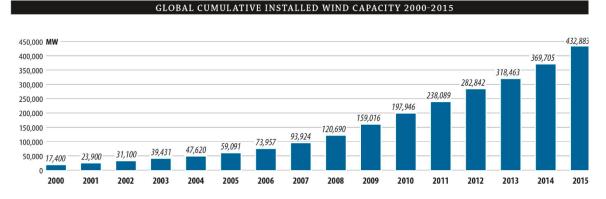

In the early 1970s, the energy supply crisis and the popular opposition to nuclear power created a stronger interest in wind energy [3]. Since then, a large number of developments in wind energy and a great increase in installed wind turbines have been experienced. Thus, in 1994 the installed capacity of wind turbines worldwide was about 3.5 GW [1] and at the end of 2015 it was more than 430 GW [4]. Fig. 1.1 shows the annual global cumulative installed wind power capacity from 2000 to 2015 which clearly shows a growing trend. This great increase has led wind energy to become the fastest developing renewable energy technology [5].

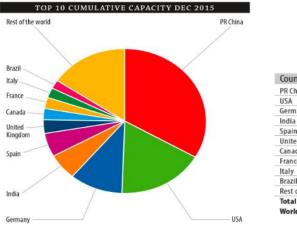

Fig. 1.2 shows the top 10 countries cumulative wind energy capacity in December 2015. The top 3 countries with more installed wind capacity at the end of 2015 are China (145.362 GW), USA (74.471 GW) and Germany (44.947 GW).

Fig. 1.1. Annual global cumulative installed wind power capacity from 2000 to 2015 [4].

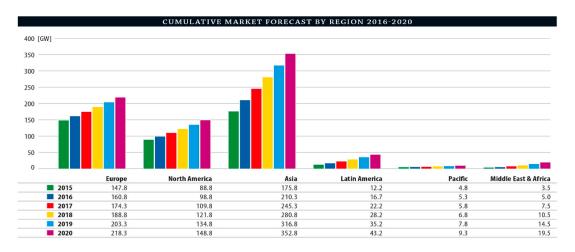

Fig. 1.3 shows the cumulative wind energy market forecast by region for 2016-2020. Asia is the continent with more expected installed wind capacity followed by Europe and America. Asia and America show a centralized wind energy distribution, focused on China and USA, respectively. Instead, Europe shows a decentralized wind energy distribution with significant MW installed in several countries. A growth trend is clear in all regions. However, the growth in Asia is forecasted to be considerably higher than in the other regions. Europe and North America will increase in a similar way and other regions will start to have a significant production such as Latin America, Pacific, and Middle East and Africa.

In order to fulfil this great energy demand, WECS are expected to be increasingly larger, especially for offshore applications. Thus, some current investigations are being focused on the design of up to 10 MW WECS [6], [7]. However, a more powerful WECS requires a higher tower with higher blade diameter, in order to increase the yielded energy. This makes the transportation and

| Country           | MW      | % Share |

|-------------------|---------|---------|

| PR China          | 145,362 | 33.6    |

| USA               | 74,471  | 17.2    |

| Germany           | 44,947  | 10.4    |

| India             | 25,088  | 5.8     |

| Spain             | 23,025  | 5.3     |

| United Kingdom    | 13,603  | 3.1     |

| Canada            | 11,205  | 2.6     |

| France            | 10,358  | 2.4     |

| Italy             | 8,958   | 2.1     |

| Brazil            | 8,715   | 2.0     |

| Rest of the world | 67,151  | 15.5    |

| Total TOP 10      | 365,731 | 84.5    |

| World Total       | 432,883 | 100     |

Fig. 1.2. Top 10 countries cumulative wind energy capacity in December 2015 [4].

Fig. 1.3. Cumulative wind energy market forecast by region for 2016-2020 [4].

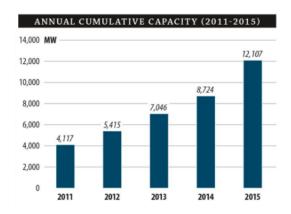

maintenance to the remote locations where wind farms are located extremely complicated. WECS are also being installed in offshore locations where the potential wind energy is grossly high. For example, the potential wind energy in the seas of the European Union with water depths of up to 50 m is easily several times larger than the total European electricity consumption [8]. Fig. 1.4 shows the global cumulative offshore wind installations from 2011 to 2015. Compared to the remarkable fast increase of onshore installations, these developments seem to be insignificant. However, they must be understood as trial balloon installations. In fact, offshore wind energy is supposed to play an important role in the future. In Europe, there are several GW offshore projects in various stages of planning [8].

The main downside of offshore wind energy is the high installation and transportation cost and the reduced accessibility. The transportation must be performed with specialized ships and the construction requires usually foundation under the sea. Besides this, the maintenance actions can be very expensive since accessing to offshore locations is limited, and a failure can take long time to be repaired. Therefore, the offshore WECS must be extremely reliable in order to increase the availability and make the investment profitable.

## 1.2. Wind Energy Conversion System Configurations

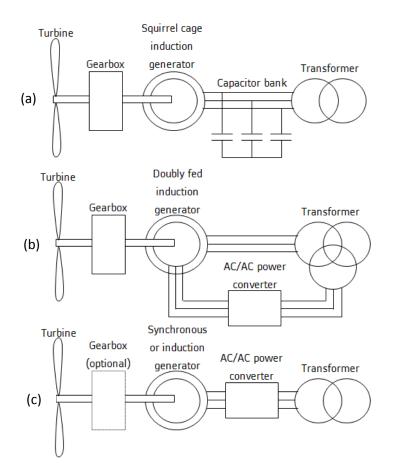

The WECS configuration is a widely reviewed issue in articles and investigations [2], [5], [9]-[13]. There are mainly three dominant WECS configurations to connect to the ac grid such as Fig. 1.5 shows, which are introduced in the following.

Fig. 1.4. Annual cumulative installed offshore wind power capacity for 2011-2015 [4].

## 1.2.1. Constant-Speed WECS

During the 1980s and 1990s, most wind turbine manufacturers mainly built constant-speed wind turbines with power levels up to 1.5 MW. The constant-speed system consists of a multistage gearbox and a squirrel cage induction generator directly connected to the grid. Normally, a capacitor bank for reactive power compensation is also used. This configuration is shown in Fig. 1.5(a).

The main advantage of this configuration is the cost and simplicity. However, the yielded energy is not optimal and may require an expensive mechanical design to absorb high mechanical stress. The following improvements have been introduced to increase the global power production:

The use of induction generators with two windings with different number of poles, so that the wind turbine can operate at two different constant speeds to improve the yielded energy and reduce audible noise [9].

Fig. 1.5. WECS configurations. (a) Constant-speed WECS. (b) Doubly-fed induction generator WECS. (c) Full power converter WECS.

2. The use of wound rotor induction generators with a variable rotor resistance. This resistance in the circuit can be adjusted by an electronic control system, which allows varying the generator speed in a limited range. However, the connection requires brushes and slip rings, which is a drawback due to the high required maintenance [5].

On the other hand, the direct connection of the induction generator to the power system produces transients with very high inrush currents, which could cause disturbances in the grid. Thus, a soft-starter is normally implemented in these WECS in order to limit the high inrush currents.

#### 1.2.2. Doubly-Fed Induction Generator (DFIG) WECS

After 1996, many manufacturers changed to a variable speed system with a DFIG for wind turbines with power levels above roughly 1.5 MW. This system consists of a multistage gearbox, a DFIG and a power electronic converter feeding the rotor winding as Fig. 1.5(b) shows.

The converter power rating is around 30% of the wind turbine rated power, which enables a speed range from roughly 70% to 120% of the synchronous speed, enough to ensure a proper energy yield.

Compared to the constant-speed system, this system provides a better performance on audible noise, mechanical stress, power quality, and yielded energy. However, the main drawback is that it requires significant maintenance due to rotor brushes, slips rings, and gearbox issues. On the other hand, according to the recent literature [6], [14], [15], grid codes are becoming stricter and, with this trend, DFIG WECS could have some difficulties to fulfil the future grid codes.

#### **1.2.3.** Full-Power Converter WECS

Since 1992, some manufacturers have also used a gearless or geared generator directly connected to the grid by means of a full-power electronic converter as depicted in Fig. 1.5(c). In recent years, full-power converter WECS have had a great increase. A clear advantage of this configuration is the complete isolation between the generator and the grid, so that the strictest grid codes can be fulfilled. There are three types of generators in full-power converter WECS:

- Gearless (or direct drive) low-speed synchronous generator

- Medium-speed synchronous generator with a single or two-stage gearbox.

- High-speed induction or synchronous generator with a three-stage gearbox.

The recent literature focuses on low-speed gearless or medium-speed gearbox with permanent-magnet synchronous generators (PMSG) [5]. Originally, the synchronous generator was mainly based on electrical excitation since permanent-magnets were too expensive. The rotor was provided with a dc excitation using slip rings, brushes and a rectifier, increasing the power losses. Later, when the price of permanent-magnets decreased, the focus shifted to PMSG, whose advantages, according to [11], are:

- Higher efficiency and yielded energy.

- No additional power supply for the magnet field excitation.

- Higher reliability due to the absence of mechanical components such as slip rings.

- Higher power-to-weight ratio.

The main advantage of gearless WECS with synchronous generator and full power converter is the increase of reliability, avoiding the gearbox maintenance and failures and reducing the number of WECS parts. However, the main drawback is the design of a low-speed high-torque synchronous generator, since it is considerably heavy, expensive and large [9].

## 1.2.4. Trends in WECS Configuration

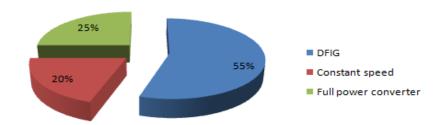

Fig. 1.6 shows the European market shares of WECS configuration in terms of power in 2010 [16]. The constant-speed WECS is the least dominating configuration and it is disappearing [9]. The market is clearly dominated by DFIG WECS with a 55% of the cumulative wind power. However, full-power converter WECS with low-speed gearless PMSG or medium-speed PMSG with gearbox are becoming an attractive solution for wind power generation, since the performance of permanent-magnets is improving, the cost of permanent-magnets is decreasing, and WECS reliability and availability could be enhanced compared to DFIG WECS [5] [11].

Fig. 1.6. European market shares of WECS configuration in terms of power in 2010 [16].

14

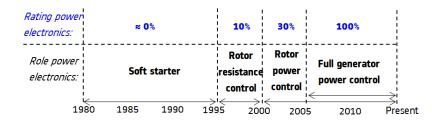

On other hand, the trend in the last decades has been to increase the use of power electronics in wind power. As observed in Fig. 1.7, it has drastically evolved from the simple soft starter for the constant-speed WECS with almost no power processing to the interesting full-power converters processing the whole power, and passing by the rotor resistance control for constant-speed WECS and the rotor power control for DFIG WECS. Thus, improving and optimizing the power converter performance in terms of efficiency, robustness, reliability, and availability must be one of the highest priorities for the future WECS.

#### **1.3. Power Converter Overview**

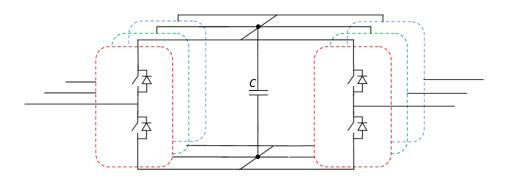

The most attractive ac-ac power converter solution in commercial market of WECS is currently the conventional two-level back-to-back voltage-source converter (2L-B2B) (Fig. 1.8) [17]. It is due to the fact that the 2L-B2B converter benefits from an extensive and well-established knowledge and it is based on a relatively simple structure with very few components, all contributing to a well-proven and reliable performance.

However, taking into consideration that the power rating of the WECS is increasing (even up to 10 MW), the 2L-B2B converters may suffer from large switching losses and low efficiency. The power rating of 2L-B2B converters can be increased through:

Fig. 1.7. Use of power electronics in wind power from 1980 to present [12].

Fig. 1.8. Conventional two level back to back voltage source converter.

- A current increase: it requires connecting in parallel several power semiconductors to withstand high-current values. It does not directly affect the reliability, but it reduces the global efficiency since the power losses of the resistive components are proportional to the squared current, and so for a given power rating, the higher the current is, the lower the global efficiency is. Moreover, the cabling can be a physical challenge in case of high-current levels. For these reasons, it is not recommendable to increase power by increasing current.

- A voltage increase: it requires either using power semiconductors from an upper voltage class or connecting in series several power semiconductors to withstand high voltage values. However, upper voltage class power semiconductors entail higher cost, higher switching timing, lower switching frequency and heavier, bigger and more expensive grid filter. On the other hand, the series connection could seriously affect to the system reliability since a uniform blocking voltage distribution among the power semiconductors must be guaranteed, even during transitions.

Therefore, it is very difficult for a single 2L-B2B topology to achieve acceptable performance with the available switching devices for the largest WECS, even though having the cost advantage [13]. Instead, multilevel converters enable a power increase without increasing neither current nor blocking voltage of the power semiconductors. Thus, multilevel converters are interesting and popular candidates in WECS above 3 MW in order to get a cost-effective design. In fact, according to some researchers, it is time for the multilevel converters to take the lead since it is becoming a mature and well-known technology [15], [18].

## 1.3.1. Multilevel Converter Concept

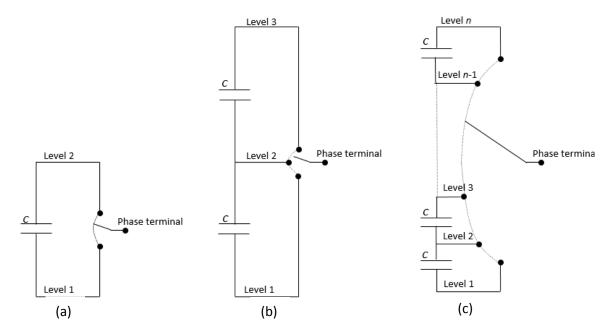

The essence of the multilevel concept is to use multiple voltage levels in the power conversion process. Fig. 1.9 shows a functional schematic of a converter leg with different number of levels. Fig. 1.9(a) corresponds to the conventional 2L case, Fig. 1.9(b) corresponds to the 3L case and Fig. 1.9(c) to an *n*-level case.

The immediate advantage of the multilevel converters is that the switching devices must not withstand the full dc-link voltage, and so it is possible to either use lower-voltage-rated power semiconductors with the same dc-link voltage or use the same power semiconductors with higher dc-link voltage. Hence, increasing the output power with the available power semiconductors is conceivable using multilevel converters.

Fig. 1.9. Functional schematic of a converter leg with different number of levels. (a) Two levels. (b) Three levels. (c) n levels.

#### 1.3.2. Comparison of 2L versus 3L Power Converters

In the following, a qualitative comparison between the global performance of 2L and 3L converters is presented, supported by previous investigations [19], [20].

Besides enabling larger output power, the 3L converter has additional advantages:

- Efficiency: For the same output power and dc-link voltage, the 3L converter shows a better global efficiency than the 2L converter since lower-voltage-rated semiconductors can be used. The main advantage of the lower-voltage-rated semiconductors resides in the reduction of the switching losses by a factor between 3 and 5 for contiguous semiconductor classes [19]. Instead, there is no great advantage in conduction losses. Thus, the higher the switching frequency is, the higher the efficiency increase of the 3L converter compared to the 2L case is.

- ac filter: The higher the number of levels is, the lower the total harmonic distortion is.

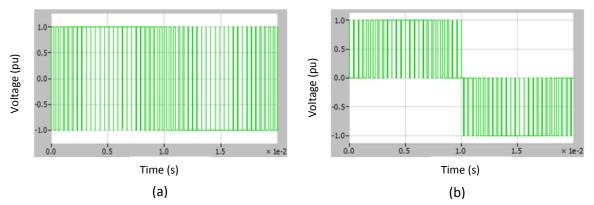

Fig. 1.10 shows a comparison of the output phase voltage waveform with reference to the midpoint of the dc-link of a 2L converter (Fig. 1.10(a)) and 3L converter (Fig. 1.10(b)).

The harmonic distortion in the 3L converter is clearly lower. This implies a great saving in cost, weight and size of the ac filter.

- Common mode voltage: The 3L converter produces a much smaller common-mode voltage. The value depends on the operating point and modulation strategy. For the conventional sinusoidal pulse width modulation, a reduction of the common-mode voltage of roughly 25%–30% can be achieved by the 3L converter [19].

- dv/dt filter: Transient over-voltages caused by the pulse-width modulation switching operation are a major concern for generators connected with long cables. The generator can suffer a full reflection and the voltage pulse amplitude would approximately double. With a 3L converter, the maximum voltage pulse is reduced a 50% compared to the 2L converter. Moreover, as the switching losses are lower in a 3L converter, the dv/dt could be reduced further by increasing the switching time, and so this issue would be even more mitigated. A potential avoidance of the dv/dt filter could justify the increased switching losses.

In terms of cost and reliability, the 3L converter could seem less reliable and more expensive than the 2L converter, because of the higher number of switching devices. However, on one hand, the thermal performance of the 3L converters could lead to lower device temperatures due to lower switching losses, providing a higher reliability. On the other hand, the higher cost of switching devices could be compensated by a reduced ac and dv/dt filter and a more inexpensive cooling system. That is to say, it is not clear if the 3L converter is more expensive and less reliable than a 2L converter. There are several reasons that can lead 3L converters to present lower cost and higher reliability in spite of having more switching devices.

Fig. 1.10. Comparison of output phase voltage waveforms with reference to the midpoint of the dc-link. (a) Two level inverter. (b) Three level inverter.

Multilevel converters have mainly been focused on high power or medium voltage applications, but thanks to their great advantages, they are also starting to be competitive in low-voltage applications [19].

#### 1.3.3. Multilevel Converter Topologies

For completeness and better understanding of the advances in multilevel technology, it is necessary to cover classic multilevel converter topologies, which are:

- Cascaded H-bridge.

- Flying capacitor.

- Diode clamped.

In the following sections, these three classic multilevel topologies are reviewed.

#### 1.3.3.1. Cascaded H-Bridge Topology

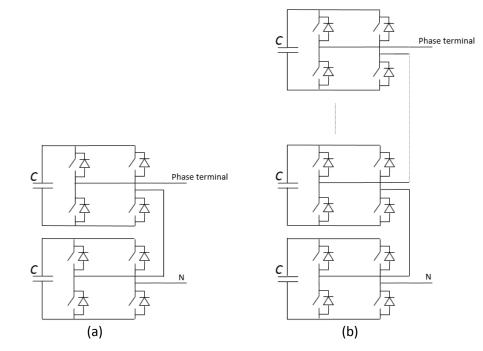

Multilevel converter technology started in the late 1960s with the introduction of the multilevel stepped voltage waveform using series-connected H-bridges, which is also known as the cascaded H-bridge topology [21]. Fig. 1.11 presents this topology. Fig. 1.11(a) depicts two series-connected H-bridges, which generates five output levels and Fig. 1.11(b) depicts the general case with *n* H-bridge inverters, which generates 2n+1 levels.

Fig. 1.11. Cascaded H-bridge topology. (a) Two H-bridges leg topology. (b) n H-bridges leg topology.

The cascaded H-bridge topology is well suited for high-power applications because of the modular structure, which enables higher voltage operation with classic low-voltage semiconductors [15]. However, the main drawback in WECS applications of this topology is that it requires an isolated and independent dc-source for each cell.

## 1.3.3.2. Flying Capacitor Topology

The cascaded H-bridge topology was closely followed by the development of a flying capacitor topology the same year [22]. Fig. 1.12 presents this topology. Fig. 1.12(a) corresponds to the 3L case and Fig. 1.12(b) to the 5L case.

The flying capacitor topology has found less industrial penetration compared to the other two classic multilevel topologies. It is mainly due to the following drawbacks [14], [15]:

- High switching frequencies are required to keep the capacitors properly balanced.

- Initial charging process of the flying capacitor voltages is required.

- The flying capacitors are a limiting factor for the converter lifetime.

Fig. 1.12. Flying capacitor multilevel topology. (a) Three-level leg topology. (b) Five-level leg topology.

#### 1.3.3.3. Diode-Clamped Topology

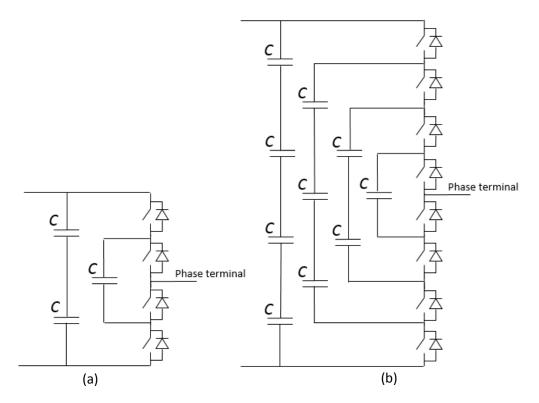

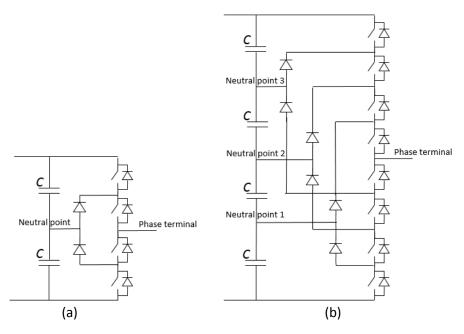

In the late 1970s, the multilevel diode-clamped concept was introduced [23]. Then, this concept evolved into the three-level neutral-point-clamped (3L-NPC) topology [24]. Fig. 1.13 shows the diode-clamped topology. Fig. 1.13(a) corresponds to the 3L case and Fig. 1.13(b) corresponds to the 5L case.

Among the multilevel topologies, the 3L-NPC is the most widely used in high power applications [25]. It is mainly thanks to its simple implementation and proper performance compared to other topologies.

However, the NPC has the next two technical drawbacks:

- The voltage values of the dc-link capacitors have to be balanced, but with the use of conventional modulation strategies, voltage balancing cannot be guaranteed for certain operating conditions. This has been an important problem of the NPC topology for a long time [26]. Nevertheless, researchers have proposed different solutions modifying the control and modulation strategies [27]-[33] and currently this problem could be considered as solved.

- 2. The power losses are unevenly distributed among the switching devices. Thus, the NPC output power capability is limited by the thermal performance of the most stressed switching device, which depends on the operating point. There is a great deal of literature about this issue [6], [7], [12]-[14], [25], [34]-[44]. Unfortunately, this drawback cannot be avoided since it is an intrinsic issue in the NPC topology. However, some investigations have focused on mitigating this downside through the proposal of specific modulation methods under low-voltage ride-through conditions that lead to a more uniform thermal performance in a 3L-NPC [45].

#### **1.3.3.4.** Recent ac-ac Multilevel Converter Topologies for WECS

A large number of investigations have focused on proposing and analyzing new ac-ac power converter topologies for WECS which are reviewed in the following [14], [46].

#### 1.3.3.4.1. Three-Level H-Bridge (3L-HB) Topology

3L-HB consists of two H-bridges per phase, one per converter side, sharing the dc-link capacitor, as Fig. 1.14 depicts. The main upsides of 3L-HB are as follows:

Fig. 1.13. Diode-clamped multilevel topology. (a) Three-level leg topology. (b) Five-level leg topology.

Fig. 1.14. Three-level H Bridge (3L-HB).

- Isolated dc-sources are not required.

- Three levels per phase voltage are achieved with very few power semiconductors.

- The topology is based on very well-known and mature technology (2L converters).

However, the topology requires an open winding transformer and generator, and so double cable length is required, which increases the cost.

## 1.3.3.4.2. Five-Level H-Bridge (5L-HB) Topology

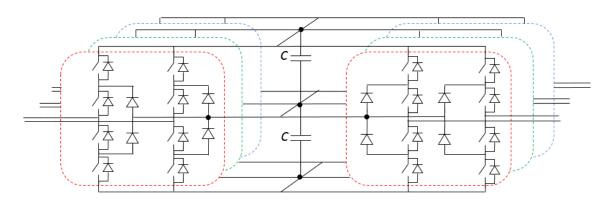

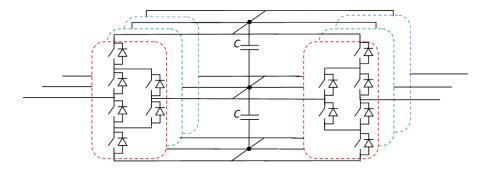

5L-HB consists of two H-bridges per phase, one per converter side, sharing the dc-link capacitor, and based on 3L-NPC converter, as Fig. 1.15 depicts. Thus, this topology is a hybrid configuration between the 3L-HB and the 3L-NPC. The main advantage is that five levels are achieved but the number of power semiconductors considerably increases. Moreover, this topology preserves the disadvantages from both 3L-NPC and 3L-HB:

Fig. 1.15. Five-level H Bridge (5L-HB).

- Open winding transformer is required in the grid side, which is more expensive and bulky than standard transformers.

- Open winding generator is also required.

- Double cable length is required, increasing the cost.

- The voltage balancing of the dc-link capacitors must be controlled by a proper modulation strategy and control.

- The power losses are unevenly distributed among the switching devices, limiting the converter output power capability.

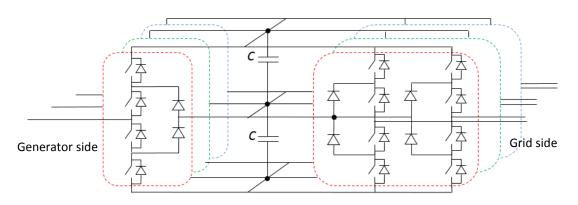

## 1.3.3.4.3. Three-Level NPC + Five-Level H-Bridge (3L-NPC + 5L-HB) Topology

This topology was developed since the power quality requirements in a WECS are much stricter in the grid side than in the generator side. Therefore, a 3L-NPC is selected for the generator side and a 5L-HB for the grid side (Fig. 1.16), in order to adapt the topology to the unsymmetrical power quality requirements. The total harmonic distortion of the grid side is lower since five output levels are achievable. Moreover, this topology avoids requiring an open winding generator and double cable length in the generator side.

Fig. 1.16. Three-level NPC + Five-level H Bridge (3L-NPC + 5L-HB).

## 1.3.3.4.4. Neutral Point Pilot (NPP) Topology

24

The NPP concept was first introduced in 1977 [47]. Instead of clamping the neutral point through diodes, it is done by bidirectional switches, as depicted in Fig. 1.17. This provides a controllable current path for the neutral point connection. In the upper and lower parts of the converter leg, two switches in series can be placed in order to get higher voltage rating. However, this topology does not offer freedom to distribute the switching power losses among the power semiconductors.

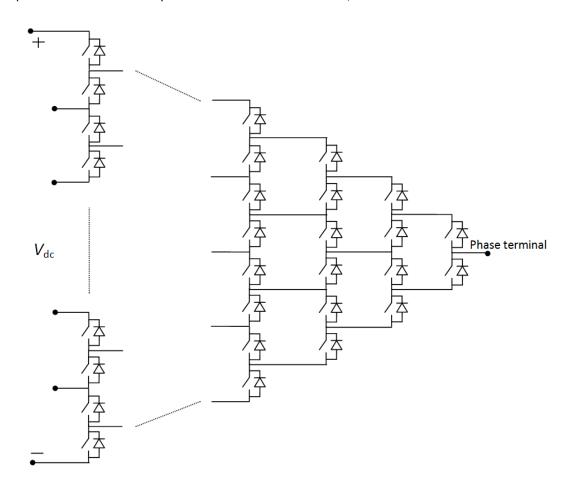

#### 1.3.3.4.5. Modular Multilevel Topology

Another multilevel converter that has recently found industrial application is the modular multilevel converter (MMC), especially in dc-ac conversion applications, and particularly for High-Voltage Direct-Current (HVDC) systems [15]. This topology is quite recent since it was developed in the early 2000s. Basically, the MMC is composed of several series-connected cells, typically consisting of a 2L half bridge and a capacitor, as Fig. 1.18 depicts. The phase leg is divided into two equal arms, each including an inductor.

The two switching devices of a cell are controlled by complementary signals. They can either bypass or connect the cell capacitor. However, an appropriate voltage balance control is necessary to keep each capacitor at the desired voltage level.

The attractive feature of this topology is its modularity and scalability to easily reach medium and high-voltage levels, as well as greatly improving the power quality compared to the classic series connection of power switches in a 2L converter configuration used in HVDC.

Fig. 1.17. Three-level Neutral Point Pilot (NPP) topology.

Fig. 1.18. Modular multilevel converter (half bridge).

#### 1.3.3.4.6. Active Neutral-Point-Clamped (ANPC) Topology

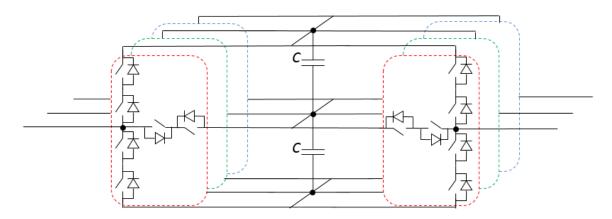

This topology was proposed in 2005 [34] in order to solve one of the major drawbacks of the NPC: the uneven power losses distribution among the power semiconductors. The 3L-ANPC replaces the clamping diodes by switching devices with antiparallel diodes to provide a controllable path for the neutral current (Fig. 1.19). Hence, 3L-ANPC is able to offer certain freedom to control the loss distribution among the power semiconductors of the converter. Thanks to that, the thermal performance is more uniform and the output power capability is enhanced, compared to the conventional 3L-NPC. Several investigations have focused on analyzing the 3L-ANPC advantages and performance [25], [34]-[43], [48].

Fig. 1.19. Three-level Active-Neutral-Point-Clamped (3L-ANPC) topology.

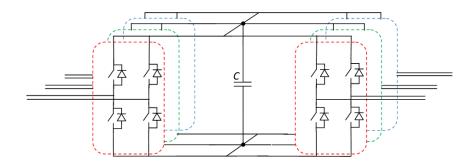

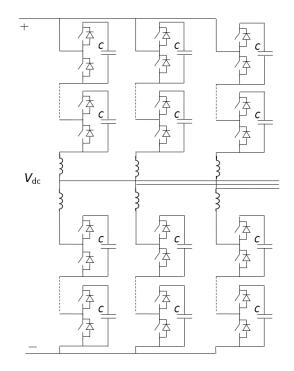

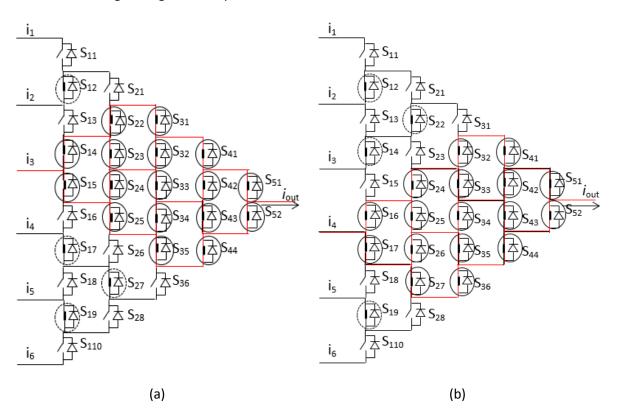

A hybrid topology combining the 3L-ANPC with a flying capacitor topology has been proposed to extend the number of output voltage levels [15]. However, the flying capacitors require an initial charging process, a voltage balancing strategy, and can reduce the system reliability, leading to low power converter lifetime. Therefore, [49] introduces an extension of the 3L-ANPC topology to any number of levels without flying capacitors. This generalized topology, known as multilevel active-clamped (MAC) topology is shown in Fig. 1.20. The leg consists of one output terminal and *n* input terminals where *n* is the number of converter levels. A capacitor or dc-voltage source is connected across every two adjacent input terminals, being the dc-voltage of each of those components typically the same ( $V_{dc}/(n-1)$ ).

## 1.4. Power Converter Reliability in WECS

26

The current availability of onshore wind turbines is approximately 98-99 % due to a frequent service and fast repair in case of failure. However, this cannot be maintained in offshore

Fig. 1.20. Multilevel active-clamped converter leg topology (n-level leg) [49].

applications due to reduced accessibility [50]. Offshore wind farms have a difficult and limited access, which leads to a high maintenance cost after a failure [6], [7] and [51]. Therefore, reliability must be seriously considered and will become a critical design criterion for the next generation of wind power converters [13], since the power converter plays a significant role in the most common WECS failures. In fact, a 17.5% of the WECS failures and the 14.3% of the WECS downtime are due to problems with the power converter according to [52].

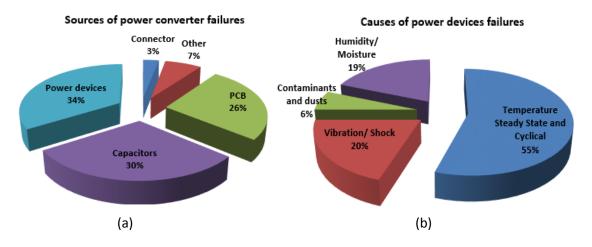

The most critical point in the power converter reliability is the thermal performance of the power semiconductors [7], [12]. The thermal performance is determined by the maximum junction temperature and the maximum junction temperature variation. Analysis of power converter failures conclude that more than one third is due to failures in the power devices, and a 55% of the power devices failures is due to the thermal performance [53] and [54], as Fig. 1.21 shows. Therefore, minimizing the thermal stress of the power semiconductors is an interesting challenge for future WECS.

Regarding the power converter reliability, 3L-NPC is not the most suitable topology due to the uneven power losses distribution among the switching devices, leading to mediocre thermal performance. Moreover, this issue does not only affect the power converter reliability, but also its power capability. Thus, some investigations [25], [34]-[43] have focused on the 3L-ANPC instead of the 3L-NPC in order to enhance the reliability and output power of the power converter. The results of these investigations confirm that either the output power capability can be increased between 20 and 30% or the switching frequency can be increased around 85% thanks to a more uniform thermal performance among the power semiconductors. Furthermore, the 3L-ANPC also improves

Fig. 1.21. (a) Sources of power converter failures. (b) Causes of power devices failures. [54].

the converter fault-tolerant capability compared to the 3L-NPC [42], [55]. Thus, the 3L-ANPC seems to be the natural evolution of the 3L-NPC for the next generation of WECS.

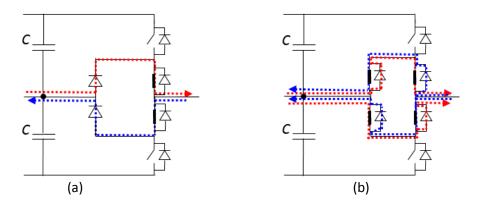

## 1.5. 3L-ANPC Operating Principle

As mentioned before, the 3L-ANPC offers certain freedom to distribute the power losses among the power semiconductors. In the 3L-ANPC, the possible paths to connect to the neutral point are doubled compared to the conventional 3L-NPC, as Fig. 1.22 depicts. Fig. 1.22(a) shows the paths to connect to the neutral point for the 3L-NPC and Fig. 1.22(b) for the 3L-ANPC. As can be seen, 3L-NPC only has one path to connect to the neutral point for a positive current and another one for a negative current. Instead, the 3L-ANPC has two paths to connect to the neutral point for a positive current and two more for a negative current. Thus, 3L-ANPC requires an operating principle to define which path must be taken to connect to the neutral point during the switching transitions. The main 3L-ANPC operating principles are reviewed in the following.

#### 1.5.1. Active Loss Balancing [34]

Active loss balancing is based on the online calculation of the junction temperatures of each power semiconductor. A power loss model and a thermal model must be defined and implemented in the power converter control. From phase currents, dc-link voltage and cooling water temperature, the power converter control is able to estimate the junction temperature of each power semiconductor. Accordingly, the connection to the neutral point is performed through the path with the coldest power semiconductor, in order to avoid heating even more the most stressed devices. However, real time junction temperature estimation requires a very fast digital controller and a considerably complex implementation.

Fig. 1.22. Paths to connect to the neutral point. (a) 3L-NPC. (b) 3L-ANPC.

#### 1.5.2. Feed-Forward Loss Balancing [36]

Feed-forward loss balancing is based on the offline calculation of the junction temperatures of each power semiconductor. The aim is the same as the active loss balancing operating principle, but the junction temperatures for all relevant operating points are calculated offline by computer simulations instead of real time calculation. Thus, the implementation is much simpler since the optimal ratios among the paths to connect to the neutral point are stored in a look-up table depending on the modulation index and power factor. However, the main drawback of this operating principle is that it is not suitable for fast transients, abnormal load conditions, and nonexpected operating points.

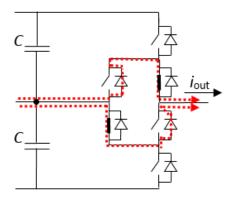

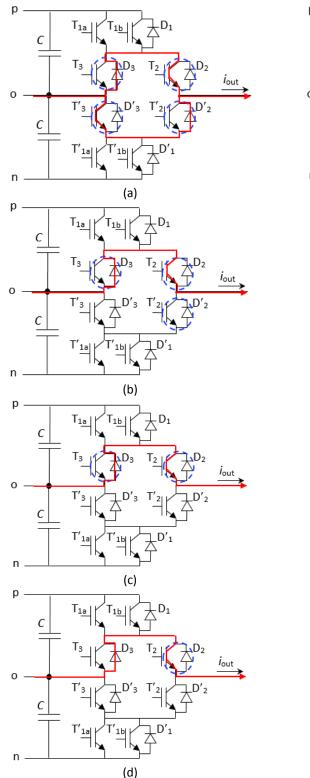

#### 1.5.3. Multilevel active-clamped operating principle [49]

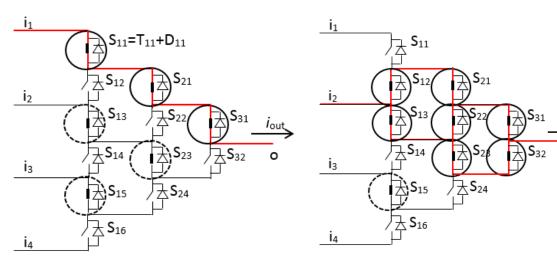

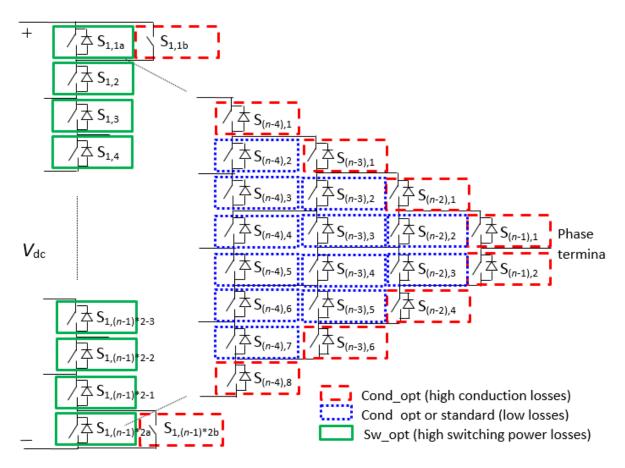

This operating principle, defined for a topology with any number of levels, consists on enabling all possible parallel current paths to connect to the inner dc-link points. In a 3L-ANPC topology, the two possible paths to connect to the neutral point are enabled. That is, four switching devices are turned on when a connection to the neutral point is required, as shown in Fig. 1.23. This leads to a reduction of the conduction losses, since the equivalent resistance of the connection to the neutral point is lower than in the case with only one path enabled.

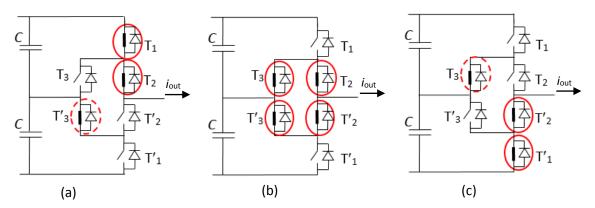

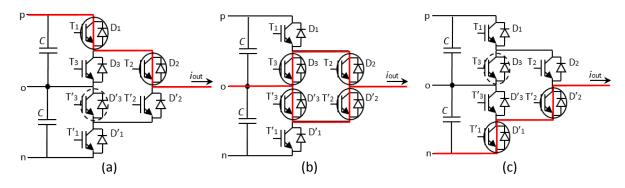

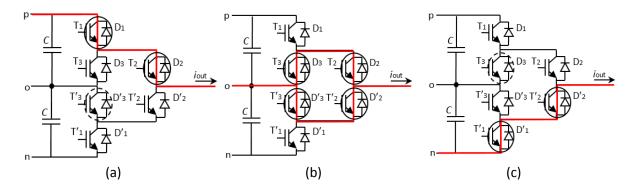

Fig. 1.24 shows the switching states in the particular case of a 3L converter leg. The uncircled switches are off-state devices. The circled switches are on-state devices. The solid-line circled switches connect the output terminal to the desired input terminal conducting the output current. The dotted-line circled switches do not conduct any significant current and simply clamp

Fig. 1.23. Neutral point connection with the multilevel active-clamped operating principle (i<sub>out</sub> > 0).

the blocking voltage of the off-state devices. Fig. 1.24(a) depicts the connection to the positive voltage level in which  $T_1$ ,  $T_2$ , and  $T'_3$  are on-state devices. However,  $T'_3$  does not conduct any significant current and just ensures a proper blocking voltage distribution between  $T'_1$  and  $T'_2$ . Fig. 1.24(b) depicts the connection to the neutral point in which  $T_2$ ,  $T_3$ ,  $T'_2$ , and  $T'_3$  are on-state devices in order to minimize the conduction power losses. Fig. 1.24(c) depicts the connection to the neutral point are on state devices. However,  $T_3$  does not conduct any negative voltage level in which  $T'_1$ ,  $T'_2$ , and  $T_3$  are on state devices. However,  $T_3$  does not conduct any significant current and just ensures a proper blocking voltage distribution between  $T_1$  and  $T_2$ .

On the other hand, the timing of the switching transitions can be adjusted to distribute some switching losses among the devices. For example, the switching steps for the transition from positive voltage level to the neutral point are:

- $1. \quad T_1 \, turn \, off$

- $2. \quad T'_2 \text{ and } T_3 \text{ turn on }$

If  $i_{out} < 0$ , switching losses will mainly concentrate on the first device turning on. Adjusting the timing of the control signals for T'<sub>2</sub> and T<sub>3</sub>, switching losses can be concentrated on either T'<sub>2</sub> or T<sub>3</sub>.

Similarly, the switching steps for the transition from the neutral point to the positive voltage level are:

- 1.  $T'_2$  and  $T_3$  turn off

- $2. \quad T_1 \, turn \, on$

Fig. 1.24. Switching states of a 3L-ANPC converter leg using the multilevel active-clamped operating principle. (a) Connection to the positive voltage level. (b) Connection to the neutral point. (c) Connection to the negative voltage level.

If  $i_{out} < 0$ , switching losses will mainly concentrate on the last device turning off. Adjusting the timing of the control signals for T'<sub>2</sub> and T<sub>3</sub>, switching losses can be concentrated on either T'<sub>2</sub> or T<sub>3</sub>.

An analogous timing adjustment can be done for the transitions between the neutral point and the negative voltage level, allowing the distribution of some switching losses among  $T_2$  and  $T'_3$ .

This topology will be the subject of study of the present thesis.

### **1.6.** Thesis objective

Following the trend of the current state of the art to define a feasible solution for the next generation of a WECS, the general objective of the proposed thesis is to determine enhanced design guidelines for dc-ac grid-connected 3L-ANPC power converter, focused on improving its reliability and electrical performance.

More specifically, the goals can be listed as follows:

- Propose hardware design guidelines for the dc-ac grid-connected 3L-ANPC power converter within WECS operating range to improve the converter thermal performance and electrical performance. These design guidelines will primarily consist on selecting the most suitable semiconductor device or combination of devices for each position in the power converter.

- Define the most suitable switching pattern for the proposed 3L-ANPC power converter to distribute evenly the power losses among the devices, leading to a better reliability and electrical performance. The switching pattern determines the timing of all gate signals.

- Exhaustive analysis of the proposed 3L-ANPC, comparing the power loss and thermal performance to the conventional 3L-NPC and 3L-ANPC topologies.

- Experimental verification of the previous contributions for the specific case of a threelevel power converter.

- Extend the previous contributions to multilevel active-clamped converters with any number of levels.

# 1.7. Thesis outline

The thesis is organized as follows.

Chapter 2 defines the proposed hardware contributions for a dc-ac grid connected 3L-ANPC power converter within WECS operating range to improve the converter reliability and electrical performance. In this chapter, the definition of the typical WECS operating range and the detailed explanation of the electro-thermal model are also introduced. The electro-thermal model has been used to obtain simulation results for the development of the present thesis.

Chapter 3 contains the contributions to the switching pattern for the proposed dc-ac grid connected 3L-ANPC power converter to distribute evenly the power losses among the devices, leading to a better reliability and electrical performance.

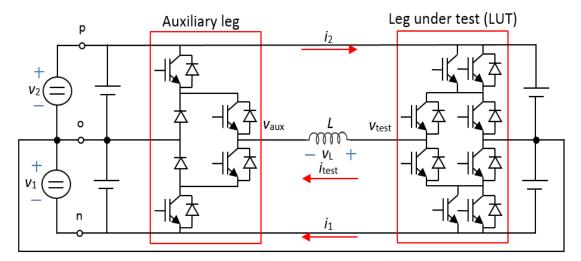

Chapter 4 focuses on the development of a prototype to validate the previous contributions through experiments. Additionally, the used electro-thermal model is also validated by comparison to the experimental results, and a silicon area analysis of the proposed 3L-ANPC power converter compared to the conventional solutions is performed.

Chapter 5 extends the proposed contributions for the specific case of a three-level power converter to the generic case of an *n*-level power converter.

The thesis is concluded in Chapter 6, in which possible future extensions of the work accomplished are proposed.

# CHAPTER 2

# ENHANCED POWER DEVICE CONFIGURATION AND OPERATION OF A GRID-CONNECTED INVERTER FOR WIND ENERGY CONVERSION SYSTEMS

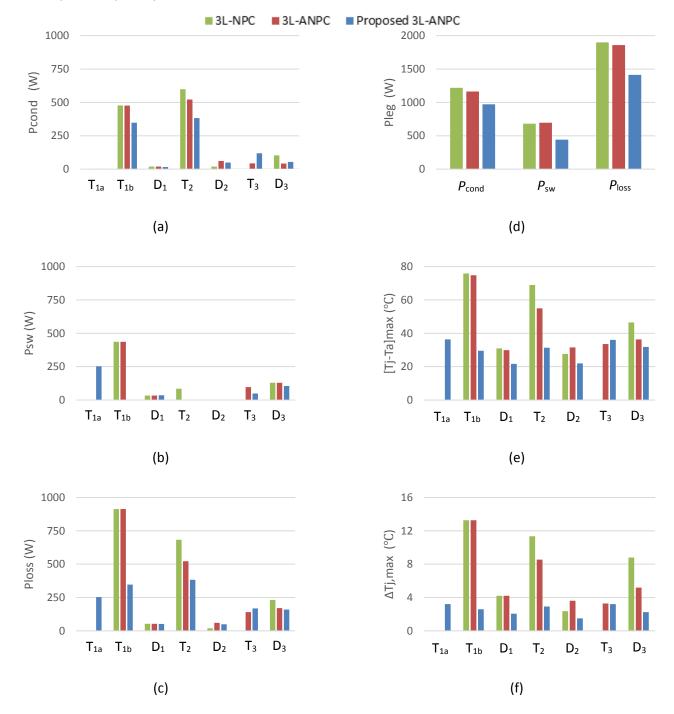

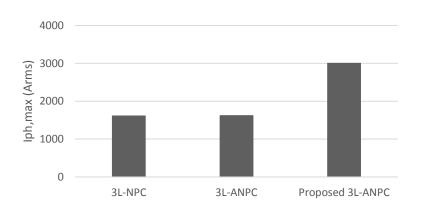

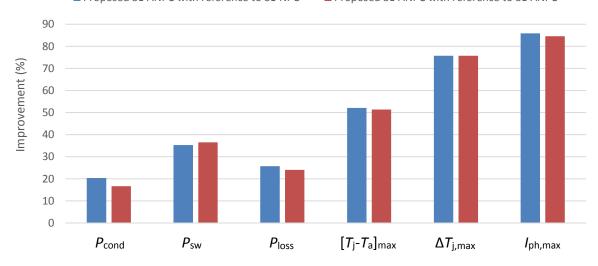

Abstract — This chapter presents new design guidelines for a dc-ac grid-connected 3L-ANPC inverter to force that each device mainly withstands either switching or conduction power losses. Then, the most suitable device is selected for each position, enabling a significant improvement in power loss distribution, thermal performance, converter efficiency and output power capability. A 2 MW WECS is simulated, reaching a reduction of around 25% in power losses, a reduction of 50% in maximum junction temperature increase above ambient temperature, a reduction of 75% in maximum junction temperature variation, and an increase of around 85% in converter output power rating, compared to the conventional 3L-NPC and the 3L-ANPC.

#### 2.1. Introduction

Multilevel converters enable a cost-effective design and they are becoming popular candidates for the largest WECS. In fact, the 3L-NPC topology has high penetration in the market of large WECS. However, it offers an uneven power loss distribution, which limits the output power capability. Instead, the 3L-ANPC replaces the clamping diodes by switching devices with antiparallel diodes to provide a controllable path for the neutral-point current. Hence, the 3L-ANPC is able to offer certain freedom to distribute the power losses among the power semiconductors. This chapter presents novel 3L-ANPC design and operation guidelines to improve the converter output power capability, efficiency, and thermal performance, within a typical operation range of a grid-connected dc-ac converter for WECS. The proposed contributions are verified by simulation of a three-phase grid-connected inverter for a 2 MW WECS.

This chapter is organized as follows. Section 2.2 presents the selected 3L-ANPC operating principle and details the switching transitions. Section 2.3 defines new design guidelines for the power device configuration and operation. Section 2.4 presents the considered WECS operating points. Section 2.5 introduces the electro-thermal model used for simulation. This model is also used in the following chapters. Section 2.6 verifies the proposed contributions by simulation of a three-phase grid-connected inverter for a 2 MW WECS. Finally, Section 2.7 outlines the conclusions.

## 2.2. 3L-ANPC Operating Principle

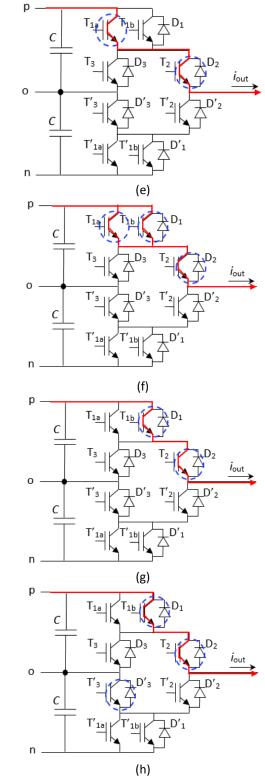

The selected 3L-ANPC operating principle is the multilevel active-clamped, introduced in [49]. Fig. 2.1 presents the corresponding three switching states for the 3L-ANPC inverter to connect the output terminal to the three possible dc-link points. The uncircled switches are off-state devices. The circled switches are on-state devices. The solid-line circled switches connect the output terminal to the desired input terminal and conduct the output current ( $i_{out}$ ), depicted in red. The dotted-line circled switches simply clamp the blocking voltage of the off-state devices. In Fig. 2.1(b), it can be observed that the connection of the output terminal to the neutral point presents two paths to conduct the output current, which leads to a reduction of the conduction losses compared to the conventional approach of applying only one path.

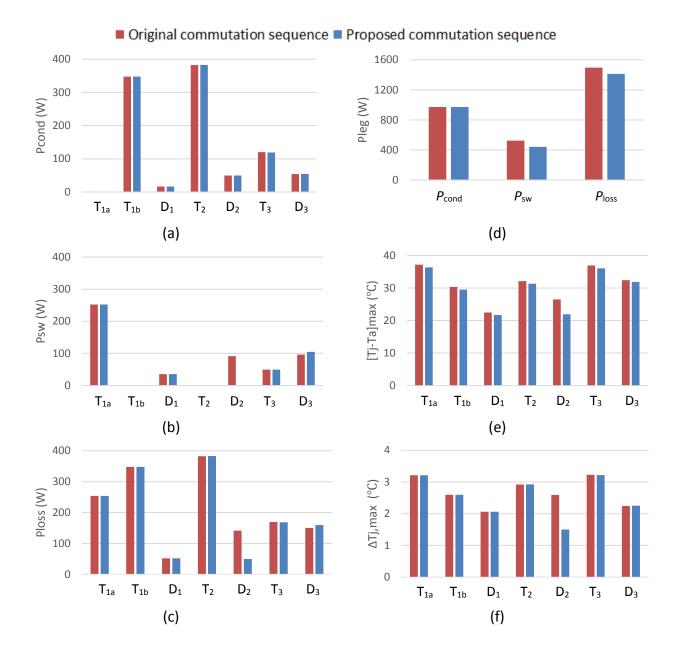

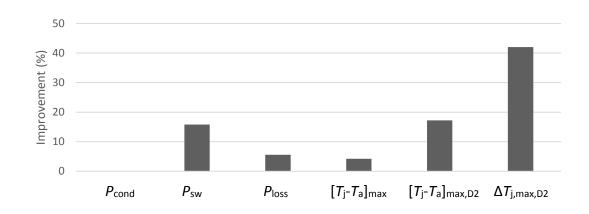

Each transition between adjacent switching states (between SS<sub>1</sub> and SS<sub>2</sub> or between SS<sub>2</sub> and SS<sub>3</sub>) requires changing the state of three switches. Depending on the direction of the current flow and the specific switching transition, switching losses will concentrate on the last switch turned off or on the first switch turned on (and associated diodes turning off). Table 2.1 summarizes the different cases. Thus, whenever losses have to be concentrated in switch pairs T<sub>2</sub>-T'<sub>3</sub> or T'<sub>2</sub>-T<sub>3</sub>, by properly delaying one of the control signals in the switch pair, switching losses will be concentrated on only one of the switches in the pair. For example, delaying one of the control signals of T<sub>2</sub> or T'<sub>3</sub> in the transition from SS<sub>3</sub> to SS<sub>2</sub> with  $i_{out} > 0$ , switching losses will be concentrated on the first switch turned on, releasing from switching losses the last switch turned on since no significant voltage is blocked during switching. As an additional example, delaying one of the concentrate on the last switch turned off, releasing from switching losses the first switch turned off, releasing from switching losses the first switch turned off since no significant voltage is blocked during switching.

Fig. 2.1. ANPC leg switching states. (a) SS<sub>1</sub>. (b) SS<sub>2</sub>. (c) SS<sub>3</sub>.

| Case | İ <sub>out</sub> | Switching transition      | Devices concentrating<br>switching losses |

|------|------------------|---------------------------|-------------------------------------------|

| 1    | +                | $SS_1 \rightarrow SS_2$   | T1                                        |

| 2    | +                | $SS_2 {\rightarrow} SS_1$ | $T_1 + D'_2 + D_3$                        |

| 3    | +                | $SS_2 \rightarrow SS_3$   | T <sub>2</sub> -T′ <sub>3</sub>           |

| 4    | +                | $SS_3 {\rightarrow} SS_2$ | $T_2-T'_3 + D'_1$                         |

| 5    | -                | $SS_1 {\rightarrow} SS_2$ | $T'_2 - T_3 + D_1$                        |

| 6    | -                | $SS_2 \rightarrow SS_1$   | T′2-T3                                    |

| 7    | _                | $SS_2 \rightarrow SS_3$   | $T'_1 + D_2 + D'_3$                       |

| 8    | _                | $SS_3 \rightarrow SS_2$   | Τ'1                                       |

Table 2.1. Devices concentrating switching losses under the possible switching transitions.

## 2.3. Proposed 3L-ANPC Design Guidelines

For a given voltage rating, the design of power semiconductor devices involves trade-offs. Low conduction losses can be achieved at the expense of degrading the switching performance, and vice versa. This leads to the availability of devices optimized for conduction (cond\_opt), devices optimized for switching (sw\_opt) and standard devices trading the conduction and switching performance (standard).

If a power device within a converter topology suffers both significant conduction and switching power losses, the most reasonable choice is to select a standard device. However, the resulting conduction power losses would increase compared to a device optimized for conduction, and the resulting switching losses would increase compared to a device optimized for switching, leading to a low conversion efficiency. In addition, this device could be a potential candidate to be the most stressed device in the topology, limiting the converter power rating.

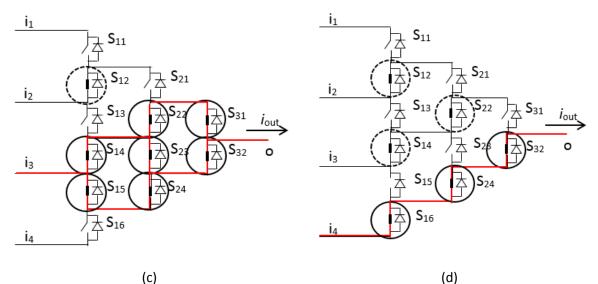

In light of the previous discussion, a design and operation of the 3L-ANPC leg allowing each device in the topology to mainly withstand only conduction or switching losses, would allow selecting an optimized device for the intended operation, leading to increased converter efficiency and power rating. This is the goal of the following proposed operation and design guidelines. The operation of a dc-ac grid-connected inverter for WECS usually requires high modulation indexes, because the dc-link voltage level is not much higher than the grid peak voltage. This implies that the inverter legs are connected to dc-link points 'p' and 'n' longer than to neutral point 'o'. This leads to substantial conduction losses in devices  $T_2$  and  $T'_2$  and low conduction losses in  $T_3$  and  $T'_3$ . Therefore, using the freedom to distribute some switching losses on certain devices provided by the topology, it is proposed to concentrate the switching losses on  $T_3$  and  $T'_3$ , through adding proper delays to the corresponding control signals. This will leave  $T_2$  and  $T'_2$  to only withstand conduction losses, while  $T_3$  and  $T'_3$  mainly withstand switching losses.

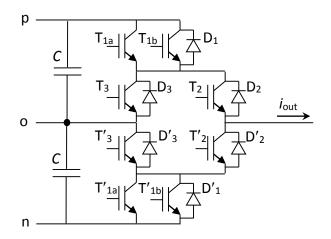

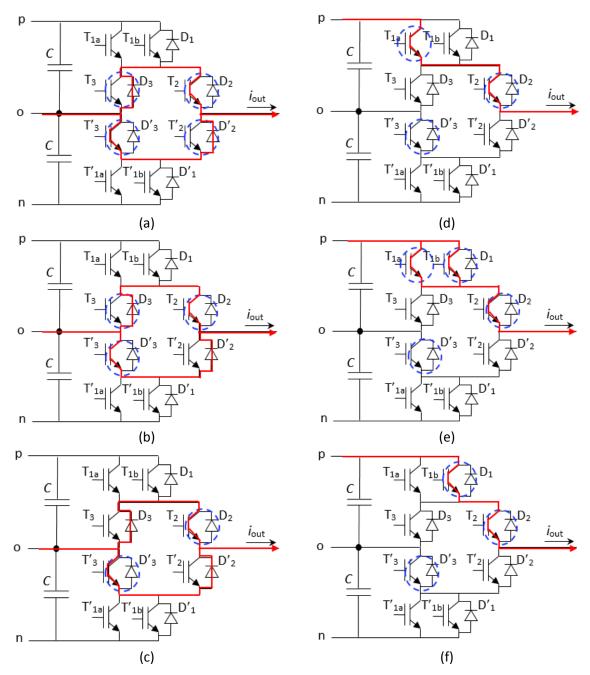

Devices  $T_1$  and  $T'_1$  will suffer significant conduction losses under high modulation indexes. In addition, they also suffer significant switching losses which are unavoidable because the selected operating principle does not allow deviating these losses to other devices. Therefore, as shown in Fig. 2.2, it is proposed to double the number of devices in these two positions. Then, through a suitable gate control signal pattern for  $T_{1a}$  and  $T_{1b}$ , it is possible to force that  $T_{1a}$  mainly withstands switching losses, while device  $T_{1b}$  mainly withstands conduction losses.

With the above design guidelines, no device withstands both significant conduction and switching losses and the device selection can be performed according to Table 2.2 (only half of the leg topology is specified due to symmetry). The D<sub>1</sub> workload is not significant since the power factor is typically close to unity in WECS application. Devices optimized for switching could be based on SiC.

Fig. 2.2. Proposed 3L-ANPC converter leg.

36

| Device reference | Device type |  |

|------------------|-------------|--|

| T <sub>1a</sub>  | Sw_opt      |  |

| T <sub>1b</sub>  | Cond_opt    |  |

| <b>D</b> 1       | Standard    |  |

| T <sub>2</sub>   | Cond_opt    |  |

| D <sub>2</sub>   | Cond_opt    |  |

| T3               | Sw_opt      |  |

| D3               | Sw_opt      |  |

|                  |             |  |

Table 2.2. Optimal power semiconductor selection

under the proposed design guidelines.

According to Table 2.2, device  $T_{1a}$  is optimized for switching and device  $T_{1b}$  is optimized for conduction. Fig. 2.3(a) shows a proposed gate control signal pattern of this pair of devices with reference to the original gate control signal of device  $T_1$  ( $s_{T1}$ ). Device  $T_{1b}$  control signal ( $s_{T1b}$ ) is approximately equal to the original device  $T_1$  control signal. Instead, device  $T_{1a}$  control signal ( $s_{T1a}$ ) turns on a small time prior to a switching transition of device  $T_{1b}$ , and turns off slightly later. This leads device  $T_{1a}$  to mainly withstand switching losses, while device  $T_{1b}$  mainly withstands conduction losses. If the conduction performance of  $T_{1a}$  is considerably worse than  $T_{1b}$  and device  $T_{1a}$  is not critical from a thermal point of view, a simpler alternative control strategy is depicted in Fig. 2.3(b). This way, again, device  $T_{1a}$  would mainly withstand switching losses would be slightly lower than using the gate pattern depicted in Fig. 2.3(a).

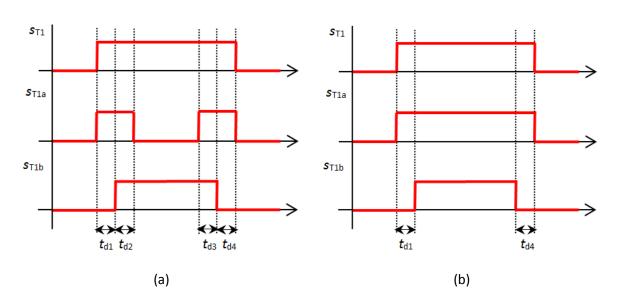

# 2.4. WECS Operating Points

WECS power curve defines the generated power as a function of the wind speed. From a certain cut-in wind speed, around 3 m/s, the WECS starts the power generation. As the wind speed increases, the generated power also increases. However, from certain wind speed, around 12 m/s, WECS reaches the rated power rating and the power generation is limited by controlling the blade angles. Fig 2.4 shows a typical WECS power curve, depicting the per unit active power as a function of the wind speed.

Fig. 2.3. Gate control signals of devices  $T_{1a}$  and  $T_{1b}$  with reference to the original gate control signal of device  $T_1$  (s = 1: ON; s = 0: OFF). (a) Gate control signal pattern 1. (b) Gate control signal pattern 2.

Fig. 2.4. WECS active power as a function of wind speed.

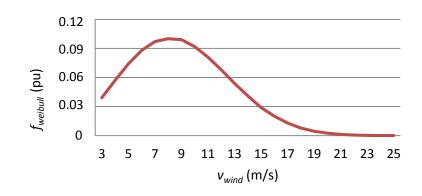

The Weibull distribution, which is widely used for wind applications [56]-[60], defines the probability for each wind speed. The Weibull distribution is defined in (2.1), where  $f_{weibull}$  is the per unit amount of time for each wind speed, k is the shape parameter and c is the scale parameter. For the development of this thesis, k = 2.5 and c = 10 have been selected. Fig 2.5 depicts the used Weibull distribution, according to the selected parameters.

$$f_{weibull} = \frac{k}{c} \cdot \left(\frac{v_{wind}}{c}\right)^{k-1} \cdot e^{\left(-\left(\frac{v_{wind}}{c}\right)\right)^k}$$

(2.1)

Fig. 2.5. Weibull distribution (k = 2.5 and c = 10).

Combining the WECS power curve and the Weibull distribution, the list of WECS operating points with their corresponding weight is represented in Table 2.3. All simulation studies will consider all the operating points and weights of Table 2.3, which allows having an accurate and complete view of the WECS behavior.

The dc-ac grid-connected inverter for WECS is designed to operate with high modulation indexes. It allows optimizing the size of the dc-link and the voltage rating of the semiconductors. Moreover, a unity power factor is desired in order to optimize the power generation. However, the operating power factor is reduced under grid over-voltage and under-voltage conditions to compensate the grid voltage fluctuations. Therefore, it is assumed that for each operating point

| Wind speed [m/s] | Converter active power<br>[pu] | Weight [pu] |

|------------------|--------------------------------|-------------|

| 3                | 0.02                           | 0.04        |

| 4                | 0.05                           | 0.059       |

| 5                | 0.1                            | 0.076       |

| 6                | 0.17                           | 0.091       |

| 7                | 0.28                           | 0.1         |

| 8                | 0.42                           | 0.103       |

| 9                | 0.59                           | 0.102       |

| 10               | 0.76                           | 0.095       |

| 11               | 0.94                           | 0.084       |

| 12-25            | 1                              | 0.25        |

Table 2.3. List of WECS operating points with their corresponding weight.

specified in Table 2.3, the converter operates at rated grid voltage with unity power factor for 50% of the time, at maximum grid voltage with minimum power factor for 25% of the time, and at minimum grid voltage with minimum power factor for the remaining 25% of the time.

## 2.5. Electro-Thermal Model

A converter electro-thermal model has been developed in PLECS [61] and it computes the instantaneous junction temperature of each power semiconductor, from the device power loss information and ambient temperature. The model is also used for simulation results in the following chapters and it is verified in chapter 4 by comparison to experimental results.

#### 2.5.1. Power Loss Model

The model computes both conduction and switching power losses of each power semiconductor from datasheet information at a junction temperature of 125  $^{\circ}$ C. Therefore, the model does not include the dependence of power losses with the junction temperature.

Conduction losses are calculated as the device forward voltage drop (as a function of the forward current) times the forward current. Switching loss is linearly scaled according to the ratio of the semiconductor blocking voltage and forward current to the corresponding loss information value provided in the datasheet. A proper amount of points is taken to properly approximate the datasheet data, considering linear interpolation. Thus, the switching transitions are considered instantaneous and the loss energy is taken from a look-up table depending on the forward current and the blocking voltage in the switching event. Finally, diode turn-on loss is neglected.

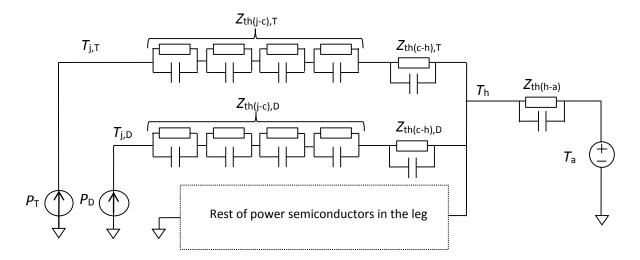

#### 2.5.2. Thermal Model

The thermal model computes the instantaneous junction temperature of each power semiconductor from the power losses and the ambient temperature ( $T_a$ ).

A single heatsink per converter leg is assumed. Fig. 2.6 shows the converter thermal model for one leg. The thermal impedance from junction to case ( $Z_{th(j-c),T}$  for the switch and  $Z_{th(j-c),D}$  for the diode) is defined by a Foster model of four elements in the datasheet. The thermal impedance from case to heatsink ( $Z_{th(c-h),T}$  for the switch and  $Z_{th(c-h),D}$  for the diode) is defined from datasheet information and consists of a thermal resistance in parallel with a relatively high thermal capacitance, forcing almost constant case temperature in steady state. The thermal

40

impedance from heatsink to ambient ( $Z_{th(h-a)}$ ) is defined according to the recommended values of IPOSIM (online software developed by Infineon [62]) for a typical water-cooled heatsink for the selected power modules. It consists of a thermal resistance in parallel with a very high thermal capacitance, forcing constant heatsink temperature in steady state. The considered thermal resistance from heatsink to ambient is 2.67 K/kW.

The heatsink temperature  $(T_h)$  is calculated from the total leg power losses  $(P_{leg})$  as

$$T_{\rm h} = T_{\rm a} + P_{\rm leg} \cdot Z_{\rm th(h-a)} \tag{2.2}$$

Finally, junction temperatures ( $T_{j,T}$  for the switch and  $T_{j,D}$  for the diode) are calculated from the junction to case and case to heatsink thermal impedances, the heatsink temperature and the respective total power losses of each power semiconductor ( $P_T$  for a switching device and  $P_D$  for a diode) as

$$\begin{bmatrix} T_{j,T} \\ T_{j,D} \end{bmatrix} = [T_h] + \begin{bmatrix} P_T \cdot (Z_{th(j-c),T} + Z_{th(c-h),T}) \\ P_D \cdot (Z_{th(j-c),D} + Z_{th(c-h),D}) \end{bmatrix}$$

(2.3)

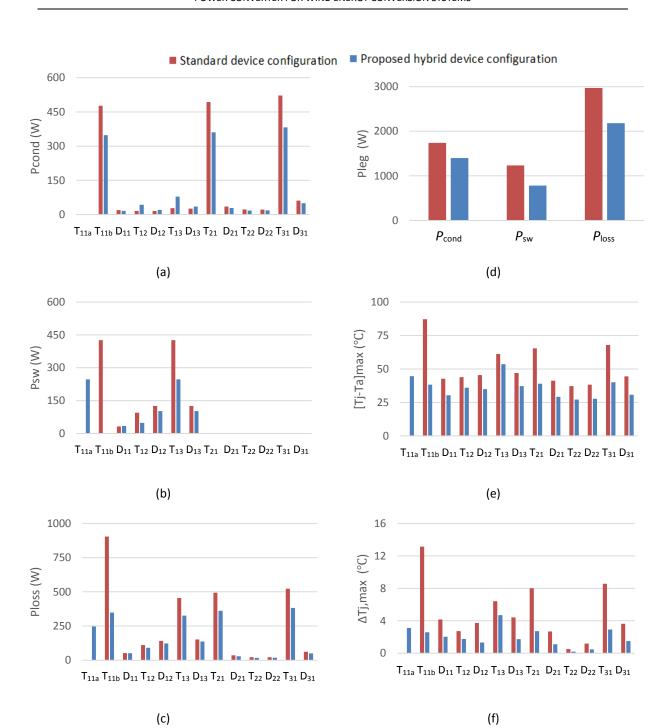

#### 2.6. Simulation Results

This section compares the performance of a conventional 3L-NPC, a conventional 3L-ANPC, and the proposed 3L-ANPC designs through a simulation in a 2 MW WECS based on a

*Fig. 2.6. Converter leg thermal model with detail for a switch and a diode.*

three-level three-phase grid-connected inverter. The electro-thermal model detailed in the previous section is used to simulate the WECS behavior. The main system parameters are summarized in Table 2.4.

In the three designs compared (conventional 3L-NPC, conventional 3L-ANPC, and proposed 3L-ANPC) the same operating principle [49] and modulation strategy [30] are used to produce a fair comparison. The selected pulse width modulation strategy guarantees capacitor voltage balancing in every switching cycle for all possible converter operating conditions, which allows a significant reduction of the dc-link capacitance. Table 2.5 presents the commercial devices selected for each converter position in each design. The selected power modules are commercial 1200 V IGBTs with antiparallel diode from Infineon [62]. The conventional 3L-NPC and 3L-ANPC designs use a module (FZ1800R12HE4\_B9) with balanced conduction and switching characteristics, while the proposed 3L-ANPC design uses two modules, one with good switching performance (FZ800R12KS4\_B2) and another one with good conduction performance (FZ3600R12HP4).

| Parameter                                | Value                |

|------------------------------------------|----------------------|

| Rated active power                       | 2 MW                 |

| dc-link voltage                          | 1500 V               |

| Rated grid line-to-line voltage          | 900 V <sub>rms</sub> |

| Grid voltage fluctuation                 | $\pm$ 10%            |

| Rated grid current                       | 1300 Arms            |

| Rated converter grid-side power factor   | 1                    |

| Minimum converter grid-side power factor | 0.87                 |

| Grid frequency                           | 50 Hz                |

| Switching frequency                      | 2.5 kHz              |

| Ambient temperature                      | 50 °C                |

Table 2.4. Main WECS inverter parameters.

| Device                           | Conventional 3L-NPC             | Conventional 3L-ANPC | Proposed 3L-ANPC |

|----------------------------------|---------------------------------|----------------------|------------------|

| T <sub>1a</sub>                  |                                 |                      | FZ800R12KS4_B2   |

| T <sub>1b</sub> + D <sub>1</sub> | FZ1800R12HE4_B9                 | FZ1800R12HE4_B9      | FZ3600R12HP4     |

| T <sub>2</sub> + D <sub>2</sub>  | FZ1800R12HE4_B9                 | FZ1800R12HE4_B9      | FZ3600R12HP4     |

| T3 + D3                          | FZ1800R12HE4_B9<br>(diode only) | FZ1800R12HE4_B9      | FZ800R12KS4_B2   |

Table 2.5. Commercial devices selected for each design.

Table 2.6 illustrates the switching and conduction performance of the selected devices, according to datasheet information. The comparison for the three devices is referred to the particular case of a junction temperature of 125 °C and 1500 A.  $V_{CE}$  and  $V_F$  indicate the conduction performance, and correspond to the voltage drop during on-state for IGBT and diode, respectively.  $E_{SW\_IGBT}$  and  $E_{SW\_DIODE}$  indicate the switching performance, and correspond to the whole switching energy during turn on and turn off for the IGBT and the switching energy during turn off for the diode (diode turn on losses are neglected). As can be observed, the standard device FZ1800R12HE4\_B9 offers a trade-off performance between the device optimized to switch and the device optimized to conduct. Therefore, switching power losses of FZ1800R12HE4\_B9 are lower than the switching power losses of FZ3600R12HP4, which is a device optimized to conduct, but higher compared to the switching power losses of FZ800R12KS4\_B2, which is a device optimized to switch. The opposite is observed when comparing the conduction power losses.

| Device          | <i>V</i> <sub>CE</sub> (V) | Esw_igbt (mJ) | <i>V</i> <sub>F</sub> (V) | Esw_diode (mJ) |

|-----------------|----------------------------|---------------|---------------------------|----------------|

| FZ1800R12HE4_B9 | 1.85                       | 499           | 1.6                       | 137            |

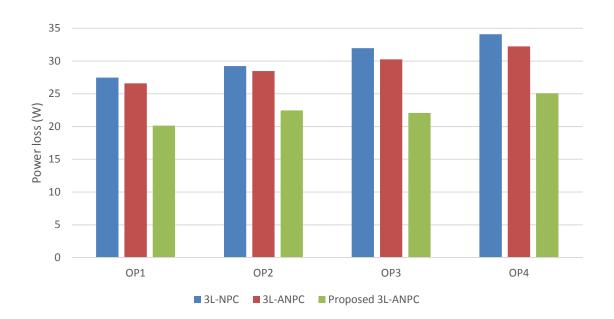

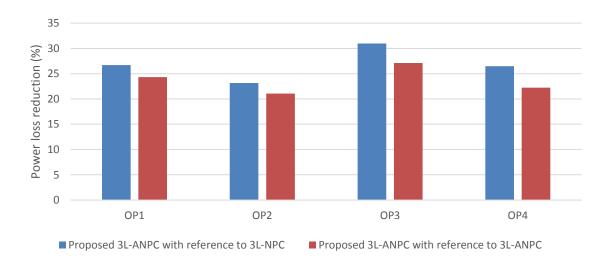

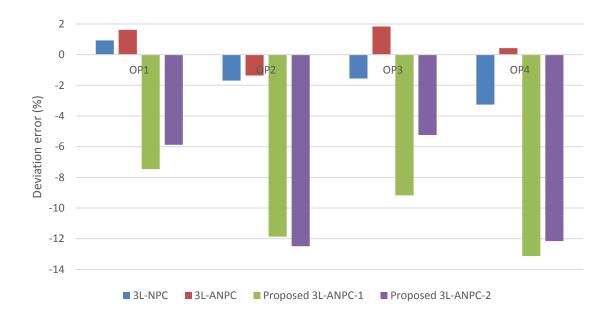

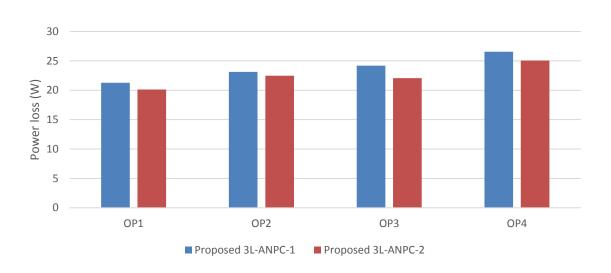

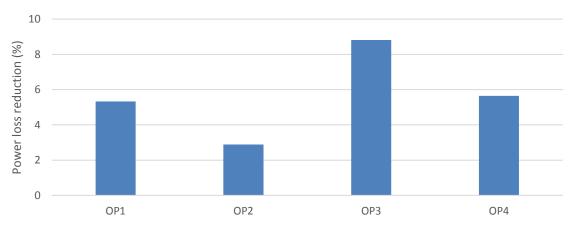

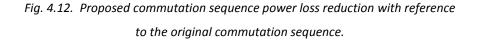

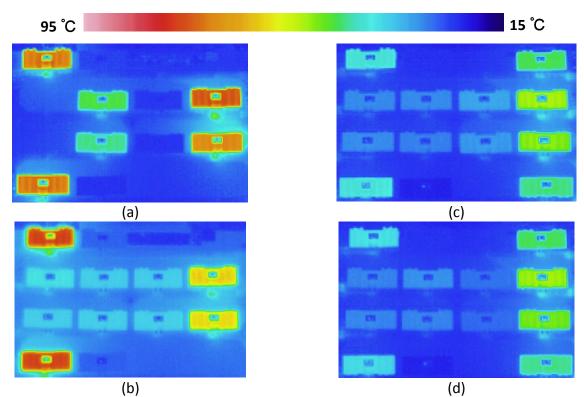

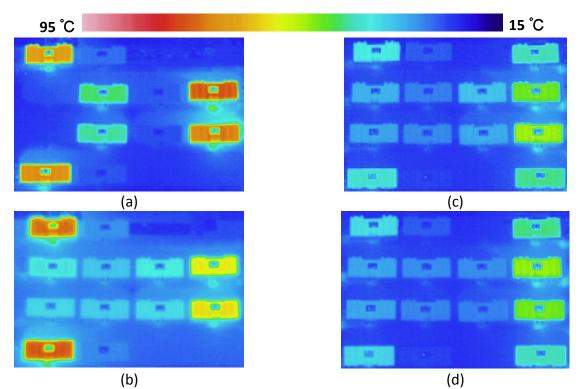

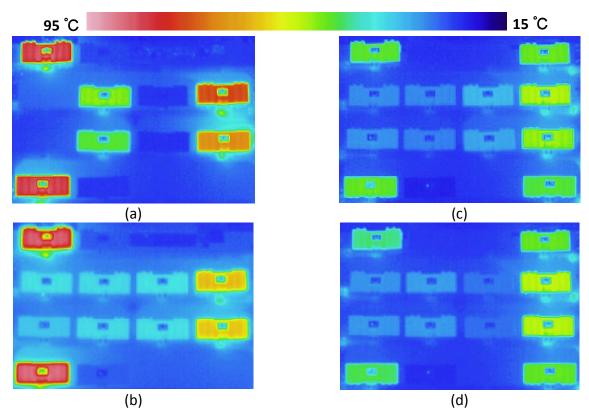

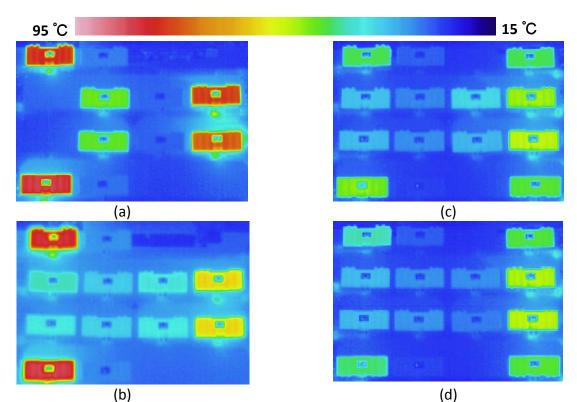

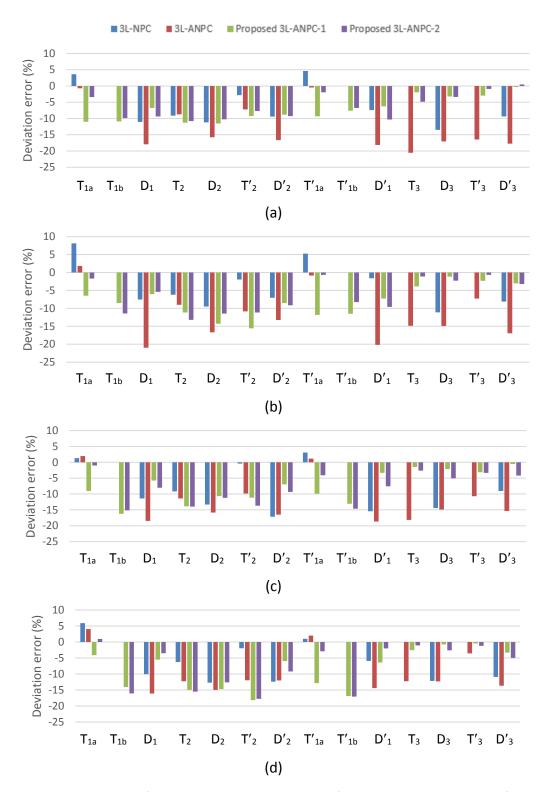

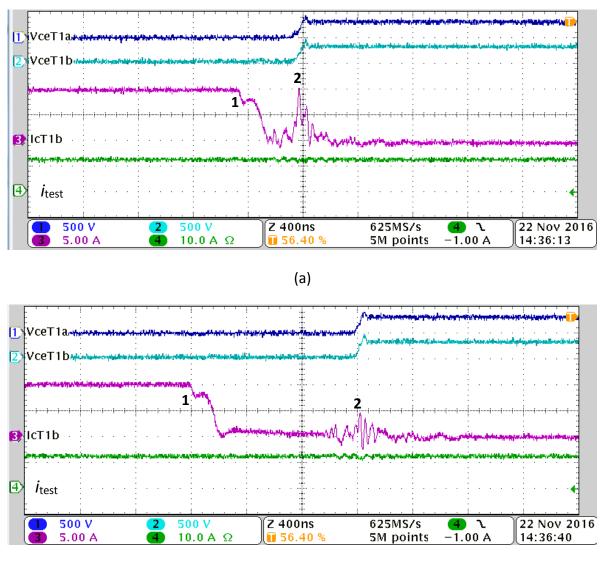

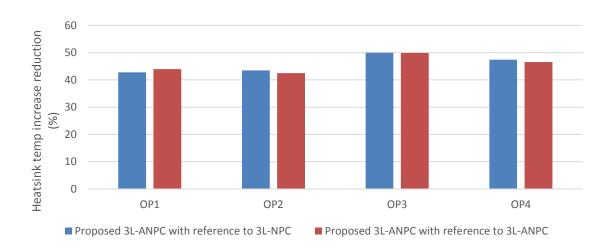

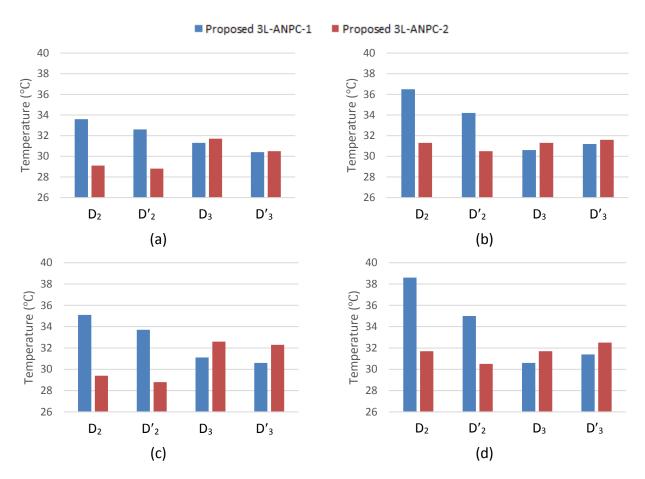

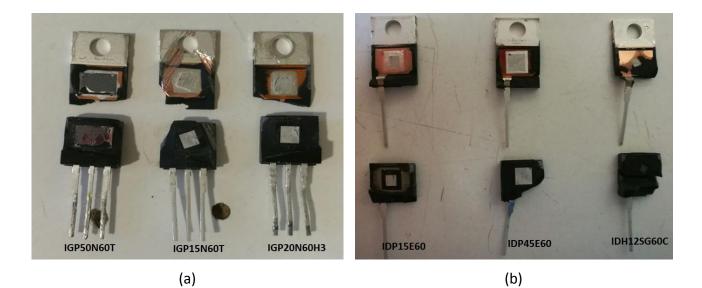

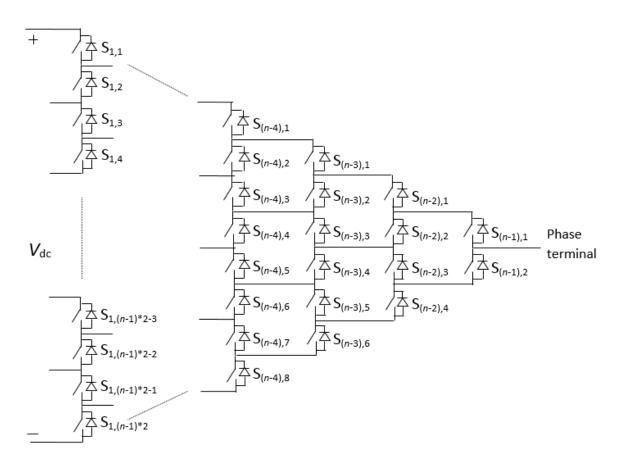

| FZ800R12KS4_B2  | 5.4                        | 325           | 2.15                      | 76             |