## TREBALL DE FI DE GRAU

# Grau en Enginyeria Electrònica Industrial i Automàtica

# DIGITAL SYSTEM FOR SPIKING NEURAL NETWORK EMULATION

**Report - Cost Estimation - Annexes**

**Autor:** Eduard-Guillem Merino Mallorquí

**Director:** Jordi Cosp Vilella

**Departament** Enginyeria Electrònica (EEL)

Convocatòria: Juny 2017

## **Abstract**

The present project is about the design, simulation and an experimentational test of a digital system in a single chip able to emulate the behavior of spiking neural networks, which is possible thanks to the use of mathematical models that emulate the behavior of these networks in the brain. A modular system has been proposed in order to provide the necessary flexibility and scalability for the simulation of different neural networks. At the same time the most flexible, simple and efficient option has been chosen in order to have a good performance without losing or reducing the necessary accuracy and exactitude for the emulation of the neural networks. The solution has been implemented by making use of different combinational blocks and totally synchronous flip-flops from a 100 MHz clock signal, besides, the description of the system was performed by using the high-level hardware description language VHDL. Finally, a neural network for pattern recognition has been implemented on a programmable logical device FPGA in order to demonstrate the correct operation of the digital system.

i

## Resum

El present projecte tracta en el disseny, simulació i test experimental d'un sistema digital en un sol xip capaç d'emular el comportament de xarxes neuronals d'impulsos, el qual és possible gràcies al ús de models matemàtics que emulen el comportament d'aquestes xarxes en el cervell. S'ha plantejat un sistema modular per tal de dotar-lo de la flexibilitat i escalabilitat necessària per a la realització de diferents xarxes neuronals. Alhora s'ha buscat la opció més simple i alhora eficient per tal de disposar d'un bon rendiment d'aquesta sense perdre o disminuir la precisió i exactitud necessària per a la emulació de les xarxes neuronals. La solució ha estat implementada fent ús de diferents blocs combinacionals i biestables totalment síncrons a partir d'un senyal de rellotge de 100 MHz, a més, la descripció del sistema s'ha realitzat mitjançant el llenguatge de descripció hardware d'alt nivell (VHDL). Finalment, per demostrar el correcte funcionament del sistema digital s'ha realitzat una xarxa neuronal per al reconeixement de patrons, la qual s'ha implementat sobre un dispositiu lògic programable FPGA.

### Resumen

El presente proyecto trata el diseño, simulación y test experimental de un sistema digital en un solo chip capaz de emular el comportamiento de redes neuronales de impulsos, el cual es posible gracias al uso de modelos matemáticos que emulan el comportamiento de estas redes en el cerebro. Se ha planteado un sistema modular para dotarlo de la flexibilidad y escalabilidad necesaria para la realización de diferentes redes neuronales. A la vez se ha buscado la opción más simple y a la vez eficiente para disponer de un buen rendimiento de esta sin perder o disminuir la precisión y exactitud necesaria para la emulación de las redes neuronales. La solución ha sido implementada haciendo uso de diferentes bloques combinacionales y biestables totalmente síncronos a partir de una señal de reloj de 100 MHz, además, la descripción del sistema se ha realizado mediante el lenguaje de descripción hardware de alto nivel (VHDL). Finalmente, para demostrar el correcto funcionamiento del sistema digital se ha realizado una red neuronal para el reconocimiento de patrones, la cual se ha implementado sobre un dispositivo lógico programable FPGA.

# **Acknowledgements**

First and foremost, I have to thank my thesis supervisor Jordi Cosp. Without his assistance and dedicated involvement in every step throughout the process, this project would have never been accomplished.

I am also grateful to Electronic Engineering Department, for providing me with all the necessary facilities for the development of this project.

Last but not the least, I would like to thank my family: my mother Marta and my sister Mireia for helping me and supporting me whenever I needed it.

# Index

| ABS | TRAC | Г                                                  |    |

|-----|------|----------------------------------------------------|----|

| RES | UM_  |                                                    | 11 |

| RES | UMEN | l                                                  |    |

| ACK | NOW  | LEDGEMENTS                                         | v  |

| 1.  |      | RODUCTION                                          |    |

|     |      | Project scope                                      |    |

|     | 1.2. | Objectives                                         | 2  |

|     | 1.3. | Biological background                              | 2  |

|     |      | 1.3.1. Neural Networks                             | 2  |

| 2.  | ART  | IFICIAL NEURAL NETWORKS                            | 7  |

|     | 2.1. | Threshold Logic Unit                               | 8  |

|     | 2.2. | Multilayer Perceptron                              | 9  |

|     | 2.3. | Spiking Neural Networks                            | 10 |

| 3.  | PRE  | LIMINARY STUDY OF ALTERNATIVES                     | 13 |

|     | 3.1. | Bluehive                                           | 13 |

|     | 3.2. | One million neuron single-FPGA neuromorphic system | 14 |

|     | 3.3. | SNAVA                                              | 15 |

| 4.  | SPIK | ING NEURAL NETWORKS                                | 17 |

|     | 4.1. | Neural models                                      | 17 |

|     |      | 4.1.1. Integrate-and-Fire model                    | 17 |

|     |      | 4.1.2. Hodgkin-Huxley model                        |    |

|     |      | 4.1.3. Izhikevich model                            |    |

|     | 4.2. | Neuronal connectivity                              |    |

|     |      | 4.2.1. AER System                                  |    |

|     | 4.3. | Learning of neural networks                        |    |

|     |      | 4.3.1. Spike-Timing-Dependent Plasticity           | 23 |

| 5.  | DES  | GN AND IMPLEMENTATION OF A SNN                     | 25 |

|     | 5.1. | Izhikevich neuron                                  |    |

|     |      | 5.1.1. Model adaptation                            |    |

|     |      | 5.1.2. Design and architecture                     | 27 |

|                  |       | 5.1.3.  | Simulations                 | 31  |

|------------------|-------|---------|-----------------------------|-----|

|                  | 5.2.  | AER Sy  | ystem                       | 33  |

|                  |       | 5.2.1.  | Design and architecture     | 33  |

|                  |       | 5.2.2.  | Simulations                 | 35  |

|                  | 5.3.  | Spike-  | Timing-Dependent Plasticity | 36  |

|                  |       | 5.3.1.  | Design and architecture     | 36  |

|                  |       | 5.3.2.  | Simulations                 | 39  |

|                  | 5.4.  | SNN E   | mulation                    | 41  |

|                  |       | 5.4.1.  | Design and architecture     | 42  |

| 6.               | PAT   | TERN R  | RECOGNITION WITH A SNN      | 45  |

|                  | 6.1.  | Neura   | l network model             | 45  |

|                  | 6.2.  | Patter  | n recognition               | 46  |

|                  | 6.3.  | Trainir | ng method                   | 47  |

|                  | 6.4.  | FPGA    | implementation              | 49  |

|                  |       | 6.4.1.  | Inputs and outputs          | 49  |

|                  |       | 6.4.2.  | Design and architecture     | 50  |

|                  |       | 6.4.3.  | Simulations                 | 51  |

|                  |       | 6.4.4.  | Experimental results        | 57  |

| CON              | CLUS  | IONS_   |                             | 65  |

| cos <sup>.</sup> | T EST | IMATIC  | ON                          | 69  |

|                  |       |         |                             |     |

|                  |       |         |                             |     |

|                  | A1.   |         | Manual                      |     |

|                  | A2.   | Comp    | uter files                  | 81  |

|                  | Δ3    |         |                             | 113 |

# 1. Introduction

One of the current challenges for the scientific community is to understand how the brain works and being able to reproduce it elsewhere, whether biologically or electronically, with the same properties. This is an ongoing research which is evolving, but unlike the search for a time-travel device or faster-than-light travel, there is a solid evidence that such quest is possible since we are the perfect example of an intelligent system [1].

Motivated by biological discoveries, many scientists take an interest on a modern approach of artificial intelligence. Therefore, they are able to replicate the behavior of the brain it may be possible to achieve a system which can become aware and react to the world that it is surrounded by.

Combining experimental studies of the biological nervous systems, from either animals or humans, several mathematical models have been developed, on which researchers try to produce a model that is sufficiently accurate and has a computational efficiency. Nevertheless, because of the available computational capabilities of the current electronic devices, it is already possible to simulate those neural systems to even fifty thousand times faster than their biological counterparts [2].

The digital system presented in this project is based on the fundamental characteristics of a biological neural network, in order to perform several functions associated with the brain like reasoning, speech recognition, movement or visual processing. Thus, the focus of this project is to proportionate a modular, flexible and scalable digital system, which is able to simulate the behavior of an artificial neural network for different uses.

## 1.1. Project scope

This project consists about the design and physical implementation of a digital system that is able to emulate the behavioral characteristics of biological neural networks in order to perform several functions associated with the brain; like reasoning, speech recognition, movement or visual processing. To achieve it, three fundamental main modules have to be designed in order to obtain a fully functional neural network.

Firstly, a module that provides the simulation of the properties, characteristics and behavior of a single neuron using an accurate, but at the same time computationally efficient mathematical model which can be adapted for its further implementation into the digital system.

Secondly, a communication or transmission system that is able to manage all the information flow of the neural network between an undetermined number of neurons.

Additionally, a training algorithm is designed to provide a functionality to the neural network, such as; like speech, movement recognition or visual processing as stated above.

Finally, the interconnection between them with the correct configuration will allow the simulation of a neural network with the given functionality. Therefore, the final digital system of this project has to be a modular, flexible and scalable platform, to cover all of the possibilities that involve the simulation of a neural network.

## 1.2. Objectives

Next, the main goals set from the very beginning of the project are written below, they are the essential requirements for the design and implementation of the digital system:

- Collecting information about the functionality of a neural network and its different models.

- Studying different models of neural networks and their most important characteristics.

- Choosing the most flexible and efficient neural network model to implement.

- Designing the digital system for neural network simulation.

- Making the description of the digital system through the high-level language VHDL.

- Verifying of the correct operation of the design through functional simulations of the digital system for neural network simulation.

- Implementation of the digital system in a programmable logic device (FPGA) and corroboration of its functionality.

## 1.3. Biological background

The aim of this section is to provide enough biological background, in order to understand the functionality of the design presented in this project. Therefore, the behavior of a neuron is described in detail, as well as the operational and transmission characteristics of the information flow between the neurons of a biological neural network.

#### 1.3.1. Neural Networks

The brain is a very complex network with millions and millions of interconnected neurons which cooperate to efficiently process input signals in order to decide the required output action. Approximately every neuron sends its output signals to over 10.000 other neurons, thus complicates the flow of information. To put it mildly, we do not even understand the brain as well as we think. In fact, we do not totally understand the behavior of a single neuron [3].

Nevertheless, there is a rough concept of how neurons operate: neurons send out short pulses of electrical energy as signals, though only if they have received enough energy from pulses of other neurons. This simple mechanism has been translated to different mathematical models, so that it becomes possible to perform computer simulations of neurons.

#### 1.3.1.1. Neurons

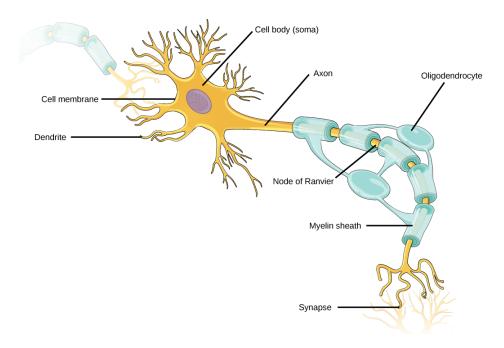

The specialized cells of the nervous system are the neurons, they are the structural and functional unit of the nervous system. Their main characteristic is the electrical excitability of their plasmatic membrane, along with their specialization in the reception of the stimuli and conduction of the nerve impulses between them [4].

The structure of the neurons can be diverse, but they have a common pattern, which can be distinguished into three main parts:

- The cell body or soma: the wider area, which forms the nucleus of the neuron and where there are all the organs that drive the cellular activity by the neuron.

- Dendrites: these are the extensions of the cell body which allow the connection with other neurons, as well as being responsible for receiving nerve impulses.

- Axon: a long and unique extension per neuron, which has the function of sending nerve impulses generated by the body cell to the next neuron.

Figure 1.1. Schematic drawing of a neuron [4].

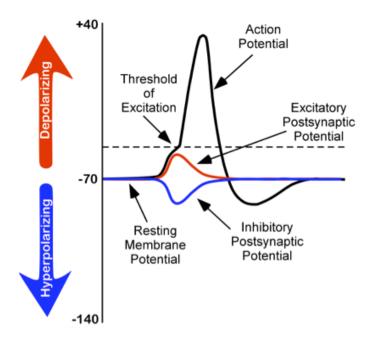

#### 1.3.1.2. Neural transmission

In a neural network, the information is transmitted by nerve impulses that cause polarity changes in the membranes of the cells and propagate through the neurons as if they were small electrical currents, ranging from dendrites and passing through the neural body until the axon. To make this communication between the neurons possible, they establish connections called synapses.

Initially, inside the neuron there are proteins and ions with negative charge. This difference in ion concentration produces a potential difference between the outside and inside of the membrane of the neuron. In fact, the usual value is about -70 mV [5].

Moreover, when a nerve impulse reaches a neuron which is at its resting state the membrane depolarizes, achieving the variation of the potential difference that presents the neuron. In the event that the depolarization causes enough variation in the membrane potential, it is said that the neuron has reached the action potential and thus generates a nerve impulse, always with the same intensity, which is transmitted to the next neuron.

It has to be noted, that the transmission of nerve impulses follows the law of all or nothing. This means that if the membrane depolarization does not reach a minimum potential, called the threshold potential, the impulse is not transmitted.

Figure 1.2. Evolution of the membrane potential of a neuron [5].

In addition, the post-synaptic impulses can be either positive or negative called, excitatory or inhibitory, respectively. One neuron receives about ten thousand potential synapses. Therefore, the sum of these potentials determines the value of polarization of the membrane of a neuron.

In short, as shown in Figure 1.2, if a neuron receives inhibitory potential, the polarization increases, however, if it receives an excitatory potential, the polarization of the membrane decreases. Only if the stimulus is sufficiently large, so that the depolarization reaches the threshold of excitation, the neuron sends a spike that is transmitted to the neural network. Then, the neuron enters into a short moment of rest, called the refractory period, in which it cannot send another spike again. Finally, the neuron will return to its initial state of rest if it does not receive more stimulus that perturbate its membrane potential charge.

## 2. Artificial Neural Networks

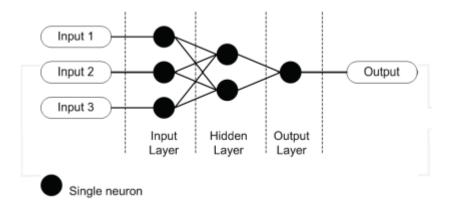

An artificial neural network (ANN) is a mathematical model that is based on the functionality of biological neural networks and thus, it can be defined as an emulation of biological neural systems. It is designed to produce and replicate the intelligent behavior, ANN's are at the vanguard of computational systems. Unlike the classical Artificial Intelligence approach, it intends to develop systems to directly simulate rational or logical reasoning, artificial neural networks aims lie at the reproduction of the underlying processing mechanisms that give a system its intelligence.

In order to take the full advantage of the artificial neural networks it is needed to interconnect the individual neural networks or its fundamental units, the neurons, in a topology that contributes to an easier, faster and more efficient problem solving. In the past, researchers have developed a series of "standardized" topographies of artificial neural networks that are suited for solving different types of problems. Therefore, after choosing the type of functionality that the neural networks need to offer, it is required to decide the appropriate topology and fine-tune it.

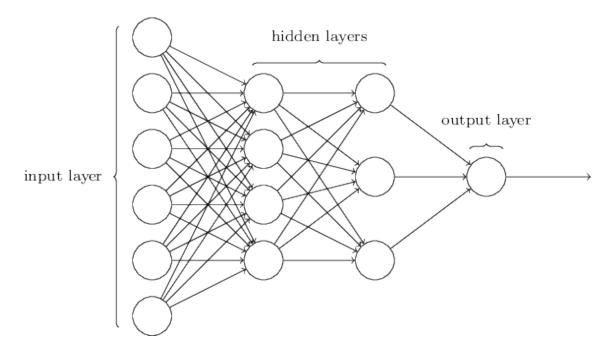

Figure 2.1. Example of a simple artificial neural network [6].

In addition, before using the neural network it is an indispensable condition to perform training to teach it problem solving. There are three major learning paradigms: supervised learning, unsupervised learning and reinforced learning. Even though these learning paradigms have their differences in their training methods they all have one thing in common: they train the neural network so it gives the desired output response in line with a series of input signals.

Some of the advantages of the artificial neural networks are [5]:

• It can be used to solve linear as well as non-linear programming tasks.

- If a component of an ANN fails, the net continues to operate (based on its highly parallel nature).

- A neural network learns and does not have to be re-programmed.

- An ANN can be used to solve classification, movement recognition or visual processing related problems.

On the other hand, the main cons of the artificial neural networks are:

- Most ANN's require a training phase to operate or function.

- As an ANN's architecture differs from microprocessors, they have to be simulated.

- Large ANN's require powerful hardware to run and accomplish reasonable execution times.

To sum up, artificial neural networks have been in use for some time now and their main application is in the field of robotics. They can be used to plan and direct the way of an autonomous vehicle, recognize obstacles or perform a classification of images. Essentially, artificial neural networks are capable of learning and generalizing from examples and experience to obtain solutions, and as its biological predecessor they are considered an adaptive system.

### 2.1. Threshold Logic Unit

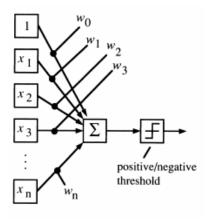

The fundamental unit of an artificial neural network is the neuron. The first computational model for neural networks was based on mathematics and algorithms, which was the Threshold Logic Unit [7], developed by Warren McCulloch and Walter Pitts in 1943.

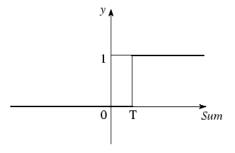

$$\varphi(v) = \begin{cases} 1, & v \ge 0 \\ 0, & v < 0 \end{cases}$$

(Eq. 2.1)

As shown in equation 2.1, the output of a neuron takes on the value of 1 if the total internal activity level of that neuron is nonnegative and otherwise 0. This statement describes the all-or-nothing property of the McCulloch-Pitts model.

Figure 2.2. Threshold activation function [7].

Additionally, the Threshold Logic Unit model of a neuron is simple yet has substantial computing potential and a precise mathematical definition. Nevertheless, it is so simple that the weight and threshold values are fixed.

## 2.2. Multilayer Perceptron

The simplest form of an artificial neural network used for the classification of patterns, which are linearly separable, is the perceptron. The single-layer perceptron consists of a single McCulloch-Pitts neuron with adjustable synaptic weights and threshold. Such network is only able to perform pattern classification with only two classes [9].

Figure 2.3. Single-layer perceptron [9].

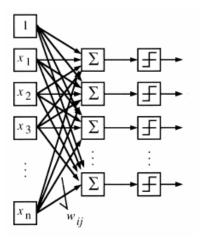

In order to perform more complex functions, several single-layer perceptron can be combined to obtain a neural network of multilayer perceptron as shown in figure 2.4.

Figure 2.4. Multilayer perceptron [9]

When the perceptrons were invented, many researchers speculated that the intelligent systems could be developed out of perceptrons. Nevertheless, as the ongoing research was evolving it turned out that it was impossible to develop a convenient learning algorithm. As an example, the exclusive-or (XOR) operation could not be solved. Only when McCulloch-Pitts neurons were replaced by neural models with a differentiable activation function, a back-propagation learning algorithm was invented.

## 2.3. Spiking Neural Networks

The first ideas and models of artificial neural networks are over fifty years old, hence they are already becoming an old technique within the computer science field. The first generation of artificial neural networks consisted of McCulloch-Pitts threshold neurons, as explained above. Rather than using a step or threshold function to compute its output signals, the second generation uses a continuous activation function, making them acceptable for analogue input and output. The last and third generation is what we call the spiking neural networks [10].

The spiking neural networks are the third generation of neural networks which raise the level of biological realism by the use of individual spikes. Just like real neurons do, this functional characteristic allows the codification of spatial-temporal information in communication and computation. Therefore, instead of using rate coding this type of neural networks use mechanisms where neurons receive and do send out individual pulses, called pulse coding, allowing the codification of information as frequency and amplitude of sound.

Figure 2.5. Spike-trains [10].

The neuronal signal of a spiking neural network consists of short electrical pulses called spikes. These pulses, called action potentials or spikes, have an amplitude of about 100 mV and a duration of 1-2 ms. As shown in Figure 2.5 individual neurons send out sequences of spikes, or spike-trains, which alter dramatically in frequency over a short period of time. Thus, neurons have to use spatial and temporal information of incoming spike patterns to encode their message to other neurons.

In short, since all neuron spikes of a spiking neural networks look alike, the form of the action potential does not carry any information. Therefore, it is the number and timing of these spikes which actually matter.

# 3. Preliminary study of alternatives

This chapter presents a few hardware implementations of artificial neural networks on FPGAs. A general analysis of these implementations has been performed in order to point out their benefits and drawbacks of their computational structures.

#### 3.1. Bluehive

Bluehive is a field-programable custom computing machine for extreme-scale real-time neural network simulation, which is capable of emulating 64k neurons along with 64M synapses per FPGA, aimed to be used for scientific simulations with high demanding communication requirements [11].

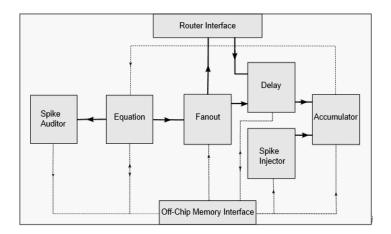

Figure 3.1. Processing engine of a node in Bluehive [11].

The design places the focus on the communication mechanism and it uses the Izhikevich neural model for neural networks simulations. The core SNN emulation is done by the processing engine that includes the following functional components:

- Equation Processor: calculates the equation of the Izhikevich neural model to performs the neuron computation.

- **Fan-out Engine**: takes the neuron firing events, looks up the destination nodes to be notified and the delay to be implemented and farms it out.

- Delay-Unit: performs the first part of the fan-in phase. Messages are placed into one of the sixteen 1ms bins, thereby delaying them until the right 1ms simulation time step.

- Accumulator: performs the second part of the fan-in phase, accumulation weights to produce an I-value for each neuron.

- Router: routes firing events destined for other processing nodes.

- **Spike auditor**: records spike events to output as the simulation results.

- **Spike injector**: allows external spike events to be injected into the simulated network. This is used to provide an initial stimulus. It could also be used to interface to external systems.

### 3.2. One million neuron single-FPGA neuromorphic system

The one million neuron single-FPGA neuromorphic system is an architecture that gives the approach for building a one million neuron system on a single FPGA. It is capable of implementing several neurons like the simple integrate and fire or the Izhikevich models, with the objective to use the system for multimodal scene analysis [12].

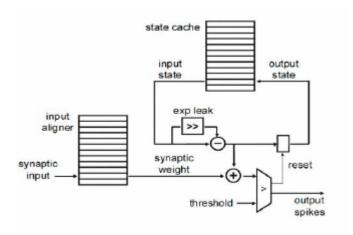

Figure 3.2. Neuron block diagram of the implementation [12]

This implementation uses the Address Event Representation (AER) communication system to handle the transmission of spikes between the neurons of the simulated neural network while the mapping of the network and the synaptic weights are stored in an external memory and fetched every cycle.

Figure 3.2 shows the neuron block diagram that uses a state cache to save the state of the several neurons that can be simulated in the same physical engine. Therefore, this block uses time multiplexing to simulate several neurons.

Finally, this design is capable of emulating up to 1 million of neurons, yet there are some drawbacks to it as it needs a large state cache and there is a significant time consumption due to the time multiplexing, as explained above.

#### **3.3. SNAVA**

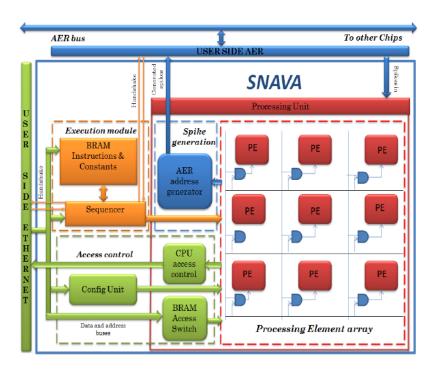

Designed to be a flexible spiking neural network emulator, SNAVA (Spiking Neural-network Architecture for Versatile Applications) is a Harvard hardware architecture capable to simulate any spiking neural network model in which the transmission of information between the neurons take place through spikes [13].

Therefore, the architecture has been designed with the aim to ensure that it can be reprogrammed to simulate different spiking neural networks models in an efficient way, giving a high level of flexibility and scalability.

Figure 3.3. Block diagram of the SNAVA architecture [13].

SNAVA consists in a scalable array of SIMD (Single Instruction Multiple Data) processing elements that assure a complete parallel execution of operations which is highly effective for the simulation of SNN since they are parallel by nature.

Furthermore, this architecture uses two communications protocols to provide the flow of information required for a SNN simulation. First the Address-Event Representation (AER) communication system, and second the Ethernet protocol. Moreover, this architecture enables the interconnection of several FPGAs to perform a SNN emulation.

# 4. Spiking neural networks

The next chapter seeks to make a brief description and analysis of the different possibilities that exist for the implementation of a spiking neural network. It has the aim of designing a flexible, modular, scalable and efficient system without losing the precision and accuracy needed for the simulation of a neural network in order to achieve its subsequent implementation. Consequently, this chapter introduces different neural models, as well as a communication system for transmitting data between different neurons and, finally, a training method for spiking neural networks.

#### 4.1. Neural models

The neural models are a mathematical approach of the behavior and the properties inspired by biological neural networks, which provide the capacity to reproduce their functionality in the field of computer simulations.

There are many different models for a spiking neural network. However, the type of model to use will depend on the needs that are required for the artificial neural network to simulate, as well as the available resources for such purpose. In other words, the challenge lies in finding a model that is sufficiently accurate and computationally efficient.

Further below, several neural models were analyzed to validate their suitability in the design of the proposed spiking neural network, always looking for the compromise between the model complexity and the cost of the implementation.

#### 4.1.1. Integrate-and-Fire model

The Integrate-and-Fire model [14], proposed in 1907 by the French neuroscientist Louis Lapicque, is recognized as one of the simplest neural models to establish itself as a canonical model to make way for a large number of variants.

In this model, a neuron is represented in time with the following equation:

$$I(t) = C_m \frac{dV_m(t)}{dt}$$

(Eq. 4.1)

Where I(t) is the current injected to the neuron,  $C_m$  is the neuron membrane capacitance and  $V_m(t)$  is the neuron membrane potential. Therefore, when a current is introduced to the input, the voltage

of the membrane increases with time until it reaches a constant threshold  $V_{th}$ , point in which the neuron generates a spike and the membrane voltage is reset to its initial value.

Moreover, you can get a more accurate model entering a refractory period  $t_{ref}$  that limits the frequency of firing of the neuron, preventing the generation of spikes during this period. In such a scenario, the function of the firing frequency with a constant input current is:

$$f(I) = \frac{I}{C_m V_{th} + t_{ref} I}$$

(Eq. 4.2)

Ultimately, due to the lack of time memory this model has the disadvantage that, at any time, if you get a signal below the threshold, the voltage of the membrane will suffer an increase but it will not return to its initial value until it fires again. Consequently, the spike frequency of this model is constant. Thus, this particular characteristic does not correspond within the observed behavior of neurons in a real biological neural network.

#### 4.1.2. Hodgkin-Huxley model

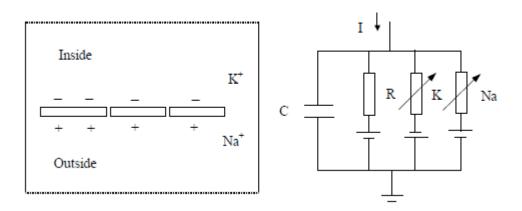

The Hodgkin-Huxley model [15] was described by physiologists and biophysicists Alan Hodgkin and Andrew Huxley in 1952 to explain the ionic mechanisms underlying the initiation and propagation of action potentials in the axon of a giant squid. It is a complex mathematical model but really accurate that describes how the potentials in neurons are initiated and transmitted. Thanks to this work they received the Nobel prize in physiology and medicine in 1963.

This model is easily explained by Figure 4.1. Firstly, the semipermeable membrane of the neuron separates the inside of the extracellular fluid and acts as a capacitor.

Figure 4.1. Schematic diagram of the Hodgkin-Huxley model [15].

If an input current I(t) is injected into the neuron, it can charge the capacitor or provide a leakage current through the different channels of the membrane of the neuron. Due to the transport of ions across the cell membrane, the ion concentration in the neuron is different than the one in the extracellular fluid. Therefore, the conservation of electric charge in the membrane implies that the applied current I(t) can be divided into a capacitive current  $I_{cap}$ , which charges capacitor C and a current  $I_k$  that is injected from presynaptic neurons.

$$I(t) = I_{cap}(t) + \sum_{k} I_{k}(t)$$

(Eq. 4.3)

Thus, the sum extends over all the ions. In the Standard model of Hodgkin-Huxley there are only three types of channels:

- Sodium channel with index Na.

- Potassium channel with index K.

- Unspecified leakage channel with resistance R.

From the definition of the Capacity,  $C=\frac{Q}{u'}$  where Q is a charge and u is the voltage across the capacitor. Since the current of the capacitor is  $I_{cap(t)}=C\frac{du}{dt'}$ , then:

$$C\frac{du}{dt} = -\sum_{k} I_k(t) + I(t)$$

(Eq. 4.4)

Therefore, in biological terms, u is the voltage across the membrane and  $\sum_k I_k(t)$  is the sum of the ionic currents that pass through the membrane of the neuron. In short, Hodgkin-Huxley formulated the three components with the following equation:

$$\sum_{k} I_k(t) = g_{Na} m^3 h(u - E_{Na}) + g_K n^4 (u - E_K) + g_L (u - E_L)$$

(Eq. 4.5)

Where  $E_{Na}$ ,  $E_K$  and  $E_L$  are the reversal potentials and  $g_{Na}m^3h$ ,  $g_Kn^4$  i  $g_L$  are the conductance resistances.

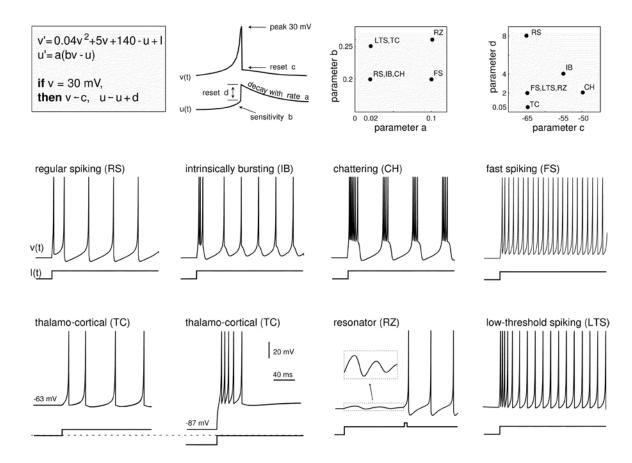

#### 4.1.3. Izhikevich model

The Izhikevich model [16] was designed with the intention to develop large-scale models of brain impulses by neural networks. Therefore, to achieve this, you need a model for a single neuron that is computationally simple, but capable of producing pulse patterns exhibited by biological neurons.

Under these premises, Eugene M. Izhikevich in 2003 presented a simple neuron model for spiking neural networks, which is as biologically plausible like the Hodgkin-Huxley model, and at the same time as computationally efficient as the Integrate-and-Fire model.

The author has reduced the accurate biophysiological models of Hodgkin-Huxley neurons into a twodimensional system of differential equations:

$$v' = 0.04v^2 + 5v + 140 - u + I$$

(Eq. 4.6)

$$u' = a(bv - u) \tag{Eq. 4.7}$$

If

$$v \ge 30 \text{ mV}, then \begin{cases} v \leftarrow c \\ u \leftarrow u + d \end{cases}$$

(Eq. 4.8)

Where v and u are dimensionless variables, and a, b, c, and d are dimensionless parameters, and  $d' = \frac{d}{dt}$ , where d' is the time. In biological terms, the variable d' represents the membrane potential of the neuron and d' represents a membrane recovery variable, which simulates the activation of d' ionic currents and inactivation of d' ionic currents, and it provides negative feedback to the membrane potential of the neuron, d'.

Regarding the behavior of the neuron, the positive synaptic currents I from other neurons increase the value of the membrane potential. In the case that these currents are not sufficient to make the neuron generate an impulse or spike, the voltage of the membrane its reset to its initial value. Alternatively, if the neuron generates a spike (+30 mV) due to sum of their input current, the membrane voltage v and the recovery variable u are reset according to equation 4.8.

The resting membrane voltage in this model is between -70 and -60 mV depending on the value of the parameter b. In addition, just like real neurons, the model does not have a fixed threshold, hence depending on the history of the membrane potential before the generation of a spike the potential threshold can be as low as -55 mV or as high as -40 mV.

The following considerations have to be taken into account for the use of the parameters exhibited in this model:

- The parameter a describes the time scale recovery of the variable u. Small values result in a slow recovery. A typical value is a=0.02.

- The parameter b describes the sensitivity of the recovery variable u to the subthreshold fluctuations of the membrane potential v. A typical value is b=0,2.

- The parameter c describes the after-spikes reset value of the membrane potential v. A typical value is c=-65~mV.

- The parameter d describes the after-spike reset of the recovery variable u. A typical value is d=8.

**Figure 4.2.** Different types of neurons based on the parameters a, b, c and d [16].

Conclusively, as shown in Figure 4.2, setting different parameters values result in different patterns of intrinsic activation, which allows the behavior emulation of diverse real biological neurons.

## 4.2. Neuronal connectivity

The digital systems implemented for neural networks emulation are still far from an equal efficiency in neural computation or neural coding like the real biological neural networks. Computers use a million times more energy for an operation than a real brain. Video cameras use a thousand times more bandwidth per bit of information than retinas do [17]. Due to these and other shortcomings, today we still cannot replace the damaged parts of the nervous system.

Due to this, it is not surprising that a small but growing community of engineers are trying to build systems that meet the efficiency and effectiveness of their biological references, in order to match the efficiency of the performance and computational communication by nature.

One of these problems arises when trying to establish the communications between neurons of an emulated neural network. In fact, the neural systems need to connect millions of neurons and thus establish a connection-efficient chip implementation, which creates a major challenge. Therefore, this section will discuss the AER system (Address-Event Representation) which aims to reduce some of these shortcomings and has been implemented in the emulated neural network of this project.

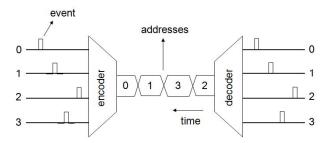

#### 4.2.1. AER System

Mahowald and Sivilotti proposed a system of event representation to be able to transmit pulses of a number of neurons on a chip to the appropriate location in an array of neurons in a second chip.

Figure 4.3. Schematic of the AER system [18].

In the schematic shown in Figure 4.3 an encoder assigns a unique address for each neuron that generates a spike. Then, a bus transmits these addresses to a decoder that selects the appropriate location of the spike.

This communication system is quite efficient to avoid the bottlenecks that occur when the information needs to be exchanged in a massively interconnected system, like the neural networks impulses or spikes.

Nevertheless, a number of issues should be considered in order to achieve an efficient implementation of the AER system. One of them is the case in which two or more events occur at the same time, then the system needs to decide in which order they are transmitted through the bus, since it can only transmit one address per time unit.

## 4.3. Learning of neural networks

To understand how the mammalian cerebral cortex performs its calculations, it is necessary to understand mainly two aspects. First, we must have a good understanding of the neuronal processing units, the neurons; and secondly, we must gain a better understanding of how the mechanisms of these neurons combine to build functional systems.

This section talks about the STDP (Spike-Timing-Dependent Plasticity) as a method for building artificial neural networks to perform complex computational operations or solving pattern recognition tasks.

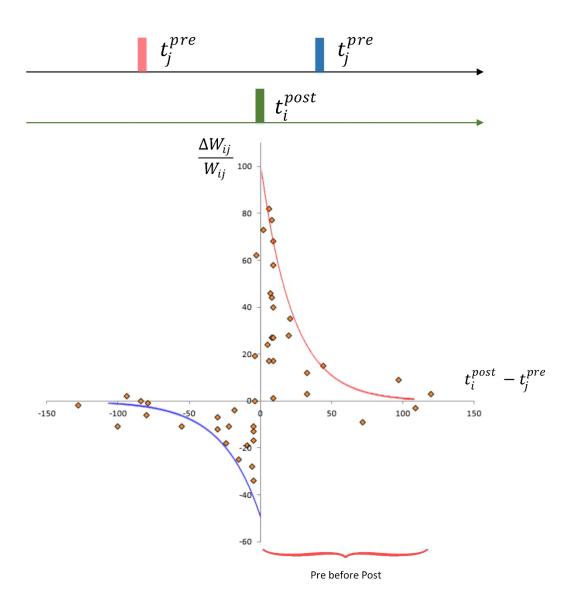

#### 4.3.1. Spike-Timing-Dependent Plasticity

The STDP (Spike-Timing-Dependent Plasticity) [19] is a biological process responsible for altering the connections, or synapses, of all the neurons in a spiking neural network. To do so, it strengthens or weakens the connectivity between the neurons based on the degree of synchronization of their spikes. This degree of connectivity is commonly known as the weight of the link or synapse.

This rule is a method of unsupervised learning, the concept of which is to strengthen synapsis that contribute to the generation of an output spike, while those that do not contribute, i.e. those that generate spikes after the output spike, are weakened.

Considering a presynaptic neuron i and a postsynaptic neuron j, the function that characterizes the modification of the synaptic weight is as follows:

$$\Delta w_j = \sum_{k=1}^{N} \sum_{l=1}^{N} W(t_j^l - t_i^k)$$

(Eq. 4.9)

Along with the function, which defines the degree of increase or decrease of the synaptic weight based on the timing of the impulses between the pre- and postsynaptic neurons expressed as:

$$W(x) = \begin{cases} A_{+} \exp\left(-\frac{x}{\tau_{+}}\right) & \text{if } x > 0\\ A_{-} \exp\left(\frac{x}{\tau_{-}}\right) & \text{otherwise.} \end{cases}$$

(Eq. 4.10)

In equations 4.9 and 4.10,  $t_j^l$  represents the activation time  $l^{th}$  of the neuron j; similarly,  $t_i^k$  represents the activation time  $k^{th}$  of the neuron i;  $A_+$  and  $A_-$  are the constants that define the extent of the change in the synaptic weight (at  $t=0_+$  and  $t=0_-$  respectively); and,  $\tau_+$  and  $\tau_-$  are the constants of the exponential decrease in the change of the synaptic weight.

Figure 4.4. Graphical representation of the STDP learning rule [20].

Figure 4.4 represents equation 4.10 of relative weight changes based on the time between the prespikes and post-spikes of the synapsis between two neurons. Therefore, it shows the reduction of the synaptic weight when a presynaptic neuron fires after a postsynaptic neuron; and on the contrary, an increase of the synaptic weight from a presynaptic neuron to a postsynaptic neuron if a presynaptic neuron fires before the postsynaptic neuron.

# 5. Design and implementation of a SNN

The simulations of neural networks, due to their intrinsic characteristic of being formed by thousands of interconnected neurons, require high computing power which in turn requires high computational power that can exceed the computing power of a generic microprocessor.

Thanks to the technological development, today we have sufficient tools to provide customized hardware systems with the ability to obtain a high computing power by reducing the energy consumption and needed resources. The fact of designing and implementing a microprocessor which is designed to perform a particular task allows us to optimize and maximize its performance with respect to a generic microprocessor.

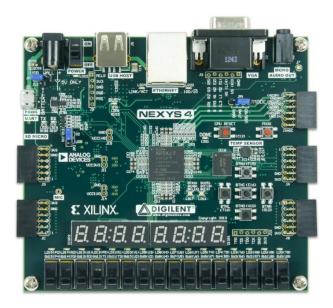

Figure 5.1. Nexys 4 Artix-7 FPGA [21]

One of the tools that allow the development and implementation of microprocessors or digital systems are the FPGA (Field-Programmable Gate Array). A FPGA is a semiconductor device based on a matrix of configurable logic blocks connected via programmable interconnections. The aim of this chapter is to explain the design and architecture of the different modules that form the spiking neural network and their interconnection to achieve its implementation in a FPGA.

In order to provide the maximum flexibility and scalability possible for the emulation of SNNs a modular system has been proposed. In the following sections, it is explained the design and architecture of a neuron, the AER communication system and the STDP learning method which interconnected allow the emulation of a SNN. Finally, in the next chapter, a SNN for pattern recognition is proposed as a proof-of-concept application.

## 5.1. Izhikevich neuron

To simplify the computing power necessary to reproduce the neuron model of Izhikevich and optimize the resources used in the FPGA, a series of adaptions have been made, similar to the fixed-point implementation of the model proposed in [22].

Due to the transition of the neuron model equations from the real numbers to the digital domain, all the properties of binary numbers have been studied in order to avoid performing complex multiplications and divisions that could complicate the implementation and exceed the resources available in a FPGA for the emulation of large-scale neural networks.

#### 5.1.1. Model adaptation

Initially, the numbers of the equations for the digital system are represented with a signed vector of 13 bits, therefore with one bit for the sign of the number. In order to start working with the equations, the parameters corresponding to the variables a, b, c and d have been set to their recommended values in order to obtain a regular spiking neuron model proposed by Izhikevich. Therefore, the following equations have been obtained:

$$v' = 0.04v^2 + 5v + 140 - u + I$$

(Eq. 5.1)

$$u' = 0.02(0.2v - u)$$

(Eq. 5.2)

lf

$$v \ge 30 \text{ mV}, then \begin{cases} v \leftarrow -65 \text{ mV} \\ u \leftarrow u + 8 \end{cases}$$

(Eq. 5.3)

Secondly, it has been decided to work with a binary representation of integers. Hence, due to the lack of decimal numbers in a binary vector representation a multiplication per ten has been performed. Thus, the membrane potential, v, along with the recovery voltage, u, are multiplied by ten, obtaining the following model:

$$v' = \frac{1}{250}v^2 + 5v + 1400 - u + I$$

(Eq. 5.4)

$$u' = \frac{1}{50} (\frac{1}{5}v - u)$$

(Eq. 5.5)

If

$$v \ge 300$$

, then  $\begin{cases} v \leftarrow -650 \\ u \leftarrow u + 80 \end{cases}$  (Eq. 5.6)

On the other hand, a way to save resources in the FPGA implementation is doing a power of two multiplications or divisions. Therefore, if you calculate a power of two multiplication in a binary number, you only need to shift left the binary vector as many positions as power of two multiplications need to be made. On the contrary, if you calculate a power of two division a shift right operation in the binary vector is enough to obtain the result.

In short, the coefficients of the equations have been adjusted to achieve multiplications and divisions by power of two in order to optimize the design. Firstly, for the equation 5.4 the number 250 has been replaced by 256, since  $256 = 2^8$ . Secondly, for equation 5.5 the divisors 50 and 5 have been replaced by 64 and 4 respectively, since  $64 = 2^6$  and  $4 = 2^2$ . In addition, the multiplication 5v and v term of the equation 5.4 have been replaced to implement a sum of six terms of the membrane potential. Since the sum of the six terms can be expressed as a sum of a 2v and 4v, this two power of two multiplications have been implemented as shift left operations. Therefore, the following equations for the adapted model have been obtained:

$$v[n+1] = 2v[n] + \frac{1}{2^8}v^2[n] + 2^2v[n] + 1400 - u[n] + I[n]$$

(Eq. 5.7)

$$u[n+1] = u[n] + \frac{1}{26} (\frac{1}{2^2} v[n] - u[n])$$

(Eq. 5.8)

If

$$v[n+1] \ge 300, then \begin{cases} v[n+1] \leftarrow -650 \\ u[n+1] \leftarrow u[n+1] + 80 \end{cases}$$

(Eq. 5.9)

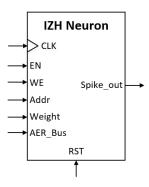

### 5.1.2. Design and architecture

As explained above, a modular, flexible and scalable digital system has been proposed in order to include all the different possibilities that can exist in the emulation of a spiking neural network, while trying to maintain its simplicity.

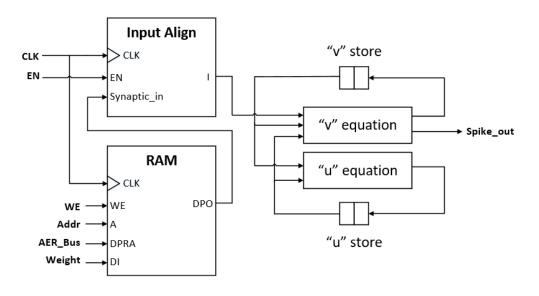

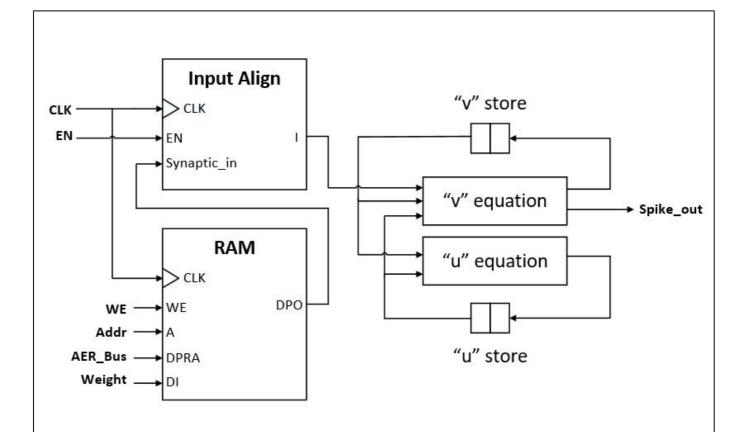

The designed module for the neuron implementation has seven entries, including the clock signal, and one output. Furthermore, the neuron has a small Random Access Memory (RAM), where it stores the different weights of the synaptic connections with other neurons.

Looking at Figure 5.2 and going in order, firstly, there is the clock signal (*CLK*), which is responsible for coordinating the different actions of the neuron; secondly, and activation signal (*EN*) which serves to activate the functioning of the neuron; thirdly, there are the signals write enable (*WE*), address (*Addr*) and synaptic weight (*Weight*) that are used to write to the internal RAM of the neuron; fourthly, there is the input of the AER bus (*AER\_Bus*) where the neuron reads which neuron of the neural network generated a spike; finally, there is a binary output signal (*Spike\_out*) which indicates whether the neuron generated a spike.

Figure 5.2. Digital bloc of a neuron.

Lowering a level in the implementation of the neuron, shown in Figure 5.3, there are the different sequential and combinational digital blocks that operate the actions of the neuron. These are: an internal RAM, a sequential block for the weight synaptic input, two registers for the membrane potential and voltage recovery, and two combinational blocks corresponding to the implementation of the differential equations presented above.

Figure 5.3. Block diagram of the neuron.

The internal RAM of the neuron is a matrix that forms a column of synaptic weights. As shown in Table 5.4, each position in the column corresponds to the weight of a synaptic connection with a neuron, so the first column corresponds to the synaptic weight of the connection with the zero neuron of the neural network.

| NEURON | SYNAPTIC WEIGHT |

|--------|-----------------|

| 0      | 70              |

| 1      | -40             |

| 2      | 0               |

| 3      | 120             |

| 4      | -15             |

Table 5.1. RAM of the neuron.

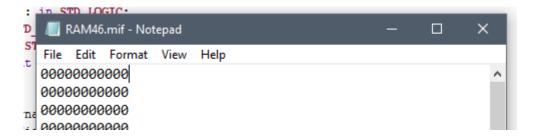

Therefore, if the value of the synaptic weight is zero, it means that there is no link between these two neurons. In addition, the used model allows the use of excitatory and inhibitory synaptic weights, i.e. positive and negative respectively. Also, as mentioned above, it is possible to modify the synaptic weights of the connections with write enable (*WE*), address (*Addr*) and synaptic weight (*Weight*) signals. Moreover it is possible to initialize the RAM of a neuron with a .mif text file.

Sequentially the functionality process of the neuron is as follows: firstly, it reads the AER communication bus for the neuron that it fired. Then, the RAM is responsible for reading the synaptic weight associated with the number written on the AER bus and it sends it to the *Input Align* sequential bloc. This blog will dispatch the synaptic weight to the combinational block of the potential membrane equation, also it is responsible for adding the synaptic weights in the case that several neurons fired at the same time. For this purpose, as it will be explained in the next section, the AER bus stops the activity of the neuron deactivating the *EN* signal, since it cannot transmit more than one spike at once and writes one of the addresses of the neurons that fired in each clock cycle.

Also, the Input Align block limits the negative value that a synaptic weight can have to -140 mV because for values under -140 mV the neuron ends up generating a spike when, biologically, the neuron should not excite for inhibitory synaptic weights. To verify that this anomaly was not a consequence of the adapted model for this implementation, several simulations were performed with the original model and it reproduced the exact same behavior with high negative synaptic weights.

Finally, the combination blocks corresponding to the model equations perform their operations with the registers "v" store and "u" store where the signals  $v_n$ ,  $v_n$  and  $v_n$  and  $v_n$  are stored respectively.

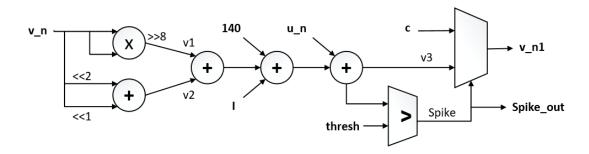

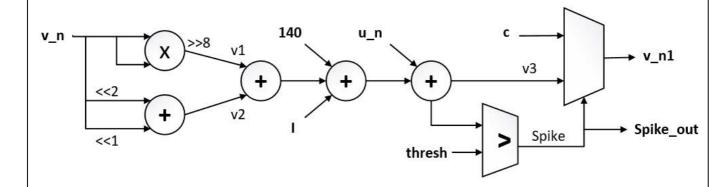

The digital implementation of the adapted equations can be seen in detail in Figure 5.5. The top of the diagram corresponds to the equation 5.7 where; firstly, the signal v1 is generated by the square of v n

signal and a binary shift right operation of eight positions; secondly, v2 signal is generated by the sum of a binary shift left operation to  $v_n$  of one and two positions respectively; thirdly, the equation is followed by performing the sum of other factors including the synaptic weight; finally, using a comparator the design determines whether the value of the membrane voltages exceeds the threshold indicated in equation 5.9. If so, the spike signal is activated indicating the firing of the neuron. In addition, if the neuron exceeds the threshold value the membrane potential is reset to the c value, otherwise it continues to operate with signal v3 until the next clock cycle in which the "v" store register will replace the  $v_n$  signal for the  $v_n$ 1 signal.

## "v" Equation implementation

### "u" Equation implementation

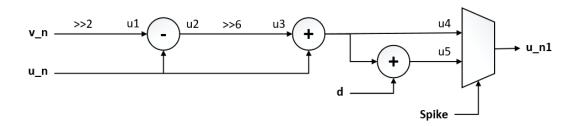

Figure 5.4. Digital implementation of the adapted neuronal equations.

Following with Figure 5.4, the bottom of the diagram corresponds to equation 5.8 where; primarily, the signal u1 is generated by performing a two binary shift right operation of the membrane voltage  $v_n$ ; leading on from this, the signal u3 is obtained by signal u1 minus  $u_n$  and a six binary shift right operation. Finally, the signals u4 and u5 are driven to a multiplexer with a channel selection based on whether the neuron fired or not (Spike signal) to set the recovery value of the membrane  $u_n1$  as equation 5.9 indicates.

Additionally, Figure 5.5 shows the comparison between the resources utilization of the adapted (left) and non-adapted (right) neuron models corresponding to equations 5.4-5.6 and 5.7-5.9 respectively.

| Resource | Utilization | Available | Utilization % | Resource | Utilization | Available | Utilization % |

|----------|-------------|-----------|---------------|----------|-------------|-----------|---------------|

| LUT      | 134         | 63400     | 0.21          | LUT      | 786         | 63400     | 1.24          |

| LUTRAM   | 16          | 19000     | 0.08          | LUTRAM   | 16          | 19000     | 0.08          |

| FF       | 130         | 126800    | 0.10          | FF       | 169         | 126800    | 0.13          |

| DSP      | 1           | 240       | 0.42          | DSP      | 1           | 240       | 0.42          |

| IO       | 28          | 210       | 13.33         | IO       | 28          | 210       | 13.33         |

| BUFG     | 1           | 32        | 3.13          | BUFG     | 1           | 32        | 3.13          |

**Figure 5.5.** Resource utilization comparison of a single Izhikevich neuron between the adapted (left) and non-adapted (right) digital model.

As it can be observed, for the implementation of a single neuron into a Nexys4 Artix-7 FPGA the non-adapted model uses about 6 times more look-up tables than the adapted model. Therefore, this difference will greatly increase when building a neural network of ten, one hundred or more neurons. Finally, by doing some rough estimations it could be said that the used FPGA could implement almost 500 neurons of the adapted model. Whereas, only 80 neurons of the non-adapted model, which equates to a difference which cannot be ignored.

#### 5.1.3. Simulations

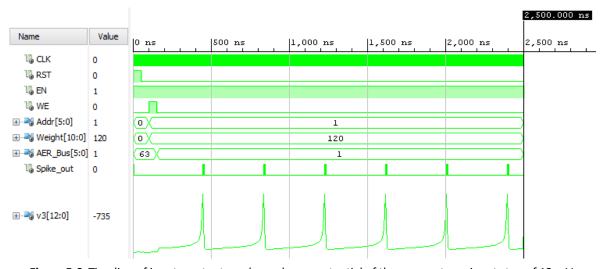

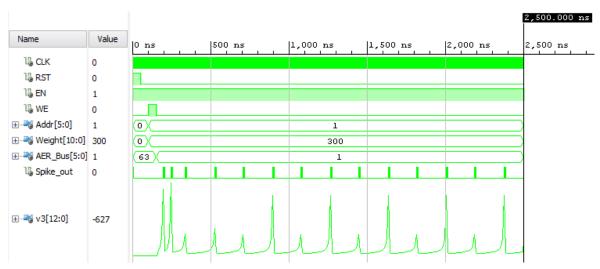

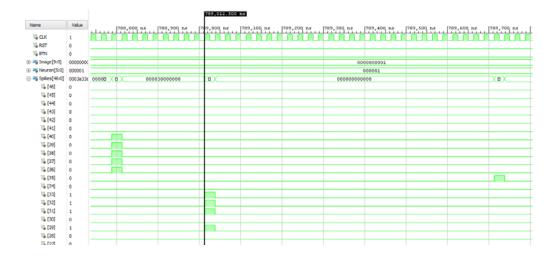

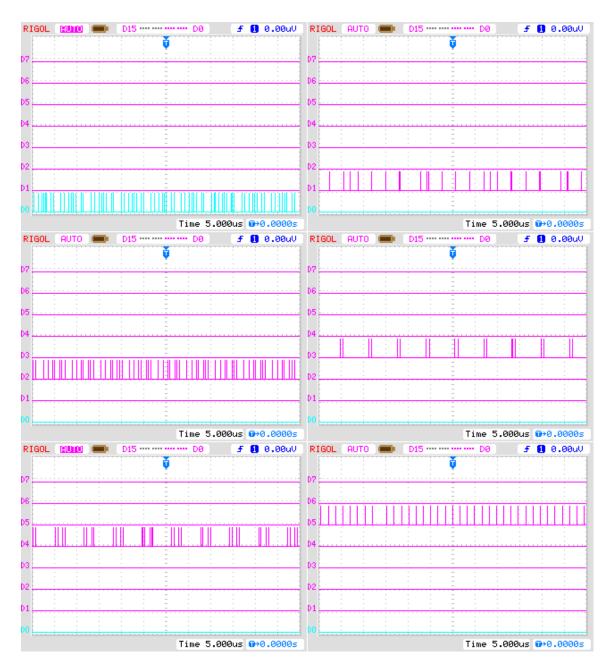

Here are various simulations of the implemented model made with Vivado in order to show the different behaviors exhibited by the neuron against different scenarios.

Figure 5.6. Timeline of inputs, outputs and membrane potential of the neuron to an input step of 12 mV.

In Figure 5.6 the response of the neuron to an input step of 12 mV is shown. Firstly, in the 50 ns a synaptic weight of 12 mV with neuron 1 is written in the internal RAM, keeping the *WE* signal activated. A few clock cycles later the address of the neuron 1 is written in the AER bus, simulating the constant firing of this neuron and therefore, generating an input step of 12 mV for the simulated neuron. Finally,

what can be seen is how the neuron starts generating neuronal impulses to the output signal *Spike\_out*.

Figure 5.7. Timeline of inputs, outputs and membrane potential of the neuron to an input step of 30 mV.

Secondly, in Figure 5.7 the neuron exhibits a similar behavior as in Figure 5.6 as a response to an input step of 30 mV and therefore generating a higher frequency of spikes.

Figure 5.8. Timeline of inputs, outputs and membrane potential of the neuron to an input step of -10 mV.

Finally, the neuron shows the response to an input step of -10 mV in Figure 5.8, thus since it is an inhibitory input the neuron does not generate any spikes. In essence, the implemented neuron shows the behavior exhibited by the original model proposed by Izhikevich, as shown in Figure 4.2 of the previous chapter.

## 5.2. AER System

Due to the design of the neuron, this is capable of reading the information written on the AER (Address-Event Representation) bus and through its own RAM, it will apply itself to the corresponding synaptic weight of the link between itself and the firing neuron.

Consequently, unlike the system proposed in the previous chapter, consisting of an encoder and decoder, the design of the AER system of this project must consist of an encoder that reading the spikes of all neurons of the SNN is capable of translating them to their corresponding neural address, to finally write in the AER communication bus, the neuron that fired.

Moreover, this design has addressed the problem of processing two or more events at the same time due to the inability to transmit more than one address through the AER communication bus, adding a condition of priority to the encoder.

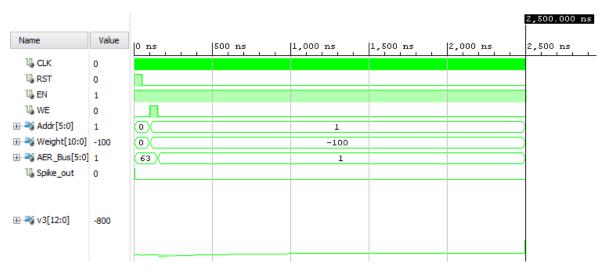

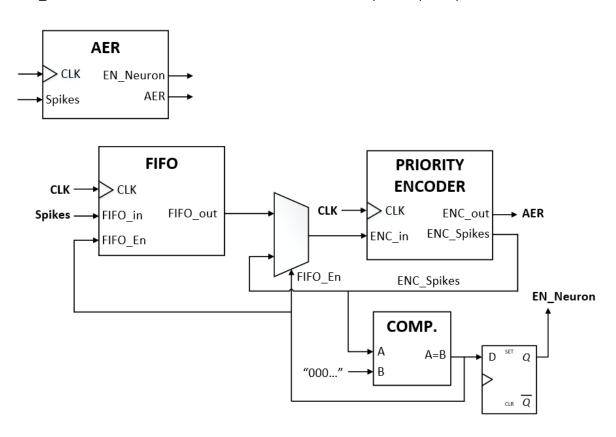

#### 5.2.1. Design and architecture

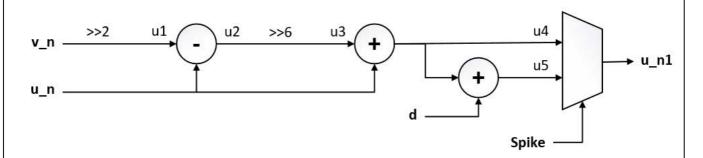

The AER system block diagram is shown in Figure 5.9, where at the top there is the block of the AER system that has two inputs and two outputs corresponding to the clock signal (*CLK*), spikes vector (*Spikes*), and an activation signal for the neurons (*EN\_Neuron*) and the AER communication bus (*AER*) respectively.

The main signal is the spikes vector (*Spikes*) that is a vector which contains as many bits as neurons form the neural network. Therefore, in the case of a neural network of five neurons the spikes vector is as: "00000". Where with a "1" it indicates the firing of a neuron, thus if neuron zero and three generate a spike at the same time, the AER system will have to process the following vector: "01001". As a result, the number 3 will be written at the output of the AER bus and at the next clock cycle the number 0 will be written in order to avoid collapsing the bus by writing two address at once. Additionally, due to the delay caused by the transmission of an impulse for each clock cycle, the AER system has a *EN\_Neuron* signal used to stop all neurons connected to the neural network, so they have time to read the synaptic weight associated with each neuron that has fired and to compute their sum.

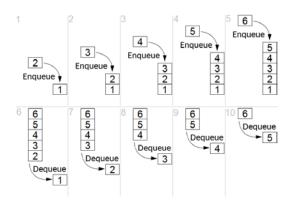

Going down one level in the implementation, as shown in Figure 5.9, the AER system is composed of four components, a type of buffer or memory called FIFO (First in, first out), a multiplexer, a priority encoder and a comparator. This AER system has two types of operation depending on whether there is one or more of a neural spike at the same time.

Continuing with the previous spikes vector, "01001", the AER system works as follows. First, the buffer called FIFO drives the vector to the multiplexer, on which if there have not been any spikes the signal *FIFO En* will be activated and it will transmit the vector directly to the priority encoder.

Figure 5.9. AER system block diagram.

One clock cycle later, the priority encoder works with the vector "01001" starting to read every bit from left to right and therefore, detecting a "1" in position four of the vector which corresponds to the third neuron. Finally, it writes the address 3 to the AER bus and generates a second signal, *ENC\_Spikes*, which is the same vector but with the spike of the neuron 3 being reset: "00001".

Then this vector is written to the comparator to determine if it is equal to a zero vector, i.e. a vector with all bits to zero. If not, the signal *FIFO\_en* along with *EN\_Neuron* are disabled, stopping all the neurons. Also, the multiplexer sends to the priority encoder the vector *ENC\_Spikes*, "00001", so it can continue to work with the rest of the other spikes. Meanwhile the FIFO performs an operation similar to the one shown in Figure 5.10. It is stopping the output of data and starting the storage of the different input spikes vectors that can arrive while the priority encoder is working with vector "01001".

Once the priority encoder finished to write all the spikes to the AER communication bus, the comparator will reset the *FIFO\_En* signal and the FIFO will start transmitting all the vectors that it saved in its memory.

Figure 5.10. Representation of FIFO functionality [23].

Note that, in principle, FIFO memory should not keep any spikes vector while the priority encoder is working since all the neurons of the neural network are stopped with *EN\_Neuron* signal. However, this system is useful just in case external impulses arrive during this period, such as the spikes of the first layer of the neural network.

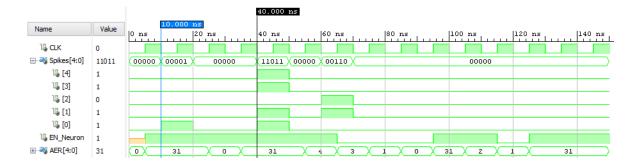

### 5.2.2. Simulations

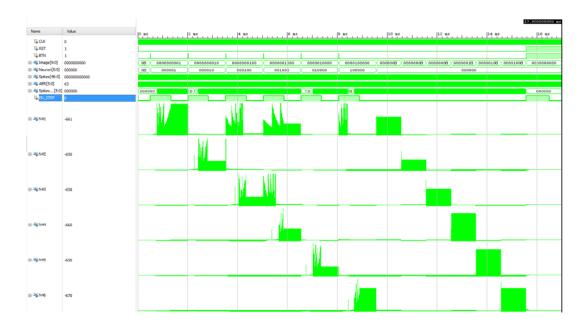

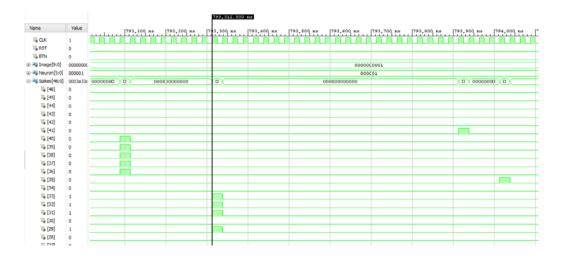

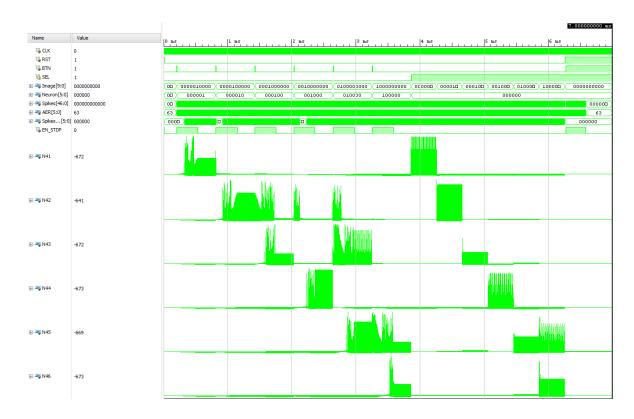

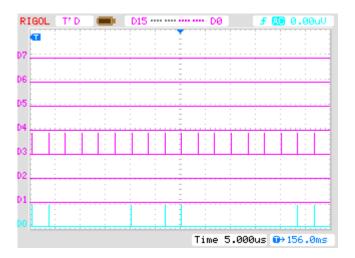

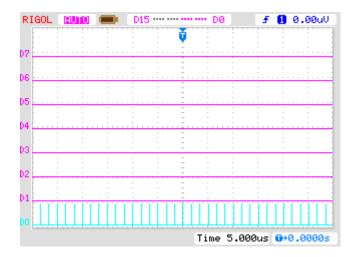

A simulation of the AER system made with VIVADO is shown in Figure 5.11 in order to show the different behaviors exhibited this communication bus in front of the spikes generated by a neural network.

Figure 5.11. Timeline of the AER system behavior.

Firstly, as it can be seen in Figure 5.11 when the AER bus does not detect any spikes it writes all of their bits to "1", so in this particular case, it shows the number 31, i.e. the AER bus can show up to 31 addresses from 0 to 30, including 0.

Secondly, at 10 ns a spike is generated by neuron number zero, therefore, according to the functionality described above, the AER bus writes the 0 address in the next clock cycle in its output.

Finally, at time 40 ns several spikes are generated by neurons number 4, 3, 1 and 0. Thus, the priority encoder starts working and the *EN\_Neuron* signal is deactivated to stop the activity of all the neurons

so it can write, in every clock cycle, the address of the firing neurons. Besides, during the transmission of these spikes neurons number 1 and 2 fire. Then, FIFO stores the corresponding spikes vector and the addresses of these two neurons are written once the priority encoder finishes the spikes transmission of neurons 4, 3, 1 and 0, implementing the functionality as shown in Figure 5.10 of the previous section.

## 5.3. Spike-Timing-Dependent Plasticity

Recent efforts in artificial intelligence studies suggest that the software can be trained and taught to obtain a behavior that goes beyond the reproduction of a fixed sequence of events. Learning is a distinction that separates the intelligent systems from the unintelligent. Thus, researchers are directing considerable effort in developing learning skills for neuronal networks and other synthetic systems.

Therefore, this chapter proceeds to explain the design and implementation of the Spike-Timing-Dependent (STDP) learning rule, that modifies the synaptic weights of the connections between neurons depending on the synchrony of their firing. That is, the synapses that contribute to the generation of an output spike of the neural network should be enhanced, while those not contributing to the generation of a spikes in the output must be weakened.

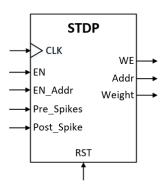

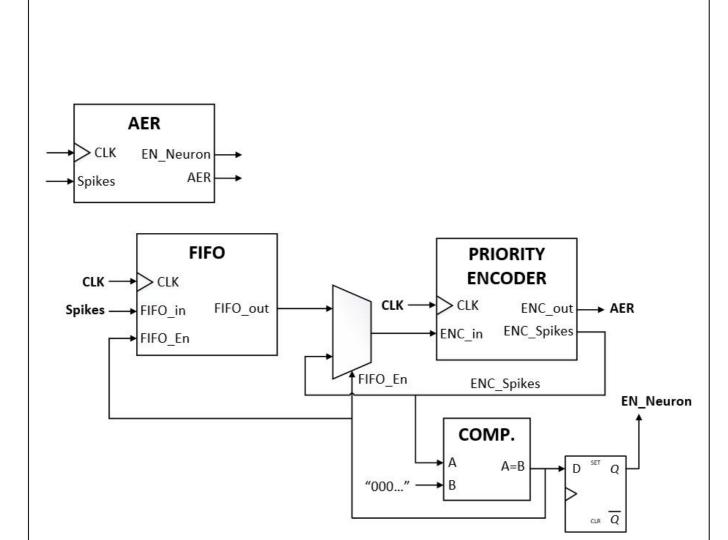

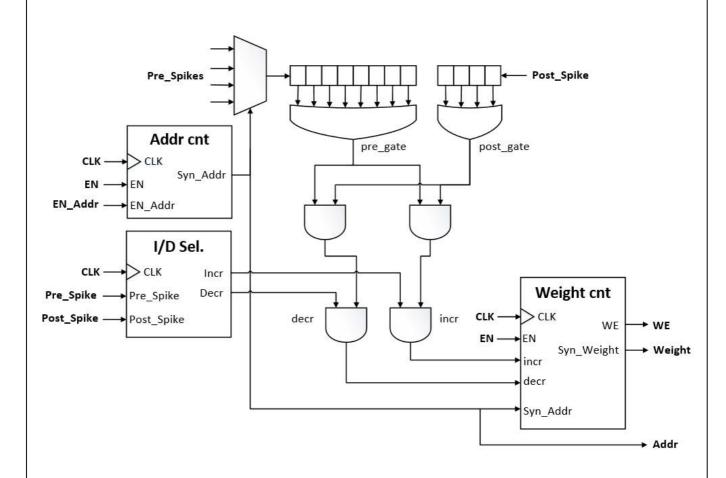

#### 5.3.1. Design and architecture

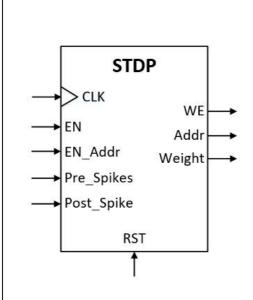

The digital block shown in figure 5.12 has been designed for the implementation of the STDP learning rule based on the digital logic approach from [24]. This block has six inputs, including the clock signal, along with three outputs corresponding to the write enable (*WE*), address (*Addr*) and synaptic weight (*Weight*) signals of the internal RAM of the neuron.

Figure 5.12. Digital block of the STDP module.

The training system described in the previous chapter is responsible of modifying the weights of all the connections of the neural network. Due to the complexity of creating a module to handle all the

synaptic weights of the neural network the following solution has been proposed: create a training module that is in charge of the connections of a single neuron. Therefore, having a learning module for each neuron of the neural network that is responsible of all the links coming to that neuron, and thus to maintain and update the RAM of it.

Observing the Figure 5.12 and going in order, primarily, there is a clock signal (*CLK*) which is responsible for coordinating the different actions of the learning module; following this, an activation signal (*EN*) which serves to activate the learning; next, an activation signal (*EN\_Addr*) that is responsible for changing the connection in which the STDP rules is applied; thus, two signals *Pre\_Spikes* and *Post\_Spike* that are the responsible of reading the firings of the previous neurons and the spike of the neuron where the STDP module is connected respectively; and finally, at the output there are the write enable (*WE*), address (*Addr*) and synaptic weight (*Weight*) signals that allow to write in the RAM of the neuron. In addition, there is a reset signal (*RST*) that along with the enable signal (*EN*) allow to reset all the synaptic weights of the neuron's RAM.

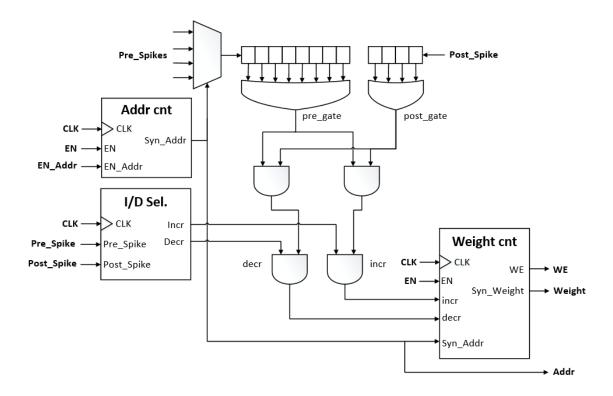

**Figure 5.13.** Block diagram of the STDP module.

As shown in Figure 5.13, there are several interconnected combinational and sequential blocks for the STDP module to function. These are: a counter address (*Addr cnt*) to select on which synaptic link the STDP rule is applied, an increment or decrement link selector (*I/D Sel*.) that actives the corresponding signal whether the pre-spike happens before or after the post-spike of the connection, a synaptic weight counter (*Weight cnt*) that is responsible for storing and modifying the synaptic weight of all the

connections of the neuron, and finally a set of combinational blocks that allow the digital logic implementation of equations 4.9 and 4.10 from the STDP learning rule.

Sequentially the operational process of the learning module is as follows: initially, the pre-spikes and post-spike signals are being read while the address counter is in charge of selecting the connection to apply the STDP rule with the *Syn\_Addr* signal, which at the same time serves as a selector channel for the multiplexer, indicates to the weight counter the link to modify and proportionate the address of the neuron's RAM.

After, in the event of a spike from the previous neurons of the neuron in which the STDP module is connected, the *I/D Sel* block activates the corresponding output signal to indicate whether the weight counter needs to increase or decrease the connection's value of the synaptic weight. Also, the spike is propagated through the shift register and activating the *pre\_gate* signal. Then, if the neuron of the training module fires, its spike is propagated by the corresponding shift register activating the *post\_gate* signal. The activation of these two logic gates along with the increased signal provided by the *I/D Sel* block generates an increment pulse for the synaptic weight counter. Therefore, depending on the duration of this pulse counter it will increase more or less the weight of the synaptic connection. Moreover, it will activate the write enable signal (WE) to allow the update of the neuron's RAM.

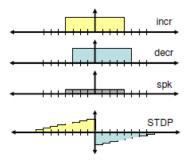

Figure 5.14. Timeline of the implemented STDP learning rule [24].

In short, as shown in Figure 5.14, depending on the increasing or decreasing pulse duration the value of the synaptic weight will increase or decrease respectively. That is, if the neuron fires after its preceding neurons generated a spike, the almost synchronous activation of the logic gates *pre\_gate* and *post\_gate* will create a long pulse length for the synaptic weight counter, which increases the weight of the connection for each clock cycle.

Finally, this design allows the regulation of the STDP function by modifying the length of the registers corresponding to the neuron's spikes. Therefore, creating a more or less sensible STDP learning rule to the synchrony of the neural impulses.

#### 5.3.2. Simulations

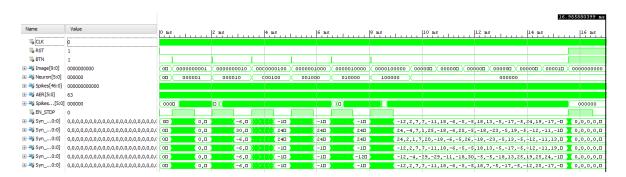

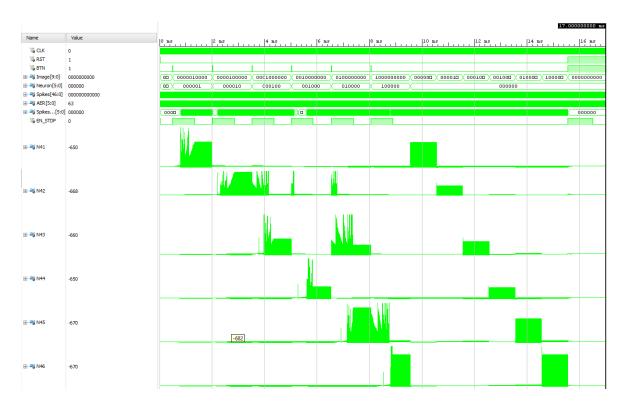

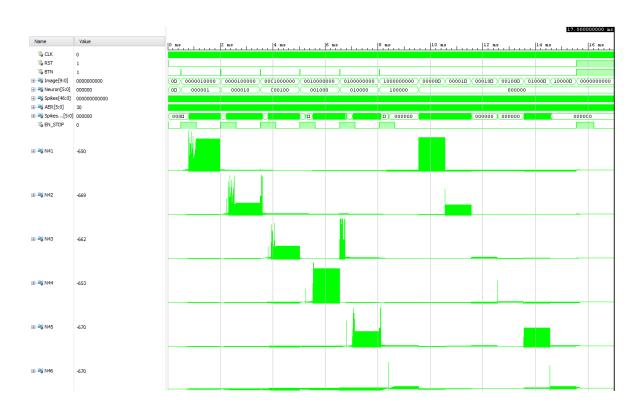

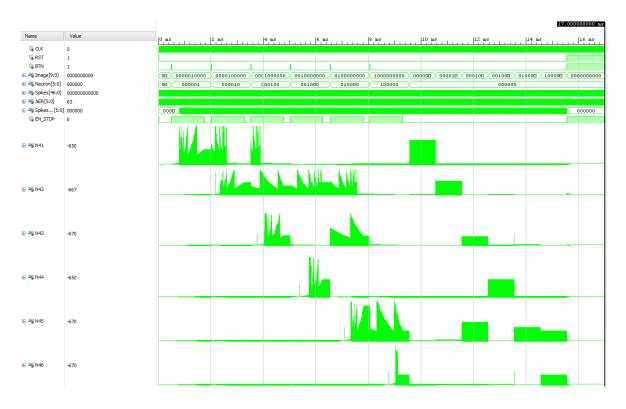

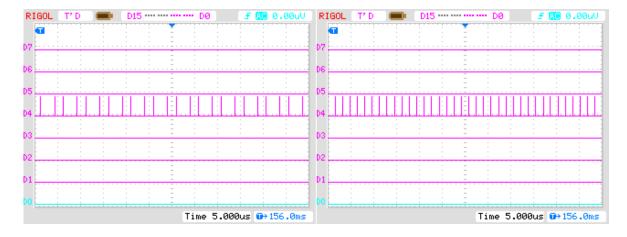

In this section, there are the various simulations of the implemented module made with Vivado in order to show the different behaviors exhibited by the learning module. In the timeline simulations, there are the inputs and outputs of the STDP module along with the *pre\_gate*, *post\_gate*, *incr* and *decr* internal signals for a better understanding of the inner workings of the design.

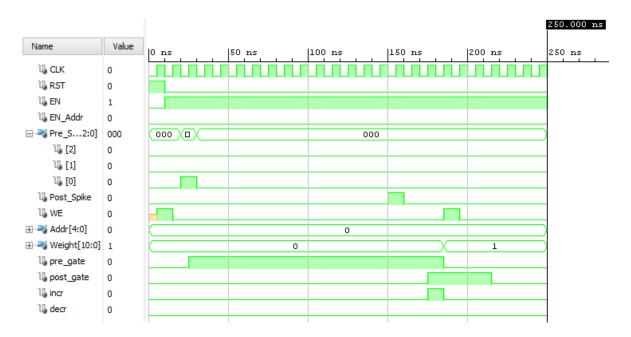

Figure 5.15. Timeline of inputs and outputs of the STDP learning module (Case 1).

First, for the preparation of the timelines a neuron connected to a previous layer of three neurons has been simulated. Therefore, the *Pre\_Spikes* signal is a vector of three binary numbers corresponding to the three synaptic connections and the *Post\_Spike* signal is a single bit that corresponds to the firing of the neuron that is connected to the STDP learning module.

Looking at figure 5.15, around the 20 ns, there is a spike from the first synaptic connection, moments later, the neuron generates a spike that is read through the *Post\_Spike* signal. Because of this, the internal signals *pre\_gate* and *post\_gate* activate respectively and when these two come together in time, the signal *incr* generates a pulse of one clock cycle that is sent to the weight counter. Finally, the value of the synaptic weight, which at the start was 0, is updated to the neuron's RAM with a value of 1 by the write enable (*WE*), address (*Addr*) and synaptic weight (*Weight*) signals.

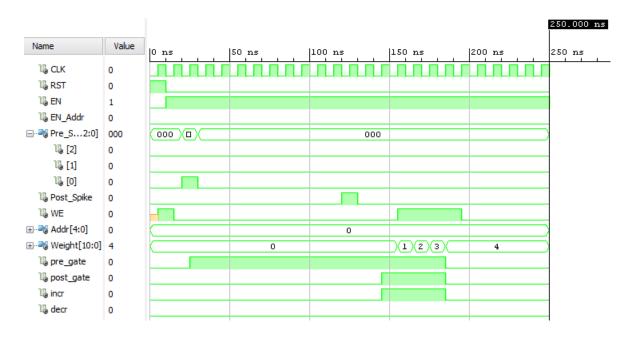

Continuing with Figure 5.16, the same functionality is exhibited with the difference that the time between the two spikes is lower, therefore the value of the synaptic weight is increased to a greater extent, i.e. from 0 to 4.

Figure 5.16. Timeline of inputs and outputs of the STDP learning module (Case 2).

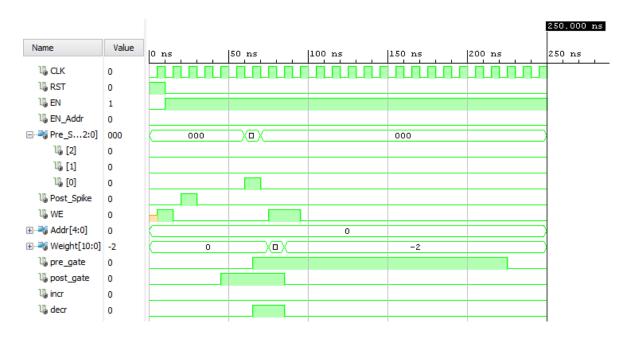

Moreover, Figure 5.17 shows the case in which a neuron of the input layer fires after the neuron where the STDP module is connected fired. Hence, due to the *I/D Sel* block and the digital combinational logic explained above, a decrement pulse is generated, indicating to the synaptic weight counter the decline in the value of the link connectivity from 0 to -2.

Figure 5.17. Timeline of inputs and outputs of the STDP learning module (Case 3).

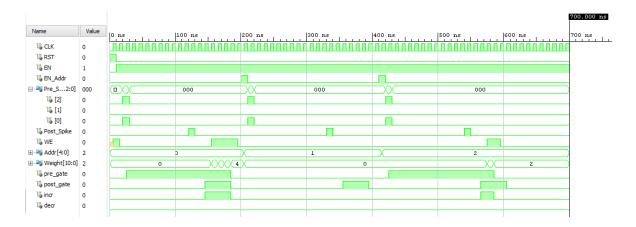

Finally, the functionality of the learning module for this small neural network is shown in Figure 5.18. As it can be observed, approximately every 200 ns the neuron receives the same trend of spikes from the neurons which is connected to. Thus, the learning module has the ability to alter one synaptic connection for each time that it receives the spikes.

Firstly, the first synapsis that corresponds to the first bit of the *Pre\_Spikes* vector is updated with a value of 4. Secondly, the *EN\_Addr* signal is activated so the learning module operates for the second synapsis, since there is no spike from it the value is not modified. Finally, the *EN\_Addr* signal is triggered again to apply the STDP learning in the third synapsis, and the weight value is updated to 2 due to the time difference between the two spikes.

Figure 5.18. Timeline of inputs and outputs of the STDP learning module (Case 4).

Ultimately, the goal of this module is to sequentially update all the synapses to which the neuron is connected to in order to implement the STDP learning rule. This way, the number of resources needed to implement this system is greatly reduced in comparison to a module that took care of all the synapses of the neural network at once.

## 5.4. SNN Emulation

As explained in the introduction to this chapter, to give the neural network the highest possible flexibility and scalability a modular system of three main entities or digitals modules has been proposed. These are: first, the neuron; second, the AER communication bus; and thirdly, the STDP learning system.

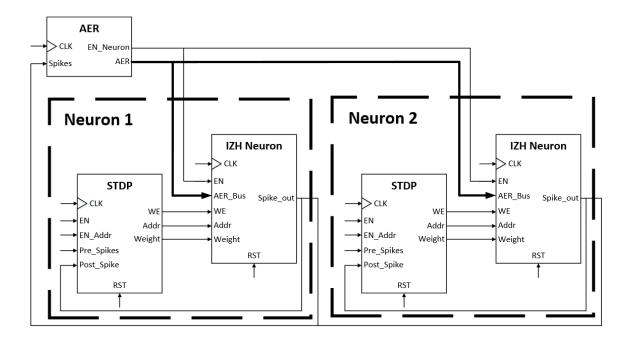

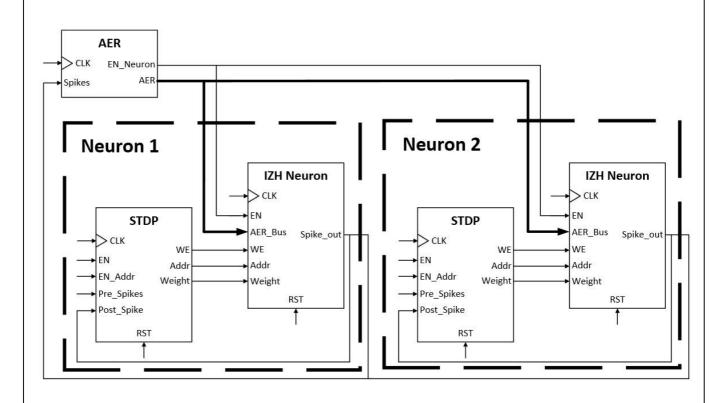

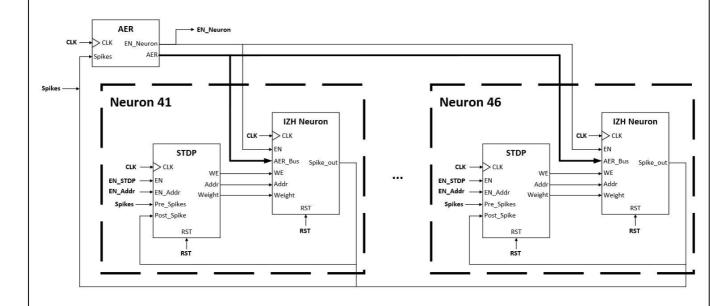

Once explained in the previous sections the internal functionality of each digital block, this section aims to explain how to perform an SNN emulation by interconnecting each one of the proposed digital modules. Meaning, how to connect and replicate these main digital modules in order to obtain a neural network of two, ten or thousands of neurons if the available resources allow it.

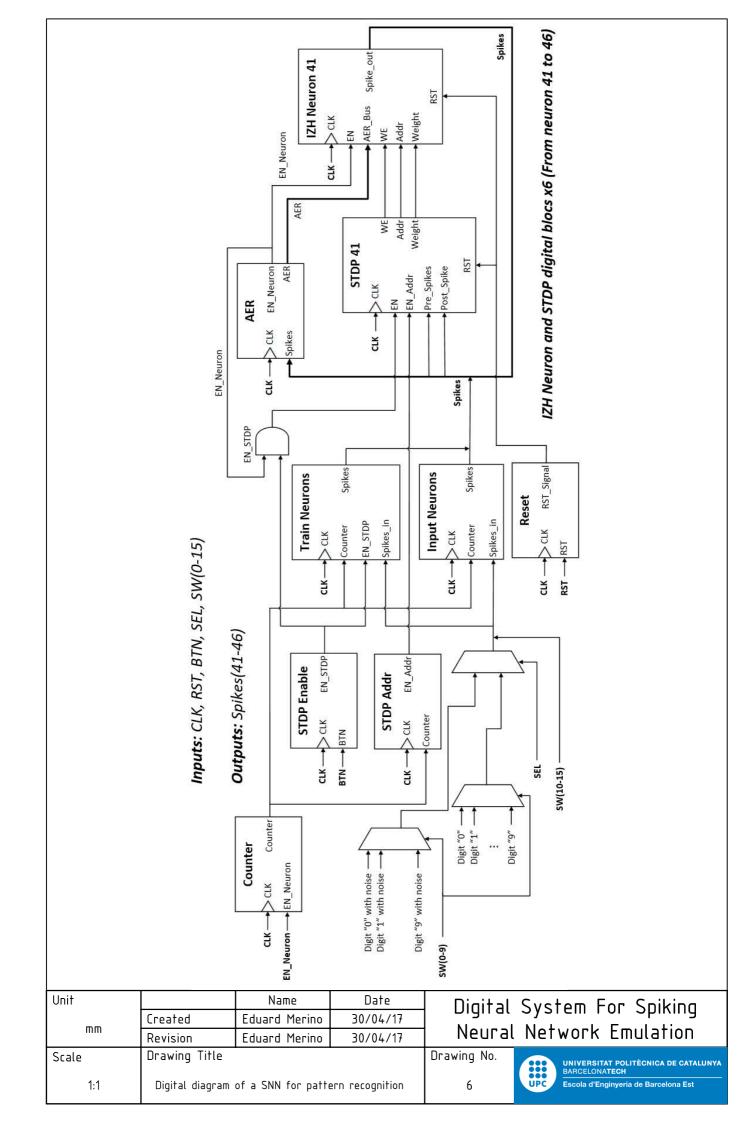

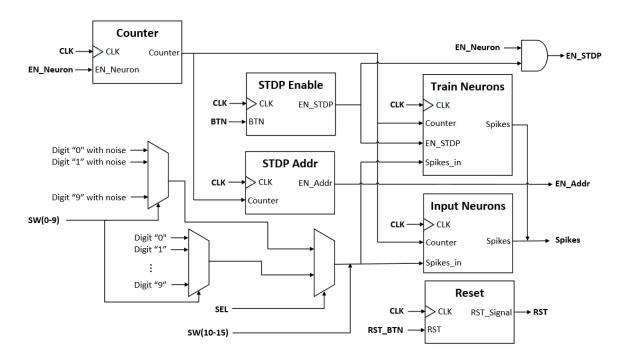

## 5.4.1. Design and architecture

To start with, a neural network made up of several layers is shown in figure 5.19. Firstly, an input layer which receives all external stimuli, second, a variable number of hidden layers that are responsible for performing the operations of the neural network, and then thirdly, an output layer in which the neural network broadcasts its stimuli or responses to the outside.

Figure 5.19. Architecture of a neural network [25].

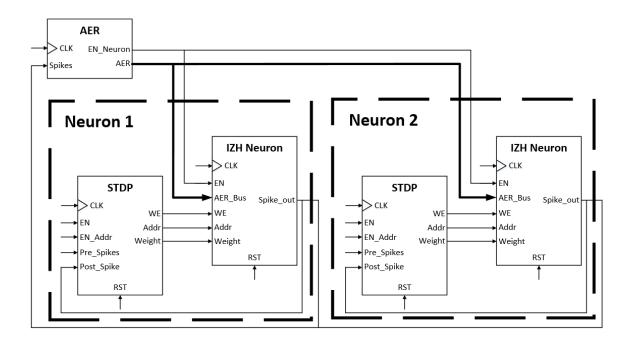

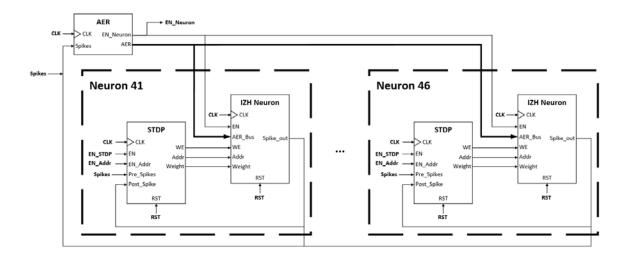

To make it simple, Figure 5.20 shows a neural network of two neurons. However, this architecture allows the implementation of as many neurons as needed.

To begin with, what can be seen is that the AER system is responsible for establishing the communication between all the neurons, i.e. read the spikes to translate them into the appropriate address and transmit them to the AER bus. All neurons are connected to the *EN\_Neuron* signal which allow to stop the activity of the neurons, since as explained before, the AER bus can only transmit one address per clock cycle. Moreover, the neurons of the input layer are merely external stimuli, so the introduction of such into the neural network is done by treating the *spikes* vector.

Additionally, each neuron is formed by its digital module and a STDP learning module. The interconnection between these two is established with the write enable (*WE*), address (*Addr*) and synaptic weight (*Weight*) signals that allow to write in the neuron's RAM.

Figure 5.20. Interconnection of the different blocks for the emulation of SNN of two or more neurons.

Utimately, the STDP modules the *EN* and *EN\_Addr* signals along with the *Pre\_Spikes* signal need to be treated with specific digital blocs. These blocks were not included in the diagram of the Figure 5.20, because they depend either from the layer architecture or the functionality of the neural network to emulate. Therefore, it is not possible to provide a standard solution for the many neural networks that this design can implement. However, in the next chapter a SNN for pattern recognition is proposed where the various blocks that allow the configuration of the STDP modules are explained.

# 6. Pattern recognition with a SNN

Below is simple spiking neural network that is presented as an example to demonstrate the functionality of the design of the previous chapter.

More specifically, it is a SNN with the functionality to recognize patterns and generate a response based on these types of networks, which are mainly used for image processing, for example to identify the letters of the alphabet or the numbers displayed in an image, recognize the movement of an object in a sequence of images or to detect cars in each lane of a motorway.

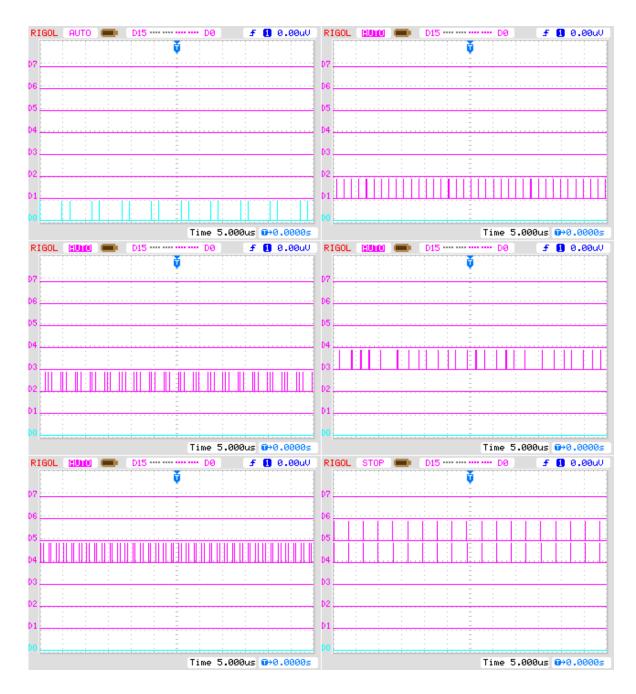

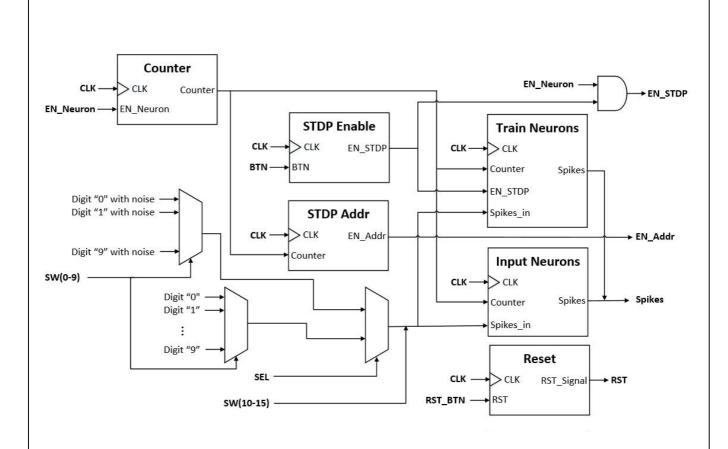

This chapter explains in detail the design of this SNN for pattern recognition beginning with the model of the network used, the patterns to recognize and the training method [20]. Finally, several simulations are carried and the final design is implemented into a FPGA to verify its functionality.

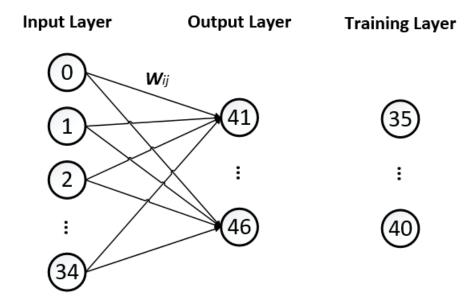

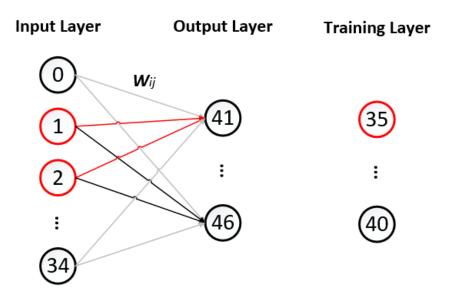

#### 6.1. Neural network model

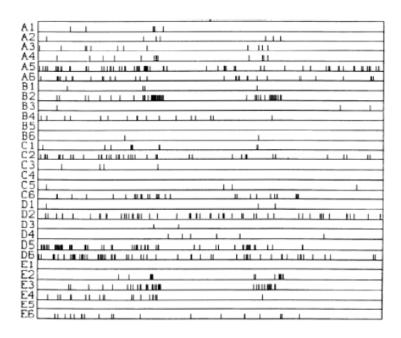

The neural network developed in this project as an example for pattern recognition tasks is presented in Figure 6.1. This network is dedicated to recognizing patterns in images of 5x7 pixels, i.e. 35 pixels.

**Figure 6.1.** Representation of the neural network developed for the recognition of six patterns.

It is composed of three layers, the first two, the input layer and output layer, are the ones that form the functional neural network. In addition, there is an extra layer, called training layer, which functionality will be explained later.

Briefly, the neural network is composed of:

- 35 input neurons corresponding to each pixel of the image.

- 6 output neurons in the output layer corresponding to each pattern. (first neuron corresponding to the first pattern, second neuron to the second pattern...)

- 6 training neurons for each training pattern.

Concisely, the functionality of the neural network is to recognize up to six different patterns depending on the emission of nerve impulses from the corresponding output neuron based on the stimuli of a 35 pixels' image through the input layer.

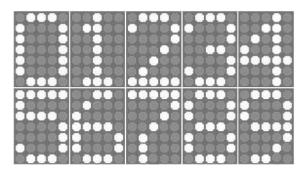

## 6.2. Pattern recognition

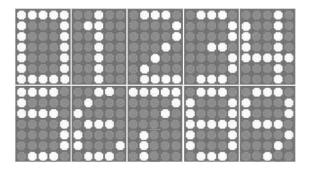

The pattern recognition task consists in differentiate up to six numbers from the digits presented in Figure 6.2. As seen in the picture, each number is represented by a 5x7 pixel image, therefore, can be used to stimulate the input layer of the neural network. Furthermore, because each pixel has a binary representation, black or white, these constitute the existence or absence of nerve stimulation of the input neurons.

Figure 6.2. Input patterns for the neural network stimulation [26].

In short, how to encode the digit corresponding to the zero digit in order to introduce it into the first input layer of the neural network is as follows. Firstly, the first row of five pixels corresponds to the zero to fourth neurons which its vector of spikes is: "01110". Secondly, the second row corresponds to the fifth to ninth neurons which its vector of spikes is: "10001". Finally, following this process a vector with a length of 35 bits is obtained and can be used to stimuli all the neurons of the input layer.

Figure 6.3. Input patterns with noise for the neural network stimulation.

In addition, some noise has been added to the digits presented in Figure 6.2 in order to prove the functionality of the neural network. Therefore, the neural networks should still be able to recognize the corresponding numbers using the digits from Figure 6.3 as stimuli after its training.

# 6.3. Training method

The training method [20] is based on the STDP learning rule, which as explained above, modifies the weights of the synaptic connections depending on the synchrony of firing of the neurons. That is, the synapses that contribute to the generation of an output spike of the neural network should be enhanced, while those not contribution to the generation of an output spikes must be weakened.

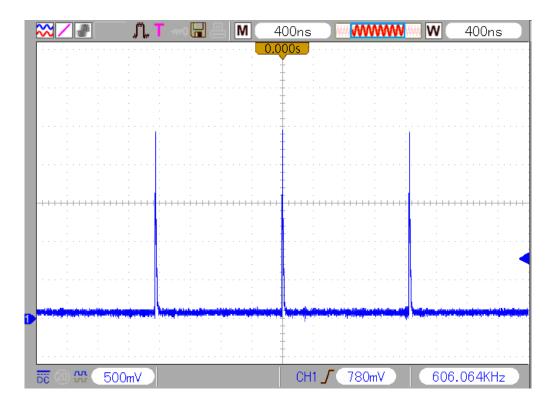

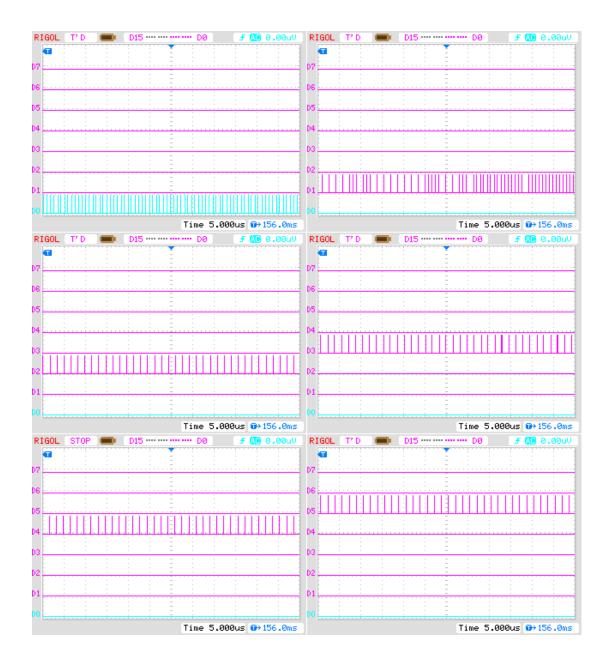

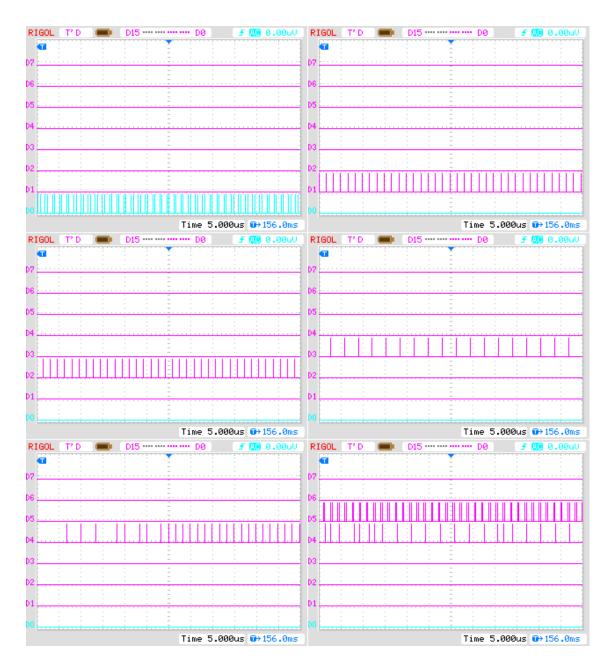

Leveraging the features of the STDP rule, a training layer has been implemented into the neural network that allows to train for each output neuron which pattern must recognize. Meaning, to what digit of Figure 6.2 the neurons needs to generate spikes and remain at rest for others digits.