Black-, Grey-, and White-Box Side-Channel Programming for Software Integrity Checking

by

Hong Liu

M.S., Beihang University, China, 2007

## AN ABSTRACT OF A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

DOCTOR OF PHILOSOPHY

Department of Computer Science College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2017

## Abstract

Checking software integrity is a fundamental problem of system security. Many approaches have been proposed trying to enforce that a device runs the original code. Softwarebased methods such as hypervisors, separation kernels, and control flow integrity checking often rely on processors to provide some form of separation such as operation modes and memory protection. Hardware-based methods such as remote attestation, secure boot, and watchdog coprocessors rely on trusted hardware to execute attestation code such as verifying memory content and examining signatures appearing on buses. However, many embedded systems do not possess such sophisticated capabilities due to prohibitive hardware costs, unacceptably high power consumption, or the inability to update fielded components. Further, security assumption may become invalid as time goes by. For Systems-on-Chip (SoCs), in particular, internal activities cannot be observed directly, while in non-SoCs, sniffing bus traffic between constituent components may suffice for integrity checking.

A promising approach to check software integrity for resource-constrained SoCs is through side-channels. Side-channels have been used mostly for attacks, such as eavesdropping from vibration of glass or plant leaves, fingerprinting machines from traffic patterns, or extracting secret key materials of cryptographic routines using power consumption measurements. In this work, side-channels are used to enhance rather than undercut security. First, we study the relationships between the internal states of a target device and side-channel information. We use the uncovered relationships to monitor the internal state of a running device and determine whether the internal state is an expected one. An unexpected state may be a sign of incorrect execution or malicious activity. To further explore the possibilities inherent in side-channel-based software integrity checking, we investigate various hardware platforms, representative of different degrees of knowledge of the hardware from the side-channel profiling point of view. In other words, sidechannel information is extracted by black-, grey-, and white-box analysis. Each one involves unique challenges requiring different techniques to successfully derive "side-channel profiles". We can use these profiles to detect unexpected states with extremely high probability, even when an adversary knows that their code may be subject to side-channel analysis, i.e., the methodology is robust to side-channel-aware adversaries.

The research includes

- 1. Constructing systematic approaches for black- and grey-box profiling of side channels (and comparing them to white-box analysis);

- 2. Designing custom measurement instrumentation; and

- 3. Developing techniques for monitoring and enforcing software integrity utilizing sidechannel profiles.

We introduce the term "side-channel programming" to refer to techniques we design in which developers explicitly utilize side-channel characteristics of existing hardware to optimize run-time software integrity checking, creating executable code which is more conducive to side-channel-based monitoring. Compared with other software integrity checking techniques, our approach has numerous benefits. Among them are that the measurement process is non-invasive, non-interruptive, and backward-compatible in that it does not require any hardware modification, meaning our approach works with processors that do not include security features. Our method can even be used to augment existing protection mechanism, as it works even when all security mechanisms internal to the device fail. Black-, Grey-, and White-Box Side-Channel Programming for Software Integrity Checking

by

Hong Liu

M.S., Beihang University, China, 2007

## A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

DOCTOR OF PHILOSOPHY

Department of Computer Science College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2017

Approved by:

Major Professor Eugene Y. Vasserman

# Copyright

ⓒ Hong Liu 2017.

## Abstract

Checking software integrity is a fundamental problem of system security. Many approaches have been proposed trying to enforce that a device runs the original code. Softwarebased methods such as hypervisors, separation kernels, and control flow integrity checking often rely on processors to provide some form of separation such as operation modes and memory protection. Hardware-based methods such as remote attestation, secure boot, and watchdog coprocessors rely on trusted hardware to execute attestation code such as verifying memory content and examining signatures appearing on buses. However, many embedded systems do not possess such sophisticated capabilities due to prohibitive hardware costs, unacceptably high power consumption, or the inability to update fielded components. Further, security assumption may become invalid as time goes by. For Systems-on-Chip (SoCs), in particular, internal activities cannot be observed directly, while in non-SoCs, sniffing bus traffic between constituent components may suffice for integrity checking.

A promising approach to check software integrity for resource-constrained SoCs is through side-channels. Side-channels have been used mostly for attacks, such as eavesdropping from vibration of glass or plant leaves, fingerprinting machines from traffic patterns, or extracting secret key materials of cryptographic routines using power consumption measurements. In this work, side-channels are used to enhance rather than undercut security. First, we study the relationships between the internal states of a target device and side-channel information. We use the uncovered relationships to monitor the internal state of a running device and determine whether the internal state is an expected one. An unexpected state may be a sign of incorrect execution or malicious activity. To further explore the possibilities inherent in side-channel-based software integrity checking, we investigate various hardware platforms, representative of different degrees of knowledge of the hardware from the side-channel profiling point of view. In other words, sidechannel information is extracted by black-, grey-, and white-box analysis. Each one involves unique challenges requiring different techniques to successfully derive "side-channel profiles". We can use these profiles to detect unexpected states with extremely high probability, even when an adversary knows that their code may be subject to side-channel analysis, i.e., the methodology is robust to side-channel-aware adversaries.

The research includes

- 1. Constructing systematic approaches for black- and grey-box profiling of side channels (and comparing them to white-box analysis);

- 2. Designing custom measurement instrumentation; and

- 3. Developing techniques for monitoring and enforcing software integrity utilizing sidechannel profiles.

We introduce the term "side-channel programming" to refer to techniques we design in which developers explicitly utilize side-channel characteristics of existing hardware to optimize run-time software integrity checking, creating executable code which is more conducive to side-channel-based monitoring. Compared with other software integrity checking techniques, our approach has numerous benefits. Among them are that the measurement process is non-invasive, non-interruptive, and backward-compatible in that it does not require any hardware modification, meaning our approach works with processors that do not include security features. Our method can even be used to augment existing protection mechanism, as it works even when all security mechanisms internal to the device fail.

# Table of Contents

| Lis | st of l    | Figures  |                                                         | xi  |  |

|-----|------------|----------|---------------------------------------------------------|-----|--|

| Lis | st of [    | Tables   |                                                         | iii |  |

| Ac  | know       | ledgem   | ents                                                    | iii |  |

| De  | edicat     | ion      |                                                         | civ |  |

| 1   | Intro      | oduction | n                                                       | 1   |  |

|     | 1.1        | Organ    | ization                                                 | 4   |  |

| 2   | Background |          |                                                         |     |  |

|     | 2.1        | Hardw    | vare platforms and security problems                    | 5   |  |

|     | 2.2        | Softwa   | are integrity checking                                  | 7   |  |

|     |            | 2.2.1    | External verifier versus internal verifier              | 8   |  |

|     | 2.3        | Side cl  | hannels                                                 | 12  |  |

|     |            | 2.3.1    | White-box analysis of side-channels                     | 13  |  |

|     |            | 2.3.2    | Side-channel analysis with limited knowledge of devices | 15  |  |

|     | 2.4        | Statist  | tics and mathematical background                        | 18  |  |

|     |            | 2.4.1    | Pattern matching                                        | 18  |  |

|     |            | 2.4.2    | Mathematical modeling                                   | 21  |  |

|     |            | 2.4.3    | Variable selection                                      | 23  |  |

| 3   | Blac       | k-box A  | Analysis                                                | 26  |  |

|     | 3.1        | Relate   | ed work                                                 | 26  |  |

|   | 3.2  | Problem definition                                                                                                   |

|---|------|----------------------------------------------------------------------------------------------------------------------|

|   |      | 3.2.1 Threat model                                                                                                   |

|   |      | 3.2.2 Experiment setup                                                                                               |

|   | 3.3  | A systematic approach for instruction-level side-channel analysis                                                    |

|   |      | 3.3.1 Semantic models $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 32$                                   |

|   | 3.4  | Side-channel models                                                                                                  |

|   |      | 3.4.1 Side-channel models of instruction operations                                                                  |

|   |      | 3.4.2 Side-channel models of internal states                                                                         |

|   |      | 3.4.3 EM measurement $\ldots \ldots 51$ |

| 4 | Side | -channel Programming                                                                                                 |

|   | 4.1  | Side-channel constrained transitions                                                                                 |

|   | 4.2  | Heuristics                                                                                                           |

|   | 4.3  | Graph of side-channel programs                                                                                       |

|   |      | 4.3.1 Random initial GPRs                                                                                            |

|   |      | 4.3.2 Zero initial GPRs                                                                                              |

|   | 4.4  | Other heuristics                                                                                                     |

| 5 | Grey | y-box Analysis                                                                                                       |

|   | 5.1  | Background                                                                                                           |

|   | 5.2  | Related work                                                                                                         |

|   |      | 5.2.1 White-box analysis of FPGA side-channels                                                                       |

|   |      | 5.2.2 Empirical models of FPGA side-channels                                                                         |

|   | 5.3  | Problem definition                                                                                                   |

|   |      | 5.3.1 Threat model $\ldots$ $74$                                                                                     |

|   | 5.4  | Experimental setup                                                                                                   |

|   | 5.5  | The test code and SoC test targets                                                                                   |

|   |      | 5.5.1 System A: NIOS II-based SoC                                                                                    |

|    |        | 5.5.2    | System B: Resource-constrained NIOS II-based SoC                                               | 79  |

|----|--------|----------|------------------------------------------------------------------------------------------------|-----|

|    |        | 5.5.3    | System C: OpenMSP430-based SoC                                                                 | 79  |

|    |        | 5.5.4    | Test code                                                                                      | 79  |

|    | 5.6    | Model    | ing side-channels                                                                              | 80  |

|    |        | 5.6.1    | Black-box analysis                                                                             | 81  |

|    |        | 5.6.2    | Grey-box analysis                                                                              | 82  |

|    | 5.7    | Valida   | tion $\ldots$ | 85  |

|    | 5.8    | Apply    | ing results to software integrity checking                                                     | 94  |

| 6  | Disc   | ussion a | and Future Work                                                                                | 101 |

| Bi | bliogr | aphy     |                                                                                                | 104 |

# List of Figures

| 2.1 | General software integrity checking problem with explicit communication chan-                                          |    |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

|     | nels and side-channels                                                                                                 | 8  |

| 2.2 | Lumped-C model of a CMOS inverter <sup>1</sup> $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 13 |

| 3.1 | The instruction set of PIC16F687 <sup>2</sup> $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$           | 29 |

| 3.2 | Measurement setup                                                                                                      | 31 |

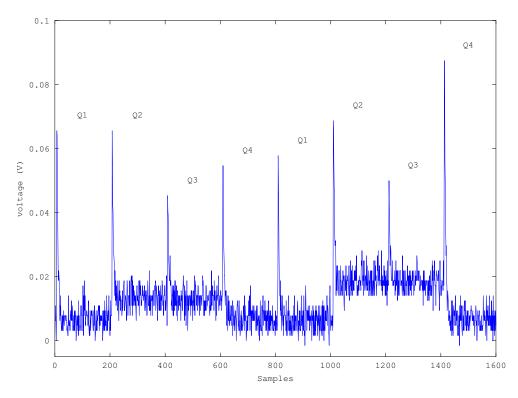

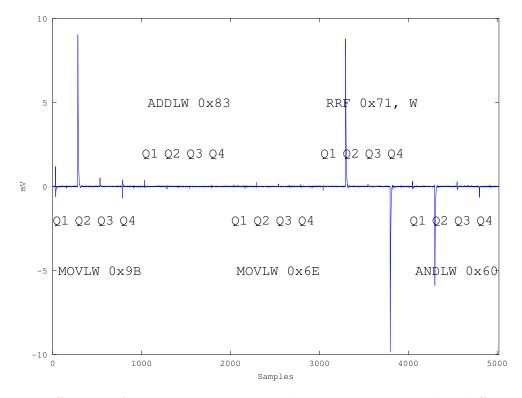

| 3.3 | A single-captured waveform of executing "MOVLW $\texttt{0x69}"$ and "ADDWF $\texttt{0x40,F}"$                          | 40 |

| 3.4 | Difference of two measurements with the same program but different register                                            |    |

|     | values.                                                                                                                | 43 |

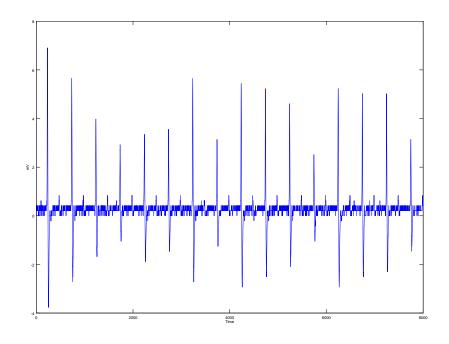

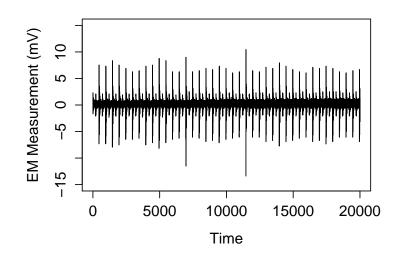

| 3.5 | A typical single-captured EM radiation of the target chip                                                              | 51 |

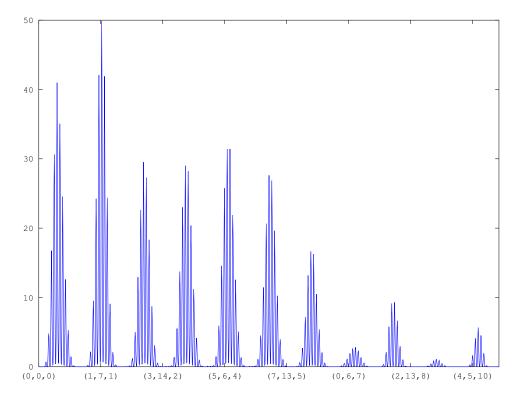

| 4.1 | The average size of search trees for one instruction cycle: the x-axis is $(q2, q3, q4)$                               |    |

|     | (ranges $(0, 0, 0), (1, 0, 0), \dots, (8, 14, 10)$ ); the y-axis is the average number of                              |    |

|     | nodes of the resulting search trees.                                                                                   | 63 |

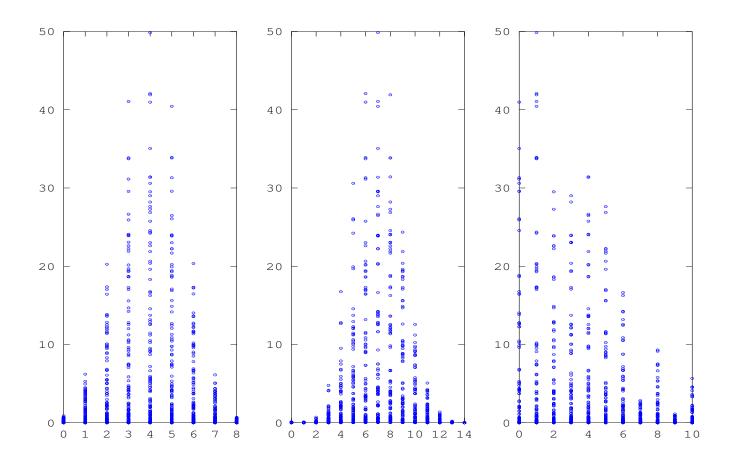

| 4.2 | The size of search trees after one instruction cycle versus $q2$ , $q3$ , and $q4$ ,                                   |    |

|     | respectively. The x-axis is $q2$ , $q3$ , or $q4$ ; the y-axis is the number of nodes of                               |    |

|     | the resulting search trees.                                                                                            | 64 |

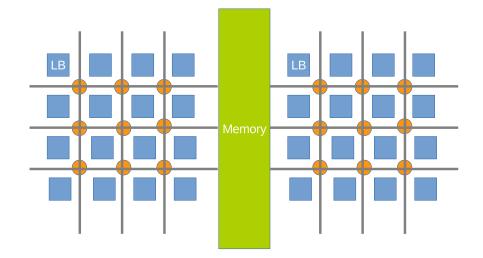

| 5.1 | FPGA architecture with logic blocks depicted as blue squares; logic blocks are                                         |    |

|     | surrounded by routing channels; several logic blocks have a dedicated memory                                           |    |

|     | column in-between.                                                                                                     | 71 |

| 5.2 | Electromagnetic measurement                                                                                            | 76 |

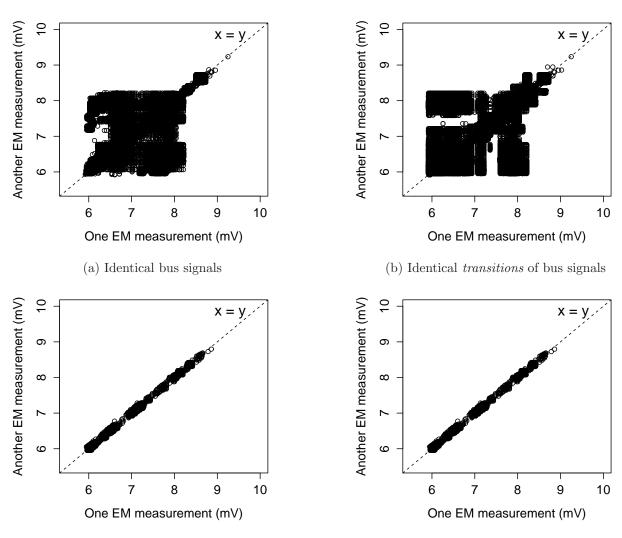

| 5.3 | Measurements of system A when a subset of internal signals are identical                                               | 84 |

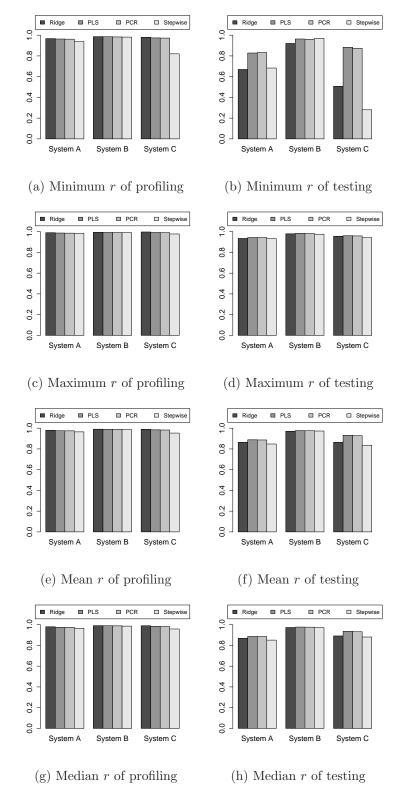

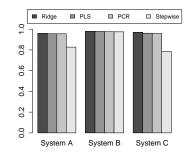

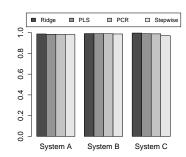

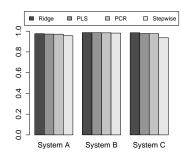

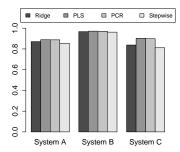

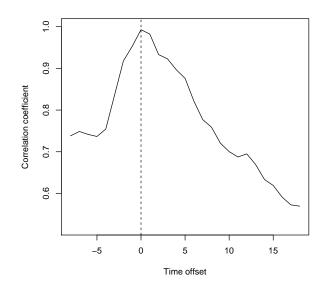

| 5.4  | Pearson's $r$ for model validation, with the profiling (modeling) results to the  |    |

|------|-----------------------------------------------------------------------------------|----|

|      | left and the testing (on another chip) results to the right; from the darkest     |    |

|      | bar to the lightest are ridge regression, PLS, PCR, and stepwise regression       | 86 |

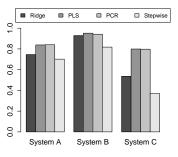

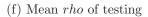

| 5.5  | Spearman's $rho$ for model validation, with the profiling (modeling) results to   |    |

|      | the left and the testing (on another chip) results to the right; from the darkest |    |

|      | bar to the lightest are ridge regression, PLS, PCR, and stepwise regression       | 87 |

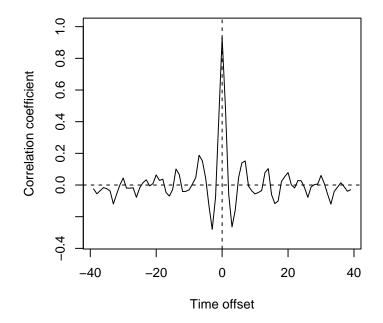

| 5.6  | Correlation of model prediction and measurement with sliding time window          |    |

|      | during profiling; the x-axis is the time offset, and the y-axis is Pearson's $r$  |    |

|      | computed from the actual measurement and the model prediction which has           |    |

|      | an offset in time.                                                                | 89 |

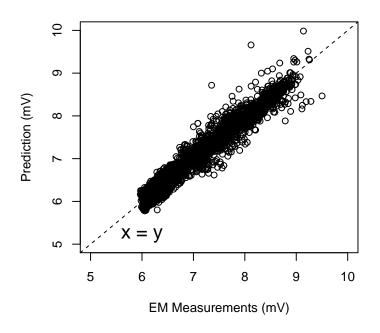

| 5.7  | Model prediction and measurements for the best PLS model of system A $$           | 90 |

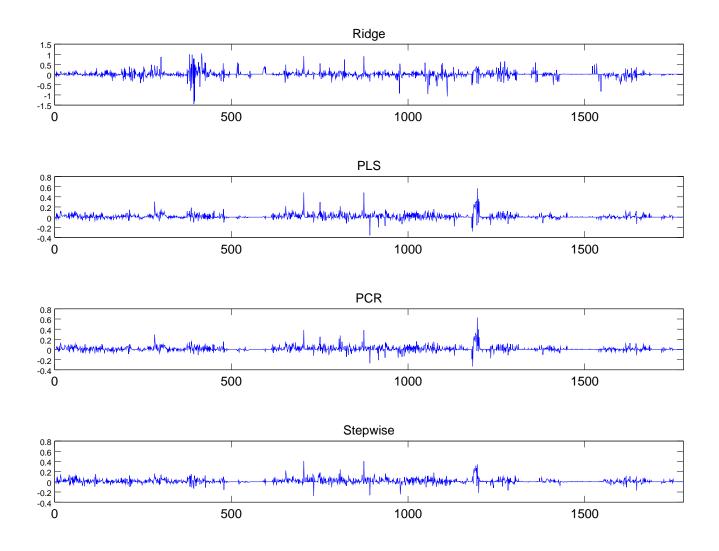

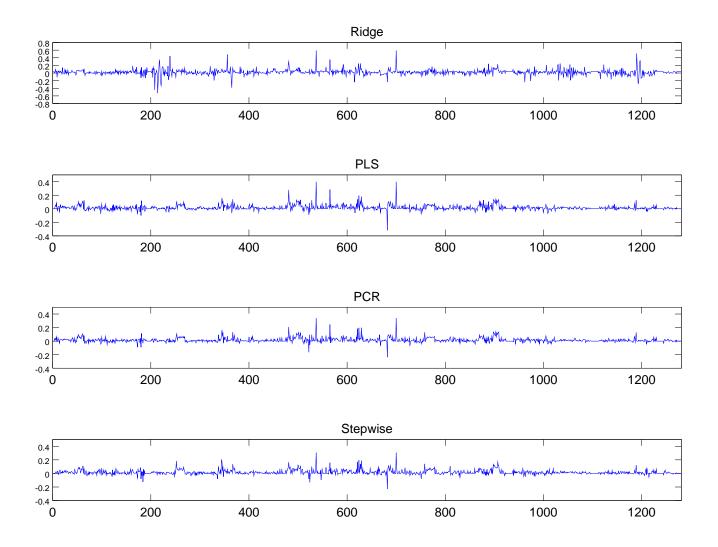

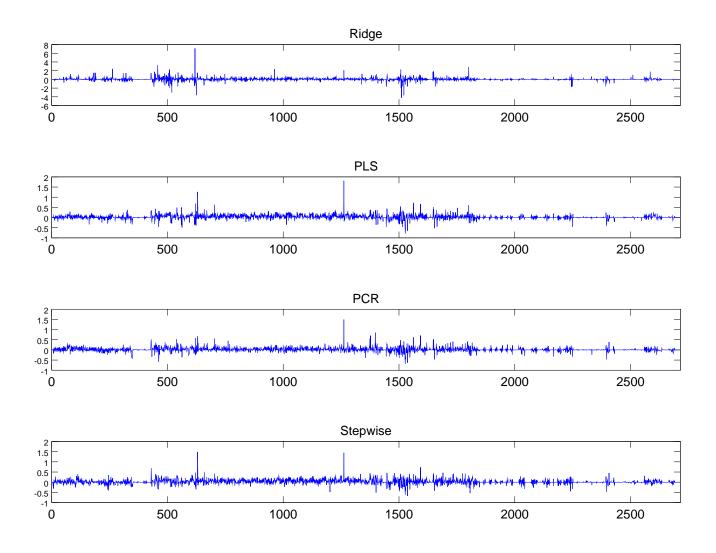

| 5.8  | The coefficients of the best models for system A, excluding the constant; from    |    |

|      | the top to bottom are coefficients of ridge, PLS, PCR, and stepwise regression,   |    |

|      | respectively.                                                                     | 91 |

| 5.9  | The coefficients of the best models for system B, excluding the constant          | 92 |

| 5.10 | The coefficients of the best models for system C, excluding the constant          | 93 |

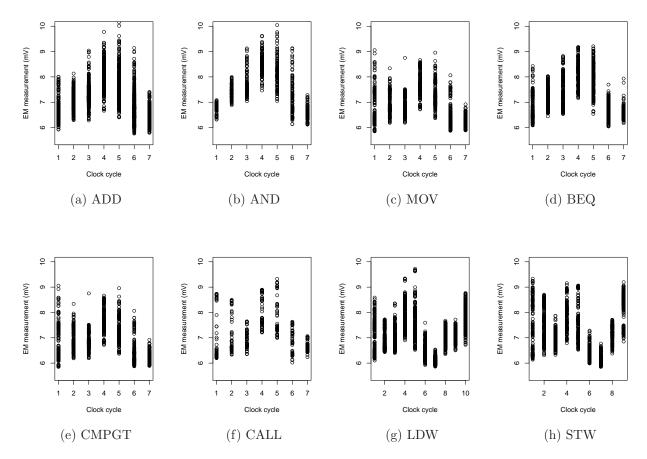

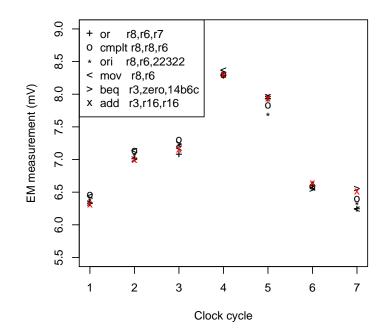

| 5.11 | EM measurements of instructions grouped by operations for system A; x-axis        |    |

|      | is the number of clock cycles; y-axis is the EM measurement                       | 97 |

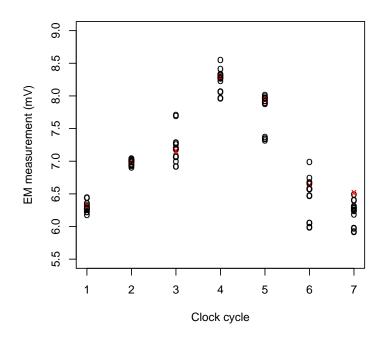

| 5.12 | EM measurements of add r3,r16,r16 for system A; red cross indicates the           |    |

|      | same instance of executing add r3,r16,r16                                         | 99 |

# List of Tables

| 3.1 | Regression analysis of power consumption in $Q2$                                                                                                                     | 46 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Regression analysis of power consumption in Q4                                                                                                                       | 48 |

| 3.3 | Regression analysis of EM radiation in Q2                                                                                                                            | 52 |

| 3.4 | Regression analysis of EM radiation in Q4                                                                                                                            | 53 |

|     |                                                                                                                                                                      |    |

| 5.1 | False positive rates (%) for a(n) (aligned) single-captured EM trace                                                                                                 | 95 |

| 5.2 | False negative rates (%) for an aligned single-captured EM trace $\ldots$                                                                                            | 95 |

| 5.3 | False negative rates (%) for an arbitrary single-captured EM trace $\ldots$                                                                                          | 95 |

| 5.4 | Class separability $J$ for system C $\ldots \ldots $ | 98 |

## Acknowledgments

I owe a lot of thanks to my academic advisor, Professor Eugene Y. Vasserman. Without him, I would not have entered the amazing world of cyber security. He has been so helpful and supportive throughout my time as his PhD student. I would not have accomplished anything without his inspiring advice, encouragement, and patience. I feel very lucky to have such a great advisor.

I would also like to thank many of the professors of the Computer Science Department, as well as the professors of the Electrical and Computer Engineering Department for their great teaching, valuable discussion and help. I owe many thanks to Professor Bala Natarajan, Professor William Hsu, and Professor Steven Warren for their suggestions and concrete help in improving my research. I would also like to thank Professor Mitchell Neilsen and Professor Yurii Maravin for reading my dissertation and giving me insightful comments.

I would like to thank my laboratory mates and friends at the Computer Science Department for their generous help both in my research and in my life. They have brought so much fun to my PhD study and have made my life so much easier.

I would like to thank my family for their support and love, without which it would not have been possible for me to devote so much time and energy to my study and research. My love to them is the drive of my work.

Finally, I would like to thank the NSF grants that have made the research possible: NSF CNS 1253930 and NSF CNS 1224007.

# Dedication

Dedicated to the humane treatment of animals

# Chapter 1

# Introduction

Electronic devices have become an integral part of our everyday life. From computers to electric cars to insulin pump to Process Logic Controls (PLCs) in industry, most electronic devices nowadays are cyber systems which are composed of one or more processors and are controlled by software. Since many of these devices are essential to our safety and well-being, verifying their integrity is an important task. Developers traditionally focus on realizing device functionality, while ignoring the fact that an attacker can change the behavior of a device by overwriting its program and/or data locally or remotely.<sup>3</sup>

Verifying software integrity is challenging. First, cyber devices are of great variety. They may be composed of general-purpose microprocessors, graphics processing units (GPUs), microcontrollers ( $\mu$ Cs), digital signal processors (DSPs), complex programmable logic devices (CPLDs), field programmable gate arrays (FPGAs), or diverse application-specific integrated circuits (ASICs). The processor architecture may be von Neuman or Harvard, the instruction set may be reduced instruction set computer (RISC) or complex instruction set computer (CISC), the word size may be 8-bit or 64-bit, pipelining may be none or super-scalar, caches may be zero or several megabytes, etc. While the variety of cyber systems helps in preventing "single point of failure" in which a security breach of one processor will affect all systems, it also limits the applicability of any security mechanisms. For example, the security problems of FPGAs are very different from those of microprocessor-based systems.<sup>4;5</sup>

Second, many cyber devices are designed to realize special functionality, and are often of very restricted resources. These devices are loosely referred to as "embedded systems". The term "embedded" means the device is a system embedded within a larger system. Typical embedded systems are the control unit of an electronic thermostat that determines when to stop boiling the water, the Electronic Brake Control Module of a car that controls how to lock brakes, and the reactor shutdown unit of a nuclear power plant that decides whether to terminate the reactor in an emergency so that the entire town can be saved from meltdown. Since these devices are designed to accomplish very specific tasks, they are often very small and highly optimized systems that may consist of an 8-bit processor and several kilo-bytes of memory. The simplicity of these systems, especially the common missing of security mechanisms in legacy devices, facilitates tampering. To guarantee integrity of these systems, without updating them with sophisticated but costly processors or security modules, requires innovative work.

In this thesis, several integrity checking approaches are presented with the goal of ensuring software integrity on various hardware platforms. These approaches are based on "side-channels" of a device. Side-channels can be defined as any channels that are not the main communication channel of a device. The term "side" is used to infer that the channel carries information as a side-effect of running desired functionality on a physical device. Common side-channels are power consumption, electromagnetic radiation, timing and quantity of traffic, thermal and light imaging, object vibrations and movement, etc.<sup>6–10</sup> There are also some uncommon side-channels, such as processor cache misses and the /proc virtual filesystem. Historically, side-channels have been used for a long time to penetrate a seemingly closed system. Here they are used instead for constructive purpose – checking software integrity of diverse devices in which security mechanisms have not ever been built in.

There are two types of integrity checking schemes that are proposed in this thesis. One is pure passive, which does not require the target device to modify its hardware *or* software. The other is a design-for-security scheme in which software of a device is rewritten based on the side-channel characteristics of its hardware so that the integrity of the software can be verified during device execution. Both schemes do not require modification of hardware or interruption of device execution. The second scheme is useful in scenarios where the first scheme is not applicable due to side-channel features of the target hardware.

The side-channel-based software integrity checking schemes proposed in this thesis are external to the target device (c.f. Section 2.2.1). The idea is to first extract side-channel information and correlate it with the internal state of a running device, and then verify real-time side-channel emanations of the target device against desired values, without any explicit checking procedures within the device. Compared with other software integrity checking techniques, this approach has numerous advantages, such as incurring low or no overhead to existing systems, easy to deploy and upgrade the verification algorithms, no interruptions of normal execution, low or no visibility to attackers who penetrate the target device, applicable to legacy and deployed systems. An external verifier is more robust than internal verifiers which are confined by the hardware resources of the target device. A verifier that constantly observe the runtime behavior of the target device is able to defend against more sophisticated attacks such as code-reuse attacks and data-based attacks. In particular, security assumptions always weakens with time. The side-channel-based methods can detect tampering and verify validity of security assumptions without modifying original systems, given that side-channel analysis of the system proves so.

However, this approach poses significant challenges. First, we usually only have very limited knowledge of the target hardware platforms. Very little information can be derived for side-channel profiling from the released documents by the hardware manufacturers. Second, noise plays an important role in the success of our study. We must carefully design experimental instrumentation and data processing algorithms to minimize the effect of noise. Third, our integrity checking approach must be accurate enough to deal with compact malware that is potentially as short as a single instruction. Fourth, we must be able to secure against side-channel-aware attackers who may write malware that minimizes side-channel deviations. Last but not least, our verification approach must be realistic. Although it is theoretically possible to verify every aspect of an integrated circuit through micro-probing and microscoping, it is not practical to perform such analysis on every device that needs integrity checking, due to the high cost of testing equipment and time and expertise needed to perform such verification.

In this thesis, the feasibility and generality of using side-channels for software integrity checking in diverse hardware platforms is explored. Since increasing side-channel leakage may violate EMI/EMC requirements. We have not made any effort to increase side-channel emanations but have instead measured the inherent side-channels of a target device. A systematic approach is present for efficiently analyzing side-channel characteristics of a target device over the entire instruction set. The effectiveness of this approach is shown by clockcycle-accurate side-channel profiling of various SoCs with different degrees of knowledge on the system. The performance of the proposed side-channel-based software integrity checking schemes is quantified by the very low probability that a tampering is not detected from sidechannel measurements, given both conventional attackers and side-channel-aware attackers who actively try to evade side-channel-based integrity checking.

### 1.1 Organization

Chapter 1 gives a brief introduction of the motivation. The background information and common related work are given in Chapter 2. Chapter 3 describes the approach to profile the side-channel emanations of a microcontroller with high accuracy that enables side-channelbased software integrity checking. Based on the side-channel-model obtained in Chapter 3, Chapter 4 proposes a novel Design-for-Security approach that utilizes side-channel characteristics of a black-box device to write code with guaranteed integrity. Chapter 5 presents the research of side-channel-based software integrity checking on a distinct hardware platform – FPGA. Three different SoCs implemented on the FPGA are studies to show the effectiveness, efficiency, and generality of the proposed approach. Finally, Chapter 6 summarizes the thesis and gives the future work.

## Chapter 2

## Background

### 2.1 Hardware platforms and security problems

One of the major difficulties in securing cyber systems is diversity. Early systems are composed of separate components, and it is easy to observe the structure and model of the system. It is also easy to analyze the functionality of the system by sniffing the signals between components (chips). From the perspective of software integrity checking, this system organization is beneficial in that the designers and testers can identify tampering and faults conveniently by using low-cost tools such as oscilloscopes and logic analyzers. On the other hand, attackers can reverse-engineer and clone the system in the same way.

With the emergence of microcontrollers, the CPU, memory, and common peripherals become integrated in a single chip package. Such a system is called System-on-a-Chip (SoC) and has become very common in cyber devices, especially embedded systems. Today's SoCs are composed of not only the traditional digital parts such as the processor, memory and popular I/O controllers, but also analog and mixed-signal parts including oscillators and phase-locked loops (PLL), analog-to-digital converters (ADCs), digital-to-analog converters (DACs), temperature sensors, and radio-frequency units to interface with WiFi, Bluetooth, and ZigBee wireless networks. Programmable hardware, such as CPLDs and FPGAs, has also become more favorable to SoC designs, by integrating "hard-core" processors and analog components such as ADCs and DACs. By combining most components into one silicon substrate and by controlling the device with software stored in internal memory, SoCs are hard to reverse-engineered using traffic sniffing. Debugging and examining runtime signals are at the meantime difficult, if not using built-in debugging mechanisms such as JTAG.

However, it is not at all impossible to observe the internal structure and signals of SoCs. At the lowest level, wafer fabrication plants and chip manufacturers are equipped with process control and failure analysis tools such as scanning electron microscopes (SEMs), transmission electron microscopes (TEMs) and focused ion beam (FIB) machines that are able to examine and modify nanometer scale structures.<sup>11;12</sup> Microprobing can measure the state of a SRAM cell or even transistor.<sup>13–15</sup> Often the plastic package of the chip is etched off in a corrosive acid solution, e.g., hot fuming nitric acid. For hermetic and ceramic packages, mechanical or thermal treatment may be used.<sup>12</sup> The silicon may be accessed from the back side of the chip, or the metal layers need to be removed layer by layer.<sup>11</sup> These techniques are the "ultimate" tools for analyzing or modifying target cells or transistors, especially memory cells that store secret keys or security fuses. They however require invasive access to the DUT and very expensive equipment which is not available for ordinary companies and university labs. Another disadvantage is that these techniques do not scale well for large circuits when design details are unknown. Today's ultra-large-scale integration (ULSI) circuits may be composed of hundreds of millions of CMOS transistors. The cost of a full chip reverse engineering is estimated to be around 100 thousands of Euros for a 130nm technology chip containing 100k logic gates.<sup>16</sup>

Semi-invasive analysis only requires depackaging the chip with the passivation layer intact.<sup>11;17;18</sup> Semi-invasive techniques require less expensive equipment but can achieve similar degree of control over the DUT. It is possible to extract information from internal memory such as SRAM and EEPROM, and to modify SRAM content and change the state of any individual CMOS transistor.<sup>11</sup>

By using invasive and semi-invasive analysis, it is fundamentally possible to verify the integrity of any cyber device, since every internal signal can be read out given enough time and equipment. In practice, however, such analysis is too expensive, especially for longterm and bulk verification. In addition, it is not practical to apply semi-invasive analysis or invasive analysis for software integrity checking of deployed devices.

One solution is to combine invasive and semi-invasive analysis with non-invasive analysis. Non-invasive analysis often utilizes "side-channel" emanations of a device to infer its internal activities. Side-channel information such as power consumption, temperature, and electromagnetic emanations can be easily measured using low-cost equipment and non-invasive access to the chip. In<sup>19</sup>, authors propose the use of side-channel profiles of chips to test against a "golden sample" for hardware trojan detection. The golden sample is a reference chip whose genuineness is verified by invasive analysis. Very often a great amount of information can be obtained solely from non-invasive analysis. In this thesis, all experiments are performed by using non-invasive access, low-cost equipment, and passive measurement, and are favorable to legacy and deployed systems.

## 2.2 Software integrity checking

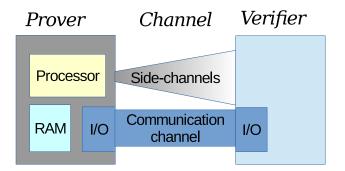

We define the general software integrity checking problem as follows. There are two parties: a prover P, a device-under-test (DUT) running the target application software S, and a verifier V, a trusted entity who would like to determine whether P runs S or S', which may be a different piece of code or original code but in an unintended execution state. P and V communicate over an explicit channel C and a side-channel E, as shown in Figure 2.1. V bases its judgment on evidence that P provides directly (e.g., by signatures) over C or indirectly (e.g., by timing or EM radiation), over E. V knows the initial configuration of P, including hardware and software.

The problem model can be instantiated in numerous ways. In a microcontroller-based system, as considered in Chapter 3 and 4, S is naturally the software running on the microcontroller, and P is the hardware including the microcontroller chip and the printed circuit board (PCB). In an FPGA-based system, as considered in Chapter 5, the situation is a bit more complex, since for FPGAs, both the hardware and the software are programmable. The FPGA configuration logic describes both the hardware (processor, memory, IO, etc.) of

Figure 2.1: General software integrity checking problem with explicit communication channels and side-channels

the system implemented on an FPGA chip, as well as the application software that runs on the system. Since there are many methods to prevent reconfiguration of an FPGA device (c.f. Section 5.3), S is therefore defined as the application software, and P incorporates the PCB, the FPGA chip, and the FPGA configuration logic describing the hardware of the system.

#### 2.2.1 External verifier versus internal verifier

Many approaches have been proposed to enforce software integrity. They can be classified by where the verifier resides. An *internal* verifier performs integrity checking in the same device with the target software and thus shares hardware resources with the software, whereas an *external* verifier does its job outside the device and therefore often has unbounded resources.

#### Internal verifiers

Internal verifiers can be either software or hardware. Conventional anti-virus software and intrusion detection/protection systems are most common software-based internal verifiers that protect or detect tampering of system software and memory by identifying software signatures, verifying checksums, analyzing traffic and software behaviors, etc. Hypervisors<sup>20–22</sup>, separation kernels<sup>23</sup>, mandatory access control<sup>24;25</sup>, and control flow integrity<sup>26–28</sup>, are more recent internal software-based approaches that provide more confined environments for un-

trusted software and/or restrict software behaviors in a finer granularity. The common property of software-based internal verifiers is that the verifier shares the same hardware with the target software. A verifier that runs on the main CPU of a system therefore cannot detect tampering on the peripherals (e.g., the Ethernet card<sup>29</sup>). In addition, usually software-based internal verifiers detect or prevent "anomalous behavior" of programs by utilizing hardware security features that provide some form of separation such as different operation modes and memory protection. While modern computers possess sophisticated processors that have rich security features, cyber devices as a whole often cannot afford such a processor because of cost, power, or space constraints. It is not uncommon that an embedded system only has an 8- or 16-bit processor that does not even support integer multiply operation. Many software-based approaches that rely on hardware-supported separation are therefore not applicable to such devices.

Software Symbiote<sup>30</sup> is a noteworthy software-based internal verifier that does not rely on sophisticated processors. Its idea is to insert verification code duplicates, which perform self-checksumming, into host software so that the code gets executed from time to time and will trigger an alarm when checksums are different. The major weakness of Symbiote is that the verification code can be inactivated or even removed by a sophisticated attacker who is aware of the existence of such a protection mechanism, as no protection on the verification code itself can be guaranteed if a processor lacks appropriate security features.

Another weakness that all software-based internal verifiers share is that the verifier competes for resources with the target software. For cyber devices that perform real-time tasks, the designers must carefully balance security and real-time requirements, in which case security is often the one that is sacrificed.

Unlike software-based approaches, hardware-based internal verifiers build dedicated hardware components for software integrity checking and are more or less invisible to the software under test. Example verifiers include watchdog coprocessors<sup>31;32</sup>, secure boot, and dynamic root of trust.<sup>33</sup> Often the trusted hardware implements some cryptographic routines and stores sensitive information such as secret keys. The hardware is responsible for verifying checksums and signatures of code, such as BIOS code and firmware, and executes the code

only if the checksum/signature is valid. It may also send out alarms to remote servers if tampering is detected. In particular, trusted platform module  $(TPM)^{34;35}$  is a security chip that exists in most enterprise-grade personal computers and costs for only around 1 dollar.<sup>35</sup> A TPM measures itself, BIOS code, the master boot record, etc., and stores integrity checksums in Platform Configuration Registers (PCRs), which is a protected memory. A verifier asks the TPM for a signed copy of the PCRs to evaluate the boot sanity. As we all see, the existence of TPMs does not guarantee that our computers are not tampered. This is because TPM is a passive device that is operated by code running on the main CPU.<sup>35</sup> At best, it can only be used to guarantee that the boot procedure of a system is clean. If the system is breached after boot, secure boot with the TPM cannot detect or prevent malicious behavior. Instead, dynamic root of trust such as Intel  $TXT^{36}$  and AMD  $SVM^{37}$  performs attestation on the current state of the software by utilizing specific CPU instruction which resets the TPM PCRs. Nevertheless, verification on solely code integrity is vulnerable to code-reuse attacks, such as return-into-libc<sup>38</sup>, Return-Oriented Programming<sup>39</sup>, and Jump-Oriented Programming<sup>40</sup>, which execute original code but in undesired order. It is also vulnerable to the even more sophisticated data-only attacks<sup>41</sup>, which execute original code in normal order but with wrong data. At a finer granularity, a coprocessor can be used to examine the runtime code that appears on buses and verify integrity by matching code patterns. If carefully designed, such a coprocessor can detect code-reuse attacks and data-only attacks. In general, hardware-based internal verifiers are more powerful than software-based internal verifiers, at the cost of additional hardware and/or more complex CPU and chipset support. It is also more difficult to deploy new hardware or fix hardware flaws.

#### **External verifiers**

The verifier can also be outside of the DUT. Compared to internal verifiers, external verifiers do not compete for resources with the normal software, or require additional hardware, and it is much easier to deploy and update an external verifier. External verifiers also have minimal visibility to attackers who penetrate the device. Moreover, a verifier that is external to a device is the only possible integrity verifier when all the security mechanisms internal to the device fail, or do not even exist.

On the other hand, since the verifier is external to the DUT, it is possible to perform "proxy attack" in which the attacker asks another device/component (proxy), instead of the tampered one, to help provide integrity proof to the verifier. Some mechanism must be used to authenticate the source of the integrity proof.

Software attestation  $^{42-44}$  is a software integrity checking scheme that relies on an external verifier. Compared to other integrity checking schemes, it has an advantage in requiring no sophisticated hardware security features or hardware modification, which makes it applicable to legacy devices. Software attestation assumes that an external verifier has direct access to the DUT – the device and integrity measurement channel are authenticated out-of-band by for example visual inspection. When attestation begins, the verifier asks the DUT to put the device to a known state and compute a checksum of the memory of the device, using a nonce provided by the verifier. The verifier tests the returned checksum and the time for the DUT to compute the checksum, so that any tampering of the memory (including all available registers and caches) will be reflected in the checksum and the device does not have enough time to remove malware before checksum computation. Software attestation is able to detect compact malware - malware composed of very few instructions – and is secure against side-channel-aware attackers. Here timing is a key side-channel information to make sure that the attacker is unable to evade detection, even if she is able to profile the computation time of the target device.

Remote attestation<sup>45–47</sup> aims to perform software attestation on a remote device. The major problem is to prevent proxy attacks, as the timing side-channel cannot be used as a reliable detector of proxies in this scenario. Current solutions are based on a trusted hardware similar to TPM that is implemented on the DUT, and proxy is prevented by using the secret key shared by the trusted hardware and the verifier. Remote attestation relies on the somewhat unrealistic assumption that a remote device cannot be tampered physically (the trusted hardware is secure) and the secret key cannot be leaked. As shown in later sections, side-channel analysis, microprobing, reverse engineering, and fault injection can

fundamentally reveal any secret of a device.

In addition, there are some common weaknesses of software attestation and remote attestation. They both attest on known memory configuration, and are therefore vulnerable to code-reuse attacks, self-delete malware, data-only attacks, and time-of-check and time-ofuse (TOCTOU) attacks (in which the memory configuration is tampered and then restored between two attestations).

The software integrity checking schemes proposed in this thesis are external approaches. The proposed approaches have the same benefits as an external verifier has: low or no visibility to penetrators, low or no overhead to normal software, and easy deployment and upgrade. Furthermore, the proposed schemes in this thesis, unlike software attestation and remote attestation, measure runtime software integrity passively, without explicit attestation procedures, and therefore do not interrupt normal execution or have the TOCTOU problem. Like software attestation, they do not require CPUs with sophisticated security features, or modification of the hardware platforms. This makes our approaches favorable to legacy and deployed devices. To achieve these goals, our approaches utilize non-invasive passive side-channel emanations of electronic devices.

### 2.3 Side channels

It is common-sense that electronic devices consume power, cause heat, and emit electromagnetic (EM) radiation during execution. Power consumption, temperature, and EM measurements are resulted from the internal activities of the complementary metal-oxidesemiconductor (CMOS) circuits that comprise most of modern electronic devices. Therefore these side-channels, beside the explicit communication channel of a device, also carry information about the runtime state of a device.

#### 2.3.1 White-box analysis of side-channels

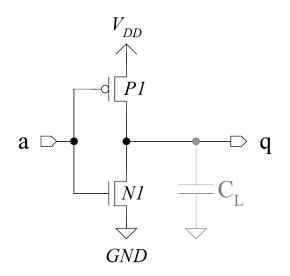

Why can power consumption, thermal and light imaging, and EM radiation carry information about a running device? It lies in the physics of electronic devices. An electronic device is often composed of analog components and digital components. For software integrity checking, only the digital part associated with a typical cyber system is concerned. Digital circuits are always built based on logic cells, which are commonly implemented by using CMOS.<sup>1</sup> Figure 2.2 shows a CMOS implementation of an inverter, a basic unit of digital circuits.

Figure 2.2: Lumped-C model of a CMOS inverter<sup>1</sup>

Power consumption of an inverter is composed of static power consumption and dynamic power consumption. CMOS inverter is designed such that there are no direct connections between Vdd and Gnd, except a small leakage current flowing through the MOS transistor that is off. This leakage current is the static consumption, which is usually 1pA. Dynamic power consumption is caused by internal or output signal switches. For the inverter, dynamic power consumption is incurred when input is changed. There are two types of dynamic power consumption: switching power and short-circuit power.<sup>1;48–50</sup> When the input switches from 1 to 0 (i.e., output from 0 to 1), the load capacitance of the cell needs to be charged, and therefore current flows from the Vdd through the load capacitance. Load capacitance incorporates the internal capacitance connected to the output, the capacitance of wire connected to other cells, and the input capacitance of these cells. Typical load capacitance ranges from 1fF to 1pF. When the input switches from 0 to 1 (i.e., output from 1 to 0), the load capacitance is discharged, and current flows in opposite direction in the load capacitance. Internal switches can be ignored because output causes much larger power consumption. Shortcircuit power consumption is the temporary short circuit between the two complementary transistors (PMOS and NMOS) during switching.

Dynamic power consumption of a circuit is often modeled as a sum of power consumed by all the nodes<sup>50</sup>:

$$P_{sw} = \frac{1}{2} f V_{dd}^2 \sum_{i=1}^n C_i \cdot E_i$$

(2.1)

$$P_{sc} = \alpha_{sc}(t_r) P_{sw} \tag{2.2}$$

where  $P_{sw}$  is the switching power consumption, f is the clock frequency,  $C_i$  is the load capacitance of node i,  $E_i$  is the transition density (frequency of switches) of node i,  $P_{sc}$  is the short-circuit power consumption,  $\alpha_{sc}(t_r)$  is a linear function of the input transition time  $t_r$ .  $\alpha_{sc}(t_r)$  is decided by a linear curve fitting of simulated dynamic power.

More accurate power models also consider the cross-talk (interference) between signals of neighboring wires<sup>51</sup>:

$$E_{total} = \sum_{i=1}^{n} \left( C_L + C_{eff,i} C_I \right) \cdot \Delta V_i \cdot V_i$$

(2.3)

$$C_{eff,i} = abs(C_L\delta_i + C_I\delta_{i,i-1} + C_I\delta_{i,i+1})$$

(2.4)

where  $E_{total}$  is the total energy consumption for a given bus transition,  $C_L$  is load capacitance seen by the driver,  $C_I$  is the inter-wire coupling capacitance between adjacent signal lines,  $C_{eff,i}$  is the effective total capacitance of the driver of *i*-th line,  $\delta_i \in \{0, 1\}$  is the normalized voltage change on *i*-th line,  $\delta_{i,i\pm 1} \in \{0, \pm 1, \pm 2\}$  is the normalized relative voltage change on *i*-th line relative to the  $(i \pm 1)$ -th line,  $\Delta V_i \in \{0, \pm V_{dd}\}$  is the voltage change on *i*-th line.

These power models are often used in combination with SPICE<sup>52</sup> simulation in company with detailed manufacture parameters to estimate dynamic power of small-scale circuits.<sup>48–50;53–55</sup> In practice, however, the complexity and lack of knowledge of cyber devices prevent such computation. Researchers in turn try to analyze side-channel properties from real measurements.

#### 2.3.2 Side-channel analysis with limited knowledge of devices

People have studied side-channel emanations from empirical measurements in diverse areas. Historically side-channels have been used mostly for attacks. In recent years, researchers start to try using side-channels for constructive purposes.

**Power-efficient device design** Empirical study of side-channel emissions of various embedded systems have long been studied to optimize power usage and perform EMI/EMC analysis. Researchers usually obtain power consumption of a target component of a cyber system by averaging the energy consumed when executing the component for a long time. This can be done at different levels. For example, application developers usually read the voltage of the battery of a mobile phone from time to time to determine the power consumption of the system so that some power-saving strategy can be applied. Researchers have also studied the empirical power consumption of instructions of various devices (most commonly mobile device) to evaluate the efficiency of the processor design or to guide power-efficient software development. In such study, researchers often execute the target instruction, e.g., multiply, for many times and compute the empirical power consumption or other side-channel information such as EM cartography by averaging the accumulative side-channel emanations. This research does not concern runtime side-channel emanations for individual instruction execution.<sup>56–58</sup>

Side-channel analysis for cryptographic hardware More recently, side-channel analysis has been used mostly for attacks. Numerous papers are published each year on how to

utilize power consumption or EM radiation of cryptographic hardware to break the embedded secret keys. Attackers are naturally of very limited knowledge of the target device, which yet cannot prevent them from correlating the side-channel emissions of the cryptographic device with the secret key materials by executing the same cryptographic routine (whose implementation details or even algorithm is unknown) a large number of times (typically thousands of times).<sup>1;59–62</sup>

**Covert channel** Another (mis-)use of side-channels is data exfiltration, in which sidechannels act as covert channels that silently transmit information about a running device. Tempest radiation is known as the stray RF emitted by electronic devices that can be used by an opponent to reconstruct the information about the data being processed.<sup>63</sup> Again, attackers do not need to build complete side-channel models for the target device in order to achieve their goals. One notable example dates back to 1980s when a researcher described how to reconstruct the picture on a VDU at a distance using a modified TV set.<sup>64</sup> More recently, researchers showed that it was possible to recover speech from the vibrations of a potato-chip bag photographed from 15 feet away through soundproof glass.<sup>65</sup>

**Fingerprinting** Empirical study of side-channels has also been used for device fingerprinting. Browser response patterns allow websites to track users without the need of client-side identifiers.<sup>66</sup> Ethernet devices can be uniquely identified by analyzing variations in their analog signal caused by hardware and manufacturing inconsistencies.<sup>67</sup> For constructive purpose, IC fingerprinting profiles the power, temperature, and EM (including light) characteristics of an IC family and further uses the profiles to detect hardware trojans (malicious circuits substituting the genuine ones).<sup>6–10;68</sup> The side-channel measurement of a DUT is compared with that of a "golden-model" which is invasively examined to ensure that no trojans exist. Hardware trojans are composed of sequential circuits and/or combinational circuits, and trojans of pure combinational circuits are hard to detect since they are barely triggered except for specific input pattern. On the other hand, if it is possible to detect combinational trojans, then so for the sequential trojans. With combinational trojans as the target, research on IC fingerprinting often scans emissions of the IC for enough time so that untriggered trojan circuits can be exposed from little bias in side-channel measurements. IC fingerprinting therefore does not concern with runtime side-channel emanations.

Side-channel disassemblers Side-channel analysis of runtime emanations has been studied for different purposes. One is to recognize instruction operations from side-channel measurements, referred to as "side-channel disassemblers" in<sup>69</sup>. Power consumption or EM radiation of some smart cards and microcontrollers are collected when running instructions using random data input, and statistic and pattern matching techniques, such as Principal Component Analysis (PCA) and template analysis, are used to classify among side-channel measurements of different instruction operations.<sup>17;18;69–74</sup> In<sup>17</sup> the authors claimed a relevant recognition rate of 96.24% on test data and 87.69% on real code by using multi-position localized EM emissions and semi-invasive access to a PIC microcontroller. In<sup>74</sup>, a 100% classification rate was reported by using power measurements on a AVR microcontroller. However, neither<sup>17</sup> nor us have succeeded in repeating the authors' results on a PIC microcontroller, which is a simpler microcontroller.

Integrity checking Another use of runtime side-channel information is to verify system integrity, as this thesis is concerned. Researchers have analyzed passive system-wide power measurements of general programs in the hope of detecting anomalous behaviors and/or malware.<sup>73;75–78</sup> These methods, however, assume malware (code) to be sufficiently long and not written to conceal its side-channel profiles. To use side-channels for rigorous integrity checking, we must consider compact and side-channel-aware malware. Software attestation<sup>42–44;79</sup> utilizes the timing side-channel and is capable of detecting malware at such precision. However, the device must support such attestation, and carrying out the process requires interruption of the device execution, a particular drawback for legacy and actively-used systems (see also Section 2.2.1).

**Micro-probing** At the lowest level, it is possible to measure the EM radiation of a single transistor or SRAM cell by using intrusive measurement and microscopic probing, as mentioned in Section 2.1. This method however does not scale well for integrity checking of a complex system that is composed of tens of thousands and more transistors. It does not solve the problem of efficiently verifying the software of a modern embedded system in practice.

## 2.4 Statistics and mathematical background

The proposed approaches in this thesis are composed of two procedures: side-channel modeling (profiling) and tampering detection. Side-channel modeling utilizes statistics, mathematical modeling, and pattern matching techniques to build relationships between the internal state of a target device and side-channel measurements. Tampering detection is to, based on the resulting side-channel model, determine from a new side-channel measurement whether the internal state of the device is a desired one or not. This section will briefly introduce the statistic and mathematical knowledge that is commonly used in the following chapters.

### 2.4.1 Pattern matching

Pattern matching/machine learning techniques are widely used in side-channel analysis since the interested internal states of a physical device are usually finite. For example, the secret sub-keys are often only 8-bit long, and at most 256 classes are needed (see<sup>80</sup> for various ways of classifying an 8-bit sub-key). So side-channel profiling can usually be applied with general classifiers. Popular techniques include Support Vector Machines (SVMs), template analysis (TA), and neural networks.<sup>70;80–82</sup> Template analysis has turned out be the most powerful one and are more relevant with the proposed approaches in this thesis.

#### Template analysis

Template analysis solves a classification problem by first build a set of reference patterns (templates) and then decide which one of the reference patterns matches best with a new test pattern; some measure is used to define the distance between reference patterns and the test pattern.<sup>83</sup> Template analysis in the context of attacking cryptographic hardware often assumes that the side-channel measurements (usually a sampled trace of power consumption) can be modeled as multi-variate Gaussian signals. Then templates are built by estimating the parameters of the Gaussian signals for each of the interested internal states (classes) from executing the device for a large number of times.<sup>69;81</sup> For each class  $\omega_i$ , select *l* samples in side-channel measurements for modeling, the templates are *l*-dimensional Gaussian distributions with parameters estimated from power consumption observations when executing the target device under  $\omega_i$ :

$$p(\boldsymbol{x}|\omega_i) = \frac{1}{(2\pi)^{l/2} |\boldsymbol{\Sigma}_i|^{1/2}} \exp\left(-\frac{1}{2} (\boldsymbol{x} - \boldsymbol{\mu}_i)^T \boldsymbol{\Sigma}_i^{-1} (\boldsymbol{x} - \boldsymbol{\mu}_i)\right)$$

$$\boldsymbol{\mu}_i = \frac{1}{N_i} \sum_{j=1}^{N_i} \boldsymbol{x}_{ij}$$

$$\boldsymbol{\Sigma}_i = \frac{1}{N_i - 1} \sum_{j=1}^{N_i} (\boldsymbol{x}_{ij} - \boldsymbol{\mu}_i) (\boldsymbol{x}_{ij} - \boldsymbol{\mu}_i)^T$$

(2.5)

where  $\boldsymbol{x}_{ij}$  is an *l*-dimensional observation of executing the device under  $\omega_i$  in the modeling data,  $N_i$  is the number of such observations in the modeling data.

When given a new observation  $\boldsymbol{x}$ , its internal state  $\hat{\omega}$  is estimated by applying the Bayes rule, which is the  $\omega_i$  that gives the maximum a posteriori probability.

$$\hat{\omega} = \operatorname*{argmax}_{\omega_i} p(\omega_i | \boldsymbol{x}) = \operatorname*{argmax}_{\omega_i} p(\boldsymbol{x} | \omega_i) P(\omega_i)$$

(2.6)

Template analysis has been shown to be the most powerful tool in breaking cryptographic hardware, as it can discover secret keys when given only a single test trace.<sup>69;82;84</sup> Other techniques usually requires hundreds or thousands of traces. Template analysis however

has some limitations. First, template building (sometimes referred to as "device profiling") requires full access to the target device, which is not always possible. Second, the profiling step requires executing the device for a very large number of times under each interested state, which may make the approach impractical, especially if the state space is large (which is not uncommon). Third, the performance of the approach will degrade significantly if the assumed model cannot accurately describe the real measurements or if the pre-selected l-dimensional observation is not well related with the interested states.

#### Class separability

A metric that is useful to examine whether the pre-selected observation (aka features in pattern matching literature) are representative to solve the template analysis problem is the class separability measure. It tells how likely the classification problem will be solved, since if classes are not well separable given selected features, then no techniques can achieve good classification performance.

The upper bound of the minimum attainable error of the Bayes classifier is<sup>83</sup>:

$$P_e \le \epsilon_{CB} = \sqrt{P(\omega_i)P(\omega_j)} \int_{-\infty}^{\infty} \sqrt{p(\boldsymbol{x}|\omega_i)p(\boldsymbol{x}|\omega_j)} d\boldsymbol{x}$$

(2.7)

where  $P_e$  is the classification error of the Bayes classifier,  $\epsilon_{CB}$  is known as the Chernoff bound,  $p(\boldsymbol{x}|\omega_i)$  is the probability density function of features  $\boldsymbol{x}$  under class  $\omega_i$ .

For multi-variate Gaussian signals, as assumed in template analysis and commonly in modeling power consumption and EM radiation:

$$\epsilon_{CB} = \sqrt{P(\omega_i)P(\omega_j)} \exp(-B_{ij}) \tag{2.8}$$

where

$$B_{ij} = \frac{1}{8} (\boldsymbol{\mu}_i - \boldsymbol{\mu}_j)^T (\frac{\boldsymbol{\Sigma}_i + \boldsymbol{\Sigma}_j}{2})^{-1} (\boldsymbol{\mu}_i - \boldsymbol{\mu}_j) + \frac{1}{2} \ln \frac{|\frac{\boldsymbol{\Sigma}_i + \boldsymbol{\Sigma}_j}{2}|}{\sqrt{|\boldsymbol{\Sigma}_i||\boldsymbol{\Sigma}_j|}}$$

(2.9)

where  $\mu_i$  is the mean of class  $\omega_i$ ,  $\Sigma_i$  is the covariance of  $\omega_i$ . B is known as the Bhattacharyya

distance and used for class separability measure of Gaussian signals. The smaller B is, the larger classification error will be incurred. See Section 3.4 for the Bhattacharyya distance of power consumption of a microcontroller grouped by instruction operations.

Another class separability measure that does not assume Gaussian distribution is to use the within-class and between-class scatter matrices<sup>83</sup>:

$$J = \frac{trace(S_m)}{trace(S_w)} \tag{2.10}$$

$$S_m = S_w + S_b \tag{2.11}$$

$$S_w = \sum_{i=1}^M P_i \Sigma_i \tag{2.12}$$

$$S_b = \sum_{i=1}^{M} P_i (\mu_i - \mu_0) (\mu_i - \mu_0)^T$$

(2.13)

where  $P_i$  is the a prior probability of class  $\omega_i$ , M is the total number of classes,  $\mu_i$  is the mean of class  $\omega_i$ ,  $\Sigma_i$  is the covariance of  $\omega_i$ , and  $\mu_0 = sum_{i=1}^M P_i \mu_i$  is the global mean vector. See Section 5.6 for the J values of EM radiation of FPGA-implemented SoCs grouped by instruction operations.

### 2.4.2 Mathematical modeling

When the modeling target is not finite, then classification techniques are not applicable. In Section 3.4 and 5.6, the side-channel measurement, which is naturally of continuous values, is the response variable, and depends on internal states of the target device. Note that literature in attacking cryptographic hardware often takes the side-channel measurements as the predictor variables (features) and the internal states as the response variables (classes). When the response variable is continuous, regression techniques are the tools to establish the relationships between side-channel measurements and internal activities. Assume the observation  $Y_t$  at time t depends on a set of variables  $\vec{x_t} = (x_{t1}, \ldots, x_{tp})$  at t, which are often controllable in experiments:

$$Y_t = f(\vec{x_t}) + N_t \tag{2.14}$$

where  $N_t$  encloses remaining components in the EM radiation including noise and timedependent components,  $Y_t$  and  $N_t$  are necessarily random variables.  $x_{tj}(j = 1, ..., p)$  are called the predictor variables and  $Y_t$  the response variable.

Regression techniques estimate the function  $f(\cdot)$  from a large number n > p of experiments to exercise the controlled predictor variables  $\{\vec{x_i}|i = 1, ..., n\}$  and collect the corresponding observations  $\{Y_i|i = 1, ..., n\}$ . Commonly assumed form of  $f(\cdot)$  is linear:

$$Y_i = \beta_0 + \beta_1 x_{i1} + \beta_2 x_{i2} + \dots + \beta_{q-1} x_{i,q-1} + N_i$$

(2.15)

where  $\beta_j (j = 0, \dots, q - 1)$  are constants.

The power consumption model of dynamic switching power 2.1 is similar to this form when we consider the transition density  $E_i$  as the predictor variables and load capacitance  $C_i$  as the constants, or vice versa.

$x_{ij}(j = 1, ..., q - 1)$  may be derived from  $x_{ij}(j = 1, ..., p)$ . For example, a polynomial regression model, which is a special case of linear regression, obtain the q predictor from a polynomial function of  $x_{ij}(j = 1, ..., p)$ . A second-order polynomial regression model with two predictor variables is:

$$Y_{i} = \beta_{0} + \beta_{1}x_{i1} + \beta_{2}x_{i2} + \beta_{11}x_{i1}^{2} + \beta_{22}x_{i2}^{2} + \beta_{12}x_{i1}x_{i2} + N_{i}$$

$$(2.16)$$

This form is familiar as the power consumption model of bus signals 2.3 that consider interference between neighboring buses has the "interaction term"  $x_{i1}x_{i2}$  too.

If the assumed linear function is a good approximator of the real function  $f(\cdot)$ , then least-square estimation can be used to estimate  $\vec{\beta} = (\beta_0, \ldots, \beta_{q-1})$ . Least-square estimation does not make any assumption on the distribution of  $x_{ij}(j = 1, \ldots, p)$ , and the resulting estimate  $\hat{\vec{\beta}}$  is the optimal unbiased estimator of  $\vec{\beta}$ , given  $E(N_i) = 0$ ,  $Var(N_i) = \sigma^2$ , where E(X) is the expectation of random variable X, and Var(X) is the variance of X.

$$\hat{\vec{\beta}} = (X'X)^{-1}X'\vec{y}$$

(2.17)

where  $X = \{x_{ij}\}_{n \times q}$  is the matrix of the predictor variables. However, as shown in Section 5.6, directly applying least-square estimation does not always work in practice. The most notable problem encountered in this thesis is the multicollinearity among the predictor variables  $x_j (j = 1, ..., q)$ . Multicollinearity is the phenomenon where some of the predictor variables are correlated with each other, which will lead to singularity of (X'X). Several techniques can be used to eliminate multicollinearity, and will be discussed in details in Section 5.6.

#### 2.4.3 Variable selection

A common problem that is encountered both in pattern matching/classification and in regression is variable/feature selection. Sometimes variable/feature selection techniques are also used for dimensionality reduction or noise reduction. Very often in our experiments, one observation (response) is associated with many predictor variables (i.e., features) and it is difficult or impractical to exclusively control a small set of variables while keeping the others constant. One may think with many predictor variables it is unlikely to omit any important variables that greatly impact the response. However, too many predictor variables are detrimental rather than beneficial to the classification/regression problem. First, many more observations are needed to exercise the space of the predictor variables. Second, the increased computation complexity may make the problem unsolvable. Third, the correlation among the predictor variables may significantly worsen the model performance.

One popular technique that appears in attacking cryptographic hardware and also in pattern matching is principal component analysis (PCA). PCA transforms the original data to a new space spanned by a set of orthogonal vectors, along the first of which the data have the largest variance, along the second the second largest variance, etc. The set of orthogonal vectors are computed from the singular value decomposition (SVD) of the empirical sample covariance matrix  $\Sigma$  of the original data  $X^{85}$ :

$$\Sigma = U * \Lambda * U^{-1} \tag{2.18}$$

$$\Sigma = S(X_i, X_j)_{p \times p}, (i = 1, \dots, p, j = 1, \dots, p)$$

(2.19)

$$S(X_i, X_j) = \frac{1}{n-1} \sum_{k=1}^n (x_{ki} - \bar{X}_i)(x_{kj} - \bar{X}_j)$$

(2.20)

where  $X_i$  (i = 1, ..., p) is the *i*-th vector of X, each  $X_i$  has *n* observations (i.e. X has *n* rows),  $\overline{X}_i$  is the sample mean of  $X_i$ . Since  $\Sigma$  is a symmetric matrix,  $\Lambda$  is a diagonal matrix and U is an orthogonal matrix of eigenvectors of  $\Sigma$ . The eigenvector corresponding to the largest eigenvalue is the first principal component, along which the original data have the largest variance; the eigenvector corresponding to the second largest eigenvalue is the direction along which the original data have the second largest variance, etc (see<sup>85</sup>). If we can keep the eigenvectors corresponding to the first k < p largest eigenvalues, then we only need to process k variables that have the majority of variance. The dimension of the variables is therefore reduced. In addition, if some variables in the original matrix are correlated, then some of the eigenvalues are zeros. We can then ignore the directions that correspond to these eigenvalues. The transformed data X' that keep only the first k eigenvectors are computed from:

$$X' = XW \tag{2.21}$$

where W is a  $p \times k$  matrix that keeps only the first k columns of U. X' instead of X will be used for further processing. If X' is used for the normal least-square-estimation of a regression model, then the procedure is called principal component regression (PCR), which is a useful technique to eliminate multicollinearity among original variables. Other common use of X' is for pre-processing in pattern matching. The purpose is to reduce dimensionality while retaining most representative signals, as the transformed data that corresponding to small variances are discarded for further processing. It is in particular useful in template analysis, as the covariance matrix of the input variables needs to be computed.

# Chapter 3

# **Black-box Analysis**

1

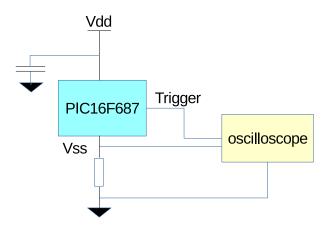

The first device studied to explore feasibility of using side-channels for software integrity checking is a PIC microcontroller ( $\mu$ C). PIC16F687 is chosen as the DUT, because most previous research in side-channel analysis for general programs has been done on this IC.<sup>17;69;72;74</sup>

### 3.1 Related work

Chapter 2 has already introduced literature on existing software integrity checking approaches that are either internal or external to the target device, as well as side-channel analysis for different purposes. The problem of side-channel-based software integrity checking for microcontrollers is distinct from side-channel analysis in other domains in that

- The analysis is on a single-captured side-channel measurement that represents a onetime execution of some code;

- The analysis is on the entire instruction set instead of a few special instructions;

- The analysis is on the entire trace in one capture instead of a few special occasions in time;

<sup>&</sup>lt;sup>1</sup>This chapter is based on work already published<sup>86</sup>

- The analysis is on a black-box device the design detail of which is unknown;

- The analysis must consider compact malware that may be composed of a single instruction, or a change of original instruction only on the operands;

- The analysis must consider side-channel-aware attackers who actively attempts to evade detection by computing alternative code that has near indistinguishable sidechannel measurement from that of the original code.

Side-channel analysis proposed in this chapter for software integrity checking is an "online" verification method in which the runtime state of a device is checked dynamically against desired one via side-channel measurements, so that "transient" malware or faulty states can be detected. This approach is in contrast with detection methods for hardware trojans, which are based on static scanning of the side-channel emissions, such as light, of a circuit.

Previous research on side-channel-based software integrity checking that performs runtime verification is either at a rather coarse granularity (e.g., function-level)<sup>73;75;76;78</sup>, or ignorant of side-channel-aware attackers<sup>77;78</sup>, or the effects of data, even operands of instructions.<sup>17;18;69–74</sup> Software attestation<sup>42–44;79</sup> utilizes the timing side-channel and is capable of detecting malware which may be as compact as one instruction. However, the device must support such attestation, and carrying out the process requires interruption of the device execution, a particular drawback for legacy and actively-used systems. Furthermore, software attestation cannot detect transient faulty states, code-reuse attacks, data-only attacks, and suffers from the TOCTOU problem (c.f. Section 2.2.1).

As shown in the following sections, the runtime side-channel emanations of a device are not only determined by the instructions, but also, if not more significantly, by data (context) that are involved in the instruction execution, such as register and memory content. More generally, the actual internal activity of the device, instead of solely the code determines side-channel emanations. To guarantee that a single execution of malware is detected, side-channel analysis must be at the granularity of at least instruction cycles, taking into consideration of both code and data. Previous research often tries to profile side-channels according to instruction operations by using pattern matching/classification methods.<sup>18;69–73;80</sup> We will show in this chapter that such analysis is unlikely to be successful due to the nature of side-channel emissions, and without considering operands and other context, it cannot solve rigorously the integrity checking problem.

### 3.2 Problem definition