# ENERGY-EFFICIENT FEATURE EXTRACTION ENGINE AND SECURE CHIP IDENTIFICATION FOR UBIQUITOUS SURVEILLANCE

## ANASTACIA B. ALVAREZ

(BS ECE, University of the Philippines, 1998)

(MS EE, University of the Philippines, 2004)

## A THESIS SUBMITTED

# FOR THE DEGREE OF DOCTOR OF PHILOSOPHY DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING NATIONAL UNIVERSITY OF SINGAPORE

## **DECLARATION**

I hereby declare that the thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis.

This thesis has also not been submitted for any degree in any university previously.

Anastacia B. Alvarez

19 December 2016

## Acknowledgement

This journey has been long one, and challenging at times, and I am grateful to Him above for the give of life, love, family and friends, without whom this wouldn't have been possible. My sincere gratitude to them.

First of all, to my supervisors, for their guidance and support. Massimo, thank you for the guidance and patience especially during the critical phases of the projects, and the opportunity to work on them. Prof. Ha Yajun, thank you for accepting me to be your student, and for the advises especially during my first few years of study. Dr. Zhou Jun, thank you for the valuable feedback and advise and for sparing your time for consultations.

My heartfelt gratitude to the Professors who reviewed my research (or part of it), for their comments and valuable criticism: Prof. Xu Yong Ping, Prof. Heng Chun Huat, Prof. Yang Zhi, Dr. Rajesh Panicker, Prof. Ganesh Samudra and Prof. Vincent Lee. To all Profs in the modules I attended (official and unofficial), thank you for sharing the knowledge. To Prof. Adekunle Adeyeye and Ms. Hemamalini, thank you for helping me through the process of the NUS graduate program.

Of course this would not have been possible without the support from the University of the Philippines and the Faculty Development Program of ERDT through the Department of Science and Technology. To ate Mimi and Ms. Daezelle, for making sure we get our allowance. To my friends back home, Tess, Franz, Chrd, Marc, Benjo, Mong and to everybody at EEEI, thank you for always welcoming me each time I come home. Special mention to Louis and Rhands for being my unofficial consultants.

To Wenfeng, my sincere thanks for being a very patient and ever dependable mentor. Gopal, thanks for all your help with EQSCALE (even after you have left the group), and to Longyang, for the discussion and assistance especially with the CAD tools. The coffee, chats and good food are definitely appreciated as well, together with Kien, Saurabh, Allan, Niranjani and Jim. Thanks to Harish, for the work with ORB, and Isha for the work with the SRAM. And to the rest of the Green-IC group, thanks for company.

Finally, and most importantly, to my family (Tatang, Mommy<sup>†</sup>, Ate Ay, Kuya King, Chel, Caitlyn, Kayla and Jared), my in-laws (Tatay<sup>†</sup>, Nanay, Liza, Rhomie, Ding, Chase, Omar<sup>†</sup>, Reiza, Ria and Marco), thanks for the love and support. And to my very supportive and loving husband, Elbert, thank you for always believing and being there for me. This one's for you!

## **Table of Contents**

| Declarationi                                                                                         |

|------------------------------------------------------------------------------------------------------|

| Acknowledgementii                                                                                    |

| Table of Contentsiv                                                                                  |

| Summaryvi                                                                                            |

| Chapter 1_Introduction                                                                               |

| 1.1 Energy- and Power-Limited Designs2                                                               |

| 1.2 Thesis Overview                                                                                  |

| Chapter 2_Feature Extraction Algorithms and their Suitability for Energy- Autonomous Computer Vision |

| 2.1. Background                                                                                      |

| 2.2. Metrics and Comparison12                                                                        |

| 2.3. State-of-the-Art Hardware Implementations                                                       |

| 2.3.1 SIFT                                                                                           |

| 2.3.2 SURF                                                                                           |

| 2.3.3 FAST-BRIEF                                                                                     |

| 2.3.4 ORB                                                                                            |

| Chapter 3_ORB Algorithm and IC Design Considerations                                                 |

| 3.1. Comparison of SIFT, SURF and ORB23                                                              |

| 3.2. Tuneable Knobs in ORB                                                                           |

| 3.2.1. Number of keypoints26                                                                         |

| 3.2.2. Threshold                                                                                     |

| 3.2.3. Descriptor length                                                                             |

| 3.2.4. Number of pyramid levels34                                                                    |

| 3.2.5. Corner measure                                                                                |

| 3.3 Hardware Model                                                                                   |

| 3.4. Summary                                                                                         |

| Chapter 4_EQSCALE Silicon Implementation and Results45                                               |

| 4.1 RTL Design45                                                                                     |

| 4.1.1 CACHE and KEYPTS46                                                                             |

| 4.1.2 CORE Design                                                                                    |

| 4.2 RTL Simulations with Tuneable Knobs57                                                            |

| 4.3 EQSCALE Results                                                  | 60  |

|----------------------------------------------------------------------|-----|

| 4.4 Effect of Cache Size                                             | 65  |

| 4.5 Further improvements to EQSCALE                                  | 69  |

| 4.5.1 Object Detection and Matching                                  | 70  |

| 4.5.2 Ranking                                                        | 71  |

| 4.5.3 Other Energy-Efficient techniques                              | 73  |

| Chapter 5_SRAM for Image and Video Application                       | 74  |

| 5.1 SRAM Basics and Metrics                                          | 74  |

| 5.2 State of the Art                                                 | 76  |

| 5.2.1 Near-threshold SRAMs                                           | 77  |

| 5.2.2 Application-Specific SRAMs                                     | 80  |

| 5.3 Non-Precharged SRAM (NPSRAM)                                     | 81  |

| Chapter 6_Secure Chip Identification Using PUFs                      | 86  |

| 6.1 PUF Introduction                                                 | 86  |

| 6.2 PUF Properties and Metrics                                       | 88  |

| 6.3 PUF Topologies and State of the Art                              | 94  |

| 6.4 Static, Monostable PUFs                                          | 99  |

| 6.4.1 Design and Operation                                           | 99  |

| 6.4.2 Testchip Measurement and Comparison                            | 103 |

| 6.5 Possible Future Work on PUFs                                     | 117 |

| Chapter 7_Energy-Efficient Microcontroller for Wireless Sensor Nodes | 124 |

| Chapter 8_Conclusion.                                                | 136 |

| References                                                           | 138 |

| List of Publications                                                 | 150 |

#### **Summary**

Making machines more human has been a long-term research goal across different disciplines. Computer vision plays a major role in this goal by giving the machine a way to analyse and interpret an image by dividing images into smaller but meaningful segments. One critical step in computer vision is feature extraction, which identifies unique features of objects in an image or video. This could lead to a wide range of applications, including ubiquitous surveillance, which involves area monitoring, object detection, tracking, and remote sensing. For applications like surveillance, real-time processing is usually required, making the processing and analysis tasks more compute intensive, resource hungry, and therefore power consuming. To cater to battery-operated devices, or those using power from energy harvesting techniques, power consumption is pushed to sub-mW at tens of MHz frequency. Thus, designers are faced with two opposing constraints: high throughput and low energy.

An energy-quality scalable feature extraction accelerator (EQSCALE) is presented as the first chip demonstration of the Oriented FAST Rotated BRIEF (ORB) algorithm. In this accelerator, tuning knobs are introduced, allowing for adjustable balance between the energy consumption and quality of the feature extraction accelerator. As proof of concept, a 40nm testchip was designed and tested to have an energy of 55.6pJ per pixel on VGA format at 30 fps, with area of 0.55 mm<sup>2</sup>. The effect of the different knobs on energy and accuracy, as well as some intuition on the trade-off between energy and performance is presented, to allow for scalability depending on the need of the application.

Memory also plays a role in both performance and energy consumption of the system. Leveraging on the high correlation of adjacent pixels in an image, a non-precharged SRAM (NPSRAM) is proposed. Compared with conventional 8T SRAM, we

show that NPSRAM can reduce energy by 30-75%, with 15% area overhead, at isospeed.

For ubiquitous surveillance, especially with sensor nodes for detecting and tracking objects, confidential information are passed from node to node. With the evergrowing number of IoT devices and nodes, security issues like node cloning are expected to arise. There is therefore a need to ensure data authenticity, integrity and confidentiality. For this, we propose to use chip identification using physically unclonable functions (PUFs). A PUF is a function that maps an input challenge to an output response in a repeatable but unpredictable manner, leveraging on chip-specific random process variations. A novel class of mono-stable static (PUFs) for secure key generation and chip identification is presented. From a statistical quality viewpoint, the 65nm PUF testchip achieved best-in-class reproducibility and uniqueness. Energy consumption was likewise shown to be the best compared to state of the art in PUFs, at 15fJ/bit.

## **List of Tables**

| Table 2.1 Comparison Results                                              | 13  |

|---------------------------------------------------------------------------|-----|

| Table 2.2 SURF Implementation Summary                                     | 20  |

| Table 2.3 FAST-BRIEF Implementation Summary                               | 22  |

| Table 3.1 Parameters considered and their trade-off                       | 38  |

| Table 3.2 Number of keypoints with NMS-3 and NMS-5                        | 40  |

| Table 3.3 Look-up table for atan2                                         | 42  |

| Table 4.1 Area and Power Estimates for Detector Block                     | 51  |

| Table 4.2 Power and Area Estimates of CORE                                | 56  |

| Table 4.3 Normalized execution time vs descriptor length                  | 58  |

| Table 4.4 Power consumption with different knob settings                  | 59  |

| Table 4.5 Energy consumption at 0.9V, 330MHz with different knob settings | 60  |

| Table 4.6 Comparison of Results                                           | 65  |

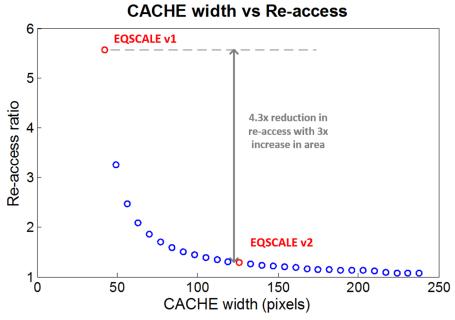

| Table 4.7 Effect of increasing CACHE width by 3x                          | 67  |

| Table 4.8 Area Comparison between EQSCALE versions                        | 67  |

| Table 5.1 Comparison of SRAM bitcells                                     | 80  |

| Table 5.2 Delay comparisons                                               | 83  |

| Table 5.3 Energy comparisons                                              | 84  |

| Table 5.4 Area comparisons                                                | 85  |

| Table 6.1 Example of SRAM PUF Silicon Cost                                | 89  |

| Table 6.2 PUF Metrics and Typical Values                                  | 89  |

| Table 6.3 NIST Statistical Test Suite                                     | 93  |

| Table 6.4 Comparison of Different PUFs                                    | 105 |

| Table 6.5 Summary of NIST Test Results                                    | 113 |

| Table 7.1 I/O Pins of Fabricated Chip                                     | 126 |

| Table 7.2 Processor Parameters at 100MHz                                  | 127 |

| Table 7.3 Processor Parameters at 100kHz                                  | 127 |

| Table 7.4 Benchmark code sizes                                            | 127 |

| Table 7.5 Brownie Core Architecture                                       | 129 |

| Table 7.6 Comparison of Brownie 32-bit and 16-bit Cores                   | 130 |

| Table 7.7 Code Size Comparison with 16- and 32-bit Cores                  | 131 |

| Table 7.8 Comparison of Cores at 0.5V, 7.5MHz                             | 132 |

| Table 7.9 BrownieMult16 Design Parameters                                 | 135 |

# **List of Figures**

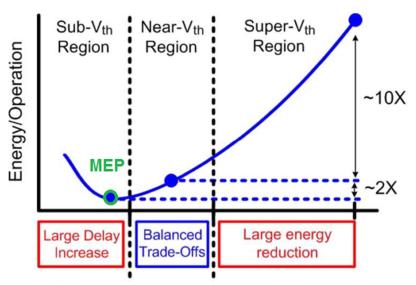

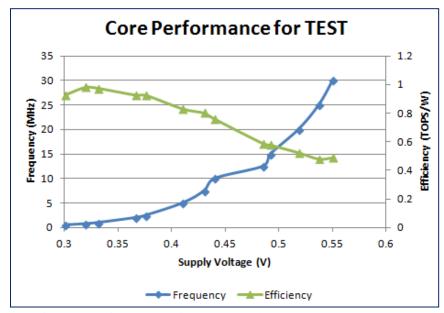

| Fig. 1.1 Supply vs energy/operation                             | 2  |

|-----------------------------------------------------------------|----|

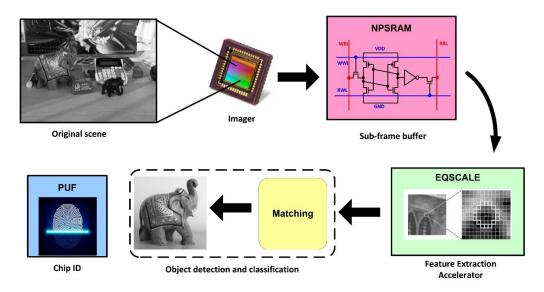

| Fig. 1.2 Feature extraction system overview                     | 3  |

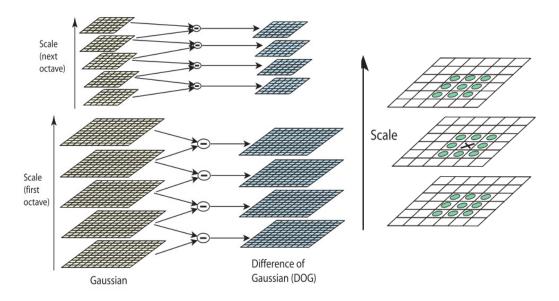

| Fig. 2.1 SIFT Interest Point Detection                          | 8  |

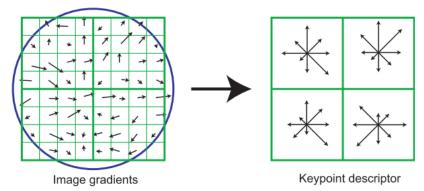

| Fig. 2.2 SIFT keypoint description                              | 9  |

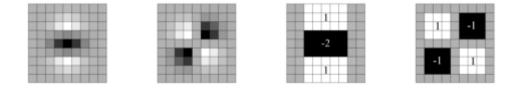

| Fig. 2.3 SURF Box Filters                                       | 9  |

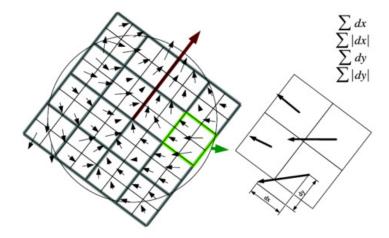

| Fig. 2.4 SURF Descriptor                                        | 10 |

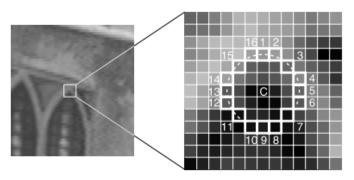

| Fig. 2.5 FAST interest point detection                          | 11 |

| Fig. 2.6 Benchmark images used for comparison                   | 13 |

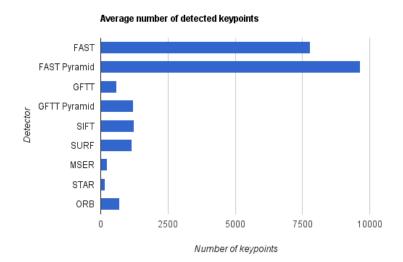

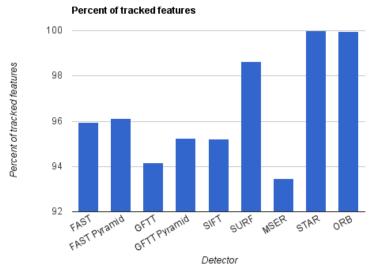

| Fig. 2.7 Average number of detected keypoints                   | 14 |

| Fig. 2.8. Comparison for scale invariance                       | 15 |

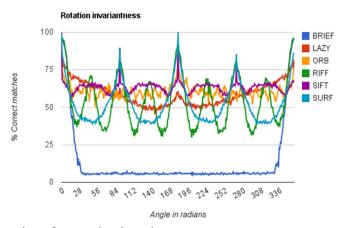

| Fig. 2.9. Comparison for rotation invariance                    | 15 |

| Fig. 2.10. Comparison for scale invariance                      | 15 |

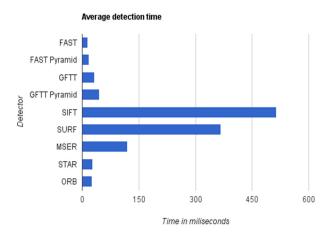

| Fig. 2.11. Comparison of detection time                         | 16 |

| Fig. 2.12. Comparison of total execution time                   | 16 |

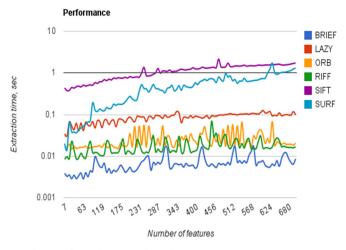

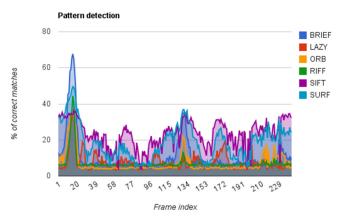

| Fig. 2.13. Performance comparison using video sequence          | 17 |

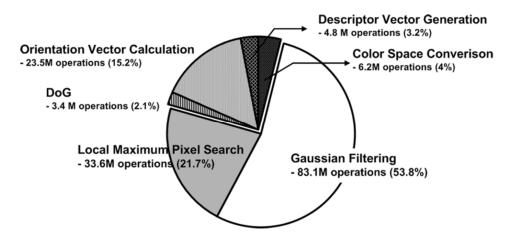

| Fig. 2.14. Breakdown of computational requirement in SIFT       | 18 |

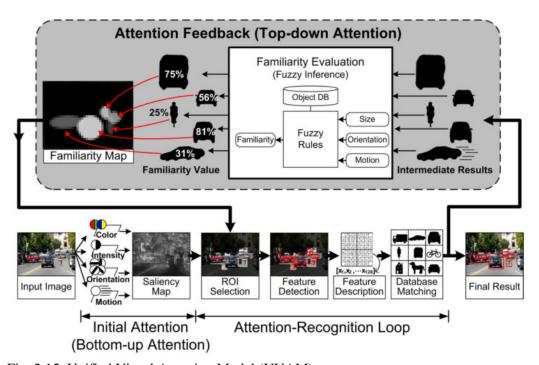

| Fig. 2.15. Unified Visual Attention Model (UVAM)                | 18 |

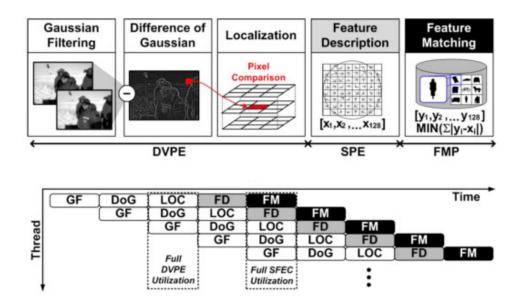

| Fig. 2.16. SIFT 5-stage Pipeline Operation                      | 19 |

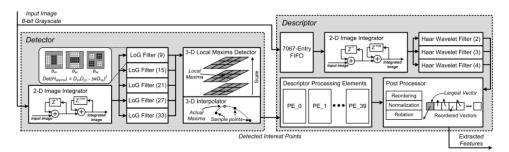

| Fig. 2.17. SURF Feature Extraction Architecture                 | 20 |

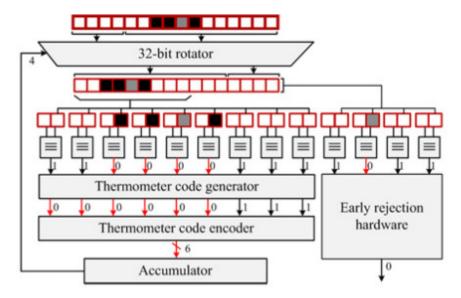

| Fig. 2.18. FAST Corner Detector                                 | 21 |

| Fig. 2.19. FAST and BRIEF Unified Hardware Platform             | 22 |

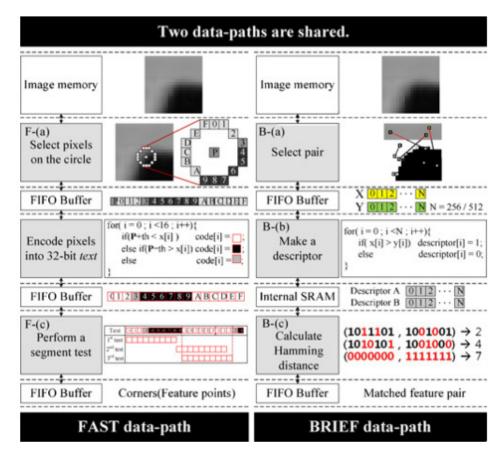

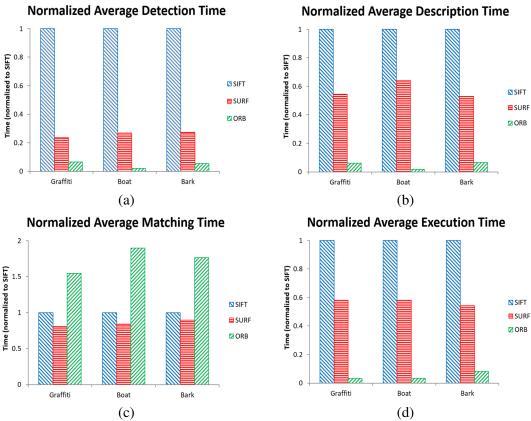

| Fig. 3.1 Normalized execution times of SIFT, SURF and ORB       | 24 |

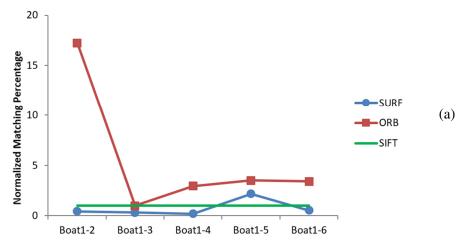

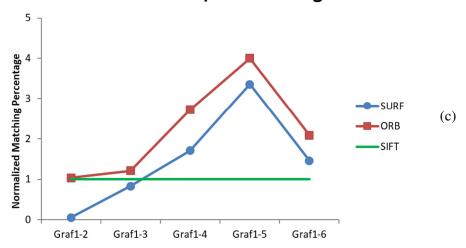

| Fig. 3.2. Normalized matching performance of SIFT, SURF and ORB | 25 |

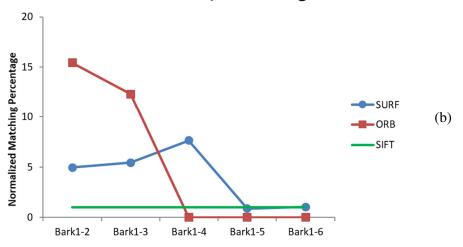

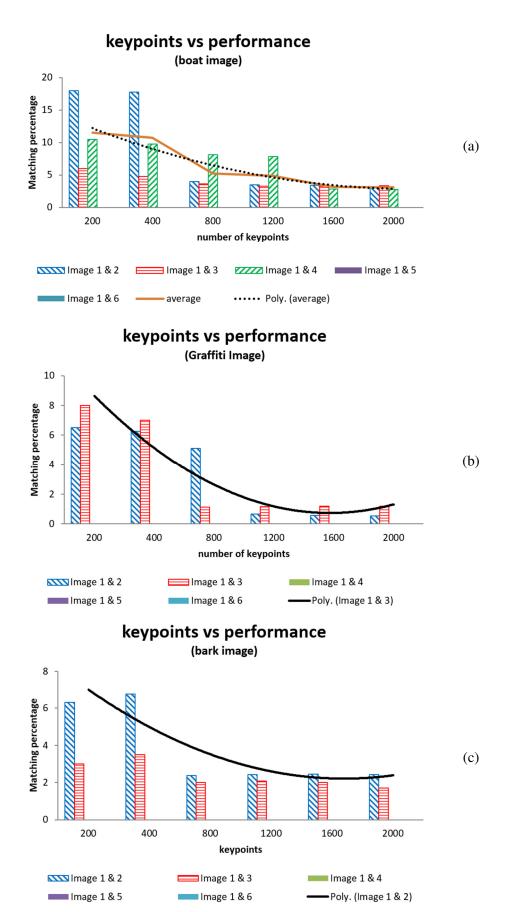

| Fig. 3.3 Effect of number of keypoints on performance           | 27 |

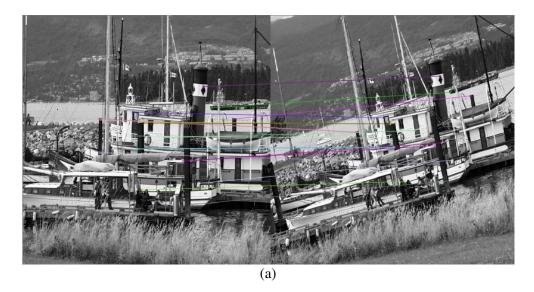

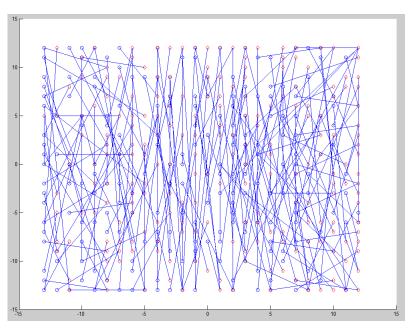

| Fig. 3.4 Image matching in boat                                 | 29 |

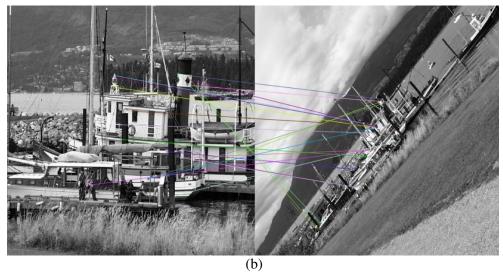

| Fig. 3.5 Total execution time of ORB for different images       | 30 |

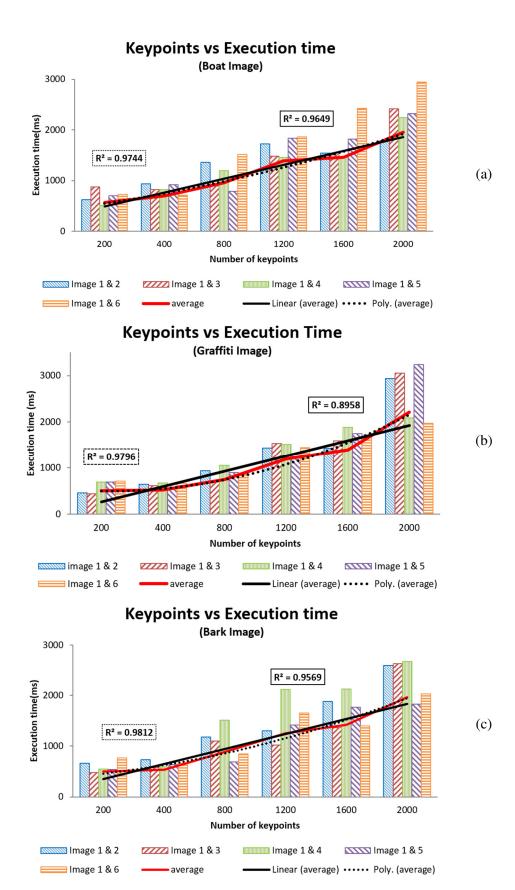

| Fig. 3.6 Effect of threshold on number of detected keypoints    | 31 |

| Fig. 3.7 Relationship between threshold and number of keypoints | 32 |

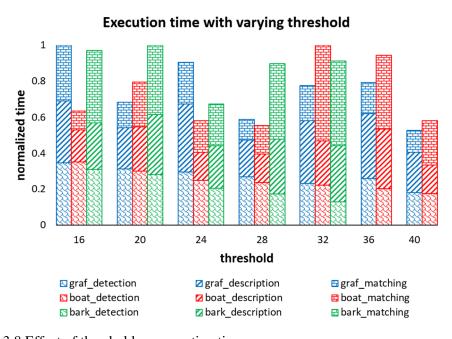

| Fig. 3.8 Effect of threshold on execution time                  | 32 |

| Fig. 3.9 Description time with varying descriptor length        | 34 |

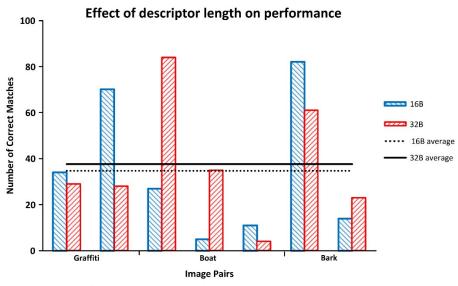

| Fig. 3.10 ORB performance with varying descriptor length        | 34 |

| Fig. 3.11 ORB performance vs number of pyramid levels           | 35 |

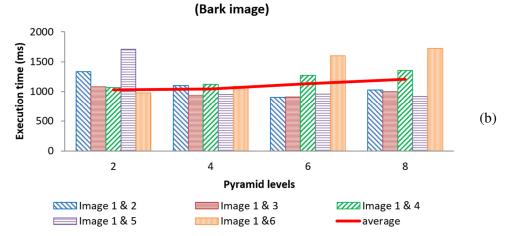

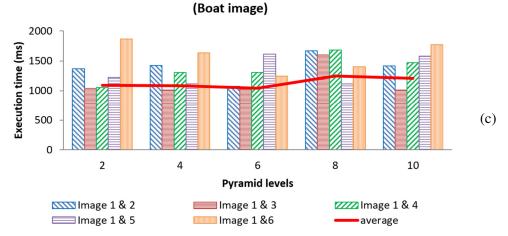

| Fig. 3.12 Total Execution time vs number of pyramid levels      | 36 |

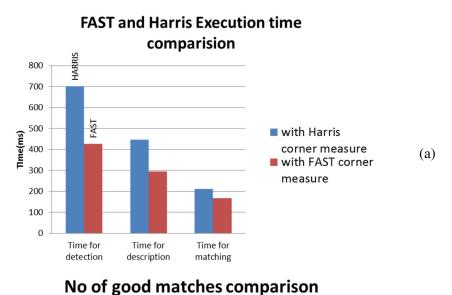

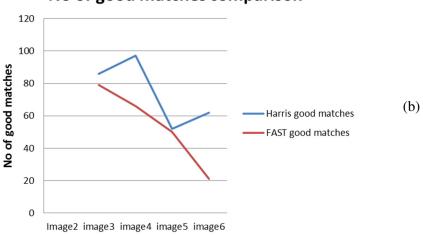

| Fig. 3.13 FAST vs Harris corner measure                                        | 37 |

|--------------------------------------------------------------------------------|----|

| Fig. 3.14 Comparison of Harris and FAST speed and performance                  | 38 |

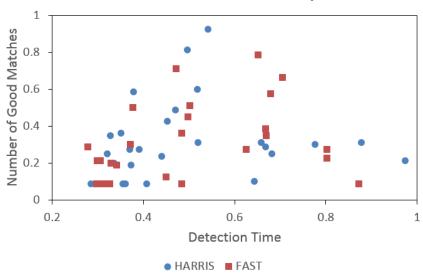

| Fig. 3.15 Comparison of NMS-3 and NMS-5                                        | 40 |

| Fig. 3.16 NMS-3 and NMS-5 illustration                                         | 41 |

| Fig. 3.17 Representation of LUT for 256-pair pixels                            | 43 |

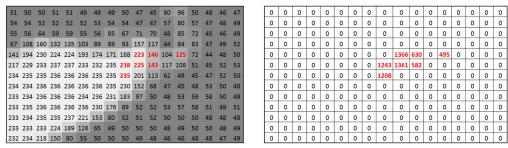

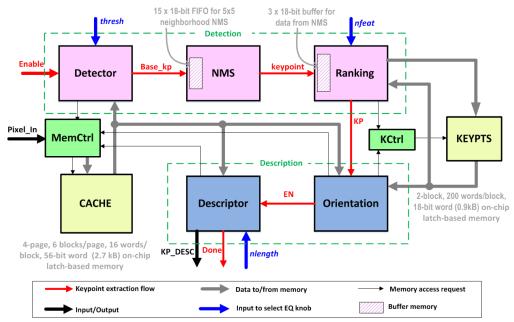

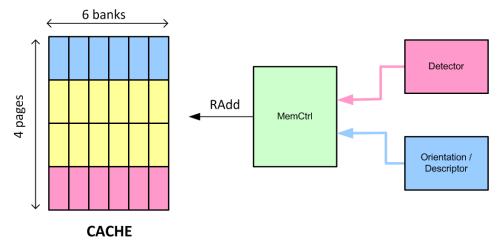

| Fig. 4.1 EQSCALE architecture                                                  | 46 |

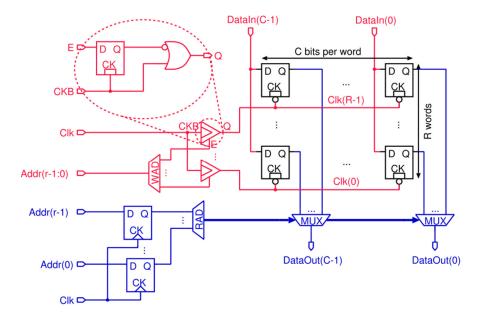

| Fig. 4.2 Standard Cell Memory Schematic                                        | 47 |

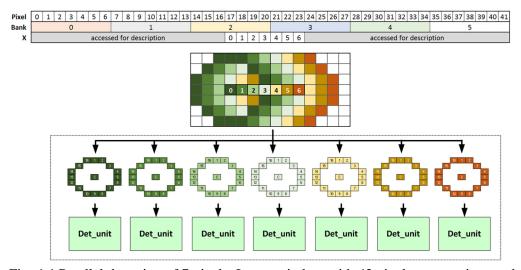

| Fig. 4.3 CACHE re-use access illustration                                      | 48 |

| Fig. 4.4 Parallel detection of 7 pixels                                        | 49 |

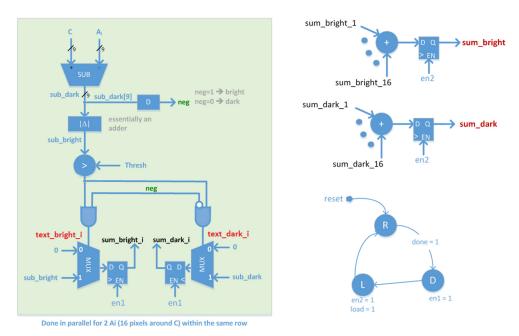

| Fig. 4.5 Det_unit operation                                                    | 50 |

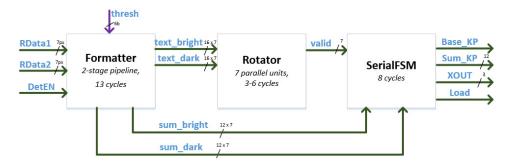

| Fig. 4.6 Detector Block Diagram                                                | 51 |

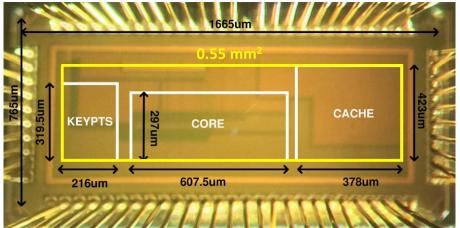

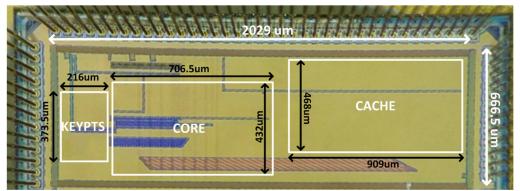

| Fig. 4.7 EQSCALE die photomicrograph                                           | 57 |

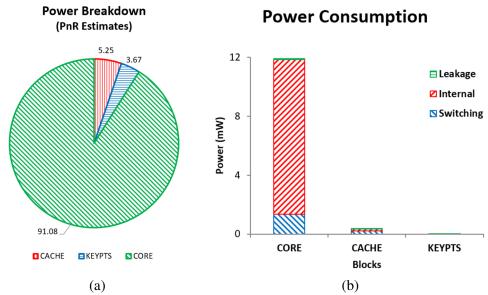

| Fig. 4.8 Power consumption breakdown from PnR estimates                        | 58 |

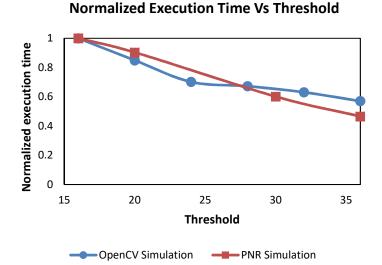

| Fig. 4.9 Normalized Execution Time vs Threshold                                | 58 |

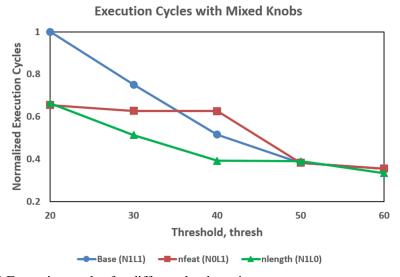

| Fig. 4.10 Execution cycles for different knob settings                         | 59 |

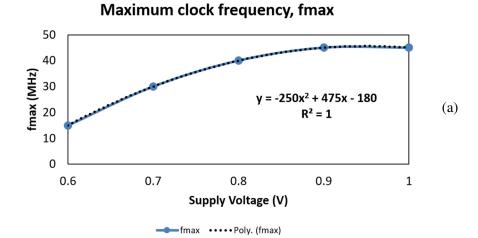

| Fig. 4.11 Measured fmax and power consumption of different blocks              | 61 |

| Fig. 4.12 Effect of VDD scaling on frame rate and energy per pixel             | 61 |

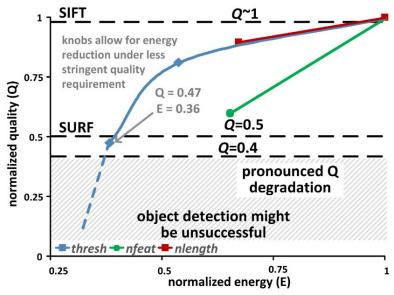

| Fig. 4.13 Energy-Quality tradeoff when tuning knobs at nominal VDD             | 63 |

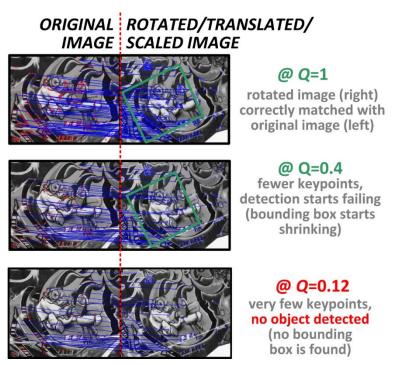

| Fig. 4.14 Illustration of image matching at different values of Q              | 63 |

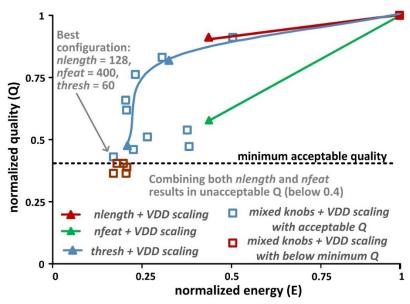

| Fig. 4.15 Quality vs. energy with joint EQ knobs combined with voltage scaling | 64 |

| Fig. 4.15 Effect of cache width on re-access ratio                             | 66 |

| Fig. 4.16 EQSCALE v2 chip microphotograph                                      | 68 |

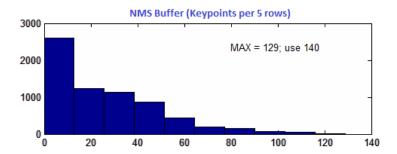

| Fig. 4.17 NMS buffer size histogram                                            | 69 |

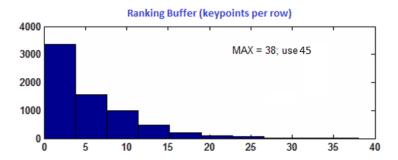

| Fig. 4.18 Ranking buffer size histogram.                                       | 69 |

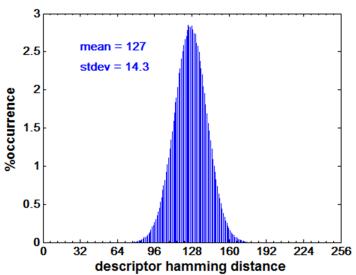

| Fig. 4.20 Descriptor hamming distance histogram                                | 70 |

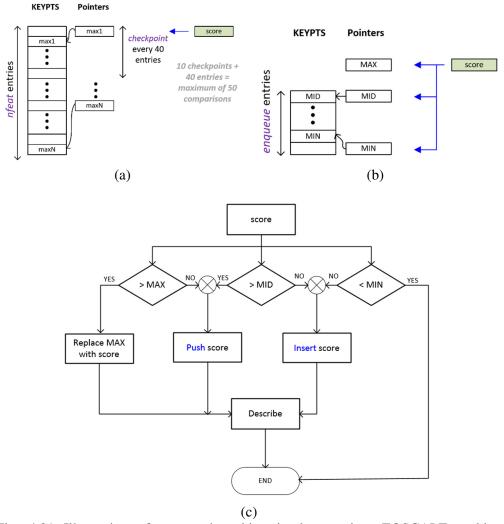

| Fig. 4.20 Illustration of proposed ranking implementation                      | 72 |

| Fig. 5.1 Conventional 6T SRAM                                                  | 75 |

| Fig. 5.2 SRAM sizing considerations for (a) read 0 and (b) write 0 contention  | 76 |

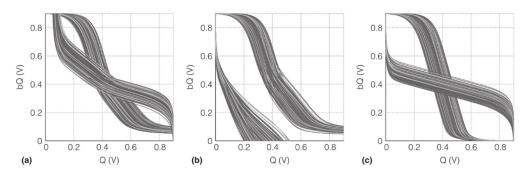

| Fig. 5.3 Static noise margin for (a) read, (b) write, and (c) hold             | 76 |

| Fig. 5.4 SNM for (a) read, (b) write and (c) hold at near-threshold voltage    | 77 |

| Fig. 5.5 7T SRAM                                                               | 77 |

| Fig. 5.6 Schmitt trigger based SRAM                                            | 78 |

| Fig. 5.7 Single-ended 6T SRAM using transmission gate as access transistors    | 79 |

| Fig. 5.8 8T SRAM with separate read port                                       | 79 |

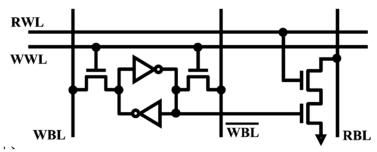

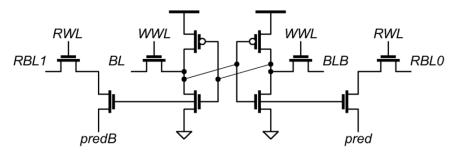

| Fig. 5.9 Prediction-based SRAM for reduced bitline activity (PB-RBSA)          | 81 |

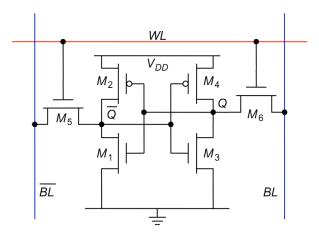

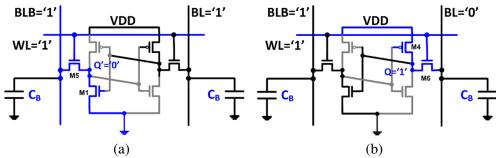

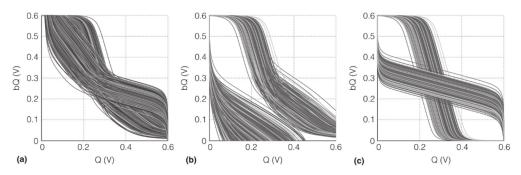

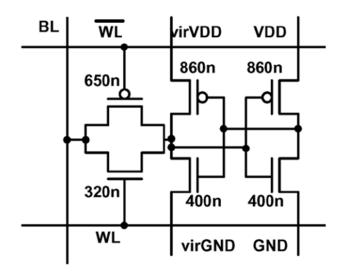

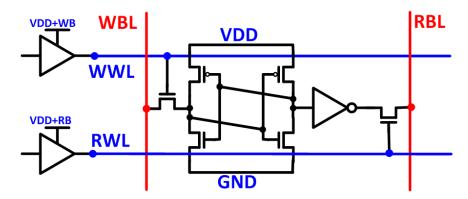

| Fig. 5.10 Proposed non-precharged SRAM (NPSRAM)                                | 82 |

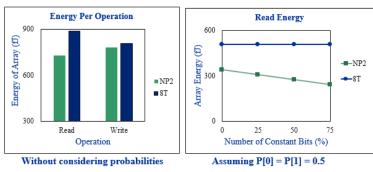

| Fig. 5.11 Estimated energy of memory array                                     | 85 |

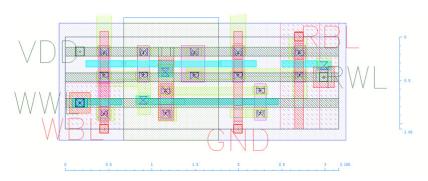

| Fig. 5.12 NPSRAM bitcell layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 85                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

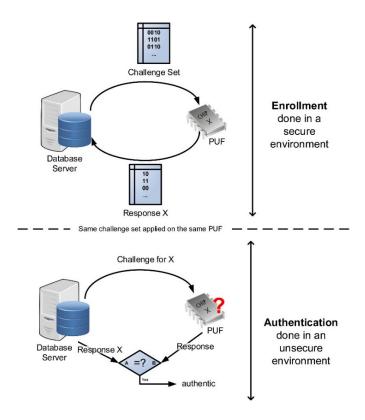

| Fig. 6.1 Illustration of typical chip enrolment and subsequent in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | n-field authentication |

| using challenge-response pairs (CRPs) from PUFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88                     |

| Fig. 6.2 Sample Inter- and Intra-PUF FHD showing decision to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | hreshold and Type I    |

| (false positive) and Type II (false negative) errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91                     |

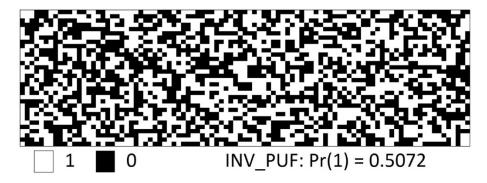

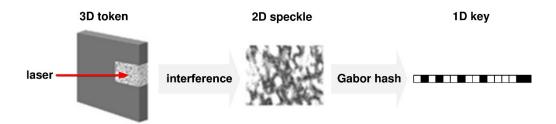

| Fig. 6.3 Sample speckle diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 92                     |

| Fig. 6.4 Physical One-Way Function from a non-homogenous ma                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | terial95               |

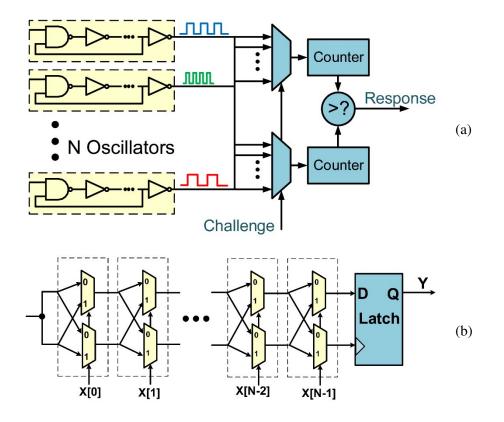

| Fig. 6.5 Delay-based PUFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 95                     |

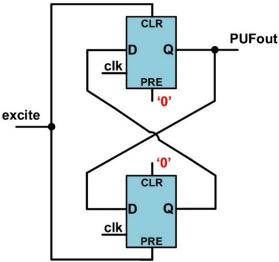

| Fig. 6.6 Butterfly PUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97                     |

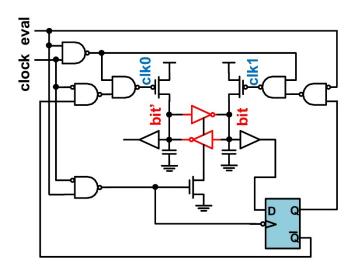

| Fig. 6.7 Metastability-based PUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98                     |

| Fig. 6.8 PTAT-based PUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 99                     |

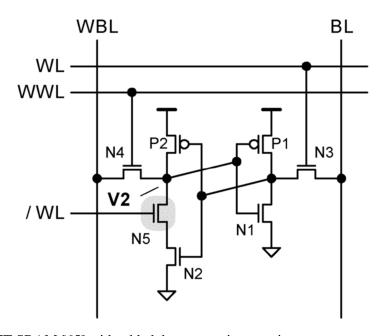

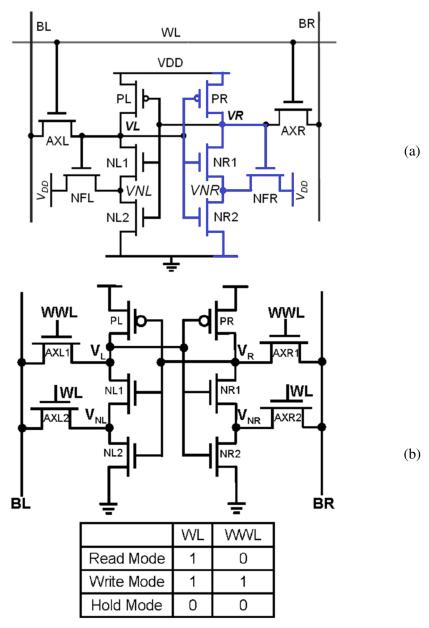

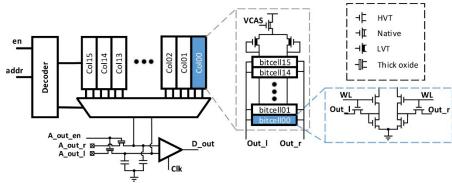

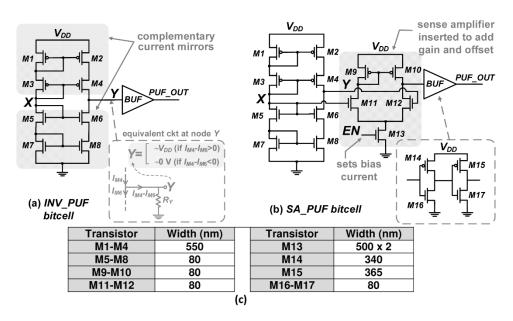

| Fig. 6.9 Static Mono-stable PUFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100                    |

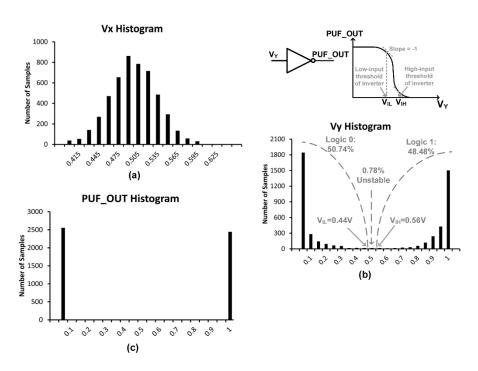

| Fig. 6.10 Sample statistical distribution of VX, VY and PUF_OU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | T101                   |

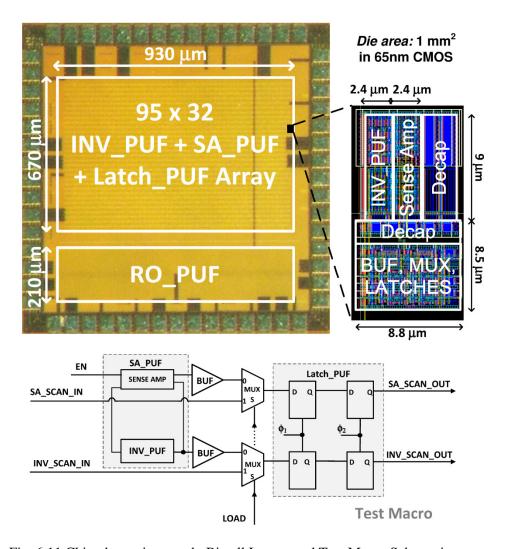

| Fig. 6.11 Chip photomicrograph, Bitcell Layout and Test Macro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Schematics102          |

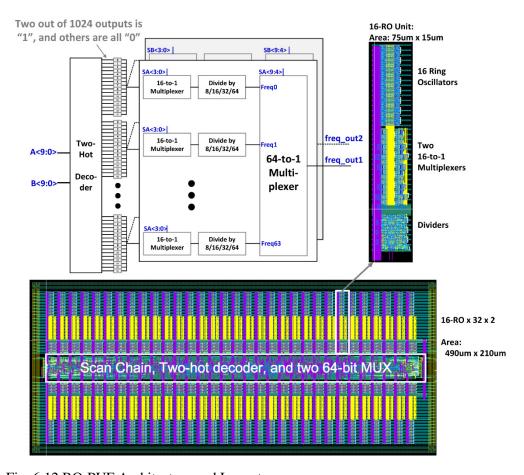

| Fig. 6.12 RO-PUF Architecture and Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 103                    |

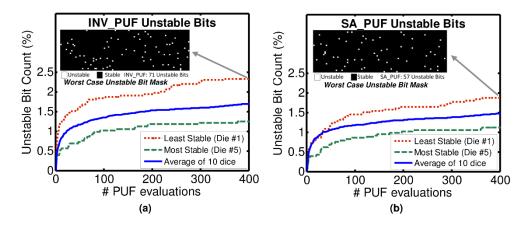

| Fig. 6.13 Native Unstable Bit Count at Nominal Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 104                    |

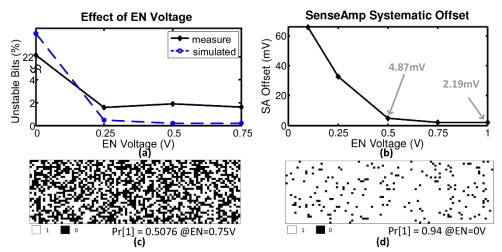

| Fig. 6.14 SA_PUF dependence on EN voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 106                    |

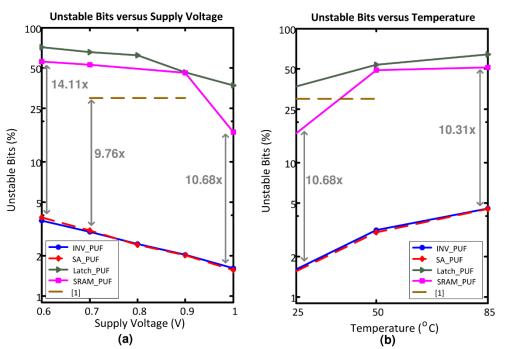

| Fig. 6.15 Percentage unstable bit versus (a) supply voltage and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | l (b) temperature for  |

| different PUFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 107                    |

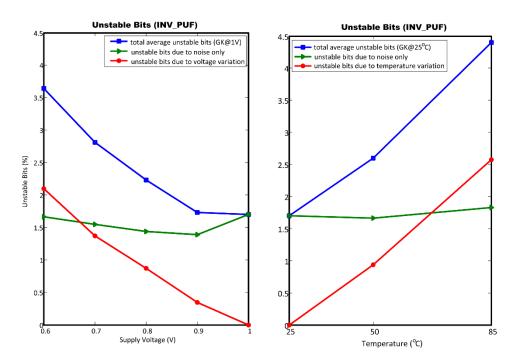

| Fig. 6.16 Breakdown of percentage unstable bits in INV_PUF d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | lue to supply voltage  |

| (left) and temperature (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 108                    |

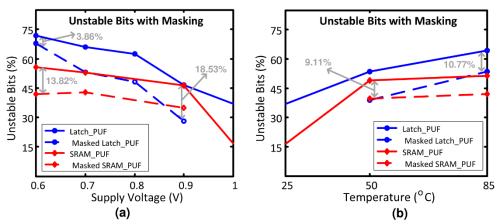

| Fig. 6.17 Effect of masking on unstable bits for Latch_PUF ar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nd SRAM_PUF with       |

| varying (a) supply voltage and (b) tempretaure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 109                    |

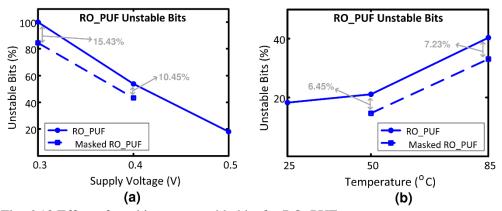

| Fig. 6.18 Effect of masking on unstable bits for RO_PUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 110                    |

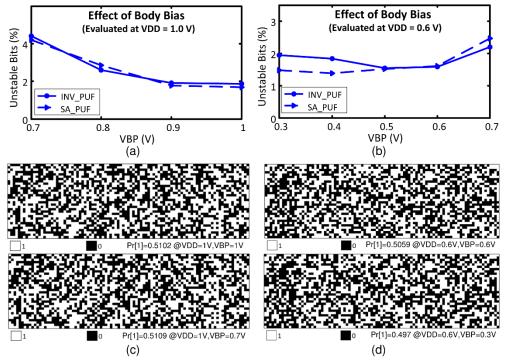

| Fig. 6.19 Effect of body bias on stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110                    |

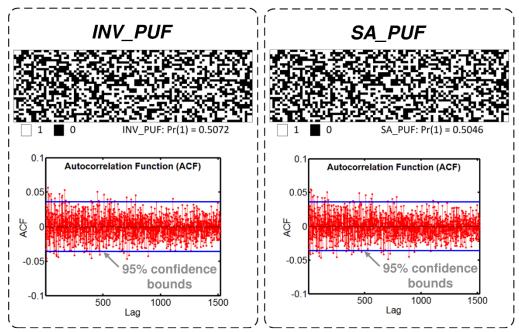

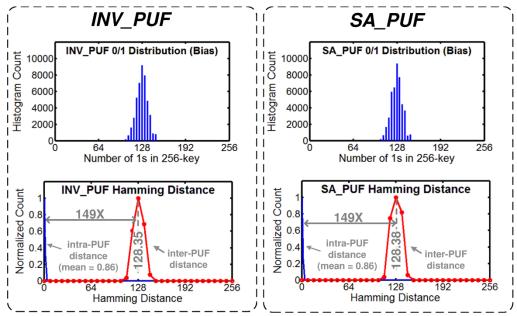

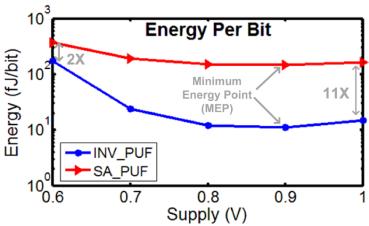

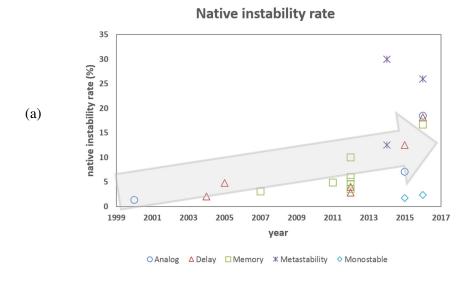

| Fig. 6.20 Speckle diagram of the golden key (top) and spatial auto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ocorrelation from die  |

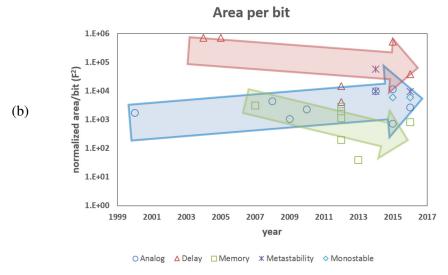

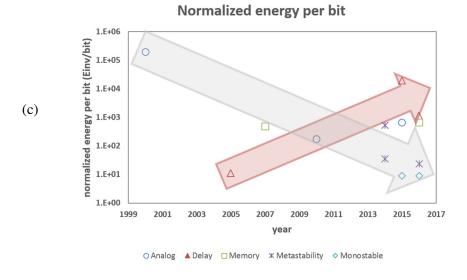

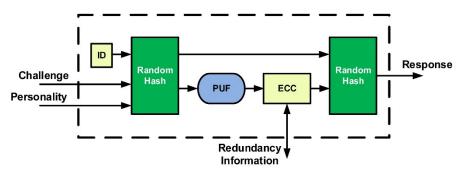

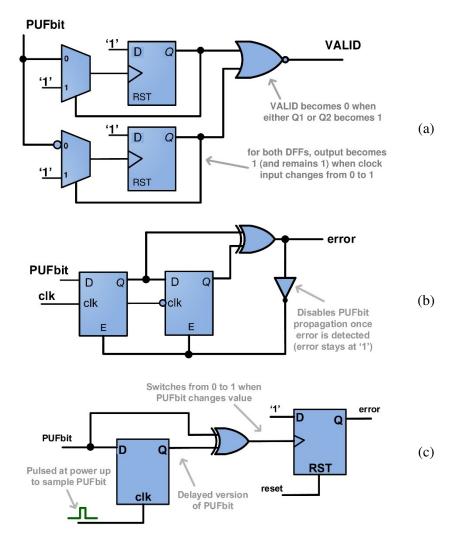

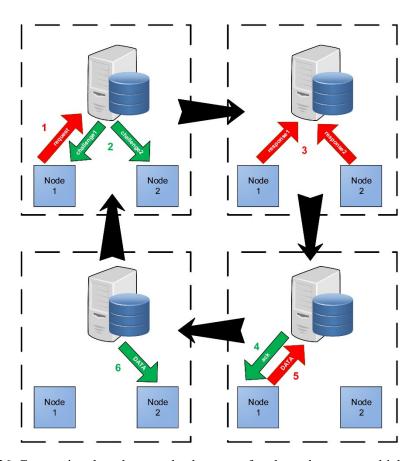

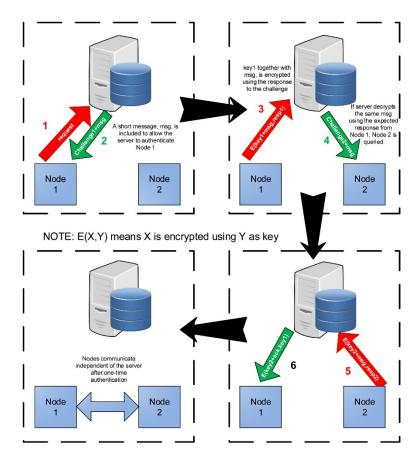

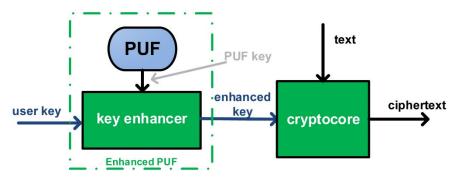

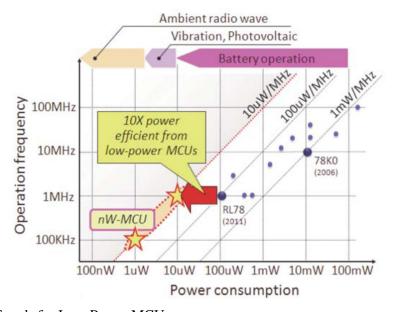

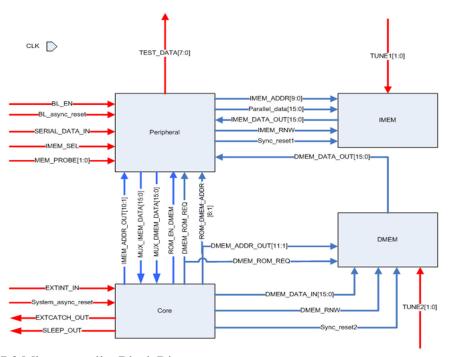

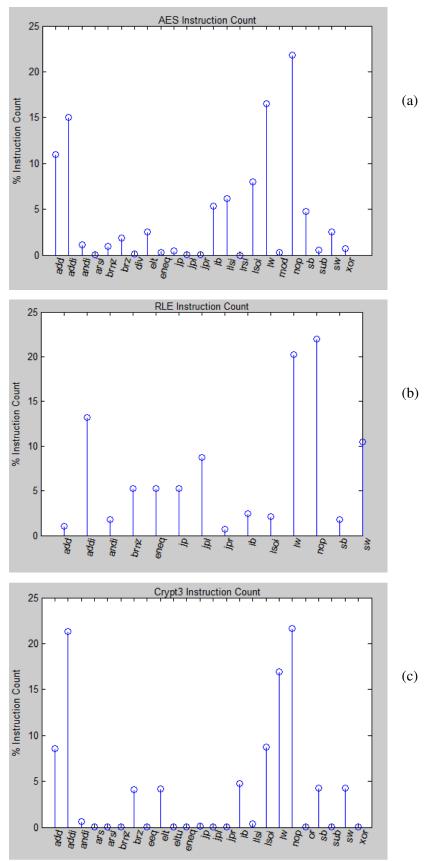

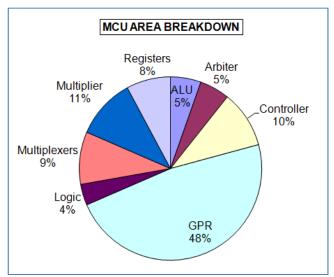

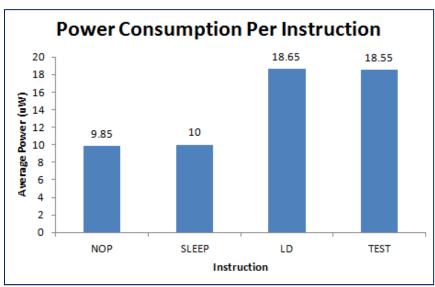

| #1 at nominal conditions for INV_PUF (left) and SA_PUF (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | right)111              |