# DISSERTATION

# submitted to the

Combined Faculties for the Natural Sciences and for Mathematics of the Ruperto-Carola University of Heidelberg, Germany

for the degree of

**Doctor of Natural Sciences**

Put forward by

M.Sc. Mitja Kleider

born in Hannover, Germany

Oral examination: November 14, 2017

# NEURON CIRCUIT CHARACTERIZATION IN A NEUROMORPHIC SYSTEM

# REFEREES:

Prof. Dr. Karlheinz Meier

Prof. Dr. Michael Hausmann

Spiking neural networks can solve complex tasks in an event-based processing strategy, inspired by the brain. One special kind of neuron model, the AdEx model, allows to reproduce several types of firing patterns, which have been found in biological neurons and may be of functional importance. In this thesis we characterize the analog neuron circuit implementation of this model within the full-custom HICANN ASIC. As the central unit of the BrainScaleS accelerated neuromorphic computing platform, it provides a tool to emulate large neural networks in short time and helps to better understand the brain.

Characterization of the neuron circuits leads to calibration of each sub-circuit, translating the desired AdEx model parameters to their corresponding HICANN parameters for each individual neuron. Device mismatch in VLSI manufacturing leads to expected variation from design parameters. These variations can be counteracted by adjustable parameters within the circuits. A wafer-scale BrainScaleS system contains over 1.9 · 10<sup>5</sup> neuron circuits with millions of parameters. Due to the large scale of the system, methods need to be fully automated in a robust way.

Characterizations presented in this work are performed from transistor level simulation to wafer-scale hardware measurements. Our commissioning and calibration efforts are enabling neural network experiments, including complex firing patterns that are computationally expensive when implemented in traditional numerical simulations.

#### ZUSAMMENFASSUNG

Vom Gehirn inspirierte spikende neuronale Netze sind trotz ihres Ereignis-basierten Kommunikations-Ansatzes in der Lage, komplexe Aufgaben lösen. Ein spezielles Neuronenmodell, das AdEx-Modell, kann verschiedene Feuermuster reproduzieren, die in biologischen Neuronen beobachtet wurden und von funktionaler Bedeutung sein könnten. In dieser Arbeit charakterisieren wir die Implementierung dieses Modells durch die analogen Neuronen-Schaltungen des HICANN-ASICs. Der HICANN stellt die zentrale Einheit des neuromorphen BrainScaleS-Systems dar und erlaubt es, große neuronale Netze in kurzer Zeit zu emulieren.

Die Charakterisierung der Neuronen-Schaltungen führt zur Kalibration der einzelnen Schaltungen, die für jedes einzelne Neuron gewünschte AdEx-Parameter in entsprechende HICANN-Parameter übersetzt. Abweichungen der Eigenschaften der Bauelemente während des Herstellungsprozesses führen zu Abweichungen von den Designparametern. Diese können durch einstellbare Parameter ausgeglichen werden. Ein Wafer-System enthält 1.9 · 10<sup>5</sup> Neuronenschaltungen mit Millionen von Parametern. Aufgrund dieser Größe müssen die Methoden vollständig automatisiert und robust sein.

Die in dieser Arbeit vorgestellten Charakterisierungen werden in Transistor-Simulationen und Wafer-übergreifenden Hardware-Messungen durchgeführt. Unsere Bemühungen zur Inbetriebnahme und Kalibration erlauben es, Netzwerkexperimente durchzuführen, einschließlich komplexer Feuermuster, die in numerischer Simulation viel Rechenaufwand erfordern.

# CONTENTS

| Ι  | IN  | TRODU                  | CTION                                           | 1  |  |  |  |

|----|-----|------------------------|-------------------------------------------------|----|--|--|--|

| 1  | NEU | UROMORPHIC COMPUTING 3 |                                                 |    |  |  |  |

| 2  | POI | NT NE                  | URON MODELS                                     | 7  |  |  |  |

|    | 2.1 | Hodg                   | kin-Huxley Model                                | 8  |  |  |  |

|    | 2.2 | Leaky                  | Integrate-and-Fire Model                        | 9  |  |  |  |

|    | 2.3 |                        | evich Model                                     | 9  |  |  |  |

|    | 2.4 | Adap                   | tive Leaky Integrate-and-Fire Model             | 10 |  |  |  |

|    | 2.5 | Adap                   | tive Exponential Leaky Integrate-and-Fire Model | 10 |  |  |  |

| II | BR  | AINSC                  | ALES SYSTEM                                     | 13 |  |  |  |

| 3  | BRA | INSCA                  | LES SYSTEM                                      | 15 |  |  |  |

| 4  | HIC | ANN C                  | HIP                                             | 17 |  |  |  |

| •  | 4.1 | Neuro                  | on Circuit                                      | 17 |  |  |  |

|    | •   | 4.1.1                  | Leakage Term                                    | 18 |  |  |  |

|    |     | 4.1.2                  | Reset Mechanism                                 | 20 |  |  |  |

|    |     | 4.1.3                  | Adaptation Term                                 | 20 |  |  |  |

|    |     | 4.1.4                  | Exponential Term                                | 21 |  |  |  |

|    |     | 4.1.5                  | Current Input and Membrane Output               | 25 |  |  |  |

|    |     | 4.1.6                  | Synaptic Input and Layer 1 Routing              | 25 |  |  |  |

|    |     | 4.1.7                  | Spiking Mechanism and Interconnection           | 27 |  |  |  |

|    | 4.2 | Neuro                  | on Parameters                                   | 27 |  |  |  |

|    |     | 4.2.1                  | Time Constant Scaling and Digital Configuration | 27 |  |  |  |

|    |     | 4.2.2                  | Floating Gate Memory                            | 28 |  |  |  |

|    |     | 4.2.3                  | Neuron Parameters                               | 29 |  |  |  |

|    |     | 4.2.4                  | Shared Parameters                               | 31 |  |  |  |

|    |     | 4.2.5                  | Parameter Translation                           | 32 |  |  |  |

|    | 4.3 | Transi                 | istor-Level Simulation                          | 35 |  |  |  |

|    | 4.4 | Mism                   | atch and Nonlinearity                           | 36 |  |  |  |

|    | 4.5 | Defec                  | t Information                                   | 36 |  |  |  |

| 5  | EXP | ERIME                  | NTAL SETUPS                                     | 37 |  |  |  |

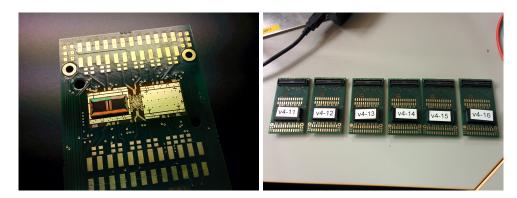

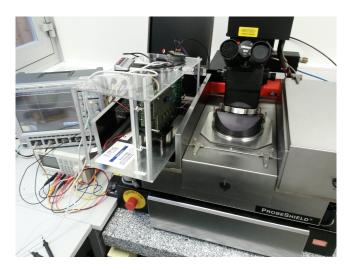

|    | 5.1 | Demo                   | onstrator Setup                                 | 37 |  |  |  |

|    |     | 5.1.1                  | System Emulator Board                           | 38 |  |  |  |

|    |     | 5.1.2                  | Virtex-5 FPGA PCB                               | 39 |  |  |  |

|    |     | 5.1.3                  | HICANN PCB                                      | 39 |  |  |  |

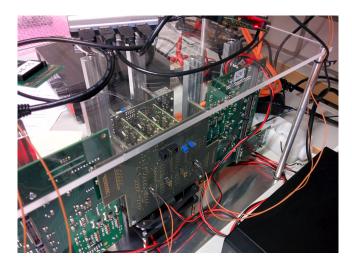

|    | 5.2 | Cube                   | Setup                                           | 40 |  |  |  |

|    |     | 5.2.1                  | Kintex-7 FPGA PCB                               | 41 |  |  |  |

|    | 5.3 | Wafer                  | Setup                                           | 42 |  |  |  |

|    | E 1 |                        | ng Readout Module                               | 12 |  |  |  |

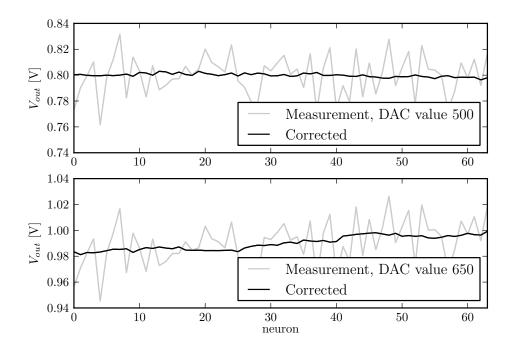

|     |                        | 5.4.1 ADC Calibration                                           | 45         |

|-----|------------------------|-----------------------------------------------------------------|------------|

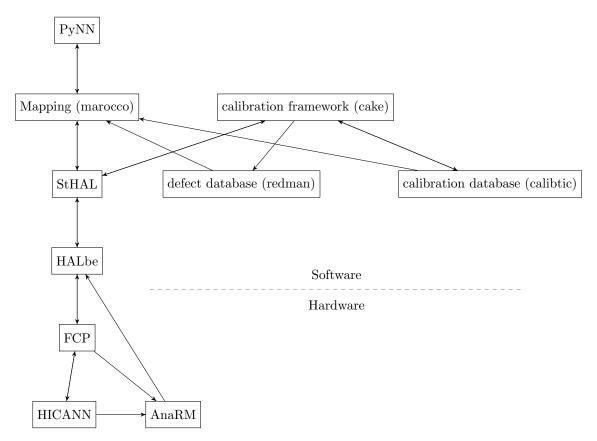

| 6   | CON                    | TTROL SOFTWARE                                                  | 49         |

|     | 6.1                    | Executing Neural Network Experiments                            | 50         |

|     | 6.2                    | Calibration Framework                                           | 51         |

|     |                        | 6.2.1 Core Concepts                                             | 5<br>51    |

|     |                        | 6.2.2 Hardware Interface                                        | 53         |

|     |                        | 6.2.3 Transformation Storage                                    | 53         |

|     | 6.3                    | Methodology                                                     | 54         |

| III | ΔD                     | EX CALIBRATION                                                  | 55         |

| 7   |                        | AMETER ESTIMATION METHODS                                       |            |

| /   | 7.1                    | Experimental Setup                                              | 57<br>57   |

|     | /.1                    | 7.1.1 Hardware Measurements                                     | 57<br>57   |

|     | 7.2                    | Disabling Terms                                                 | 57<br>58   |

|     | 7.2<br>7.3             | Previous Work                                                   | 59         |

|     | 7·3<br>7·4             | Output Buffer Offset                                            | 59<br>59   |

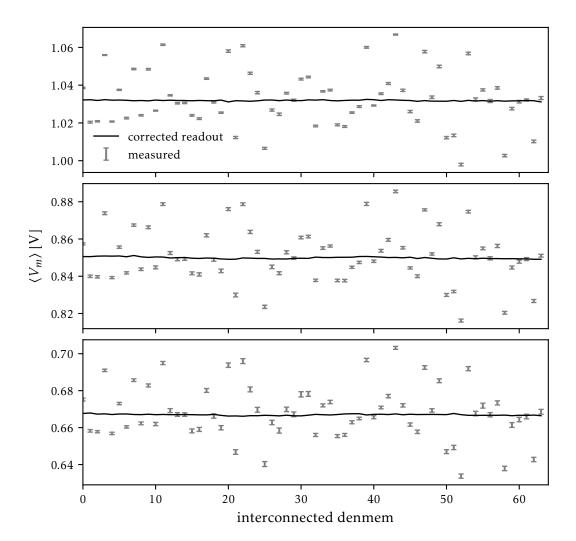

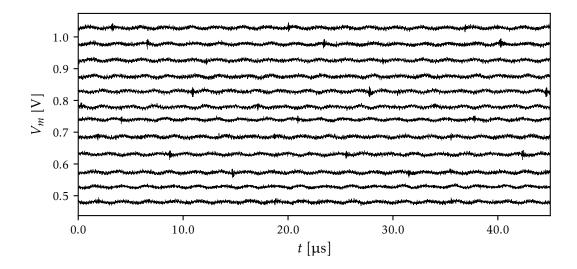

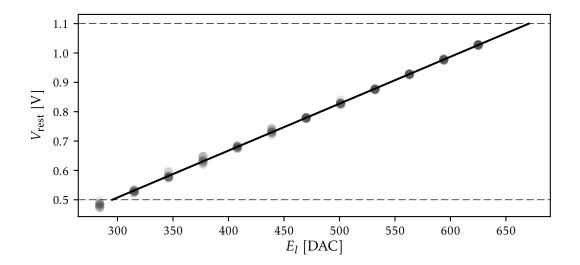

|     | 7· <del>4</del><br>7·5 | Resting Potential                                               | 62         |

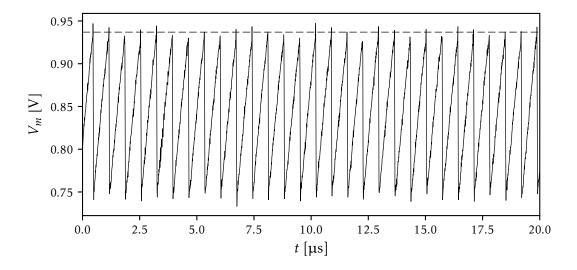

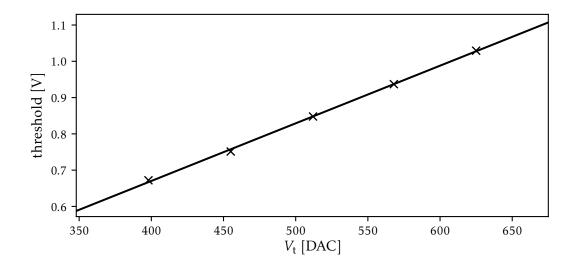

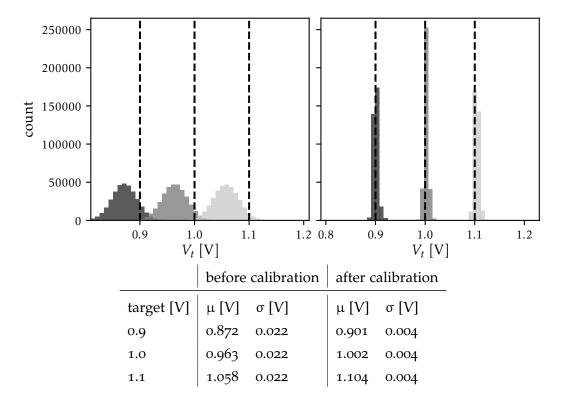

|     | 7.6                    | Threshold Potential                                             | 62         |

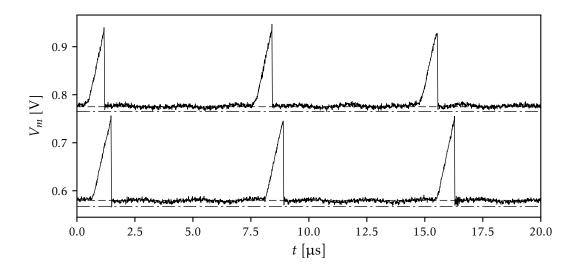

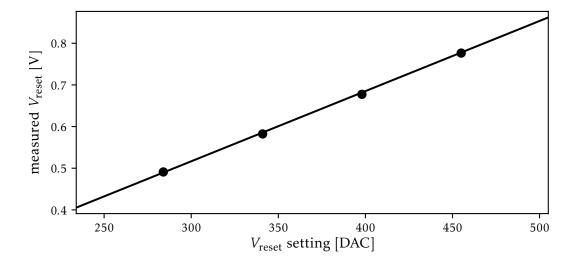

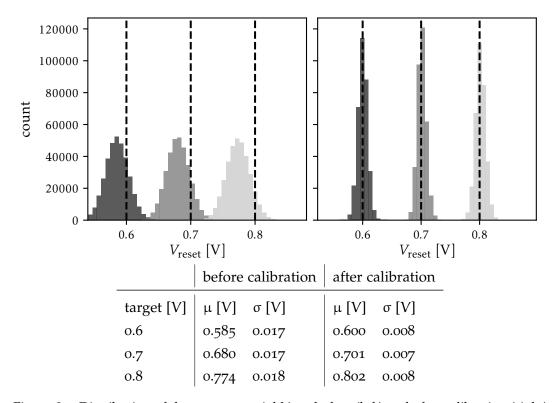

|     | 7.0<br>7.7             | Reset Potential                                                 | 64         |

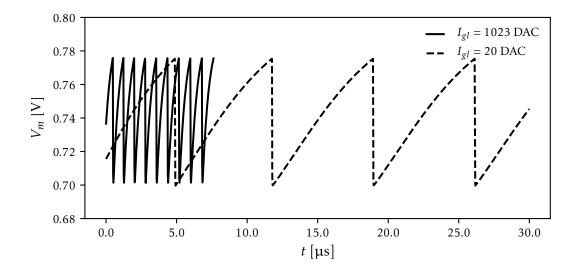

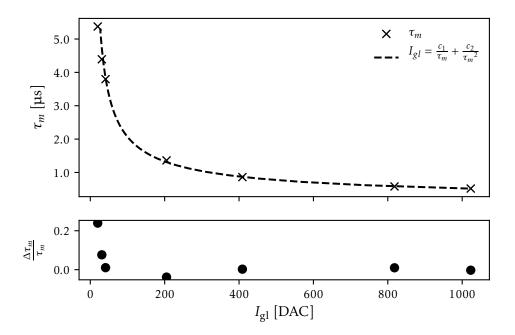

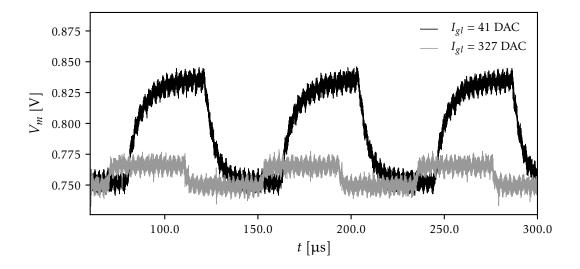

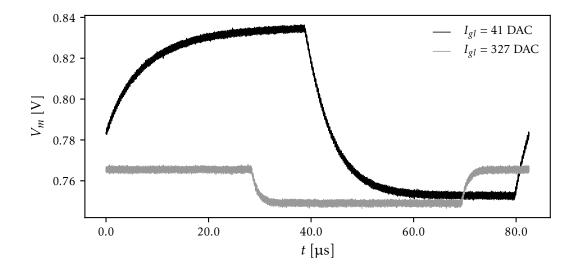

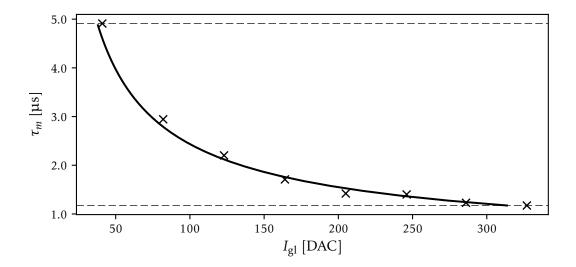

|     | 7.7<br>7.8             | Membrane Time Constant                                          | 66         |

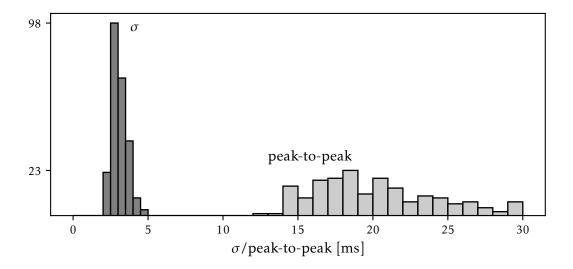

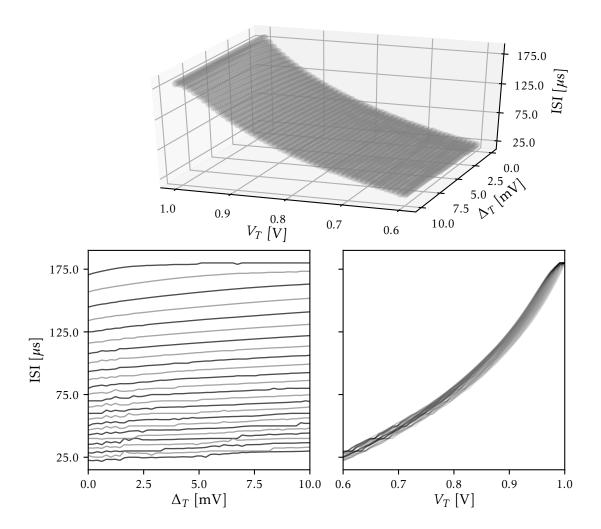

|     | 7.0                    | 7.8.1 ISI-based Method                                          | 66         |

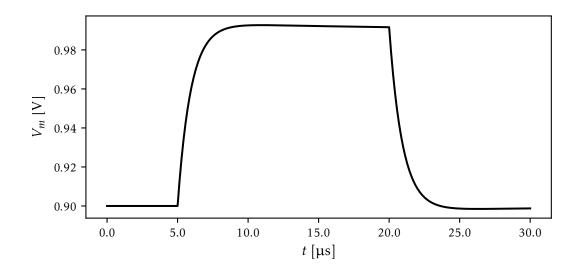

|     | 7.9                    | Stimulation-Based Method                                        | 68         |

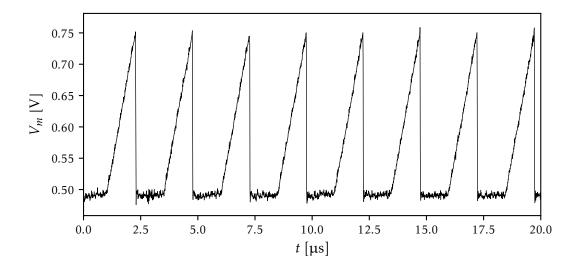

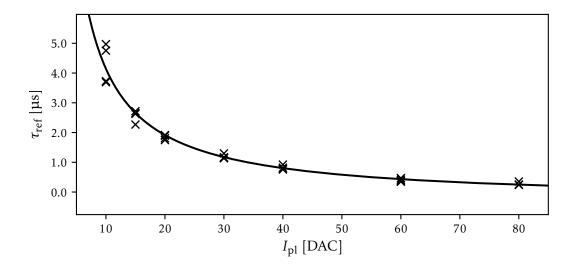

|     | • /                    | Refractory Period                                               | 71         |

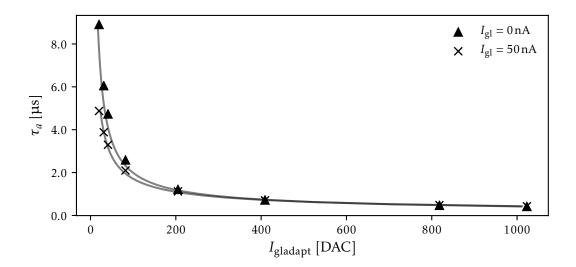

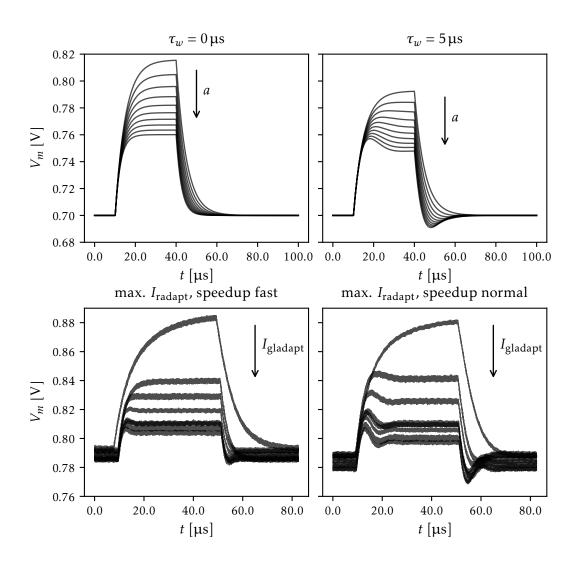

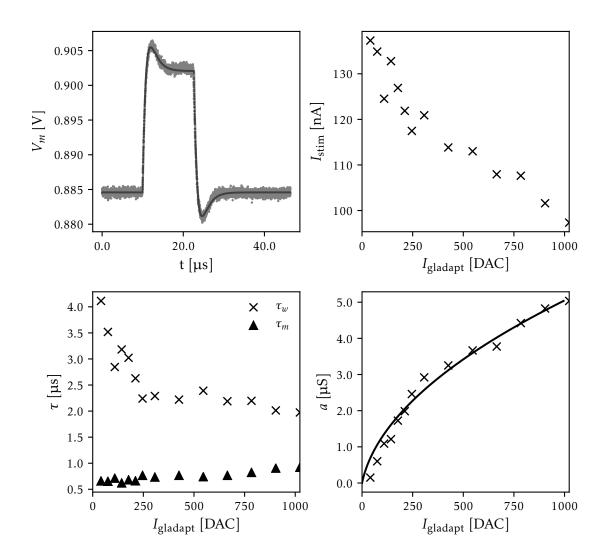

|     |                        | Adaptation Parameters                                           | 72         |

|     | ,                      | 7.11.1 ISI-Based Determination of the Coupling Parameter a      | <b>7</b> 3 |

|     |                        | 7.11.2 Determination of Coupling a in Analogy to Leakage Term   | 75         |

|     |                        | 7.11.3 Determining Adaptation Parameters via Differential Equa- | , ,        |

|     |                        | tion Fitting                                                    | 76         |

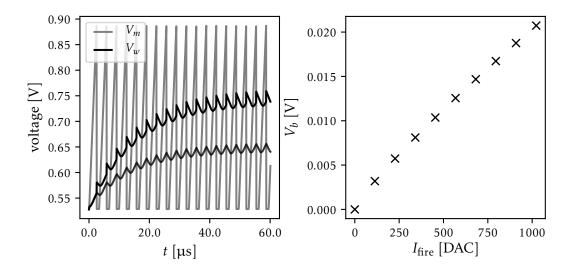

|     |                        | 7.11.4 Determining the STA Parameter b                          | 78         |

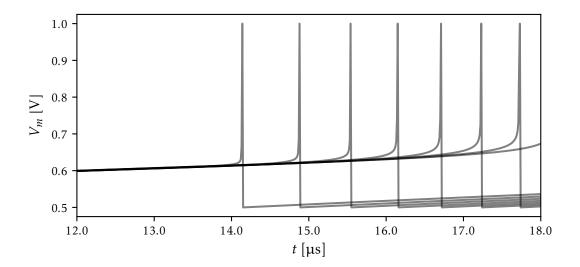

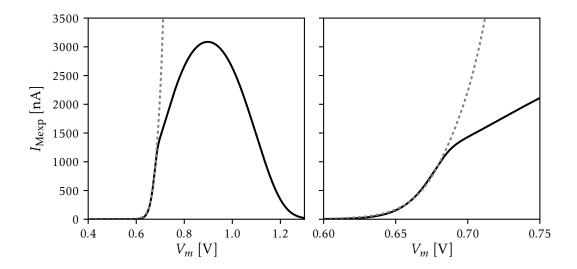

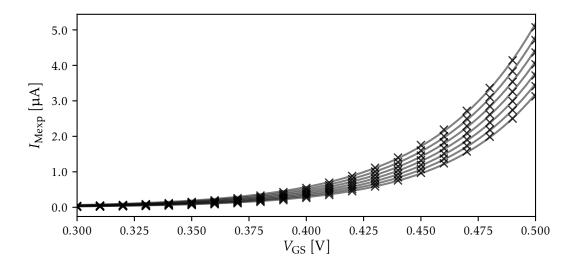

|     | 7.12                   | Exponential Parameters                                          | 80         |

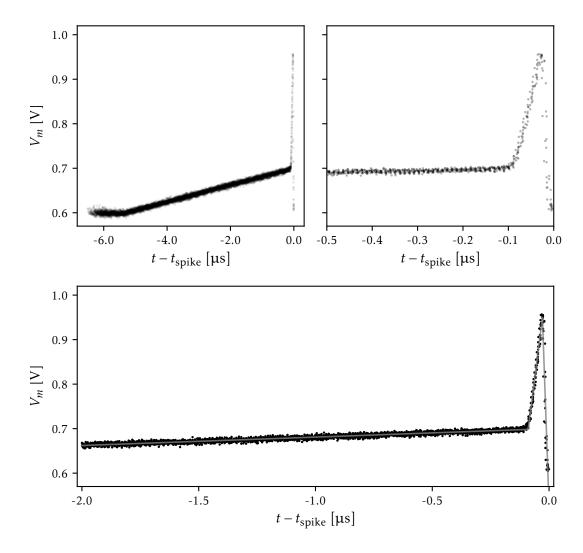

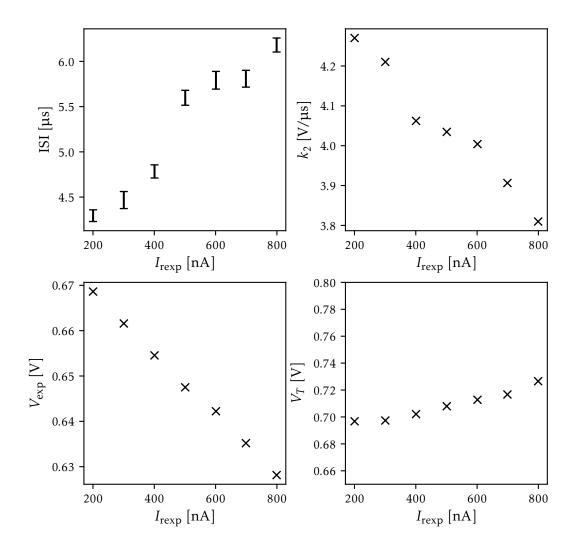

|     |                        | 7.12.1 General Considerations                                   | 80         |

|     |                        | 7.12.2 Previous Work                                            | 84         |

|     |                        | 7.12.3 Keeping $V_T$ Constant                                   | 85         |

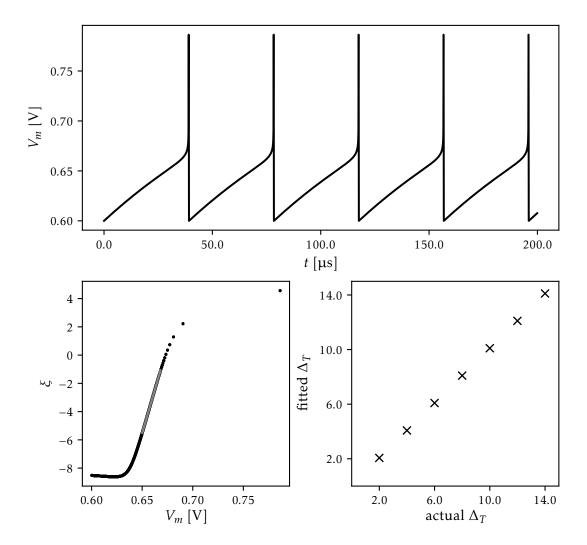

|     |                        | 7.12.4 Determining $\Delta_T$                                   | 87         |

|     |                        | 7.12.5 Hardware Measurement of $\Delta_T$ and $V_T$             | 90         |

| IV  | WA                     | FER CALIBRATION                                                 | 97         |

| 8   | WAI                    | FER-SCALE LIF CALIBRATION                                       | 99         |

|     |                        |                                                                 |            |

| V   |                        | SCUSSION                                                        | 107        |

| 9   |                        | ICLUSION AND OUTLOOK                                            | 109        |

|     | 9.1                    | Discussion of Methods                                           | 109        |

|     | 9.2                    | Time Requirement of Calibration                                 | 111        |

|    | 9.3  | Current And Future Network Experiments | 113 |

|----|------|----------------------------------------|-----|

| VI | AP   | PENDIX                                 | 115 |

| A  | EXP  | ERIMENT DURATION                       | 117 |

| В  | PAR  | AMETER SETTINGS                        | 119 |

|    | B.1  | Base Configuration                     | 119 |

|    | B.2  | Resting Potential                      | 119 |

|    | B.3  | Reset Potential                        | 120 |

|    | B.4  | Threshold Potential                    | 120 |

|    | B.5  | Refractory Period                      | 120 |

|    | в.6  | Membrane Time Constant                 | 120 |

|    |      |                                        |     |

| ΒI | BLIO | GRAPHY                                 | 127 |

# Part I INTRODUCTION

NEUROMORPHIC COMPUTING

The human brain is a powerful computation system (Piccinini and Bahar, 2013): being energy efficient, robust against defects, and able to learn quickly, it has inspired new approaches to process information by copying aspects of its dynamics and structure. Traditional computing separates memory and logic, while the human brain accomplishes both in a network consisting of roughly 10<sup>10</sup> neurons and 10<sup>14</sup> synaptic connections (Pakkenberg et al., 2003) between neurons. Connectivity between units is high, at up to 10<sup>4</sup> incoming synapses per neuron. Boolean logic, which is trading energy for precision, does not seem to be required to accomplish information processing features of a brain. Although lots of data has been collected on properties of neurons and their connectivity, the details of how the brain represents, memorizes and processes information are not yet fully understood.

Modern machine learning algorithms, especially artificial neuronal networks initially inspired by the brain, are able to perform increasingly complex tasks that could previously only be performed by humans: image recognition, decision making, driving cars, or winning the board game Go (Bojarski et al., 2016; Silver et al., 2016) are just a few examples. As the number of everyday applications is growing and energy budget is limited, a new conceptual approach to computing is required. Companies are already building specialized hardware to reduce power consumption of their algorithms (Jouppi et al., 2017). However, there are still some pronounced differences. The algorithms may even be better at specialized tasks than a human, while the human brain is much more universal. In some cases, such as playing Go, the human brain is able to learn from observing very few examples, while artificial networks require way more training examples.

In order to better understand how the brain processes and stores information, numerical simulations of neural networks on traditional hardware are a powerful tool in the field of computational neuroscience. Several simplified neuron models are introduced in chapter 2. Efficiently scaling such simulations to large networks is a difficult task, communication can be the major bottleneck limiting parallel simulations (Migliore et al., 2006). The human brain excels at energy consumption of about 20 W (Drubach, 2000), compared to traditional computers based on the von Neumann architecture. For example, Helias et al. (2012) simulated neural networks based on a simplified neuron model on the K supercomputer, consuming approximately 10<sup>10</sup> times more energy than an equivalent sized part of the brain. Time evolution in such simulations is about 10<sup>3</sup> times slower than biological time, although methods have been developed to increase performance of such large-scale simulations (Kunkel et al., 2013).

There is an even more radical approach to casting aspects of brain computation into silicon, called neuromorphic computing. The idea to operate electronic transistors similar to neurons was first established by Carver Mead (Mead, 1990; Mead, 1989). Mead proposed to build very-large-scale integration (VLSI) systems with analog circuits working similar to the nervous system of a biological brain, emulating ion flow across the membrane of a neuron by electron flow through a transistor. Originally the term neuromorphic computing was used for subthreshold analog electronics, today it is used in a much broader sense and also includes purely digital and mixed-signal circuits.

There are many diverse examples for neuromorphic systems with different goals, including sensors (Vanarse, Osseiran, and Rassau, 2016), winner-take-all circuits (Indiveri, Chicca, and Douglas, 2009), and systems designed for large neural networks (Furber, 2016). One goal of such neuromorphic computing systems is to perform tasks where the brain outperforms traditional computers, at similarly low power consumption. Aside from the computing aspect in the interdisciplinary field of brain-inspired computing, building such systems may also help the field of neuroscience in exploring and understanding features of the brain such as representation of information, computations, robustness to defects and learning. Due to their neural network architecture, some systems also feature built-in robustness (Kalampokis et al., 2003; Petrovici et al., 2016) and may be able to compensate yield issues in modern chip manufacturing processes.

Compared to numerical integration of differential equations in computer simulations on super computers, the approach of building neuromorphic hardware as simulation tools uses less energy. Neuromorphic systems that are designed for large neural networks are aiming at simulation of these networks in real-time or faster, after an initial configuration phase. Due to the neuromorphic architecture, the speed just depends weakly, if at all, on the network size.

Many analog hardware implementations of spiking neurons exist today (Indiveri, Linares-Barranco, et al., 2011). In this thesis we will work with the BrainScaleS system, a large-scale neuromorphic system that uses an analog neuron model. Apart from the BrainScaleS system, there are several other neuromorphic hardware projects of similar scale, which have also been developed over similar time spans: TrueNorth (Sawada et al., 2016), being developed by IBM, SpiNNaker (Furber, Galluppi, et al., 2014), developed at the University of Manchester, and Neurogrid (Benjamin et al., 2014), developed at Stanford University. Their approaches are complementary, each choosing a different compromise between flexibility, accuracy, power consumption and detailed features of the supported neuron models:

The TrueNorth chip is designed as an application delivery platform for real-time cognitive applications (Esser, Andreopoulos, et al., 2013). One chip consists of 4096 cores of 256 digital integrate-and-fire neurons with 256 synaptic inputs each (Cassidy et al., 2013). Chips can be interconnected for larger applications. Incoming spike events are connected to selected neurons via a  $256 \times 256$  cross-bar. Output events are connected to one other core, if several cores should be connected,

identical neurons that receive the same input can be used to generate identical output to each core. The hardware behaves deterministically and can be simulated in software, which is required for off-line training. The idea is to provide a library of cognitive modules which can be combined for a specific application (Amir et al., 2013). A possible application for example is efficient image classification using deep convolutional networks, processing more than 6000 frames per Joule (Esser, Merolla, et al., 2016).

The SpiNNaker system is similar to a conventional supercomputer with several optimizations towards simulation of neural networks in real time. The processors are integer ARM969 cores originally developed for embedded applications. Communication through a multicast packet router is optimized for large numbers of very small data packets (Furber, 2016), typically single spikes. This approach allows high scalability (Furber, Lester, et al., 2012) and energy efficiency compared to conventional supercomputers while retaining some flexibility with respect to neuron models, but with the restriction of integer operations.

The Neurogrid system is based on subthreshold analog circuits (Benjamin et al., 2014). One board holds 16 Neurocore chips of  $256 \times 256$  neurons, emulating ion channel activity in analog circuits. Spike communication and routing is digital. The neurons implement a quadratic integrate-and-fire model with shared leaky integrator dendritic circuits, operating in real time. Several parameters and the synapses are shared, reducing the network modeling possibilities, but leading to extremely low power consumption of less than two Watts for the whole board.

A possible application of neuromorphic real-time systems are small mobile robots, especially when they are battery powered. Future applications of systems that are able to process input faster than biological time are temporal data streams: detecting patterns and making predicitions, analyzing large volumes of data, in the areas of science, medicine, business, or civil services. Possible future industry applications of low power neuromorphic systems include mobile medical diagnostics, analyzing Lidar data on an automobile and other tasks that require fast processing of information from high-throughput sensors, because such systems need to respond on a similar time scale as the physical system. In particular for applications requiring high speeds, technology developed for the BrainScaleS system may be suitable to be adapted towards such applications.

In the next chapter we will give an overview of neuron models that lead to the neuron model emulated by the BrainScaleS system. In chapter 3 the BrainScaleS system is introduced, followed by details on its central component, the High Input-Count Analog Neural Network (HICANN) chip (chapter 4), experimental setups (chapter 5) and their control software (chapter 6). Chapter 7 presents the methods that have been developed to characterize the neuron circuits. The application of these methods to a full wafer is shown in chapter 8, followed by a discussion of the results in chapter 9.

A biological neuron can be roughly divided into three functional parts: dendrites, soma and axon. The dendrites collect input signals, short electrical pulses, from other neurons and transmit them to the soma. The soma generates an output signal if the input exceeds a certain threshold. The output pulse, called action potential or spike, is transmitted to other neurons via the axon. The junction between two neurons is the synapse, where, most commonly the signal is transmitted chemically between neurons via transmitter molecules. The sending cell is called presynaptic neuron and the receiving cell is called postsynaptic neuron. A single neuron typically connects to 10<sup>4</sup> presynaptic neurons (Gerstner et al., 2014) in a neural network. Action potentials of a given neuron always have roughly the same form. They are essentially binary signals (Sterling and Laughlin, 2015), information is encoded in the timing and number of spikes. The sequence of spikes from a single neuron is called spike train. In some sense, one can view the brain itself as a mixed-signal device: in contrast to the fast digital signalling via spikes, the signal processing in neurons and synapses is an efficient analog chemical process. Usually it is not possible to excite a second spike immediately after a spike, the neuron needs to recover during a refractory period.

Like other cells, neurons have a cell membrane separating its interior from the extracellular space. The concentration of ions inside the cell differs from the outside. This generates an electric potential over the membrane, the cell membrane potential. A typical neuron at rest, without any input, has a negative polarisation of about  $-65 \, \text{mV}$ . The potential changes with incoming spikes. If it increases, reducing (depolarizing) the negative polarization, the synapse is excitatory. If it decreases, the synapse is inhibitory. The change from the resting potential caused by a spike at the postsynaptic neuron is the post-synaptic potential (PSP). The dynamic range of the membrane potential is in the order of tens of millivolts, whereas the resulting action potential has an amplitude of about 100 mV.

There are controversial discussions which level of detail is still relevant in order to realize brain functionality. From the biologist point of view, details at the molecular level are still important. A cognitive scientist might not even care about action potentials. The field of machine learning in computer science is able to perform certain tasks as good or better than humans with fine-tuned artifical neural networks, using very simple neuron models far from biology. However, these models might lack critical features to provide other functionality of an actual brain. In the following we will introduce several models that lead to the physical model implementation which is characterized in this thesis.

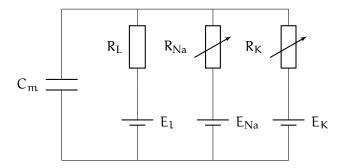

Figure 2.1: Ion channels as modeled by the Hodgkin-Huxley model. The unspecific leakage channel  $R_{\rm L}$  is time-independent. The conductances of the sodium and potassium channels depend on activation and inactivation variables m, n, h.

#### 2.1 HODGKIN-HUXLEY MODEL

The conductance-based Hodgkin-Huxley neuron model consists of a set of non-linear differential equations describing the membrane potential and the state of several ion channels. Ion channels move charge in the form of ions through the membrane. The membrane potential at which there is no net flow through one type of ion channel is called its reversal potential or Nernst potential. In its original form (Hodgkin and Huxley, 1952) the Hodgkin-Huxley neuron model describes three types of ion channels: a sodium channel with resistance  $R_{Na}$  and reversal potential  $E_{Na}$ , a potassium channel with resistance  $R_{K}$  and reversal potential  $E_{K}$  and an unspecific channel with resistance  $R_{L}$  and reversal potential  $E_{L}$ . This model has later been extended by many additional types of ion channels after they have been discovered. The unspecific leakage channel has a voltage-independent conductance  $g_{L} = \frac{1}{R_{L}}$ .

The conductances of the voltage-gated sodium and potassium channels contain time-dependent gating variables  $\mathfrak{m}(t)$ ,  $\mathfrak{n}(t)$  and  $\mathfrak{h}(t)$ , each with its own differential equation. The resulting currents onto the membrane capacitance  $C_\mathfrak{m}$  cause a change in the membrane potential  $V_\mathfrak{m}$  as

$$C_{m}\frac{dV_{m}}{dt}=-\hat{g}_{Na}\,m^{3}h\left(V_{m}-E_{Na}\right)-\hat{g}_{K}\,n^{4}\left(V_{m}-E_{K}\right)-g_{L}\left(V_{m}-E_{L}\right)+I\text{, (2.1)}$$

with additional external current stimulus I. The terms containing the gating variables m, n and h are responsible for spike generation and will be replaced by a reset mechanism in the next section.

The description of action potentials on the level of ion channels forms the basis for detailed biophysical neuron models. These models include varying sets of additional ion channels, which have been discovered in electrophysiological experiments. For example, spike-frequency adaptation is not present in the original Hodgkin-Huxley model.

#### 2.2 LEAKY INTEGRATE-AND-FIRE MODEL

In a rough approximation, neuronal dynamics consist of integration of inputs and a firing mechanism, replacing the coupled nonlinear differential equations from the previous section by a reset condition. The class of neuron models describing action potentials as events are called Integrate-and-Fire models (Gerstner et al., 2014). Firing events are often defined as delta function at the time when the membrane potential is crossing a threshold  $V_t$ . The other component is an equation describing the evolution of the membrane potential  $V_m$ . The simplest model of this class is the Leaky Integrate-and-Fire (LIF). In the absence of external current stimulus I or synaptic input, the potential is at its resting value  $E_1$ . The cell membrane acts like a capacitor  $C_m$  that is charged by a current stimulus. The charge will slowly leak through the cell membrane with a conductance  $g_I$ :

$$C_{m} \frac{dV_{m}}{dt} = -g_{L}(V_{m} - E_{l}) + I.$$

(2.2)

The differential equation is complemented by a firing condition: the LIF model introduces a non-continuous firing mechanism by defining a firing threshold  $V_t$ . The neuron is firing when  $V_m$  crosses  $V_t$  from below and its membrane potential is reset immediately to a reset potential  $V_{reset}$ :

$$V_{\rm m} \rightarrow V_{\rm reset}$$

. (2.3)

This approach also reduces computational complexity for computer simulations.

As this model is highly simplified, it can not reproduce many aspects of neuronal dynamics, such as adaptation, bursting and inhibitory rebound. Two major limitations of the basic LIF model are the linear integration of synaptic or external stimulus current and the spiking mechanism that does not keep any memory of previous spikes. If adaptation and refractoriness are added to the model, it is able to predict biological spike times more accurately (Gerstner et al., 2014).

Refractoriness can be added by clamping the membrane potential to  $V_{reset}$  during the refractory period  $\tau_{ref}$  after a spike at  $t_{spike}$ :

$$V_{m}\left(t_{spike} < t \leqslant t_{spike} + \tau_{ref}\right) = V_{reset}. \tag{2.4}$$

### 2.3 IZHIKEVICH MODEL

Izhikevich proposed a quadratic integrate-and-fire model that reproduces spiking and bursting behavior of neurons (Izhikevich, 2003):

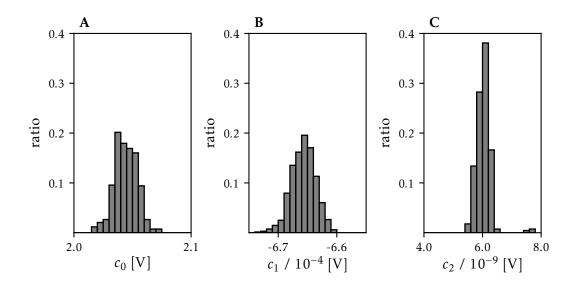

$$\frac{dV_{m}}{dt} = c_{2} \cdot V_{m}^{2} + c_{1} \cdot V_{m} + c_{0} - w + I, \tag{2.5}$$

$$\frac{\mathrm{d}w}{\mathrm{d}t} = a \cdot (b \cdot V_{\mathrm{m}} - w),\tag{2.6}$$

with a reset condition: if  $V_m \geqslant 30\,\text{mV}$ , set  $V_m = c$  and w = w + d. The variables  $V_m$  and w as well as the parameters a, b, c and d are dimensionless. The constants  $c_0$ ,  $c_1$  and  $c_2$  in equation (2.5) were fitted to match recorded neuron dynamics.  $V_m$  represents the membrane potential, w represents a recovery variable, accounting for activation of the potassium ion current and inactivation of the sodium current. a describes the recovery time scale, b the sensitivity of w to fluctuations of  $V_m$ . c is the reset value of  $V_m$ , and d is a spike-triggered change of the recovery variable w.

#### 2.4 ADAPTIVE LEAKY INTEGRATE-AND-FIRE MODEL

The LIF model can be extended by adding an adaptation variable, similar to the recovery variable in the Izhikevich model:

$$C_{m} \frac{dV_{m}}{dt} = -g_{L}(V_{m} - E_{l}) - w,$$

(2.7)

$$\tau_{w} \frac{\mathrm{d}w}{\mathrm{d}t} = \alpha \left( V_{m} - E_{l} \right) - w. \tag{2.8}$$

The firing condition remains as defined by the LIF model. For Spike-Triggered Adaptation (STA) the adaptation current is increased by a constant value b at each firing event:

$$w \to w + b. \tag{2.9}$$

#### 2.5 ADAPTIVE EXPONENTIAL LEAKY INTEGRATE-AND-FIRE MODEL

Introduced by Brette and Gerstner (2005), the Adaptive Exponential Leaky Integrateand-Fire (AdEx) model extends the two-variable model from the previous section by an exponential nonlinearity proposed in Fourcaud-Trocmé et al. (2003). The resulting AdEx model is described by two differential equations:

$$C_{m}\frac{dV_{m}}{dt} = -g_{L}(V_{m} - E_{l}) + g_{L}\Delta_{T} \exp\left(\frac{V_{m} - V_{T}}{\Delta_{T}}\right) - w + I. \tag{2.10}$$

And as before,

$$\tau_{w} \frac{\mathrm{d}w}{\mathrm{d}t} = \alpha \left( V_{m} - E_{l} \right) - w. \tag{2.11}$$

The first equation describes the evolution of the membrane potential  $V_m$  on a membrane capacity  $C_m$ . There are several current terms, beginning with a leakage current through the leak conductance  $g_L$ , pulling the membrane voltage towards the resting potential  $E_l$ . The second term on the right hand side is the exponential term with slope factor  $\Delta_T$  and exponential threshold  $V_T$ . Third comes the adaptation current w, its course is described by the second differential equation. Its time

evolution is described by the adaptation coupling conductance  $\alpha$  and adaptation time constant  $\tau_w$ . The last term in equation (2.10) I is the sum of input currents, which can be synaptic currents or external stimulus. The firing condition remains as introduced in section 2.2. With the addition of the exponential term, in a purely mathematical description the neuron would be firing at time  $t^f$  when its membrane potential  $V_m$  diverges towards infinity.

This model is able to reproduce several other neuron models. Removing the adaptation variable w results in the exponential integrate-and-fire model (Fourcaud-Trocmé et al., 2003). In the limit  $\Delta_T \to 0$ , we obtain the adaptive LIF model. Without exponential term ( $\Delta_T \to 0$ ) and by setting  $\alpha = 0$ , there remains LIF with STA as proposed in Treves (1993). Setting b = 0 results in subthreshold adaptation (Richardson, Brunel, and Hakim, 2003).

There are many similarities to the Izhikevich model: the AdEx model remains fast to simulate numerically, shows the same bifurcation patterns and a large variety of firing patterns. Quantitative fits to experimental data are better when using the AdEx model (Naud et al., 2008). There are also a few differences between the two models: while the Izhikevich model contains a quadratic voltage dependency, the nonlinear dependency of the AdEx model is exponential. The resulting upswing of the action potential in the AdEx model is more realistic (Badel et al., 2008). The AdEx model also remains linear in the subthreshold regime as observed in experiments, while the Izhikevich model shows unrealistic nonlinearities (Badel et al., 2008). The attenuation of high frequency inputs follows as  $\frac{1}{f}$  in the AdEx model, compared to  $\frac{1}{f^2}$  in the Izhikevich model (Fourcaud-Trocmé et al., 2003).

In summary, the Adaptive Exponential Leaky Integrate-and-Fire (AdEx) model is a good compromise between computational complexity and reproducibility of firing characteristics which have been observed in biological experiments.

This model is implemented in the BrainScaleS system introduced in chapter 3. The firing patterns presented in (Naud et al., 2008) have been reproduced using this system in Schwartz (2013), Tran (2013), and Kiene (2014).

# Part II BRAINSCALES SYSTEM

The neuromorphic hardware located in Heidelberg is called BrainScaleS. The idea behind this large-scale system is that configurable synaptic connectivity and weights as well as configurable individual neuron parameters provide the flexibility to realize various functionality in artificial neural circuits. Simulating learning on traditional computing architectures takes a long time, even if it is possible to provide the large amount of required energy. Our approach is to develop a new computing architecture which is much faster at emulating neural networks than traditional computing architectures and requiring less energy at the same time.

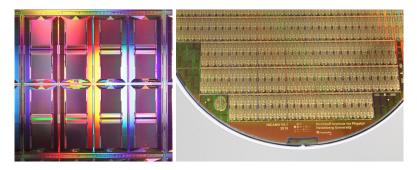

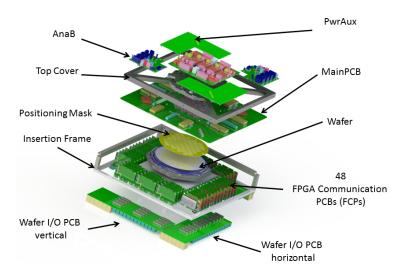

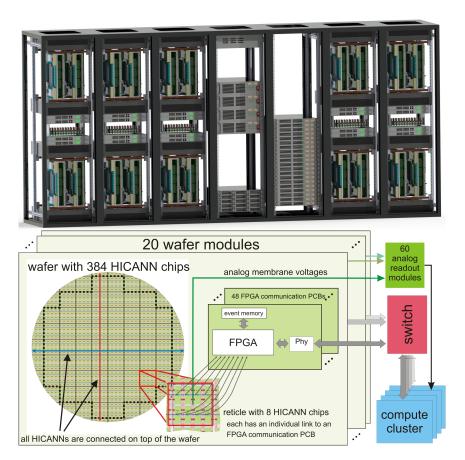

The central component of the BrainScaleS system is the full-custom, mixed-signal HICANN chip, which is introduced in chapter 4. There are three key concepts: each wafer module features a high neuron count without depending on external connections, due to an architecture called wafer-scale integration (Schemmel, Fieres, and Meier, 2008). In order to achieve higher bandwidths and use less energy in signal transmission compared to single chips being connected externally via a printed circuit board (PCB), the silicon wafer used to manufacture HICANN chips side-byside is not cut into separate chips. 384 chips on the wafer are instead interconnected by additional metal layers in a post-processing step and directly connected to a main PCB using elastomeric connectors. The next concept is physical emulation: a set of differential equations (section 2.5) is not solved numerically, but emulated by a physical model implementation of the differential equations. This limits the system to the physically implemented model equations, but allows for a very fast and energy efficient time evolution (Schemmel, Fieres, and Meier, 2008). The choice of conductances and capacitances allows the system to emulate the model 10<sup>4</sup> times faster than real time, whereas computer simulations usually are slower than real time. This acceleration allows to evolve network dynamics in experiments faster than real-time and thus gain insights into processes that would take too much time to simulate them numerically. The third key concept is learning being integrated into the system, which also benefits from the accelerated time evolution. There is already support for Short Term Plasticity (STP) (Schemmel, Grübl, et al., 2006; Billaudelle, 2014) and Spike-Timing Dependent Plasticity (STDP) (Schemmel, Grübl, et al., 2006; Nonnenmacher, 2015). The next generation of the system will contain a plasticity processor to facilitate learning (Friedmann, Frémaux, et al., 2013; Friedmann, Schemmel, et al., 2016; Friedmann, 2013).

Apart from researching and designing circuits for energy-efficient realization of new computing paradigms, the BrainScaleS system is intended as a tool for theretical neuroscientists. Access for early adopters is already available via the neuromorphic computing platform of the Human Brain Project (HBP). First proof of concept networks have already been published (Schmitt et al., 2016). As simulation of a day is compressed to seconds, the next generation of the BrainScaleS system will also allow to observe learning over a larger time scale.

The physical emulation of the neuron dynamics is implemented by analog electronic circuits, detailed in the following chapters. Spike communication is realized by transmitting binary information via digital circuits, and received by 4 bit synapses (Millner, 2012; HBP SP9 partners, 2014). The system is highly configurable: each neuron has individual neuron parameters to control its behavior, the synaptic connectivity can be reconfigured to implement arbitrary neural networks. The synaptic connectivity is designed to be scalable, such that a single model neuron can receive input from up to 10<sup>4</sup> sources.

The HICANN mixed-signal Application Specific Integrated Circuit (ASIC) is the central component of the BrainScaleS system. It implements the AdEx model in full-custom analog circuits (Millner, 2012), which is discussed in section 4.1.

In addition, HICANN contains a digital part to configure and connect these analog circuits. Communication with HICANN takes place via the Automated Repeat reQuest (ARQ) protocol (Philipp, 2008; Karasenko, 2014). On chip the neural network activity is transmitted digitally (Hartel, 2016; Jeltsch, 2014). The digital spikes are then processed by the synaptic input circuits and converted to a current (section 4.1.6).

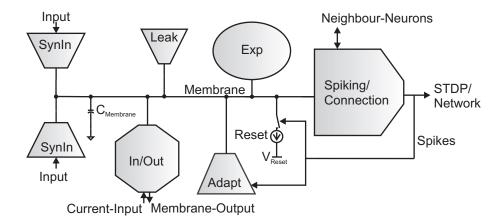

#### 4.1 NEURON CIRCUIT

The analog Dendritic Membrane Circuit (denmem) is the central subject of investigation in this work. In the following, we give an overview over the circuits relevant for this thesis and explore in detail how to control their behavior. Figure 4.1 shows a simplified schematic. We are using the term *denmem* as established in Millner (2012) instead of neuron, because a model neuron can consist of several denmems. This circuit realizes the physical AdEx model implementation (equations (2.3) and (2.9) to (2.11)) with an electronic capacitor  $C_m$  for the membrane capacitance, which can be digitally configured to two values (section 4.2.1): a smaller capacitance  $C_{\text{smallcap}} = 0.16\,\text{pF}$  and a bigger capacitance  $C_{\text{bigcap}} = 2.16\,\text{pF}$ . There are individual circuits to implement the currents from each term in equation (2.10) on the membrane capacitance: the leakage term (section 4.1.1), adaptation term (section 4.1.3) and exponential term (section 4.1.4), as well as the reset mechanism for equation (2.3) (section 4.1.2). This approach allows to observe the membrane potential as a time-continuous quantity, a physical voltage.

In total, there are 512 denmems on a single HICANN chip. The membrane capacitances of neighboring denmems can be interconnected up to a block of 64 denmems to act as a single model neuron (Jeltsch, 2014). This can be used to achive a higher number of available synaptic inputs (see section 4.1.7). The boundary of these blocks of 64 denmems can not be shifted, smaller block sizes are possible within these boundaries.

Further details on the design can be found in Millner (2012), where the full denmem circuit is discussed in detail. One exception is the revised synaptic input circuit, which has been discussed and characterized in Koke (2016).

There are two types of adjustable parameters in these circuits: 23 parameters are shared by 128 or 256 denmems. They are also known as global parameters, intro-

Figure 4.1: Simplified schematic of the AdEx physical model implementation in a denmem circuit (Millner, 2012). Most sub-circuits are introduced in this chapter. From left to right there is the excitatory and inhibitory synaptic input circuit, the membrane capacitance C<sub>m</sub>, external current stimulus and membrane voltage readout, leakage term, adaptation term, exponential term, reset mechanism and spiking mechanism. The denmem can be interconnected with neighboring denmems for higher synaptic connectivity. The spiking mechanism is also triggering the reset mechanism as well as Spike-Triggered Adaptation (STA). Schematic from Millner et al. (2010).

duced in section 4.2.4. Another 22 parameters can be adjusted for each denmem individually, known as neuron parameters (section 4.2.3).

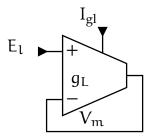

#### 4.1.1 Leakage Term

Several conductances in HICANN are implemented by an operational transconductance amplifier (OTA). This circuit has two voltage inputs and ideally outputs a current proportional to the product of a conductance, which is controlled by a biasing current, as well as the voltage difference at the inputs (Geiger and Sanchez-Sinencio, 1985):

$$I_{out} \propto \sqrt{I_{bias}} \cdot (V_+ - V_-) \,. \tag{4.1}$$

The leakage conductance  $g_L$  is implemented by a single OTA with bias current  $I_{gl}$  (figure 4.2). The resting potential  $E_l$  is connected to its positive input and its output is connected to the membrane capacitance as well as the negative input, resulting in a leakage current onto the membrane towards the equilibrium at  $E_l$ .

$$I_{leak} = -g_L (V_m - E_l) \propto \sqrt{I_{gl}} (E_l - V_m).$$

(4.2)

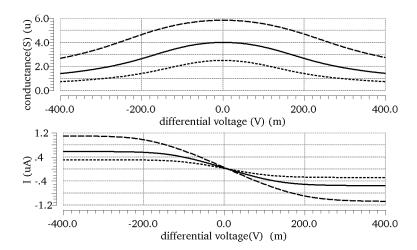

The real behavior of the OTA circuit implemented in HICANN has been simulated in detail in previous works (Millner, 2012; Koke, 2016; Kiene, 2014). Figure 4.3

Figure 4.2: The leakage conductance  $g_L$  is realized by an OTA with bias current  $I_{gl}$ . The positive input is connected to the resting potential  $E_l$ , the output is connected to the membrane capacitance with voltage  $V_m$  as well as the negative input, resulting in a leakage current onto the membrane towards the equilibrium at  $E_l$  (adapted from Millner (2012)).

shows its characteristic curves for the conductance and the resulting output current as a function of the differential voltage between its inputs. Due to saturation effects, the OTA's conductance depends on the voltage-difference at its inputs. Depending on the network model this effect may be negligible. We can operate at small voltage

Figure 4.3: Characteristic curves of the OTA used in several HICANN circuits, obtained from transistor level simulations. At the top, the conductance of the OTA is plotted depending on the differential voltage at its inputs. The three line styles depict three different bias current settings. At the bottom, the resulting current output of the OTA is shown. The ideal conductance would be constant, resulting in a linear current. The actual conductance shows a dependency on the voltage difference at the inputs with saturation at high differential voltage. In order to avoid deviations from the AdEx model with constant conductance, the parameter translation (section 4.2.5) and neuron configuration can be chosen to avoid large differential voltages. From (Millner, 2012).

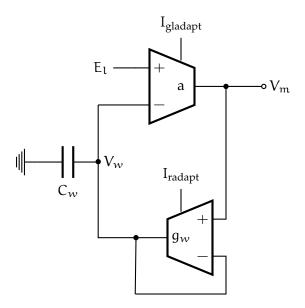

Figure 4.4: Simplified schematic of the adaptation circuit. Adaptation in form of equations (4.3) and (4.7) is realized using two OTAs and a capacitor  $C_w$ . The capacitor is storing the state w as voltage  $V_w$ . The output of the conductance a, with bias current  $I_{gladapt}$ , is the adaptation current w.  $V_w$  is coupled to  $V_m$  via the conductance  $g_w$  (equation (4.7)), with bias current  $I_{radapt}$ .

differences by choosing an appropriate parameter translation (section 4.2.5) and corresponding neuron parameters in order to remain close to the theoretical model.

### 4.1.2 Reset Mechanism

The theoretical model defines that if the membrane voltage crosses the spike threshold,  $V_m$  is set to the reset potential  $V_{reset}$ . In physical emulation there is a current pulling the membrane voltage  $V_m$  to the reset potential  $V_{reset}$ . Its strength is adjustable via global parameter  $I_{reset}$ . It is designed to be strong enough to dominate in comparison to leakage and synaptic currents, resulting in an almost instantaneous reset. The duration during which the membrane is held at  $V_{reset}$  can be adjusted via parameter  $I_{pl}$ , resulting in a refractory period  $\tau_{ref}$ . The reset is triggered by a comparator with inputs  $V_m$  and  $V_t$ , which also triggers the emission of a digital spike signal (see section 4.1.7).

## 4.1.3 Adaptation Term

On HICANN, the present value of the adaptation variable w is stored as voltage  $V_w$  on a capacitor  $C_w = 2 \, pF$  (figure 4.4). The capacitances  $C_w$  of interconnected denmems are not connected to each other. The adaptation current w onto the mem-

brane in equation (2.10) is the output of an OTA, the conductance  $\alpha$ , with  $E_1$  and  $V_w$  at its input terminals. This gives the following relation:

$$w = a \left( V_w - E_l \right), \tag{4.3}$$

and its time-derivative

$$\frac{\mathrm{d}w}{\mathrm{d}t} = \mathbf{a} \cdot \frac{\mathrm{d}V_w}{\mathrm{d}t}.\tag{4.4}$$

Putting equations (4.3) and (4.4) into equation (2.11) gives

$$-\alpha \tau_{w} \frac{dV_{w}}{dt} = \alpha (V_{w} - E_{l}) - \alpha (V_{m} - E_{l})$$

(4.5)

$$\Leftrightarrow -\tau_w \frac{dV_w}{dt} = (V_w - V_m) \tag{4.6}$$

$$\Leftrightarrow -C_w \frac{dV_w}{dt} = g_w (V_w - V_m). \tag{4.7}$$

In the last step, we have introduced another conductance  $g_w$  to realize the time constant  $\tau_w = \frac{C_w}{g_w}$ . Equation (4.7) is also implemented by an OTA, very similar to the leakage circuit.

Spike-Triggered Adaptation (STA) as defined in equation (2.9) is triggered by the digital spike signal. The increase of current w by b can be expressed as a voltage increase by  $V_b$  on  $C_w$ :

$$b = a \cdot V_b = a \cdot \frac{q_b}{C_w},\tag{4.8}$$

equation (2.9) becomes

$$V_w \to V_w + V_b. \tag{4.9}$$

The required charge  $q_b$  flowing on the capacitor is added by enabling an adjustable current  $I_{fire}$  during the digital firing pulse with pulse length  $t_{fire} \ll \tau_w$  and  $\tau_m$ :

$$q_b = t_{fire} \cdot I_{fire}. \tag{4.10}$$

The bias current  $I_{\rm fire}$  can be used to set the desired value for b. When the adaptation term is reset,  $V_w$  is connected to  $V_{\rm m}$  by a transistor not shown in figure 4.4. The reset signal opens the transistor, circumventing  $g_w$  and resulting in  $V_w = V_{\rm m}$ . If  $V_w$  is at the resting potential, equation (4.3) becomes w = 0. This concludes the required level of detail to control the adaptation term. Additional details on this realization and its limitations can be found in Millner (2012).

#### 4.1.4 Exponential Term

The exponential term in equation (2.10) is an exponential current

$$I_{exp} = g_{L} \cdot \Delta_{T} \exp\left(\frac{V_{m} - V_{T}}{\Delta_{T}}\right) \tag{4.11}$$

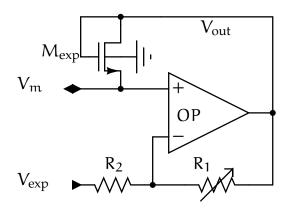

Figure 4.5: Simplified schematic of the exponential term. The transistor  $M_{exp}$  is operated in its subthreshold regime to provide a current depending exponentially on  $V_{out} - V_m$ . The threshold at which the OpAmp becomes active is determined by its negative input  $V_-$  and can be controlled by  $V_{exp}$ . The slope of the exponent is controlled by the voltage divider consisting of an adjustable resistance  $R_1$  and constant resistance  $R_2$ . Adapted from (Millner, 2012).

with a threshold voltage  $V_T$  and slope factor  $\Delta_T$ .

The exponential feedback was implemented by connecting the output of an operational amplifier (OpAmp) to a transistor  $M_{exp}$  (figure 4.5) operated in its subthreshold regime: its gate-to-source voltage is below the conducting threshold voltage,  $V_{GS} \leq V_{th}$ . This configuration results in a subthreshold leakage current

$$I_{DS} = I_{Do} \exp\left(\frac{V_{GS} - V_{th}}{n \cdot u_t}\right) \tag{4.12}$$

from drain to source which depends exponentially  $V_{GS}$  (Allen and Holberg, 2002).  $I_{Do}$  is a constant with a temperature dependency. The temperature is assumed to be constant over time in local areas of the system. The constant n is called subthreshold swing parameter and characterizes the subthreshold slope of the transistor (Millner, 2012; Hu, Liu, and Jin, 1998).  $u_t = \frac{k_B \cdot T}{q}$  is the thermal voltage, with Boltzmann constant  $k_B$ , elementary charge q and temperature T.

In order to calculate  $V_{GS}$ , we need to know the voltage  $V_{out}$  at the output of the OpAmp. Assuming an ideal OpAmp, there is no current flowing through its input terminals. Let us consider the current flowing from the OpAmp's output to  $V_{exp}$ :

$$I_1 = \frac{V_{\text{out}} - V_{\text{exp}}}{R_1 + R_2}. (4.13)$$

The same current is flowing through  $R_2$ , giving us the voltage at its negative terminal  $V_-$ :

$$\begin{aligned} V_{-} &= V_{exp} + R_{2} \cdot I_{1} \\ &= V_{exp} + R_{2} \cdot \frac{V_{out} - V_{exp}}{R_{1} + R_{2}} \\ &= V_{exp} + (V_{out} - V_{exp}) \cdot \frac{R_{2}}{R_{1} + R_{2}}. \end{aligned}$$

$$(4.14)$$

The OpAmp regulates its output  $V_{out}$  to equalize the voltages present at its input terminals, such that  $V_+ \stackrel{!}{=} V_-$ . We can hence write

$$V_{m} = V_{exp} + (V_{out} - V_{exp}) \cdot \frac{R_{2}}{R_{1} + R_{2}}$$

(4.15)

$$\Leftrightarrow V_{\text{out}} = \left(V_{\text{m}} - V_{\text{exp}}\right) \frac{R_1 + R_2}{R_2} + V_{\text{exp}}. \tag{4.16}$$

Now we can calculate  $V_{GS}$  of  $M_{exp}$ :

$$V_{GS} = V_{out} - V_{m} \tag{4.17}$$

$$= (V_{m} - V_{exp}) \frac{R_{1} + R_{2}}{R_{2}} - (V_{m} - V_{exp}) \frac{R_{2}}{R_{2}}$$

(4.18)

$$= (V_{m} - V_{exp}) \frac{R_{1}}{R_{2}}. \tag{4.19}$$

By inserting equation (4.19) into equation (4.12), we obtain

$$I_{Mexp} \equiv I_{DS} \approx I_{Do} \exp\left(\frac{\left(V_{m} - V_{exp}\right) \frac{R_{1}}{R_{2}} - V_{th}}{n \cdot u_{t}}\right) \tag{4.20}$$

$$= \alpha \exp\left(\frac{V_{\rm m} - V_{\rm exp}}{\frac{\beta}{R_1}}\right) \tag{4.21}$$

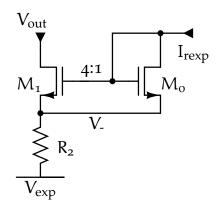

for the current through  $M_{exp}$ , with two constants  $\alpha = I_{Do} \exp\left(\frac{-V_{th}}{n \cdot u_t}\right)$  and  $\beta = R_2 \cdot n \cdot u_t$ . The adjustable resistance  $R_1$  in the voltage divider is realized with a current mirror (figure 4.6). If  $M_1$  is in saturation, the total current through  $R_1$  is adjustable as scaled mirror of the bias  $I_{rexp}$ :

$$I_1 \approx (4+1) \cdot I_{\text{rexp}} = 5 \cdot I_{\text{rexp}}. \tag{4.22}$$

Therefore  $R_1$  in the voltage divider is inversely proportional to  $I_{rexp}$ , assuming ohmic behavior. Due to its design,  $R_1$  does not behave like an ideal resistor, but also has a dependency on the voltage difference. Correct behavior of the exponential term is most relevant at  $V_m$  close to  $V_T$ , where  $R_1$  behaves as intended. Combined with saturation of the OpAmp,  $I_{Mexp}$  will decrease if  $V_m \gg V_T$  (Millner, 2012). If this saturation is occurring just before reaching the spiking threshold  $V_t$ , the effect

Figure 4.6: Schematic of the voltage divider as part of the exponential circuit (figure 4.5). The current through  $M_1$  is controlled via  $I_{rexp}$ . Adapted from (Millner, 2012).

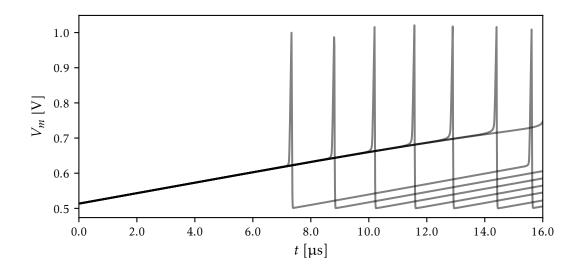

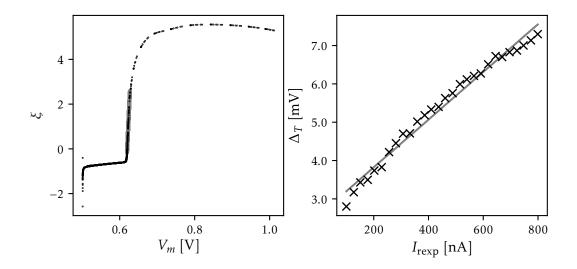

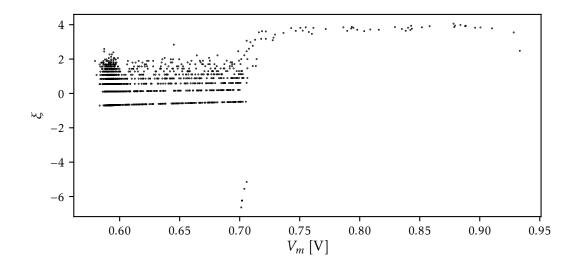

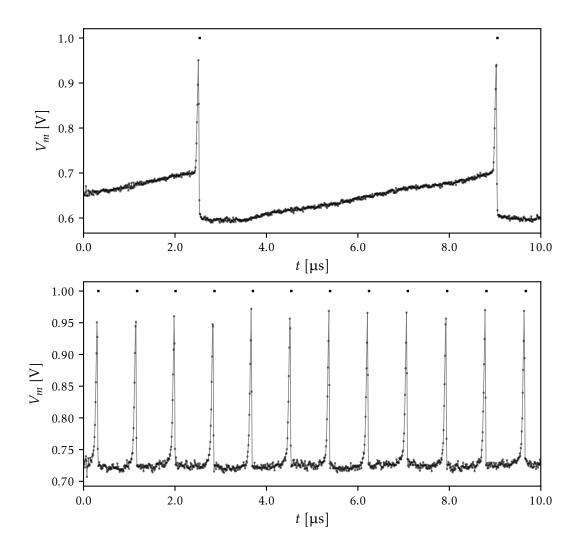

is negligible. In transistor level simulations at  $I_{Mexp}=100\,\text{nA}$  the relation between  $I_{rexp}$  and  $\Delta_T$  is almost linear in the range of  $I_{rexp}\approx 100\,\text{nA}$  to  $800\,\text{nA}$ , resulting in  $\Delta_T\approx 3\,\text{mV}$  to  $14\,\text{mV}$  (Millner, 2012). Larger values for  $I_{rexp}$  in this configuration lead to saturation of the OpAmp.

Comparing equation (4.21) to equation (4.11), we see that

$$\Delta_{\mathsf{T}} = \frac{\beta}{\mathsf{R}_1}.\tag{4.23}$$

The factor  $g_L \Delta_T$  is determined by  $V_{exp}$ :

$$g_{L}\Delta_{T} \exp\left(\frac{V_{m} - V_{T}}{\Delta_{T}}\right) \stackrel{!}{=} \alpha \exp\left(\frac{V_{m} - V_{exp}}{\frac{\beta}{R_{1}}}\right)$$

(4.24)

$$\Rightarrow \exp\left(\frac{V_{\rm m} - V_{\rm T} - (V_{\rm m} - V_{\rm exp})}{\Delta_{\rm T}}\right) = \frac{\alpha}{g_{\rm L} \Delta_{\rm T}} \tag{4.25}$$

$$\frac{V_{\exp} - V_{T}}{\Delta_{T}} = \ln\left(\frac{\alpha}{q_{T} \Delta_{T}}\right) \tag{4.26}$$

$$V_{\text{exp}} = V_{\text{T}} - \Delta_{\text{T}} \ln \left( \frac{g_{\text{L}} \Delta_{\text{T}}}{\alpha} \right). \tag{4.27}$$

Note that  $g_L$  represents the model's leak conductance and is otherwise unrelated to the OTA bias of the leakage term. From equation (4.27) we can see that the value of  $V_{\text{exp}}$  required to achieve a fixed  $V_T$  will decrease when  $\Delta_T$  is increased.

In summary, the exponential slope  $\Delta_T$  is proportional to  $I_{rexp}$ . The exponential threshold voltage  $V_T$  depends on both  $I_{rexp}$  and  $V_{exp}$  and is linear with  $V_{exp}$  at a fixed  $I_{rexp}$ .

### 4.1.5 Current Input and Membrane Output

The denmem can be stimulated by a programmable current source, intended for single neuron experiments. Amplitude configuration is stored in the floating gate (FG) cell memory, allowing 129 discrete steps which can optionally be repeated periodically. When connected to the membrane capacitor, the current stimulus line introduces a non-negligible additional parasitic capacitance (Schmidt, 2014; Millner, 2012) which adds to  $C_m$ . It should only be connected to a single denmem at the same time to avoid low impedance effects (Hartel, 2016).

This sub-circuit, denoted as In/Out in figure 4.1, also contains the circuitry to read out the membrane voltage  $V_m$ . This feature is used to deduce circuit behavior from voltage traces (chapter 7). A HICANN chip has two output amplifiers for simultaneous membrane voltage readout of two neurons, i. e. interconnected or single denmems. Additionally, the two analog readout lines are shared by all HICANNs on a reticle, limiting the simultaneous membrane voltage readout to two neurons per reticle in multi-HICANN experiments or parallel calibration runs. The output amplifier causes a systematic error by shifting the voltage by  $(4.5 \pm 0.8) \, \text{mV}$  (Millner, 2012), which can be equalized by our software (section 7.4).

# 4.1.6 Synaptic Input and Layer 1 Routing

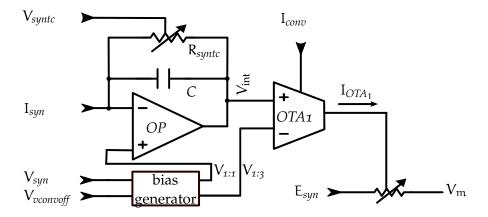

The synaptic inputs generate an exponentially shaped conductance trace between a synaptic reversal potential  $E_{\rm syn}$  and the membrane  $V_{\rm m}$ . Digital spike signals are routed over a continuous-time serial bus system, called Layer 1 (L1), using both onchip and post-processing lines for intra-wafer communication (Fieres, Schemmel, and Meier, 2008). Both inputs, inhibitory and excitatory, can be activated by incoming signals, generating current pulses  $I_{\rm syn}$  arriving at the circuit in figure 4.7. The neuron implementation in HICANN revision 4 has two different synaptic input circuits, one for excitatory and one for inhibitory input. Their circuit parameters are suffixed by "x" or "i", respectively.

The two synaptic input circuits per denmem in the previous revision were idential. We have analyzed the previous implementation and provided possible workarounds for the raised issues in Schmidt (2014). These have been fixed in the new synaptic input implementation of HICANN revision 4, which has been characterized in Koke (2016) and is not analyzed in this thesis.

The L1 network is not part of the denmem, but provides input to the synapse circuit. Spike events are transmitted as digital signals on the L1 network, with a 6 bit event address (EA). Two of these bits are used to select a synapse driver. The other four bits are matched by the individual synapses. For digital spike communication between one or several HICANNs there are 256 vertical and 64 horizontal L1 buses, which can be connected to each other via crossbar switches: a horizontal line can be connected by crossbar switches to four vertical lines on the left and right side of the chip each (Fieres, Schemmel, and Meier, 2008; HBP SP9 partners, 2014). Vertical

Figure 4.7: Schematic of the synaptic input circuit. Current pulses  $I_{syn}$  are integrated by the OpAmp and decay exponentially in the RC circuit with time constant  $\tau_{syn}$ , controlled by  $V_{syntc}$ , towards  $V_{syn}$ . The integrated voltage  $V_{int}$  generates a current from the OTA, which controls the resistive element connecting  $E_{syn}$  to  $V_{m}$ . In order to compensate an offset of  $V_{int}$  to  $V_{syn}$  in the absence of input, an offset to  $V_{syn}$  can be added at the negative input of the OTA via  $V_{convoff}$ . Schematic adapted from Koke (2016).

L1 lines can be connected to synapse drivers, where one synapse driver can be fed from 16 different vertical lines. Synapse drivers with configurable L1 address decoder can be connected to a vertical bus lane via a switch matrix. The signal from the synapse driver is then scaled by  $V_{\rm gmax}$  and the synaptic weight, resulting in a current pulse  $I_{\rm syn}$  to the connected synaptic input if the address is matching (Koke, 2016):

$$I_{\text{syn}} = V_{\text{gmax}} \cdot g_{\text{scale}} \cdot \frac{w}{g_{\text{div}}}. \tag{4.28}$$

One HICANN has a synapse array of  $512 \times 220$  horizontal and vertical synapses. Compared to HICANN revision 2, four vertical synapse lines were removed, because the new synapse circuit in HICANN revision 4 required additional space. The L1 network allows to reconfigure connectivity for each target experiment (section 6.1).

At the chip boundaries, repeaters help to propagate the differential spike signal to the neighbouring chip. L1 repeaters use delay-locked loops (DLLs) to align their timing. These circuits need to be *locked* before an experiment and will stabilize themselves by spike activity present during an experiment.

There are two mechanisms to inject additional spikes into the L<sub>1</sub> bus during experiments: spike events can be either sent from the FPGA Communication PCB (FCP) (introduced in section 5.2.1) at user-defined times or generated by background generators inside HICANN. The eight background generators on a chip

can be configured to emit periodic spike events or Poisson-distributed events. As the pseudo-random number generator is periodic, the random events are not perfectly Poisson-distributed (Petrovici, 2015). In random mode, the target address is restricted to 0 in HICANN revision 4. Because the repeaters require spike events during an experiment to maintain their DLL lock (Ziegler, 2013), background generators are usually configured for periodic events on address 0.

## 4.1.7 Spiking Mechanism and Interconnection

In the chip's layout, two neighboring neurons are combined in a pair and share their spiking and connection circuit (Millner, 2012).

The connection circuit allows to connect the membrane capacitor to neighboring denmems, forming a multi-denmem neuron with more synaptic inputs than a single one. As the sum of currents increases linearly with the membrane capacitance, the behavior remains identical to a single denmem as long as all denmems are configured for identical behavior (Schmidt, 2014).

If the membrane potential of a denmem is higher than its firing threshold potential, a digital firing signal can be emitted with the denmem's configured address on the L<sub>1</sub> bus. In case of interconnected denmems, only one denmem of the group is configured to emit a spike signal (Jeltsch, 2014).

Addresses that are not associated with a background generator can be used to identify spike times from up to 63 distinguishable denmems simultaneously in calibration experiments. As long as the experiment does not require any synaptic connectivity and DLL locking, address o could be used for this purpose as well.

#### 4.2 NEURON PARAMETERS

The denmem circuits feature many adjustable parameters, some of which have been mentioned in the previous section. Here we will give an overview how they are stored and which parameters can be configured to influence the individual analog circuits.

# 4.2.1 Time Constant Scaling and Digital Configuration

The membrane time constant  $\tau_m$  and adaptation time constant  $\tau_w$  depend on the conductances  $g_1$ , a and  $g_w$ . These are controlled by analog bias currents (compare section 4.1). Analog parameters are stored in floating gate (FG) cells, which are introduced in the next section.

On HICANN there are digital switches that rescale time constants by amplifying the bias currents to cover a larger range of values for the time constants. Two bits each for the bias currents  $I_{\rm gl}$ ,  $I_{\rm gladapt}$  and  $I_{\rm radapt}$  allow three different current mirror scaling selections: slow, normal and fast. They can be set individually for each bias

current, resulting in current scaling of 1:1, 1:3 or 1:27. Each scaling is available once for the upper and once for the lower two FG blocks, i. e. the first or second group of 256 denmems each.

Additionally the membrane capacitance can be configured. The switch *bigcap* enables or disables the connection of several capacitors to a larger membrane capacitance. The small capacitance is 0.16 pF, enabling *bigcap* results in a sum of  $C_{\rm m}=2.16$  pF. The acceleration factor  $\alpha_{\rm acc}$  of the physical emulation on hardware compared to the model results from the relation between capacitances and conductances:

$$\alpha_{\rm acc} = \frac{C_{\rm Model}}{g_{\rm Model}} \cdot \frac{g_{\rm Hardware}}{C_{\rm Hardware}}.$$

(4.29)

The achievable conductance value ranges were chosen such that typical model ranges can be reached at  $\alpha_{acc} = 10^4$ . This factor is used for parameter translation in section 4.2.5.

Taking the conductances measured for the default capacitance ( $C_{bigcap}$ ) as a reference, all conductances are scaled by  $g_{smallcap} = g_{bigcap} \cdot \frac{C_{smallcap}}{C_{bigcap}}$  if the small capacitance is chosen. For higher accuracy, the actual conductances can be measured again in separate experiments with  $C_{smallcap}$ .

The digital denmem configuration also allows to set the switches for membrane voltage readout and current input (section 4.1.5).

# 4.2.2 Floating Gate Memory

The analog parameters are stored in floating gate (FG) cells (Millner, 2012; Hock, 2009; Srowig et al., 2007; Loock, 2006).

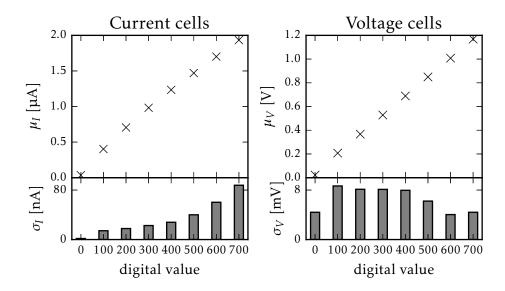

There are two types of FG cells in HICANN: voltage cells and current cells, with a programmable voltage range from 0 V to 1.8 V and a current range of 0  $\mu$ A to 2.5  $\mu$ A. The resulting value is programmed from a 10 bit Digital-to-Analog Converter (DAC) reference output before an experiment run. A fully isolated Positive Metal–Oxide–Semiconductor (PMOS) transistor gate is charged and discharged using Fowler-Nordheim-Tunneling (Lande et al., 1996). This requires a large programming voltage of at least 10 V. A more detailed description of this process is given in Koke (2016), Hartel (2016), and Millner (2012). Additional parameters allow adjusting the FG controller's behavior during programming.

The charge on the FG determines the cell's output: in a voltage cell the FG transistor together with a biasing transistor forms a source follower, buffering the gate voltage as the cell's output. The output current of current cells is provided by a current mirror. Several current parameters can be scaled by additional current mirrors (section 4.2.1). A current cell which is configured to 0 DAC will still output a small current, which is estimated to range between 20 nA and 50 nA. By repeatedly changing the charge stored in the FG from zero to a desired value, a trial-to-trial

Figure 4.8: Floating gate cell trial-to-trial variation. The top part shows the mean, the bottom part shows the standard deviation of the current or voltage resulting from repeatedly configuring identical digital settings of FG current and voltage cells over 100 repetitions. Current cell precision decreases for higher currents, voltage cell precision shows a standard deviation between 5 mV to 9 mV over the measurable range. Figure from (Koke, 2016).

variation in the order of several millivolts is observed for voltage cells (figure 4.8). Current cells show a variation that is growing with the desired output current.

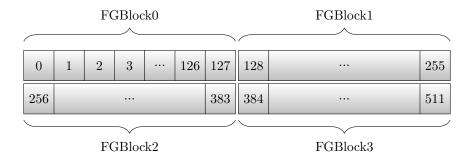

Physically, HICANN's analog parameter storage is divided into four blocks of 129 · 24 FG cells. The first column of 24 parameters stores the shared parameters (table 4.3). The other 128 columns store neuron parameters (table 4.2) for 128 denmems. Note that not all cells are used (compare table 4.1), leaving room for future circuit improvements.

Table 4.1 provides an overview how analog parameters have been layouted to connect to FG cells. The functionality of the parameters is described in sections 4.2.3 and 4.2.4.

## 4.2.3 Neuron Parameters

Neuron parameters, potentials and bias currents, can be configured for an individual denmem. This enables us to fine-tune each circuit to get as close to the desired behavior as possible. The resulting precision is limited by the ability to deduce the desired behavior from the accessible data (see section 4.1.5), as well as the precision of setting a value (see section 4.2.2). Table 4.2 shows the available parameters and their function. The parameters for 512 denmems are supplied by four different FG blocks. The connection scheme is depicted in figure 4.9.

| row | type    | global parameter                                    | left denmem         | right denmem        |

|-----|---------|-----------------------------------------------------|---------------------|---------------------|

| О   | voltage | V <sub>reset</sub> (left: even,                     | -                   | E <sub>synx</sub>   |

|     |         | right: odd blocks)                                  |                     | ,                   |

| 1   | current | I <sub>OPbias</sub> (intern. OP bias)               | I <sub>bexp</sub>   | $I_{convi}$         |

| 2   | voltage | $V_{\rm dllres}$                                    | $V_{convoffx}$      | $E_{\mathrm{syni}}$ |

| 3   | current | V <sub>bout</sub> (left), V <sub>bexp</sub> (right) | $I_{convi}$         | I <sub>convx</sub>  |

| 4   | voltage | $V_{fac}$                                           | $V_{convoffi}$      | $V_{exp}$           |

| 5   | current | I <sub>breset</sub>                                 | $I_{spikeamp}$      | I <sub>intbbx</sub> |

| 6   | voltage | $V_{dep}$                                           | $E_1$               | $V_{synx}$          |

| 7   | current | I <sub>bstim</sub>                                  | $I_{\mathrm{fire}}$ | I <sub>intbbi</sub> |

| 8   | voltage | $V_{thigh}$                                         | $V_{ m syni}$       | $V_{ m syntci}$     |

| 9   | current | $V_{gmax < 3}$                                      | $I_{gladapt}$       | $I_{pl}$            |

| 10  | voltage | $V_{tlow}$                                          | $V_{syntci}$        | $V_{ m syni}$       |

| 11  | current | $V_{gmax<0>}$                                       | $I_{gl}$            | $I_{gladapt}$       |

| 12  | voltage | V <sub>clra</sub> (left), V <sub>crlc</sub> (right) | $V_t$               | $V_{syntcx}$        |

| 13  | current | $V_{gmax<1>}$                                       | $I_{pl}$            | $I_{rexp}$          |

| 14  | voltage | $V_{stdf}$                                          | $V_{syntcx}$        | $V_{t}$             |

| 15  | current | $V_{gmax<2>}$                                       | $I_{radapt}$        | $I_{bexp}$          |

| 16  | voltage | $V_{\rm m}$                                         | $E_{synx}$          | $E_{l}$             |

| 17  | current | $V_{bstdf}$                                         | $I_{convx}$         | $I_{spikeamp}$      |

| 18  | voltage | -                                                   | $E_{syni}$          | $V_{convoffi}$      |

| 19  | current | $V_{ m dtc}$                                        | $I_{intbbx}$        | $I_{fire}$          |

| 20  | voltage | -                                                   | $V_{exp}$           | $V_{convoffx}$      |

| 21  | current | $V_{br}$                                            | $I_{intbbi}$        | $I_{gl}$            |

| 22  | voltage | -                                                   | $V_{synx}$          | -                   |

| 23  | current | $V_{ccas}$ , $V_{cbias}$                            | $I_{rexp}$          | $I_{radapt}$        |

Table 4.1: Correspondence of row in the floating gate array with global parameter (first column) or neuron parameter (following 128 columns), adapted for HICANN revision 4 from HBP SP9 partners (2014). There are four FG blocks in total, storing parameters for 512 denmems. Even blocks are 0 and 2, odd blocks are 1 and 3. The type of FG cell is alternating between voltage and current cell. Global current parameters starting with the letter 'V' are part of distributed current mirrors and are usually matching the naming in the schematic.

| neuron parameter        | function                                               |

|-------------------------|--------------------------------------------------------|

| $E_{l}$                 | leakage potential, section 4.1.1                       |

| $I_{pl}$                | refractory time bias, section 4.1.2                    |

| $I_{gl}$                | leak conductance bias, section 4.1.1                   |

| $I_{\mathrm{fire}}$     | adaptation current increase (b) bias, section 4.1.3    |

| ${ m I}_{ m gladapt}$   | adaptation conductance, section 4.1.3                  |

| ${ m I}_{ m radapt}$    | adaptation time constant, section 4.1.3                |

| $V_{exp}$               | exponential threshold control, section 4.1.4           |

| $I_{bexp}$              | V <sub>exp</sub> buffer bias, section 4.1.4            |

| $I_{rexp}$              | exponential slope and threshold control, section 4.1.4 |

| $V_{t}$                 | spike threshold, section 4.1.7                         |

| $V_{ m synx}$           | excitatory synaptic input reference voltage            |

| $V_{ m syni}$           | inhibitory synaptic input reference voltage            |

| $I_{intbbx}$            | integrator bias in excitatory synaptic input           |

| $I_{intbbi}$            | integrator bias in inhibitory synaptic input           |

| $I_{convx}$             | OTA bias in excitatory synaptic input                  |

| $I_{convi}$             | OTA bias in inhibitory synaptic input                  |

| $V_{convoffx}$          | excitatory synapse integrator offset                   |

| $V_{convoffi}$          | inhibitory synapse integrator offset                   |

| $E_{synx}$              | excitatory synaptic reversal potential                 |

| $E_{syni}$              | inhibitory synaptic reversal potential                 |

| $V_{\text{syntcx}}$     | excitatory synaptic time constant                      |

| $V_{ m syntci}$         | inhibitory synaptic time constant                      |

| $I_{\mathrm{spikeamp}}$ | spike threshold comparator bias, section 4.1.7         |

Table 4.2: Parameters which can be set for each individual denmem and the summary of their function. Details on each parameter can be found in the corresponding section or reference therein. Synaptic input parameters are shortly introduced in section 4.1.6 and explained in detail in Koke (2016).

# 4.2.4 Shared Parameters

Global parameters of a FG block are shared between 128 denmems. The only shared parameter directly present in equation (2.10) is  $V_{reset}$ . The fact that this parameter is shared is utilized to determine a voltage readout offset in section 7.4. Other shared parameters are used for STP (Billaudelle, 2014), STDP (Nonnenmacher, 2015), energy saving functionality or other biases. With the exception of STP calibration

Figure 4.9: Denmem coordinates for a single HICANN and associated FG block that supplies neuron parameters to each denmem. Even blocks are left, odd blocks are right. Blocks o and 1 supply the top half of denmems, 2 and 3 supply the bottom half. These coordinates and terms are used in the software interface introduced in chapter 6.

these parameters are usually not changed during calibration. Table 4.3 lists the available shared parameters and their function.

The association between shared parameters and FG blocks is different from the connectivity for neuron parameters (figure 4.9). Even denmems are supplied by even FG blocks, and blocks 0 and 1 connect to the top half, blocks 1 and 2 connect to the bottom half. Figure 4.10 shows the connection scheme.

## 4.2.5 Parameter Translation

HICANN's implementation of the AdEx model operates in a different parameter range than found in biological neuron models. The model neuron parameters need to be rescaled to the range that is realized by the physical model. Analog voltages on HICANN range from 0 V to 1.8 V. The OTA and other circuits were designed for a common mode of 0.9 V. Therefore, the resting potential should be close to or a bit

Figure 4.10: Denmem coordinates for a single HICANN and associated FG block that supplies shared parameters to each denmem. Connectivity for shared parameters, including  $V_{\text{reset}}$ , is different than connectivity for neuron parameters (figure 4.9). Even denmems are supplied by even blocks, 0 and 1 connect to top, 2 and 3 connect to bottom denmems.

| shared parameter               | function                                                    |

|--------------------------------|-------------------------------------------------------------|

| $I_{breset}$                   | reset current bias, section 4.1.2                           |

| $I_{bstim}$                    | current stimulus bias, section 4.1.5                        |

| $V_{bexp}$ (right only)        | V <sub>exp</sub> buffer bias, section 4.1.4                 |

| V <sub>bout</sub> (left only)  | neuron readout bias, section 4.1.5                          |

| $V_{br}$                       | STDP readout bias                                           |

| $V_{bstdf}$                    | STP bias                                                    |

| $V_{ccas}$                     | L1 input amplifier bias                                     |

| V <sub>clra</sub> (left only)  | acausal STDP accumulation rate                              |

| V <sub>clrc</sub> (right only) | causal STDP accumulation rate                               |

| $V_{ m dep}$                   | STP depression mode offset                                  |

| $V_{\rm dllres}$               | L1 repeater DLL reset voltage                               |

| $V_{ m dtc}$                   | STP recovery current control                                |

| $V_{fac}$                      | STP facilitation mode offset                                |

| $V_{gmaxo}$                    | max. synaptic conductance reference current (!) o           |

| $V_{gmax1}$                    | max. synaptic conductance reference current (!) 1           |

| $V_{gmax2}$                    | max. synaptic conductance reference current (!) 2           |

| $V_{gmax3}$                    | max. synaptic conductance reference current (!) 3           |

| $V_{\rm m}$                    | causal STDP                                                 |

| $V_{reset}$                    | reset potential, section 4.1.2                              |

| $V_{stdf}$                     | Short Term Depression and Facilitation (STDF) reset voltage |

| $V_{ m thigh}$                 | STDP readout comparison voltage                             |

| $V_{\rm tlow}$                 | STDP readout comparison voltage                             |

| int op bias                    | FG cell internal amplifier bias                             |

Table 4.3: Parameters which are shared between all denmems connected to one of the four FG blocks. Two parameters appear on the left or right blocks only, they are connected to denmems belonging to the opposite block as well. STDP related parameters are explained in Nonnenmacher (2015), STP / STDF related parameters are explained in Billaudelle (2014).