## A Study of Time and Energy Efficient Algorithms for Parallel and Heterogeneous Computing

Thesis submitted in accordance with requirements of the University of Liverpool for the degree of Doctor in Philosophy

by

Jude-Thaddeus OJIAKU

September 2016

Degree of Doctor of Philosophy

### Abstract

This PhD project is motivated by the need to develop and achieve better and energy efficient computing through the use of parallelism and heterogeneous systems. Our contribution consists of both theoretical aspects, as well as in-depth and comprehensive empirical studies that aim to provide more insight into parallel and heterogeneous computing.

Our first problem is a theoretical problem that focuses on the scheduling of a special category of jobs known as deteriorating jobs. These kind of jobs will require more effort to complete them if postponed to a later time. They are intended to model several industrial processes including steel production, fire-fighting and financial management. We study the problem in the context of parallel machine scheduling in an online setting where jobs have arbitrary release times. Our main results show that List Scheduling is  $(1 + b_{max})$ -competitive and that no deterministic algorithm is better than  $(1 + b_{max})^{1-\frac{1}{m}}$ , where  $b_{max}$  is the largest deteriorating rate. We also extend our results to online deterministic algorithms and show that no deterministic online algorithm is better than  $(1 + b_{max})$ -competitive.

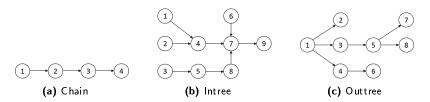

Our next study concerns the scheduling of n jobs with precedence constraints on m parallel machines. We are interested in the precedence constraint known as chain precedence constraint where each job can have at most one predecessor and at most one successor. The jobs are modelled as directed acyclic graphs where nodes represent the jobs and edges represent the precedence constraints between jobs. The jobs have a strict deadline that must be met. The parallel machines are considered to be unrelated and a communication network connects each pair of machines. Execution of the jobs on the machines as well as communication across the network incurs costs in the form of time and energy. These costs are given by cost matrices that covers processing and communication. The goal is to construct a feasible schedule that minimizes the total energy required to execute the chain of jobs on the machines, such that all deadlines are met. We present a dynamic programming solution to the problem that leads to a pseudo polynomial time

algorithm with running time  $O(nm^2d_{max})$ , where  $d_{max}$  is the largest deadline. We show that the algorithm computes an optimal schedule where one exists.

We then proceed to a similar problem that involves the scheduling of jobs to minimize flow time plus energy. This problem is based on a dynamic speed scaling heuristic in literature that is able to adjust the speed of a processor based on the number of active jobs, called AJC. We present a comprehensive empirical study that consists of several job selection, speed selection and processor allocation heuristics. We also consider both single processor and multi processor settings. Our main goal is to investigate the viability of designing a fixed-speed counterpart for AJC, that is not as computationally intensive as AJC, while being very simple. We also evaluate the performance of this fixed speed heuristic and compare it with that of AJC.

Our fourth and final study involves the use of graphics processing unit (GPU) as an accelerator for compute intensive tasks. The GPU has become a very popular multi processor for heterogeneous computing both from an economical point of view and performance standpoint. Firstly, we contribute to the development of a Bioinformatics tool, called GAPSMIS, by implementing a heterogeneous version that uses graphics processors for acceleration. GAPSMIS is a tool designed for the alignment of sequences, like protein and DNA sequences, and allows for the insertion of gaps in the alignment. Then we present a case study that aims to highlight the various aspects, including benefits and challenges, involved in developing heterogeneous applications that is vendor-agnostic. In order to do this we select four algorithms as case studies including GAPSMIS and the algorithm presented in our second problem. The other two algorithms are based on the Velocity-Verlet integration and the Fruchterman-Reingold force-based method for graph layout. We make use of the Open Computing Language (OpenCL) and C++ for implementation of the algorithms on a range of graphics processors from Advanced Micro Devices (AMD) and NVIDIA Corporation. We evaluate several factors that can affect performance of these applications on each hardware. We also compare the performance of our algorithms in a multi-GPU setting and against single and multi-core CPU implementations. Furthermore, several metrics are defined to capture several aspects of performance including execution time of application kernel(s), execution time of application including communication times, throughput, power and energy consumption.

## Acknowledgements

Firstly I would like to show my deepest gratitude to my supervisors Dr. Prudence Wong and Prof. Leszek Gąsieniec for their support and advice throughout the duration of my PhD studies. I have learned a lot during this period and they have always guided me in the right direction.

I am very grateful to my family for their unending love, encouragement and support, and for giving me the means to ensure that I complete my PhD studies.

I would also like to thank all my friends and colleagues for their help and support including Dr. O. Nwamadi, whose help, discussions and advice benefited me a great deal.

# Contents

| A            | bstra            | ct     |                                                                                                     |    |

|--------------|------------------|--------|-----------------------------------------------------------------------------------------------------|----|

| A            | cknov            | wledge | ements                                                                                              | ii |

| $\mathbf{C}$ | Contents         |        |                                                                                                     |    |

| Li           | List of Figures  |        |                                                                                                     | vi |

| Li           | List of Tables x |        | хv                                                                                                  |    |

| 1            | Intr             | oducti | ion                                                                                                 | 1  |

| •            | 1.1              | Overv  |                                                                                                     | 1  |

|              | 1.2              | Backg  | round on Scheduling                                                                                 | Ş  |

|              |                  | 1.2.1  | Inputs and outputs                                                                                  | 3  |

|              |                  | 1.2.2  | The $\alpha  \beta  \gamma$ scheduling notation                                                     | 4  |

|              |                  | 1.2.3  | Classes of scheduling problems                                                                      | 5  |

|              |                  | 1.2.4  | Input structure and constraints                                                                     | 6  |

|              | 1.3              |        | ems Studied and related work                                                                        |    |

|              |                  | 1.3.1  | Online scheduling of deteriorating jobs on parallel machines                                        | 6  |

|              |                  | 1.3.2  | Energy-efficient scheduling of precedence-constrained jobs on par-                                  |    |

|              |                  | 1.3.3  | allel machines                                                                                      | 10 |

|              |                  | 1.3.4  | Parallel and heterogeneous computing with graphics processors                                       |    |

|              | 1.4              |        | ibution of thesis                                                                                   |    |

| 2            | Onli             | ine Sc | heduling of Linear Deteriorating Jobs on Parallel Machines                                          | 17 |

|              | 2.1              | Introd | ${\it luction} \ \ldots \ $ | 17 |

|              | 2.2              | Prelin | ninaries                                                                                            | 18 |

|              |                  | 2.2.1  | Problem definition                                                                                  |    |

|              |                  | 2.2.2  | Property of simple linear deterioration                                                             |    |

|              | 2.3              |        | ower bounds in online-time model                                                                    |    |

|              |                  | 2.3.1  | List Scheduling on m parallel machines                                                              |    |

|              | 2.4              | 2.3.2  | Lower bounds for deterministic online scheduling                                                    |    |

|              | 2.4              | -Concl | $\operatorname{usion}$                                                                              | 28 |

<u>Contents</u> v

| 3 | Ene | ergy-Efficient Scheduling of Jobs with Precedence Constraints                                   | 29   |

|---|-----|-------------------------------------------------------------------------------------------------|------|

|   | 3.1 | Introduction                                                                                    | . 29 |

|   | 3.2 | Preliminaries                                                                                   | . 30 |

|   |     | 3.2.1 Problem definition                                                                        | . 30 |

|   | 3.3 | Discussion                                                                                      | . 31 |

|   |     | 3.3.1 A dynamic programming solution                                                            | . 31 |

|   |     | 3.3.2 Algorithm DPS                                                                             | . 33 |

|   | 3.4 | Conclusion and future work                                                                      | . 36 |

| 4 | Ene | ergy-Efficient Flow Time Scheduling                                                             | 38   |

|   | 4.1 | Introduction                                                                                    | . 38 |

|   | 4.2 | Problem Definition                                                                              | . 40 |

|   | 4.3 | Heuristics                                                                                      | . 41 |

|   |     | 4.3.1 Job selection strategies                                                                  | . 41 |

|   |     | 4.3.2 Speed functions                                                                           | . 41 |

|   |     | 4.3.3 Processor allocation strategies                                                           | . 42 |

|   | 4.4 | Simulations Conducted and Results                                                               | . 43 |

|   |     | 4.4.1 Preliminaries                                                                             | . 43 |

|   |     | 4.4.2 Results on job selection strategies                                                       | . 45 |

|   |     | 4.4.3 Results on speed functions                                                                | . 49 |

|   |     | 4.4.4 Results on processor allocation strategies                                                | . 55 |

|   |     | 4.4.5 Conclusion                                                                                | . 57 |

| 5 | Bac | ekground on Parallel Computing with General Purpose GPUs                                        | 71   |

|   | 5.1 | Introduction                                                                                    | . 71 |

|   | 5.2 | Comparison of CPU and GPU Hardware Architecture                                                 | . 71 |

|   |     | 5.2.1 Memory management in a computer system                                                    | . 72 |

|   |     | 5.2.2 Stream processing hardware implementation                                                 | . 73 |

|   |     | 5.2.3 Scheduling - threads, warps and wavefronts                                                | . 74 |

|   | 5.3 | Vendor-specific SIMD implementations                                                            |      |

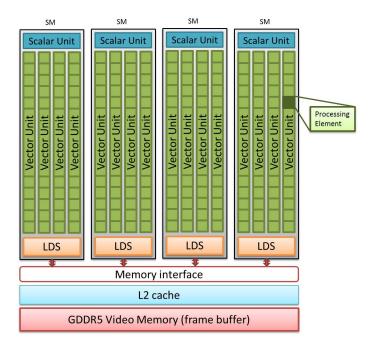

|   |     | 5.3.1 The Graphics Core Next architecture (AMD)                                                 |      |

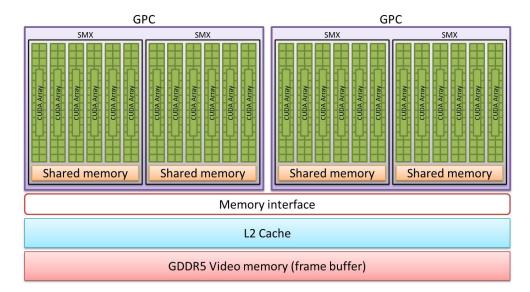

|   |     | 5.3.2 The Kepler architecture (NVIDIA)                                                          |      |

|   | 5.4 | GPU Computing Framework                                                                         |      |

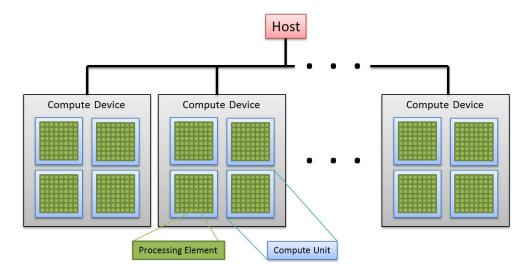

|   |     | 5.4.1 The Open Computing Language                                                               |      |

| 6 | Par | allel Algorithms for Heterogeneous Systems with GPGPUs                                          | 87   |

|   | 6.1 | Introduction                                                                                    | . 87 |

|   | 6.2 | Theoretical analysis of parallel algorithms                                                     | . 89 |

|   | 6.3 | Naming convention and notations                                                                 | . 90 |

|   | 6.4 | DPS: energy-aware scheduler for precedence-constrained jobs on parallel                         | 0.0  |

|   |     | machines                                                                                        |      |

|   |     | 6.4.1 Sequential approach                                                                       |      |

|   |     | 6.4.2 Task-parallel approach                                                                    |      |

|   |     | 6.4.3 Data-parallel approach                                                                    |      |

|   | 6.5 | ${\tt GapsMis}: a \ tool \ for \ sequence \ alignment \ with \ bounded \ number \ of \ gaps  .$ |      |

|   |     | 6.5.1 Introduction                                                                              |      |

|   |     | 6.5.2 Problem definition                                                                        | . 96 |

Contentsvi

97

228

|            |      | 6.5.3  | Sequential GapsMis Algorithm                                  |

|------------|------|--------|---------------------------------------------------------------|

|            |      | 6.5.4  | Task-parallel approach                                        |

|            |      | 6.5.5  | Data-parallel approach                                        |

|            | 6.6  | Velve  | t: Velocity-Verlet integrator                                 |

|            |      | 6.6.1  | Sequential approach                                           |

|            |      | 6.6.2  | Task-parallel approach                                        |

|            |      | 6.6.3  | Data-parallel approach                                        |

|            | 6.7  | FDGV:  | Force-directed graph visualizer                               |

|            |      | 6.7.1  | Sequential approach                                           |

|            |      | 6.7.2  | Task-parallel approach                                        |

|            |      | 6.7.3  | Data-parallel approach                                        |

|            | 6.8  | Prelim | inary discussion                                              |

|            |      | 6.8.1  | Evaluation model and performance metrics                      |

|            |      | 6.8.2  | Hardware and software specifications                          |

|            |      | 6.8.3  | Input data for experiments                                    |

|            |      | 6.8.4  | Aims of experiments conducted                                 |

|            | 6.9  | Discus | sion of experiment results                                    |

|            |      | 6.9.1  | Results on device-host communication overheads                |

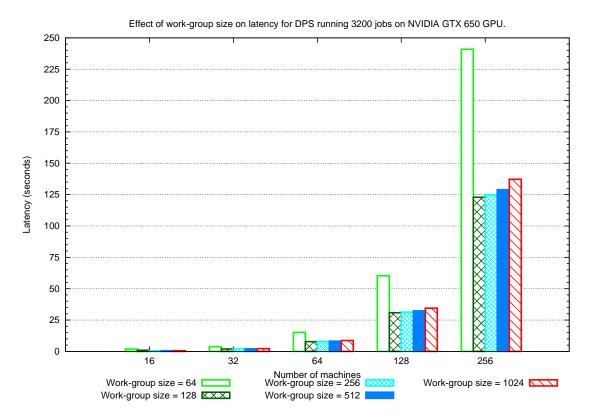

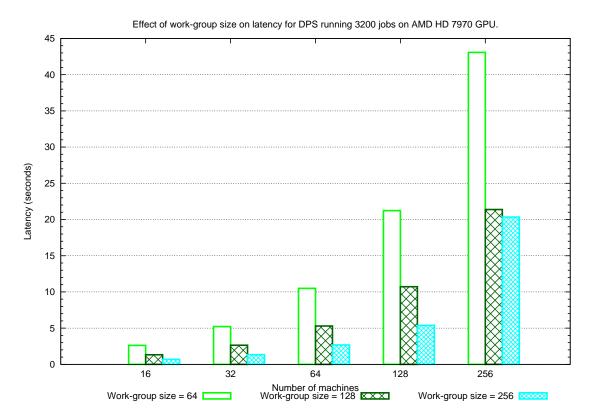

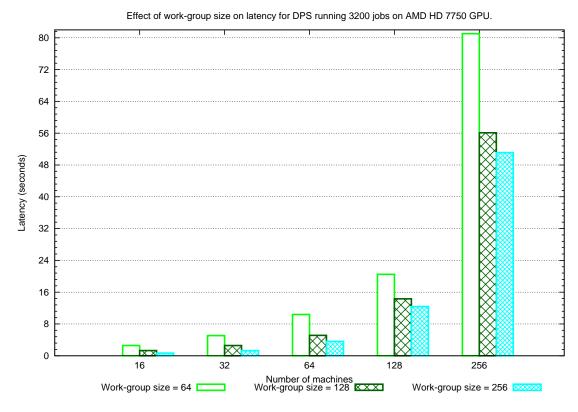

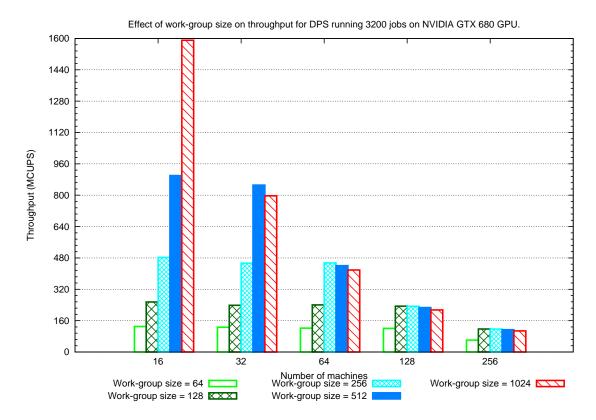

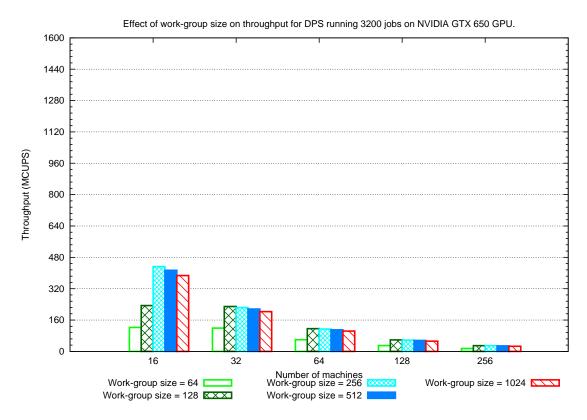

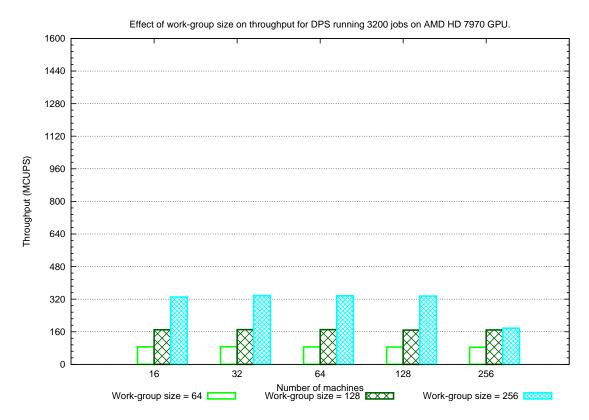

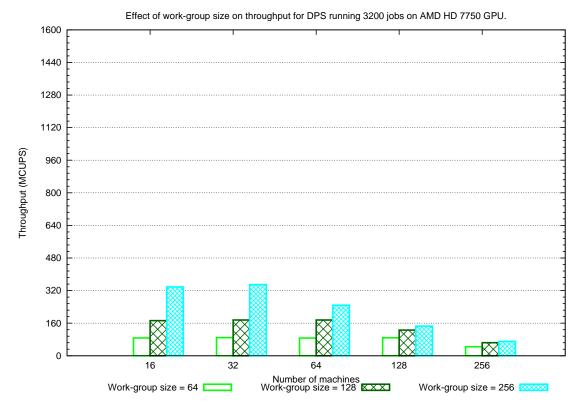

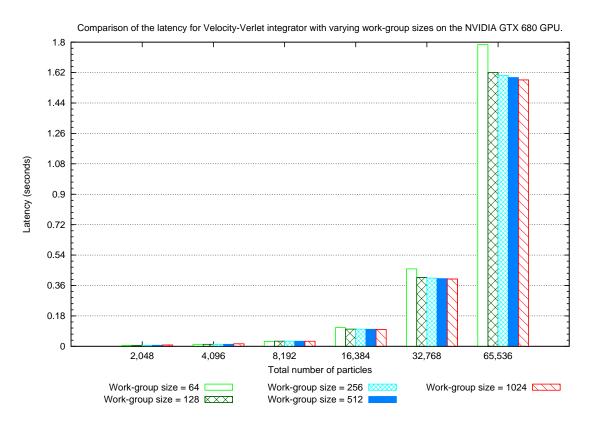

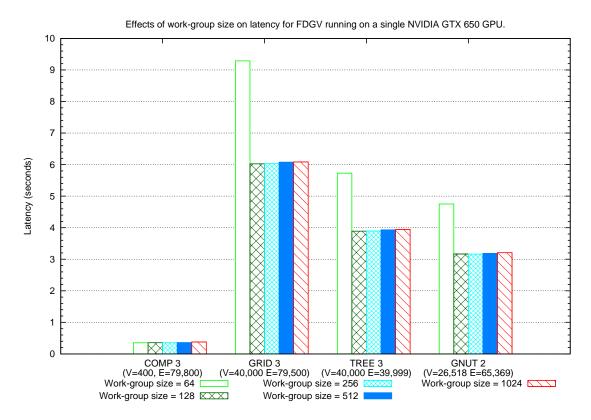

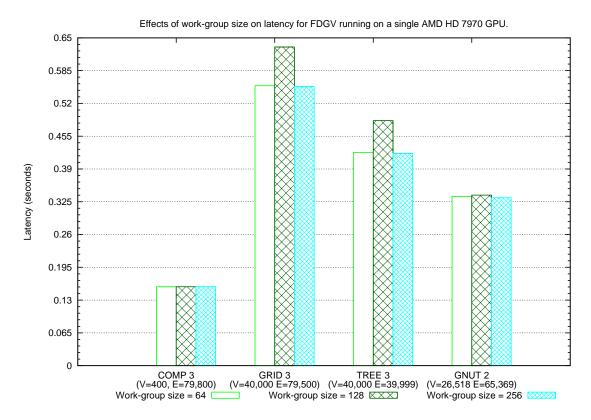

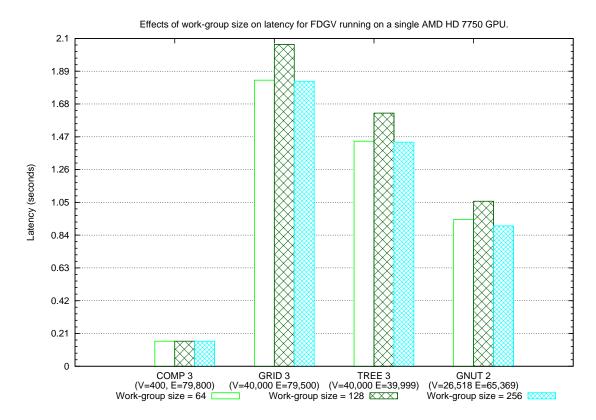

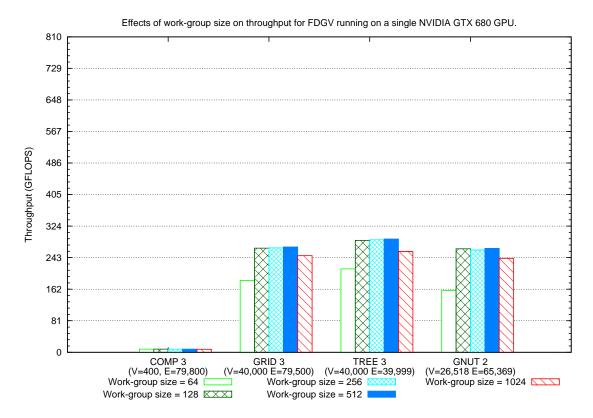

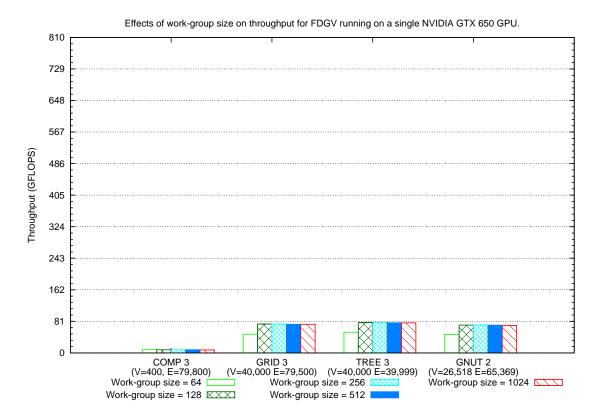

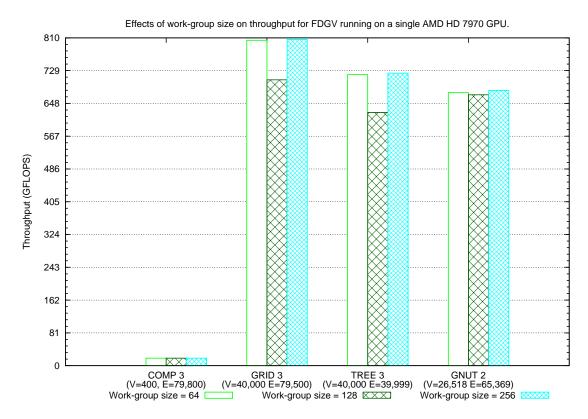

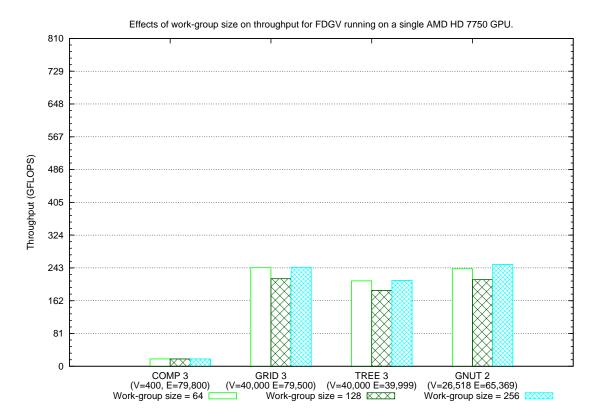

|            |      | 6.9.2  | Results on effects of work-group size                         |

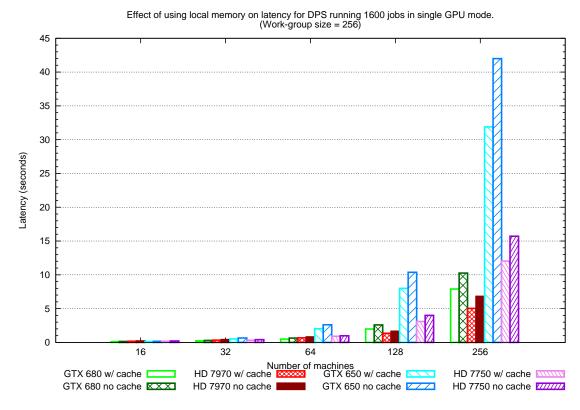

|            |      | 6.9.3  | Results on effects of local memory                            |

|            |      | 6.9.4  | Results on benefits of pre-pinned memory and DMA 152          |

|            |      | 6.9.5  | Results on application scaling with multi-GPUs                |

|            |      | 6.9.6  | Results on comparison of CPU vs.GPU performance               |

|            | 6.10 | Conclu | ısion and future work                                         |

|            |      |        |                                                               |

| A          | Mor  | e Evn  | eriment Results for Energy-Efficient Flow Time Scheduling 179 |

| <b>1 L</b> |      | _      | s on job selection strategies                                 |

|            |      | A.1.1  | ·                                                             |

|            |      | A.1.2  | Multi-processor simulations                                   |

|            | A 2  |        | s on speed functions                                          |

|            | 11.2 | A.2.1  | Effectiveness of speed scaling                                |

|            |      | A.2.2  | Speed scaling vs. semi-clairvoyant fixed speed function       |

|            |      | A.2.3  | Effectiveness of AJC speed spectrum                           |

|            | A.3  |        | s on processor allocation strategies                          |

|            |      |        |                                                               |

|            |      |        |                                                               |

**Bibliography**

# List of Figures

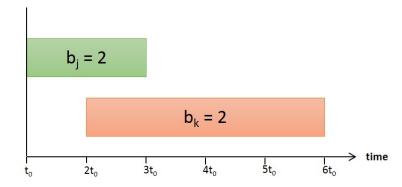

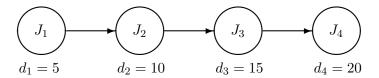

| 1.1<br>1.2 | An illustration of linear deterioration.  Examples of job precedence constraints.                                                                                                                                                                                                                                                                                                          | 10                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

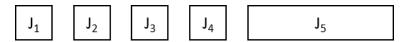

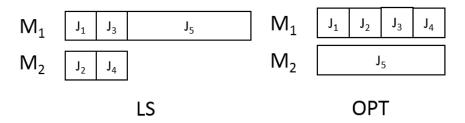

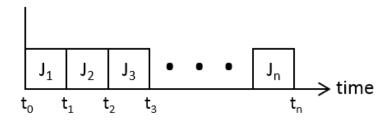

| 2.1<br>2.2 | An illustration of jobs based on the deteriorating rates                                                                                                                                                                                                                                                                                                                                   | 19                  |

| 2.3        | shown in Figure 2.1.  An illustration of $n$ jobs assigned to one machine                                                                                                                                                                                                                                                                                                                  | 19<br>20            |

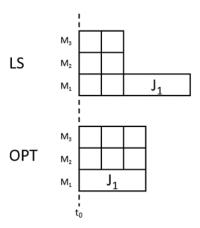

| 2.4        | Stage 1 of adversary: The deteriorating rate, $b_1$ , of job $J_1$ satisfies $1+b_1=(1+b)^3$ where $b$ is the deteriorating rate of each of the smaller jobs depicted in the illustration. Jobs are released at time $t_0$ and scaled according to                                                                                                                                         |                     |

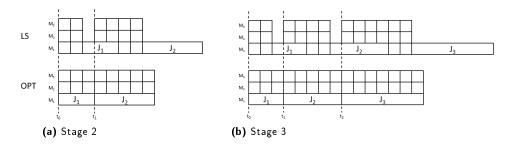

| 2.5        | deteriorating rates only.  Stages 2 and 3 of adversary: (A) In stage 2, jobs are released at time $t_1 = t_0(1+b_1)$ and as a result, LS cannot schedule them earlier on $M_1$ and $M_2$ . This means machines $M_1$ and $M_2$ are idle until time $t_1$ . (B) In stage 3 new jobs start arriving at time $t_2 = t_1(1+b_2)$ and the trend continues as with the previous stages.          | 21                  |

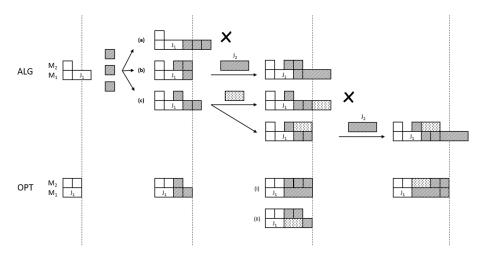

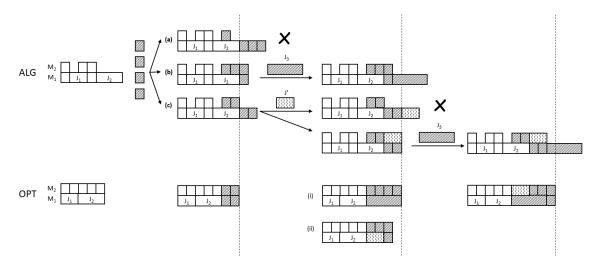

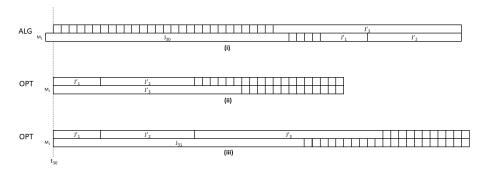

| 2.6        | Illustration of the 3 representative cases, labelled (a), (b) and (c), in stage                                                                                                                                                                                                                                                                                                            | <i>Z</i> , <i>Z</i> |

|            | 2 of the general lower bound.                                                                                                                                                                                                                                                                                                                                                              | 25                  |

| 2.7<br>2.8 | Example showing Stage 3 of the general lower bound. Illustration of the general lower bound for Stage 31 where $k=31$ and $h=15$ . (i) At $t_{30}$ ALG is still processing $J_{30}$ from Stage 30 on $M_1$ . (ii) OPT has completed all jobs released before $t_{30}$ including $J_{30}$ . (iii) OPT schedule for Stage 31. Note that OPT can maintain the same makespan on both machines. | 26                  |

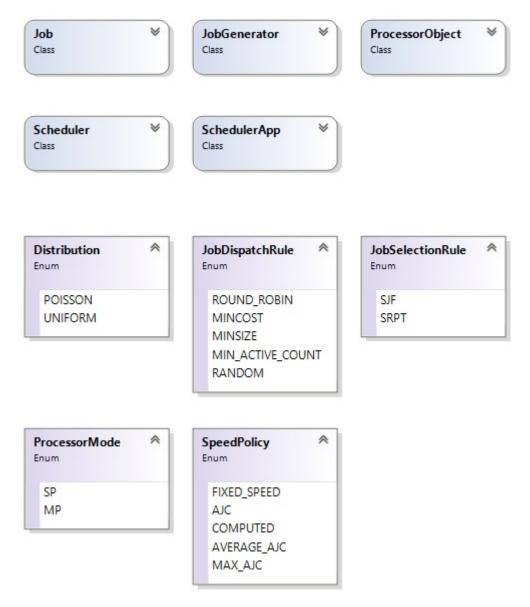

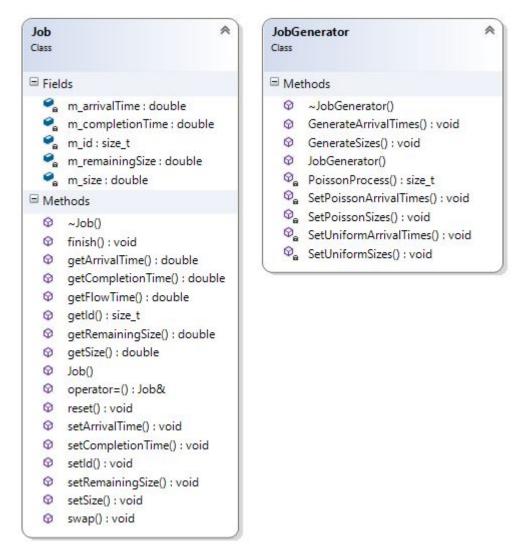

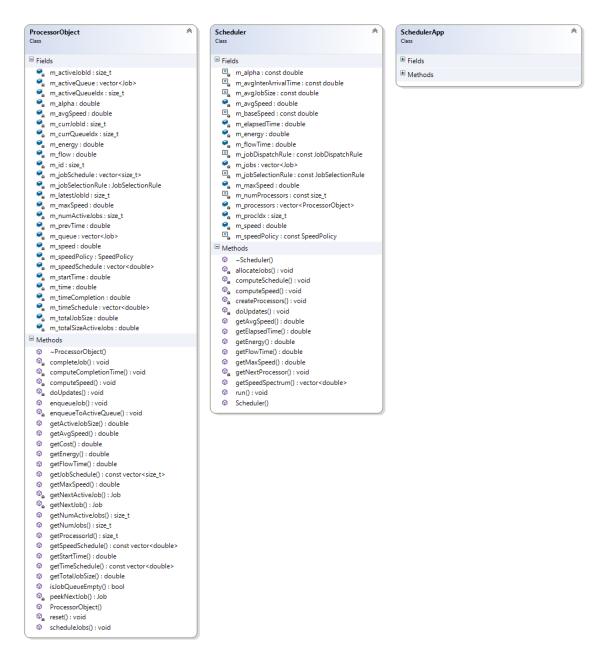

| 4.1        | Class diagram of the simulator software program.                                                                                                                                                                                                                                                                                                                                           | 44                  |

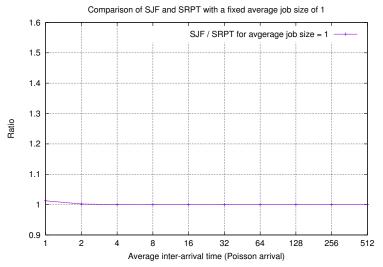

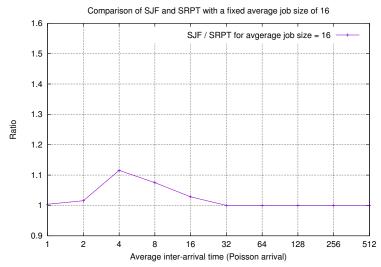

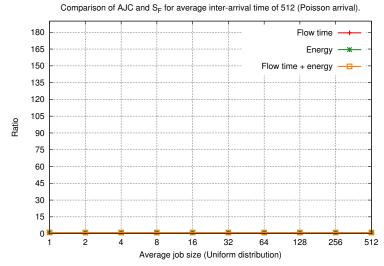

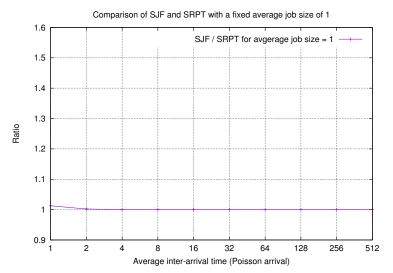

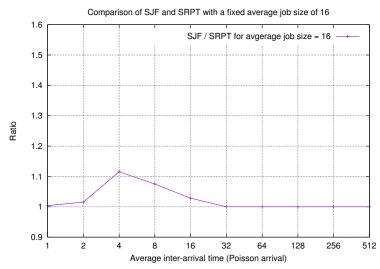

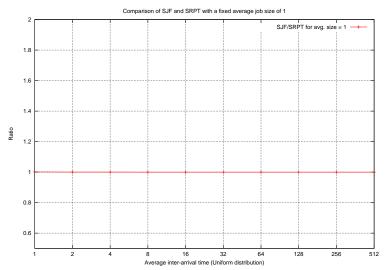

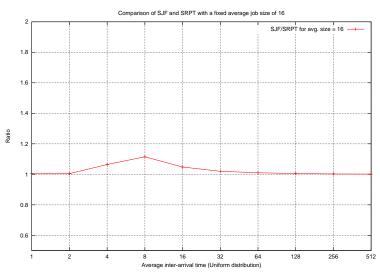

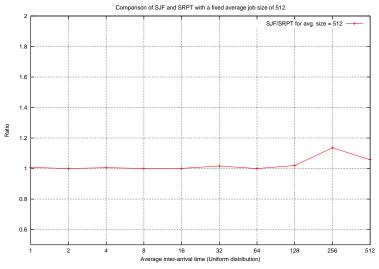

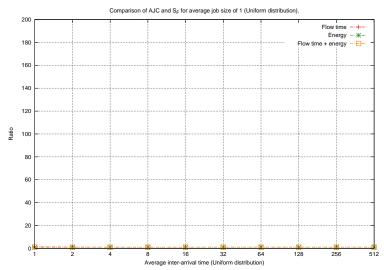

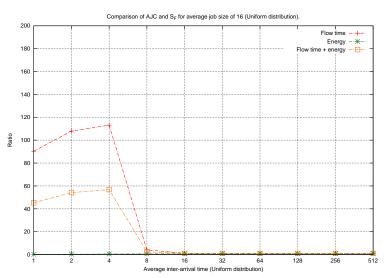

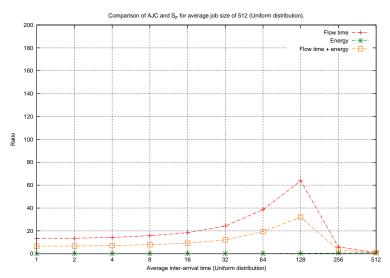

| 4.2        | Details of the Job and JobGenerator classes                                                                                                                                                                                                                                                                                                                                                | 45                  |

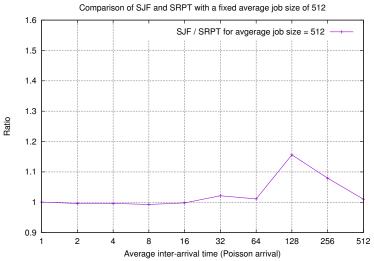

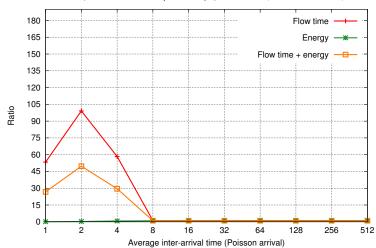

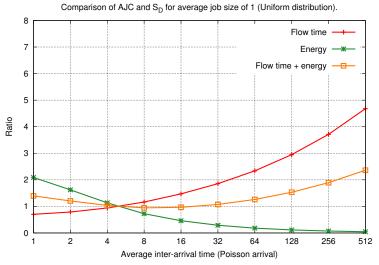

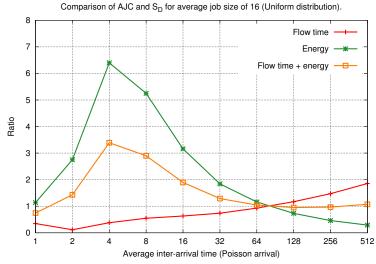

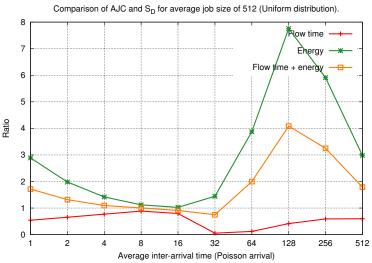

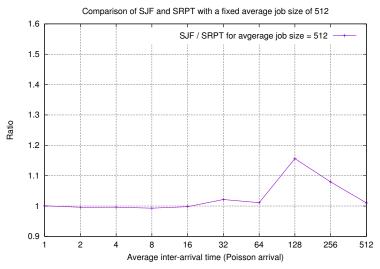

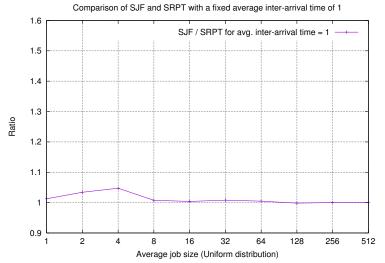

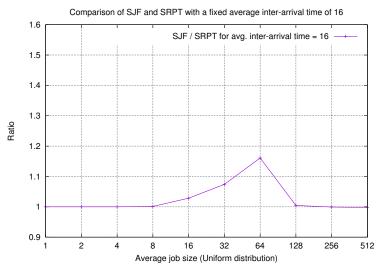

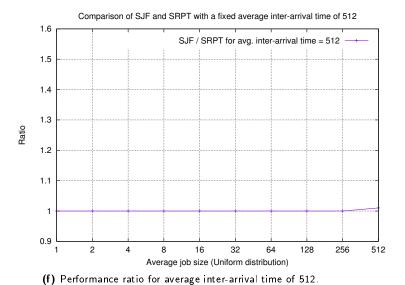

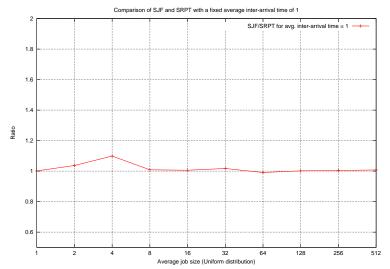

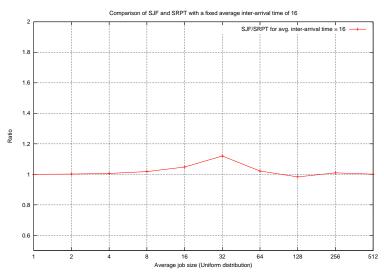

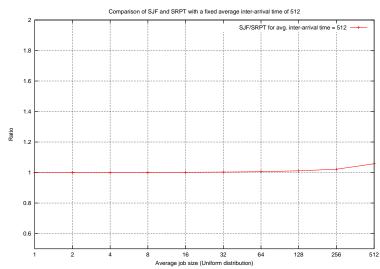

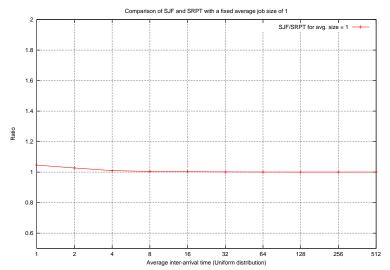

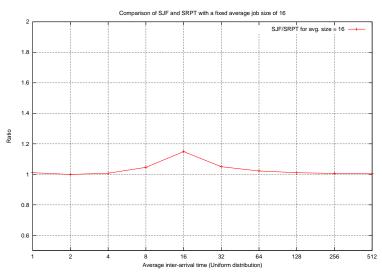

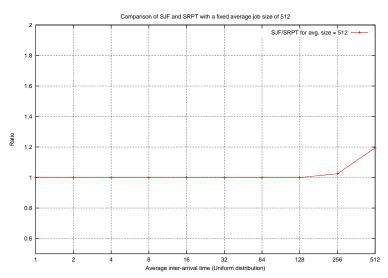

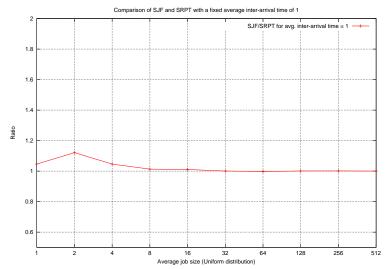

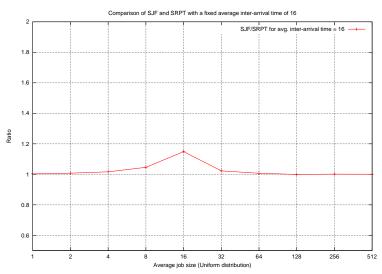

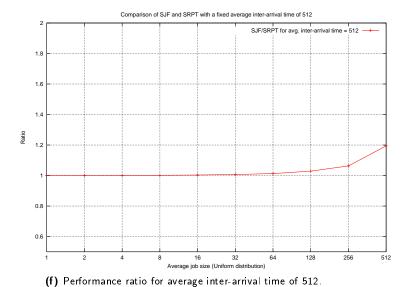

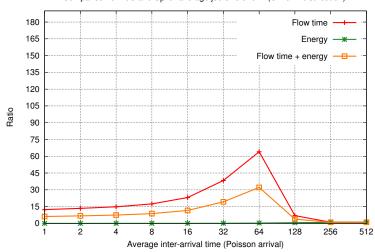

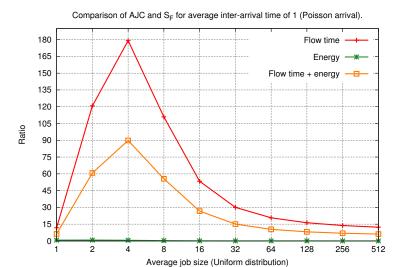

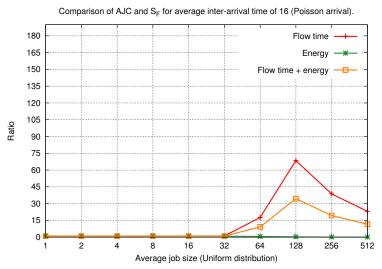

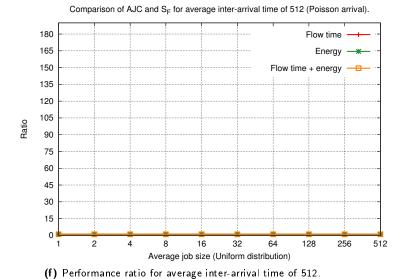

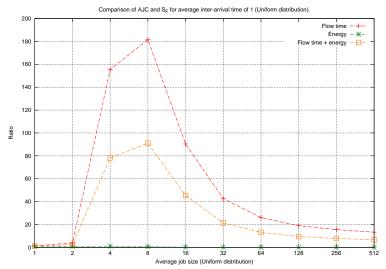

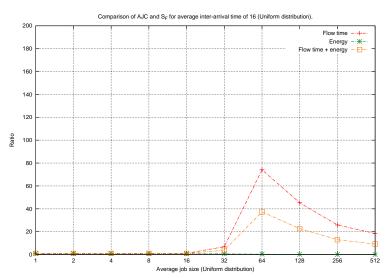

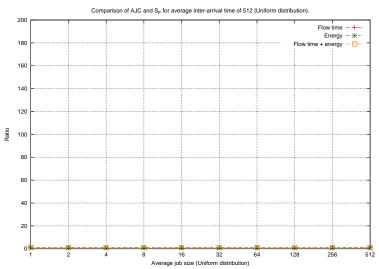

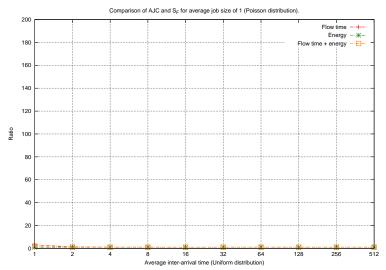

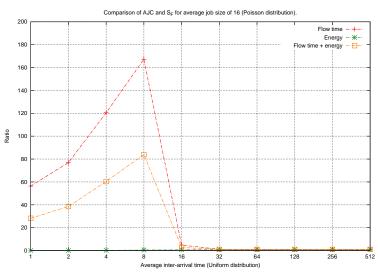

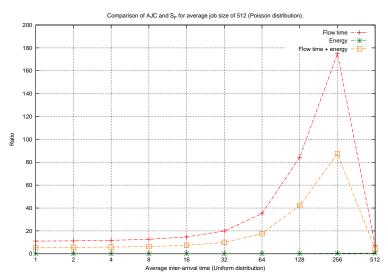

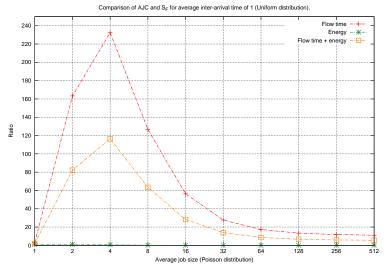

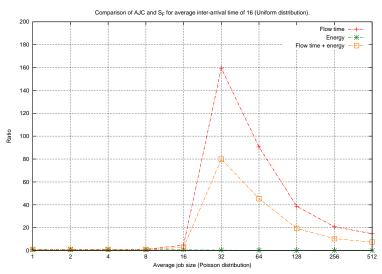

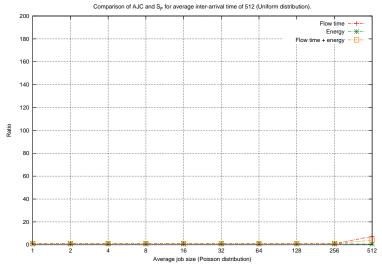

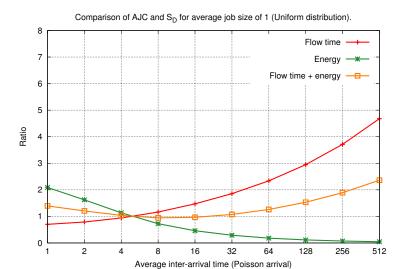

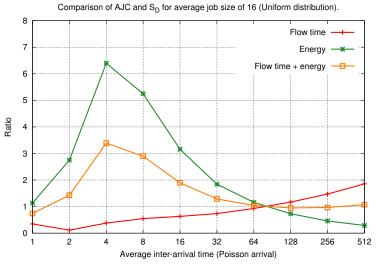

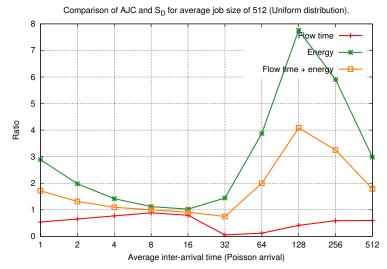

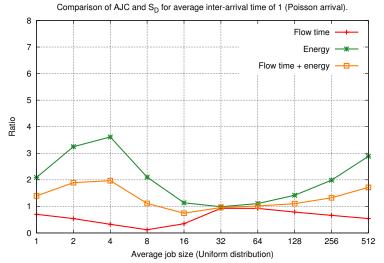

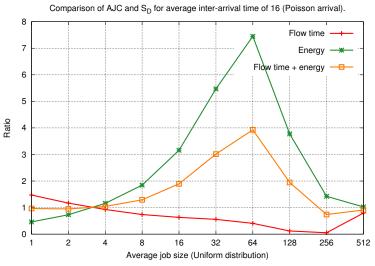

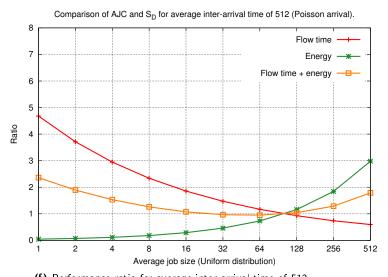

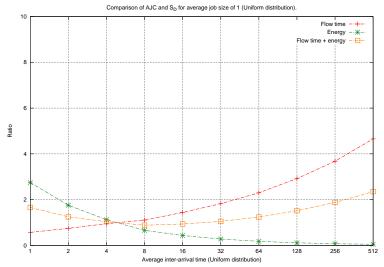

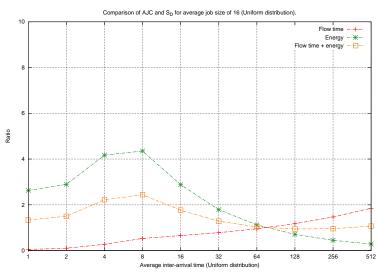

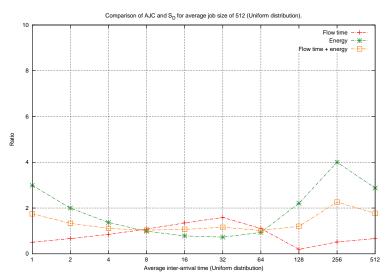

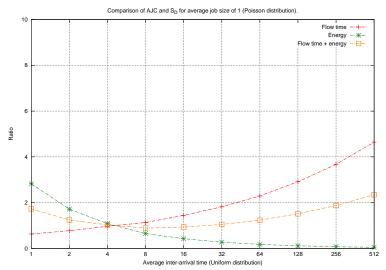

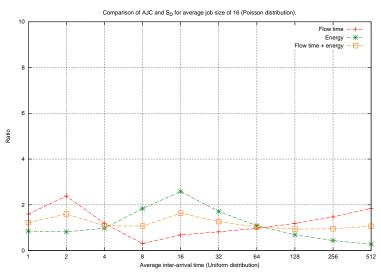

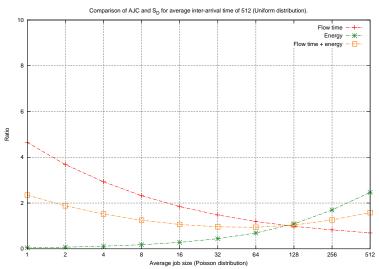

| 4.3<br>4.4 | Details of the scheduler part of the simulator.  Measurement shows the ratio of total flow time plus energy for SJF vs AJC on a single processor. Results are grouped according to average job                                                                                                                                                                                             | 46                  |

| 4.5        | Measurement shows the ratio of total flow time plus energy for SJF vs AJC on a single processor. Results are grouped according to average                                                                                                                                                                                                                                                  | 47                  |

| 4.0        | inter-arrival time.                                                                                                                                                                                                                                                                                                                                                                        | 48                  |

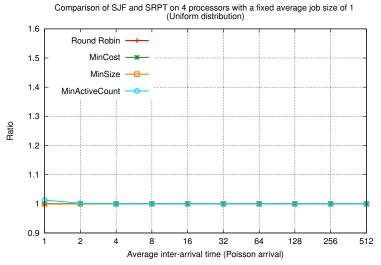

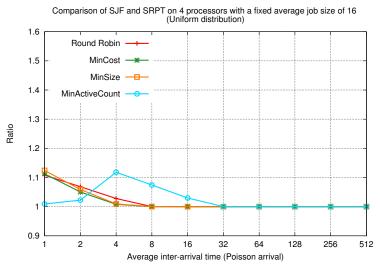

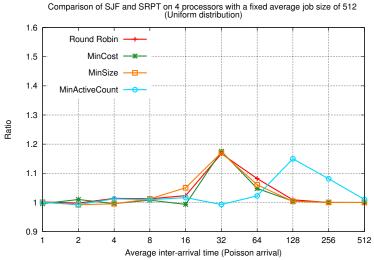

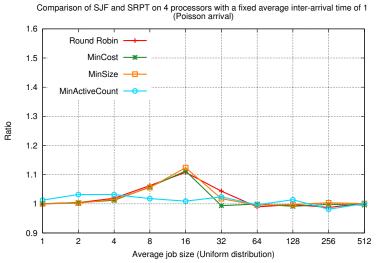

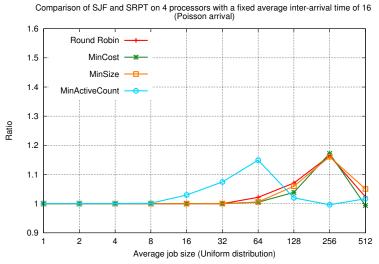

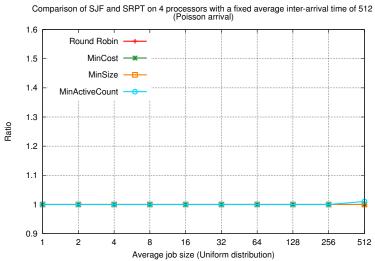

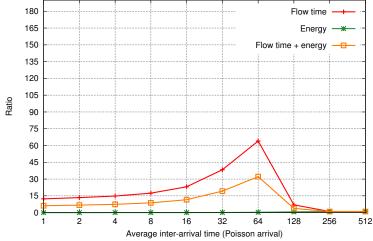

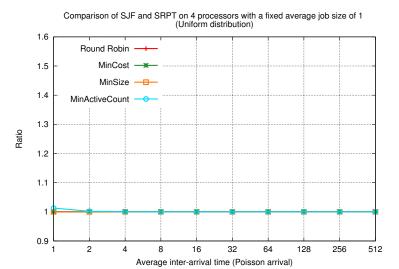

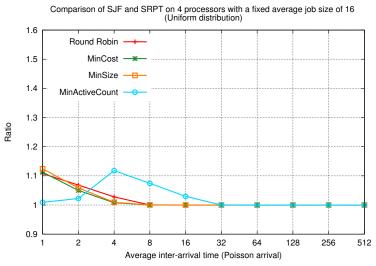

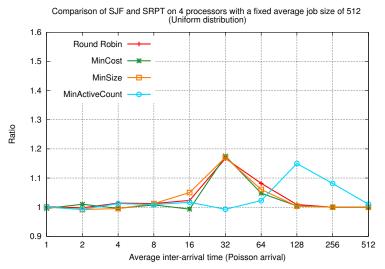

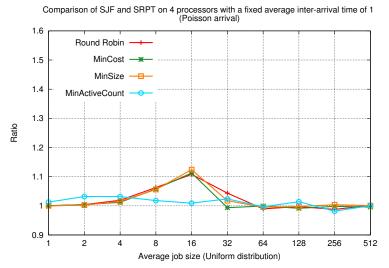

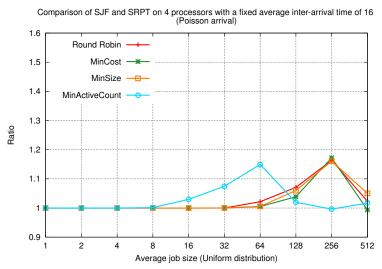

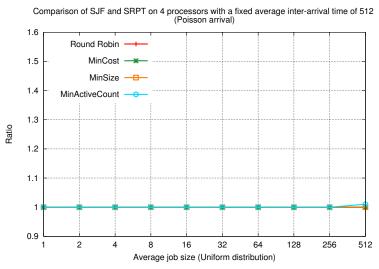

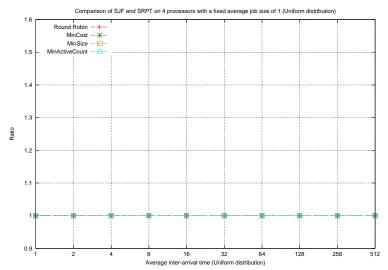

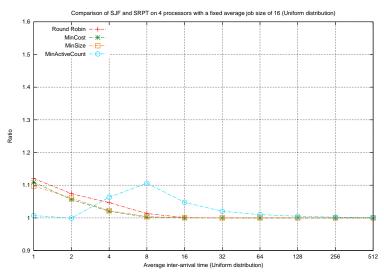

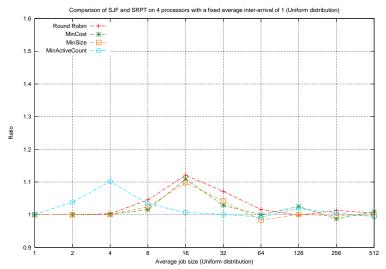

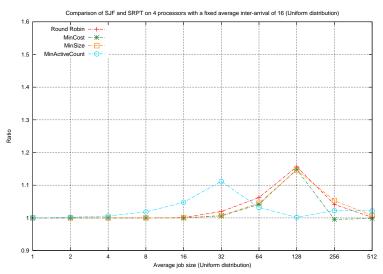

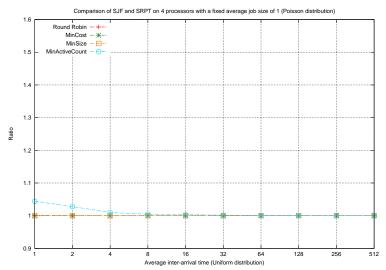

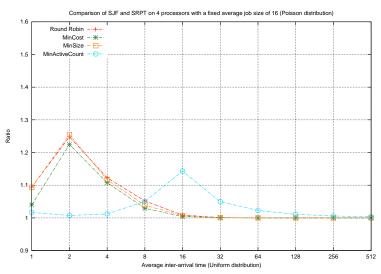

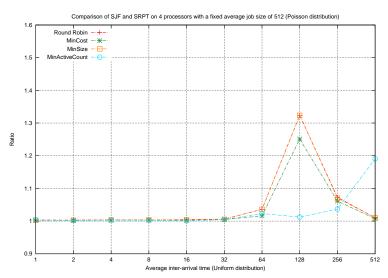

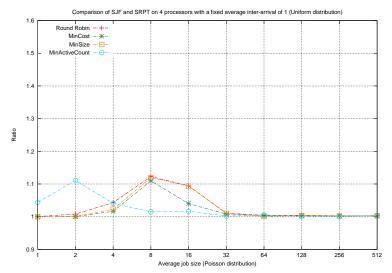

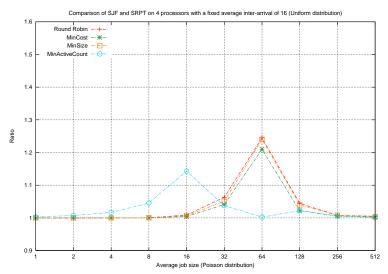

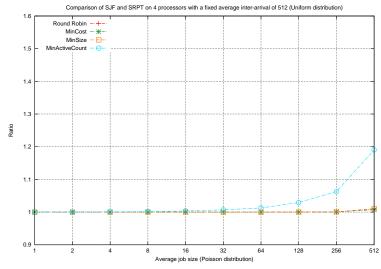

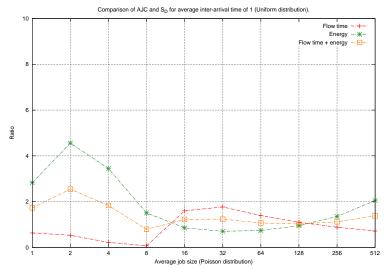

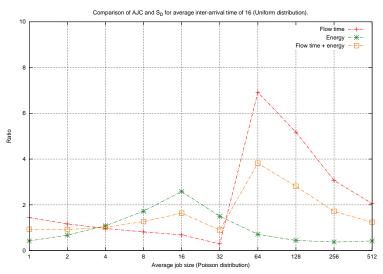

| 4.6        | Measurement shows the ratio of total flow time plus energy for SJF vs AJC on 4 processors. Results are grouped according to average job size.                                                                                                                                                                                                                                              | 50                  |

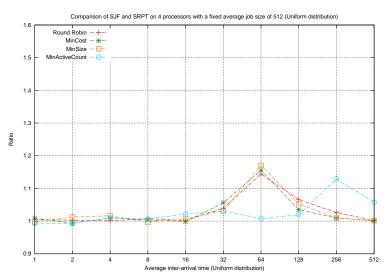

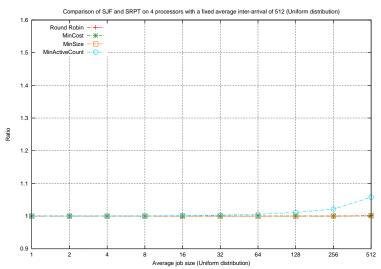

| 4.7        | Measurement shows the ratio of total flow time plus energy for SJF vs AJC on 4 processors. Results are grouped according to average inter-arrival time.                                                                                                                                                                                                                                    | 51                  |

List of Figures viii

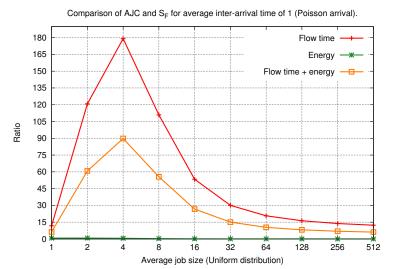

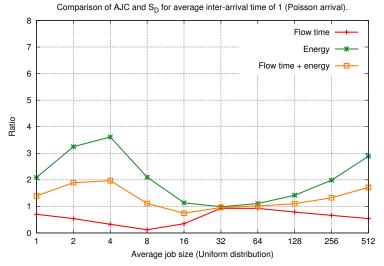

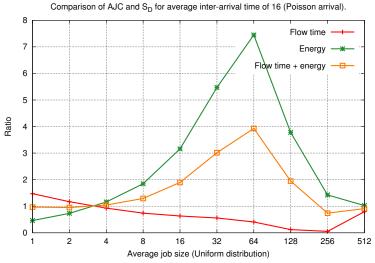

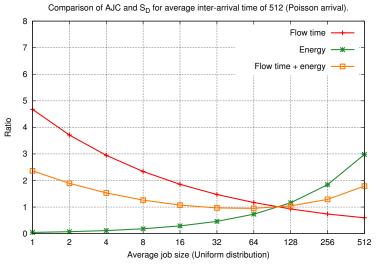

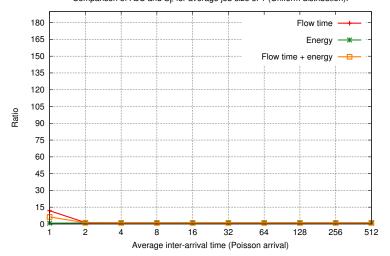

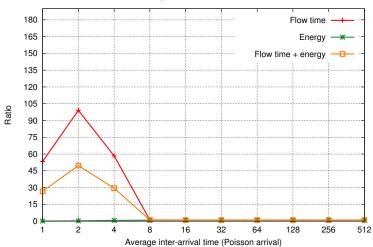

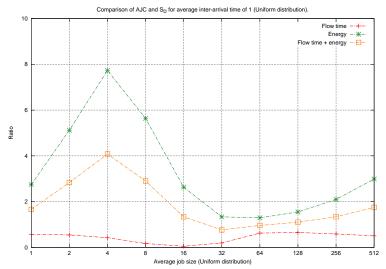

| 4.8  | Effectiveness of speed scaling: Measurement shows the ratio of total flow time plus energy for a fixed speed heuristic using a speed of 1 against AJC                                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | on a single processor. Results are grouped according to average job size.  Note: ratio is always at least 1                                                                                                                                                 | 52 |

| 4.9  | Effectiveness of speed scaling: Measurement shows the ratio of total flow time plus energy for a fixed speed heuristic using a speed of 1 against AJC on a single processor. Results are grouped according to average                                       |    |

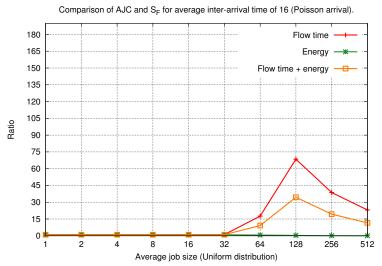

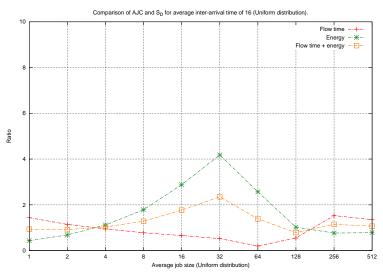

| 4.10 | inter-arrival time. Note: ratio is always at least 1                                                                                                                                                                                                        | 53 |

|      | the ratio of total flow time plus energy between AJC and a fixed speed function that has some information about the job set. Results are grouped                                                                                                            | 50 |

| 4.11 | according to average job size.  Speed scaling vs. semi-clairvoyant fixed speed function: Measurement shows the ratio of total flow time plus energy between AJC and a fixed speed function that has some information about the job set. Results are grouped | 59 |

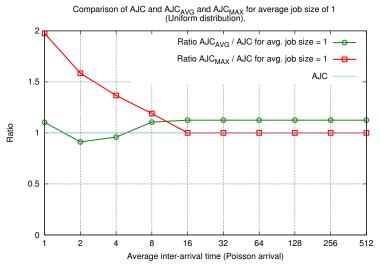

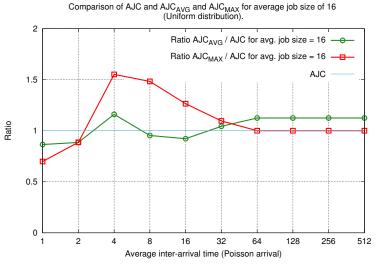

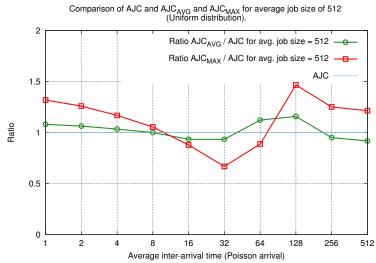

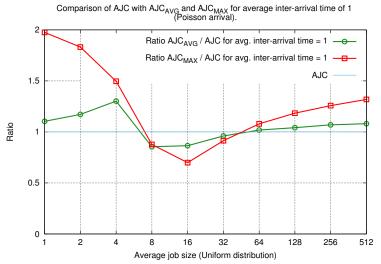

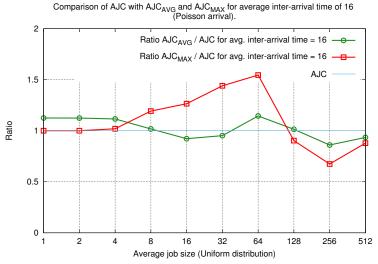

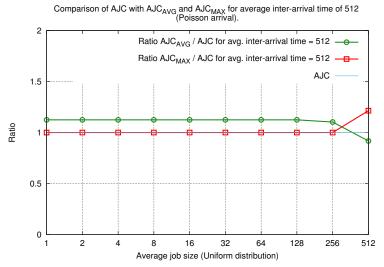

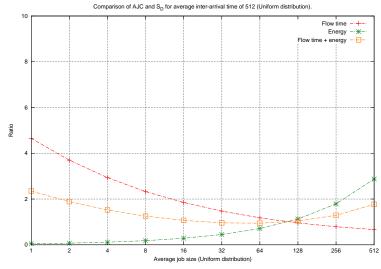

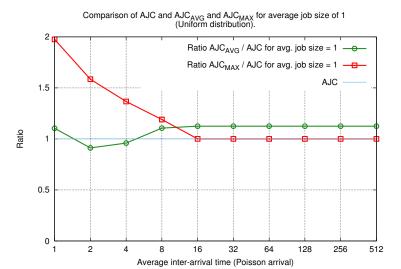

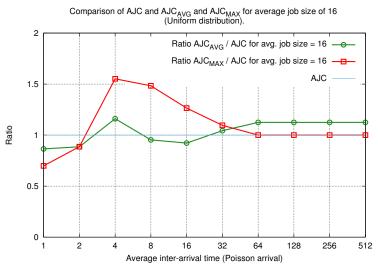

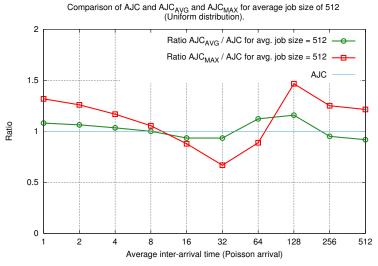

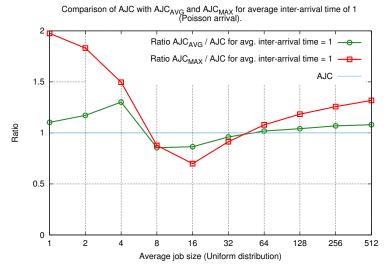

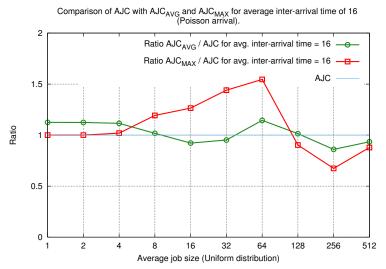

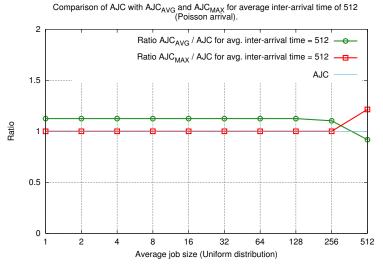

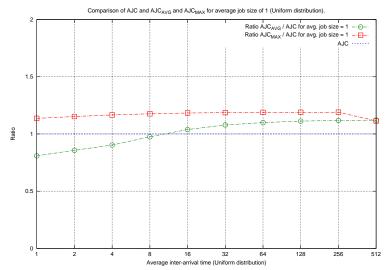

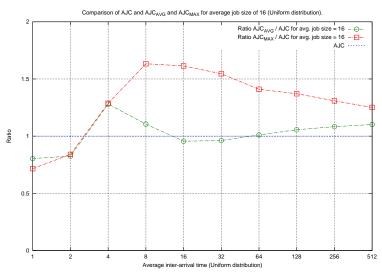

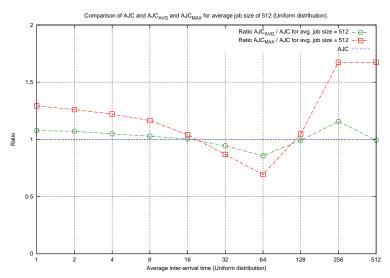

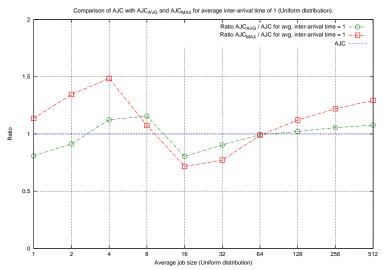

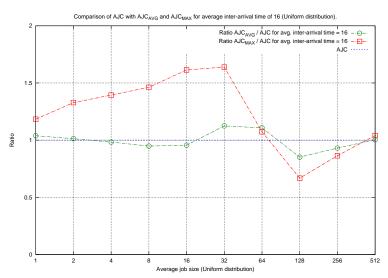

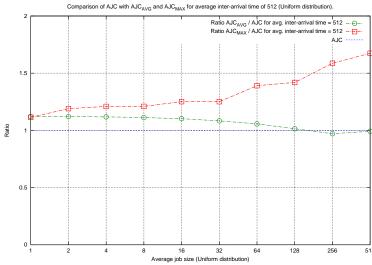

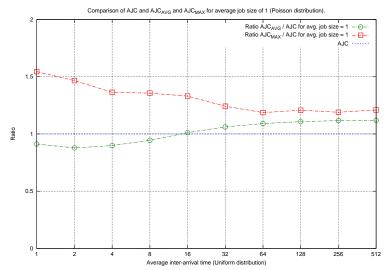

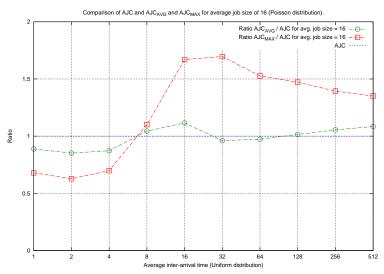

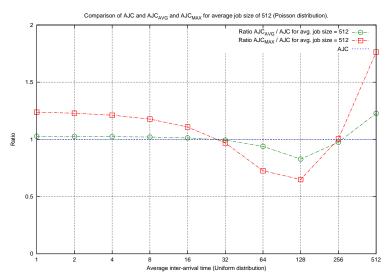

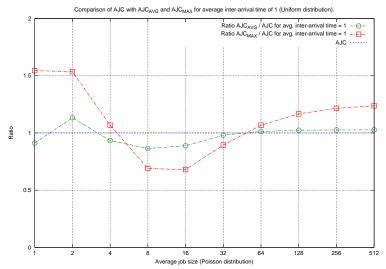

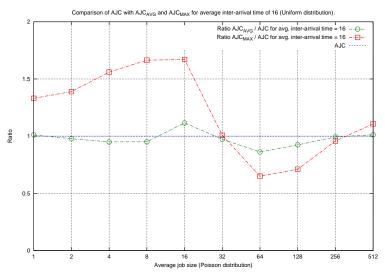

| 4.12 | according to average inter-arrival time.<br>$ Effectiveness\ of\ AJC\ speed\ spectrum\colon \mbox{Comparison of AJC to a fixed speed} $ function that uses, as fixed speed values, the average and maximum speeds                                           | 60 |

| 4 10 | obtained from a prior AJC run. Results show the performance ratio of the total flow time plus energy of fixed speed functions vs.AJC.                                                                                                                       | 61 |

| 4.13 | Effectiveness of AJC speed spectrum: Comparison of AJC to a fixed speed function that uses, as fixed speed values, the average and maximum speeds obtained from a prior AJC run. Results show the performance ratio of                                      |    |

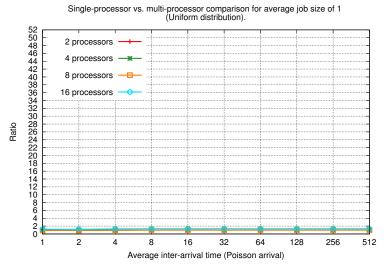

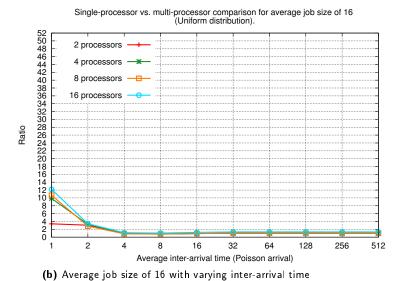

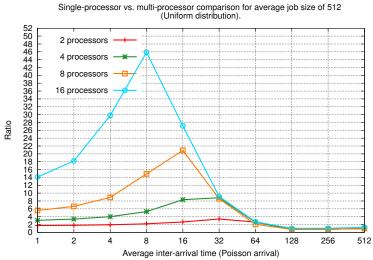

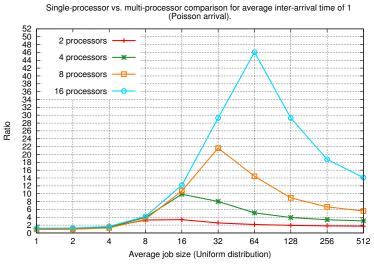

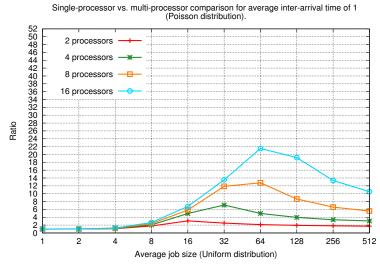

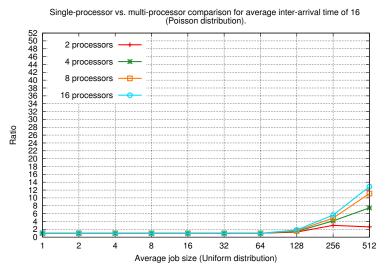

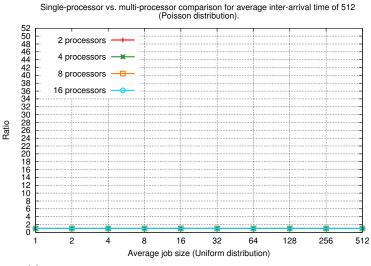

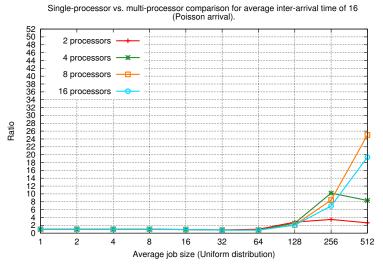

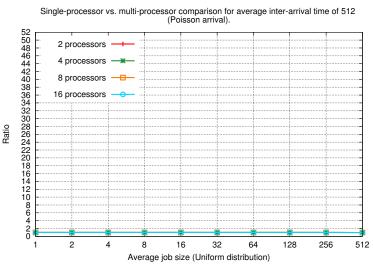

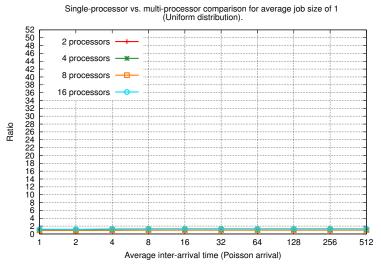

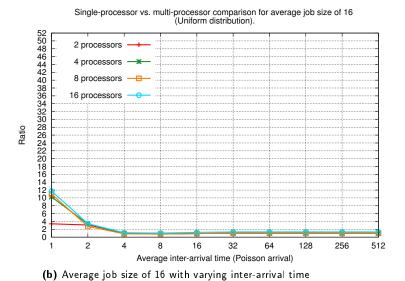

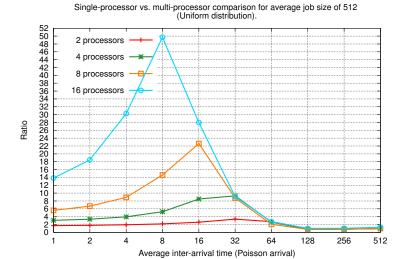

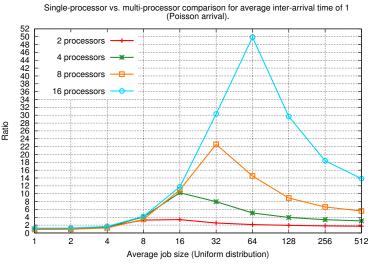

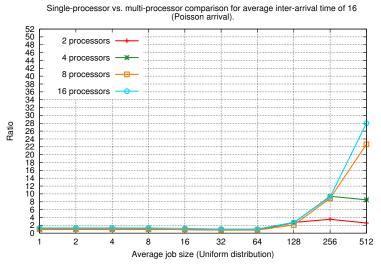

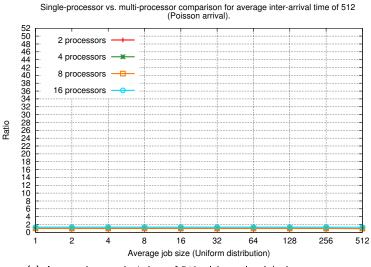

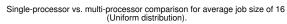

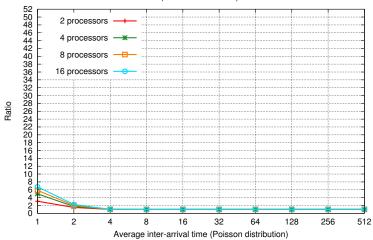

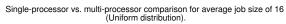

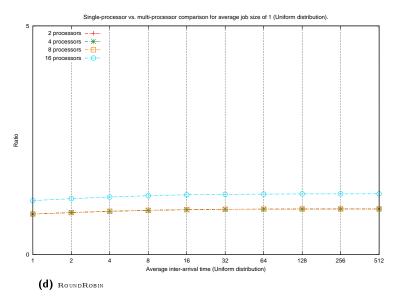

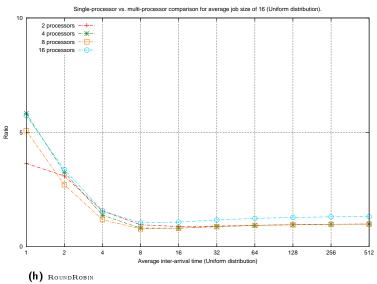

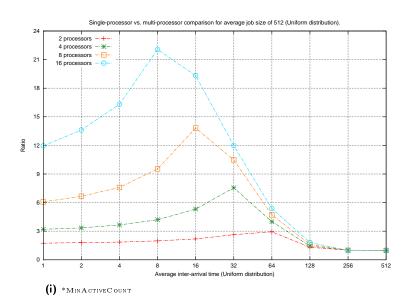

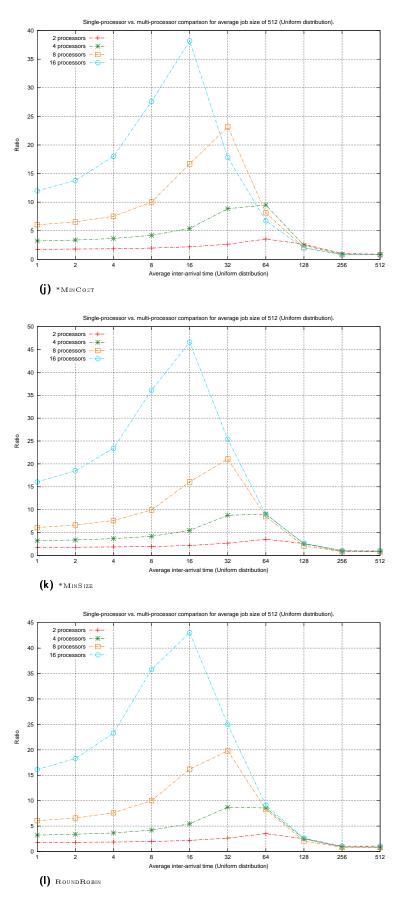

| 4.14 | the total flow time plus energy of fixed speed functions vs.AJC Results for ROUNDROBIN in terms of average job size comparing the performance ratio of total flow time plus energy for a single processor                                                   | 62 |

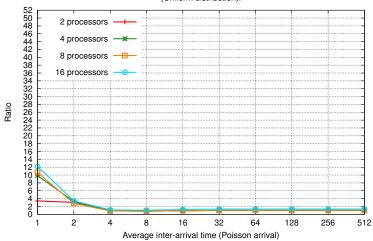

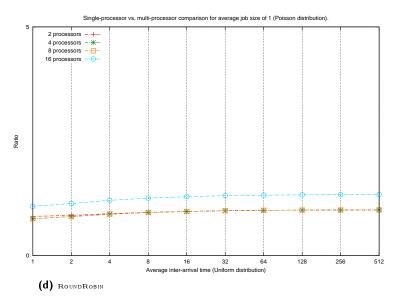

| 4 15 | vs.multiple processors.  Results for ROUNDROBIN in terms of average inter-arrival time comparing                                                                                                                                                            | 63 |

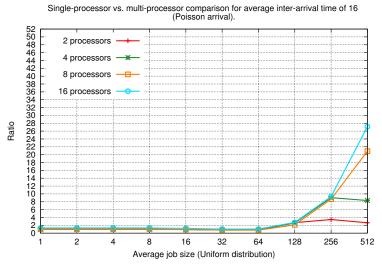

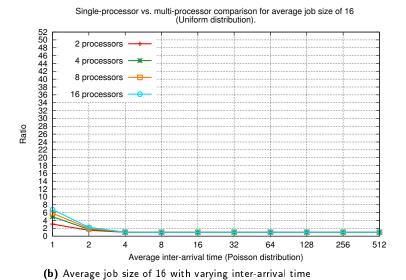

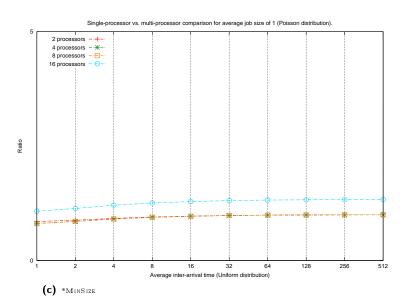

| 1.10 | the performance ratio of total flow time plus energy for a single processor vs.multiple processors.                                                                                                                                                         | 64 |

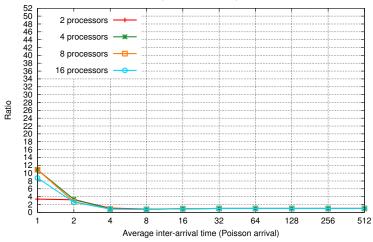

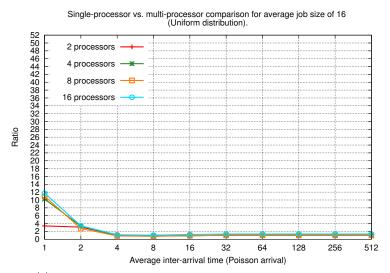

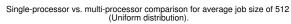

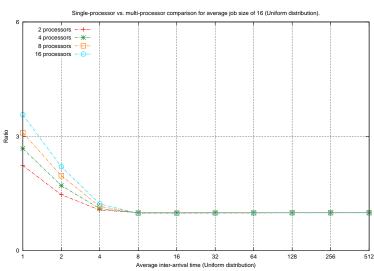

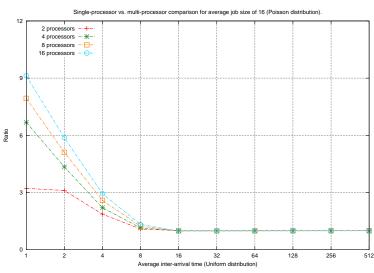

| 4.16 | Results for *MINACTIVECOUNT in terms of average job size comparing the performance ratio of total flow time plus energy for a single processor vs.multiple processors.                                                                                      | 65 |

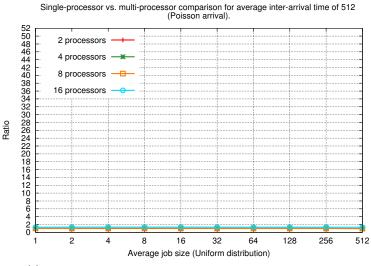

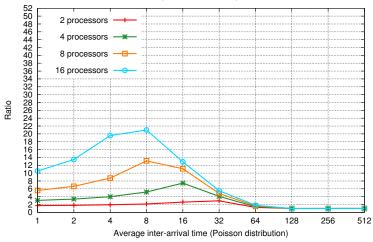

| 4.17 | Results for *MINACTIVECOUNT in terms of average inter-arrival time comparing the performance ratio of total flow time plus energy for a single                                                                                                              |    |

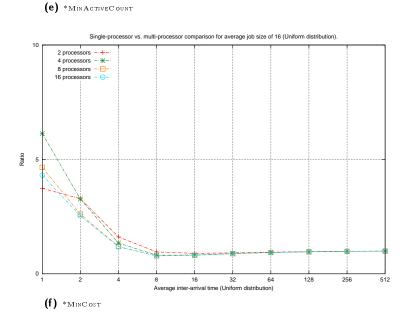

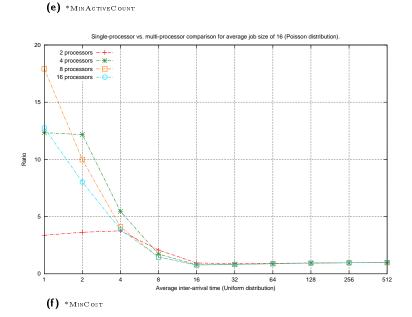

| 4.18 | processor vs.multiple processors.  Results for *MinCost in terms of average job size comparing the performance ratio of total flow time plus energy for a single processor vs.multiple                                                                      | 66 |

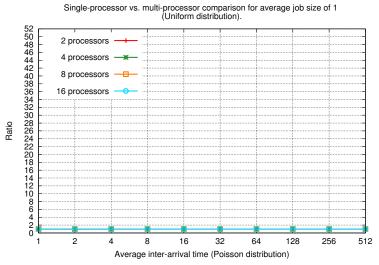

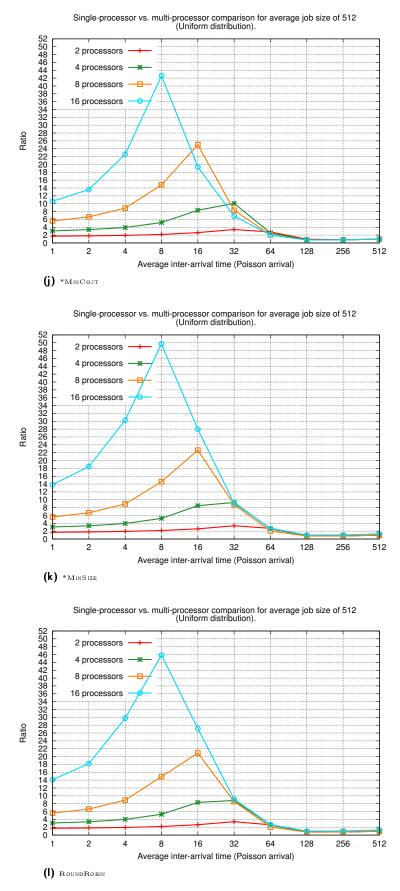

| 4.19 | processors                                                                                                                                                                                                                                                  | 67 |

|      | the performance ratio of total flow time plus energy for a single processor vs.multiple processors.                                                                                                                                                         | 68 |

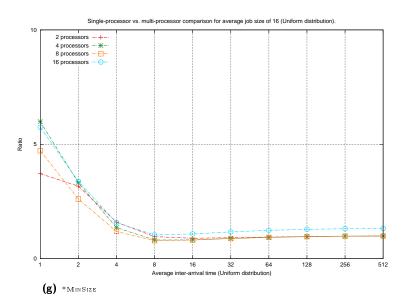

| 4.20 | Results for *MINSIZE in terms of average job size comparing the performance ratio of total flow time plus energy for a single processor vs.multiple processors.                                                                                             | 69 |

| 4.21 | Results for *MinSize in terms of average inter-arrival time comparing the performance ratio of total flow time plus energy for a single processor                                                                                                           |    |

|      | vs.multiple processors.                                                                                                                                                                                                                                     | 70 |

List of Figures ix

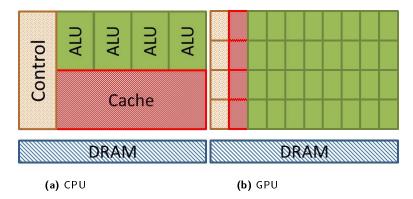

| 5.1  | A fundamental difference between a CPU and a GPU is that the GPU dedicates majority of its transistors to execution units.                                                                                           | 74  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

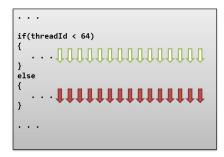

| 5.2  | Thread divergence occurs as a result of threads within a wavefront/warp taking different code paths.                                                                                                                 | 76  |

| 5.3  | Thread divergence can be avoided if branch granularity of the GPU hardware is maintained                                                                                                                             | 77  |

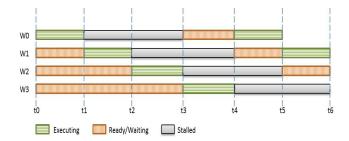

| 5.4  | The GPU is able to hide latency by swapping out wavefronts/warps that stall during memory operations.                                                                                                                | 78  |

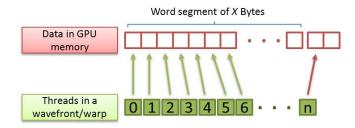

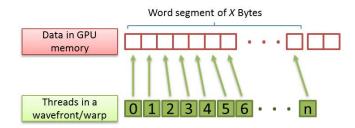

| 5.5  | Non-coalesced memory access patterns can result in poor performance on the GPU hardware.                                                                                                                             | 79  |

| 5.6  | Coalesced memory access patterns can improve performance on the GPU hardware.                                                                                                                                        | 79  |

| 5.7  | Generalized block diagram of AMD's GCN architecture.                                                                                                                                                                 | 80  |

| 5.8  | Generalized block diagram of NVIDIA's Kepler architecture                                                                                                                                                            | 81  |

| 5.9  | Block diagram illustrating the major components of the OpenCL platform.                                                                                                                                              | 83  |

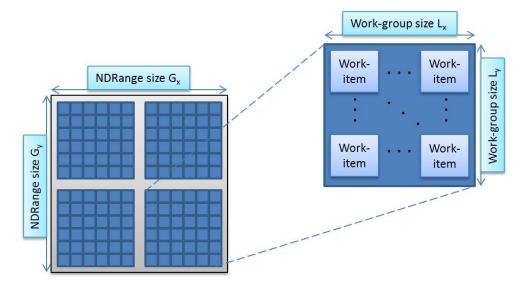

| 5.10 | $\label{lem:composition} Decomposition of an \ OpenCL \ index \ space \ into \ work-groups \ and \ work-items.$                                                                                                      | 84  |

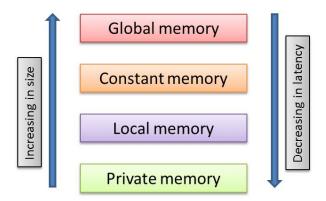

| 5.11 | Illustration of the OpenCL memory model                                                                                                                                                                              | 85  |

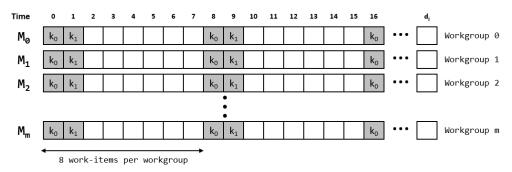

| 6.1  | Illustration of how the NDRange is defined so that work-groups are mapped to machines in the input and a work-item maps to a time index                                                                              | 94  |

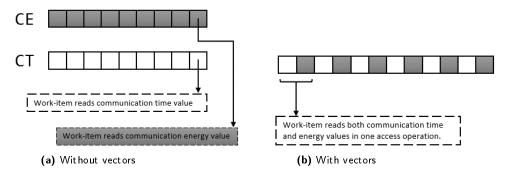

| 6.2  | An example showing the advantage of using vector data type. (a) Without vectors, work-items need 4 memory accesses in order to retrieve values from tables. (b) Using vectors, two read operations are merged into a |     |

|      | single read.                                                                                                                                                                                                         | 95  |

| 6.3  | Alignment with no gap.                                                                                                                                                                                               | 97  |

| 6.4  | Alignment with 1 gap.                                                                                                                                                                                                | 97  |

| 6.5  | Alignment with 2 gaps                                                                                                                                                                                                | 97  |

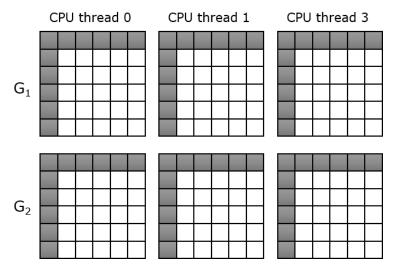

| 6.6  | Block diagram showing the memory requirement for matrix G for each processor in GapsMis-t when executing for a 2-gap alignment                                                                                       | 100 |

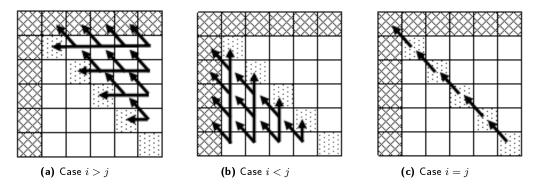

| 6.7  | Illustration of the data dependencies among cells in the three cases within the GapsMis algorithm.                                                                                                                   |     |

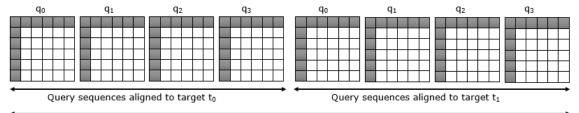

| 6.8  | Illustration of how GapsMis-d maps alignment tasks to the GPU device across work-groups.                                                                                                                             |     |

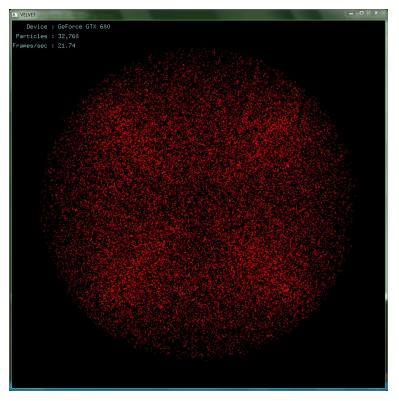

| 6.9  | A screenshot of Velvet capturing the starting positions of 32,768 particles projected inside a 3-ball. This sample is running on an NVIDIA GTX 680 GPU.                                                              |     |

| 6.10 | FDGV running a visualization of a graph with a grid-like structure consisting of 6,400 vertices and 12,640 edges.                                                                                                    |     |

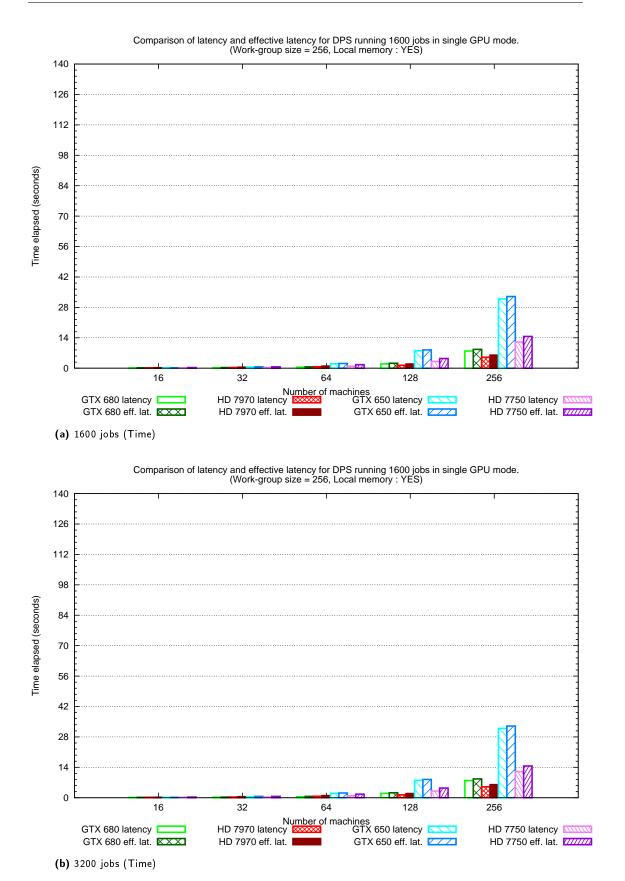

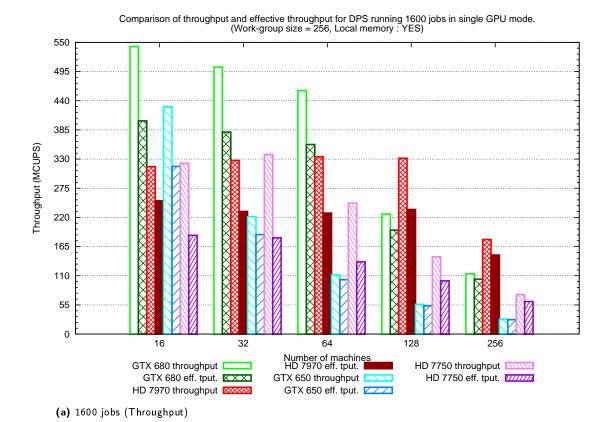

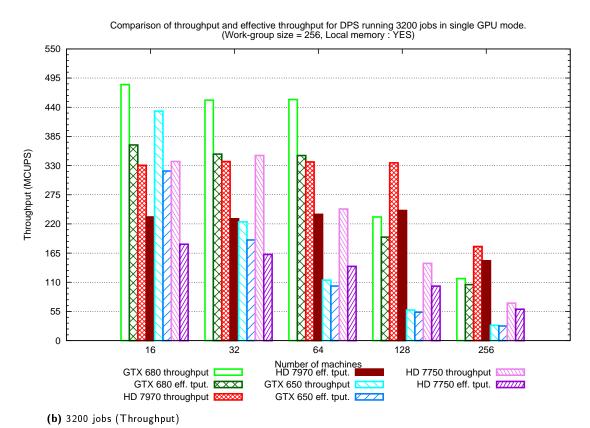

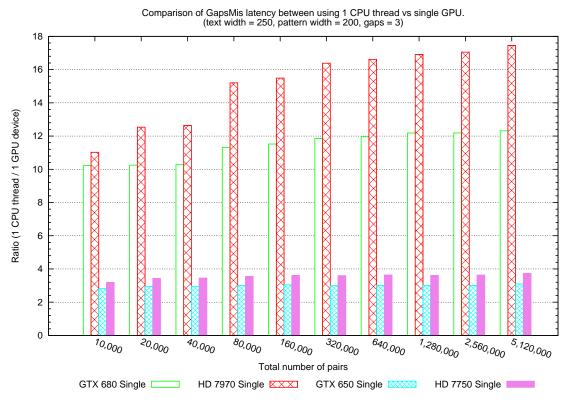

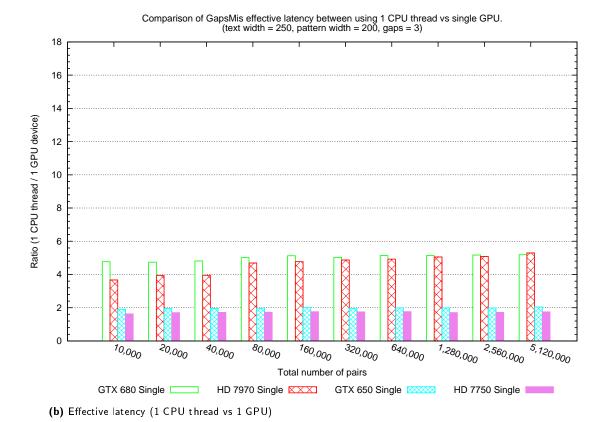

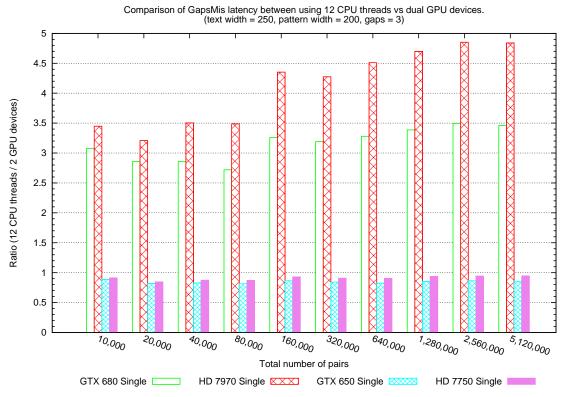

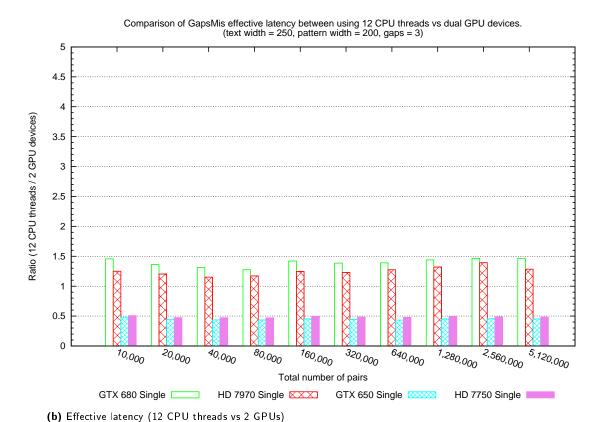

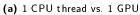

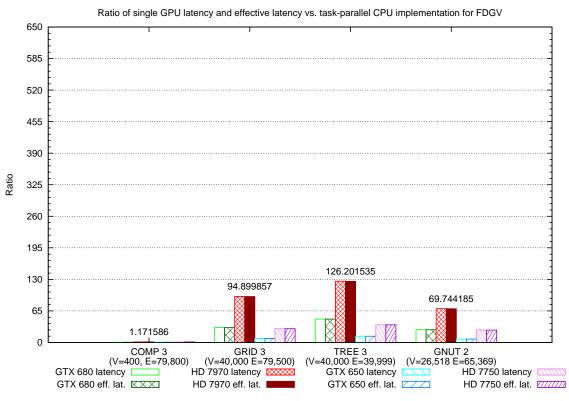

| 6.11 | Comparison of latency vs.effective latency for single GPU performance                                                                                                                                                | 119 |

|      | Comparison of throughput vs.effective throughput for single GPU performance.                                                                                                                                         |     |

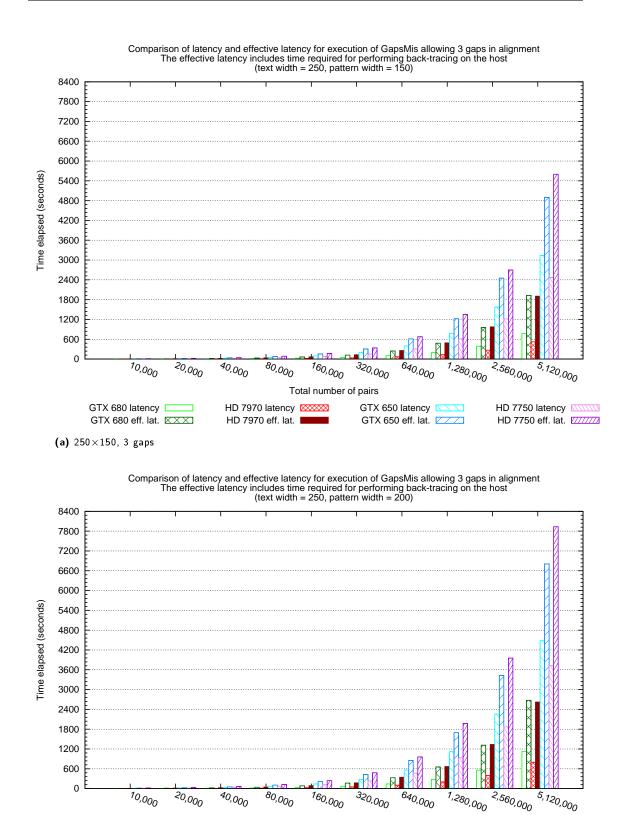

| 6.13 | Comparison of the latency and effective latency for GapsMis-d running on a single GPU device performing alignments allowing 2 gaps.                                                                                  |     |

| 6.14 | Comparison of the latency and effective latency for $GapsMis-d$ running on                                                                                                                                           | 123 |

List of Figures x

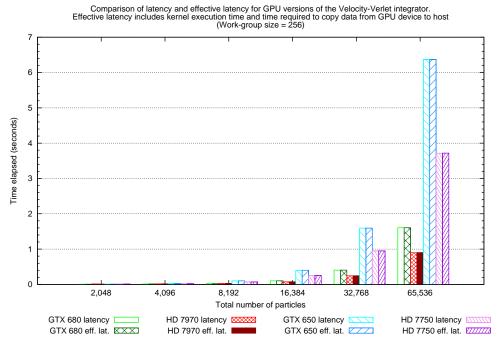

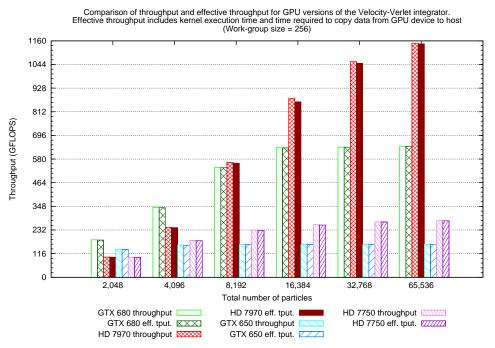

| 6.15 | Results comparing the latency and effective latency of executing $Velvet-d$ for all problem sizes (Figure 6.15(a)). Resulting throughput performance is shown in Figure 6.15(b). Here, due to the small data to computation ratio, the communication time between host and compute device is marginal. | 125 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

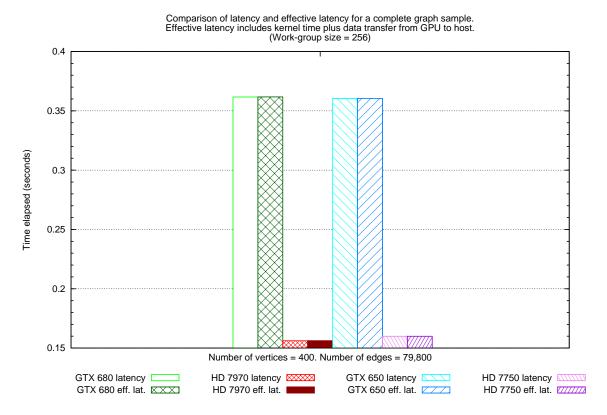

| 6.16 | Comparison of latency vs.effective latency for complete graph (400 vertices, 79,800 edges)                                                                                                                                                                                                             |     |

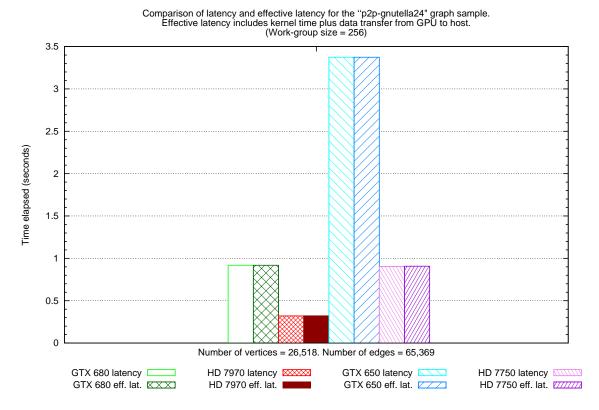

| 6.17 | Comparison of latency vs.effective latency for Gnutella p2p network graph (26,518 vertices, 65,369 edges)                                                                                                                                                                                              |     |

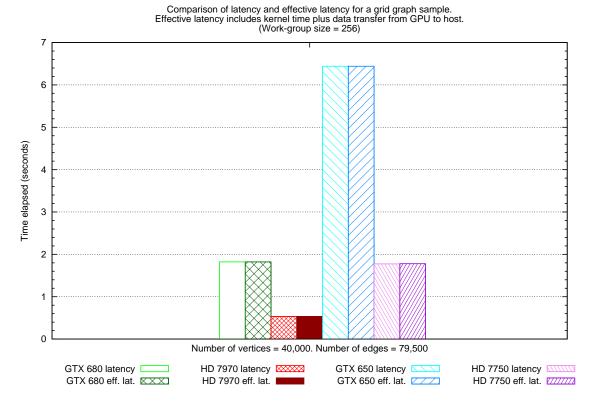

| 6.18 | Comparison of latency vs.effective latency for grid graph (40,000 vertices, 79,500 edges)                                                                                                                                                                                                              |     |

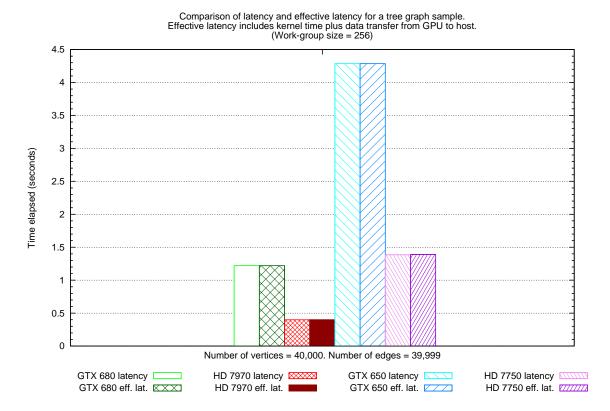

| 6.19 | Comparison of latency vs.effective latency for tree graph (40,000 vertices,                                                                                                                                                                                                                            |     |

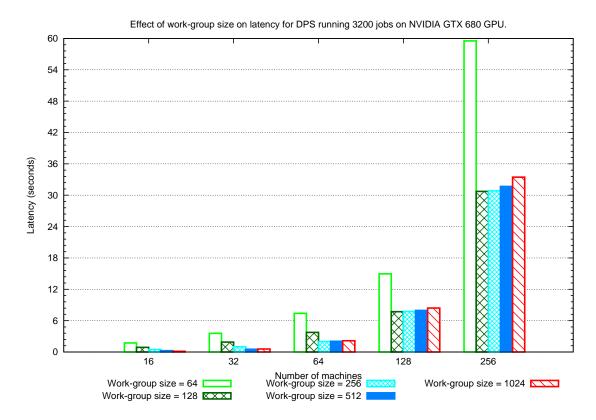

| 6.20 | 39,999 edges) Latency for DPS- $d$ with $3,200$ jobs with varying work-group sizes on NVIDIA GTX $680$ GPU.                                                                                                                                                                                            |     |

| 6.21 | Latency for DPS-d with 3,200 jobs with varying work-group sizes on NVIDIA GTX 650 GPU.                                                                                                                                                                                                                 |     |

| 6.22 | Latency for DPS-d with 3,200 jobs with varying work-group sizes on AMD HD 7970 GPU.                                                                                                                                                                                                                    |     |

| 6.23 | Latency for DPS- $d$ with 3,200 jobs with varying work-group sizes on AMD HD 7750 GPU.                                                                                                                                                                                                                 |     |

| 6.24 | Throughput for DPS-d with 3,200 jobs with varying work-group sizes on NVIDIA GTX 680 GPU.                                                                                                                                                                                                              |     |

| 6.25 | Throughput for DPS- $d$ with 3,200 jobs with varying work-group sizes on NVIDIA GTX 650 GPU.                                                                                                                                                                                                           |     |

| 6.26 | Throughput for DPS- $d$ with 3,200 jobs with varying work-group sizes on AMD HD 7970 GPU.                                                                                                                                                                                                              |     |

| 6.27 | Throughput for DPS-d with 3,200 jobs with varying work-group sizes on AMD HD 7750 GPU                                                                                                                                                                                                                  | 133 |

| 6.28 | Latency for Velvet-d with varying work-group sizes on NVIDIA GTX 680 GPU.                                                                                                                                                                                                                              | 134 |

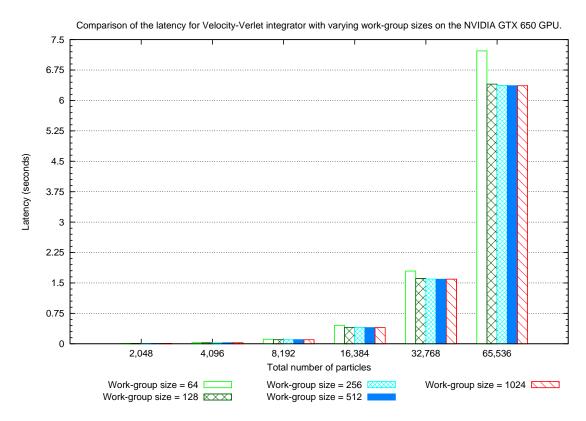

| 6.29 | Latency for $\mathtt{Velvet}\text{-}d$ with varying work-group sizes on NVIDIA GTX 650 GPU.                                                                                                                                                                                                            | 135 |

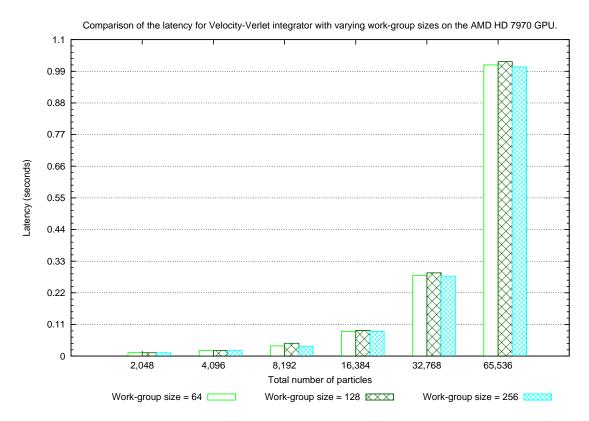

| 6.30 | Latency for $Velvet-d$ with varying work-group sizes on AMD HD 7970 GPU.                                                                                                                                                                                                                               | 136 |

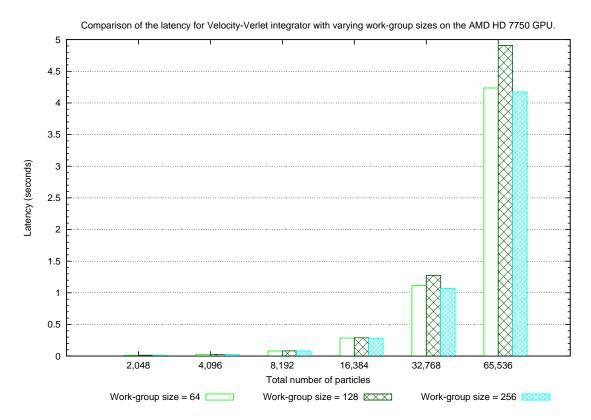

| 6.31 | Latency for Velvet-d with varying work-group sizes on AMD HD 7750 GPU                                                                                                                                                                                                                                  | 137 |

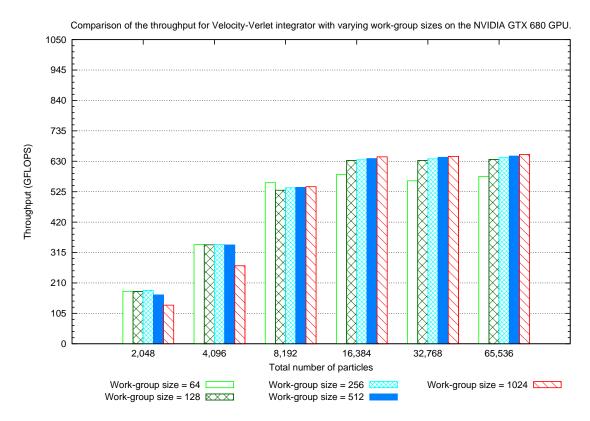

|      | Results showing the throughput performance of $\tt Velvet-d$ as work-group size varies on the NVIDIA GTX 680 GPU.                                                                                                                                                                                      | 138 |

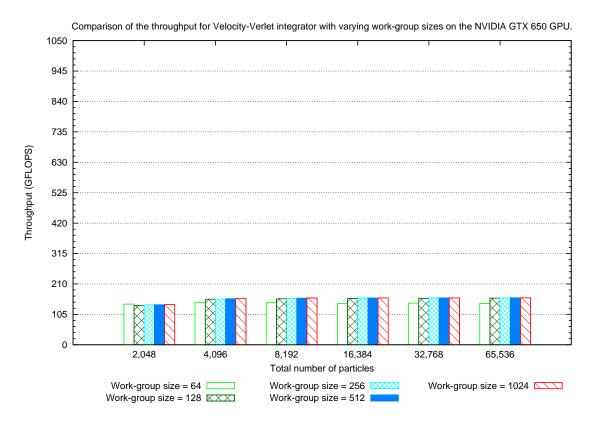

|      | Results showing the throughput performance of $Velvet-d$ as work-group size varies on the NVIDIA GTX 650 GPU.                                                                                                                                                                                          | 139 |

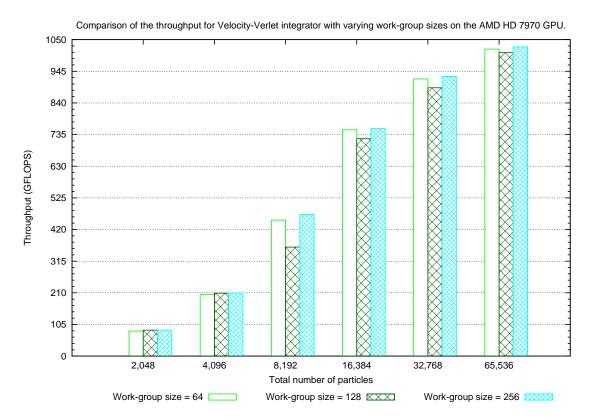

|      | Results showing the throughput performance of Velvet-d as work-group size varies on the AMD HD 7970 GPU                                                                                                                                                                                                | 140 |

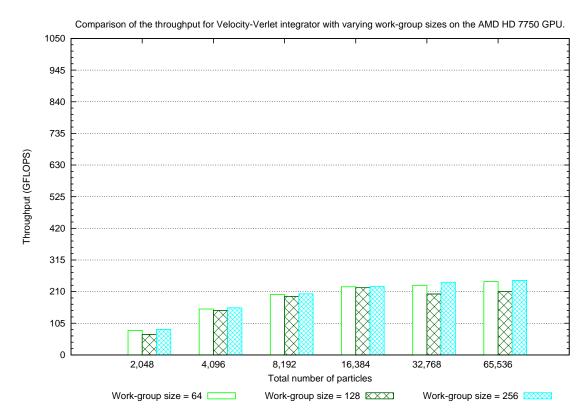

|      | Results showing the throughput performance of Velvet-d as work-group size varies on the AMD HD 7750 GPU                                                                                                                                                                                                | 141 |

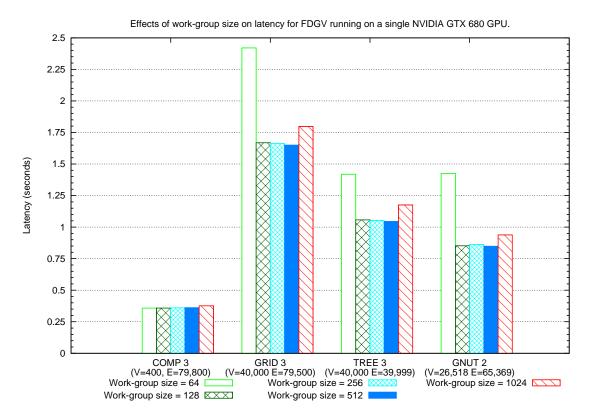

|      | Results showing latency performance FDGV-d as work-group size varies for NVIDIA GTX 680 GPU                                                                                                                                                                                                            | 141 |

| 6.37 | Results showing latency performance FDGV- $d$ as work-group size varies for NVIDIA GTX 650 GPU                                                                                                                                                                                                         | 142 |

List of Figures xi

| 6.38 | Results showing latency performance FDGV- $d$ as work-group size varies for AMD HD 7970 GPU.                                                                                                                   | . 142 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 6.39 | Results showing latency performance FDGV- $d$ as work-group size varies for AMD HD 7750 GPU.                                                                                                                   | . 143 |

| 6.40 | Results showing throughput performance FDGV- $d$ as work-group size varies for NVIDIA GTX 680 GPU.                                                                                                             |       |

| 6.41 | Results showing throughput performance FDGV- $d$ as work-group size varies for NVIDIA GTX 650 GPU.                                                                                                             |       |

| 6.42 | Results showing throughput performance FDGV- $d$ as work-group size varies for AMD HD 7970 GPU.                                                                                                                |       |

| 6.43 | Results showing throughput performance FDGV-d as work-group size varies for AMD HD 7750 GPU.                                                                                                                   |       |

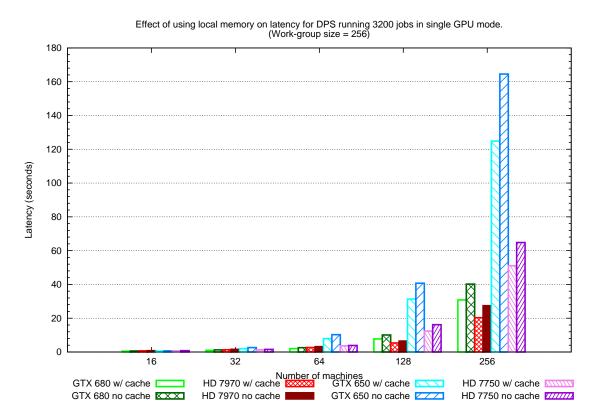

| 6.44 | Comparison of latency for $1,600$ jobs with and without using GPU local                                                                                                                                        |       |

| 6.45 | memory                                                                                                                                                                                                         |       |

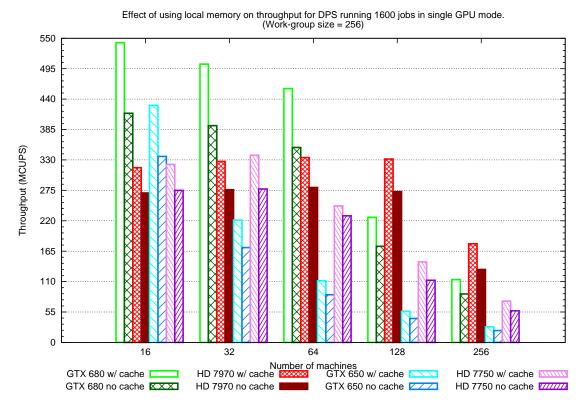

| 6.46 | memory.  Comparison of throughput for 1,600 jobs with and without using GPU                                                                                                                                    | . 140 |

|      | local memory. Throughput is measured in millions of cell updates per second (MCUPS)                                                                                                                            | . 146 |

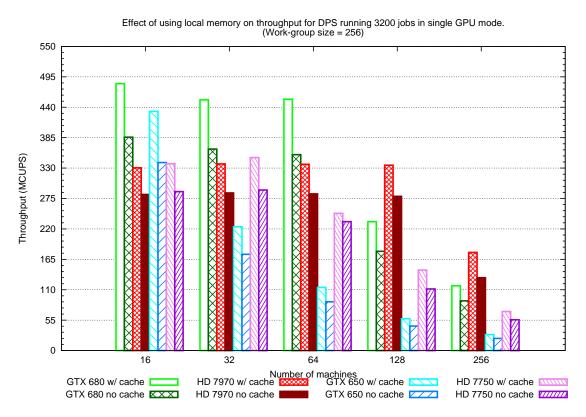

| 6.47 | Comparison of throughput for 3,200 jobs with and without using GPU local memory. Throughput is measured in millions of cell updates per                                                                        |       |

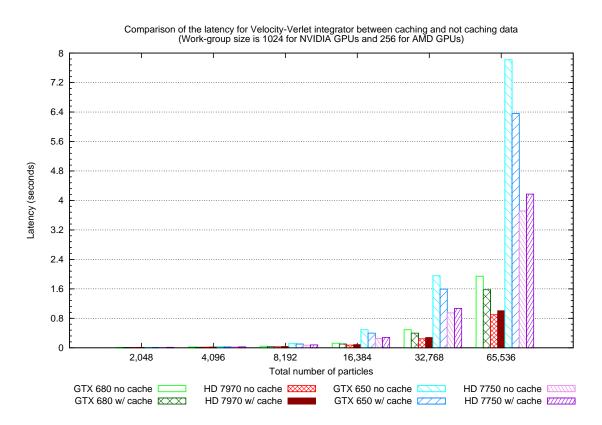

| 6.48 | second (MCUPS)                                                                                                                                                                                                 | . 147 |

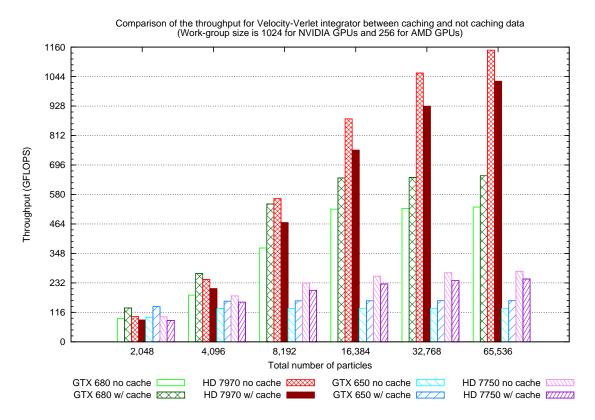

|      | $\tt Velvet-d$ for all GPU devices. The work-group sizes in these results are 1024 for NVIDIA GPUs and 256 for AMD GPUs.                                                                                       | . 148 |

| 6.49 | Results showing the effect of local memory on the throughput performance of Velvet-d for all GPU devices. The work-group sizes in these results are 1024 for NVIDIA GPUs and 256 for AMD GPUs. Throughput is   |       |

| 6.50 | measured in billions of floating-point operations per second                                                                                                                                                   | . 149 |

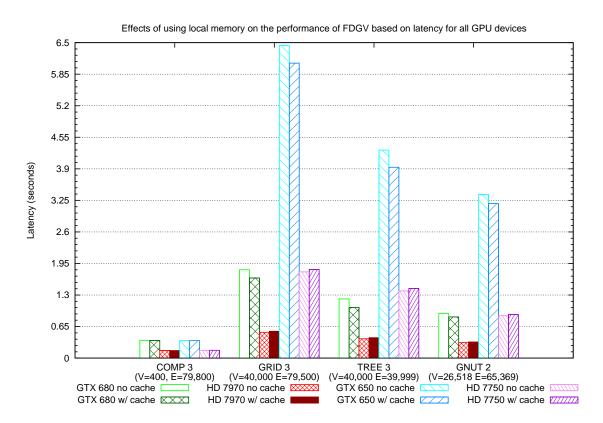

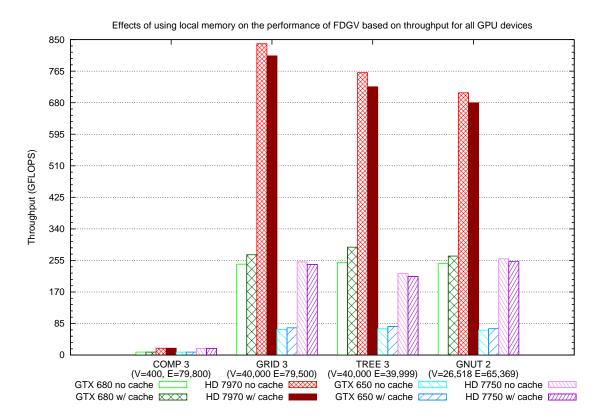

| 0.00 | FDGV-d for all GPU devices. The work-group sizes in these results are 512 for NVIDIA GPUs and 256 for AMD GPUs.                                                                                                | 150   |

| 6.51 | Results showing the effect of local memory on latency performance of FDGV-d for all GPU devices. The work-group sizes in these results are 512 for NVIDIA GPUs and 256 for AMD GPUs. Throughput is measured in | . 150 |

| 0.50 | billions of floating-point operations per second.                                                                                                                                                              | . 151 |

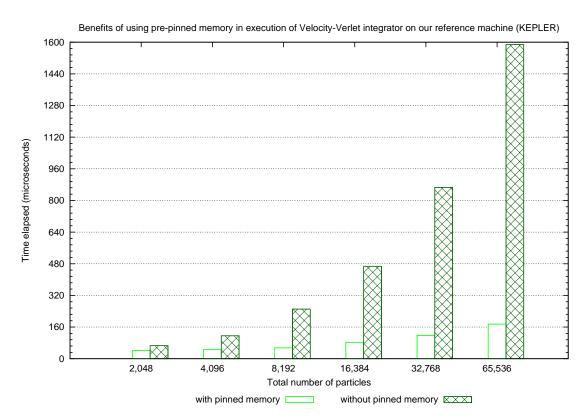

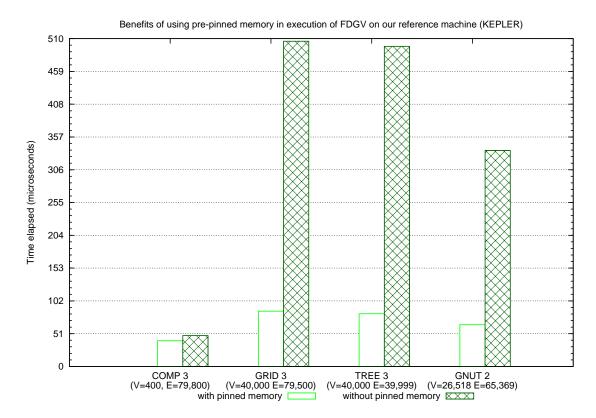

| 0.52 | Results showing the benefits of using pre-pinned memory for $\mathtt{Velvet}-d$ and $\mathtt{FDGV}-d$ running on our designated reference machine. Time elapsed is                                             | 150   |

| 6.53 | given in microseconds.  Results showing the benefits of using pre-pinned memory for Velvet-d and FDGV-d running on our designated reference machine. Time elapsed is                                           | . 152 |

| 6 53 | given in microseconds                                                                                                                                                                                          | . 153 |

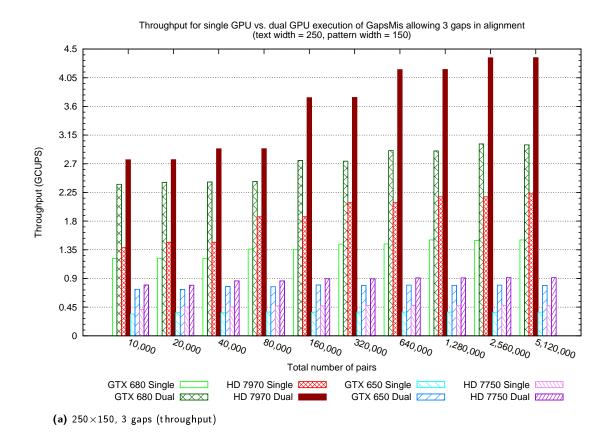

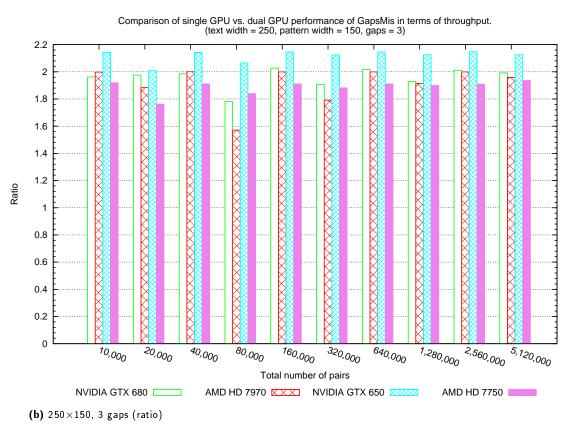

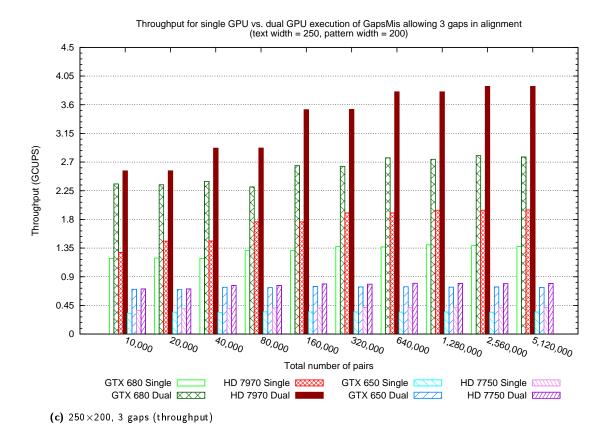

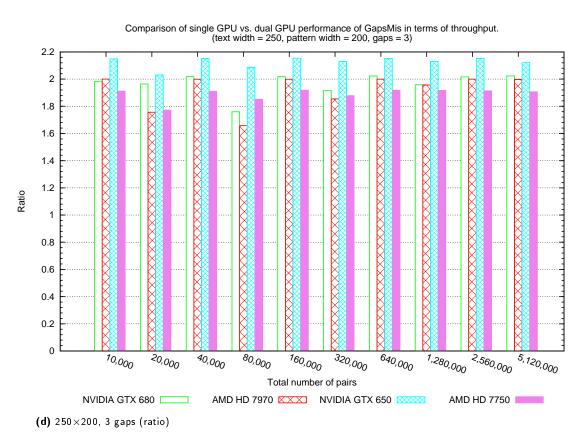

| 0.00 | device. Results shown here are for an alignment that allows 3 gaps. Throughput is measured in billions of cell updates per second (GCUPS)                                                                      | . 160 |

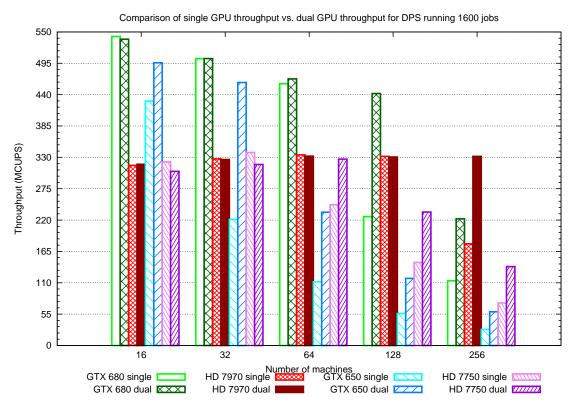

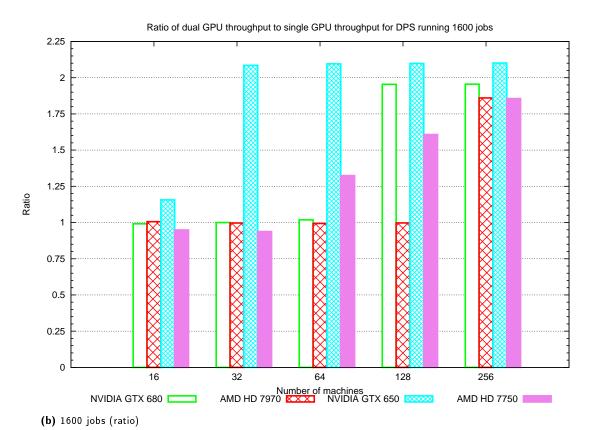

| 6.54 | Throughput performance comparison of how DPS- $d$ scales with the addition of a second GPU device for simulation with 1,600 jobs. The work-                                                                    | -     |

|      | group size used for these results is 256 for all GPU devices                                                                                                                                                   | . 161 |

List of Figures xii

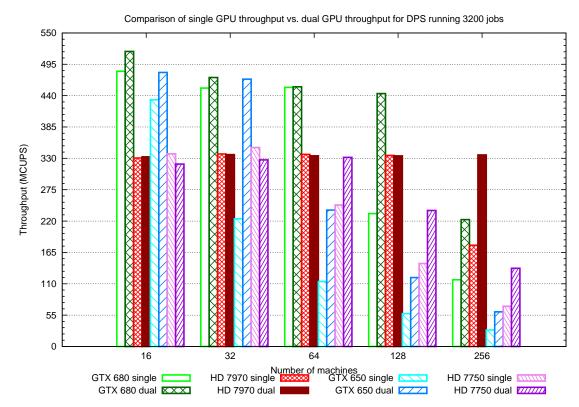

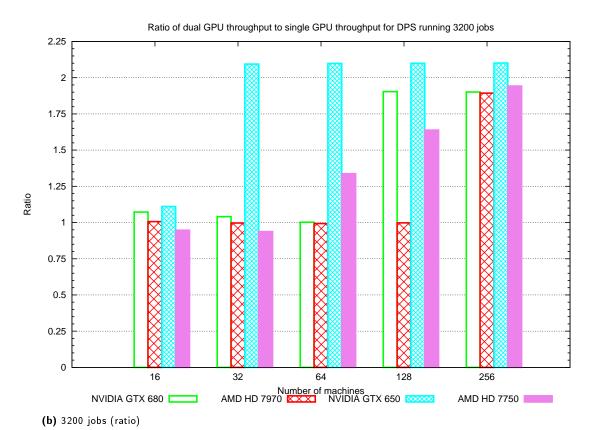

| 6.55 | Throughput performance comparison of how DPS-d scales with the addition of a second GPU device for simulation with 3,200 jobs. The workgroup size used for these results is 256 for all GPU devices.                                                                                           | . 162 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

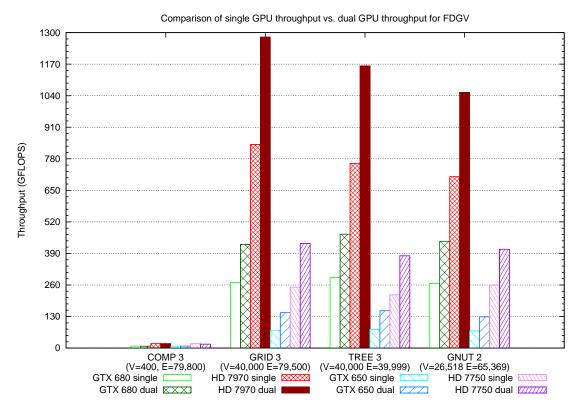

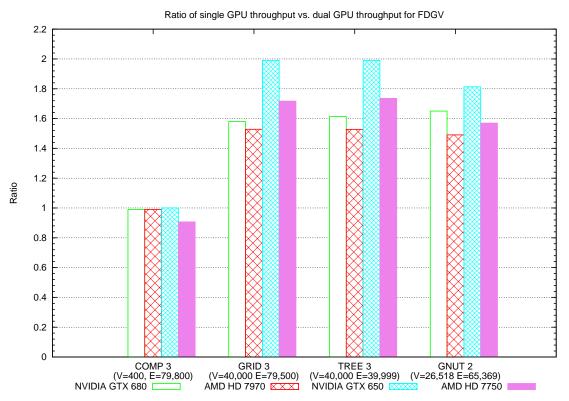

| 6.56 | Comparison of how FDGV- $d$ scales with the addition of a second GPU device. The results for NVIDIA GPUs are obtained using a work-group size of 512 and using local memory. The AMD GPUs use a work-group size of 256 and without using local memory. Throughput is measured in               |       |

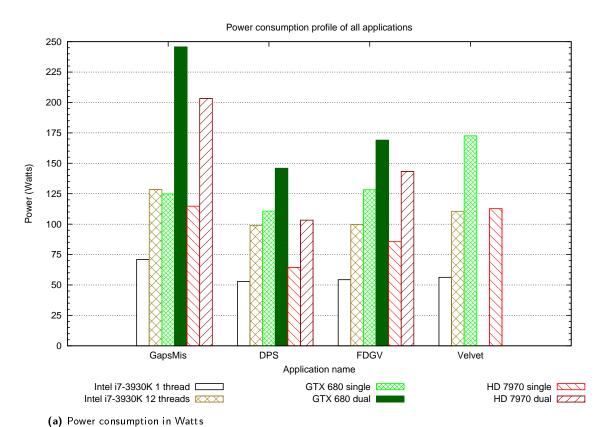

| 6.57 | billions of floating-point operations per second.  Results of power consumption profiling for each application on each device configuration.                                                                                                                                                   |       |

| 6.58 | Latency performance of GapsMis-s vs GapsMis-d on single GPU for a 3-gap alignment. The length of target sequences is 250 and 200 for query sequences.                                                                                                                                          |       |

| 6.59 | Latency performance of $\mathtt{GapsMis-}t$ with 12 CPU threads vs $\mathtt{GapsMis-}d$ on dual GPUs for a 3-gap alignment. The length of target sequences is 250 and 200 for query sequences.                                                                                                 | . 166 |

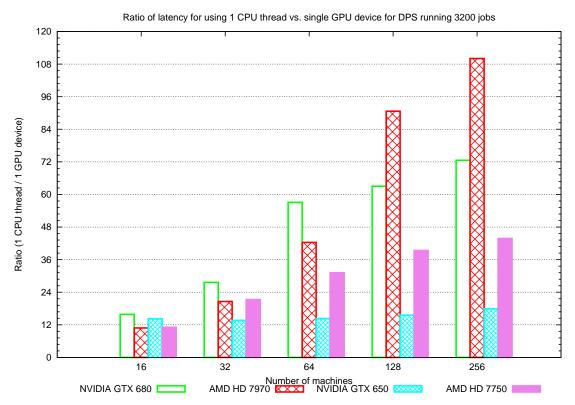

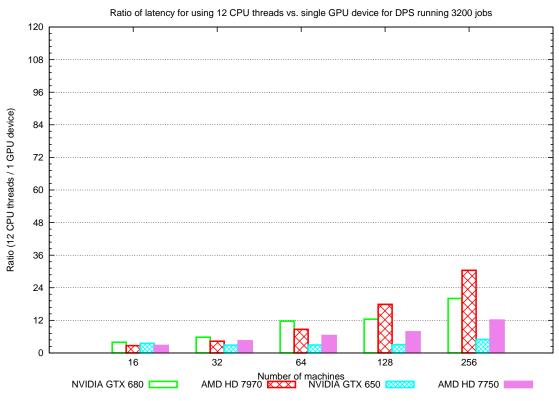

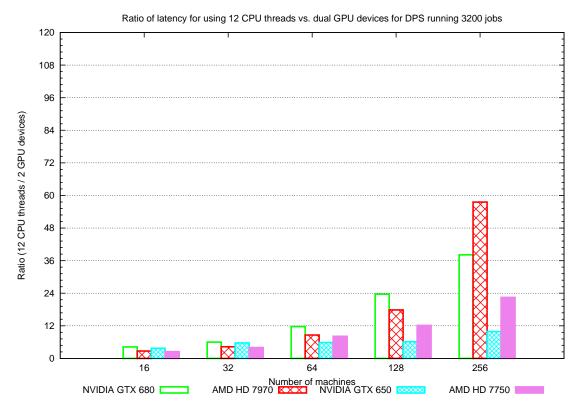

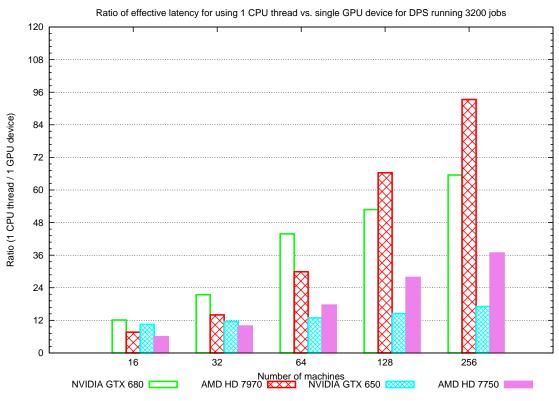

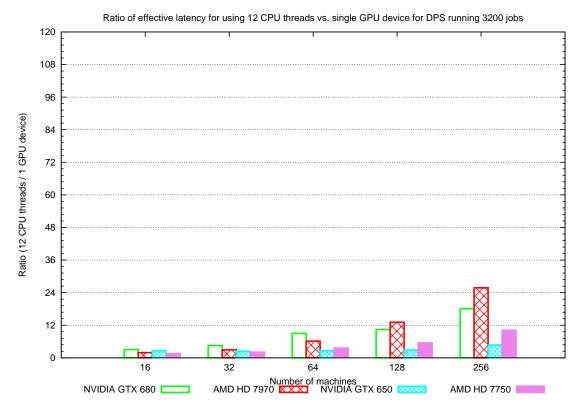

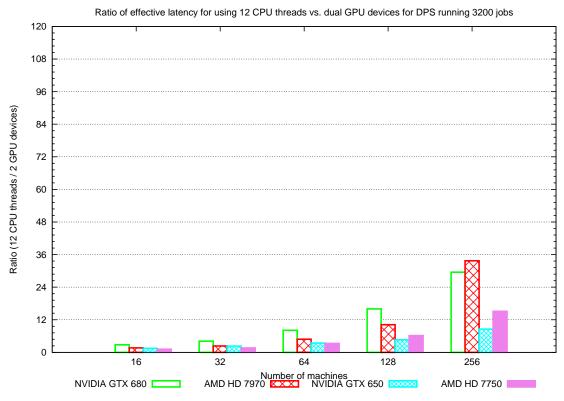

| 6.57 | Comparison of CPU vs GPU performance of DPS for a problem size consisting of 3200 jobs                                                                                                                                                                                                         | . 169 |

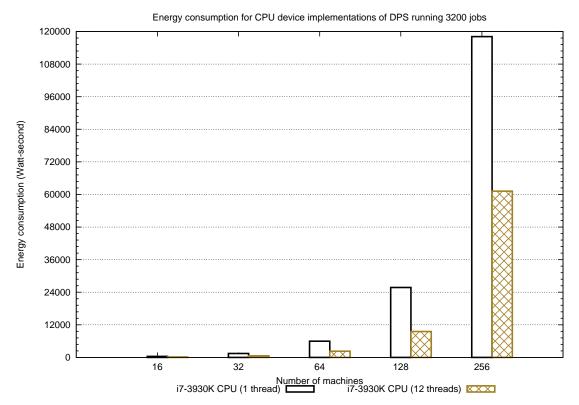

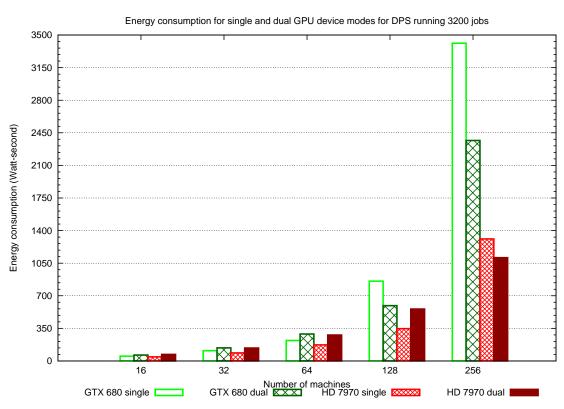

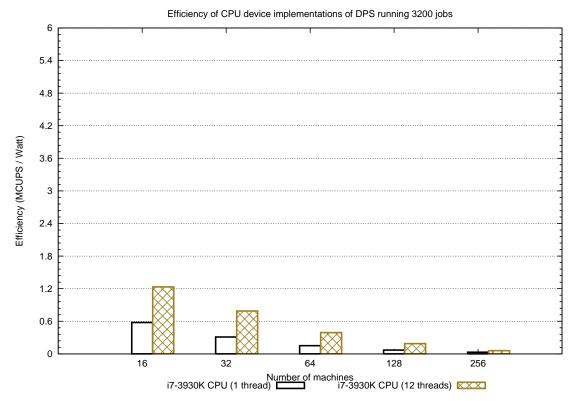

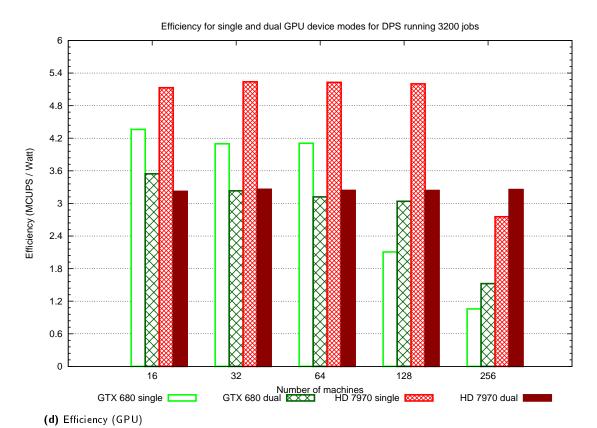

| 6.57 | Comparison of energy consumption and efficiency for CPU and GPU devices for DPS. Energy consumption is given in Watt-second while efficiency is given in millions of cell updates per second per Watt.                                                                                         | 171   |

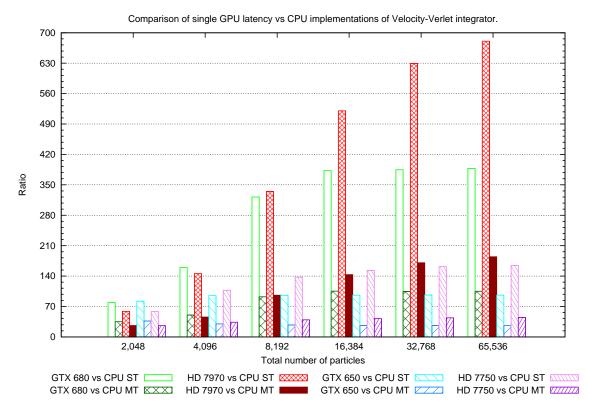

| 6.57 | (a) Ratio of CPU performance to single GPU performance with respect to latency. (b) Comparison of CPU vs.GPU in terms of efficiency measured in billions of floating-point operations per Watt.                                                                                                |       |

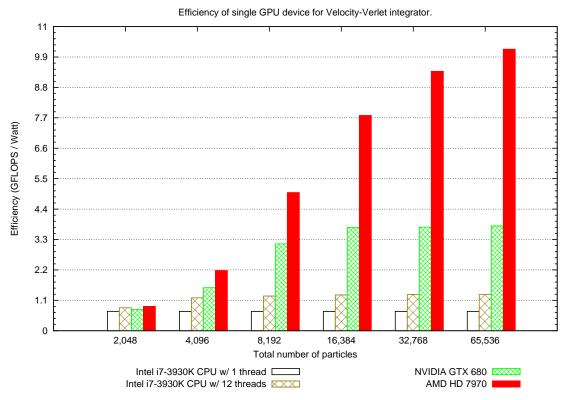

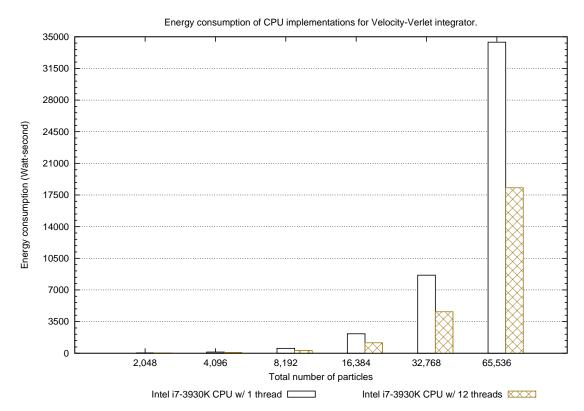

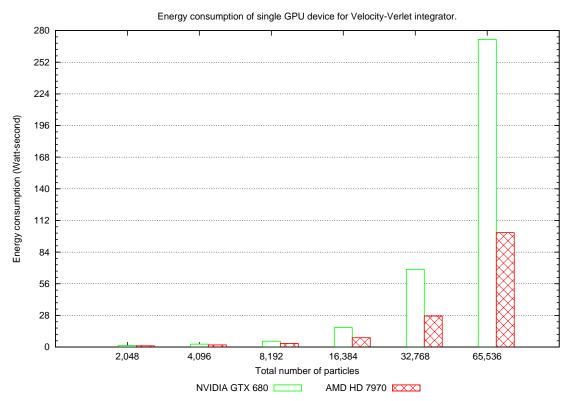

| 6.57 | Comparison of energy consumption for CPU and GPU devices for Velvet.<br>Energy consumption is measured in Watt-second                                                                                                                                                                          | . 173 |

| 6.57 | Comparison of CPU vs.GPU execution times for FDGV. The largest value for each graph is shown in the labels within the plot.                                                                                                                                                                    |       |

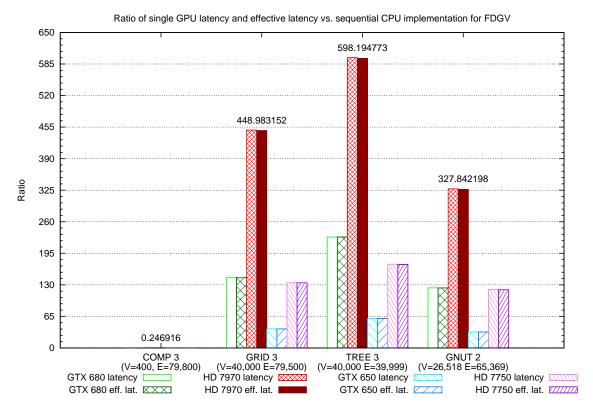

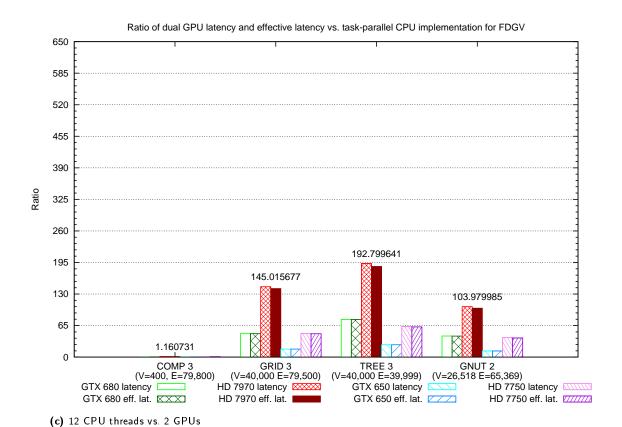

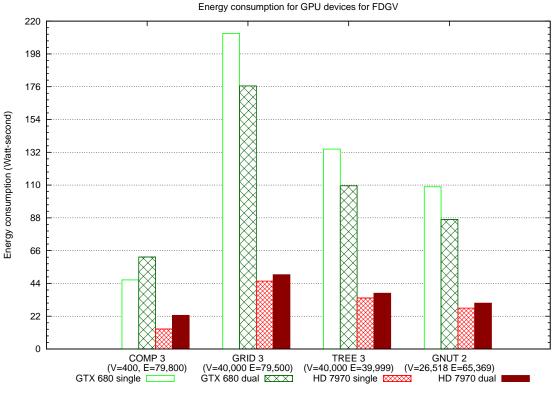

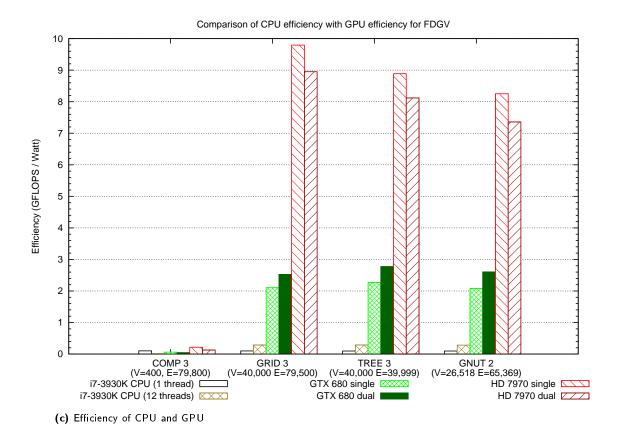

| 6.57 | Comparison of CPU vs.GPU energy consumption and efficiency for FDGV. Energy consumption is measured in Watt-second and efficiency is measured in GFLOPS/Watt.                                                                                                                                  |       |

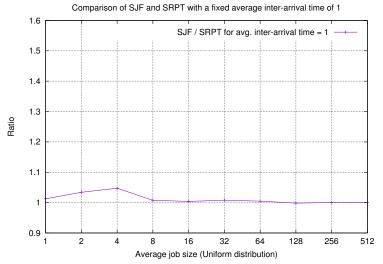

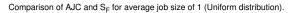

| A.0  | Comparison of the performance ratio based on total flow time plus energy of AJC when using SJF vs. SRPT on a single processor. Inter-arrival times are given by Poisson distribution and job sizes are given by uniform distribution.                                                          | 189   |

| A.0  | Comparison of the performance ratio based on total flow time plus energy of AJC when using SJF vs. SRPT on a single processor. Uniform                                                                                                                                                         |       |

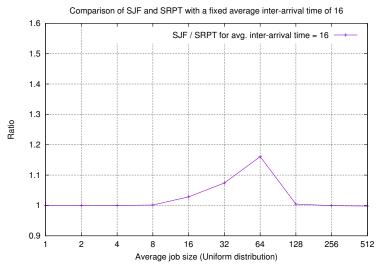

| A.0  | distribution is used for both inter-arrival times and job sizes Comparison of the performance ratio based on total flow time plus energy of AJC when using SJF vs. SRPT on a single processor. Uniform distribution is used for job sizes while Poisson distribution is used for inter-arrival | . 104 |

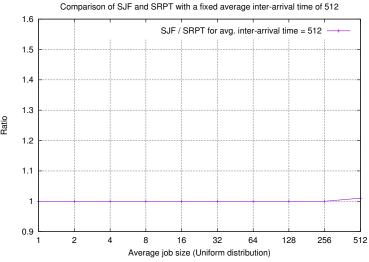

| A.0  | times.  Comparison of the performance ratio based on total flow time plus energy for AJC when using SJF vs. SRPT on 4 processors. Poisson distribution is used for the inter-arrival times while uniform distribution is used for                                                              | . 186 |

|      | the jobs sizes                                                                                                                                                                                                                                                                                 | . 189 |

List of Figures xiii

| A.0  | Comparison of the performance ratio based on total flow time plus energy for AJC when using SJF vs. SRPT on 4 processors. Uniform distribution is used for both the inter-arrival times and jobs sizes.                                                                                                               | . 191 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| A.0  | Comparison of the performance ratio based on total flow time plus energy for AJC when using SJF vs. SRPT on 4 processors. Uniform distribution is used for the inter-arrival times and Poisson distribution is used for jobs                                                                                          |       |

| A.0  | Effectiveness of speed scaling: Comparison of the performance ratio based on total flow time plus energy between AJC and a fixed speed heuristic that uses a fixed speed of 1 on a single processor. Poisson distribution is                                                                                          | . 193 |

| A.0  | used for inter-arrival times and uniform distribution is used for job sizes.<br>Effectiveness of speed scaling: Comparison of the performance ratio based on total flow time plus energy between AJC and a fixed speed heuristic that uses a fixed speed of 1 on a single processor. Uniform distribution is          | . 196 |

| A.0  | used for both inter-arrival times and job sizes.  Effectiveness of speed scaling: Comparison of the performance ratio based on total flow time plus energy between AJC and a fixed speed heuristic                                                                                                                    | . 198 |

| A.0  | that uses a fixed speed of 1 on a single processor. Uniform distribution is used inter-arrival times and Poisson distribution is used for job sizes Speed scaling vs. semi-clairvoyant fixed speed function: Comparison of the performance ratio based on total flow time plus energy between AJC and a               | . 200 |

|      | fixed speed function that has some information about the job set. Poisson distribution is used for inter-arrival times and uniform distribution is used for job sizes.                                                                                                                                                | . 203 |

| A.0  | Speed scaling vs. semi-clairvoyant fixed speed function: Comparison of the performance ratio based on total flow time plus energy between AJC and a fixed speed function that has some information about the job set. Uniform distribution is used for both inter-arrival times and job sizes.                        | . 205 |

| A.0  | Speed scaling vs. semi-clairvoyant fixed speed function: Comparison of the performance ratio based on total flow time plus energy between AJC and a fixed speed function that has some information about the job set. Uniform                                                                                         |       |

| A.0  | distribution is used for inter-arrival times and Poisson distribution is used for job sizes.  Effectiveness of AJC speed spectrum: Comparison of AJC to a fixed speed                                                                                                                                                 | . 207 |

| 11.0 | function that uses, as fixed speed values, the average and maximum speeds obtained from a prior AJC run. Results show the performance ratio of the total flow time plus energy of fixed speed functions vs. AJC. Poisson distribution is used for inter-arrival times and uniform distribution is used for job sizes. | 210   |

| A.0  | Effectiveness of AJC speed spectrum: Comparison of AJC to a fixed speed function that uses, as fixed speed values, the average and maximum speeds obtained from a prior AJC run. Results show the performance ratio of the total flow time plus energy of fixed speed functions vs. AJC. Uniform                      | . 210 |

|      | distribution is used for both inter-arrival times and job sizes.                                                                                                                                                                                                                                                      | 212   |

List of Figures xiv

| A.0  | Effectiveness of AJC speed spectrum: Comparison of AJC to a fixed speed         |     |

|------|---------------------------------------------------------------------------------|-----|

|      | function that uses, as fixed speed values, the average and maximum speeds       |     |

|      | obtained from a prior AJC run. Results show the performance ratio of            |     |

|      | the total flow time plus energy of fixed speed functions vs. AJC. Uniform       |     |

|      | distribution is used for inter-arrival times and Poisson distribution is used   |     |

|      | for job sizes                                                                   | 214 |

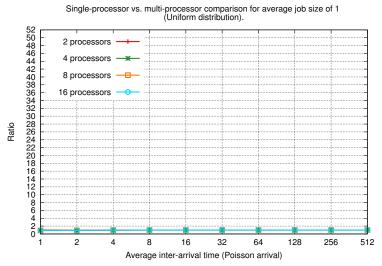

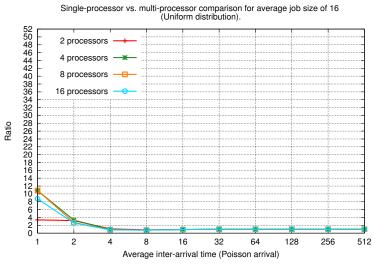

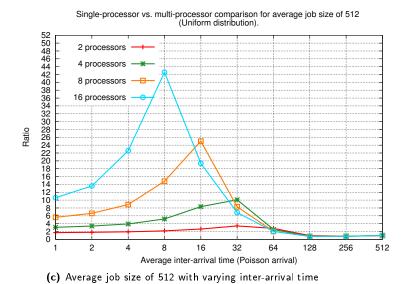

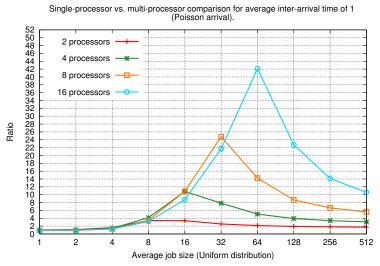

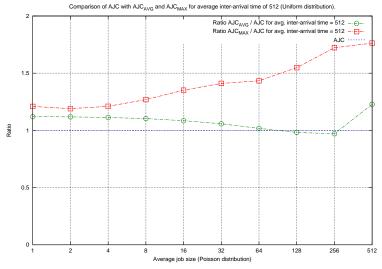

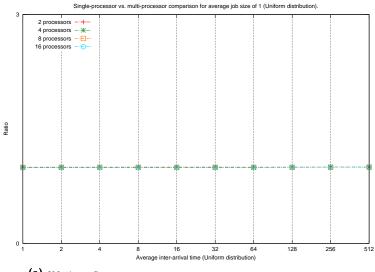

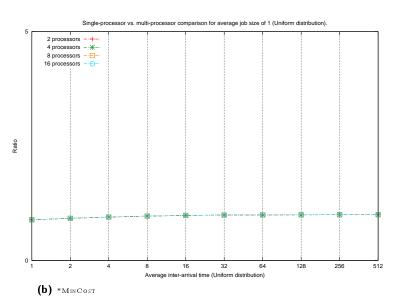

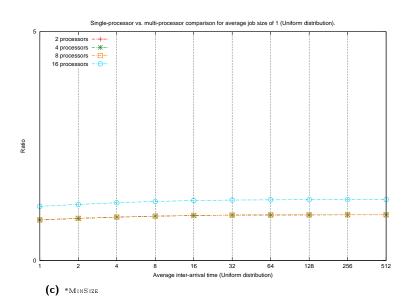

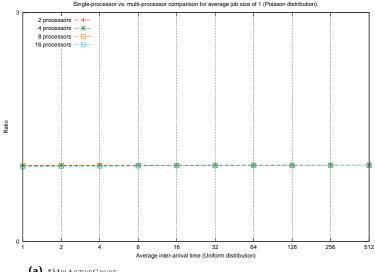

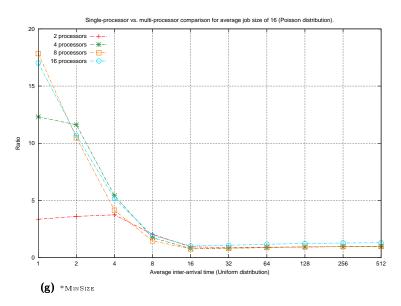

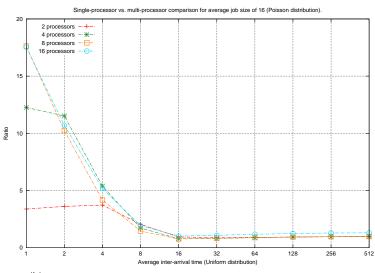

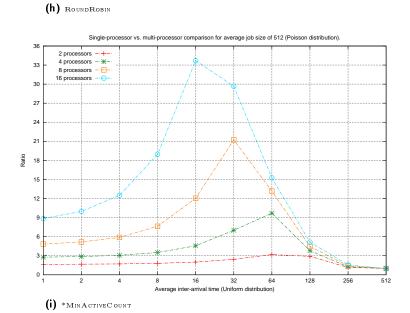

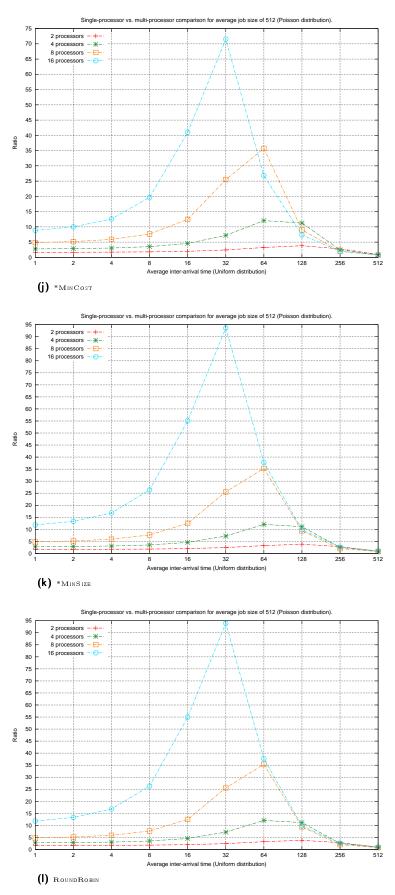

| A2   | Results on processor allocation strategies in terms of average job size: Fig-   |     |

|      | ures A.1(a) to A.1(d) show the performance ratios for average job size of       |     |

|      | 1. Results for average sizes of 16 and 512 are shown in Figures A.0(g),         |     |

|      | A.0(h), A.1(e) and A.1(f) and Figures A1(j) to A1(l) and A.0(i) re-             |     |

|      | spectively. Results measure the performance ratio of total flow time plus       |     |

|      | energy for a single processor vs. multiple processors. Poisson distribution     |     |

|      | is used for inter-arrival times and uniform distribution is used for job sizes  | 219 |

| A4   | Results on processor allocation strategies in terms of average job size: Fig-   |     |

|      | ures A1(a) to A1(d) show the performance ratios for average job size            |     |

|      | of 1. Results for average sizes of 16 and 512 are shown in Figures A2(g),       |     |

|      | A2(h), A1(e) and A1(f) and Figures A3(j) to A3(l) and A2(i) re-                 |     |

|      | spectively. Results measure the performance ratio of total flow time plus       |     |

|      | energy for a single processor vs. multiple processors. Uniform distribution     |     |

|      | is used for both inter-arrival times and job sizes.                             | 223 |

| Α _6 | Results on processor allocation strategies in terms of average job size: Fig-   |     |

| 110  | ures A3(a) to A3(d) show the performance ratios for average job size            |     |

|      | of 1. Results for average sizes of 16 and 512 are shown in Figures A4(g),       |     |

|      | A4(h), A3(e) and A3(f) and Figures A5(j) to A5(l) and A4(i) re-                 |     |

|      | spectively. Results measure the performance ratio of total flow time plus       |     |

|      | energy for a single processor vs. multiple processors. Uniform distribution     |     |

|      | is used for inter-arrival times and Poisson distribution is used for job sizes. | 227 |

|      | is used for inter-affival times and roisson distribution is used for Job Sizes. | 441 |

## List of Tables

| 3.1 | Lookup tables showing processing and communication costs with respect        |     |

|-----|------------------------------------------------------------------------------|-----|

|     | to time and energy.                                                          | 31  |

| 3.2 | Dynamic programming table for job $J_1$ in the problem described in Ex-      |     |

|     | ample 3.1                                                                    | 32  |

| 3.3 | Solution for the dynamic programming table for the problem described in      |     |

|     | Example 3.1.                                                                 | 33  |

| 3.4 | Solution for the dynamic programming table for the problem described in      |     |

|     | Example 3.1 without the redundant values                                     | 33  |

| 4.1 | Summary of the best performance ratios for all processor allocation strate-  |     |

| 1.1 | gies.                                                                        | 58  |

|     |                                                                              | , , |

| 6.1 | Table listing hardware specifications of all host systems used in the exper- |     |

|     | iments                                                                       | 11  |

| 6.2 | Intervals used in data generation for DPS. These intervals are inclusive in  |     |

|     | the resulting data                                                           | 12  |

| 6.3 | Information for GenBank databases used to generate input sequences for       |     |

|     | GapsMis                                                                      | 14  |

| 6.4 | Details of the real graph data obtained from SNAP                            | 14  |

| 6.5 | Details of the synthetic graph data generated for FDGV application 1         | 15  |

Dedicated to my family, for providing me with the means to pursue my dreams. And to my supervisor, Dr. Prudence Wong, for making those dreams a reality.

## Chapter 1

## Introduction

#### 1.1 Overview

The study of scheduling dates back as far as the 1950s when researchers in operations research, industrial engineering and management were faced with the problem of managing various activities occurring in a workshop [64]. An organization can lower production costs in its manufacturing processes thereby enabling it to stay competitive. Later on in the 1960s computer scientists also encountered scheduling problems during the development of operating systems. During this time period computer resources such as CPU, memory and I/O devices were considerably scarce so it was crucial that they had to be efficiently utilized in order to minimize the cost of running these computer systems. Therefore an economic reason to study scheduling was established and eventually various classes of scheduling problems have been developed to take into account the different scenarios they aim to address. Even in present times, new scheduling problems arise from various sources such as the introduction of a new technology in various fields like systems design, automated industrial processes and so on.

Advances in the technology of microprocessor development and chip fabrication process means that the density of transistors that make up these chips continue to grow. In addition, the computational power and processing capability of these chips somewhat doubled with each new design as manufacturers are able to ramp up the clock speeds with the introduction of subsequent generations of microprocessors. Consequently, operating at high clock speeds usually comes at the expense of incurring exponential increase in power consumption and in order to mitigate this issue, manufacturers resorted to shrinking chip sizes but this process has been restricted by available technology. As a result, the growth in clock speeds began to slow down [103] and the gains in the performance levels of these chips began to diminish. Chip manufacturers pursued other

means of achieving higher performance and this brought about the advent of multi-core technology and mainstream parallel computation. Multi-core processor technology was particularly attractive and promising especially because manufacturers were able to more than double performance without necessarily increasing the operating frequency by simply adding more processing cores. This means that devices are able to do more as more processing power became readily available and this lead to an age of ubiquitous computing as these chips powered almost everything ranging from small devices such as mobile phones and tablets to our home computers to enterprise server systems and super-computers. However, the problem of energy consumption soon re-surfaced and it became highly imperative that system designers and developers tackle the issue for both technical and economic reasons in order to prolong the sustainability of multi-core and parallel systems.

On the economic side, apart from the costs of powering these computer systems, extra costs are incurred as a result of cooling systems required to keep them within their optimal operating conditions. Since significant amount of the energy drawn by these systems is dissipated as heat, the life span of a system can be greatly shortened due to the adverse effects of high temperatures such as degraded transistor performance and damage to components like soldering which can cause permanent damages. Therefore, the problem of managing energy has become a critical topic in both industrial and academic research and various approaches have been considered leading to innovations in algorithm designs, software and hardware. Among the several approaches of managing energy consumption, a growing trend is the adoption of heterogeneous computing to deliver high performance. This is evident from the recent rankings of the 500 most powerful and energy-efficient supercomputers where the 17 most energy-efficient supercomputers [38] as well as the most powerful supercomputer [106] are heterogeneous systems utilizing graphics processing units (GPU) and other co-processors.

The development of heterogeneous and parallel systems offer exciting prospects in the quest to find a balance between energy consumption and performance of computer systems. The GPU has shot to the forefront as most used co-processor in heterogeneous systems quite simply because it was already part of existing systems where it is used for visual and rendering tasks making its adoption very easy. As a part of this thesis, we will present a detailed study to demonstrate the benefits of a heterogeneous system that includes the GPU with respect to saving energy while achieving high computational performance.

This chapter is organized as follows; in Section 1.2, we discuss some of the basic concepts related to scheduling problems. The problems we studied along with related works are

introduced in Section 1.3. Finally, in Section 1.4, we outline the contribution of the thesis.

#### 1.2 Background on Scheduling

Scheduling can be generally considered as dealing with allocation concerns involving scarce resources and tasks or operations that demand them with the goal of optimizing one or more performance measures of interest in a given setting. These resources could refer to a number of entities depending on the situation being considered. These may include cores in a multi-core CPU, CPUs in a multiprocessor system, servers in a server farm or cluster, memory, I/O devices, machines in an assembly line, airport runways, train stations, personnel assignment in workplaces, just to mention a few. Operations, on the other hand, may also refer to train calls at stations, airport landing and take-offs, an operation in a manufacturing process, execution of a computer program, manning workstations in an industrial setting or call centres.

#### 1.2.1 Inputs and outputs

The inputs in a scheduling problem includes a set consisting of a number of jobs to be executed on a set consisting of a number of machines and each job or machine can be uniquely referenced by a subscript. The time at which a job becomes available for processing is known as the release or arrival time. The time it takes for a job j to completely execute on a machine i is known as its processing time, and this value is assumed to be finite and non-negative unless explicitly stated. The point in time at which job j finishes its execution is known as its completion time. In some cases a job is required to finish execution at a particular time or deadline, however, a job might finish at a time greater than the time specified as its deadline. The term tardiness measures how late a job completes past its deadline and is expressed as  $\max\{completion\ time - deadline,\ 0\}$ , while earliness, expressed as  $\max\{deadline - completion\ time,\ 0\}$ , measures how much a job completes before its deadline. Hence, when a job completes before its deadline its tardiness is 0, and when a job completes after its deadline then its earliness is 0.

In order to represent each scheduling problem in a concise way including the inputs, constraints and objective function(s), I would like to mention the well-known three-field  $\alpha |\beta| \gamma$  notation first introduced by Graham et al. [35]. However, we will be describing the notation that was later introduced to incorporate machine availability constraints [95].

#### 1.2.2 The $\alpha |\beta| \gamma$ scheduling notation

The first field  $\alpha = \alpha_1 \alpha_2 \alpha_3$  in the notation describes the machine environment in a problem setting. Parameter  $\alpha_1 \in \{\emptyset, P, Q, R, F, J, O\}$  is used to characterize the machines in single machine, identical, uniform and unrelated parallel machines, flow shop, job shop and open shop problem settings respectively. Parameter  $\alpha_2 \epsilon \{\emptyset, m\}$ , where m is a positive integer, indicates that the number of machines in a parallel machine environment or number of stages for dedicated machines is assumed to be the variable m. Parameter  $\alpha_3 \in \{\emptyset, h_{i,k}\}\$  describes unavailability intervals which occur on the machines otherwise referred to as holes. In this notation  $\alpha = \emptyset$  represents a problem setting with no holes and  $h_{i,k}$  specifies the number of holes and the machine(s) on which they occur. However  $\alpha = h_{i,k}$  represents a problem setting with an arbitrary number of holes on each machine. If i is replaced by a positive integer it means that holes only occur on machine  $M_i$ otherwise holes will occur on all machines but if k is replaced by a positive integer it denotes the number of holes occurring on the corresponding machine. For instance,  $\alpha = h_{1,k}$  denotes a problem with an arbitrary number of holes on  $M_1$  only;  $\alpha = h_{i,1}$ represents a problem with one hole on each machine while  $\alpha = h_{1,1}$  represents a problem with one hole on machine  $M_1$  only.

The second field  $\beta=\beta_1,...,\beta_5$  describes characteristics or constraints associated with operations (jobs) and resources. Parameter  $\beta_1 \in \{\emptyset, t-pmtn, pmtn\}$  denotes the kind of preemption constraint in place which is either non-preemption, operation preemption or arbitrary preemption respectively. An operation is said to be preempted if its processing on a particular machine is interrupted at any time and resumed later at any time and restarted at no cost. It must either remain on the same machine until it can be continued later (operation preemption) or it can be shifted to another machine (arbitrary preemption). However, there are several studies that use  $\beta_1 = r - a$ ,  $\beta_1 = nr - a$  and  $\beta_1 = sr - a$ to represent resumable, non-resumable and semi-resumable availability constraints respectively [68]. In the resumable case preemption is allowed so if an operation cannot be completed before the unavailability period of a machine it can resume later when the machine becomes available again. The non-resumable case does not allow preemption so the disrupted operation has to completely restart instead of continue. However, in the semi-resumable case, operations can only be restarted partially after the machine becomes available again. Parameter  $\beta_2 \epsilon \{\emptyset, r_i\}$  indicates release time for operations (jobs), which can either be zero or differ respectively. Parameter  $\beta_3 \epsilon \{\emptyset, d_i\}$  denotes deadline constraints on the job set where  $\beta_3 = \emptyset$  indicates no assumed deadlines, however, due dates may be defined if necessary. On the other hand,  $\beta_3 = d_j$  indicates a deadline constraint imposed in the job set. Parameter  $\beta_4 \epsilon \{\emptyset, q_j\}$  indicates the absence or presence of tails in the jobs while  $\beta_5 \epsilon \{\emptyset, online\}$  represents an offline or online problem. A

problem is said to be offline if we have full knowledge regarding job data before building a schedule or online if a scheduling decision is required once a job arrives without any information about jobs that are yet to arrive in the future [68]. The  $\beta$  field can also be left blank to denote no constraints on the job set and that all the jobs are available before the construction of the schedule begins.

The third field  $\gamma$  represents the performance measure or objective function to be optimized. Some of the commonly studied objective functions include maximum completion time of all jobs or  $makespan\ (C_{max})$ , minimum completion time  $(C_{min})$ , maximum lateness  $(L_{max})$ , maximum tardiness  $(T_{max})$ , total completion time  $(\sum C_i)$ , total weighted completion time  $(\sum w_i C_i)$ , number of tardy jobs  $(\sum U_i)$  and weighted number of tardy jobs  $(\sum w_i U_i)$ .

#### 1.2.3 Classes of scheduling problems

#### Single machine problems.

The single machine problem simply involves scheduling a set of jobs on one machine only which can either be assumed to be continuously available throughout the processing period of the job set or have periods of unavailability or holes. It is the simplest form of the scheduling problems.

#### Parallel machine problems.