This copy of the thesis has been supplied on condition that anyone who consults it is understood to recognise that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the author's prior consent. Unless otherwise specified, all content in this thesis, including images, are the copyright of the author.

# PLUGGABLE OPTICAL CONNECTOR INTERFACES FOR ELECTRO-OPTICAL CIRCUIT BOARDS

by

#### **RICHARD CHARLES ALEXANDER PITWON**

A thesis submitted to Plymouth University

in partial fulfilment for the degree of

#### DOCTOR OF PHILOSOPHY

Faculty of Science and Technology

September 2016

### **ACKNOWLEDGEMENTS**

I would like to sincerely thank Dr Jasper Graham-Jones and Dr John Summerscales for their incredible support and guidance throughout the period of my PhD.

I would like to thank my colleague and friend Dr Kai Wang, as well as Dr David Selviah and Dr Ioannis Papakonstantinou from University College London, with whom I started this journey a long time ago and have collaborated extensively over the years.

I would also like to acknowledge my collaborating partners on the European projects SEPIANet, PhoxTrot and Nephele, whose collective expertise in these areas has deeply enriched my study and complemented my research activities. It has been a great privilege to know them and learn from them.

Finally my deepest and most heartfelt thanks go to my partner Anna for her unceasing support, encouragement and patience over the years, without which this work would not have been possible.

I dedicate this work faithfully to my mother.

## **AUTHOR'S DECLARATION**

At no time during the registration for the degree of Doctor of Philosophy has the author been registered for any other University award without prior agreement of the Graduate Sub-Committee.

Work submitted for this research degree at the Plymouth University has not formed part of any other degree either at Plymouth University or at another establishment.

This study was financed with the aid of a studentship from Xyratex Technology Ltd and carried out in collaboration with Xyratex Technology Ltd.

A programme of advanced study was undertaken.

Relevant scientific seminars and conferences were regularly attended at which work was often presented; external institutions were visited for consultation purposes and several papers prepared for publication.

Word count of main body of thesis: 73,746

Signed .....

Date .....

## ABSTRACT

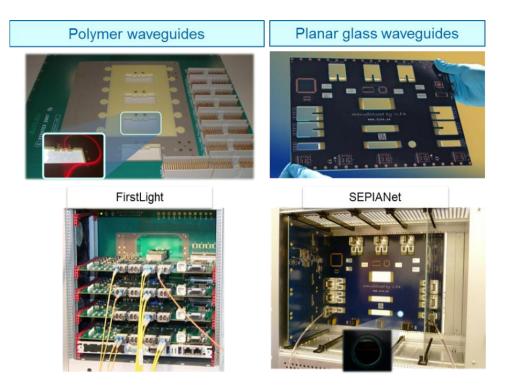

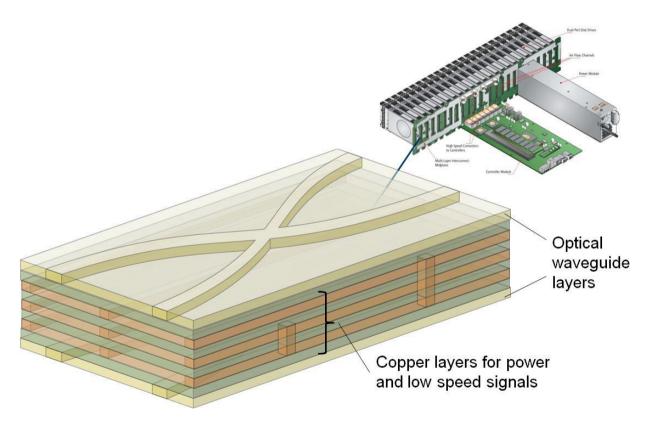

A study is hereby presented on system embedded photonic interconnect technologies, which would address the communications bottleneck in modern exascale data centre systems driven by exponentially rising consumption of digital information and the associated complexity of intra-data centre network management along with dwindling data storage capacities. It is proposed that this bottleneck be addressed by adopting within the system electro-optical printed circuit boards (OPCBs), on which conventional electrical layers provide power distribution and static or low speed signaling, but high speed signals are conveyed by optical channels on separate embedded optical layers. One crucial prerequisite towards adopting OPCBs in modern data storage and switch systems is a reliable method of optically connecting peripheral cards and devices within the system to an OPCB backplane or motherboard in a pluggable manner. However the large mechanical misalignment tolerances between connecting cards and devices inherent to such systems are contrasted by the small sizes of optical waveguides required to support optical communication at the speeds defined by prevailing communication protocols. An innovative approach is therefore required to decouple the contrasting mechanical tolerances in the electrical and optical domains in the system in order to enable reliable pluggable optical connectivity.

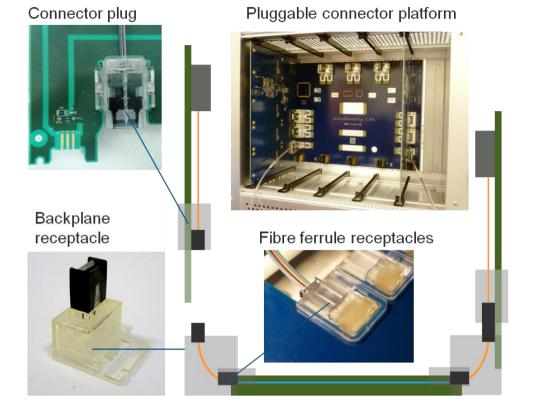

This thesis presents the design, development and characterisation of a suite of new optical waveguide connector interface solutions for electro-optical printed circuit boards (OPCBs) based on embedded planar polymer waveguides and planar glass waveguides. The technologies described include waveguide receptacles allowing parallel fibre connectors to be connected directly to OPCB embedded planar waveguides and board-to-board connectors with embedded parallel optical transceivers allowing daughtercards to be orthogonally connected to an OPCB backplane.

For OPCBs based on embedded planar polymer waveguides and embedded planar glass waveguides, a complete demonstration platform was designed and developed to evaluate the connector interfaces and the associated embedded optical interconnect.

Richard Pitwon Pluggable Optical Connector Interfaces for Electro-Optical Circuit Boards

Furthermore a large portfolio of intellectual property comprising 19 patents and patent applications was

generated during the course of this study, spanning the field of OPCBs, optical waveguides, optical connectors,

optical assembly and system embedded optical interconnects.

## LIST OF CONTENTS

| 1 | Intro           | luction                                                                                                                              | 1  |

|---|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1             | Background                                                                                                                           | 1  |

|   | 1.2             | Motivation and aim                                                                                                                   |    |

|   | 1.2.1           | Chapter 1: Introduction                                                                                                              | 4  |

|   | 1.2.2           | Chapter 2: System embedded optical interconnect technology survey                                                                    | 4  |

|   | 1.2.3<br>based  | Chapter 3: First generation pluggable active optical circuit board connector for polymer wa optical circuit boards                   |    |

|   | 1.2.4<br>wave   | Chapter 4: Second generation pluggable active optical circuit board connector for polymer guide based electro-optical circuit boards | 7  |

|   | 1.2.5<br>optica | Chapter 5: Pluggable passive optical circuit board connector for planar glass waveguide bas<br>al circuit boards                     |    |

|   | 1.2.6           | Chapter 6: Intellectual Property                                                                                                     | 10 |

|   | 1.2.7           | Chapter 7: Conclusion                                                                                                                | 10 |

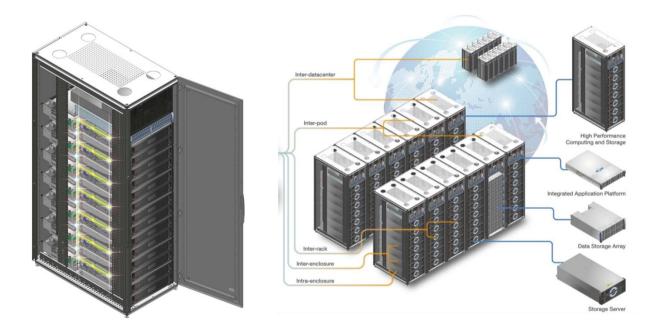

|   | 1.3             | Optical interconnect migration in data centres                                                                                       | 11 |

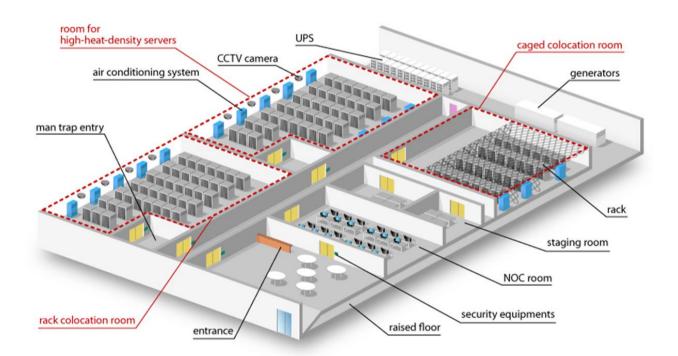

|   | 1.3.1           | Data centre overview                                                                                                                 | 12 |

|   | 1.3.2           | Data storage system interconnect topologies                                                                                          | 13 |

|   | 1.3.3           | Data centre switching architectures                                                                                                  | 14 |

|   | 1.3.4           | Resource disaggregation                                                                                                              | 17 |

|   | 1.3.5           | Optical interconnect migration                                                                                                       | 19 |

|   | 1.4             | Data centre network communication protocols                                                                                          | 20 |

|   | 1.4.1           | Serial Attached SCSI                                                                                                                 | 20 |

|   | 1.4.2           | Infiniband                                                                                                                           | 21 |

|   | 1.4.3           | PCI Express                                                                                                                          | 22 |

|   | 1.4.4           | Fibre Channel                                                                                                                        | 23 |

|   | 1.4.5           | Ethernet                                                                                                                             | 23 |

|   | 1.4.6           | Network Convergence                                                                                                                  | 25 |

|   | 1.5             | International research projects targeting system embedded optical data communications                                                | 26 |

|   | 1.5.1           | SEPIANet project                                                                                                                     | 26 |

|   | 1.5.2           | PhoxTroT project                                                                                                                     | 27 |

|   | 1.5.3           | Nephele project                                                                                                                      | 29 |

|   | 1.5.4           | HDPuG Optoelectronics project                                                                                                        |    |

|   | 1.6             | Summary                                                                                                                              | 31 |

| 2 | Syste           | m embedded optical interconnect technology survey                                                                                    | 32 |

|   | 2.1             | Introduction                                                                                                                         |    |

|   | 2.2             | System embedded optical interconnect technologies                                                                                    | 35 |

|   | 2.2.1           | Host side pluggable transceivers                                                                                                     | 35 |

|   | 2.2.2           | Passive optical connector interface                                                                                                  | 36 |

|   | 2.2.3           | Board-mountable optical transceivers                                                                                                 |    |

|   | 2.3             | Performance limiters on high frequency electronic channels                                                                           | 43 |

| 2.3.1  | Overview                                                                                                        | 43  |

|--------|-----------------------------------------------------------------------------------------------------------------|-----|

| 2.3.2  | Crosstalk                                                                                                       | 44  |

| 2.3.3  | Impedance mismatch                                                                                              | 45  |

| 2.3.4  | Signal attenuation                                                                                              | 46  |

| 2.4    | Board-level optical interconnect                                                                                | 47  |

| 2.4.2  | Milestones in polymer OPCB research and development                                                             | 52  |

| 2.5    | Design attributes of embedded optical channels                                                                  | 56  |

| 2.5.1  | Density comparison between printed copper and polymer waveguides                                                | 56  |

| 2.5.2  | Bend radius routing constrictions                                                                               | 60  |

| 2.5.3  | In-plane vs out-of-plane optical coupling to OPCBs                                                              | 62  |

| 2.6    | Summary                                                                                                         | 62  |

|        | eneration pluggable active optical circuit board connector for polymer waveguide based optical                  | 64  |

| 3.1    | Introduction                                                                                                    | 64  |

| 3.1.1  | Objective                                                                                                       | 65  |

| 3.1.2  | Methodology                                                                                                     | 65  |

| 3.2    | OPCB connectivity in data storage enclosures                                                                    | 67  |

| 3.2.1  | Electro-optical midplane architecture                                                                           | 67  |

| 3.2.2  | Midplane interconnect requirements                                                                              | 68  |

| 3.2.3  | Electro-optical PCB connection scheme                                                                           | 69  |

| 3.2.4  | Electro-optical PCB connection concept                                                                          | 70  |

| 3.3    | Electro-optical PCB demonstration platforms                                                                     | 72  |

| 3.4    | Storlite - first generation passive optical backplane system with active pluggable connectors                   | 73  |

| 3.4.1  | Storlite project summary                                                                                        | 73  |

| 3.4.2  | System design overview                                                                                          | 74  |

| 3.4.3  | StorConn2 - Storlite quad 10 Gb/s parallel optical transceiver                                                  | 75  |

| 3.4.4  | Storlite connector mechanism                                                                                    | 93  |

| 3.4.5  | StorConnOpt2 - Storlite optical waveguide backplane                                                             | 98  |

| 3.4.6  | Storlite optical waveguide receptacle                                                                           | 102 |

| 3.4.7  | Passive optical assembly process                                                                                | 104 |

| 3.4.8  | StorConnTest2 - Storlite 10 Gb/s test daughtercard                                                              | 116 |

| 3.4.9  | Storlite platform firmware design                                                                               | 125 |

| 3.4.10 | StorConnPwr2 – passive electrical backplane                                                                     | 131 |

| 3.4.11 | Storlite demonstration platform                                                                                 | 133 |

| 3.4.12 | Test and measurement                                                                                            | 135 |

| 3.5    | Summary                                                                                                         | 151 |

|        | d generation pluggable active optical circuit board connector for polymer waveguide based electro<br>uit boards |     |

| 4.1    | Introduction                                                                                                    | 152 |

| 4.1.1  | FirstLight project summary                                                                                      | 152 |

| 4.1.2  | FirstLight system design                                                                                        | 153 |

| 4.2    | FirstLight pluggable active electro-optical backplane connector                                                 | 155 |

| 4.2.1  | StorConn3 – FirstLight quad parallel optical transceiver                                                        | 157 |

| 4.2.2         | StorConn3 circuit hardware design                                                            | 161        |

|---------------|----------------------------------------------------------------------------------------------|------------|

| 4.2.3         | Dual lens coupling solution                                                                  |            |

| 4.2.4         | StorConn3 component layout                                                                   |            |

| 4.2.5         | StorConn3 card assembly process                                                              |            |

| 4.2.6         | Pluggable connector mechanism                                                                | 174        |

| 4.3           | StorConnOpt3 - electro-optical backplane with embedded polymeric waveguides                  | 177        |

| 4.3.1         | Polymer optical waveguide layer                                                              | 177        |

| 4.3.2         | Optical interconnect design                                                                  | 178        |

| 4.3.3         | Electro-optical PCB fabrication process                                                      |            |

| 4.3.4         | Insertion loss measurements                                                                  |            |

| 4.3.5         | Optical waveguide signal integrity characterisation                                          |            |

| 4.4           | Passive alignment and assembly method                                                        | 191        |

| 4.4.1         | Improvements over Storlite design                                                            |            |

| 4.4.2         | Fabrication of passive alignment features                                                    |            |

| 4.4.3         | Lensed waveguide receptacle design                                                           |            |

| 4.4.4         | Assembly of microlens array into receptacle                                                  |            |

| 4.4.5         | Assembly of waveguide receptacle onto OPCB                                                   |            |

| 4.5           | StorConnTest3 - FirstLight 10 Gb/s test daughtercard                                         |            |

| 4.5.1         | Functional overview                                                                          |            |

| 4.5.2         | StorConnTest3 component listing                                                              |            |

| 4.5.3         | FirstLight demonstration platform                                                            |            |

| 4.5.4         | FirstLight platform FPGA firmware design                                                     |            |

| 4.5.5         | FirstLight Graphical User Interface (GUI)                                                    |            |

| 4.5.6         | FirstLight test and measurement results                                                      |            |

| 4.6           | Summary                                                                                      |            |

| 5 Plug<br>224 | gable passive optical circuit board connector for planar glass waveguide based optical circu | uit boards |

| 5.1           | Introduction                                                                                 | 224        |

| 5.1.1         | Glass waveguide based optical circuit boards                                                 | 225        |

| 5.1.2         | SEPIANet project                                                                             | 225        |

| 5.1.3         | SEPIANet technology overview                                                                 |            |

| 5.1.4         | Objectives                                                                                   | 226        |

| 5.2           | Optical waveguide layout design                                                              | 227        |

| 5.3           | Glass waveguide fabrication                                                                  | 231        |

| 5.3.1         | Glass waveguide fabrication process flow                                                     | 231        |

| 5.3.2         | Waveguide characterisation by Fraunhofer IZM                                                 |            |

| 5.4           | Electro-optical circuit board fabrication using low temperature lamination processes         |            |

| 5.5           | Pluggable optical connector design and assembly                                              |            |

| 5.5.1         | MT ferrule compliant waveguide receptacle                                                    |            |

| 5.5.2         | Board-to-board connector plug and backplane receptacle design                                | 247        |

| 5.5.3         | Board assembly of fibre ferrule receptacles                                                  |            |

| 5.5.4         | Assembly of connector plugs and receptacles                                                  | 252        |

| 5.5.5         | SEPIANet platform design                                                                     |            |

| 4 | 5.6    | Optical interconnect test and measurement                                                    |             |

|---|--------|----------------------------------------------------------------------------------------------|-------------|

|   | 5.6.1  | Bidirectional insertion loss measurements                                                    |             |

|   | 5.6.2  | Insertion loss measurements through both daisy chained demonstration platforms               |             |

|   | 5.6.3  | Correlation between contamination and non-reciprocal insertion loss profiles                 |             |

|   | 5.6.4  | Bidirectional signal integrity measurements at 10.3 Gb/s                                     |             |

|   | 5.6.5  | Bit Error Rate characterisation of on-board 850 nm transceiver subassemblies                 |             |

|   | 5.6.6  | Bit Error Rate characterisation up to 32 Gb/s                                                |             |

| 4 | 5.7    | Summary                                                                                      |             |

| 6 | Intell | ectual Property                                                                              |             |

| 6 | 5.1    | Introduction                                                                                 |             |

| 6 | 5.2    | Optical intellectual property summary                                                        |             |

| 6 | 5.3    | Areas of invention                                                                           |             |

| 6 | 5.4    | Optical intellectual property portfolio                                                      |             |

|   | 6.4.1  | Patent 1: Optical transceiver connector module [170]                                         |             |

|   | 6.4.2  | Patent 2: High-precision passive component alignment to PCB [171]                            |             |

|   | 6.4.3  | Patent 3: Daughtercard optical waveguide interconnects [172]                                 |             |

|   | 6.4.4  | Patent 4: Reconfigurable optical printed circuit board [173]                                 |             |

|   | 6.4.5  | Patent 5: Crosstalk suppression on optical waveguides [174]                                  |             |

|   | 6.4.6  | Patent 6: Passive optical waveguide integrated CWDM device [175]                             |             |

|   | 6.4.7  | Patent 7: Method of manufacturing multimode CWDM multiplexer / demultiplexer struct 296      | tures [176] |

|   | 6.4.8  | Patent 8: Optical adapter module [177]                                                       |             |

|   | 6.4.9  | Patent 9: Fabricating a hybrid electro-optical PCB with optical surface layers [178]         |             |

|   | 6.4.1  | Patent 10: Lossless tapered waveguides [179]                                                 |             |

|   | 6.4.1  | Patent 11: Directly pluggable orthogonal in-plane optical PCB connector [180]                |             |

|   | 6.4.12 | 2 Patent 12: Optical capstan to simplify routing of optical waveguides [181]                 |             |

|   | 6.4.1  | Patent 13: Directly pluggable orthogonal in-plane optical PCB connector [182]                |             |

|   | 6.4.14 | Patent 14: Modular interconnectable electro-optical backplane [183]                          |             |

|   | 6.4.1  | 5 Patent 15: Optical amplification devices for polymer optical printed circuit boards [18    | 34]312      |

|   | 6.4.1  | 6 Patent 16: Design and manufacture of polymer optical waveguide amplification struct<br>314 | tures [185] |

| e | 5.5    | Summary                                                                                      |             |

| 7 | Conc   | lusion                                                                                       |             |

| 7 | 7.1    | Summary                                                                                      |             |

|   | 7.1.1  | Introduction to data centres and system embedded photonic eco-system                         |             |

|   | 7.1.2  | Pluggable active optical connectors for polymer waveguide interfaces                         |             |

|   | 7.1.3  | Pluggable passive optical connectors for glass interfaces                                    |             |

|   | 7.1.4  | Intellectual property                                                                        |             |

| 7 | 7.2    | Challenges and future work                                                                   |             |

|   | 7.2.1  | Higher density active connectors                                                             |             |

|   | 7.2.2  | Standardisation of polymer waveguide connectorisation                                        |             |

|   | 7.2.3  | Connectorisation of single mode polymer waveguides                                           |             |

|   | 7.2.4  | Method of futher improving robustness of passive alignment technique                         |             |

|   | 7.2.5   | Multilayer glass waveguide couplers                        | 323 |

|---|---------|------------------------------------------------------------|-----|

|   | 7.2.6   | High yield alignment and assembly processes on glass OPCBs | 323 |

|   | 7.2.7   | Wavelength dependent performance                           | 323 |

|   | 7.3 P   | Publications                                               | 324 |

|   | 7.3.1   | Journal papers                                             | 324 |

|   | 7.3.2   | Conference papers                                          | 325 |

|   | 7.3.3   | Articles                                                   | 326 |

|   | 7.4 I   | nvited talks and presentations                             | 327 |

| 8 | Referen | 1ces                                                       |     |

| 9 | Append  | dix - FirstLight platform firmware coding                  | 349 |

|   | 9.1 P   | CI command structure                                       | 349 |

|   | 9.1.1   | General static control lines                               | 349 |

|   | 9.1.2   | XFP I <sup>2</sup> C interface (XFPIO)                     | 353 |

|   | 9.1.3   | Crosspoint switch interface (CPSIO)                        | 354 |

|   | 9.1.4   | StorConn3 transceiver interface (SC3IO)                    | 359 |

|   | 9.1.5   | LED control interface (LEDIO)                              |     |

# LIST OF FIGURES

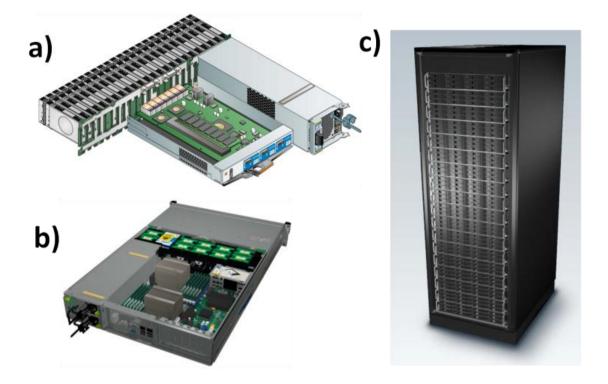

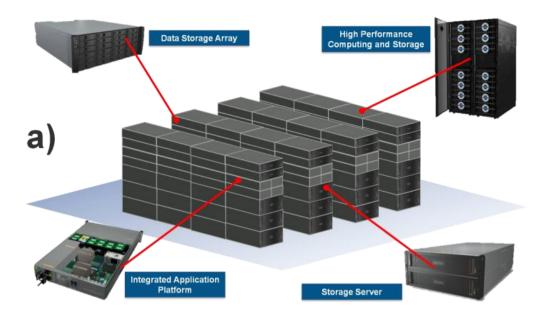

| Figure 1-1: Optical circuit board varieties and associated demonstration platforms                                | 4  |

|-------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2: SEPIANet glass waveguide optical circuit board connector platform                                     |    |

| Figure 1-3: Optical interconnect migration in data centre environments                                            |    |

| Figure 1-4: Floor plan of a single storey data centre (Source: NTT Japan)                                         |    |

| Figure 1-5: a) Generic data storage array system, b) Data storage integrated application platform, c) 42U data    | a  |

| storage rack                                                                                                      | 13 |

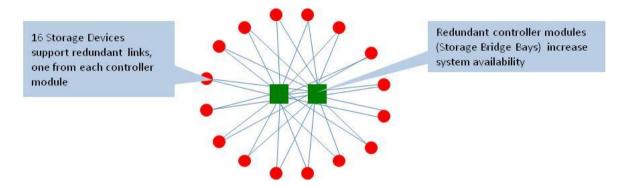

| Figure 1-6: Example of a Dual Star interconnect topology whereby 2 controller nodes each have a link to 16        |    |

| storage devices, thus eliminating the controller module as a single point of failure                              | 14 |

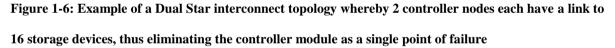

| Figure 1-7: Schematic view of traditional fat tree with links becoming thicker as we move up the hierarchy        |    |

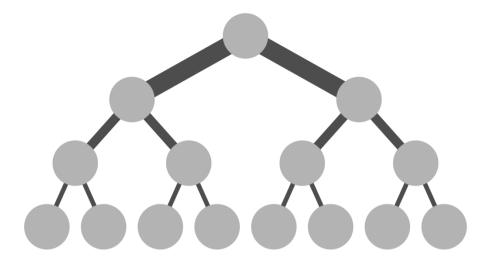

| Figure 1-8: Fat tree network where all three levels are built out of uniform rate port commodity TOR switches     |    |

| a (folded) Clos topology (Source: Nephele project [11])                                                           |    |

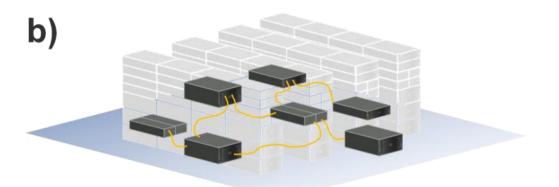

| Figure 1-9: a) Building blocks of modern data centres, b) Schematic of optical links connecting geographical      |    |

| dispersed subsystems within a data centre architecture                                                            |    |

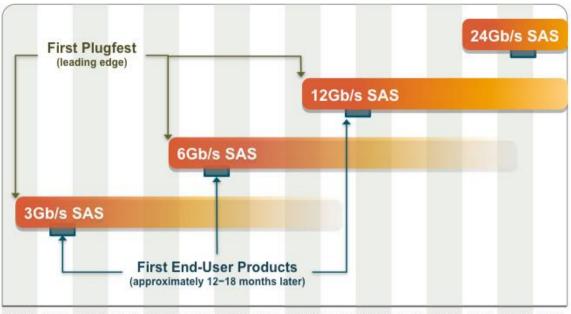

| Figure 1-10: Serial Attached SCSI Roadmap (Source SCSI Trade Association – March 2014)                            |    |

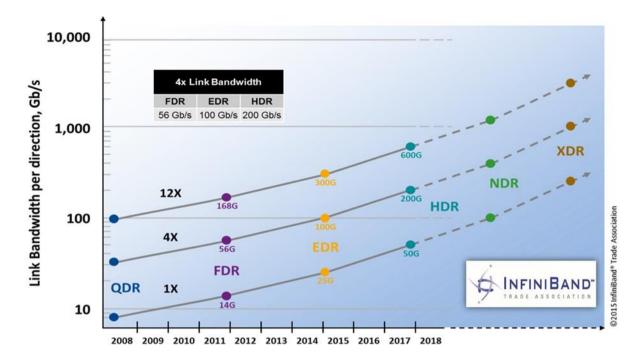

| Figure 1-11: Infiniband <sup>™</sup> Roadmap (Source: InfiniBand <sup>™</sup> Trade Association)                  |    |

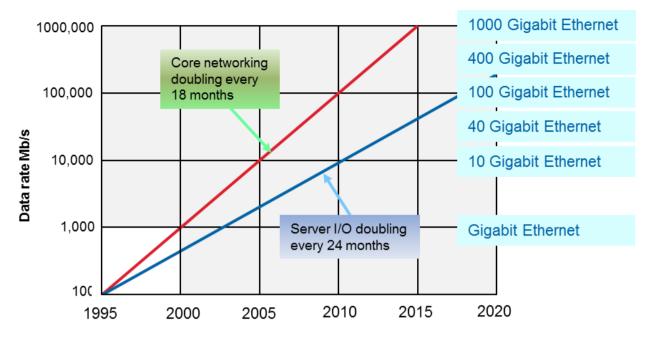

| Figure 1-12: Ethernet roadmap [29]                                                                                |    |

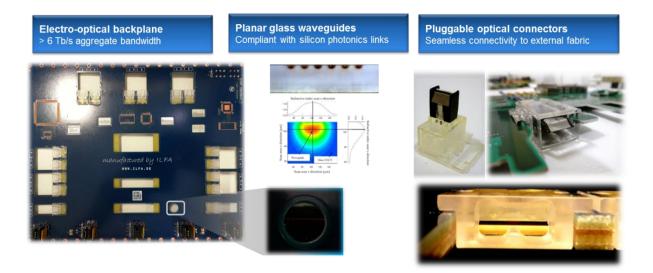

| Figure 1-13: SEPIANet project technology overview                                                                 |    |

| Figure 1-14: PhoxTrot vision: On-chip, chip-to-chip, board-to-board and rack-to-rack optical interconnect         |    |

| solutions deployed in PhoxTrot demonstration platform                                                             | 28 |

| Figure 1-15: Multimode optical interconnect deployed in systems, chips and OPCBs                                  |    |

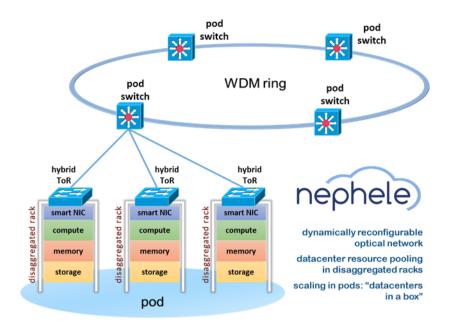

| Figure 1-16: Nephele hybrid electro-optical scale out data centre architecture                                    |    |

| Figure 1-17: HDPuG demonstrators a) 1.4 metre spiral polymer waveguide sample (source: Dow Corning), b)           |    |

| MT ferrule terminated optical waveguides with visible pink and green light illuminating 2 waveguides (Source      |    |

| Optical Interlinks), c) OPCB with straight waveguide illuminated with green light (source: TTM Technologie        |    |

| d) Two MT ferrules assembled onto the edge of a polymer waveguide based OPCB (Source: Optical Interlink           |    |

|                                                                                                                   |    |

| Figure 2-1: Generic data storage enclosure with passive and active optical connectors                             |    |

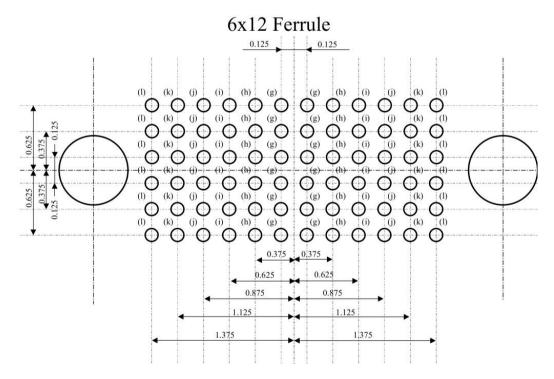

| Figure 2-2: MT parallel optical interface showing the positions of six rows of 12 small circular fibre channels   |    |

| relative to two large circular mechanical alignment slots on the left and right hand side                         |    |

| Figure 2-3: a) MT ferrule, b) PrizmMT <sup>™</sup> ferrule, c) MXC connector                                      |    |

| Figure 2-4: PCB stack-up showing electrical signal propagation between a copper trace on the top layer and a      |    |

| copper trace on an intermediate layer, passing along part of a via. A) fully filled via causes the exposed unuse  |    |

| section to create localised impedance mismatch, which gives rise to a partial reflection, b) back-drilling of the |    |

| via to minimise discontinuity and therefore partial reflection                                                    |    |

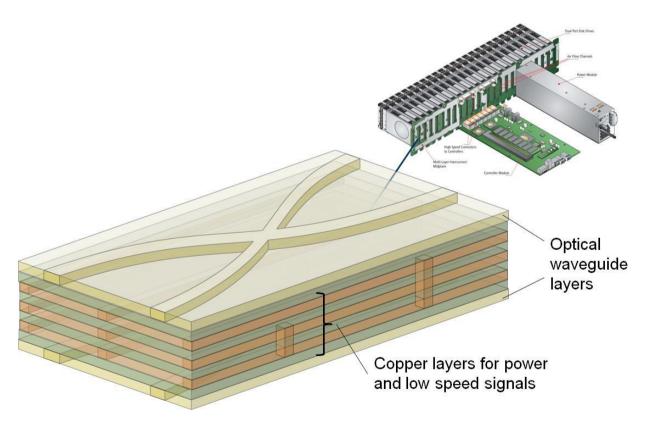

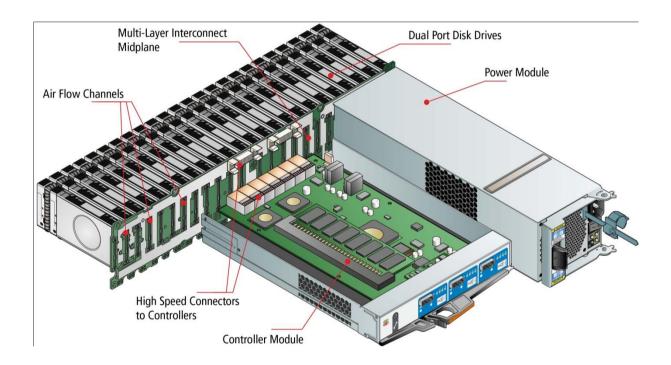

| Figure 2-5: Schematic view of electro-optical midplane architecture comprising copper layers to accommodat        |    |

| power, static and low speed signal distribution and at least one optical transmission layer to convey high spee   | ed |

| signals along optical waveguides                                                                                  |    |

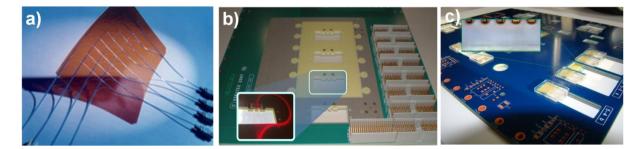

| Figure 2-6: Electro-optical PCB interconnect technologies a) Fibre-optic flexible circuits, b) PCB embedded       |    |

| polymer waveguides, c) PCB embedded planar glass waveguides (Source: Fraunhofer IZM)                              | 48 |

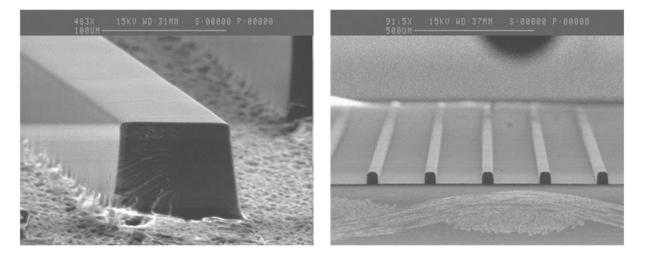

| Figure 2-7: Scanning Electron Microscope image of exposed 50µm x 50µm polymer waveguide core without              | t  |

| upper cladding (left) and array of exposed parallel polymer waveguide cores (right)                               | 50 |

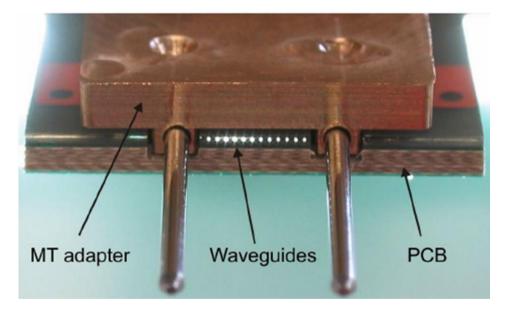

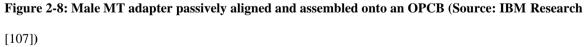

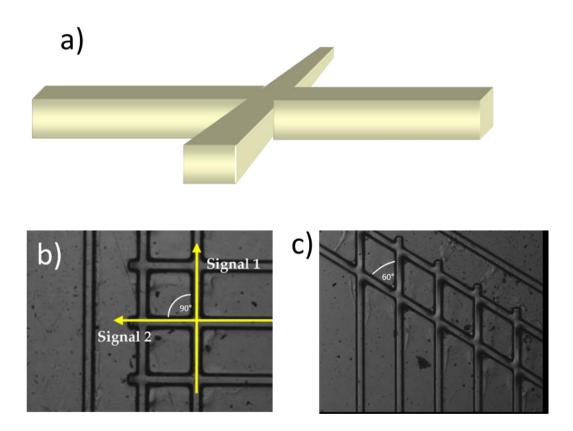

| Figure 2-8: Male MT adapter passively aligned and assembled onto an OPCB (Source: IBM Research [107]).            | 52 |

| Figure 2-9: Optical transceiver connectivity to OPCBs a) active optical transceiver interface in a fixed butt-    |    |

| coupled arrangement to embedded polymer waveguide interfaces in OPCBs (Source: IBM Research [108]), b             | )) |

| active optical transceiver and pluggable connector mechanism developed by author and described in Chapter         | 4, |

| allowing optical transceiver interface to be selectively butt-coupled to embedded polymer waveguide interfac      | es |

| on OPCB during engagement of a daughter card                                                                      | 53 |

| Figure 2-10: Channel density comparison between 24 Gb/s copper differential trace and polymeric optical           |    |

| channels                                                                                                          | 57 |

| Figure 2-11: Waveguide crossovers a) Schematic view of waveguide crossover, b) Photo of 50µm x 50µm               |    |

| polymer waveguides patterned photolithographically with multiple 90° crossovers (Source: Exxelis Ltd), c)         |    |

| Photo of 50µm x 50µm polymer waveguides patterned photolithographically with multiple 60° crossovers              |    |

| (Source: Exxelis Ltd)                                                                                             | 59 |

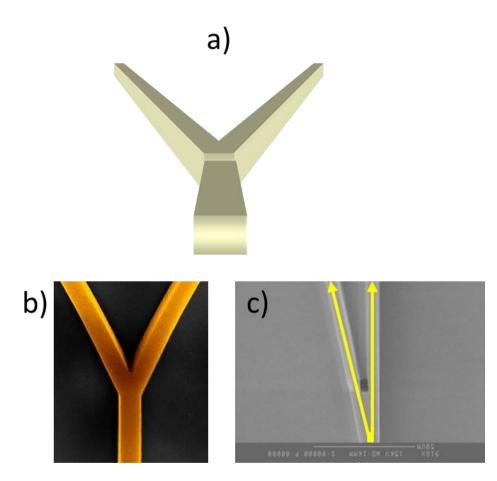

| Figure 2-12: Waveguide splitters a) Schematic view of 1 x 2 waveguide splitter, b) Photo of 50µm x 50µm           |    |

| polymer waveguides with 1 x 2 symmetric Y-branch splitter (Source: IBM Research), c) Photo of 50µm x 50           |    |

| polymer waveguides with 1 x 2 splitter (Source: Exxelis Ltd)                                                      |    |

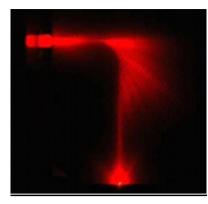

| Figure 2-13: Photo of polymer waveguide 90° arc bend illuminated with 650 nm visible light                        | 62 |

|                                                                                                                   |    |

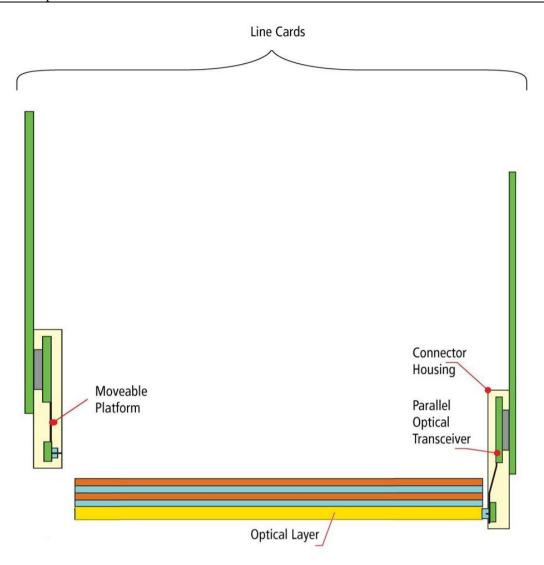

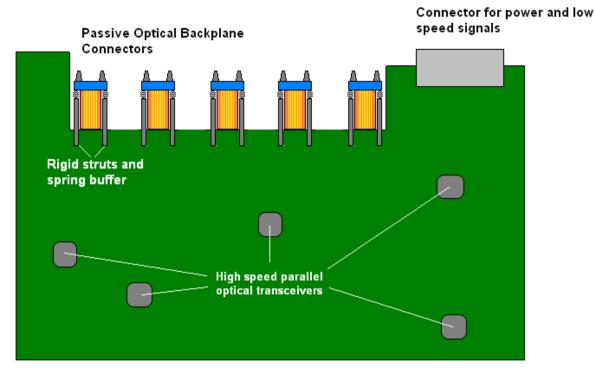

| Figure 3-1: Schematic view of electro-optical midplane architecture comprising copper layers to accommod                                                                                                    |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| power, static and low speed signal distribution and at least one optical transmission layer to convey high sp                                                                                               |      |

| signals along optical waveguides<br>Figure 3-2: Data storage array with 24 drives, two controller modules (one shown) and two power supply                                                                  | 67   |

| modules (one shown)                                                                                                                                                                                         | 68   |

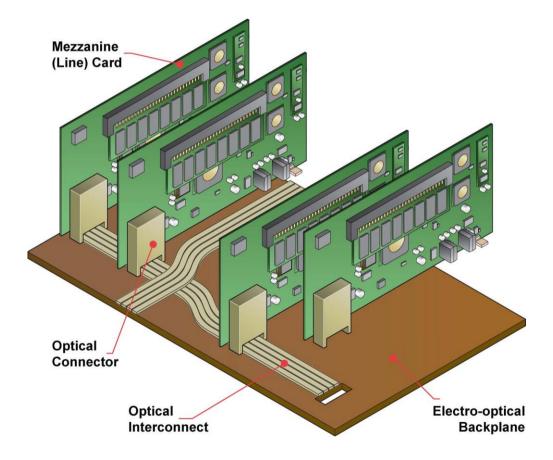

| Figure 3-3: Schematic view of line cards with optical edge connectors plugging in orthogonally to an electr                                                                                                 |      |

| optical backplane with embedded optical interconnect                                                                                                                                                        |      |

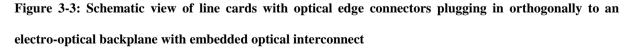

| Figure 3-4: Butt-coupled optical connection between surface emitting and receiving devices on the line card                                                                                                 |      |

| planar optical waveguide interface on electro-optic backplane                                                                                                                                               |      |

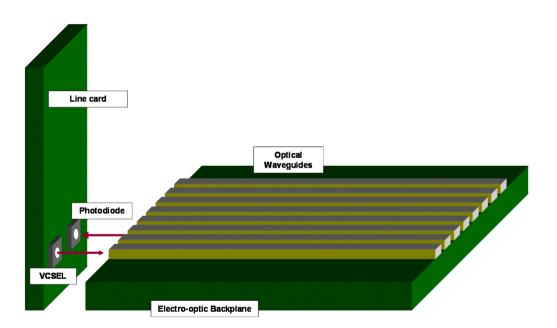

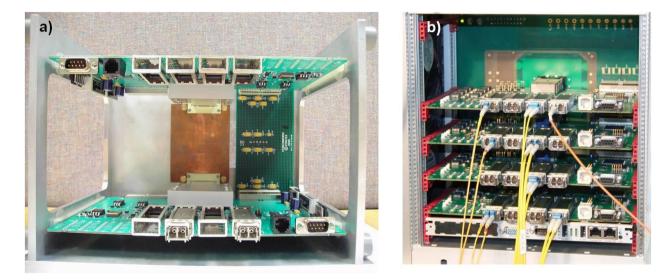

| Figure 3-5: a) Storlite Demonstrator - First generation optical backplane connector platform, b) FirstLight                                                                                                 |      |

| Demonstrator - second generation optical backplane connector platform                                                                                                                                       |      |

| Figure 3-6: Storlite optical backplane connection scheme                                                                                                                                                    |      |

| Figure 3-7: Storlite parallel optical transceiver circuit                                                                                                                                                   | 76   |

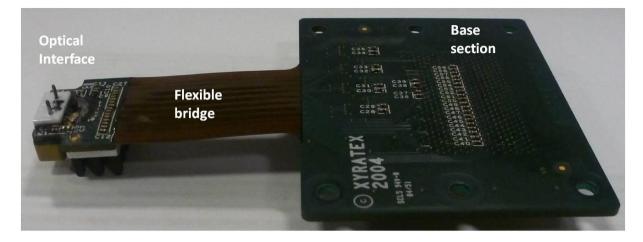

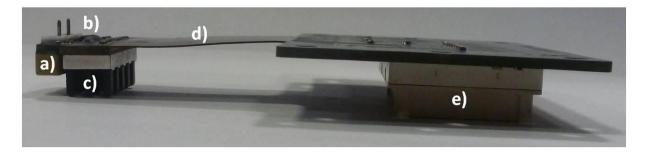

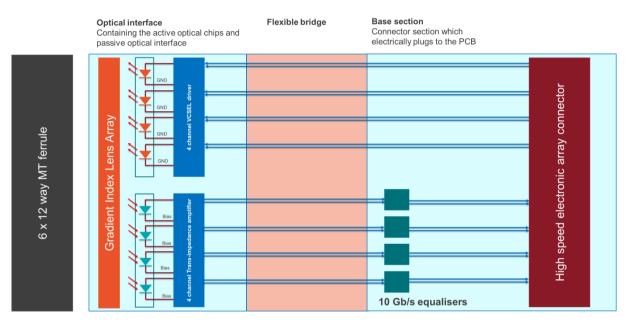

| Figure 3-8: Storlite parallel optical transceiver side-view: a) MT pin holder, b) Opto-mechanical interface,                                                                                                |      |

| Heat sink, d) Flexible bridge, e) GigArray® high speed connector                                                                                                                                            |      |

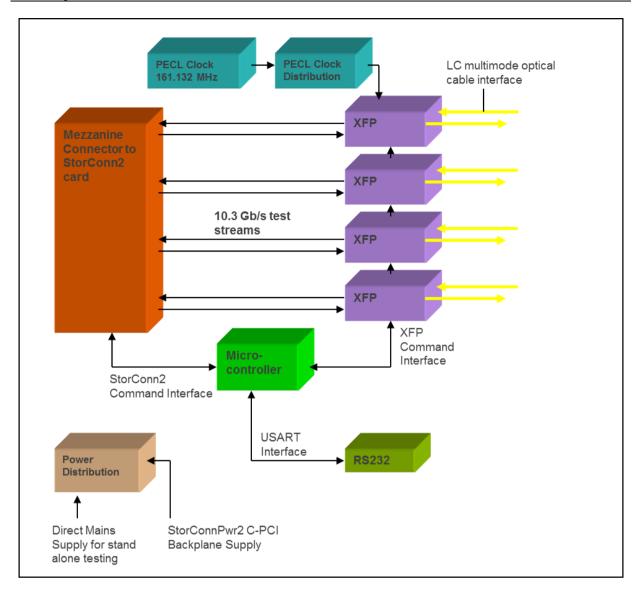

| Figure 3-9: Functional diagram of quad transceiver circuit                                                                                                                                                  |      |

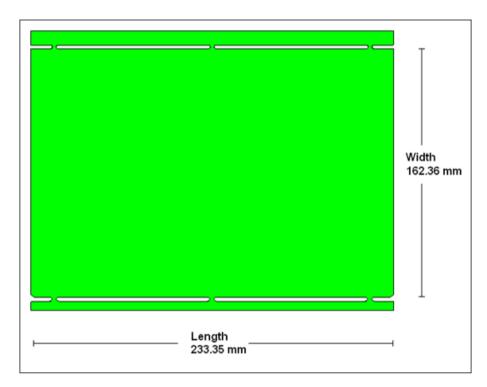

| Figure 3-10: StorConn2 raw card outline dimensions                                                                                                                                                          |      |

| Figure 3-11: StorConn2 PCB layer stack-up                                                                                                                                                                   |      |

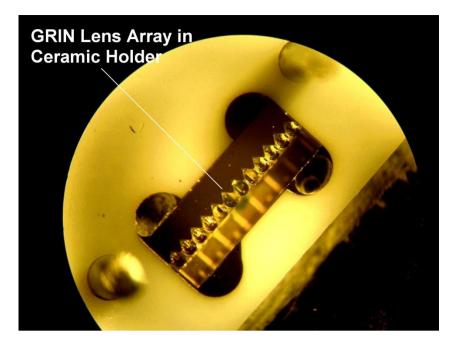

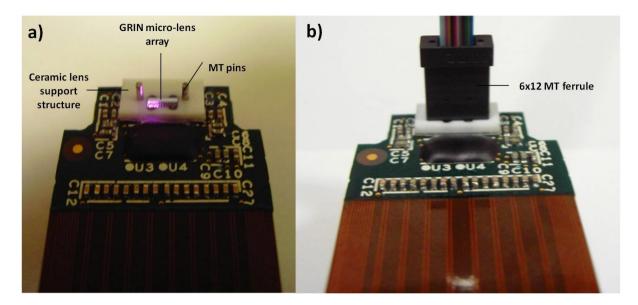

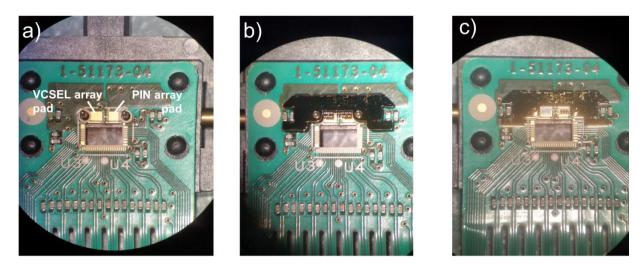

| Figure 3-12: Optical interface a) Quad VCSEL and PIN photodiode die array aligned and assembled onto F                                                                                                      |      |

| b) GRIN micro-lens array in ceramic holder aligned over active areas of VCSEL and PIN photodiodes                                                                                                           |      |

| Figure 3-13: Physical drawings of Gradient Index Micro-lens array and custom ceramic holder<br>Figure 3-14: 6x12 MT ferrule interface. The lowest (or highest) row of optical channels is offset from the d |      |

| of the MT pins by 625 μm                                                                                                                                                                                    |      |

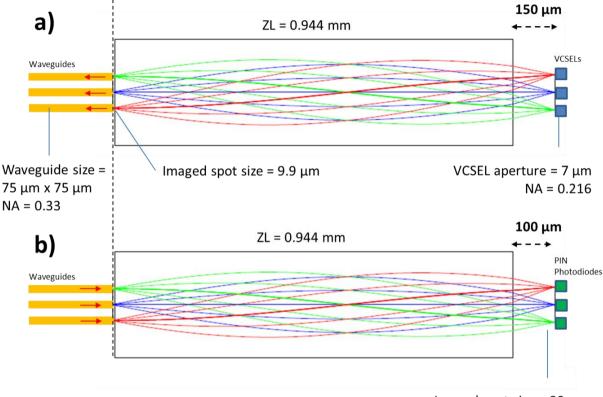

| Figure 3-15: ZEMAX simulation provided by GRINTech of optimum GRIN lens length (ZL) required to en                                                                                                          |      |

| a) imaging of the 75 $\mu$ m x 75 $\mu$ m waveguide output into the 75 $\mu$ m circular aperture of the PIN photodiode                                                                                      |      |

| b) imaging of the VCSEL output into the waveguide                                                                                                                                                           |      |

| Figure 3-16: StorConn2 component layout: a) top view, b) side view                                                                                                                                          |      |

| Figure 3-17: Gig array receptacle (Source: FCI Interconnect - GS-20-016 Rev B)                                                                                                                              |      |

| Figure 3-18: Equaliser Chip – 10.3 Gb/s                                                                                                                                                                     |      |

| Figure 3-19: MT pin block                                                                                                                                                                                   |      |

| Figure 3-20: Photo of VCSEL array and photodiode assembly prior to wire bonding (photo through microsof                                                                                                     |      |

|                                                                                                                                                                                                             | - ·  |

| Figure 3-21: GRIN lens assembly (photo through microscope)                                                                                                                                                  | 93   |

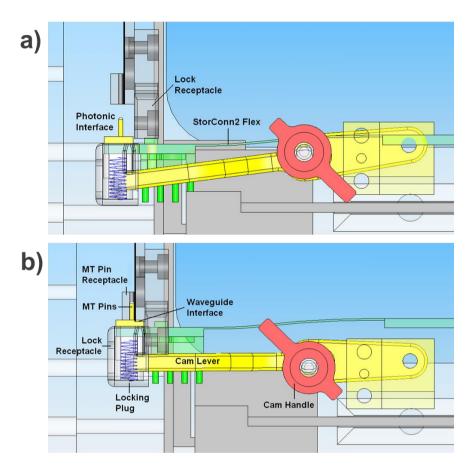

| Figure 3-22: Storlite connector CAD model - side view a) optical interface retracted, b) optical interface ele                                                                                              |      |

|                                                                                                                                                                                                             |      |

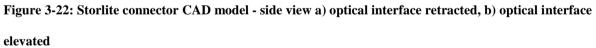

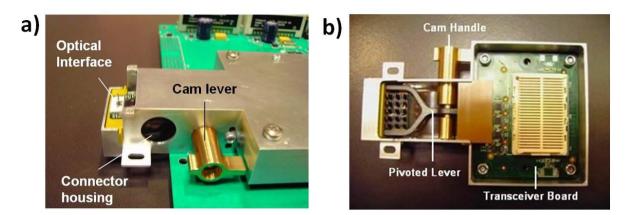

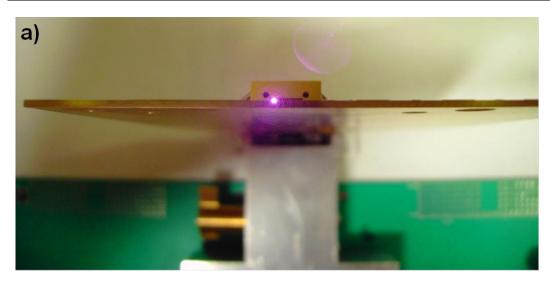

| Figure 3-23: Photo of Storlite connector - side view a) photonic interface retracted, b) photonic interface ele                                                                                             |      |

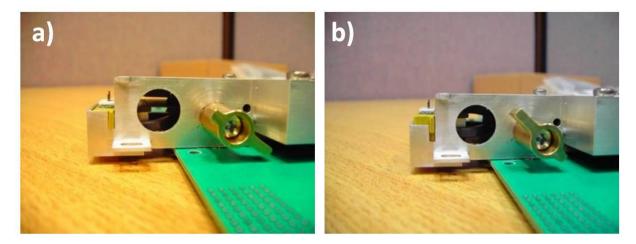

| Eigure 2.24. a) Starlite connector with retracted antical interface h) Starlite connector bettom view showin                                                                                                |      |

| Figure 3-24: a) Storlite connector with retracted optical interface, b) Storlite connector bottom view showin                                                                                               |      |

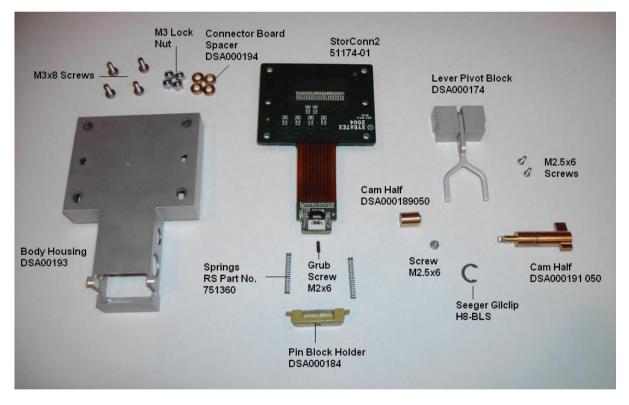

| bifurcated pivoted lever mechanism and electronic high speed GigArray® connector<br>Figure 3-25: Storlite connector exploded view                                                                           |      |

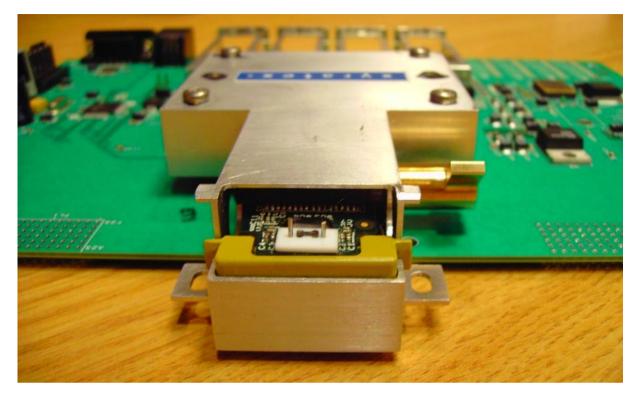

| Figure 3-26: Storlite connector attached to line-card - front view                                                                                                                                          |      |

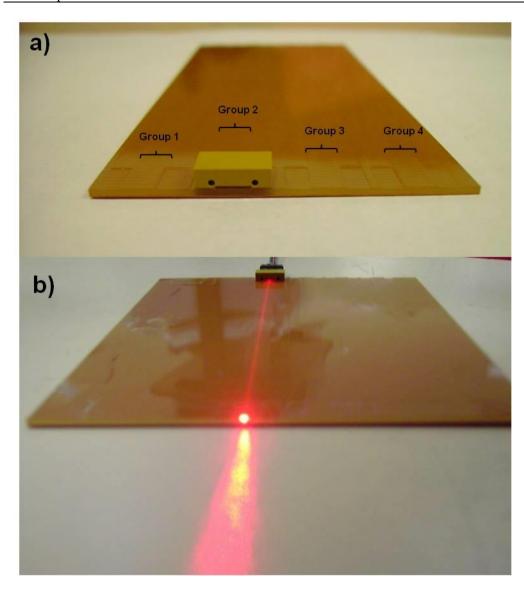

| Figure 3-27: Storlite optical waveguide PCB: a) four groups of 12 parallel straight waveguides. MT compli                                                                                                   |      |

| receptacle with MT pins slots offset from waveguide array by 625 µm (centre to centre), b) Single waveguid                                                                                                  |      |

| illuminated with 635 nm visible light to demonstrate effectiveness of passive alignment method and device                                                                                                   |      |

| Figure 3-28: Polymeric optical PCB interface                                                                                                                                                                |      |

| Figure 3-29: Fabrication process for Storlite optical waveguide PCB                                                                                                                                         | 101  |

| Figure 3-30: Mechanical drawings of Storlite waveguide receptacle                                                                                                                                           |      |

| Figure 3-31: Diagrams from patent "Optical printed circuit board and manufacturing method" [144]: a) opt                                                                                                    |      |

| waveguide receptacle socket showing exposed registration stubs, b) optical waveguide receptacle assemble                                                                                                    |      |

| optical waveguide receptacle socket                                                                                                                                                                         |      |

| Figure 3-32: Passive self-alignment assembly procedure: a) Storlite waveguide receptacle and OPCB wave                                                                                                      |      |

| interface with mechanical recesses and exposed registration structures, b) Waveguide receptacle assembled                                                                                                   | onto |

| OPCB (view facing waveguide interface), c) Waveguide receptacle assembled onto OPCB (side view show                                                                                                         | ing  |

| front face of unit flush with waveguide interface)                                                                                                                                                          |      |

| Figure 3-33: Shadowgraph image of an optical waveguide group with a receptacle passively aligned over it                                                                                                    |      |

| the mechanical registration features fabricated in the peripheries of the 12 communication waveguides                                                                                                       |      |

| Figure 3-34: First stage alignment verification using visible light: a) Class 2 635 nm laser source is connect                                                                                              |      |

| one fibre of a lowest row populated 6x12 MT to 12 LC fibre jumper, b) view of lowest row populated 6x12                                                                                                     |      |

| interface with channel five illuminated (fifth channel from left), c) MT ferrule about to engage with optical                                                                                               |      |

| waveguide receptacle, d) MT ferrule fully engaged with optical waveguide receptacle, e) optical waveguide                                                                                                   |      |

| receptacle passively aligned into waveguide registration recess with one waveguide channel illuminated                                                                                                      | 110  |

| Figure 3-35: Contour maps of relative insertion loss compared to the optimum coupling position for a) VCSI misalignment at $z = 0$ , b) PD misalignment [2] |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

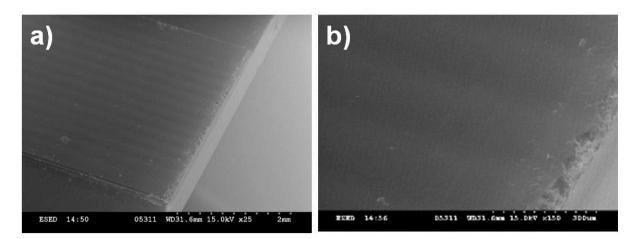

| Figure 3-36: SEM images of waveguide array interface which has been diced and polished: a) Full view of a                                                   |      |

| of 12 communications waveguides and peripheral recesses in upper cladding layer to enable mechanical acco                                                   |      |

| to mechanical registration features, b) Close view of roughness and surface degradation over waveguide                                                      |      |

| interface                                                                                                                                                   | 114  |

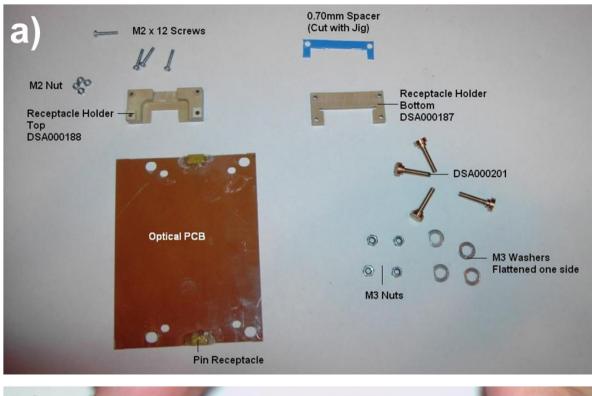

| Figure 3-37: optical backplane assembly: a) Exploded view of optical backplane assembly and parts includir                                                  |      |

| the receptacle holder, b) optical waveguide interface                                                                                                       |      |

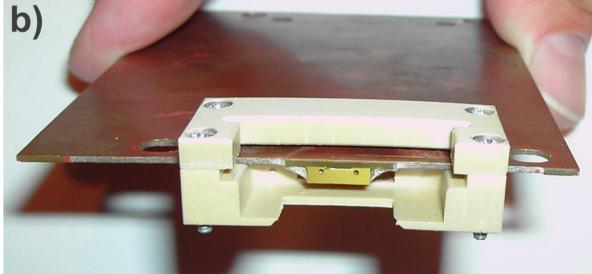

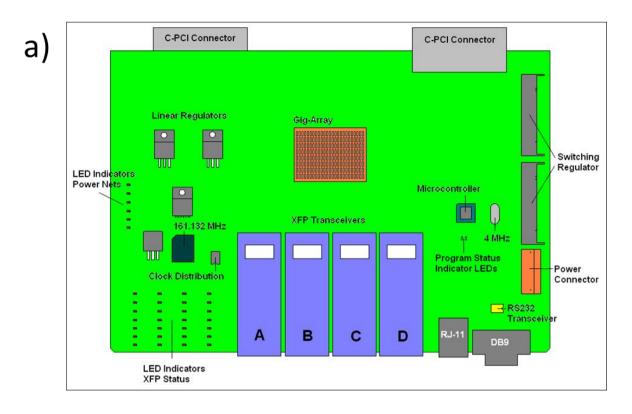

| Figure 3-38: Storlite test daughtercard: a) GigArray® connector receptacle, b) microcontroller, c) four                                                     |      |

| commercial XFP transceivers, d) RS232 connector and transceiver                                                                                             | 116  |

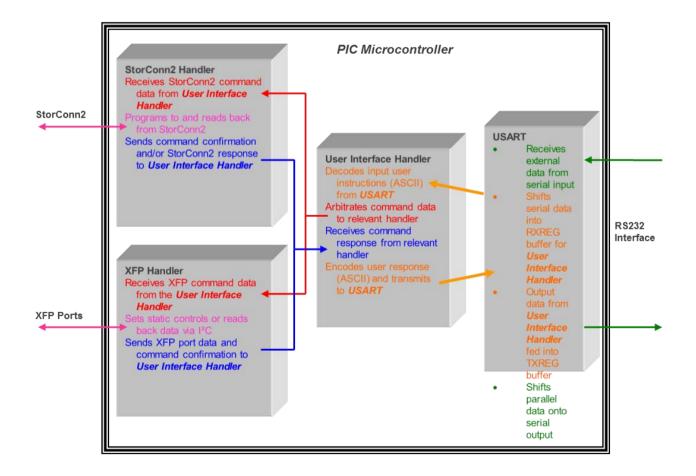

| Figure 3-39: StorConnTest2 functional diagram                                                                                                               |      |

| Figure 3-40: StorConnTest2 card profile                                                                                                                     |      |

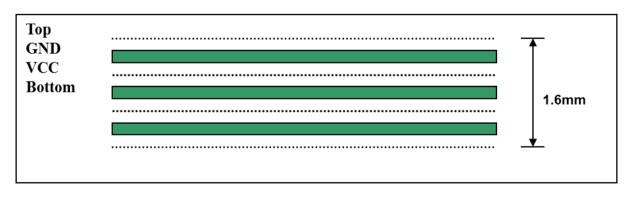

| Figure 3-41: StorConnTest2 raw card stack-up                                                                                                                |      |

| Figure 3-42: a) Schematic showing StorConnTest2 component layout, b) photo of StorConnTest2                                                                 | 124  |

| Figure 3-43: StorConnTest2 microcontroller flow diagram                                                                                                     | 125  |

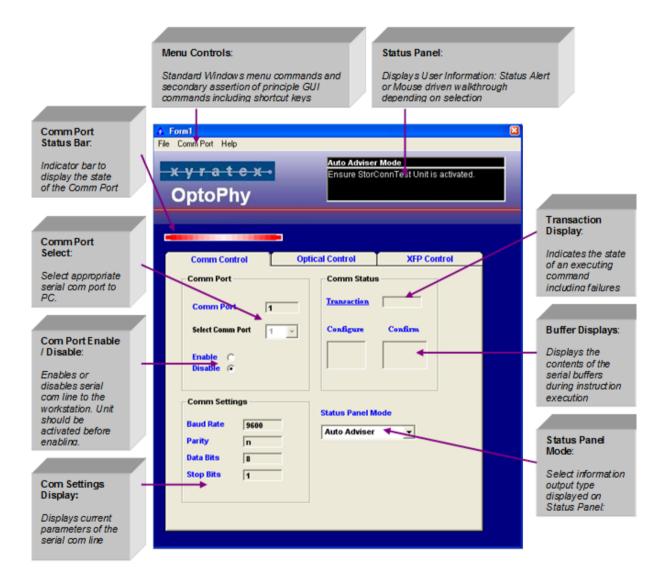

| Figure 3-44: Main screen / comm control tab                                                                                                                 |      |

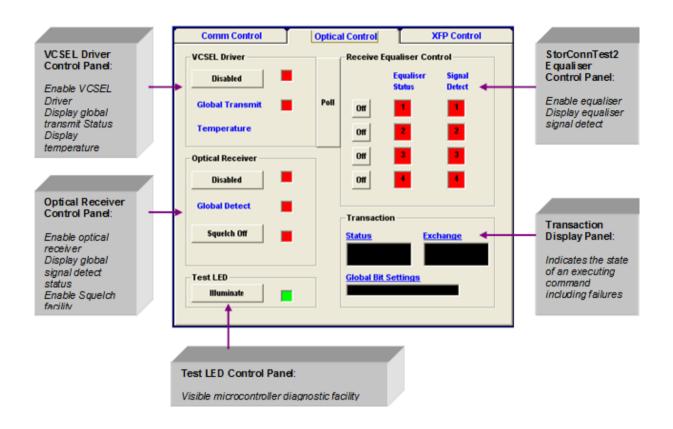

| Figure 3-45: Optical control tab                                                                                                                            |      |

| Figure 3-46: XFP control tab                                                                                                                                |      |

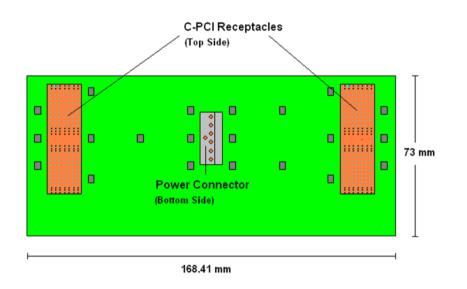

| Figure 3-47: StorConnPwr2 physical layout                                                                                                                   |      |

| Figure 3-48: StorConnPwr2 PCB layup                                                                                                                         |      |

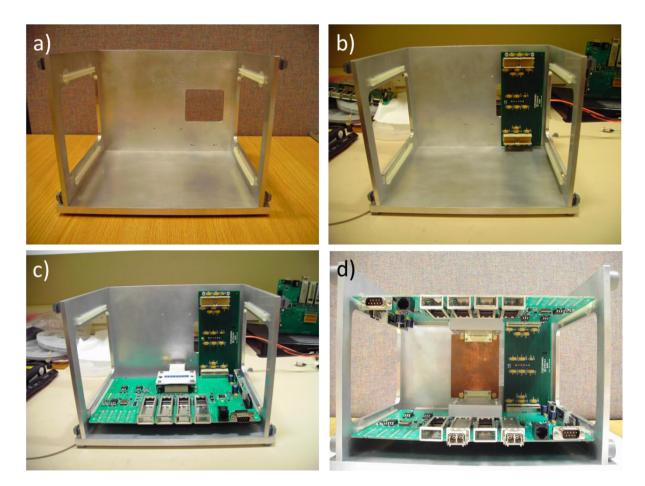

| Figure 3-49: Assembly process for Storlite demonstration enclosure: a) unpopulated enclosure, b) Enclosure                                                  |      |

| populated with only StorConnPwr2, c) enclosure populated with StorConnPwr2 and StorConnTest2, d) fully                                                      | r    |

| populated enclosure                                                                                                                                         | 133  |

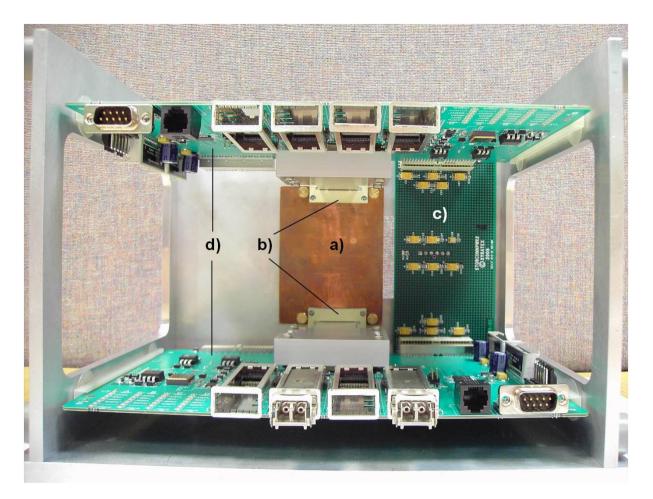

| Figure 3-50: Storlite demonstration platform a) Passive optical waveguide backplane (copper clad side show                                                  | 'n), |

| b) Pluggable optical backplane connectors, c) Electrical backplane, d) two test daughtercards                                                               | 134  |

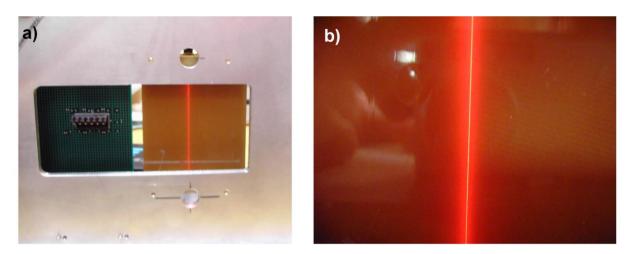

| Figure 3-51: a) View of Storlite demonstration system from the back, b) Single waveguide illuminated with                                                   | 635  |

| nm visible light                                                                                                                                            |      |

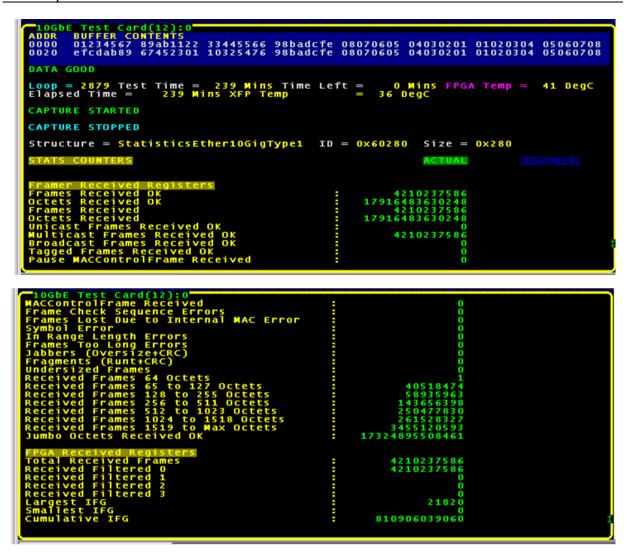

| Figure 3-52: Screen shots from Xyratex proprietary 10GbE LAN test traffic generator and error counter                                                       |      |

| Figure 3-53: a) Storlite transceiver opto-mechanical interface with all VCSELs activated, b) Storlite transcei                                              |      |

| opto-mechanical interface with MT patchcord attached for stand-alone testing                                                                                |      |

| Figure 3-54: Storlite test line card (powered) with transceiver attached (without connector housing) for stand                                              | 1-   |

| alone evaluation of the transceiver with an MT patchcord                                                                                                    |      |

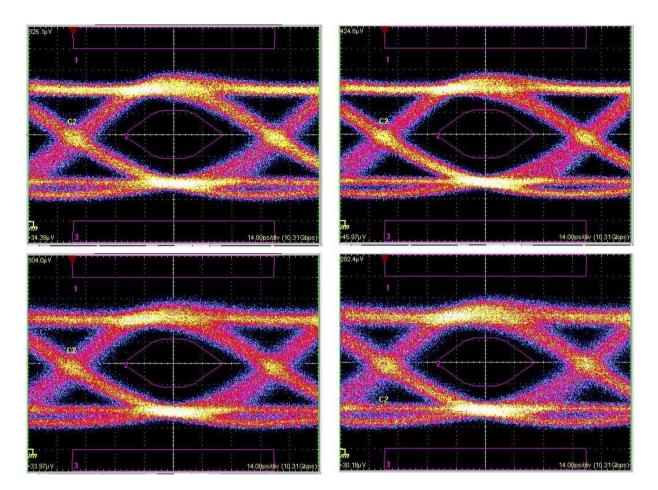

| Figure 3-55: Eye diagrams of all four VCSEL channels driven at 10.3 Gb/s with a bias current of 11.91 mA                                                    |      |

| a modulation current of 9.8 mA.                                                                                                                             |      |

| Figure 3-56: Eye diagrams of 10.3 Gb/s optical signals after propagation through 12 waveguides under test.                                                  |      |

| Eye diagrams captured without index damping fluid applied on waveguide end facets, b) Eye diagrams captu                                                    |      |

| with index damping fluid applied on both ingress and egress waveguide end facets                                                                            |      |

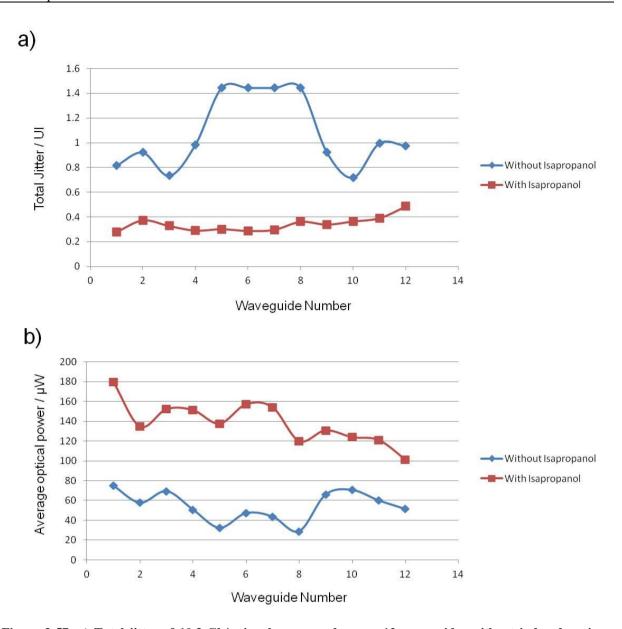

| Figure 3-57: a) Total jitter of 10.3 Gb/s signals measured across 12 waveguides without index damping fluid                                                 |      |

| (blue graph) and with index damping fluid (red graph), b) Comparative average optical power measured at the                                                 |      |

| communications signal analyser across 12 waveguides without index damping fluid (blue graph) and with in                                                    |      |

| damping fluid (red graph)                                                                                                                                   |      |

| Figure 3-58: View of exposed optical backplane waveguide egress interface with Storlite connector attached                                                  | to   |

| ingress interface. a) VCSEL channel one (furthest left) activated and 850 nm light exiting single egress                                                    |      |

| waveguide, b) VCSEL channels one and four activated and 850 nm light exiting two egress waveguides 750                                                      |      |

| apart<br>Figure 3-59: Characterisation setup for Storlite optical interface connection to optical backplane                                                 |      |

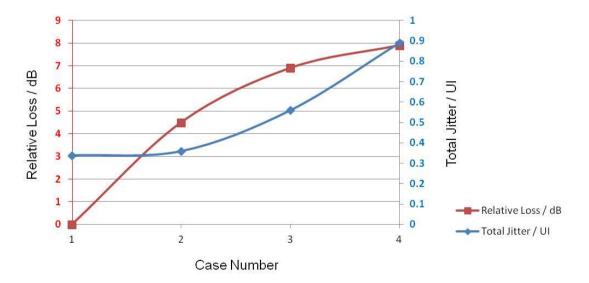

| Figure 3-60: Relative loss / dB and total jitter / UI for each use case listed in Table 3-9.                                                                |      |

| Figure 3-60: Relative loss / dB and total filter / of for each use case instead in Table 3-9.                                                               |      |

| analyser via MT fibre-optic patchcord (Reference), b) VCSEL connected to waveguide with isopropanol app                                                     | 0    |

| to ingress and egress end facets, c) VCSEL connected to waveguide with sopropanor app                                                                       | meu  |

| VCSEL connected to waveguide with end facets only diced                                                                                                     | 1/19 |

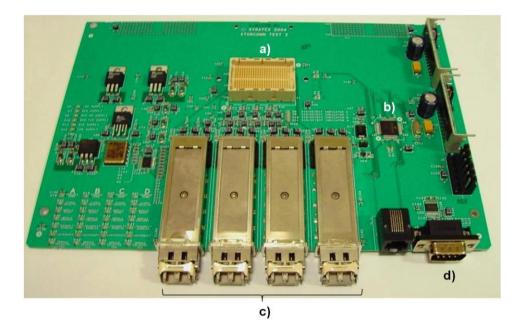

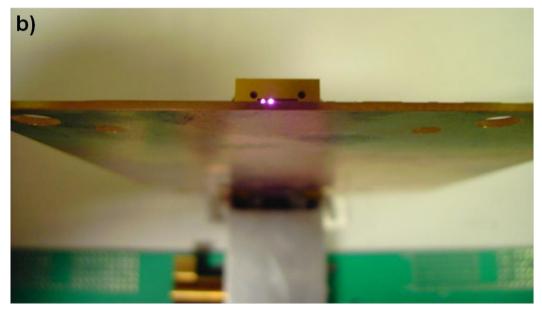

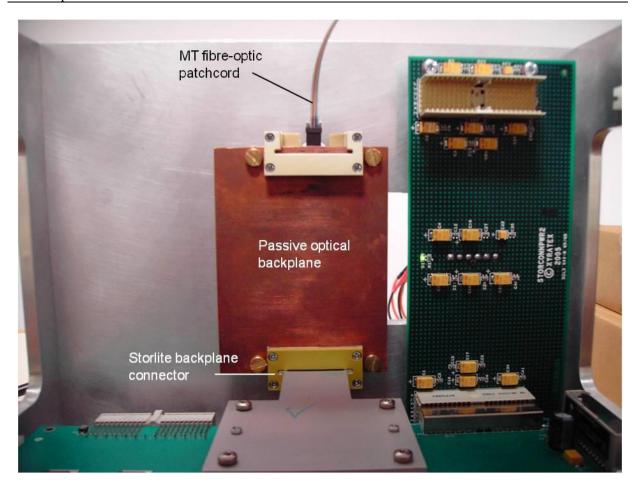

| Figure 3-62: Storlite demonstration platform populated with two test line cards with proprietary pluggable                                                  |      |

| connectors plugged into a passive optical backplane and a passive electrical backplane.                                                                     | 150  |

| Figure 4-1: a) FirstLight demonstration enclosure fully populated, b) FirstLight demonstration enclosure                                                    |      |

| powered                                                                                                                                                     |      |

| Figure 4-2: FirstLight pluggable optical PCB connector concept. Pluggable active connector modules are                                                      |      |

| inserted into the top of an optical backplane and engage with an optical layer on the bottom side of the                                                    |      |

| backplane: (a) Electro-optical backplane connection scheme; active pluggable connectors housed on the edge                                                  | e of |

| peripheral line cards engage with the embedded optical layer in the backplane PCB.                                                                          |      |

| Figure 4-3: Functional diagram of StorConn3                                                                                                                 |      |

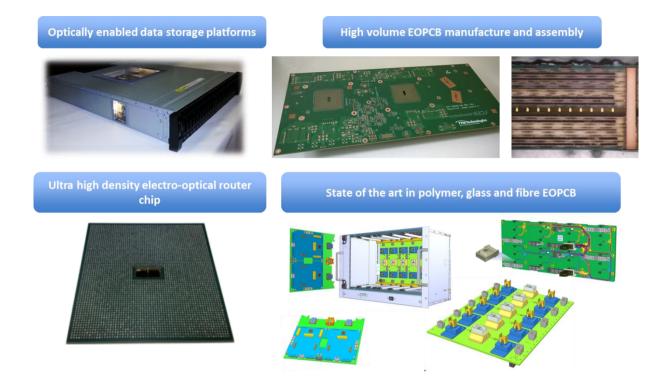

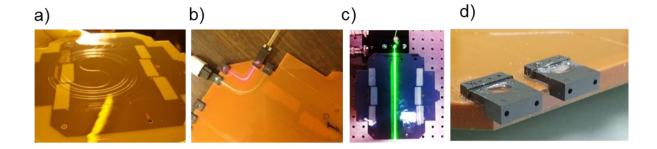

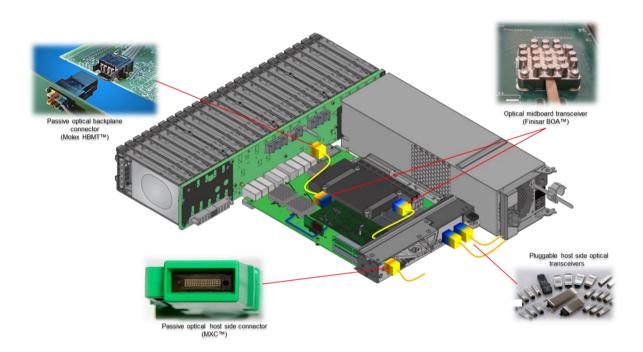

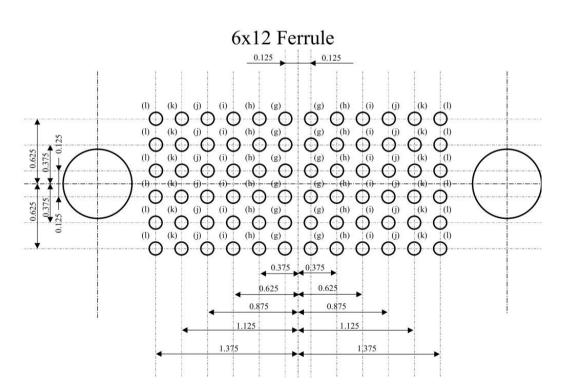

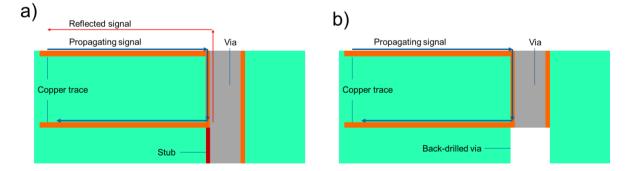

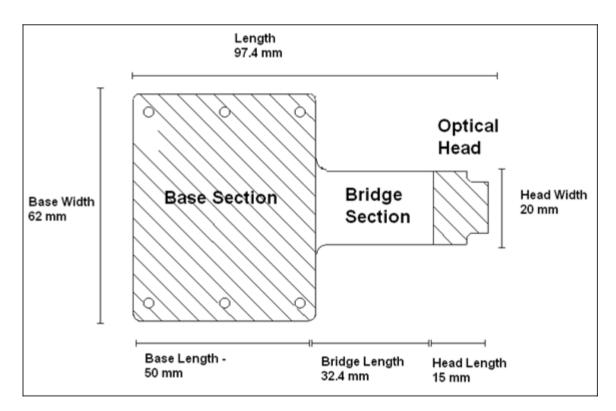

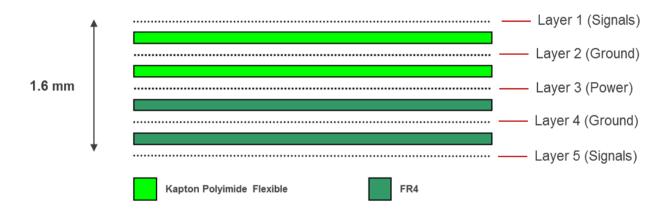

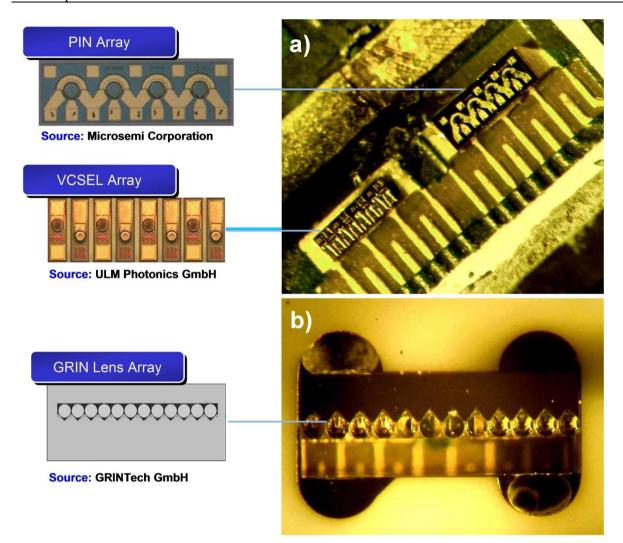

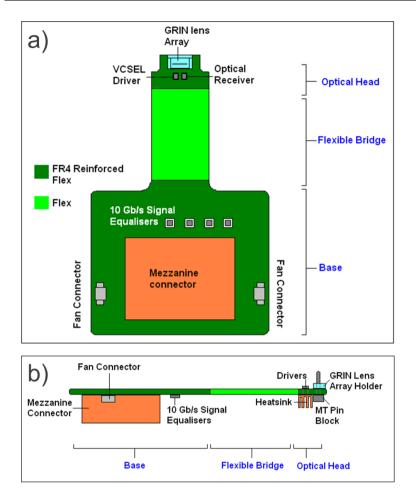

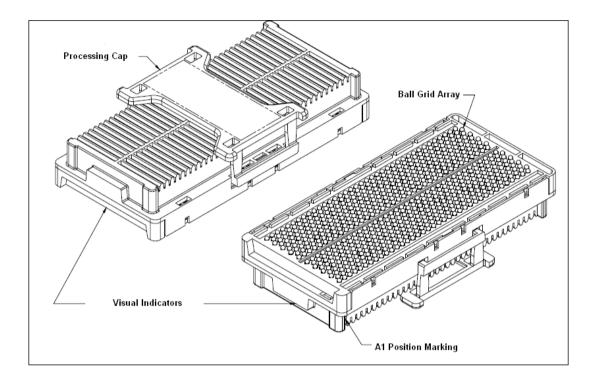

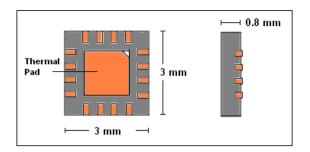

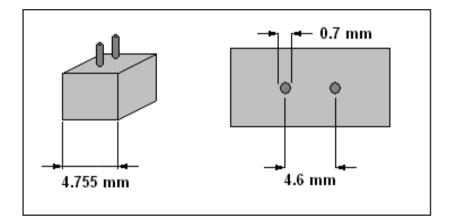

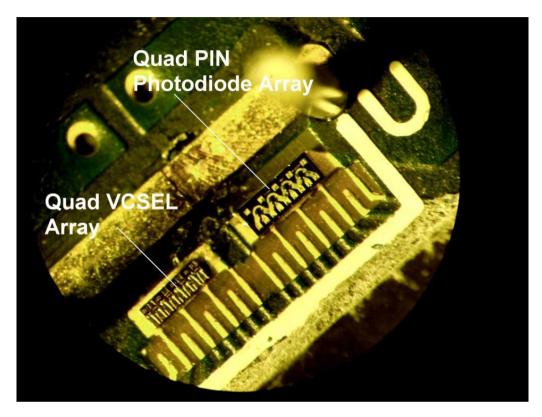

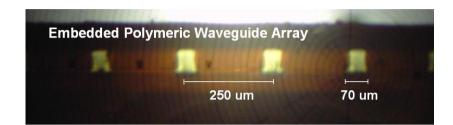

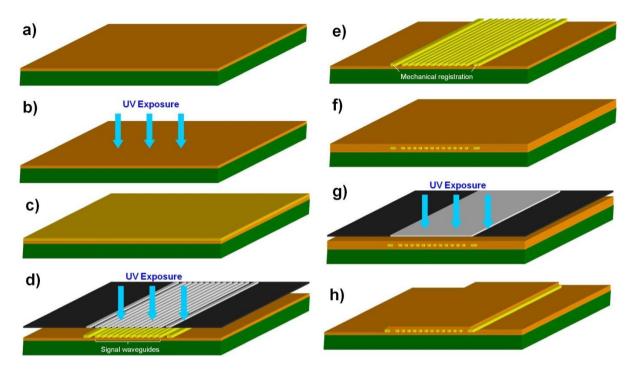

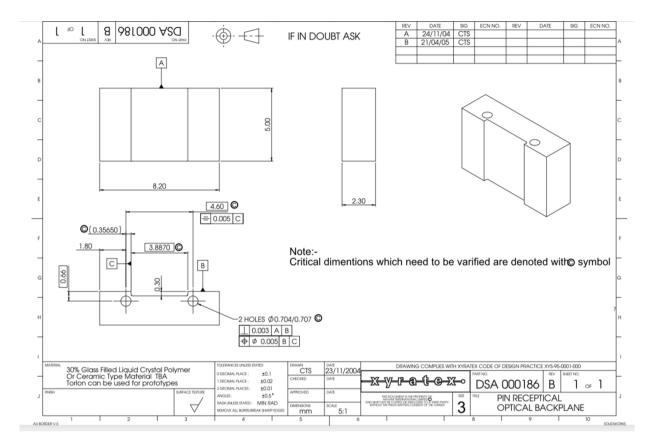

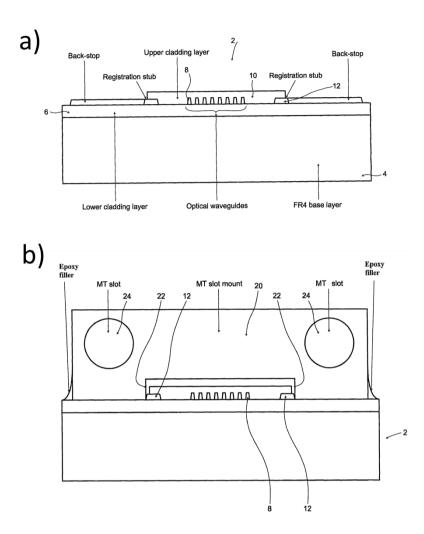

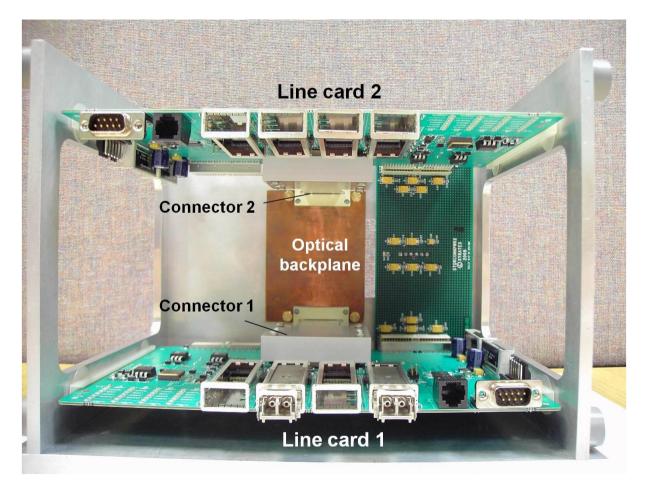

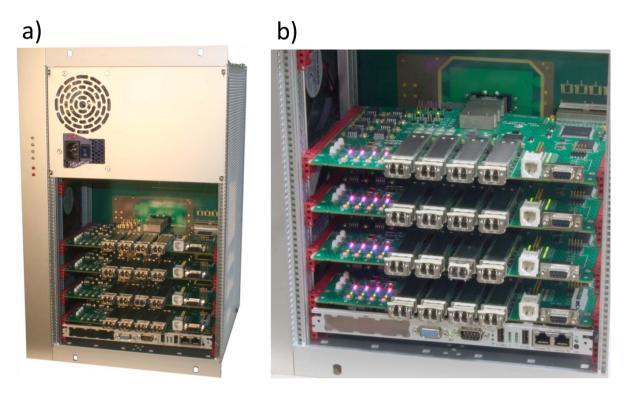

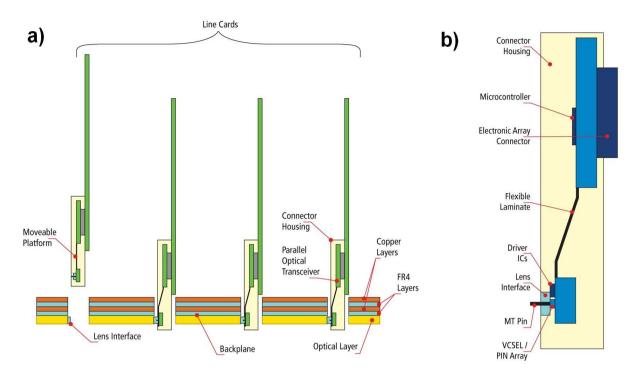

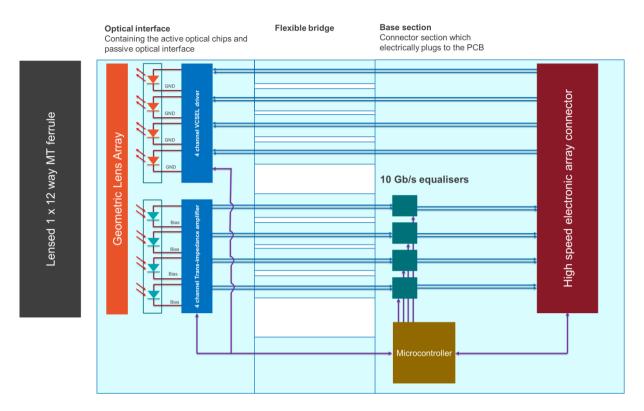

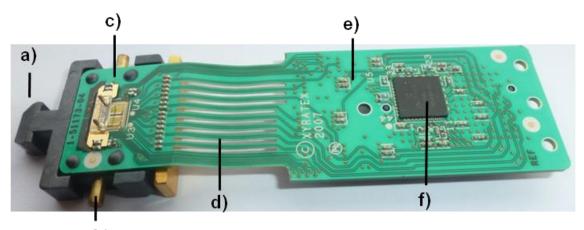

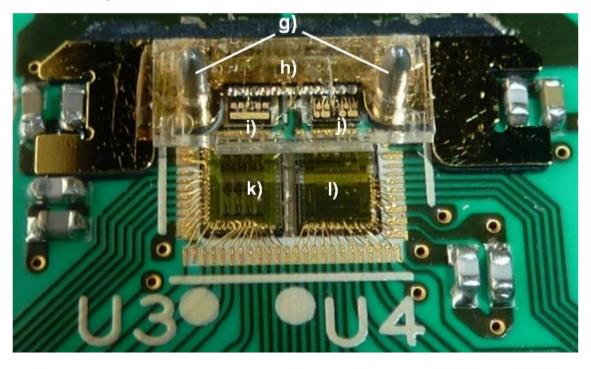

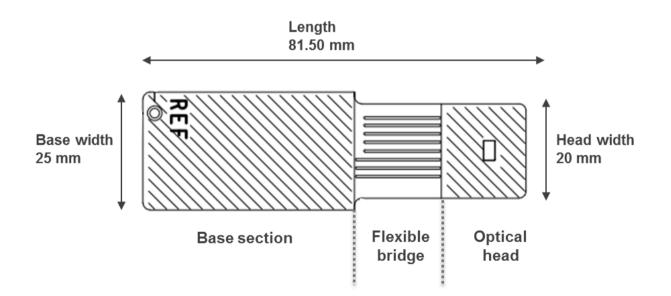

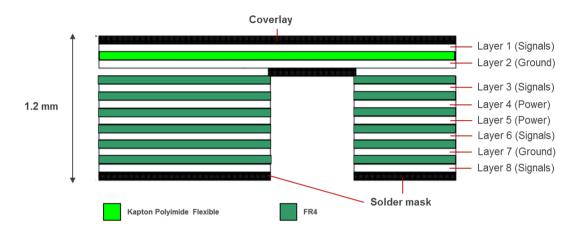

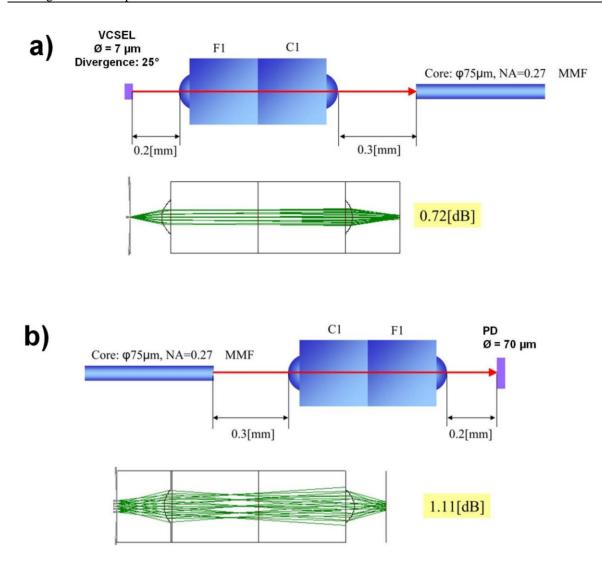

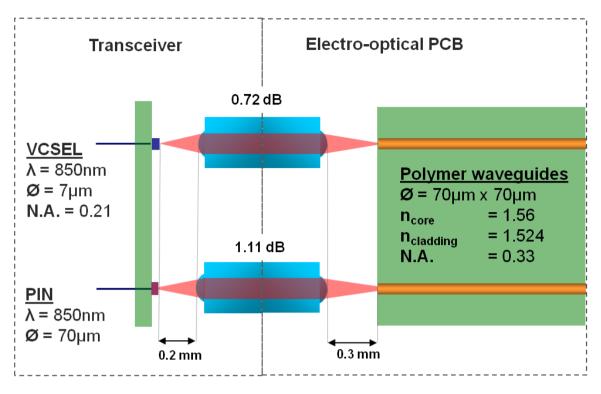

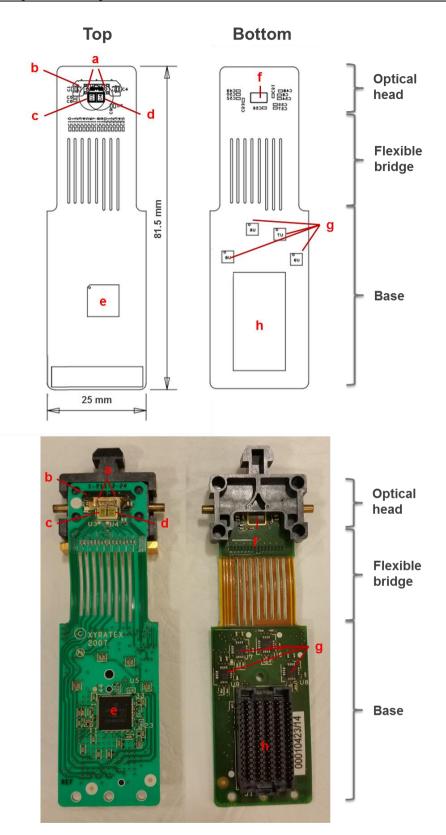

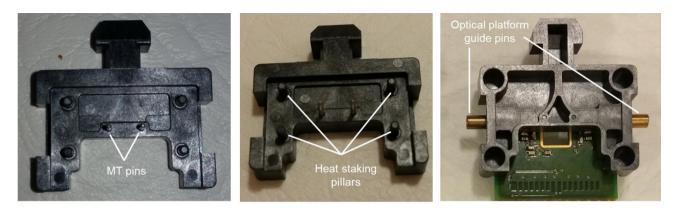

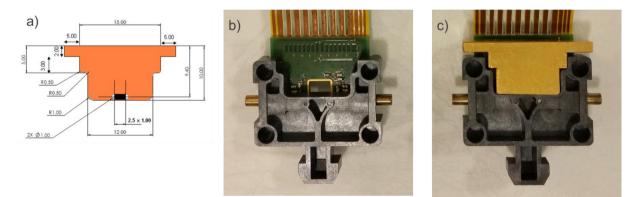

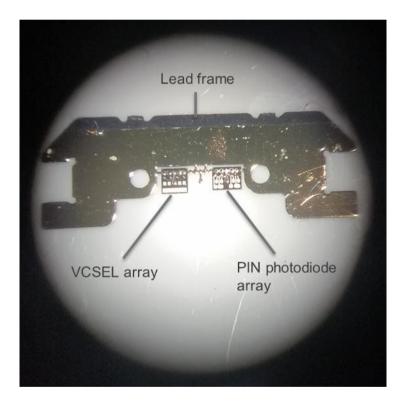

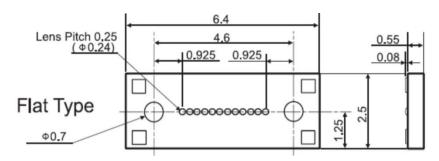

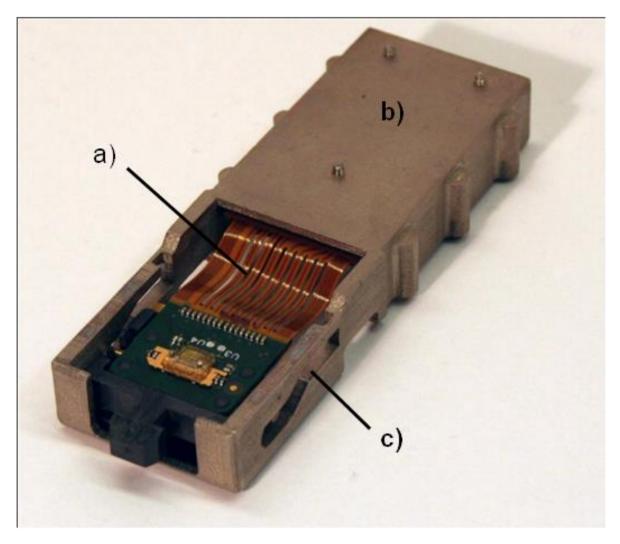

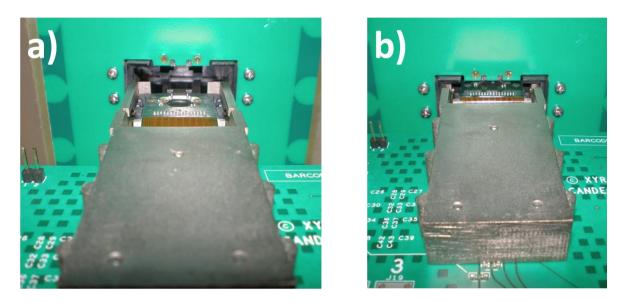

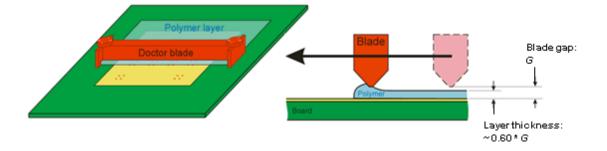

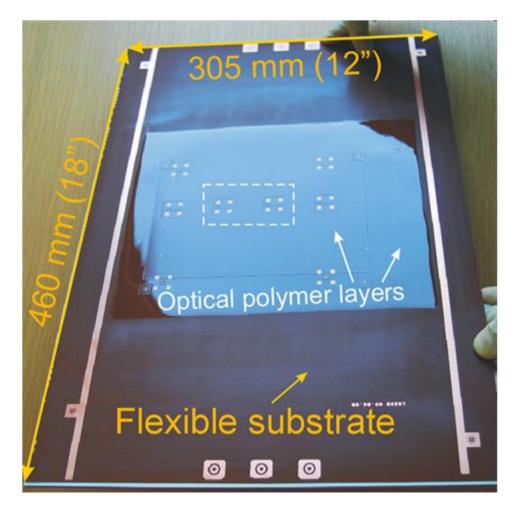

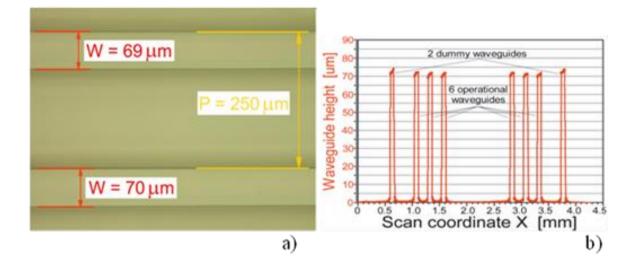

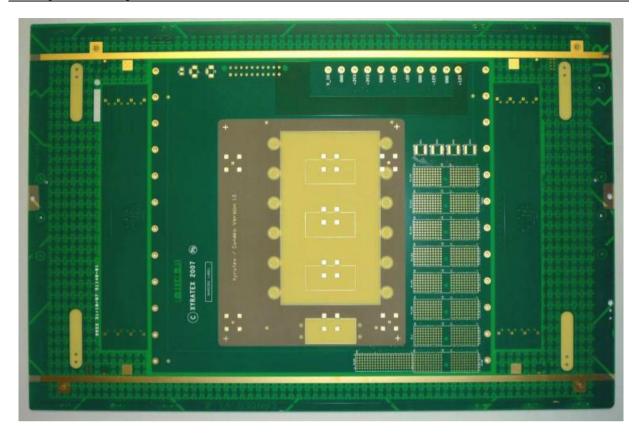

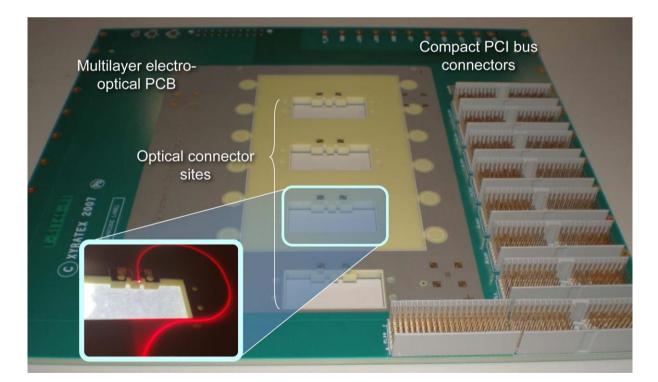

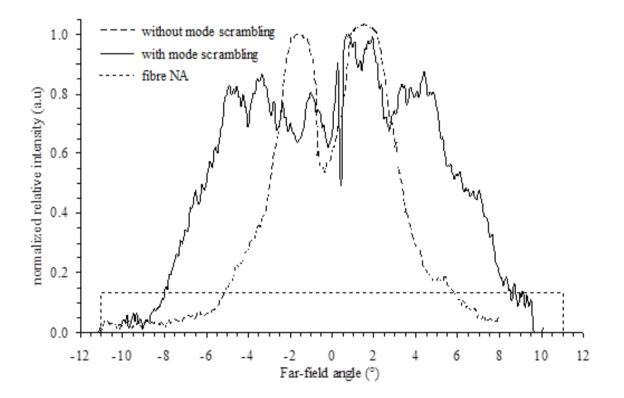

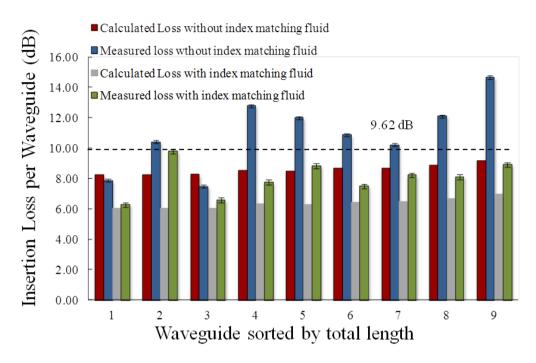

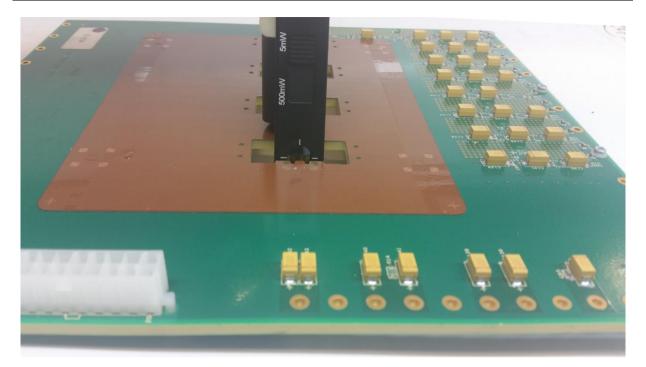

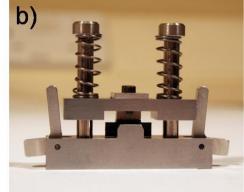

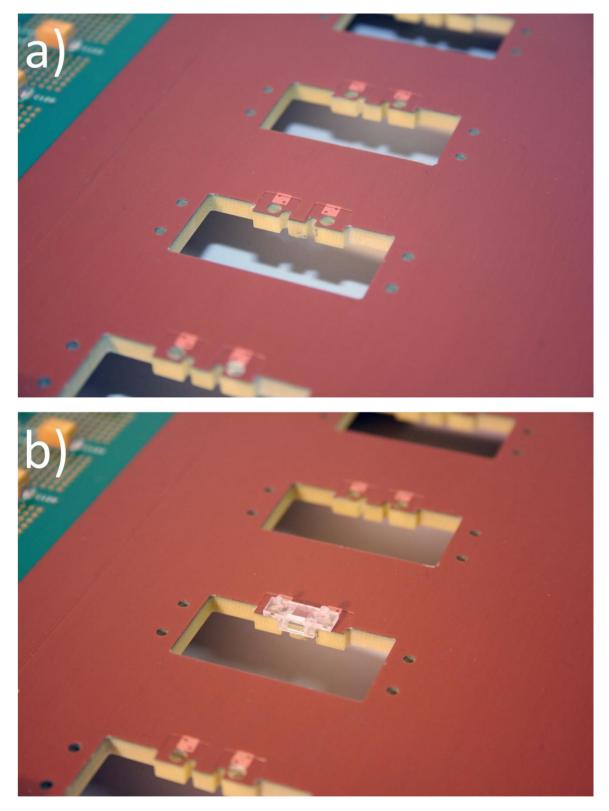

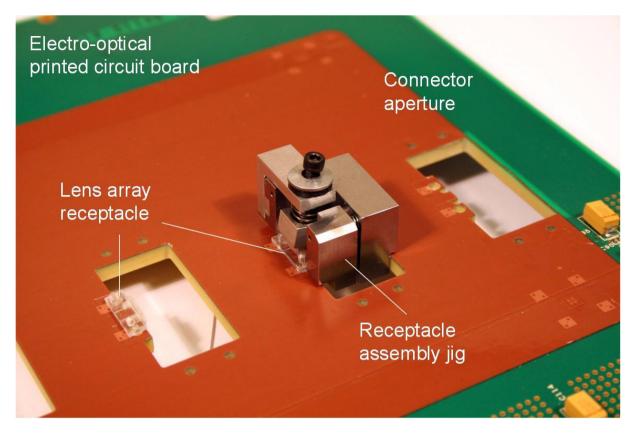

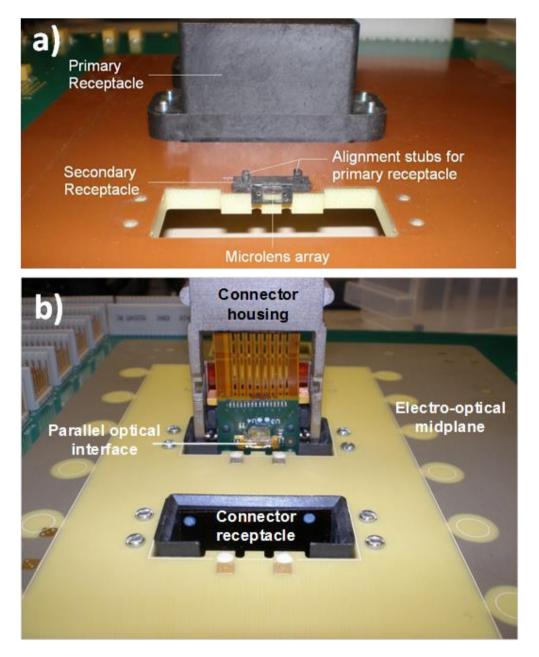

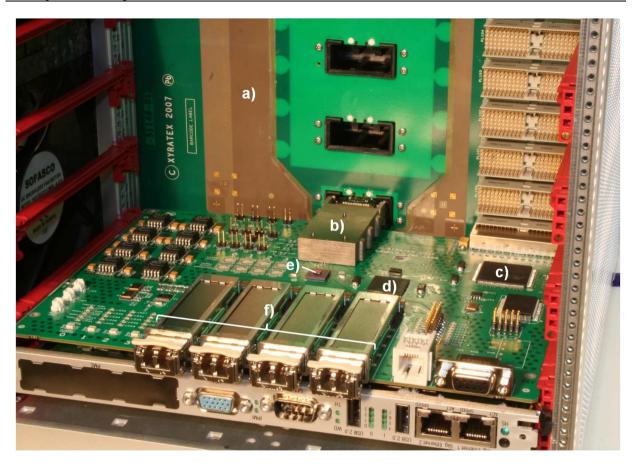

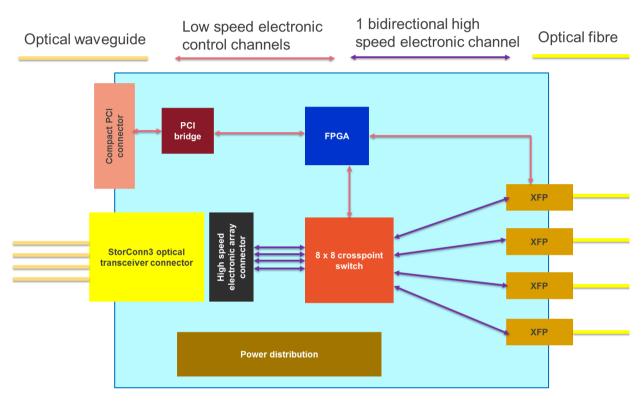

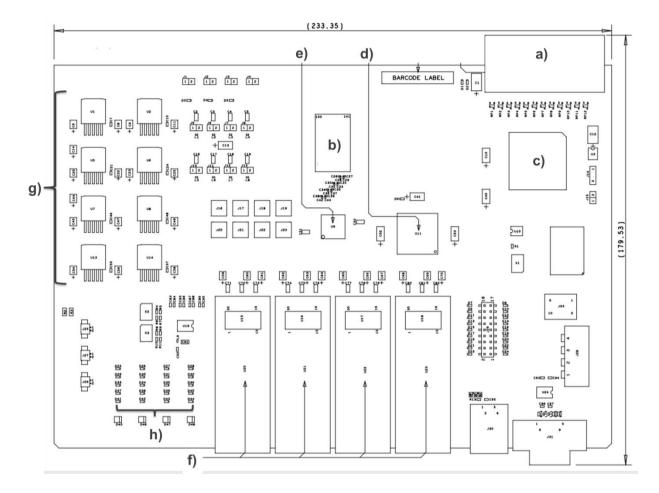

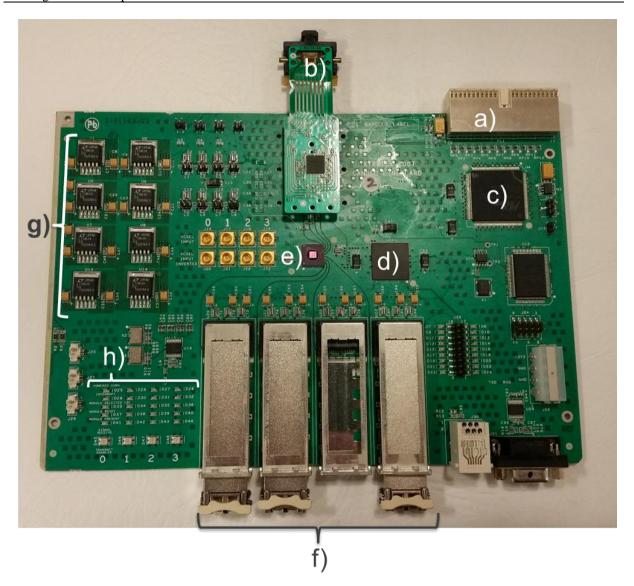

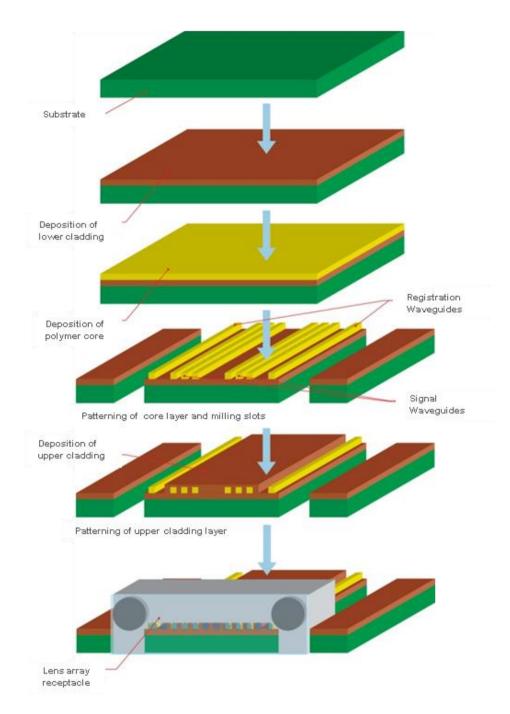

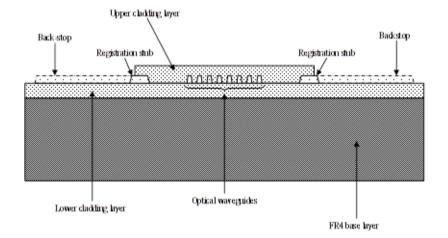

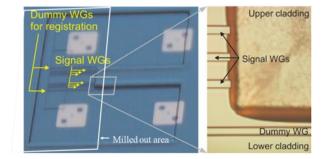

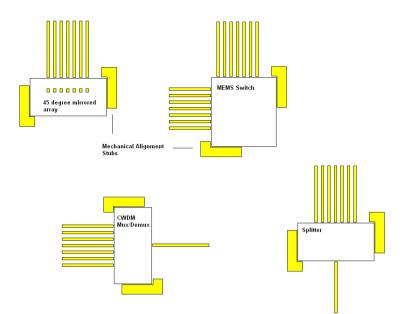

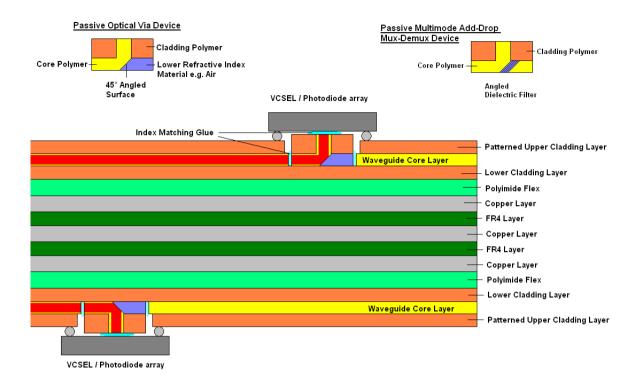

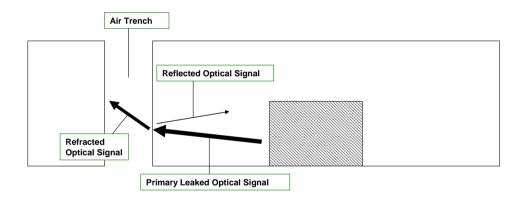

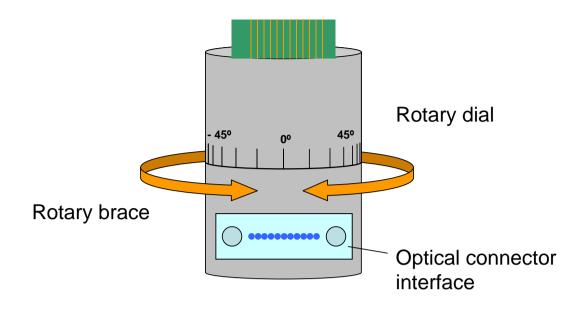

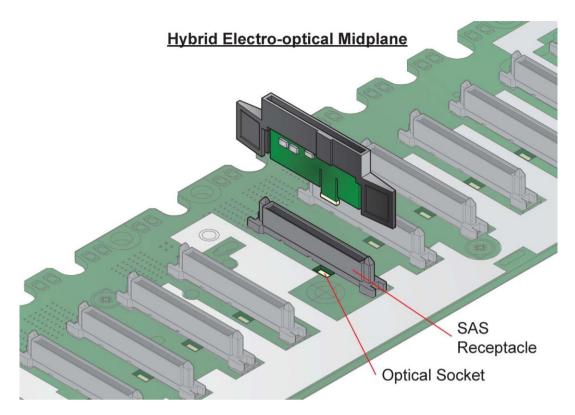

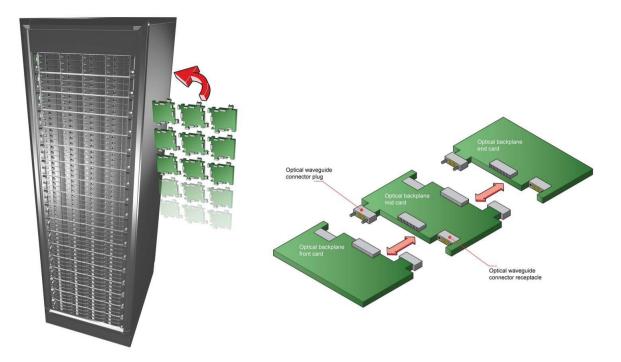

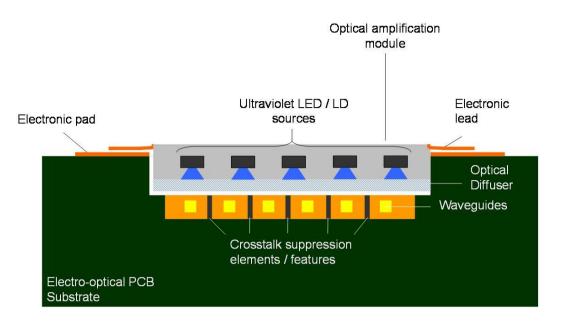

Figure 4-4: Parallel optical transceiver circuit and optical interface a) Front ramped plug, b) Optical platform guide pins, c) Optical interface, d) Flexible bridge, e) Rigid base section, f) Microcontroller, g) MT compatible alignment pins, h) Micro-lens array, i) Ouad VCSEL array, j) Ouad PIN photodiode array, k) Ouad VCSEL Figure 4-5: StorConn3 circuit board form factor .....161 Figure 4-6: StorConn3 PCB layer stack-up......162 Figure 4-7: a) Model and simulation results of optimum dual lens arrangement to image VCSEL to multimode ingress waveguide end facet predicting 0.72 dB loss in this transition, b) Model and simulation results for optimum dual lens arrangement to image egress waveguide end facet onto PD active area predicting 1.11 dB in Figure 4-9: StorConn3 component layout: a) MT compatible alignment pins, b) lead frame holding the VCSEL array and PIN photodiode array, c) quad VCSEL driver array IC, d) transimpedance amplifier/limiting amplifier TIA/LA array IC, e) microcontroller, f) rectangular slot in PCB for copper slug, g) adaptive signal equalisers, h) Figure 4-11: Custom heatsink: a) heatsink design, b) optical head section prior to heatsink attachment, c) optical Figure 4-13: Lead frame alignment: a) optical head with two MT pins protruding through the PCB, b) lead frame slots aligned over the MT pins, c) lead frame fully descended into place. During actual assembly the VCSEL Figure 4-14: Dimensioned drawings of Omron P1L lens array (Source: Omron) ......173 Figure 4-16: a) Optical transceiver circuit mounted on flexi-rigid substrate, b) Connector module housing, c) Figure 4-17: a) Optical connector during first stage of coarse engagement with OPCB connector receptacle, b) Figure 4-18: Schematic illustrating waveguide embedded in lower and upper claddings (Source: IBM Research -Figure 4-19: a) Waveguide routing pattern with four optical engagement apertures for the FirstLight Figure 4-20: Top view micrographs showing two waveguides intersecting with (a) a crossing angle of  $90^{\circ}$  and Figure 4-21: a) Schematic of optical surface scan performed on an OPCB containing up to ten laminated copper layers. b) Experimental results of optical surface scan showing height variations up to  $\pm 50 \ \mu m$ . (Source: IBM Figure 4-22: Schematic depiction of polymer layer deposition using doctor blade method. (Source: IBM Figure 4-23: Separate flexible polyimide substrate with optical polymer layers deposited and patterned. (Source: Figure 4-24: a) Waveguides measured by microscopic top view fulfil width specification of 70  $\mu$ m within  $\pm$  2  $\mu$ m. b) Waveguide heights experimentally determined by optical surface scanning satisfy target height of 70  $\mu$ m Figure 4-26: StorConnOpt3 electro-optical backplane with optical connector slots milled out and electronic CompactPCI connectors populated. A close-up view of a connector aperture is shown with a single curved Figure 4-28: Predicted and measured values for insertion loss on a group of nine waveguides on the OPCB. The Figure 4-29: Use of large area thin silicon photodetector to fit into the mid board waveguide connector interface Figure 4-30: Process to deposit smooth thin film over waveguide end facets in order to reduce coupling loss Figure 4-31: Top view of OPCB backplane with one waveguide illuminated with 650 nm light ......189 Figure 4-32: Requirements specification for FirstLight waveguide receptacle: a) waveguide receptacle with 1x12 MT compliant interface, b) waveguide array with self-alignment features and PCB machined recesses, c)

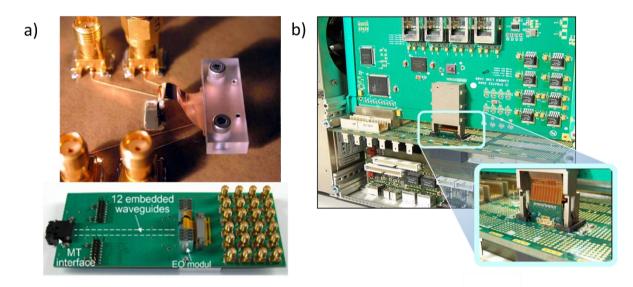

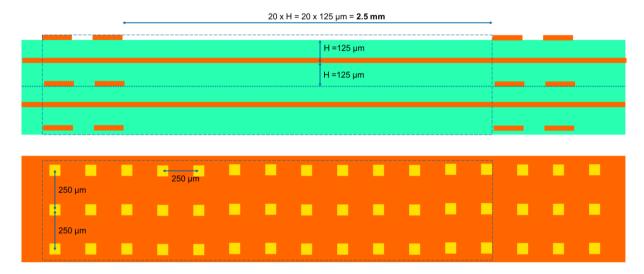

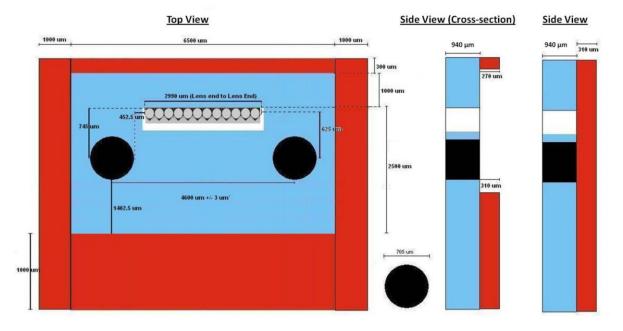

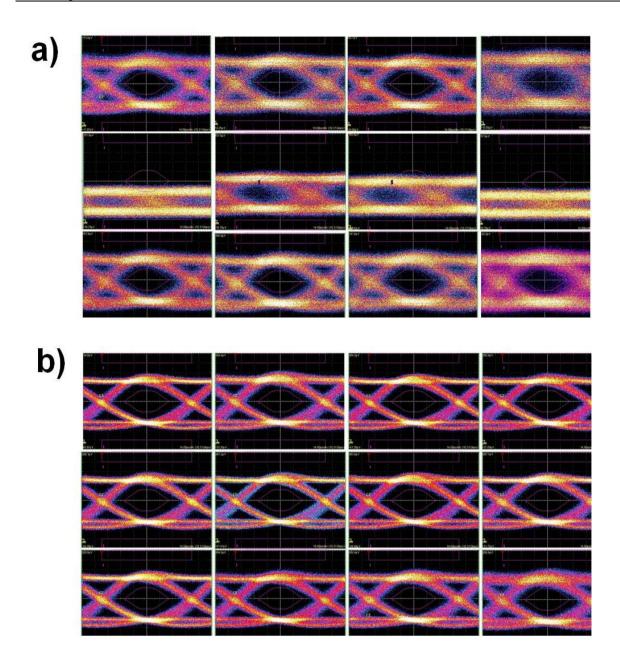

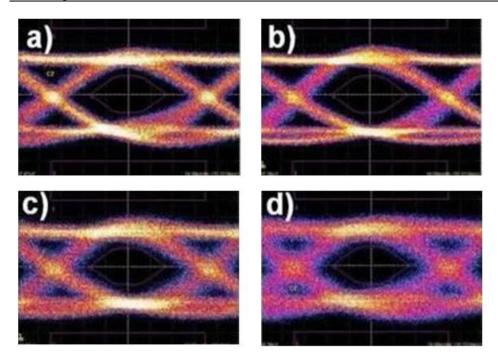

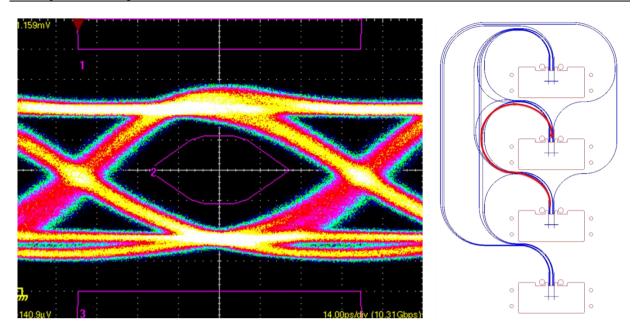

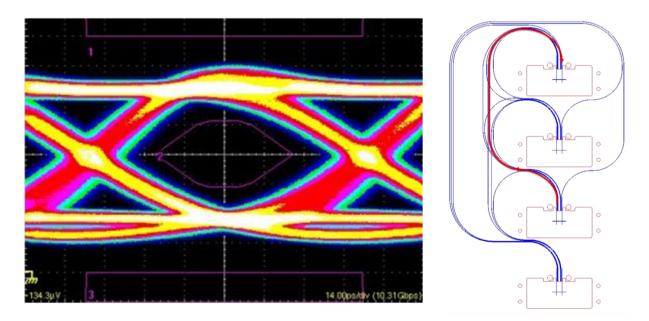

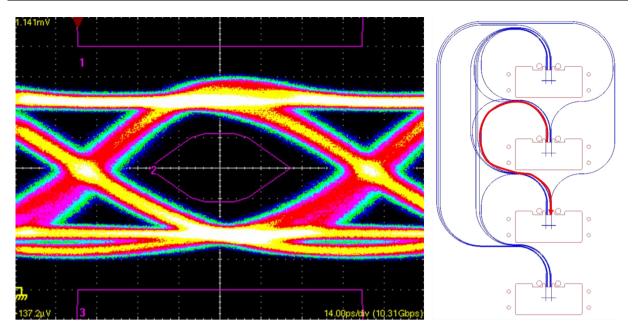

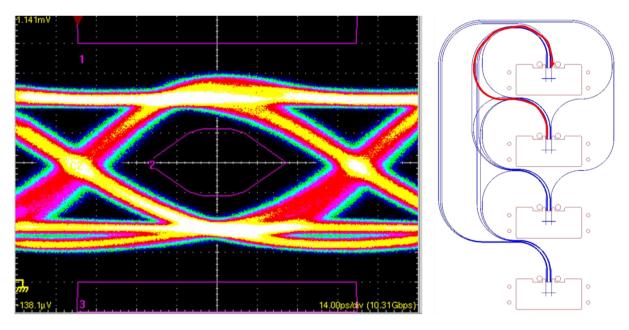

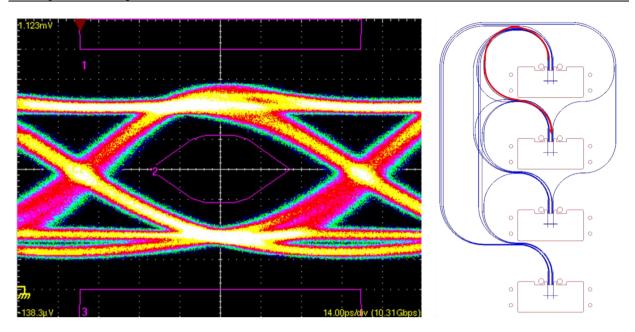

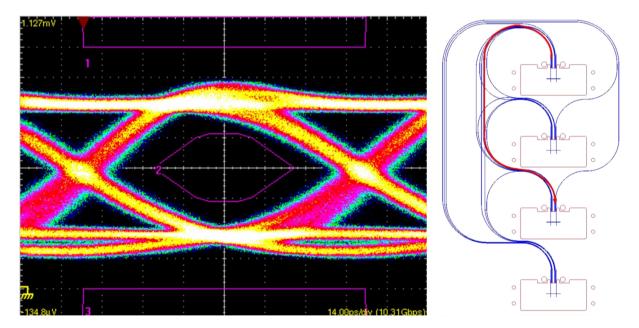

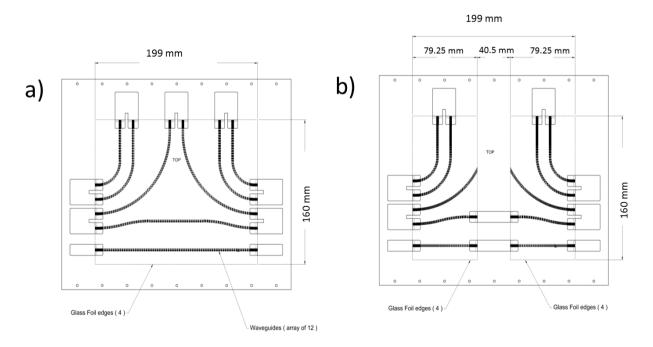

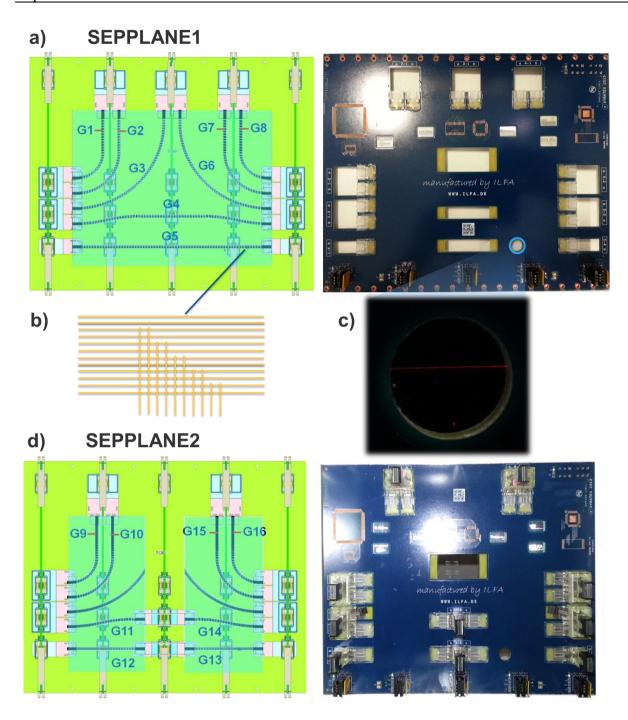

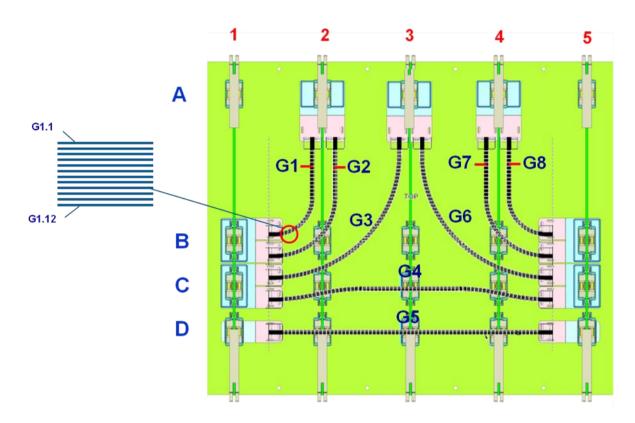

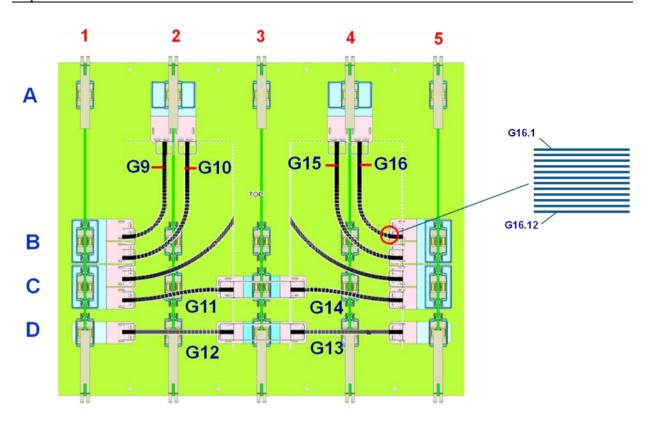

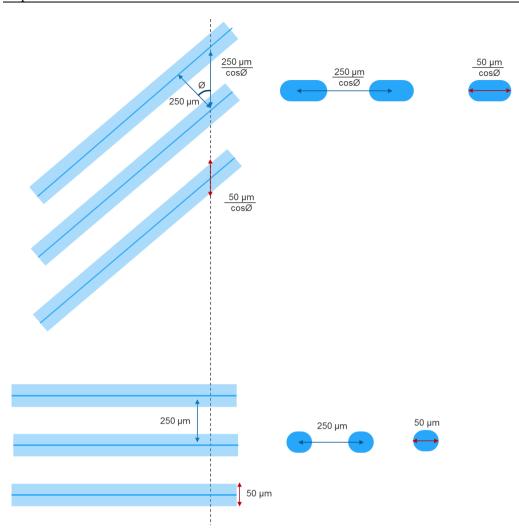

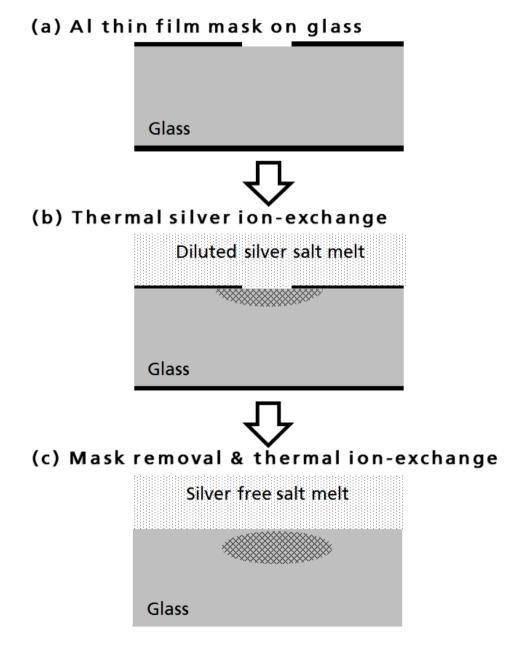

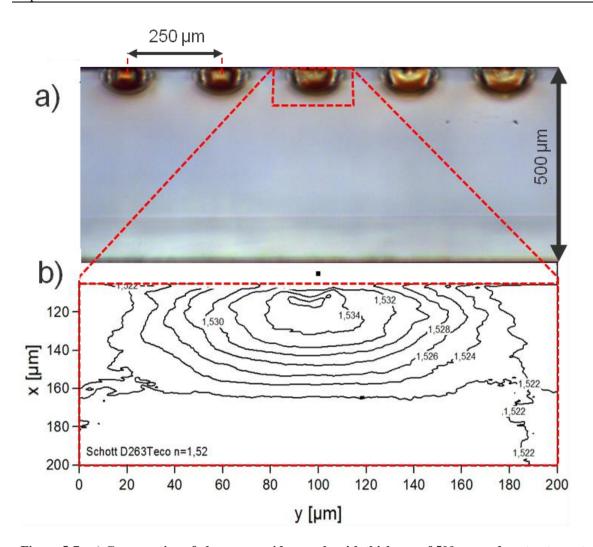

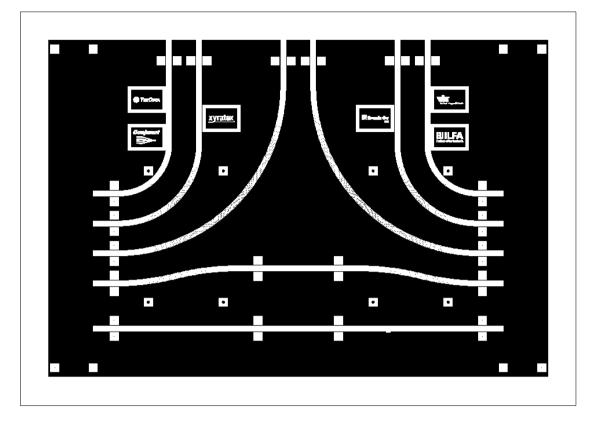

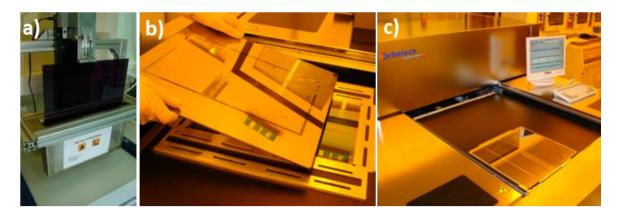

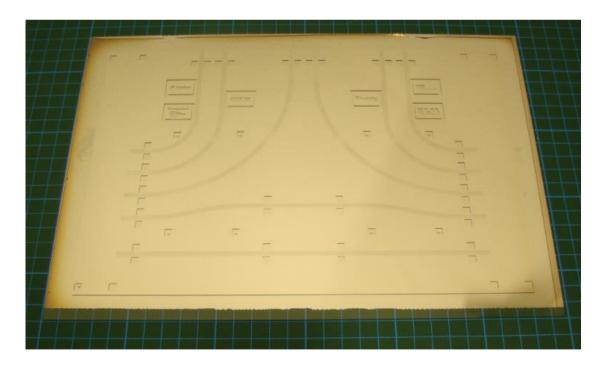

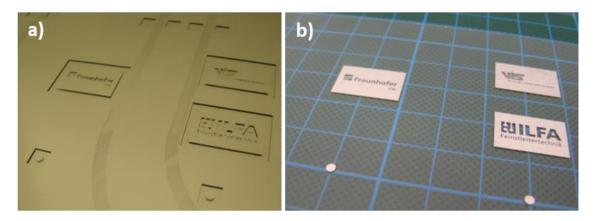

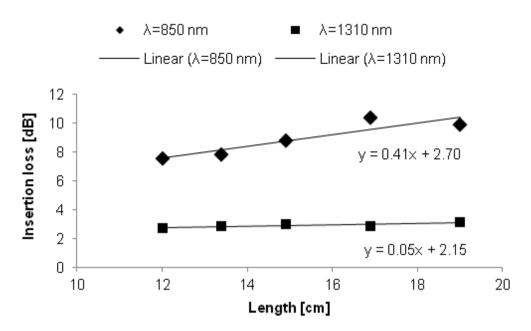

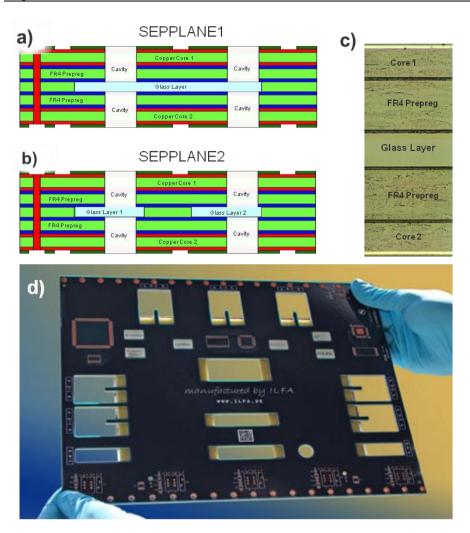

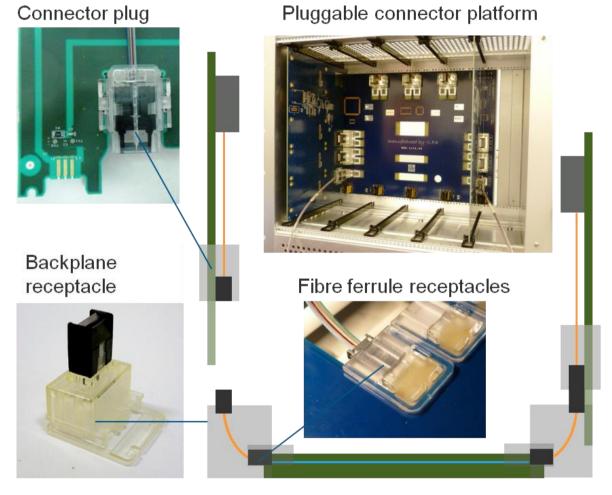

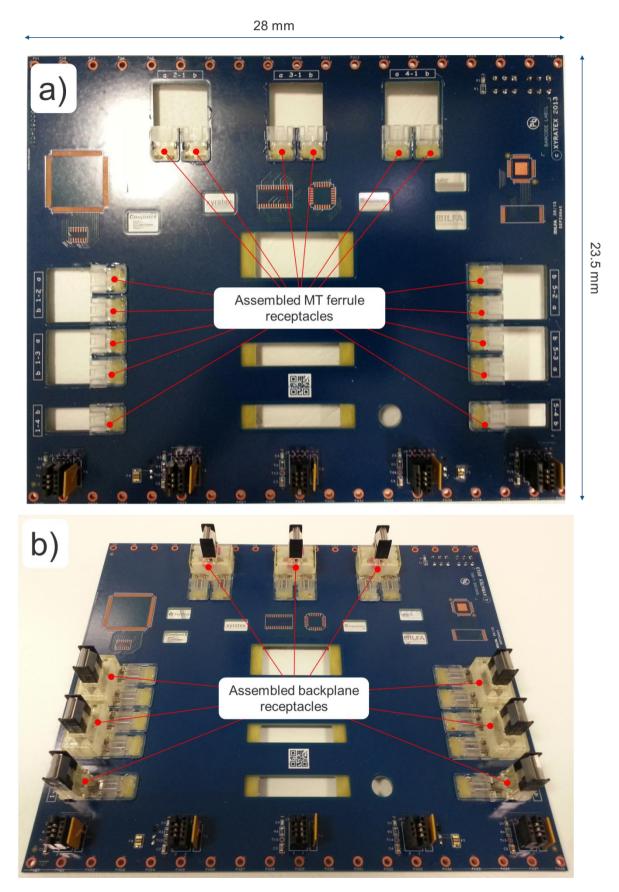

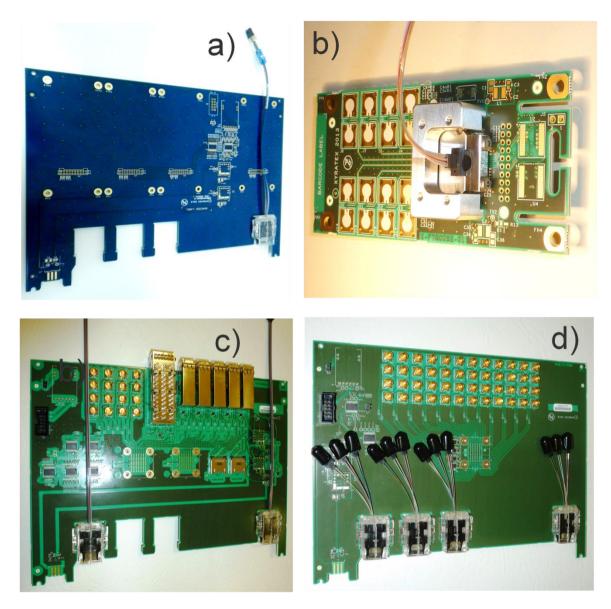

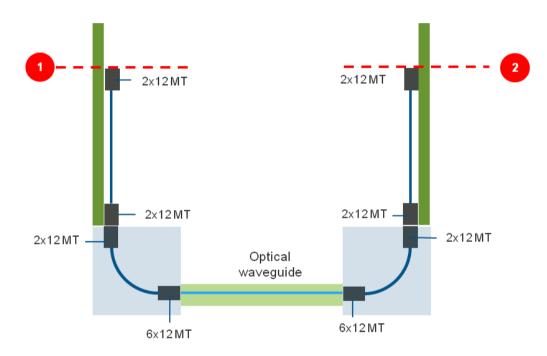

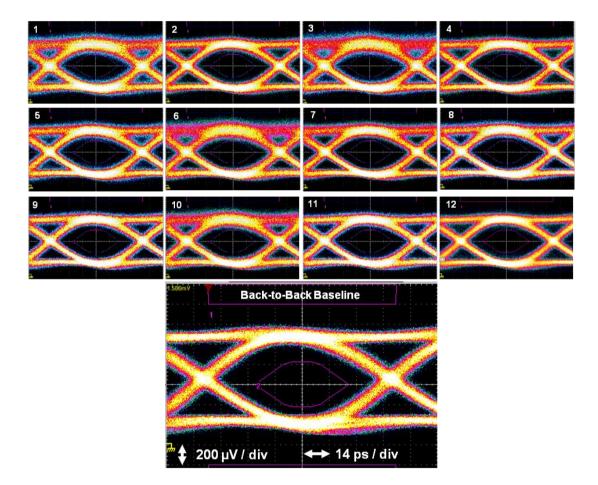

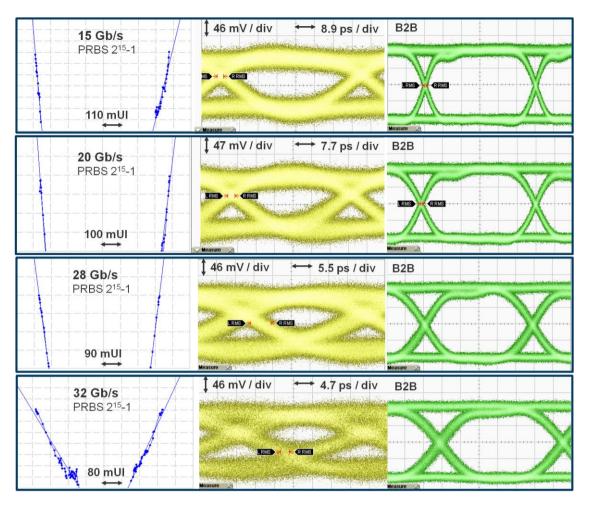

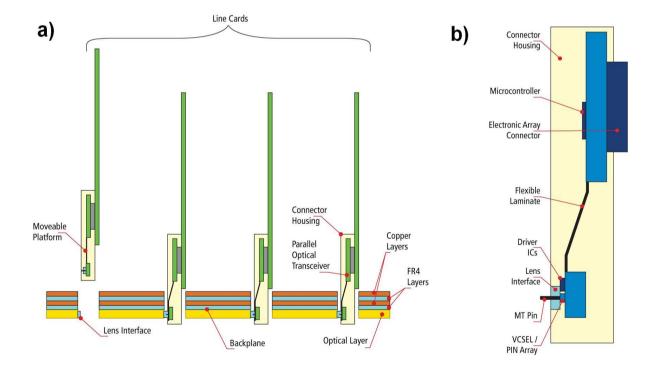

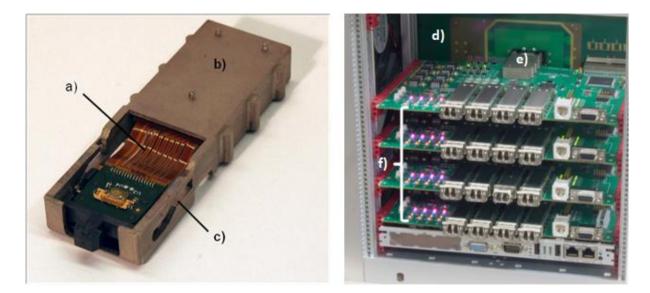

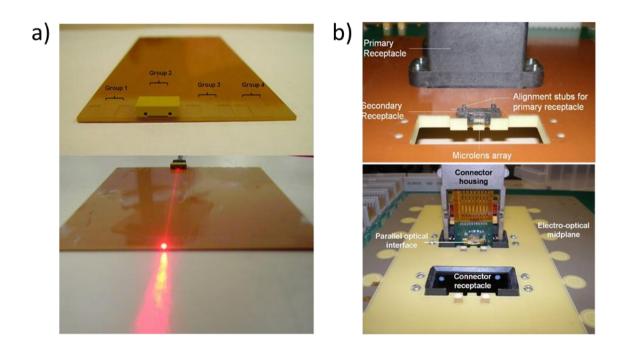

Figure 4-34: View of the PCB layout of the FirstLight waveguide interface using the Cadence Allegro PCB Figure 4-35: Photographs of upper cladding opening showing waveguides for signal transmission as well as Figure 4-36: (a) Clearance areas in upper cladding layer to provide mechanical access for optical connector Figure 4-37: Lensed waveguide receptacle front views: a) trimmed receptacle without lens array holder section, b) complete receptacle, c) complete receptacle with Omron microlens array integrated and receptacle assembled Figure 4-40: Mechanical lens assembly jig A designed to align the Omron microlens array into the custom Figure 4-41: a) OPCB waveguide interface without receptacle, b) OPCB waveguide interface with receptacle Figure 4-42: Receptacle assembly jig B required to register lensed receptacle with waveguide alignment features Figure 4-43: a) Assembly of primary receptacle and secondary receptacle in optical engagement slots, b) Pluggable optical connector prior to engagement with OPCB. Parallel MT compliant optical interface is visible Figure 4-44: Demonstration assembly with one test card inserted. a) Electro-optical backplane, b) FirstLight connector plugged into backplane receptacle, c) PCI bridge chip next to CompactPCI connector connected to electro-optical backplane providing electrical power and low speed electronic signal interface, d) FPGA to Figure 4-46: StorConnTest3 board dimensions and component layout: a) CompactPCI connector plug, b) high speed electronic array connector, c) PCI bridge chip, d) FPGA to regulate test card, e) crosspoint switch, f) four commercial XFP cages, g) linear voltage regulators to provide different voltage supplies to card components, h) Figure 4-47: StorConntest3 card with StorConn3 transceiver circuit (without connector module): a) CompactPCI connector plug, b) StorConn3 transceiver circuit, c) PCI bridge chip, d) FPGA to regulate test card, e) crosspoint switch, f) four commercial XFP cages, g) linear voltage regulators to provide different voltage supplies to card Figure 4-48: StorConnTest3 raw card stack-up ......210 Figure 4-49: FirstLight demonstration platform fully populated with all four test line cards and powered up....211 Figure 4-50: Compact PCI slot population by singleboard computer motherboard and four StorConnTest3 daughtercards. Slots C, E and G are unpopulated as the daughtercards require a separation of at least 2 slots ...212 Figure 4-52: Characterisation of optical jitter from VCSEL channel one operating 10.3 Gb/s with modulation Figure 4-54: Eye diagram of 10.3 Gb/s optical signals received from demonstration platform on selected Figure 4-55: Eye diagram of 10.3 Gb/s optical signals received from demonstration platform on selected Figure 4-56: Eye diagram of 10.3 Gb/s optical signals received from demonstration platform on selected Figure 4-57: Eye diagram of 10.3 Gb/s optical signals received from demonstration platform on selected Figure 4-58: Eye diagram of 10.3 Gb/s optical signals received from demonstration platform on selected Figure 4-59: Eye diagram of 10.3 Gb/s optical signals received from demonstration platform on selected Figure 4-60: Eve diagram of 10.3 Gb/s optical signals received from demonstration platform on selected Figure 4-61: Eve diagram of 10.3 Gb/s optical signals received from demonstration platform on selected Figure 5-2: Schematic layouts and photos of fully populated OPCB backplane variants: a) SEPPLANE1 with single glass waveguide panel and connector layout, b) iterated waveguide crossover section, c) top view of

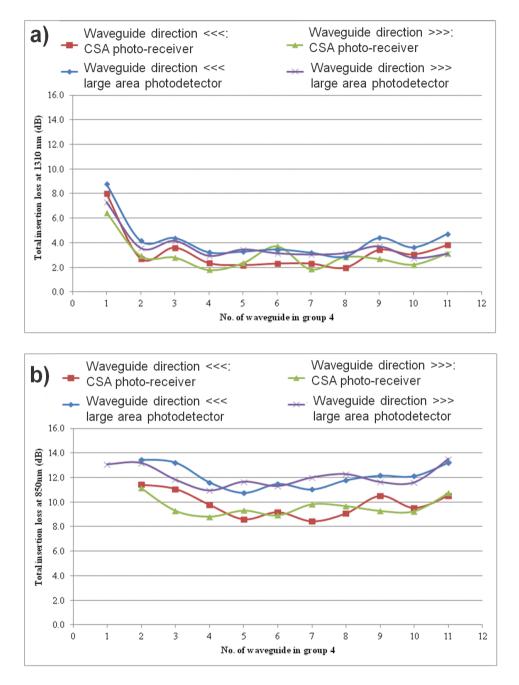

embedded glass panel showing single waveguide illuminated, d) SEPPLANE2 with dual glass waveguide panel Figure 5-3: SEPPLANE1 with waveguide groups G1 to G8, test card slots (vertical) 1-5 and connector positions A to D. Individual waveguides in each group are always numbered 1 - 12 going from top to bottom in Figure 5-4: SEPPLANE2 with waveguide groups G9 to G16, test card slots (vertical) 1-5 and connector positions A to D. Individual waveguides in each group are always numbered 1 - 12 going from top to bottom in Figure 5-5: Change of optical interface dimensions for non-orthogonal waveguide - interface intersections .....231 Figure 5-7: a) Cross-section of glass waveguide sample with thickness of 500 µm and centre-to-centre waveguide pitch of 250 µm. b) Refractive index profile at measurement wavelength of 678 nm as measured by a Figure 5-8: Layout diffusion mask on glass containing waveguide layout, partner logos and alignment marks Figure 5-9: a) Dip-coating, b) positioning mount and c) mask exposure with LDI (Source: Fraunhofer IZM)...236 Figure 5-10: Aluminium diffusion mask layer on glass panel (297 x 210 mm<sup>2</sup>) (Source: Fraunhofer IZM)......236 Figure 5-11: a) Detail of mask layer on glass, b) protected partner logos and fiducial marks after removing Figure 5-12: Propagation loss and coupling loss measurements based on best fitting line of cut-back Figure 5-13: Glass foil laminated into PCB stack-up with conventional hot lamination technique shows bulging Figure 5-14: a) SEPPLANE1 stack-up with one single panel optical and two electrical packages with solder mask, b) SEPPLANE2 stack-up with one dual panel optical and two electrical packages, c) Photo of OPCB Figure 5-15: Complete pluggable connection system comprising connector plug on connecting edge of Figure 5-16: a) MT ferrule receptacle made of polycarbonate material, b) exposed dual glass waveguide array interfaces, c) front view of waveguide array interface with MT compliant receptacle port assembled, d) vertical offset between MT pins datum and waveguide array, e) dual ferrule mounts with MT fibre jumper plugged into Figure 5-17: a) Pluggable connector assembled on card edge (front view), b) rear view of pluggable connector showing fibre ribbon from internal MT ferrule, c) pluggable connector and receptacle head, d) connector plugs assembled on edge of test daughtercard, e) 4 variants of full backplane receptacle with receptacle head (black) in Figure 5-18: OPCB backplane type SEPPLANE 1 with ferrule receptacles and jumpers populated, a) schematic view of ferrule receptacle populated with MT terminated fibre ribbon, b) schematic view of dual edge board fibre jumper (connecting to 2 adjacent interfaces), c) schematic view of dual mid-board fibre jumper (connecting Figure 5-19: Ferrule receptacle assembly process steps: a) backplane suspended in ficonTEC assembly rig, b) active launch fibre alignment with 3-axis translation stage, c) active detection fibre and ferrule receptacle alignment with 5-axis translation stage, d) MT ferrule receptacle glued in place, e) fibre patch cord plugged into Figure 5-20: a) SEPPLANE1 after assembly of all MT ferrule receptacles, b) SEPPLANE1 after assembly of all Figure 5-21: Two test and measurement platforms SEPDEM1 and SEPDEM2......255 Figure 5-22: SEPIANet test cards: a) SEPTEST1 test card with vacant slots for mezzanine cards and populated with 1 edge connector plug, b) SEPTEST1C mezzanine card populated with alignment brace and MT patchcord attached, c) SEPTEST2 populated with 2 edge connector plugs, d) SEPTEST3 fully populated with 4 edge Figure 5-24: Bidirectional insertion loss on SEPPLANE1 - waveguide group 4 in both directions as recorded directly using a large area photodetector and CSA: a) at 1310 nm, b) at 850 nm. Propagation direction >>> signifies propagation from left to right along a given waveguide as viewed from the top of the backplane, while Figure 5-25: Schematic view of complete daisy chained link under test through both SEPDEM1b and Figure 5-26: a) Bidirectional insertion loss and b) jitter measurements at 1310 nm as measured through daisychained link over both demonstration platforms, through SEPPLANE1b G2 in propagation direction 2A -1B and through SEPPLANE2a G12 in propagation direction 3D-1D......264

Figure 5-27: Eye diagrams measured through SEPPLANE1b G2 in propagation direction 2A-1B and through SEPPLANE2a G12 in propagation direction 3D-1D......265 Figure 5-28: Correlation between glue contamination pattern on waveguide interfaces and bidirectional insertion Figure 5-29: Eye diagrams for 10.3 Gb/s with PRBS 2<sup>31</sup>-1 test signal conveyed at 1310 nm over all 12 Figure 5-30: BER bathtub curves and eye diagrams for 850 nm optical test signals conveyed through full optical connector and waveguide link and corresponding B2B profiles. The increased degradation observed on the 32 Gb/s profile is partly due to a reduced power budget and insufficient light being received to resolve a clean eye Figure 6-1: (a) Electro-optical midplane connection scheme; active pluggable connectors housed on the edge of Figure 6-2: a) Optical transceiver circuit mounted on flexi-rigid substrate, b) Connector module housing, c) Grooves to enable required movement of optical interface during mating process, d) Electro-optical midplane in FirstLight demonstration platform fully populated with all 4 test line cards and powered up, e) Connector module Figure 6-5: Photographs of upper cladding opening on FirstLight electro-optical midplane showing waveguides Figure 6-8: Various passive and active optical components which are passively aligned into optical sockets and Figure 6-9: Electro-optical printed circuit board with optical sockets housing optical transceiver devices and out-Figure 6-16: FirstLight electro-optical midplane with optical connector slots milled out and electronic CompactPCI connectors populated. A close-up view of a connector aperture is shown with a single curved Figure 6-18: Orthogonal optical connector with alignment rails and grooves. A free space lens coupling system Figure 6-23: a) Optical amplification node in which optical waveguides are brought together for collective Figure 7-1: IEC polymer MT (PMT) ferrule standard for the termination of optical waveguides a) PMT connector components, b) PMT connector structure after assembly, c) photo of commercial PMT assembled onto Figure 7-2: Firstlight precision alignment concept deployed in singlemode polymer waveguide connectorisation -a) precision alignment concept diagram from Pitwon patent [171], b) shadowgraph photo of precision alignment of an MT compliant Storlite receptacle passively aligned to an array of multimode waveguides, c) concept diagram for silicon V-groove to singlemode polymer waveguide [145], d) photo of silicon V-groove Figure 7-3: Excerpts from published passive alignment patent showing slanted registration guides a) straight passive alignment features will require clearance, b) slanted alignment features will require clearance however

# LIST OF TABLES

| Table 1-1: Serial Attached SCSI protocol generations                                                                   | 20  |

|------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1-2: PCI Express protocol generations                                                                            | 22  |

| Table 1-3: Fibre Channel protocol generations                                                                          | 23  |

| Table 2-1: Strategic purchases by optical connector companies of mid-board transceiver start-ups                       | 40  |

| Table 2-2: Survey of commercial midboard optical engine technologies                                                   | 41  |

| Table 3-1: Storlite card designations                                                                                  | 75  |

| Table 3-2: Component layout and description                                                                            | 86  |

| Table 3-3: Optical waveguide testbed attributes                                                                        |     |

| Table 3-4: StorConnTest2 component listing                                                                             | 121 |

| Table 3-5: StorConnTest2 User Interface ASCII Command Format                                                           | 127 |

| Table 3-6: StorConnTest2 Microcontroller ASCII Command Exchange                                                        | 128 |

| Table 3-7: StorConnPwr2 component listing                                                                              | 132 |

| Table 3-8: Test conditions to estimate BER on a 10 Gb/s signal from error counts with a 99% confidence le              | vel |

| ~<br>                                                                                                                  |     |

| Table 3-9: Waveguide end facet characterisation                                                                        | 148 |

| Table 4-1: Storlife card designations                                                                                  |     |

| Table 4-2: StorConn3 component list and description                                                                    |     |

| Table 4-3: StorConnTest3 key component listing                                                                         |     |

| Table 5-1: Insertion, propagation and bend losses at 1310 nm of waveguide groups in SEPPLANE1 panel                    |     |

| dependent on bend radii and launching condition (Source: Fraunhofer IZM)                                               | 240 |

| Table 5-2: Summary of insertion loss as measured on all backplanes with 1310 nm and 850 nm optical test                |     |

| signals modulated at 10.3 Gb/s. The standard deviation of each measurement set is also shown to provide at             | n   |

| indication of the measurement spread and variability of results due to contamination                                   |     |

| Table 5-3: Summary of peak to peak jitter as measured on all backplanes with 1310 nm and 850 nm optical                |     |

| signals modulated at 10.3 Gb/s. The standard deviation of each measurement set is also shown to provide at             |     |

| indication of the measurement spread and variability of results due to contamination                                   | 269 |

| Table 6-1: Summary of filed patents                                                                                    |     |

| Table 9-1: PCI command map - PCI write and read command set for general static control status lines                    |     |

| Table 9-2: PCI command sequence example - general IO PCI commands                                                      | 351 |

| Table 9-3: PCI command sequence - execute read of XFP I <sup>2</sup> C memory device                                   |     |

| Table 9-4: PCI command sequence - read back contents of previous read instruction                                      |     |

| Table 9-5: PCI command sequence - execute write to XFP I <sup>2</sup> C memory device                                  |     |

| Table 9-6: PCI command sequence - CPS write sequence to configure switch                                               |     |

| Table 9-7: PCI command sequence - CPS read sequence to read switch configuration                                       |     |

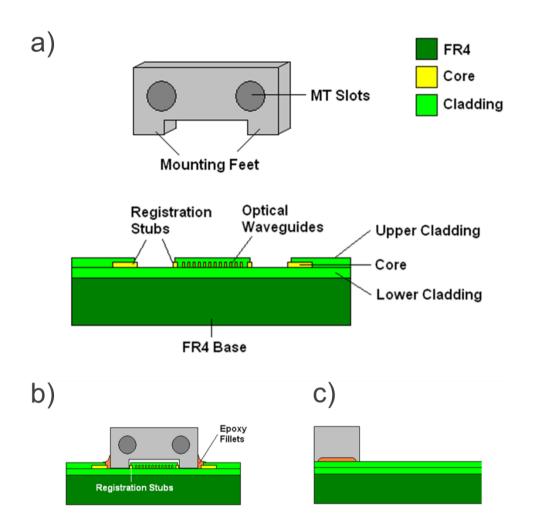

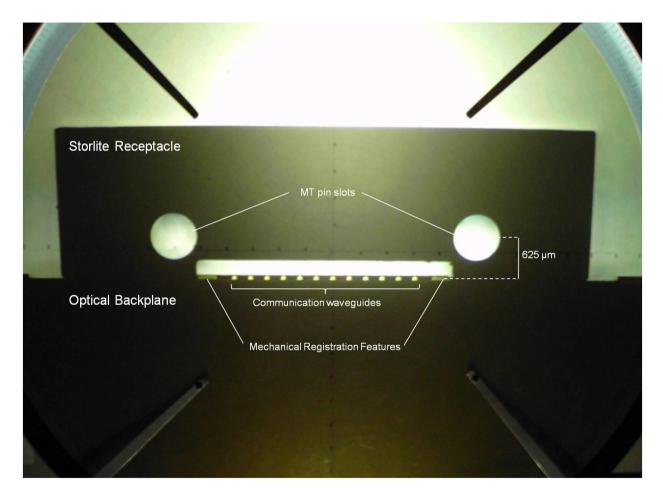

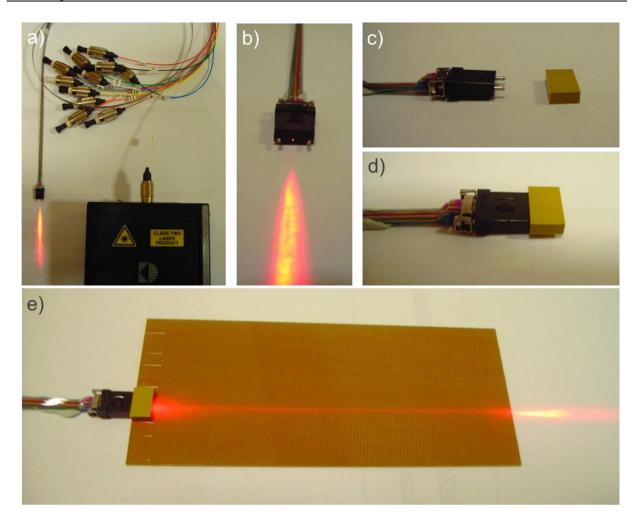

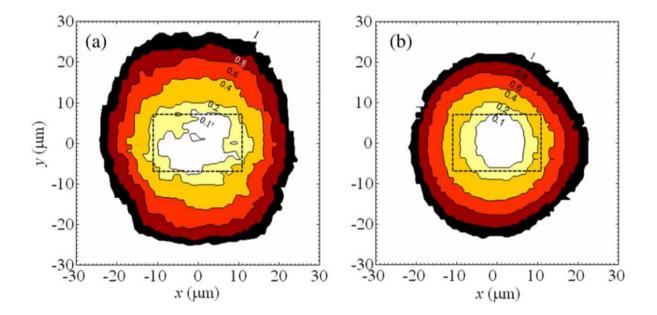

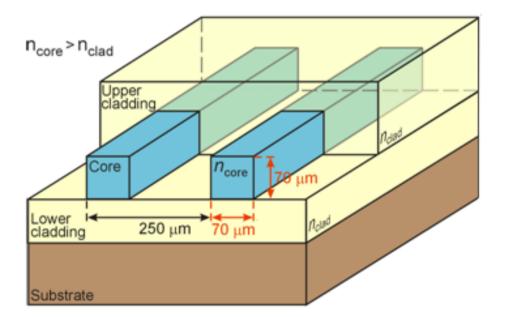

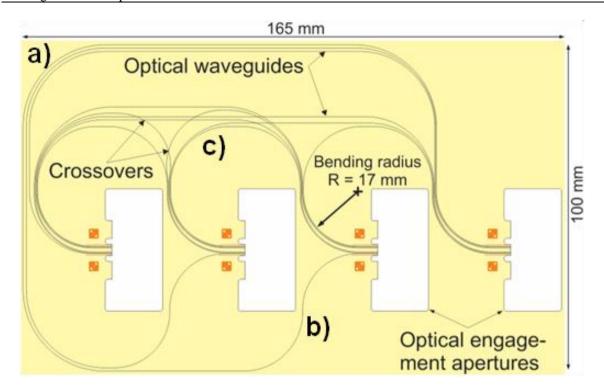

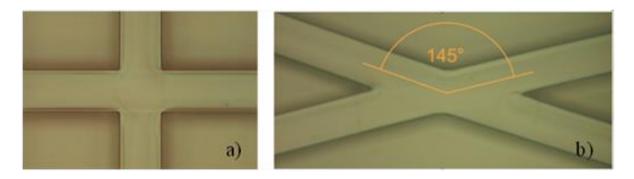

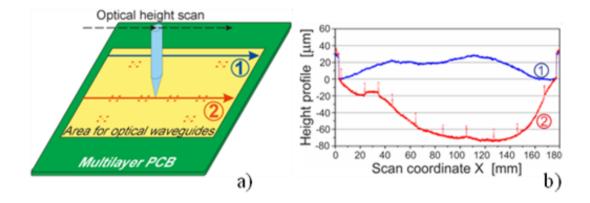

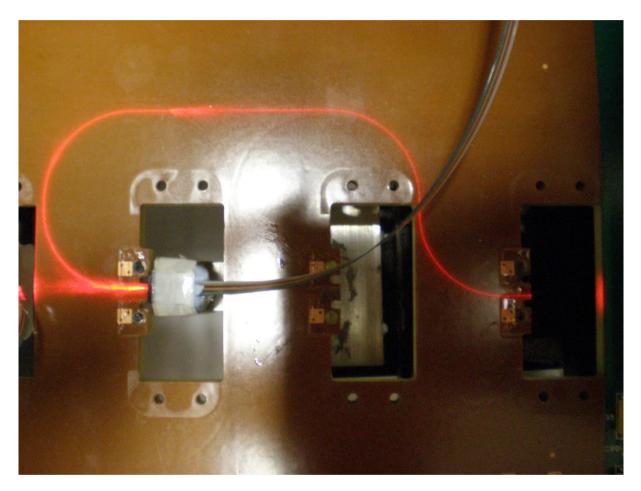

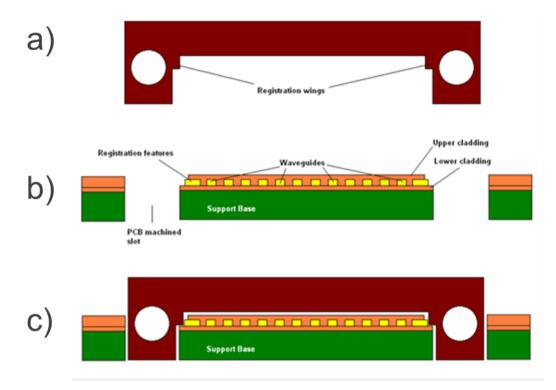

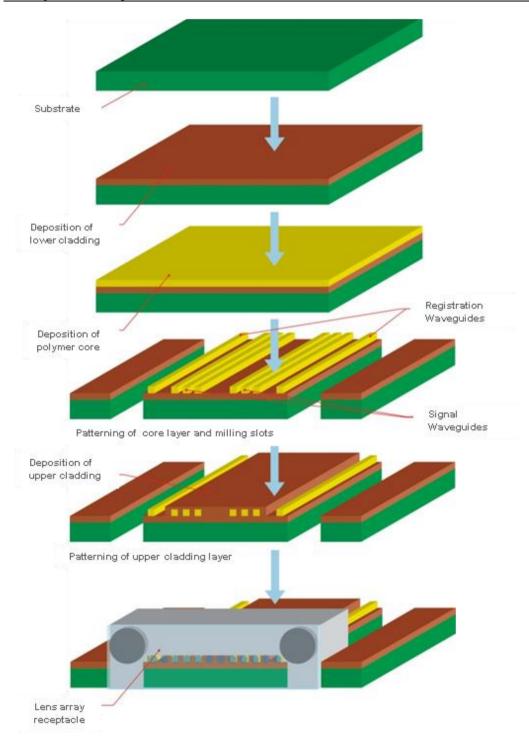

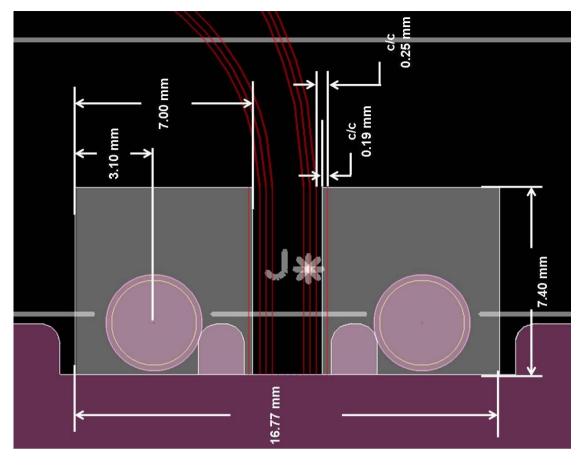

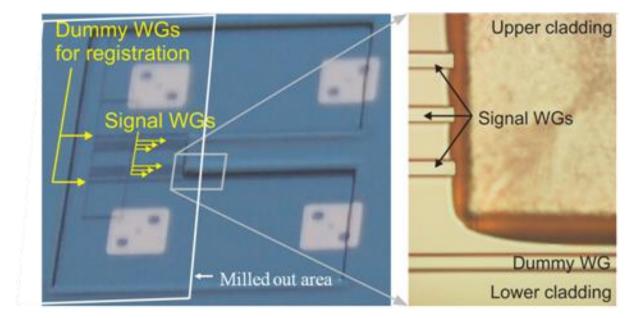

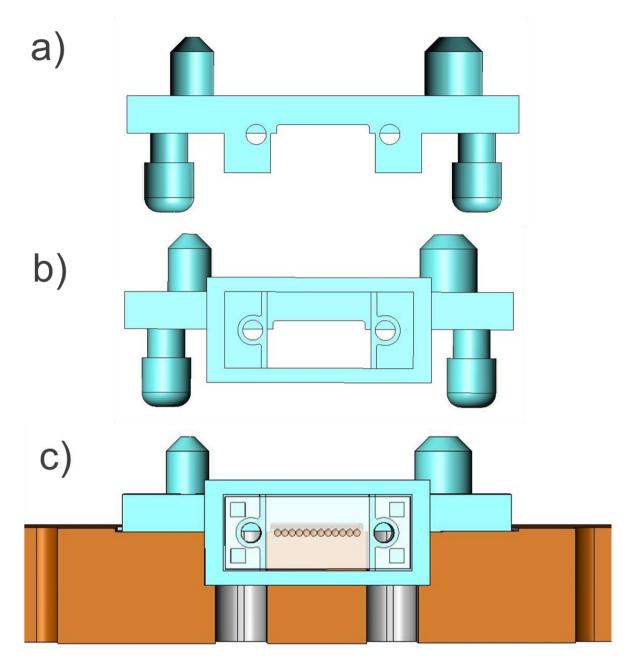

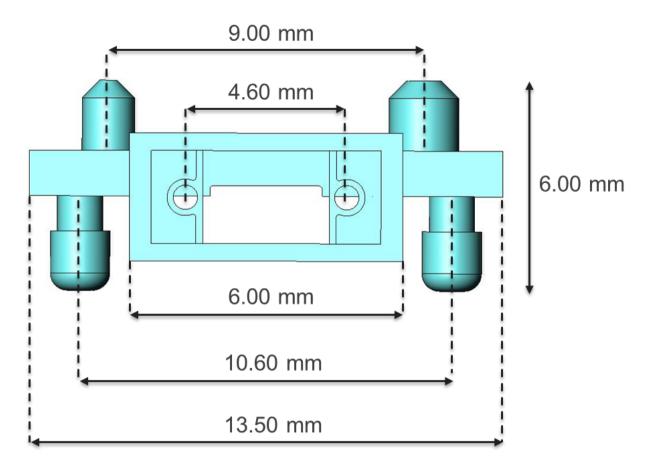

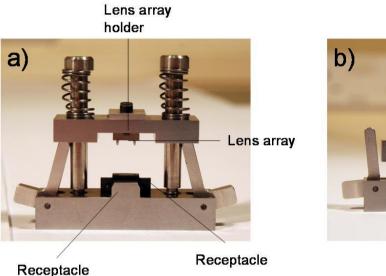

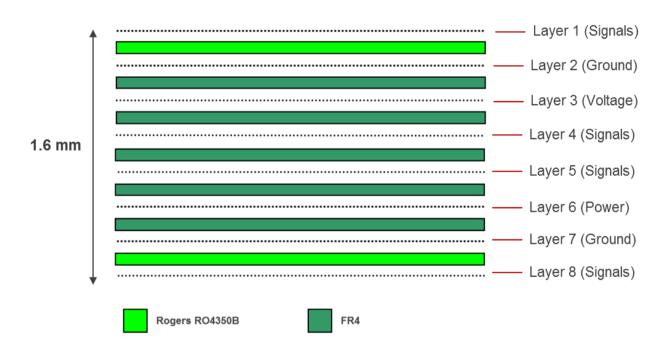

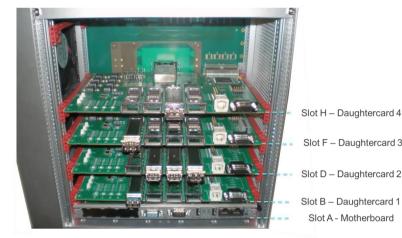

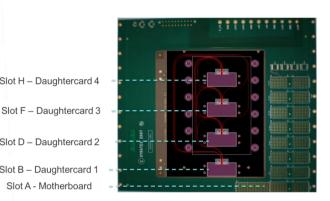

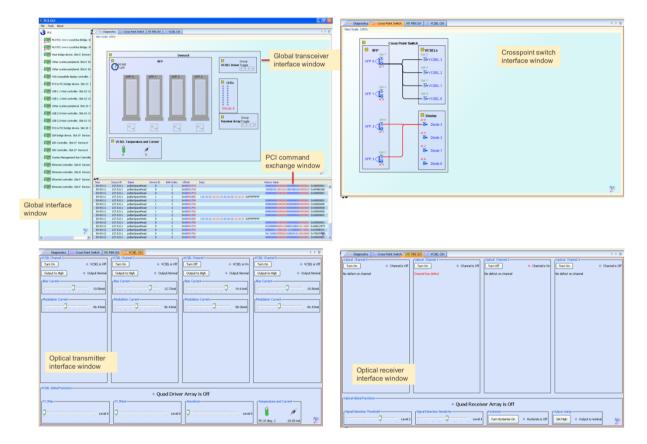

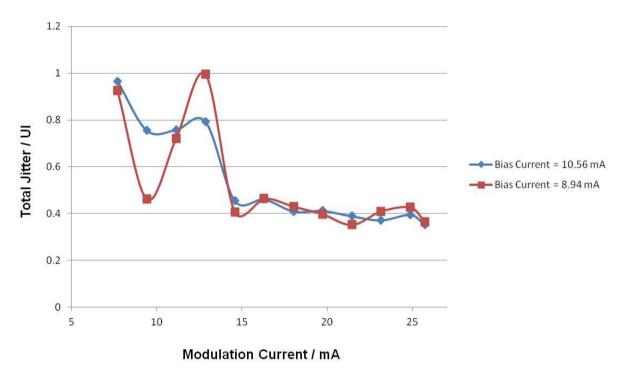

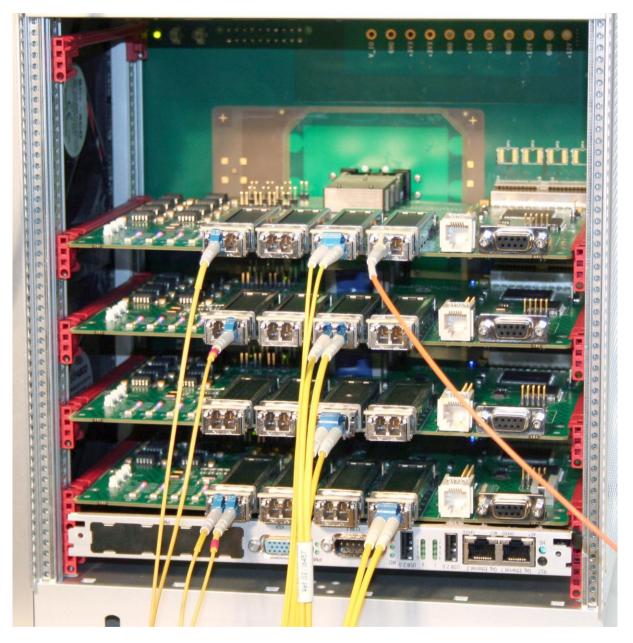

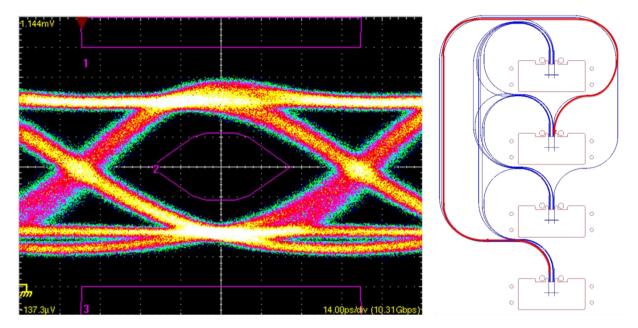

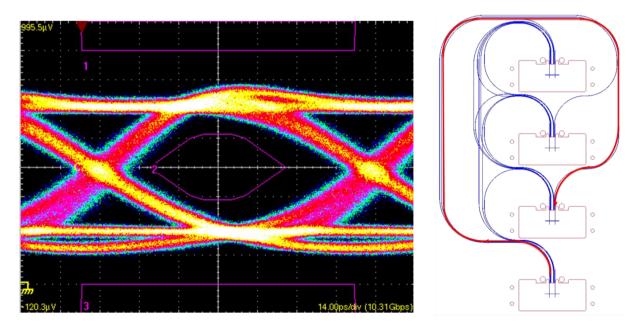

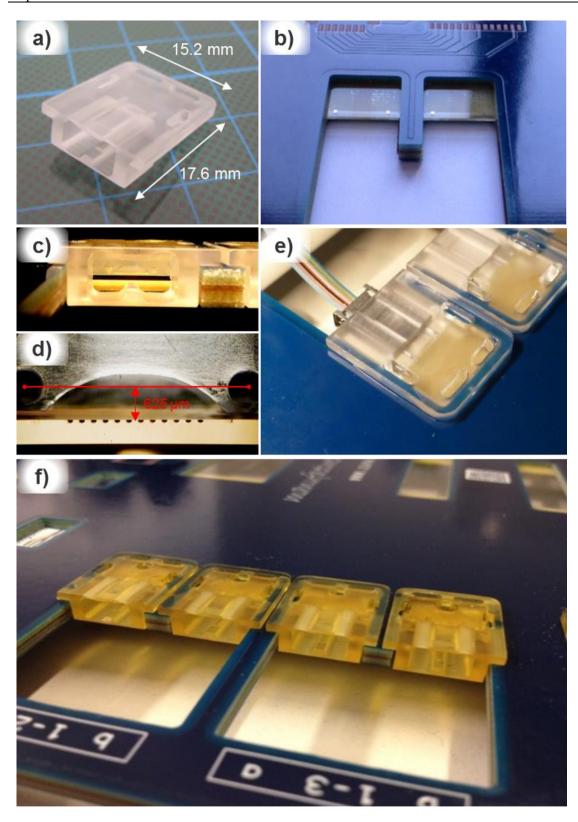

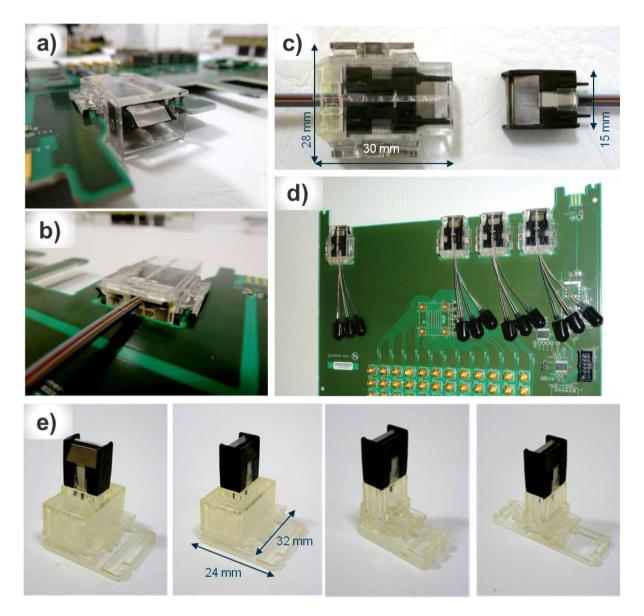

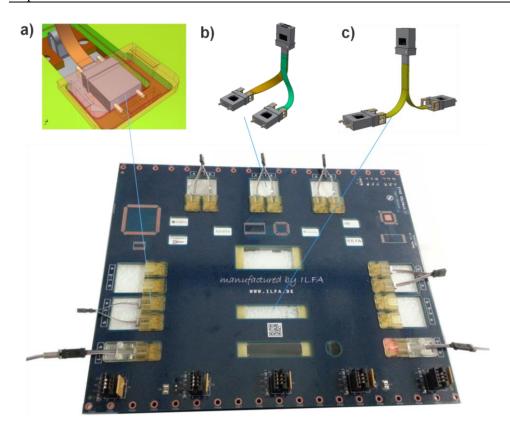

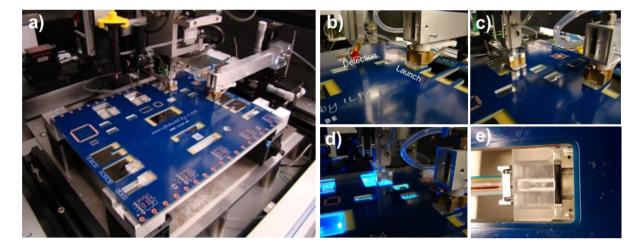

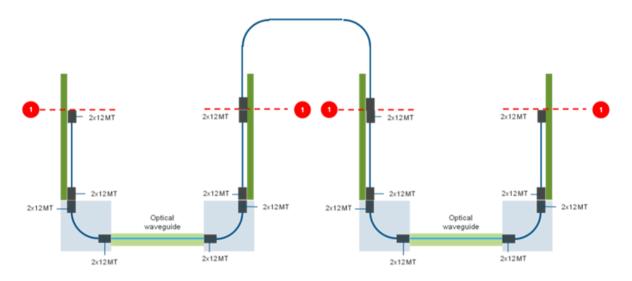

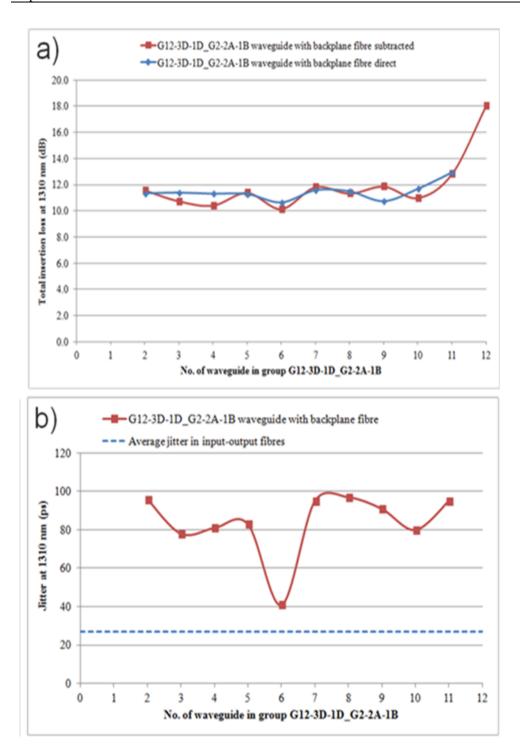

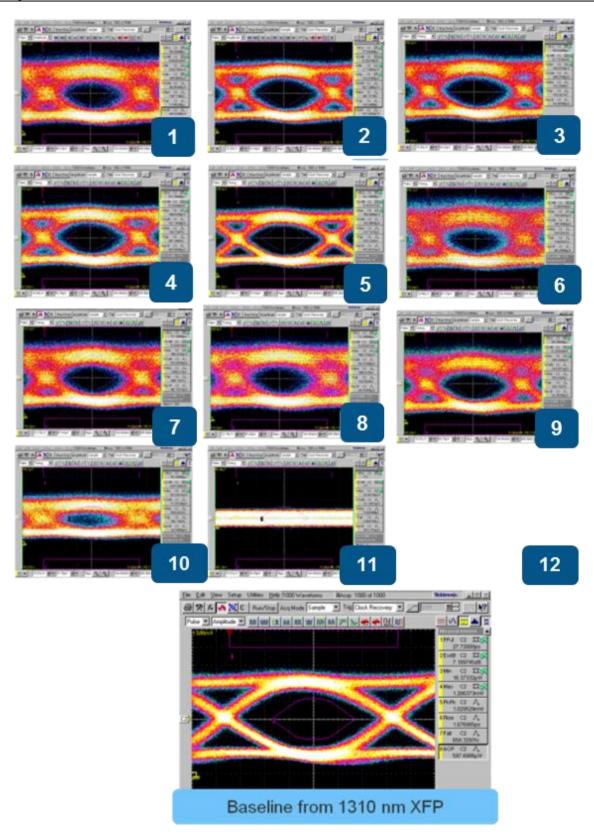

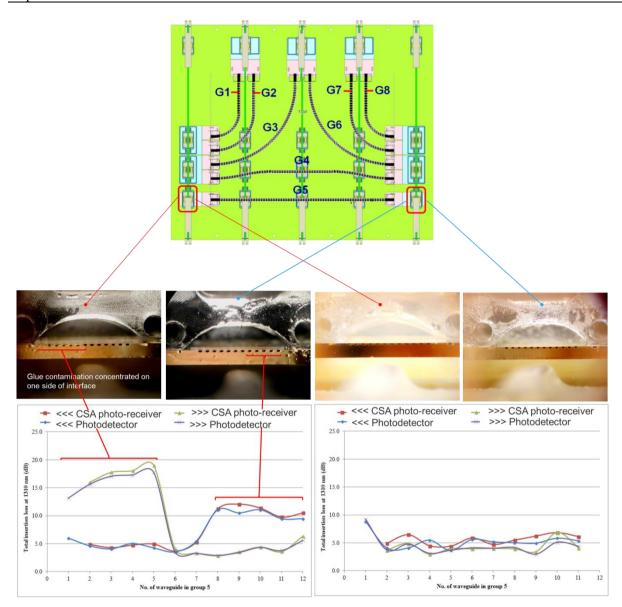

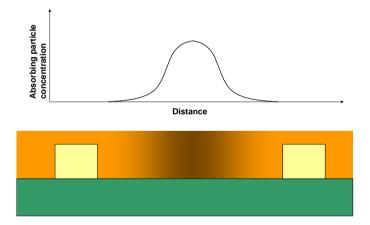

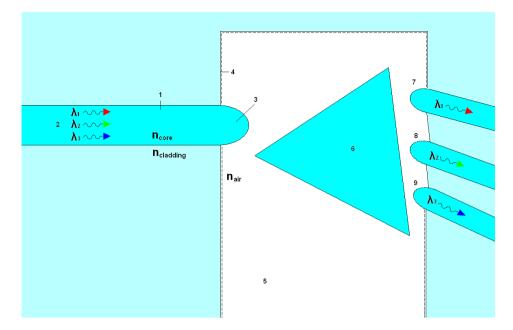

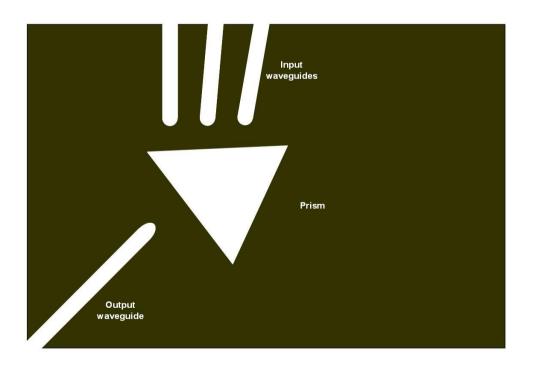

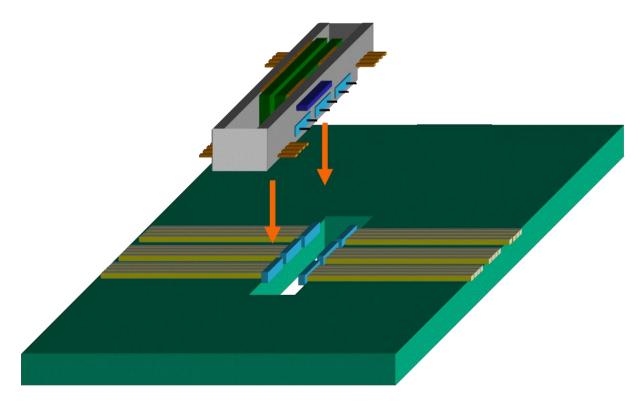

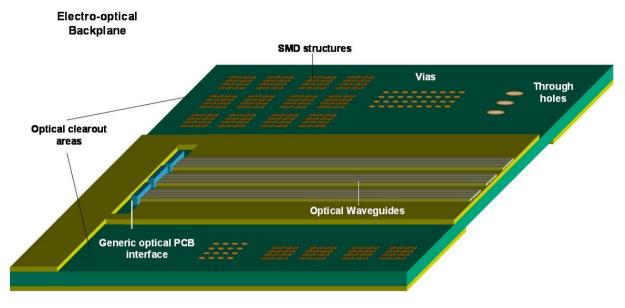

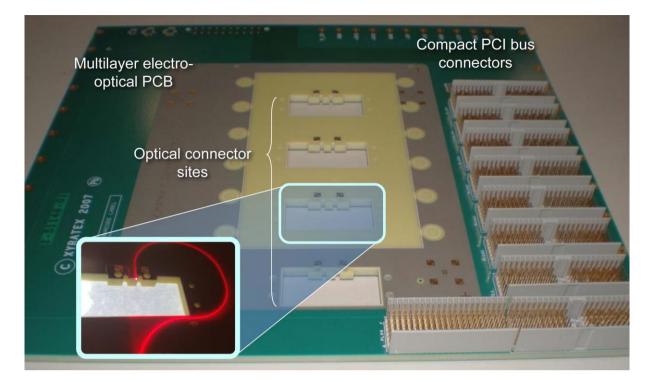

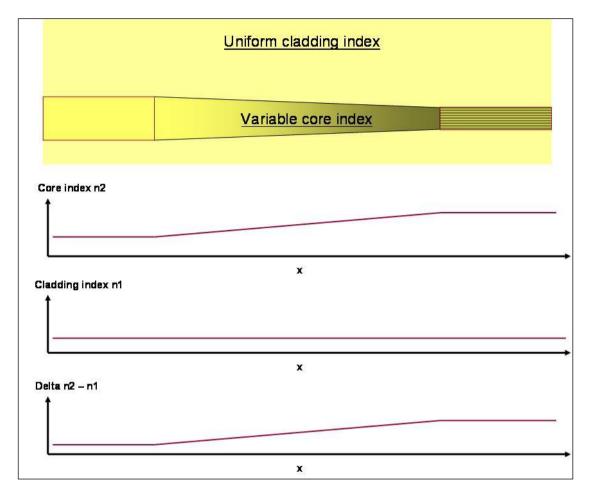

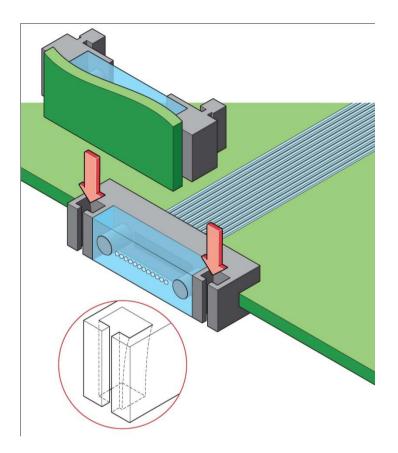

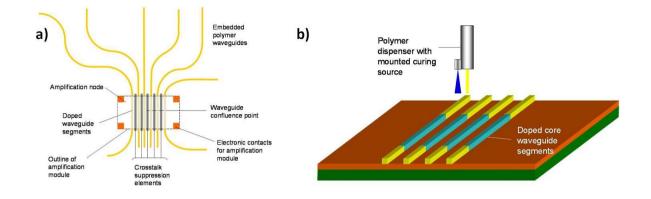

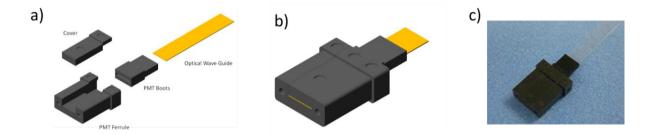

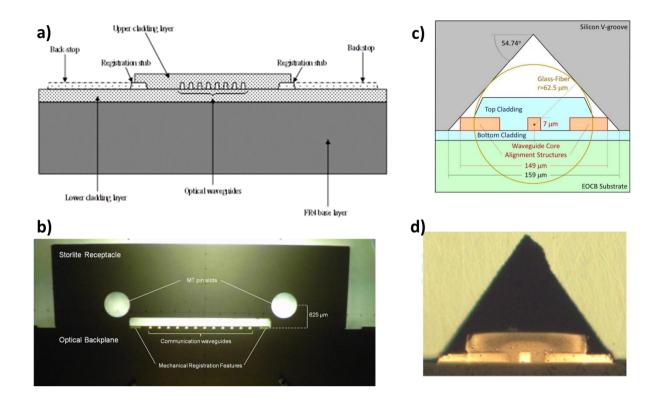

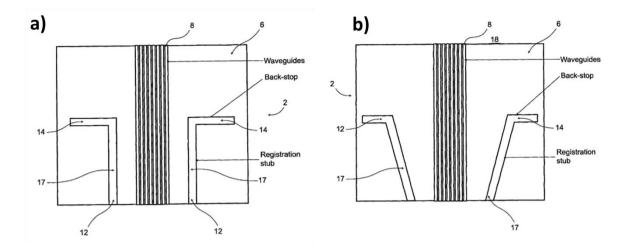

| Table 9-8: PCI command sequence - CPS Output pre-emphasis configuration                                                |     |