# A MODIFIED BOOST CONVERTER WITH REDUCED INPUT CURRENT RIPPLE

A Thesis

presented to the Faculty of California Polytechnic State University, San Luis Obispo

In Partial Fulfillment of the Requirements for the Degree Master of Science in Electrical Engineering

> by Nathan H. Lentz June 2017

© 2017

## Nathan H. Lentz ALL RIGHTS RESERVED

#### COMMITTEE MEMBERSHIP

- TITLE: A Modified Boost Converter with Reduced Input Current Ripple

- AUTHOR: Nathan H. Lentz

DATE SUBMITTED: June 2017

COMMITTEE CHAIR: Taufik, Ph.D. Professor of Electrical Engineering

COMMITTEE MEMBER: David Braun, Ph.D. Professor of Electrical Engineering

COMMITTEE MEMBER: Xiao-Hua (Helen) Yu, Ph.D. Professor of Electrical Engineering

#### ABSTRACT

# A Modified Boost Converter with Reduced Input Current Ripple Nathan H. Lentz

Battery-powered trends in consumer electronics, transportation, and renewable energy sectors increase demands on DC/DC converter technology. Higher switching frequency and efficiency reduces solution size and cost, while increasing power capabilities. Still, switching noise remains the primary drawback associated with any DC/DC converter. Reducing a converter's input ripple helps prevent switching noise from spreading to other systems on a shared DC power bus. This thesis covers the analysis, simulation, and implementation of a recently-proposed boost converter topology, alongside an equivalent standard boost converter, operating in steady-state, continuous conduction mode. A Matlab-based simulation predicts each converter's input ripple performance using a state-space model. The converters' hardware implementation minimizes component and layout differences to create an equivalent comparison. The simulation and hardware measurements demonstrate a 40% input current ripple reduction using the modified topology. Replacing standard boost converters with the modified topology minimizes the switching noise conducted through a system's DC power network.

Keywords: dc/dc, boost, converter, input, current, ripple

iv

## TABLE OF CONTENTS

| LIST O           | F TA    | BLES                                      | viii |  |

|------------------|---------|-------------------------------------------|------|--|

| LIST OF FIGURESx |         |                                           |      |  |

| СНАРТ            | CHAPTER |                                           |      |  |

| 1. IN            | TROI    | DUCTION                                   | 1    |  |

| 2. BA            | CKG     | ROUND                                     | 3    |  |

| 2.1              | Swi     | tching Noise                              | 3    |  |

| 2.2              | Inpu    | ut Ripple                                 | 4    |  |

| 2.3              | Inpu    | ut Filters                                | 5    |  |

| 2.4              | Inte    | rleaved Multiphase                        | 8    |  |

| 2.5              | Boo     | ost Converter                             | 11   |  |

| 2.5              | 5.1     | Switch-ON State                           | . 12 |  |

| 2.5              | 5.2     | Switch-OFF State                          | . 12 |  |

| 2.5              | 5.3     | DC Transfer Function                      | . 13 |  |

| 2.5              | 5.4     | Continuous Conduction Mode Operation      | . 14 |  |

| 2.5              | 5.5     | Component Ratings                         | . 15 |  |

| 2.5              | 5.6     | Capacitor Sizing                          | . 18 |  |

| 2.6              | Nov     | vel and Modified Topologies               | 20   |  |

| 3. DE            | ESIGN   | N REQUIREMENTS                            | 21   |  |

| 3.1              | Cur     | rent Ripple Performance                   | 21   |  |

| 3.2              | Fun     | ctional Parameters                        | 22   |  |

| 3.3              | Star    | ndard Boost Design                        | 23   |  |

| 4. AN            | JALY    | SIS AND SIMULATION                        | 25   |  |

| 4.1              | Stat    | e Space Analysis                          | 26   |  |

| 4.1              | 1.1     | Standard Boost Converter                  | . 27 |  |

| 4.1              | 1.2     | Modified Boost Converter                  | . 30 |  |

| 4.2              | Stea    | ady-State m-Domain State Equations        | 34   |  |

| 4.2              | 2.1     | Standard Boost Converter                  | . 36 |  |

| 4.2              | 2.2     | Modified Boost Converter                  | . 36 |  |

| 4.3              | Nur     | nerical m-Domain State Equation Solutions | 37   |  |

| 4.3.1   | Initial Condition Estimates       |    |

|---------|-----------------------------------|----|

| 4.3.2   | Iterative State Equation Solution |    |

| 4.4 N   | Aodified Boost Design Process     | 39 |

| 4.4.1   | Resonant Frequencies              | 40 |

| 4.4.2   | Component Sizing                  | 42 |

| 4.5 I   | Design Simulation                 | 43 |

| 4.5.1   | Matlab Simulation                 | 44 |

| 4.5.2   | LTSpice Simulation                |    |

| 4.5.3   | Simulation Comparison             | 51 |

| 5. HAR  | DWARE                             | 54 |

| 5.1 F   | Power Components                  | 54 |

| 5.1.1   | Inductors                         |    |

| 5.1.2   | Capacitors                        | 55 |

| 5.1.3   | Switch and Diode                  | 56 |

| 5.2 S   | witching Controller               | 56 |

| 5.2.1   | Switching Frequency               | 57 |

| 5.2.2   | Sense Resistor                    | 57 |

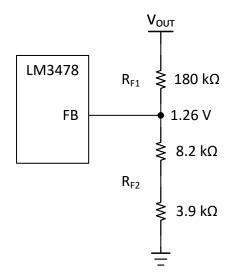

| 5.2.3   | Output Voltage Divider            | 59 |

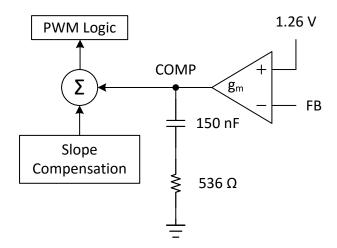

| 5.2.4   | Loop Compensation                 | 60 |

| 5.3 I   | mplementation and Testing         | 61 |

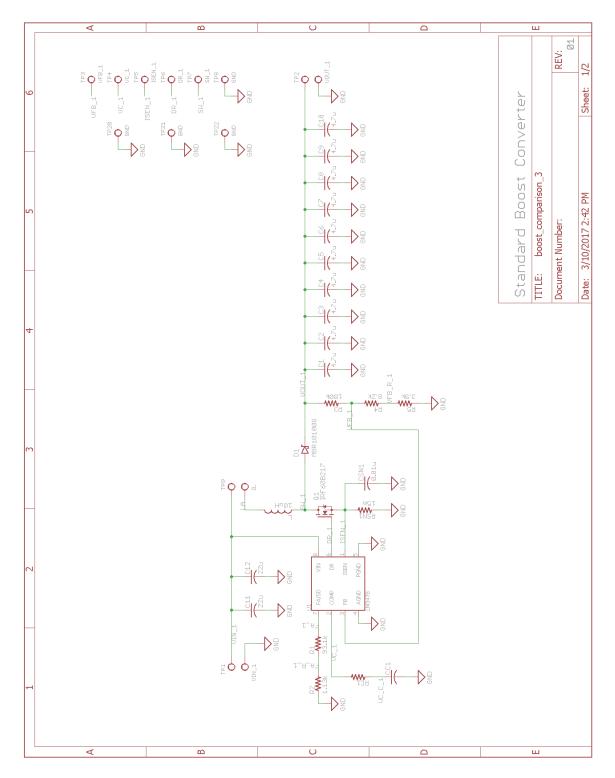

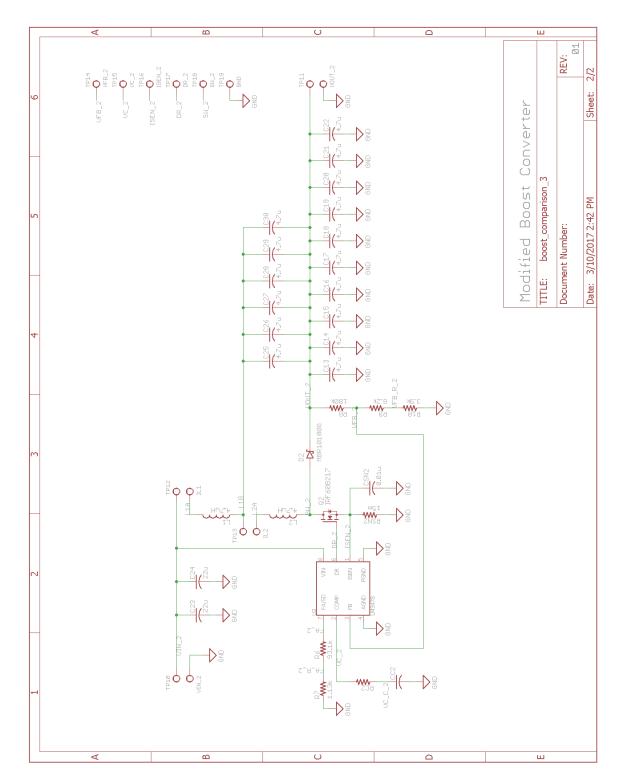

| 5.3.1   | Schematics                        | 62 |

| 5.3.2   | PCB Layout                        | 63 |

| 5.3.3   | Test Configuration                | 65 |

| 5.3.4   | State Variable Measurements       | 68 |

| 5.3.5   | Irregular Conduction Limitations  | 73 |

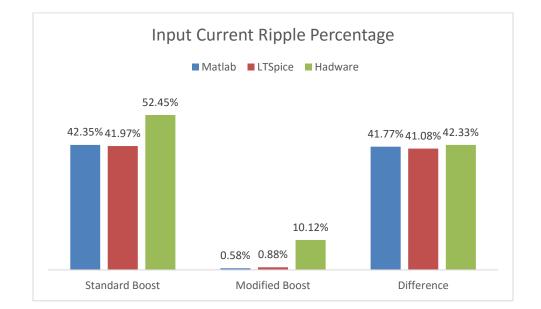

| 5.4 F   | Performance Comparison            | 75 |

| 6. CON  | CLUSION                           | 77 |

| REFEREN | VCES                              | 79 |

| APPEND  | ICES                              |    |

| A. N    | /IATLAB Scripts                   | 82 |

| boost   | _cycle.m                          | 82 |

|         | mod_cycle.m                       |    |

| boost   | _mod_design_comp.m                | 85 |

|   | boost_sim.m                  |    |

|---|------------------------------|----|

|   | boost_mod_sim.m              | 87 |

| В | B. Design Simulation Data    | 90 |

|   | Matlab                       |    |

|   | LTSpice                      |    |

| С | C. Control Loop Compensation | 92 |

| D | D. Hardware Documentation    | 94 |

|   | Eagle CAD Schematics         |    |

|   | Eagle CAD PCB Layout         |    |

|   | Bill of Materials            |    |

## LIST OF TABLES

| Table 2-1. Interleaved Multiphase Converter Properties                 | 9  |

|------------------------------------------------------------------------|----|

| Table 2-2. Boost Converter Component Ratings [27]                      | 17 |

| Table 3-1. Functional Converter Parameters                             | 22 |

| Table 3-2. Converter Design Parameters                                 | 24 |

| Table 4-1. Standard Boost Converter Component Averages                 |    |

| Table 4-2. Modified Boost Converter Component Averages                 |    |

| Table 4-3. State Equation Initial Condition Estimates                  |    |

| Table 4-4. Modified Boost Converter Component Values                   | 43 |

| Table 4-5. Converter Design Parameter Summary                          | 44 |

| Table 4-6. Matlab and Theoretical Standard Boost Design Performance    | 45 |

| Table 4-7. Matlab and Theoretical Modified Boost Design DC Performance | 47 |

| Table 4-8. Standard Boost Simulation Measurement Comparison            | 51 |

| Table 4-9. Modified Boost Simulation Measurement Comparison            | 52 |

| Table 4-10. Simulated Boost Converter Input Current Ripple Reduction   | 53 |

| Table 5-1. WE-FAMI Series Inductor Properties                          | 54 |

| Table 5-2. Power-Path Capacitor Current and MLCC Configuration         | 55 |

| Table 5-3. Power-Path MLCC Properties                                  | 55 |

| Table 5-4. Switching Component Rating Margins                          | 56 |

| Table 5-5. LM3487 Pin Descriptions [37]                                | 57 |

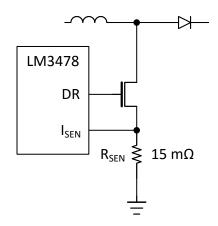

| Table 5-6. LM3478 Current Sense Feedback Parameters [37]               | 59 |

| Table 5-7. Converter Output Voltage Difference at Full Load            | 66 |

| Table 5-8. Converter Full Load DC Characteristics Comparison           | 67 |

| Table 5-9. State Variable Oscilloscope Measurement Methods             | 69 |

| Table 5-10. Standard Boost Converter Hardware Test Results             | 70 |

| Table 5-11. Modified Boost Converter Hardware Test Results             | 73 |

| Table 5-12. Hardware Input Current Ripple Comparison                   | 76 |

| Table B-1. Matlab-simulated Standard Boost Design Measurements         | 90 |

| Table B-2. Matlab-Simulated Modified Boost Design Measurements         | 00 |

| Table B-3. LTSpice Standard Boost Design Measurements | 91 |

|-------------------------------------------------------|----|

| Table B-4. LTSpice Modified Boost Design Measurements | 91 |

| Table D-5. Electrical Bill of Materials               | 99 |

### LIST OF FIGURES

| Figure 2-1. Typical Triangular and Trapezoidal Switching Waveforms    | 3  |

|-----------------------------------------------------------------------|----|

| Figure 2-2. DC/DC Converter with Input Filter Network                 | 6  |

| Figure 2-3. Middlebrook Criteria with Generic Impedance Curves        | 6  |

| Figure 2-4. Shunt (Left) and Parallel (Right) Damped LC Filters       | 7  |

| Figure 2-5. Three-Phase Interleaved Switching                         | 8  |

| Figure 2-6. Two-Phase Buck Converter Current Ripple Cancellation [20] | 9  |

| Figure 2-7. Two-Phase Boost Converter                                 | 10 |

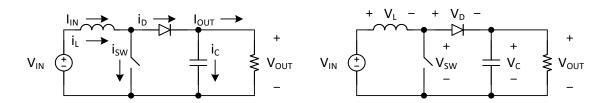

| Figure 2-8. Standard Boost Converter Topology                         | 11 |

| Figure 2-9. Boost Converter Switch-ON State                           | 12 |

| Figure 2-10. Boost Converter Switch-OFF State                         | 13 |

| Figure 2-11. Boost Converter Steady-State Inductor Current            | 14 |

| Figure 2-12. Boost Converter BCM Inductor Current                     | 15 |

| Figure 2-13. Boost Converter Current and Voltage Polarities           | 16 |

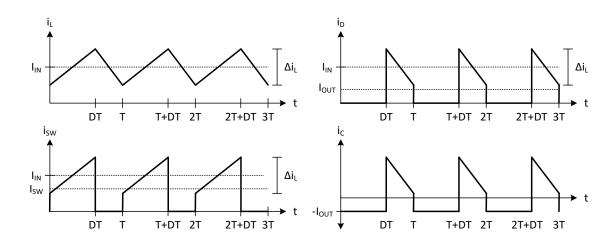

| Figure 2-14. Boost Converter Current Waveforms                        | 16 |

| Figure 2-15. Boost Converter Voltage Waveforms                        | 17 |

| Figure 2-16. Boost Converter Output Capacitor Charge Storage          | 18 |

| Figure 2-17. Boost Converter Input Capacitor Charge Storage           | 19 |

| Figure 2-18. Modified Boost Converter                                 | 20 |

| Figure 4-1. Modified Boost Converter DC Voltages                      | 25 |

| Figure 4-2. Standard Boost Converter State Variables                  | 27 |

| Figure 4-3. Standard Boost Converter Switch-On State Variables        | 27 |

| Figure 4-4. Standard Boost Converter Switch-Off State Variables       | 28 |

| Figure 4-5. Modified Boost Converter State Variables                  | 30 |

| Figure 4-6. Modified Boost Converter Switch-On State Variables        | 30 |

| Figure 4-7. Modified Boost Converter Switch-Off State Variables       | 31 |

| Figure 4-8. Time-domain and m-domain Switching Transitions            | 35 |

| Figure 4-9. Iterative Numerical State Equation Solution               | 39 |

| Figure 4-10. LTSpice Modified Boost Converter Resonance Simulation    | 41 |

| Figure 4-11. LTSpice Modified Boost Converter Simulated Input Impedance | 41 |

|-------------------------------------------------------------------------|----|

| Figure 4-12. Max. Modified Boost Resonant Frequency versus C1 Value     | 42 |

| Figure 4-13. Modified Boost Converter Component Sizing Chart            | 42 |

| Figure 4-14. Matlab State Variable Waveforms for Standard Boost         | 44 |

| Figure 4-15. Matlab Modified Boost Inductor Current Waveforms           | 46 |

| Figure 4-16. Matlab Modified Boost Capacitor Voltage Waveforms          | 46 |

| Figure 4-17. Matlab Modified Boost Capacitor Current Waveforms          | 47 |

| Figure 4-18. LTSpice Standard Boost Transient Simulation                | 48 |

| Figure 4-19. LTSpice State Variable Waveforms for Standard Boost        | 49 |

| Figure 4-20. LTSpice Modified Boost Transient Simulation                | 49 |

| Figure 4-21. LTSpice Modified Boost Inductor Current Waveforms          | 50 |

| Figure 4-22. LTSpice Modified Boost Capacitor Voltage Waveforms         | 50 |

| Figure 4-23. LTSpice Modified Boost Capacitor Current Waveforms         | 51 |

| Figure 5-1. LM3478 Current Sense Resistor                               | 58 |

| Figure 5-2. Output Voltage Feedback Divider                             | 60 |

| Figure 5-3. LM3478 Type-I Loop Compensator                              | 61 |

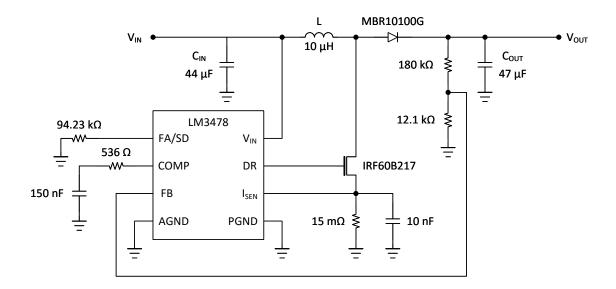

| Figure 5-4. Simplified Standard Boost Design Schematic                  | 62 |

| Figure 5-5. Simplified Modified Boost Design Schematic                  | 63 |

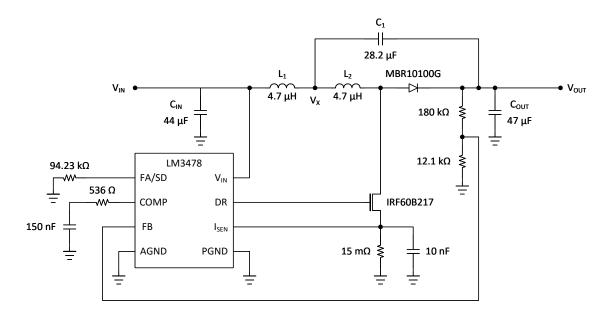

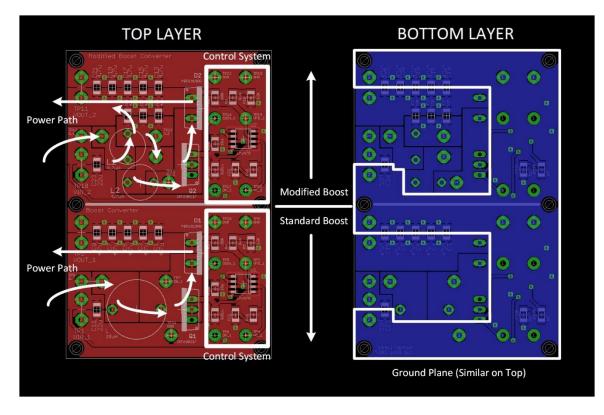

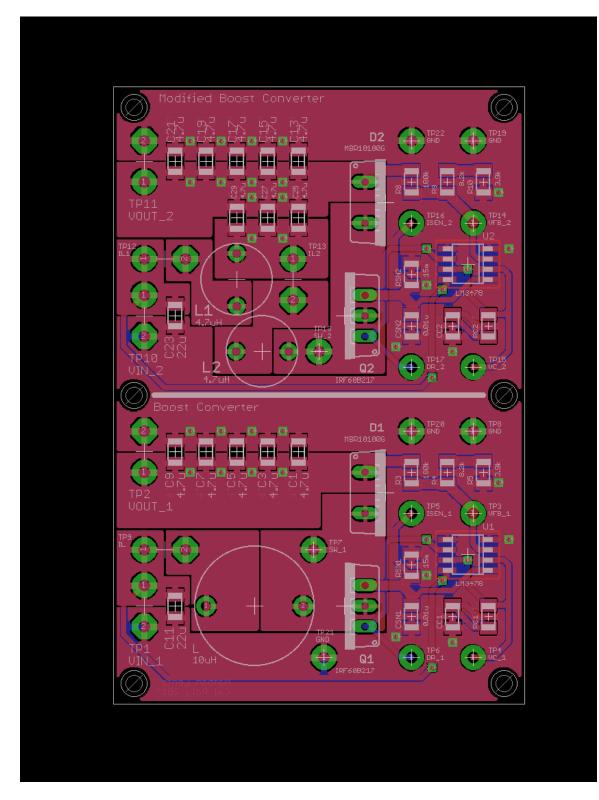

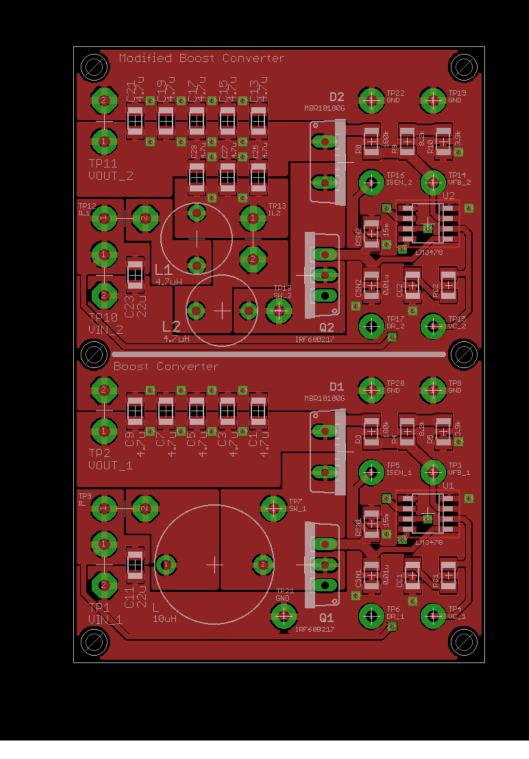

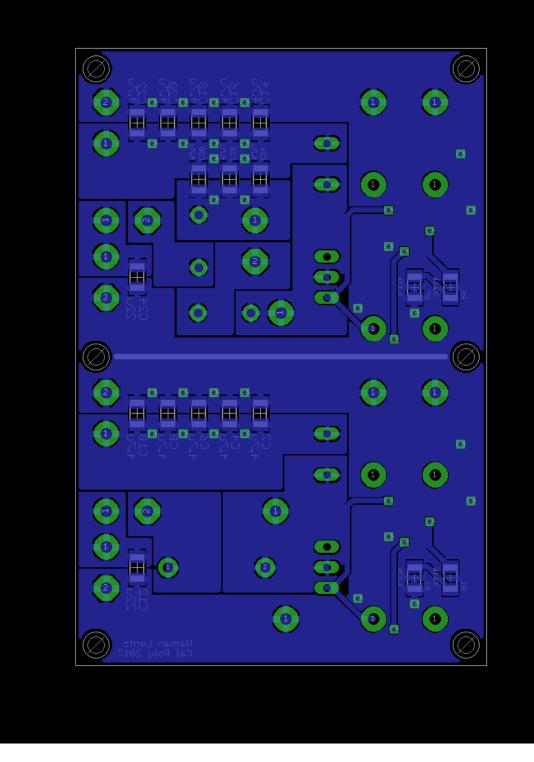

| Figure 5-6. Top and Bottom PCB Layers Annotated                         | 64 |

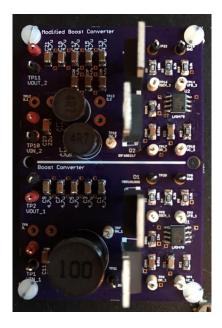

| Figure 5-7. Assembled PCB (Top View)                                    | 64 |

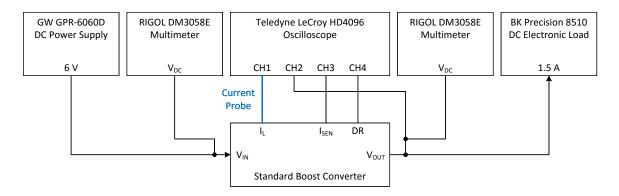

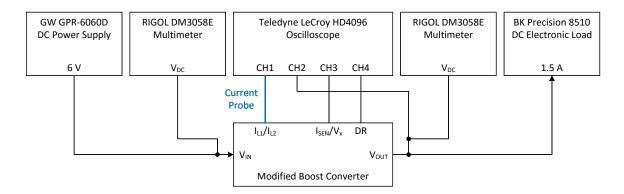

| Figure 5-8. Standard Boost Converter Hardware Test Connections          | 65 |

| Figure 5-9. Modified Boost Converter Hardware Test Connections          | 66 |

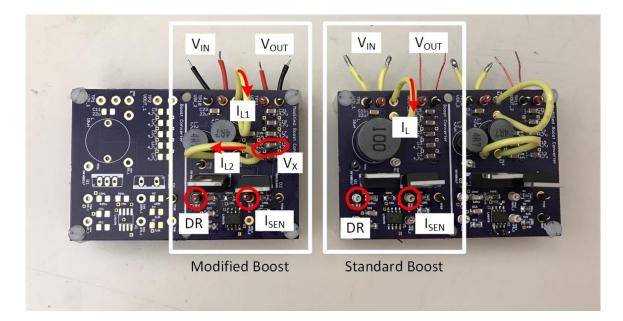

| Figure 5-10. Final Converter Assembly Test Points                       | 67 |

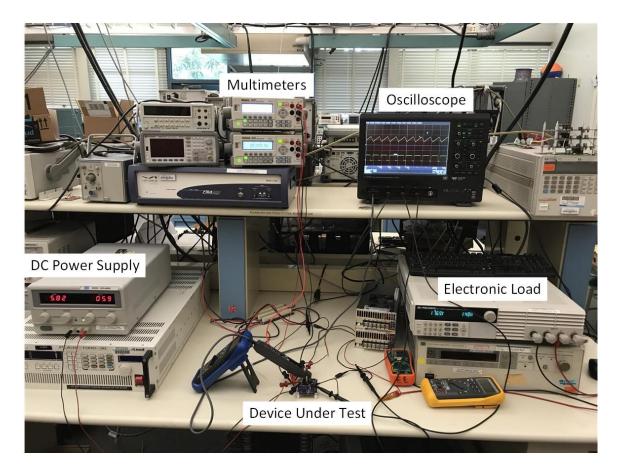

| Figure 5-11. Laboratory Test Configuration                              | 68 |

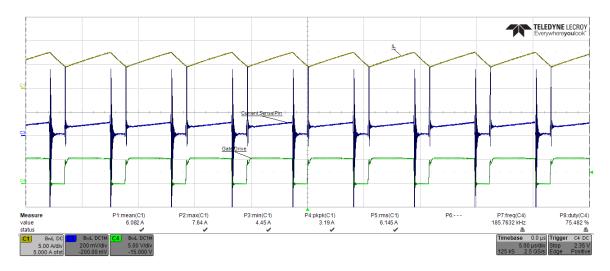

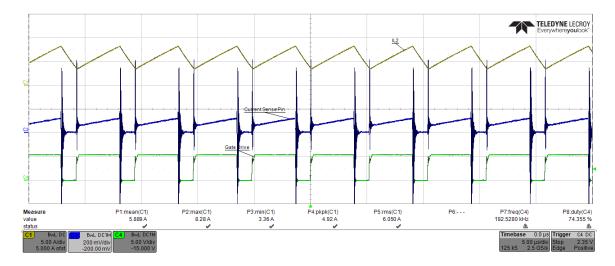

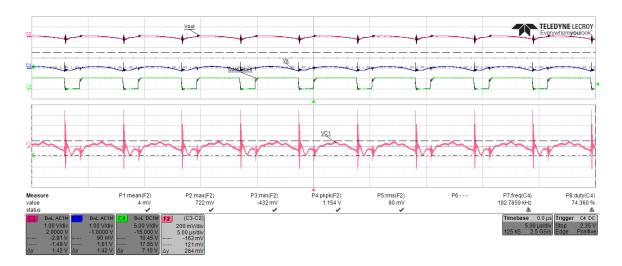

| Figure 5-12. Standard Boost Hardware Inductor Current                   | 69 |

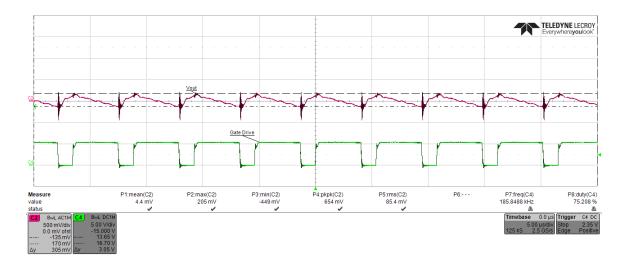

| Figure 5-13. Standard Boost Hardware Output Voltage (AC Coupling)       | 70 |

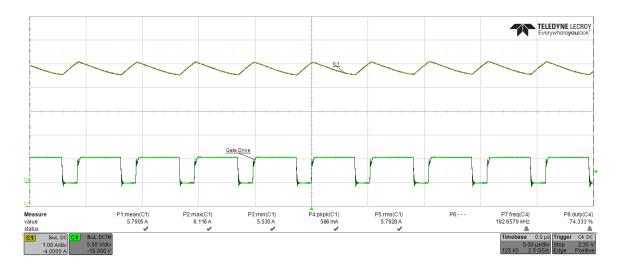

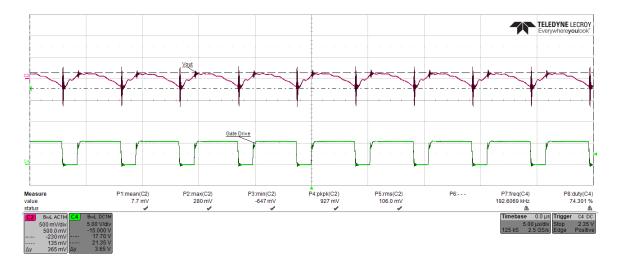

| Figure 5-14. Modified Boost Hardware L1 Current                         | 71 |

| Figure 5-15. Modified Boost Hardware L2 Current                         | 71 |

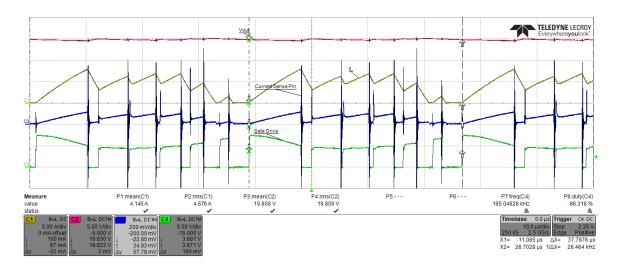

| Figure 5-16. Modified Boost Hardware C1 Voltage (AC Coupling)           | 72 |

| Figure 5-17. Modified Boost Hardware Output Voltage (AC Coupling)       | 72 |

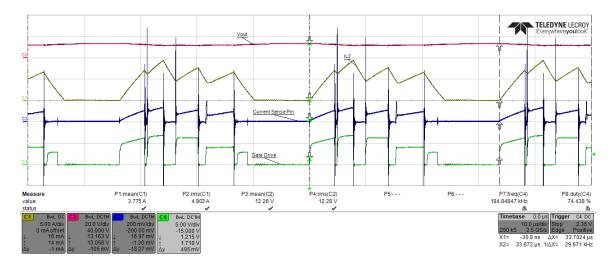

| Figure 5-18. Standard Boost Subharmonic Oscillation at 800 mA Load      | 74 |

| Figure 5-19. Modified Boost Subharmonic Oscillation at 1.1 A Load        | 74 |

|--------------------------------------------------------------------------|----|

| Figure 5-20. Input Current Ripple Performance in Simulation and Hardware | 76 |

| Figure D-1. Standard Boost Converter Eagle CAD Schematic                 | 94 |

| Figure D-2. Modified Boost Converter Eagle CAD Schematic                 | 95 |

| Figure D-3. Eagle CAD PCB Layout                                         | 96 |

| Figure D-4. Top PCB Layer                                                | 97 |

| Figure D-5. Bottom PCB Layer                                             | 98 |

#### **1. INTRODUCTION**

Globally, electricity continues growing faster than any form of end-use energy consumption [1]. Many primary energy sources, including fossil fuels, nuclear, hydro, solar, and wind, fuel the electric power generation serving numerous end-uses. Between generation and end-use, power electronics control the electrical energy flow to countless systems. Electrical systems increasingly rely on power electronics as growing electricity demand strains global energy supplies.

Power electronics achieve high-efficiency energy transfer using switches. While on, an ideal switch conducts current without a voltage drop across the device. Conversely, the ideal switch does not conduct current while off, regardless of voltage imposed across the device. The product of voltage across the device and current through the device always remains zero, preventing the ideal switch from dissipating power. Transistors, diodes, and other semiconductor devices provide the electronic switching capability to realize power converters. General Electric introduced the first power semiconductor device, a thyristor, in 1958 [2]. Later technologies including power bipolar and field-effect transistors increased energy capacity and switching frequency. A power converter's switches alternately direct energy from the source into reactive storage elements, typically inductors and capacitors, and from storage elements to the load. This switch-mode behavior resembles a metro station, where trains periodically transfer passenger groups to their destination [3].

Power converters adapt energy flow between alternating current (AC) and direct current (DC) forms at varying voltage levels. These circuits commonly perform a combination of rectification (AC/DC conversion), inversion (DC/AC conversion), and

1

step-up or step-down DC/DC conversion. Traditional electronic power supplies stepdown AC line voltage through a large 60-Hz transformer, rectify the low-voltage AC, and distribute power to different subsystems using linear voltage regulators. DC/DC converters eliminate the need for bulky transformers and inefficient linear regulators by increasing (step-up) or decreasing (step-down) DC voltages. High-efficiency and highfrequency operation minimize heat dissipation and magnetic component size, reducing overall power supply size. These characteristics enable the miniaturization of modern electronic devices.

Today, DC power source trends increase systems' DC/DC converter performance demands. Portable electronics need high efficiency to reduce size and extend battery life. Battery electric vehicles operate at high DC voltages to manage increasing power requirements. Microinverters for solar photovoltaic (PV) modules often include intermediate DC/DC conversion to reach appropriate AC output voltage levels. These trends point toward increased DC/DC converter deployment and a need to continue improving converter performance.

#### 2. BACKGROUND

#### 2.1 Switching Noise

The primary drawback associated with DC/DC converters, switching noise, presents a significant challenge for system engineers. Switch-mode operation adds AC ripple to a converter's DC input and output signals. Poorly designed DC/DC converters allow this switching noise to spread to nearby circuits, causing electromagnetic interference (EMI). EMI refers to undesired conducted or radiated electromagnetic signals that degrade or impair the performance of electrical systems. Minimizing switching noise and preventing its transmission helps improve system reliability.

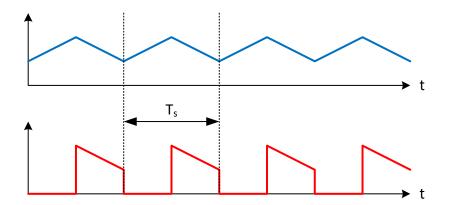

Figure 2-1. Typical Triangular and Trapezoidal Switching Waveforms

Switching noise spreads through both electromagnetic conduction and radiation. DC/DC converters typically produce triangular and trapezoidal waveforms such as those shown in Figure 2-1. These waveforms carry significant energy at the switching frequency (2-1) and its harmonics which typically sit between 100 kHz and several MHz. The sharp transitions particularly associated with trapezoidal waveforms contain energy at much higher frequencies in the GHz range. Conduction dominates EMI transmission at lower frequencies, before parasitic effects dominate electrical circuits, and radiation increases at higher frequencies, when wavelength approaches physical conductor length.

$$f = \frac{1}{T} \tag{2-1}$$

EMI regulations reflect the characteristics of switching noise among other sources. Typical tests limit conducted emissions between 150 kHz to 30 MHz and radiated emissions from 30 MHz to 2 GHz. Government regulators impose EMI limits to ensure electrical interoperability, particularly among wireless electronics and power supplies connected to the AC grid. Mitigating switching noise helps achieve EMI compliance in many applications. At a system level, specific grounding and shielding techniques reduce conducted and radiated EMI introduced by switching noise sources [4]. Switching noise also propagates within systems from power converters to nearby signal conductors [5]. Printed circuit board (PCB) layout and grounding techniques help minimize EMI radiation along high-frequency current paths [6] [7]. These approaches primarily focus on containing radiated switching noise emission. Preventing switching noise conduction relies on reducing or containing ripple at the power converter's input and output terminals.

#### 2.2 Input Ripple

The discontinuous currents caused by switch-mode operation add an AC ripple component to any DC/DC converter's input current. When input current ripple conducts through a voltage source, switching noise spreads to other circuits connected to the same source. This conducted EMI significantly impacts systems that draw power from rectified AC-line voltage or a battery. Current ripple also adversely impacts maximum power

4

point tracking (MPPT) and the transfer efficiency of solar photovoltaic modules [8] [9]. Reducing the current ripple seen by a converter's input source beneficially impacts many systems.

Designers may choose a DC/DC converter topology based on the relative amount of current ripple introduced. Inductor-fed topologies (boost, Cuk, and SEPIC) produce significantly less input current ripple than switch-fed topologies (buck and buck-boost). At a minimum, most designs employ an input capacitor for input ripple reduction. This simple solution provides adequate filtering performance for some applications. Highperformance converters must incorporate additional input ripple reduction methods, including more complex filters, multiphase interleaving, and specialized topologies.

#### 2.3 Input Filters

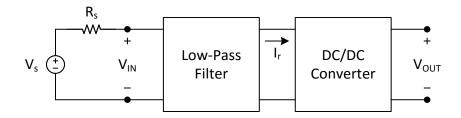

Adding a filter between the input source and power converter provides bidirectional noise isolation. Figure 2-2 displays the general input filter configuration, using a low-pass response to attenuate high-frequency AC ripple. The filter attenuates both voltage ripple introduced by the source and current ripple introduced by the converter. This behavior prevents noise from spreading between systems connected to the same voltage source, such as a battery or rectified line voltage feeding multiple DC/DC converters. Input filters help system designers contain EMI without changing the DC/DC converter topology.

5

Figure 2-2. DC/DC Converter with Input Filter Network

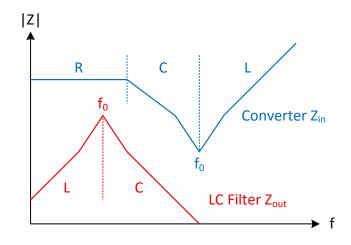

Though adding the filter improves ripple suppression, the interaction between filter and converter may destabilize the system. Yu and Biess first described these conditions in 1971 [10]. Later analysis performed by R. D. Middlebrook, provided graphical criteria that predict instability when the filter's output impedance exceeds the converter's input impedance at any frequency [11] [12]. Middlebrook developed a canonical DC/DC converter model capable of predicting a converter's input impedance based on design parameters [11] [12]. Figure 2-3 presents the canonical converter input impedance determined by the converter's inductance, output capacitance, and load resistance. Jang and Erickson later adapted the Middlebrook criteria to predict instability in current-mode controlled converters [13]. These tools provide the means to design an input filter in conjunction with a converter or as a modification to an existing converter.

Figure 2-3. Middlebrook Criteria with Generic Impedance Curves

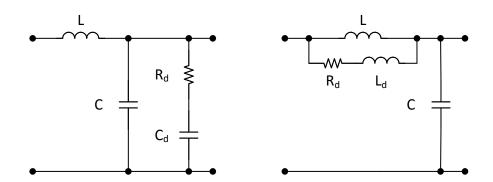

Higher-order input filters present instability risk due to resonant behavior. A generic LC filter exhibits output impedance characteristics of the form shown in Figure 2-3. Resonant frequency location and damping factor determine whether the filter violates the Middlebrook criteria. Lowering the filter's resonant frequency eases damping requirements but increases the filter component sizes. Figure 2-4 presents two damped LC filter circuits; Erickson demonstrates optimal damping for both filters [14]. Yu and Salato offer a damping technique that uses the LC filter's parasitic series resistances to minimize the number of filter components [15]. Most input filter design approaches either seek to minimize the filter's impact on converter performance or the filter's cost (number of components, size, etc.) [16] [17] [18] [19].

Figure 2-4. Shunt (Left) and Parallel (Right) Damped LC Filters

Input filter designers minimize conducted EMI in new or existing systems. Input filters help compensate for noisy converter topologies. The filter must be designed to prevent impacting the DC/DC converter's stability by employing one of many available damping techniques. An optimally designed input filter reduces switching noise conduction, without impacting transient response, at minimal additional cost and physical size.

#### 2.4 Interleaved Multiphase

High-power applications often require multiphase power converters, which operate several implementations of the same converter topology in parallel. In these designs, each phase only provides a fraction of the total load, reducing the converter's total power dissipation [20]. Low-voltage, high-power computer processor applications influence many designs based around the multiphase buck topology [21] [22] [23].

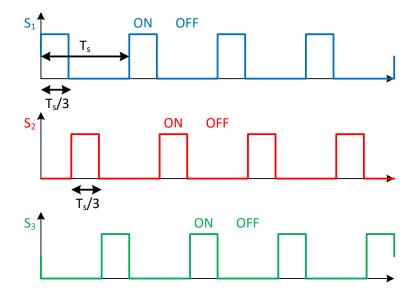

Figure 2-5. Three-Phase Interleaved Switching

Interleaving the multiphase converter's switching signals reduces the ripple introduced and scales the ripple frequency proportional to the number of phases. Interleaved switching signals turn on each phase alternately rather than in unison. Figure 2-5 demonstrates three-phase interleaved switching. The switching controller implements interleaving by introducing a proportional delay between each converter phase. The delayed current waveforms sum at the input and output terminals, and the resulting ripple appears at a multiple of the switching frequency. Table 2-1 summarizes the relationship between the number of converter phases, switching delay, and overall ripple frequency.

| Number of Phases | Switching Delay | <b>Ripple Frequency</b> |

|------------------|-----------------|-------------------------|

| 2                | $\frac{1}{2}T$  | 2 <i>f</i>              |

| 3                | $\frac{1}{3}T$  | 3 <i>f</i>              |

| 4                | $\frac{1}{4}T$  | 4f                      |

Table 2-1. Interleaved Multiphase Converter Properties

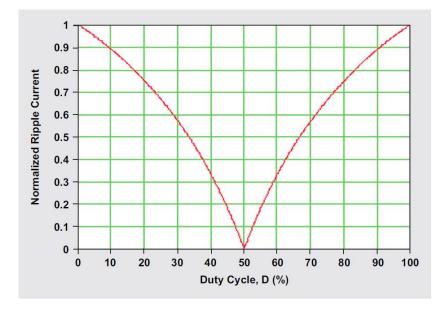

Interleaving creates ripple reduction because of the delay between each phase. The duty cycle, shared across all phases, determines the ripple cancellation. Figure 2-6 demonstrates current ripple cancellation at the output terminal of a two-phase buck converter. The inductor current ripple flowing through the output capacitor cancels, when the converter operates at a 50% duty cycle. Similarly, a three-phase converter would achieve complete ripple cancellation at 33% and 67% duty cycles, and a four-phase converter would achieve complete cancellation at 25%, 50%, and 75%.

Figure 2-6. Two-Phase Buck Converter Current Ripple Cancellation [20]

The combined ripple cancellation and frequency scaling eases filtering requirements. A multiphase converter requires a much smaller filter than a single-phase converter to achieve equivalent ripple performance. Ripple cancellation also reduces the inductance per phase required to match single-phase performance. These characteristics decrease the solution size for high-power applications. However, the relationship between duty cycle and ripple cancellation restricts design choices. A two-phase converter only achieves significant ripple reduction at duty cycle around 50%. Increasing the number of phases provides more options, but significantly increases design complexity.

Figure 2-7. Two-Phase Boost Converter

Parallel converters in a multiphase solution reduce the conduction losses associated with a large input current, and interleaved switching provides some ripple cancellation. A multiphase boost converter, shown in Figure 2-7, also exhibits inductor ripple cancellation properties at the input terminal [24]. High-power solar PV inverters benefit from using multiphase boost converters because of current sharing and ripple cancellation [25] [26]. These converters undoubtedly improve efficiency, but restrict duty cycle selection when operated for maximum ripple reduction.

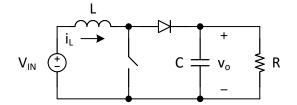

#### 2.5 Boost Converter

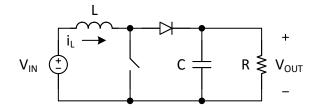

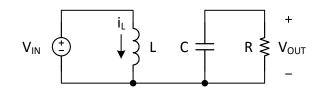

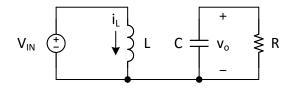

Figure 2-8 depicts the boost topology, a standard DC/DC step-up converter, which contains a single switch and operates alternately between two states: switch-on and switch-off.

Figure 2-8. Standard Boost Converter Topology

Duty cycle, referred to as a percentage or a ratio less than unity, relates the switching period to the time spent in the switch-on (2-2) and switch-off (2-3) states.

$$t_{ON} = D \cdot T \tag{2-2}$$

$$t_{OFF} = (1-D) \cdot T \tag{2-3}$$

Circuit operation depends on the relationship between inductor current and voltage (2-4).

$$V_L = L \cdot \frac{di_L}{dt} \tag{2-4}$$

Turning the switch on and off changes the voltage applied across the inductor, alternately increasing and decreasing inductor current. This action, stores energy from the input source in the inductor's magnetic field, and then releases energy to the load. Because the converter always applies voltage across the inductor, the converter's input current never settles to a flat DC level. Inductor current ripple manifests as input current ripple in a boost converter.

#### 2.5.1 Switch-ON State

In the switch-on state, the inductor stores energy from the input, while the capacitor releases energy to drive the load. Turning the switch on, reverse biases the diode, separating the circuit's two halves as in Figure 2-9.

Figure 2-9. Boost Converter Switch-ON State

The inductor current ramps up with slope (2-5) defined by equation (2-4).

Constant input voltage guarantees a fixed linear slope (2-6), equivalent to the change in current relative to the time spent in the switch-on state (2-2). This equivalence leads to a description of the peak-to-peak current ripple (2-7).

$$\frac{di_L}{dt} = \frac{V_{IN}}{L} \tag{2-5}$$

$$\frac{\Delta i_{L(ON)}}{\Delta t_{ON}} = \frac{V_{IN}}{L} \tag{2-6}$$

$$\Delta i_{L(ON)} = \frac{V_{IN} \cdot DT}{L} \tag{2-7}$$

#### 2.5.2 Switch-OFF State

In the switch-off state, energy from input source and energy stored in the inductor flow to the capacitor and load. With the switch off, the diode becomes forward biased and connects the inductor to the output node as in Figure 2-10.

Figure 2-10. Boost Converter Switch-OFF State

The difference between input and output voltage determines inductor current slope (2-8) while the switch remains 'OFF'. Assuming constant DC input and output voltage, the switch-off state also exhibits linear inductor current slope (2-9). Equation (2-10) presents the peak-to-peak inductor current ripple during the switch-off state.

$$\frac{di_L}{dt} = \frac{V_{IN} - V_{OUT}}{L} \tag{2-8}$$

$$\frac{\Delta i_{L(OFF)}}{\Delta t_{OFF}} = \frac{V_{IN} - V_{OUT}}{L}$$

(2-9)

$$\Delta i_{L(OFF)} = \frac{(V_{IN} - V_{OUT}) \cdot (1 - D)T}{L}$$

(2 - 10)

#### 2.5.3 DC Transfer Function

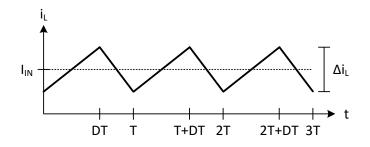

Under steady-state operating conditions, inductor current reaches a fixed DC value. Figure 2-11 depicts these conditions, where net inductor current change reaches zero.

Figure 2-11. Boost Converter Steady-State Inductor Current

Equation (2-11) describes the steady-state operating condition mathematically.

$$\Delta i_{L(ON)} = \Delta i_{L(OFF)} \tag{2-11}$$

Substituting the inductor current ripple expressions in the switch-on (2-7) and switch-off (2-10) state leads to the boost converter's DC voltage transfer function (2-13).

$$\frac{V_{IN} \cdot DT}{L} = \frac{(V_{IN} - V_{OUT}) \cdot (1 - D)T}{L}$$

(2 - 12)

$$V_{OUT} = \frac{V_{IN}}{(1-D)}$$

(2-13)

The ideal power relationship (2-14), in a lossless converter, extends the DC voltage transfer function to the DC current transfer function (2-15).

$$P_{OUT} = V_{OUT} I_{OUT} = P_{IN} = V_{IN} I_{IN}$$

(2 - 14)

$$I_{IN} = \frac{I_{OUT}}{(1-D)}$$

(2-15)

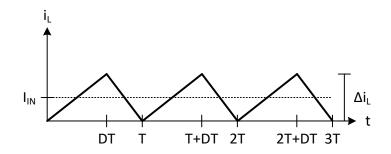

#### 2.5.4 Continuous Conduction Mode Operation

A DC/DC converter's inductor current describes the operating mode. Continuous conduction mode (CCM) implies inductor current flow throughout the switching cycle. Discontinuous conduction mode (DCM) occurs when the inductor current drops to zero during the switch-off state. In this scenario, the diode prevents negative current flow and

the inductor current remains at zero until the next switch-on cycle. DCM naturally occurs, when a converter operates under light loads well below specified maximums. The general converter design process assumes CCM operation at maximum rated load.

A special CCM case called boundary conduction mode (BCM), illustrated by Figure 2-12, delineates the barrier between CCM and DCM. BCM represents the minimum conditions for CCM operation.

Figure 2-12. Boost Converter BCM Inductor Current

Maintaining CCM operation constrains inductor current ripple given the desired average inductor current level. The BCM constraint (2-16) describes a minimum inductance, known as the critical inductance (2-17) required to maintain continuous conduction.

$$\frac{\Delta i_L}{2} \le I_L \tag{2-16}$$

$$L_c \ge \frac{V_{IN} \cdot DT}{2I_{IN}} \tag{2-17}$$

#### 2.5.5 Component Ratings

Voltage and current waveforms help determine each component's basic ratings. Manufacturers specify voltage ratings as peak values and current ratings as average or

RMS values. Figure 2-13 defines component current and voltage polarities in the boost converter.

Figure 2-13. Boost Converter Current and Voltage Polarities

Inductor current splits between the switch and diode. These components conduct alternately; the switch carries the inductor current during the 'ON' state and the diode carries the inductor current during the 'OFF' state. Diode current splits between the output capacitor and the load. The load conducts the DC output current and the output capacitor conducts the AC component of the diode current. Figure 2-14 depicts the current waveforms for each component.

Figure 2-14. Boost Converter Current Waveforms

During the switch-on state, the inductor see the input voltage and the reversebiased diode sees the output voltage. During the switch-off state, the inductor sees a negative voltage, equal to the difference between input and output voltages, while the switch sees the output voltage across its terminals. Capacitor voltage always equals the output voltage, including the additional ripple caused by integrating the capacitor current. Figure 2-15 illustrates each component's voltage waveform.

Figure 2-15. Boost Converter Voltage Waveforms

Table 2-2 summarizes the boost converter's relevant component ratings

determined based on voltage and current waveforms.

| Component | Rating                          | Value                                                 |

|-----------|---------------------------------|-------------------------------------------------------|

| G 4.1     | Drain Current                   | $I_d > I_{IN} \cdot D$                                |

| Switch    | Drain-Source Voltage            | $V_{ds} > V_{OUT}$                                    |

|           | Forward Current                 | $I_F > I_{OUT}$                                       |

| Diode     | Max. Repetitive Reverse Voltage | $V_{rrm} > V_{OUT}$                                   |

| Capacitor | DC Voltage                      | $V_{C(\max)} > V_{OUT} + \frac{\Delta V_{OUT}}{2}$    |

|           | Saturation Current              | $I_{sat} > I_{IN} + \frac{\Delta i_L}{2}$             |

| Inductor  | RMS Current                     | $I_{rms} > \sqrt{I_{IN}^2 + \frac{\Delta i_L^2}{12}}$ |

Table 2-2. Boost Converter Component Ratings [27]

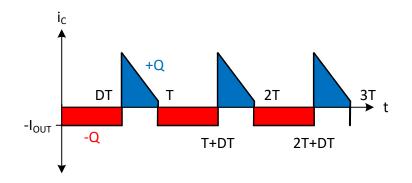

#### 2.5.6 Capacitor Sizing

Capacitors handle the AC current ripple at a DC/DC converter's input and output terminals. During steady-state operation, the net charge stored and released by a capacitor must approach zero over the switching cycle. Charging and discharging the capacitor introduces voltage ripple across the capacitor (2-18), the primary design parameter associated with input and output capacitors.

$$\Delta V = \frac{Q}{C} \tag{2-18}$$

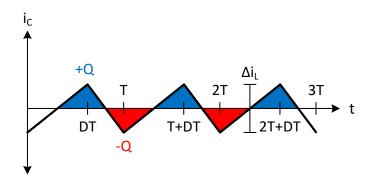

Integrating the positive or negative portion of the ripple current over a half switching cycle specifies the maximum charge stored or released by the capacitor. Figure 2-16 applies this technique to a boost converter's output capacitor.

Figure 2-16. Boost Converter Output Capacitor Charge Storage

The DC output current and switching cycle parameters determine the output capacitor charge (2-19). Combining equations (2-18), (2-19), and (2-20) expresses the required output capacitance to achieve a specified voltage ripple ratio (2-21).

$$Q_{C_{out}} = I_{OUT} \cdot D \cdot T \tag{2-19}$$

$$I_{OUT} = \frac{V_{OUT}}{R} \tag{2-20}$$

$$C_{out} = \frac{D \cdot T}{R \cdot \frac{\Delta V_{out}}{V_{OUT}}}$$

(2 - 21)

Though often omitted from schematics during theoretical analysis, practical DC/DC converter implementations require an input capacitor. This provides a lowimpedance source for high-frequency current ripple drawn by the converter. Inductor current ripple determines the charge stored on a boost converter's input capacitor, as Figure 2-17 depicts.

Figure 2-17. Boost Converter Input Capacitor Charge Storage

Like the output, input voltage ripple requirements determine input capacitance. Applying inductor current ripple (2-7) and input capacitor charge (2-22) expressions to the capacitor's charge-voltage relationship (2-18) specifies input capacitance in terms of converter parameters and input voltage ripple specifications (2-23).

$$Q_{C_{in}} = \frac{\Delta i_L \cdot T}{8} \tag{2-22}$$

$$C_{in} = \frac{D \cdot T^2}{8L \cdot \frac{\Delta V_{IN}}{V_{IN}}} \tag{2-23}$$

#### 2.6 Novel and Modified Topologies

Many step-up converter applications require performance beyond the standard boost converter's capabilities. Such needs produce novel step-up topologies designed to optimize different performance criteria; including efficiency, ripple performance, step-up conversion ratio, size, and cost [28] [29] [30] [31].

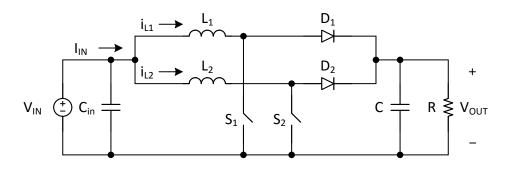

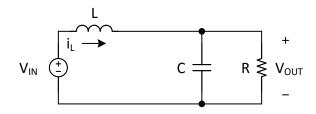

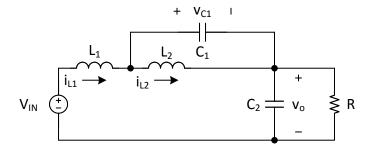

Figure 2-18. Modified Boost Converter

New and modified topologies trade additional complexity for performance enhancement. Figure 2-18 shows a relatively simple modification proposed by Karanam as part of a step-up inverter application [32]. Karanam implemented the modified boost converter, focusing on performance of the inverter rather than the boost converter itself. Using analysis, simulation, and hardware implementation techniques, this work intends to prove the following thesis statement. During steady-state, CCM operation, Karanam's modified boost converter provides a 40% input current ripple reduction compared against an equivalent standard boost converter.

#### **3. DESIGN REQUIREMENTS**

Comparing two related converter topologies requires common performance criteria and design constraints. Equivalent operating conditions and performance measurements ensure proper evaluation of topological converter modifications. This performance comparison primarily concerns the converter's input current ripple, measured through the input inductor. Physical size and cost constitute secondary comparative concerns as some applications value performance over size and cost. A valid performance comparison requires uniform design constraints on input voltage, output voltage, output power, switching frequency, inductance, input capacitance, and output capacitance. Selecting these parameters per standard boost converter characteristics establishes the comparative baseline.

#### **3.1 Current Ripple Performance**

Input current ripple relates to the converter's inductor current ripple, especially in boost topologies which place the inductor at the input terminal. Current ripple measurements typically concern the peak-to-peak value. But specifications typically remain relative to the established DC current level, as a percentage much like voltage ripple. The boost topology's input current ripple percentage (3-1) relates directly to peakto-peak inductor current ripple (2-7) and DC input current (2-14).

$$\%\Delta i_{IN} = \frac{\Delta i_L}{I_{IN}} \tag{3-1}$$

$$\%\Delta i_{IN} = \frac{V_{IN}^2 \cdot D}{L \cdot f \cdot P_{OUT}}$$

(3-2)

Specific applications dictate the tolerable inductor current ripple percentage.

Generally, most design guidelines suggest ripple below 40%. Choosing a relatively large ripple percentage differentiates a topological modification that reduces ripple. Targeting 40% current ripple in a standard boost design provides adequate opportunity to improve performance without exceeding practical limits.

#### **3.2** Functional Parameters

A DC/DC converter's functional parameters determine the component values that complete the converter's design requirements. Table 3-1 summarizes the chosen functional parameters for both boost converters. Three factors influence power and voltage level selection: DC input current, DC voltage gain, and laboratory power supply capabilities. DC/DC converters with large DC input current require larger inductors to achieve low current ripple. A topological modification designed to reduce input current ripple provides greater benefit among converter with large DC input current. Because DC voltage gain correlates with DC input current, high-gain converters also benefit from input ripple current reduction. The available DC power supplies also informed power and voltage parameters. The voltage ripple values reflect compensation for non-ideal capacitors, which produce more ripple due to equivalent series resistance (ESR).

| Parameter               | Value |

|-------------------------|-------|

| Output Power            | 30 W  |

| Output Voltage          | 20 V  |

| Input Voltage           | 6 V   |

| Output Voltage Ripple   | 0.5%  |

| Input Voltage Ripple    | 0.5%  |

| Inductor Current Ripple | 40%   |

Table 3-1. Functional Converter Parameters

22

#### 3.3 Standard Boost Design

The functional parameters listed in Table 3-1 determine converter component values and operating conditions. Two key operating conditions, duty cycle (3-3) and load resistance (3-4), directly relate to functional power and voltage levels.

$$D = 1 - \frac{V_{IN}}{V_{OUT}} \tag{3-3}$$

$$R = \frac{V_{OUT}^2}{P_{OUT}} \tag{3-4}$$

The chose power and voltage levels specify a 70% duty cycle and  $13.333\Omega$  load resistance.

$$D = 1 - \frac{6V}{20V} = 0.7$$

$$R = \frac{(20V)^2}{30W} = 13.333 \,\Omega$$

A third operating condition, switching frequency, provides a degree of freedom to adjust component values. Increased switching frequency reduces the inductor (3-5), output capacitor (2-21) and input capacitor (2-23) component values. Because the performance comparison regards inductor current ripple, switching frequency's impact on inductor value outweighs the impact on capacitor values.

$$L = \frac{V_{IN}^2 \cdot D}{\% \Delta i_{IN} \cdot f \cdot P_{OUT}}$$

(3-5)

Switching frequency also constrains switching controller selection. Some controllers offer adjustable switching frequency, while others operate at a fixed frequency. Generally, most controllers operate between 100 kHz and 2 MHz. Selecting a

200 kHz switching frequency keeps all three component values within reasonable ranges and preserves a wide selection of switching controllers.

$$L = \frac{(6 V)^2 \cdot 0.7}{0.4 \cdot (200 \ kHz) \cdot (30 \ W)} = 10.5 \ \mu H$$

$$C_{out} = \frac{D \cdot T_s}{R \cdot \frac{\Delta V_{out}}{V_{out}}} = \frac{0.7 \cdot (5 \ \mu s)}{(13.333 \ \Omega) \cdot (0.005)} = 52.5 \ \mu F$$

$$C_{in} = \frac{D \cdot T_s^2}{8L \cdot \frac{\Delta V_{IN}}{V_{IN}}} = \frac{0.7 \cdot (5 \ \mu s)^2}{8 \cdot (10 \ \mu H) \cdot (0.005)} = 43.75 \ \mu F$$

Table 3-2 presents the complete design requirements, derived from the functional parameters and stated design goals, using standard boost converter relationships. These constraints establish the baseline performance of the standard boost converter and limit the modified design to validate the performance comparison.

| Parameter           | Value    |

|---------------------|----------|

| Output Power        | 30 W     |

| Output Voltage      | 20 V     |

| Output Current      | 1.5 A    |

| Input Voltage       | 6 V      |

| Input Current       | 5 A      |

| Load Resistance     | 13.333 Ω |

| Switching Frequency | 200 kHz  |

| Switch Duty Cycle   | 70%      |

| Inductance          | 10 µH    |

| Output Capacitance  | 50 µF    |

| Input Capacitance   | 44 µF    |

Table 3-2. Converter Design Parameters

# 4. ANALYSIS AND SIMULATION

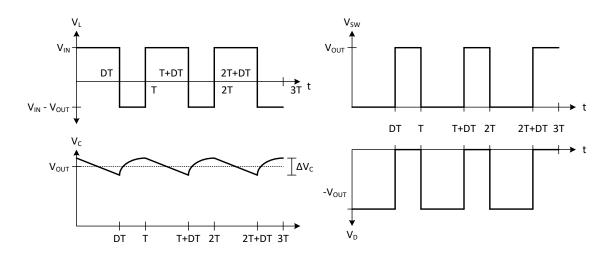

Basic converter analysis techniques describe converter performance by exploiting inductor current slope assumptions. These assumptions eliminate the need to solve the underlying differential equations that describe inductor current and capacitor voltage. Section 2.5 presents a typical boost converter analysis assuming a linear inductor current slope during both switching states. Linear inductor current slope implies pure DC voltage across the inductor and a converter switching frequency higher than the converter's LC resonant frequency. These assumptions remain valid for properly-designed boost converters, and the simple analysis accurately predicts inductor current ripple.

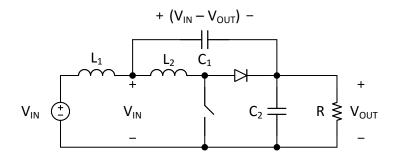

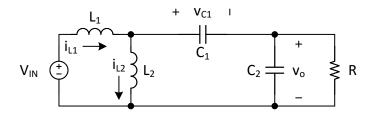

The modified boost converter topology challenges the assumptions that facilitate simplified analysis. Assuming the converter's switching frequency exceeds the circuit's resonant frequencies, linear current slope analysis predicts large  $L_2$  current ripple, proportional to  $V_{IN}$ , and zero  $L_1$  current ripple, based on the DC voltages Figure 4-1 depicts across each inductor.

Figure 4-1. Modified Boost Converter DC Voltages

This simple analysis ignores the small voltage ripple on both capacitors, which induces a small current ripple in both inductors. The linear current slope analysis remains accurate when large current ripple introduced by DC voltage across the inductor masks the small addition. In the modified boost converter, simple analysis accurately predicts  $L_2$  current ripple, but not  $L_1$  current ripple, which depends entirely on small AC voltage ripple applied across the inductor. Therefore, input current ripple prediction requires more complex analysis of the modified boost converter.

State space analysis describes a DC/DC converter using a set of time differential equations. Averaging the state space representations during switch-on and switch-off operation provides the converter's DC transfer function, verifying boost-type behavior. Transformation to the *m*-domain, normalizes the time-domain state equation over the converter's switching period. Solving the *m*-domain state equation describes steady-state converter behavior. Unlike sinusoidal waveforms, analytical switching waveform expressions provide little intuition towards performance measurements such as peak-to-peak, RMS, and average values [33]. Computer-aided, numerical solutions provide relevant boost converter performance measurements, particularly peak-to-peak and percent input current ripple, facilitating converter design choices. Analyzing the known standard topology alongside the modified topology validates the steady-state model.

## 4.1 State Space Analysis

The state space analysis method describes a system's dynamic elements, state variables, as a set of first-order differential equations known as the state equation. DC/DC converters require a state equation, for each switching state. Control loop and DC transfer function analysis rely on the averaged state equation over all the converter's switching states. Combining the individual state equations sequentially describes the converter's dynamic behavior across the complete switching cycle.

26

Energy storage elements, capacitors and inductors, determine a DC/DC converter's dynamic behavior. Simple differential relationships make inductor currents and capacitor voltages the best state variable choices. Circuit analysis completes the associated first order differential equations. Kirchhoff's voltage law (KVL) replaces inductor voltage with capacitor voltage state variables and Kirchhoff's current law (KCL) replaces capacitor current with inductor current state variables. The complete state equation describes each state variable's derivative using the system's state variables and inputs.

### 4.1.1 Standard Boost Converter

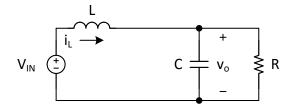

The standard boost converter's state model requires two state variables, inductor current,  $i_L$ , and output voltage,  $v_o$ , shown in Figure 4-2.

Figure 4-2. Standard Boost Converter State Variables

Figure 4-3 displays the standard boost state variables during the switch-on state.

Figure 4-3. Standard Boost Converter Switch-On State Variables

KVL determines the inductor current differential equation (4-1) and KCL

provides the output voltage differential equation (4-2).

$$\frac{di_L}{dt} = \frac{1}{L} V_{IN} \tag{4-1}$$

$$\frac{dv_o}{dt} = -\frac{1}{CR}v_o \tag{4-2}$$

The switch-on state equation (4-3) summarizes the state variable differential equations in matrix form.

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_o}{dt} \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ 0 & -\frac{1}{CR} \end{bmatrix} \begin{bmatrix} i_L \\ v_o \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} V_{IN}$$

(4-3)

Figure 4-4 depicts the standard boost state variables in the switch-off state.

Figure 4-4. Standard Boost Converter Switch-Off State Variables

KVL around the circuit and KCL at the output node determine the inductor

current (4-4) and output voltage (4-5) differential equations.

$$\frac{di_L}{dt} = \frac{1}{L} V_{IN} - \frac{1}{L} v_o \tag{4-4}$$

$$\frac{dv_o}{dt} = \frac{1}{C}i_L - \frac{1}{CR}v_o \qquad (4-5)$$

The switch-off state equation (4-6) summarizes both state-variable differential equations in matrix form.

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_o}{dt} \end{bmatrix} = \begin{bmatrix} 0 & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{CR} \end{bmatrix} \begin{bmatrix} i_L \\ v_o \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} V_{IN}$$

(4-6)

Summing the switch-on and switch-off state equations, weighted by duty cycle and inverse duty cycle, provides the average state equation across the switching period (4-7).

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_o}{dt} \end{bmatrix} = D \begin{bmatrix} 0 & 0 \\ 0 & -\frac{1}{CR} \end{bmatrix} \begin{bmatrix} i_L \\ v_o \end{bmatrix} + (1-D) \begin{bmatrix} 0 & -\frac{1}{L} \\ \frac{1}{C} & -\frac{1}{CR} \end{bmatrix} \begin{bmatrix} i_L \\ v_o \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ 0 \end{bmatrix} V_{IN} \qquad (4-7)$$

The DC transfer functions describe the circuit's behavior as the state variables reach pure DC values. Under these conditions both differentials approach zero.

$$\begin{bmatrix} \frac{di_L}{dt} \\ \frac{dv_o}{dt} \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \end{bmatrix}$$

Solving the resulting inductor current equation (4-8) yields the DC voltage transfer function (4-9).

$$0 = (1 - D)\left(-\frac{1}{L}\right)V_{OUT} + \frac{1}{L}V_{IN}$$

(4 - 8)

$$V_{OUT} = \frac{V_{IN}}{(1-D)}$$

(4-9)

Solving the output voltage equation (4-10) yields the DC current transfer function (4-12).

$$0 = D\left(-\frac{1}{CR}\right)V_{OUT} + (1-D)\left(\frac{1}{C}\right)I_{IN} + (1-D)\left(-\frac{1}{CR}\right)V_{OUT} \qquad (4-10)$$

$$I_{OUT} = \frac{V_{OUT}}{R} \tag{4-11}$$

$$I_{IN} = \frac{I_{OUT}}{(1-D)}$$

(4 - 12)

State space averaging produces the same DC transfer functions presented in Section 2.5.3 using steady-state current ripple constraints.

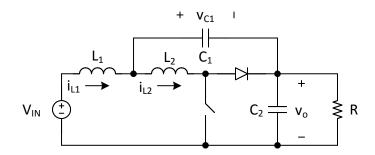

# 4.1.2 Modified Boost Converter

The modified boost converter's state space model requires two additional state variables. Figure 4-5 shows the two inductor currents,  $i_{L1}$  and  $i_{L2}$ , and two capacitor voltages,  $v_{C1}$  and  $v_0$ , describing the modified boost converter's dynamics.

Figure 4-5. Modified Boost Converter State Variables

Figure 4-6 depicts the modified boost state variables during the switch-on state.

Figure 4-6. Modified Boost Converter Switch-On State Variables

KVL around the outer loop provides the L<sub>1</sub> current differential equation (4-13)

and KVL around the inner loop provides the L<sub>2</sub> current differential equation (4-14).

$$\frac{di_{L1}}{dt} = -\frac{1}{L_1}v_{C1} - \frac{1}{L_1}v_o + \frac{1}{L_1}V_{IN}$$

(4 - 13)

$$\frac{di_{L2}}{dt} = \frac{1}{L_2}v_{C1} + \frac{1}{L_2}v_o \tag{4-14}$$

KCL at the circuit's two nodes provide the capacitor voltage differential equations for  $v_{C1}$  (4-15) and  $v_o$  (4-16).

$$\frac{dv_{C1}}{dt} = \frac{1}{C_1}i_{L1} - \frac{1}{C_1}i_{L2} \tag{4-15}$$

$$\frac{dv_o}{dt} = \frac{1}{C_2}i_{L1} - \frac{1}{C_2}i_{L2} - \frac{1}{C_2R}v_o \qquad (4-16)$$

The modified boost converter's switch-on state equation (4-17) contains the statevariable differential equations in matrix form.

$$\begin{bmatrix} \frac{di_{L1}}{dt} \\ \frac{di_{L2}}{dt} \\ \frac{dv_{c1}}{dt} \\ \frac{dv_{o}}{dt} \end{bmatrix} = \begin{bmatrix} 0 & 0 & -\frac{1}{L_1} & -\frac{1}{L_1} \\ 0 & 0 & \frac{1}{L_2} & \frac{1}{L_2} \\ \frac{1}{C_1} & -\frac{1}{C_1} & 0 & 0 \\ \frac{1}{C_2} & -\frac{1}{C_2} & 0 & -\frac{1}{C_2R} \end{bmatrix} \begin{bmatrix} i_{L1} \\ i_{L2} \\ v_{c1} \\ v_{o} \end{bmatrix} + \begin{bmatrix} \frac{1}{L_1} \\ 0 \\ 0 \\ 0 \end{bmatrix} V_{IN}$$

(4 - 17)

Figure 4-7 shows the modified boost converter state variables in the switch-off state.

Figure 4-7. Modified Boost Converter Switch-Off State Variables

KVL around the circuit's outer loop determines the L1 current differential

equation (4-18). KVL in the C<sub>1</sub> loop determines the L<sub>2</sub> current differential equation (4-19).

$$\frac{di_{L1}}{dt} = -\frac{1}{L_1}v_{C1} - \frac{1}{L_1}v_o + \frac{1}{L_1}V_{IN}$$

(4 - 18)

$$\frac{di_{L2}}{dt} = \frac{1}{L_2} v_{C1} \tag{4-19}$$

KCL at the circuit's nodes determines the  $C_1$  voltage differential equation (4-20) and  $C_2$  voltage differential equation (4-21).

$$\frac{dv_{C1}}{dt} = \frac{1}{C_1}i_{L1} - \frac{1}{C_1}i_{L2} \qquad (4-20)$$

$$\frac{dv_o}{dt} = \frac{1}{C_2} i_{L1} - \frac{1}{C_2 R} v_o \tag{4-21}$$

The modified boost converter's switch-off state equation (4-22) contains the four state-variable differential equations in matrix form.

$$\begin{bmatrix} \frac{di_{L1}}{dt} \\ \frac{di_{L2}}{dt} \\ \frac{dv_{C1}}{dt} \\ \frac{dv_{O}}{dt} \end{bmatrix} = \begin{bmatrix} 0 & 0 & -\frac{1}{L_{1}} & -\frac{1}{L_{1}} \\ 0 & 0 & \frac{1}{L_{2}} & 0 \\ \frac{1}{C_{1}} & -\frac{1}{C_{1}} & 0 & 0 \\ \frac{1}{C_{2}} & 0 & 0 & -\frac{1}{C_{2}R} \end{bmatrix} \begin{bmatrix} i_{L1} \\ i_{L2} \\ v_{C1} \\ v_{o} \end{bmatrix} + \begin{bmatrix} \frac{1}{L_{1}} \\ 0 \\ 0 \\ 0 \end{bmatrix} V_{IN}$$

(4 - 22)

Summing the modified boost converter's state equations, weighted by their switching period fraction, produces the average state equation (4-23).

$$\begin{bmatrix} \frac{di_{L1}}{dt} \\ \frac{di_{L2}}{dt} \\ \frac{dv_{c1}}{dt} \\ \frac{dv_{o}}{dt} \end{bmatrix} = D \cdot A_{switch-on} \begin{bmatrix} i_{L1} \\ i_{L2} \\ v_{c1} \\ v_{o} \end{bmatrix} + (1-D) \cdot A_{switch-off} \begin{bmatrix} i_{L1} \\ i_{L2} \\ v_{c1} \\ v_{o} \end{bmatrix} + \begin{bmatrix} \frac{1}{L_{1}} \\ 0 \\ 0 \\ 0 \end{bmatrix} V_{IN} (4-23)$$

$$A_{switch-on} = \begin{bmatrix} 0 & 0 & -\frac{1}{L_1} & -\frac{1}{L_1} \\ 0 & 0 & \frac{1}{L_2} & \frac{1}{L_2} \\ \frac{1}{C_1} & -\frac{1}{C_1} & 0 & 0 \\ \frac{1}{C_2} & -\frac{1}{C_2} & 0 & -\frac{1}{C_2R} \end{bmatrix}$$

$$A_{switch-off} = \begin{bmatrix} 0 & 0 & -\frac{1}{L_1} & -\frac{1}{L_1} \\ 0 & 0 & \frac{1}{L_2} & 0 \\ \frac{1}{C_1} & -\frac{1}{C_1} & 0 & 0 \\ \frac{1}{L_2} & 0 & 0 & -\frac{1}{C_2R} \end{bmatrix}$$

The differentials approach zero as the state variables reach their DC value.

$$\begin{bmatrix} \frac{di_{L1}}{dt} \\ \frac{di_{L2}}{dt} \\ \frac{dv_{C1}}{dt} \\ \frac{dv_o}{dt} \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

Solving the averaged  $L_1$  current equation (4-24) and the averaged  $L_2$  current equation (4-25) determine the relationships between the circuit's average voltages (4-25 and 4-27).

$$-\frac{D}{L_1}(V_{C1} + V_{OUT}) - \frac{(1-D)}{L_1}(V_{C1} + V_{OUT}) + \frac{1}{L_1}V_{IN} = 0 \qquad (4-24)$$

$$V_{IN} = V_{C1} + V_{OUT} (4 - 25)$$

$$\frac{D}{L_2}(V_{C1} + V_{OUT}) + \frac{(1-D)}{L_2}V_{C1} = 0$$

(4-26)

$$V_{C1} = -DV_{OUT} \tag{4-27}$$

Consolidating both relationships produces the modified boost converter's DC transfer function (4-28).

$$V_{OUT} = \frac{V_{IN}}{(1-D)}$$

(4 - 28)

Solving the average C1 voltage equation (4-29) demonstrates the equality between the average inductor currents (4-30).

$$\frac{D}{C_1}(I_{IN} - I_{L2}) + \frac{(1-D)}{C_1}(I_{IN} - I_{L2}) = 0 \qquad (4-29)$$

$$I_{IN} = I_{L2}$$

(4 - 30)

Considering the equality of the average inductor currents while solving the average  $C_2$  voltage equation (4-31) yields the DC current transfer function (4-32).

$$\frac{D}{C_2} \left( I_{IN} - I_{L2} - \frac{V_{OUT}}{R} \right) + \frac{(1-D)}{C_2} \left( I_{IN} - \frac{V_{OUT}}{R} \right) = 0$$

(4-31)

$$I_{IN} = \frac{I_{OUT}}{(1-D)}$$

(4-32)

The modified boost converter's DC transfer functions match the standard boost topology, demonstrating functional equality. On average, both converters share the same relationships between switch duty cycle and input and output quantities.

# 4.2 Steady-State m-Domain State Equations

During steady-state operation, a DC/DC converter returns to the same state at the beginning of each switching cycle. The switch-on and switch-off state equations each govern a portion of the cycle. Modeling the switching transition creates a unified, periodic state equation. An *m*-domain state equation describes the converter's behavior over a generalized switching cycle.

Independent variable transformation (4-33) partitions the time domain into a set of discrete switching cycles in the *m*-domain [33].

$$t = (n + m)T$$

(4 - 33)

$n = 0, 1, 2, 3, ...$

$0 \le m < 1$

Applying the transformation reduces a periodic, time-domain differential equation (4-34) into an *m*-domain differential equation (4-35) describing the  $n^{th}$  time-domain cycle.

$$\frac{dx(t)}{dt} = x(t) \tag{4-34}$$

$$\frac{dx_n(m)}{dm} = x_n(m) \cdot T \tag{4-35}$$

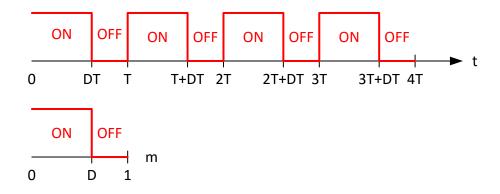

The transformation also simplifies the converter's switching transition model. Transitions in the time domain occur relative to the switching period and duty cycle. However, *m*-domain switching transitions depend only on duty cycle, allowing a simple piecewise function to model the transition. Figure 4-8 illustrates this difference.

Figure 4-8. Time-domain and m-domain Switching Transitions

# 4.2.1 Standard Boost Converter

The standard boost converter's switch-off state equation (4-6) contains two terms not present in the switch-on state equation (4-3). Applying the standard boost switching function (4-36) to the switch-off equation models the transition in the *m*-domain.

$$f_b(m) = \begin{cases} 0, for \ 0 \le m < D\\ 1, for \ D \le m < 1 \end{cases}$$

(4-36)

The standard boost *m*-domain state equation (4-37) describes the converter's behavior during a generalized, steady-state switching cycle.

$$\begin{bmatrix} \frac{di_{L,n}}{dm} \\ \frac{dv_{o,n}}{dm} \end{bmatrix} = \begin{bmatrix} 0 & -f_b(m)\frac{T}{L} \\ f_b(m)\frac{T}{C} & -\frac{T}{CR} \end{bmatrix} \begin{bmatrix} i_{L,n} \\ v_{o,n} \end{bmatrix} + \begin{bmatrix} T \\ L \\ 0 \end{bmatrix} V_{IN}$$

(4-37)

# 4.2.2 Modified Boost Converter

The modified boost switch-on state equation (4-17) contains two terms not present in the switch-off state equation (4-18). Applying the modified boost switching function (4-38) to the switch-on equation models the transition in the *m*-domain.

$$f_{mb}(m) = \begin{cases} 1, for \ 0 \le m < D\\ 0, for \ D \le m < 1 \end{cases}$$

(3-38)

The modified boost *m*-domain state equation (4-39) describes the converter's behavior during a generalized, steady-state switching cycle.

$$\begin{bmatrix} \frac{di_{L1,n}}{dm} \\ \frac{di_{L2,n}}{dm} \\ \frac{dv_{C1,n}}{dm} \\ \frac{dv_{o,n}}{dm} \\ \frac{dv_{o,n}}{dm} \end{bmatrix} = \begin{bmatrix} 0 & 0 & -\frac{T}{L_1} & -\frac{T}{L_1} \\ 0 & 0 & \frac{T}{L_2} & f_{mb}(m) \frac{T}{L_2} \\ \frac{T}{C_1} & -\frac{T}{C_1} & 0 & 0 \\ \frac{T}{C_2} & -f_{mb}(m) \frac{T}{C_2} & 0 & -\frac{T}{C_2R} \end{bmatrix} \begin{bmatrix} i_{L1,n} \\ i_{L2,n} \\ v_{O,n} \end{bmatrix} + \begin{bmatrix} \frac{T}{L_1} \\ 0 \\ 0 \\ 0 \end{bmatrix} V_{IN} \quad (4-39)$$

# 4.3 Numerical m-Domain State Equation Solutions

Matlab's *ode45* function provides numerical state equation solutions. Solving the system of first-order differential equations requires initial conditions (ICs). State variable average values, obtained through circuit analysis, provide initial condition estimates. Under steady-state conditions, each state variable's final value during the switch-off state equals its initial value during the switch-on state. Iteration gradually reduces the solutions' steady-state error; the difference between final switch-off value and initial switch-on value.

### 4.3.1 Initial Condition Estimates

A converter's state variable averages depend on the average voltages and currents associated with its reactive components. During steady-state operation, the average voltage across an inductor and the average current through a capacitor both approach zero. Under these conditions, the average inductor currents and capacitor voltages relate to the converter's known input and output parameters.

Table 4-1 summarizes the average voltage and current associated with the standard boost converter's inductor and capacitor.

| Component | Voltage          | Current         |

|-----------|------------------|-----------------|

| L         | 0 V              | I <sub>IN</sub> |

| С         | V <sub>OUT</sub> | 0 A             |

Table 4-1. Standard Boost Converter Component Averages

Table 4-2 summarizes the average voltage and current associated with the modified boost converter's reactive components.

| Component      | Voltage                            | Current         |

|----------------|------------------------------------|-----------------|

| L <sub>1</sub> | 0 V                                | I <sub>IN</sub> |

| L <sub>2</sub> | 0 V                                | I <sub>IN</sub> |

| C <sub>1</sub> | V <sub>IN</sub> - V <sub>OUT</sub> | 0 A             |

| C <sub>2</sub> | V <sub>OUT</sub>                   | 0 A             |

Table 4-2. Modified Boost Converter Component Averages

Table 4-3 lists the estimated initial condition for each state variable in the standard and modified boost converters, based on functional requirements and the associated DC transfer functions.

| Standard Boost Converter |      | Modified Boost Converter |          |  |

|--------------------------|------|--------------------------|----------|--|

| State Variable Estimate  |      | State Variable           | Estimate |  |

|                          | 5 1  | i <sub>L1</sub>          | 5 A      |  |

| 1L                       | 5 A  | iL2                      | 5 A      |  |

|                          | 20 V | VC1                      | -14 V    |  |

| Vo                       | 20 V | Vo                       | 20 V     |  |

Table 4-3. State Equation Initial Condition Estimates

These functional converter design parameters provide reasonable initial condition estimates that allow the iterative state equation solution to converge.

# 4.3.2 Iterative State Equation Solution

Custom Matlab functions implement the iterative state equation solution process for both the standard and modified boost converters. Each function requires converter design information, including component values, switching period, input voltage, output voltage, and output power. Component values and switching period populate the state equation matrices, while input-output parameters provide the initial condition estimates for each state variable. The scripts decouple the state equation into switch-on and switchoff equations, facilitating Matlab's *ode45* function, and return the concatenated solution over the *m*-domain after iteration converges. Figure 4-9 depicts the iteration process, controlled by the steady-state error. Once the final state variable values of the switch-off solution match the initial values of the switch-on solution, within 0.0001%, the function stops iterating.

Figure 4-9. Iterative Numerical State Equation Solution

### **APPENDICES**

MA contains the Matlab files *boost\_cycle.m* and *boost\_mod\_cycle.m*, which implement the iterative state equation solution functions for the standard and modified boost converters.

## 4.4 Modified Boost Design Process

The baseline design restricts modified boost converter design choices. These parameters, detailed in Chapter 3, set switching frequency and output capacitance ( $C_2$ ) directly and constrain the modified topology's total inductance. Dividing the specified total inductance between  $L_1$  and  $L_2$ , and sizing the additional capacitor  $C_1$  remain the only topology design choices.

Design constraints limit the converter's total inductance at  $10\mu$ H, the sum of L<sub>1</sub> and L<sub>2</sub>. This design process considers three allocations of  $10\mu$ H between L<sub>1</sub> and L<sub>2</sub>: a 50/50 split, a 25/75 split, and a 75/25 split. Converter resonant frequencies and physical size limit the  $C_1$  value range. The converter's resonant behavior determines the minimum  $C_1$  value keeping the highest resonant frequency below the 200-kHz switching frequency. Setting the maximum  $C_1$  value at 50  $\mu$ F, the specified converter output capacitance, limits the modified boost converter's additional physical size. Matlab informs final component value selection, based on input current ripple performance predicted by the numerical state space equation solutions.

### 4.4.1 **Resonant Frequencies**

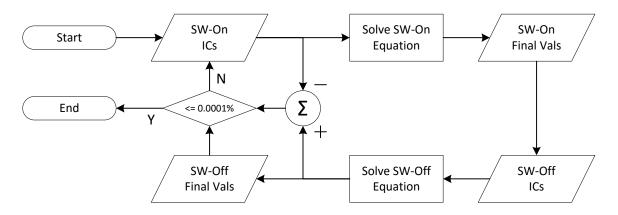

The modified boost converter topology complicates resonant frequency analysis. The standard topology contains one resonance during the switch-off state. Inspection suggests multiple resonances in the modified boost converter during the switch-of state. Figure 4-10 illustrates an AC simulation of the modified boost converter's switch-on and switch-off circuits used to observe the converter's resonant frequencies.

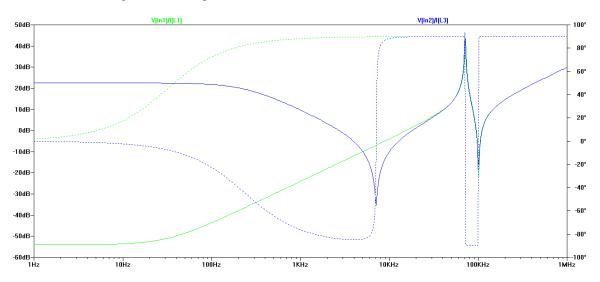

Each circuit's input impedance characteristics indicate resonant behavior. Figure 4-11 portrays the switch-on circuit's two resonant frequencies and the switch-off circuit's three resonant frequencies with  $C_1$  equal to 1  $\mu$ F. The impedance curves align at higher frequencies, suggesting the circuits share two similar resonances. However, these resonant frequencies do not match exactly; they separate as  $C_1$  value increases.

40

Figure 4-10. LTSpice Modified Boost Converter Resonance Simulation

Figure 4-11. LTSpice Modified Boost Converter Simulated Input Impedance

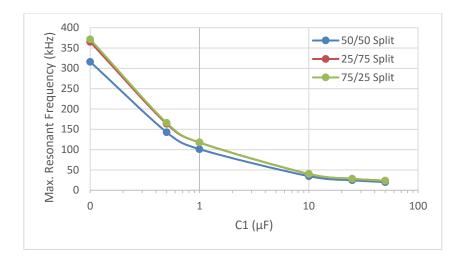

Figure 4-12 plots the converter's highest resonant frequency, obtained from the Figure 4-10 simulation, over a range of  $C_1$  values. These data suggest  $C_1$  values greater than 1uF prevent the converter's maximum resonant frequency from exceeding the 200kHz switching frequency. The data also indicate that the inductance split between  $L_1$  and  $L_2$  impacts resonant frequency less as  $C_1$  value approaches output capacitance value.

Figure 4-12. Max. Modified Boost Resonant Frequency versus C1 Value

## 4.4.2 Component Sizing

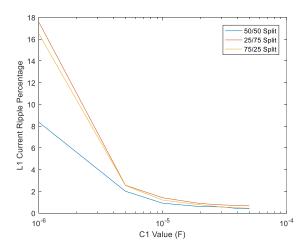

The  $L_1$  current state variable predicts the converter's input current ripple performance. Matlab provides the numerical state equation solution, calculating ripple performance using the maximum, minimum, and average  $L_1$  current values. Appendix A contains the script *boost\_mod\_design\_comp.m*, executing these calculations for all three  $L_1/L_2$  inductance splits over the selected C<sub>1</sub> value range. Figure 4-13 charts the converter's performance based on component sizing.

Figure 4-13. Modified Boost Converter Component Sizing Chart

These performance predictions agree with a simplistic explanation of the input current ripple. A larger  $C_1$  value reduces the voltage ripple across  $L_1$ , and smaller  $v_{L1}$ changes induce smaller  $i_{L1}$  changes. The  $L_1/L_2$  inductance split's impact on current ripple performance and maximum resonant frequency decrease as  $C_1$  value approaches output capacitance value. Selecting a 50/50 inductance split simplifies component selection. Table 4-4 lists the modified boost converter design parameters chosen based on predicted input current ripple performance.

| Component      | Selected Nominal Value |

|----------------|------------------------|

| L <sub>1</sub> | 5 μΗ                   |

| L <sub>2</sub> | 5 μΗ                   |

| C1             | 30 µF                  |

| C <sub>2</sub> | 50 µF                  |

Table 4-4. Modified Boost Converter Component Values

### 4.5 Design Simulation

The numerical state equation solution method provides limited design simulation by directly solving for each state variable over a single, steady-state switching cycle. These waveforms provide all necessary information, either directly or indirectly, to physically implement the converter. Given specific converter design parameters, a Matlab-simulation script performs iterative state equation solution, plots the state variable waveforms, and calculates relevant state variable measurements indicating converter performance. Comparing each converter's Matlab-simulation against theoretical DC performance and a complementary LTSpice simulation, evaluates the *m*-domain state equation model's efficacy. Table 4-5 summarizes the simulated converter designs, including functional parameters and component values. Section 4.5.3 compares both simulation technique's relevant converter performance measurements.

| Standard B       | oost Design | Modified Boost Design |          |

|------------------|-------------|-----------------------|----------|

| V <sub>IN</sub>  | 6 V         | V <sub>IN</sub>       | 6 V      |

| V <sub>OUT</sub> | 20 V        | V <sub>OUT</sub>      | 20 V     |

| P <sub>OUT</sub> | 30 W        | P <sub>OUT</sub>      | 30 W     |

| f <sub>sw</sub>  | 200 kHz     | $f_{SW}$              | 200 kHz  |

| R                | 13.333 Ω    | R                     | 13.333 Ω |

| , T              | 1011        | L <sub>1</sub>        | 5 µH     |

| L                | 10 µH       | $L_2$                 | 5 μΗ     |

| C                | 50 µF       | C1                    | 30 µF    |

| C                |             | C <sub>2</sub>        | 50 µF    |

Table 4-5. Converter Design Parameter Summary

# 4.5.1 Matlab Simulation

The *boost\_sim.m* script in Appendix A simulates the standard boost design's performance. Figure 4-14 portrays the Matlab-simulated inductor current and capacitor voltage in the standard boost converter design. The simulated waveforms take the expected shape Section 2.5.5 presents.

Figure 4-14. Matlab State Variable Waveforms for Standard Boost

Table 4-6 compares relevant Matlab simulation measurements and theoretical standard boost converter design values. The simulated average state variable values match theoretical values within one percent, while the peak-to-peak and percent ripple values match to five percent error. Appendix B contains complete standard boost measurements obtained through Matlab-simulation.

|           | Inductor Current (A) |        |         | Capacitor Voltage (V) |        | e (V)  |

|-----------|----------------------|--------|---------|-----------------------|--------|--------|

|           | Matlab               | Theory | %Diff   | Matlab                | Theory | %Diff  |

| Average   | 4.9591               | 5      | -0.818% | 19.998                | 20     | -0.01% |

| Peak-Peak | 2.1                  | 2      | 5%      | 0.105                 | 0.1    | 5%     |

| %Ripple   | 42.346%              | 40%    | 5.865%  | 0.5249%               | 0.5%   | 4.98%  |

Table 4-6. Matlab and Theoretical Standard Boost Design Performance

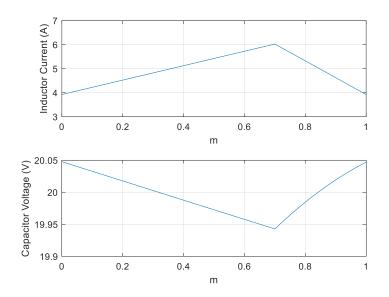

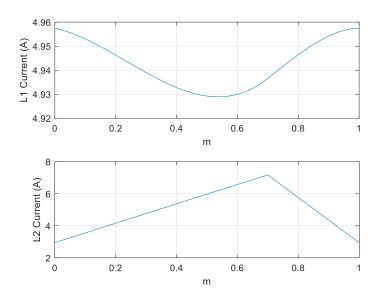

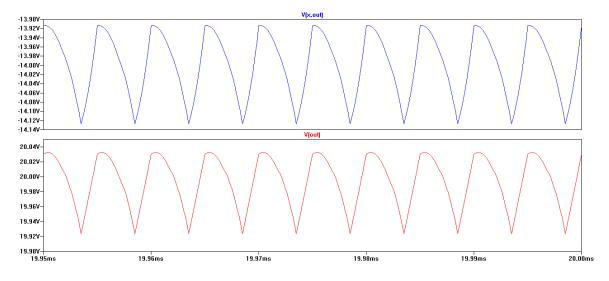

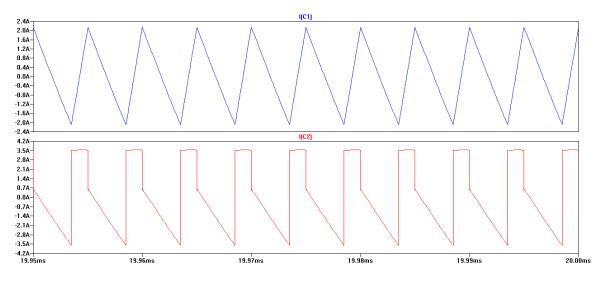

The *boost\_mod\_sim.m* script in Appendix A simulates the modified boost design's performance. Figure 4-15 presents the simulated inductor current waveforms, demonstrating agreement between the state equation model and the simplistic circuit analysis. The voltage across L1 approaches zero, and the small voltage ripple produced by current through C1 induces small current ripple through L1. The voltage across L2 approaches the standard boost converter's inductor voltage, but at half the total inductance of the standard boost design, L2 experiences twice the current ripple. These waveforms indicate the modified design's ability to contain switching noise, presenting only a small current ripple at the converter input.

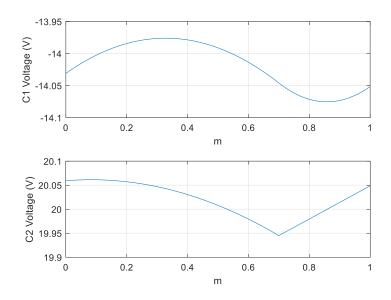

Figure 4-16 depicts both capacitor voltage waveforms, demonstrating voltage ripple performance comparable to the standard boost design. The iterative state equation solution method favors minimizing  $L_1$  current's steady-state error, the difference between initial and final values, based on the state design goal. Both capacitor voltage waveforms suffer larger steady-state error due to the chosen hierarchy.

Figure 4-15. Matlab Modified Boost Inductor Current Waveforms

Figure 4-16. Matlab Modified Boost Capacitor Voltage Waveforms

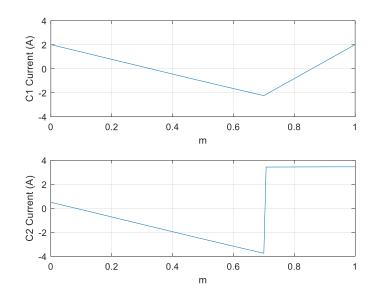

The simulation script determines capacitor current waveforms calculated from inductor current solutions and the known DC output current, using KCL relationships during each switching state. Figure 4-17 shows simulated capacitor current waveforms which help determine capacitor current ratings. Under ideal steady-state conditions, average capacitor current approaches zero. These waveforms exhibit non-zero averages and indicate the Matlab-simulation's functional limitations; small state variable solution error compounds through further calculation required to determine related waveforms.

Figure 4-17. Matlab Modified Boost Capacitor Current Waveforms

Table 4-7 compares simulated average state variable values and theoretical state variable averages derived from DC circuit analysis and functional converter parameters. Despite favoring minimal inductor current steady-state error, the Matlab simulation predicts average state variable values within approximately one percent of theory. Appendix B contains complete Matlab simulation performance measurements.

|        | L <sub>1</sub> Current (A) | L <sub>1</sub> Current (A) L <sub>2</sub> Current (A) C <sub>1</sub> Ve |         | C <sub>2</sub> Voltage (V) |

|--------|----------------------------|-------------------------------------------------------------------------|---------|----------------------------|

| Matlab | 4.9446                     | 5.0384                                                                  | -14.032 | 20.012                     |

| Theory | 5                          | 5                                                                       | -14     | 20                         |

| %Diff  | -1.108%                    | 0.768%                                                                  | 0.2286% | 0.6%                       |

Table 4-7. Matlab and Theoretical Modified Boost Design DC Performance

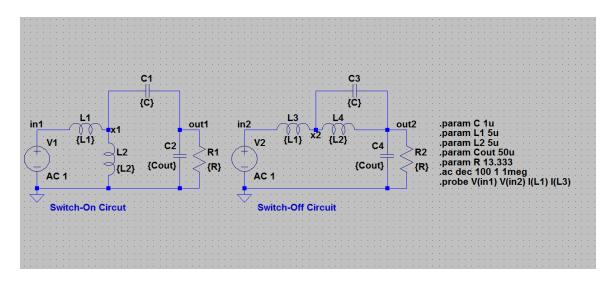

### 4.5.2 LTSpice Simulation

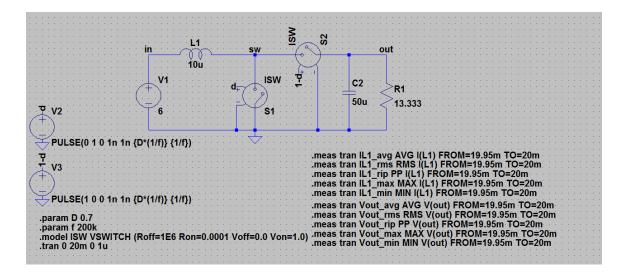

LTSpice transient simulations provide complete benchmark comparison against the Matlab-based simulations. Both converter spice simulations use non-ideal switches and open-loop PWM control. The measure command captures the relevant converter performance data over the simulation's final 50 ms, ten switching cycles; average and peak-to-peak measurements determine Spice-simulated ripple percentage. Appendix B contains complete LTSpice performance measurements for both standard and modified boost designs.

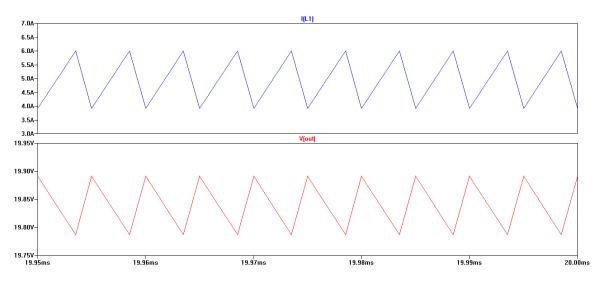

Figure 4-18 depicts the LTSpice transient simulation of the standard boost converter design. Figure 4-19 shows the standard boost state variable waveforms over the transient simulation's final ten switching cycles. These waveforms indicate approximate ripple performance similar to the Matlab simulation.

Figure 4-18. LTSpice Standard Boost Transient Simulation

Figure 4-19. LTSpice State Variable Waveforms for Standard Boost

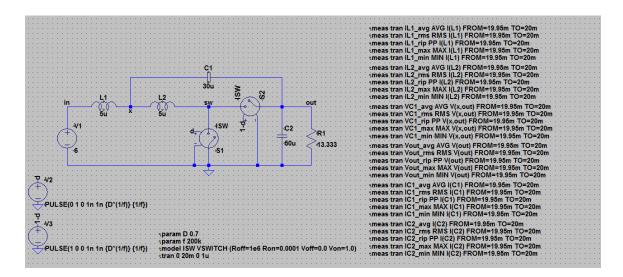

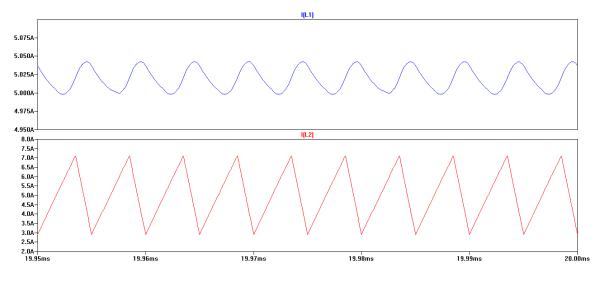

Figure 4-20 shows the LTSpice transient simulation for the modified boost converter design. Figure 4-21 presents the LTSpice modified boost inductor current waveforms, again demonstrating the design's small input current ripple. LTSpice also predicts L<sub>2</sub> current ripple twice the standard boost design's value.

Figure 4-20. LTSpice Modified Boost Transient Simulation

Figure 4-21. LTSpice Modified Boost Inductor Current Waveforms