University of Pennsylvania **ScholarlyCommons**

Publicly Accessible Penn Dissertations

Summer 8-13-2010

# Energy Efficient Load Latency Tolerance: Single-Thread Performance for the Multi-Core Era

Andrew D. Hilton University of Pennsylvania, adhilton@cis.upenn.edu

Follow this and additional works at: http://repository.upenn.edu/edissertations

Part of the Other Computer Sciences Commons

### Recommended Citation

Hilton, Andrew D., "Energy Efficient Load Latency Tolerance: Single-Thread Performance for the Multi-Core Era" (2010). Publicly Accessible Penn Dissertations. 188.

http://repository.upenn.edu/edissertations/188

$This \ paper \ is \ posted \ at \ Scholarly Commons. \ http://repository.upenn.edu/edissertations/188$ For more information, please contact libraryrepository@pobox.upenn.edu.

# Energy Efficient Load Latency Tolerance: Single-Thread Performance for the Multi-Core Era

#### **Abstract**

Around 2003, newly activated power constraints caused single-thread performance growth to slow dramatically. The multi-core era was born with an emphasis on explicitly parallel software. Continuing to grow single-thread performance is still important in the multi-core context, but it must be done in an energy efficient way.

One significant impediment to performance growth in both out-of-order and in-order processors is the long latency of last-level cache misses. Prior work introduced the idea of load latency tolerance---the ability to dynamically remove miss-dependent instructions from critical execution structures, continue execution under the miss, and re-execute miss-dependent instructions after the miss returns. However, previously proposed designs were unable to improve performance in an energy-efficient way---they introduced too many new large, complex structures and re-executed too many instructions.

This dissertation describes a new load latency tolerant design that is both energy-efficient, and applicable to both in-order and out-of-order cores. Key novel features include formulation of slice re-execution as an alternative use of multi-threading support, efficient schemes for register and memory state management, and new pruning mechanisms for drastically reducing load latency tolerance's dynamic execution overheads.

Area analysis shows that energy-efficient load latency tolerance increases the footprint of an out-of-order core by a few percent, while cycle-level simulation shows that it significantly improves the performance of memory-bound programs. Energy-efficient load latency tolerance is more energy-efficient than---and synergistic with---existing performance technique like dynamic voltage and frequency scaling (DVFS).

### Degree Type

Dissertation

### Degree Name

Doctor of Philosophy (PhD)

### **Graduate Group**

Computer and Information Science

### First Advisor

Amir Roth

#### Keywords

BOLT, iCFP, Computer Architecture, Latency Tolerance, Speculative Retirement

#### **Subject Categories**

Other Computer Sciences

# ENERGY EFFICIENT LOAD LATENCY TOLERANCE: SINGLE-THREAD PERFORMANCE FOR THE MULTI-CORE ERA

Andrew D. Hilton

A DISSERTATION

in

Computer and Information Science

Presented to the Faculties of the University of Pennsylvania

in

Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

2010

Amir Roth, Associate Professor of Computer and Information Science Supervisor of Dissertation

Jianbo Shi, Associate Professor of Computer and Information Science Graduate Group Chairperson

### **Dissertation Committee**

Milo Martin, Associate Professor of Computer and Information Science

José Martínez, Associate Professor of Electrical and Computer Engineering

Andre DeHon, Associate Professor of Electrical and System Engineering

Rahul Mangharam, Assistan Professor of Electrical and System Engineering

# Energy Efficient Load Latency Tolerance: Single-Thread Performance for the Multi-Core Era

**COPYRIGHT**

2010

Andrew D. Hilton

# Acknowledgements

Graduate school has been a long journey with many ups and downs, successes and frustrations, joys and sorrows. There are many people who I would like to thank for their help along the way.

First, I would like to thank my advisor, Amir Roth. If not for my enjoyment of your class, I would probably have never become an architect. Your help along the way has been invaluable—advice, refinements to ideas, and encouragement.

I would like to thank my committee—Milo Martin, Jose Martinez, Andre DeHon, and Rahul Mangharam—for their useful advice and suggestions along the way.

My academic siblings—Vlad Petric, Anne Bracy, and Tingting Sha—have provided help and encouragement, and have been with me through many all-nighters. I would also like to thank the other members of my research group, past and present—Marc Corliss, Colin Blundell, Arun Raghavan, Santosh Nagarakatte, Neeraj Eswaran, and Vivek Rane.

I have had many outstanding friends here, who provided moral support and encouragement, as well as fun. Jeff Vaughan and Nick Taylor were the best house-mates one could ask for. I'd also like to thank Karl Mazurak, Kuzman Ganchev, Brian Aydemir, Emily Pitler, and Jenn Wortman Vaughan for their friendship and support. I'd like to thank Maestro Mark Masters and everyone at the Fencing Academy of Philadelphia for all the enjoyment I had fencing during my time in graduate school.

I'd like to thank my family for all they have done for me throughout my life. I'd specifically like to thank my parents for pushing me to excel academically throughout my entire childhood.

Finally, I'd like to thank my girlfriend, Margaret Foster for all of her support, encouragement, and love.

### **ABSTRACT**

# ENERGY EFFICIENT LOAD LATENCY TOLERANCE: SINGLE-THREAD PERFORMANCE FOR THE MULTI-CORE ERA

#### Andrew D. Hilton

### Amir Roth

Around 2003, newly activated power constraints caused single-thread performance growth to slow dramatically. The multi-core era was born with an emphasis on explicitly parallel software. Continuing to grow single-thread performance is still important in the multi-core context, but it must be done in an energy efficient way.

One significant impediment to performance growth in both out-of-order and in-order processors is the long latency of last-level cache misses. Prior work introduced the idea of *load latency tolerance*—the ability to dynamically remove miss-dependent instructions from critical execution structures, continue execution under the miss, and re-execute miss-dependent instructions after the miss returns. However, previously proposed designs were unable to improve performance in an energy-efficient way—they introduced too many new large, complex structures and re-executed too many instructions.

This dissertation describes a new load latency tolerant design that is both energy-efficient, and applicable to both in-order and out-of-order cores. Key novel features include formulation of slice re-execution as an alternative use of multi-threading support, efficient schemes for register and memory state management, and new pruning mechanisms for drastically reducing load latency tolerance's dynamic execution overheads.

Area analysis shows that energy-efficient load latency tolerance increases the footprint of an out-of-order core by a few percent, while cycle-level simulation shows that it significantly improves the performance of memory-bound programs. Energy-efficient load latency tolerance is more energy-efficient than—and synergistic with—existing performance technique like dynamic voltage and frequency scaling (DVFS).

# **Contents**

| A | Acknowledgements |        |                                                       |    |  |

|---|------------------|--------|-------------------------------------------------------|----|--|

| 1 | Introduction     |        |                                                       |    |  |

|   | 1.1              | DVFS   | : Accelerating Computation-Bound Programs             | 2  |  |

|   | 1.2              | Load I | Latency Tolerance: Accelerating Memory-bound Programs | 4  |  |

|   | 1.3              | Energy | y Efficient Load Latency Tolerance: BOLT and iCFP     | 5  |  |

|   | 1.4              | Contri | ibutions                                              | 9  |  |

|   | 1.5              | Previo | ously Published Work                                  | 10 |  |

|   | 1.6              | Docum  | ment Organization                                     | 11 |  |

| 2 | Bac              | kgroun | d                                                     | 12 |  |

|   | 2.1              | Non-s  | calability of the Out-of-order Window                 | 14 |  |

|   |                  | 2.1.1  | Issue Queue                                           | 14 |  |

|   |                  | 2.1.2  | Physical Register File                                | 18 |  |

|   |                  | 2.1.3  | Store Queue                                           | 21 |  |

|   |                  | 2.1.4  | Load Queue                                            | 23 |  |

|   |                  | 2.1.5  | Load Latency Tolerance: Virtually Scaling the Window  | 25 |  |

|   | 2.2              | Runah  | nead Execution                                        | 27 |  |

|   |                  | 2.2.1  | Load and Store Queues                                 | 28 |  |

|   |                  | 2.2.2  | Efficiency                                            | 28 |  |

|   | 2.3 | Check   | pointed Early Load Retirement and                                |    |

|---|-----|---------|------------------------------------------------------------------|----|

|   |     | Check   | point Assisted Value Prediction                                  | 29 |

|   |     | 2.3.1   | Load and Store Queues                                            | 30 |

|   | 2.4 | Waitin  | g Instruction Buffer                                             | 30 |

|   | 2.5 | Contin  | nual Flow Pipelines                                              | 31 |

|   |     | 2.5.1   | Register management: Checkpoint Processing and Recovery          | 32 |

|   |     | 2.5.2   | Slice Management and Processing                                  | 33 |

|   |     | 2.5.3   | Load and store management                                        | 34 |

|   | 2.6 | KILO-   | and Decoupled KILO-Instruction Processors                        | 36 |

|   |     | 2.6.1   | Decoupled KILO-Instruction Processor                             | 36 |

|   |     | 2.6.2   | Scalability of Load Latency Tolerant Designs                     | 37 |

|   | 2.7 | Scalab  | ole Load and Store Queues                                        | 39 |

|   |     | 2.7.1   | Store Vulnerability Window (SVW)                                 | 39 |

|   |     | 2.7.2   | Store Queue Index Prediction (SQIP)                              | 40 |

|   |     | 2.7.3   | SVW/SQIP Example                                                 | 40 |

|   |     | 2.7.4   | Multiprocessor Issues                                            | 42 |

|   |     | 2.7.5   | Scalability                                                      | 43 |

| 3 | BOI | T Micr  | roarchitecture                                                   | 46 |

|   | 3.1 | BOLT    | Overview                                                         | 47 |

|   | 3.2 | Regist  | er Management                                                    | 52 |

|   |     | 3.2.1   | ROB-style Register Management as Reference Counting              | 53 |

|   |     | 3.2.2   | Combining ROB-style and CPR-style Register Management            | 55 |

|   |     | 3.2.3   | Tracking Live-Out Destination Registers of Deferred Instructions | 55 |

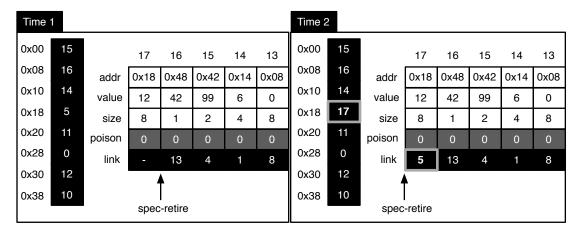

|   | 3.3 | Store-1 | to-load Forwarding                                               | 58 |

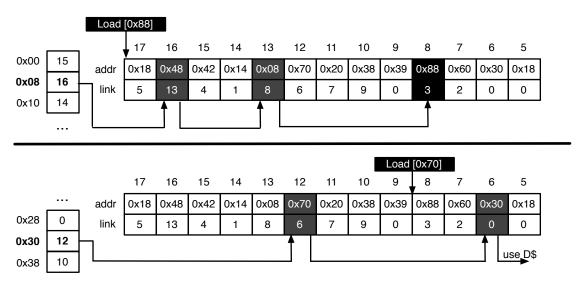

|   |     | 3.3.1   | Chained Store Buffer Mechanics                                   | 60 |

|   |     | 3.3.2   | Implementation Issues                                            | 63 |

|   | 3.4 | Load V  | Verification                                                     | 66 |

|   |     | 3 4 1   | Verification Relative to Same-thread Stores                      | 67 |

|   |      | 3.4.2   | Verification Relative to Stores from Other Threads           | 69  |

|---|------|---------|--------------------------------------------------------------|-----|

|   | 3.5  | Instruc | etion Granularity Retirement                                 | 72  |

|   |      | 3.5.1   | SDR (Silent Deterministic Replay) and                        |     |

|   |      |         | DSC (Decoupled Store Completion)                             | 73  |

| 4 | Dyn  | amic E  | fficiency                                                    | 75  |

|   | 4.1  | Miss F  | Re-execution Pruning                                         | 75  |

|   |      | 4.1.1   | Implementation: Antidotes                                    | 76  |

|   |      | 4.1.2   | Store-to-load Dependences                                    | 78  |

|   |      | 4.1.3   | Restarting A Re-execution Pass: Optimizing Loads that Return |     |

|   |      |         | Out of Order                                                 | 79  |

|   |      | 4.1.4   | Need For More Sophisticated Pruning                          | 79  |

|   | 4.2  | Join R  | e-execution Pruning: Optimizing Parallel Load Misses         | 80  |

|   |      | 4.2.1   | Implementation: Refining Antidote Propagation                | 82  |

|   | 4.3  | Pointe  | r-chasing Deferral Pruning: Optimizing Dependent Load Misses | 84  |

|   |      | 4.3.1   | Implementation: Extended Antidote Bit-vectors                | 86  |

|   |      | 4.3.2   | Design Choices                                               | 88  |

| 5 | Perf | ormano  | ee Analysis                                                  | 90  |

|   | 5.1  | BOLT    | Configuration: Load Latency Tolerance for L2 and L3 Misses   | 98  |

|   | 5.2  | BOLT    | vs. DVFS                                                     | 100 |

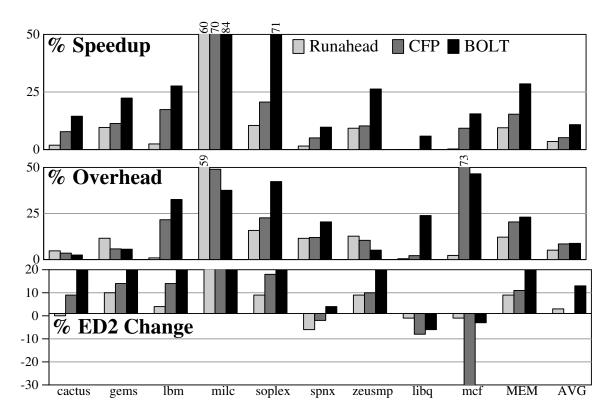

|   | 5.3  | BOLT    | vs. Runahead                                                 | 102 |

|   | 5.4  | BOLT    | vs. CFP                                                      | 105 |

|   |      | 5.4.1   | Effect Isolation: Register Substrate                         | 107 |

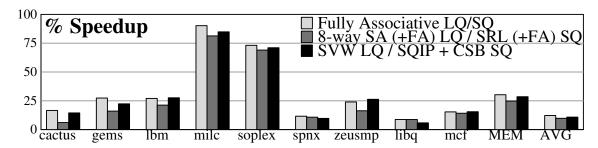

|   |      | 5.4.2   | Effect Isolation: Load and Store Queue Designs               | 109 |

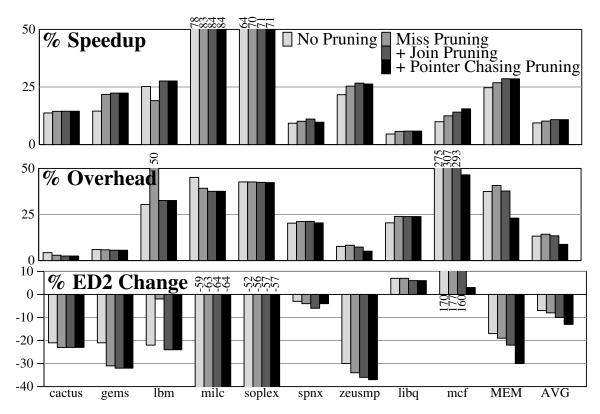

|   |      | 5.4.3   | Effect Isolation: Pruning Mechanisms                         | 111 |

|   | 5.5  | Summ    | ary Comparison                                               | 113 |

|   |      | 5.5.1   | Behavior on Non-Memory Bound Benchmarks                      | 114 |

|   |      | 5.5.2   | Oualitative Comparison of All Five Designs                   | 116 |

| •  | CVV  |          | Overhead and Optimizations 151                  |

|----|------|----------|-------------------------------------------------|

| Ap | pend | ices     | 151                                             |

|    | 7.1  | Future   | Work                                            |

| 7  | Con  | clusions | s 147                                           |

|    |      | 6.2.5    | Qualitative Comparison Summary                  |

|    |      | 6.2.4    | Sun's Rock                                      |

|    |      | 6.2.3    | Simple Latency Tolerant Processor               |

|    |      | 6.2.2    | "Flea-flicker" Multipass Pipelining             |

|    |      | 6.2.1    | Runahead Execution                              |

|    | 6.2  | Other    | In-order Load Latency Tolerance Designs         |

|    |      | 6.1.3    | Load Verification                               |

|    |      | 6.1.2    | Store-Load Forwarding                           |

|    |      | 6.1.1    | Register Management                             |

|    | 6.1  | iCFP:    | In-order Continual Flow Pipeline                |

| 6  | iCFl | P: Load  | Latency Tolerance for In-order Processors 134   |

|    |      | 5.7.6    | Baseline Micro-architecture Sensitivity         |

|    |      | 5.7.5    | Issue Queue and Physical Register File Capacity |

|    |      | 5.7.4    | Issue Queue Capacity                            |

|    |      | 5.7.3    | Slice Buffer Capacity                           |

|    |      | 5.7.2    | CSB Root Table Capacity                         |

|    |      | 5.7.1    | Load and Store Queue Capacity                   |

|    | 5.7  | Sensiti  | vity Analysis                                   |

|    |      | 5.6.2    | Evaluation                                      |

|    |      | 5.6.1    | Design                                          |

|    | 5.6  | Why N    | Not a Transactional Data Cache?                 |

| B | Ene | nergy Model Sensitivity Analysis |     |  |  |  |  |

|---|-----|----------------------------------|-----|--|--|--|--|

|   | B.1 | Dynamic Energy Conversion Factor | 156 |  |  |  |  |

|   | B.2 | Static Energy Conversion Factor  | 157 |  |  |  |  |

|   | B.3 | Static vs. Dynamic Split         | 158 |  |  |  |  |

# **List of Tables**

| 3.1 | CSB Run-bit Rules                                                     | 66  |

|-----|-----------------------------------------------------------------------|-----|

| 4.1 | Antidote Bit-vectors: Miss Pruning                                    | 77  |

| 4.2 | Antidote Bit-vectors: Join Pruning                                    | 82  |

| 5.1 | Simulated processor configurations                                    | 91  |

| 5.2 | Benchmark characterization                                            | 94  |

| 5.3 | Area Overheads (mm²)                                                  | 98  |

| 5.4 | Comparison and contrast of out-of-order load latency tolerant designs | 116 |

| 5.5 | Area and energy costs for age and poison tracking in BOLT+TD\$        | 120 |

| 5.6 | Area Overheads (mm $^2$ )                                             | 121 |

| 6.1 | Comparison and contrast of in-order load latency tolerant designs     | 144 |

# **List of Figures**

| 1.1  | Clock frequency performance and $ED^2$                                     | 3  |

|------|----------------------------------------------------------------------------|----|

| 1.2  | Example Cache Hierarchy                                                    | 4  |

| 1.3  | Performance and $ED^2$ comparison: CFP, BOLT                               | 8  |

| 2.1  | Performance Impact of Load Latency                                         | 13 |

| 2.2  | Energy scaling of the issue queue. The dashed line indicates designs       |    |

|      | where 1-cycle wakeup/select requires increasing voltage or decreasing      |    |

|      | clock frequency                                                            | 15 |

| 2.3  | Performance scaling of the issue queue                                     | 16 |

| 2.4  | Slowdowns from 2-cycle wakeup/select                                       | 17 |

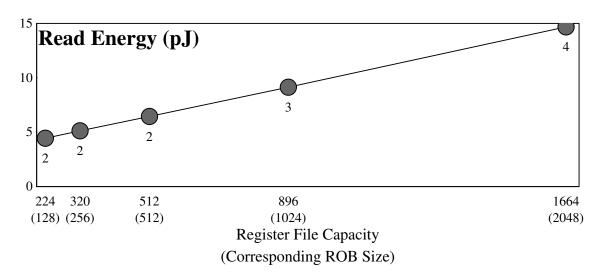

| 2.5  | Energy and latency scaling of the register file. Numeric labels indicate   |    |

|      | access time in 3.2 GHz clock cycles. The x-axis is labeled with both       |    |

|      | the register file size, and the corresponding Reorder Buffer (ROB) size in |    |

|      | parenthesis                                                                | 19 |

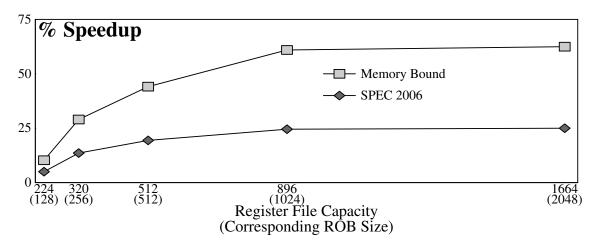

| 2.6  | Performance impact of register file                                        | 20 |

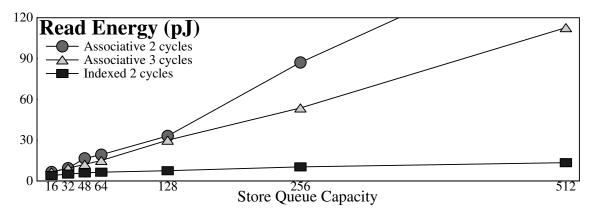

| 2.7  | Energy scaling of the store queue                                          | 22 |

| 2.8  | Performance impact of store queue                                          | 23 |

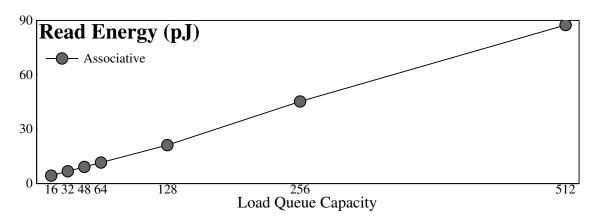

| 2.9  | Energy scaling of the load queue                                           | 24 |

| 2.10 | Performance impact of store queue                                          | 24 |

| 2.11 | Execution Example: Runahead Execution                                      | 27 |

| 2.12 | Execution Example: WIB                                                     | 31 |

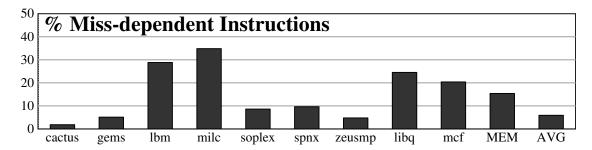

| 2.13 | Percentage of instructions which are miss-dependent                        | 38 |

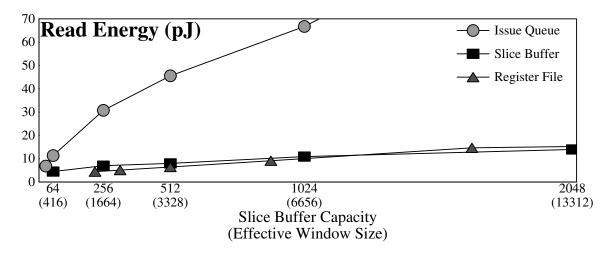

| 2.14 | Scalability of a slice buffer                                              | 38  |

|------|----------------------------------------------------------------------------|-----|

| 2.15 | Example: SVW and SQIP                                                      | 41  |

| 2.16 | Energy scaling of the load queue with SVW                                  | 43  |

| 2.17 | Energy scaling of the store queue with SQIP                                | 44  |

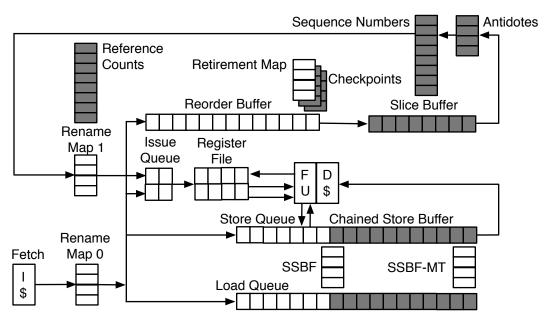

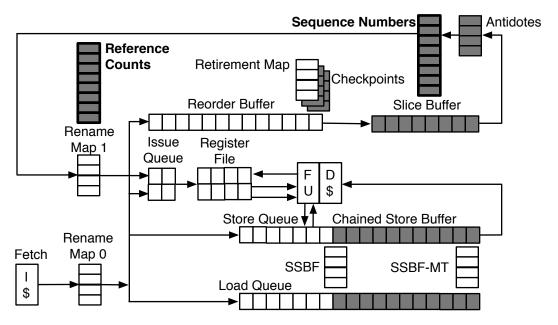

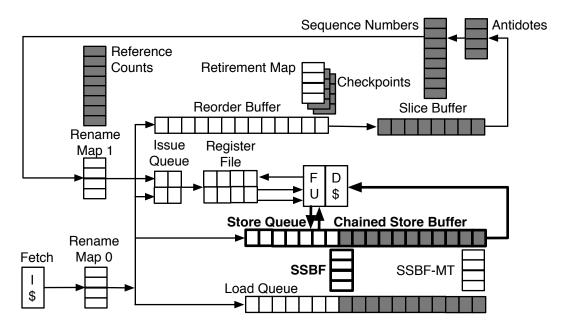

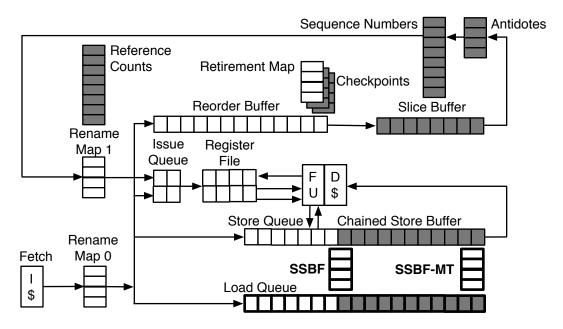

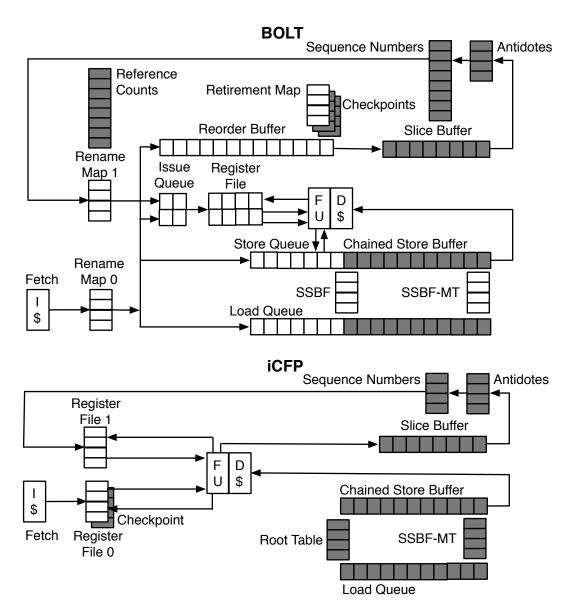

| 3.1  | Structural diagram of BOLT. BOLT-specific structures are shaded grey       | 47  |

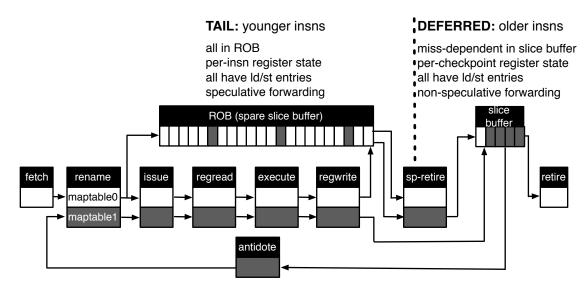

| 3.2  | BOLT Pipeline                                                              | 48  |

| 3.3  | Structural diagram of BOLT with register management related structures     |     |

|      | highlighted                                                                | 52  |

| 3.4  | ROB-style Register Management as Reference Counting                        | 53  |

| 3.5  | Slice Live-out Destination Registers                                       | 56  |

| 3.6  | Structural diagram of BOLT with store management related structures        |     |

|      | highlighted                                                                | 59  |

| 3.7  | Chained Store Buffer                                                       | 61  |

| 3.8  | CSB Search                                                                 | 62  |

| 3.9  | Structural diagram of BOLT with load verification related structures high- |     |

|      | lighted                                                                    | 67  |

| 3.10 | Circular Dependence in a Checkpoint                                        | 72  |

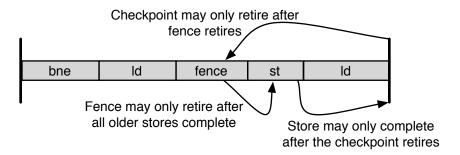

| 3.11 | DSC/SDR                                                                    | 74  |

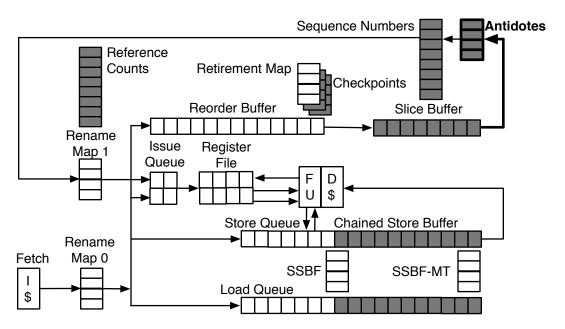

| 4.1  | Structural diagram of BOLT with the antidote bit-vector highlighted        | 77  |

| 4.2  | Code Example: Parallel Loads                                               | 80  |

| 4.3  | Execution Example: Parallel Loads                                          | 81  |

| 4.4  | Antidote Propagation and Pruning                                           | 83  |

| 4.5  | Code Example: Serial Loads                                                 | 84  |

| 4.6  | Execution Example: Pointer Chasing                                         | 85  |

| 4.7  | Code Example: Benign Indirection                                           | 86  |

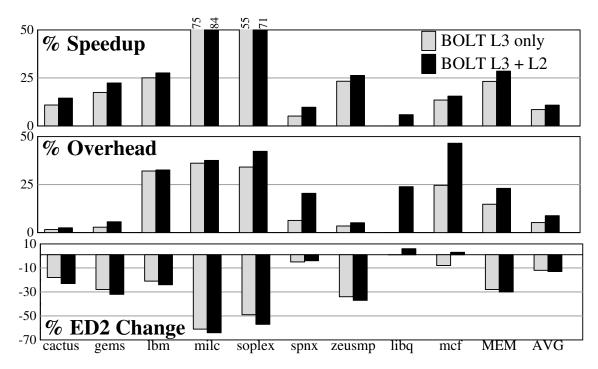

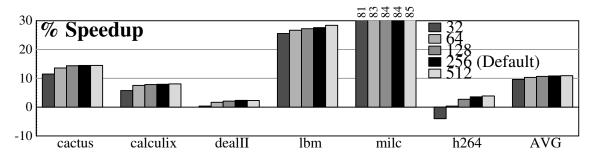

| 5.1  | Applying BOLT to L3 misses only or to L2 and L3 misses                     | 99  |

| 5.2  | BOLT vs. DVFS                                                              | 101 |

| 5.3  | Performance of BOLT and Baseline at various clock frequencies           | 102 |

|------|-------------------------------------------------------------------------|-----|

| 5.4  | Applying Runahead to L3 misses only or to L2 and L3 misses with and     |     |

|      | without pruning                                                         | 103 |

| 5.5  | Applying CFP's load latency tolerance to L3 misses only or to L2 and L3 |     |

|      | misses                                                                  | 106 |

| 5.6  | Comparison of CFP and BOLT register substrate                           | 108 |

| 5.7  | BOLT with three different load and store queue designs                  | 110 |

| 5.8  | Impact of BOLT's pruning algorithms                                     | 111 |

| 5.9  | Runahead, CFP, and BOLT                                                 | 113 |

| 5.10 | Performance on Non-memory-Bound Benchmarks                              | 114 |

| 5.11 | BOLT+TD\$ vs. BOLT                                                      | 122 |

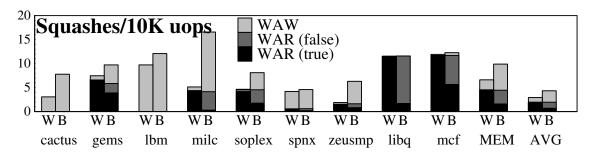

| 5.12 | BOLT+TD\$ squashes per 10,000 $\mu$ ops                                 | 123 |

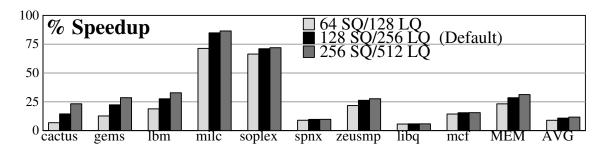

| 5.13 | Sensitivity to load and store queue sizes                               | 125 |

| 5.14 | Sensitivity to CSB's root table size                                    | 126 |

| 5.15 | Load hop histograms                                                     | 127 |

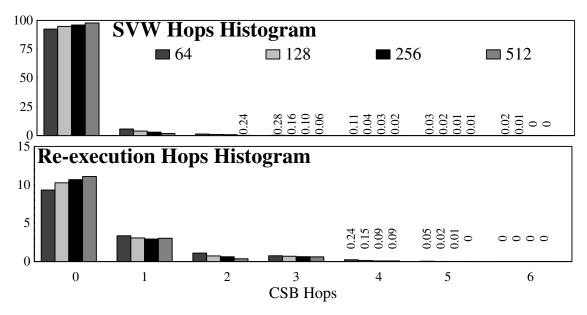

| 5.16 | Sensitivity to slice buffer size                                        | 128 |

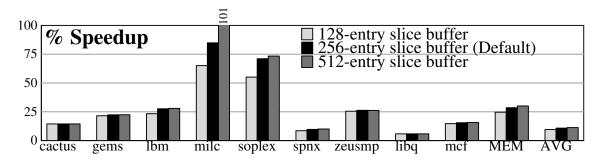

| 5.17 | Sensitivity to issue queue size                                         | 129 |

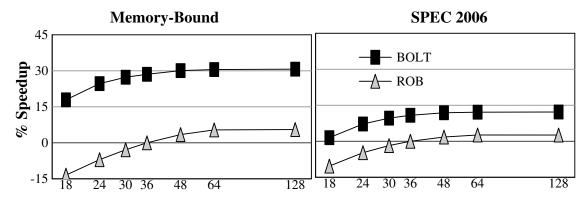

| 5.18 | Sensitivity to ROB/IQ size                                              | 131 |

| 6.1  | BOLT vs iCFP                                                            | 136 |

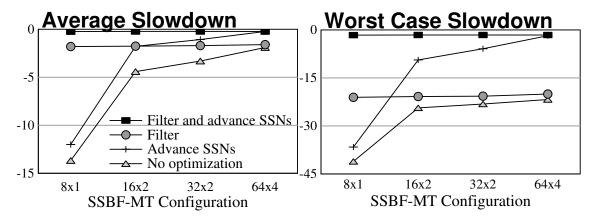

| A.1  | Performance Impact of SVW-MT                                            | 152 |

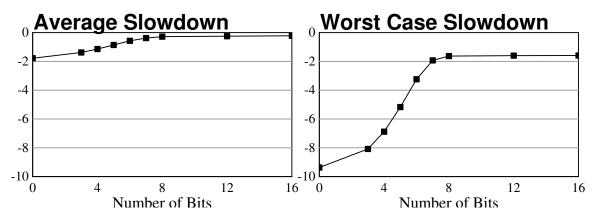

| A.2  | Impact of number of bits used for SVW-MT filtering                      | 154 |

| B.1  | Comparison of dynamic energy model parameter $\delta$                   | 157 |

| B.2  | Comparison of static energy model parameter $\sigma$                    | 157 |

| B.3  | Sensitivity of energy model to static/dynamic split                     | 158 |

# **Chapter 1**

# Introduction

Historically, efforts to extract single-thread performance at almost any cost have been a significant theme in computer architecture. Starting around 2005, this trend changed as energy became a primary concern in a wide range of domains—from embedded devices in which battery life is critical to large server rooms where power supply and cooling costs dominate budgets.

The promotion of energy to a first-order design constraint has slowed single-thread performance growth. One way in which this has happened is by slowing the scaling of clock frequency. Increasing clock frequency increases performance at most linearly. In a limited range it can be done by increasing power linearly as well. Increasing clock frequency in a broader range requires increasing the voltage as well, which leads to a quadratic increase in energy consumption. The 1980s and 1990s *modus operandi* of obtaining performance by increasing clock frequency is not suited to modern energy-constrained designs. Improving performance by increasing instruction level parallelism (ILP)—executing more instructions in a single clock cycle—is also constrained by energy. Techniques that increase ILP typically require increasing superscalar width, or making pipeline structures larger, or both. Both of these increase energy consumption but increase performance sublinearly.

The need for more energy-efficient performance has led to the proliferation of multi-core designs. Multiple independent cores can deliver high performance if programs are written to take advantage of them—explicitly multi-threaded, so that threads can run on different cores. The energy efficiency of multi-core designs comes from avoiding the quadratic costs associated with many aspects of single-thread performance. Four structures of size N consume less energy than one structure of size 4N. Similarly, four structures with one port each consume less energy than one structure with four ports, and four cores operating at 1GHz consume less energy than one core operating at 4GHz.

Future multi-cores are likely to be heterogeneous and will include a small number of large high-performance cores (*i.e.*, superscalar, out-of-order cores similar to Intel's Core i7) and a large number of small simple cores (*i.e.*, scalar, in-order similar to Intel's Atom). The simple cores will execute parallel regions of code, while the large cores will execute serial regions. One aspect of exploiting multi-cores is parallelizing important applications. However, an equally important aspect is single-thread performance of both the small and large cores. The large cores will have to deliver high performance to prevent the serial portions of the workload from dominating performance [29]—this is Amdahl's Law. While the small cores will exploit parallelism where it exists, their individual performance will be important because parallelism is not perfectly elastic—many applications will not scale to arbitrarily large numbers of threads. Because energy considerations will limit the number of cores which may be active at any given time, the performance techniques used in both the high-performance and simple cores must be energy efficient.

# 1.1 DVFS: Accelerating Computation-Bound Programs

One simple and common technique for increasing the performance of both out-of-order and in-order cores is Dynamic Voltage and Frequency Scaling (DVFS), also known as "TurboBoost" [1]. When single-thread performance is needed on a given core, the voltage

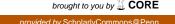

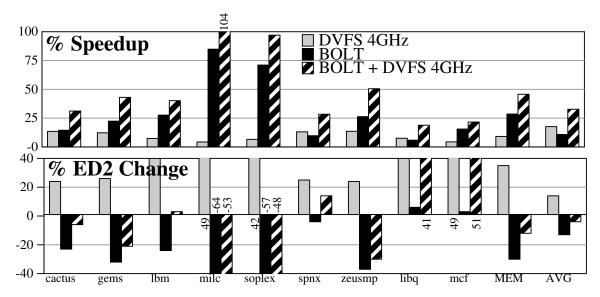

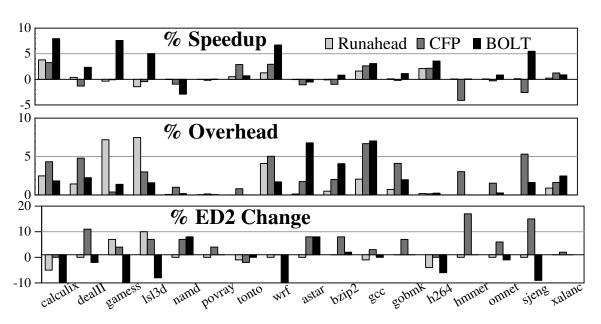

Figure 1.1: Top: Performance impact of using DVFS to increase clock frequency from 3.2 GHz to 4.0 GHz on a simulated design similar to Core i7. Bottom: Energy efficiency as measured by percent change in Energy  $\times$  Delay<sup>2</sup>.

and clock frequency of that core are increased. DVFS increases the energy consumption of the core quadratically, so it cannot be applied to all cores at once, and it most likely requires other cores to be powered down in order to meet the power budget. This quadratic increase in energy consumption corresponds to a linear increase in performance in the ideal case, when a program experiences no cache misses and its performance is constrained by in-core computation. It corresponds to almost no increase in the worst case, when a program misses the cache frequently and its performance is constrained by latencies outside the core.

The top graph in Figure 1.1 shows the performance impact of a 25% increase in clock frequency on a simulated configuration similar to Core i7. For more details about the simulated configuration, benchmarks used, and simulation methodology, see Chapter 5. In this graph, the benchmarks on the right (namd, hmmer, povray) obtain the ideal 25% speedup. Under these ideal conditions, DVFS keeps Energy × Delay<sup>2</sup> (ED<sup>2</sup>) constant, making ED<sup>2</sup> a useful metric for energy efficiency [47]. The bottom graph of Figure 1.1 shows the percent change in ED<sup>2</sup> corresponding to the speedups in the top graph. While

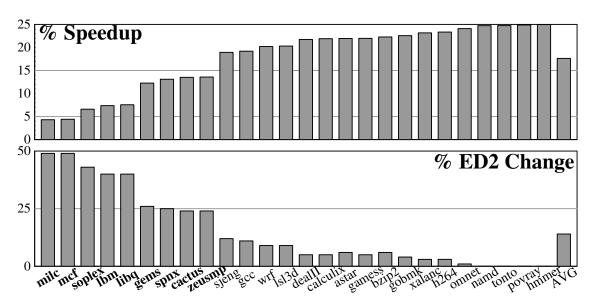

Figure 1.2: An example cache hierarchy for a hypothetical future heterogenous multi-core chip.

the benchmarks on the right side of the graph obtain ideal speedups, other benchmarks do not. In fact, the left-most benchmarks (*mcf*, *milc*, *soplex*, etc.) on the graph obtain little speedup. Correspondingly, these benchmarks have significant increases in ED<sup>2</sup>—almost 50%—indicating that their performance gains are highly energy *inefficient*. The problem with these programs is that they are memory-bound—their performance is dominated by misses to memory or to the last level cache, which are not in the core's clock domain and are not affected by DVFS.

# **1.2** Load Latency Tolerance:

### **Accelerating Memory-bound Programs**

Figure 1.2 shows an example cache hierarchy for a (hypothetical) heterogenous multicore. The cache hierarchy itself is modeled on the cache hierarchy of current 4-core Core i7s, but some of the Core i7s have been replaced with in-order Atom cores. Accesses which hit the first level (L1) cache incur no latency penalty, while those which miss incur latency penalties ranging from 10 cycles (hitting the L2) to 250 cycles (missing all the way to memory). A program is "memory-bound" when its performance is dominated by long-latency memory accesses, typically loads. When a long-latency load occurs, a processor may be able to execute a few independent instructions, but its critical execution resources—physical registers and issue queue entries for out-of-order; pipeline latches

for in-order—quickly fill and executions halts. Latencies that are long enough to pose significant performance issues can be incurred not only by accesses which go all the way to main memory, but also by sufficiently large numbers of accesses which are serviced by the L3 cache. For an in-order core, a program may be memory-bound due to a sufficiently large number of L1 misses, even if they hit in the L2.

Increasing the core's clock frequency does little to help memory-bound programs. Only the first two levels of cache (shown in light grey) operate on the same clock as the core. The L3 cache and main memory, are in different clock domains. Accesses handled at these levels take the same amount of time no matter what the core's clock frequency is. Increasing the clock frequency however, makes these accesses take relatively more clock cycles, meaning that the core consumes more energy while waiting for the data.

Previous work [44, 58, 60, 76] introduced the technique of *load latency tolerance*—long-latency misses and their dependents temporarily release their resources, wait on the side, then re-execute after the miss returns. Load latency tolerant processors improve the performance of memory-bound programs by allowing the pipeline to continue to execute younger instructions while waiting for the long-latency miss to return. However, previous latency-tolerant processor designs are not energy-efficient. They used too many additional structures and deferred and re-executed too many miss-dependent instructions to justify their performance gains.

# 1.3 Energy Efficient Load Latency Tolerance: BOLT and iCFP

To achieve industry adoption, a load latency tolerant design must be energy efficient both statically—it must re-use existing structures when possible and ensure that new structures impose little energy overhead—and dynamically—it must minimize the energy overhead

introduced by re-executing instructions. This dissertation describes BOLT (Better Outof-order Latency Tolerance) [35] and iCFP (In-order Continual Flow Pipeline) [31] respectively out-of-order and in-order load latency tolerant designs which achieve energy

efficiency. BOLT and iCFP implement the re-execution of miss-dependent instructions

as an alternative use of multi-threading hardware, maximizing re-use of existing structures. They avoid associative structures for load and store management, favoring simple,

low-overhead indexed structures. Additionally, they employ simple pruning techniques to

minimize the re-execution overheads introduced by load latency tolerance. This dissertation focuses primarily on BOLT. It includes a detailed description of all mechanisms and

a comparative, simulation-driven performance evaluation. In the interest of completeness,

it also describes iCFP and qualitatively compares it to other in-order load latency tolerant

designs. However, it does not include a simulation-driven performance/energy evaluation

of iCFP<sup>1</sup>.

The novel mechanisms presented in this dissertation include:

- Out-of-order register management for load latency tolerance. This dissertation describes an efficient implementation of a new hybrid physical register management algorithm for out-of-order load latency tolerant processors. This new algorithm combines the benefits of conventional register management for the youngest in-flight instructions with the benefits of aggressive register reclamation for the oldest miss-dependent instructions. This register management scheme also allows rerenaming of miss-dependent instructions to be framed as an alternative use of existing multi-threading hardware.

- In-order register management for load latency tolerance. This dissertation describes efficient register management for an in-order load latency tolerant processor. Like the out-of-order design, the in-order design frames re-execution of miss-dependent instructions as an alternative use for existing multi-threading support.

<sup>&</sup>lt;sup>1</sup>Simulated performance results for iCFP are available in previously published work [31], however, that work uses a different ISA, simulation environment, baseline configuration, and set of benchmarks than the rest of this dissertation.

- Pruning mechanisms for load latency tolerance. This dissertation describes pruning mechanisms which reduce the number of instructions requiring re-execution.

These mechanisms address two different forms of inefficiency—avoiding unnecessary re-execution and avoiding applying load latency tolerance to "pointer chasing" code, where it is ineffective.

- Chained Store Buffer. This dissertation describes a chained store buffer—a novel scalable, searchable store buffer design. Scalable search is obtained by overlaying an address-indexed hash-table on top of an indexed store buffer, allowing loads to search using iterative indexed access.

- **SVW-MT.** This dissertation describes SVW-MT—the inter-thread verification aspects of SVW—and two optimizations needed to make it work efficiently.

- Decoupled Store Completion/Silent Deterministic Replay. This dissertation describes Silent Deterministic Replay (SDR), a technique which permits non-speculative retirement of instructions in between checkpoints in a speculative retirement setting. SDR enables Decoupled Store Completion (DSC), the ability to non-speculatively complete stores to the data cache before the checkpoint they reside in is completed.

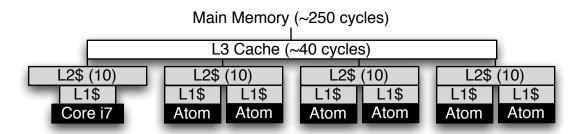

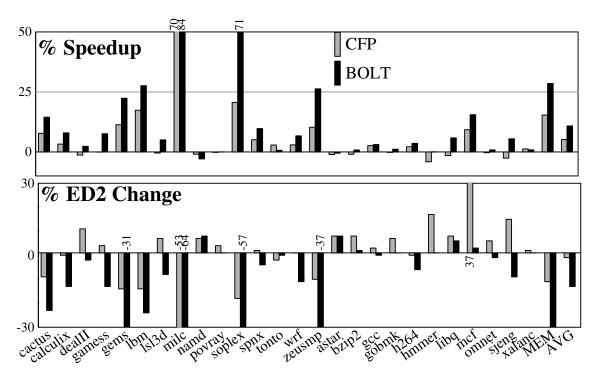

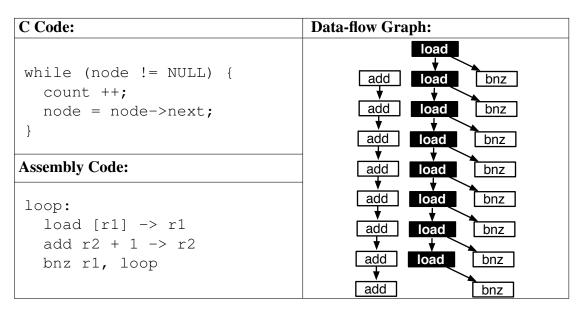

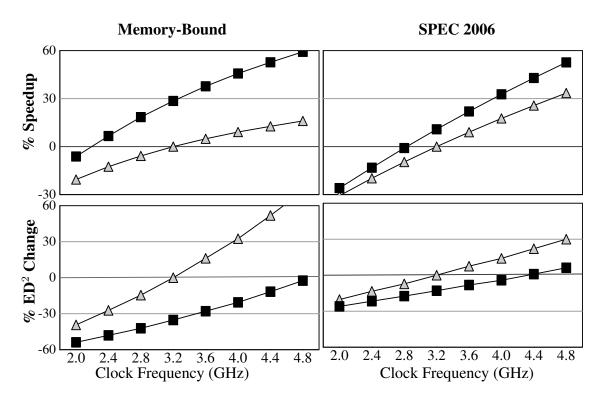

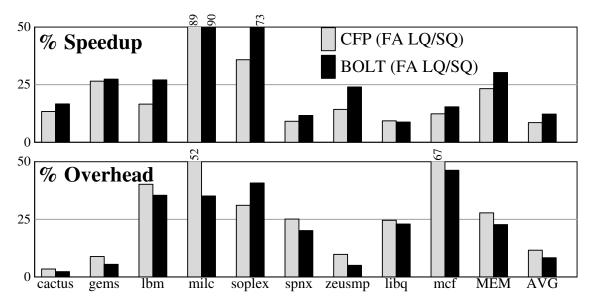

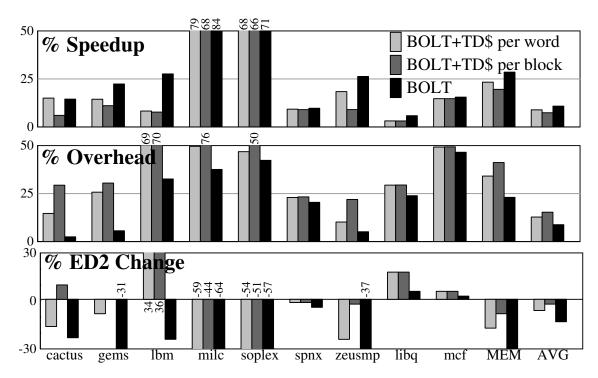

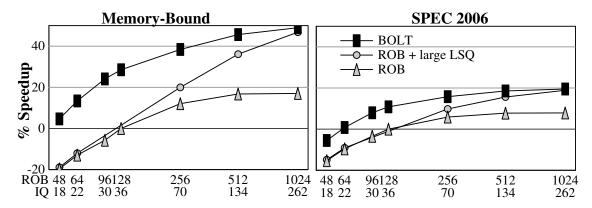

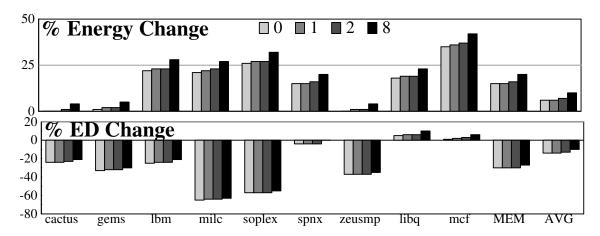

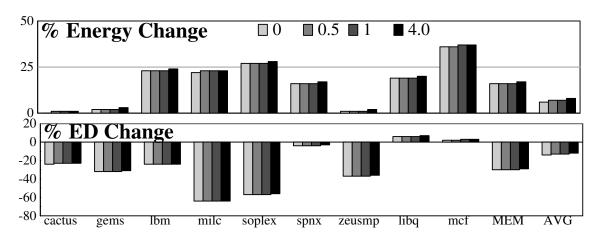

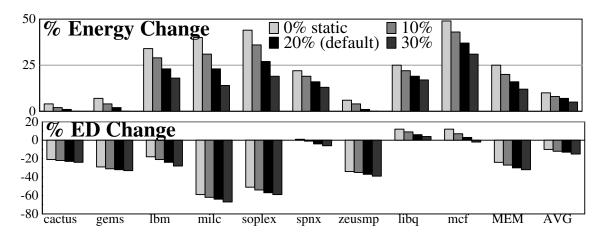

Figure 1.3 highlights the results presented in this dissertation. It compares Continual Flow Pipelines [76], the prior state-of-the-art out-of-order load latency tolerant design, to BOLT in terms of performance (top, higher is better) and energy efficiency (bottom, lower is better). A more detailed comparison of the two micro-architectures is presented in Section 5.4. These results show three significant advantages for BOLT:

• **Performance.** BOLT out-performs CFP by a significant amount. The difference here is most noticeable in the average across the memory-bound subset of the SPEC 2006 benchmarks where BOLT's performance gains are almost *twice* those CFP (29% vs 15%).

Figure 1.3: Top: The performance improvements of Continual Flow Pipelining (prior state-of-the-art load latency tolerant design), and BOLT. Bottom: The corresponding percent change in  $ED^2$ .

- Energy efficiency. BOLT has significantly better energy efficiency (lower ED<sup>2</sup>) than CFP. While CFP averages only 1% ED<sup>2</sup> improvement overall and 11% on the memory-bound subset of SPEC, BOLT averages 13% overall and 30% on the memory-bound programs.

- **Performance and energy efficiency robustness.** BOLT more closely adheres to the architectural "Hippocratic Oath." CFP suffers slowdowns of more than 1% on five programs, compared to one for BOLT. In terms of energy efficiency, CFP increases (harms) ED<sup>2</sup> by more than 1% on 16 programs—more than half—including four programs which it harms by more than 10%. By contrast, BOLT only increases ED<sup>2</sup> by more than 1% on five programs and its worst case ED<sup>2</sup> increase is 8%.

### 1.4 Contributions

The main contributions of this dissertation are:

- Similarities of in-order and out-of-order load latency tolerance. This dissertation shows that both in-order and out-of-order processors can tolerate load latency using almost identical mechanisms.

- Framing re-execution as multi-threading. This dissertation shows that the instructions re-executed by load latency tolerant designs behave similarly to a thread.

BOLT and iCFP re-use existing multi-threading support for this re-execution.

- Hybrid register management in out-of-order processors. This dissertation shows

how different register management schemes may be hybridized in an out-of-order

processor using reference counting. In BOLT, this hybridization is used to attach a

register-efficient post-processing step to a conventional out-of-order processor.

- Efficient, scalable load/store queue design. This dissertation shows how SQIP, CSB, DSC/SDR, SVW, and SVW-MT can be combined into an efficient, scalable load/store queue design which is well-suited to load latency tolerance in an out-of-order processor. An in-order latency processor does not need SQIP and SVW, but can use the other mechanisms.

- **Deferral and re-execution pruning mechnaisms.** This dissertation shows that re-execution overheads can be a significant energy in-efficiency in a load latency tolerant design, and proposes mechanisms to address the inefficiency while still maintaining performance.

This dissertation presents a simulation-driven performance and energy evaluation of BOLT—the out-of-order design—including the impact of the register substrate, load and store structures, and the pruning mechanisms. iCFP is qualitatively compared to other in-order load latency tolerance designs. A quantitative evaluation of iCFP's performance may be found in previously published results [31].

# 1.5 Previously Published Work

Aspects of this dissertation have been published already. These publications include:

- iCFP: Tolerating All-Level Cache Misses in In-Order Processors. This 2009 publication appeared in the 15<sup>th</sup> International Symposium on High Performance Computer Architecture [31]. It describes the in-order register state management in iCFP, as well as the chained store buffer. iCFP also appeared in MICRO's Top-Picks [32]. That manuscript also included a qualitative comparison of iCFP and Sun's Rock processor.

- DSC/SDR: Enabling Scalable Data Memory for CPR/CFP Processors. This 2009 publication appeared in the 36<sup>th</sup> International Symposium on Computer Architecture [34]. It describes Decoupled Store Completion and Silent Deterministic Replay.

- BOLT: Energy-Efficient Out-of-Order Latency-Tolerant Execution. This 2010 publication appeared in the 16<sup>th</sup> International Symposium on High Performance Computer Architecture [35]. It describes BOLT— the out-of-order load latency tolerance design—including its register management and pruning mechanisms.

This dissertation differs from the previously published work in the following ways:

- BOLT is evaluated more thoroughly.

- SVW-MT is explained in detail, including optimizations which make it work efficiently.

- The "pointer chasing" pruning mechanism presented in this dissertation (in Section 4.3) is different from the one presented in the BOLT paper.

# 1.6 Document Organization

The remainder of this dissertation is organized as follows. Chapter 2 presents background on previously proposed out-of-order load latency tolerance designs. Chapter 3 describes the BOLT micro-architecture. Chapter 4 describes the pruning mechanisms. Chapter 5 analyses the performance and energy efficiency of BOLT and compares it to other designs. Chapter 6 describes iCFP and other in-order load latency tolerance designs. Chapter 7 concludes. Appendix A provides an evaluation of SVW-MT. Appendix B examines the sensitivity of the energy model to the assumptions it makes.

# Chapter 2

# **Background**

Long latency loads pose a significant performance problem, as the processor must stall for many cycles while waiting for data. This problem can be mitigated by a processor's ability to execute independent instructions while waiting for a long latency miss to return. Gains can come from one of two types of parallelism. Memory-level parallelism (MLP) occurs when the processor overlaps the memory latency of two or more independent loads. Instruction-level parallelism (ILP) occurs when the processor executes independent instructions under the miss, preserves that work, and does not revisit those instructions after the miss returns. Both forms of parallelism are limited by the processor's ability to re-order instructions and find independent operations. Alternatively, the processor may decrease its voltage and clock frequency while a long latency miss is pending to save energy [45].

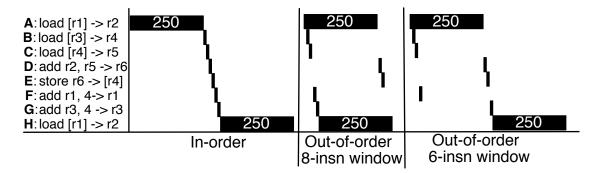

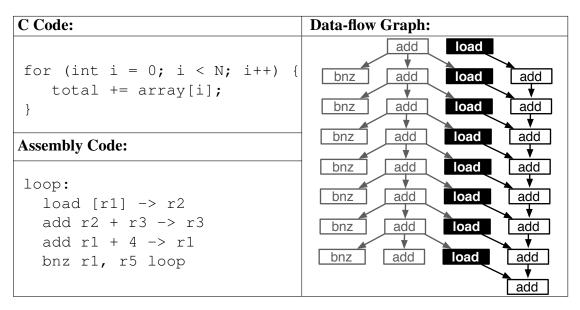

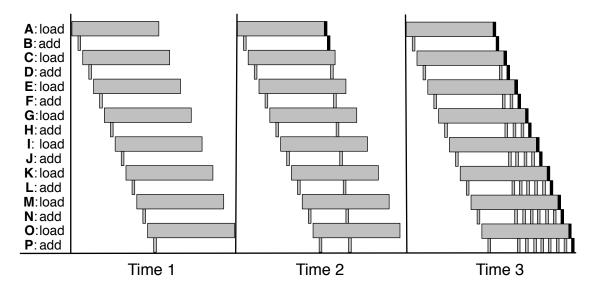

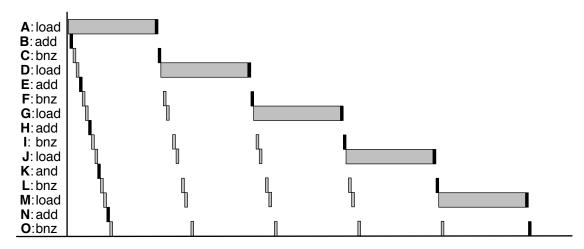

An in-order processor has little to no ability to re-order instructions, and typically can not extract ILP or MLP under long latency cache misses. The left side of Figure 2.1 shows an example of how long latency operations inhibit performance in the in-order case. This example depicts a sequence of 8 instructions, A–H, shown on the far left. The diagram shows how each of these instructions executes in time. Loads A and H miss the last level cache, resulting in long latencies, as indicated by the wide bars in their rows. The other instructions (B–G) each have short latency and execute quickly. As this is an in-order processor, no re-ordering is performed, the misses serialize, and their latencies add. The

Figure 2.1: Execution behavior over time. Loads A and H miss the caches. Left: An in-order processor serializes all instructions. The misses dominate performance. Middle: An out-of-order processor can execute independent operations while waiting for A's miss to return. It may be able to overlap A's miss with H's, exposing MLP. Right: If the out-of-order processor's window is too small, it may not be able to overlap A and H, resulting in performance closer to the in-order case.

miss latencies dominate performance, accounting for 99% of execution time.

In many real processors, sequential accesses such as those in Figure 2.1 are often detected and prefetched—a dedicated hardware structure monitors cache accesses, detects simple patterns, and initiates misses before any load attempts to read the data [17, 18, 39, 40, 70, 71]. Prefetching improves performance, but is limited by the types of patterns it can discern. Many of the examples in this dissertation ignore prefetching to facilitate simple and clear examples. However, the simulated results in Chapter 5 include stream prefetching all configurations.

The middle of Figure 2.1 shows the performance gains that an out-of-order processor can achieve in this same situation. Here, the processor can execute independent instructions B, C, F, G, and H while it waits for A's miss to return. The most significant performance gain here comes from MLP—the out-of-order processor overlaps H's miss with A's, meaning their latencies no longer add. The processor also obtains some performance gains from ILP—the execution of B,C, F, and G—however, in this example, those gains are a small component of the overall performance improvement.

While an out-of-order processor is able to perform some re-ordering of independent operations to improve performance, it has a limited *window*—the range of instructions in which the processor can seek re-orderings—in which is able to do so. The size of this

window determines how much ILP and MLP an out-of-order processor can extract under a miss. The out-of-order processor in the middle of Figure 2.1 has a window of eight instructions, meaning it can examine all instructions from A to H to find independent instructions. By contrast, if the out-of-order window were only six instructions, as pictured on the right side of Figure 2.1, then the processor could not execute G until A finished and exited the window. The important consequence of this smaller window is that H cannot execute until after A exits the window, again serializing the misses and causing their latencies to add.

## 2.1 Non-scalability of the Out-of-order Window

While a large out-of-order window is desirable for performance, it is neither practical nor energy efficient. The out-of-order window is restricted by four non-scalable structures: the issue queue, the physical register file, the load queue, and the store queue. In modern, conventional out-of-order processors, these structures are sized to tolerate moderate latencies of about 20–30 cycles. Latencies of this magnitude correspond to last-level cache hits, serially dependent loads hitting the L2 cache, or the longest floating point operations. To tolerate the long latency of last-level cache misses—250 cycles—the capacities of these structures would have to increase by 4–10×. Such increases would drastically increase the access latency and energy consumption of these structures.

### 2.1.1 Issue Queue

The issue queue holds all un-executed instructions and schedules instructions for execution as their inputs become available. Scheduling consists of two parts—select selects N instructions for execution from among the instructions whose inputs are available; wakeup updates the ready bits of all instructions that depend on the instructions just selected. Select is usually implemented using priority encoders. Wakeup is implemented using a content associative memory (CAM) that holds the input physical register names of all

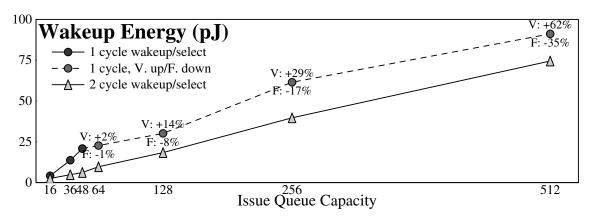

Figure 2.2: Energy scaling of the issue queue. The dashed line indicates designs where 1-cycle wakeup/select requires increasing voltage or decreasing clock frequency.

un-executed instructions. The issue queue in the Intel Core i7 processor has 36 entries, limiting the out-of-order window to 36 un-executed instructions.

**Physical scalability.** One difficulty with scaling the issue queue arises from the fact that its latency is critical. Scheduling that takes multiple clock cycles, prevents dependent instructions from executing in consecutive cycles. Essentially, the minimum execution latency in the processor becomes that of the scheduler's *wakeup/select* loop. The complexity (and therefore latency) of both wakeup and select increases as the size of the issue queue increases [56].

Figure 2.2 quantifies the scalability of issue queue wakeup. The graph plots the energy required for a single wakeup operation for different issue queue sizes. The data in this graph is derived from a modified version of CACTI 4.1 [79] assuming a 4-wide out-of-order processor. We model an *I*-entry issue queue as 2 *I*-word 8-bit CAMs, each with four write ports and 4 associative match ports—each 8-bit entry corresponds to one 8-bit physical register tag. Two CAMs are modeled as each instruction may have two register inputs. CACTI cannot model the select logic, so its latency is estimated from the base-line processor's issue queue. CACTI reports the baseline issue queue (36-entry) has a minimum latency of 284 ps. CACTI reports a design with a 292 ps latency which uses approximately two-thirds as much energy and about one-half the area of the minimum latency design. Assuming that a 3.2GHz Core i7 uses the second design, 20.5 ps remain

Figure 2.3: Performance scaling of the issue queue for both 1- and 2-cycle wakeup/select. All other window structures are infinite.

for the select logic. The data in the graph uses this estimation—20.5 ps—for all points and does not model the longer select latencies of larger issue queues.

The line marked by dark circles in Figure 2.2 plots the energy requirements for different issue queues sizes when the wakeup/select loop is constrained to a single cycle. For issue queue sizes of 64-entries and larger, CACTI is unable to produce any configuration which permits single-cycle wakeup/select at the baseline clock frequency and voltage. Issue queue designs of these sizes with single-cycle wakeup/select require either increasing voltage or decreasing clock frequency (or some of both). These designs are indicated with slightly lighter circles and a dashed line. Each point has the voltage increase/frequency decrease noted above/below it. The energy values plotted do not account for the voltage change *i.e.*, they are the energy required if frequency were changed. The line marked with light triangles shows the energy consumption when wakeup/select is relaxed to two cycles.

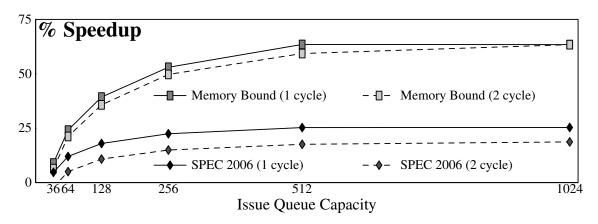

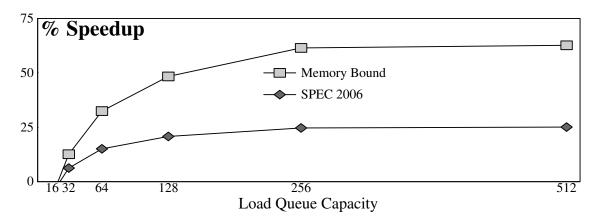

**Performance impact.** Figure 2.3 shows the geometric mean speedup over the base-line Core i7 configuration of different issue queue sizes and latencies for all of SPEC 2006 (diamonds) and the memory-bound subset (boxes). The solid lines represent single cycle wakeup/select, and the dashed lines represent two cycle wakeup/select. In all configurations, window structures other than the issue queue are made ideally large. This means that even in the configuration with the same size and latency issue queue as the baseline (36-entries, 1-cycle), the idealized window enjoys some speedups due to the benefits of

Figure 2.4: Slowdowns suffered by individual programs from 2-cycle wakeup/select.

the other structures. The clock frequency is un-modified in all experiments.

Maximizing IPC throughput on the memory-bound programs requires a 512-entry issue queue. Such a design requires a 6–7× increase in the per-search energy of the issue queue as well as either 2-cycle wakeup select, a 35% frequency decrease, or a 62% voltage increase. Neither drastically increasing voltage nor decreasing frequency are attractive options. The 2-cycle wakeup/select design is also not attractive [10]. Experiments show that programs suffer *average* performance losses of about 7%. However, the designs with 2-cycle wakeup/select suffer slowdowns *compared to the baseline* for individual benchmarks.

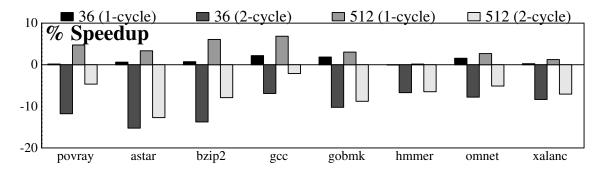

Figure 2.4 shows the impact of 2-cycle wakeup select on individual benchmarks. The graph shows four bars—36-entry/1-cycle, 36-entry/2-cycle, 512-entry/1-cycle, and 512-entry/2-cycle. The benchmarks selected for this graph are those which suffer a slowdown of greater than 2% in the 512-entry/2-cycle configuration. These programs suffer from the latency added to operations which are normally single-cycle. Some of these programs (*e.g.*, *povray*, *gcc*, and *bzip2*) mitigate this cost slightly by having large window, but the longer latency operations are the dominant effect here.

Other approaches. Prior research has attacked the non-scalability of the issue queue in various ways. Cyclone [24] replaces a traditional associative wakeup/select issue queue with a FIFO queue/ An extended rename stage places instructions into this queue according to calculated dataflow height. The Cyclone scheduler is scalable, but cache misses result in costly performance penalties. Forwardflow [27] represents register dependences as

linked lists—the readers of a given register are chained in a list that starts at that register—and implements wakeup by following list pointers. Forwardflow scales the issue queue, but may impact performance for long dependence lists *i.e.*, register values with high fanout.

Other techniques examine modifications to the traditional wakeup/select-based design. One approach exploits the fact that most instructions entering the window need to only wait for one input to become available. Putting such instructions into a CAM which only matches one physical register tag allows for lower latency and energy [23]. Other approaches create a large issue queue from multiple smaller structures [56,63].

Other techniques attack the latency problem of wakeup/select fitting in one cycle, while allowing dependent instructions to issue in consecutive cycles. One approach speculatively wakes up grandchildren (*i.e.*, a dependent instruction's dependent instructions) [77]. This allows wakeup and select to take two cycles, but requires issue queue entries to hold more tags (*i.e.* the parents' inputs) or to speculate one which inputs will arrive last.

### 2.1.2 Physical Register File

Out-of-order processors rename registers—mapping logical register names to a larger set of physical registers—to eliminate false dependences. The physical register file limits the out-of-order window due to the in-order nature of register allocation and freeing. Registers are allocated in-order at the rename stage, in the front-end of the pipeline. As each instruction is renamed, it is allocated a new physical register for its destination, but also notes the previous physical register mapped to the same logical designation. When an instruction retires—exits the pipeline in program order and updates architected state—the processor reclaims the physical register which the instruction overwrites that was noted at rename. The only other way in which physical registers are reclaimed is during misprediction recovery, when the destination registers of squashed instructions are reclaimed.

Figure 2.5: Energy and latency scaling of the register file. Numeric labels indicate access time in 3.2 GHz clock cycles. The x-axis is labeled with both the register file size, and the corresponding Reorder Buffer (ROB) size in parenthesis.

The consequence of this conventional register management scheme is that the total number of register writing instructions between rename and retirement is limited by the size of the physical register file. The physical register file is both latency-critical and high-bandwidth. The latency of the physical register file impacts the number of pipeline stages between issue and execution. Increasing the number of pipeline stages here increases the bypass complexity, scheduler speculation depth and complexity, and the branch misprediction penalty. The register file must also support 2N reads and N writes on an N-wide processor. On a 4-wide out-of-order machine, this means the register file requires 12 ports. This bandwidth requirement may be reduced slightly under the assumption that some instructions will receive inputs from the bypass network rather than the register file and that some instructions will not produce register output values. The combination of these two factors limits the register file to a modest number of entries—in Intel's Core i7, enough to support architected state plus about 128 in-flight instructions.

**Physical scalability.** Figure 2.5 shows the read energy and latency of register files of varying sizes. In CACTI, we model an *R*-register register file as an *R*-word 64-bit RAM with 6 read ports and 3 write ports. Under each register file size label on the x-axis, the

Figure 2.6: Performance impact of register file. Other window structures are infinite. The x-axis is labeled with both the register file size, and the corresponding Reorder Buffer (ROB) size in parenthesis.

corresponding Reorder Buffer (ROB) size is listed in parenthesis. Specifically, this is the ROB size appropriate for the given register file size, assuming 128 architectural registers (64 per-thread with two threads), and that three-quarters of instructions require an output register. The register file access latency in clock cycles is listed under each point. Unlike the other window structures, CACTI does not produce significantly different numbers for the smaller register files with relaxed cycle time constraints.

**Performance impact.** Figure 2.6 shows the performance effects (again, geometric mean speedup over the baseline configuration) of scaling the register file when all other window structures are ideally large. The ROB size corresponding to each register file size is listed for reference, but the ROB is treated as infinite in all simulations. These simulations also assume that the larger sizes have no impact on access latency, and model 2 cycle register reads for all configurations. An 896-entry register file (*i.e.*, one large enough to support a 1024 instruction window) is required to achieve maximum performance. A register file this large requires 3 cycles to access instead of 2, which reduces performance by up to 3%. The access energy for a register file of this size approximately doubles compared to the baseline 224-entry register file.

Other approaches. Prior research has attacked the non-scalability of the physical

register file in various ways. Some approaches, such as *Checkpoint Processing and Recovery* [2], *Cherry* [48], and *Early Register Release* [22] improve register file utilization by freeing registers sooner than in a conventional processor. *Physical Register Inlining* [46] releases physical registers with small values, placing the values directly in the rename map table. Other approaches, such as *Virtual Physical Registers* [50] allocate physical registers only when they are needed by executing instructions. *Ephemeral Registers* [19] combine both late allocation and early release.

Some techniques scale the effective capacity of the register file by allowing certain instructions to share registers with older instructions that produce the same value [25,41, 61,62,75] or by fusing multiple instructions into larger blocks and eliminating register storage for block-interior values [11]. Most of these techniques also amplify the capacity of the issue queue.

#### 2.1.3 Store Queue

Processors must respect data dependences via memory as well as registers. Because cache writes cannot be undone in a conventional processor, a store may not complete to the data cache until after it retires in program order. A load may read the memory location written by an older store which has not yet completed to the data cache. To avoid stalling such loads until the relevant store completes, out-of-order processors allow loads to *forward* values from in-flight stores. To support store-to-load forwarding, out-of-order processors use a store queue that holds the addresses and data values of in-flight stores in program order. When a load executes, it searches the store queue for an older store to the same address. If a match is found, the load uses the value forwarded from the store queue. If not match is found, the load uses the value from the data cache.

Conventional store queues are implemented using content associative memory (CAM), which supports the search functionality required. The CAM is combined with age logic that determines which matching store is the youngest store older than the executing load. As with the issue queue, the use of a CAM prevents the store queue from scaling to large

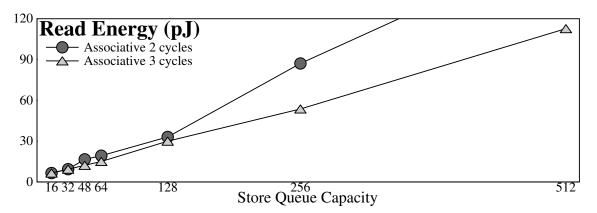

Figure 2.7: Energy scaling of the store queue.

sizes. However, the latency constraints of the store queue are somewhat more relaxed than those of the issue queue. The access latency of the store queue (the CAM plus the age logic) must fit within the data cache access latency, which is typically three or four clock cycles—in this dissertation, we assume a three-cycle data cache. The store queue in a Core i7 processor has 32 entries, limiting the window to 32 stores which have not yet completed to the data cache.

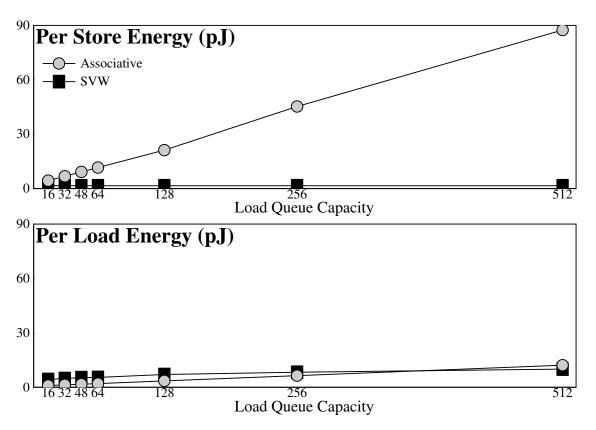

Physical scalability. Figure 2.7 shows the per-read (search) energy reported by CACTI for the CAM portion of the associative store queue. An *S*-entry store queue is modeled as an *S*-word 12-bit CAM with a 104-bit data array, 1 indexed write port, 1 indexed read port, and 1 associative read port. Each 116-bit entry includes a 48-bit physical address—the low-order 12-bits are searched —a 64-bit value, a 3-bit size field, and a valid bit. CACTI does not model age logic. To account for the latency of the age logic across a reasonable range of possibilities, two models are used. In the first model (shown by the top line, marked with circles), the CAM is limited to designs which fit into two clock cycles. This model assumes a full cycle for the age logic. The second model (shown by the middle line, marked with triangles) constrains the designs to three clock cycles. This model assumes zero-latency age logic. If the actual latency for the age logic is between zero and one cycle, then the actual energy curve for the store queue will fall between these two.

<sup>&</sup>lt;sup>1</sup>This allows store queue access in parallel with DTLB access.

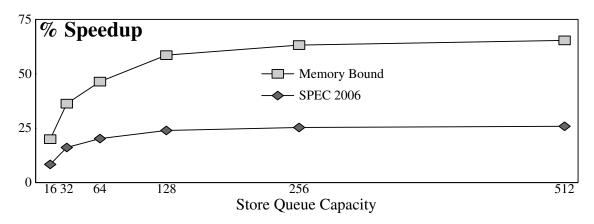

Figure 2.8: Performance impact of the store queue. Other window structures are infinite.

**Performance impact.** Figure 2.8 shows the performance impact of varying the store queue size when the other window structures are infinite. The top line (marked with light grey boxes) shows the geometric mean speedup for the memory-bound programs. The bottom line (marked with dark grey diamonds) shows the geometric mean speedup for all of SPEC. Memory-bound programs need at least a 128-entry store queue to fully utilize a large window. As Figure 2.7 shows, this requires a  $3-5\times$  increase in the per-read energy of the store queue.

Other approaches. Prior research has attacked the scalability of a conventional store queue in various ways. Store Queue Index Prediction (SQIP) [74] replaces the associative store queue with an indexed store queue. SQIP is discussed in detail in Section 2.7.2. Other techniques remove the store queue entirely [75, 78]. Other techniques reduce the number of entries searched in an associative design [7, 57, 73].

# 2.1.4 Load Queue

In many out-of-order processors, store-to-load forwarding is performed speculatively. A load may execute before the forwarding store, causing a *memory ordering violation*. Memory ordering violations can also occur due to stores from other threads, potentially on other cores. When either form of violation occurs, the processor must detect the situation, squash the incorrect load, and re-execute it.

Figure 2.9: Energy scaling of the load queue.

Figure 2.10: Performance impact of the load queue. Other window structures are infinite.

To support memory ordering violation detection, conventional out-of-order processors track the addresses of all in-flight loads in a program-order associative load queue (*i.e.*, a CAM). Executing stores and invalidations due to stores on other processors trigger load queue searches to find any load which may have executed prematurely and read an incorrect value. Unlike the store queue and issue queue, latency is not critical for load queue search.

**Physical scalability.** Figure 2.9 shows the energy scaling of an associative load queue. An *L*-entry load queue is modeled as an *L*-word 48-bit CAM with a 4-bit data array, one read port and one write port. Each entry contains a 48-bit physical address, a 3-bit size field, and a valid bit. As the load queue search latency is not critical, these are modeled with no specific latency constraints. Access latencies range from 2–4 clock cycles.

**Performance impact.** Figure 2.10 shows the performance impact of scaling the load queue when all other window structures are infinitely large. A 256-entry load queue is needed to maximize performance for the memory-bound programs. A load queue this large uses approximately  $5 \times$  as much energy as the baseline 48-entry load queue.

Other approaches. Prior work has attacked the scalability of the load queue primarily by re-executing loads in-order prior to commit [12, 67, 68]. One of these approaches—Store Vulnerability Window—is discussed in detail in Section 2.7.1.

#### 2.1.5 Load Latency Tolerance: Virtually Scaling the Window

The high-level idea of load latency tolerance is to *virtually* scale the issue queue and physical register file. Load latency tolerance designs remove miss-dependent instructions from these key window resources to allow younger instructions to enter the pipeline and execute. When a miss returns, the instructions which depend on it are re-injected into the pipeline—re-acquiring issue queue entries and physical registers—and re-execute.

The remove-and-re-inject technique works well for the issue queue and physical register file, but does not work for the load and store queues. This technique works for the issue queue because the issue queue is simply a scheduling structure and the miss-dependent instructions are known not to be ready. The physical register file, however, contains the register state of the program, so releasing physical registers early removes the instruction-granularity register state which processors typically maintain. Instead, a processor can track register state at a coarser granularity using register checkpoints. For memory state—tracked in the load and store queues—such an exchange is more difficult to make. Replacing instruction-granularity register state with checkpoints works for four reasons. First, the number of registers is small. Second, register values are not vulnerable to actions from other threads and processes. Third, the register checkpoint captures all dependences from the point at which it was taken to younger instructions. Finally, register dependences are explicit, meaning that independent miss-independent inputs can be

captured so that re-execution is decoupled from the main program. Memory state, however, has exactly the opposite behavior of register state in each of those dimensions. First, memory state is large. Second, loads are vulnerable to stores from other threads. Third, a finite-sized snapshot cannot capture all data dependences between stores and younger loads. Finally, store-to-load dependences are only known when the address of the load and communicating store are both known, making it impossible to capture inputs in the presence of loads with unknown addresses.

In this dissertation, we define a *true load latency tolerant design* as one that incorporates scaling for all four window structures (the issue queue, the physical register file, the load queue, and the store queue), and retains miss-independent work completed under a miss, exploiting ILP as well as MLP. Scaling techniques for all four structures must allow them to accommodate a large enough window to avoid dispatch stalls under long latency misses, without decreasing the clock frequency or drastically increasing energy consumption. These techniques may include virtual scaling—removal and re-injection to achieve a larger effective size—or replacement of non-scalable associative structures with scalable indexed structures.

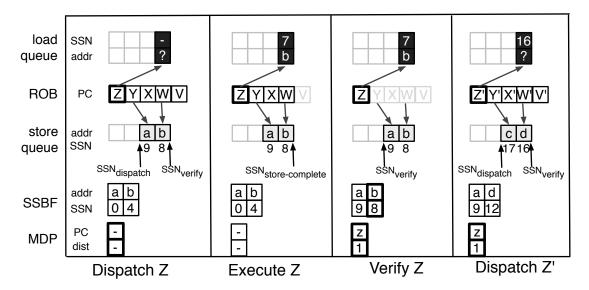

Several prior works make important steps towards improving performance under long-latency cache misses, but not all of them qualify as true load latency tolerant designs—some of these works either only address some aspects of the design, or only obtain part of the benefits of load latency tolerance. Even among those designs that do qualify as true load latency tolerance, some provide the ability to tolerate dependent long latency misses—miss-dependent loads which are themselves long latency misses—while others do not.

Prior load latency tolerance work varies in its terminology. The following discussion of this prior work uses BOLT's terminology for consistency and simplicity.

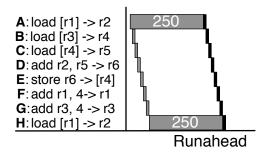

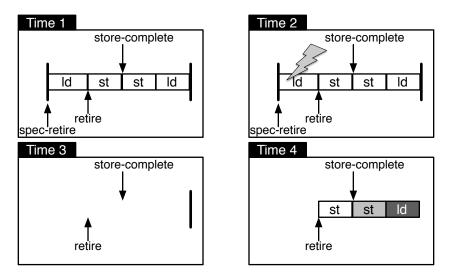

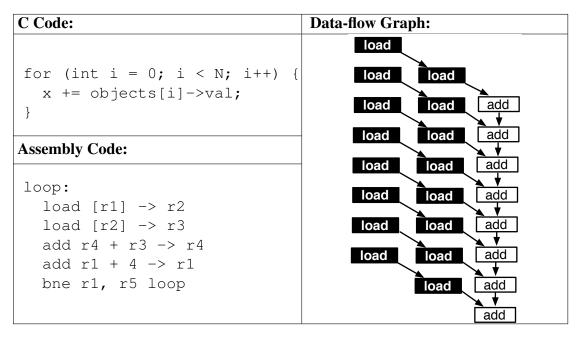

Figure 2.11: Execution of the example code sequence under Runahead Execution. Grey boxes indicate executions in Runahead mode which are discarded. Black boxes indicate actual executions.

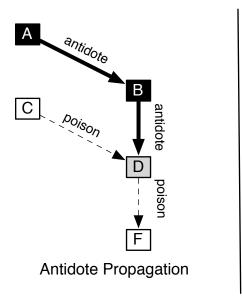

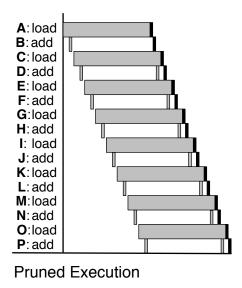

#### 2.2 Runahead Execution

An out-of-order processor uses Runahead Execution [20,54] to expose MLP in the presence of last-level cache misses. When a pending last-level cache miss reaches the head of the re-order buffer, Runahead checkpoints architected register state, and begins Runahead execution mode. In this mode, loads which miss the last level cache undergo a pseudo-execution which produces "poison" rather than an actual output value. This poison is indicated by an extra bit in the destination register which indicates the value is not known. The pseudo-execution of the missing load causes the load to release its issue queue entry and wake up dependent instructions as if it had executed. When dependent instructions read their input values, they ingest poison, pseudo-execute, and propagate poison to their own outputs. Runahead mode retirement processes executed instructions in program order, removes them from the ROB, and frees their physical registers but does not commit them to architected state—specifically, Runahead stores do not write the data cache.

When the miss that triggered the Runahead episode returns, the processor restores the register checkpoint and re-fetches and re-executes all instructions younger than the miss. Re-execution of the instructions that already executed in Runahead mode is accelerated because Runahead execution initiated parallel last-level cache misses and warmed up the caches. Runahead Execution is not a true load latency tolerant design as it discards all miss-independent work after the miss returns and does not exploit ILP under cache misses.

Figure 2.11 shows an example of Runahead execution. When Runahead encounters A's

miss, it checkpoints register state and enters Runahead mode. Runahead mode exposes MLP by executing H's miss. However, it is unable to expose ILP—it discards and reexecutes the independent instructions: B,C, F, and G.

#### 2.2.1 Load and Store Queues

Runahead's approach to virtually scaling the load and store queues hinges on the fact that it discards all instructions from Runahead mode. Since Runahead instructions will be discarded, it is acceptable if load ordering violations are not detected for Runahead loads, so Runahead simply removes loads from the load queue when they exit the ROB. For stores, forwarding is performed in a best-effort fashion via a Runahead cache. When Runahead stores exit the ROB, they write the Runahead cache and release their store queue entries. Younger Runahead loads check the Runahead cache to see if there are any matching stores. When a Runahead episode ends, the forwarding cache is cleared. As stores may age out of the Runahead cache, a proper forwarding may be missed. This possibility is acceptable because all loads and stores re-execute when the Runahead episode ends.

# 2.2.2 Efficiency

If Runahead mode does not expose any MLP, it not only does not help performance, but also wastes energy. To avoid such wastes, Runahead can implement heuristics which predict whether a Runahead episode is likely to expose MLP or not [53]. One heuristic avoids useless periods of Runahead by learning which static loads have historically exposed MLP and which have not. Another heuristic avoids overlapping periods of Runahead by tracking how many instructions were pseudo-retired during Runahead mode, and preventing the processor from re-entering Runahead mode until at least that many instructions have been retired conventionally. These techniques occasionally harm Runahead's performance, but greatly improve its overall energy efficiency (see Section 5.3).

# 2.3 Checkpointed Early Load Retirement and Checkpoint Assisted Value Prediction

Two similar designs: Checkpointed Early Load Retirement (CLEAR) [42] and Checkpoint Assisted Value Prediction (CAVA) [14] use value prediction to tolerate long load latency. When a load misses the last-level cache, a predictor is used to guess the output value. The load then binds this value and dependent instructions execute normally, releasing their issue queue entries.

CLEAR and CAVA both couple value prediction with *speculative retirement* to scale the physical register file. Speculative retirement is not traditional retirement made speculative—instructions are not made globally visible and then pulled back. Instead it is a more resource efficient way of buffering speculative instructions. Specifically, it uses register checkpointing to buffer a large number of instructions without explicitly representing the register output of each instruction. In CLEAR and CAVA, speculative retirement begins when a value-predicted load reaches the head of the ROB. The processor checkpoints architected register state and begins retiring instructions speculatively. Speculatively retired instructions exit the processor and release their physical registers allowing younger instructions to enter behind them. When value-predicted load misses return, the actual output value is compared against the predicted value. If all predictions are correct, then the checkpoint is released, making speculative retirement non-speculative. If any mismatch occurs, then speculation is aborted to the checkpoint. Both CLEAR and CAVA use more than one checkpoint to reduce the number of instructions squashed on a mis-speculation.

As mis-speculations would result in squashes of many independent instructions, it is only beneficial to apply value prediction to those loads whose value is very predictable. Unfortunately, most loads have difficult to predict values (CLEAR reports that only 24.3% (integer) and 39.6% (floating point) of loads are high confidence [42]), meaning that value prediction is not a general enough solution for a processor to achieve true load latency

tolerance.

#### 2.3.1 Load and Store Queues

CAVA uses a *transactional cache* to buffer speculatively retired loads and stores. A transactional cache is a data cache which accepts speculative writes and can abort them if needed. The transactional cache handles the verification of loads relative to stores from other threads by tracking which cache lines have been speculatively read and signaling a violation if one of these lines must be evicted before the read is made non-speculative. The transactional cache works well with value prediction-based designs like CAVA, but is ill-suited to other forms of load latency tolerance which re-execute miss-dependent instructions. In designs which depend on the re-execution of miss-dependent instructions, a re-executing load may need a value which has been overwritten in the cache, preventing the load from executing properly.

CLEAR assumes large load and store queues, but notes that other solutions exist, including a transactional cache.

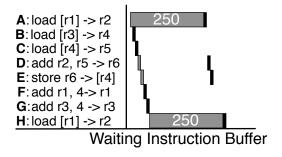

# 2.4 Waiting Instruction Buffer

Waiting InstructionBuffer (WIB) [44] differs from Runahead in that it attempts to obtain ILP as well as MLP under misses by retaining miss-independent work. To accomplish this, WIB places miss-dependent instruction in a new structure<sup>2</sup> called the waiting instruction buffer as they pseudo-execute. The process of removing the miss-dependent instructions and buffering them for later re-execution is termed *slicing out*. Unlike the issue queue, the WIB does not support associative search and is not latency critical, meaning it can be made large. When a long latency miss returns, it and its dependent instructions are *sliced in*—re-injected into the issue queue for re-execution.

<sup>&</sup>lt;sup>2</sup>It is possible to simply let the ROB double as the WIB since there is a one-to-one correspondence between the structures. The WIB paper describes it as a separate structure, so that is how it is described here.

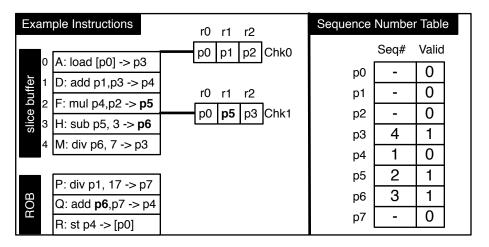

Figure 2.12: Execution under WIB. Black boxes represent actual executions, while grey boxes represent pseudo-executions to propagate poison.