# San Jose State University SJSU ScholarWorks

#### Master's Theses

Master's Theses and Graduate Research

Summer 2017

# Time-based, Low-power, Low-offset 5-bit 1 GS/s Flash ADC Design in 65nm CMOS Technology

Mehdi Nasrollahpour San Jose State University

Follow this and additional works at: https://scholarworks.sjsu.edu/etd\_theses

## **Recommended** Citation

Nasrollahpour, Mehdi, "Time-based, Low-power, Low-offset 5-bit 1 GS/s Flash ADC Design in 65nm CMOS Technology" (2017). *Master's Theses.* 4853. DOI: https://doi.org/10.31979/etd.6wsv-p773 https://scholarworks.sjsu.edu/etd\_theses/4853

This Thesis is brought to you for free and open access by the Master's Theses and Graduate Research at SJSU ScholarWorks. It has been accepted for inclusion in Master's Theses by an authorized administrator of SJSU ScholarWorks. For more information, please contact scholarworks@sjsu.edu.

# TIME-BASED, LOW-POWER, LOW-OFFSET 5-BIT 1 GS/s FLASH ADC DESIGN IN 65nm CMOS TECHNOLOGY

A Thesis

Presented to

The Faculty of the Department of Electrical Engineering

San José State University

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

by

Mehdi Nasrollahpour

August 2017

© 2017

Mehdi Nasrollahpour

# ALL RIGHTS RESERVED

The Designated Thesis Committee Approves the Thesis Titled

# TIME-BASED, LOW-POWER, LOW-OFFSET 5-BIT 1 GS/s FLASH ADC DESIGN IN 65nm CMOS TECHNOLOGY

by

Mehdi Nasrollahpour

# APPROVED FOR THE DEPARTMENT OF ELECTRICAL ENGINEERING

# SAN JOSÉ STATE UNIVERSITY

August 2017

Dr. Sotoudeh Hamedi-Hagh Dr. Morris Jones

Dr. Robert H. Morelos-Zaragoza

Department of Electrical Engineering Department of Electrical Engineering Department of Electrical Engineering

#### ABSTRACT

# TIME-BASED, LOW-POWER, LOW-OFFSET 5-BIT 1 GS/s FLASH ADC DESIGN IN 65nm CMOS TECHNOLOGY

#### By Mehdi Nasrollahpour

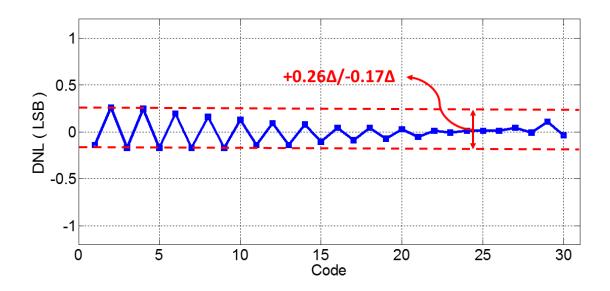

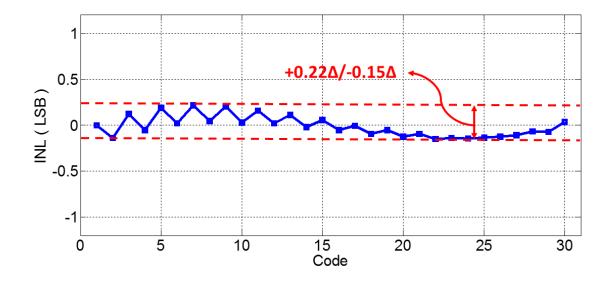

Low-power, medium resolution, high-speed analog-to-digital converters (ADCs) have always been important block which have abundant applications such as digital signal processors (DSP), imaging sensors, environmental and biomedical monitoring devices. This study presents a low power Flash ADC designed in nanometer complementary metal-oxide semiconductors (CMOS) technology. Time analysis on the output delay of the comparators helps to generate one more bit. The proposed technique reduced the power consumption and chip area substantially in comparison to the previous state-ofthe-art work. The proposed ADC was developed in TSMC 65nm CMOS technology. The offset cancellation technique was embedded in the proposed comparator to decrement the static offset of the comparator. Moreover, one more bit was generated without using extra comparators. The proposed ADC achieved 4.1 bits ENOB at input Nyquist frequency. The simulated differential and integral non-linearity static tests were equal to +0.26/-0.17 and +0.22/-0.15, respectively. The ADC consumed 7.7 mW at 1 GHz sampling frequency, achieving 415 fJ/Convstep Figure of Merit (FoM).

#### DEDICATION

I would like to dedicate this thesis to my parents. My father who is my role model in the whole aspects of my life. He is the reason I continued my education to make him lofty and proud as he coveted, and my mother who always supports me with her everlasting love. My parents offered unwavering encouragement for the endeavors I have pursued. Their staunch supports, love, and inspiration have given me valor to attain this degree. They made my life be in debt to them.

I would also like to dedicate my works and achievements to my nephews, Parham and Amirpasha that they have always been missed. Love all of you to the moon and back.

#### ACKNOWLEDGEMENTS

"Think for your lord's gratification, be intellectual and truthful - Ferdowsi"

First, I would like to express my gratefulness to my thesis adviser, Professor Sotoudeh Hamedi-Hagh. This thesis would have not been accomplished without his dedication, kindness, and his perpetual support. I would like to thank Professor Hamedi-Hagh for providing me the access to Radio Frequency Integrated Circuits (RFIC) lab and Cadence software.

I am inclined to thank Professor Thuy Le, the graduate adviser of San Jose State University, for his continuous support during the hardship times. I would like to show my gratitude to all my colleagues, Rahul Sreekumar, Andrew Chen, Daniel Mazidi, Priyanka Agrawal, and Fleura Hajilou in Analog Mixed-Signal (AMS) center and RFIC lab for creating friendly atmosphere along with treasured discussions.

Eventually, I should express my appreciativeness to my brothers, Habib, Hamed, and Hamid for their unconditional supports, and all the people who made the privations facilitated for me in this path.

vi

# TABLE OF CONTENTS

| List of Tablesi                                                                                                                                                                                                                          | ix             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| List of Figures                                                                                                                                                                                                                          | х              |

| List of Abbreviationsx                                                                                                                                                                                                                   | ii             |

| CHAPTER ONE. Introduction                                                                                                                                                                                                                | 1              |

| CHAPTER TWO. Time-Based ADCs                                                                                                                                                                                                             | 3              |

| <ul> <li>2.1 Slope and Integrating ADCs.</li> <li>2.2 PWM ADC.</li> <li>2.3 Level-Crossing or Asynchronous ADC.</li> <li>2.4 Voltage Controlled Delay Cell Based ADCs.</li> <li>2.5 Voltage to Frequency Converter Based ADC.</li> </ul> | 4<br>5<br>7    |

| CHAPTER THREE. Flash ADC Background1                                                                                                                                                                                                     | 11             |

| 3.1 Comparator.3.2 Offset Consideration.3.3 Encoder.3.4 Errors in FLASH ADC.3.5 Resistor Ladder.                                                                                                                                         | 13<br>15<br>16 |

| CHAPTER FOUR. Circuit Implementation                                                                                                                                                                                                     | 21             |

| <ul> <li>4.1 Proposed Extra Bit Generation Idea.</li> <li>4.2 Comparator Circuit Implementation.</li> <li>4.3 Phase Detector Design.</li> <li>4.4 Overall Circuit Diagram.</li> </ul>                                                    | 24<br>30       |

| CHAPTER FIVE. Simulation Results                                                                                                                                                                                                         | 35             |

| 5.1 Power Consumption.       3         5.2 Static Tests.       3         5.2.1 Differential Non-linearity.       3         5.2.2 Integral Non-linearity.       3         5.3 Dynamic Tests.       3                                      | 35<br>35<br>37 |

| CHAPTER SIX. Results Comparison                                                                                                                                                                                                          | 46             |

| CHAPTER SEVEN. Conclusion                                                                                                                                                                                                                | 49             |

| References |  |

|------------|--|

| Appendices |  |

# LIST OF TABLES

| Table 1. Thermometer to Binary Gray Encoder                                 | . 18 |

|-----------------------------------------------------------------------------|------|

|                                                                             |      |

| Table 2. Comparison to The Previous State-of-th-art Prestigious Publication | . 48 |

# LIST OF FIGURES

| Fig. 2.1 Slope and integrating ADC schematic diagram                | 4  |

|---------------------------------------------------------------------|----|

| Fig. 2.2 PWM ADC schematic diagram                                  | 5  |

| Fig. 2.3 Level-Crossing or asynchronous ADC schematic diagram       | 6  |

| Fig. 2.4 Clocking in Level-Crossing ADC                             | 7  |

| Fig. 2.5 Voltage-controlled delay cell based ADCs schematic diagram |    |

| Fig. 2.6 Voltage-to-frequency converter based ADC schematic diagram | 9  |

| Fig. 2.7 Non-linearity improvement with feedback loop               | 10 |

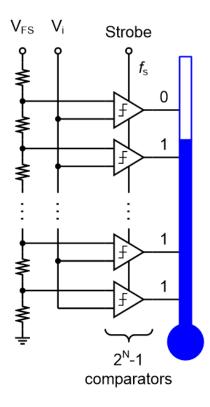

| Fig. 3.1 Conventional Flash ADC architecture                        | 11 |

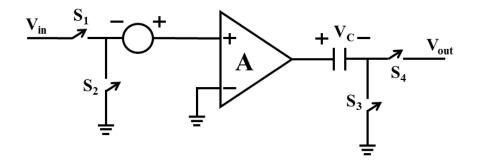

| Fig. 3.2 Output series offset cancellation                          | 14 |

| Fig. 3.3 Input offset cancellation                                  | 14 |

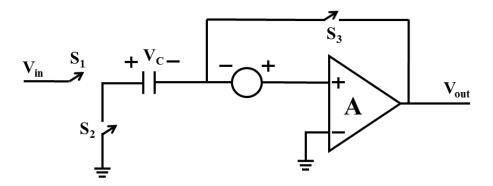

| Fig. 3.4 Auto-zeroing technique offset cancellation                 | 15 |

| Fig. 3.5 Output thermometer code                                    | 16 |

| Fig. 3.6 Bubble error correction                                    | 17 |

| Fig. 3.7 Bubble error correction with Gray coding                   | 19 |

| Fig. 3.8 Noise injection to the resistor ladder                     | 19 |

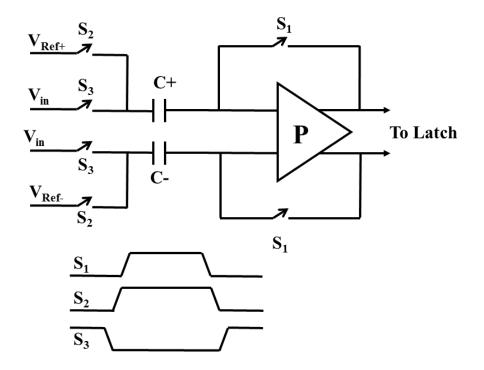

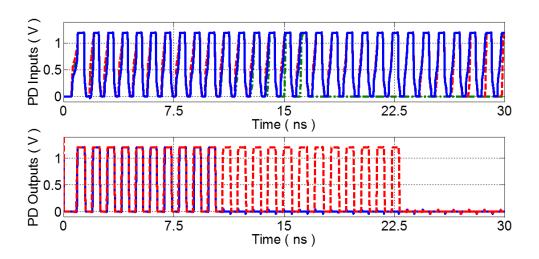

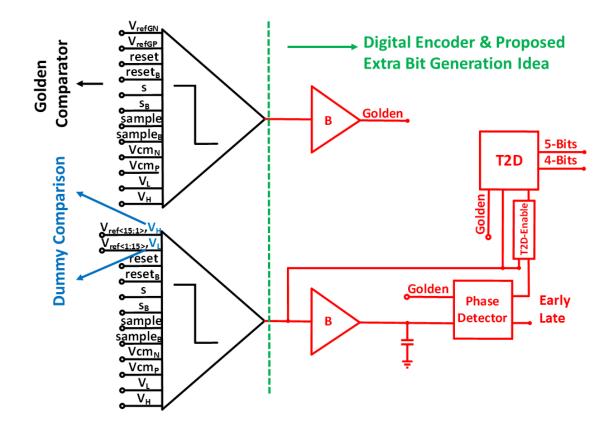

| Fig. 4.1 Proposed idea block diagram                                | 21 |

| Fig. 4.2 Proposed idea concept                                      | 22 |

| Fig. 4.3 Extra generated bit adding                                 |    |

| Fig. 4.4 Comparator delay characteristics                           | 24 |

| Fig. 4.5 Proposed comparator used in the Flash ADC                  | 25 |

| Fig. 4.6 Comparator delay                                           | 27 |

| Fig. 4.7 Comparator average current                                              | 28 |

|----------------------------------------------------------------------------------|----|

| Fig. 4.8 Comparator overdrive recovery test                                      | 29 |

| Fig. 4.9 Comparator clock signals                                                | 30 |

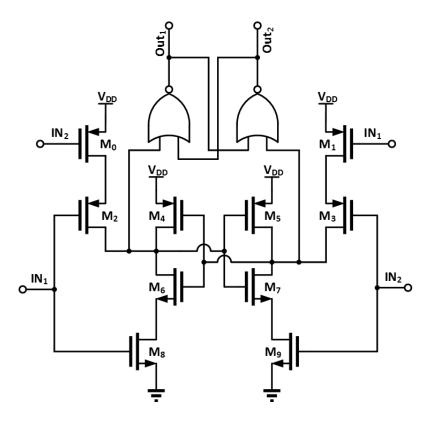

| Fig. 4.10 Phase detector internal circuitry                                      | 31 |

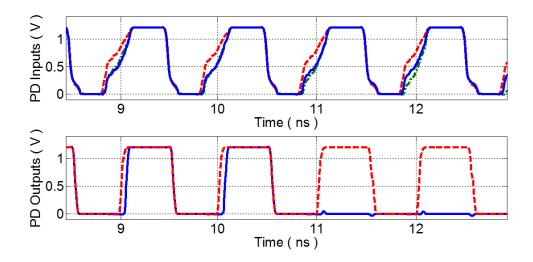

| Fig. 4.11 Phase detector performance from close point of view                    | 32 |

| Fig. 4.12 Phase detector performance from far point of view                      | 32 |

| Fig. 4.13 Overall proposed Flash ADC block diagram                               | 34 |

| Fig. 5.1 DNL simulation results                                                  | 36 |

| Fig. 5.2 INL simulation results                                                  | 38 |

| Fig. 5.3 Input analog signal conversion to digital code transfer characteristics | 39 |

| Fig. 5.4. Dynamic test block diagram                                             | 40 |

| Fig. 5.5 Nyquist input frequency dynamic test results                            | 43 |

| Fig. 5.6 DC input frequency dynamic test results                                 | 43 |

| Fig. 5.7 SNDR measurements in different input frequencies                        | 44 |

| Fig. 5.8 ENOB measurements in different input frequencies                        | 44 |

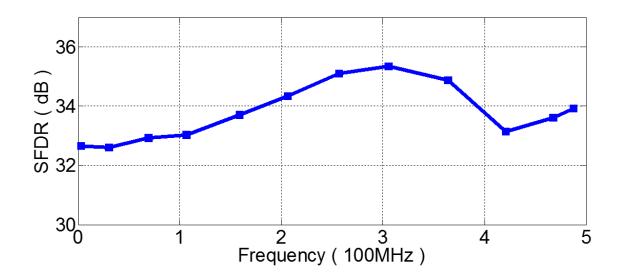

| Fig. 5.9 SFDR measurements in different input frequencies                        | 45 |

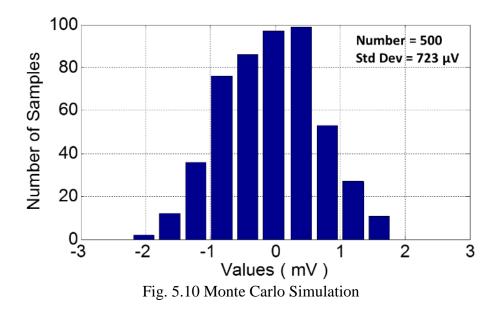

| Fig. 5.10 Monte Carlo Simulation                                                 | 45 |

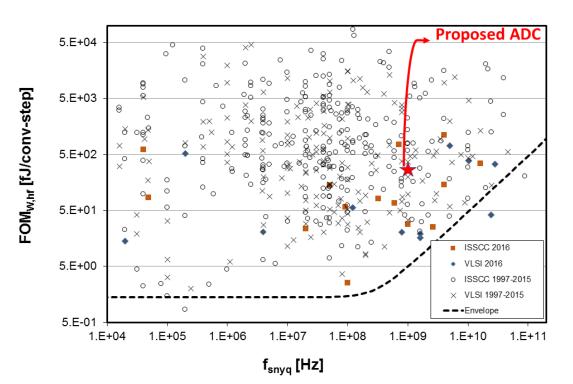

| Fig. 6.1 Walden FoM comparison                                                   | 46 |

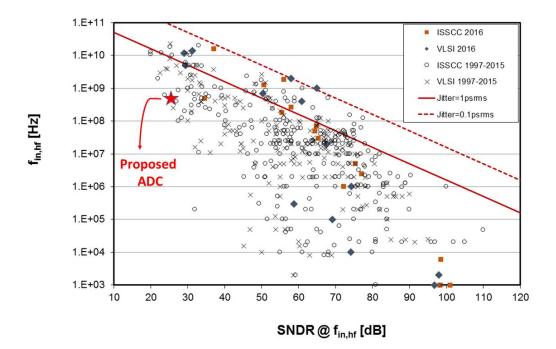

| Fig. 6.2 Aperture Comparison                                                     | 47 |

| Fig. 6.3 Energy comparison                                                       | 47 |

#### LIST OF ABBREVIATIONS

- ADC Analog-to-Digital Converter

- CMOS Complementary Metal Oxide Semiconductor

- DAC Digital-to-Analog Converter

- DNL Differential Non-linearity

- ENOB Effective Number of Bits

- FoM Figure of Merit

- INL Integral Non-linearity

- LSB Least Significant Bit

- PVT Process, Variation, and Temperature

- SFDR Spurious-Free Dynamic Range

- SNDR Signal-to-Noise Distortion Ratio

- SNR Signal-to-Noise Ratio

- S&H Sample-and-Hold

- TG Transmission Gate

- UWB-Ultra-Wideband

- PWM Pulse Width Modulation

- TDC Time-to-Digital Converter

- VCO Voltage-Controlled Oscillator

- SAR Successive Approximation Register

- LDO Low Drop-Out

- PLL Phase-Locked-Loop

FFT – Fast Fourier Transform

# CHAPTER ONE Introduction

Analog-to-digital converters (ADCs) form the interface between the exterior world and digital circuitry. They convert true-to-life signals into digital bits in order to further digitally process and evaluate the signal. Flash ADCs have been a pertinent choice for several applications because they have a much lower latency and an instantaneous comparison of the signal with pre-assigned reference levels. The use of Flash ADC in renewable energy systems has been of great interest recently due to their ability to be operated within a stringent power usage limit and high resolution [1].

However, there are several other applications in which Flash ADCs are given priority, especially in the digital signal processing field and in ultra-wideband (UWB) transceiver architecture [2-4]. In recent years, there has been extensive research in the development of low power ADCs for bio-medical applications that have very high sensitivity [5]. One of the major reasons for the extensive research is that all of these applications work on a limited power supply; hence, power consumption is of the utmost priority. The ADC accounts for a sizeable portion of power consumption in any module; hence, a reduction in its power consumption is highly favorable while optimizing such mixed-signal-based application modules.

In this work, we describe the working, design and simulated results of a 5-bit 1 GS/s Flash ADC that is optimized for low power consumption, while also employing an offset cancellation technique in order to decrement the static offset of the comparator, which is a fully differential dynamic comparator [6]. The ADC described in this thesis has fairly

1

low power consumption when compared to the other state-of-the-art 5-bit ADCs [7-9]. The thermal code generated is digitally processed with a Verilog-A code that will be presented in the appendix.

The thesis is divided into the following sections: Chapter 2 describes the different time-based Flash ADC architectures and their functionality and Chapter 3 discusses the Flash ADC different design concerns and blocks. Chapter 4 accentuates the working and design calculations involved in the comparator, phase detector, bit generation idea, and the Flash ADC architecture circuit implementation. The fifth chapter focuses on the simulation results obtained from the same ADC and a concise comparison with other state-of-the-art work, which is presented in Chapter 6. The final chapter provides a conclusion for the proposed study.

### CHAPTER TWO Time-Based ADCs

There are several ADCs that do not work based on voltage quantizing. Instead, these architectures quantize the time, frequency, or current. This chapter will talk about various time-based Flash ADCs. Based on the power budget, resolution, and dynamic range, the right decision can be made for designing the ADC.

## 2.1 Slope and Integrating ADCs

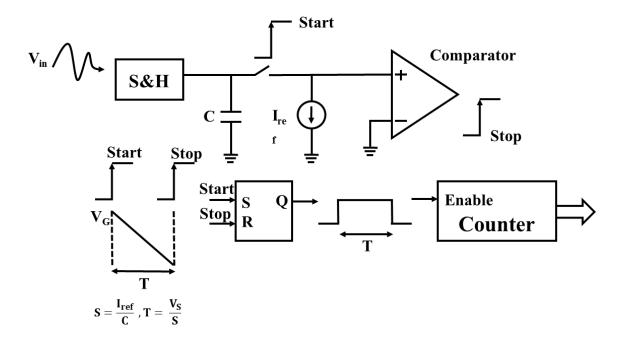

Slope and integrating ADCs try to convert the analog signal to digital binary codes in the time domain. The basic block diagram is shown in Fig. 2.1. The analog signal will be sampled through the sample-and-hold (S&H) block and kept on the capacitor. Stored voltage on the capacitor will be discharged by the current source,  $I_{ref}$ . A ramp signal will be generated on the capacitor during this process. By starting the ramp signal, a triggered signal will be activated to enable the counter. Another triggered signal will be generated by reaching the zero voltage that disables the counter. The digital counter is directly proportional to the input signal [10]. This ADC does not have any complexity since the integral non-linearity (INL) will be defined by linearity of the ramp signal. Therefore, the differential non-linearity (DNL) does not depend on the component that will result in ADC monotonicity.

Fig. 2.1 Slope and integrating ADC schematic diagram

Obviously, the capacitor plays the most important role in the performance of this ADC, so the sampling frequency for this ADC architecture cannot be so high. High resolution is achievable by having the high-frequency clock. This high-frequency clock itself consumes large power. It is recommended that the counter be replaced with a sophisticated time-to-digital converter (TDC) to have high-speed slope-based ADCs [11,12].

#### 2.2 PWM ADC

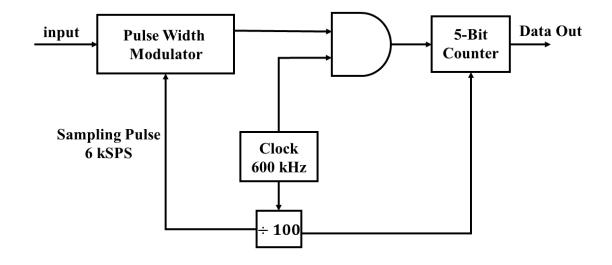

PWM time-based architecture developed and filed about 70 years ago [13]. The conceptual schematic of the PWM ADC is depicted in Fig. 2.2 [14].

First of all, the input signal is pulse modulated through the pulse width modulator; then it will be quantized through a counter. As we know, PWM is a process for transferring the data from the amplitude domain to the time domain. This block includes a non-linear behavior that creates considerable distortion. It is proved in [15] that the non-linearities and distortions can be circumvented if the modulation frequency is eight times more than the input signal frequency. A complicated TDC can be substituted by the counter, like the slope-based ADCs.

Fig. 2.2 PWM ADC schematic diagram

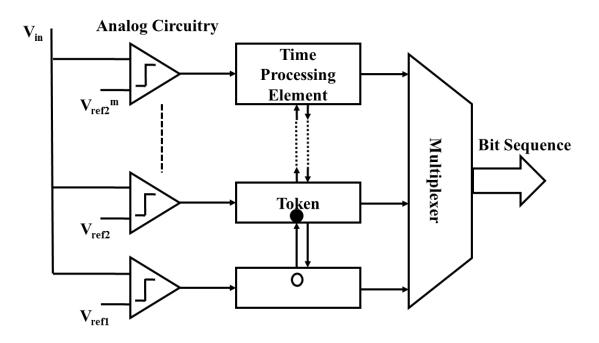

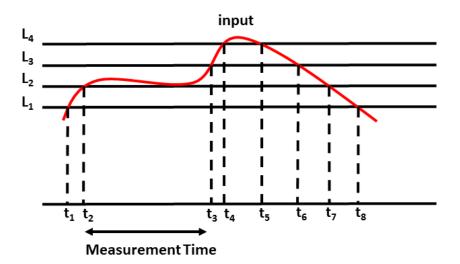

#### 2.3 Level-Crossing or Asynchronous ADC

Level-crossing ADCs, also known as asynchronous ADCs, have some reference voltages and comparators [16-20]. When the input signal passes a specific value (threshold level), the ADC starts sampling and quantization during these instants. The signals and the basic schematic are depicted in Fig. 2.3 and Fig. 2.4 [21]. Since the input signal is time variable, the samples are different. At the instant the input voltage crosses the threshold value, the comparator makes the decision and generates output. The ADC is called asynchronous because the working performance does not depend on any reference clock. On the contrary, it depends on the input signal. A sign or block is required to

discern which comparator is working. Since the performance depends on the input signal, the power consumption severely changes due to the input activity. For example, if the input signal remains the same, there is no digital power consumption as no threshold value is passed. Like the Flash ADCs, comparator offset and mismatches play an important role in ADC performance. The quantization block works at a certain frequency, which is referred to as the sampling frequency. Time quantization should occur at Nyquist frequency to reconstruct the original signal from the discrete signal. Nyquist frequency requires that the sampling frequency should be at least two times the input signal. Higher input frequencies need a greater sampling frequency.

Fig. 2.3 Level-Crossing or asynchronous ADC schematic diagram

Fig. 2.4 Clocking in Level-Crossing ADC

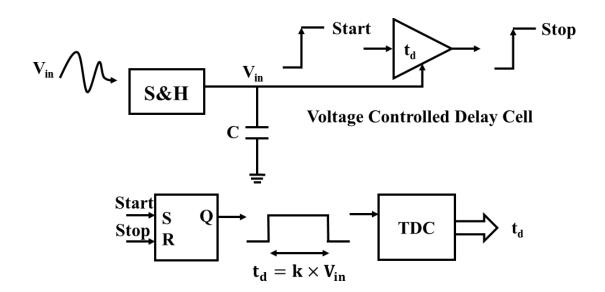

# 2.4 Voltage Controlled Delay Cell-Based ADCs

The schematic diagram of the voltage-controlled delay cell based ADC is shown in Fig. 2.5. Obviously, a delay will be given to the input signal after the sampling, and the delay time will be digitized by a TDC. The start signal will go through the voltagecontrolled delay cell which is controlled by the input voltage. The TDC output depends on the input signal. Designing a delay cell which can linearly modulate the input signal in a large dynamic range mandates a challengeable design.

Fig. 2.5 Voltage-controlled delay cell based ADCs schematic diagram

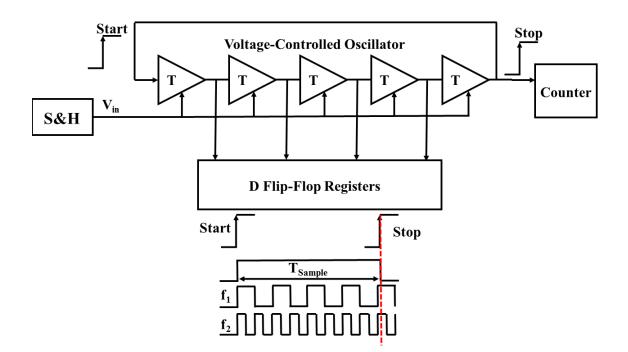

## 2.5 Voltage to Frequency Converter Based ADC

Frequency can be interpreted by the phase and the phase is another definition for the time. In this ADC, the input signal is going to be converted to the frequency (phase); then the frequency (phase) can be digitized by a frequency (phase) to digital converter.

In this ADC type, the input analog signal should be converted to the frequency (phase), which is exactly the definition of the voltage-controlled oscillators (VCOs) [22,23]. The VCO-based ADC schematic is depicted in Fig. 2.6. As is obvious in Fig. 2.6, the small period of time between start and stop signals is available for quantizing the frequency through the counter. The mapping table which usually shows the VCO characteristics is exploited for processing the counter output. The ADC resolution can be determined by:

Resolution =

$$\log_2 \left( \frac{f_{max}}{f_{sample}} - \frac{f_{min}}{f_{sample}} \right)$$

(2.1)

Where  $f_{sample}$  is the inverse of time between the start and stop signal,  $f_{max}$  is the maximum VCO frequency and  $f_{min}$  is the minimum VCO generated frequency.

As we know, the ring oscillator has the maximum tuning range between the other VCOs. It means it can be used as the VCO in this ADC type to have the maximum resolution. The speed can be increased by using the multi-phase VCOs. The input voltage is converting to the frequency domain through the VCO and the counter counts the rising and falling edges. Assuming N stages ring oscillator, the resolution can be calculated by:

Resolution =

$$\log_2 \left[ \left( \frac{f_{max}}{f_{sample}} - \frac{f_{min}}{f_{sample}} \right) \times 2N \right]$$

(2.2)

Fig. 2.6 Voltage-to-frequency converter based ADC schematic diagram

Jitter, linearity, process and temperature variations are some issues which make designers give careful consideration to this architecture design. One of the advantages which this circuit has, is that the voltage-to-frequency converter and the quantizer are simultaneously happening in VCO. Since the phase of the output is a quantity which depends on the input voltage, VCO can be served as the first order noise shaping constructor [24-26].

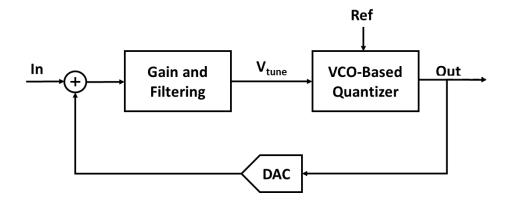

As mentioned above, the jitter and the non-linearity of the input and output are suffering the VCOs. VCO non-linearity can be improved by applying a feedback which acts like a  $2^{nd}$  order  $\sum \Delta$  ADC as represented in Fig. 2.7. There have been several state-of-the-art published works with the same idea [25-27].

Fig. 2.7 Non-linearity improvement with feedback loop

# CHAPTER THREE Flash ADC Background

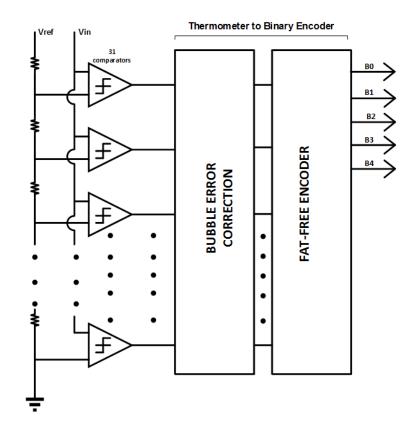

Fig. 3.1 depicts the schematic block diagram of the conventional Flash ADC architecture. Flash ADC usually consists of a comparator, resistor ladder, and logic encoder [28]. The critical component of any A/D converter is the comparator circuit. The characteristics and performance of the comparator determine the overall performance of the ADC. The different parts of the conventional Flash ADC will be explained in the following subsections.

Fig. 3.1 Conventional Flash ADC architecture

#### **3.1 Comparator**

The major trade-off in designing a comparator is between the offset voltage and the power consumption of the comparator. The static power consumption of a comparator can be drastically reduced by dynamic topology implementation [29]. This also would mean that positive feedback will be provided by means of a latch, thereby speeding up the decision-making process. To ensure that the offset of a comparator remains low, larger input transistors should be used and ensure that the amplification phase of the comparator provides large enough differential voltage to subside the offset of the cross-coupled latch stage. In order to find a trade-off between offset and power consumption, the comparator circuit used here comprises of a cascaded amplifying stage along with a usual regenerative latch stage [30].

The comparators mainly compare the two instantaneous differential input voltages and will return the result in the form of high or low voltages based on the difference sign. There are three different architectures for building the comparators [31]:

- 1. Amplifier with the high gain, differential input, and single ended output.

- 2. Latched comparators which are implemented in two different ways: latch only comparator, and high sensitivity latch with low gain preamplifier.

- 3. Sampled data comparators with track and hold input circuit, in which the offset can be nullified.

The first kind of comparator needs to have a large gain which is not accessible in MOSFET technologies. Therefore, many stages should be used to satisfy the required gain of the comparator. This method unveils the tradeoff between bandwidth and offset. The comparator gain does not need to be linear since it should pull the output voltage up or down rapidly. Hence, a back-to-back inverter which forms a latch can be used for regeneration by forming a positive feedback loop. The Latch small signal model shows that the latch can be modeled by the amalgamation of single-pole amplifier and positive feedback. The latch can compensate the amplifier gain since the latch is three times faster than the amplifier. However, the latch has a fairly high input offset voltage, as high as 100 mV. Using the preamplifier along with the latch can resolve this issue [32]. The gain of the preamplifier will compromise the comparator speed and input referred offset of latch.

### **3.2 Offset Consideration**

A major hurdle while designing Flash ADC is the kickback noise and the effect it has on the resistive ladder and offset voltage. These can often lead to a shift in the reference level, resulting in an erroneous decision. Some procedures for implementing the resistor ladder have been established to prevent these errors [33,34].

Offset in amplifier-based comparators can be canceled by using a capacitor in series with cascaded amplifiers. The capacitor can be used either in the input of the amplifiers or the output. Output offset can be nullified by using the recommended switching circuits, as shown in Fig. 3.2 [30]. Output series offset cancellation can almost cancel the offset, and there is no need for closed loop stability. Nonetheless, the gain for each amplifier stage should be small, and the utilized offset cancellation capacitor can degrade the overall performance of the circuit.

13

Fig. 3.2 Output series offset cancellation

Input offset cancellation circuit can be built like Fig. 3.3 [35]. The feedback loop should provide stability conditions due to the feedback loop around the amplifier. A C-array can be used to store the offset in the applications such as C-array successive approximation register (SAR) ADCs [36]. Input offset cancellation cannot completely cancel the offset. In the same manner, the capacitor can reduce the overall performance.

Fig. 3.3 Input offset cancellation

The offset voltage of latched comparators can be omitted with the auto-zeroing technique. The proposed technique is shown in Fig. 3.4 [37]. During the phase  $S_1$ , the amplifier brings the offset to the input by the unity gain. The capacitor C+ is charged to the offset value and the input voltage was previously applied to the capacitor's left plate

before  $S_1$ . The offset will be stored on the capacitor and will be canceled in the differential performance of the amplifier during  $S_3$ .

Fig. 3.4 Auto-zeroing technique offset cancellation

# 3.3 Encoder

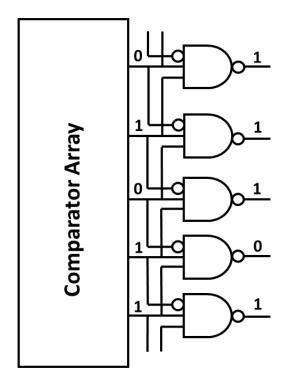

As mentioned in the previous sections, the comparator outputs are high or low which the values more than the reference voltage are high and the values less than the reference voltage are low. To some extent, the generated outputs act like the thermometer as shown in Fig. 3.5.

Fig. 3.5 Output thermometer code

Therefore, the necessity of the blocks at the output might arise here to convert the thermal code of the comparator array to the binary codes. Each thermometer code converts to one of the N codes before converting into binary. Two challenges will appear in the thermometer to binary encoder design: Speed and error handling capability [38, 39].

## **3.4 Errors in FLASH ADC**

The errors in Flash ADC are divided into two categories; metastability and bubble errors. Metastability happens when the comparator cannot decide and compare the inputs, so the output is neither high nor low. The comparator output is indistinguishable, and the encoder interprets the thermal code as either high or low. Based on Flash ADC performance and Fig. 3.5, the thermal codes should act like a thermometer. Therefore, a wrong decision can be made by the comparator corruption called "bubble errors". There are three sources which can result in bubble errors:

- Comparator offset voltage larger than half of the least significant bit (LSB) that might change zero crossing points for the comparators which are next to each other.

- 2. Error in comparators sampling time.

- 3. Propagation delay variations which happen in high input frequencies [40].

Bubbles can be suppressed easily. By using three-input NAND instead of two-input NAND, one bubble can be suppressed as depicted in Fig. 3.6 [41]. In the same manner, two bubbles can be suppressed by four-input NAND.

Fig. 3.6 Bubble error correction

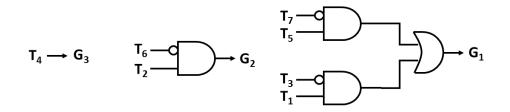

Gray coding is another efficient way to overcome the errors. The gray coding is summarized in the following table. Each G<sub>i</sub> is affected by only one T<sub>i</sub> that means the contribution of each input is less and consequently less errors. Metastability state probabilities are lower with Gray coding and this encoder provides more time for the generation by using pipelining [42].

| Thermometer Code |            |            |    |            | Gray       |            |    | Binary |    |            |                       |            |

|------------------|------------|------------|----|------------|------------|------------|----|--------|----|------------|-----------------------|------------|

| <b>T</b> 1       | <b>T</b> 2 | <b>T</b> 3 | T4 | <b>T</b> 5 | <b>T</b> 6 | <b>T</b> 7 | G3 | G2     | G1 | <b>B</b> 3 | <b>B</b> <sub>2</sub> | <b>B</b> 1 |

| 0                | 0          | 0          | 0  | 0          | 0          | 0          | 0  | 0      | 0  | 0          | 0                     | 0          |

| 1                | 0          | 0          | 0  | 0          | 0          | 0          | 0  | 0      | 1  | 0          | 0                     | 1          |

| 1                | 1          | 0          | 0  | 0          | 0          | 0          | 0  | 1      | 1  | 0          | 1                     | 0          |

| 1                | 1          | 1          | 0  | 0          | 0          | 0          | 0  | 1      | 0  | 0          | 1                     | 1          |

| 1                | 1          | 1          | 1  | 0          | 0          | 0          | 1  | 1      | 0  | 1          | 0                     | 0          |

| 1                | 1          | 1          | 1  | 1          | 0          | 0          | 1  | 1      | 1  | 1          | 0                     | 1          |

| 1                | 1          | 1          | 1  | 1          | 1          | 0          | 1  | 0      | 1  | 1          | 1                     | 0          |

| 1                | 1          | 1          | 1  | 1          | 1          | 1          | 1  | 0      | 0  | 1          | 1                     | 1          |

Table 1. Thermometer to Binary Gray Encoder

Fig. 3.7 Bubble error correction with Gray coding

#### **3.5 Resistor Ladder**

The voltage divider is the first section of Flash ADCs to generate the different level of the references. The common voltage divider is based on the equal resistors which are connected in series to provide equal voltage levels as the reference voltages to be compared to the input voltage. The important parameters are power consumption and the susceptibility to the noise. If the voltage divider uses small resistors, power consumption will increase, while the small resistors will suppress the noise injection. Feeding the input signal to the resistor ladder is the major source for the noise injection. The procedure for injecting the noise through the input signal is depicted in Fig. 3.8 [43].

Fig. 3.8 Noise injection to the resistor ladder

As the resistor at the input of the preamplifier increase, the noise injected to the ladder is higher. It is obvious that the worst case will happen in the middle of the ladder. In practical circuits and fabrication, it should be noted to minimize the wiring from the ladder to the preamplifier. These sources can degrade the voltage divider performance.

The voltage divider is mainly consisting of the resistors, so the thermal noise contribution regarding the resistor ladder should be considered. Resistor thermal noise can be calculated as follows [44]:

$$\mathbf{v}_{\mathbf{n}} = \sqrt{4\mathbf{k}\mathbf{T}\mathbf{R}\Delta\mathbf{f}} \tag{3.1}$$

Where k is constant, T is the temperature and R is the resistor. Since the resistor value is small in the voltage divider, the thermal noise contribution is negligible.

There are different structures for Flash ADC ladders using capacitors, resistors, and the combination of them which are presented in [45-47]. Besides, a low drop-out (LDO) voltage regulator can be used to make the resistor ladder stable [48, 49].

## CHAPTER FOUR Circuit Implementation

The description of the proposed Flash ADC design is divided into four different sections. First, the novel idea which is used for extra bit generation is explained. Next section describes the comparator circuitry design, and the required features. The phase detector circuit implementation is then presented. Finally, the last section will describe the overall circuit diagram and integration of all the blocks.

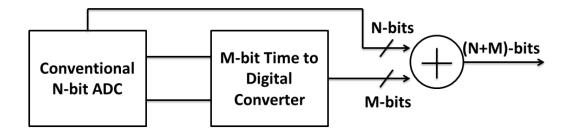

#### 4.1 Proposed Extra Bit Generation Idea

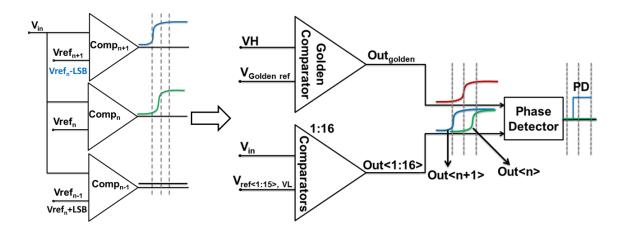

Flash ADC requires 2<sup>N</sup>-1 comparators to quantize the input voltage. Therefore, it is evident that one more bit data conversion rate will cost eight times more power consumption [50]. Generation of one more bit for high-resolution Flash ADCs is challenging. The main idea which will be explained thoroughly in the following paragraphs is depicted in Fig. 4.1. As shown in Fig. 4.1, a TDC can be used instead of the huge number of extra comparators to generate more bits.

Fig. 4.1 Proposed idea block diagram

A Flash ADC consists of the resistor ladder, comparator, and encoding logic. The comparator plays the most significant role in the decision-making process. The proposed

idea is achieved from the fact that each comparator used in Flash ADC needs a certain time to reach the final value which can be defined as follows [51,52]:

$$t = \tau \times Ln^{\frac{V_{in(diff)}}{A_{pre}V_0}}$$

(4.1)

Where  $\tau$ , A<sub>pre</sub>, V<sub>in(diff)</sub>, and V<sub>0</sub> are latch time constant, preamplifier gain, input differential voltage, and output voltage, respectively. It is evident from (4.1), the time needed for making the decision extremely depends on the input differential voltage between the input analog signal and the reference voltage generated by the resistor ladder, preamplifier gain, and the latch time constant. When the input difference voltage is smaller, the comparator output voltage can compare the inputs more slowly; hence, more time is required for the final decision to be reached. This time can be a good opportunity to do more comparisons. The conceptual schematic of proposed idea is shown in Fig. 4.2.

Fig. 4.2 Proposed idea concept

With regards to (4.1), the delay is at the maximum point for the closest comparator to the reference voltage, which is mainly contributing to the comparison. Therefore, a comparator can be utilized as reference, called the golden comparator. It will carry out the comparator's output comparison with the golden reference through the phase detector to perceive the anticipated comparison edge. Hence, the higher half-LSB and lower LSB can be distinguished by time analysis, as depicted in Fig. 4.3.

Fig. 4.3 Extra generated bit adding

In effect, each LSB distance is divided by two which means the input analog voltage could be converted by half-LSB, which is the new resolution. The proposed ADC could generate one more bit by using the only  $2^{N-1}+1$  comparators which is less than the conventional method that we traditionally had used  $2^{N}-1$  comparators. It is worth mentioning that one more extra comparator has been used for the last edge detection.

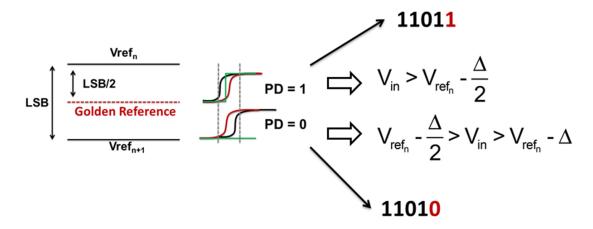

The proposed idea works based on the comparator delay and it will be saturated after a certain input voltage difference, as demonstrated in Fig. 4.4.

Fig. 4.4 Comparator delay characteristics

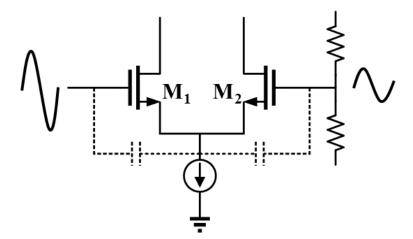

# **4.2 Comparator Circuit Implementation**

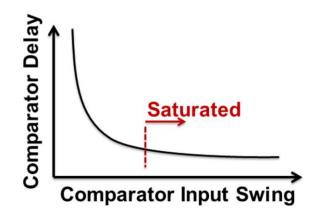

A two-stage fully differential comparator has been designed in this thesis. Clocked regenerative comparators are suitable for high-speed Flash and SAR ADCs. Proposed comparator internal circuitry is shown in Fig. 4.5. Input voltage appears on the left plate of C<sub>s</sub> and the common mode voltage will be applied to another plate when the clock is low. Consequently,  $V_{ref}$  and  $V_{cm}\neg V_{in}+V_{ref}$  are applied to the left and right plates when the clock is high, respectively. It is worth mentioning that the comparator has been chosen to be differential since the proposed idea and time analysis are so sensitive to process, variation, and temperature (PVT).

Fig. 4.5 Proposed comparator used in the Flash ADC

The proposed idea depends on the time analysis and the output delay of the comparator. The proposed comparator delay consists of the preamplifier and latch delay. Latch delay can be written as [53]:

$$t_{\text{latch}} = \frac{C_{\text{L}}}{g_{\text{m,eff}}} \ln \left( \frac{\Delta V_{\text{out}}}{\Delta V_{\text{in}}} \right)$$

(4.2)

Where  $g_{m,eff}$ ,  $\Delta V_{out}$ ,  $C_L$ , and  $\Delta V_{in}$  are defined as back to back effective

transconductance, output differential voltage, load capacitor, and differential input voltage, respectively. The differential preamplifier output voltage can be calculated as:

$$A_{\rm pre} = \frac{g_{\rm m} \times R_{\rm D}}{1 + \frac{j\omega}{\omega_{\rm 0}}} \tag{4.3}$$

$$\Delta V_{o,pre} = 2R_{D}\omega_{0} \left(\frac{I_{D,1}}{V_{OD,1}} + \frac{I_{D,2}}{V_{OD,2}}\right) e^{-\omega_{0}t_{pre}}$$

(4.4)

Where  $R_D$  is the differential pair output resistor,  $\omega_0$  is the 3dB-bandwidth of the preamplifier,  $I_{D,i}$  and  $V_{OD,i}$  are the i-th transistor biasing current and overdrive voltage. Based on the (4.4) and (4.2), the total propagation delay for the two-stage comparator is:

$$t_{\rm p} = t_{\rm latch} + t_{\rm pre} \tag{4.5}$$

$$t_{p} = \frac{C_{L}}{g_{m,eff}} \ln\left(\frac{\Delta Vout}{\Delta Vo,diff}\right) + \ln\left(\frac{2 R_{D} \omega_{0}}{\Delta Vo,diff} \times \frac{V_{OD,1} I_{D,2} + V_{OD,2} I_{D,1}}{V_{OD,2} V_{OD,1}}\right)^{\frac{1}{\omega_{0}}}$$

(4.6)

Equation (4.6) unveils the effects of different parameters on the propagation delay. The propagation delay of the comparator is inversely proportional to input common mode voltage. It is obvious by decreasing the common-mode voltage, the propagation delay will be increased. The proposed extra bit generation relies on the time analysis of the comparators output delay. Therefore, keeping the common mode voltage constant, is the main challenge which is considered into comparator design through the  $\phi_2$  switch when the clock is low.

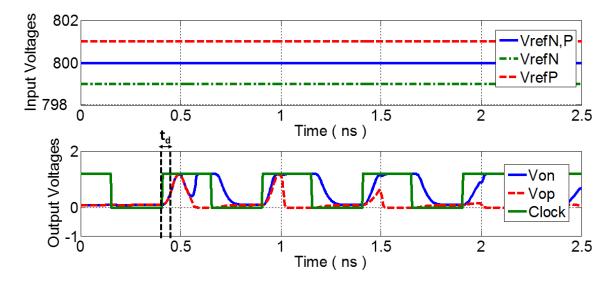

The comparator delay with 1 mV voltage difference with respect to the reference voltage is simulated and the measured delay is 115 ps which shows that the comparator can work properly to 4.5 GHz. However, because of the time analysis on the comparator outputs, sampling frequency should not be high to provide enough time.

Fig. 4.6 Comparator delay

Comparators consume the most part of the total circuit power consumption. Comparator average power consumption at the worst case is  $856 \,\mu$ W. The worst comparator delay happens while the input voltage difference is minimum. As shown in Fig. 4.7, the current drawn from the power supply is more while the latch is in regeneration state.

Fig. 4.7 Comparator average current

Dual offset cancellation is embedded to the circuit through the capacitors,  $C_S$  and  $C_{OC}$ .  $C_S$  will store the input offset voltage along with sampling the input signals, and the output offset voltage will be stored on  $C_{OC}$ .  $C_S$  should be chosen larger than  $C_{OC}$  since it has been used for the input offset storage purpose [54].

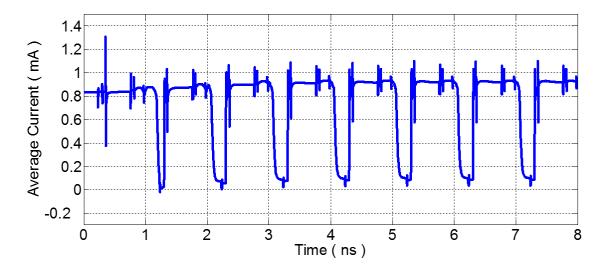

Comparator overdrive recovery plays an integral role in comparator design. The comparator will not be able to resolve the next input if the recovery time is not enough to discharge the previous state, an error will occur in the comparator output. Overdrive recovery test has been done and the results are shown in Fig. 4.8. It is obvious from the overdrive recovery test which the comparator can compare two different inputs right after each other without error occurance. Passive clamp, active restore, and low gain per each stage can minimize this effect.

Fig. 4.8 Comparator overdrive recovery test

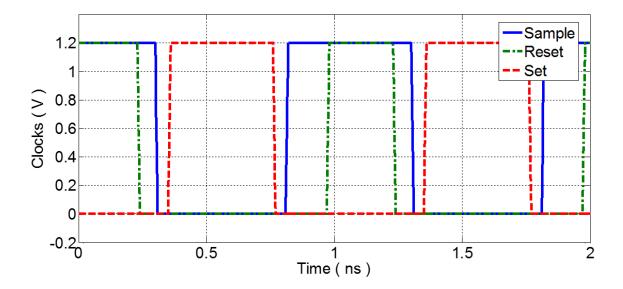

Several clocks with different duty cycles have been used to excite the comparator. This comparator works very fast because of the strong back to back inverter used at the comparator output. The latch should be deactivated when the preamplifier is amplifying the input voltage difference to reduce the power consumption. The other reason for the latch deactivation is preventing the comparator output from saturation. Since the comparator works based on the input voltage storage on the capacitor, it takes a time to charge and discharge the capacitor with respect to the input voltages. Therefore, the sample and set signals should be non-overlapping clocks. Clock signals used in the proposed comparator for transmission gates (TGs) are shown in Fig. 4.9.

Fig. 4.9 Comparator clock signals

### **4.3 Phase Detector Design**

The phase detector PD is an essential block in the various applications such as phaselocked-loops (PLL) which will turn the input phase difference over as high or low in output. In the other words, it works as a comparator which compares the phase, so it can be called as phase comparator. It can be made up of frequency mixer, analog multiplier, or logic circuits. Detecting the phase difference between the different comparators is so imperative in the proposed idea, so a precision phase detector which can detect the differences in the order of picoseconds is required. There are lots of different phase detector architectures which are suitable for various digital and analog applications [55-58].

The input voltages  $IN_1$  and  $IN_2$  have some phase differences. Consider the  $IN_1$  is lagged; hence, the transistors  $M_1$ ,  $M_9$ , and  $M_3$  are off and  $M_2$ ,  $M_8$ , and  $M_3$  are on. The voltage difference will define the voltages at the XOR input gates through the back to

back inverters. Hence, the early signal will be high and the late signal will be down. The internal circuitry for the utilized phase detector is shown in Fig. 4.10.

Fig. 4.10 Phase detector internal circuitry

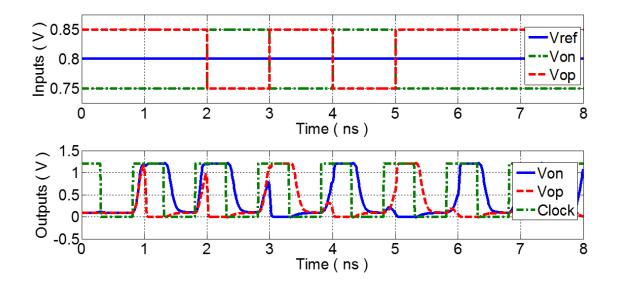

The phase detector performance is evaluated and the results are brought in Fig. 4.11. As shown in Fig. 4.11, when the golden comparator output is lagged, the phase detector starts to generate a pulse at the output. In the same way, the phase detector output is low while the golden comparator is lead. The functionality of the circuits is shown at the transition edge but the complete process from far point of view has been shown in Fig. 4.12.

Fig. 4.11 Phase detector performance from close point of view

Fig. 4.12 Phase detector performance from far point of view

# 4.4 Overall Circuit Diagram

The comparator, phase detector, and the proposed idea were discussed in above sections. The integration of the blocks will be described in this section. Sixteen comparators used for the comparison purpose which the last one is added as a dummy comparator because of the last transition edge detection. The upper comparator, called the golden comparator, is used for the extra bit generation through the comparator output comparison to the golden one.

The buffers are used to make the comparator outputs and the golden comparator output more clear for the comparison purpose and preparing enough drive capability for the comparator output since the output capacitor seen at the comparator output is considerable. Golden comparator senses the most capacitance due to the connection to the sixteen phase detector inputs. Each phase detector input capacitance has been monitored and it acts like 50 fF capacitor. Therefore, fifteen 50 fF capacitors are used at the output of each comparator to make the delay equal and the comparison valid. It is worth mentioning that the input characteristics of each phase detector have been processed by R-C test which means the input resistor and capacitor can be found by finding the input time constant.

Three Verilog-A blocks are built to help the simulations because an ideal DAC is required for doing the dynamic test. Therefore, the internal codes of Verilog-A blocks can be found in the appendix.

Fig. 4.13 Overall proposed Flash ADC block diagram

### CHAPTER FIVE Simulation Results

Proposed Flash ADC functionality has been monitored and assessed by doing the required simulations. The power consumption, dynamic test, and static test which can unveil the transient and frequency characteristics of the proposed ADC are done and the results are presented in the following subsections.

### **5.1 Power Consumption**

Power consumption is one of the significant parameters considered in this study. As explained before, adding one more bit to the ADC will cause eight times more power consumption [50]. The proposed Flash ADC has been designed in TSMC 65 nm CMOS technology with 1.2 V power supply. The total power consumption includes three different sections; resistor ladder, comparators, and digital bit extraction circuit.

## **5.2 Static Tests**

The more critical linearity measurement is measuring INL and DNL static tests which cannot be easily compensated in the digital domain because it depends on the overall performance of the ADC. They are known as the dynamic metrics for assessing the frequency performance of the presented ADC.

### **5.2.1 Differential Non-linearity**

DNL is defined as the deviation of code width from ideal  $\Delta$  (1LSB) when going through the transfer curve of an ADC. The end points should be connected to take away the offset and full scale error effects, and then the ideal transfer curve of the ADC will be achieved with the same offset and full scale error. Ideally, ADC transition points are equal to  $\Delta$  (1LSB) and the offset and full-scale error are removed for DNL calculation. DNL[k] shows the difference between the widths of the k-th code from its ideal width. Therefore, the DNL can be calculated as follows [59]:

$$DNL[k] = \frac{Width[k] - LSB}{LSB}$$

(5.1)

Where Width[k] is the width of k-th code. It is obvious from (5.1) that the worst case DNL is -1 when the code width is zero which can be considered as a missing code. Moreover, it can be shown that the sum of all DNL numbers should be ideally equal to zero for an ADC.

The DNL performance of the proposed ADC is shown in Fig. 5.1. The DNL is calculated by applying a very slow ramp signal at the input so that 100 samples are taken for each code to reach reliable DNL value. According to the calculations, the worst case DNL is equal to +0.26 for the positive side and -0.17 for the negative side.

Fig. 5.1 DNL simulation results

#### **5.2.2 Integral Non-linearity**

The main static measure for quality of a data converter is usually INL which is more global type of measurement. It is basically a deviation of code transition from its ideal location. In the same way, the endpoints are connected to find the ideal characteristics. Ergo, the INL would be the difference between the real transition point and the ideal transition point.

The INL can be calculated by constructing an ideal staircase between first and last transition, and then the INL can be calculated by using the equation (5.2) [59].

$$INL[m] = \frac{T[m] - T[ideal]}{W[ideal]}$$

(5.2)

Where W[ideal] is the ideal width for each code (LSB), T[m] is the m-th transition point and the T[ideal] is the m-th ideal transition point. However, the most common way for calculating the INL is (5.3). It can be inferred from (5.3) that the last code INL will be zero with respect to (5.1).

$$INL[m] = \sum_{i=1}^{m-1} DNL[i]$$

(5.3)

INL performance of the proposed ADC is shown in Fig. 5.2. The INL is calculated by applying a very slow ramp signal at the input so that 100 samples are taken for each code to reach a reliable INL value. According to the calculations, the worst case INL is equal to +0.22 for the positive side and -0.15 for the negative side.

Fig. 5.2 INL simulation results

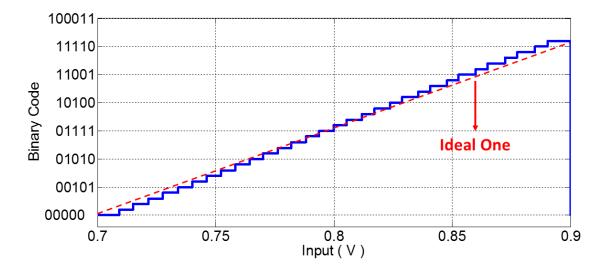

The transfer function can be generated by applying a low slope ramp. The slope should be too low to make sure that the simulation results are valid. One hundred samples per each code are required for running the ramp test based on the rule of thumb. A ramp test with the slope of 62.5k is applied to the input. The proposed ADC transfer function, which is monotonic, is depicted in Fig. 5.3.

Fig. 5.3 Input analog signal conversion to digital code transfer characteristics

# **5.3 Dynamic Tests**

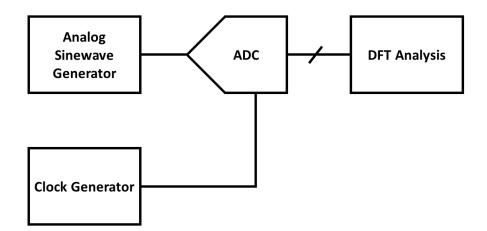

The static test does not tell the full story of the ADC as we know that there was no information about the noise and high frequency effects on the static test. Therefore, there should be another test metric to assess the frequency characteristics.

In case of ADC testing, the device under test is an ADC that the input signal would be a sinusoidal signal from analog signal generator; the output would be digital codes. One way to find the quality of the proposed ADC is to have a DAC with much better performance. Hence, the output digital codes of the ADC would be the input of the digital to analog converter, and then the DAC output would be an analog signal. Ergo, the output signal frequency characteristics can be evaluated through a spectrum analyzer. The dynamic test block diagram of the analog-to-digital conversion is depicted in Fig. 5.4. A clean sinewave should be applied to the input and the spectral performance should be assessed at the output by using an ideal DAC converter.

Fig. 5.4. Dynamic test block diagram

Another way of doing the dynamic test is using data acquisition system. Data acquisition system will grab the digital code from ADC and save it as a file. Then the process can be done by running a MATLAB code which is presented in the appendix.

There are some spectral performance metrics for ADCs including non-idealities which are going to be explained and simulated here. These parameters show how far the proposed ADC is from the ideal one.

Signal-to-noise ratio (SNR) which is defined as the signal power over the noise power which includes quantization noise, thermal noise, and flicker noise. It is worth mentioning that the signal power, DC component, and the harmonics power should set to zero for measuring the noise power. SNR is defined as follows [60,61]:

Signal – to – noise ratio =

$$\frac{\text{Signal Power}}{\text{Noise Power}}$$

(5.4)

Signal-to-noise distortion ratio (SNDR) which is defined as the signal power over the noise power plus the distortion power that includes all the harmonic components. SNDR can be measured by:

$$SNDR = \frac{Signal Power}{Noise Power+Distortion Power}$$

(5.5)

The other parameter is spurious-free dynamic range (SFDR) which is defined as the signal power over the largest harmonic power. SFDR can be expressed by:

$$SFDR = \frac{Signal Power}{Largest Harmonic Power}$$

(5.6)

Effective number of bits (ENOB) is another dynamic test metrics of the proposed ADC. A question that might arise here is whether an ADC with less than 31.86 dB SNDR is exactly 5-bits ADC or not? 5-bits ADC needs at least 31.86 dB SNDR. Hence, ENOB is a parameter which shows how far the proposed Flash ADC is close to the ideal 5-bits Flash ADC. The ENOB can be computed as:

$$ENOB = \frac{SNDR - 1.76 \, dB}{6.02 \, dB}$$

(5.7)

The ideal ENOB is achievable only in the case of neglecting thermal noise, DNL, and INL. Usually, it can be achieved by building low frequency and low resolution ADC but for the high frequency and high resolution ADCs is almost impossible. Rule of thumb for good performance/power trade-off is about one bit less than the specified number of bits.

Low noise design is costly because there is four times penalty in power per bit (ENOB) or 6 dB extra SNDR. That comes from the fact which the  $\frac{g_m}{c}$  should be kept constant because of the working frequency of the ADC. The current should be bigger to increase the transconductance gain of the amplifier to make the noise smaller (transit frequency of MOS transistor is constant value) as it is obvious from the following equations:

$$v_n = \sqrt{\frac{KT}{C}}$$

(5.8)

$$f_{\rm T} = \frac{g_{\rm m}}{c} \tag{5.9}$$

$$g_m \propto I$$

(5.10)

The spectral test is done in two different input frequencies; Nyquist and DC. Because of the fast Fourier transform (FFT), the input frequency should be defined by (5.11). Bin 3 and bin 499 has been considered as the DC and Nyquist frequency, respectively. N shows the number of FFT points which is assumed 1024 in this study. Therefore, the DC frequency is equal to 487.3 MHz and the Nyquist frequency is equal to 2.93 MHz.

$$f_{\rm in} = \rm bin \times \frac{f_{\rm sample}}{N}$$

(5.11)

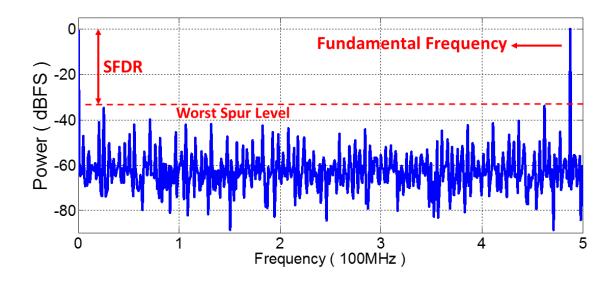

The dynamic test for the Nyquist input frequency has been done and the simulation result is depicted in Fig. 5.5. As shown in the simulation results, achieved SNDR and SFDR are equal to 26.4 dB and 33.91 dB, respectively. Therefore, the calculated ENOB is 4.1 bits.

Fig. 5.5 Nyquist input frequency dynamic test results

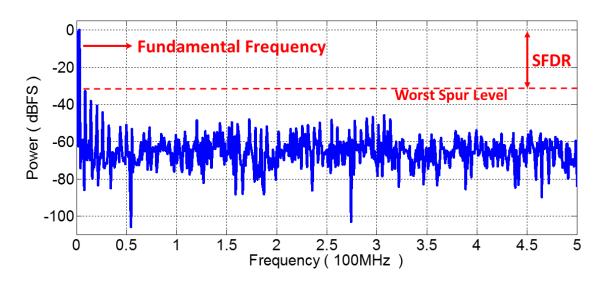

In the same manner, the dynamic test for the DC input frequency is done and the simulation result is depicted in Fig. 5.6. As shown in the simulation results, achieved SNDR and SFDR are equal to 28.69 dB and 32.66 dB, respectively. Therefore, the calculated ENOB is 4.47.

Fig. 5.6 DC input frequency dynamic test results

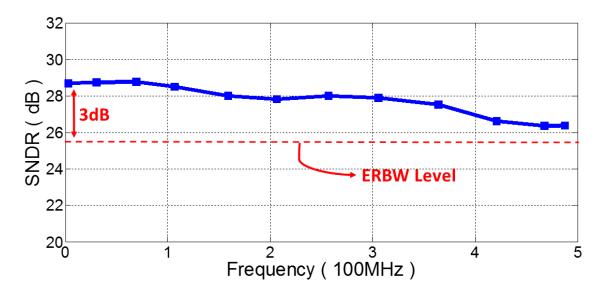

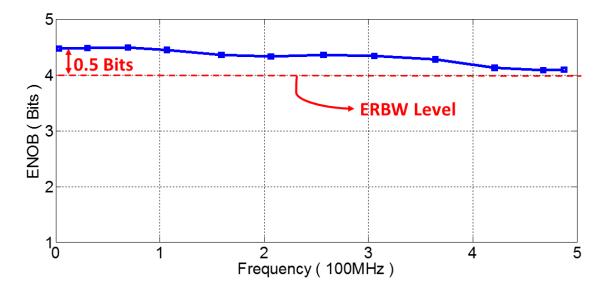

The dynamic test has been done in different input frequencies and the results are shown in Fig. 5.7, Fig. 5.8, and Fig. 5.9. It can be seen from Fig. 5.7 which the effective resolution bandwidth (ERBW) for the proposed ADC is more than Nyquist frequency.

Fig. 5.7 SNDR measurements in different input frequencies

Fig. 5.8 ENOB measurements in different input frequencies

Fig. 5.9 SFDR measurements in different input frequencies

The comparator offset rejection performance is assessed by running the Monte Carlo simulation with 500 points iterations. Monte Carlo simulation confirms that the input referred offset voltage is equal to  $\sigma_{OS} = 723 \ \mu V$ . Simulated Monte Carlo histogram is demonstrated in Fig. 5.10.

# CHAPTER SIX Results Comparison

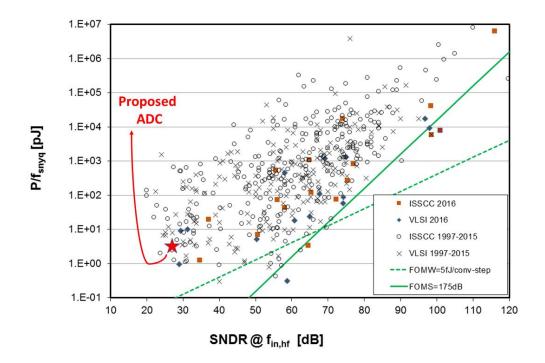

The performance of the proposed ADC is compared to previous works with the same Flash architecture and the results are summarized in Table 2. The calculated FoM is equal to 415 fJ/Convstep. Furthermore, comparison with all of the previously published ADCs has been done through the Murmann survey as shown in Fig. 6.1, Fig. 6.2, and Fig. 6.3 [62]. The  $f_{synq}$ ,  $f_{in,hf}$  are the sampling frequency and the input frequency which the dynamic test including ENOB measurement has been done. It is worth mentioning that the FoM used for this comparison is Walden FoM which can be defined as [63]:

$$FOM = \frac{P}{2^{ENOB} \times f_s}$$

(6.1)

Fig. 6.1 Walden FoM comparison

Fig. 6.2 Aperture Comparison

Fig. 6.3 Energy comparison

| Reference           | [64]  | [65] | [66]  | [67] | [68]  | [69] | [70] | [71] | This  |

|---------------------|-------|------|-------|------|-------|------|------|------|-------|

| Parameter           |       |      |       |      |       |      |      |      | Work  |

| Technology          | 65    | 90   | 180   | 90   | 45    | 90   | 90   | 90   | 65    |

| ( <b>nm</b> )       |       |      |       |      |       |      |      |      |       |

| Resolution          | 7     | 6    | 4     | 7    | 7     | 6    | 5    | 6    | 5     |

| V <sub>Supply</sub> | 1.2   | 1.2  | 1.8   | 1.2  | 1.15  | 0.9  | 1    | 1.2  | 1.2   |

| ( <b>V</b> )        |       |      |       |      |       |      |      |      |       |

| fs                  | 2     | 1    | 1.8   | 1.5  | 1.4   | 3.5  | 1.75 | 3    | 1     |

| (GHz)               |       |      |       |      |       |      |      |      |       |

| ENOB                | 6.04  | 5.4  | 3.7   | 6.05 | 6.17  | 4.69 | 4.6  | 5.3  | 4.1   |

| (Bits)              |       |      |       |      |       |      |      |      |       |

| INL                 | 0.64  | 0.74 | 0.3   | 0.64 | 1     | 0.96 | 0.39 | 0.2  | 0.22  |

| (LSB)               |       |      |       |      |       |      |      |      |       |

| DNL                 | 0.58  | 0.49 | 0.29  | 0.7  | 0.74  | 0.5  | 0.38 | 0.2  | 0.26  |

| (LSB)               |       |      |       |      |       |      |      |      |       |

| Power               | 20.7  | 18.7 | 15.5  | 204  | 33.24 | 98   | 7.6  | 90   | 7.7   |

| (W)                 |       |      |       |      |       |      |      |      |       |

| FoM                 | 0.157 | 0.44 | 0.695 | 2.06 | 0.57  | 0.95 | 0.15 | 2.28 | 0.415 |

| (pJ/Conv.step)      |       |      |       |      |       |      |      |      |       |

Table 2. Comparison to The Previous State-of-the-art Publication

## CHAPTER SEVEN Conclusion

A time-based Flash ADC has been designed in deep-submicron CMOS technologies. The number of comparators has been reduced about 45% in compare to the traditional Flash ADCs which are usually power hungry. The proposed Flash ADC was designed in 65 nm TSMC CMOS technology and has been compared to previous work through the calculated Walden FoM which is 415 fJ/Conv.step.

The static and dynamic tests are done to assess the proposed ADC's performance. The proposed architecture could achieve 4.1 bits ENOB at Nyquist frequencies and 4.47 bits ENOB at DC frequencies. The static performance of the proposed ADC was evaluated by doing a static test which resulted in 0.26 and 0.22 LSB for DNL and INL, respectively. The analog-to-digital conversion process was done by consuming merely 7.7 mW while the sampling frequency is 1 GHz.

It can be concluded that the proposed Flash ADC is suitable for low power applications such as biomedical devices. As the number of the comparators has been reduced considerably, the chip area is reduced. Therefore, a 5-bit analog-to-digital conversion process is done just by implementing 4-bit conversion.

#### References

- Ying-Zu Lin, Yu-Chang Lien and Soon-Jyh Chang, "A 0.35-1V 0.2-3 GS/s 4-bit low power Flash ADC for a solar powered wireless module," *VLSI Design and Automation*, 2010, pp. 299 - 302.

- [2] Mohammad Masoumi, Erik Markert, Ulrich Heinkel, Georges Gielen, "Ultra Low power lash ADC for UWB Transciever applications," *ECCTD 2009*, pp. 41 44.

- [3] Liyaqat Nazir, Roohie Naaz Mir, Najeeb-ud-din Hakim, "Low power comparator with offset cancellation technique for Flash ADC," *SMACD 2017*, Pages: 1 4.

- [4] E. Martin I. Gustafsson, Ana Rusu, Mohammed Ismail: "Behavioral modelling of Programmable UWB/ Bluetooth ADC," *ICECS 2007*, pp. 1159 - 1162.

- [5] Guohe Yin, U-Fat Chio, He-Gong Wei, Sai-Weng Sin, Seng-Pan U, Rui Paulo Martins, Zhihua Wang, "An Ultra low power 9-bit 1MS/s SAR ADC for bio-medical applications," *ICECS 2010*, pp. 878 - 881.

- [6] Mohsen Hassanpourghadi, Milad Zamani, Mohammad Sharifkhani, "A low power low offset dynamic comparator for analog to digital converters," *Microelectronics Journal*, vol. 45, no. 2, Feb 2014, pp. 256–262.

- [7] Jonathan E. Proesel and Lawrence T. Pileggi, "A 0.6-1 V Inverter based 5-bit Flash ADC in 90nm Digital CMOS," *IEEE CICC 2008*, pp. 153 156.

- [8] Masaya Miyahara, James Lin, Kei Yoshihara, and Akira Matsuzawa, "A 0.5V, 1.2 mW, 60fJ, 600 MS/s 5-bit Flash ADC," *IEEE Asia Solid State Circuit Conference*, 2010, pp. 1 - 4.

- [9] Jiale Yang, Yong Chen, He Qian, Yan Wang, Ruifeng Yue, "A 3.65mW 5 bit 2GS/s Flash ADC ith built- in reference voltage in 65 nm CMOS process," *IEEE ICSICT* 2012, pp. 1 - 4.

- [10] Maxim Integrated Circuits, "Understanding Integrating ADCs," [Online]. Available: http://www.maximic.com.cn/pdfserv/en/an/AN1041.pdf

- [11] E. Delagnes, D. Breton, F. Lugiez, and R. Rahmanifard, "A Low Power Multi-Channel Single Ramp ADC With Up to 3.2 GHz Virtual Clock," *IEEE Transactions On Nuclear Science*, vol. 54, no. 5, pp. 1735-1742, Oct 2007.

- [12] T. Fusayasu, "A Fast Integrating ADC Using Precise Time-to-Digital Conversion," *Nuclear Science Symposium Conference Record*, vol. 1, pp. 302-304, Oct. 2007.

- [13] A. H. Reeves, "Electrical Signaling System," US Patent 2 272 070, Feb. 3,1942.

- [14] Analog Devices, "Analog Devices Data Conversion Handbook," [Online]. Available: http://analog.com/library/analogDialogue/archives/3906/data\_conversion\_handbook.h tml.

- [15] F. Marvasti, "Nonuniform Sampling Theory and Practice," Kluwer Academic Publisher, 1990.

- [16] E. Allier, et al., "120nm Low Power Asynchronous ADC," ISLPED'OS, Aug. 2005

- [17] F. Akopyan, R. Manohar, A. B. Apsel, "A Level-Crossing Flash Asynchronous Analog-to-Digital Converter," *Proceedings of the 12th IEEE International Symposium on Asynchronous Circuits and Systems(ASYNC'06).*

- [18] B. Schell and Y. Tsividis, "A clockless ADC/DSP/DAC System with Activity-Dependent Power Dissipation and No Aliasing," *ISSCC Dig. Tech. Papers*, pp. 550-551, Feb. 2008.

- [19] N. Sayiner, H. V. Sorensen and T. R. Viswanathan "A Level-Crossing Sampling Scheme for A/D Conversion," *IEEE Transactions on Circuits and Systems II*, vol. 43, no. 4, pp. 335 – 339, Apr. 1996.

- [20] E. Allier, et al., "A New Class of Asynchronous A/D Converters Based on Time Quantization," *Ninth International Symposium on Asynchronous Circuits and Systems* (ASYNC), pp. 196 – 205, May 2003.

- [21] H. Pekau, A. Yousif and J. W. Haslett, "A CMOS Integrated Linear Voltage-to-Pulse-Delay-Time Converter for Time-Based Analog-to-Digital Converters," *ISCAS 2006*, pp. 2373-2376.

- [22] J. Kim and S. Cho, "A Time-Based Analog-to-Digital Converter Using a Multi-Phase Voltage-Controlled Oscillator," *ISCAS 2006*, pp. 3934-3937.

- [23] T. Watanabe, T. Mizuno and Y. Makino, "An All-Digital Analog-to-Digital Converter With 12-μV/LSB Using Moving-Average Filtering," *IEEE Journal of Solid State Circuits*, vol. 38, no. 1, pp. 120–125, Jan. 2003.

- [24] B. M. Helal, M. Z. Straayer, G. Y. Wei and M. H. Perrott, "A Low Jitter 1.6 GHz Multiplying DLL Utilizing a Scrambling Time-to-Digital Converter and Digital Correlation," VLSI Symp. Dig. Tech. Papers, pp. 302-303, Feb. 2007.

- [25] A. Iwata, N. Sakimura, M. Nagata and T. Morie, "The Architecture of Delta Sigma Analog-to-Digital Converters Using a Voltage-Controlled Oscillator as a Multibit

Quantizer," *IEEE Transactions on Circuits and Systems II*, vol. 46, no. 7, pp. 941-945, July 1999.

- [26] R. Naiknaware, H. Tang and T. S. Fiez, "Time-Referenced Single-Path Multi-Bit ΣΔ ADC using a VCO-Based Quantizer," *IEEE Transactions on Circuits and Systems II*, vol. 47, no. 7, pp. 596 – 602, July 2000.

- [27] M. Z. Straayer and M. H. Perrott, "A 10-bit 20MHz 38mW 950MHz CT ΣΔ ADC with a 5-bit noise-shaping VCO-based Quantizer and DEM circuit in 0.13µ CMOS," VLSI Symp. Dig. Tech. Papers, pp. 246-247, June 2007.

- [28] Y. Yoshii; K. Asano; M. Nakamura; C. Yamada, "An 8 bit, 100 mS/s flash ADC," IEEE Journal of Solid-State Circuits, Vol. 19, no. 6, pp. 842 – 846, 1984.

- [29] Daiguo Xu; Shiliu Xu; Guangbing Chen, "High-speed low-power and low-power supply voltage dynamic comparator," *Electronics Letters*, Vol. 51, no. 23, pp. 1914 – 1916, 2015.

- [30] J.T. Wu, et al., "A 100-MHz pipelined CMOS comparator," *IEEE Journal of Solid-State Circuits*, vol. 23, pp. 1379 1385, 1988.

- [31] Gabriele Manganaro, "Advanced Data Converters", Springer.

- [32] Vladimir Milovanović; Horst Zimmermann, "A fully differential CMOS self-biased two-stage preamplifier-latch threshold detection comparator," *ISCAS 2013*, pp. 606 609, 2013.

- [33] Davicle De Caro, Marino Coppola, Nicola Petra, Ettore Napoli, Antonio G. M. Strollo, Valeria Garofalo, "High-speed differential resistor ladder for A/D converters," *Proceedings of 2010 IEEE International Symposium on Circuits and Systems*, pp. 1723 - 1726, 2010.

- [34] M. Mokhtari, J. F. Jensen, T. Kaplan, C. Fields, D. McLaughlin, W. Ng, "4-bit flash ADC in InP-HBT technology using distributed resistor ladder," *Proceedings. 2004 IEEE Radio and Wireless Conference*, pp. 143 - 146, 2004.

- [35] R. Poujois and J. Borel, "A low drift fully integrated MOSFET operational amplifier," *IEEE Journal of Solid-State Circuits*, vol. 13, pp. 499 503, August 1978.

- [36] Xuan-Lun Huang, Ping-Ying Kang, Jiun-Lang Huang, Yung-Fa Chou, Yung-Pin Lee, Ding-Ming Kwai, "On Pre/Post-Bond Testing and Calibrating SAR ADC Array in 3-D CMOS Imager," 2011 IEEE 17th International Mixed-Signals, Sensors and Systems Test Workshop, Pages: 25 - 28, 2011.

- [37] I. Mehr and L. Singer, "A 500-Msample/s, 6-Bit Nyquist-Rate ADC for Disk-Drive Read-Channel Applications," *IEEE Journal of Solid-State Circuits*, 1999, pp. 912-20.

- [38] S. Tsukamoto, W. G. Schofield, and T. Endo, "A CMOS 6-b, 400-MSample/s ADC with error correction," *IEEE Journal of Solid-State Circuits*, vol. 33, pp. 1939–1947, 1998.

- [39] C. Portmann and T. Meng, "Power-efficient metastability error reduction in CMOS flash A/D converters," *IEEE Journal of Solid-State Circuits*, vol. 31, pp. 1132–1140, August 1996.

- [40] M. Choi and A. Abidi, "A 6-bit 1.3-GSample/s flash ADC in 0.35μm CMOS," IEEE Journal of Solid-State Circuits, vol. 36, pp. 1847–1858, December 2001.

- [41] D. Johns and K. Martin, "Analog Integrated Circuit Design," John Wiley, 1997.

- [42] B. Razavi, "Principles of Data Conversion System Design," New York, IEEE Press, 1995.

- [43] B. Razavi, "Design of sample-and-hold amplifiers for high-speed low-voltage A/D converters," *IEEE Custom Integrated Circuits Conference (CICC)*, pp. 59-66, May 1997.

- [44] P. R. Gray, P. J. Hurst, S. H. Lewis, and R. G. Meyer, "Analysis and Design of Analog Integrated Circuits," 4th ed. New York: John Wiley, 2001.

- [45] Nikola Katic, Radisav Cojbasic, Alexandre Schmid, Yusuf Leblebici, "A sub-mW pulse-based 5-bit flash ADC with a time-domain fully-digital reference ladder," *Microelectronics Journal*, Vol. 46, no. 12, Pages 1343–1350, December 2015.

- [46] Siqiang Fan, He Tang, Hui Zhao, Xin Wang, Albert Wang, Bin Zhao, Gary G Zhang, "Enhanced Offset Averaging Technique for Flash ADC Design," *Tsinghua Science and Technology*, Vol. 16, No. 3, 2011.

- [47] Sunghyun Park, Yorgos Palaskas, Ashoke Ravi, Ralph E. Bishop, and Michael P. Flynn, "A 3.5 GS/s 5-b Flash ADC in 90 nm CMOS," *IEEE CICC 2006*, pp. 489 -492.

- [48] Mehdi Nasrollahpour, Sotoudeh Hamedi-hagh, Yasin Bastan, Parviz Amiri, "ECP technique based capacitor-less LDO with high PSRR at low frequencies, -89dB PSRR at 1MHz and enhanced transient response," *SMACD 2017*, Pages: 1 4.

- [49] M. Nasrollahpour and S. Hamedi-Hagh, "Fast transient response and high PSRR low drop-out voltage regulator," DCAS 2016, 2016, pp. 1-4, Arligton, TX, USA.

- [50] Boris Murmann, "VLSI Data Conversion Circuits," [Online]. Available: https://www.coursehero.com/file/8386361/ee315b-reader-2012/

- [51] Benwei Xu, Yuan Zhou, Yun Chiu, "A 23mW 24GS/s 6b Time-interleaved hybrid two-step ADC in 28nm CMOS," *VLSI 2016*, pp. 1 2.

- [52] Haideh Khorramabadi, "Analog-Digital Interface Integrated Circuits," [Online]. Available: https://inst.eecs.berkeley.edu/~ee247/fa07/files07/lectures/L21\_f07.pdf

- [53] Samaneh Babayan-Mashhadi, Reza Lotfi, "Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator," *IEEE TVLSI 2014*, Vol. 22, No. 2, pp. 343 – 352.

- [54] Franco Maloberti, "Data Converters," Springer Science & Business Media, 2007.

- [55] Seojin Choi, Seyeon Yoo; Younghyun Lim; Jaehyouk Choi, "A PVT-Robust and Low-Jitter Ring-VCO-Based Injection-Locked Clock Multiplier with a Continuous Frequency-Tracking Loop Using a Replica-Delay Cell and a Dual-Edge Phase Detector," *IEEE Journal of Solid-State Circuits*, Vol. 51, pp. 8, pp. 1878 – 1889, 2016.

- [56] Wei-Sung Chang, Po-Chun Huang, Tai-Cheng Lee, "A Fractional-N Divider-Less Phase-Locked Loop with a Subsampling Phase Detector," *IEEE Journal of Solid-State Circuits*, vol. 49, no. 12, pp. 2964 – 2975, 2014.

- [57] M. Verbeke, P. Rombouts, X. Yin, G. Torfs, "Inverse Alexander phase detector," *Electronics Letters*, vol. 52, no. 23, pp. 1908 1910, 2016.

- [58] Dongil Lee, Taeho Lee, Young-Ju Kim, Lee-Sup Kim, "A 21%-Jitter-Improved Self-Aligned Dividerless Injection-Locked PLL With a VCO Control Voltage Ripple-Compensated Phase Detector," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 63, no. 8, pp. 733 – 737, 2016.

- [59] Maxim Integrated Circuits, "INL/DNL Measurements for High-Speed Analog-to-Digital Converters (ADCs)," [Online]. Available: https://www.maximintegrated.com/en/app-notes/index.mvp/id/283.

- [60] Maxim Integrated Circuits, "Defining and Testing Dynamic Parameters in High-Speed ADCs, Part 1," [Online]. Available: https://www.maximintegrated.com/en/app-notes/index.mvp/id/728.

- [61] Maxim Integrated Circuits, "Dynamic Testing of High-Speed ADCs, Part 2," [Online]. Available: https://www.maximintegrated.com/en/appnotes/index.mvp/id/729.

- [62] B. Murmann, "ADC Performance Survey 1997-2016," [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

- [63] R. H. Walden, "Analog-to-digital converter survey and analysis," *IEEE Journal on Selected Areas in Communications*, vol. 17, no. 4, pp. 539 550, 1999.

- [64] Jong-In Kim, Dong-Ryeol Oh, Dong-Shin Jo, Ba-Ro-Saim Sung, Seung-Tak Ryu, "A 65 nm CMOS 7b 2 GS/s 20.7 mW Flash ADC With Cascaded Latch Interpolation," *IEEE Journal of Solid-State Circuits*, vol. 50, no. 10, Pages: 2319 - 2330, 2015.

- [65] Jong-In Kim, Ba-Ro-Saim Sung, Wan Kim, Seung-Tak Ryu, "A 6-b 4.1-GS/s Flash ADC With Time-Domain Latch Interpolation in 90-nm CMOS," *IEEE Journal of Solid-State Circuits*, Vol. 48, no. 6, pp. 1429 – 1441, 2013.

- [66] Mohammad Chahardori, Mohammad Sharifkhani, Sirus Sadughi, "A 4-Bit, 1.6 GS/s Low Power Flash ADC, Based on Offset Calibration and Segmentation," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 60, no. 9, pp. 2285 – 2297, 2013.

- [67] J. Pernillo and M. Flynn, "A 1.5 GS/s Flash ADC with 57.7 dB SFDR and 6.4 bit ENOB in 90 nm digital CMOS," *IEEE Trans. Circuits Syst. II*, vol. 58, no. 12, pp. 837–841, Dec. 2011.

- [68] Y. Nakajima, N. Kato, A. Sakaguchi, T. Ohkido, and T. Miki, "A 7-bit, 1.4 GS/s ADC with offset drift suppression techniques for one-time calibration," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, pp. 1979–1990, Aug. 2013.

- [69] K. Deguchi, N. Suwa, M. Ito, T. Kumamoto, and T. Miki, "A 6-bit 3.5 GS/s 0.9-V 98-mW flash ADC in 90 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 10, pp. 2303–2310, Oct. 2008.

- [70] B. Verbruggen, P. Wambacq, M. Kuijk, and G. Van der Plas, "A 7.6 mW 1.75 GS/s 5 b flash A/D converter in 90 nm digital CMOS," *Dig. Symp. VLSI Circuits*, 2008, pp. 14–15.

- [71] M. Kijima, K. Ito, K. Kamei, and S. Tsukamoto, "A 6 b 3 GS/s flash ADC with background calibration," *Proc. IEEE Custom Integr. Circuits Conf.*, pp. 283–286, Sep. 2010.

#### Appendix A: Ideal DAC Verilog-A Code

// VerilogA for TIME-BASED-FLASH-ADC, DAC-Ideal, veriloga

`include "constants.vams"

`include "disciplines.vams"

module dac\_5bit\_ideal (vd4, vd3, vd2, vd1, vd0, vout);

electrical vd4, vd3, vd2, vd1, vd0, vout;

parameter real vref = 0.8 from [0:inf);

parameter real trise = 0 from [0:inf);

parameter real tfall = 0 from [0:inf);

parameter real tdel = 0 from [0:inf);

parameter real vtrans = 0.4;

real out\_scaled; // output scaled as fraction of 32

analog begin

out\_scaled = 0;

out\_scaled = out\_scaled + ((V(vd4) > vtrans) ? 16 : 0);

out\_scaled = out\_scaled + ((V(vd3) > vtrans) ? 8 : 0);

out\_scaled = out\_scaled + ((V(vd2) > vtrans) ? 4 : 0);

out\_scaled = out\_scaled + ((V(vd1) > vtrans) ? 2 : 0);

out\_scaled = out\_scaled + ((V(vd0) > vtrans) ? 1 : 0);

V(vout) <+ transition( vref\*out\_scaled/32, tdel, trise, tfall );

end

endmodule

# Appendix B: Thermal-to-Digital Converter Verilog-A Code

// VerilogA for Flash\_ADC, T2D, veriloga

`include "constants.vams"

`include "disciplines.vams"

module T2D(in,clk,in\_e,out\_5Bits,out\_4Bits,B0,B1,B2,B3,B4);

input [1:15] in;

input in\_e, clk;

output out\_4Bits,out\_5Bits,B0,B1,B2,B3,B4;

integer A,B,C,D, E,F,G,H,I, E2,F2,G2,H2;

genvar jc;

electrical [1:15] in;

electrical out\_5Bits,out\_4Bits,in\_e,B0,B1,B2,B3,B4;

electrical clk;

analog begin

@(initial\_step)

begin

A=0;

- // F=0;

- // G=0;

// H=0;

// I=0;

end

@(cross(V(clk)-0.6,+1))

# begin

A = 0; if ( V(in\_e) > 0.6 ) C = 1;

else

$$C = 0;$$

for (jc=1; jc<16; jc=jc+1)

begin

```

if ( V(in[jc]) > 0.6 )

D = 1;

else

D = 0;

A = A + D;

```

end

$$B = A*2 + C;$$

$E = B \% 2;$

$E2 = B / 2;$

F = E2 % 2;

F2 = E2 / 2; G = F2 % 2; G2 = F2 / 2; H = G2 % 2; H2 = G2 / 2;I = H2 % 2;

end

V(out\_5Bits) <+ B;

- V(out\_4Bits) <+ A;

- V(B0) <+ E;

- V(B1) <+ F;

- V(B2) <+ G;

- V(B3) <+ H;

- V(B4) <+ I;

- end // of analog

endmodule

# Appendix C: Thermal-to-Digital Converter Enable Verilog-A code

// VerilogA for mehdi, T2D\_Enable, veriloga

`include "constants.vams"

`include "disciplines.vams"

module T2D\_Enable(in1, in2, out);

input [1:16] in1,in2;

output out;

real A, B, C, D;

genvar jc;

electrical [1:16] in1,in2;

electrical out;

analog begin

@(initial\_step)

begin

A=0;

B=0;

end

A = 0;

B = 0;

for (jc=1; jc<17; jc=jc+1)

begin

else

$$D = 0;$$

$$A = A + D;$$

end

for (jc=1; jc<17; jc=jc+1)

begin

el

$$\mathbf{B}=\mathbf{B}+\mathbf{C};$$

end

begin

if ((

$$A == B$$

) && ( $A != 0$ ))

else

$$V(out) <+ 0;$$

end

end //analog

endmodule

# Appendix D: Dynamic Test Measurement MATLAB Code

clear all

clc data = csvread('1024.csv',1,0); x = data(1:end,1); y = data(1:end,2); %z = abs(y); P = abs(y); %P = (z.^2)/1024; plot(x,abs(P)) N = 5; Power\_Sort = sort((P(2:end)),'descend'); %removing DC bin Sig\_Power = (Power\_Sort(1)) %fin Ext\_Power = (sum(Power\_Sort(2:end))) %measuring the distortion and noise SNDR = 10\*log10(Sig\_Power/Ext\_Power)

SQNR = 6.02\*N+1.76

NFloor = SQNR -  $10*\log 10((2^{10})/2)$

ENOB = (SNDR-1.76)/6.02

SFDR = 10\*log10(Sig\_Power/max(Power\_Sort(2:end)))

$Tot_Power = sum(P(1:end))$