Portland State University

PDXScholar

**Dissertations and Theses**

**Dissertations and Theses**

Summer 7-21-2017

## Synthesis of Linear Reversible Circuits and EXOR-AND-based Circuits for Incompletely Specified Multi-Output Functions

Ben Schaeffer Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons Let us know how access to this document benefits you.

#### **Recommended Citation**

Schaeffer, Ben, "Synthesis of Linear Reversible Circuits and EXOR-AND-based Circuits for Incompletely Specified Multi-Output Functions" (2017). *Dissertations and Theses.* Paper 3783. https://doi.org/10.15760/etd.5667

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact pdxscholar@pdx.edu.

Synthesis of Linear Reversible Circuits and EXOR-AND-based Circuits for Incompletely

Specified Multi-Output Functions

by

Ben Schaeffer

# A dissertation submitted in partial fulfillment of the requirements for the degree of

## Doctor of Philosophy in Electrical and Computing Engineering

### Dissertation Committee: Marek Perkowski, Chair Douglas Hall Steven Bleiler Yih-Chyun Jenq Zeshan Chishti

Portland State University 2017

© 2017 Ben Schaeffer

#### Abstract

At this time the synthesis of reversible circuits for quantum computing is an active area of research. In the most restrictive quantum computing models there are no ancilla lines and the quantum cost, or latency, of performing a reversible form of the AND gate, or Toffoli gate, increases exponentially with the number of input variables. In contrast, the quantum cost of performing any combination of reversible EXOR gates, or CNOT gates, on *n* input variables requires at most  $O(n^2/\log_2 n)$  gates. It was under these conditions that EXOR-AND-EXOR, or EPOE, synthesis was developed.

In this work, the GF(2) logic theory used in EPOE is expanded and the concept of an EXOR-AND product transform is introduced. Because of the generality of this logic theory, it is adapted to EXOR-AND-OR, or SPOE, synthesis. Three heuristic spectral logic synthesis algorithms are introduced, implemented in a program called XAX, and compared with previous work in classical logic circuits of up to 26 inputs. Three linear reversible circuit methods are also introduced and compared with previous work in linear reversible logic circuits of up to 100 inputs.

## Acknowledgments

I would like to thank my advisor Marek Perkowski, the graduate office representative Steven Bleiler, committee members Douglas Hall, Yih-Chyun Jenq, and Zeshan Chishti, and members of the Portland Quantum Logic Group for their time and feedback. I would like to thank Addy Gronquist for his copyediting efforts and work in creating parallel-processing versions of the predecessor to XAX, as well as his conversations with Milena Stanković and Radomir S. Stanković that advanced this work to its present state. They all have my gratitude.

## **Table of Contents**

| Abstract i |                                                                   |      |  |  |  |

|------------|-------------------------------------------------------------------|------|--|--|--|

| Ac         | Acknowledgements ii                                               |      |  |  |  |

| Lis        | List of Tablesv                                                   |      |  |  |  |

| Lis        | List of Figures vii                                               |      |  |  |  |

| 1.         | Introduction                                                      | 1    |  |  |  |

| 2.         | Theory                                                            | 3    |  |  |  |

|            | 2.1 Definitions                                                   | 3    |  |  |  |

|            | 2.2 Theorems                                                      | . 10 |  |  |  |

|            | 2.3 Matrix Inversion                                              | . 11 |  |  |  |

| 3.         | Linear Reversible Circuit Synthesis                               | . 14 |  |  |  |

|            | 3.1 Overview                                                      | . 14 |  |  |  |

|            | 3.2 Subrow Elimination-based Methods for Inverting GF(2) Matrices | . 17 |  |  |  |

|            | 3.3 Alternating Elimination                                       | . 21 |  |  |  |

|            | 3.4 The Multiple CNOT Gate Method                                 | . 24 |  |  |  |

|            | 3.5 Variants of Gauss-Jordan Elimination                          | . 25 |  |  |  |

|            | 3.6 Experimental Results                                          | . 34 |  |  |  |

|            | 3.7 Conclusion                                                    | . 40 |  |  |  |

| 4.         | Linear Reversible Circuit Synthesis                               | . 42 |  |  |  |

|            | 4.1 Overview                                                      | . 42 |  |  |  |

|            | 4.2 Theoretical Comparisons with Other Approaches                 | . 48 |  |  |  |

|            | 4.3 Introduction to XAX                                           | . 49 |  |  |  |

|    | 4.4 XAX EPOE Synthesis of Completely Specified Functions   | . 51 |

|----|------------------------------------------------------------|------|

|    | 4.5 XAX EPOE Synthesis of Incompletely Specified Functions | . 55 |

|    | 4.6 XAX SPOE Synthesis of Incompletely Specified Functions | . 58 |

|    | 4.7 Postprocessing                                         | 61   |

|    | 4.8 Complexity                                             | . 62 |

|    | 4.9 Experimental Results                                   | . 63 |

|    | 4.10 Conclusion                                            | . 77 |

| 5. | Summary                                                    | . 79 |

| Re | ferences                                                   | . 81 |

## List of Tables

| Table 3.1. CNOT gate truth table                                                           | 1 |

|--------------------------------------------------------------------------------------------|---|

| Table 3.2. Comparisons of linear reversible circuit synthesis methods (average CNOT)       |   |

| gates)                                                                                     | 5 |

| Table 3.3. Comparisons of quantum linear reversible circuit synthesis methods (average)    |   |

| quantum gates)                                                                             | 7 |

| Table 3.4. Best performing minimum density subcolumn parameter ( <i>dmin</i> ) frequencies |   |

| corresponding to quantum gate counts produced by the GJCO4 method 40                       | ) |

| Table 4.1. Total gate inputs (#TI) for XAX EPOE and ESPP synthesis of selected MCNC        |   |

| benchmark functions                                                                        | ) |

| Table 4.2. Total gate inputs (#TI) of both XAX EPOE synthesis methods of selected          |   |

| incompletely specified MCNC and Espresso benchmark functions                               | ) |

| Table 4.3. Total CMOS gate inputs (#TI) for EXORCISM4, EXORCISM4 with                      |   |

| quality=16, and XAX EPOE/EPOE with don't cares using multi-output synthesis of             |   |

| selected Espresso benchmark functions72                                                    | 2 |

| Table 4.4. Total CMOS gate inputs (#TI) for XAX EPOE default mode, greedy mode,            |   |

| and random mode syntheses of selected MCNC benchmark functions                             | 3 |

| Table 4.5. Total CMOS gate inputs (#TI) for XAX SPOE default mode, greedy mode,            |   |

| and random mode syntheses of selected MCNC benchmark functions                             | 1 |

| Table 4.6. Literals for XAX SPOE using a single postprocessing stage, SPPk where $k = 0$   |   |

| (SPP0), and Exact SPP synthesis of selected Espresso benchmark functions                   | 5 |

| Table 4.7. Total CMOS gate inputs (#TI) for exact-minimum SOP, XAX SPOE, and |    |

|------------------------------------------------------------------------------|----|

| Exact SPP synthesis of selected Espresso benchmark functions                 | 76 |

| Table 4.8. Total CMOS gate inputs (#TI) for XAX SPOE and ORAX synthesis of   |    |

| selected Espresso benchmark functions                                        | 77 |

## List of Figures

Figure 2.1. The pseudocube matrix corresponding to the pseudoproduct

| $(x_0 \oplus x_1)(x_2 \oplus x_3) \dots$                                                | 5  |

|-----------------------------------------------------------------------------------------|----|

| Figure 3.1. The reversible circuit schematic of the CNOT gate                           | 14 |

| Figure 3.2. The Matrix representation of an adjacent CNOT-down gate                     | 15 |

| Figure 3.3. The GF(2) Gaussian Elimination-based synthesis output of function $M_{F1}$  | 17 |

| Figure 3.4. The "Algorithm 1" synthesis output of function $M_{F1}$ using $m = 2$       | 19 |

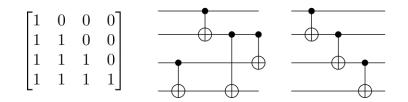

| Figure 3.5. A 4×4 linear function, the corresponding "Algorithm 1" circuit realization  |    |

| (middle), and an exact minimum circuit realization (right)                              | 20 |

| Figure 3.6. A CNOT gate-based circuit and two logically equivalent quantum gate-base    | ed |

| circuits                                                                                | 20 |

| Figure 3.7. The 16-gate, GJCO1 linear reversible circuit realization of the function in |    |

| (13)                                                                                    | 32 |

| Figure 3.8. The 30-gate GJCO1 quantum linear reversible circuit realization of the      |    |

| function in (13)                                                                        | 32 |

| Figure 3.9. The 15-gate, A1CO linear reversible circuit realization of the function in  |    |

| (13)                                                                                    | 33 |

| Figure 3.10. The 35-gate, A1CO quantum linear reversible circuit realization of the     |    |

| function in (13) which contains two redundant gates                                     | 33 |

| Figure 3.11. The 15-gate, A1CO linear reversible circuit realization of the function in |    |

| (13) after gate reordering                                                              | 33 |

| Figure 3.12. The 33-gate, A1CO quantum linear reversible circuit realization of the        |

|--------------------------------------------------------------------------------------------|

| function in (13) after gate reordering                                                     |

| Figure 3.13. The average CNOT gate counts of synthesizing 100 randomized linear            |

| reversible circuits with multiple methods                                                  |

| Figure 3.14. The average quantum gate counts of synthesizing 100 randomized linear         |

| reversible circuits with multiple methods                                                  |

| Figure 4.1. A logic function used to discuss redundant cubes in SOP minimization 42        |

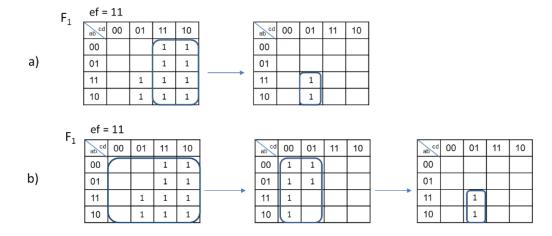

| Figure 4.2. The Karnaugh maps of alternative ESOP syntheses of the function $F_1$ : a) for |

| expression $cef \oplus ac'def$ and b) for expression $ef \oplus c'ef \oplus ac'def$        |

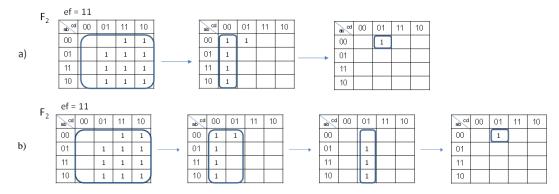

| Figure 4.3. The Karnaugh maps of alternative ESOP syntheses of function $F_2$ : a) for     |

| expression $ef \oplus c'd'ef \oplus a'b'c'def$ and b) for expression                       |

| $ef \oplus c'ef \oplus c'def \oplus a'b'c'def$                                             |

| Figure 4.4. The Karnaugh map and corresponding spectral coefficients of an example         |

| switching function                                                                         |

#### Introduction

A number of different quantum computing architectures, such as quantum dot, scalable ion-trap, and linear optical quantum computing [1, 2], have been proposed and used experimentally. There are many challenges in realizing a quantum computer and it remains an open question which approach will be the most commercially viable. A parallel open question is how best to convert irreversible Boolean functions into a quantum form (or quantum circuit). A commonly used quantum computing model for logic synthesis is one in which ancilla lines are unavailable, the quantum cost or latency of performing a reversible form of the AND gate (known as the multiple-controlled Toffoli gate) increases exponentially with the number of input variables, and the quantum cost of performing a reversible form of the EXOR gate (which is known as the CNOT gate) is one [3]. It was under these conditions that the EXOR-AND-EXOR (or EPOE) logic synthesis methodology presented herein was developed [4]. Specifically, the original goal for EPOE logic synthesis was to realize reversible circuits which would use a minimal number of Toffoli gates at a cost of increasing the number of CNOT gates. This Toffoli-gate-CNOT-gate tradeoff strategy is general and can lead to multi-level logic forms significantly more complicated than the three-level forms presented herein.

In this work the two fundamental problems in EPOE logic synthesis, Linear Reversible Circuit Synthesis and EXOR-AND-based logic synthesis, are covered in separate sections. Previous work on linear reversible circuit synthesis used the Four Russians Method for Inverting a GF(2) matrix to achieve an upper-bound of  $O(n^2/n^2)$

$\log_2 n$  CNOT gates per circuit [5, 6]. Compared to that work, the methods presented herein translate more efficiently into both reversible gates and quantum gates.

The closest previous work to EPOE synthesis was an Exclusive-OR sum of pseudoproducts (or ESPP) approach developed by Ishikawa et al. [7]. Their experiments were limited to circuits of 10 inputs with no synthesis times reported, they had no optimizations for multi-output functions, and they did not make the connection to quantum computing. In contrast there have been many papers on EXOR-AND-OR synthesis formulated as a sum of pseudoproducts (or SPP) which was introduced by Luccio and Pagli [8]. Herein a technology-independent approach to EXOR-AND-based logic synthesis is presented and compared with previous work. For compatibility with reversible circuit notation, the presented EXOR-AND logic synthesis algorithms use a GF(2) linear transform formulation employed in describing error correction codes and logic decomposition by Meinel and Theobald [9], and Günther and Drechsler [10], and Karpovsky, Stanković, and Astola [11]. Comparisons are made between the GF(2) linear transform formulation and the SPP/pseudoproduct formulation in order to bridge these two approaches.

The presented EXOR-AND-based logic synthesis algorithms differ from the majority of logic synthesis algorithms in two fundamental ways. First, they rely on EXOR-AND product transformations in a postprocessing stage to increase similarity across EXOR-AND expressions, and second, they employ a Hadamard transform spectral approach to generate logic expressions. This spectral approach improves the speed of synthesis but at a cost of increased variability in the results compared to other methods.

#### Theory

2.1 Definitions (extending [12])

Previously defined terms relevant to logic synthesis [13, 14, 15, 16] The following conventions are used herein:

- 1. Logical sums are denoted by terms separated by the "V" operator.

- 2. Logical products are denoted by both " $\prod x_i$ " and concatenated expressions.

- 3. Boolean expressions that contain products of Exclusive-OR sums will be expressed in algebraic normal form, e.g., as  $(x_i \oplus 1)(x_j \oplus x_k \oplus 1)$  rather than  $\overline{x}_i(\overline{x}_j \oplus x_k), \overline{x}_i(x_j \oplus \overline{x}_k)$ , or  $\overline{x}_i(\overline{x}_j \oplus x_k)$ .

- 4. Where noted Galois Field 2 (GF(2)) matrix algebra will be used. In GF(2) algebra, values are restricted to either 0 or 1, multiplication is equivalent to logical AND, and addition is modulo two.

A completely specified  $n \times 1$  switching function, or equivalently a two-valued logic function, is a Boolean mapping of the form  $f: \mathbb{B}^n \to \mathbb{B}$ . The *n* input variables of a switching function are specified herein in one of two ways: either as an *n*-bit binary variable in the form  $x_0x_1x_2 \dots x_{n-1}$ , or as an  $n \times 1$  binary vector in the form  $\vec{x} = [x_0, x_1, \dots, x_{n-1}]^T$ . Given a constant  $n \times 1$  binary vector  $\vec{a}$  in the domain of switching function *f*, the expressions  $f \mid_{a_0a_1a_2\dots a_{n-1}} \equiv f(a_0, a_1, a_2, \dots a_{n-1}) \equiv f(\vec{a})$  denote the particular value in the range of *f* to which *f* maps  $\vec{a}$ . When the domain of a switching function *f* is restricted by holding a collection of input variables constant, the restricted

functions will be denoted similarly. For instance, the expressions  $f \mid_{a_0} \equiv f \mid_{x_0=a_0} \equiv$  $f(a_0, x_1, x_2, \dots x_{n-1})$  denote the subfunction of f where  $x_0 = a_0$ ;  $f \mid_{a_0 a_1} \equiv$  $f \mid_{x_0=a_0,x_1=a_1} \equiv f(a_0,a_1,x_2,\dots,x_{n-1})$  denote the subfunction of f where  $x_0 = a_0$  and  $x_1 = a_1$ , etc. In the logic synthesis literature these restricted functions are often called cofactors. The specification of a switching function can be denoted in multiple ways,  $2^n$ such as a vector of binary constants in the form  $[f|_{0...000}, f|_{0...001}, f|_{0...010}, ..., f|_{1...111}]$ , or as a set of all binary vectors  $\vec{x}$  such that  $f(\vec{x}) = 1$ . The latter specification is sometimes referred to as the ON-set of f. Further, a given ON-set can be denoted either as a list of unsigned binary values or as a list of integers via the  $\mathbb{B}^n \to \mathbb{Z}$  mapping  $\vec{x} \to 2^{n-1}x_0 + 2^{n-2}x_1 + 2^{n-3}x_2 \dots + 2^0x_{n-1}$ . The OFF-set of f is the Boolean complement in the domain of f of the ON-set for f, i.e., the set of all  $\vec{x}$  such that  $f(\vec{x}) = 0$ .

In an *incompletely specified switching function*, binary vectors in the domain of a switching function belong to either the *ON-set* of f, the *OFF-set* of f, or the *don't-care set* (*DC-set*) of f which is the set of all binary vectors  $\vec{x}$  for which  $f(\vec{x}) = 0$  or  $f(\vec{x}) = 1$  is acceptable. Each of these sets can be represented as an independent switching function, i.e.,  $f_{ON}$ ,  $f_{OFF}$ , and  $f_{DC}$ .

Given the  $n \times 1$  switching function f, we define the following:

The expression |f| denotes the number of elements in the ON-set of f.

A *literal*  $l_i$  is an input variable in either direct or negated form, e.g.,  $l_i$  where  $l_i \in \{\overline{x_i}, x_i\}$ .

A *minterm* is a product of exactly *n* literals in which each input variable appears precisely once, e.g.,  $\prod_{i=0}^{n-1} l_i$  where  $l_i \in \{\overline{x_i}, x_i\}$ . A minterm can be regarded either as a *lminterm* when  $f_{ON}(l_0, l_1, l_2, ..., l_{n-1}) = 1$ , or a *0-minterm* when  $f_{OFF}(l_0, l_1, l_2, ..., l_{n-1}) =$ 1, or a *DC-minterm* when  $f_{DC}(l_0, l_1, l_2, ..., l_{n-1}) = 1$ .

A *cube* is either the Boolean value 1, a single literal, or the product of two or more literals, e.g.,  $c = \prod_{i=0}^{n-1} m_i$  where  $m_i \in \{\overline{x_i}, x_i, 1\}$ . The cubes  $c_0$  and  $c_1$  are *disjoint* when  $c_0c_1 = 0$  for all  $\vec{x}$ , otherwise they *intersect* each other.

A sum of products (SOP) expression for the function f is a logical sum of cubes which corresponds to the ON-set of f.

The *canonical* SOP expression for the function f is the logical sum of unique minterms which corresponds to the ON-set of f. For example, the canonical SOP expression for the  $3 \times 1$  function  $f_1 = x_0 x_1 \vee x_2$  is  $\overline{x}_0 \overline{x}_1 x_2 \vee \overline{x}_0 x_1 x_2 \vee x_0 \overline{x}_1 x_2$ .

A *disjoint sum of products* (DSOP) expression for the function f is an SOP expression which is comprised of disjoint cubes. Note that all canonical SOP expressions are DSOP expressions. An advantage of DSOP expressions is that they can be treated flexibly as SOP expressions or ESOP expressions.

Figure 2.1. The pseudocube matrix corresponding to the pseudoproduct

$$(x_0 \oplus x_1)(x_2 \oplus x_3)$$

Previously Luccio and Pagli defined the terms pseudocube and canonical expression of a pseudocube or *pseudoproduct*, [8] which are summarized here briefly. A pseudoproduct such as  $(x_0 \oplus x_1)(x_2 \oplus x_3)$  is a product of Exclusive-OR sums of literals (or equivalently a product of EXOR-factors) which is algorithmically constructed from a specific type of matrix of minterms called a pseudocube. A pseudoproduct expression will be either 1, an Exclusive-OR sum of one or more literals, or a product in which each factor is either a literal or an Exclusive-OR sum of literals for which the number of literals is bounded. Specifically, in pseudoproduct expressions consisting of p EXORfactors, the maximum number of literals in each EXOR-factor is n - p + 1. Further, a pseudocube is a binary encoded matrix representation of  $2^k$  minterms, where  $0 \le k \le n$ , that satisfies the following requirements: all rows are unique; all rows are sorted in ascending order; the entries in each column are either all 0, all 1, or half 0's and half 1's; and, the upper half of each column is equal to either the lower half of the same column or the Boolean complement of the lower half of the same column. Further, these requirements must continue to hold for all submatrices created from recursively dividing a pseudocube matrix into two submatrices corresponding to its upper-half rows and lower-half rows. For example, the pseudoproduct  $(x_0 \oplus x_1)(x_2 \oplus x_3)$  will be constructed from the pseudocube matrix in Figure 2.1.

In its verb form the term *cover* denotes either an expression representing an entire function or an inclusion relationship. With regard to the latter, an example would be as

follows: given the cubes  $c_1 = x_0 x_1$  and  $c_2 = x_0 x_1 x_2$ , since  $c_1$  covers  $c_2$  it follows that  $c_1 c_2 = c_2$ . Conversely  $c_2$  is an *implicant* of  $c_1$ .

Given the two nonzero switching functions  $f_1$  and  $f_2$ , we define the following:

The function  $f_1$  approximately covers or fractionally covers  $f_2$  when the ON-set of  $f_2$  is not a subset of the ON-set of  $f_1$  and  $|f_1f_2| \neq 0$ . Here it follows that  $|f_1f_2| < |f_2|$ . For example, the function  $f_1 = x_0x_1 \lor x_2$  approximately covers the function  $f_2 = x_0$ . Conversely the function  $f_2$  is an *approximate implicant* of the function  $f_1$ .

An approximate cover criterion or fractional cover criterion is a real number between  $\frac{1}{2}$  and 1, typically denoted as w, used in the approximate covering criterion equation  $|f_1f_2| > w \times |f_2|$ . For example, given w = 0.57 and the  $3 \times 1$  functions  $f_1 = x_0x_1 \vee x_2$  and  $f_2 = x_0$ , the equation  $3 > 0.57 \times 4$  holds and therefore  $f_2$  is an acceptable approximate implicant of  $f_1$ . The approximate covering criteria equation for incompletely specified switching functions is  $|f_1^{ON}f_2| > w \times |(f_1^{ON} \vee f_1^{OFF})f_2|$ ; i.e., minterms in  $f_1^{DC}$  are excluded from consideration.

The Hadamard transform, or Walsh-Hadamard transform, is a self-inverse spectral transform which herein is used to perform the  $\mathbb{Z}^n \to \mathbb{Z}^n$  mapping: multiplication of an input vector of length  $2^n$  with the matrix  $(\frac{1}{2})^{n/2} \bigotimes_{1}^{n} H_i$  where  $H_1 = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix}$ . For convenience, elements of this input vector will be restricted to  $\{0,1\}$  and the scalar  $(\frac{1}{2})^{n/2}$  will be omitted; consequently a correcting scalar of  $(\frac{1}{2})^n$  must be used when computing inverses.

Given an invertible GF(2)  $n \times n$  matrix M, an input vector  $\vec{x} = [x_0, x_1, x_2, ..., x_{n-1}]^T$ , a constant vector  $\vec{b} = [b_0, b_1, ..., b_{n-1}]^T$ , and the output vector  $\vec{7}$

$\vec{y} = [y_0, y_1, y_2, ..., y_{n-1}]^T$ , when  $\vec{b} = [0, ..., 0, 0, 0]^T$  the mapping  $\vec{y} = M\vec{x} + \vec{b}$  denotes a GF(2) *linearly transformed vector* or a *linear transform* of  $\vec{x}$ . When  $\vec{b}$  can take any constant value the mapping  $\vec{y} = M\vec{x} + \vec{b}$  denotes a GF(2) *affine-linearly transformed vector* or an *affine-linear transform* of  $\vec{x}$ . In these transforms the matrix M is restricted to invertible matrices, thus preventing elements of  $\vec{y}$  from attaining values such as  $0x_0$ ,  $x_1x_1, \overline{x}_1x_1$ , and  $x_0(x_0 \oplus x_1 \oplus 1)x_1$ .

The above transformations can be extended to switching functions. For example, linearly transforming all elements of a function's ON-set, OFF-set, and DC-set into a transformed ON-set, transformed OFF-set, and transformed DC-set creates a linearly transformed function.

A product of Exclusive-OR sums (POE) is a product of two or more unique

elements of  $\vec{y}$ . For example, given  $M = \begin{bmatrix} 1 & 1 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 \end{bmatrix}$ ,  $\vec{b} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$ , and  $\vec{y} = M\vec{x} + \vec{b} =$

$\begin{bmatrix} x_0 \oplus x_1 \\ x_1 \\ x_2 \oplus x_3 \\ x_3 \end{bmatrix}$ , the expression  $y_0 y_2 = (x_0 \oplus x_1)(x_2 \oplus x_3)$  is a POE expression.

A product cube of Exclusive-OR sums (POE cube) is either 1, a component of  $\vec{y}$ , or the product of two or more unique elements of  $\vec{y}$ .

A product minterm of Exclusive-OR sums (POE minterm) is a POE cube that is a product of all *n* elements of  $\vec{y}$ . Further, each element of  $\vec{y}$  may be in negated form.

A sum of products of Exclusive-OR sums (SPOE) expression is a logical sum of POE cubes, e.g.,  $(x_0 \oplus x_1)x_2 \lor (x_0 \oplus x_1)x_3$ . Each POE cube in an SPOE expression may correspond to a different affine-linear transform.

An *Exclusive-OR sum of products of Exclusive-OR sums* (EPOE) expression is an Exclusive-OR sum of POE cubes, e.g.,  $x_0 \oplus x_1 \oplus (x_0 \oplus x_1)(x_2 \oplus 1)(x_3 \oplus 1)$ . Each POE cube in an EPOE expression may correspond to a different affine-linear transform.

A disjoint sum of products of Exclusive-OR sums (DPOE) expression for the function f is an SPOE expression comprised of disjoint POE cubes, e.g.,  $(x_0 \oplus x_1)(x_2 \oplus x_3) \lor (x_0 \oplus x_1)x_2x_3$ .

Given rows  $m_{k,*}$  and  $m_{l,*}$  in matrix M and  $k, l \in \{0,1,2, ..., n-1\}$  such that  $k \neq l$ , elementary row addition over GF(2) is the operation  $m_{k,*} \oplus m_{l,*} \to m_{k,*}$ . Given corresponding vector elements  $b_k$  and  $b_l$  in the vector  $\vec{b}$ , the linear combination complement (LCC) operation is the operation  $m_{k,*} \oplus m_{l,*} \to m_{k,*}, b_k \oplus b_l \oplus 1 \to b_k$ . When applying LCC operations the property  $\prod_{i=0}^{n-1} y_i^{old} = \prod_{i=0}^{n-1} y_i^{new}$  holds. For example, performing the LCC operation  $m_{0,*} \oplus m_{2,*} \to m_{0,*}, b_0 \oplus b_2 \oplus 1 \to b_0$  on the previous

matrix *M* and vector  $\vec{b}$  results in  $M = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 \end{bmatrix}$  and  $\vec{b} = \begin{bmatrix} 1 \\ 0 \\ 0 \\ 0 \end{bmatrix}$ . Further, because of

the Boolean identity  $y_j y_k = y_j (y_j \oplus y_k \oplus 1)$ , it holds that the POE minterm  $(x_0 \oplus x_1) x_1 (x_2 \oplus x_3) x_3$ , associated with the previous  $M\vec{x} + \vec{b}$  expression, is equal to the POE minterm  $(x_0 \oplus x_1 \oplus x_2 \oplus x_3 \oplus 1) x_1 (x_2 \oplus x_3) x_3$ , associated with the resultant  $M\vec{x} + \vec{b}$

expression. *Product transformation* is computation of these equivalent EXOR-AND expressions.

When  $f|_{x_i} = f|_{\overline{x}_i}$  holds for one or more input variables of a switching function, it is known as a *degenerate function*. A degenerate function can be linearly transformed, and the linearly transformed function may or may not be degenerate. Conversely Bernasconi et al. define a *k-autosymmetric function* (paraphrasing, using the notation defined herein) as a function which can be linearly transformed into a new function consisting of n - k input variables which are elements of  $\vec{y}$  [17, 18]. Alternatively this new function can be viewed as an *n*-input function which is degenerate in *k* input variables.

#### 2.2 Theorems

**Theorem 1.** Given the three unique forms of the POE expression  $c = y_k y_l =$  $y_k(y_k \oplus y_l \oplus 1) = (y_k \oplus y_l \oplus 1)y_l$  where the number of input variables n is evenly divisible by three, the number of input variables appearing in the first EXOR factor of cadded to the number of input variables appearing in the second EXOR factor of c is at most  $\frac{4}{3}n$  in at least one of three unique forms. **Proof.** Let r denote the number of input variables in the vector component  $y_k$ . Considering the number of input variables in the vector component expression  $y_k \oplus y_l$ the equation and  $y_1$  $Min(variables(y_l), variables(y_k \oplus y_l))$  reaches a maximum when  $y_l$  and  $y_k \oplus y_l$  both consist of n-r input variables not appearing in  $y_k$  plus  $\frac{1}{2}r$  input variables shared with  $y_k$ . As a result, the number of input variables is  $h_1(r) = r + \left(n - r + \frac{1}{2}r\right) = n + \frac{1}{2}r$  for the forms  $y_k y_l$  and  $y_k (y_k \oplus y_l \oplus 1)$ ; the number of input variables is  $h_2(r) = 2 \times (n - r + \frac{1}{2}r) = 2n - r$  for the form  $(y_k \oplus y_l \oplus 1)y_l$ . The equation  $Min(h_1, h_2)$  reaches a maximum when  $r = \frac{2}{3}n$ ; therefore the number of input variables is at most  $n + \frac{1}{2} \times \frac{2}{3}n = \frac{4}{3}n$  in one of the three unique forms.

*Example.* Let n = 6,  $y_k = x_0 \oplus x_1 \oplus x_2 \oplus x_3 \oplus 1$ , and  $y_l = x_1 \oplus x_2 \oplus x_3 \oplus x_4 \oplus x_5$ . The POE expression  $y_k y_l$  collectively has nine input variables, which is greater than  $\frac{4}{3}6=8$ . From Theorem 1 at least one of the alternative POE expression forms of  $y_k y_l$  will not exceed eight input variables. The form  $y_k(y_k \oplus y_l \oplus 1)$ , which collectively has seven input variables, is the most compact form.

#### 2.3 Matrix Inversion

Given an invertible matrix  $M_F$  consisting of real entries, Gaussian Elimination computes  $M_F^{-1}$  as the product of three types of elementary row operation matrices: those which scale a row, those which swap two rows, and those which either add one row to or subtract one row from another row. Performing each elementary row operation creates a new remainder matrix as shown in (1). As these remainder matrices evolve they typically become sparser and increasingly similar to the identity matrix. An inverse matrix decomposition produced by Gaussian Elimination can be used to solve for the original function as in (2).

$$M_k \dots (M_3(M_2(M_1M_F))) = I$$

(1)

$$M_F = M_1^{-1}M_2^{-1}M_3^{-1}\dots M_k^{-1}$$

(2)

In the typical application of Gaussian Elimination on real-valued matrices, elementary row operations are employed first to solve for an upper triangle matrix and then to solve for the identity matrix. This two-phase process can be visualized as solving lower-triangle matrix entries from the left-most column to the right-most column, then solving upper-triangle entries from the right-most column to the left-most column. The entries in a column are individually processed through elementary row operations called forward substitution and backward elimination. When elementary row operations are employed, forward substitution is defined as the operation  $row_i + row_i \rightarrow row_i$  given that matrix entry  $a_{ii}$  is zero and  $a_{ji}$  is nonzero, and backward elimination is defined as the operation  $row_i - row_i \rightarrow row_i$  given that matrix entry  $a_{ii}$  is nonzero and  $a_{ii} = a_{ii}$ . Gaussian Elimination can also be performed with elementary column operations. When elementary column operations are employed, forward substitution is defined as the operation  $column_i$ +  $column_i \rightarrow column_i$  given that matrix entry  $a_{ii}$  is zero and  $a_{ij}$  is nonzero, and backward elimination is defined as the operation  $column_i - column_i \rightarrow column_i$  given that matrix entry  $a_{ii}$  is nonzero and  $a_{ij} = a_{ii}$ . In the first phase of Gaussian Elimination, solving for a lower triangle matrix could be performed using either elementary row or elementary column operations.

A GF(2) variant of Gaussian Elimination can be used to compute the inverse of an invertible Boolean matrix. In GF(2) Gaussian Elimination, matrix multiplication and addition operations become vector-based AND and EXOR operations. Considering elementary row operations with GF(2) matrices, there is no operation analogous to scaling a row, nor is there a difference between row subtraction operations and row

addition operations. Two rows can be swapped via three modulo-2 (i.e., EXOR) row addition operations. Consequently GF(2) Gaussian Elimination can be performed by using only elementary row addition operations. Because GF(2) elementary row addition operations are self-inverse, any GF(2) function inverse decomposition can be simplified as follows.

$$M_F = M_1^{-1} M_2^{-1} M_3^{-1} \dots M_k^{-1} = M_1 M_2 M_3 \dots M_k$$

(3)

### 3

#### Linear Reversible Circuit Synthesis

3.1 Overview

Expanding [20, 21],

... reversibility in a gate or circuit means that the gate or circuit implements a bijective correspondence between the input and output sets. In particular, the two-input, two-output controlled-NOT (CNOT) gate, illustrated in Figure 3.1 and defined in Table 3.1, does precisely this for the exclusive or (EXOR) operation. When the implemented correspondence is in fact linear, then the implementing gate or circuit is defined as a linear reversible gate or circuit. Note that linear reversible circuits form a natural subclass of the class of reversible circuits.

$$\begin{array}{ccc} Input & Output \\ D_1 = x_1 & & \\ D_2 = x_2 & & \\ \end{array} \begin{array}{c} D_2 = x_1 \\ D_2 = x_1 \oplus x_2 \end{array}$$

Figure 3.1. The reversible circuit schematic of the CNOT gate.

Table 3.1. CNOT gate truth table.

| Input                 |   | Output |       |  |

|-----------------------|---|--------|-------|--|

| <b>D</b> <sub>1</sub> | D | $D_1$  | $D_2$ |  |

| 0                     | 0 | 0      | 0     |  |

| 0                     | 1 | 0      | 1     |  |

| 1                     | 0 | 1      | 1     |  |

| 1                     | 1 | 1      | 0     |  |

When primitive swap gates are unavailable, linear reversible circuits can be GF(2) synthesized solely from CNOT gates which will be the treatment herein. Moreover, linear reversible circuits often play a bridging role in more complex reversible circuits. For 14

example, linear reversible circuits can realize permutation functions or can prepare affine-linear functions used on the control lines of a Toffoli gate.

Given a Boolean input vector  $\vec{x}$  of length *n*, an invertible GF(2) matrix *M* of dimension  $n \times n$ , and Boolean output vector  $\vec{y}$  of length n, the general equation for Boolean linear reversible functions is  $\vec{y} = M\vec{x}$ . The matrix M represents the GF(2) linear function to be performed by a linear reversible circuit, with each row of M corresponding to a reversible circuit line whose output value is the EXOR sum of corresponding input variables. For instance, the *GF*(2) product of the input vector  $\vec{x} = [x_1, x_2, ..., x_n]^T$  and the matrix in Figure 3.2 is  $\vec{y} = [x_1, x_1 \oplus x_2, x_3, x_4, ..., x_n]^T$ . This matrix is an example of an elementary row addition matrix. Elementary row addition matrices are similar to the identity matrix except that they contain one off-diagonal entry with a value of 1. Each elementary row addition matrix synthesizes to one CNOT gate with a control value equal to the column of the off-diagonal entry and a target value equal to the row of the offdiagonal entry. Multiplication with the matrix in Figure 3.2 performs the elementary row addition operation  $Row_1 \oplus Row_2 \rightarrow Row_2$ ; this matrix is synthesized as a CNOT gate with a control line of one and a target line of two. For convenience this type of gate will be referred to as an adjacent CNOT-down gate, and if the control line is immediately below the target line it will be referred to as an adjacent CNOT-up gate.

|   | 0                |                                                                             |                                                                                                       | 0                                                    |

|---|------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1 | 0                | 0                                                                           | •••                                                                                                   | 0 \                                                  |

| 0 | 1                | 0                                                                           | •••                                                                                                   | 0                                                    |

| 0 | 0                | 1                                                                           | •••                                                                                                   | 0                                                    |

| : | :                | :                                                                           | ٠.                                                                                                    | :                                                    |

| 0 | 0                | 0                                                                           |                                                                                                       | 1/                                                   |

|   | 1<br>0<br>0<br>: | $\begin{array}{ccc} 1 & 0 \\ 0 & 1 \\ 0 & 0 \\ \vdots & \vdots \end{array}$ | $\begin{array}{cccccccc} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \\ \vdots & \vdots & \vdots \end{array}$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

Figure 3.2. The matrix representation of an adjacent CNOT-down gate.

When elementary row operations are restricted to modulo-2 row addition, Gaussian Elimination can be adapted to synthesize linear reversible circuits over GF(2). As Gaussian Elimination of a function evolves, synthesis is performed by converting each modulo-2 row addition to an ordered pair representing CNOT gate control and target values. These values are stored in an output-side CNOT gate list, as applying the CNOT gate list to a reversible circuit in forward order executes the linear reversible function  $M^{-1}$ . Applying a Gaussian Elimination-generated CNOT gate list to a reversible circuit in reverse order executes the linear reversible function M.

Alternative syntheses can be generated several ways. In the typical case where  $M^{-1} \neq M$ ,  $M^{-1}$  can be synthesized to an input-side CNOT gate list which may be shorter than the original. Similarly, alternative syntheses can be generated from the transposed matrix  $M^{T}$  and its inverse. Due to the linear algebra property  $(AB)^{T} = B^{T}A^{T}$ , a CNOT gate list resulting from transposed matrix synthesis must have the target and control values of each gate swapped before it can be used [6].

Each elementary row addition operation is denoted as CNOT(*control*, *target*) where *control* =  $row_{modifying}$  and  $target = row_{modified}$  for each  $M_i$ . For example, in (4) the matrix  $M_{F1}$  represents the function  $f([a, b, c, d]^T) = [a, a \oplus b, a \oplus b \oplus c, d]^T$ ; Gaussian Elimination generates the CNOT gate list CNOT(1, 2), CNOT(1, 3), and CNOT(2, 3).

$$M_{F1} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}, M_{F1}^{-1} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

(4)

Figure 3.3. The GF(2) Gaussian Elimination-based synthesis output of function  $M_{F1}$ .

Performing GF(2) Gaussian Elimination with elementary column operations leads to the decomposition in (5) and (6). In this case GF(2) Gaussian Elimination generates a CNOT gate list from input to output, with each elementary column operation corresponding to a CNOT(*control*, *target*) gate where *control* = *column*<sub>modified</sub> and *target* = *column*<sub>modifying</sub> for each  $M_i$ . Under the convention that rows are processed from bottom to top in the first phase, column operation-based Gaussian Elimination of  $M_{F1}$  synthesizes the gates CNOT(2, 3), CNOT(1, 3), and CNOT(1, 2). While this resulting gate list is identical to the prior list produced with row operations, the list will typically be different in larger and more complicated functions.

$$(((M_F M_1) M_2) M_3) \dots M_k = I \quad (5)$$

$$M_F = M_k^{-1} \dots M_3^{-1} M_2^{-1} M_1^{-1} = M_k \ \dots M_3 \ M_2 \ M_1 \quad (6)$$

3.2 Subrow Elimination-based Methods for Inverting GF(2) Matrices

The Four Russians Method for inverting a GF(2) matrix (4RMI) [5] and its related linear reversible circuit synthesis method "Algorithm 1" [6] are variants of GF(2) Gaussian Elimination. While GF(2) Gaussian Elimination iteratively processes entries in a single column, 4RMI and "Algorithm 1" use *subrow elimination* to iteratively process entries in *m* adjacent columns. In our implementation of "Algorithm 1" the subrow width variable *m* is computed as  $[\frac{1}{2}log_2n + \frac{1}{2}]$ . As a result *m* tends to have small values such as two, three, or, when synthesising linear reversible circuits with 128 through 511 lines, four. The key idea "Algorithm 1" inherits from 4RMI is that equivalent subrows are guaranteed to occur whenever  $2^m < n - i + 1$ , given that elementary row operations are used and the left-most unprocessed lower-triangle entries are in the range  $a_{ii}$  through  $a_{ni}$ . For dense matrices where  $2^{m+1} < n - i + 1$  frequently holds, it is likely that the majority of elementary row operations needed to process *m* adjacent columns can be performed in one O(n) pass. This leaves each column except the last with an O(1) forward substitution and all columns with  $O(log_2n)$  backward eliminations. These substitution and elimination operations can be performed via GF(2) Gaussian Elimination or a table lookup when *m* is small.

The "Algorithm 1" method uses a strategy of iteratively processing n/m sets of m adjacent columns to achieve an upper-triangle matrix, transposing the matrix, and again iteratively processing m columns to achieve an identity matrix. The corresponding linear reversible circuit is synthesized from the function decomposition derived in (7), (8), and (9).

$$M_{k} \dots (M_{j+3}(M_{j+2}(M_{j+1}(M_{j}\dots(M_{3}(M_{2}(M_{1}M_{F}))))^{T})))) = I \quad (7)$$

$$M_{F} = M_{1}^{-1}M_{2}^{-1}M_{3}^{-1}\dots M_{j}^{-1}(M_{k}^{-1})^{T}\dots(M_{j+3}^{-1})^{T}(M_{j+2}^{-1})^{T}(M_{j+1}^{-1})^{T} \quad (8)$$

$$M_{F} = M_{1} M_{2} M_{3} \dots M_{j} M_{k}^{T}M_{k-1}^{T}M_{k-2}^{T}\dots M_{j+3}^{T}M_{j+2}^{T}M_{j+1}^{T} \quad (9)$$

In "Algorithm 1" subrow elimination, operations are performed through a table with  $2^m$  entries. This table operates similarly to the tag storage component of a direct-mapped cache, with each entry consisting of either an *INVALID* marker or a valid row index. The table position of each valid row index is computed by treating each corresponding subrow as an *m*-bit number. Because zero subrows are treated as solved, it

is unnecessary to have or use table index 0. Subrow elimination is performed on each column by first setting all table entries to *INVALID*, then processing subrows  $[a_{(i, i)}, a_{(i, i + 1)}, a_{(i, i + 2), \dots}, a_{(i, i + m - 1)}]$  through  $[a_{(n, i)}, a_{(n, i + 1)}, a_{(n, i + 2), \dots}, a_{(n, i + m - 1)}]$  as follows:

```

For each j from i to n

If table_entry[a<sub>(j, i)</sub>, a<sub>(j, i + 1)</sub>, a<sub>(j, i + 2)</sub>, ... a<sub>(j, i + m - 1)</sub>] = INVALID

table_entry[a<sub>(j, i)</sub>, a<sub>(j, i + 1)</sub>, a<sub>(j, i + 2)</sub>, ... a<sub>(j, i + m - 1)</sub>] := j

Else

CNOT(table_entry[a<sub>(j, i)</sub>, a<sub>(j, i + 1)</sub>, a<sub>(j, i + 2)</sub>, ... a<sub>(j, i + m - 1)</sub>], j)

```

Performing "Algorithm 1" on function  $M_{F1}$  using m = 2 results in  $row_1$  being stored in the table,  $row_2$  being stored in the table, a subrow elimination with  $row_2$ modifying  $row_3$ , and a backward elimination with  $row_1$  modifying  $row_2$ . This yields the linear reversible circuit shown in Figure 3.4, going from output toward input, a CNOT(2, 3) gate and a CNOT(1, 2) gate.

Figure 3.4. The "Algorithm 1" synthesis output of function  $M_{F1}$  using m = 2.

Linear reversible circuit synthesis via Gaussian Elimination has an upper bound of  $O(n^2)$  CNOT gates, which typically is not minimal. Previously Patel, et. al. [6] established that the "Algorithm 1" method has an upper bound of  $O(n^2/\log_2 n)$  CNOT gates. While "Algorithm 1" is "asymptotically optimal up to a multiplicative constant" [6], i.e., bounded, it is too simplistic to find an exact minimum solution to the function  $y = [x_1, x_1 \oplus x_2, x_1 \oplus x_2 \oplus x_3, x_1 \oplus x_2 \oplus x_3 \oplus x_4]^T$  illustrated in Figure 3.5 [22].

Figure 3.5. A 4×4 linear function, the corresponding "Algorithm 1" circuit realization (middle), and an exact minimum circuit realization (right).

As an alternative to "Algorithm 1", three linear reversible circuit synthesis methods are introduced herein: the Alternating Elimination with Cost Minimization method (AECM), the Multiple CNOT Gate method (MCG), and several variants of the Gauss-Jordan Elimination with Column Operations (GJCO) method. Both the AECM and MCG methods were developed to reduce CNOT gate counts in small-sized to medium-sized circuits. The GJCO method was developed to reduce quantum gate counts.

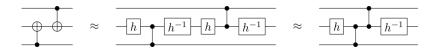

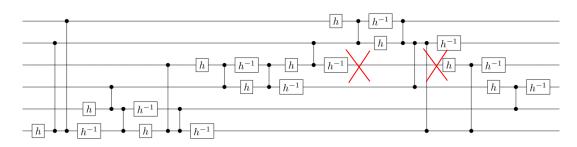

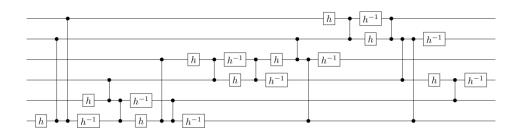

Figure 3.6. A CNOT gate-based circuit and two logically equivalent quantum gate-based circuits.

The mechanism by which the GJCO method reduces quantum gate counts is illustrated in Figure 3.6 and reasoned as follows: In many quantum technologies CNOT gates are implemented by groups of pseudo-Hadamard, controlled-Z, and inverse pseudo-Hadamard gates. When adjacent CNOT gates use the same target lines, pseudoHadamard-inverse/pseudo-Hadamard gate pairs result; these gate pairs can be eliminated from the circuit. Since a series of backward eliminations using column operations synthesizes groups of CNOT gates that use the same target lines, synthesis methods that use column operations are of interest.

In comparison with the "Algorithm 1," the AECM, MCG, and GJCO methods solve rows and columns in a data dependent, nondeterministic order which provides the greatest cost reduction. The main heuristic cost function depends on the GF(2) linear function M and its inverse (10). When synthesis begins, these matrices correspond to the input function specification, and as CNOT gates are synthesized, these matrices correspond to a remainder function more closely resembling the identity matrix. An alternative cost function (11) is based on the sparseness of a matrix and its inverse. The alternative cost function facilitates synthesis of a permutation of an input linear reversible function specification [22].

$$\sum_{i=1}^{n} \sum_{j=i}^{n} \left( \left( M_{(i,j)} \oplus I_{(i,j)} \right) + \left( M_{(i,j)}^{-1} \oplus I_{(i,j)} \right) \right)$$

(10)

$$-2n + \sum_{i=1}^{n} \sum_{j=i}^{n} \left( M_{(i,j)}^{-1} + M_{(i,j)} \right)$$

(11)

#### 3.3 Alternating Elimination

The AECM method is built on the Alternating Elimination method [21]. The Alternating Elimination method extends the Gaussian Elimination approach of forward substitution and backward elimination to iteratively process diagonal entries. Since there are n! possible orderings of diagonal matrix entries, Alternating Elimination can generate

a large number of functionally equivalent circuit solutions which have a range of CNOT gate counts.

Because AECM is based on Alternating Elimination, it will always converge to a solution for any invertible GF(2) matrix given as input [21] and therefore cannot be trapped in a local minimum. The AECM method iteratively compares O(n) matrix diagonalizations and then commits to the diagonalization which produces the greatest cost reduction per CNOT gate ratio. It is possible, though rare, that for one iteration all matrix diagonalizations will result in a negative cost reduction per CNOT gate.

The AECM diagonalization function has four stages: preparation, forward substitution, row-based backward elimination, and column-based backward elimination. In each stage the changes in cost of choosing different CNOT gates are compared. The preparation stage performs preprocessing through an O(n) search to find row and column forward substitutions which reduce cost by two or more. Using a cost reduction of at least two is based on testing which showed that in over half the syntheses examined it produced lower CNOT gate counts than using a cost reduction of at least one or skipping the preprocessing stage. Using a cost reduction of at least three was in some instances superior and in other instances inferior to using at least two. Each CNOT gate synthesized in this stage replaces two or more CNOT gates which would have been synthesized in the third and fourth stages.

If the diagonal matrix entry associated with the current iteration is a 0, then a forward substitution stage is used. In this stage either a row or column forward substitution is chosen through an O(n) search to find the CNOT gate which establishes a

22

1 on the diagonal and results in the lowest-cost remainder function. When it is necessary to perform a forward substitution, a check is made to ensure that the forward substitution CNOT gate was not synthesized in the first stage. This situation is unusual but possible. In these cases the CNOT gate list can be rearranged to detect pairs of identical CNOT gates. Because CNOT gates are self-inverse, all detected identical CNOT gate pairs can be erased.

In the row-based backward elimination stage O(n) eliminations are performed to process column entries which are equal to 1. Unlike Gauss-Jordan Elimination which performs eliminations using the diagonally intersecting row, here each row elimination employs an O(n) search to find the lowest-cost backward elimination operation. Similarly in the column-based backward elimination stage O(n) eliminations are performed to process row entries which are equal to 1, each employing an O(n) search to find the lowest-cost backward elimination operation.

Performing one row or column addition with a cost difference computation takes O(n) time. Therefore the entire AECM diagonalization function takes  $O(n) \cdot (O(n) + O(n) + O(n^2) + O(n^2) \approx O(n^3)$  time. Since the outer AECM loop requires O(n) iterations through O(n) comparisons, the total time is  $O(n) \cdot O(n) \cdot O(n^3) \approx O(n^5)$ .

In order to support partial syntheses the AECM algorithm uses the parameter threshold. Using AECM with threshold = 0 causes a complete synthesis to be performed. Using AECM with larger threshold values causes synthesis to terminate when the cost of the remainder function c1 goes below threshold. In the outermost loop of the algorithm, CNOT gate selection is performed by comparing gain3 with

gain2. These gain values are computed as  $(Cost(f_{k-1}) - Cost(f_k))/(Gates (f_k) - Gates(f_{k-1})))$  for remainder function f at iteration k. The AECM algorithm can be extended to handle occurrences in which these ratios are equal, thus facilitating algorithm extensions such as recursion and probabilistic gate selection.

#### 3.4 The Multiple CNOT Gate Method

The MCG synthesis method synthesizes linear reversible circuits as a collection of linear subfunctions, and each of these subfunctions may correlate to two or more CNOT gates. Subfunction selection is based solely on cost minimization, and consequently the MCG method is completely outside the Gaussian Elimination family of methods. Herein the MCG synthesis method is restricted to two-CNOT-gate subfunctions. This is a practical choice, as larger subfunctions require significant increases in computation time.

The two-CNOT-gate subfunctions can be categorized as one of three types: 1) subfunctions of two elementary row operations corresponding to two CNOT gates synthesized from output toward input; 2) subfunctions of two elementary column operations corresponding to two CNOT gates synthesized from input toward output; 3) subfunctions of one elementary row operation and one elementary column operation representing one CNOT gate synthesized from output toward input and another synthesized from input toward output. The MCG method iteratively compares the cost of applying all possible two-CNOT-gate subfunctions and commits to the pair of CNOT gates which produces the greatest cost reduction. In the event that the cost reaches a local minimum, synthesis temporarily switches to AECM until the cost drops below the local

minimum. In this situation a flag is set indicating that MCG failed to converge and MCG synthesis resumes. In each iteration, MCG retrieves a two-CNOT-gate subfunction from an  $O(n^4)$  length list. Performing elementary row or column operations and cost difference computations on each two-CNOT-gate subfunction requires O(n) time. Since the maximum cost is  $2n^2$ , the smallest cost 0, and the minimum cost reduction is 1 at each iteration, the two-CNOT-gate function search takes at most  $O(n^2)$  outermost loop iterations. Therefore the total time is  $O(n^4) \cdot O(n) \cdot O(n^2) \approx O(n^7)$ .

Like AECM, MCG can be extended to perform more sophisticated gate selections in iterations where multiple minimum-cost alternatives exist. This will be demonstrated later using a probabilistic gate selection. Also, the speed of the MCG algorithm can be improved by using precalculated two-CNOT-gate subfunctions. In the above MCG algorithm all possible CNOT gate sequences are generated, and many will be redundant. For instance, the two-CNOT-gate function CNOT(1, 2) followed by CNOT(3, 4) is equivalent to CNOT(3, 4) followed by CNOT(1, 2). If MCG is extended to use three-CNOT-gate subfunctions, a greater variety of redundant sequences will be generated.

#### 3.5 Variants of Gauss-Jordan Elimination

There are multiple ways to create variants of the Gauss-Jordan Elimination algorithm for linear reversible synthesis. The first variant, named GJCO1, will employ the most rudimentary form of Gauss-Jordan; i.e., performing O(n) iterations of O(1)forward substitutions followed by O(n) backward eliminations. Consequently the GJCO1 method has an upper bound of  $O(n^2)$  CNOT gates. Although it is possible to process matrix rows and columns in any order, for simplicity all Gauss-Jordan Elimination variants will use a convention of processing matrix elements from top to bottom and from left to right.

The remaining Gauss-Jordan Elimination variants introduced herein use combinations of the following seven strategies. A variant of the "Algorithm 1" method which is optimized for quantum linear reversible circuit synthesis will be included for comparison.

Strategies for Quantum Linear Reversible Circuit Synthesis

1. Use elementary column operations. Using elementary column operations with GF(2) Gaussian Elimination may require up to n - 1 column elimination operations per row. This corresponds to the synthesis of up to n - 1 CNOT gates with the same target line per row, minimizing quantum gate counts.

2. Use a Gauss-Jordan Elimination approach for substitution and elimination operations. Gauss-Jordan Elimination-based linear reversible circuit synthesis of parallel circuits was introduced in [23], but herein it will be used in the context of serial circuits. Gauss-Jordan Elimination has the advantage of being a single-phase algorithm and, in linear reversible circuit synthesis using elementary column operations, this creates sequences of up to n - 1 CNOT gates with the same target line being grouped together.

3. Use variable-width subcolumn eliminations before processing each row, searching from the longest possible subcolumns to the shortest subcolumns. This strategy is illustrated using matrix  $M_{F3}$  in (12).

$$M_{F3} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 \\ a_{31} & a_{32} & a_{33} & a_{34} & a_{35} & a_{36} \\ a_{41} & a_{42} & a_{43} & a_{44} & a_{45} & a_{46} \\ a_{51} & a_{52} & a_{53} & a_{54} & a_{55} & a_{56} \\ a_{61} & a_{62} & a_{63} & a_{64} & a_{65} & a_{66} \end{bmatrix}$$

(12)

The first and second rows of  $M_{F3}$  have already been processed and are equal to their corresponding identity matrix rows. Before performing substitution and elimination operations on matrix cell  $a_{33}$ , subcolumn eliminations are performed on equal subcolumns of width four, three, and finally two. The width-four subcolumn searches begin with a comparison of  $[a_{33}, a_{43}, a_{53}, a_{63}]^{T}$  with all subcolumns to the left of the third column,  $[a_{32}, a_{42}, a_{52}, a_{62}]^{T}$  and  $[a_{31}, a_{41}, a_{51}, a_{61}]^{T}$ . If  $[a_{33}, a_{43}, a_{53}, a_{63}]^{T}=[a_{32}, a_{42}, a_{52}, a_{62}]^{T}$  then the subcolumn elimination  $C_2 \bigoplus C_3 \rightarrow C_2$  is performed and the gate CNOT(2, 3) is added to the input-side gate list. Similarly if  $[a_{33}, a_{43}, a_{53}, a_{63}]^{T}=[a_{31}, a_{41}, a_{51}, a_{61}]^{T}$ then the subcolumn elimination  $C_1 \bigoplus C_3 \rightarrow C_1$  is used and the gate CNOT(1, 3) is added to the input-side gate list. Next  $[a_{34}, a_{44}, a_{54}, a_{64}]^{T}$  is compared with all subcolumns to the left of the third column, followed by  $[a_{35}, a_{45}, a_{55}, a_{65}]^{T}$  and  $[a_{36}, a_{46}, a_{56}, a_{66}]^{T}$  using the same comparison. Because a column cannot be equal to any other column in an invertible matrix, at this stage no comparisons are necessary between subcolumns on and to the right of the third column.

The width-three subcolumn searches begin with a comparison of  $[a_{33}, a_{43}, a_{53}]^{T}$  with all subcolumns to the left and right of the third column. Next is a comparison of  $[a_{34}, a_{44}, a_{54}]^{T}$  with all subcolumns to the left of the third column and to the right of the fourth column, then a comparison of  $[a_{35}, a_{45}, a_{55}]^{T}$  with all subcolumns to the left of the third columns to the left of the third columns to the left of the third column and to the right of the fifth column, and lastly a comparison of  $[a_{36}, a_{46}, a_{56}]^{T}$

with all subcolumns to the left of the third column. The width-two subcolumn searches are similar, beginning with a comparison of  $[a_{33}, a_{43}]^T$  with all subcolumns to the left and right of the third column, then a comparison of  $[a_{34}, a_{44}]^T$  with all subcolumns to the left of the third column and to the right of the fourth column, then a comparison of  $[a_{35}, a_{45}]^T$  with all subcolumns to the left of the third column and to the right of the third column and to the right of the third column and to the right of the fourth column and to the right of the fifth column, and lastly a comparison of  $[a_{36}, a_{46}]^T$  with all subcolumns to the left of the third column. In all subcolumn searches only columns on and to the right of the diagonally intersecting column are permitted to modify other columns, thus ensuring solved rows are not disturbed.

There are two qualifying requirements for subcolumns to be considered as acceptable for use in subcolumn elimination. First, the uppermost subcolumn entry must be equal to 1 to avoid disturbing solved columns. Second, the number of entries equal to 1 in a subcolumn must be greater than or equal to a specified minimum subcolumn density parameter (*dmin*). Using a minimum subcolumn density parameter maximizes the effectiveness of isolated subcolumn eliminations. Synthesising the same function with different minimum subcolumn density parameter values can give a range of results depending on the dimensions of the circuit and whether CNOT gate count or quantum gate count is of interest.

The algorithm for variable-width subcolumn elimination is as follows:

//i is the index of the row currently being processed

//M is an n by n linear reversible function

//Arrays use 1-based indexes

//dmin is the minimum subcolumn density parameter

28

```

n := M.columns

IF i = n THEN return

FOR c1 FROM i TO n BY 1

IF (M(i, c1) = 1 AND M.Subcolumn(c1, i, n) has at least

dmin entries = 1) THEN

FOR c2 FROM i - 1 TO 1 BY -1

IF M.Subcolumn(c1, i, n) = M.Subcolumn(c2, i, n) THEN

DoColumnCNOT(M, c1, c2)

r := n - 1 //Second row from bottom index

IF dmin <= 2 THEN

boundaryrow := i

ELSE

boundaryrow := i + dmin - 2

WHILE r > boundaryrow

FOR c1 FROM i TO n BY 1

IF (M(i, c1) = 1 \text{ AND } M.\text{Subcolumn}(c1, i, r) has at least

dmin entries = 1) THEN

FOR c2 FROM i - 1 TO 1 BY -1

IF M.Subcolumn(c1, i, r) = M.Subcolumn(c2, i, r) THEN

DoColumnCNOT(M, c1, c2)

FOR c3 FROM c2 + 1 TO n BY 1

IF M.Subcolumn(c1, i, r) = M.Subcolumn(c3, i, r) THEN

DoColumnCNOT(M, c1, c3)

r := r - 1

```

4. Use a cost minimization approach in subcolumn elimination. During subcolumn elimination, when two or more equivalent subcolumns are discovered on or to the right of a subcolumn being processed, a series of partial syntheses using different column orderings is performed. The partial synthesis with the lowest-cost result is chosen. The cost function in equation (10) is defined as the sum of differences between a given remainder function and the identity matrix added to the sum of differences between the inverse of a given remainder function and the identity matrix. For simplicity and effective quantum gate count minimization, these partial syntheses use one subcolumn to eliminate all equivalent subcolumns. In instances where the subcolumn  $[a_{(i, i)}, a_{(i + 1, i)}, a_{(i + 2, i)}, \dots, a_{(i + m - 1, i)}]^T$  is one of the matching subcolumns, it is used to modify all other columns.

5. Use a cost minimization approach in forward substitution. When multiple columns can be used to perform forward substitution, a partial synthesis is performed using each available column. The partial synthesis works through all elementary row operations for the current row being processed, and then computes the circuit cost. The partial synthesis with the lowest cost is selected.

6. *Use multiple passes*. For the "Algorithm 1" variant which uses column operations, seven syntheses will be performed using subcolumn widths between 2 and 8. For the new Gauss-Jordan Elimination-based methods, seven syntheses will be performed using minimum subcolumn density parameter values between 1 and 7.

7. *Use gate reordering*. Following experimentation, an iterative three-stage gate reordering approach was adopted to postprocess CNOT gate lists from input to output: 1)

when two separate groups of CNOT gates with the same target line are detected, an attempt is made to move the first group toward the output so it is adjacent to the second group; 2) if 1) fails, an attempt is made to move the second, third, fourth,... and *n*th groups of CNOT gates with the same target line toward the input so they are adjacent to the first group; and 3) if 2) fails, an attempt is made to individually relocate each CNOT gate from the second, third, fourth,... and *n*th groups mentioned previously into groups as close to the input as possible. This method is applied *n* times to synthesized CNOT gate lists, once per each possible target line.

The new "Algorithm 1" and Gauss-Jordan Elimination-based methods are organized as follows:

A1CO: employs strategies 1, 6, and 7.

GJCO1: employs strategies 1, 2, and 7.

GJCO2: employs strategies 1, 2, 3, 6, and 7.

GJCO3: employs strategies 1, 2, 3, 4, 6, and 7.

GJCO4: employs strategies 1, 2, 3, 5, 6, and 7.

GJCO5: employs strategies 1, 2, 3, 4, 5, 6, and 7.

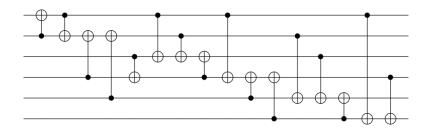

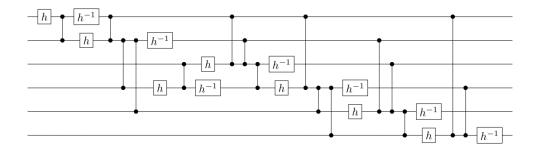

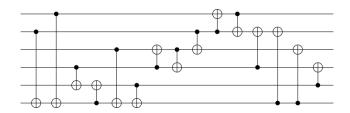

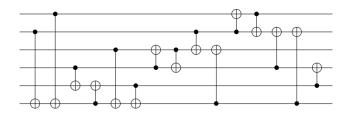

With regard to the last strategy, the function in equation (13) [6] will be used to illustrate gate reordering using GJCO1 and A1CO. The synthesis output of GJCO1 is 16 CNOT gates, shown in Figure 3.7, and 30 quantum gates, shown in Figure 3.8. The synthesis output of A1CO is 15 CNOT gates, shown in Figure 3.9, and 35 quantum gates, shown in Figure 3.10. Gate reordering on the GJCO1 circuit results in no change. After

gate reordering, the A1CO circuit in Figure 3.11 shows the 14<sup>th</sup> CNOT gate has moved to the 10<sup>th</sup> position, resulting in 33 quantum gates in Figure 3.12.

| г1 | 1 | 0 | 0 | 0 | ך0                    |      |

|----|---|---|---|---|-----------------------|------|

| 1  | 0 | 0 | 1 | 1 | 0                     |      |

| 0  | 1 | 0 | 0 | 1 | 0<br>0<br>0<br>1<br>1 | (12) |

| 1  | 1 | 1 | 1 | 1 | 1                     | (13) |

| 1  | 1 | 0 | 1 | 1 | 1                     |      |

| LO | 0 | 1 | 1 | 1 | 01                    |      |

Figure 3.7. The 16-gate, GJCO1 linear reversible circuit realization of the function in

Figure 3.8. The 30-gate GJCO1 quantum linear reversible circuit realization of the

function in (13).

Figure 3.9. The 15-gate, A1CO linear reversible circuit realization of the function in (13).

Figure 3.10. The 35-gate, A1CO quantum linear reversible circuit realization of the

function in (13) which contains two redundant gates.

Figure 3.11. The 15-gate, A1CO linear reversible circuit realization of the function in

(13) after gate reordering.

Figure 3.12. The 33-gate, A1CO quantum linear reversible circuit realization of the

function in (13) after gate reordering.

For comparison the above methods will be tested with probabilistic variants of the AECM method and MCG method, named AECMP and MCGP respectively. In the AECM method and MCG method, whenever there are two or more subfunctions which yield equivalent cost reductions selection defaults to the first subfunction encountered. In the probabilistic variants subfunction selection is random.

### 3.6 Experimental Results

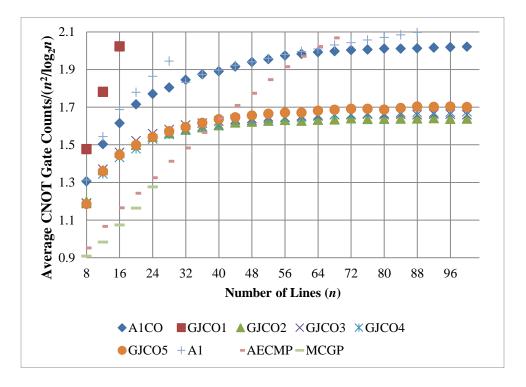

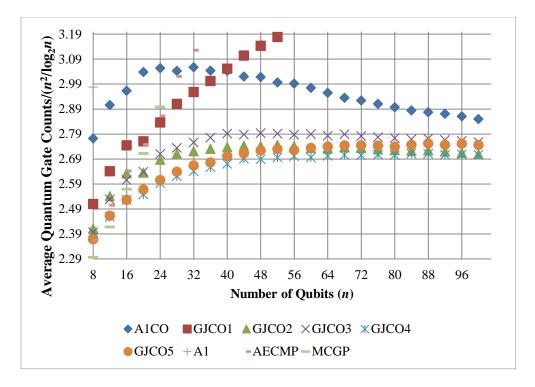

A set of tests similar to that used in [20] was performed on circuits with 8 to 100 lines; each set consisted of synthesising 100 randomized linear reversible circuits with multiple methods. The *n*-line circuit randomization function used  $2n^2$  operations on the identity matrix, and each of these operations represented either a random distant CNOT gate or a random distant SWAP gate. AECMP and MCGP were run seven times per function to attempt to make a more fair comparison with the new methods which used multiple passes. In addition, MCGP testing was restricted to 24 or fewer lines due to long run times and known performance drop-off above this circuit dimension. All results were recorded in terms of both CNOT gate counts and, after gate reordering, quantum gate counts. Compared with the new methods, "Algorithm 1", AECMP, and MCGP were expected to produce lower CNOT gate counts but higher quantum gate counts.

The results for average CNOT gate counts and quantum gate counts are shown in Table 3.2 and Table 3.3 respectively. Figure 3.13 and Figure 3.14 illustrate the best performing methods using a normalized gate count. Examining the new methods in both CNOT gate counts and quantum gate counts, A1CO and GJCO1 performed poorly whereas GJCO2, GJCO3, GJCO4, and GJCO5 performed better. In circuits with more

than 40 lines GJCO2 was the most likely method to find the lowest CNOT gate count. In circuits with more than 16 lines GJCO4 was the most likely method to yield the lowest quantum gate count, although by 100 lines GJCO2 achieved similar performance. Table 3.4 shows the best-performing minimum subcolumn density parameters of GJCO4 for quantum gate counts. As the number of lines increased, GJCO4 performed best with a minimum subcolumn density parameter value of either four or five. Similar results were found in GJCO2, GJCO3, and GJCO5.

The quantum gate count reductions due to gate reordering ranged from 0 to 19.7%. Another benefit of gate reordering was that all pairs of identical CNOT gates that could be placed adjacent to each other were identified and deleted. This is a known issue with AECM-based methods (and indirectly MCG-based methods) [22]. No pairs of identical CNOT gates were discovered in the syntheses of any of the other methods.

Both AECMP and MCGP produced low CNOT gate counts for small circuits but also comparatively low quantum gate counts (following gate reordering) in circuits with 8 through 20 lines. This last result was unanticipated and indicates a possible direction for developing synthesis methods designed specifically for small quantum linear reversible circuits.

Table 3.2. Comparisons of linear reversible circuit synthesis methods (averageCNOT gates).

| Lines | A1CO   | GJCO1  | GJCO2  | GJCO3  | GJCO4  | GJCO5  | A1     | AECMP  | MCGP   |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 8     | 27.87  | 31.5   | 25.56  | 25.39  | 25.33  | 25.29  | 28.01  | 20.3   | 19.38  |

| 12    | 60.37  | 71.55  | 54.83  | 55.02  | 54.03  | 54.57  | 62     | 42.84  | 39.47  |

| 16    | 103.32 | 129.46 | 93.22  | 93.39  | 91.71  | 92.58  | 107.97 | 74.54  | 68.75  |

| 20    | 158.72 | 197.68 | 138.71 | 140.81 | 136.81 | 138.73 | 164.64 | 115    | 107.66 |

| 24    | 222.4  | 286.1  | 193.8  | 195.75 | 192.28 | 193.54 | 234.16 | 166.47 | 160.33 |

| 28    | 294.2  | 391.94 | 254.61 | 257.81 | 253.63 | 256.41 | 317.06 | 230.33 |        |

| 32    | 377.81 | 511.26 | 323.48 | 328.54 | 323.32 | 326.48 | 375.05 | 303.65 |        |

| 36    | 469.87 | 646.85 | 399.24 | 404.76 | 400.27 | 405.09 | 469.57 | 392.37 |        |

| 40    | 568.57 | 799.67 | 482.2  | 488.82 | 481.99 | 491.91 | 570.37 | 493.38 |        |

| 44    | 679.37 | 969.66 | 573.8  | 580.09 | 578.56 | 583.6  | 681.85 | 606.02 |        |

| 48    | 799.93 | 1154.9 | 669.28 | 676.56 | 672.7  | 682.97 | 800.54 | 731.67 |        |

| 52    | 927.36 | 1353.6 | 772.15 | 781.86 | 777.84 | 789.66 | 929.18 | 875.63 |        |

| 56    | 1066   | 1568.9 | 881.05 | 888.81 | 889.43 | 902.11 | 1068.7 | 1033.9 |        |

| 60    | 1208.3 | 1794.9 | 991.91 | 1008.1 | 1003.5 | 1018.4 | 1216.1 | 1200.9 |        |

| 64    | 1360.1 | 2045   | 1114.2 | 1128.7 | 1132.7 | 1147.6 | 1371.4 | 1380.5 |        |

| 68    | 1516.9 | 2312.3 | 1241.5 | 1261.1 | 1260.6 | 1281   | 1542.2 | 1570.8 |        |

| 72    | 1683.4 | 2590.8 | 1378   | 1394.5 | 1397.7 | 1420.8 | 1716.2 | 1790.1 |        |

| 76    | 1854   | 2885.5 | 1512.8 | 1537.8 | 1541.7 | 1563.5 | 1901.4 | 2021.5 |        |

| 80    | 2035.3 | 3202.4 | 1658   | 1680   | 1687.4 | 1708.1 | 2096.3 | 2254.6 |        |

| 84    | 2220   | 3526.6 | 1808.4 | 1835.2 | 1845.3 | 1871.6 | 2300.3 | 2507.9 |        |

| 88    | 2412.8 | 3875   | 1965   | 1990   | 2005.3 | 2042.2 | 2513.7 | 2774.7 |        |

| 92    | 2615.9 | 4230.8 | 2129.2 | 2158   | 2168   | 2208   | 2737.1 | 3057.2 |        |

| 96    | 2825.3 | 4611.8 | 2291.8 | 2326.3 | 2341.3 | 2383.7 | 2971.3 | 3351.4 |        |

Table 3.3. Comparisons of quantum linear reversible circuit synthesis methods (average quantum gates).

| Lines | A1CO   | GJCO1  | GJCO2  | GJCO3  | GJCO4  | GJCO5  | A1     | AECMP  | MCGP   |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 8     | 59.14  | 53.54  | 51.45  | 51.13  | 50.7   | 50.53  | 63.53  | 50.43  | 48.99  |

| 12    | 116.72 | 106.07 | 102.05 | 101.54 | 98.74  | 98.92  | 130.98 | 100.62 | 97.12  |

| 16    | 189.64 | 175.64 | 168.47 | 166.74 | 161.67 | 161.66 | 215.61 | 169.11 | 164.43 |

| 20    | 281.19 | 255.52 | 243.85 | 244.21 | 235.79 | 237.59 | 315.52 | 254.34 | 251    |

| 24    | 383.59 | 356.32 | 337.59 | 340.48 | 325.7  | 327.3  | 433.4  | 359.54 | 364    |

| 28    | 496.23 | 474.62 | 442.07 | 445.96 | 427.4  | 430.34 | 569.82 | 492.64 |        |

| 32    | 626.14 | 605.76 | 557.18 | 564.49 | 540.85 | 545.54 | 697.37 | 640.09 |        |

| 36    | 763.09 | 752.61 | 684.49 | 695.69 | 666.03 | 670.9  | 862.11 | 815.55 |        |

| 40    | 914.68 | 917.49 | 823.1  | 839.15 | 802.75 | 812.27 | 1031.9 | 1016.9 |        |

| 44    | 1071   | 1100.8 | 972.61 | 988.4  | 954.24 | 961.99 | 1223.5 | 1243.6 |        |

| 48    | 1245.2 | 1296.6 | 1131.1 | 1152.2 | 1109.2 | 1123.7 | 1412.4 | 1491.8 |        |

| 52    | 1421.3 | 1507.5 | 1302.5 | 1324   | 1278.8 | 1294.5 | 1629.1 | 1771.8 |        |

| 56    | 1615.6 | 1735.4 | 1480.5 | 1504.9 | 1458.6 | 1471.7 | 1854.8 | 2085.7 |        |

| 60    | 1812.9 | 1973.2 | 1666.1 | 1700.3 | 1643.2 | 1666.4 | 2090.2 | 2416.1 |        |

| 64    | 2017.3 | 2234.6 | 1864.5 | 1899.9 | 1844.9 | 1870.3 | 2334.5 | 2765.1 |        |

| 68    | 2229.1 | 2514.4 | 2078.3 | 2118.2 | 2055.2 | 2084.1 | 2611.1 | 3141.1 |        |

| 72    | 2456.7 | 2805.9 | 2296.8 | 2337.3 | 2272.9 | 2305.9 | 2889.2 | 3576.8 |        |

| 76    | 2690.5 | 3112.2 | 2522   | 2567.6 | 2502.9 | 2535.9 | 3181.6 | 4030   |        |

| 80    | 2932.9 | 3440.4 | 2758.1 | 2807.6 | 2738.2 | 2772.7 | 3477.1 | 4485.9 |        |

| 84    | 3183.9 | 3776.8 | 3005.3 | 3056.6 | 2993.7 | 3031.4 | 3801.1 | 4981.7 |        |

| 88    | 3449.2 | 4136.7 | 3266   | 3322.5 | 3249.8 | 3299.8 | 4133.2 | 5505.1 |        |

37

| 92  | 3724.6 | 4503.7 | 3528.3 | 3589.1 | 3511.1 | 3563.9 | 4471.1 | 6055.5 |

|-----|--------|--------|--------|--------|--------|--------|--------|--------|

| 96  | 4003.6 | 4898.9 | 3799.5 | 3866.3 | 3790.1 | 3850.2 | 4842.6 | 6628.9 |

| 100 | 4289.6 | 5297.4 | 4077   | 4150.4 | 4074   | 4132.6 | 5192.6 | 7217.4 |

Figure 3.13. The average CNOT gate counts of synthesizing 100 randomized linear reversible circuits with multiple methods.

Figure 3.14. The average quantum gate counts of synthesizing 100 randomized linear reversible circuits with multiple methods.

| Lines | dmin=1 | dmin=2 | dmin=3 | dmin=4 | dmin=5 | dmin=6 | dmin=7 |

|-------|--------|--------|--------|--------|--------|--------|--------|

| 8     | 29     | 33     | 19     | 14     | 5      | 0      | 0      |

| 12    | 12     | 21     | 30     | 18     | 12     | 6      | 1      |

| 16    | 0      | 19     | 37     | 20     | 17     | 7      | 0      |

| 20    | 0      | 9      | 25     | 33     | 18     | 15     | 0      |

| 24    | 0      | 3      | 27     | 35     | 20     | 12     | 3      |

| 28    | 0      | 0      | 21     | 47     | 23     | 8      | 1      |

| 32    | 0      | 1      | 13     | 50     | 29     | 6      | 1      |

| 36    | 0      | 0      | 20     | 47     | 28     | 3      | 2      |

| 40    | 0      | 0      | 15     | 47     | 29     | 9      | 0      |

| 44    | 0      | 0      | 7      | 65     | 25     | 2      | 1      |

| 48    | 0      | 0      | 3      | 63     | 33     | 1      | 0      |

| 52    | 0      | 0      | 4      | 64     | 30     | 1      | 1      |

| 56    | 0      | 0      | 6      | 61     | 27     | 6      | 0      |

| 60    | 0      | 0      | 2      | 59     | 34     | 5      | 0      |

| 64    | 0      | 0      | 2      | 55     | 39     | 4      | 0      |

| 68    | 0      | 0      | 2      | 64     | 29     | 5      | 0      |

| 72    | 0      | 0      | 1      | 63     | 35     | 1      | 0      |

| 76    | 0      | 0      | 1      | 66     | 32     | 1      | 0      |

| 80    | 0      | 0      | 0      | 54     | 46     | 0      | 0      |

| 84    | 0      | 0      | 0      | 61     | 37     | 2      | 0      |

| 88    | 0      | 0      | 1      | 63     | 36     | 0      | 0      |

| 92    | 0      | 0      | 0      | 68     | 32     | 0      | 0      |

| 96    | 0      | 0      | 0      | 69     | 31     | 0      | 0      |

| 100   | 0      | 0      | 0      | 60     | 39     | 1      | 0      |

Table 3.4. Best performing minimum density subcolumn parameter (*dmin*) frequencies corresponding to quantum gate counts produced by the GJCO4 method.

## 3.7 Conclusion