#### **University of Windsor**

## Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1-1-1987

# VLSI design of high-speed adders for digital signal processing applications.

Seyfollah Seyfollahi Bazarjani University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Bazarjani, Seyfollah Seyfollahi, "VLSI design of high-speed adders for digital signal processing applications." (1987). *Electronic Theses and Dissertations*. 6804. https://scholar.uwindsor.ca/etd/6804

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

## VLSI DESIGN OF HIGH-SPEED ADDERS

#### DIGITAL SIGNAL PROCESSING APPLICATIONS

by

Seyfollah Seyfollahi Bazarjani

A Thesis

Submitted to the

Faculty of Graduate Studies and Research

through the Department of

Electrical Engineering in Partial Fulfillment

of the requirements for the Degree

of Master of Applied Science at

the University of Windsor

Windsor, Ontario, Canada 1987 UMI Number: EC54793

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform EC54793

Copyright 2010 by ProQuest LLC

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### ABSTRACT :

In work the VLSI design and implementation of arithmetic circuits for digital signal processing applications, using the Residue Number System. investigated. Different techniques for high-speed Binary and RNS arithmetic implementation are discussed. It will high-speed, shown that for high-precision arithmetic computations, pipelined RNS adders offer advantages their binary counterparts. These advantages manifest themselves in throughput rate, latency time. complexity, and testability.

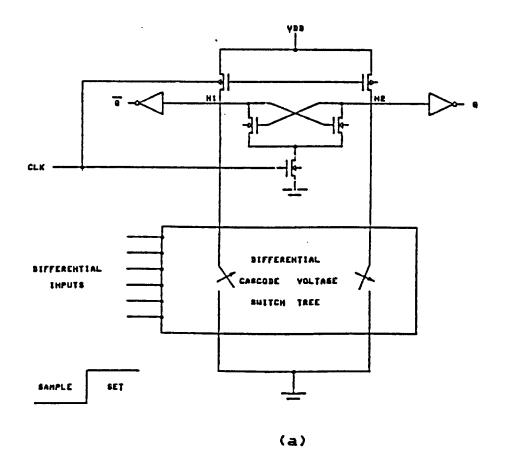

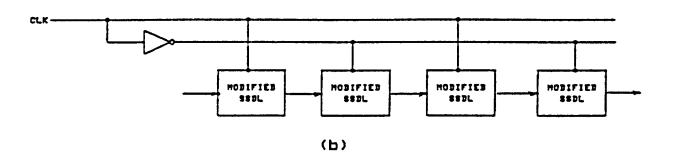

Various CMOS logic families are presented. Charge redistribution problems in DOMINO and DCVSL are addressed and some techniques to alleviate these problems are studied. Delay time analysis of Sample-Set Differential Logic, has not yet appeared in the literature, is described and an analytical expression for the delay time of an SSDL gate is derived. This expression is applied to the delay time optimization of SSDL gates. The application of SSDL in pipelined architectures is presented along with simplification in the circuit design.

#### **ACKNOWLEDGEMENTS**

My Thanks and sincere appreciation is directed especially to Dr. G.A. Julien for his guidance, support and creative suggestions. I am also thankful to Dr. W.C. Miller for his support. I would also like to thank Dr. S. Bandyopadhyay, and Dr. M. Sid-Ahmed for their Assistance.

## TABLE OF CONTENTS

|          | Par                                                                                                                                                                                                                                                                                                                                           | ge                                                     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| ABSTRACT | Г                                                                                                                                                                                                                                                                                                                                             | i v                                                    |

| ACKNOWLE | EDGEMENTS                                                                                                                                                                                                                                                                                                                                     | <b>v</b>                                               |

| LIST OF  | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                 | i×                                                     |

| LIST OF  | APPENDICES xi                                                                                                                                                                                                                                                                                                                                 | ii                                                     |

| CHAPTER  | 1 INTRODUCTION .                                                                                                                                                                                                                                                                                                                              |                                                        |

|          | 1.1 Introduction                                                                                                                                                                                                                                                                                                                              | 1<br>3<br>4<br>4                                       |

| CHAPTER  | 2 LOGICAL DESIGN OF BINARY ARITHMETIC CIRCUITS                                                                                                                                                                                                                                                                                                |                                                        |

|          | 2.3.1 Carry Look-Ahead Adder  2.3.2 Ripple Carry Look-Ahead Adder  2.3.3 First-Order Carry Look-Ahead  Adder  2.3.4 Carry Select Adder  2.4 Parallel Multiplier  2.5 Pipelined Arithmetic  2.5.1 The Concept of Pipeline System  2.5.2 Pipelined Carry Save Adder  2.5.3 Pipelined Ripple-Carry Adder  2.5.4 Pipelined Carry Look-Ahead Adder | 7<br>7<br>13<br>15<br>19<br>22<br>25<br>29<br>29<br>35 |

| CHAPTER  | RNS ADDER  3.1 Introduction                                                                                                                                                                                                                                                                                                                   | 37<br>37                                               |

|          | 3.2 Residue Representation 3.3 Residue Arithmetic                                                                                                                                                                                                                                                                                             | 37<br>41<br>41<br>41<br>43<br>43                       |

|          | <ul><li>3.5 Pipelined Ripple-Carry RNS adder</li><li>3.6 Comparison of the Pipelined Ripple-Carry Binary and RNS Adder</li></ul>                                                                                                                                                                                                              | 46<br>46                                               |

|           |            | 3.6.1 Hardware Complexity 3.6.2 Throughput Rate 3.6.3 Testability 3.6.4 Latency Time Example Summary | 49<br>50<br>51<br>52<br>52<br>53 |

|-----------|------------|------------------------------------------------------------------------------------------------------|----------------------------------|

| CHAPTER 4 | CIRC       | CUIT AND LOGIC DESIGN WITH CMOS                                                                      |                                  |

|           | 4.1<br>4.2 |                                                                                                      | 55<br>55<br>c 56<br>57<br>60     |

|           | •          | 4.2.4 Clocked CMOS Logic                                                                             | 62<br>65<br>71                   |

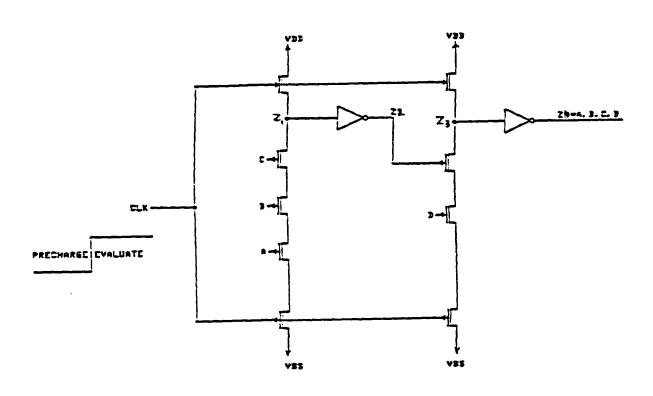

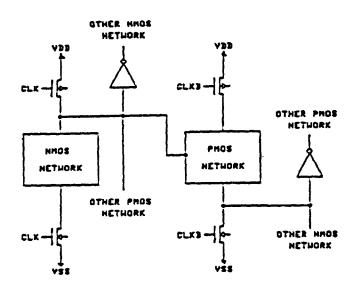

|           |            | √4.2.7 NORA CMOS Logic  (N-P Dynamic Logic)                                                          | 75                               |

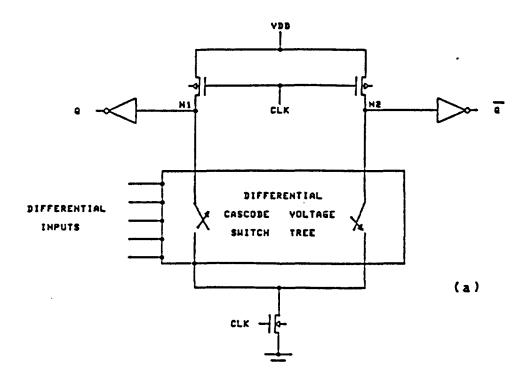

|           |            | Switch Logic (DCVSL)<br>4.2.9 Latched Domino CMOS Logic                                              | 77<br>79                         |

|           |            | 4.2.10 Sample-Set Differential Logic (SSDL)                                                          | 82                               |

|           | 4.3<br>4.4 | Charge Redistribution in Domino CMOS Logic Noise Margin of Domino Gates                              | 84<br>86                         |

|           | 4.5        | Methods of Improving the Charge<br>Sharing Problem In Domino CMOS Gates                              | 87                               |

|           |            | 4.5.1 Control of Layout Dependent Capacitances                                                       | 88                               |

|           |            | 4.5.2 P-Channel Feedback Transistor 4.5.3 Multiple Precharging of                                    | 88                               |

|           | 4          | Internal Nodes                                                                                       | 90<br>90                         |

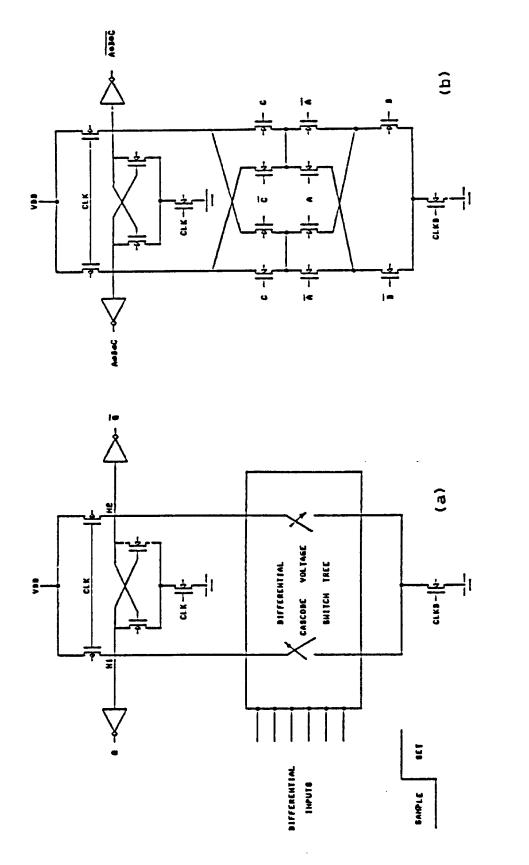

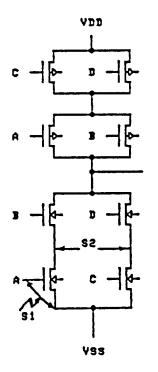

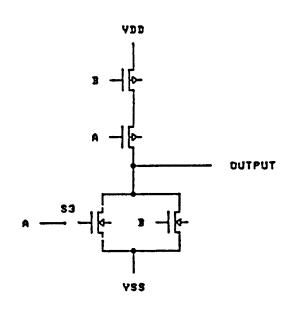

|           | 4.6        | Design of Differential Cascode Voltage Switch Tree                                                   | 93                               |

|           | 4.7        | Analysis and Optimization of the SSDL Gate                                                           | 98                               |

|           |            | 4.7.1 Derivation of the Delay Time 4.7.1.1 Sample Phase                                              | 98<br>100                        |

|           |            | 4.7.2.2 Set Phase 4.7.2 Delay Optimization of the                                                    | 101                              |

|           |            | SSDL Gate                                                                                            | 104<br>105                       |

|           |            | 4.7.3.1 Calculation of D(VN) 4.7.4 Application of SSDL to                                            | 106                              |

|           | 4 0        | Pipelined Architecture                                                                               | 108                              |

|           | 4.8        | Testing                                                                                              | 110<br>110                       |

|           |            | 4.8.2 Design for Testability                                                                         | 111                              |

| CHAPTER 5 | DESIGN AND OPTIMIZATION OF CMOS FULL ADDERS |                   |

|-----------|---------------------------------------------|-------------------|

|           | 5.1 Introduction                            | 115<br>115<br>117 |

|           | Full Adder for Standard Cell Library        | 127               |

|           | 5.4.1 Logic Domain Optimization             | 127               |

|           | 5.4.2 Circuit Domain Optimization           | 127               |

|           | 5.4.2.1 Derivation of the                   |                   |

|           | Delay Time                                  | 128               |

|           | 5.4.2.2 Calculation of the                  | 131               |

|           | Area                                        | 131               |

|           | Different Criteria                          | 131               |

|           | 5.4.3 Layout Domain Optimization            | 132               |

| CHAPTER 6 | SUMMARY AND CONCLUSIONS                     |                   |

|           | 6.1 Summary                                 | 136               |

|           | 6.2 Conclusions                             | 137               |

|           | 6.3 Future Work                             | 138               |

## LIST OF ILLUSTRATIONS

| Truth Table and Block Diagram of Half Adder                                        |

|------------------------------------------------------------------------------------|

| Half Adder (HA) Logic Circuit                                                      |

| Truth Table and Block Diagram of Full Adder                                        |

| Full Adder (FA) Logic Diagram                                                      |

| Controlled Add/Subtract (CAS) Cell                                                 |

| Two's Complement Binary Adder/Subtractor<br>Configuration                          |

| The Functional Block Diagram of a 4-bit Carry Look-Ahead Adder                     |

| The Schematic Logic of 4-bit Carry Look-Ahead Adder<br>Units                       |

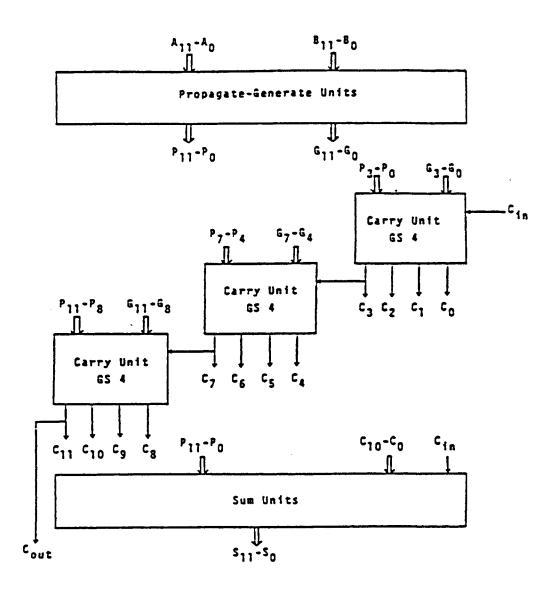

| The Organization of a 12-bit Ripple-Carry Look-<br>Ahead Adder                     |

| The Functional Block Diagram of 12-bit First-Order<br>Carry Look-Ahead Adder       |

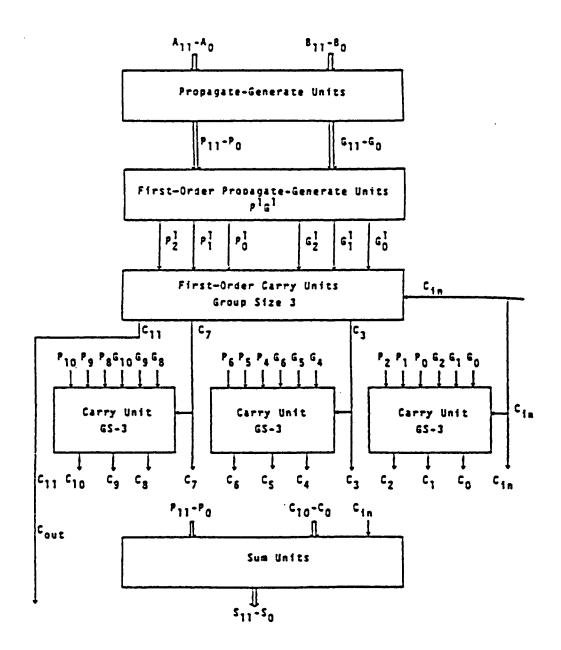

| The Organization of a 16-bit Carry-Select Adder                                    |

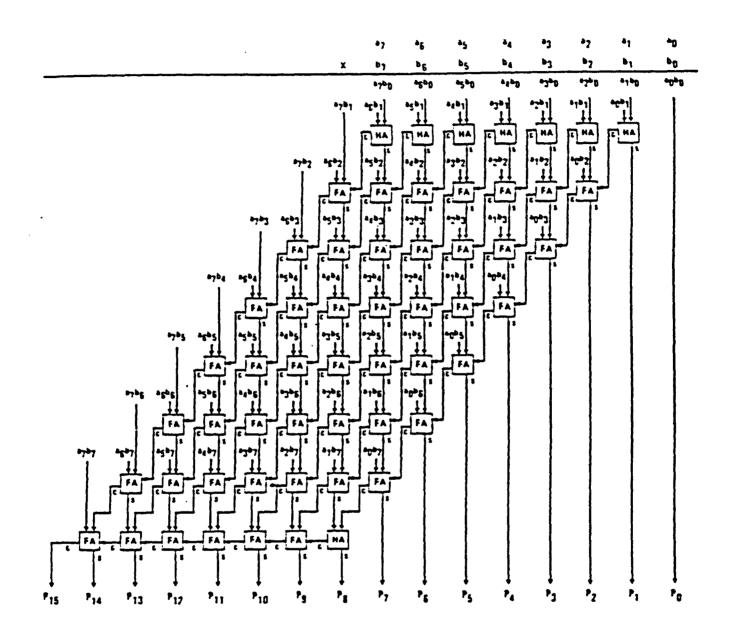

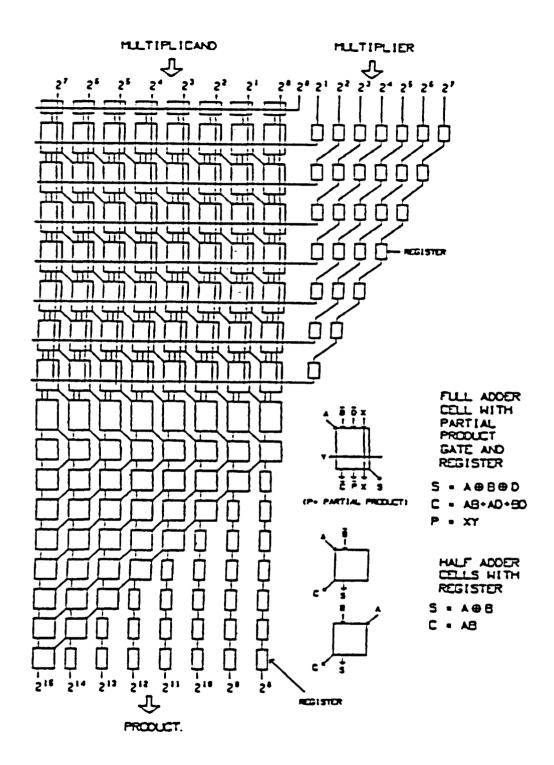

| The schematic Block Diagram of an 8x8-bit Parallel<br>Multiplier                   |

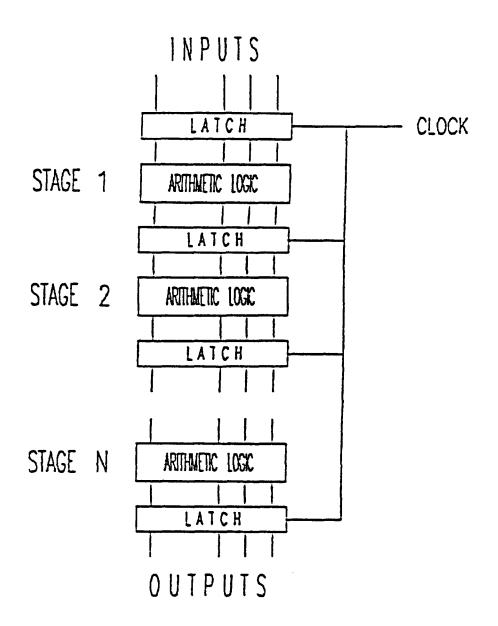

| The Functional Organization of an Arithmetic<br>Pipeline with k Stages             |

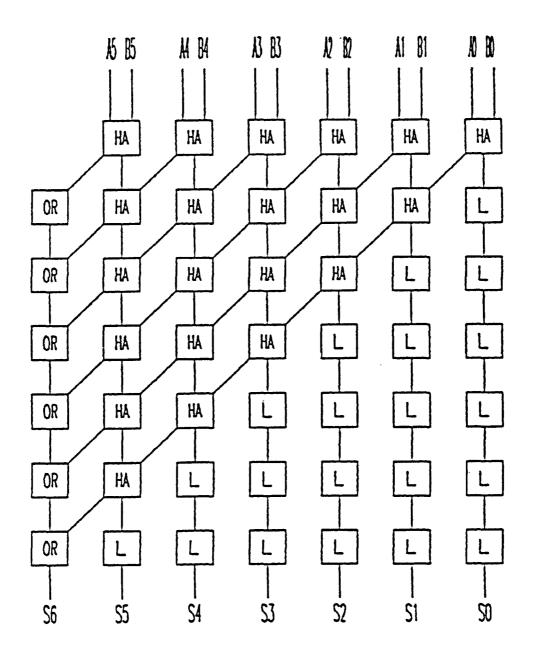

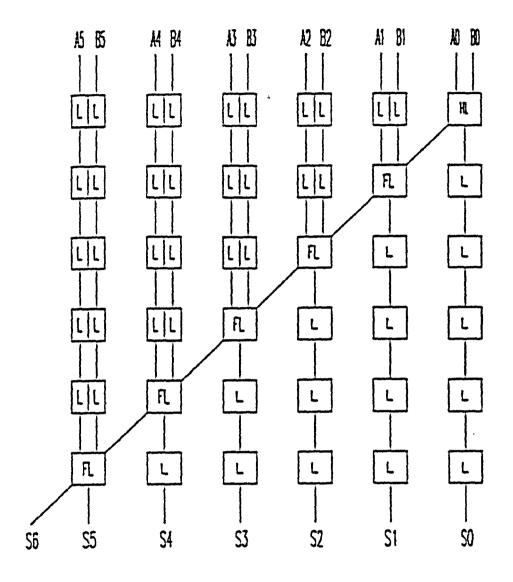

| Block Diagram of a 6+6 -bit Pipelined Binary Adder (HA Array)                      |

| Block Diagram of a 6+6 -bit Fipelined Binary Adder (FA Array)                      |

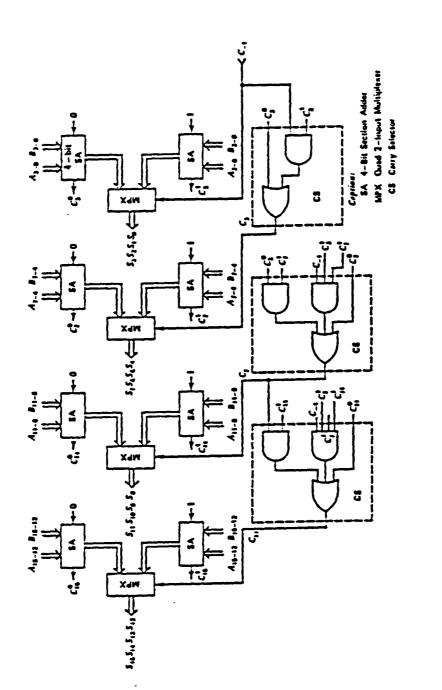

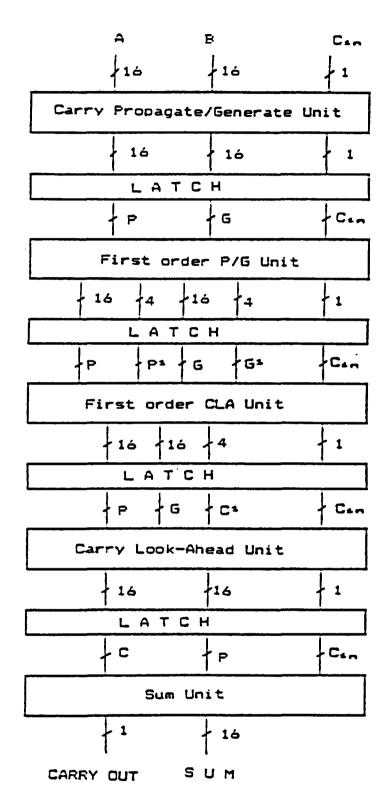

| Architecture of a 16-bit Pipelined Carry Look-Ahead<br>Adder                       |

| Block Diagram of an 8x8-bit Parallel Pipelined<br>Multiplier<br>Modulo m RNS Adder |

|                                                                                    |

| 3.3 | 2 | Αn | RNS | Adder | Using | the | Hybrid | Approach |

|-----|---|----|-----|-------|-------|-----|--------|----------|

|-----|---|----|-----|-------|-------|-----|--------|----------|

- 3.3 A Counter-Based RNS Adder

- 3.4 Time Chart of the RNS Adder of Fig. 3.3

- 3.5 A 5-bit Pipelined Ripple-Carry RNS Adder (FA Array)

- 3.6 A 5-bit Pipelined Carry Save RNS Adder (HA Array)

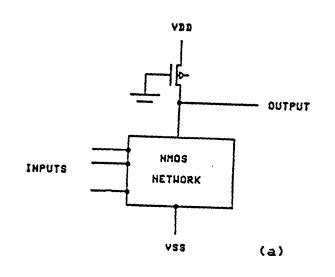

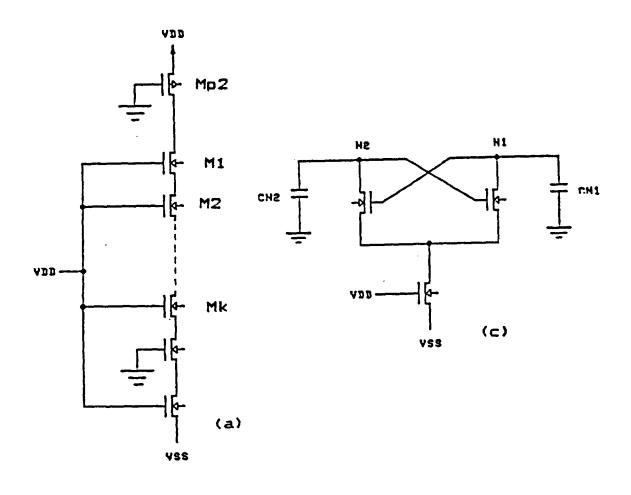

- 4.1 (a) General CMOS Complementary Logic

- (b) Fully Complementary CMOS 32A0I Gate

- 4.2 (a) General Pseudo-NMOS Logic

- (b) Pseudo-NMOS 32ADI Gate

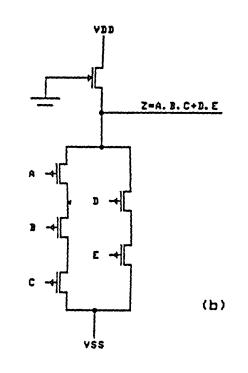

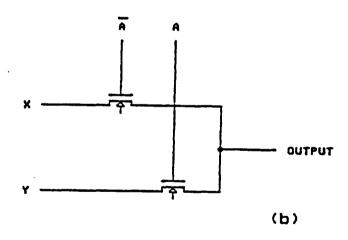

- 4.3 (a) Pass-Transistor logic Model

- (b) Pass Transistor Structures for Basic Logic Functions AND, NAND, OR, NOR, and XOR

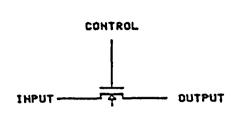

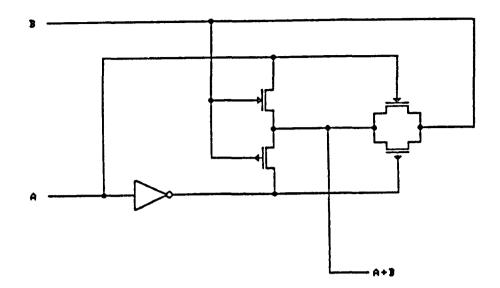

- 4.4 Transmission Gate (TG) XOR Circuit

- 4.5 Transmission Gate Half Adder Circuit

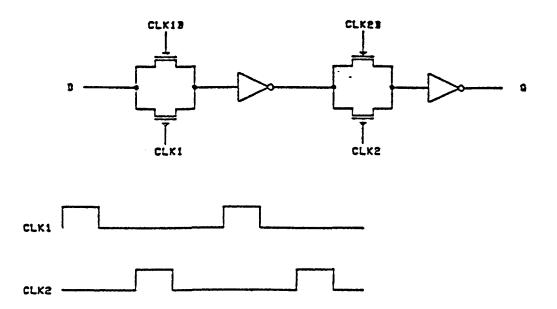

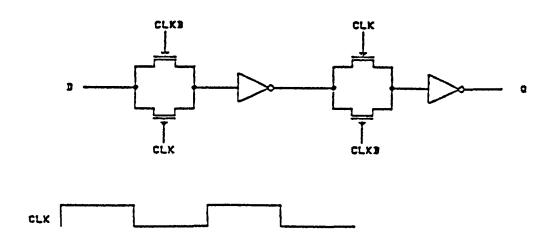

- 4.6 Pseudo Two-Phase TG Flip-Flop

- 4.7 Two-Phase TG Flip-Flop

- 4.8 (a) Clocked CMOS Inverter (without Charge Sharing)

- (b) Clocked CMOS Inverter (with Charge Sharing)

- 4.9 Clocked CMOS 32AOI Gate

- 4.10 (a) Dynamic CMOS NOR2 Gate

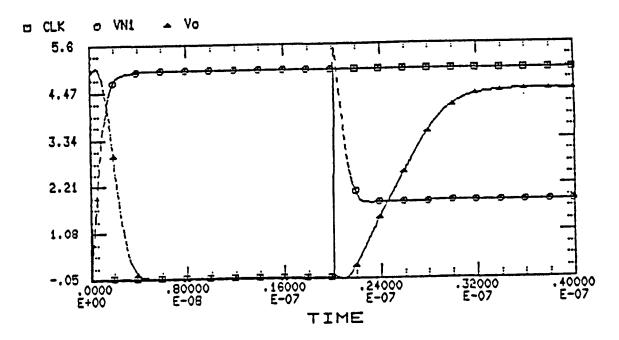

- (b) Discharge Timing Diagram of the Precharged Node (Vo), Obtained from SPICE

- 4.11 N-Type Dynamic CMOS 32ADI Gate

- 4.12 (a) Cascaded Dynamic CMOS Logic

- (b) SPICE Simulation for A=B=C=1 & D=O, Showing the Internal Delay Race Problem

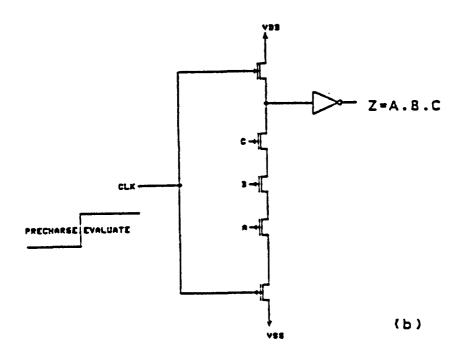

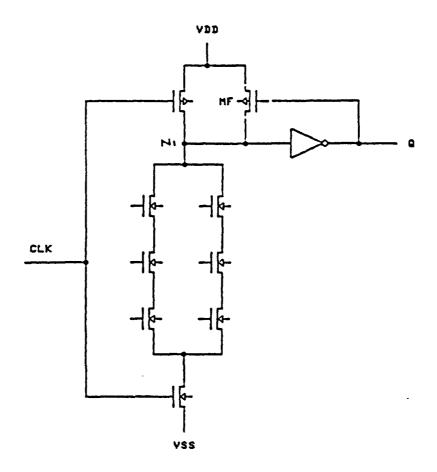

- 4.13 (a) Domino CMOS Logic

- (b) Domino CMOS AND3 Gate

- 4.14 Two-Stage Domino CMOS Gate

- 4.15 N-P Dynamic CMOS Logic

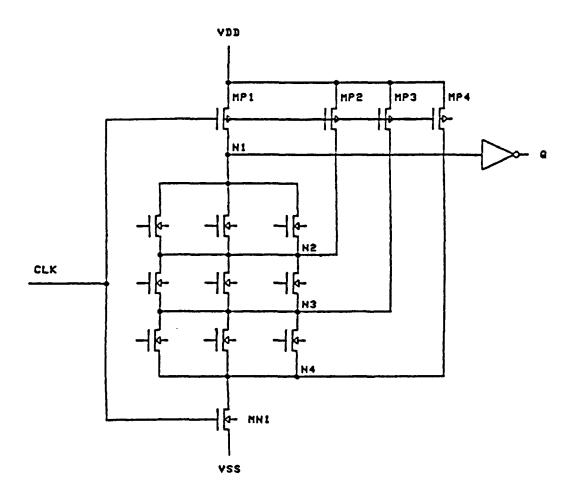

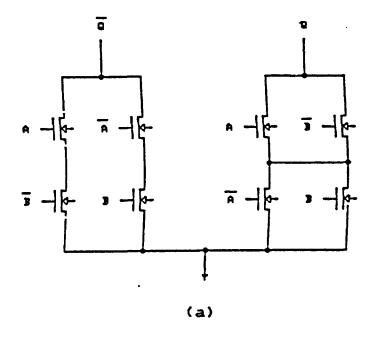

- 4.16 (a) Differential Cascode Voltage Switch Logic (DCVSL)

- (b) Three-Input XOR DCVSL Gate

| 4.17 | Basic Latched Domino Gate                                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

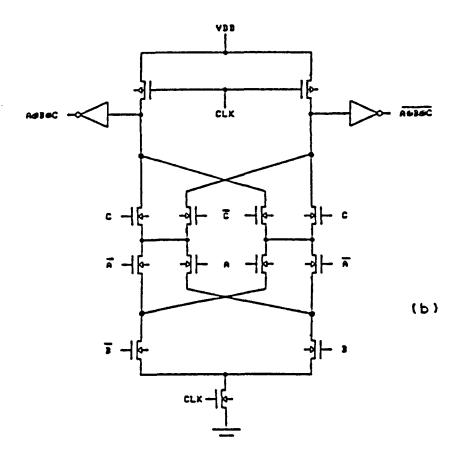

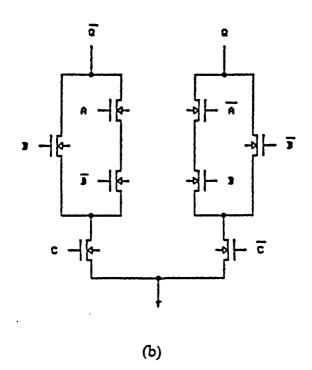

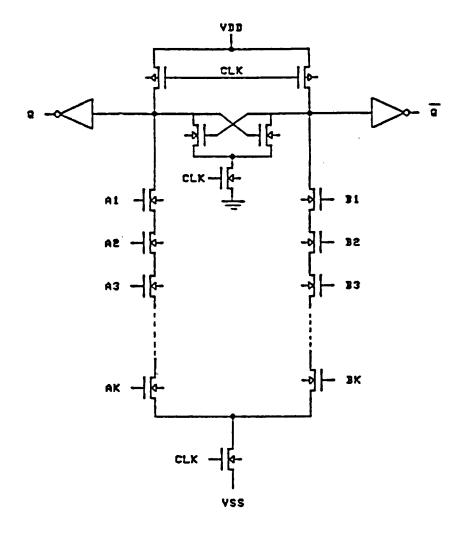

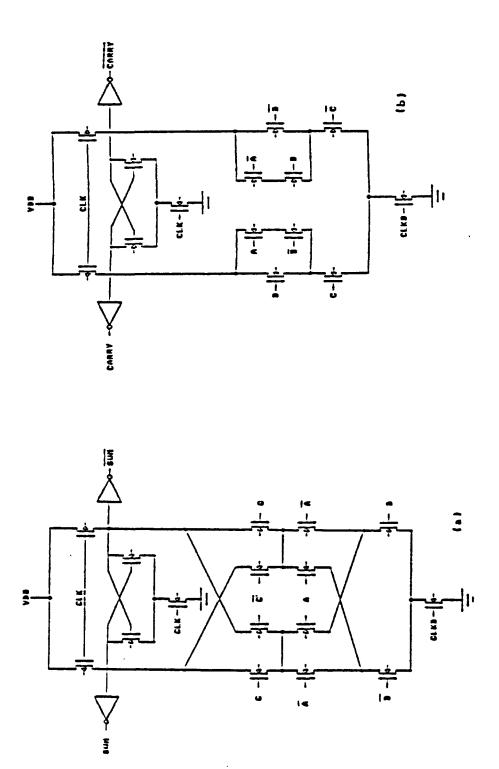

| 4.18 | <ul><li>(a) Basic Sample-Set Differential Logic (SSDL)</li><li>(b) Three-Input XOR SSDL Gate</li></ul>                                                                   |

| 4.19 | <ul> <li>(a) Domino Circuit</li> <li>(b) Waveforms Associated with Domino Logic (Fig 4.19a). The Effect of Charge Sharing is Seen on Node N1</li> </ul>                  |

| 4.20 | A Domino Circuit Using PMOS Feedback Device to<br>Reduce Charge Sharing Effect                                                                                           |

| 4.21 | A Domino Circuit Using Multiple precharging Devices to Frevent Charge Sharing .                                                                                          |

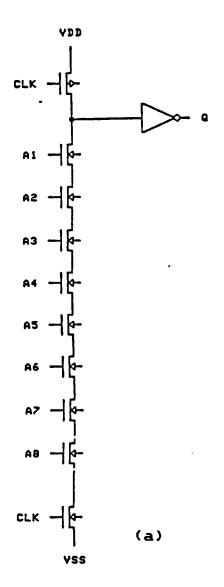

| 4.22 | (a) A Domino 8-Input AND Gate<br>(b) NOR Buffered 8-Input AND Gate                                                                                                       |

| 4.23 | (a) DCVS 2-Input XOR<br>(b) Logic Minimized DCVS 2-Input XOR                                                                                                             |

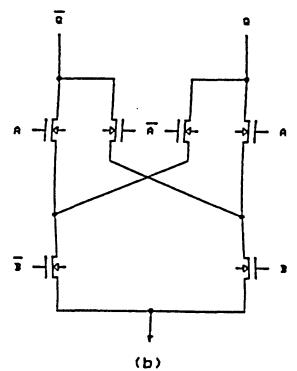

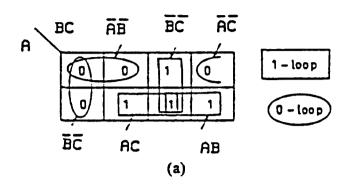

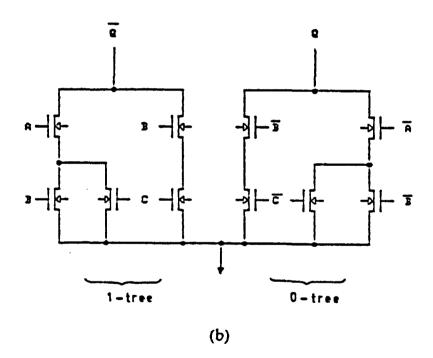

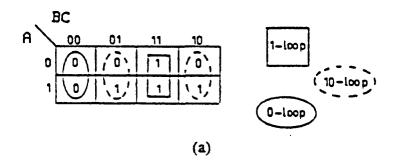

| 4.24 | <ul> <li>(a) K-map Of the Carry-Out Function of a Full Adder</li> <li>(b) DCVS Implementation of the Carry-Out Function of a Full Adder</li> </ul>                       |

| 4.25 | <ul> <li>(a) K-map of the Carry-Out Function of a Full Adder (Different Encirclement)</li> <li>(b) The DCVS Tree of the Carry-Out Resulting From Fig. 4.24(a)</li> </ul> |

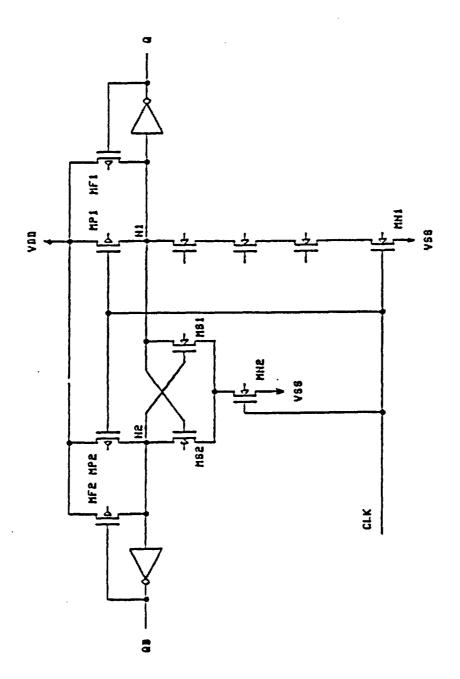

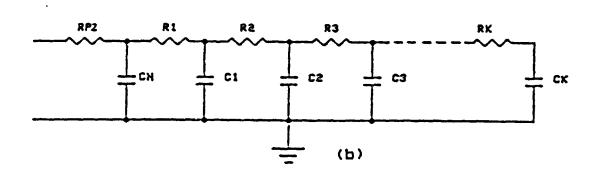

| 4.26 | Equivalent Circuit of SSDL Gate                                                                                                                                          |

| 4.27 | (a) Equivalent Circuit of the Off-Side During Sample Phase                                                                                                               |

|      | (b) RC Equivalent Circuit of the Off-Side During Sample Phase                                                                                                            |

|      | (a) Equivalent Circuit of the Conco Amplifier                                                                                                                            |

- (c) Equivalent Circuit of the Sense Amplifier During Set Phase

- 4.28 (a) Equivalent Circuit of the On-Side During

- Sample Phase

(b) RC equivalent circuit of the On-side During Sample Phase

- 4.29 (a) Modified SSDL Circuit

- (b) Modified SSDL CMOS Pipelined Circuit

- 4.30 (a) Fault Example in CMOS Gate

- (b) Fault in CMOS Circuit

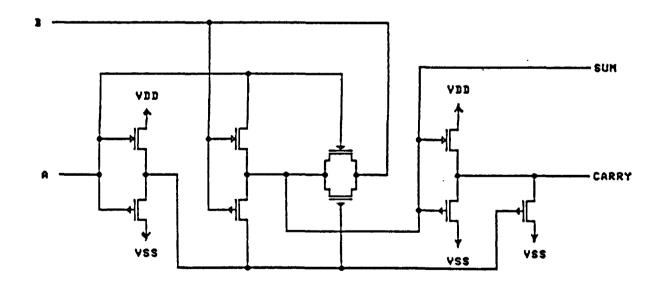

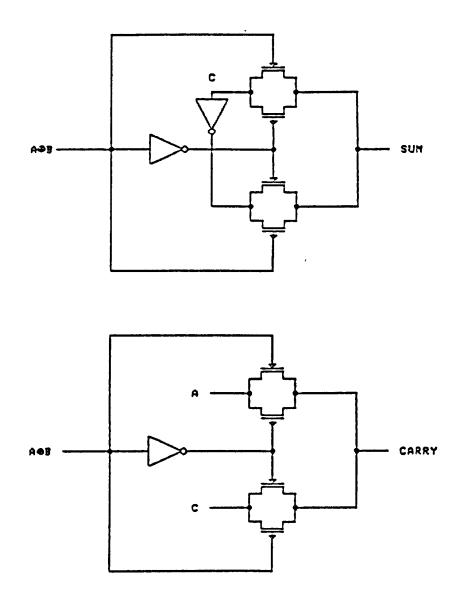

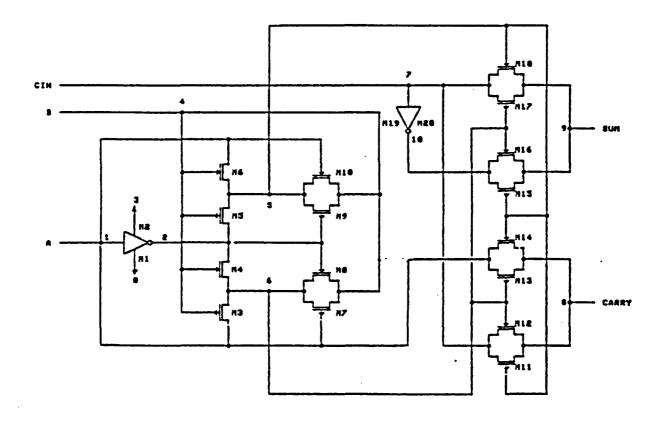

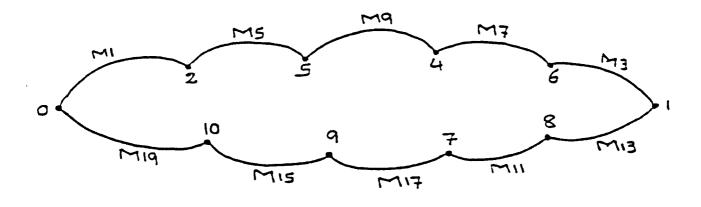

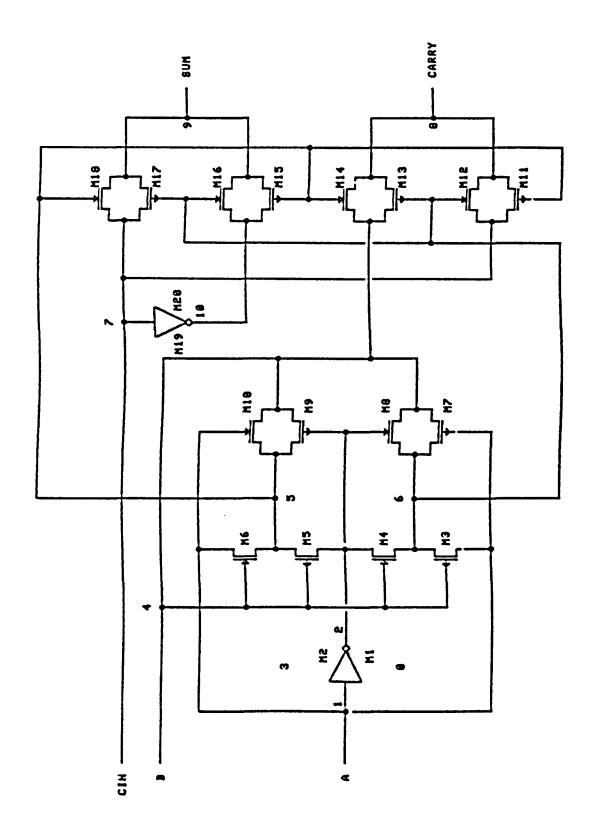

- 5.1 Transmission Gate (TG) Full Adder

- 5.2 24-Transistor TG Full Adder (TGFA#1)

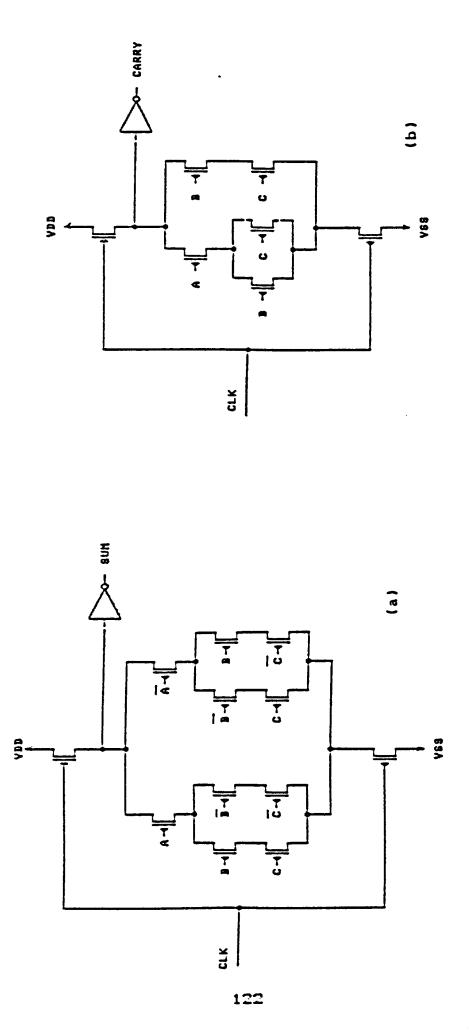

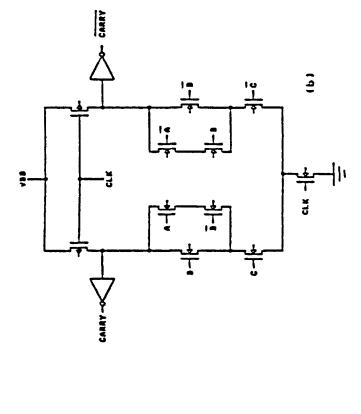

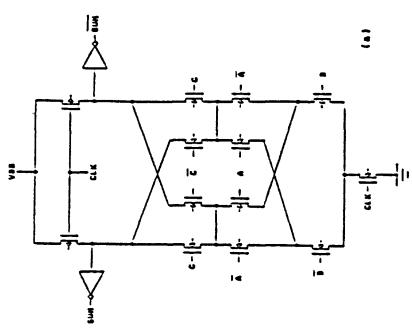

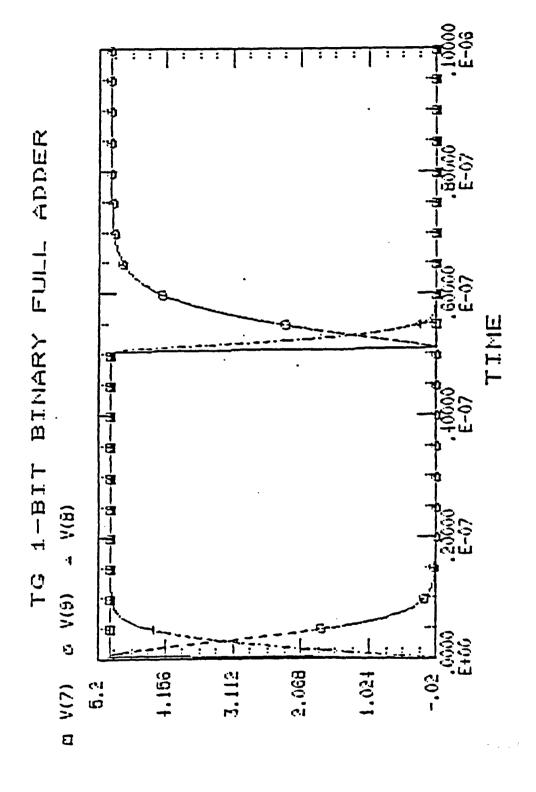

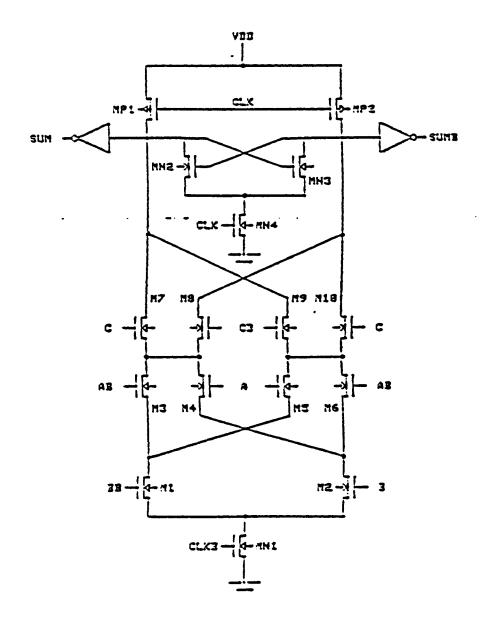

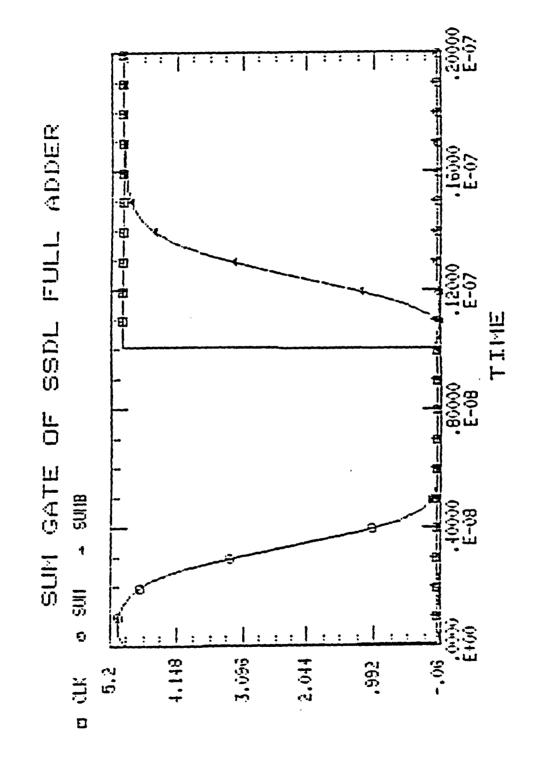

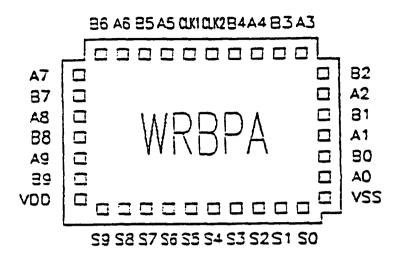

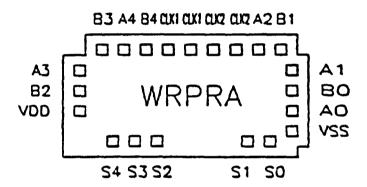

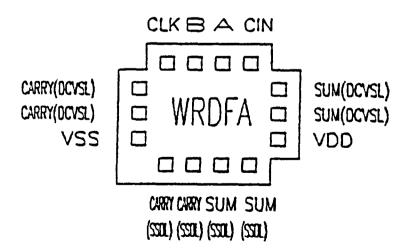

20-Transistor TG Full Adder (TGFA#2) 5.3 5.4 18-transistor TG Full Adder (TGFA#3) 5.5 16-Transistor TG Full Adder (TGFA#4) 5.6 Domino CMOS Full Adder 5.7 DCVSL CMOS Full Adder 5.8 NORA CMOS Full Adder 5.9 SSDL CMOS Full Adder 5.10 n-Graph Model of TGFA#2 A-1 Schematic circuit of TGFA#2 A-2 Waveforms Associated with the Fig. A-1, obtained from SPICE A-3 The SUM section of the SSDL CMOS full adder A-4 Waveforms Associated with the Fig. A-3, obtained from SPICE B-1 A TG Half Adder Layout B-2 A TG Full Adder Layout B-3 A Pseudo Two-phase Dynamic Register Layout B-4 IC3WRDFA Chip Layout B-5 IC3WRBPA Chip Layout B-6 IC3WRPRA Chip Layout P-7 Pinouts of IC3WRDFA, IC3WRPRA and IC3WRBPA

### LIST OF AFFENDICES

|          |   |       | rage |

|----------|---|-------|------|

| APPENDIX | Α | ••••• | 139  |

| AFFENDIX | B | ••••• | 148  |

| AFFENDIX | С | ••••• | 157  |

| AFFENDIX | D | ••••• | 161  |

| APPENDIX | Ε |       | 162  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Introduction

Digital signal processing has applications in a variety of areas such as, speech processing, biomedical engineering, geophysics research, telecommunication, and processing. In the majority of these applications high-speed and high-precision computation is essential in order to have real-time and accurate processing. The term "real time processing" is defined as "the processing of data at the same rate as the input data rate". Consider, for example, an image processing application such as image enhancement. Smoothing operations are used to diminish the noises, due to sharp transitions in the gray levels, of the image. technique for image smoothing is neighborhood averaging. The smoothed image is obtained by replacing the gray level of each pixel by the average of the gray level values of the surrounding pixels. Consider an image of size MxN pixels and T.V. scan rate of K frames/s: if L arithmetic operations are required for each pixel, the total number of arithmetic operations that have to be performed in one second is K.L.M.N . To process an image in real time, a processor has to be able to process the image at 30 frame/s for flickerfree viewing. For a 512x512-pixel image, 30 frame/s, and a 3x3 window, a multiplier/accumulator would have to operate at 71 Mhz to process the image in real time [1].

Some other applications can require throughputs from 100 Mhz to 1 Ghz. Achieving such a high-speed operation requires careful study and improvements in three major areas: arithmetic, architectural, and implementation domains [2]. Parallelism is naturally achieved over the dynamic range by using Residue Number System (RNS) arithmetic. The use of RNS arithmetic results in inherently parallel hardware designs because of independence over the dynamic range of arithmetic operations within each modulus. More on ENS is discussed in chapter 3.

In the architectural domain, pipelining techniques are utilized to increase the computation rate of a digital system. The effectiveness of this method depends on the structure of the algorithm. This structure is very effective when the algorithm is applied repeatedly to a stream of input data. In this case a significant increase in speed is obtained with only moderate increase in hardware.

High-speed low-power CMOS VLSI technology is used for the implementation of digital signal processors. The three main implementation approaches are as follows:

- I Microprocessor approach

- II Semicustom Integrated Circuit approach

- III Full Custom Integrated Circuit approach

Implementing a high-throughput rate (e.g. 200 Mhz) DSP function with microprocessors and building blocks is neither possible nor cost effective. Even dedicated processors such as Finite Impulse Response (FIR) filter chips fall short in bandwidth.

Semicustom approaches such as gate arrays, standard cells, and ASIC's (Application-Specific) also cannot provide the speed needed for most of the real time signal processing applications.

Full custom DSP approaches, which use 1-micron or submicron technology is often the only solution for meeting the speed performance requirement. Custom IC development is usually characterized by being expensive and having long development DSP However. because of the regularity of cycles. architectures the development time can be reduced. Even in some cases, large functional blocks such as FIR filter and Fast Fourier Transform (FFT) can be added to the library This reduces the development cycles, macros. making custom approach competitive with semicustom approaches [1]. the circuit domain investigations must be carried out to determine the most suitable logic family to be Α complete study of CMOS logic design techniques is given chapter 4.

#### 1.2 COMPUTER AIDED DESIGN TOOLS UTILIZED

A DAISY chipmaster work station was used for all mask layouts. The masks were design rule checked and verified using the Phoenix Data System integrated software package. The circuits were simulated extensively using the SPICE 2G analog simulation program to predict circuit performance and delay times.

#### 1.3 OBJECTIVES

The main objective of this thesis is "CMOS VLSI design and implementation of high-speed arithmetic for digital signal processing applications". To achieve this goal the following steps has been taken:

- 1 Investigation of various algorithms for high-speed arithmetic in Binary.

- 2 Study of Residue Number System arithmetic and investigation of different algorithms for RNS addition.

- 3 CMOS VLSI design and implementation of pipelined binary and RNS adders.

- 4 Study of different CMOS logic families including, DOMINO, NORA, DCVSL, LDOMINO, CLOCKED CMOS, and SSDL.

- 5 Design and optimization of a static full adder for standard cell application.

- 6 Analysis and optimization of SSDL gate for pipelined architectures.

#### 1.4 THESIS DRGANIZATION

In this chapter, the need for high-speed arithmetic in various areas of digital signal processing applications was described. The three main areas namely, arithmetic, architectural, and implementation domains, which all require careful study for speed improvement, have been reviewed.

Chapter 2 describes the random logic design of binary arithmetic circuits. Different techniques for designing fast two-operand adders are presented and logic design of parallel multipliers are discussed. Pipelined architectures

are studied and the structure of high throughput rate adders and multipliers are also explained.

Residue Number System arithmetic is reviewed in chapter 3. Different methods of implementing RNS adders are discussed and the design of a pipelined RNS adder is presented. Finally, it is shown that for wide-dynamic range of operations (cross over point of 10 bits), the RNS adders have advantages over binary adders in four areas; namely hardware complexity, speed, testability, and latency time. Chapter 4 contains a comprehensive study of various CMOS logic families. Charge redistribution problem of dynamic CMOS logic circuits is addressed and different techniques to alleviate this problem are presented. A simple K-map procedure for the design of differential cascode voltage switch tree circuit is discussed. Delay time analysis of sample-set differential logic (SSDL) which has not appeared in the literature so far, is described and an analytical expression for the delay time is obtained. This expression is applied to the delay optimization of SSDL gates. The application of SSDL gates to pipelined structures is also presented along with a simplification of the SSDL structure. Finally, testing issues of CMOS VLSI digital circuits are studied.

Chapter 5 presents a number of designs for the implementation of CMOS full adders. Design optimization of a transmission gate full adder for use in a standard cell library is discussed.

Chapter 6 contains the summary and main conclusions of this work.

#### CHAPTER 2

• ,

#### LOGICAL DESIGN OF BINARY ARITHMETIC CIRCUITS

#### 2.1 INTRODUCTION

This chapter will discuss the design methodology combinational logic circuits for use in binary arithmetic One of the most important components in any digital arithmetic architecture is the binary adder. Adders are essential not only for addition, but also for subtraction, multiplication, and division. The operational speed of digital arithmetic processors depends on the performance of the adders which are used in the system. example, high-speed digital signal processors require parallel pipelined multipliers. The throughput rate of these multipliers depends on the delay of the 1-bit full adder cell used in the circuit [3]. So the delay introduced by the adder usually limits the maximum clock frequency at which a system may operate.

In section 2.2 an overview on logic design of the Half Adder (HA), Full Adder (FA), and Ripple-Carry (borrow) Adder (Subtractor) is presented. High-speed adders will be discussed in section 2.3, and section 2.4 deals with the structure of parallel multipliers. Finally, pipelined binary arithmetic architectures will be studied.

2.2 LOGIC DESIGN OF BASIC BINARY ADDER (SUBTRACTOR)

In this section the design of combinational logic circuits for the binary half adder, full adder, and ripple-carry

(borrow) adder (subtractor) will be examined. Let us consider the addition of two binary digits A and B .

C : Carry

S : Sum

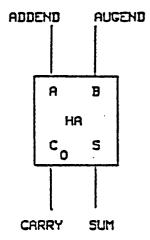

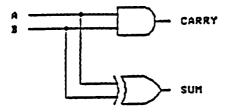

The half adder adds two binary digits A and B to produce a sum output S and a carry output C. The truth table and block diagram for the Half-adder is shown in Fig. 2.1. From the truth table of the half-adder the following boolean equations can be obtained:

Carry = A.B

Sum =  $A \oplus B$

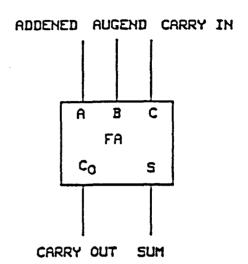

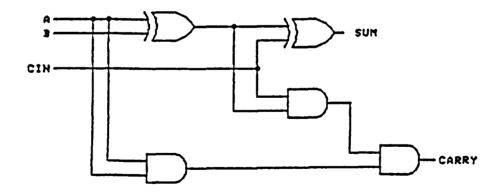

Fig. 2.2 shows the logic circuit which realizes these equations. The addition of two n-bit numbers requires an adder with three inputs (A; addend bit, B; augend bit, and Cin; carry information from the previous stage) to produce a sum output S and a carry output C. This type of adder is called a Full Adder and the truth table and block diagram of the full adder can be seen in Fig. 2.3. The two outputs are related to the three inputs by the following boolean equations:

Sum = ABC + ABC + ABC + ABC

= A ( B

$$\oplus$$

C ) + A ( B  $\oplus$  C )

= A  $\oplus$  B  $\oplus$  C

| A | B | SUM | CARRY |

|---|---|-----|-------|

| 8 | 8 | 0   | 0     |

| 8 | 1 | 1   | 9     |

| 1 | 9 | 1   | Ø     |

| 1 | 1 | 8   | 1     |

Fig. 2.1 Truth Table and Block Diagram of Half Adder

Fig. 2.2 Half Adder (HA) Logic Circuit

Carry =  $\overrightarrow{ABC}$  +  $\overrightarrow$

Carry = AB + C (A + B)

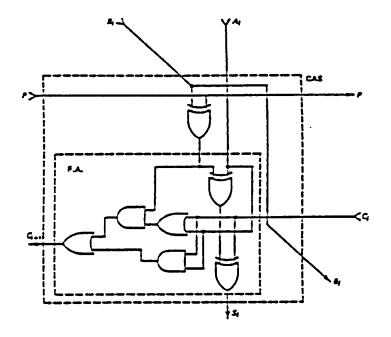

The schematic diagram of the full adder is shown in Fig. 2.4. This basic adding cell can be modified to become a 4-input 4-output Controlled Adder/Subtractor cell (CAS) as shown in Fig. 2.5 [4]. The additional input P is used to control the ADD (P = 0) or SUBTRACT (P = 1) operations. In the case of subtraction, the Ci input is called the borrowin and the Ci+1 output, the borrow-out. The input-output relationship of a CAS cell is specified by the following boolean equations.

Si = Ai + ( Bi + F ) + Ci

$Ci+1 = (Ai + Ci)(Bi \oplus F) + Ai Ci$

When P = 0 these equations are identical with the equations of the full adder. When P = 1 we have

Si = Ai + Bi + Ci

Ci+1 = Ai Bi + Bi Ci + Ai Ci

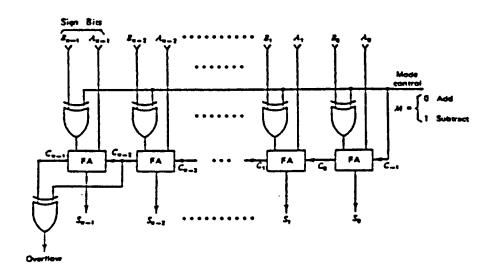

By cascading n Full adders, an n-bit ripple-carry adder is formed. This cell can also be used for subtraction. Subtraction of two's complement numbers is performed by first obtaining the two's complement of the subtrahend and then adding it to the minuend. The schematic design of a binary two's complement adder/subtractor is illustrated in Fig. 2.6. The initial carry input to the rightmost full adder is connected to the function mode line M, which equals

| A | B | С | SUM | CARRY |

|---|---|---|-----|-------|

| 0 | 8 | 8 | 8   | 8     |

| 8 | 8 | 1 | 1   | 8     |

| 0 | 1 | Ø | 1   | 8     |

| 0 | 1 | 1 | 8   | 1     |

| 1 | Ø | Ø | 1   | 0     |

| 1 | 0 | 1 | 8   | 1     |

| 1 | 1 | Ø | 8   | 1     |

| 1 | 1 | 1 | 1   | r     |

Fig. 2.3 Truth Table and Block Diagram of Full Adder

Fig. 2.4 Full Adder (FA) Logic Diagram

Fig. 2.5 Controlled Add/Subtract (CAS) Cell

Fig. 2.6 Two's Complement Binary Adder/Subtractor Configuration

"O" for addition and "1" for subtraction. This ripple through carry (borrow) is a problem when high-speed operation with a large number of bits is required. The delay time of an n-bit carry ripple adder is almost equal to nTc, where Tc is the delay of one carry stage. In the next section we will explain some methods for high-speed addition.

#### 2.3 HIGH-SPEED ADDERS

#### 2.3.1 CARRY LOOK-AHEAD ADDER

As we have seen in the previous section, the delay time of the ripple carry adder is linearly proportional to the size of the input variables. Carry look-ahead (CLA) is a technique which is used to speed up the carry propagation in an adder. The carries to each stage of a parallel adder are calculated simultaneously by additional logic circuitry. As a result the addition time will improve at the cost of using more hardware for the carry look-ahead unit.

Let us denote the addend and augend of an n-bit adder by :

$A = An-1 \dots A1A0$

B = Bn-1 .... B1B0

We will let, Ci-1 be the carry input to the i-th stage. The carry input to the first stage (least significant position) is denoted by C-1. Let the Si be the output sum and Ci be the carry of the i-th stage, now we define:

Gi : the i-th carry generate function.

Gi = Ai.Bi

Pi : the i-th carry propagate function.

Pi = Ai + Bi

substituting Gi and Pi into equations for sum and carry of the full adder we get:

Si = Fi ⊕ Ci-1

Ci = Gi + Pi Ci-1

These equations show that since Pi and Gi are generated simultaneously, for  $i=1,2,3,\ldots,n$ , then all the sum bits can be computed in parallel if Cn-2, ..., C2, C1, C0 are available. Because of fan-in limitation of CMOS circuits, the number of stages of carry look-ahead adder is usually limited to four. Four bit carry look-ahead equations are:

C-1 = Cin

C0 = 60 + P0 C-1

C1 = G1 + P1 C0

C2 = G2 + F2 C1

C3 = G3 + P3 C2

Now if we expand each carry equation in terms of Pi, Gi and Cin we obtain:

CO = GO + Cin PO

C1 = G1 + G0 P1 + Cin P0 P1

C2 = G2 + G1 P2 + G0 P1 P2 + Cin P0 P1 P2

C3 = G3 + G2 P3 + G1 P2 P3 + G0 P1 P2 P3 + Cin P0 P1 P2 P3

This set of equations shows that all the carries can be generated simultaneously, and as a result the sum also can be calculated simultaneously.

SO = PO ⊕ Cin

S1 = P1 ⊕ C0

S2 = P2 ⊕ C1

S3 = P3 ⊕ C2

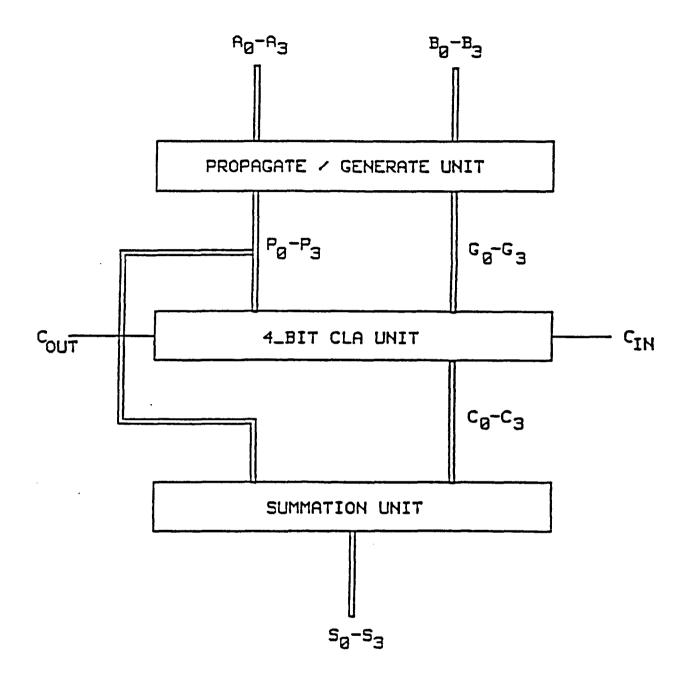

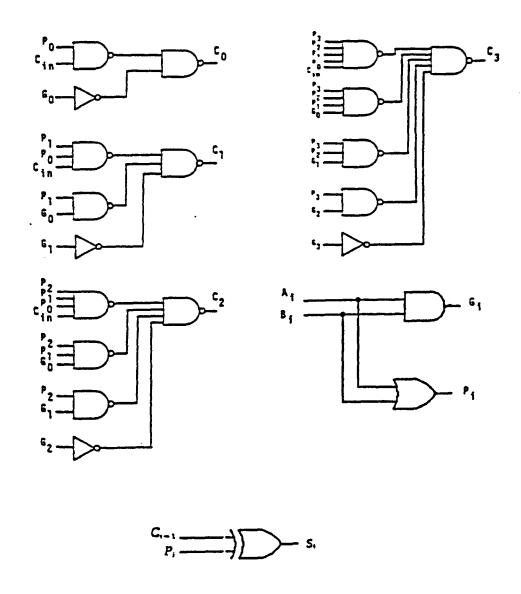

and C3 is the carry overflow. The functional block diagram of a 4-bit carry look-ahead adder is illustrated in Fig. 2.7. The gate schematic of different blocks of a carry look-ahead adder are shown in Fig. 2.8.

Theoretically one should be able to expand the CLA unit freely and build CLA adders of any word length. Due to the constraints described before ( fan-in and fan-out limitation), however, single-level CLA is applied only to the design of adders of lengths 4 in CMOS circuits.

The total delay time of a 4-bit carry look-ahead adder is the sum of the delay times due to the propagate-generate unit ( NAND2 ), carry look-ahead unit ( NAND5 ), and summation unit ( XOR ).

#### 2.3.2 RIPPLE CARRY LOOK-AHEAD ADDER

As we mentioned before, the number of stages in the carry look-ahead adder is limited to four. One solution to the high fan in problem is to break the large single CLA unit into a number of smaller CLA units and let the carries ripple between the units. The organization of a 12-bit ripple carry look-ahead adder with three carry look-ahead units each of size 4 is shown in Fig. 2.7. The total delay of this type of adder is the sum of the delays due to propagate/generate unit (NAND2) and sum unit (XOR) plus the delays through all CLA units (3 NAND5).

Fig. 2.7 The Functional Block Diagram of a 4-bit Carry Look-Ahead Adder

Fig. 2.8 The Schematic Logic of 4-bit Carry Look-Ahead Adder Units

Fig. 2.9 The Organization of a 12-bit Ripple-Carry Look-Ahead Adder

#### 2.3.3 FIRST ORDER CARRY LOOK-AHEAD ADDER

It was noted in the previous section that the delay time in ripple carry look-ahead adder depends on the size of the adder. Another technique called the first order carry look-ahead (FOCLA) adder will be explained [5]. This technique allows the propagation delay to be independent of the size of the adder, but requires more hardware. Let us re-examine the carry equations C3, C7, and C11 of the 12-bit ripple carry look-ahead adder

Now the question is, how can these carries be calculated simultaneously as was done for a simple CLA adder? We define a set of first order carry propagate/generate functions Pi, Gi. as follows:

$$60 = 63 + 62 P3 + 61 P2 P3 + 60 P1 P2 P3$$

$$G1 = G7 + G6 P7 + G5 P6 P7 + G4 P5 P6 P7$$

$$P2 = P8 P9 P10 P11$$

Using these newly defined equations, then C3, C7, and C11 can be written as:

$$C3 = 60 + Cin PO$$

$$C7 = G1 + G0 P1 + Cin F0 P1$$

From these equations all three carries can be generated simultaneously. The equations for a 12-bit FOCLA adder can be summarized as follows:

Propagate generate unit :

Pi = Ai ⊕ Bi

$i = 0, 1, 2, \ldots, 11$

Gi = Ai Bi

First order propagate/generate unit

PO = PO P1 P2 P3

GO = G3 + G2 P3 + G1 P2 P3 + G0 P1 P2 P3

P1 = P4 P5 P6 P7

G1 = G7 + G6 P7 + G5 P6 P7 + G4 P5 P6 P7

P2 = P8 P9 P10 P11

G2 = G11 + G10 P11 + G9 P10 P11 + G8 P9 P10 P11

First order carry unit :

C3 = 60 + Cin F0

C7 = G1 + G0 P1 + Cin P0 P1

C11 = G2 + G1 P2 + G0 P1 P2 + Cin P0 P1 P2

Carry unit :

CO = GO + Cin PO

C1 = G1 + G0 P1 + Cin P0 P1

C2 = G2 + G1 P2 + G0 P1 P2 + Cin P0 P1 P2

C4 = G4 + C3 P4

C5 = G5 + G4 P5 + C3 P4 P5

C6 = G6 + G5 P6 + G4 P5 P6 + C3 P4 P5 P6

C8 = 68 + C7 P8

C9 = G9 + G8 P9 + C7 P8 P9

C10 = G10 + G9 P10 + G8 P9 P10 + C7 P8 P9 P10

Summation unit :

Si = Pi

$$\oplus$$

Ci-1 i = 0, 1, 2, ..., 11

The block diagram of a 12-bit first order carry look-ahead adder is shown in Fig. 2.10 .

#### 2.3.4 CARRY SELECT ADDER

carry select adder is another high-speed addition technique which is of great value for the addition of large length numbers [4]. In this system of addition, the addend and augend are broken into subaddend and subaugend sections that are added twice. The first addition with a O carry-in and the second with a 1 carry-in. These two sections produce two subsums. The correct value of carry-in selects the appropriate subsum ( 2-input multiplexer ). The selection of the carry input to each section is generated in carry selection unit. Let us consider a 16-bit carry select adder. First, the 16-bit word is divided into 4 sections each of size 4-bit. Each 4-bit section adder could either be a ripple-carry adder or a carry-lookahead adder. The logical expressions for carry selection circuits are:

$$C11 = C11 C7 + C11$$

$$=$$

C11 C7 C3 Cin + C11 C7 C3 + C11 C7 + C11

Fig. 2.10 The Functional Block Diagram of 12-bit First-Order Carry Look-Ahead Adder

Figure 2.11 shows the basic scheme of the 16-bit carry select adder. The superscript "O" and "1" shows the carry obtained from the sections of "zero" and "one" forced carryin respectively.

# 2.4 PARALLEL MULTIPLIER

The multiplication of two n-bit integers, A and B, will create a 2n-bit product,  $P = A \times B$ . Where A is called the multiplicand and B is the multiplier. Consider two unsigned binary integers:

$A = am-1 \dots a1a0$

$B = bn-1 \dots b1b0$

With values Av and Bv respectively

$$Av = \sum_{i=0}^{m-1} (ai 2^i)$$

$$Bv = \sum_{i=0}^{n-1} (bi 2)$$

In binary, the product of A and B results in a (m+n)-bit number P.

Pv = Av Bv

$$= \left[\sum_{i=0}^{m-1} (ai 2)\right] \left[\sum_{j=0}^{i-1} (b_j 2)\right] = \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} \left[(ai b_j) 2\right]$$

$$= \sum_{k=0}^{m+n-1} (pk 2)$$

All partial product terms (ai bj) are generated in parallel by  $m \times n$  AND gates. The design of an  $8 \times 8$ -bit unsigned array multiplier is selected to demonstrate the parallel

The Organization of a 16-bit Carry-Select Adder Fig. 2.11

multiplication architecture using carry-save adders. The advantage of this approach is that design issues are minimal layout is highly modular. The logic diagram of an bit parallel multiplier is shown in Fig. 2.12 [6]. The implementation of such a multiplier of size nxn-bits requires (n-1)(n-1)-1 Full adders, n Half adders, and nxn AND gates. Therefore the entire multiplier is designed using three unit cells: a full adder, a half adder, and an AND gate cell. The last stage of the array multiplier is an (n-1)-bit ripple-carry adder which can be replaced by a carry lookahead adder to improve the speed of the operation.

## 2.5 PIPELINED ARITHMETIC

## 2.5.1 THE CONCEPT OF PIPELINE SYSTEM

The computing power of a machine is determined by two major factors, one is throughput rate (bandwidth) and the other is latency [4]. Throughput is the rate at which new data can be fed to the processor. Latency is the time required for the data to traverse the processor. For a system that performs one operation at a time (such as the adders that have been discussed so far), throughput rate is the inverse of latency.

In most digital signal processing applications the throughput rate of the processor is the critical factor, not the latency time. In conventional designs, an increase in the throughput rate of arithmetic processors has been achieved by reducing the latency with faster logic circuitry. For example, high-speed adders have been designed

Fig. 2.12 The schematic Block Diagram of an 8x8-bit Parallel Multiplier

to reduce the propagation delay time.

A simple solution to the throughput rate problem is to allow simultaneous execution of many tasks by multiple arithmetic units. Farallel processing with straight hardware duplication, however, may not be economical or cost effective. Pipelining allows a significant increase in throughput rate with only moderate increase in hardware. Pipeline computing refers to the subdivisions of the total computational workload into individual tasks, so that they can be executed in an overlapped fashion through a higharithmetic speed pipeline under certain precedence constraints. The functional organization of a pipelined arithmetic unit is illustrated in Fig. 2.13 . The pipeline is characterized by the succession of stages. In a pipelined structure, successive stages are interfaced with data latches ( synchronized registers ), which hold the input and output bit pattern of the successive stages. Different stages may have different delay times. In order to regulate the pipeline operation, the synchronizing clock pulse should have a clock period of

$$T > Max \{ Ti + Tl \}$$

$i \in [1, k]$

Where Ti is the delay time of the i-th stage and Tl is the delay time of a single latch. Therefore the throughput rate of the pipelined system is determined by the maximum delay of one stage plus the delay time of a latch. The latency of such a system is k clock cycles.

Fig. 2.13 The Functional Organization of an Arithmetic Pipeline with k Stages

# 2.5.2 PIPELINED CARRY-SAVE ADDER (HALF ADDER ARRAY)

Pipelined adders remove the problem of carry propagation at the cost of extra hardware. Fig. 2.14 shows the architecture of a fully pipelined adder using an array of half adders. The pipelining is achieved by placing latches between each stage of operation. In this way the inputs can arrive separated by only one clock cycle. The maximum clock frequency of operation is determined by the delay of a half adder plus the delay of a single latch.

# 2.5.3 PIPELINED RIPPLE-CARRY ADDER (FULL ADDER ARRAY)

The general architecture of a pipelined ripple-carry adder (FA array) is shown in Fig. 2.15. This design requires less hardware than the similar structure using an array of half adders (almost 25% reduction in transistor count). As before, throughput rate of this structure is determined by the delay time of a full adder plus the delay of a latch.

A 10-bit pipelined ripple-carry adder was implemented using

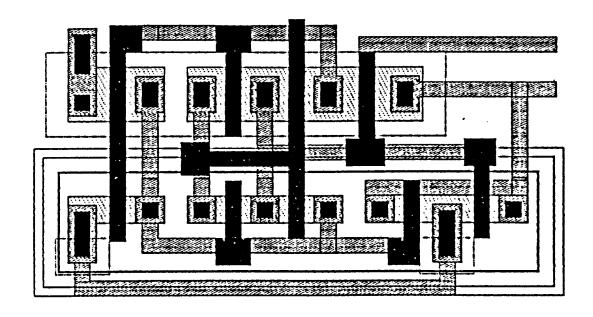

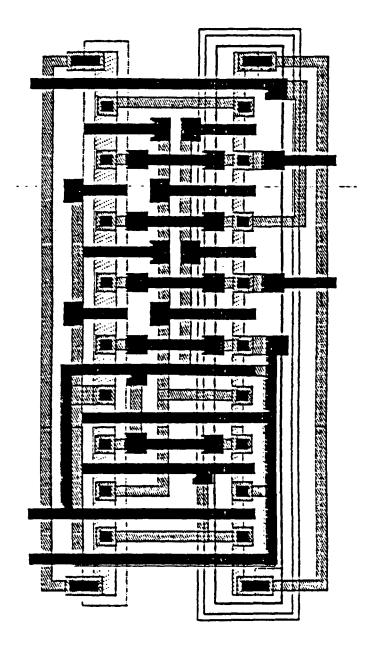

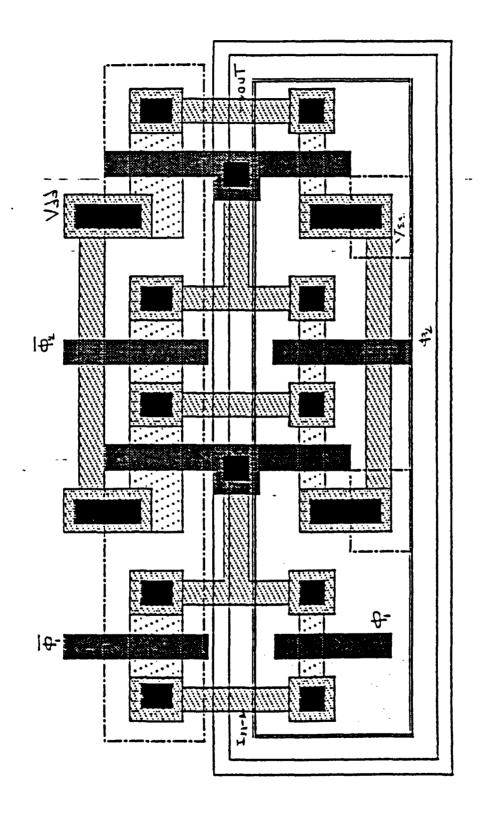

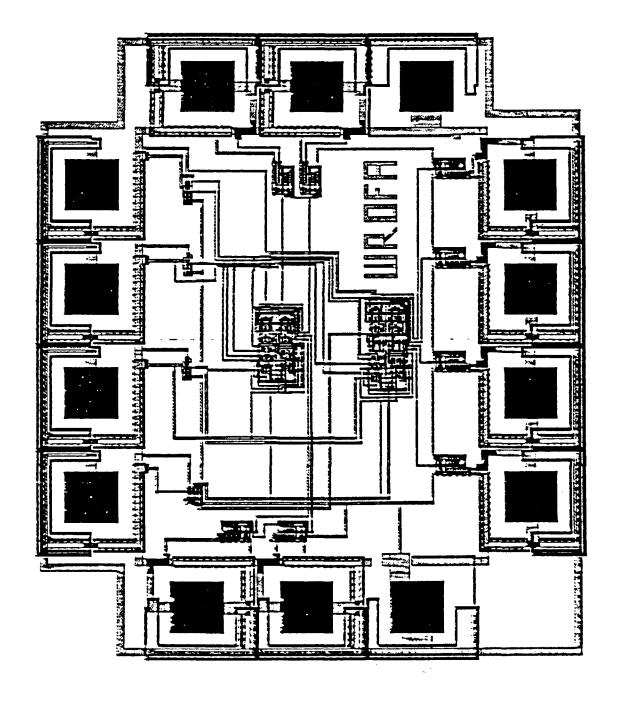

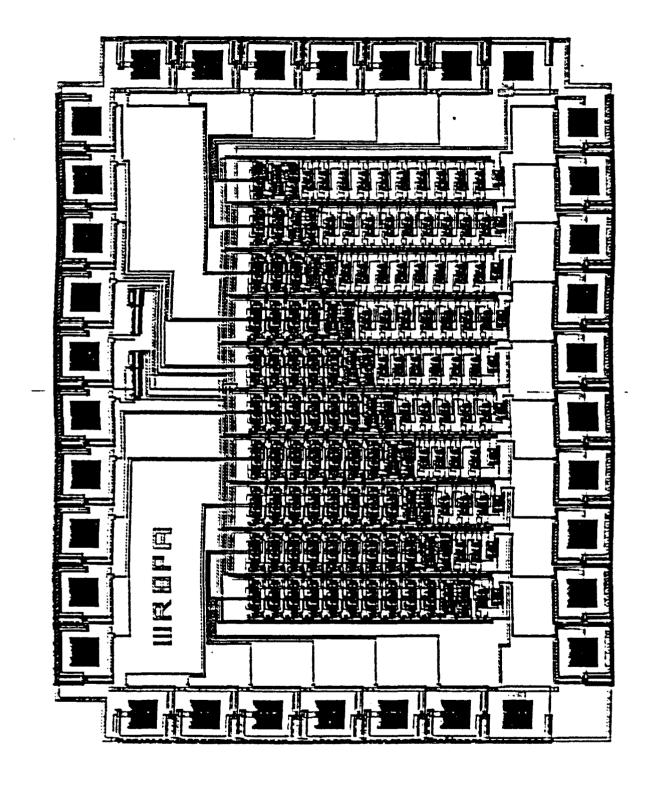

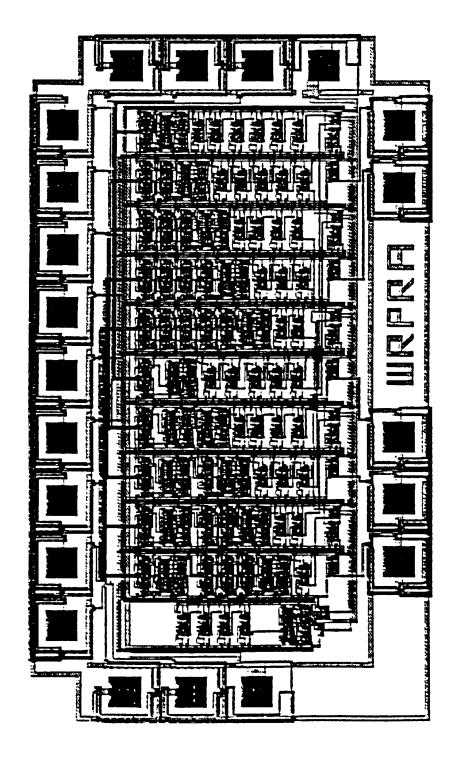

Sum CMOS technology. Appendix B (Fig. B-5) shows the chip layout of this adder.

## 2.5.4 PIPELINED CARRY LOOKAHEAD ADDER

In section 2.3.3, the organization of the first order (two-level) carry lookahead adder was discussed. This adder can be converted to pipelined version by placing latches between the different stages. Figure 2.16 shows the architecture of a 16-bit pipelined carry lookahead adder. The adder has five stages:

Fig. 2.14 Block Diagram of a 6+6 -bit Pipelined Binary Adder (HA Array)

Fig. 2.15 Block Diagram of a 6+6 -bit Pipelined Binary Adder (FA Array)

Fig. 2.16 Architecture of a 16-bit Pipelined Carry Look-Ahead Adder

Stage 1 - Propagate / Generate Unit:

Each pair of input bits (A, B) is used to produce the generate (G) and propagate (P) bits according to the following equations

P = A + B

$G = A \cdot B$

Stage 2 - First Order Propagate / Generate Unit:

Each group of four generate and propagate signals from the previous stage are used to produce the first order propagate and generate vectors according to the following equations:

PO = PO P1 P2 P3

GO = G3 + G2 P3 + G1 P2 P3 + G0 P1 P2 P3

P1 = P4 P5 P6 P7

G1 = G7 + G6 P7 + G5 P6 P7 + G4 P5 P6 P7

P2 = P8 P9 P10 P11

G2 = G11 + G10 P11 + G9 P10 P11 + G8 F9 P10 P11

P3 = P12 P13 P14 P15

G3 = G15 + G14 P15 + G13 P14 P15 + G12 P13 P14 P15

Stage 3 - First order Carry Lookahead Unit:

First order propagate / generate vectors are used with the carry input Cin to produce the intermodular carry signals according to the following equations:

C3 = 60 + Cin PO

C7 = 61 + 60 P1 + Cin P0 P1

C11 = 62 + 61 P2 + 60 P1 P2 + Cin P0 P1 P2

C15 = G3 + G2 P3 + G1 P2 P3 + G0 P1 P2 P3 + Cin P0 P1 P2 P3

Stage 4 - Carry Lookahead Unit:

The final carries are produced in carry lookahead unit

according to the following equations

CO = GO + Cin PO

C1 = G1 + G0 P1 + Cin P0 P1

C2 = G2 + G1 P2 + G0 P1 P2 + Cin P0 P1 P2

C4 = G4 + C3 P4

C5 = G5 + G4 P5 + C3 P4 P5

C6 = G6 + G5 P6 + G4 P5 P6 + C3 P4 P5 P6

C8 = G8 + C7 F8

C9 = 69 + 68 P9 + C7 P8 P9

C10 = G10 + G9 P10 + G8 P9 P10 + C7 P8 P9 P10

C12 = G12 + C11 P12

C13 = G13 + G12 P13 + C11 P12 P13

C14 = G14 + G13 P14 + G12 P13 P14 + C11 P12 P13 P14

Stage 5 - Sum Unit

In the sum unit, the carries are combined with the generate signals to produce the sum bits

Si = Fi ⊕ Ci-1

As before, pipelined registers are used between the stages. The pipelined carry lookahead adder has the advantage of smaller latency time compared to the pipelined ripple carry adder. For a 16-bit pipelined ripple-carry adder, 16 clock cycles are required before the first result is output while the pipelined carry lookahead adder requires only 5 clock cycles. The disadvantage of the pipelined carry lookahead adder is its irregular structure compared to the pipelined ripple -carry adder ( HA & FA array). The throughput rates of both adders are almost the same.

## 2.5.5 PIPELINED MULTIPLIER

Most digital signal processing algorithms require the use of high-speed multipliers. In applications where a is operating on a input data stream, a pipelined multiplier used to improve the throughput rate of the operations. is The maximum clock rate of a pipelined multiplier i s determined by the delay due to one stage, which is equal the delay of a full adder plus a register. Fig. 2.17 shows schematic block diagram of a multiplier array using a the carry-save adder (CSA) technique [3]. It is readily observed that data flows vertically from one stage to the next. The registers, which are placed at the outputs of each individual cells, make the architecture fully pipelined. method results in a high-throughput rate operation. Further improvement in speed is still possible by replacing full adder by two half-adders and then pipelining the each half adders. In this way the throughput rate is determined by the half-adder delay plus a register. Since the chip area increase considerably the area-time product of this design will be higher.

Fig. 2.17 Block Diagram of an 8x8-bit Parallel Pipelined Multiplier

#### CHAPTER 3

## RESIDUE ARITHMETIC AND DESIGN OF HIGH-SPEED RNS ADDER

## 3.1 INTRODUCTION

This chapter describes the representation of a number in the Residue Number System (RNS), and will also discuss the operations of addition, subtraction, and multiplication using the RNS representation. VLSI implementations of RNS adders are discussed and four different realization approaches are presented: Binary adder, look-up table, hybrid, and counter-based method. In the final part of this chapter a pipelined Binary ripple-carry adder is compared with a pipelined RNS adder (ripple-carry-based) and the advantages of the RNS adder over the Binary adder are shown.

## 3.2 RESIDUE REPRESENTATION

The Residue Number System is a nonweighted integer number system which is described by an N-tuple of integers [7]:

called moduli (each number is called a modulus). The representation of an integer X in RNS takes the form of an N-tuple of residues,

$$X = \{x, x, x, \dots, x\}$$

1 2 3 N

Where  $\varkappa$  is the remainder of X when divided by m . The i following set of N equations define  $\varkappa$

$$X = q + x$$

$i = 1, 2, 3, ..., N$

$i i i$

$$X = mi [X/mi] + xi$$

The dynamic range of X is represented by

$$0 \le X \le M$$

$$M = m1.m2....mN$$

The residue representation of a number is unique but the converse of the statement is true only if :

- (1) The set of moduli are pairwise relative prime

- (2) Only numbers within the dynamic range are considered

# Example 1

Consider a Residue Number System with moduli m1 = 3 and m2 = 5. What is the residue representation of X = 13?

For m1 = 3 we obtain [13/3] = 4 and for modulus 5 the integer value is [13/5] = 2. Hence

$$x1 = X - m1 [X/m1] = 13 - 3 * 4 = 1$$

$$x2 = X - m2 [X/m2] = 13 - 5 * 2 = 3$$

Therefore the residue representation of 15 is  $\{1,3\}$ Table 3.1 shows the residue representation of the numbers -4

to 20 for moduli 3,5.

Examination of table 3.1 shows that residue representation is periodic (in this case the period is 15). If the Residue Number System is restricted to a single period, ambiguity in this system will be prevented.

| Integer | Residue  <br>  Digits |          | Integer | Résidue  <br>  Digits  <br>  <br>  moduli |          |

|---------|-----------------------|----------|---------|-------------------------------------------|----------|

|         | moduli                |          |         |                                           |          |

|         | 3<br>-!               | 5 !<br>! |         | :3<br>:!                                  | 5 :<br>: |

| -4      | . 2                   | 1 !      | 9       | . 0                                       | 4 :      |

| -3      | 1 0                   | 2        | 10      | 1 1                                       | 0 ;      |

| -2      | 1 1                   | 3 (      | 11      | 1 2                                       | 1 ;      |

| -1      | 1 2                   | 4 (      | 12      | 1 0                                       | 2        |

| 0       | 1 0                   | 0 !      | 13      | 1 1                                       | 3 !      |

| 1       | 1 1                   | 1        | 14      | 1 2                                       | 4 ;      |

| 2       | 1 2                   | 2        | 15      | 1 0                                       | 0 :      |

| 3       | ; 0                   | उ ।      | 16      | ; 1                                       | 1 1      |

| 4       | 1 1                   | 4 1      | 17      | 1 2                                       | 2 :      |

| 5       | 1 2                   | 0 :      | 18      | 10                                        | 2 :      |

| 6       | ; 0                   | 1 :      | 19      | 1 1                                       | 4 1      |

| 7       | 1 1                   | 2 1      | 20      | 1 2                                       | 0:       |

| 8       | : 2                   | 3 !      |         |                                           |          |

Table 3.1

## 3.3 RESIDUE ARITHMETIC

For the residue number system with moduli m1, m2, ...., mN, let X and Y be represented by residue digits.

Addition, subtraction, and multiplication of residue numbers  $\boldsymbol{X}$  and  $\boldsymbol{Y}$  are given by

The above equations imply that addition, subtraction, and multiplication in residue number system can be performed completely independently and, hence, in parallel on each residue digit. The absence of a carry (or borrow) between

digits in residue arithmetic gives an inherent speed advantage to the system.

Note that in the above equations each operation (addition, subtraction, and multiplication) is obtained modulo M. Hence if, for example, sum X + Y exceeds M, an ambiguity will arise.

# Example 3.2:

For the moduli 3 and 5, add, subtract, and multiply X=2 and Y=7.

#### Solution:

The validity of these operations may be checked by looking at the table 3.1.

#### 3.4 VLSI IMPLEMENTATION OF RNS ADDERS

In this section four different realization approaches for modulo m adders are analyzed. The implementation methods are as follows:

- I Binary-based (random logic) RNS adders

- II- Look-up table implementation

- III- Hybrid method

- IV Counter-based RNS adder

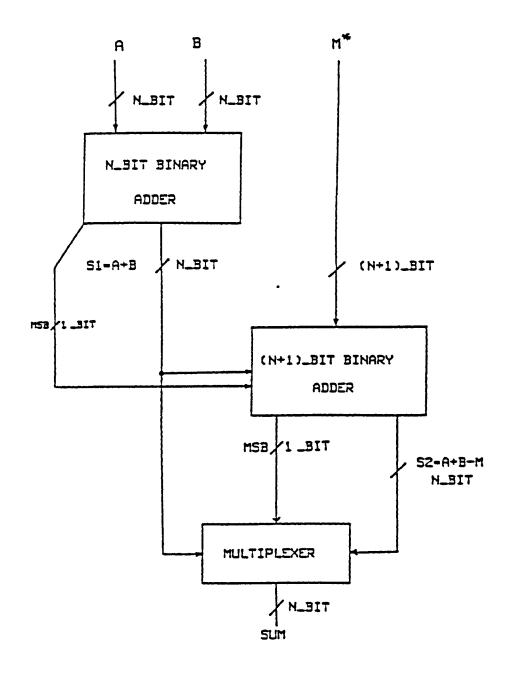

## 3.4.1 BINARY-BASED (RANDOM LOGIC) RNS ADDER

To achieve a high throughput rate, the RNS adder implemented with combinational logic. The architecture of a RNS adder is shown in figure 3.1 [2]. general Two binary adders are used to perform the RNS addition. The first adder computes S1 = A + B and the second adder computes S2 = A + BThe carry overflow which results from the second adder indicates whether S1 is the correct answer or S2. carry overflow is zero the correct answer is S1. otherwise S2 is the right answer. Any of the types of highspeed binary adders, discussed in chapter 2, can be used for the implementation of this residue adder. The throughput rate is achieved by using pipelined ripple-carry or carry look-ahead adder structures. In section 3.5 we give details of the architecture of the pipelined ripple-carrybased RNS adder.

## 3.4.2 LOOK-UP TABLE RNS ADDER

This method is based on storing the RNS addition in a look-

Fig. 3.1 Modulo m RNS Adder

A: ADDEND

B: AUGEND

H: 2'S COMPLEMENT OF THE MODULUS

up table. The total number of memory locations required for a word length of k-bits is k(22\*) entries. For large moduli, a large capacity memory is required in this approach and this limits the speed of operation. One of the advantages of the look-up table method is the large savings in hardware for fixed operands. Since constants can be added, subtracted, or multiplied simply by changing the RNS addition table, these are often referred to as "free operations" [8].

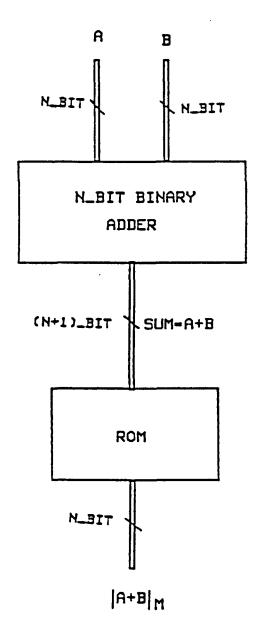

## 3.4.3 HYBRID METHOD

This approach combines both random logic binary adder modules and look-up table modules [9]. Fig 3.2 shows an RNS adder using the hybrid method. It consists of a k-bit binary adder and a (k+1)-bit address ROM. The ROM is used to correct the output of the binary adder and to provide free operations with constants.

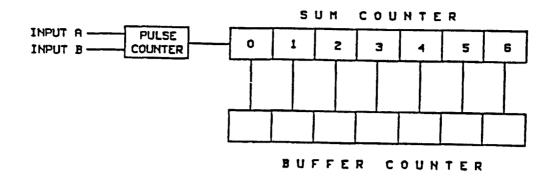

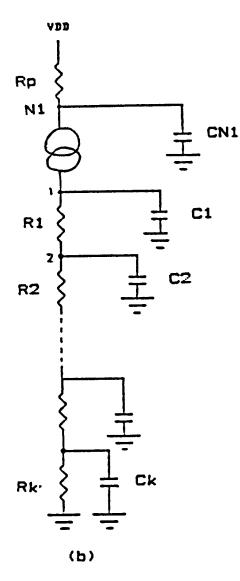

## 3.4.4 COUNTER-BASED RNS ADDER

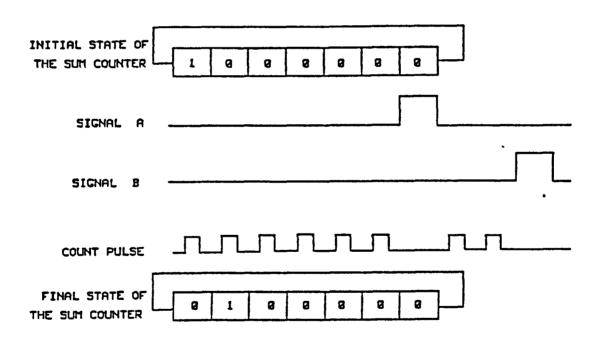

In this approach, residue addition is performed by a ring counter [10]. The schematic diagram of the adder is shown in Fig. 3.3. The adder consists of a counter-pulse generator, a sum counter, and a buffer counter. The addition time of two m-bit numbers is performed in 2m clock cycles. The ring counter is constructed by D-type flip-flops cascaded in a feed-back shift register form. The number of flip-flops is equal to m (modulus). It is obvious that X mod m is obtained by shifting the data X times. The time chart of the adder is shown in Fig 3.4, for the operation !6 + 2:7.

Fig. 3.2 An RNS Adder Using the Hybrid Approach

Fig. 3.3 A Counter-Based RNS Adder

Fig. 3.4 Time Chart of the RNS Adder of Fig. 3.3

# 3.5 PIPELINED RIPPLE-CARRY RNS ADDER

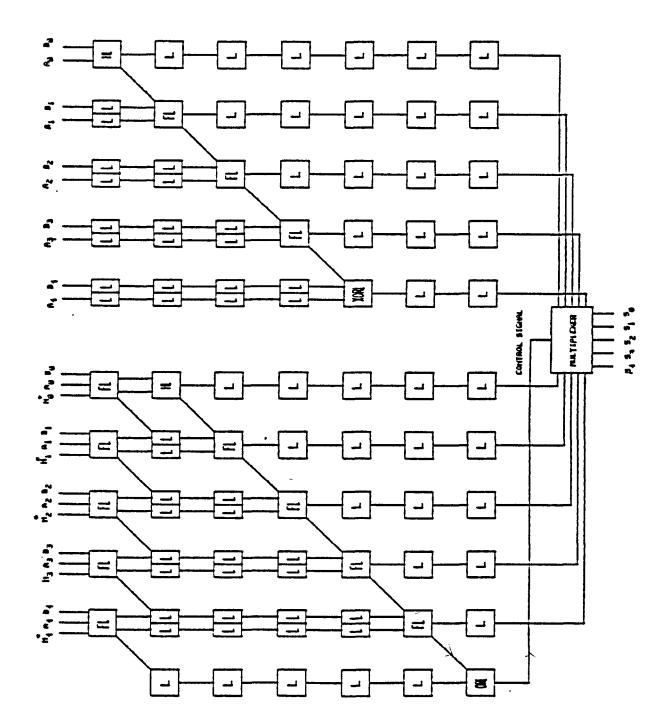

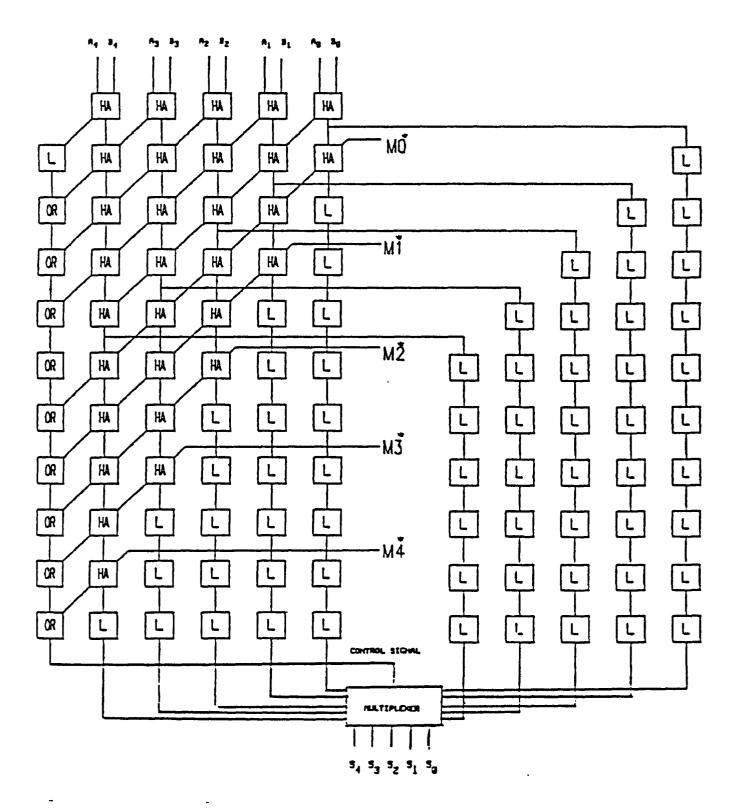

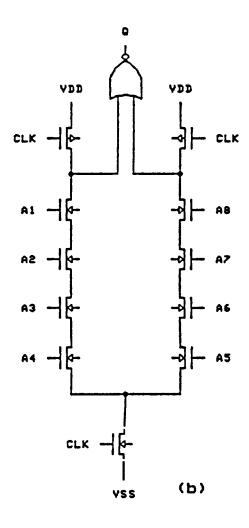

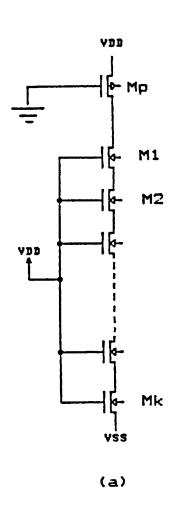

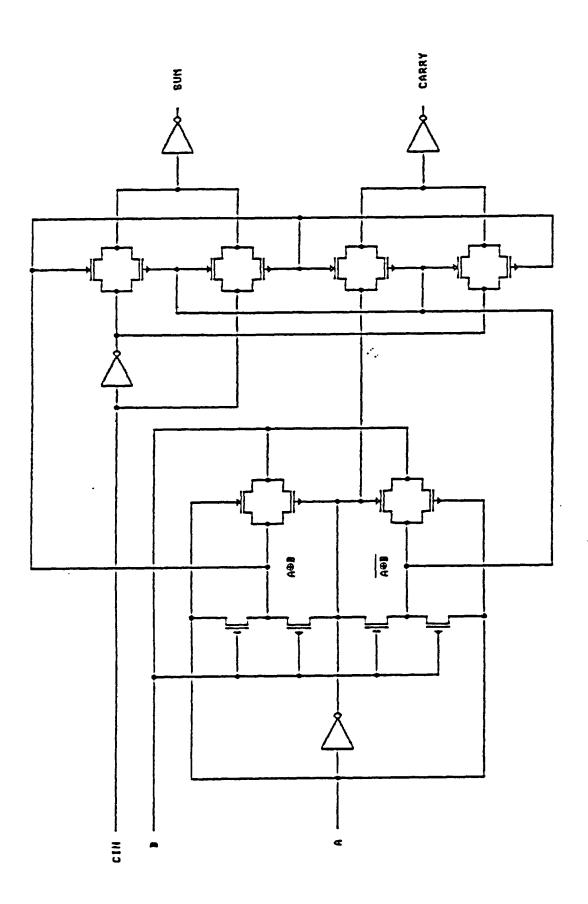

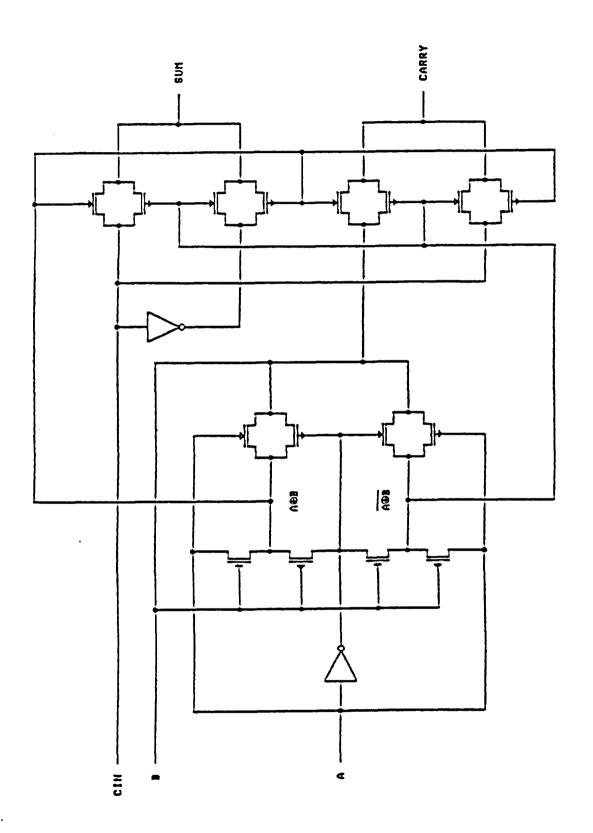

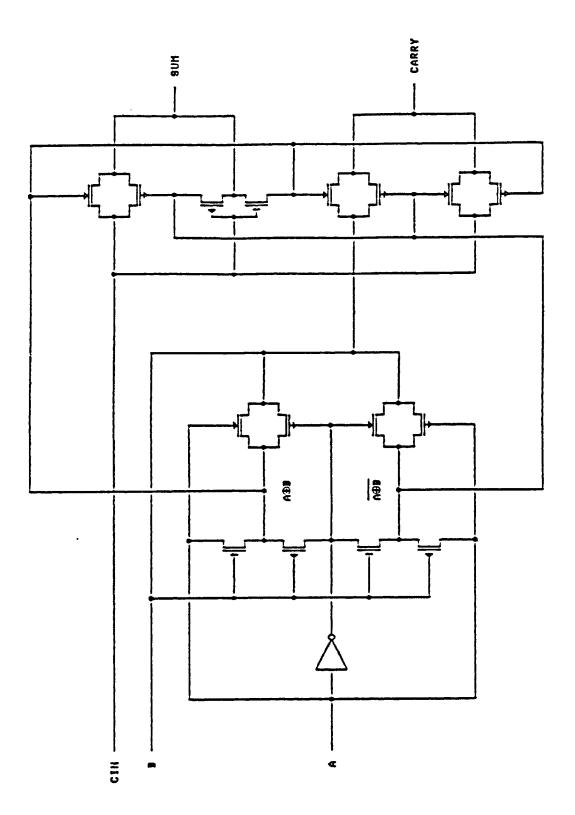

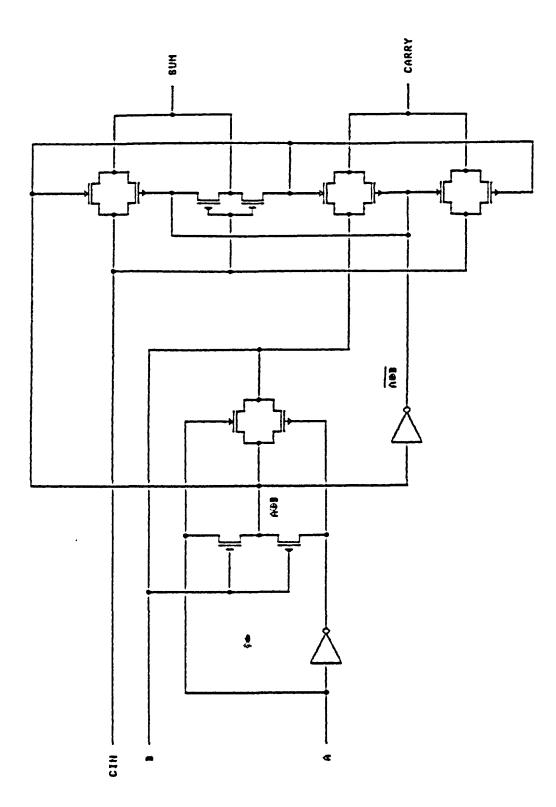

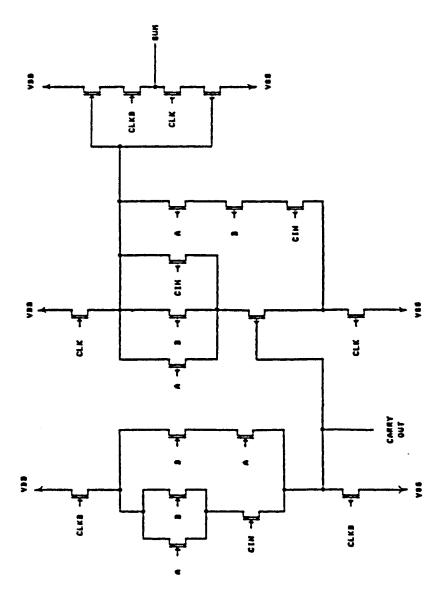

The schematic block diagram of the pipelined ripple-carrybased modulo-M adder is shown in Fig. 3.5. The carry save adder technique is utilized to obtain the maximum throughput rate which reduces to the delay of a single full adder plus a register. The two-operand pipelined adder performs the binary addition of the two numbers S1 = A + B. The threeoperand pipelined adder performs the binary addition of A, B, and Mc, where Mc is the 2's complement of the base ( M ). The carry overflow (Co ) which is generated by the threeoperand adder is used as a control signal to a multiplexer to enable the selection of the correct output. Higher throughput rate is obtained by using half adders in the design of pipelined RNS adder. Figure 3.6 shows the schematic diagram of such an adder.

A 5-bit pipelined RNS adder (FA array) has been implemented using Jum CMOS technology. Appendix B shows the chip layout of this adder.

# 3.6 COMPARISON OF THE PIPELINED RIPPLE-CARRY BINARY AND RNS ADDERS

In this section it will be shown that for a wide-dynamic range of operation, the RNS adder offers advantages over the binary adder in four areas: hardware complexity; speed; testability; latency time. The factor linking these advantages is that RNS arithmetic permits a wide-dynamic arithmetic range to be broken into several independent small-dynamic ranges.

A 5-bit Pipelined Ripple-Carry RNS Adder (FA Array) พ เม Fig.

Fig. 3.6 A 5-bit Pipelined Carry Save RNS Adder (HA Array)

## 3.6.1 HARDWARE COMPLEXITY

Consider the pipelined ripple-carry Binary adder illustrated in Fig. 2.15. It is assumed that each cell is realized as a combinational logic circuit. The system parameters are defined as:

N : Dynamic range of the adder (in bits)

Nfa : The total number of Full adders

NI : The total number of latches

Tfa : Delay time of the Full adder cell

Tl : Delay time of the latch

Tlat.: Latency time of the system

Fclk: maximum clock frequency

For an N-bit pipelined ripple-carry binary adder we need

Nfa = N

N1 = N (3N + 1)/2

As we can see from these equations the number of the latches is proportional to  $N^2$ . For large values of N, the total number of latches will be very large. One possible way of reducing the number of the latches is to partition N such that

N < n1 + n2 + n3 + ... + nk

This is a natural effect of using the Residue Number System, where operations are performed over several rings in parallel.

Consider the pipelined system illustrated in Fig 3.5. Let us define the following parameters

ni : Dynamic range of the i-th residue adder

k : Total number of modules

'(Nfa)i : Number of full adders in the i-th module

(N1)i : Number of latches in the i-th module

(Nmux)i : Number of multiplexers in the i-th module

For an ni-bit pipelined RNS adder we need

(Nfa)i = 3ni

(N1)i = 3ni(ni + 1)

(Nmux)i = ni

It should be mentioned that the modulo (2<sup>m</sup>) addition is performed by an ordinary m-bit binary adder with carry overflow discarded.

So the pipelined RNS adder requires;

$$Nfa = \sum_{i=1}^{k} [(Nfa)i]$$

$$N1 = \sum_{i=1}^{k} C(N1)iJ$$

$$N_{\text{mux}} = \sum_{i=1}^{k} [(N_{\text{mux}})_{i}]$$

We will show by an example: in the next section that the comparison between the RNS and Binary adders depend on dynamic-range; the higher the dynamic range, the greater the savings.

# 3.6.2 THROUGHPUT RATE

In the pipelined structure the synchronization of the data transfer is made by the use of a global clock. One of the problems with this type of global timing is the clock skew, which becomes intolerable for very-large-scale arrays.

Controlling clock skew in VLSI systems is a big problem because the clock transition time is fairly long compared to the propagation delay through a fast MOS gate. The following quotation is from A. Fisher and H.T. Kung [11];

" Unfortunately, large clocked systems can be difficult to implement because of the inevitable problem of the clock skews and the delays which can be especially acute in VLSI system as the feature size shrinks"

The clock skew problem is alleviated by using a pseudo twophase clock design at the cost of less speed and extra area due to the second runners.

Clock skew is not a significant problem in RNS because RNS implementations require several small-scale arrays which can also be clocked with two phases (single clock).

## 3.6.3 TESTABILITY

One of the critical factors in VLSI design is testing complex digital circuits. Consider, for example, a 30-bit binary adder. To test this adder exhaustively a sequence of (200) inputs must be applied to test the circuit. Assuming one had the pattern and applied them at a rate of 1-us per pattern, the testing will take about 36 thousand years[12]! It is clearly not feasible to do a complete functional test of this circuit. There are some techniques which enable one to generate a test vector which is of reasonable size and also covers about 90% of the faults. Now consider the same 30-bit addition in RNS. Several modules of 5 and 6-bit RNS adders will be adequate to do the job. The test vectors (

exhaustive testing ) would be a few sequences of (210) inputs. The same pattern tester would be able to test this adder in a few milliseconds. This ease of testing is again due to working with small dynamic ranges within the RNS.

## 3.6.4 LATENCY TIME

The latency time of an N-bit pipelined ripple-carry Binary adder is

Tlat. = N\*Tclk

The latency time of the pipelined RNS adder depends on the module with the highest dynamic range ( n )

Tlat. = (n+1)\*Tclk

It is obvious that n<<N and therefore latency time of the RNS adder is generally much less than the binary adder.

#### 3.7 EXAMPLE

In this example it will be shown that a 20-bit pipelined RNS adder has advantages over its binary counterpart.

The dynamic range of 20-bit is equal to 1048580. A Residue Number System with moduli 31, 16, 15, 13, and 11 has a dynamic range of 1063920; the systems are virtually equivalent in dynamic range. The necessary hardware to realize a 20-bit Pipelined Binary adder is:

Nfa = 20

N1 = 610

The Pipelined RNS adder with moduli (31, 16, 15, 13, 11) needs;

Nfa = 55

N1 = 296

$\cdot$ Nmux = 17

It should be noted that the modulo 16 adder is simply a 4-bit binary adder.

In order to make a comparison between the two systems assume that the area of a register is of unit area. The area of the full adder is almost equal to two unit areas and the area of a multiplexer is almost half the unit area. Therefore:

Area of the 20-bit Pipelined Binary adder = 650 unit

Area of the 20-bit Pipelined RNS adder = 414 unit

This means a saving of 37 percent in area for RNS adder.

Latency time the of 20-bit Pipelined Binary adder = 20\*Tclk

Latency time of the 20-bit Pipelined RNS adder = 6\*Tclk

and this is less than 1/3 of its Binary counterpart.

The improvement in testability and clock skew in RNS adders is evident because of the smaller size of the arrays.

In the same manner it can be shown that the use of RNS for 30-bit addition, results in about a 50 percent saving in area.

## 3.8 SUMMARY

In this chapter it has been shown that for a wide-dynamic range of operations, pipelined RNS adders offer the following advantages over their binary counterparts:

# (I) - Hardware complexity

The chip area of a pipelined binary adder is proportional to  $N^2$ , whereas the chip area of a pipelined RNS adder is proportional to  $\sum_{i=1}^{K} ni^2$ . By proper selection of the moduli

one can have

Which means a saving in chip area for the RNS adder.

# (II) - Testability

For pipelined binary and RNS adders, the computer run time to do the test generation and fault simulation is approximately proportional to  $N^3$  and  $\sum_{i=1}^K ni^3$ , respectively [12]. As before by proper selection of moduli an improvement in testability of RNS adders can be achieved since

## (III) THROUGHPUT RATE

In the pipelined architecture, clock skew increases with the size of the array. As clock skew increases, the throughput rate decreases. Since in RNS ni << N, clock skew becomes insignificant and hence the array can be clocked at higher speeds.

# (IV) Latency time

The latency time of pipelined binary adders depends on the number of bits of the bigger operand, N, whereas the latency time of the pipelined RNS adder depends on the module with the highest dynamic range, n. Since n<<N, therefore, latency time of the RNS adder is generally much less than that of the binary adder.

#### CHAPTER 4

#### CIRCUIT AND LOGIC DESIGN WITH CMOS

#### 4.1 INTRODUCTION

CMOS emerged as the most suitable technology for VLSI design and will be the dominant technology for the decade [13]. The greatest advantage of CMOS over NMOS is its inherent low power characteristics. Since the heat generated by the power dissipation within the chip is difficult remove from the package and because the performance of the MOS transistors decreases as the temperature of the increases, the design of NMOS VLSI circuit becomes quite complex [14]. NMOS has had some advantages in terms of speed silicon area needed to produce the same functionality, but with shrinking feature size and the utilization dynamic circuit design, those advantages are evaporating. As transistor dimensions are reduced, the current delivered by PMOS is approaching the current provided by NMOS of the same size. So small CMOS circuits are not much slower than their NMOS counterparts [15]. Another advantage of CMOS is better noise margin characteristics.

In the next Section we are going to examine different CMOS logic families.

# 4.2 CMOS LOGIC TECHNIQUES

There are two fundamental approaches to the implementation of logic circuits in CMOS VLSI design.

- (I) Static logic where electrical connections and feedback are used to transfer and maintain the logic levels.

- (II) Dynamic logic where logic levels are transferred by means of a clock and charge storage on capacitive nodes is employed to retain the logic levels between the clock periods.

Some advantages of static logic are:

- Good noise margin

- No need for clock driver circuits

- Logic level retention at D.C.

- Fredictable performance at high temperature

Replacement of static cell by dynamic can offer potential improvements in three areas:

- Power dissipation

- Silicon area

- Speed

Some disadvantages of dynamic logic circuits are :

- Poor noise margin

- Need for clock driver circuits

- Logic retention is not achieved at D.C.

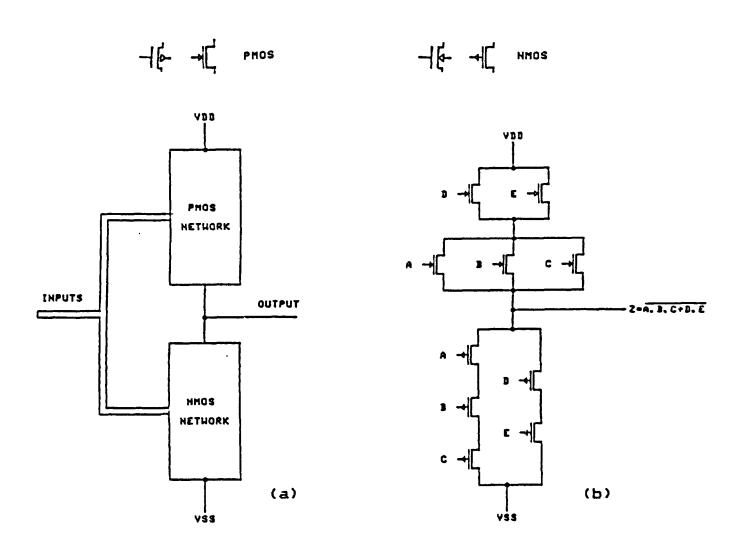

## 4.2.1 STATIC CMOS COMPLEMENTARY LOGIC

In the conventional static CMOS technique ( fully complementary CMOS logic ) the logic function of each gate is implemented by two combinational networks. Figure 4.1(a) shows the structure of the general CMOS static gate. The top PMOS network acts as a good switch to transmit undegraded logic 1 to the output and the bottom NMOS network provides

good logic O switching.

The CMOS network that performs AND/OR INVERT (AOI) function for one 3-input AND, and one 2-input AND (32 AOI), is shown in Fig. 4.1(b). Several points may be noted from this example. Firstly the NMOS network is the logical dual of the PMOS network. Secondly, for all input combinations there is always a path from Vdd (logic 1) or Vss (logic 0) to the output and the full supply voltages appear at the output. All CMOS static gates may be designed as ratioless circuits [30]. Thirdly, for any input combination there is never a path from Vdd to Vss, except for the very brief period when the output or inputs are undergoing transitions.

## 4.2.2 PSEUDO-NMOS LOGIC

One of the major disadvantages of the fully complementary CMOS approach is that CMOS circuits occupy more area than NMOS circuits. For example the 32AOI function could be made with 6 transistors in NMOS or pseudo-NMOS, as shown in Fig. 4.2(b). General pseudo-NMOS logic is shown in Fig. 4.2(a). Pseudo-NMOS is equivalent to NMOS except that the depletion or enhancement NMOS load is replaced by a P-device. The main problem with this gate is the high static power dissipation that occurs whenever the NMOS network is in a low impedance state.

In complementary CMOS circuits for every gate driven by the output there is a connection to both an N-device and a P-device. As a result the capacitive load on gates of a fully complementary CMOS circuit is at least a factor of two

Fig. 4.1 (a) General CMOS Complementary Logic (b) Fully Complementary CMOS-32AOI Gate

Fig. 4.2 (a) General Pseudo-NMOS Logic (b) Pseudo-NMOS 32AOI Gate

higher than the load on a pseudo-NMOS circuit. However, in pseudo-NMOS the pull-up device is always on even when the gate is pulling down. This, in turn, slows the pull down. The gain ratio of the P-transistor load to N-transistors has to be selected such that the correct switching is ensured. Usually the gain of the pull-up is chosen smaller than half the pull-down( Ratioed Logic). As a result the speed of the pseudo-NMOS and static CMOS are close. Pseudo-NMOS has less load capacitance but also smaller pull-up gain. The trade-off of choosing one or the other is between the low power of the CMOS and the low area of the pseudo-NMOS.

# 4.2.3 PASS TRANSISTOR LOGIC (TRANSMISSION GATE)

Pass transistor logic is a popular technique in NMOS circuits. Mead and Conway used pass transistors in the design of latches, flip-flops, multiplexers and some combinational logic structures. Pass-network implementation of a logic function results in a faster gate with less area and power dissipation than using conventional logic design. Formal methods for deriving pass transistor logic have been presented for NMOS [16]. Figure 4.3(a) shows the pass gate and its logical function. Figure 4.3(b) shows the basic logic functions — AND, NAND, OR, NOR and XOR — that can be implemented with the assistance of pass transistors.

In CMOS, these structures can be replicated by using a full transmission gate for each original N-transistor. One of the advantages of transmission gates over pass transistors is the ability to pass both logic 1 and 0 without degradation.

| PASS_GATE TRUTH TABLE |                |           |  |

|-----------------------|----------------|-----------|--|

| INPUT                 | CONTROL OUTPUT |           |  |

| 8                     | 8              | UNDEFINED |  |

| 1                     | 8              | UNDEFINED |  |

| 9                     | 1              | 9         |  |

| 1                     | 1              | 1         |  |

(a)

| OUTPUT      | × | Y |

|-------------|---|---|

| BA          | 8 | В |

| ĀB          | 1 | B |

| A+B         | B | 1 |

| A+B         | B | 8 |

| A®B         | B | B |

| <del></del> |   |   |

Fig. 4.3 (a) Pass-Transistor logic Model

(b) Pass Transistor Structures for Basic Logic

Functions - AND, NAND, OR, NOR, and XOR

Figure 4.4 shows the schematic of a novel 6-transistor transmission gate Exclusive-OR gate [30]. The same function when realized in conventional static CMOS requires 14 devices. Transmission gates can be used in the design of half adder, Fig. 4.5, which results in a very compact circuit. This logic technique can also be used in the design flip-flops. The schematic of a Pseudo 2-phase flip-flop is shown in Fig. 4.6. It uses a 2-phase nonoverlapping NMOS scheme ( Mead and Conway [34]) adds clocking and complementary clocks (clk1b & clk2b). Note that clk1.clk2=0 for all time. During clk1, the first transmission gate is closed. thereby the input level is stored on the capacitance the inverter. During c1k2, the of gate is open and the second transmission gate transmission is closed, causing the inverse of the stored logic value to be placed on the gate of the second inverter. The delays between the clocks are chosen to ensure that, for worst case clock skew, the two clocks do not overlap. A 2-phase dynamic flip-flop is shown in Fig. 4.7 . A clock

A 2-phase dynamic flip-flop is shown in Fig. 4.7. A clock race condition, similar to that experienced in pseudo 2-phase clocking, can arise in this structure. If clkb is delayed from the clk signal, we see that the first TG NMOS device can be turned on at the same time as the second TG N-transistor. So the clock skew must be carefully studied and minimized.

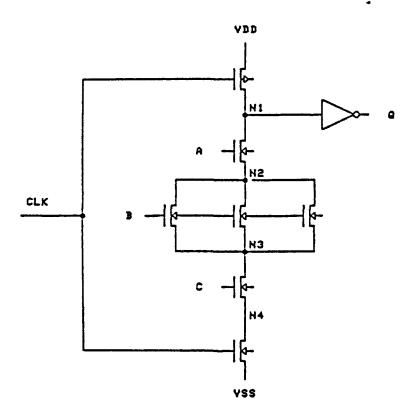

# 4.2.4 CLOCKED CMOS LOGIC ( C MOS )

The clocked CMOS circuitry is basically composed of

Fig. 4.4 Transmission Gate (TG) XOR Circuit

Fig. 4.5 Transmission Gate Half Adder Circuit

Fig. 4.6 Pseudo Two-Phase TG Flip-Flop

Fig. 4.7 Two-Phase TG Flip-Flop

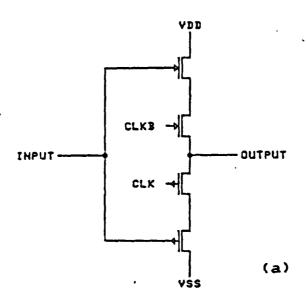

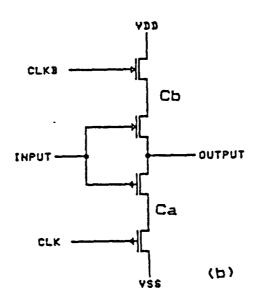

conventional static CMOS and two extra MOS switches connected in series [17]. Two types of clocked CMOS inverter are shown in Fig. 4.8. In Figure 4.8(b) the MOS switches are sandwiched between the CMOS inverter while in Fig. MOS switches are connected on both sides of the conventional CMOS inverter. The operation of the clocked CMOS inverter is as follows. Whenever clk = 1 the circuit acts as a conventional CMOS inverter. When clk = 0, the output holds the previous value.

When the input data makes a transition and the clock pulses are not supplied to the clocked CMOS inverter of Fig. 4.8(b), some of the charges stored in the output will be transferred from the output capacitance to the parasitic capacitances Ca or Cb. This is called charge sharing and happens whenever there is a phase difference between the clock pulses and input data pulses. The circuit of Fig. 4.8(a) does not have such problem.

The clocked CMOS circuit of (32 AOI) is shown in Fig. 4.9. The main use of this logic technique is to form clocked circuits that incorporate latches or interface with other dynamic logics. It will be shown later that clocked CMOS latches and shift registers are more compact than conventional static CMOS counterparts.

#### 4.2.5 BASIC DYNAMIC CMOS LOGIC

Dynamic CMOS circuits generally work based on the principle of precharging a node to a particular level (usually high for NMOS), while the current path to the other level (ground

Fig. 4.8 (a) Clocked CMOS Inverter (without Charge Sharing)

(b) Clocked CMOS Inverter (with Charge Sharing)

Fig. 4.9 Clocked CMOS 32AOI Gate

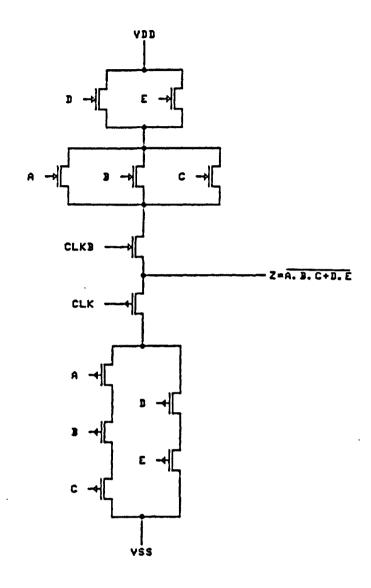

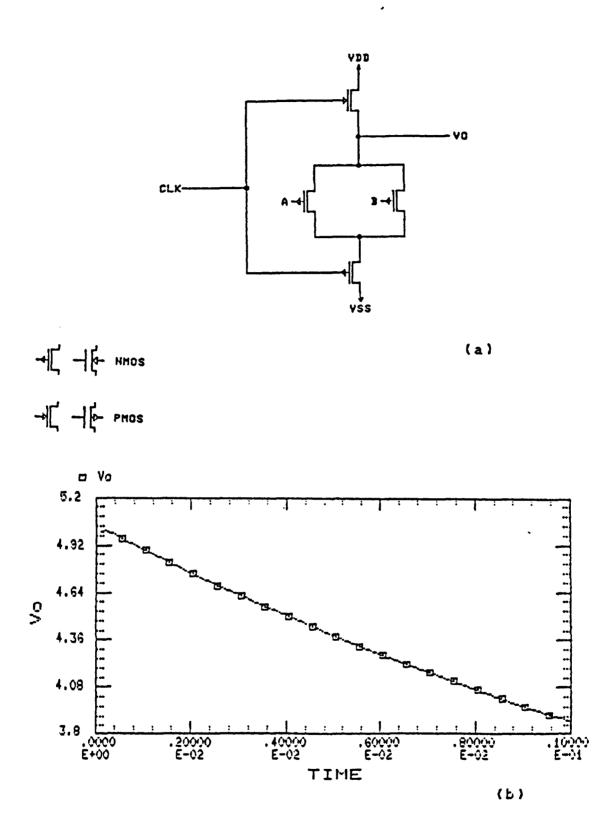

for NMOS) is turned off [18]. During the precharge inputs to the circuit change. The next phase the operation is the evaluate phase. Here the path to Vdd turned off by a clock and the path to ground (Vss) is turned Depending on the state of the inputs, the output either be pulled down or will float at the high level. The fundamental characteristic of dynamic logic is that employs charge storage on capacitive 'soft' nodes to retain logic levels between the clock periods. Charge leakage from such a soft node limits the minimum clock frequency. Figure shows a dynamic NOR2 gate. The discharge diagram of the soft node obtained from SPICE is shown Fig. 4.10(b). The time constant of this curve is a milliseconds. The typical value for the minimum clock frequency of this circuit is about 1-2 KHz.

schematic circuit of the dynamic CMOS gate for (32AOI) function is given in Fig. 4.11 One the advantages of the dynamic CMOS circuits is the reduced Whereas there are 2n transistors in a silicon area. conventional static CMOS gate, the dynamic style needs only n+2 transistors. The load capacitance of dynamic CMOS circuits is the same as the pseudo-NMOS gate but full pulldown current is available. The pull-up time is improved by virtue of the precharge transistor, and power dissipation is closer to static CMOS than static pseudo-NMOS. Since in dynamic CMOS each gate must be precharged high every cycle, even if its output is to continue low, there is some power penalty compared to static CMOS.

Fig. 4.10 (a) Dynamic CMOS NOR2 Gate

(b) Discharge Timing Diagram of the Precharged

Node (Vo), Obtained from SPICE

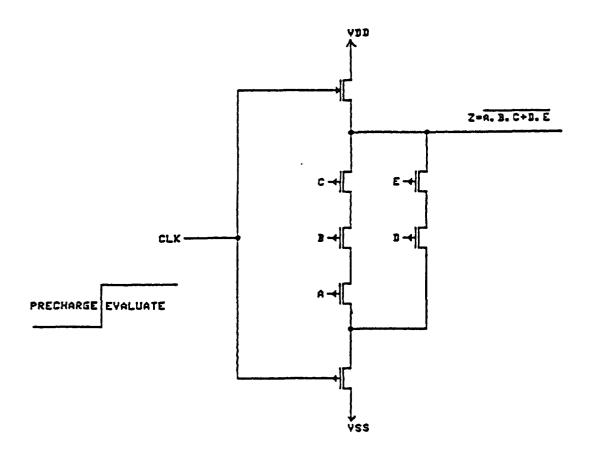

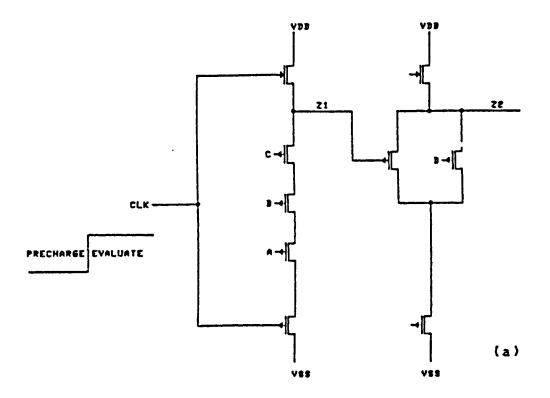

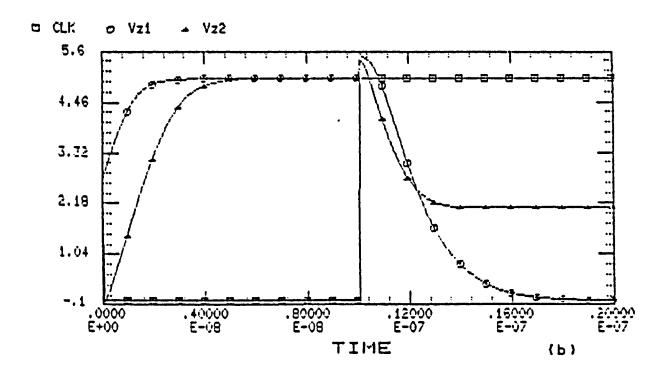

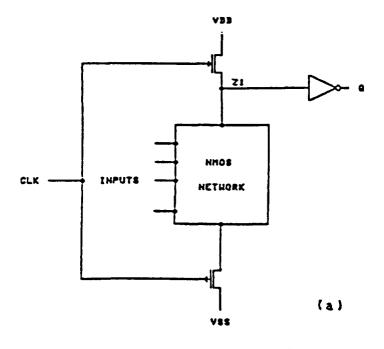

Fig. 4.11 N-Type Dynamic CMOS 32AOI Gate