## University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

1-1-1964

## The logic design of a digital control computer.

Richard E. Shiner University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Shiner, Richard E., "The logic design of a digital control computer." (1964). *Electronic Theses and Dissertations*. 6368.

https://scholar.uwindsor.ca/etd/6368

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# THE LOGIC DESIGN OF A DIGITAL CONTROL COMPUTER

BY

RICHARD E. SHINER

#### A Thesis

Submitted to the Faculty of Graduate Studies Through the Department of Electrical Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at University of Windsor

> Windsor, Ontario 1964

#### UMI Number: EC52549

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

# UMI®

UMI Microform EC52549 Copyright 2008 by ProQuest LLC. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest LLC 789 E. Eisenhower Parkway PO Box 1346 Ann Arbor, MI 48106-1346

AB 14723

Approved by

P.A.V. Thomas

Dr. P. A. V. Thomas Associate Professor

Dr. S. N. Kalra Associate Professor

Mr. N. Dock

Ør. J. N. Deck Associate Professor

#### ABSTRACT

This thesis presents the logic design of a digital control computer presently being constructed at the University of Windsor.

The computer incorporates a pluggable program board, a magnetostrictive delay line memory, several working registers, and an arithmetic unit capable of addition, subtraction, multiplication, and division. The computer has the ability to modify data locations and to execute program jumps. Input facilities accept data from a keyboard and also from an external rotating shaft position digitizer. Output facilities are a set of lamps which indicate the contents of an accumulator register and also an output order which can be used to control an external system.

This thesis includes a complete set of logic diagrams of the computer, which utilizes NAND logic.

**iii**

#### ACKNOWLEDGEMENTS

The author wishes to express sincere appreciation to Dr. P. A. V. Thomas, who supervised this work, for his helpful guidance and advice.

Acknowledgement is also due the National Research Council of Canada for financial assistance provided for this project.

iv

### TABLE OF CONTENTS

| ABSTRACT                                                                                                                                                                                                                                                                                      | <b>i</b> ii                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                              | iv                                               |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                             | v                                                |

| I. INTRODUCTION                                                                                                                                                                                                                                                                               | 1                                                |

| II. SYSTEM DESIGN                                                                                                                                                                                                                                                                             | 2                                                |

| 2.1 The Number System 2.2 The Instruction Format 2.3 Computer Organization 2.4 Delay Line Store 2.5 Registers 2.6 Arithmetic Unit 2.7 Adder/Subtractor 2.8 Multiplication Unit 2.9 Division Unit 2.10 Control Unit 2.11 Program Board 2.12 Modification and Program Looping 2.13 Input/Output | 2<br>3<br>10<br>11<br>12<br>13<br>15<br>18<br>25 |

| III. IMPLEMENTATION                                                                                                                                                                                                                                                                           | 28                                               |

| 3.1 The Logic Elements<br>3.2 The Physical Structure                                                                                                                                                                                                                                          | 28<br>31                                         |

| IV. LOGIC DIAGRAMS                                                                                                                                                                                                                                                                            | 34                                               |

| V. CONCLUSIONS AND RECOMMENDATIONS                                                                                                                                                                                                                                                            | 71                                               |

| REFERENCES                                                                                                                                                                                                                                                                                    | 72                                               |

| APPENDIX                                                                                                                                                                                                                                                                                      | 73                                               |

| VITA AUCTORIS                                                                                                                                                                                                                                                                                 | 77                                               |

**v** .

#### I. INTRODUCTION

The Electrical Engineering Department at the University of Windsor began, in June 1963, the study of a digital control system<sup>1</sup> which requires an on-line digital computer. The exact nature of the problems and programs to be solved by the digital computer were not yet known. It was assumed that, as the research on the control system proceeded, new techniques of controlling would be found. It was decided, therefore, to develop a DIGITAL CONTROL COMPUTER and to incorporate into this computer the desired flexibility. This flexibility would include an extensive list of computer instructions, a suitable means of data storage, and special input and output facilities. This thesis presents the logic design of the digital control computer.

#### II. SYSTEM DESIGN

A concept of the design of the computing system is given.

2.1 The Number Format

The computer works in the binary number system using the two digits, ZERO and ONE. These two digits are represented in the machine by two voltage levels, 0 volts and -6 volts, respectively. The machine data word length is 12 bits long. The signed-2's complement representation is used for negative numbers. The sign of the binary number is denoted by the most significant digit called the sign bit. The 0 and 1 of the sign bit are chosen to represent, respectively, the positive and negative signs. These are taken to mean 0 and -1. The other digits are called the number digits and they have weights of  $2^{-1}$ ,  $2^{-2}$ ,  $2^{-3}$ ,... $2^{-11}$ . Thus, for example

0.0110000000 = 3/8

1.1010000000 = -3/8

Notice that a decimal place is used to separate the sign bit from the number bits. This decimal place does not, however, appear in the machine. The last number may be thought of as -1 + 5/8 = -3/8.

This number system limits the number range to fractions. Furthermore, since one of the external input devices is limited to 10 digits (excluding sign digit), the following range of numbers is adopted:

#

1.10000000000 to 1.111111111 (i.e.  $-1/2 \le x < 0$ ).

This system will give an accuracy of one part in 1024. In practice, all numbers will be reduced to fractions by a suitable scaling factor.

#### 2.2 The Instruction Format

Instructions to be executed by the computer are divided into four parts. The first part specifies the particular order being called for, the second part gives the location number of the stored data, the third part specifies any required register, and the fourth part states whether modification of the data location number takes place.

A complete description of how instructions are entered into the computer is given in section 2.11 below.

#### 2.3 Computer Organization

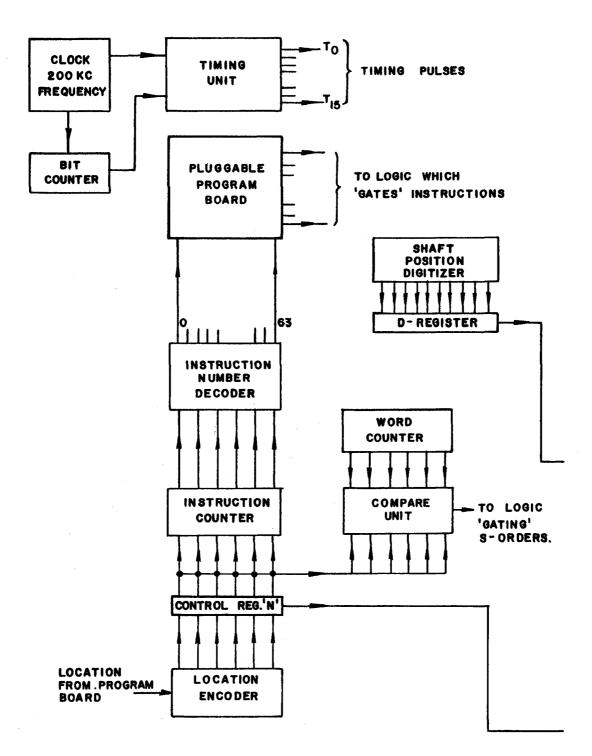

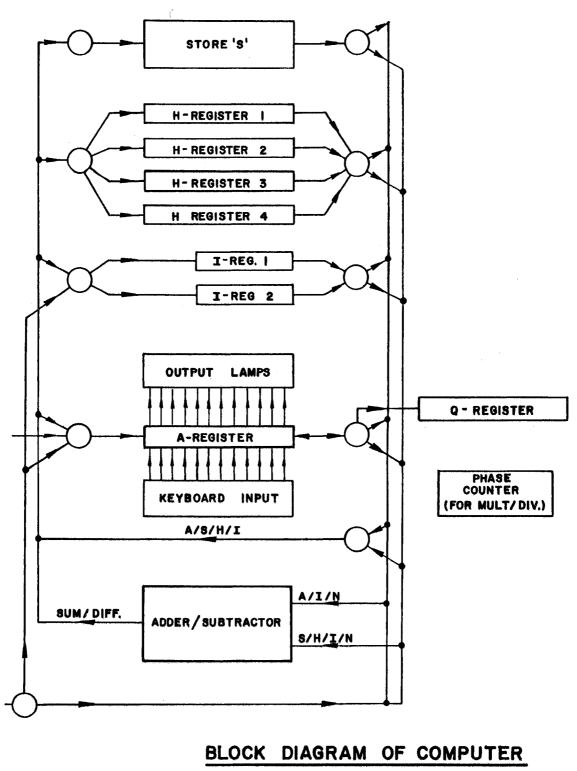

A block diagram of the entire computer is presented in fig. 1. This diagram shows the organization of the computer. It presents the various registers and counters and indicates the general flow of information.

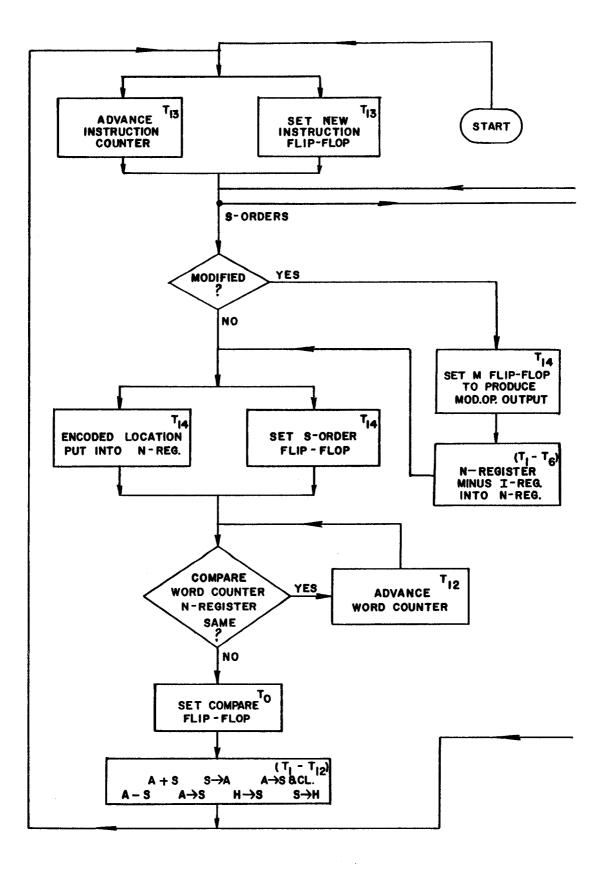

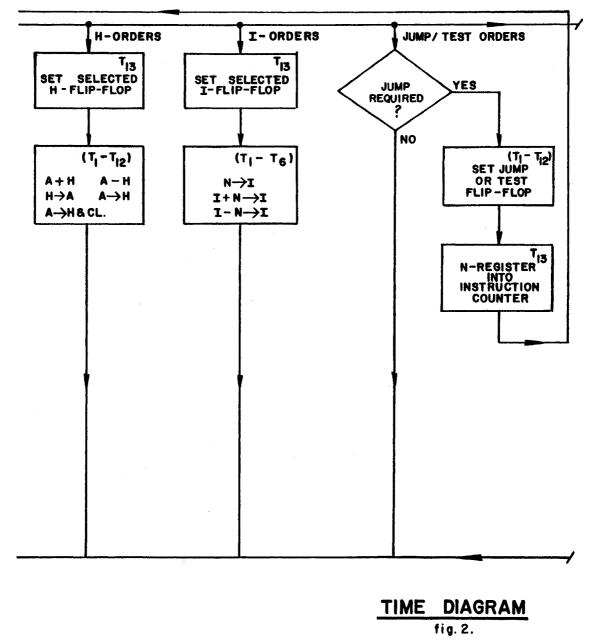

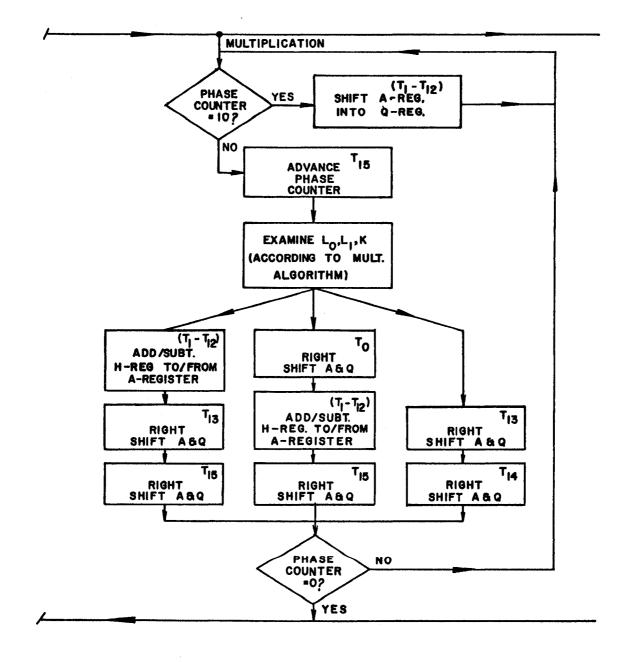

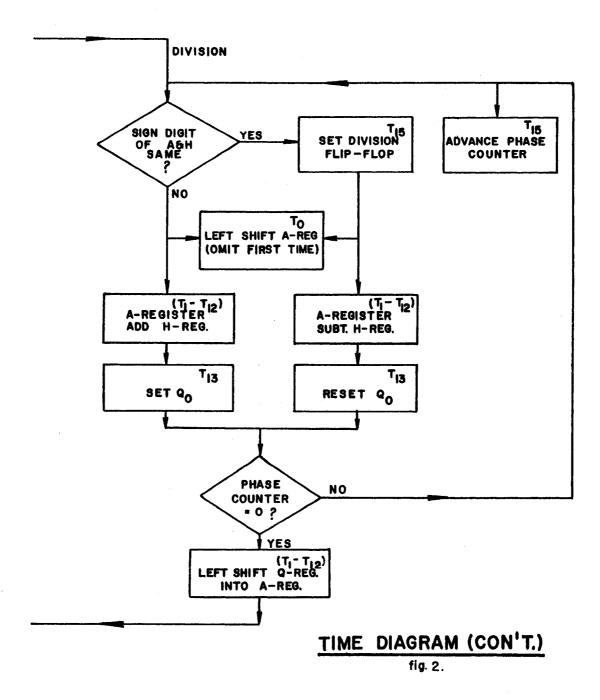

A time diagram for the computer is presented in fig.2. This diagram shows the sequence of operations for each type of instruction.

fig. I.

#### 2.4 Delay Line Store

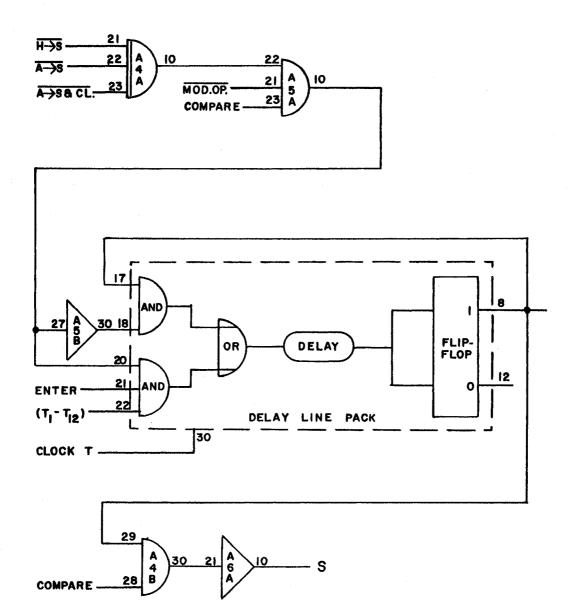

The computer uses a recirculating, magnetostrictive delay line as the main data memory, STORE S. Magnetostrictive delay lines are passive electromechanical devices capable of delaying electrical signals. They reduce the velocity of an electrical wave by converting it to a sound wave and then reconverting it to an electrical signal. The delay line pack includes gating logic for entering information into the memory and a flip-flop to provide both assertion and negation outputs.

STORE S stores 61 data words of 12 bits, each of which are separated by 4 spacer bits to make up a computer word of 16 bits. The data words appear in serial mode at the output of the delay line with the least significant bit coming first and are recirculated to form a continuous, sequential access memory.

The computer operates at a clock frequency of 200 kilocycles per second. Bits appear at the output of the delay line at the rate of 200 thousand per second, or 5 microseconds apart. The delay line has a delay of 4880 microseconds and stores 976 bits of information, i.e. 61 words of 16 bits each.

The words in the STORE S are assigned location numbers LO through L60. Program steps involving S specify the required location number. The computer can modify the location number during execution of the program, if desired.

#### 2.5 Registers

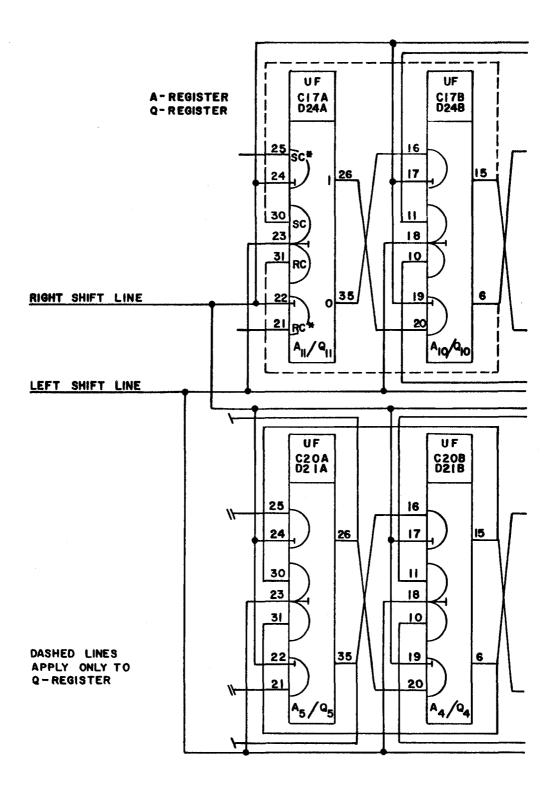

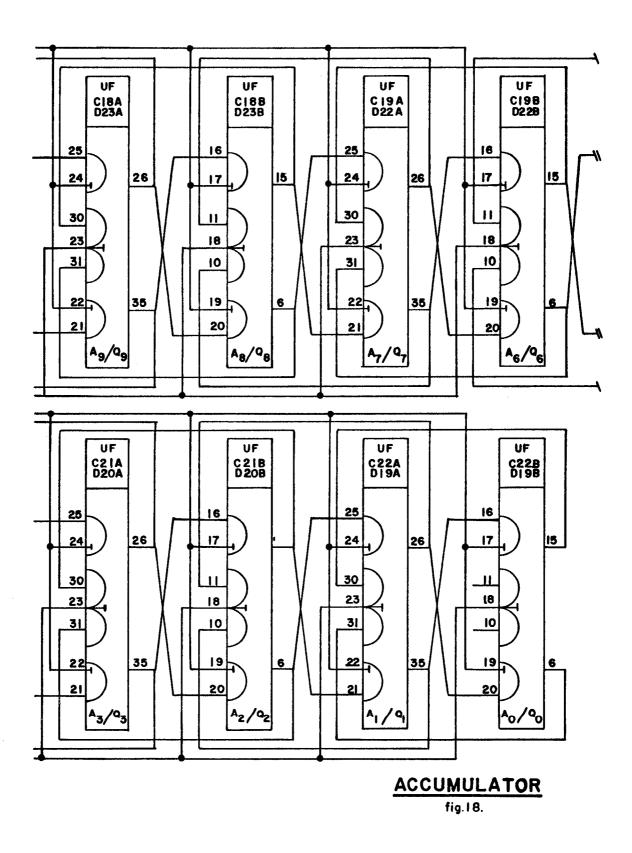

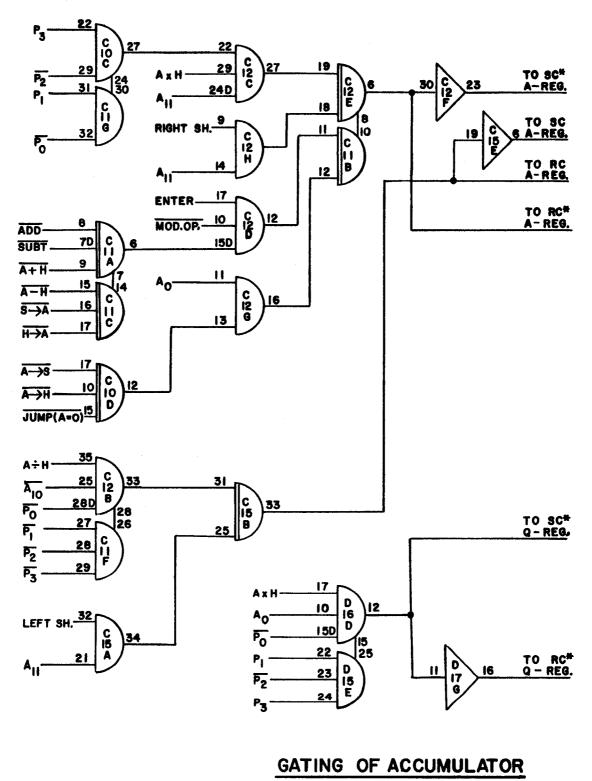

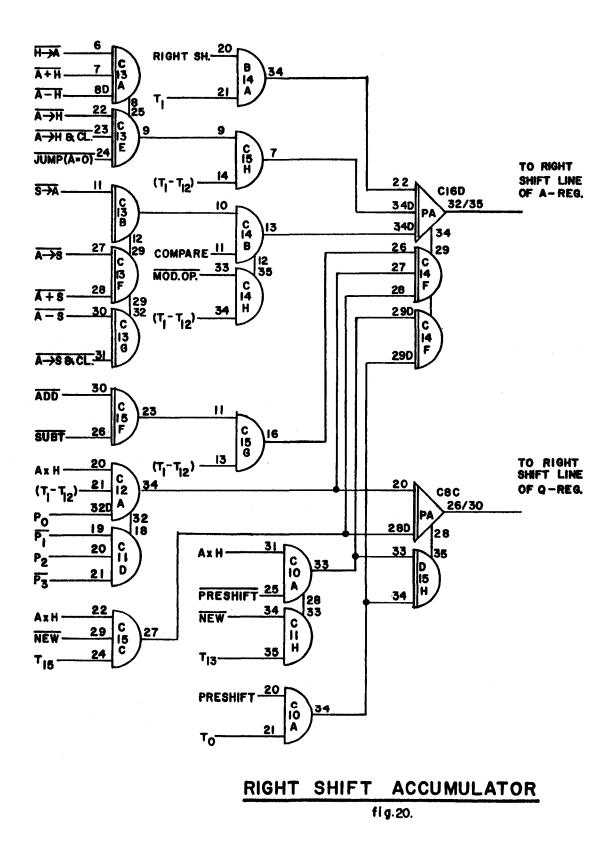

The computer has an accumulator consisting of two, 12 bit, right and left shifting registers called the A-REGISTER and the Q-REGISTER. The A-REGISTER is the main input/output register for communication with the peripheral equipment. It also holds the augend or minuend for addition and subtraction operations and the multiplier and dividend for multiplication and division operations. The A-REGISTER also holds the operand in conditional jump operations. The Q-REGISTER is required for multiplication and division.

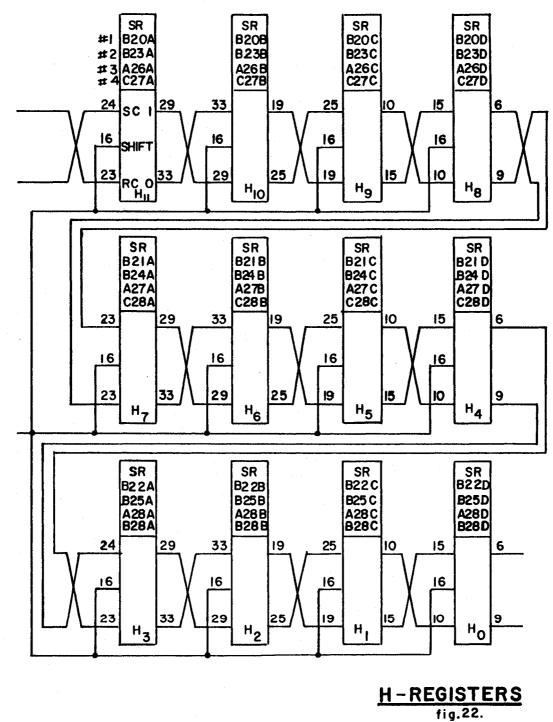

The computer is provided with four, 12 bit, HOLD REGISTERS or H-REGISTERS which serve as an immediate access working store. The H-REGISTERS partly overcome the disadvantage that the delay line store is not immediate access. Any one of the four H-REGISTERS can hold the addend, subtrahend, multiplicand or divisor for the addition, subtraction, multiplication and division instructions, respectively. Transfer instructions move data between the A-REGISTER and the H-REGISTER, and between the S-STORE and the H-REGISTERS.

Also provided are two, 6 bit, INDEX REGISTERS or I-REGISTERS which are required for modification of S-STORE location numbers.

#### 2.6 Arithmetic Unit

The arithmetic unit is capable of addition, subtrac-

11

tion, multiplication, and division. It has a serial ADDER/ SUBTRACTOR unit. The addition and subtraction time is one machine word length (not counting the access time required for operations involving the S-STORE). Multiplication and division are performed by repeated use of the ADDER/SUBTRACTOR. Multiplication time is seven machine word lengths (560 microseconds). Division time is twelve machine word lengths (960 microseconds).

The arithmetic unit can shift the number in the A-REGISTER one bit to the left or one bit to the right. These operations require only one machine word length and are equivalent to multiplying or dividing the number in the A-REGISTER by 2. This provides a fast way of doubling or halving a number.

#### 2.7 Adder/Subtractor Unit

The following symbols are defined.

- X = augend or minuend

- Y = addend or subtrhend

- Z = sum or difference

- W<sub>1</sub> = input carry or input borrow

- C. = output carry

- $B_{o} = output borrow$

The truth table for a full adder/subtractor is is given in fig. 3.

| X | Y | W <sub>i</sub> | Z | Co | Bo |

|---|---|----------------|---|----|----|

| 0 | 0 | 0              | 0 | 0  | 0  |

| 0 | 0 | 1              | 1 | 0  | 1  |

| 0 | 1 | 0              | 1 | 0  | 1  |

| 0 | 1 | 1              | 0 | 1  | 1  |

| 1 | 0 | 0              | 1 | 0  | 0  |

| 1 | 0 | 1              | 0 | l  | 0  |

| 1 | 1 | 0              | 0 | 1  | 0  |

| 1 | 1 | 1              | 1 | 1  | 1  |

fig. 3. ADDER/SUBTRACTOR TRUTH TABLE

This truth table is implemented by the ADDER/SUBTRAC-TOR logic.

#### 2.8 Multiplication Unit

The computer performs multiplication by the serial, repeated addition and subtraction method. An algorithm for multiplication in the signed-2's complement form, developed by A. D. Booth, depends on the examination of the two least significant digits of the multiplier register. This is followed by either an addition or subtraction, or neither, of the multiplicand to the partial product after which a right shift of the partial product and the multiplier takes place. This is repeated until multiplication is complete.

This computer uses a multiple digit multiplication

method<sup>3</sup> which is an extension of the above method and which reduces by almost one-half the time required for multipliction.

The operation is as follows. For the first phase, the multiplier in the A-REGISTER is shifted into the Q-REGISTER. For the following six phases, three digits of the multiplier (the two least significant bits of the Q-REGISTER, and the bit held in the KEEP FLIP-FLOP) are examined according to the algorithm in fig. 4.

|    | Multiplier Keep<br>Digits Digit |   | Algorithm                                |  |  |

|----|---------------------------------|---|------------------------------------------|--|--|

| Ll | <sup>L</sup> 0                  | K |                                          |  |  |

| 0  | 0                               | 0 | Neither add nor subt. Shift right twice. |  |  |

| 0  | 1                               | 0 | Add. Then shift right twice.             |  |  |

| 1  | 0                               | 0 | Shift right. Subt. Shift right again.    |  |  |

| 1  | 1                               | 0 | Subtract. Then shift right twice.        |  |  |

| 0  | 0                               | 1 | Add. Then shift right twice.             |  |  |

| 0  | 1                               | 1 | Shift right. Add. Shift right again      |  |  |

| 1  | 0                               | 1 | Subtract. Then shift right twice.        |  |  |

| 1  | 1                               | 1 | Neither add nor subt. Shift right twice. |  |  |

fig. 4. MULTIPLICATION ALGORITHM

To implement this algorithm, a PHASE COUNTER is used to count the phases (each phase is one machine word in length), and a SHIFT MEMORY FLIP-FLOP is used to count the shifts.

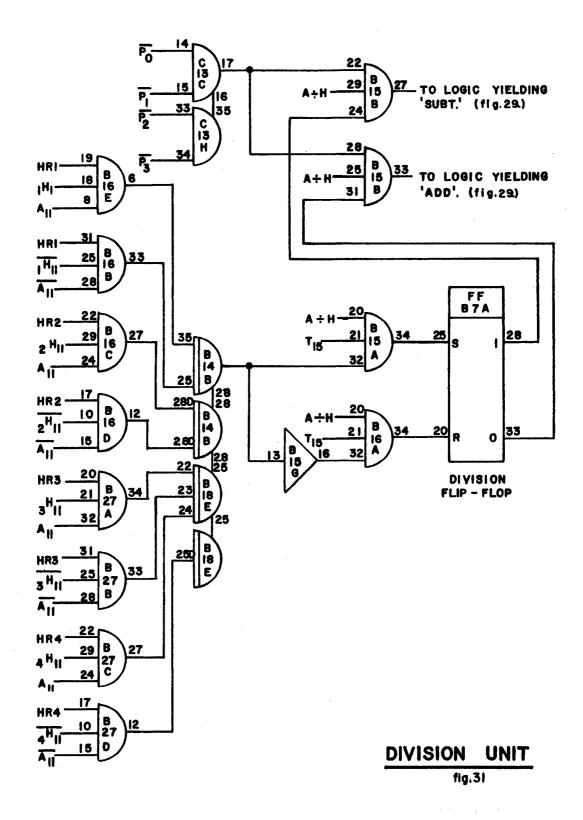

#### 2.9 Division Unit

The computer performs division by the non-restoring method<sup>2</sup>. The divisor is either added to, or subtracted from, the partial remainder, depending on the sign of the divisor and that of the partial remainder. If these two signs agree, a subtraction is performed and the quotient digit is 1. If the signs do not agree, an addition is performed and the quotient digit is zero. In either case, a new partial product is next formed by the proper left shift. This process continues until the complete quotient is built up in the Q-REGISTER. The final answer is obtained by left shifting the Q-REGISTER into the A-REGISTER during phase 12.

#### 2.10 Control Unit

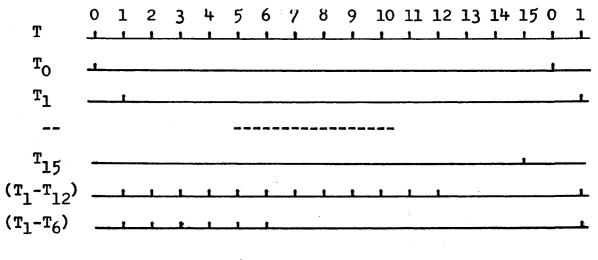

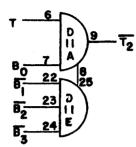

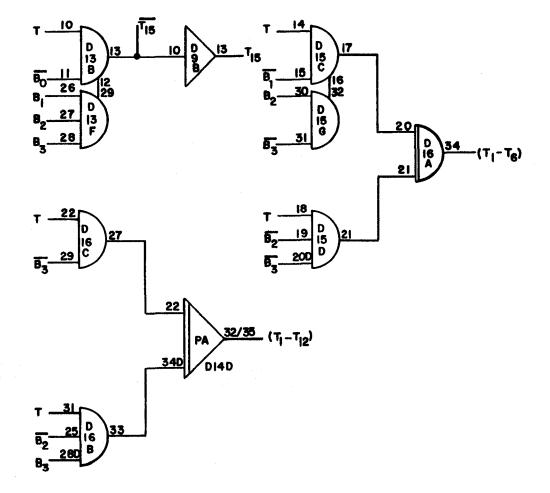

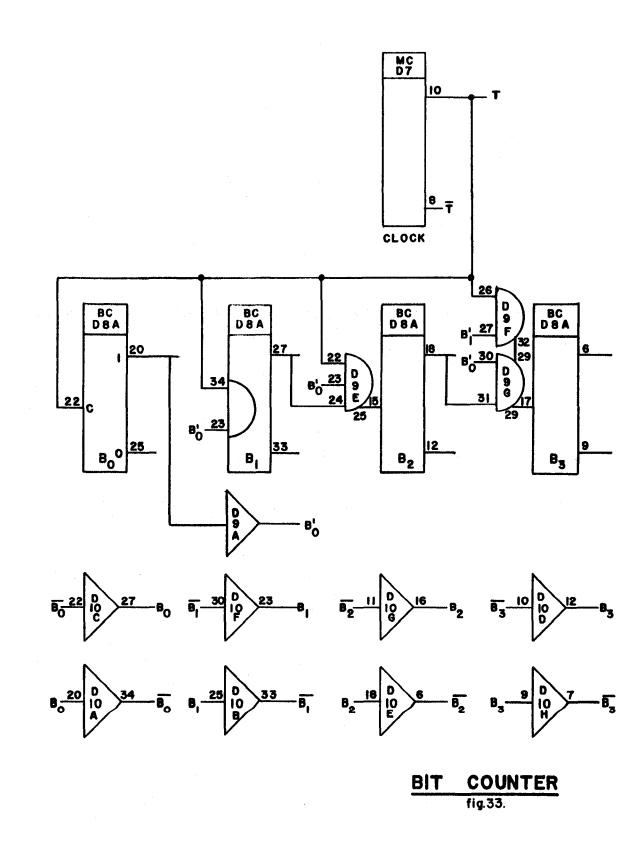

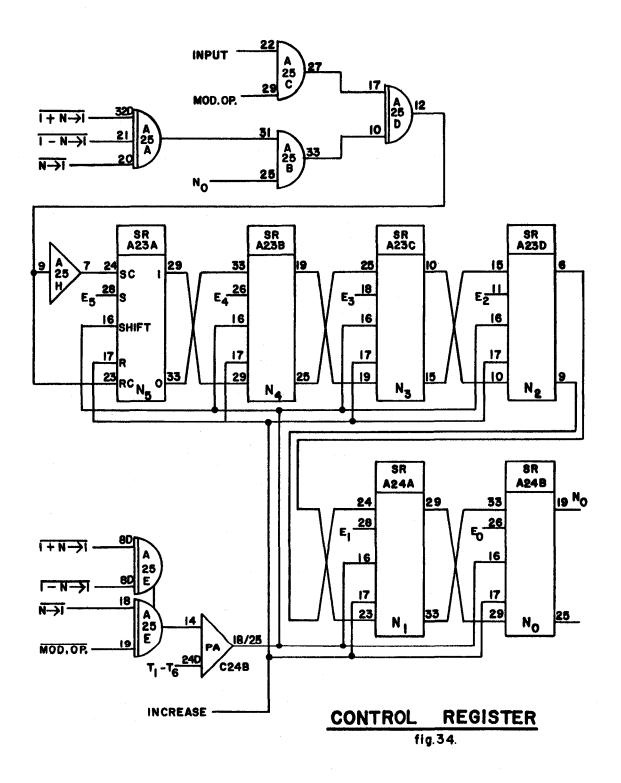

The control unit directs the internal operation of the computer causing operations to occur in proper sequence and at the right time. A master CLOCK, operating at a frequency of 200 kilocycles per second, supplies a continuous train of 2 microsecond pulses, T. A four stage BIT COUNTER counts the pulses, T, in order to provide a binary count of zero to fifteen. A TIMING UNIT provides separate timing signals T<sub>0</sub> through T<sub>15</sub>. It also provides two pulse trains called  $(T_1-T_{12})$ , and  $(T_1 - T_6)$ . This is clarified by fig. 5. These timing signals correspond to the consecutive bits of the 16 bit machine word and supply the basic timing for the Computer.

fig. 5. TIMING SIGNALS

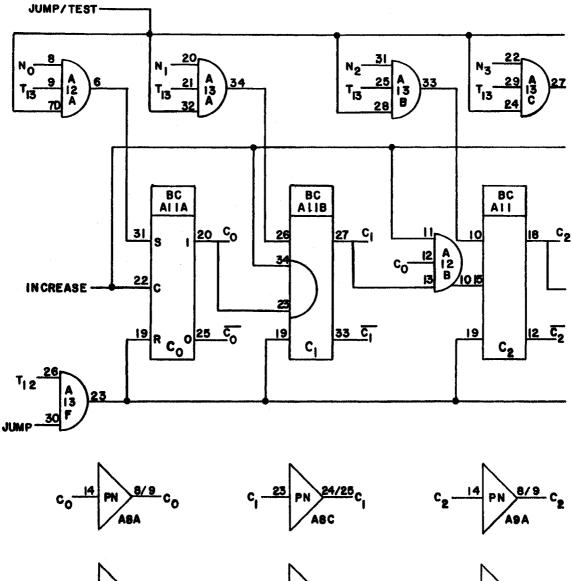

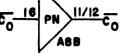

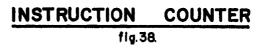

The control unit has a six bit INSTRUCTION COUNTER. This counter is initially set to zero by the ZERO COUNTER button. Then the START button is pressed, the counter is increased by 1. This begins the program whose first step number is one. The INSTRUCTION COUNTER counts the program steps as they are performed and increases consecutively to each new program step when the previous step is completed. The INSTRUCTION COUNTER begins counting at 1 and counts up to 63, after which it returns to zero and repeats counting. This gives a total of 64 consecutive program steps (including step zero). A HALT order will stop the counter.

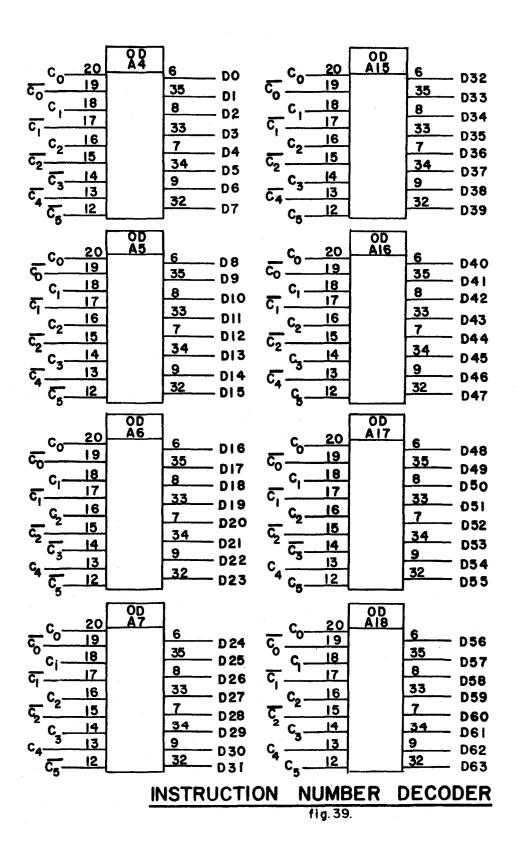

In conjunction with the INSTRUCTION COUNTER is an INSTRUCTION NUMBER DECODER. There are 64 output lines from the decoder, labelled DO through D63. These output lines correspond to the particular program step being executed. For example, if program step 5 is being executed, the INSTRUCTION COUNTER contains 000101 (5 in binary notation), and line D5

is energized. The output lines DO through D63 are connected to the PROGRAM BOARD described later.

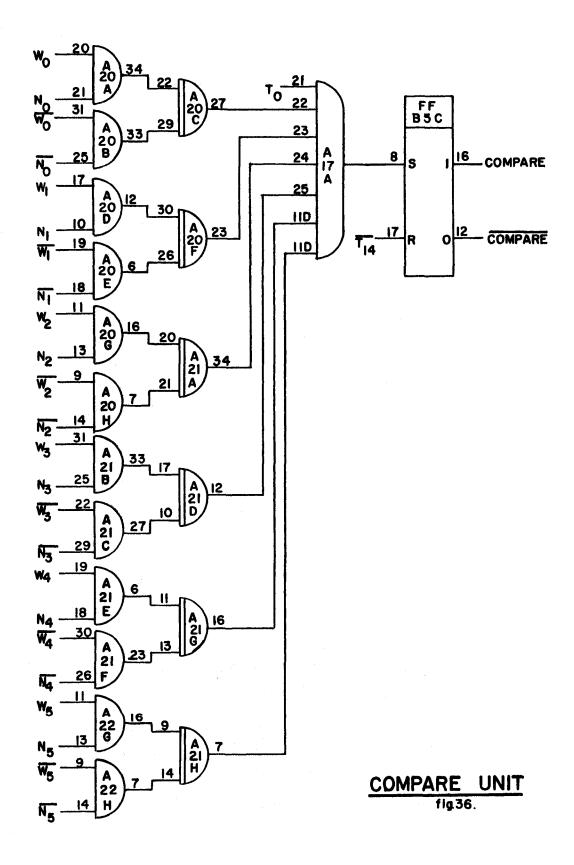

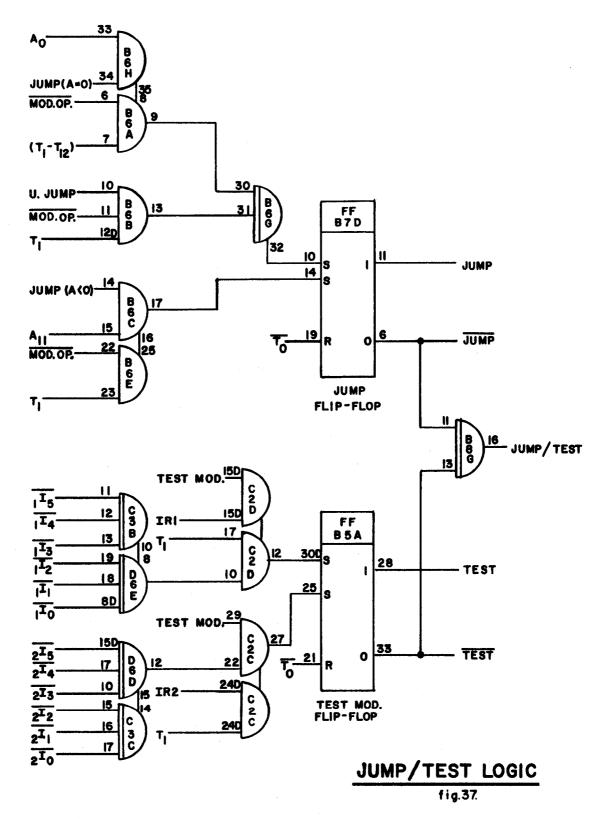

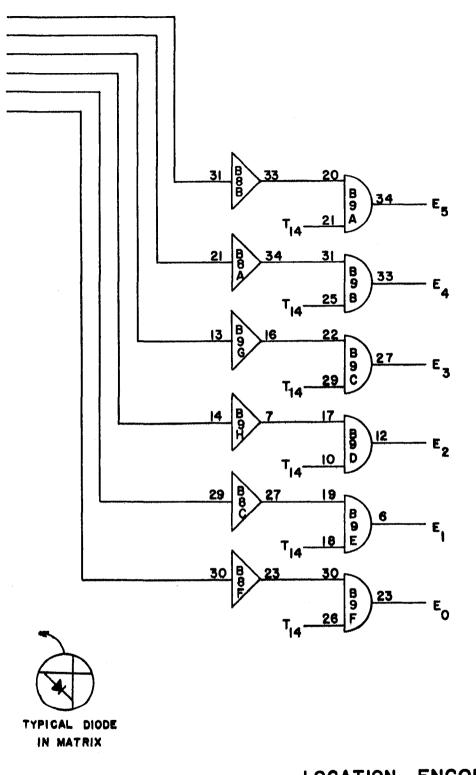

The control unit also has a CONTROL REGISTER or The CONTROL REGISTER has several purposes. It N-REGISTER. is used during the execution of orders involving the S-STORE. For these orders, the data location number, LO through L60, is placed in binary form into the N-REGISTER. This binary number comes from the LOCATION ENCODER which in turn has received the location number from the PROGRAM BOARD. The WORD COUNTER is a six bit binary counter. The number in the WORD COUNTER corresponds to the location number of the data word which will appear next (not the present word) at the output of the delay line S-STORE. By comparing the binary number in the CONTROL REGISTER and in the WORD COUNTER, a COMPARE UNIT determines when the required S-STORE location becomes available for use. The COMPARE UNIT will at this time gate the S-order.

A further use of the CONTROL REGISTER is in JUMP/ TEST orders. For these orders the CONTROL REGISTER contains the number of the next program step to be executed if a program jump is to be performed. As before, this number comes from the LOCATION ENCODER which receives the program step number from the PROGRAM BOARD. If the jump is to be performed, the number in the CONTROL REGISTER is transferred to the INSTRUCTION COUNTER so that the INSTRUCTION COUNTER now holds the next program step number. If the jump is not to be performed, the INSTRUCTION COUNTER is increased by 1

so that the computer performs the next consecutive program step.

A final use of the CONTROL REGISTER is to hold the number N, in conjunction with I-REGISTER orders and for modification of data location numbers. Here N is considered to be a six bit binary integer which is entered into the CONTROL REGISTER from the PROGRAM BOARD after encoding. N can be right-shifted out of the CONTROL REGISTER as required.

#### 2.11 Program Board

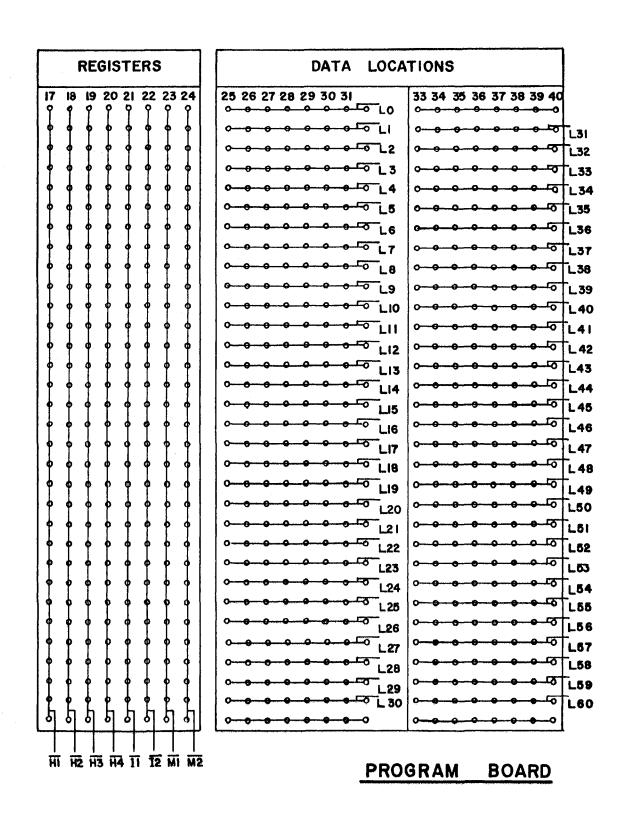

The program to be executed by the computer enters the machine on a PROGRAM BOARD. The PROGRAM BOARD is a panel containing 32 rows by 40 columns of holes or "hubs". When the PROGRAM BOARD is inserted into the machine it provides the operator access to internal circuitry. By inserting wires into the panel holes according to a definite pattern, the operator may design any desired program.

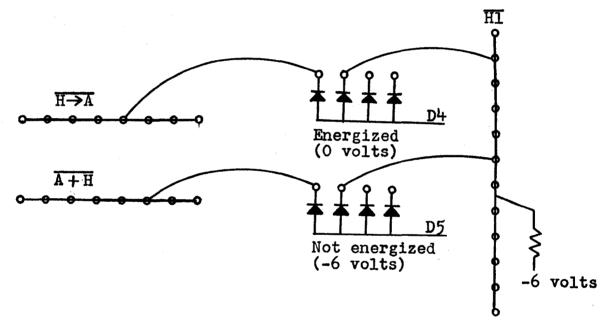

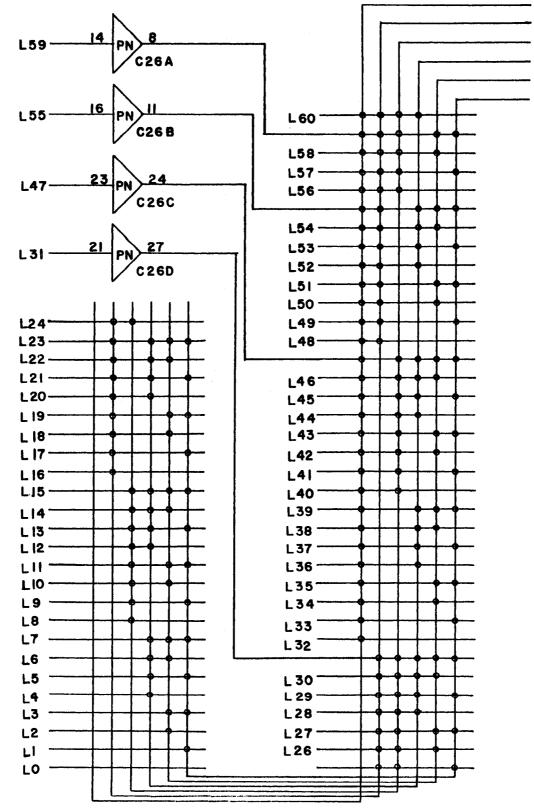

The program board is shown in fig. 7. It is divided into four sections, namely: ORDERS, PROGRAM STEPS, REGISTERS, and DATA LOCATIONS. The section called PROGRAM STEPS contains 64 groups of four hubs each. These in turn are labelled 0, R, L, M for Order, Register, Location and Modifier, respectively. Each group of four hubs is numbered and is connected through four diodes to the corresponding output of the INSTRUCTION NUMBER DECODER. The INSTRUCTION

NUMBER DECODER outputs are energized (0 volts) in sequence starting at number DO and proceeding to number D63 so that each group of hubs will also be energized in like sequence. The energized hubs are at 0 volts, whereas, all others remain at -6 volts.

The hubs in the section called ORDERS are connected as bus bars of eight hubs each. These bus bars are labelled  $H\rightarrow A$ ,  $A\rightarrow H$ ,  $A\rightarrow H$  & Cl., etc. corresponding to the names of all the available orders. The hubs in the section called REGISTERS are connected as bus bars of 32 hubs each and are labelled H1, H2, H3, H4, I1, I2, M1, and M2. Finally, the hubs in the section called DATA LOCATIONS are connected as bus bars of eight hubs each. Each bus bar in this section is assigned one location number from L0 through L60. All bus bars are connected to internal circuitry.

To set a PROGRAM STEP, the operator connects the corresponding hub 0 to the particular bus bar in the section called ORDERS which calls for the required order. If the order involves an H-REGISTER or I-REGISTER, the hub R is connected to the particular H1, H2, H3, H4, I1, or I2 required. If the order involves the data S-STORE, and hence requires a data location, then L is connected to the appropriate hub L0 through L60. If the order involves the N-REGISTER, the section called DATA LOCATIONS is now used to assign a value to N. For example, if N is to have the binary value 001110 (which is equivalent 14), the hub L is connected to L14. Finally, if the order involves a data S-STORE location number which is to be modified, the hub M is connected to Ml or M2, depending upon whether the modifier register is I1, or I2, respectively.

In the section called PROGRAM STEPS, the diodes are used for isolation of each step. For example, consider the two program steps shown in fig. 6. It is clear that if the diodes were replaced by short circuits, then D5, and hence  $\overline{A+H}$ , would be taken to 0 volts. The diodes prevent this.

fig. 6. DIODE ISOLATION

This section has shown how to program the orders onto the PROGRAM BOARD. In all, there are 26 different orders, which are given in the Appendix.

|    | ORDERS                                                                 |                       |      |        | þ              | P        |                | RAM   | ST     |               | · .     | 14             |

|----|------------------------------------------------------------------------|-----------------------|------|--------|----------------|----------|----------------|-------|--------|---------------|---------|----------------|

|    | 1 2 3 4 5 6 7                                                          |                       |      | 0<br>9 | <u>R</u><br>10 | <u> </u> | <u>M</u><br>12 |       | 0<br>8 | <u></u><br>14 | L<br>15 | <u>M</u><br>16 |

| I  |                                                                        | H-JA                  | DO   | ŏ      | 0              | 0        | 0              | D 32  |        | 0             | 0       | 60             |

| 2  | 0-0-0-0-0-0                                                            | A->H                  | DI   | 0      | 0              | ο        | o              | D33   | 0      | 0             | 0       | 0              |

| 3  | 0-0-0-0-0-0-0                                                          | A->H& CL              | D2   | 0      | 0              | 0        | 0              | D 34  | 0      | 0             | 0       | 0              |

| ŀ  | 0-0-0-0-0-0                                                            | ATH                   | D3   | 0      | 0              | 0        | 0              | D35   | 0      | 0             | 0       | 0              |

| 5  | 0                                                                      | H-A                   | D4   | 0      | 0              | 0        | 0              | D36   | 0      | 0             | 0       | 0              |

| 8  | <b></b>                                                                | AxH                   | D5   | 0      | 0              | 0        | 0              | D37   | 0      | 0             | 0       | 0              |

| 7  | 0-0-0-0-0-0-0                                                          | A+H                   | D6   | 0      | 0              | 0        | 0              | D 3 8 | 0      | 0             | 0       | 0              |

| 8  | <b>~~~~~</b>                                                           |                       | D7   | 0      | 0              | 0        | 0              | D 3 9 | 0      | 0             | 0       | 0              |

| )  | 0                                                                      | <br>₽H                | D8   | •      | 0              | 0        | 0              | D40   | 0      | 0             | 0       | 0              |

| 0  | 0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-                               | H->S                  | D9   | 0      | 0              | 0        | 0              |       | ٩      | ९             | ٩       | ٩              |

| 1  | 0-0-0-0-0-0-0                                                          | S-→A                  | D 10 | 0      | 0              | 0        | 0              | D4 2  | 0      | 5)            | 5)      | <b>F</b> )     |

| 2  | 0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-                               | Ā-→S                  | DII  | 0      | 0              | 0        | 0              | D43   | 0      | 1             | YP      |                |

| 3  | 0 <del>0</del> -0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0-0                      | A->S&CL               | D 12 | 0      | 0              | 0        | 0              | D44   | •      | 0             | 0       | 0              |

| 4  | 0                                                                      | A+S                   | D13  | 0      | 0              | 0        | 0              | D45   | 0      | 0             | 0       | 0              |

| 5  | 0                                                                      | A-S                   | D 14 | •      | 0              | 0        | 0              | D46   | 0      | 0             | 0       | 0              |

| 6  | ०●●00                                                                  |                       | D15  | 0      | 0              | 0        | 0              | D47   | 0      | 0             | 0       | 0              |

| 7  | 0- <b>0-0</b> -0-0 <sup>-0</sup>                                       | RT.ST.A               | D16  | 0      | 0              | 0        | 0              | D 48  | 0      | 0             | 0       | 0              |

| 9  | 0- <b></b> -                                                           | LT. ST.A              | D17  | 0      | 0              | 0        | 0              | D49   | 0      | 0             | 0       | 0              |

| 9  | 0                                                                      | JUMP(A(O)             | D 18 | 0      | 0              | 0        | 0              | D 50  | •      | 0             | 0       | 0              |

| 20 | 0-0-0-0-0-0-0                                                          | JUMP(A=0)             | D 19 | 0      | 0              | 0        | 0              | D51   | •      | 0             | 0       | 0              |

| 24 | 0                                                                      | N-N                   | D20  | 0      | 0              | 0        | 0              | D 52  | 0      | 0             | 0       | 0              |

| 2  | 0                                                                      | $I + N \rightarrow I$ | D21  | 0      | 0              | 0        | 0              | D 53  | 0      | 0             | 0       | 0              |

| 23 | 0                                                                      | <br>I – N → I         | D22  | 0      | 0              | 0        | 0              | D 54  | •      | 0             | 0       | 0              |

| 4  | 0                                                                      | TEST MOD.             | D23  | 0      | 0              | 0        | 0              | D 55  | 0      | 0             | 0       | 0              |

| ;6 | <b></b>                                                                |                       | D24  | 0      | 0              | 0        | 0              | D 56  | 0      | 0             | 0       | 0              |

| :6 | <b>~~~~~</b> ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                           |                       | D25  | 0      | 0              | 0        | 0              | D 57  | 0      | 0             | 0       | 0              |

| 7  | 0                                                                      | INPUT                 | D28  | 0      | 0              | 0        | 0              | D58   | 0      | 0             | 0       | 0              |

| 8  | <b></b>                                                                | OUTPUT                | D 27 | 0      | 0              | 0        | ٥              | D59   | •      | 0             | 0       | 0              |

| 9  | 0 <b>-</b> - <b>-</b> - <b>-</b> - <b>-</b> - <b>-</b> - <b>------</b> | U, JUMP               | D28  | 0      | 0              | 0        | 0              | D 60  | •      | 0             | 0       | 0              |

| 0  | 00                                                                     |                       | D29  | 0      | 0              | 0        | 0              | D61   | 0      | 0             | 0       | 0              |

| 11 | • • • • • • • • • • • • • • • • • • •                                  | HALT                  | 030  | 0      | 0              | 0        | 0              | D62   | •      | 0             | 0       | 0              |

| 2  | 00                                                                     |                       | D 31 | 0      | 0              | 0        | 0              | D63   | 0      | 0             | 0       | 0              |

0 - ORDER R - REGISTER L - LOCATION M - MODIFIER

#### 2.12 Modification and Program Looping

Often a program will require a program loop, that is, a set of sequential program steps are to be repeated a number of times before the program proceeds to the next instruction. Also, the data location of some, or all, of the S-orders in the loop are to be incremented by an integral value, N, each time around the loop. This process of modifying the data location is called MODIFICATION.

Modification and program looping can best be shown by the sample program given in fig. 8.

| Program<br>Steps | Instructions        | Comments                   |

|------------------|---------------------|----------------------------|

| 1                |                     |                            |

|                  | > Preceeding orders |                            |

| 10               | )                   |                            |

| 11               | N→I                 | (N = 10)                   |

| 12               | S→A (M)             | Typical S-order (Modified) |

| 13               |                     |                            |

|                  | > Other orders      |                            |

| 22               |                     |                            |

| 23               | I – N→I             | (N = 1)                    |

| 24               | TEST MOD.           | (N = 12)                   |

| 25               |                     |                            |

|                  | Following orders    |                            |

| 63               | J                   |                            |

fig. 8. SAMPLE OF MODIFICATION AND LOOPING

Suppose that, in this program, the loop is to be repeated 10 times, with the initial location to be 30 and the final location to be 39. Program step 11, i.e.  $N \rightarrow I$ , is used to preset the I-REGISTER to 10. The steps 12 to 24 constitute the program loop. It is assumed that step 12 requires modification. Step 12 is programed on the PROGRAM BOARD with L connected to L40 (not L30). This is explained as follows.

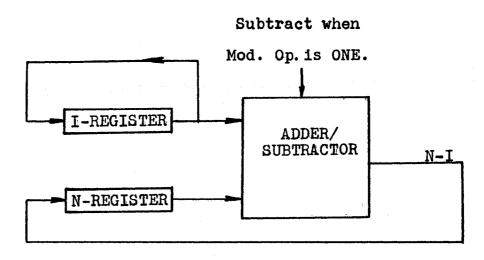

fig. 9. MODIFICATION PROCESS

Modified instructions are executed in two stages. The location is modified during the first stage and the instruction is carried out during the second stage. During the first stage the signal MODIFICATION OPERATION (Mod. Op.) is generated. This signal causes the difference, N-I, to be placed into the N-REGISTER as shown in fig. 9. During the second stage, the effective value of the data location is now N-I. In the sample problem, the effective location for the first time around the loop is 40 - 10 = 30.

Refering still to the sample problem, program steps 23 and 24 cause the program to loop. Step 23, i.e.  $I - N \rightarrow I$ , changes the number in the I-REGISTER. In the sample problem, N equals 1, so that at the completion of the first loop the number in the I-REGISTER is 10 - 1 = 9. The  $I - N \rightarrow I$  order also controls the TEST FLIP-FLOP. If I - N is zero, the TEST FLIP-FLOP is set to ONE, otherwise to ZERO. Step 24 is the TEST MODIFIER order. It depends on the previous setting of the TEST FLIP-FLOP. If the TEST FLIP-FLOP is ZERO, this order causes the computer to jump to the given program step (back to step 12 in the sample program), and hence to loop. If the TEST FLIP-FLOP is ONE, this order causes the computer to go to the next consecutive program step (step 25 in the sample program), and hence leave the 100p.

#### 2.13 Input/Output

The computer has two means of data input. The first is a KEYBOARD with one CLEAR ACCUMULATOR button and 12 INPUT buttons for entering ONE'S into the twelve bit positions of the A-REGISTER. To enter data into the S-STORE from the KEYBOARD, the subroutine shown in fig. 10. may be used. 96373

# **UNIVERSITY OF WINDSOR LIBRARY**

| Program<br>Steps | Instructions | Comments                                                               |

|------------------|--------------|------------------------------------------------------------------------|

| 0                |              | Press ZERO COUNTER and START.                                          |

| 1                | N→I          | N = Number of data words                                               |

| 2                | HALT         | Enter data into A-REGISTER<br>through KEYBOARD. Press START.           |

| - 3              | A→S          |                                                                        |

| 4                | I - N→I      | N = increment in data location (usually 1).                            |

| 5                | TEST MOD.    | This causes a loop back to step 2.                                     |

| 6                | HALT         | If desired to go directly on<br>with program, this HALT is<br>omitted. |

| 7                |              | Out cled.                                                              |

|                  |              | Main program.                                                          |

| 63               |              |                                                                        |

#### fig. 10 INPUT SUBROUTINE

The second means of input is a SHAFT POSITION DIGITIZER. This unit continually monitors the position of a rotating shaft in the external system and converts the shaft position into a 10 bit binary number which is stored in a 10 bit register called the D-REGISTER. This register is actually a part of the DIGITIZER. The INPUT order transfers the data in the D-REGISTER to the 10 least significant bits of the A-REGISTER.

The computer has two means of output. The first is a set of 12 lamps connected to the outputs of the twelve stages of the A-REGISTER to indicate the contents of the

A-REGISTER. Usually a HALT order is used to make the A-REGISTER static. The second means of output is the OUTPUT order. The OUTPUT order sets one of two OUTPUT FLIP-FLOPS to ONE. These flip-flops can be used to gate control signals in any external on-line system.

#### III. IMPLEMENTATION

A discussion of how the computer logic is implemented by the use of NAND logic follows.

#### 3.1 The Logic Elements

The physical circuitry which implements the logic for the computer has been purchased commercially from Computer Control Company, Inc. The circuitry is in the form of digital logic modules. Each module contains a number of basic logic elements.

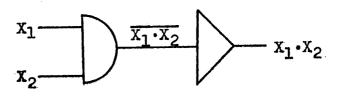

The fundamental logic element used is the NAND (NOT-AND) gate. The NAND function is as follows:

$$\mathbf{Y} = \overline{\mathbf{X}_1 \cdot \mathbf{X}_2 \cdot \mathbf{X}_3 \cdots \mathbf{X}_n}$$

where Y is the output,  $X_1, X_2, X_3, \ldots X_n$  are the inputs, the dot (•) is the function AND, and the bar over the terms means negation. The truth table for the NAND function is given in fig. 11.

| x <sub>1</sub> | x <sub>2</sub> | x1.x2 |

|----------------|----------------|-------|

| 1              | l              | 0     |

| 1              | 0              | 1     |

| 0              | 1              | 1     |

| 0              | 0              | 1     |

fig. 11. NAND TRUTH TABLE

The NAND gate is a universal element; it can be used to synthesize AND-OR-NOT logic which would otherwise

require three logic elements. A method of converting the familiar AND-OR logic to NAND logic is required.

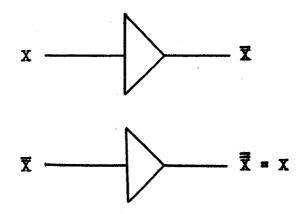

A device which performs the NOT function must produce as an output the negation, or opposite value of its input. Thus, a ONE (-6 volts) input signal is changed to a ZERO (0 volts) output signal; and a ZERO input signal is changed to a ONE output signal. A single NAND circuit performs this function. A logic element used this way is referred to as an INVERTER.

fig. 12. NOT FUNCTION

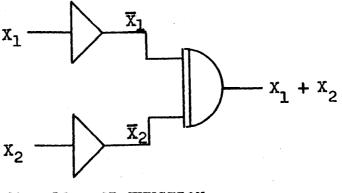

A device which performs the OR function must have a ONE output when any of its inputs is ONE; and ZERO output when all of its inputs are ZERO. To accomplish the OR function with NAND circuits, each signal is first inverted and then applied to the NAND circuit. Thus, a NAND circuit performs the OR function if its inputs are the negation of the signals that are to be ORed together. This follows from De Morgan's theorem

$$x_1 + x_2 = \overline{\overline{x_1} \cdot \overline{x_2}}$$

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

where + is the function OR.

fig. 13. OR FUNCTION

A device which performs the AND FUNCTION must have a ONE output when all of its inputs are ONE, and a ZERO output when any of its inputs are ZERO. By definition, the NAND circuit produces the negation of the AND function. A second NAND can be used to remove this negation and thus form the pure AND function.

fig. 14. AND FUNCTION

Figures 12, 13, and 14 show the NOT, OR, and AND functions as they appear in the logic diagrams that follow. The functions are drawn this way so as to be readily recognized. Note, however, that all logic elements are NAND gates.

There are a set of rules that permit direct substitution of NAND gates for both AND and OR gates.

- 1. A NAND gate ( used as an inverter) must be inserted between any AND gate that drives another AND gate and between any OR gate that drives another OR gate.

- 2. All inputs to OR gates that are not from within the logic network must be inverted. (If the negation is not available as an input, a NAND gate can be used to perform the inversion.)

- 3. The last gate should be an OR gate. If not, a NAND gate must be added to obtain the assertions of the function being implemented.

#### 3.2 The Physical Structure

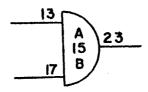

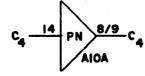

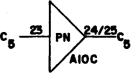

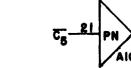

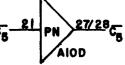

The physical computer structure consists of an internal power supply and four racks. The four racks are designed to hold the logic modules. These are labelled from top to bottom as A, B, C, and D, respectively. Each rack holds 28 logic modules, numbered 1 through 28. Each module has 35 pins, numbered 1 through 35. Each module contains from 1 to 8 logic elements and these are assigned letters, A, B, C, etc.

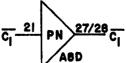

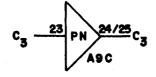

Therefore, an element can be fully identified as shown in fig. 15. This is a NAND gate situated in the 15th module position of RACK A. B refers to the letter assigned to

this particular element within this module. 13 and 17 are the pin inputs and 23 is the pin output.

fig. 15. NAND LOGIC NOTATION

Logic elements other than NAND Gates are also assigned a neumonic code as follows:

| FF Basic flip-flo | p |

|-------------------|---|

|-------------------|---|

- FA Gated flip-flop

- UF Universal flip-flop

- SR Shift register

- BC Binary counter

- PA Inverting power amplifier

- PN Non-inverting power amplifier

- OD Octal/decimal decoder

- MC Master clock

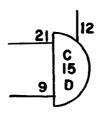

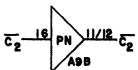

Diode Clusters may be used to expand the number of inputs to a NAND gate. These are identified as shown in fig. 16. If only one or two diodes are required (rather than a large cluster), these diodes may be wired externally. They are identified by giving the pin number, followed by a D.

### fig. 16. DIODE CLUSTER

The Reference Manual for the logic modules gives complete information concerning each logic circuit.

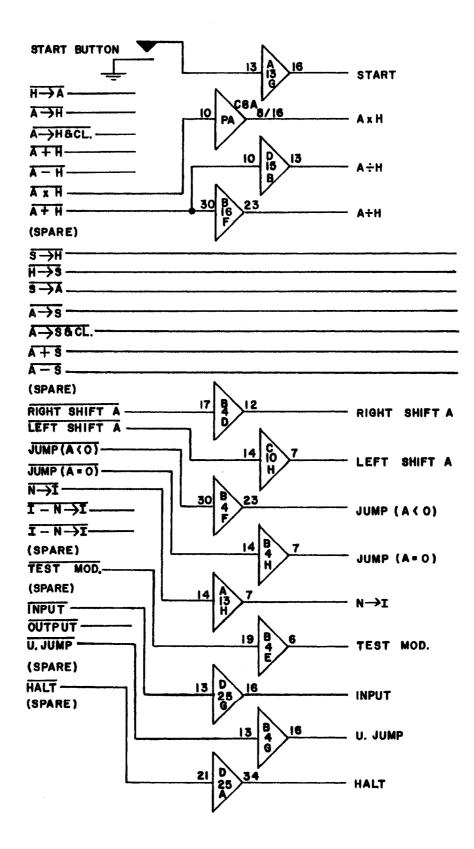

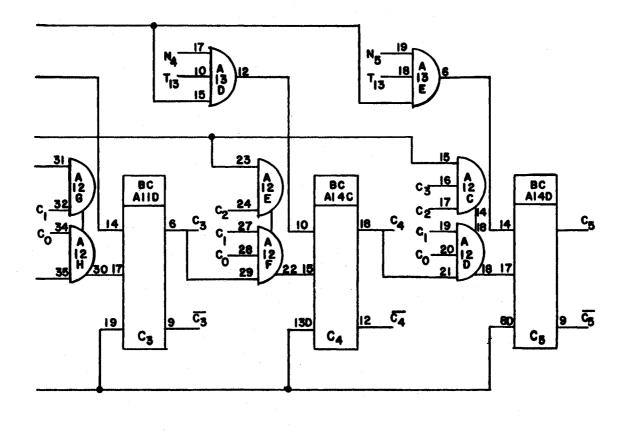

### IV. LOGIC DIAGRAMS

At this point a complete set of logic diagrams is given. These logic diagrams are tabulated below.

#### LOGIC DIAGRAMS OF COMPUTER

| DELAY LINE STORE           | fig. 17. |

|----------------------------|----------|

| ACCUMULATOR                | fig. 18. |

| GATING OF ACCUMULATOR      | fig. 19. |

| RIGHT SHIFT ACCUMULATOR    | fig. 20. |

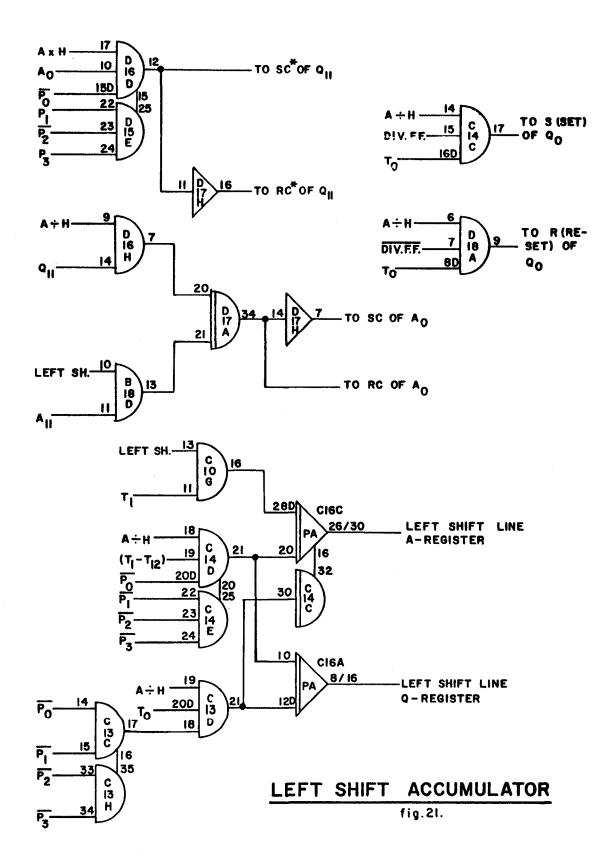

| LEFT SHIFT ACCUMULATOR     | fig. 21. |

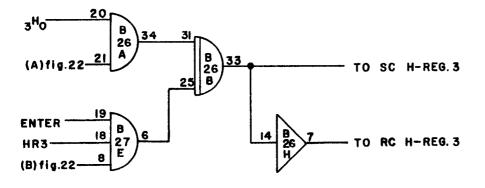

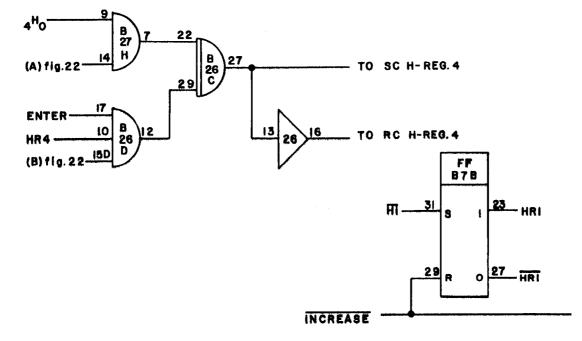

| H-REGISTERS                | fig. 22. |

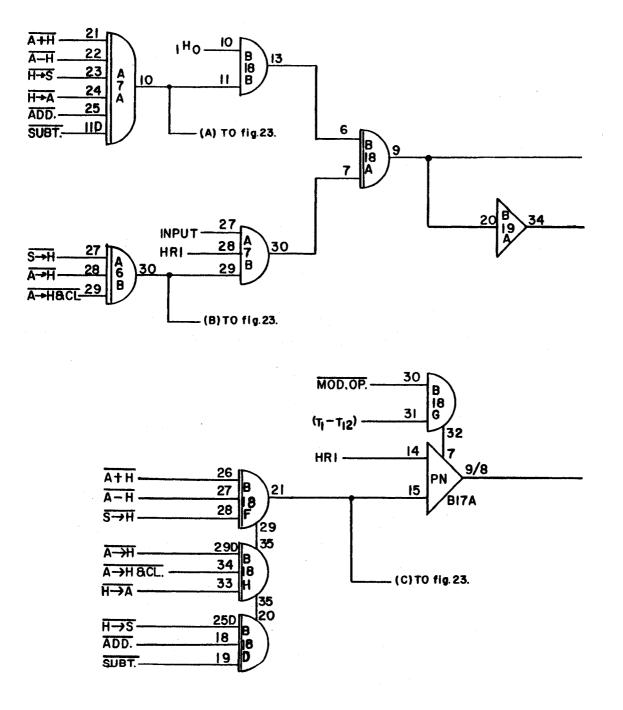

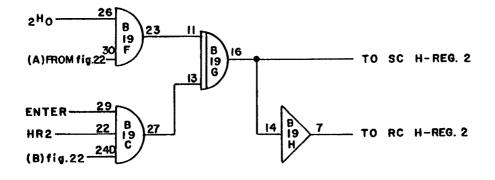

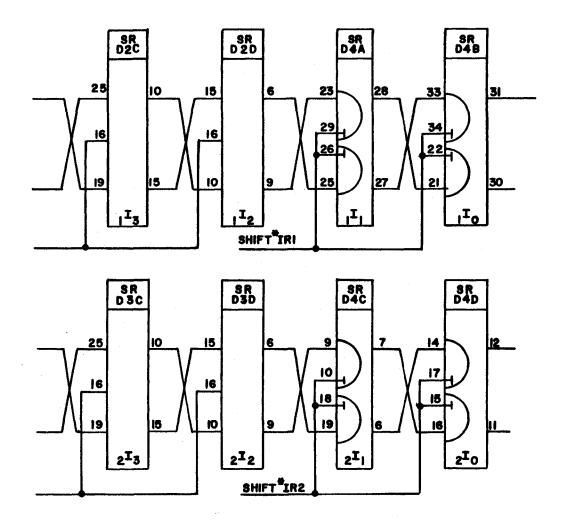

| GATING H-REGISTERS         | fig. 23. |

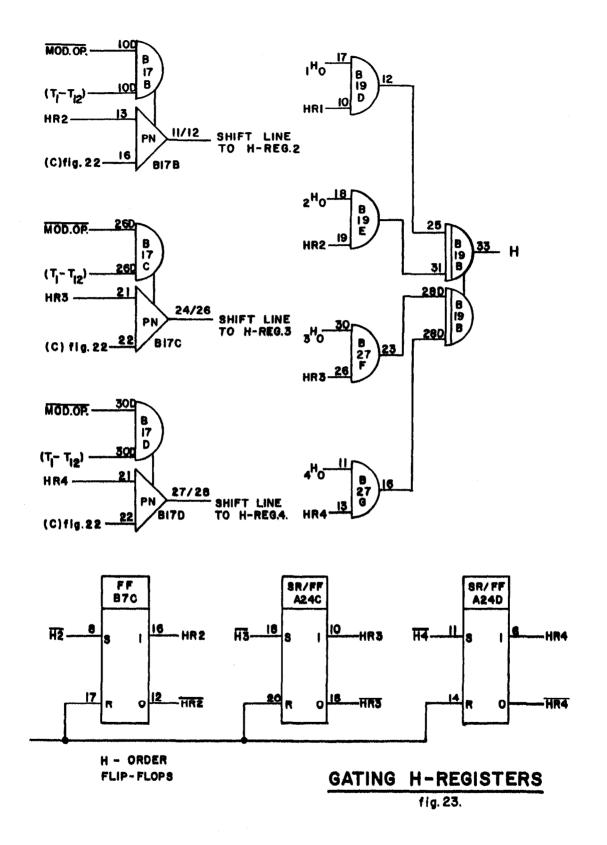

| I-REGISTERS                | fig. 24. |

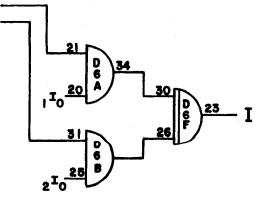

| 'ENTER' BUS                | fig. 25. |

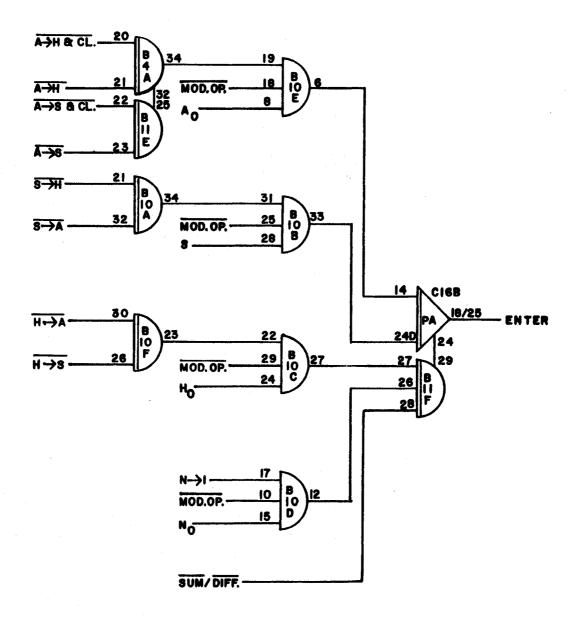

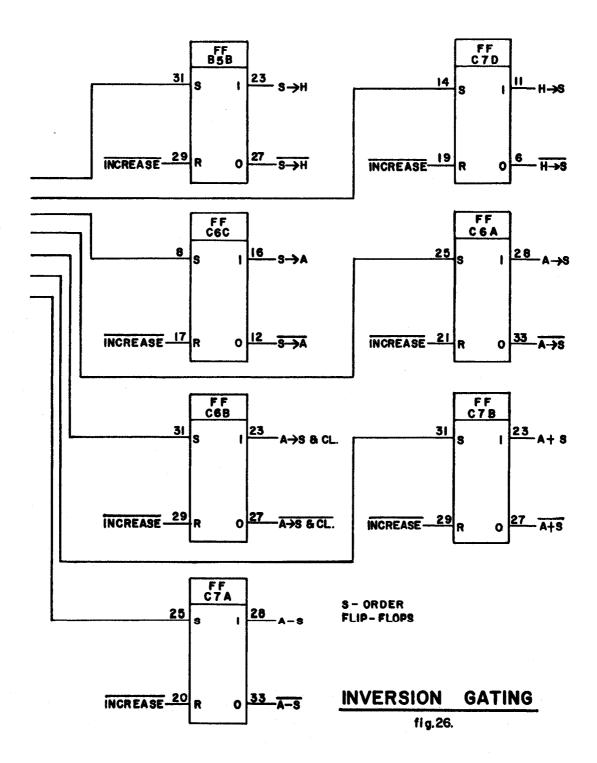

| INVERSION GATING           | fig. 26. |

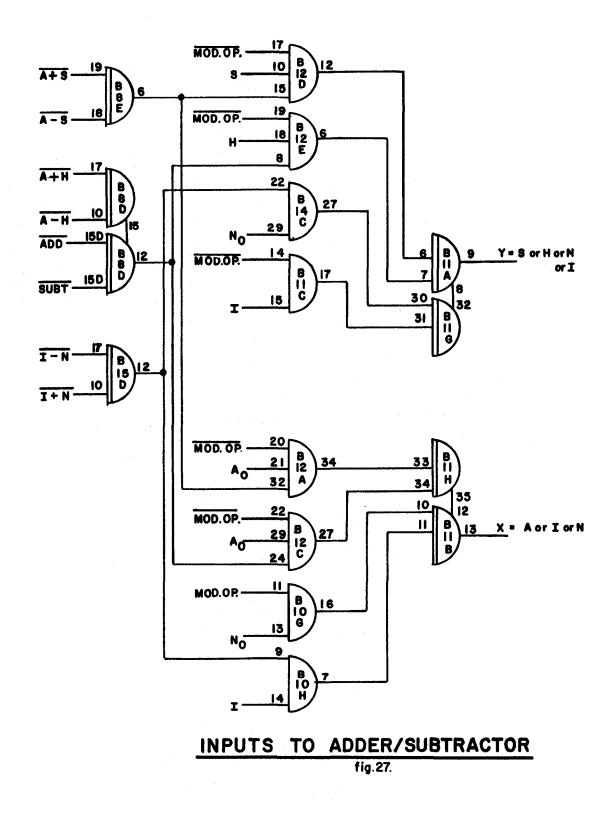

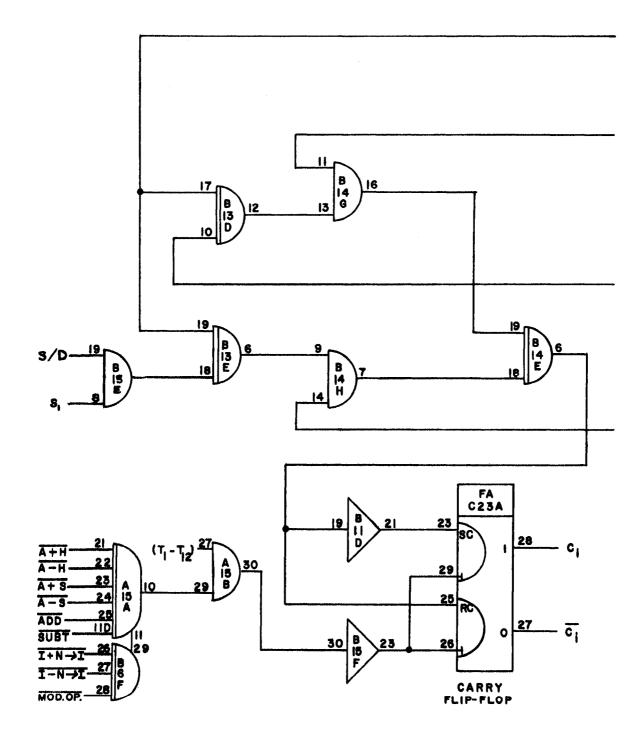

| INPUTS TO ADDER/SUBTRACTOR | fig. 27. |

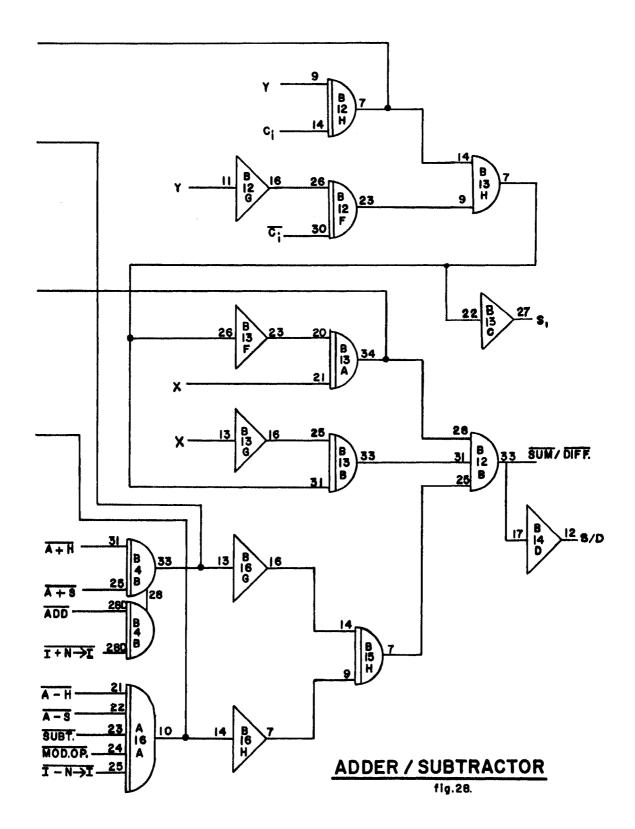

| ADDER/SUBTRACTOR           | fig. 28. |

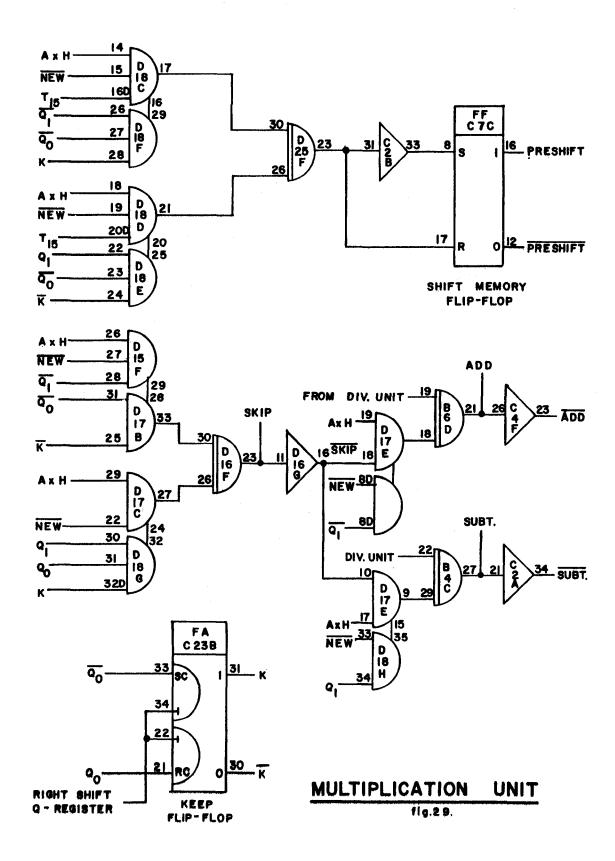

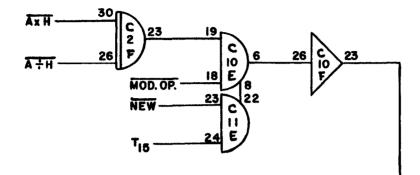

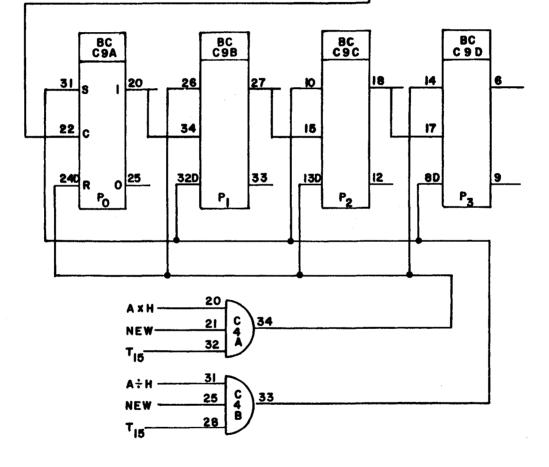

| MULTIPLICATION UNIT        | fig. 29. |

| PHASE COUNTER              | fig. 30. |

| DIVISION UNIT              | fig. 31. |

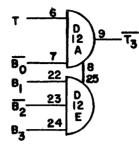

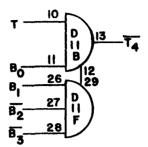

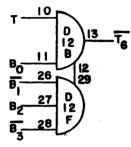

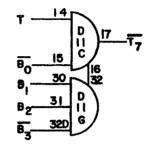

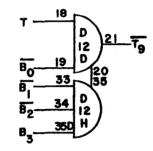

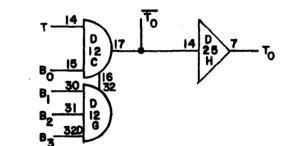

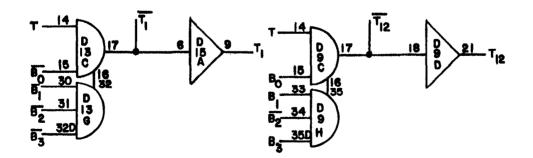

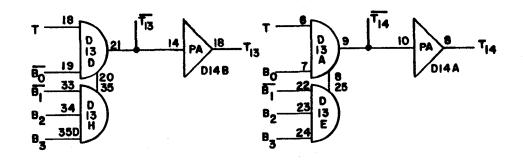

| TIMING UNIT                | fig. 32. |

| BIT COUNTER                | fig. 33. |

| CONTROL REGISTER           | fig. 34. |

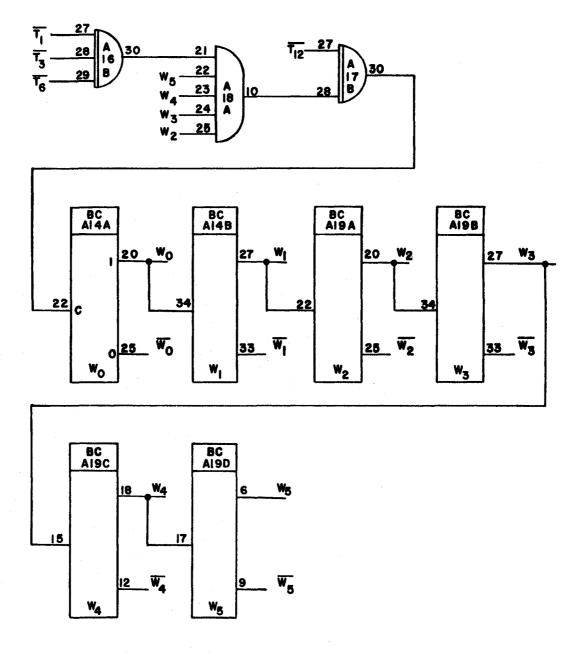

| WORD COUNTER               | fig. 35. |

34

| COMPARE UNIT         | fig. 36. |

|----------------------|----------|

| JUMP/TEST LOGIC      | fig. 37. |

| INSTRUCTION COUNTER  | fig. 38. |

| INSTRUCTION DECODER  | fig. 39. |

| LOCATION ENCODER     | fig. 40. |

| MODIFICATION         | fig. 41. |

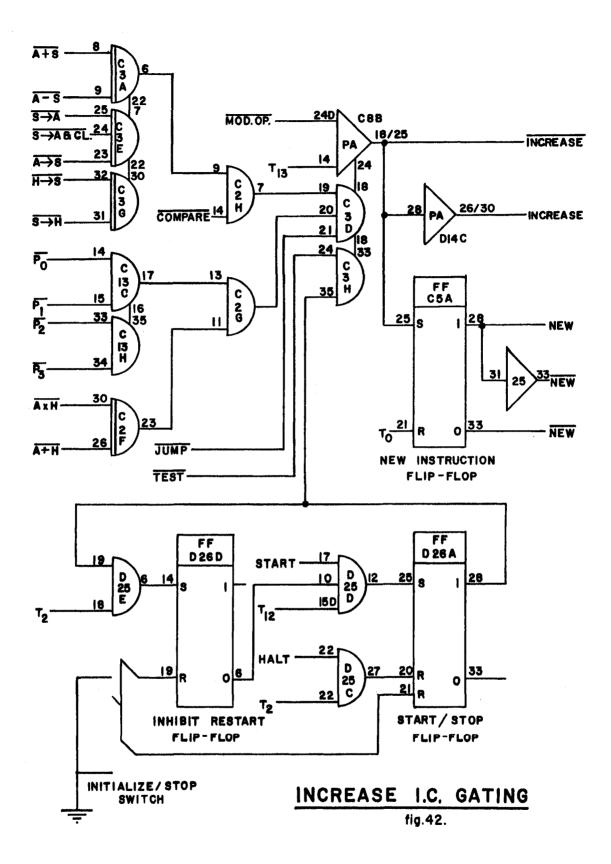

| INCREASE I.C. GATING | fig. 42. |

## LINE STORE - S fig. 17. DELAY

# UNIVERSITY OF WINDSOR LIBRARY

fig. 19.

I-REGISTERS fig.24 47

| I        | EN | TE | <u>:R'</u> | BUS |  |

|----------|----|----|------------|-----|--|

| fig. 25. |    |    |            |     |  |

PHASE COUNTER fig.30.

TIMING UNIT

fig.32.

# UNIVERSITY OF WINDSOR LIBRARY

| WORD    | COUNTER |  |  |

|---------|---------|--|--|

| fig.35. |         |  |  |

A9D

**C**3

AIOB

6

65

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

LOCATION ENCODER

## V. CONCLUSIONS AND RECOMMENDATIONS

A complete digital control computer has been designed; a large part of which has now been constructed, and tested. It is felt that the computer achieves its goal of flexibility. The list of available orders can be extended to include other orders if required. With the present number of H-registers, and one delay line, suitable working and data storage is achieved. The number of H-registers and delay lines can easily be increased if necessary.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### REFERENCES

- RAYZAK, R. J.; <u>A Digital Controller Strategy for</u> <u>Optimization and Adaptation of Control Systems</u> <u>Representable in the Phase Plane</u>, M. A. Sc. Thesis, University of Windsor (1964).

- 2. CHU, Yaohan; <u>Digital Computer Design Fundamentals</u>, Mc Graw-Hill Book Company, Inc., Toronto (1962).

- 3. THOMAS, P. A. V.; <u>The Design Philosophy of a Small</u> <u>Electronic Automatic Digital Computer</u>, Ph. D. Thesis, University of Glasgow (1961).

- 4. STAFF OF COMPUTER CONTROL COMPANY, INC.; <u>Instruction</u> <u>Manual for 200-KC S-PAC Digital Modules</u>, Computer Control Company, Inc., Framingham, Massachusetts (1963).

#### APPENDIX

## COMPUTER INSTRUCTION LIST

Note: Unless specified, an operand source remains unaltered.

- 1. H->A Transfer the contents of specified H-register (H1, H2, H3, H4) to A-register.

- 2. A-H Transfer contents of A-register into specified H-register.

- 3. A $\rightarrow$ H & CL.A Transfer contents of A-register to specified H-register and clear A-register to zero.

- 4.  $A + H \rightarrow A$  Add number in the specified H-register to number in the A-register. Put sum in A-register.

- 5. A H→A Subtract number in the specified H-register to number in the A-register. Put difference in A-register.

- 6. A x H->A Multiply the number in the A-register by the number in the specified H-register and place the product into the A-register.

- 7.  $A \div H \rightarrow A$  Divide the number in the A-register by the number in the specified H-register and place the quotient into the A-register.

- 8. (spare)

- 9. S→H Transfer contents of given location (LO through L60) in store S to specified H-register.

73

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

- 10. H->S Transfer contents of specified H-register to given location in store S.

- 11.  $S \rightarrow A$  Transfer contents of given location in store S to specified H-register.

- 12.  $A \rightarrow S$  Transfer contents of A-register to given location in store S.

- 13. A→S & CL.A Transfer contents of A-register to given location in store S and clear A-register to zero.

- 14. A + S→A Add number in given location of store S to number in A-register and place sum in A-register.

15. A S→A Subtract number in given location of store S

- from number in A-register and place the difference in A-register.

- 16. (spare)

- 17. Right Shift contents of A-register one bit to the Shift A right. Repeat the sign bit.

- 18. Left Shift contents of A-register one bit to the Shift A left. Repeat the sign bit.

- 19. Jump (A <0) If the number in A-register is less than zero, jump to the given program step (given by L0 through L60). If not, go to the next consecutive program step.

- 20. Jump (A = 0) If the number in the A-register is equal to zero, jump to the given program step. If not, go to the next consecutive program step.

- 21. N→I Transfer the binary equivalent of an integer, N (given by LO through L60), into specified I-register (Il or I2).

- 22.  $I + N \rightarrow I$  Add the integer, N, to number in specified I-register and place the sum into the same register.

- 23. I-N→I Subtract the integer, N, from the number in the specified I-register and place the difference into the same register. Also, if the result of (I - N) is zero, set the TEST FLIP-FLOP to ONE. (Note: this is for location modification.)

- 24. (spare)

- 25. Test Modifier If TEST FLIP-FLOP is ZERO, jump to the given program step (given by LO through L60). If TEST FLIP-FLOP is ONE, go to the next consecutive program step.

- 26. (spare)

- 27. Input Transfer data from D-register (digitizer register on the shaft position encoder) to A-register.

- 28. Output Set OUTPUT FLIP-FLOP (1 or 2) to ONE. (Note: these flip-flops can be used to gate control signals in any external on-line system.)

29. Unconditional Jump to the given program step (given by LO through L60).

30. (spare)

31. Halt Stop the execution of the program at the Halt program step.

32. (spare)

## COMPUTER BUTTONS

CLEAR ACCUMU- Set A-register to zero LATOR

STOP and Reset START-STOP logic. This button must INITIALIZE preceed START button at all times.

ZERO COUNTER Set Instruction counter to zero.

START Increase Instruction Counter by 1 and allow counter to continue counting until a Halt order is reached.

ACCUMULATOR Input data to A-register from a keyboard. Each INPUTS (12 buttons  $A_{11} - A_{0}$ ) to ONE.

# VITA AUCTORIS

| 1940 | Born on July 18, in Windsor, Ontario.          |

|------|------------------------------------------------|

| 1954 | Completed elementary education at St. Bernard  |

|      | Elementary School, Windsor, Ontario.           |

| 1959 | Completed Grade XIII at Walkerville Collegiate |

|      | Institute, Windsor, Ontario.                   |

| 1963 | Graduated from Assumption University, Windsor, |

|      | Ontario, with degree of B.A.Sc. in Electrical  |

|      | Engineering.                                   |

| 1964 | Candidate for degree of M.A.Sc. degree in      |

|      | Electrical Engineering at the University of    |

|      | Windsor.                                       |