# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

8-2017

# A Low Temperature Co-fired Ceramic (LTCC) Interposer Based Three-Dimensional Stacked Wire Bondless Power Module

Atanu Dutta University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd Part of the <u>Power and Energy Commons</u>

## **Recommended** Citation

Dutta, Atanu, "A Low Temperature Co-fired Ceramic (LTCC) Interposer Based Three-Dimensional Stacked Wire Bondless Power Module" (2017). *Theses and Dissertations*. 2515. http://scholarworks.uark.edu/etd/2515

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

## A Low Temperature Co-fired Ceramic (LTCC) Interposer Based Three-Dimensional Stacked Wire Bondless Power Module

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering

by

Atanu Dutta National Institute of Technology Bachelor of Technology in Electronics and Communication Engineering, 2007 University of Arkansas Master of Science in Electrical Engineering, 2010

## August 2017 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council.

Dr. Simon S. Ang Dissertation Director

Dr. Juan C. Balda Committee Member

Dr. H. Alan Mantooth Committee Member

Dr. Jia Di Committee Member

## Abstract

The objective of this dissertation research is to develop a low temperature co-fired ceramic (LTCC) interposer-based module-level 3-D wire bondless stacked power module. As part of the dissertation work, the 3-D wire bondless stack is designed, simulated, fabricated and characterized. The 3-D wire bondless stack is realized with two stand-alone power modules in a half-bridge configuration. Each stand-alone power module consists of two 1200 V 25 A silicon insulated-gate bipolar transistor (IGBT) devices in parallel and two 1200 V 20 A Schottky barrier diodes (SBD) in an antiparallel configuration. A novel interconnection scheme with conductive clamps and a spring loaded LTCC interposer is introduced to establish electrical connection between the stand-alone power modules to connect them in series to realize a half-bridge stack. Process development to fabricate the LTCC based 3-D stack is performed.

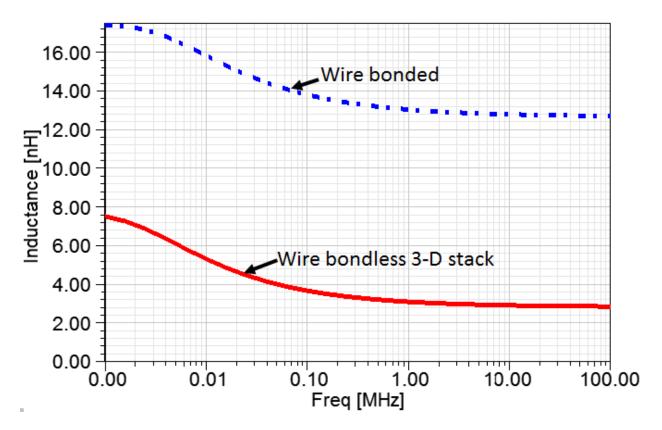

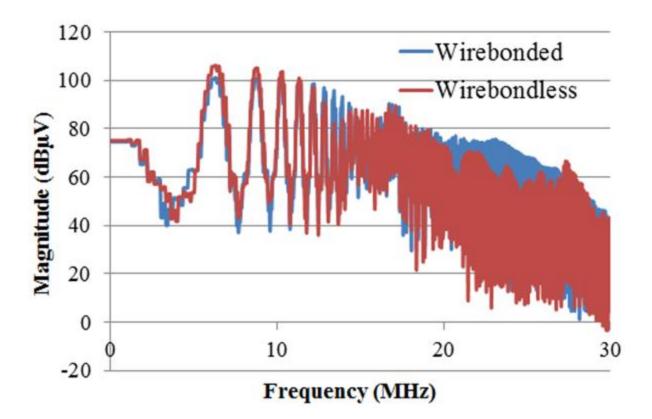

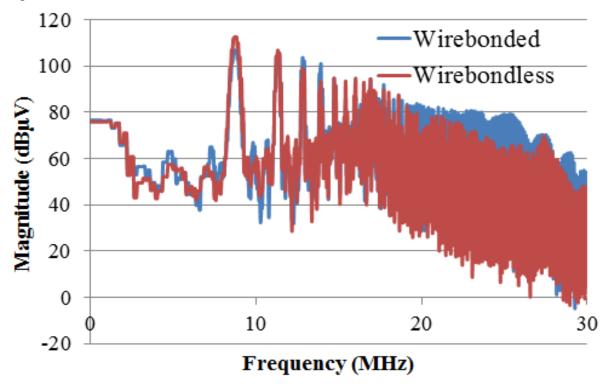

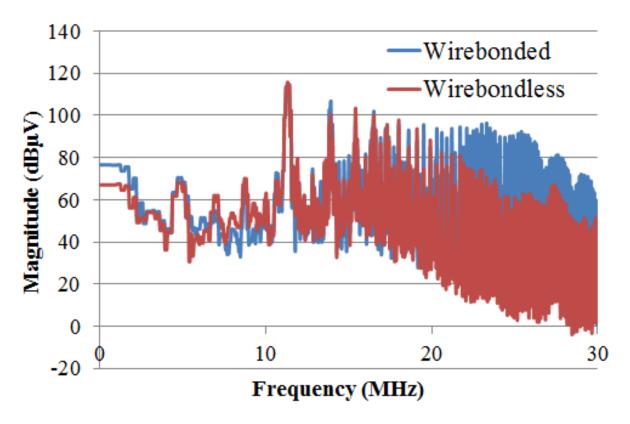

In traditional power modules, wire bonds are used as a top side interconnections that introduce additional parasitic inductance in the current conduction path and prone to failure mechanism under high thermomechanical stresses. The loop inductance of the proposed 3-D half-bridge module exhibits 71% lower parasitic inductance compared to a wire bonded module. The 3-D stack exhibits better switching performance compared to the wire bonded counterpart. The measurement results for the 3-D stack shows 30% decrease in current overshoot at turn-on and 43% voltage overshoot at turn-off compared to the wire bonded module. Through measurements, it has been shown that the conducted noise reduces by 20 dB in the frequency range 20-30 MHz for the 3-D stack compared to the wire bonded counterpart.

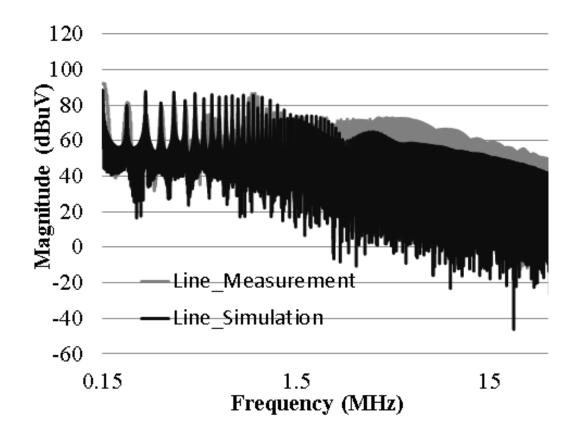

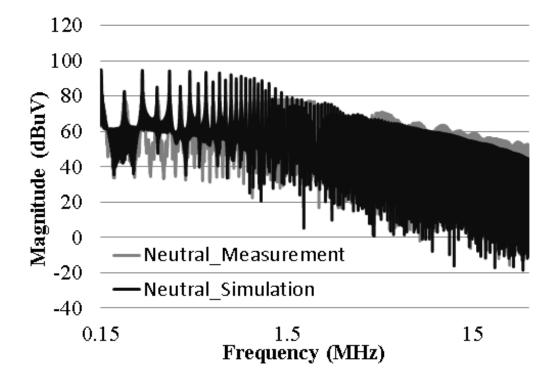

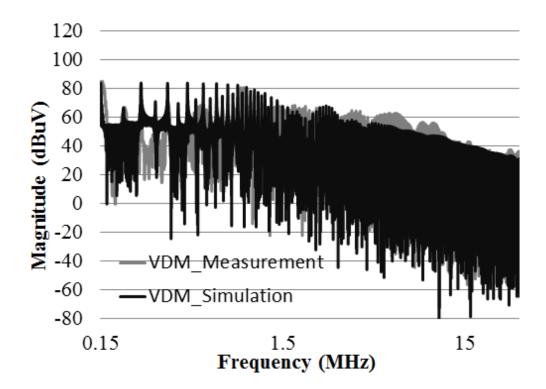

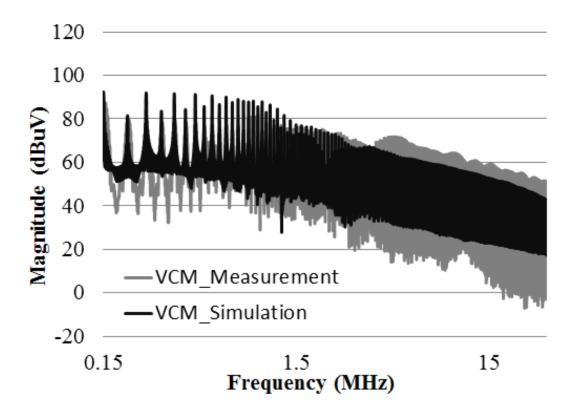

A simulation methodology using co-simulation techniques using ANSYS EM software tools is developed to predict EMI of a power module. Hardware verification of the proposed simulation methodology is performed to validate the co-simulation technique. The correlation coefficient between the measurement and simulation is found to be 0.73. It is shown that 53% of the variability in the simulation can be explained by the simulated result. Moreover, the simulated and measured amplitudes of the EMI spectrum closely match with each other with some variations due to round-off errors due to the FFT conversion.

#### Acknowledgements

I would like to convey my sincere gratitude and appreciation to my research advisor Dr. Simon S. Ang for his unconditional support and advice throughout my dissertation work. I wouldn't have completed the dissertation work without the support that Dr. Ang has provided me throughout the years of my degree.

I would also like to take this opportunity to thank Dr. Alan H. Mantooth, Dr. Juan C. Balda, and Dr. Jia Di for their consent to serve as my committee members. I appreciate the time and support they have provided me throughout the years.

With utmost respect, I would like to remember Dr. Michael D. Glover, although no longer with us. I have received training and certifications on numerous fabrication processes from him that has prepared me to progress with my dissertation research. Dr. Glover will always remain as a source of inspiration.

I would like to thank the staff members of High-Density Electronics Center (HiDEC). Tom Cannon, Kaoru Uema Porter, Errol Porter, Mike Steger, Clint Hardee has always been extremely helpful. I have always received utmost cooperation and help from all of them when I needed it most. They have unconditionally contributed a lot of effort to make my research a success.

I would like to thank all my lab and packaging team colleagues Hao Zhang, Jinchang Zhou, Sai Kishore, Shijie Wang, Shilpa Prabhudeva, Xingeng Yang, Xingsong Zhang, Si Huang, Mohammad Nasiri, Anish Kumar, Marzia Zaman, Akrem Elrojoubi, Sayan Seal, Chirs Farnell, Andrea Wallace, Nan Zhu, Zeke Zumbro whom I have worked with during my time at University of Arkansas. My special thanks go to Ramchandra Kotecha and Arman Rashid for helping me with measurements.

I would not be able to finish this dissertation research without the support of my wife Nandita Halder. She has always been on my side at most difficult of times and gave me encouragement to progress along with my research. I am blessed to have such a motivator in my life.

I thank my elder brother Shantanu Dutta, sister-in-law Falguni Sengupta, my nephew, my niece for giving me the motivation to keep moving forward. I also want to express my sincere thanks to my in-laws Ruhidas Halder, Lauxmi Halder and Rupack Halder for their support.

Lastly, I want to mention about my parents, Shekhar Dutta and Ava Dutta. They always encouraged and motivated me to pursue a Ph.D. degree. They have always been the greatest inspiration and support of my life. Whatever I am as a person today, it is due to their support and affection from the very day I was born.

# Dedication

This dissertation research is dedicated to my parents, Shekhar Dutta and Ava Dutta. They have been the greatest source of inspiration and support of my life.

# **Table of Contents**

| Chapter 1 Introduction                                                    | 1         |

|---------------------------------------------------------------------------|-----------|

| 1.1 Background and Motivation                                             |           |

| 1.2 Objective of Dissertation                                             |           |

| 1.3 Organization of Dissertation                                          |           |

| 1.4 References                                                            | 5         |

| Chapter 2 Design of 3-D Wire Bondless Half-Bridge Stacked Power Module    |           |

| 2.1 Design of Wire Bondless Power Module                                  |           |

| 2.2 LTCC Die Carrier Interposer Design                                    |           |

| 2.3 Top and Bottom DBC Design                                             |           |

| 2.4 Spring Loaded LTCC Interposer Design                                  |           |

| 2.5 Chapter Summary                                                       |           |

| 2.6 References                                                            |           |

| Chapter 3 Simulations of the Wire Bondless 3-D Half-Bridge Stack Power M  | lodule 26 |

| 3.1 Equivalent Parasitic Model for 3-D Half-Bridge Stack                  |           |

| 3.2 DC+ Inductance of 3-D Stack                                           |           |

| 3.3 DC- Inductance of 3-D Stack                                           |           |

| 3.4 Common Source Inductance of 3-D Stack                                 |           |

| 3.5 Gate Loop Inductance                                                  |           |

| 3.6 DC+ to DC- Loop Inductance                                            |           |

| 3.7 Effect of Connector Placement on Parasitic Inductance                 |           |

| 3.8 Measurement of Parasitic Inductance                                   |           |

| 3.9 High voltage simulation                                               |           |

| 3.10 Thermal Simulations                                                  |           |

| 3.11 Chapter Summary                                                      |           |

| 3.12 References                                                           |           |

| Chapter 4 Parasitic and Switching Characteristics Comparison of Wire Bone |           |

| and Wire Bonded Power Module                                              | 64        |

| 4.1 Parasitic Inductance Comparison                                       |           |

| 4.2 DC+ Inductance Comparison                                             | 67        |

| 4.3 DC- Inductance Comparison                                             |           |

| 4.4 Common Emitter Inductance Comparison                                  |           |

| 4.5 Gate Loop Inductance Comparison                                       |           |

| 4.6 DC+ to DC- Loop Inductance Comparison                                 |           |

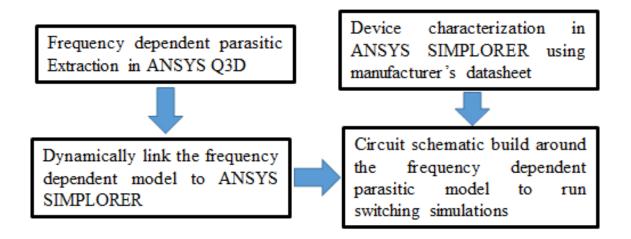

| 4.7 Simulation flow                                                       | 73        |

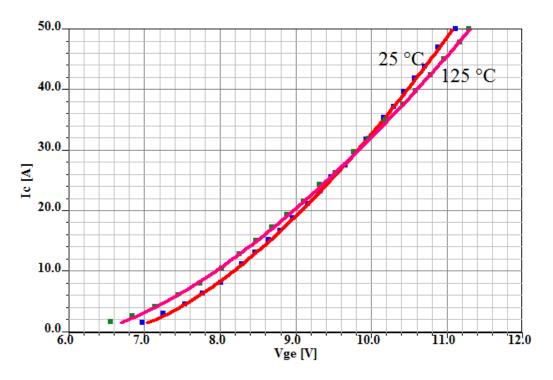

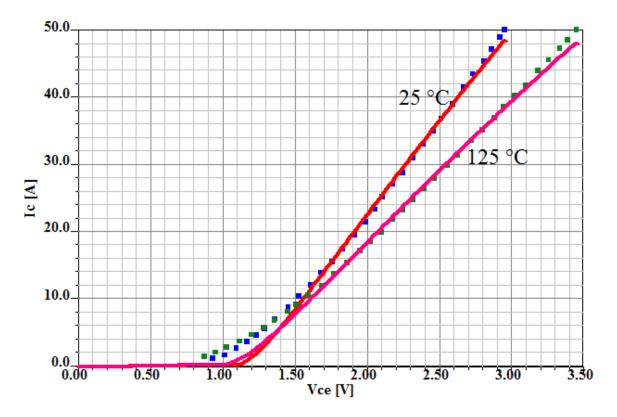

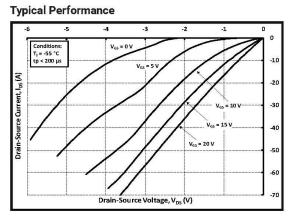

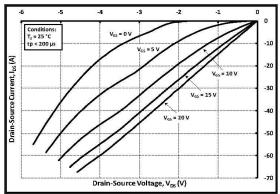

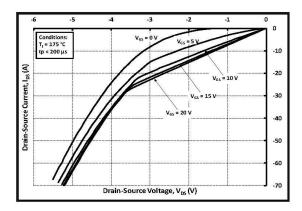

| 4.8 Device Characterization                                               | 74        |

| 4.9 Dynamic Coupling of Parasitic Model to ANSYS SIMPLORER                  | 80  |

|-----------------------------------------------------------------------------|-----|

| 4.10 Switching results                                                      |     |

| 4.11 Summary                                                                | 86  |

| 4.12 References                                                             | 87  |

| Chapter 5 Fabrication of the Wire Bondless 3-D Half-Bridge Power Module     | 89  |

| 5.1 Fabrication of Stand Alone Wire Bondless Power Module                   |     |

| 5.2 Die Top Surface Preparation                                             |     |

| 5.3 Top and bottom direct bond copper (DBC) preparation                     | 100 |

| 5.4 Connector attachment                                                    | 107 |

| 5.5 Low temperature co-fired ceramic (LTCC) device carrier preparation      | 110 |

| 5.6 LTCC punch profile creation                                             | 110 |

| 5.7 Precondition of the LTCC tapes                                          | 113 |

| 5.8 Creating device cut-outs and vias                                       | 113 |

| 5.9 Via fill and conductive metallization printing                          | 115 |

| 5.10 Lamination                                                             | 119 |

| 5.11 Co-firing                                                              |     |

| 5.12 Stand-alone Power Module Fabrication                                   | 128 |

| 5.13 Spring Loaded LTCC Interposer                                          |     |

| 5.14 Assembly of 3-D Module-Level Press-Pack Stack                          |     |

| 5.15 Summary                                                                |     |

| 5.16 References                                                             |     |

| Chapter 6 Characterization of 3-D Wire Bondless Half-Bridge Power Module    | 138 |

| 6.1 Switching Characteristics of the 3-D Stacked Power Module               | 138 |

| 6.2 Static Characteristics of the 3-D Stack                                 | 146 |

| 6.3 Conducted Electromagnetic Interference Measurement                      |     |

| 6.4 Thermal Cycling Test                                                    | 155 |

| 6.5 Leakage Current Measurement                                             | 157 |

| 6.6 Chapter Summary                                                         | 163 |

| 6.7 References                                                              |     |

| Chapter 7 Electromagnetic Interference Simulations for Wide Bandgap Power E |     |

| Modules                                                                     |     |

| 7.1 Introduction                                                            |     |

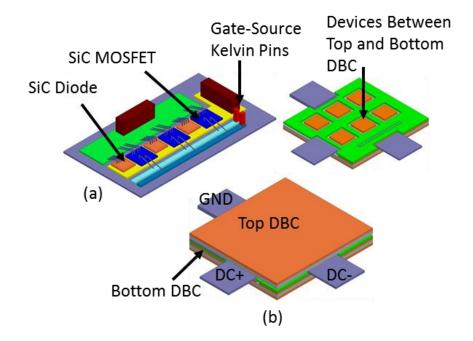

| 7.2 Design and Layout of Power Module                                       | 169 |

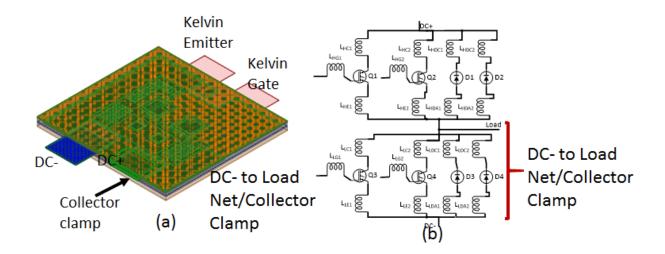

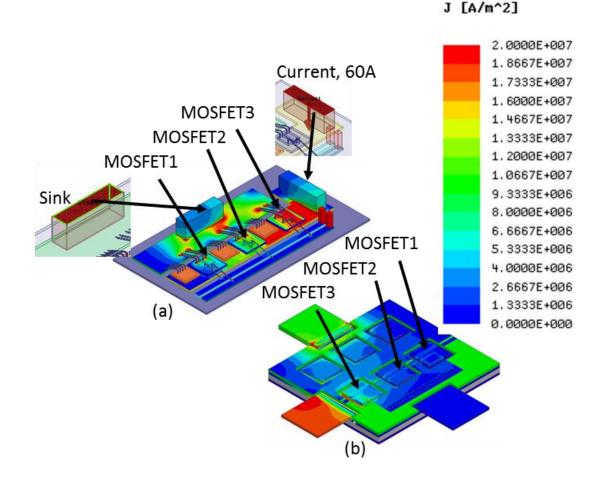

| 7.3 Static Current Distribution Analysis                                    |     |

| 7.4 Parasitic Extraction                                                    | 172 |

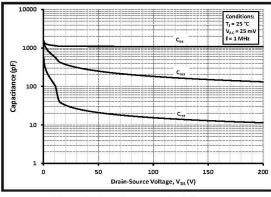

| 7.5 Device Characterization                                                 | 174 |

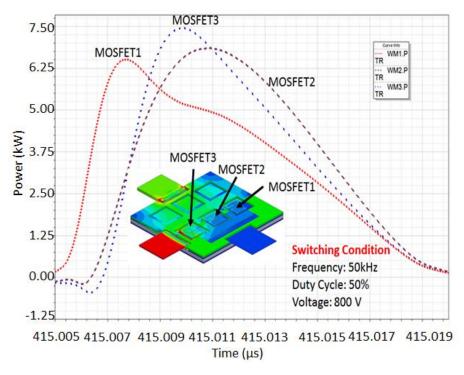

| 7.6 Circuit and System Simulation                                           | 175 |

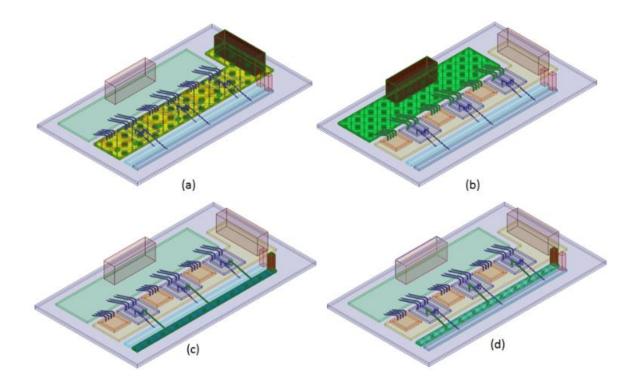

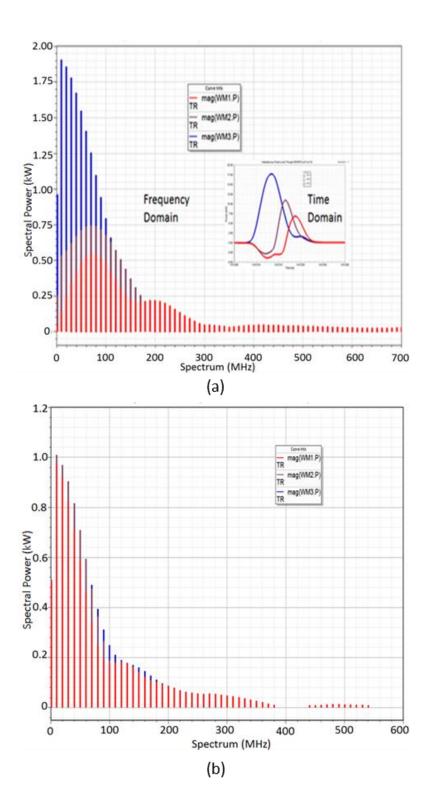

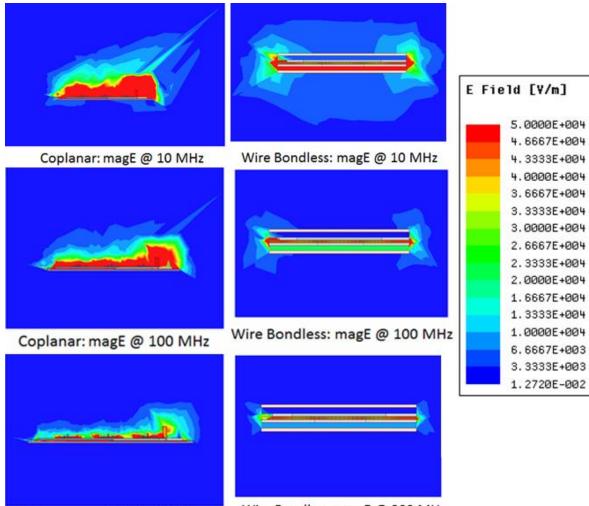

| 7.7 Full Wave Simulation                                                    | 179 |

| Appendix                                    |  |

|---------------------------------------------|--|

| References                                  |  |

| 8.2 Future Work                             |  |

| 8.1 Dissertation Contribution               |  |

| Chapter 8 Conclusion and Future Work        |  |

| 7.12 References                             |  |

| 7.11 Acknowledgement                        |  |

| 7.10 Conclusions                            |  |

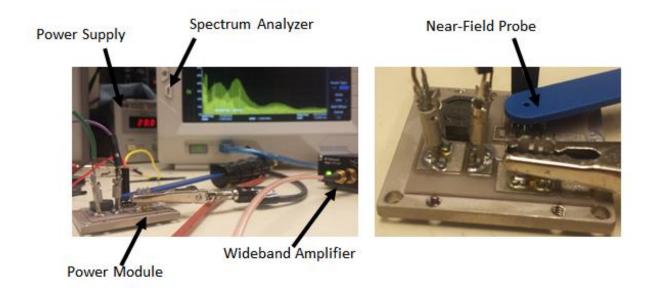

| 7.9 Conducted EMI Simulation and Validation |  |

| 7.8 Radiated EMI Validation                 |  |

# List of Figures

| Fig. 2.1. Exploded view of the 3-D stacked wire bondless power module                          | 8       |

|------------------------------------------------------------------------------------------------|---------|

| Fig. 2.2. 3-D rendition of the proposed 3-D power module stack                                 | 9       |

| Fig. 2.3. (a) 3-D rendition of the interconnection scheme for the 3-D power module stack [     | 2], (b) |

| side view of the interconnection scheme (only conducting objects are shown in figure for       |         |

| simplicity)                                                                                    | 11      |

| Fig. 2.4. Antiparallel current path configuration for the proposed 3-D power module stack      | [2].12  |

| Fig. 2.5. Current conduction loop of an overlapping current path separated by a dielectric     | 12      |

| Fig. 2.6. Loop inductance vs. dielectric separation                                            | 13      |

| Fig. 2.7. Overlapping forward and return current path [3]                                      | 14      |

| Fig. 2.8. Single layer current path [3]                                                        | 15      |

| Fig. 2.9. (a) 3-D rendition of the wire bondless power module, (b) exploded view of the wi     | re      |

| bondless power module                                                                          | 16      |

| Fig. 2.10. (a) Layer 1, device cutout (b) layer 2, metallization for attaching Si-IGBTs (c) la | yer 3,  |

| metallization for SiC diode attachment (d) layer 4, back side metallization for direct solder  |         |

| attachment to bottom DBC                                                                       | 17      |

| Fig. 2.11. (a) LTCC die carrier interposer with device placement shown (b) exploded view       | of the  |

| multilayer LTCC interposer                                                                     | 18      |

| Fig. 2.12. Dimensions in mm for LTCC interposer (a) layer 1 (b) layer 2 (c) layer 3 (d) layer  | er 4 19 |

| Fig. 2.13. Illustration of LTCC interposer with different cavity depths                        | 20      |

| Fig. 2.14. (a) Layout of bottom DBC (b) layout of top DBC                                      | 21      |

| Fig. 2.15. (a) Bottom (b) top DBC substrate with gate, emitter, collector and Kelvin connect   | ctors   |

|                                                                                                |         |

| Fig. 2.16. LTCC fixture designed in AutoCAD                                                    | 23      |

| Fig. 2.17. Side view of the LTCC interposer with critical dimensions (mm)                      | 24      |

| Fig. 3.1. Equivalent inductance map of the proposed 3-D half-bridge stack power module         |         |

| Fig. 3.2. DC+ inductance associated with the 3-D stack power module                            |         |

| Fig. 3.3. Frequency dependent parasitic inductance and resistance for DC+ net of the 3-D s     | tack    |

| power module                                                                                   |         |

| Fig. 3.4. DC- inductance associated with the 3-D stack power module                            |         |

| Fig. 3.5. Frequency dependent parasitic inductance and resistance for DC- net of the 3-D s     |         |

| power module                                                                                   |         |

| Fig. 3.6. Common source net associated with the 3-D stack power module                         |         |

| Fig. 3.7. Frequency dependent parasitic inductance and resistance for common emitter net       |         |

| high-side devices of the 3-D stack power module                                                |         |

| Fig. 3.8. Frequency dependent parasitic inductance and resistance for common source net f      |         |

| low-side devices of the 3-D stack power module                                                 |         |

| Fig. 3.9. Gate net of the 3-D stack power module                                               | 36      |

| Fig. 3.10. Frequency dependent parasitic inductance and resistance of gate net of the 3-D stack | ζ    |

|-------------------------------------------------------------------------------------------------|------|

| power module                                                                                    | 36   |

| Fig. 3.11. DC+ to DC- loop net for 3-D half-bridge stack power module configuration             | 37   |

| Fig. 3.12. Frequency dependent inductance and resistance for DC+ to DC- loop net of the 3-D     |      |

| half-bridge stack power module                                                                  | 38   |

| Fig. 3.13. Connectors placed opposite to each other (case 1)                                    | 39   |

| Fig. 3.14. Connectors placed opposite to each other (case2)                                     | 40   |

| Fig. 3.15. Connectors placed on the same side of the module (case 3)                            | 40   |

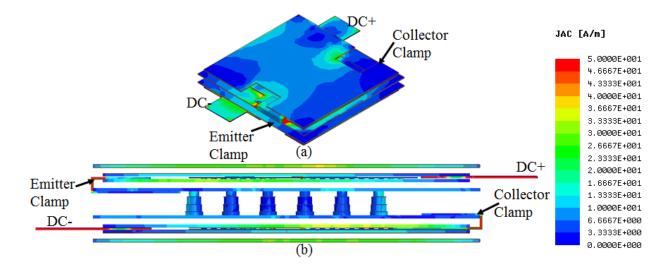

| Fig. 3.16. Surface current density with connectors and conductive clamps placed opposite to ea  | ach  |

| other (case 1)                                                                                  | 41   |

| Fig. 3.17. Surface current density with connectors and conductive clamps placed opposite to ea  | ach  |

| other (case 2)                                                                                  | 42   |

| Fig. 3.18. Surface current density with connectors placed on the same side (case 3)             | 42   |

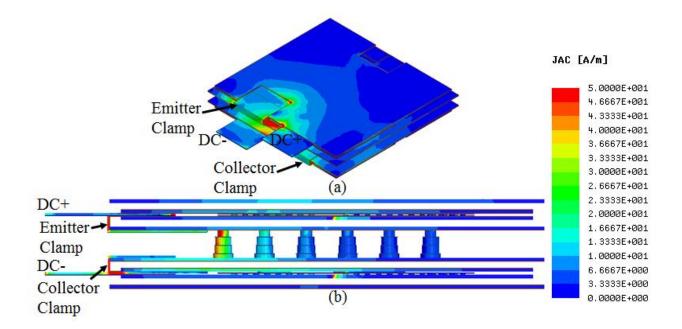

| Fig. 3.19. Comparison of DC+ to DC- loop parasitic inductance between cases 1, 2 and 3          | 43   |

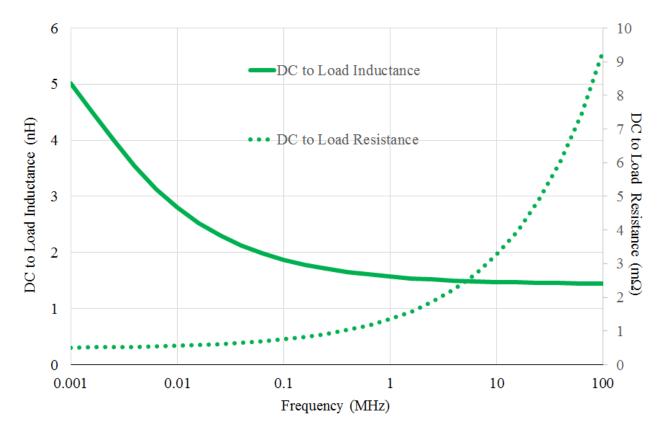

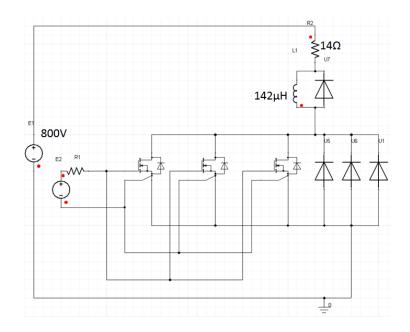

| Fig. 3.20. DC terminal to load loop net (stand-alone modules)                                   | . 44 |

| Fig. 3.21. Frequency dependent inductance for DC to load loop net                               |      |

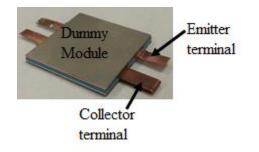

| Fig. 3.22. Dummy module fabricated for inductance measurement                                   | 45   |

| Fig. 3.23. Test setup for the inductance measurement using HP 4284A LCR meter and HP            |      |

| 160474 test fixture                                                                             |      |

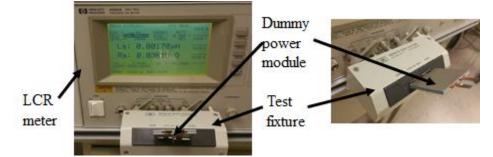

| Fig. 3.24. Comparison between simulated and measured parasitic inductance of collector-emitt    |      |

| loop of stand-alone power module                                                                | 46   |

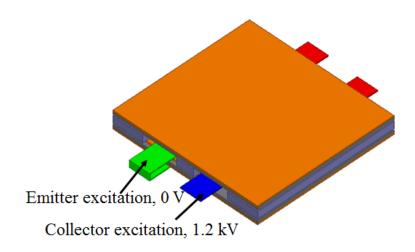

| Fig. 3.25. High voltage simulation setup for wire bondless power module                         |      |

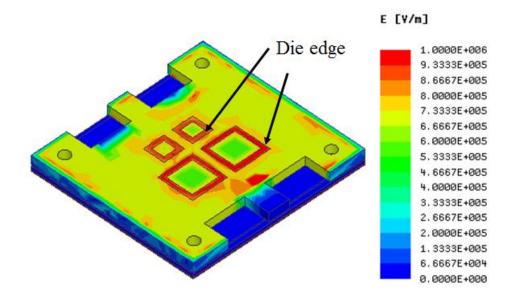

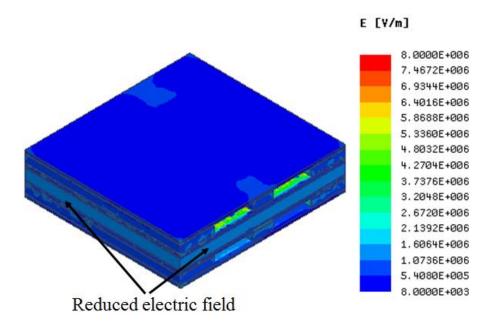

| Fig. 3.26. Electric field simulation under 1.2 kV applied voltage                               |      |

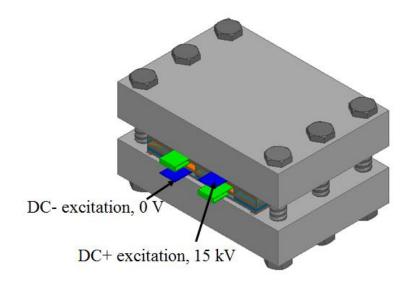

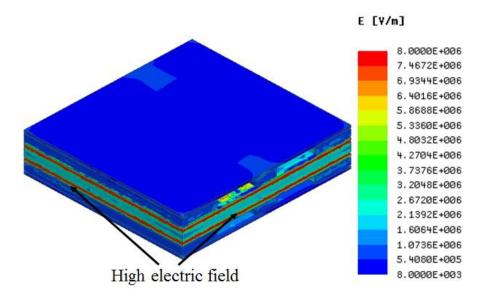

| Fig. 3.27. High voltage simulation setup for 3-D stack                                          |      |

| Fig. 3.28. Electric field simulation without edge termination                                   |      |

| Fig. 3.29. Electric field simulation with 2 mm edge termination                                 |      |

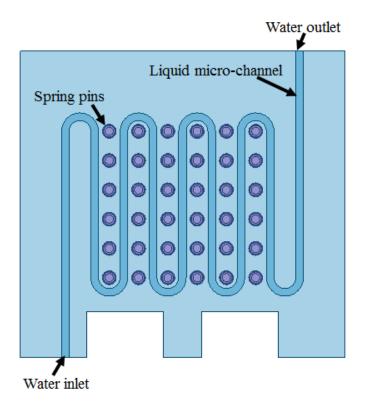

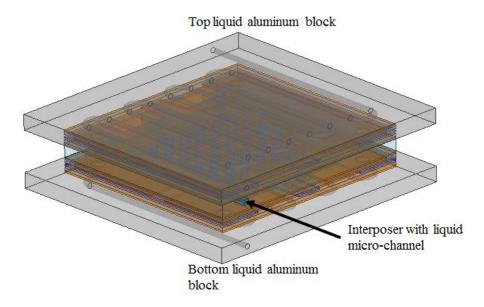

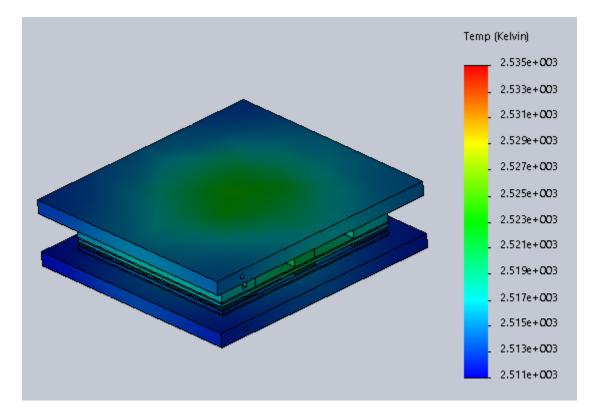

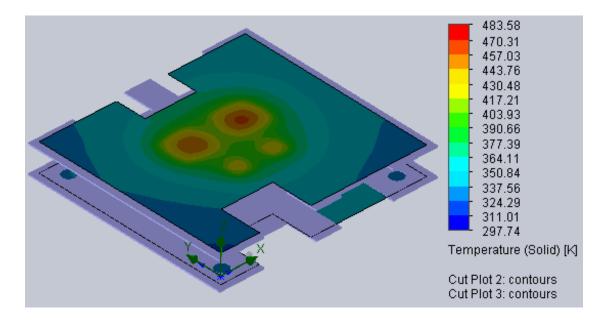

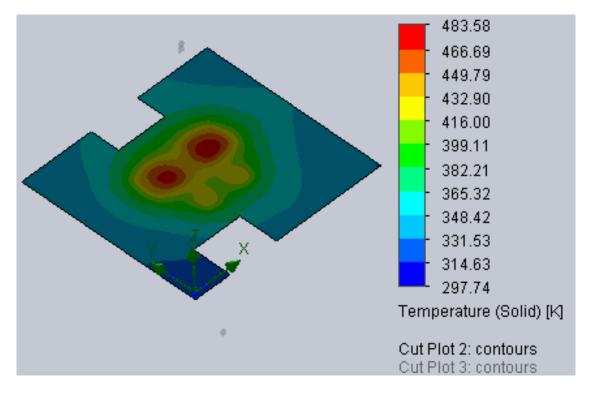

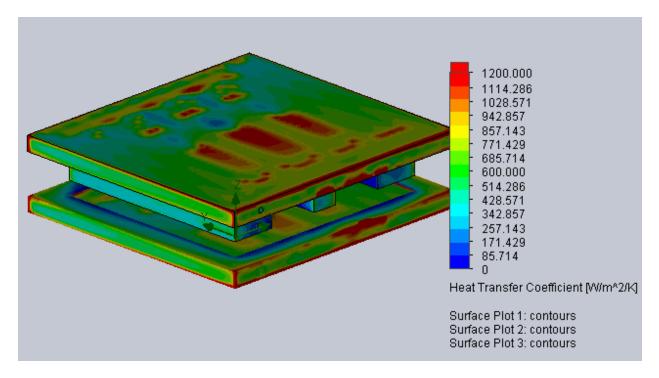

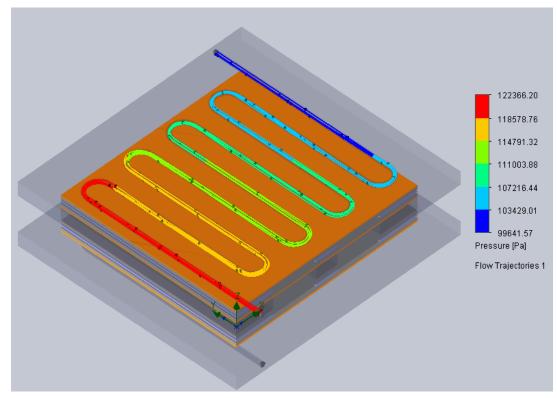

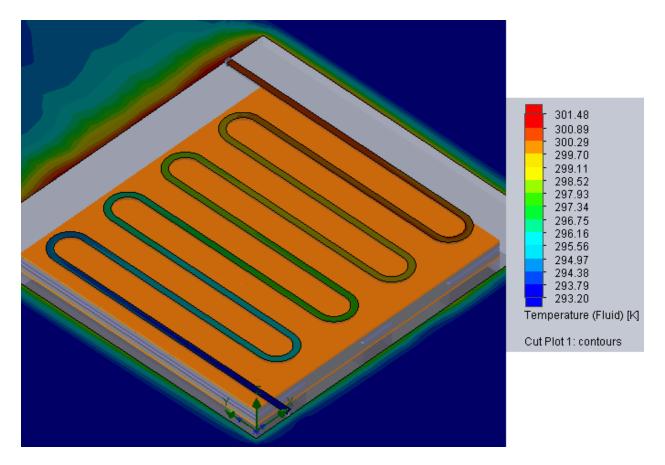

| Fig. 3.30. Liquid microchannel embedded into the spring loaded LTCC interposer                  |      |

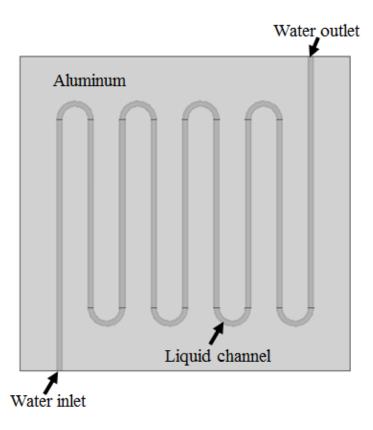

| Fig. 3.31. Top and bottom aluminum block with liquid channel showing inlet and outlet           |      |

| Fig. 3.32. Thermal simulation model for 3-D wire bondless power module with liquid channels     | S    |

|                                                                                                 |      |

| Fig. 3.33. Thermal simulation without liquid microchannel convection                            |      |

| Fig. 3.34. Junction temperature of top module                                                   |      |

| Fig. 3.35. Junction temperature of bottom module                                                |      |

| Fig. 3.36. Heat transfer coefficients of the liquid micro-channels blocks                       |      |

| Fig. 3.37. Change of pressure along the fluid flow direction                                    |      |

| Fig. 3.38. Fluid temperature contour of liquid microchannel                                     |      |

| Fig. 4.1. Wire bonded half-bridge power module                                                  |      |

| Fig. 4.2. Conducting nets of the wire bonded half-bridge module                                 |      |

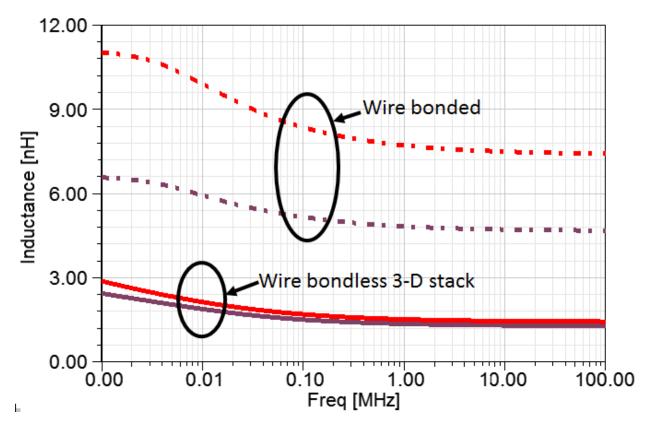

| Fig. 4.3. DC+ parasitic inductance comparison between 3-D stack and wire bonded half-bridge     |      |

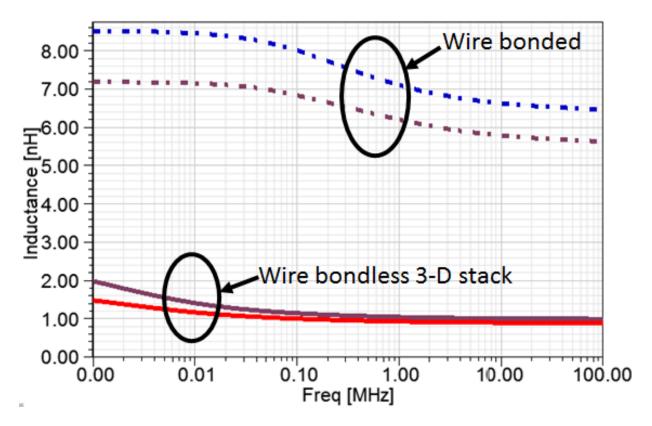

| Fig. 4.4. DC- parasitic inductance comparison between 3-D stack and wire bonded half-bridge     | 69   |

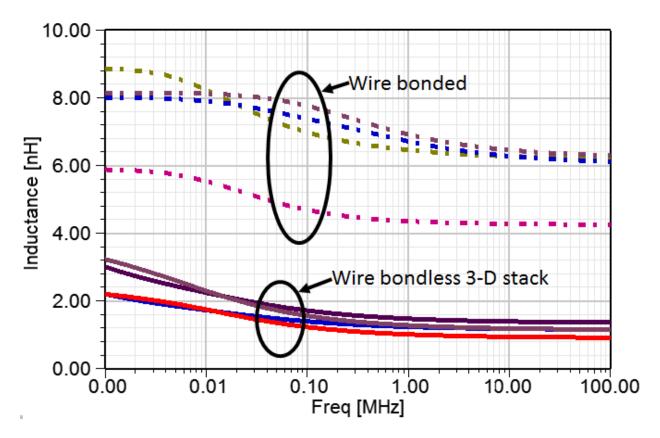

| Fig. 4.5. Common emitter parasitic inductance comparison between 3-D stack and wire bonded            |    |

|-------------------------------------------------------------------------------------------------------|----|

| half-bridge                                                                                           | 70 |

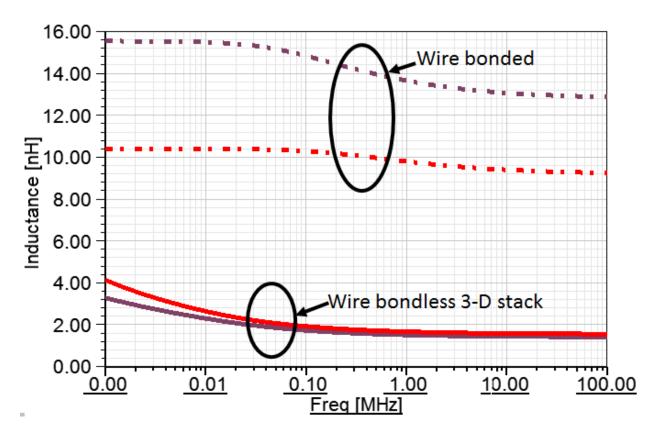

| Fig. 4.6. Gate loop parasitic inductance comparison between 3-D stack and wire bonded half-<br>bridge | 71 |

| Fig 4.7. DC+ to DC- loop inductance comparison between the 3-D stack and the wire bonded              |    |

| power module                                                                                          |    |

| Fig. 4.8 Simulation process flow to simulate the switching behavior of the power module               |    |

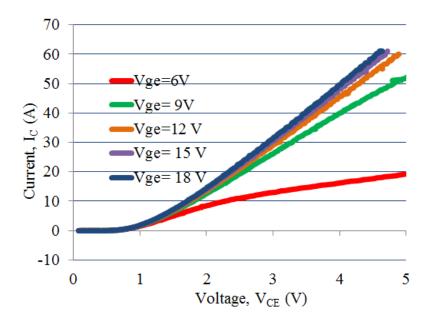

| Fig. 4.9. Transfer characteristics of Si-IGBT fitted in ANSYS SIMPLORER                               |    |

| Fig. 4.10. Output characteristics of Si-IGBT fitted in ANSYS SIMPLORER                                | 77 |

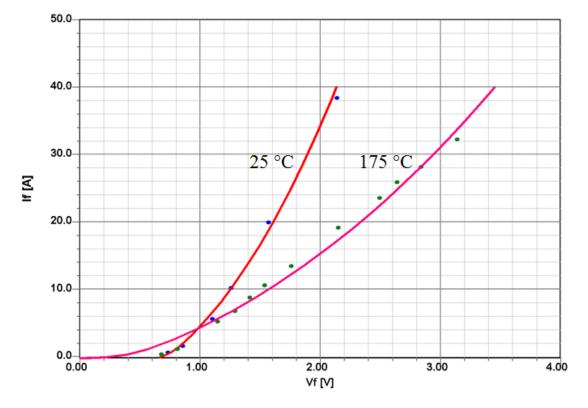

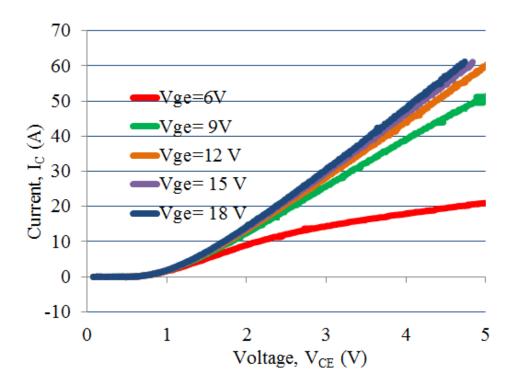

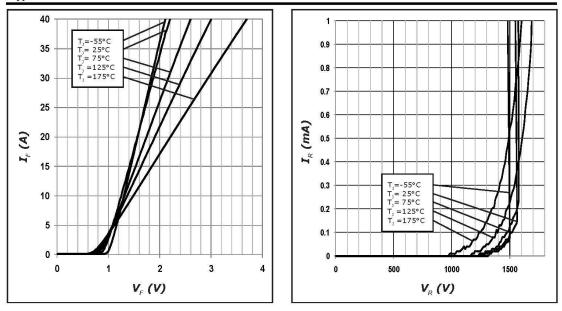

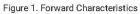

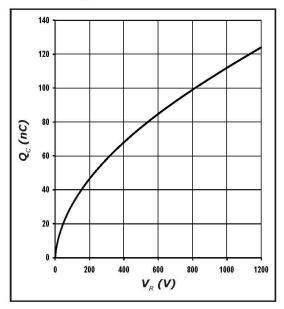

| Fig. 4.11. Forward characteristics of SiC Schottky barrier diode fitted in ANSYS SIMPLORER            | ł  |

|                                                                                                       |    |

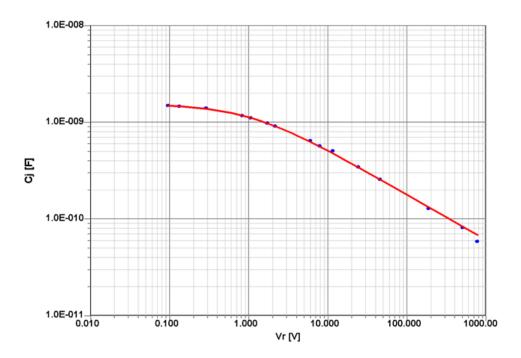

| Fig. 4.12. Junction capacitance of SiC Schottky barrier diode fitted in ANSYS SIMPLORER               |    |

| Fig. 4.13. Frequency dependent parasitic model for wire bonded half-bridge power module               | 81 |

| Fig. 4.14. Frequency dependent parasitic model for the 3-D half-bridge stack                          | 82 |

| Fig. 4.15. Switching circuit of the wire bonded module build around the parasitic model               |    |

| Fig. 4.16. Switching circuit of 3-D stack built around the parasitic model                            | 84 |

| Fig. 4.17. Simulated waveforms of the 3-D stack power module compared to the wire bonded              |    |

| power module                                                                                          | 86 |

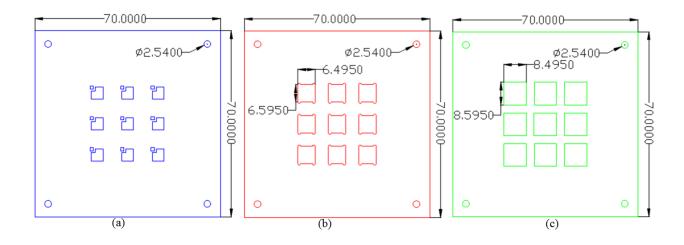

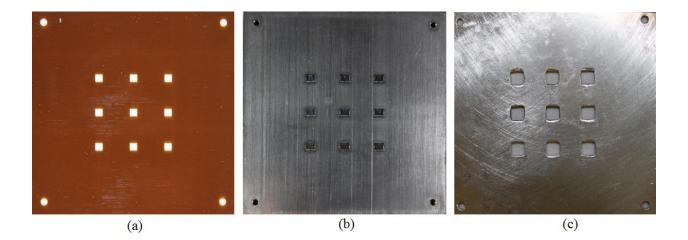

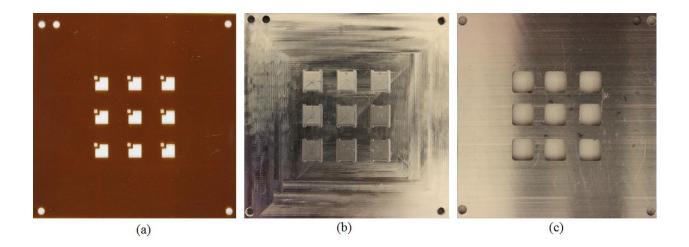

| Fig. 5.1. AutoCAD design (a) Kapton mask, (b) bottom Aluminum fixture, (c) top Aluminum               |    |

| fixture for E-beam evaporation on SiC diode                                                           | 91 |

| Fig. 5.2 AutoCAD design (a) Kapton mask, (b) aluminum bottom frame, (c) aluminum top fram             |    |

| for E-beam evaporation on Si-IGBT                                                                     |    |

| Fig. 5.3. (a) Kapton mask, (b) bottom Aluminum fixture with cavity, (c) top Aluminum fixture          |    |

| with device cutouts for thin film deposition on Anode of SiC Schottky barrier diodes                  |    |

| Fig. 5.4. Kapton mask, (b) bottom Aluminum fixture with cavity, (c) top Aluminum fixture with         |    |

| device cutouts for thin film deposition on gate and emitter of Si-IGBT devices                        | 94 |

| Fig. 5.5. Assembly used for Ti/Ni/Ag E-beam evaporation on gate and emitter of Si-IGBT                |    |

| devices                                                                                               |    |

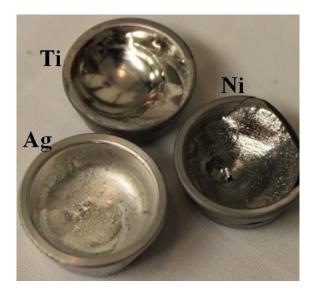

| Fig. 5.6. Glass coated graphite and Molybdenum (Mo) crucibles used for Ti/Ni/Ag deposition            |    |

| Fig. 5.7. Silicon IGBT device with Ti/Ni/Ag evaporated on the gate and emitter electrodes             | 97 |

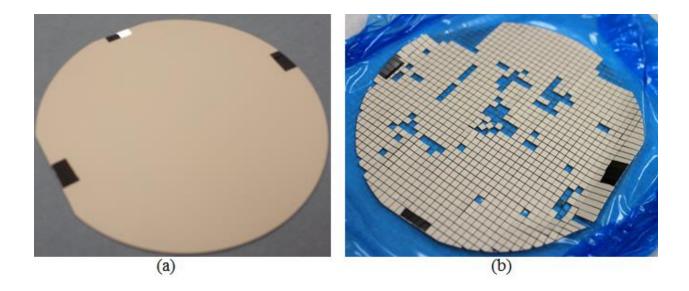

| Fig. 5.8. (a) Silicon wafer with Ti/Ni/Ag evaporation to prepare dummy devices for die shear          |    |

| test, (b) diced 2.75 mm $\times 2.75$ mm dummy devices                                                |    |

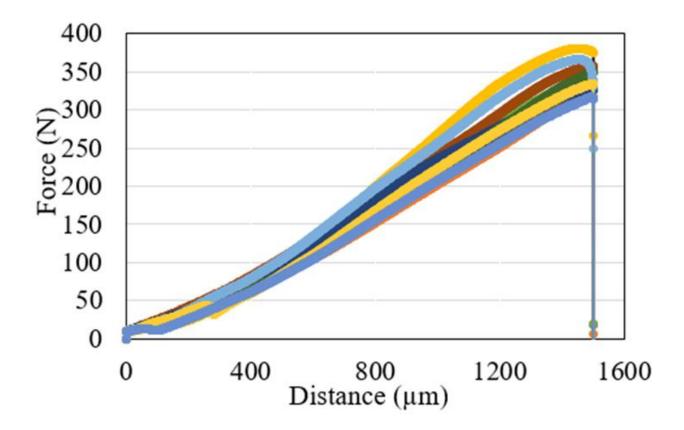

| Fig. 5.9. Die shear strength for ten samples                                                          |    |

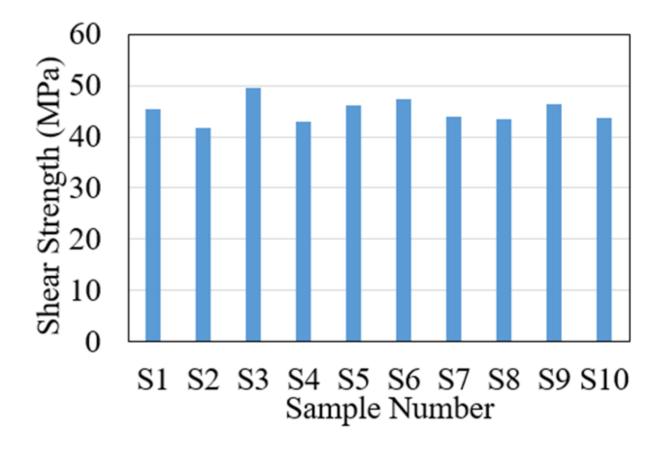

| Fig. 5.10. Die shear strength in mega pascle (MPa) for ten samples                                    |    |

| Fig. 5.11 (a) Ultrasonic acetone clean of DBC, (b) 10% HCl clean of DBC 1                             | 01 |

| Fig. 5.12. Nickel plating setup 1                                                                     |    |

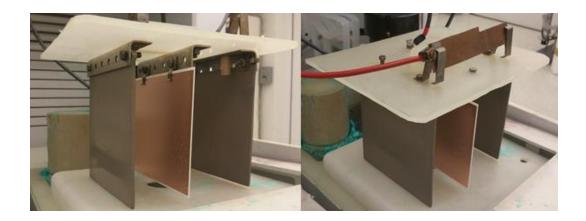

| Fig. 5.13. (a) Bare copper DBC substrate, (b) nickel plated DBC substrate                             | 02 |

| Fig. 5.14. Negative photomask used to pattern the bottom DBC of the stand-alone power modu            |    |

|                                                                                                       |    |

| Fig. 5.15. Negative photomask used to pattern the top DBC of the stand-alone power module 1           | 05 |

| Fig. 5.16. Chemcut spray etcher for chemical etching of DBC                                    | 106 |

|------------------------------------------------------------------------------------------------|-----|

| Fig. 5.17. K&S dicing saw used for dicing the DBC substrates                                   | 106 |

| Fig. 5.18. Bottom and top DBC of the stand-alone power module                                  | 107 |

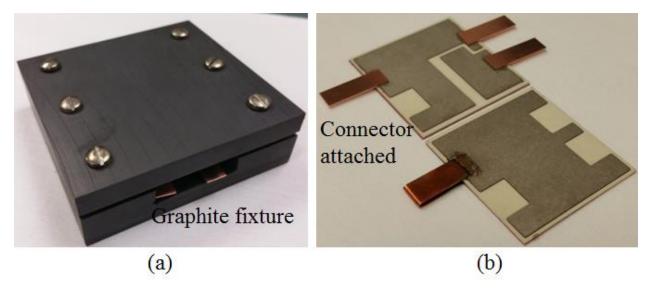

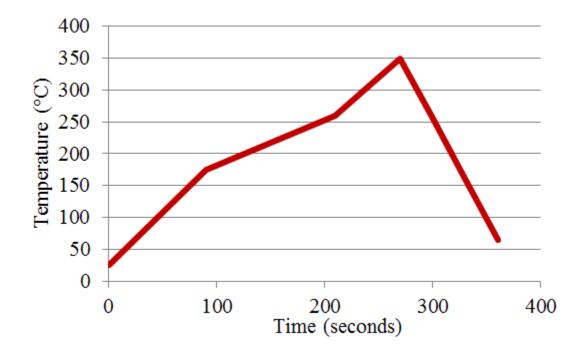

| Fig 5.19. Graphite fixture for solder reflow, (b) connectors attached to the DBC               | 109 |

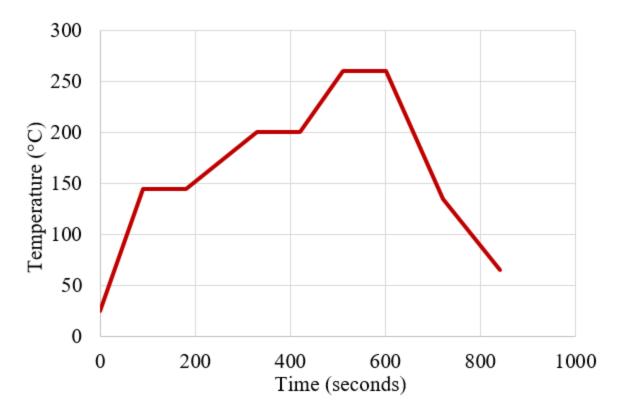

| Fig. 5.20. Reflow profile used for connector attachment                                        | 109 |

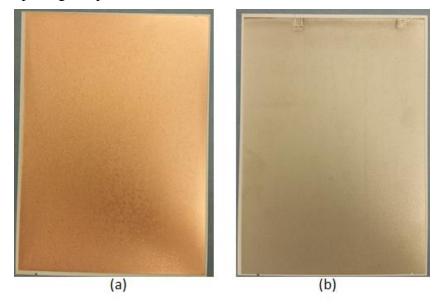

| Fig. 5.21. AutoCAD drawing of different layers of the LTCC die carrier                         | 111 |

| Fig. 5.22 AutoCAD drawing of multi-layer LTCC overlaid on top of each other                    | 112 |

| Fig. 5.23. Punch profile design in AutoCAD for punching vias and cavities on LTCC              | 112 |

| Fig. 5.24. Via punch equipment                                                                 | 114 |

| Fig. 5.25. 6"×6" LTCC GreenTape <sup>™</sup> after via punch and formation of device cutout    | 114 |

| Fig. 5.26. Via fill process using a squeegee                                                   |     |

| Fig. 5.27. Screen used to print the metallization of the LTCC GreenTape <sup>TM</sup>          |     |

| Fig. 5.28. Screen printing of LTCC metallization                                               | 117 |

| Fig. 5.29. Edge cutter used to separate the different layers of LTCC tapes from a 6"×6"        |     |

| GreenTape <sup>TM</sup>                                                                        |     |

| Fig. 5.30. Different layers of multi-layer LTCC die carrier                                    |     |

| Fig. 5.31. Stacked LTCC GreenTape <sup>TM</sup> in preparation for lamination process          |     |

| Fig. 5.32. LTCC GreenTape <sup>™</sup> sandwiched between two aluminum bases                   |     |

| Fig. 5.33. LTCC GreenTape <sup>™</sup> assembly wrapped in latex in preparation for lamination | 124 |

| Fig. 5.34. AUDIONVAC VM 101H vacuum sealer                                                     |     |

| Fig. 5.35. Vacuum sealed LTCC GreenTape <sup>TM</sup> assembly to carry out lamination process |     |

| Fig. 5.36. Isostatic laminator used for laminating LTCC GreenTape <sup>TM</sup>                |     |

| Fig. 5.37. LTCC die carrier after the firing process                                           |     |

| Fig. 5.38. Diced LTCC die carrier                                                              |     |

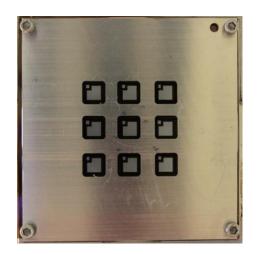

| Fig. 5.39. MRSI-503M flip-chip bonder                                                          |     |

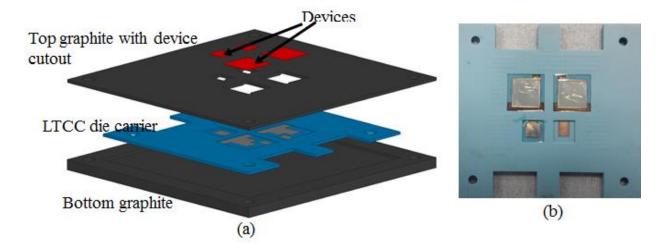

| Fig. 5.40 (a) Exploded view of the die attach assembly on LTCC die carrier substrate (b) LTC   |     |

| die carrier with attached Si-IGBT and SiC Schottky barrier diodes                              |     |

| Fig. 5.41. Exploded view of the assembly to fabricate the stand-alone power modules            |     |

| Fig. 5.42. Fixturing used to fabricate the stand-alone power module                            |     |

| Fig. 5.43. SAC 305 reflow profile used for attaching the top and the bottom DBC substrate wi   |     |

| the LTCC die carrier                                                                           |     |

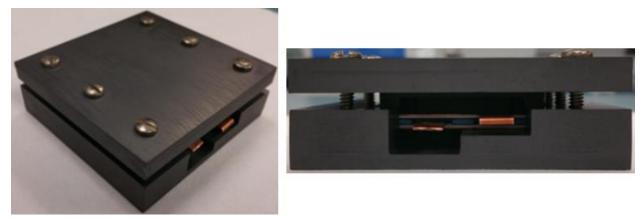

| Fig. 5.44. Fabricated stand-alone power module showing all the terminals                       |     |

| Fig. 5.45. Side view of the LTCC interposer with critical dimensions (mm)                      |     |

| Fig. 5.46. Fabricated LTCC spring-loaded interposer                                            |     |

| Fig. 5.47. Chronological step by step representation of the process to assemble the 3-D modul  |     |

| level half-bridge power module stack                                                           |     |

| Fig. 5.48. Fabricated prototype of the 3-D module-level half-bridge stack                      |     |

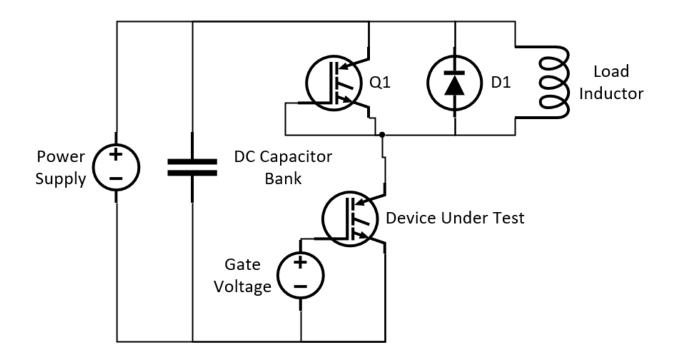

| Fig. 6.1. Double pulse test circuit                                                            |     |

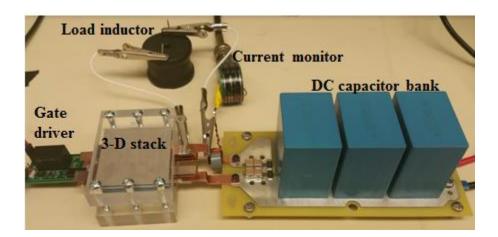

| Fig. 6.2. Double pulse test setup for switching test                                           |     |

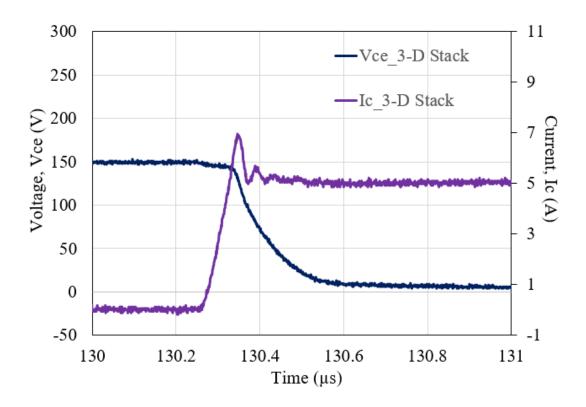

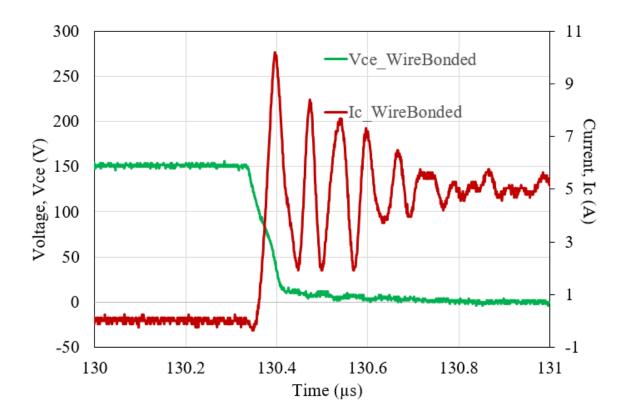

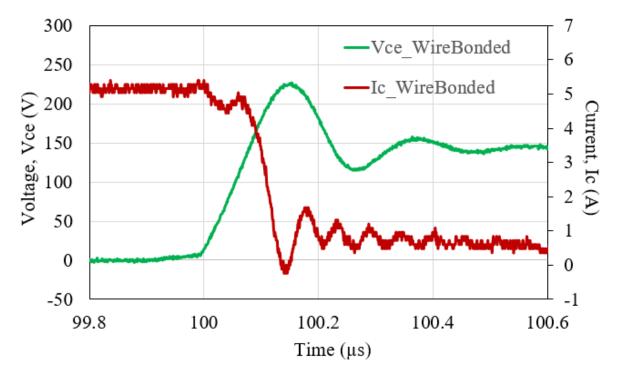

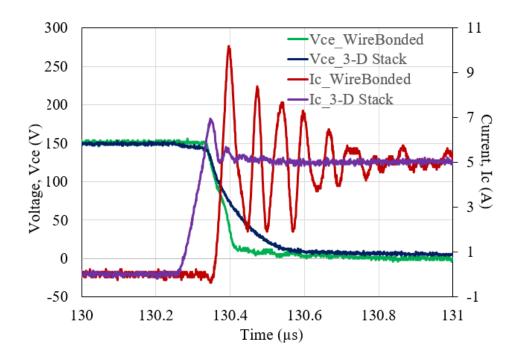

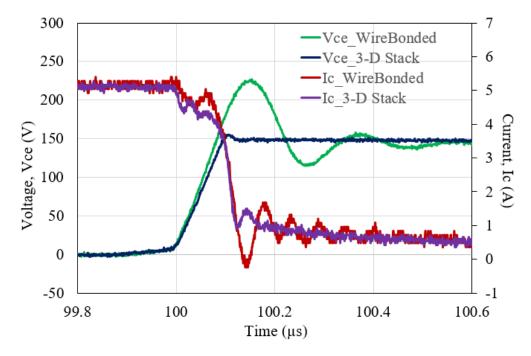

| Fig. 6.3. Turn-on current and voltage waveform of the wire bondless 3-D stack (measured)       | 141 |

| Fig. 6.4. Turn-off current and voltage waveform of the wire bondless 3-D stack (measured) 141          |

|--------------------------------------------------------------------------------------------------------|

| Fig. 6.5 Fabricated wire bonded half-bridge module                                                     |

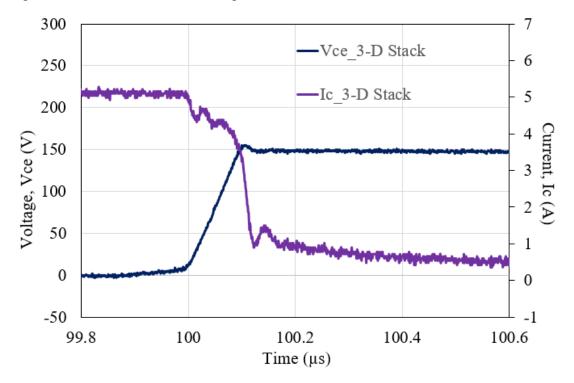

| Fig. 6.6. Turn-on current and voltage waveform of the wire bonded module (measured) 143                |

| Fig. 6.7. Turn-off current and voltage waveform of the wire bonded module (measured) 143               |

| Fig. 6.8. Comparison of the turn-on voltage and current waveform between 3-D stack and wire            |

| bonded power module                                                                                    |

| Fig. 6.9 Comparison of the turn-off voltage and current waveforms between 3-D stack and wire           |

| bonded power module                                                                                    |

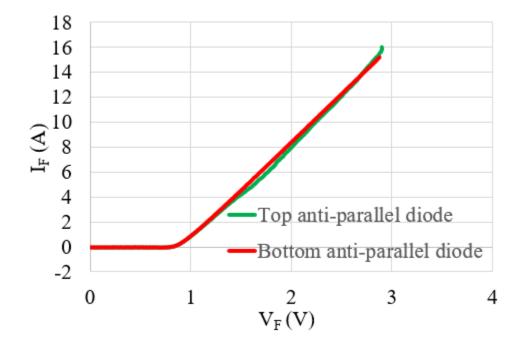

| Fig. 6.10. On-state characteristics of top module                                                      |

| Fig. 6.11. On-state characteristics of bottom module                                                   |

| Fig. 6.12. Forward characteristics of the SiC Schottky barrier diode                                   |

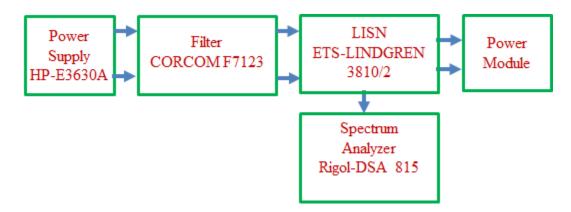

| Fig. 6.13. Measurement setup for conducted EMI measurement                                             |

| Fig. 6.14. Circuit schematic of a half-bridge inverter                                                 |

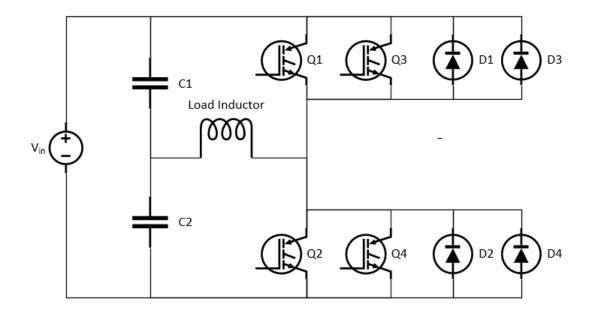

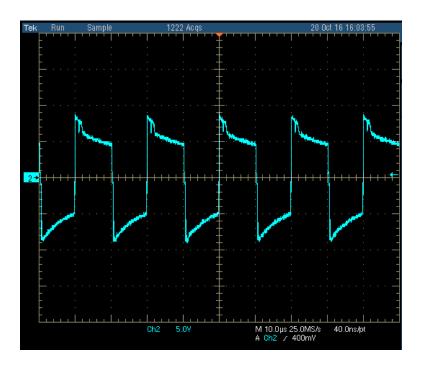

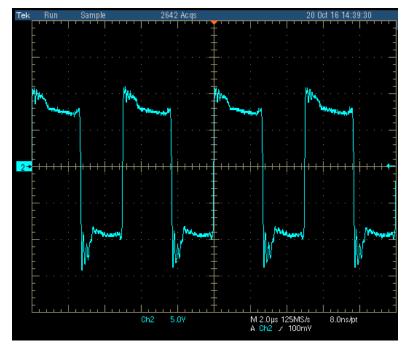

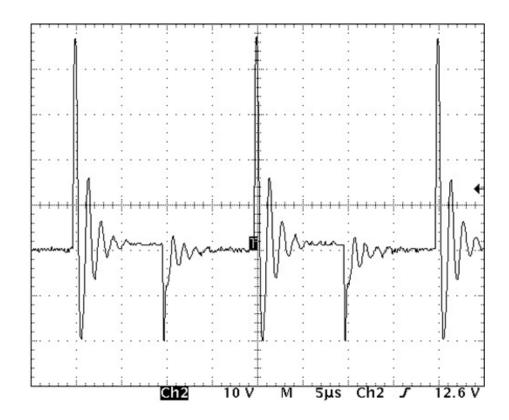

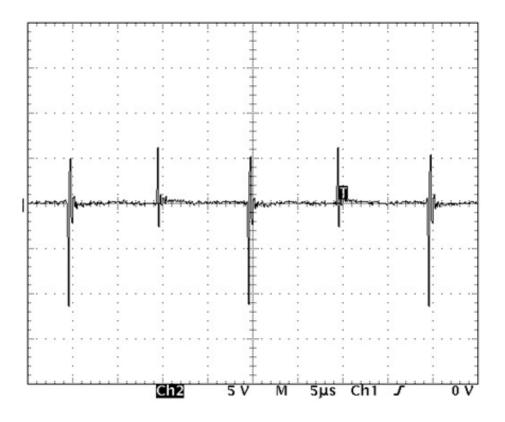

| Fig. 6.15. Output voltage at 50 kHz switching frequency (3-D wire bondless half-bridge) 151            |

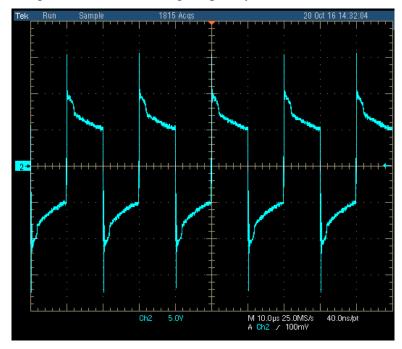

| Fig. 6.16. Output voltage at 50 kHz switching frequency (wire bonded half-bridge)                      |

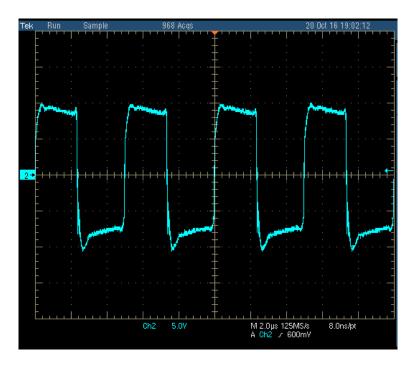

| Fig. 6.17. Output voltage at 200 kHz switching frequency (3-D wire bondless half-bridge) 152           |

| Fig. 6.18. Output voltage at 200 kHz switching frequency (wire bonded module)                          |

| Fig. 6.19. Measured conducted EMI at 50 kHz [1] 154                                                    |

| Fig. 6.20. Measured conducted EMI at 100 kHz [1] 154                                                   |

| Fig. 6.21. Measured conducted EMI at 200 kHz [1] 155                                                   |

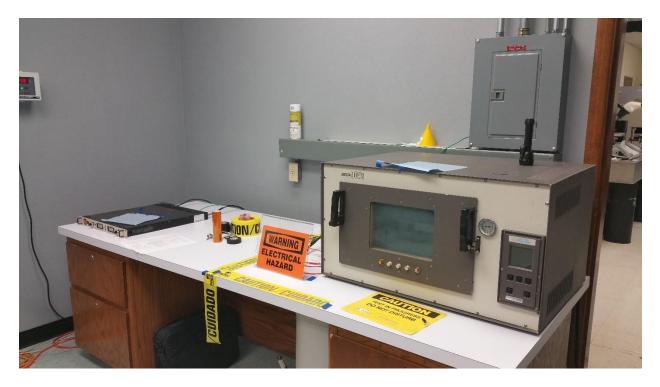

| Fig. 6.22. Samples placed inside oven for thermal cycling experiment                                   |

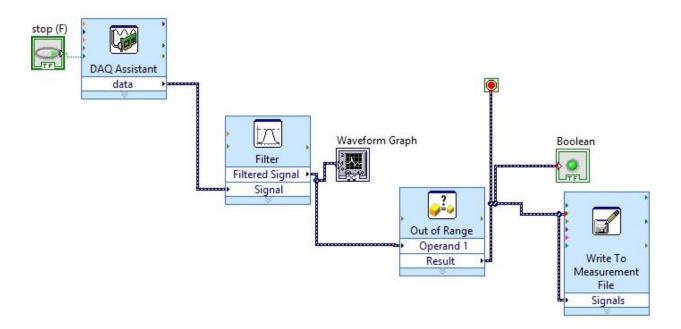

| Fig. 6.23. Leakage current measurement setup                                                           |

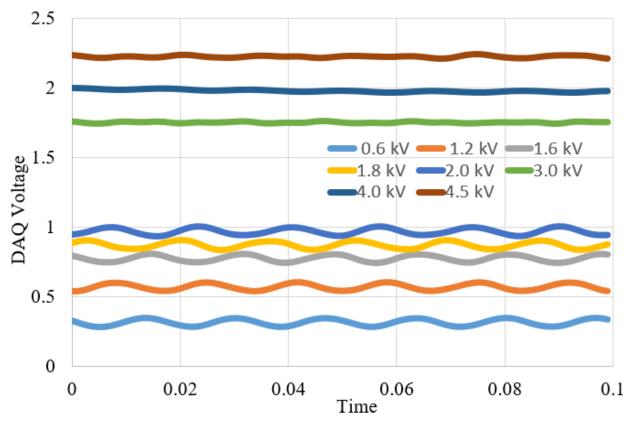

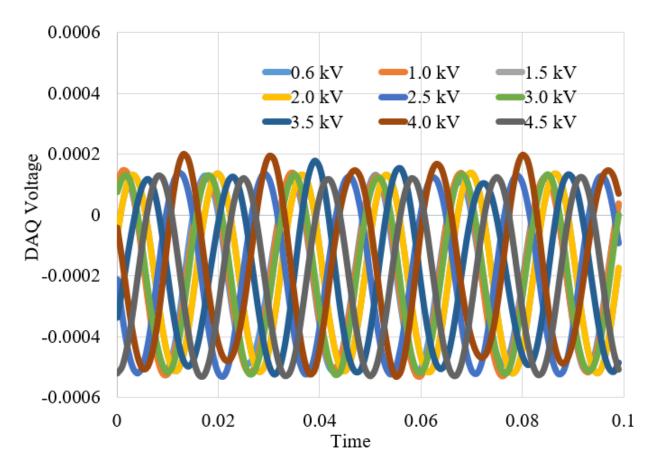

| Fig. 6.24. LABVIEW interface to facilitate data acquisition using a DAQ system                         |

| Fig. 6.25. Data acquisition system voltage levels of channel 1 in LABVIEW interface for                |

| corresponding high voltage DC supply                                                                   |

| Fig. 6.26. Data acquisition system voltage levels of channel 3 (across 249 $\Omega$ shunt resistor) in |

| LABVIEW interface corresponding to high voltage DC supply                                              |

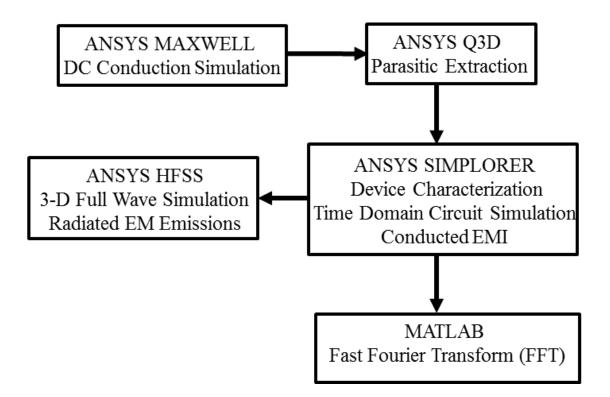

| Fig. 7.1. Flow chart of the simulation methodology                                                     |

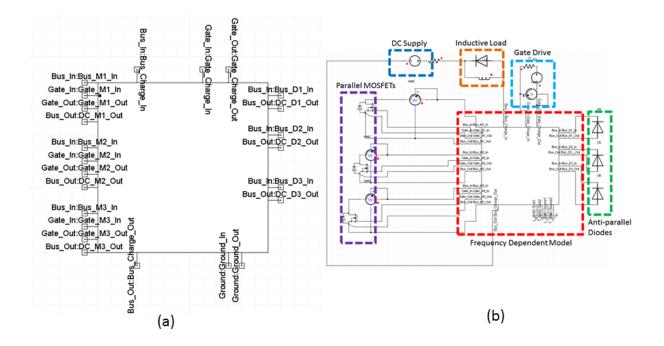

| Fig. 7.2. (a) Coplanar wire bonded power module, (b) Wire bondless power module                        |

| Fig. 7.3. DC conduction simulation (a) Wire bonded module (b) Wire bondless module 171                 |

| Fig. 7.4. Conducting nets in ANSYS Q3D for parasitic analysis (coplanar wire bonded module)            |

|                                                                                                        |

| Fig. 7.5. Conducting nets in ANSYS Q3D for parasitic analysis (wire bondless module) 174               |

| Fig. 7.6. Circuit schematic for switching simulations (without parasitc inductance) 176                |

| Fig. 7.7. (a) Frequency dependent circuit model, (b) Circuit schematic built around frequency          |

| dependent parasitic model                                                                              |

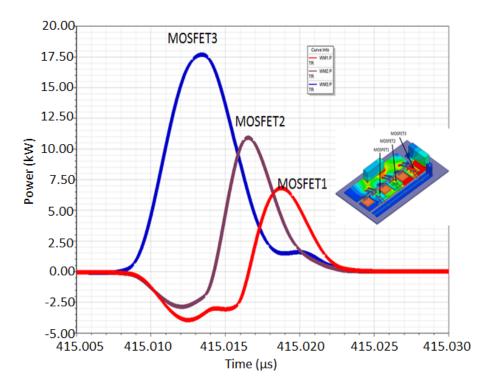

| Fig. 7.8. Instantaneous power through paralleled power MOSFETs ( coplanar wire bonded                  |

| module)                                                                                                |

| Fig. 7.9. Instantaneous power throug paralleled power MOSFETs (wire bondless module) 178               |

| bondless module                                                                        | 180     |

|----------------------------------------------------------------------------------------|---------|

| Fig. 7.11. E-field strength at different frequencies for wire bonded and wire bondless | modules |

|                                                                                        |         |

| Fig. 7.12. Test setup for near-field measurement                                       | 185     |

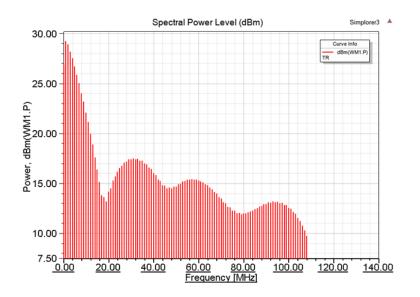

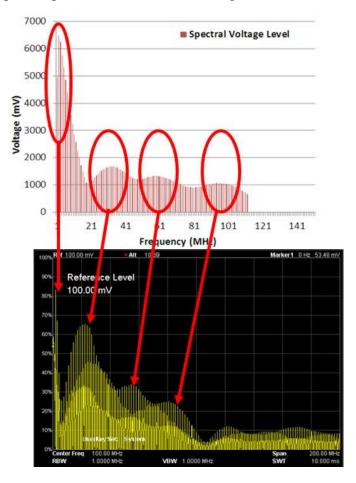

| Fig. 7.13. Simulated spectral power for the fabricated single device module            |         |

| Fig. 7.14. Comparison between simulation (above) and measurement (below)               |         |

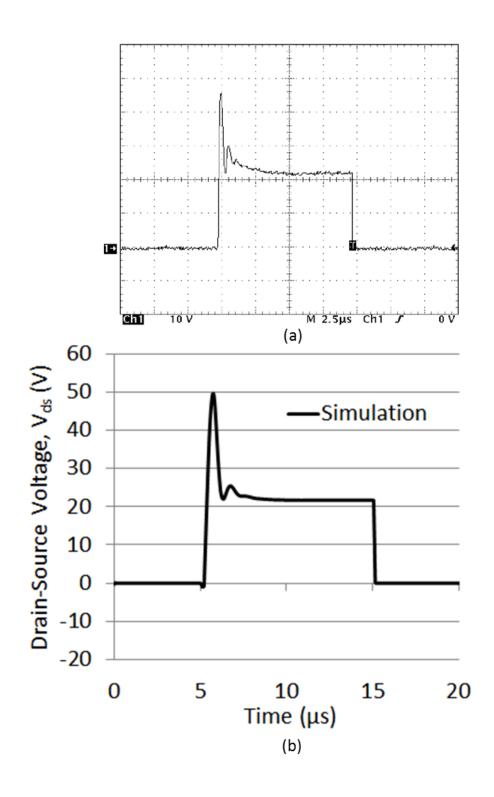

| Fig. 7.15. Switching waveform (a) measurement , (b) simulation                         | 188     |

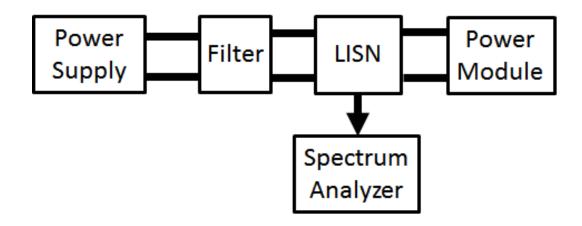

| Fig. 7.16. Conducted EMI measurement setup                                             | 190     |

| Fig. 7.17. Voltage level at line of LISN monitored from oscilloscope                   | 190     |

| Fig. 7.18. Voltage level at neutral of LISN monitored from oscilloscope                | 191     |

| Fig. 7.19.Simulated and measured voltages at LISN line                                 | 192     |

| Fig. 7.20. mulated and measured voltages at LISN neutral                               | 193     |

| Fig. 7.21.Differential mode noise                                                      |         |

| Fig. 7.22. Common mode noise                                                           | 195     |

# List of Tables

| Table 3.1. Electric field level at different applied voltage                          | 49    |

|---------------------------------------------------------------------------------------|-------|

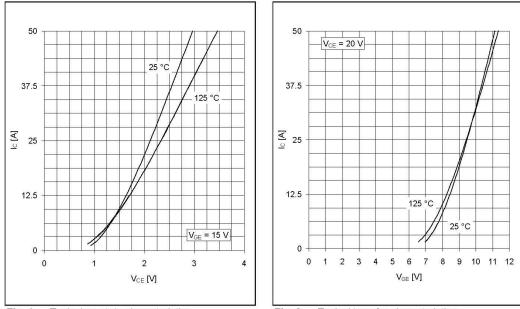

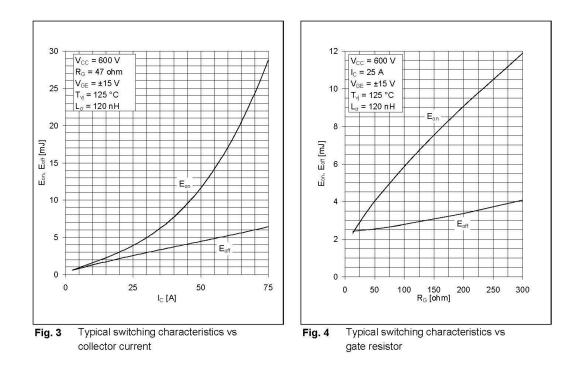

| Table 4.1 Switching Energy Measurement Conditions                                     | 75    |

| Table 4.2 Nominal Working Point Values (Si-IGBT)                                      | 76    |

| Table 4.3 Switching Energy and Time                                                   | 78    |

| Table 4.4: Nominal Working Point Values (SiC Schottky Barrier Diode)                  | 79    |

| Table 5.1. Process Parameters Used For Ti/Ni/Ag Evaporation                           | 96    |

| Table 6.1. Double pulse test condition for 3-D stack                                  | . 140 |

| Table 6.2 Calibrated voltage levels between high voltage power supply and DAQ voltage | 160   |

## **List of Published Papers**

Chapter 7 consists of a published IEEE paper with the following citation:

A. Dutta and S. S. Ang, "Electromagnetic Interference Simulations for Wide-Bandgap Power Electronic Modules," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 757-766, Sept. 2016. doi: 10.1109/JESTPE.2016.25733

## **Chapter 1 Introduction**

## **1.1 Background and Motivation**

With the advent of fast switching wide bandgap semiconductor devices, such as silicon carbide and gallium nitride, power packaging has become a challenge [1]-[12]. The theoretical limits of wide bandgap devices, for example, silicon carbide exhibit hundred times faster switching speed, four times higher operating temperature, ten times higher blocking voltage, five times higher current density, lower switching losses compared to their silicon counterparts [13]. However, packaging technologies, new materials available to package wide bandgap devices are the primary preventive factors in achieving these high theoretical limits. The existing packaging technologies for silicon devices are not optimized for silicon carbide, as such, newer optimized packaging technologies need to be investigated to utilize the full potential of wide bandgap devices.

High voltage and high current power modules require several power semiconductor devices/modules to be connected in series and parallel to achieve the specific rating for an application. However, series and parallel connection of several devices require larger substrate area that introduces parasitic inductance, unbalanced current/voltage sharing, unequal operating temperature between the devices in the package. Moreover, connecting several power modules in series and parallel introduces additional DC bus inductances that are undesirable to achieve optimum switching efficiency of the power devices/modules. Failure to address these aspects from a packaging standpoint can give rise to reliability issues and reduce the life cycle of the devices and the power modules [14].

1

In traditional power module packaging approach, wire bonds are used as top side (gate/emitter for IGBTs, gate/source for MOSFETs, anode for diodes) electrical connection for power semiconductor devices [15]. Wire bonds introduce additional parasitic inductance in the current conduction loop and prone to mechanical failure at high operating temperatures due to thermomechanical stresses [16]-[18].

Press-pack packaging technology from ABB excludes wire bonds from the power module structure. Instead of wire bonds, the top side interconnection is achieved by pressure contact using spring pin. The spring pins are placed directly on the top side electrode pads to make direct contact [19]-[21]. However, due to the coefficient of thermal expansion (CTE) mismatch, different thermal and mechanical properties, the contact materials become subject to high thermomechanical stress and strains during operation. Due to high junction temperature and a wide range of temperature variations, these mechanical interfaces become fatigued and the metallization on the electrode pads on the devices gradually wear away, termed as fretting [22]. This ultimately results in the failure of the power devices.

In this dissertation research, a module-level press-pack structure is proposed. In the proposed module-level press-pack structure the semiconductor devices are attached to the power substrate using flip-chip die attach method as opposed to direct spring contacts on the electrode pads of the devices to avoid fretting in device level press-pack. A half-bridge module-level press-pack structure is realized using two stand-alone power modules each consisting of a switching position to represent the high and low side switching positions of a half-bridge power module.

#### **1.2 Objective of Dissertation**

The objective of this dissertation research is to design and develop a novel module-level threedimensional (3-D) wire bondless half-bridge stack for semiconductor devices. Design, simulation, fabrication, and characterization of the 3-D wire bondless stack are performed as part of this dissertation research. The characterization of the 3-D wire bondless half-bridge power module is performed and compared with the characteristics of a traditional wire bonded power module in terms of parasitic inductance, switching performance, and electromagnetic interference (EMI) response.

The module level 3-D wire bondless half-bridge stack is in general based on the following:

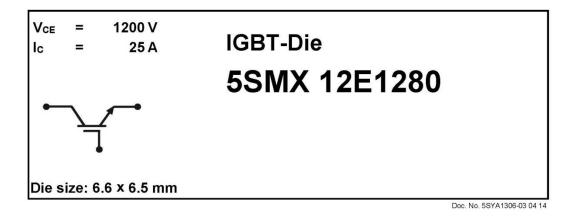

- a) The 3-D stack consists of two wire bondless stand-alone power modules. Each standalone wire bondless modules represent a switching position (high and low side) of the half-bridge module consists of two 1200 V 25 A silicon IGBT devices in parallel with two 1200 V 36 A Schottky barrier in an antiparallel configuration.

- b) The two stand-alone wire bondless power modules are connected in series with a novel interconnection technique.

- c) The interconnection between the two stacked modules will be achieved through:

- i. An array of spring loaded mechanical contacts embedded into low temperature co-fired ceramic (LTCC) substrate [24].

- Conductive clamps to establish electrical connection between both sides of DBC copper metallization.

- d) Top and bottom holding frames to hold the stand-alone wire bondless power modules[24].

3

In addition to the module level 3-D stack, the scope of this dissertation research will incorporate the development of a simulation methodology and hardware validation of the methodology to predict the electromagnetic interference in the design phase of the power module using ANSYS EM tools. A correlation study will be performed to correlate the simulation and measurement.

#### **1.3 Organization of Dissertation**

This dissertation research is organized in the following way:

In Chapter 2, the design of the 3-D wire bondless half-bridge stack is presented. The detailed design process using various software platforms are illustrated. In Chapter 3, the electrical, thermal simulation results for the 3-D wire bondless half-bridge stack are presented. Parasitic inductance of the 3-D stacked module is extracted for all current conducting paths. The effect of connector placement on parasitic inductance is investigated and optimum connector placement to minimize loop inductance is performed. High voltage simulation to validate the 3-D stack structure is performed. Thermal simulations are also presented. In Chapter 4, a comparison between the proposed 3-D wire bondless half-bridge power module and a traditional wire bonded power module is performed in terms of parasitic inductance and switching performance. It is shown through simulations using co-simulation techniques that the proposed 3-D wire bondless power module exhibits better switching performance compared to a wire bonded power module. In Chapter 5, the detailed process flow is presented to fabricate the proposed 3-D wire bondless half-bridge stacked power module. In Chapter 6, the characterization of the proposed module is performed. Double pulse test is carried out to characterize the switching behaviors of the proposed power module and compare the results with switching performance of a traditional wire bonded power module. EMI response of the proposed power module is compared with the traditional power module. The static characteristic of the power modules is measured to

investigate the influence of packaging on device characteristics. High voltage leakage current measurement is performed to investigate the insulation resistance to validate the power module architecture. In Chapter 7, a simulation methodology to predict electromagnetic interference in the design phase of a power module is proposed. The simulation methodology incorporates co-simulation technique using ANSYS EM tools to predict EMI [23]. The simulation methodology is validated by hardware measurements. In Chapter 8, conclusions for this dissertation research is drawn and some possible proposed future work is listed to set the direction for continued research.

#### **1.4 References**

- [1] J. Fabre, P. Ladoux and M. Piton, "Characterization and Implementation of Dual-SiC MOSFET Modules for Future Use in Traction Converters," *Power Electronics, IEEE Transactions on*, vol. 30, pp. 4079-4090, 2015.

- [2] Fan Xu, T. J. Han, Dong Jiang, L. M. Tolbert, Fei Wang, J. Nagashima, Sung Joon Kim, S. Kulkarni and F. Barlow, "Development of a SiC JFET-Based Six-Pack Power Module for a Fully Integrated Inverter," *Power Electronics, IEEE Transactions on*, vol. 28, pp. 1464-1478, 2013.

- [3] Jian Yin, Zhenxian Liang and J. D. van Wyk, "High Temperature Embedded SiC Chip Module (ECM) for Power Electronics Applications," *Power Electronics, IEEE Transactions on*, vol. 22, pp. 392-398, 2007.

- [4] T. Nomura, M. Masuda, N. Ikeda and S. Yoshida, "Switching Characteristics of GaN HFETs in a Half Bridge Package for High Temperature Applications," *Power Electronics, IEEE Transactions on*, vol. 23, pp. 692-697, 2008.

- [5] B. Passmore, S. Storkov, B. McGee, J. Stabach, G. Falling, A. Curbow, P. Killeen, T. Flint, D. Simco, R. Shaw and K. Olejniczak, "A 650 V/150 A enhancement mode GaN-based half-bridge power module for high frequency power conversion systems," in *Energy Conversion Congress and Exposition (ECCE), 2015 IEEE, 2015, pp. 4520-4524.*

- [6] Puqi Ning, Fei Wang and Di Zhang, "A High Density 250 Junction Temperature SiC Power Module Development," *Emerging and Selected Topics in Power Electronics, IEEE Journal of*, vol. 2, pp. 415-424, 2014.

- [7] Puqi Ning, T. G. Lei, Fei Wang, Guo-Quan Lu, K. D. T. Ngo and K. Rajashekara, "A Novel High-Temperature Planar Package for SiC Multichip Phase-Leg Power Module," *Power Electronics, IEEE Transactions on*, vol. 25, pp. 2059-2067, 2010.

- [8] R. Wang, Zheng Chen, D. Boroyevich, Li Jiang, Yiying Yao and K. Rajashekara, "A Novel Hybrid Packaging Structure for High-Temperature SiC Power Modules," *Industry Applications, IEEE Transactions on*, vol. 49, pp. 1609-1618, 2013.

- [9] Zheng Chen, Yiying Yao, D. Boroyevich, K. D. T. Ngo, P. Mattavelli and K. Rajashekara, "A 1200-V, 60-A SiC MOSFET Multichip Phase-Leg Module for High-Temperature, High-Frequency Applications," *Power Electronics, IEEE Transactions on*, vol. 29, pp. 2307-2320, 2014.

- [10] Zhenxian Liang, Puqi Ning and F. Wang, "Development of Advanced All-SiC Power Modules," *Power Electronics, IEEE Transactions on*, vol. 29, pp. 2289-2295, 2014.

- [11] A. Escobar-Mejia, C. Stewart, J. K. Hayes, S. S. Ang, J. C. Balda and S. Talakokkula, "Realization of a Modular Indirect Matrix Converter System Using Normally Off SiC JFETs," *Power Electronics, IEEE Transactions on*, vol. 29, pp. 2574-2583, 2014.

- [12] A. Dutta, Shijie Wang, Jinchang Zhou, S. S. Ang, June-Chien Chang and Chang-Sheng Chen, "The design and fabrication of a 50KVA 450A silicon carbide power electronic module," in *Power Electronics for Distributed Generation Systems (PEDG), 2013 4th IEEE International Symposium on, 2013, pp. 1-5.*

- [13] A. Elasser and T. P. Chow, "Silicon carbide benefits and advantages for power electronics circuits and systems," *Proceedings of the IEEE*, vol. 90, pp. 969-986, 2002.

- [14] D. P. Sadik *et al*, "Analysis of Parasitic Elements of SiC Power Modules With Special Emphasis on Reliability Issues," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, pp. 988-995, 2016.

- [15] S. Ang, T. Evans, J. Zhou, K. Schirmer, H. Zhang, B. Rowden, J.C. Balda, H.A Mantooth, "Packaging issues for high voltage power electronic modules," ECS Transaction, 34(1)893-898(2011)

- [16] L. D. Stevanovic, R. A. Beaupre, E. C. Delgado and A. V. Gowda, "Low inductance power module with blade connector," *Applied Power Electronics Conference and Exposition (APEC), 2010 Twenty-Fifth Annual IEEE*, Palm Springs, CA, 2010, pp. 1603-1609

- [17] K. B. Pedersen and K. Pedersen, "Bond wire lift-off in IGBT modules due to thermomechanical induced stress," 2012 3rd IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aalborg, 2012, pp. 519-526

- [18] C. Busca, R. Teodorescu, F. Blaabjerg, S. Munk-Nielsen, L. Helle, T. Abeyasekera, and P. Rodriguez, "An overview of the reliability prediction related aspects of high power

IGBTs in wind power applications," Microelectronics Reliability, vol. 51, no. 9-11, pp. 1903-1907, Sep./Nov. 2011.

- [19] S. Kaufmann, T. Lang and R. Chokhawala, "Innovative press pack modules for high power IGBTs," in Proc. *International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, 2001, pp. 59-62. doi: 10.1109/ISPSD.2001.934559

- [20] S. Gunturi and D. Schneider, "On the operation of a press pack IGBT module under short circuit conditions," *IEEE Transactions on Advanced Packaging*, vol. 29, no. 3, pp. 433– 440, 2006. doi: 10.1109/TADVP.2006.875090.

- [21] P. Bill, A. Welleman, E. Ramezani, S. Gekenidis and R. Leutwyler, "Novel press pack IGBT device and switch assembly for Pulse Modulators," in Proc. *IEEE Pulsed Power Conference*, 2011, pp. 1120-1123. doi: 10.1109/PPC.2011.6191655.

- [22] R. Wu, F. Blaabjerg, H. Wang, M. Liserre and F. Iannuzzo, "Catastrophic failure and fault-tolerant design of IGBT power electronic converters - an overview," *IECON 2013 -39th Annual Conference of the IEEE Industrial Electronics Society*, Vienna, 2013, pp. 507-513.

- [23] A. Dutta and S. S. Ang, "Electromagnetic Interference Simulations for Wide-Bandgap Power Electronic Modules," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 757-766, Sept. 2016.

- [24] A. Dutta and S. S. Ang, "A 3-D stacked wire bondless silicon carbide power module," 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, 2016, pp. 11-16.

## Chapter 2 Design of 3-D Wire Bondless Half-Bridge Stacked Power Module

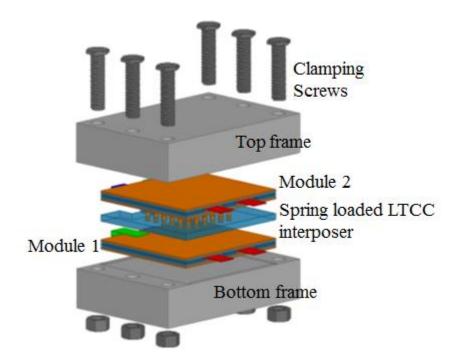

In this chapter, the detailed design of the module level 3-D wire bondless half-bridge stacked power module is presented. The proposed wire bondless 3-D half-bridge power module consists of several individual components. The primary building blocks for the proposed 3-D stack are as follows:

- i. Two wire bondless power modules

- ii. Spring loaded low temperature co-fired ceramic (LTCC) interposer

- iii. Top and bottom holding frames

- iv. Clamping screws

Fig. 2.1. Exploded view of the 3-D stacked wire bondless power module

Fig. 2.2. 3-D rendition of the proposed 3-D power module stack

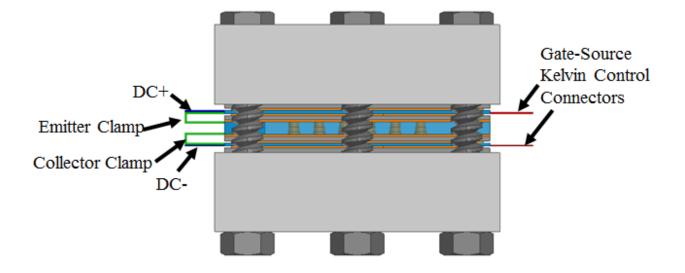

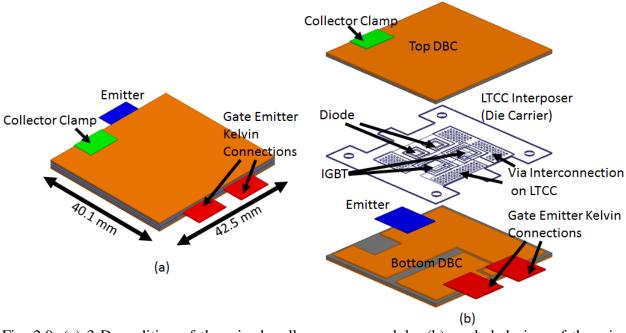

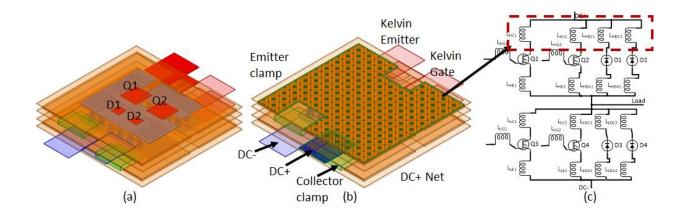

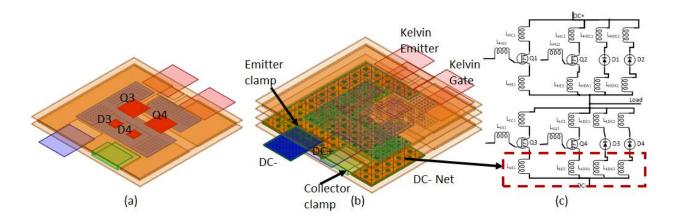

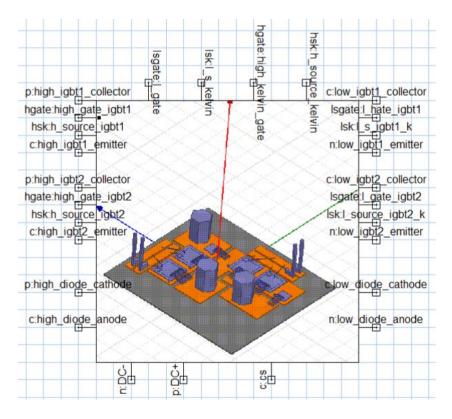

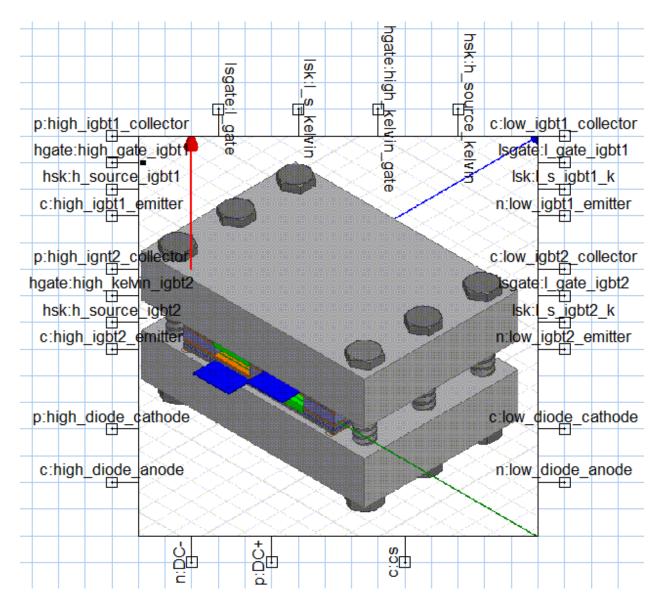

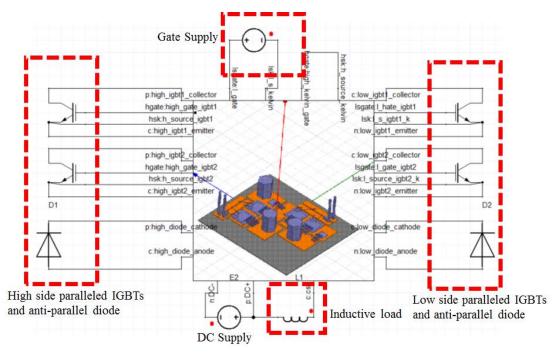

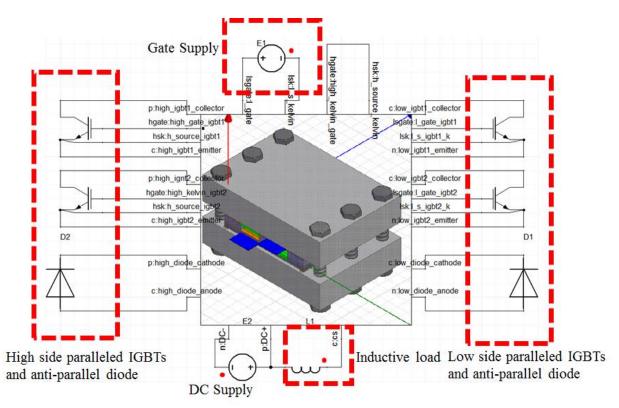

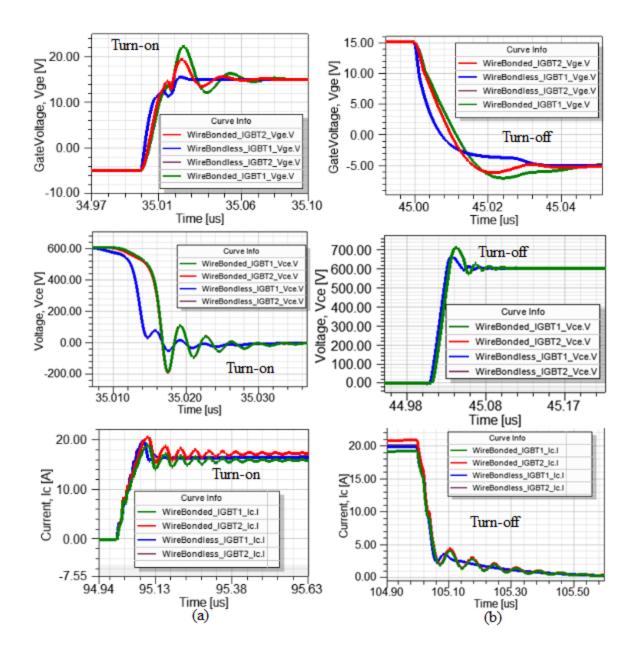

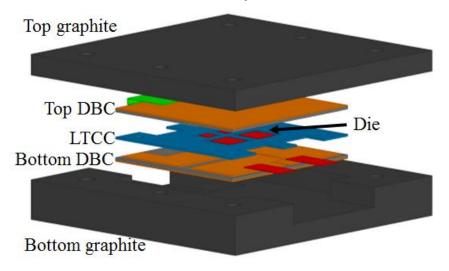

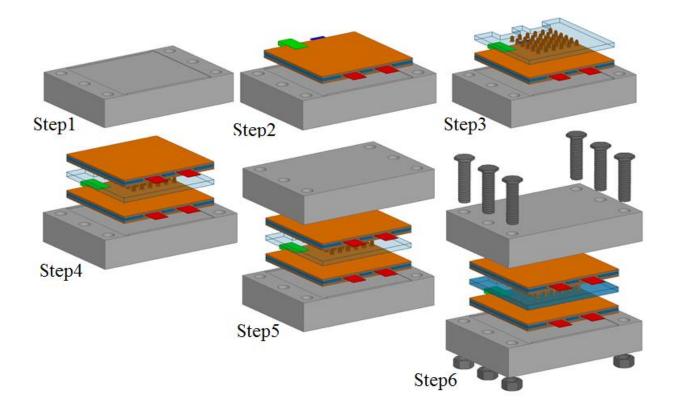

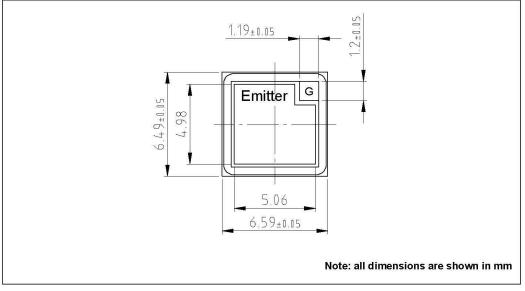

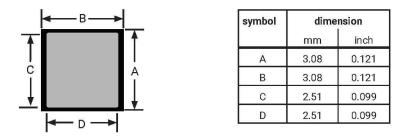

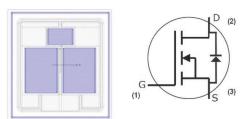

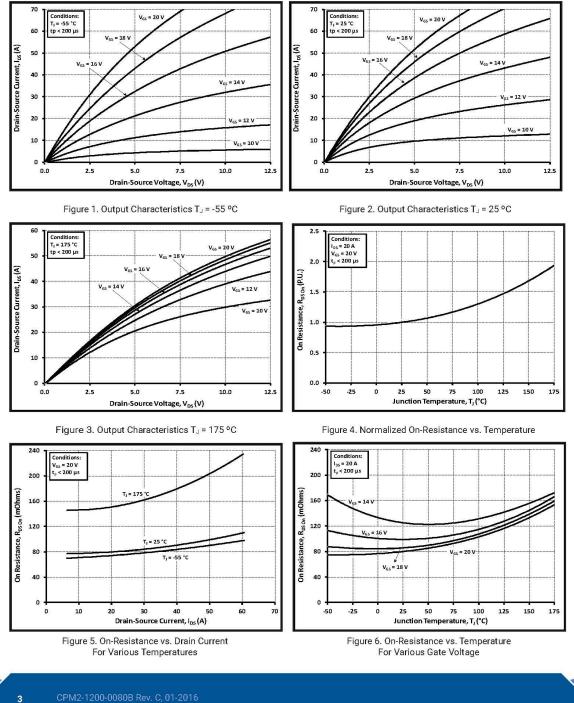

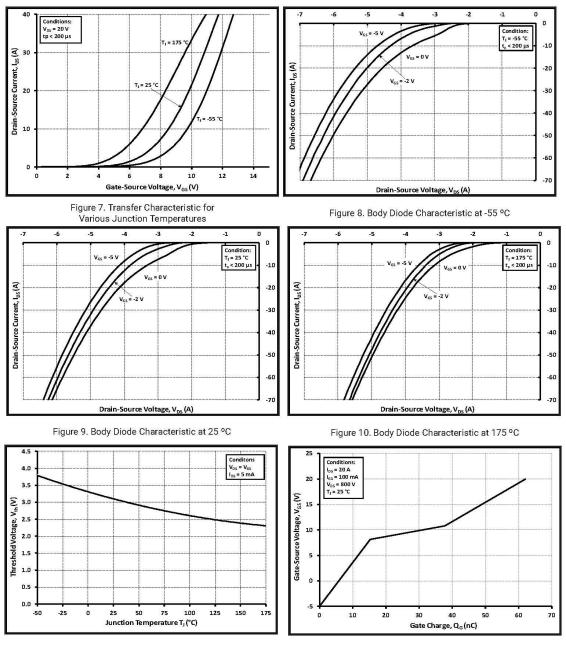

Fig. 2.1 and Fig. 2.2 represent the exploded view and 3-D rendition of the proposed power module structure respectively. As shown in Fig. 2.2, modules 1 and 2 are stand-alone power modules in the 3-D stack. The stand-alone power modules each consist of a switching position having two Si-IGBT devices from ABB (Part no. 5SMX12E1280) in parallel with two SiC Schottky barrier diodes from Wolfspeed (Part no. CPW4-1200-S020B) in an anti-parallel configuration. As such, modules 1 and 2 form the high side and the low side switching positions for a half-bridge topology. The paralleling of the power devices is performed inside each stand-alone module to increase the current handling capability. The two power modules are series-connected using a novel interconnection scheme to achieve the half-bridge power module configuration [2]. A two-step interconnection scheme is followed to interconnect the power module. At first, clamped interconnections are used to route the emitter and collector of the power modules to the outside copper metallization of the direct bond copper (DBC) substrate.

collector and the emitter of the two power modules to connect them in series to form a halfbridge power module [2].

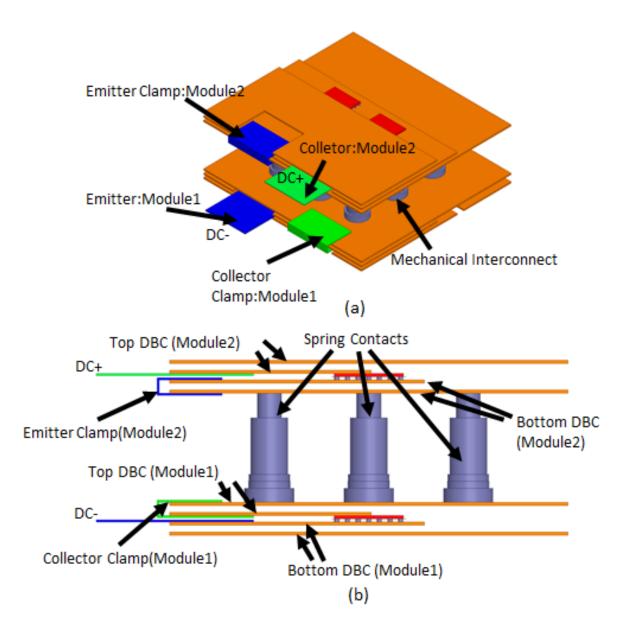

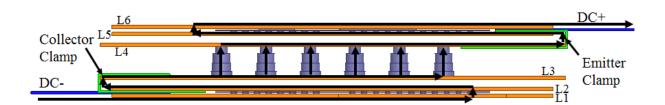

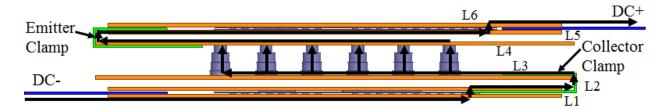

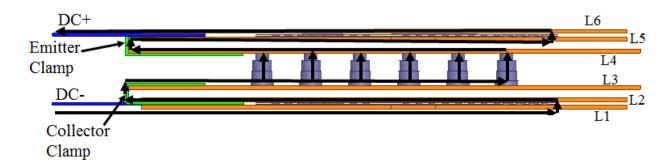

Fig. 2.3 represents the 3-D rendition and the side view of the interconnection scheme used to achieve series connection between the bottom (module 1) and top (module 2) modules. In the proposed interconnection scheme, two conductive clamps, namely emitter, and collector clamps are used to route the electrical connection from the inner copper layer of top DBC of module 1 to the bottom DBC of module 2 [2]. The entire loop from DC+ to DC- starts from the collector (Green) of the top module (module 2). The emitter clamp (Blue) of module 2 routes the emitter of the devices placed in the top module (module 2) to the outer layer of the bottom DBC of module 2 [2]. The collector of the bottom module (module 1) is also routed to the outer copper layer of the top DBC of module 1 using a similar collector clamp (Green) [2]. The electrical connection between the emitter of module 2 and collector of module 1 is achieved by a low temperature co-fired ceramic (LTCC) interposer embedded with spring loaded mechanical contacts [2]. The conductive clamps used to route the electrical connections are machined out of thin copper sheets. Mill-max spring loaded pins (Part No. 0965-0-15-20-80-14-11-0) are used as mechanical contacts for the proposed interconnection [1]. As such, a series connection is achieved between modules 1 and 2 to realize a wire bondless half-bridge 3-D stacked power module.

Fig. 2.3. (a) 3-D rendition of the interconnection scheme for the 3-D power module stack [2], (b) side view of the interconnection scheme (only conducting objects are shown in figure for simplicity)

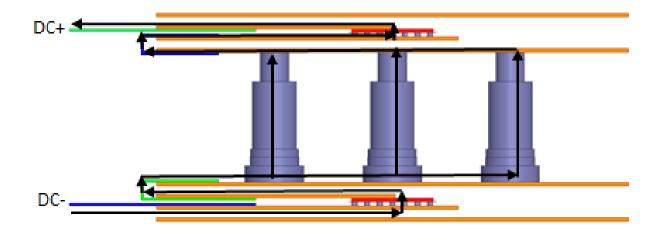

For optimum parasitic design, electrical routing for the current conduction paths plays a vital role. For the wire bondless power module, the electrical routing of the gate, emitter, and collector are achieved using through hole conductive vias on LTCC substrate. The electrical routing for the current conduction paths is designed in such a way that the forward and the return current

paths are overlapped on top on each other and in opposite direction. The overlapping antiparallel current paths reduce the magnetic fields generated through current conduction by magnetic field cancellation [2]-[4]. As such, reducing the overall parasitic inductance of the current conduction loops to achieve optimum parasitic inductance. Fig. 2.4 represents the anti-parallel current path configuration for the 3-D power module stack. The total inductance

Fig. 2.4. Antiparallel current path configuration for the proposed 3-D power module stack [2]

of the loop consisting of an overlapping antiparallel current path depends on the self-inductance of each conductor and the mutual inductance between the conductors.

Fig. 2.5. Current conduction loop of an overlapping current path separated by a dielectric

Fig. 2.5 represents a current loop consisting of an overlapping current path separated by a dielectric layer of thickness, d. The total loop inductance can be given by the following:

$$L_{total} = L_1 + L_2 - 2M_{12} \qquad (2.1)$$

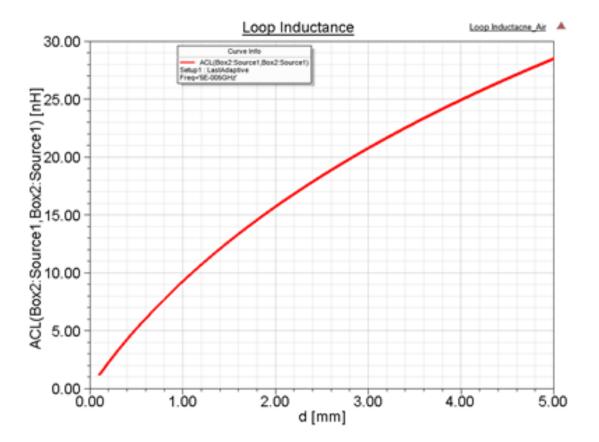

where,  $L_1$  = self-inductance of top conductor,  $L_2$  = self-inductance of bottom conductor,  $M_{12}$  = the mutual inductance between the top and bottom conductor. Fig. 2.6 shows that as the dielectric separation between the top and the bottom conductors increases the mutual inductance decreases between the conductors, as such, the overall loop inductance increases.

Fig. 2.6. Loop inductance vs. dielectric separation

In traditional wire bonded power modules, the current conduction paths are generally coplanar having all the current conduction loops in a single layer. On the contrary, 3-D power modules

can utilize multilayer current conduction paths. As such, the forward and return current paths can be routed leveraging the multilayer design freedom offered by multilayer laminate substrates to design an antiparallel current path configuration to reduce parasitic inductance by mutual coupling. This theoretically cancels out the effect of opposing current.

Fig. 2.7 and Fig. 2.8 represent the direction of current flow of an overlapping forward and the return path and a single layer current path respectively. In Fig. 2.7, the dimensions of the forward and return current path are assumed to be  $20 \text{ mm} \times 10 \text{ mm}$  and  $26 \text{ mm} \times 10 \text{ mm}$  respectively. The single layer current path is assumed to be  $20 \text{ mm} \times 10 \text{ mm}$ . The parasitic extraction simulation performed in ANSYS Q3D yields 1.9 nH and 5.9 nH for the overlapping and the single layer current paths respectively. As such, an antiparallel forward and current path configuration is implemented to design the proposed wire bondless 3-D half-bridge power module stack.

Fig. 2.7. Overlapping forward and return current path [3]

## Fig. 2.8. Single layer current path [3]

In the subsequent sections, the design process for the stand-alone wire bondless power modules along with the other components necessary to build the 3-D stack will be discussed in detail.

## 2.1 Design of Wire Bondless Power Module

The design and fabrication of wire bondless power module is an integral part of the proposed 3-D power module stack. In this section, the detailed design approach for the wire bondless power module will be discussed.

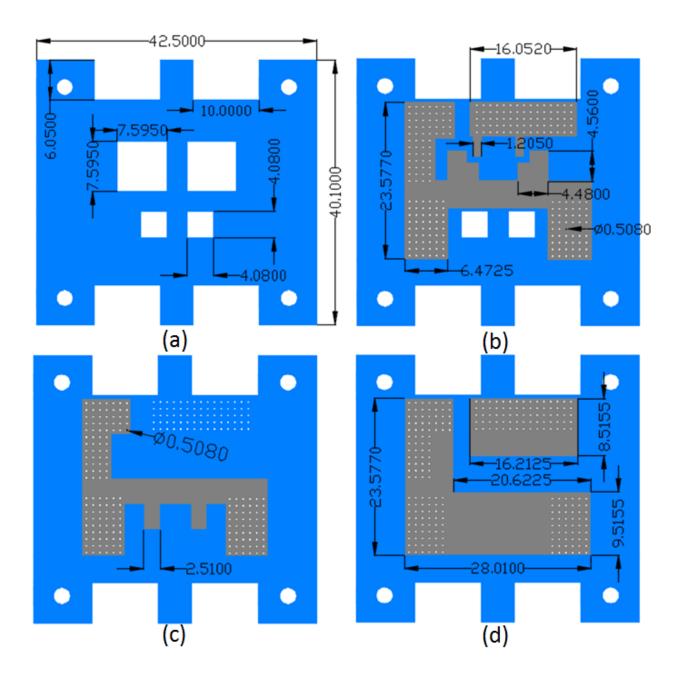

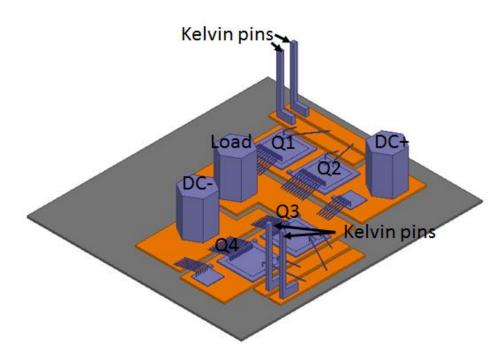

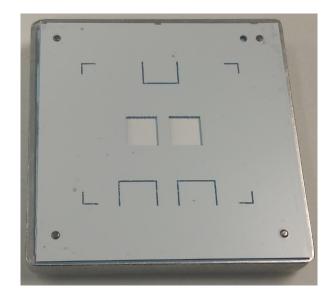

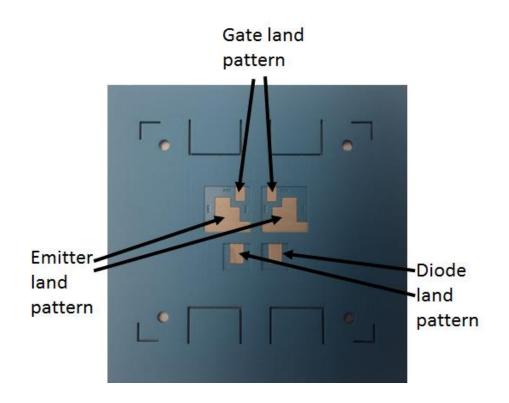

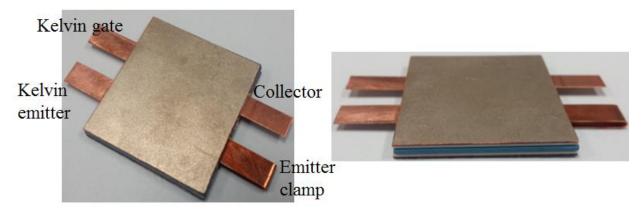

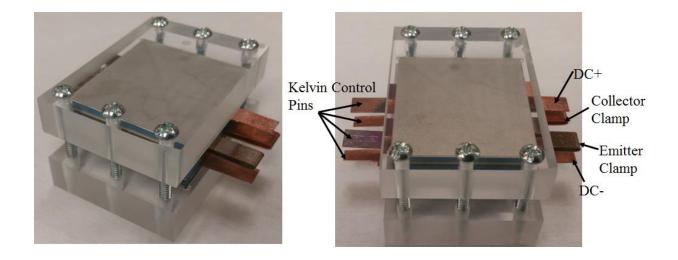

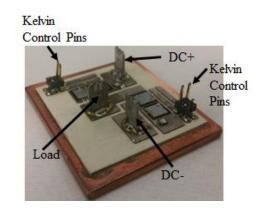

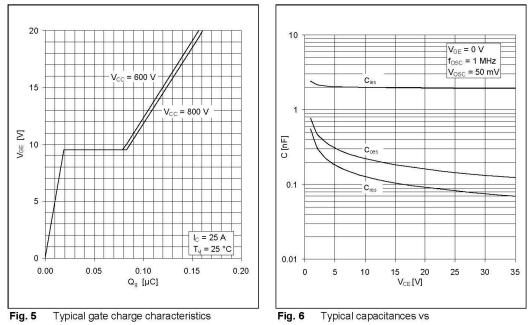

Fig. 2.9 (a) and (b) show the graphical representation of the stand-alone wire bondless power modules and the exploded view of the power module respectively. The dimension of the wire bondless power module for the proposed 3-D stack is 42.5 mm×40.1 mm. As can be seen, the power module consists of top and bottom direct bond copper substrates. The LTCC interposer in between the top and bottom direct bond copper substrates acts as a semiconductor device carrier. The electrical routings for the semiconductor devices are achieved by through hole vias and screen printed metallization patterns on a low temperature co-fired ceramic (LTCC) substrate. The LTCC interposer with the devices is solder attached to the top and bottom DBCs to route the gate, emitter and collector region. The input/output and the Kelvin connections terminals are achieved by copper connectors machined out of thin copper sheets.

Fig. 2.9. (a) 3-D rendition of the wire bondless power module, (b) exploded view of the wire bondless power module

## 2.2 LTCC Die Carrier Interposer Design

LTCC interposer in between the top and bottom DBCs is designed as a multilayer substrate. As mentioned earlier, the LTCC interposer in the proposed wire bondless power module acts as the semiconductor device carrier and also provides electrical isolation between the emitter, collector of Si-IGBTs and anode, cathode of SiC Schottky barrier diodes.

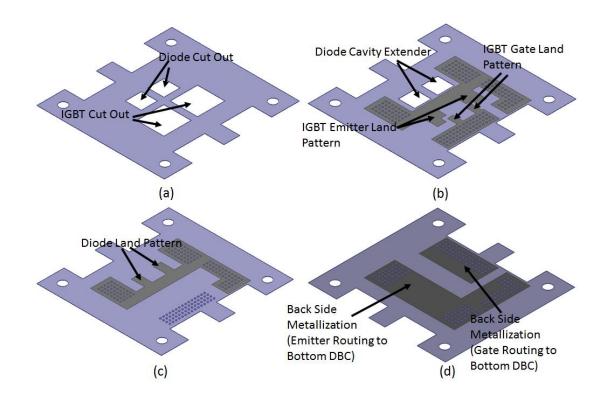

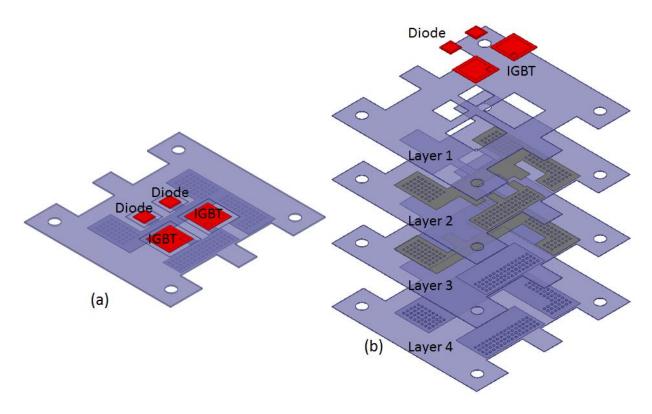

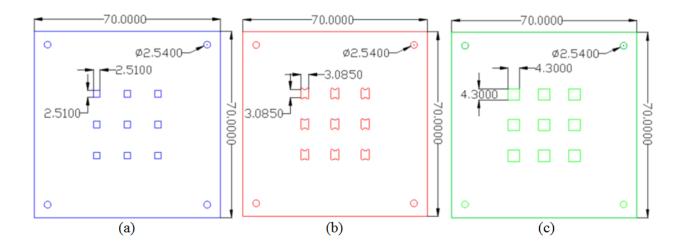

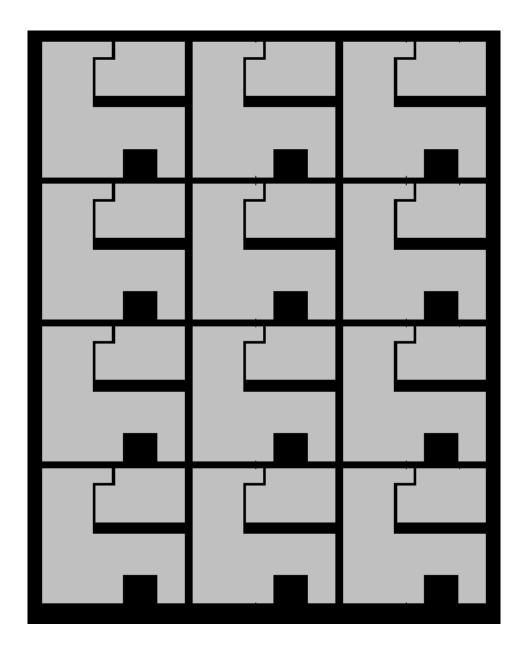

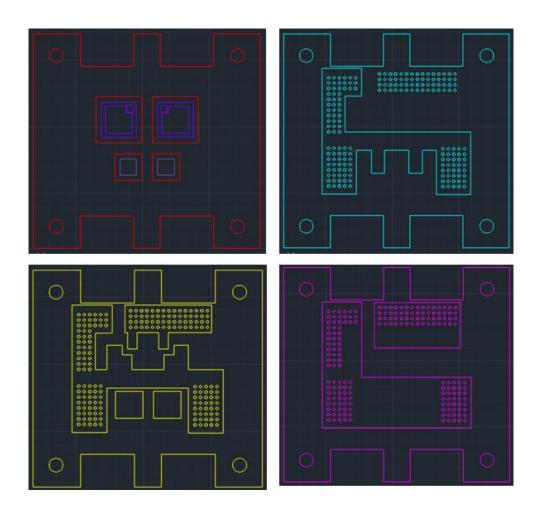

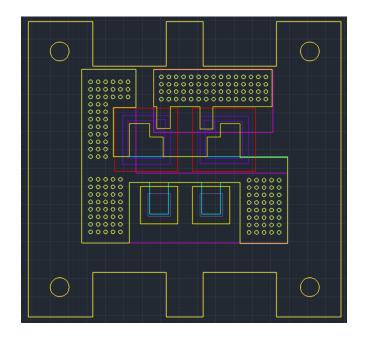

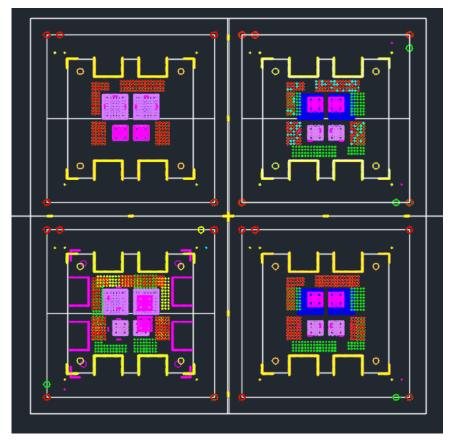

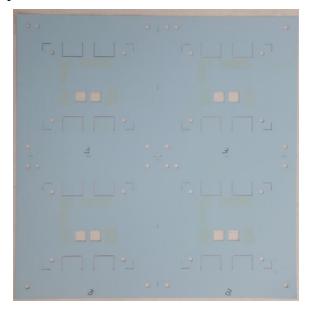

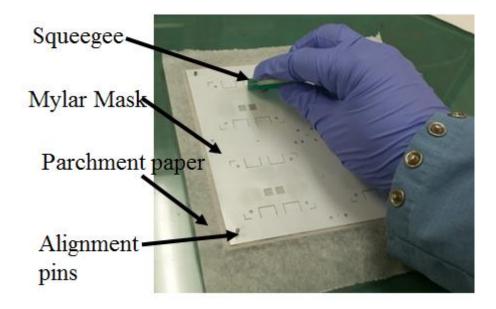

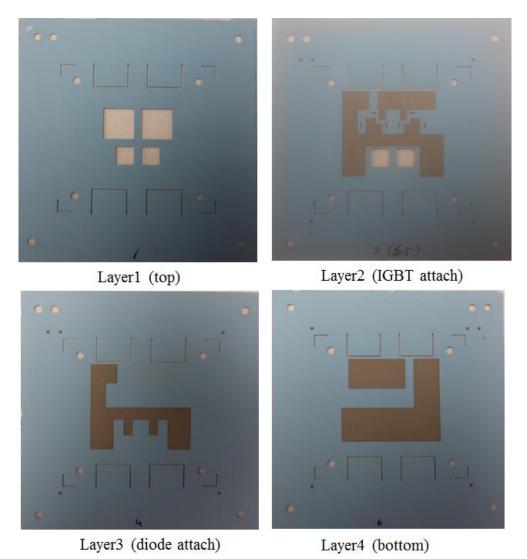

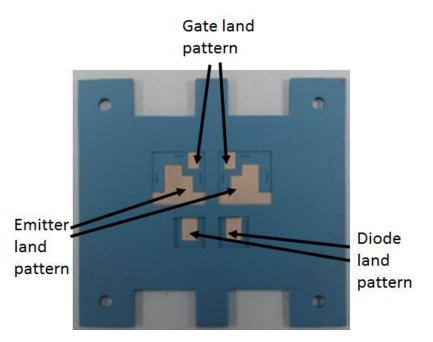

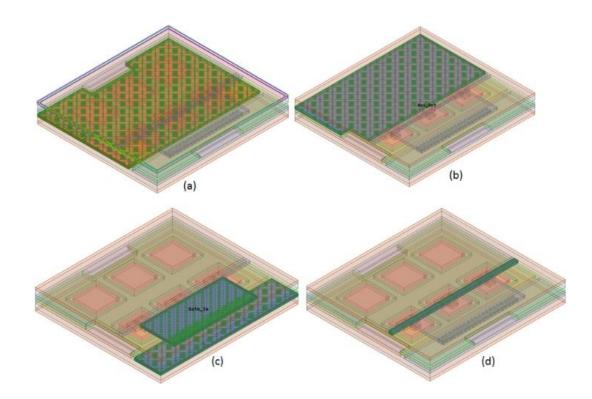

DuPonts<sup>™</sup> GreenTape<sup>™</sup> 951 is used to prepare the die carrier substrate. The x, y, z shrinkages need to be considered in the design phase of the substrate to accommodate any shrinkage after firing. The manufacturer provided x, y shrinkages are 12.7% and z shrinkage is 15% [4]. In total, there are four layers in the designed LTCC interposer as shown in Fig. 2.10. The first layer as shown in Fig. 2.10 (a) holds the cut-outs for the Si-IGBT and SiC diodes. Layer 2, as shown in Fig. 2.10 (b), holds the metallization for attaching the Si-IGBT devices. Also, layer 2 acts as a

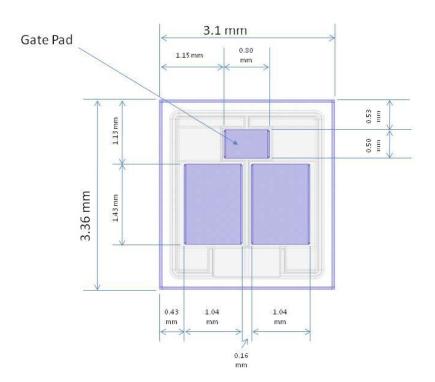

cavity extender to increase the cavity depth to match the thickness of the SiC diode. The interconnections between the multilayer LTCC are achieved by through hole vias. Layer 3, as shown in Fig. 2.10 (c), is used as the diode attachment layer. Fig. 2.10 (d), represents the back-side metallization for direct solder attachment of LTCC substrate to the bottom DBC substrate. Fig. 2.11 shows the exploded view of the multilayer LTCC interposer. Fig. 2.12 shows the dimension of each layer of the LTCC die carrier in mm.

Fig. 2.10. (a) Layer 1, device cutout (b) layer 2, metallization for attaching Si-IGBTs (c) layer 3, metallization for SiC diode attachment (d) layer 4, back side metallization for direct solder attachment to bottom DBC

Fig. 2.11. (a) LTCC die carrier interposer with device placement shown (b) exploded view of the multilayer LTCC interposer

Fig. 2.12. Dimensions in mm for LTCC interposer (a) layer 1 (b) layer 2 (c) layer 3 (d) layer 4

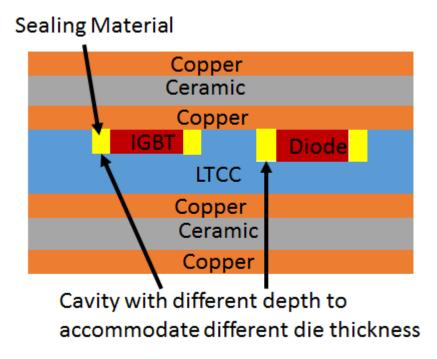

The inconsistent device thickness for the Si-IGBT and SiC Schottky diode pose a significant challenge to design and fabricate the cavities on the LTCC interposer with different thicknesses. The thicknesses of the Si-IGBT and the SiC diode are 140  $\mu$ m and 377  $\mu$ m, respectively. In order

to facilitate direct solder attachment for the collector of the IGBT and cathode of the diode with the

Fig. 2.13. Illustration of LTCC interposer with different cavity depths

top DBC substrate, the semiconductor devices must be on the same level and flashed with the top surface of the LTCC interposer. Fig. 2.13 shows the graphical representation of the side view of the LTCC interposer with different cavity depths for Si-IGBT and SiC diode that are sandwiched between the top and bottom DBCs. In order to accommodate the different die thickness, different combinations of 4.5 mils, 6 mils and 10 mils LTCC 951 GreenTape<sup>TM</sup> is used to achieve the desired cavity depths. The z-direction shrinkage of the LTCC 951 GreenTape<sup>TM</sup> is about 15% after firing [4]. As such, the shrinkage of the tapes is considered during the design process of the interposer.

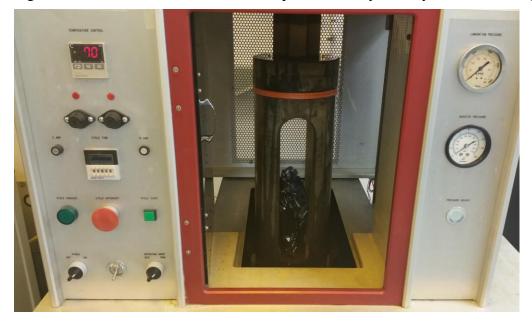

In order to fabricate the multilayer LTCC interposer, each layer is first prepared separately. Subsequently, the layers are laminated together to form the multilayer interposer. The fabrication of the LTCC interposer will be discussed in details in Chapter 5.

## 2.3 Top and Bottom DBC Design

The top and the bottom direct bond copper substrates are directly soldered attached to the LTCC device carrier. The gate and, emitter of the Si-IGBT devices are routed to the bottom DBC and the collector is attached to the top DBC. The top and bottom DBC conductors are designed using 12 mils Cu/ 25 mils Al<sub>2</sub>O<sub>3</sub>/ 12 mils Cu substrate. In addition to electrical routing, DBC substrates act as good thermal spreader for the proposed design, as such providing cooling mechanism from both sides of the devices.

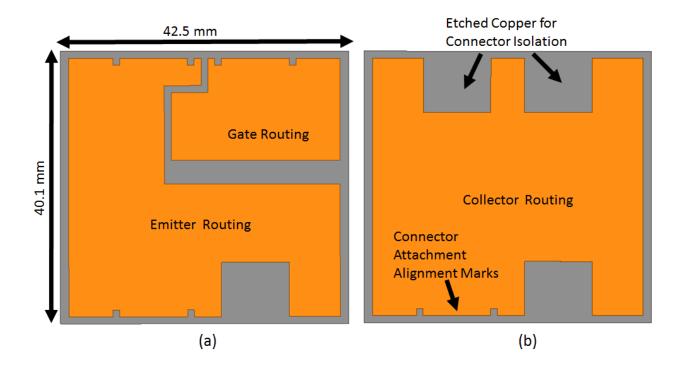

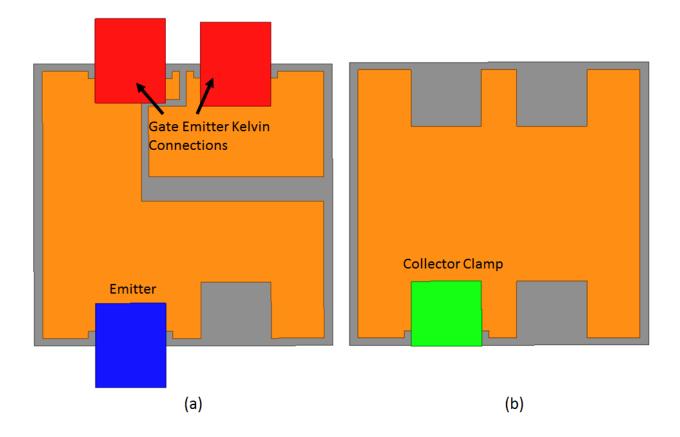

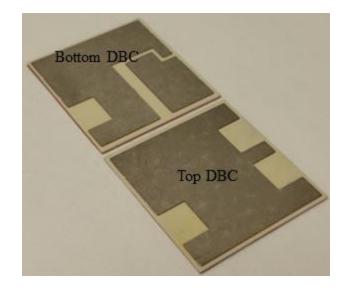

Fig. 2.14. (a) Layout of bottom DBC (b) layout of top DBC

Fig. 2.14 (a) and (b) show the layouts of the bottom and top DBC substrates respectively. As can be seen, the bottom DBC layout contains the gate and emitter routing pads. The gate, emitter, and the collector connectors are solder attached to the DBC. The connector alignment marks are etched during the fabrication process and taken into consideration while designing the DBC substrates to facilitate connector attachment later in the fabrication process flow. Also, the copper is etched from the top DBC where the gate and emitter connectors are attached on the bottom DBC. Similarly, copper is etched from the bottom DBC where the collector connector is attached on the top DBC. As such providing electrical isolation to avoid any shorting between the top and bottom DBC substrates.

Fig. 2.15. (a) Bottom (b) top DBC substrate with gate, emitter, collector and Kelvin connectors

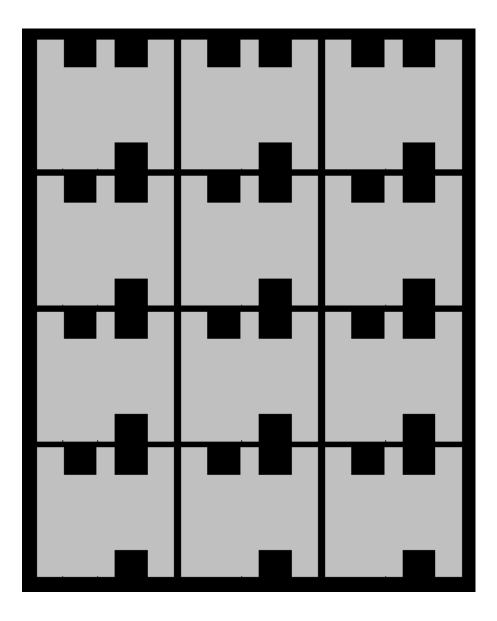

# 2.4 Spring Loaded LTCC Interposer Design

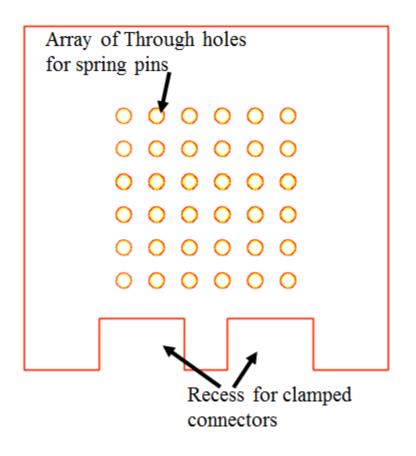

In the proposed power module, a spring loaded LTCC interposer is used to establish interconnections between the top and bottom stand-alone power modules to form the 3-D half-bridge stacked power module. The spring loaded LTCC interposer provides a better mechanical compliance to the 3-D stacked power module structure. The LTCC fixture that holds the spring-loaded pins is designed using AutoCAD. Fig. 2.16 shows the design of the LTCC fixture in AutoCAD.

Fig. 2.16. LTCC fixture designed in AutoCAD

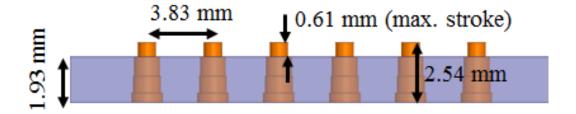

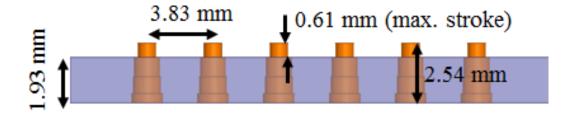

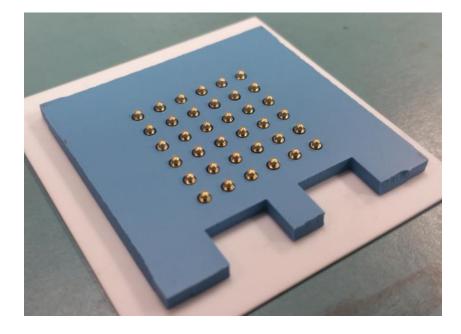

The LTCC interposer is fabricated by populating an LTCC fixture with spring-loaded pins. The spring-loaded pins used to fabricate the interposer are manufactured by Mill-Max (Part No. 0965-0-15-20-80-14-11-0) [1]. Each spring-loaded contact is gold plated with a plating thickness of 0.508 µm and carries 3 A of continuous current [1]. An array of 36 paralleled spring loaded contacts are used to fabricate the interposer to ensure a higher current handling capability of the interposer. The spring-loaded contacts are rated to endure 1,000,000 cycles [1]. The total height of each spring-loaded pins is 2.54 mm with a maximum stroke of 0.61 mm [1]. The total thickness of the LTCC interposer is designed to be 1.93 mm to ensure the utilization of the maximum stroke of the spring-loaded pins is designed to be 3.83 mm. The hole diameter on the LTCC fixture is designed to be slightly bigger than the diameter of the spring-loaded pins to easily populate the fixture with the spring pins. Fig. 2.17 represents the side view of the LTCC interposer showing all the critical dimensions.

Fig. 2.17. Side view of the LTCC interposer with critical dimensions (mm)

## 2.5 Chapter Summary

In this chapter, the detailed design of the module-level 3-D wire bondless half-bridge stacked power module is presented. The design aspect of each individual components of the stack is addressed. The detailed layouts of the stand-alone power modules are presented. The novel interconnection technique used to electrically interconnect the two stand-alone power modules to realize a half-bridge power module is discussed in detail. The anti-parallel forward and return current path technique to reduce inductance by magnetic field cancellation is discussed.

## **2.6 References**

- [1] "Mill-Max: 0965-Spring-Loaded Pin". *Mill-max.com*. N.p., 2017. Web. 6 May 2017.

- [2] A. Dutta and S. S. Ang, "A 3-D stacked wire bondless silicon carbide power module," 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, 2016, pp. 11-16.

- [3] Dutta and S. S. Ang, "Electromagnetic interference simulations of power electronic modules," in *Integrated Power Packaging (IWIPP), 2015 IEEE International Workshop on,* 2015, pp. 83-86.

- [4] E. Hoene, A. Ostmann and C. Marczok, "Packaging very fast switching semiconductors," in *Integrated Power Systems (CIPS), 2014 8th International Conference on, 2014, pp. 1-7.*

- [5] Low temperature co-fired ceramic system, DuPont<sup>TM</sup> GreenTape<sup>TM</sup>, DuPont<sup>TM</sup>, November 2009

#### Chapter 3 Simulations of the Wire Bondless 3-D Half-Bridge Stack Power Module

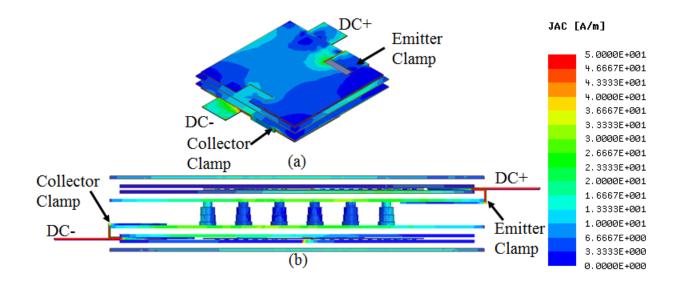

In this chapter simulation studies of the 3-D wire bondless half-bridge stack are performed. Electrical and thermal simulations are performed to investigate the feasibility of the 3-D wire bondless power module structure. Stray parasitic inductance induced by the packaging has a significant impact on the switching behavior of the power devices [1]-[8]. In order to achieve fast, efficient switching performance of the power modules, it is necessary to minimize the parasitic inductance in the power module. In general, DC bus inductance, common source inductance, and gate-source loop inductance are of primary importance and needs to be optimized for optimum switching performance. Depending on the placement of the supply terminals, input/output terminals, Kelvin connection pins, the stray inductance associated with each device can be different within a power module [9]. The imbalance in stray inductance is more prominent in power modules where paralleling and a series connection of several power devices/modules are necessary in order to achieve high current and voltage handling capability, respectively.

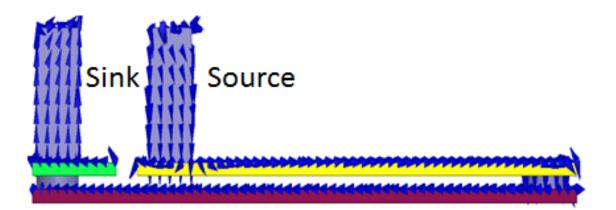

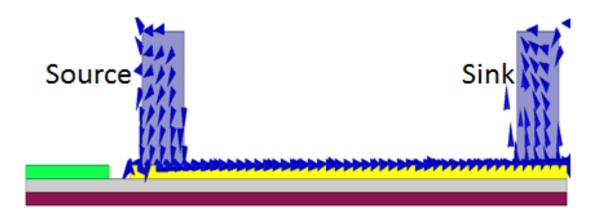

In the proposed 3-D half-bridge power module stack, careful design considerations are given to optimize the parasitic inductances of the power module. The parasitic extraction of the 3-D half-bridge stack is performed using ANSYS Q3D parasitic extraction tool. ANSYS Q3D implements quasi-static 3-D electromagnetic field solver based on methods of moments (MoM) and finite element method (FEM) to extract the resistance, inductance, capacitance and the conductance parameters for 3-D and 2-D geometries, respectively [10]. In order to extract parasitic parameters between two terminals on the layout, the current conducting path is defined by assigning source and sink excitations on the terminals. ANSYS Q3D implements an adaptive meshing to refine the mesh. A frequency sweep is performed to extract the parasitic parameters at various

frequencies. In this chapter, frequency dependent parasitic inductance and resistance associated with the various current conducting nets of the 3-D stack will be extracted and subsequently, measurement results for the parasitic inductance will be discussed to validate the simulated parasitic results.

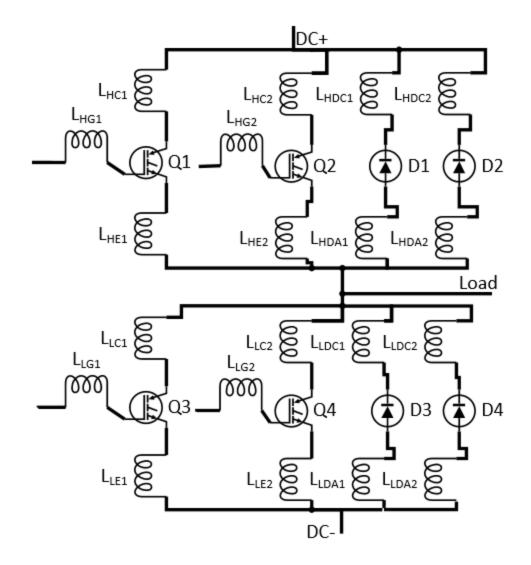

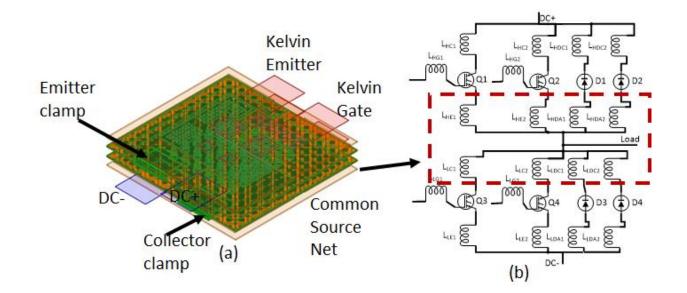

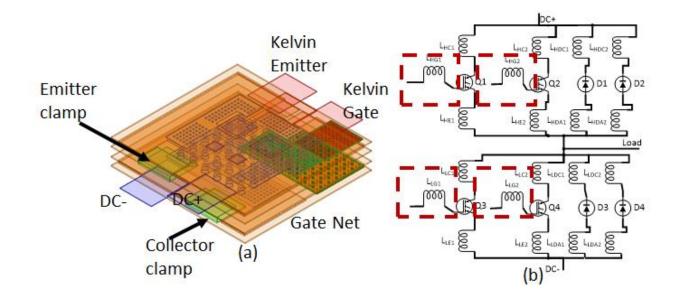

#### **3.1 Equivalent Parasitic Model for 3-D Half-Bridge Stack**

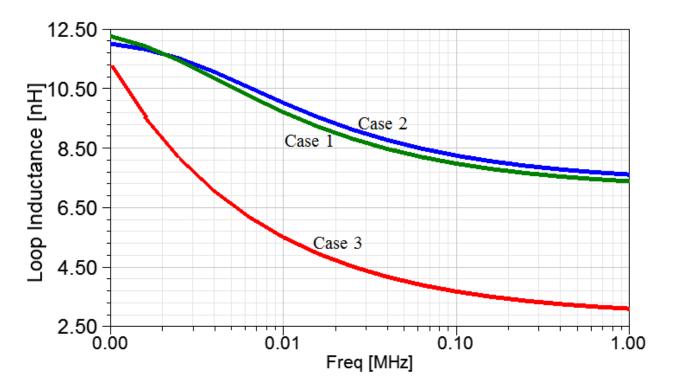

An equivalent parasitic inductance map of the proposed 3-D half-bridge power module is shown in Fig. 3.1, where the inductance associated with collector/emitter/gate and anode/cathode of the Si-IGBT and SiC Schottky diodes are shown. In Fig. 3.1, LHC1/LHC2 and LHDC1/LHDC2 are inductances for the current path starting from the DC+ terminal to the collector of the two paralleled high side Si-IGBTs and cathode of the two anti-paralleled high-side SiC Schottky diodes, respectively.  $L_{HE1}/L_{HE2}$  and  $L_{HDA1}/L_{HDA2}$  are inductance associated with the current path from the emitter of the high-side paralleled Si-IGBTs and anode of the anti-paralleled SiC diodes to the load terminal. Similarly, L<sub>LC1</sub>/L<sub>LC2</sub> and L<sub>LDC1</sub>/L<sub>LDC2</sub> are inductances associated with the current path from load terminal to the collector and cathode of the low side paralleled Si-IGBTs and anti-paralleled SiC diodes, respectively. LLE1/LLE2 and LLDA1/LLDA2 are inductances associated with the current path starting from the emitter and anode of the low side Si-IGBTs and SiC diodes to the DC- terminal. Also, L<sub>HG1</sub>/L<sub>HG2</sub> and L<sub>LG1</sub>/L<sub>LG2</sub> are gate inductances associated with the high-side and low-side paralleled Si-IGBTs respectively. A frequency dependent parasitic extraction is performed within a frequency range of 1 kHz to 100 MHz for each of the inductance parameters shown in Fig. 3.1.

Fig. 3.1. Equivalent inductance map of the proposed 3-D half-bridge stack power module

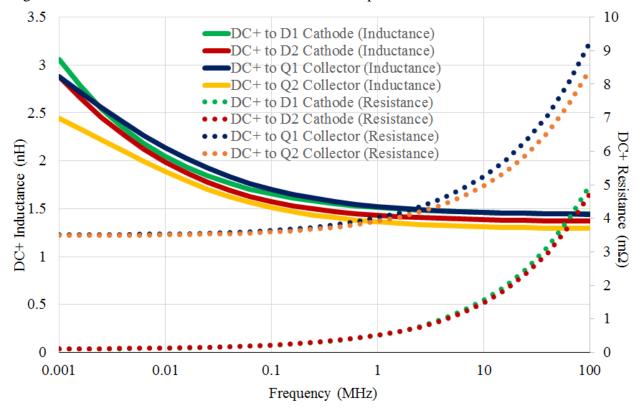

### **3.2 DC+ Inductance of 3-D Stack**

Fig. 3.2 corresponds to the DC+ inductance associated with the proposed 3-D stack half-bridge module. The DC+ net includes the path starting from the DC+ terminal to the collector of the IGBTs and cathode of the anti-parallel diodes for the high-side switching position. These inductances are defined as  $L_{HC1}$ ,  $L_{HC2}$ ,  $L_{HDC1}$  and  $L_{HDC2}$  in Fig. 3.1. In order to extract the parasitic inductance and resistance between the DC+ terminal and the collector and cathode of

the high-side IGBTs and diodes, the DC+ terminal is assigned as sink excitation and four source excitations are assigned at very close proximity to the collector of the paralleled IGBTs and cathode of the anti-paralleled diodes on the layout. Fig. 3.3 shows the frequency dependent plots of the parasitic inductance and resistance corresponding to the DC+ net. As can be seen, the parasitic inductance decreases with frequency while the parasitic resistance increases with increasing frequency.

Fig. 3.2. DC+ inductance associated with the 3-D stack power module

Fig. 3.3. Frequency dependent parasitic inductance and resistance for DC+ net of the 3-D stack power module

### 3.3 DC- Inductance of 3-D Stack

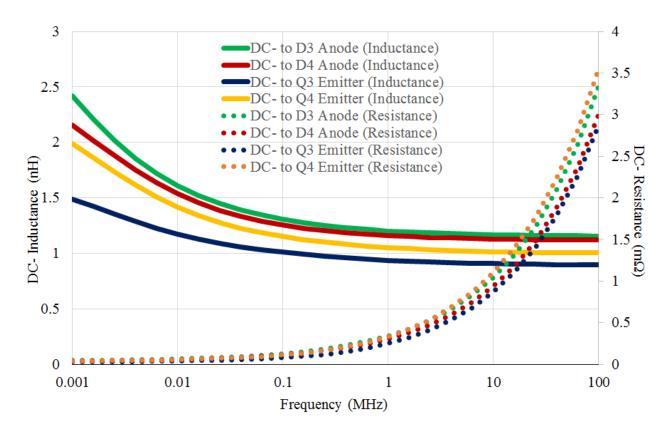

The DC- net includes the current path starting from DC- terminal to the emitter of the IGBTs and anode of the antiparallel diodes for the low-side switching position. These inductances are defined as L<sub>LE1</sub>, L<sub>LE2</sub>, L<sub>LDA1</sub>, and L<sub>LDA2</sub> in Fig. 3.1. Fig. 3.4 shows the current conducting net associated with the DC- net. Fig. 3.5 plots the frequency dependent inductance and resistance corresponding to the DC- net. As can be seen, the parasitic inductance decreases with frequency while the parasitic resistance increases with increasing frequency.

Fig. 3.4. DC- inductance associated with the 3-D stack power module

Fig. 3.5. Frequency dependent parasitic inductance and resistance for DC- net of the 3-D stack power module

# 3.4 Common Source Inductance of 3-D Stack

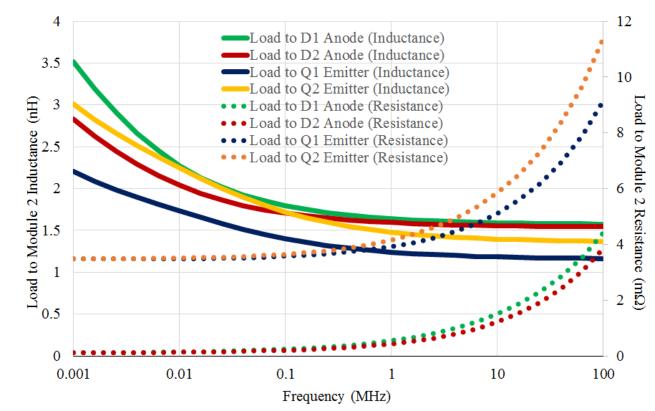

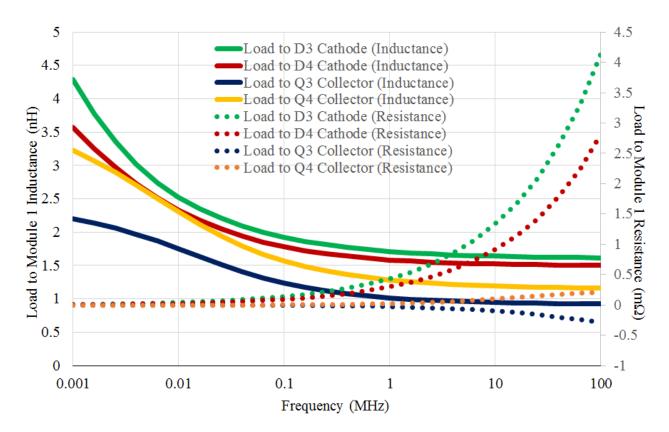

Two common emitter inductance paths are associated with the half-bridge module. One common emitter inductance path is between the load/output terminal to the high-side devices and the other path is associated with the load/output terminals to the low-side devices. Fig. 3.6 represents the common emitter inductance associated with the 3-D stack.  $L_{HE1}$ ,  $L_{HE2}$ ,  $L_{HDA1}$ , and  $L_{HDA2}$  as defined in Fig. 3.1 are common emitter inductances associated between the load/output terminals to the high-side devices. Additionally,  $L_{LC1}$ ,  $L_{LC2}$ ,  $L_{LDC1}$ , and  $L_{LDC2}$  are common emitter inductances associated between the load/output terminal to the low-side devices as shown in Fig. 3.1. The frequency dependent inductance and resistance plots for the common source net associated with the high and the low side devices are shown separately in Fig. 3.7 and Fig. 3.8, respectively. As can be seen, both the parasitic inductance for high and low side devices decreases with frequency while the parasitic resistance increases with increasing frequency.

Fig. 3.6. Common source net associated with the 3-D stack power module

Fig. 3.7. Frequency dependent parasitic inductance and resistance for common emitter net for the high-side devices of the 3-D stack power module

Fig. 3.8. Frequency dependent parasitic inductance and resistance for common source net for the low-side devices of the 3-D stack power module

## **3.5 Gate Loop Inductance**

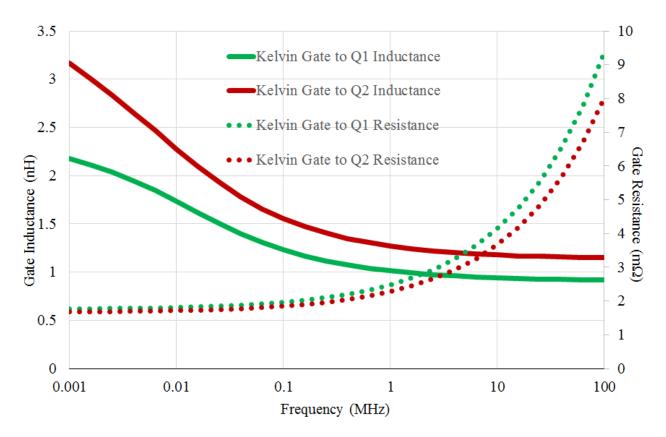

The gate inductance of the power module is associated with the path starting from the Kelvin gate terminal to the gate of the device. Fig. 3.9 show the gate net associated with the stand-alone power module. As the power modules are identical the gate net associated with the high-side devices, Q1 and Q2, respectively, are shown in Fig. 3.9. Fig. 3.10 plots the frequency dependent inductance and the resistance associated with the gate net of the stand-alone power module.

Fig. 3.9. Gate net of the 3-D stack power module

Fig. 3.10. Frequency dependent parasitic inductance and resistance of gate net of the 3-D stack power module

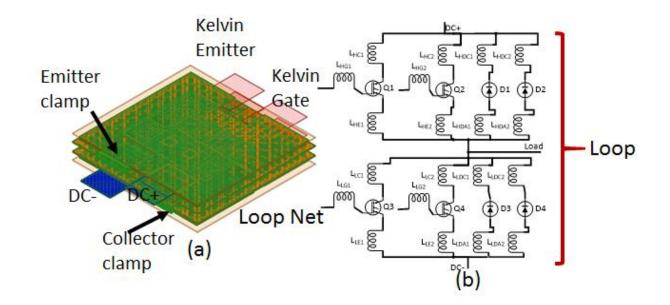

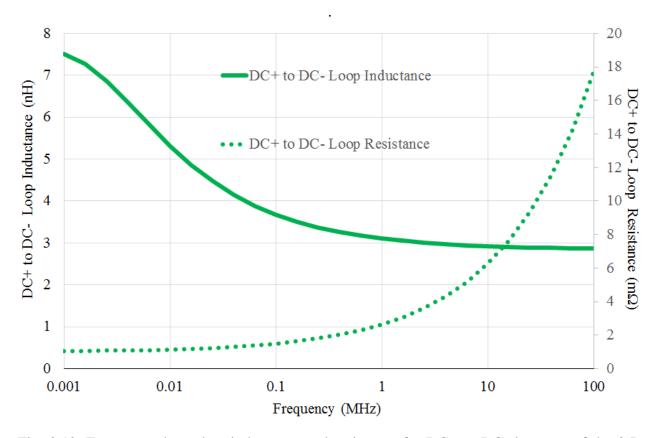

# **3.6 DC+ to DC- Loop Inductance**

The overall loop inductance that is associated with the path has a significant effect on the switching behavior of the power module. As such, the loop inductance should be minimized. As discussed earlier, an anti-parallel current path configuration is implemented to layout the forward and return current paths, the resultant partial current cancellation helps reduce the overall parasitic inductance of the loop. There are two commutation loops associated with the half-bridge stack. One loop includes the high-side IGBT devices and the low-side anti-parallel diodes. The other loop includes the low side IGBT devices and the high side anti-parallel diodes. Fig. 3.11 shows the loop inductance net for the 3-D module stack. Fig. 3.12 plots the frequency dependent inductance and resistance associated with the loop.

Fig. 3.11. DC+ to DC- loop net for 3-D half-bridge stack power module configuration

Fig. 3.12. Frequency dependent inductance and resistance for DC+ to DC- loop net of the 3-D half-bridge stack power module

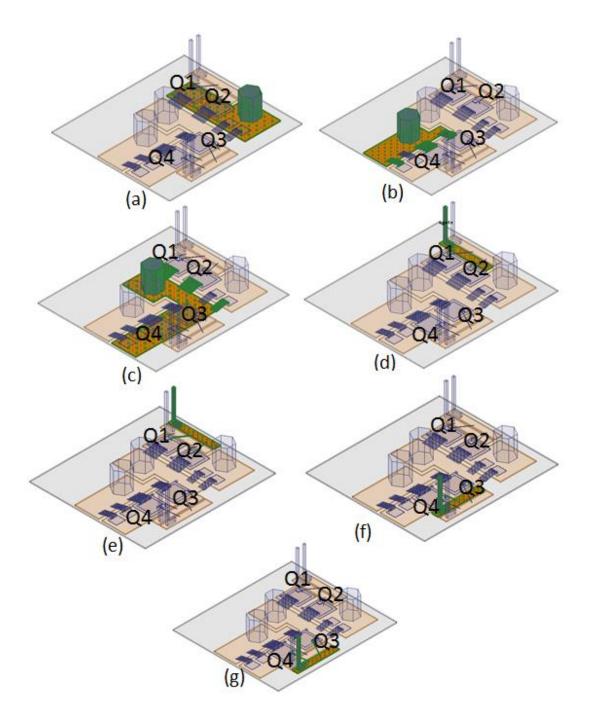

## 3.7 Effect of Connector Placement on Parasitic Inductance