# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

8-2014

# Unbalanced Current Static Compensator

Manuel Antonio Sanchez Tejada University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the Power and Energy Commons

# Recommended Citation

Sanchez Tejada, Manuel Antonio, "Unbalanced Current Static Compensator" (2014). Theses and Dissertations. 2260. http://scholarworks.uark.edu/etd/2260

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

# Unbalanced Current Static Compensator

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

Manuel Antonio Sánchez Tejada Universidad Tecnológica de Panamá Bachelor of Science in Electrical Engineering, 2010

# August 2014 University of Arkansas

| This thesis is approved for recommenda | tion to the Graduate Council. |

|----------------------------------------|-------------------------------|

| Dr. Juan Carlos Balda                  |                               |

| Thesis Director                        |                               |

|                                        |                               |

| Dr. Alan Mantooth                      | Dr. Roy McCann                |

| Committee Member                       | Committee Member              |

#### **ABSTRACT**

The objective of this thesis is to present and evaluate a solution to the unbalanced current issue that can be found in three-phase electrical power grids. The solution is named unbalanced current static compensator (UCSC) and has the goal of balancing the currents at the source in order to mitigate adverse issues such as of negative- and zero-sequence currents that are generated by three-phase current unbalances.

The solution topology consists of three single-phase H-bridge converters that are controlled through an algorithm working in the d-q frame of reference. The algorithm is divided in three different stages: the phase synchronization and reference current generator stage, the DC-link voltage and current controller stage, and the PWM stage. The design and functionality of the UCSC topology and algorithm is validated through MATLAB/SIMULINK<sup>TM</sup> simulations.

### **ACKNOWLEDGEMENTS**

I want to express my gratitude to God and my family for giving me the strength to keep moving forward every day.

I also want to thank Dr. Balda for his time, guidance and support during my time as one of his students and also for giving me the opportunity to work in his lab. Also, I want to thank Dr. Alan Mantooth and Dr. Roy McCann for being part of my thesis committee.

My gratitude also goes to the Fulbright program for giving me the opportunity to study in the United States.

Finally, I want to thank my friends David, Nicki, Luis, Samuel, Luciano and Andres for their support.

# **DEDICATION**

Esta tesis va dedicada a mi madre Maria, mi padre Manuel, mi abuela Celia y a mis dos hermanas, Milena y Angie. Sin su apoyo nunca hubiera llegado hasta donde estoy hoy en día.

# TABLE OF CONTENTS

| ~    |   |             |     |   |     |

|------|---|-------------|-----|---|-----|

| / \l |   | <b>1</b> 11 | " " |   | ) 1 |

|      | - | 4 P         |     | - | < 1 |

|      |   |             |     |   |     |

| INTRO | DDUCTION                                                    | 1     |

|-------|-------------------------------------------------------------|-------|

| 1.1   | Motivations for This Research                               | 1     |

| 1.2   | Existing Solutions to Three-Phase Unbalanced Currents       | 4     |

| 1.3   | Thesis Objectives                                           | 13    |

| 1.4   | Case Study of a Distribution System with Unbalanced Loading | 13    |

| 1.5   | Thesis Organization                                         | 20    |

| 1.6   | Conclusions                                                 | 20    |

| 1.7   | References                                                  | 21    |

| CHAP' | TER 2                                                       |       |

| SYSTE | EM FUNDAMENTAL CONCEPTS                                     | 23    |

| 2.1   | Background Concepts Related to Power Electronic Converters  | 23    |

| 2.2   | H-Bridge: Rectifier and Inverter Operations                 | 25    |

| 2.3   | Current Control of a H-Bridge                               | 29    |

| 2.4   | Reference Frame Theory                                      | 33    |

| 2.5   | Conclusions                                                 | 36    |

| 2.6   | References                                                  | 36    |

| CHAP' | TER 3                                                       |       |

| UNBA  | LANCED CURRENT STATIC COMPENSATOR: COMPONENTS AND CO        | NTROL |

| ALGO  | PRITHM                                                      | 38    |

| 3 1   | Introduction                                                | 38    |

| 3.2  | UCSC System Description                                   | 38  |

|------|-----------------------------------------------------------|-----|

| 3.3  | UCSC Control Algorithm                                    | 47  |

| 3.4  | Conclusions                                               | 62  |

| 3.5  | References                                                | 62  |

| APPE | ENDIX A.1                                                 |     |

| UCSO | C CASE STUDY: MATLAB/SIMULINK <sup>TM</sup> MODELS        | 65  |

| CHA  | PTER 4                                                    |     |

| SIMU | JLATION RESULTS AND ANALYSIS OF THE UCSC CASE STUDY       | 68  |

| 4.1  | Introduction                                              | 68  |

| 4.2  | Simulation Cases                                          | 68  |

| 4.3  | Case A – Ideal DC Link: Results and Analysis              | 69  |

| 4.4  | Case B – Capacitor-based DC Link                          | 90  |

| 4.5  | Case C – Capacitor-based DC Link Enhanced UCSC Controller | 107 |

| 4.6  | Conclusions                                               | 125 |

| 4.7  | References                                                | 126 |

| CHA  | PTER 5                                                    |     |

| CON  | CLUSIONS AND RECOMMENDATIONS FOR FUTURE WORK              | 127 |

| 5.1  | Conclusions                                               | 127 |

| 5.2  | Recommendations for Future Work                           | 129 |

| 5.3  | References                                                | 132 |

# LIST OF FIGURES

| Fig. 1-1. A generic three-phase distribution system [2]                                 | 1       |

|-----------------------------------------------------------------------------------------|---------|

| Fig. 1-2. a) Symmetrical components of an unbalanced three-phase set of variables. b) A | ddition |

| of the symmetrical component phasors.                                                   | 3       |

| Fig. 1-3. Compensator configuration proposed in [12]                                    | 6       |

| Fig. 1-4. Current controller scheme proposed in [12]                                    | 8       |

| Fig. 1-5. Voltage controller scheme proposed in [12]                                    | 9       |

| Fig. 1-6. Integrated controller scheme proposed in [12]                                 | 10      |

| Fig. 1-7. a) Unbalanced system schematic [13]. b) Steinmetz Bridge from [13]            | 11      |

| Fig. 1-8. AC-choppers solution proposed in [13]                                         | 12      |

| Fig. 1-9. Current profile of an unbalanced 34.5 kV three-phase distribution feeder      | 14      |

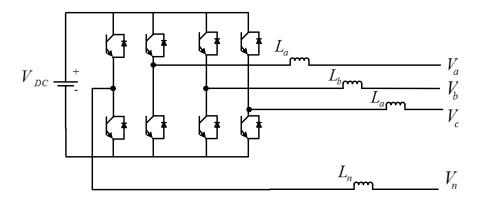

| Fig. 1-10. Inverter topologies.                                                         | 15      |

| Fig. 1-11. Three-phase three-wire inverter topology                                     | 16      |

| Fig. 1-12. Three-phase four-wire inverter topology                                      | 17      |

| Fig. 1-13. Three-phase four-legged inverter topology                                    | 18      |

| Fig. 1-14.One-line diagram for the case study                                           | 19      |

| Fig. 2-1. Single-phase H-bridge converter.                                              | 26      |

| Fig. 2-2. Filtered single-phase H-bridge output waveforms [2]                           | 26      |

| Fig. 2-3. Unipolar PWM voltage switching scheme.                                        | 28      |

| Fig. 2-4. Closed-loop current control diagram.                                          | 29      |

| Fig. 2-5. MATLAB/SIMULINK <sup>TM</sup> H-bridge model.                                 | 31      |

| Fig. 2-6. MATLAB/SIMULINKTM control algorithm block diagram.                            | 31      |

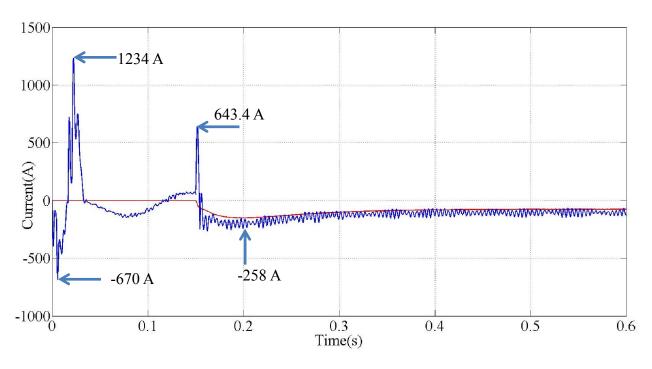

| Fig. 2-7. Output current $i$ (blue) and reference current $iref$ (red) waveforms                  | 32     |

|---------------------------------------------------------------------------------------------------|--------|

| Fig. 2-8. Closed-loop current control diagram with feed forward compensation                      | 33     |

| Fig. 2-9. Output current $i$ (blue) and reference current $iref$ (red) waveforms with feed for    | ward   |

| compensation                                                                                      | 33     |

| Fig. 2-10. a) Representation of the $abc$ and the $d-q$ variables. b) Representation of the $abc$ | bc and |

| the $\alpha - \beta$ variables                                                                    | 35     |

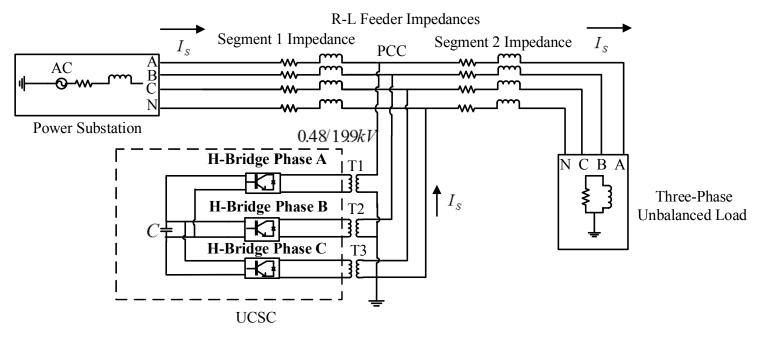

| Fig. 3-1.One-line diagram for the UCSC case study                                                 | 39     |

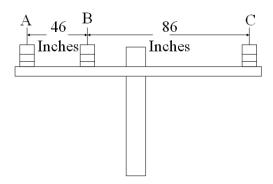

| Fig. 3-2. Pole configuration for segments 1 and 2 of the considered three-phase system [2]        | 40     |

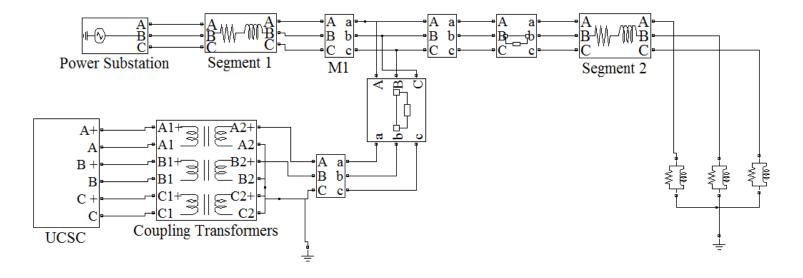

| Fig. 3-3. Unbalanced current static compensator system                                            | 43     |

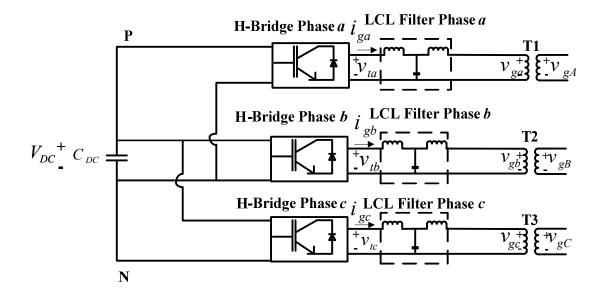

| Fig. 3-4. UCSC single-phase H-Bridge converter topology schematic                                 | 44     |

| Fig. 3-5. LCL filter schematic.                                                                   | 45     |

| Fig. 3-6. Multi-stage UCSC control algorithm block diagram                                        | 48     |

| Fig. 3-7. Phase-locked control algorithm block [18]                                               | 49     |

| Fig. 3-8. Phase <i>a</i> H-Bridge converter                                                       | 51     |

| Fig. 3-9. Phase <i>a</i> reference current generator block                                        | 51     |

| Fig. 3-10. Current controller stage for phase <i>a</i>                                            | 52     |

| Fig. 3-11. Phase <i>a</i> H-bridge converter output current and voltage phasor diagram            | 55     |

| Fig. 3-12. H-Bridge converter phase <i>a</i> equivalent circuit                                   | 56     |

| Fig. 3-13. PWM control algorithm [25]                                                             | 61     |

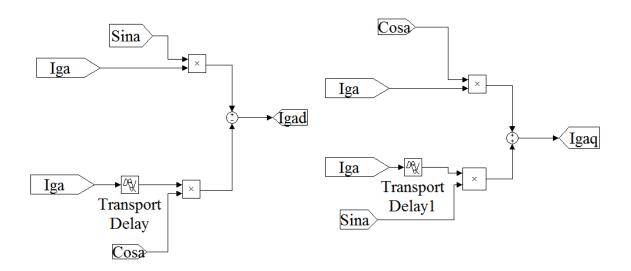

| Fig. A-1. Phase a H-bridge output current $\alpha - \beta$ to $d - q$ transformation              | 65     |

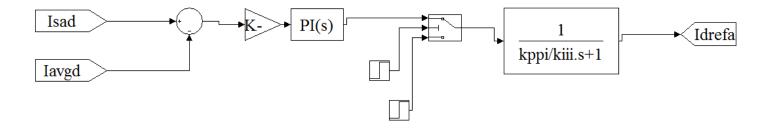

| Fig. A-2. Phase <i>a d</i> -axis reference current generator                                      | 66     |

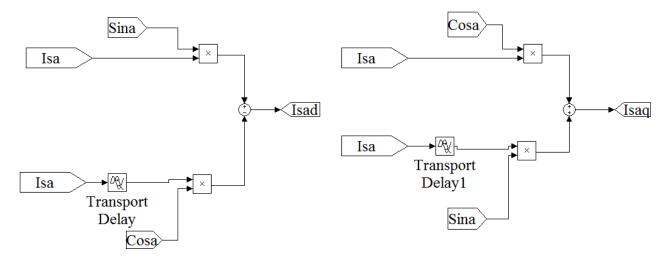

| Fig. A-3. Phase a source current $\alpha - \beta$ to $d - q$ transformation                       | 66     |

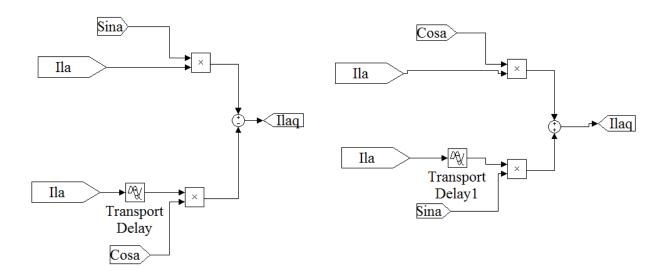

| Fig. A-4. Phase $a$ load current $\alpha - \beta$ to $d - q$ transformation                       | 67     |

| Fig. 4-1. Three-phase four-wire MATLAB/SIMULINK <sup>TM</sup> model             | 70 |

|---------------------------------------------------------------------------------|----|

| Fig. 4-2. UCSC MATLAB/SIMULINK <sup>TM</sup> model for case A                   | 71 |

| Fig. 4-3. Phase <i>a</i> MATLAB/SIMULINK <sup>TM</sup> H-bridge model           | 71 |

| Fig. 4-4. UCSC control algorithm MATLAB/SIMULINK <sup>TM</sup> mode for case A  | 73 |

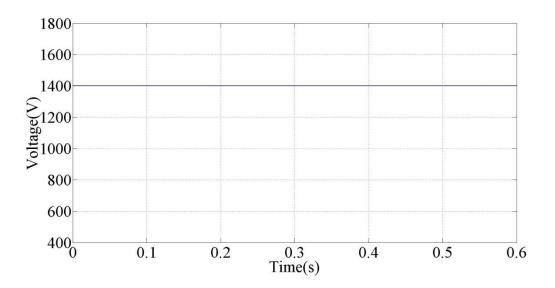

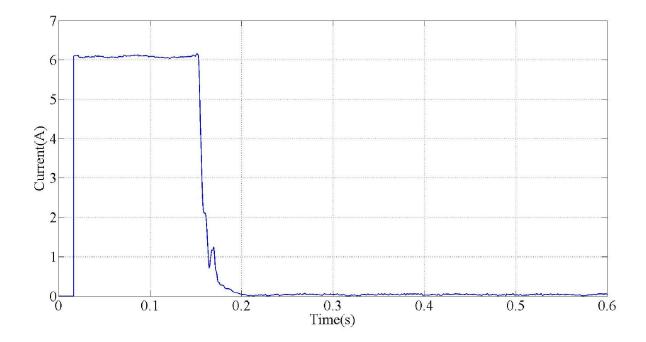

| Fig. 4-5. DC-link voltage waveform for case A                                   | 76 |

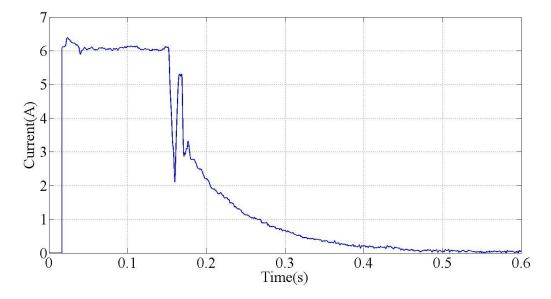

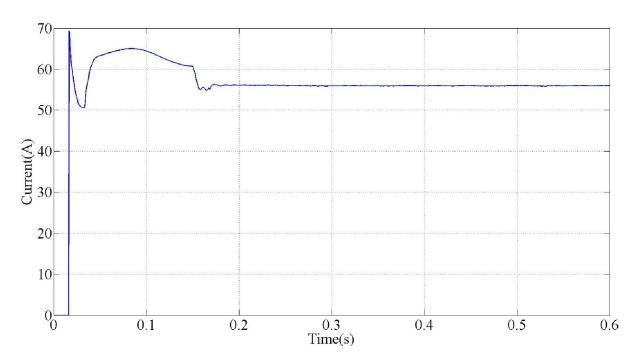

| Fig. 4-6. Current $i_{gad}$ and $i_{gad}^*$ waveforms for case A                | 77 |

| Fig. 4-7. Current $i_{gaq}$ and $i_{gaq}^*$ waveforms for case A                | 78 |

| Fig. 4-8. Current $i_{gbd}$ and $i_{gbd}^*$ waveforms for case A                | 78 |

| Fig. 4-9. Current $i_{gbq}$ and $i_{gbq}^*$ waveform for case A                 | 79 |

| Fig. 4-10. Current $i_{gcd}$ and $i_{gcd}^*$ waveforms for case A               | 79 |

| Fig. 4-11. Current $i_{gcq}$ and $i_{gcq}^*$ waveforms for case A               | 80 |

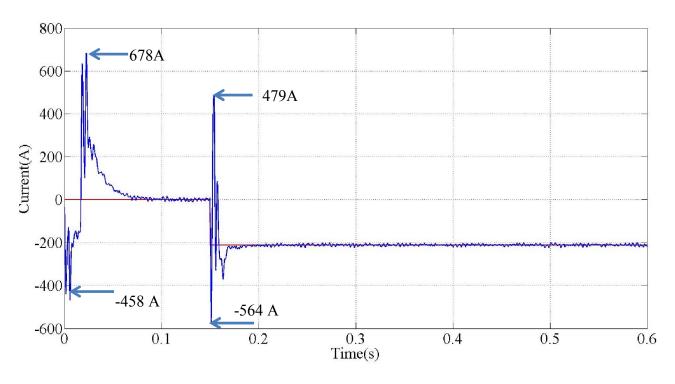

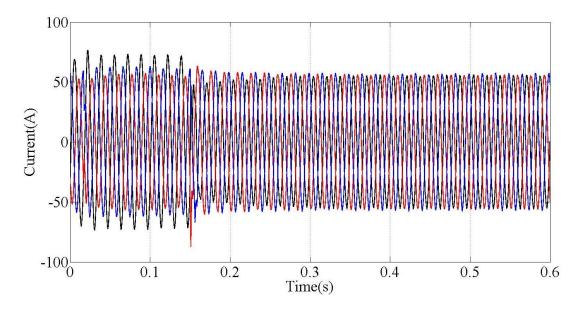

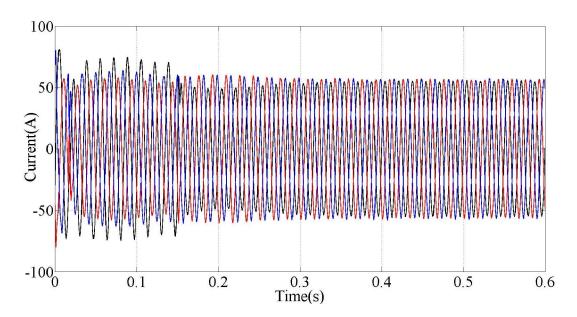

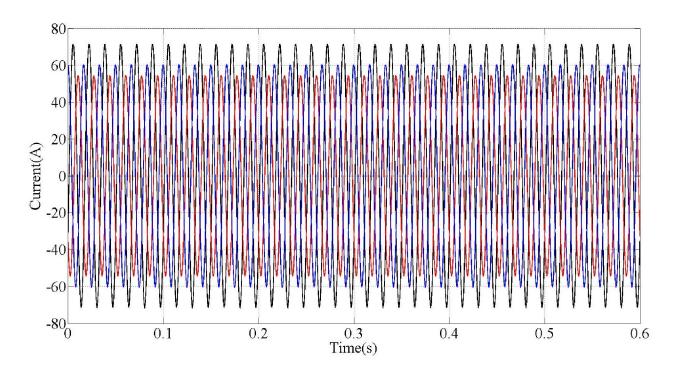

| Fig. 4-12. UCSC current waveforms for case A                                    | 81 |

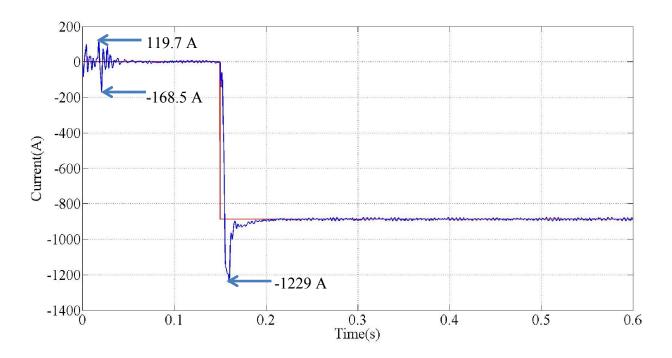

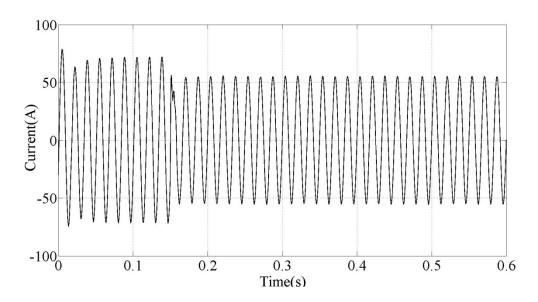

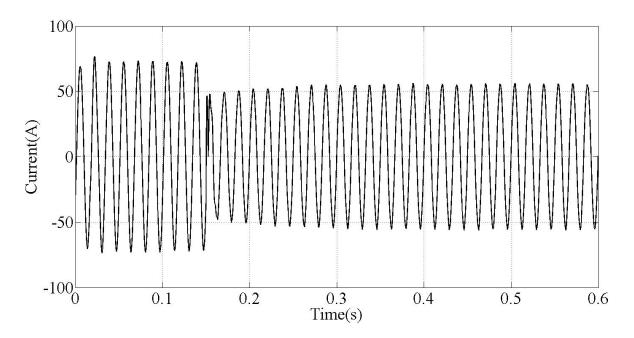

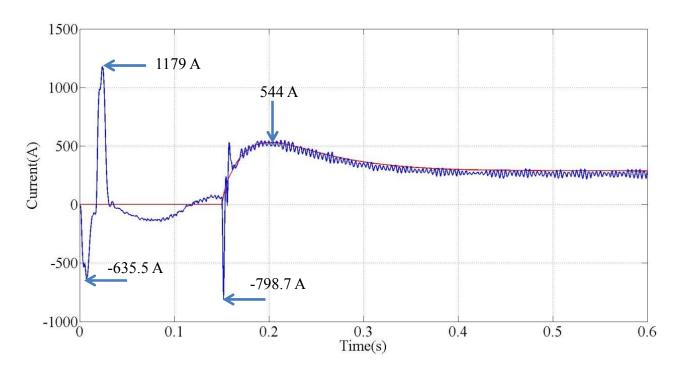

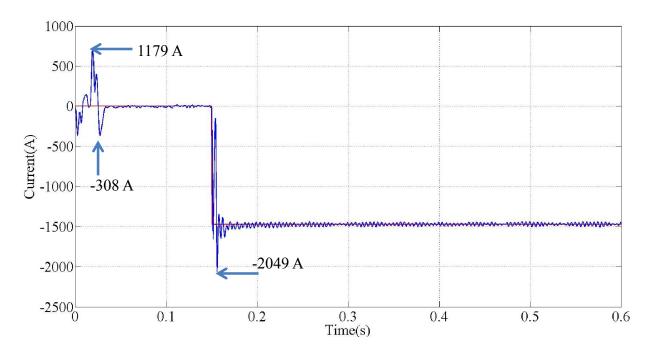

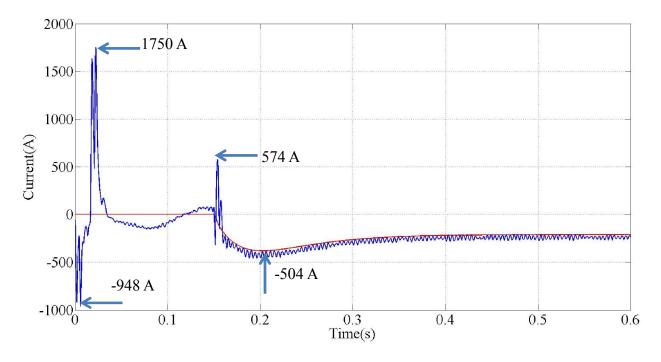

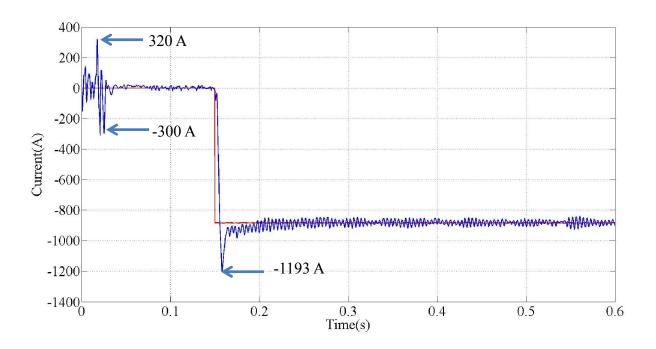

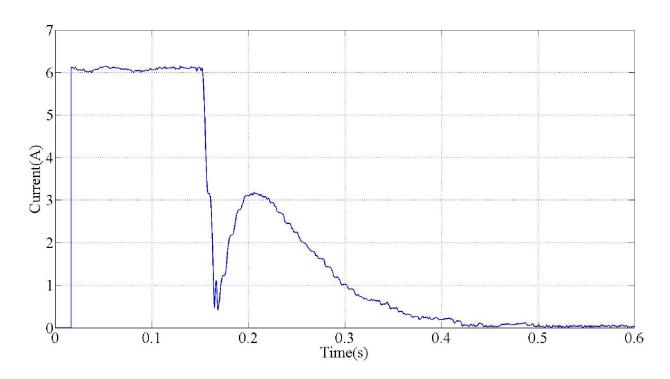

| Fig. 4-13. Phase a source current waveform for case A                           | 83 |

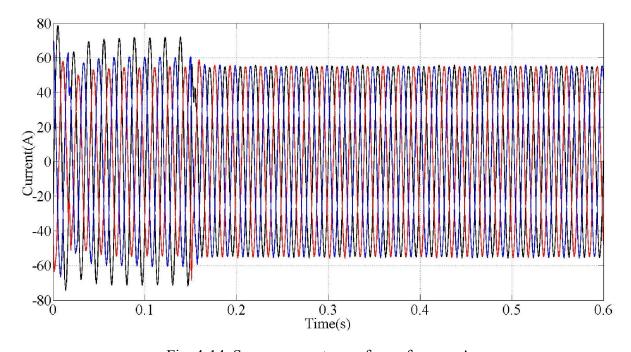

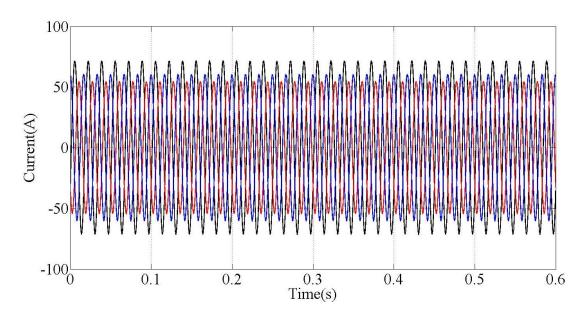

| Fig. 4-14. Source current waveforms for case A                                  | 83 |

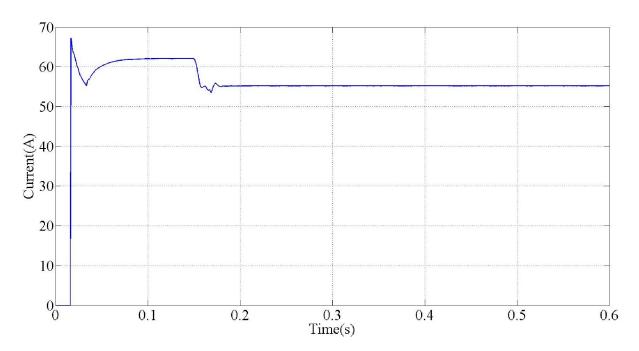

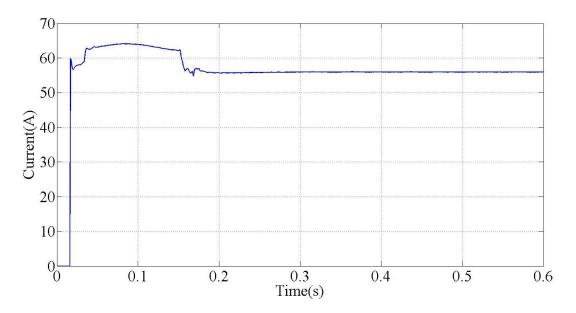

| Fig. 4-15. Positive-sequence current magnitude at the source for case A         | 86 |

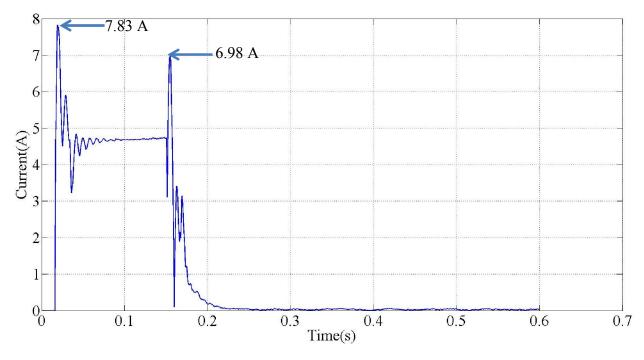

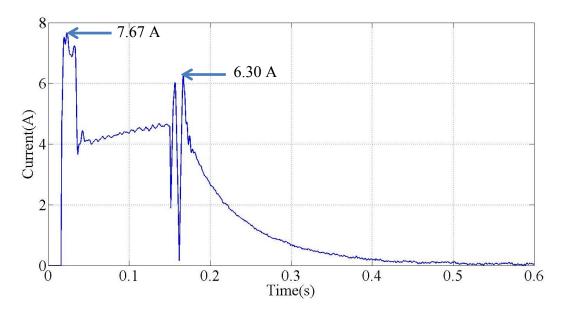

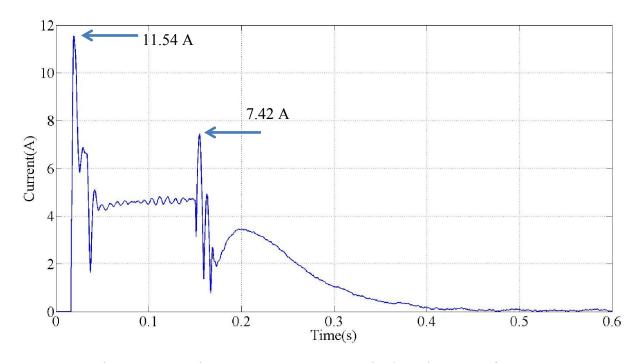

| Fig. 4-16. Negative-sequence current magnitude at the source for case A         | 86 |

| Fig. 4-17. Zero-sequence current magnitude at the source for case A             | 87 |

| Fig. 4-18. Load current waveforms for case A                                    | 90 |

| Fig. 4-19. UCSC MATLAB/SIMULINK <sup>TM</sup> model for case B                  | 91 |

| Fig. 4-20. UCSC control algorithm MATLAB/SIMULINK <sup>TM</sup> mode for case B | 92 |

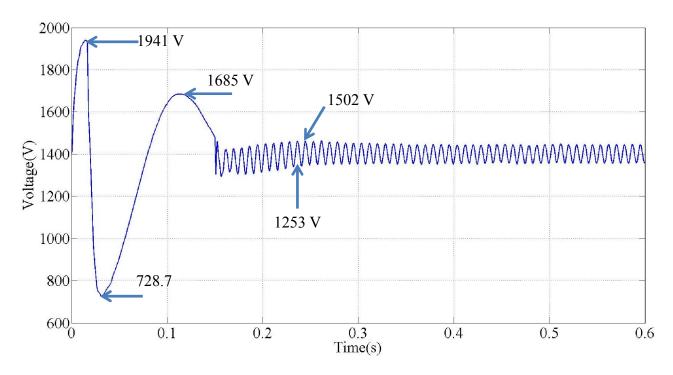

| Fig. 4-21. DC-link voltage waveform for case B.                                 | 94 |

| Fig. 4-22. Current $i_{gad}$ and $i_{gad}^*$ waveforms for case B               | 94 |

| Fig. 4-23. Current $i_{gaq}$ and $i_{gaq}^*$ waveforms for case B               | 95 |

|                                                                                 |    |

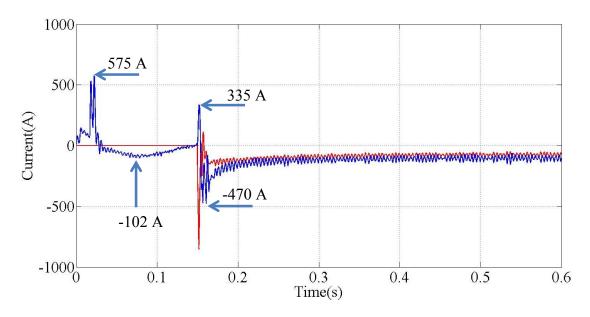

| Fig. 4-24. Current $i_{gbd}$ and $i_{gbd}^*$ waveforms for case B               | 95  |

|---------------------------------------------------------------------------------|-----|

| Fig. 4-25. Current $i_{gbq}$ and $i_{gbq}^*$ waveforms for case B               | 96  |

| Fig. 4-26. Current $i_{gcd}$ and $i_{gcd}^*$ waveforms for case B               | 96  |

| Fig. 4-27. Current $i_{gcq}$ and $i_{gcq}^*$ waveforms for case B               | 97  |

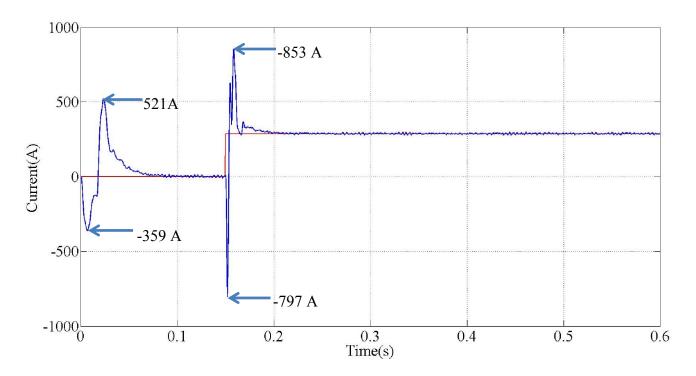

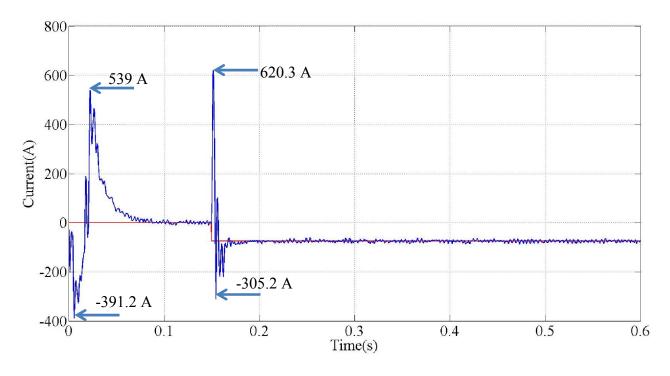

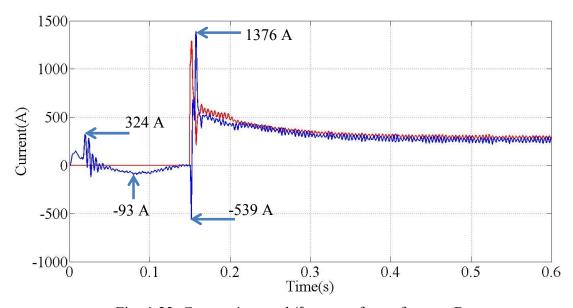

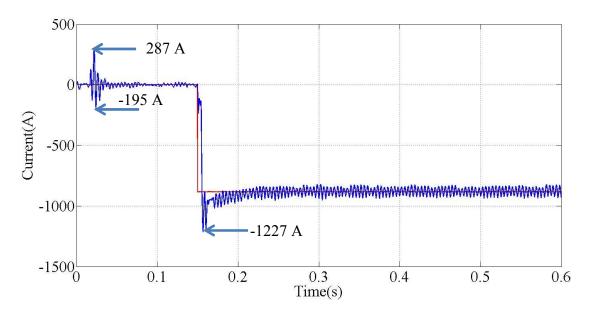

| Fig. 4-28. UCSC phase <i>a</i> current waveforms for case B                     | 98  |

| Fig. 4-29. Phase a source current waveform for case B                           | 101 |

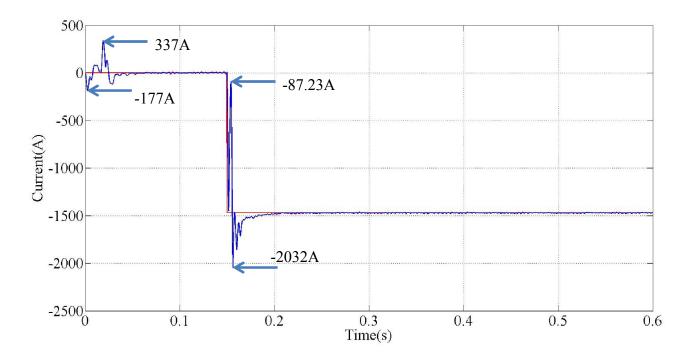

| Fig. 4-30. Source current waveforms for case B                                  | 101 |

| Fig. 4-31. Positive-sequence current magnitude at the source for case B         | 102 |

| Fig. 4-32. Negative-sequence current magnitude at the source for case B         | 103 |

| Fig. 4-33. Zero-sequence current magnitude at the source for case B             | 103 |

| Fig. 4-34. Load current waveforms for case B                                    | 106 |

| Fig. 4-35. Modified <i>d-axis</i> current generator algorithm                   | 107 |

| Fig. 4-36. Low-pass filters added to the DC-link voltage controller             | 108 |

| Fig. 4-37. UCSC control algorithm MATLAB/SIMULINK <sup>TM</sup> mode for case C | 109 |

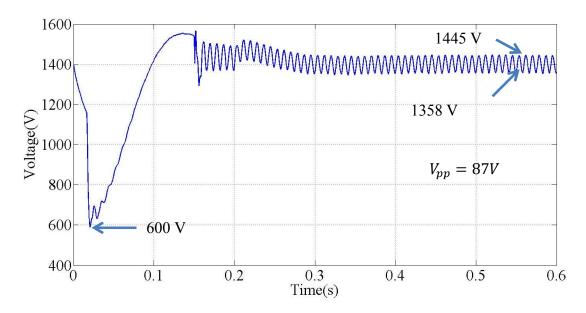

| Fig. 4-38. DC-link voltage waveform for case C                                  | 110 |

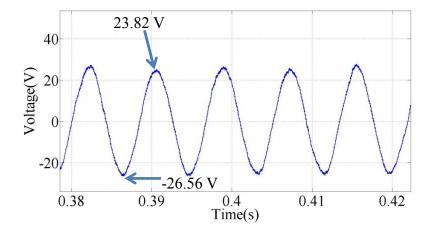

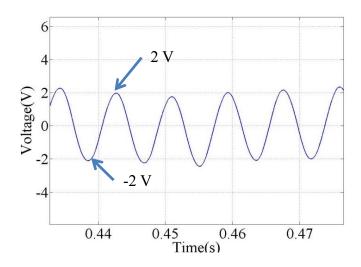

| Fig. 4-39. Ripple signal without low-pass filter for case C                     | 110 |

| Fig. 4-40. Ripple signal with low-pass filter for case C                        | 111 |

| Fig. 4-41. Current $i_{gad}$ and $i_{gad}^*$ waveforms for case C               | 112 |

| Fig. 4-42. Current $i_{gaq}$ and $i_{gaq}^*$ waveforms for case C               | 113 |

| Fig. 4-43. Current $i_{gbd}$ and $i_{gbd}^*$ waveforms for case C               | 113 |

| Fig. 4-44. Current $i_{gbq}$ and $i_{gbq}^*$ waveforms for case C               | 114 |

| Fig. 4-45. Current $i_{gcd}$ and $i_{gcd}^*$ waveforms for case C               | 114 |

| Fig. 4-46. Current $i_{gcq}$ and $i_{gcq}^*$ waveforms for case C               | 115 |

|                                                                                 |     |

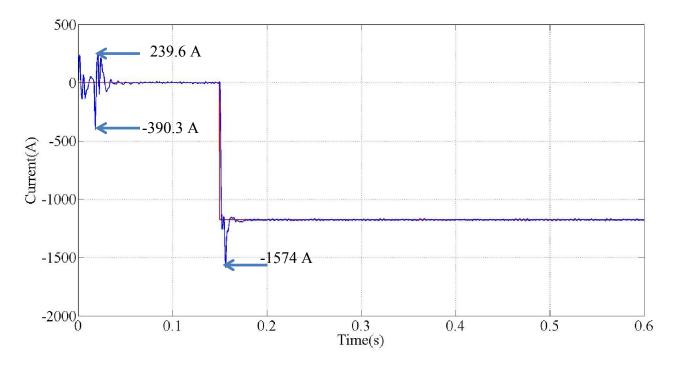

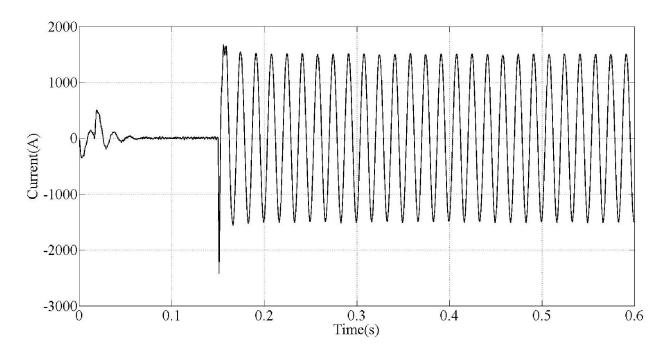

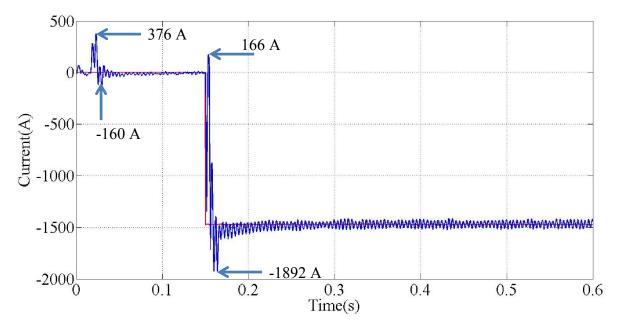

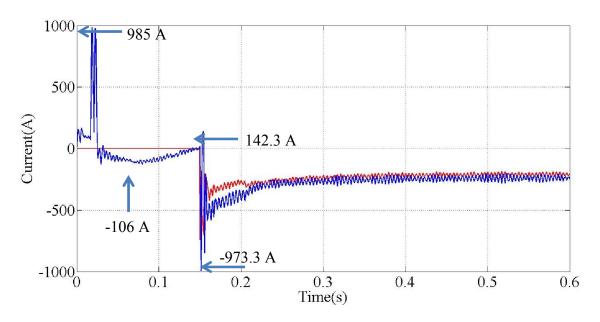

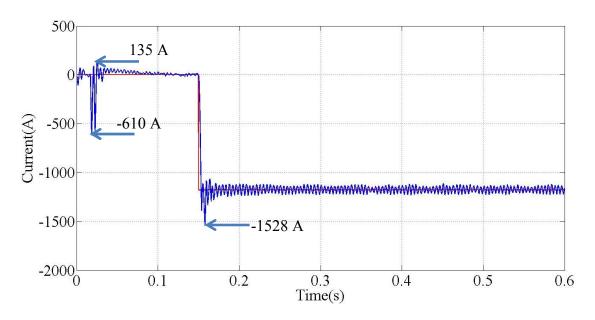

| Fig. 4-47. UCSC phase a current waveforms for case C                    | 115 |

|-------------------------------------------------------------------------|-----|

| Fig. 4-48. Phase a source current waveform for case C                   | 118 |

| Fig. 4-49. Current waveforms at the source for case C                   | 118 |

| Fig. 4-50. Positive-sequence current magnitude at the source for case C | 120 |

| Fig. 4-51. Negative-sequence current magnitude at the source for case C | 120 |

| Fig. 4-52. Zero-sequence current magnitude at the source for case C     | 121 |

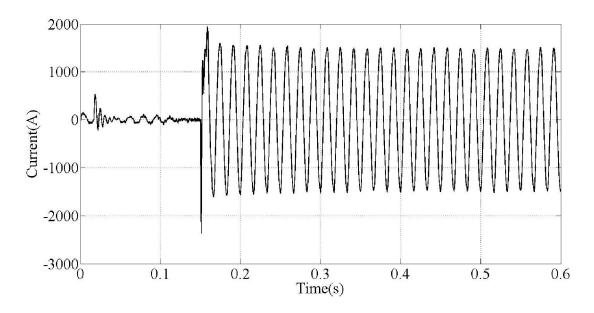

| Fig. 4-53. Load current waveforms for case C                            | 123 |

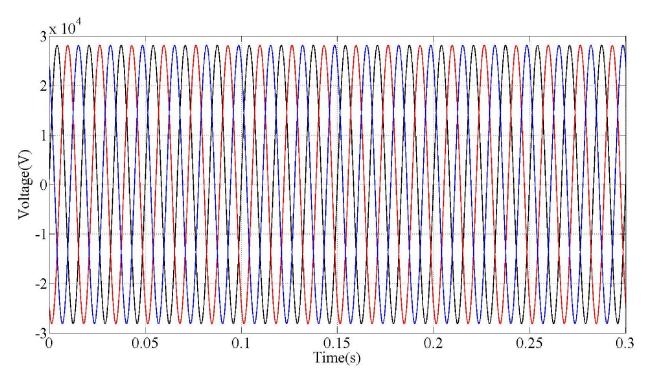

| Fig. 4-54. Voltage waveforms at the PCC                                 | 124 |

| Fig. 5-1. Three-phase three-wire inverter topology                      | 130 |

| Fig. 5-2. Three-phase four-wire inverter topology                       | 131 |

| Fig. 5-3. Three-phase four-legs inverter topology [6]                   | 131 |

# LIST OF TABLES

| Table 2-1. Current controller example parameters [1]                                       | 30 |

|--------------------------------------------------------------------------------------------|----|

| Table 3-1. UCSC system parameters                                                          | 43 |

| Table 3-2. IGBT's parameters                                                               | 44 |

| Table 3-3. LCL filter parameters                                                           | 47 |

| Table 3-4. Controller parameters for case B                                                | 60 |

| Table 4-1. UCSC system parameters                                                          | 75 |

| Table 4-2. Load parameters                                                                 | 75 |

| Table 4-3. Current controller parameters for case A                                        | 75 |

| Table 4-4. Undershoot, overshoot and values for the $d-q$ axes control currents for case A | 77 |

| Table 4-5. UCSC current phasor values for case A                                           | 80 |

| Table 4-6. UCSC positive-sequence current phasor values for case A                         | 81 |

| Table 4-7. UCSC negative-sequence current phasor values for case A                         | 81 |

| Table 4-8. UCSC zero-sequence current phasor values for case A                             | 82 |

| Table 4-9. Current phasors values at source for case A                                     | 84 |

| Table 4-10. Positive-sequence current phasor values at the source for case A               | 87 |

| Table 4-11. Negative-sequence current phasor values at the source for case A               | 88 |

| Table 4-12. Zero-sequence current phasor values at the source for case A                   | 88 |

| Table 4-13. Load current phasor values for case A                                          | 88 |

| Table 4-14. Load positive-sequence current phasor values for case A                        | 89 |

| Table 4-15. Load negative-sequence current phasor values for case A                        | 89 |

| Table 4-16. Load zero-sequence current phasor values for case A                            | 89 |

| Table 4-17. Controller parameters for cases B and C                                     | 91  |

|-----------------------------------------------------------------------------------------|-----|

| Table 4-18. Case B undershoot, overshoot values for the $d-q$ axes control currents for | 97  |

| Table 4-19. UCSC current phasor values for case B                                       | 98  |

| Table 4-20. UCSC positive-sequence current phasor values for case B                     | 99  |

| Table 4-21. UCSC negative-sequence current phasor values for case B                     | 99  |

| Table 4-22. UCSC zero-sequence current phasor values for case B                         | 99  |

| Table 4-23. Current phasors at the source for case B                                    | 100 |

| Table 4-24. Positive-sequence current phasor values at the source for case B            | 104 |

| Table 4-25. Negative-sequence current phasor values at the source for case B            | 104 |

| Table 4-26. Zero-sequence current phasor values at the source for case B                | 104 |

| Table. 4-27. Load current phasor values for case B                                      | 105 |

| Table 4-28. Load positive-sequence current phasor values for case B                     | 105 |

| Table 4-29. Load negative-sequence phasor current values for case B                     | 106 |

| Table 4-30. Load zero-sequence current phasor values for case B                         | 106 |

| Table 4-31. THD values for the UCSC phase a output current                              | 111 |

| Table 4-32. Case C undershoot, and overshoot values for the $d-q$ axes control currents | 112 |

| Table 4-33. UCSC current phasor values for case C                                       | 116 |

| Table 4-34. UCSC positive-sequence current phasor values for case C                     | 116 |

| Table 4-35. UCSC negative-sequence current phasor values for case C                     | 116 |

| Table 4-36. UCSC zero-sequence current phasor values for case C                         | 117 |

| Table 4-37. Current phasor values at source for case C                                  | 119 |

| Table 4-38. Positive-sequence current phasor values at the source for case C            | 121 |

| Table 4-39. Negative-sequence current phasor values at the source for case C            | 121 |

| Table 4-40. Zero-sequence current phasor values at the source for case C | 122 |

|--------------------------------------------------------------------------|-----|

| Table 4-41. Load current phasors values for case C                       | 123 |

| Table 4-42. Load positive-sequence current phasors values for case C     | 123 |

| Table 4-43. Load negative-sequence current phasors values for case C     | 124 |

| Table 4-44. Load zero-sequence current phasor values for case C          | 124 |

| Table 4-45. RMS voltage phasor values at PCC for case C                  | 125 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Motivations for This Research

The main systems of an electrical power grid are the generation, transmission, distribution and load systems [1]. The generation system is where the electrical energy is produced, then, the transmission system transports the electrical energy to the distribution system which delivers to the loads of the end users [1].

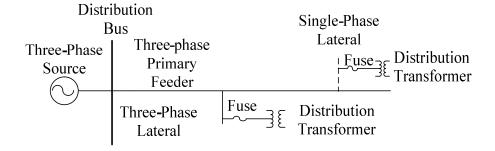

The distribution system delivers electrical energy to the loads through three-phase primary feeders that divide themselves into three- or single-phase branches and laterals as depicted in Fig. 1-1 [2]. There are three main types of loads [1]:

- residential loads that are mainly single-phase loads;

- commercial loads such as shopping malls, schools and hospitals that are a combination of single- and three-phase loads;

- industrial loads having electric motors, resistive loads, control panels and production equipment being mainly a combination of three- and single-phase loads.

Fig. 1-1. A generic three-phase distribution system [2]

The diversity of the three- and single-phase loads leads to unbalanced loading of threephase distribution feeders that can present issues such as the raise of the voltage level and circulating current in the neutral conductor of four-wire systems [3]. These two issues may lead to the interruption of power flow to end-user devices, unnecessary relay tripping and also safety concerns since the neutral conductor could be touched by humans [3], [4].

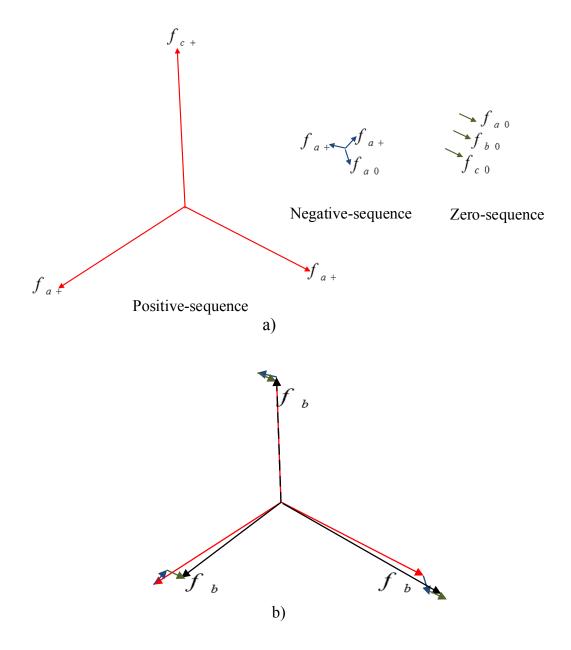

Steady-state unbalanced operation of three-phase systems results in positive- negative-, and zero-sequence components depending on the system wire configuration [5]. Unbalanced cases are studied using analytical tools such as the symmetrical component theory by decomposing the unbalanced three-phase variables such as currents and voltages into three sets of balanced components as illustrated in Fig. 1-2. For counter-clockwise rotation, the sets have following characteristics [6]:

- positive-sequence components consisting of three phasors having equal magnitudes

and a 120° phase shifts between them;

- negative-sequence components consisting of three phasors having equal magnitudes and a 120° phase shifts between them;

- zero-sequence components consisting of three phasors having equal magnitudes and a 0° phase shifts between them.

Synchronous generators can also be affected by unbalanced loading of three-phase distribution feeders. The unbalance can produce a decrease in the generator efficiency due to the overheating of the rotor circuits [7], [8]. The damage to the rotor circuits may also happen because the negative-sequence current leads to the generation of a magneto motive force (MMF) which interacts with the MMF that is generated by the positive-sequence component of the currents.

Fig. 1-2. a) Symmetrical components of an unbalanced three-phase set of variables. b) Addition of the symmetrical component phasors

This interaction produces a torque with a sinusoidal variation at a higher frequency than the fundamental frequency, and results in the velocity of the machine during steady-state condition not being constant [9].

Negative-sequence current components can also produce issues like supersynchronous resonance and subsynchronous resonance on generator turbine blades [8]. So, accidents could happen if the negative-sequence current caused by unbalanced systems is not reduced [8].

Likewise, induction motors are also affected by unbalanced voltages due to the negative-sequence currents. Some of the issues produced by negative-sequence currents are [10]:

- an heterogeneous distribution of heat in the stator due to unbalanced currents;

- additional copper losses in the rotor and stator circuits;

- increased noise;

- increased vibrations that can cause damage to insulation, bearings and interconnecting mechanical equipment.

Lastly, three-legged-core grounded wye-grounded wye transformers may experience tank heating during unbalanced scenarios due to the absence of iron-core return path for the zero-sequence fluxes that leads to the flow of zero-sequence fluxes through the transformer air gap and tank where fluxes induce eddy currents that cause tank heating [11]. Another problem that may be caused by unbalanced currents in distribution feeders is an increase of investment and operating costs of the system [4].

Unfortunately, the unbalanced loading issue has been around for a long time and has not been fully addressed but some solutions to unbalanced currents are presented in the literature and will be briefly described in the next section [8], [12]-[14].

### 1.2 Existing Solutions to Three-Phase Unbalanced Currents

There are some solutions proposed in the literature that provide their own unique ways to correct unbalanced loading in distribution systems. Three of these solutions are the following:

- negative-sequence current reduction for generator/turbine protection [8];

- voltage and current unbalance compensation using a static var compensator [12];

- a solution for three-phase unbalanced system loading based on PWM AC choppers [13].

# Negative-Sequence Current Reduction for Generator/Turbine Protection

The solution proposed in [7] consists in the application of a special-function static var compensator (SVC) that would compensate for only the reactive component in order to reduce the negative-sequence current at the generator terminals. According to [7], the main reasons to not compensate for the active component are:

- the control algorithm would be too complicated;

- high cost of installation and operation.

Reference [7] states that some utilities adopt passive solutions to this issue; for example:

- Generator units are disconnected from the system once the negative-sequence current level reaches a pre-established limit; this is not an attractive solution since other units would need to pick up the power deficit;

- A temporary rearrangement of the distribution system in order to achieve a balanced condition but it could generate issues with the protection scheme.

### Voltage and Current Unbalance Compensation Using a Static Var Compensator (STATCOM)

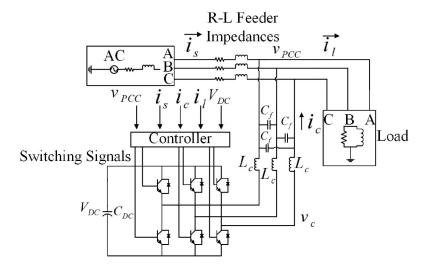

The STATCOM solution proposed in [12] provides reactive compensating currents to correct the voltage and current unbalances. This is achieved by providing reactive power in three-phase three-wire systems with loads where the active component is balanced. The proposed

topology depicted in Fig. 1-3 consists of a three-phase inverter connected in parallel with the load through an L-C filter.

The compensation process is performed by three control schemes [12]:

- current control for unbalanced currents;

- voltage control for unbalanced voltages at the PCC;

- integrated control for both functions.

The three controller schemes in [12] are based on the reactive instantaneous compensation theory proposed in [14] instead of the d-q frame of reference theory that is used in the UCSC system. The equations defining the instantaneous power theory are the following [12]:

$$p(t) = \boldsymbol{v}^{T}(t)\boldsymbol{i}(t) \tag{1-1}$$

$$P(t) = \frac{1}{T_c} \int_{t-T_c}^{t} p(\tau) d\tau$$

(1-2)

Fig. 1-3. Compensator configuration proposed in [12]

where

- p(t) is the instantaneous power;

- P(t) is the average power;

- $v^T(t)$  is the transpose of the voltage vector;

- *i*(*t*) is the current vector;

- $T_c$  is the averaging interval.

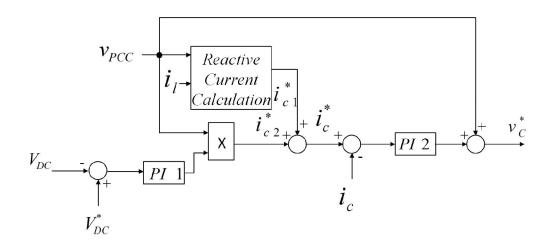

### • Current Controller Scheme

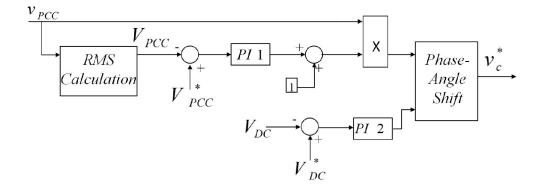

For the current control scheme depicted in Fig. 1-4, the compensator provides the reactive component in the load to balance the source currents and provide unity power factor [1]. The equation that defines the reactive component of the load current is the following [12]:

$$\mathbf{i}_{active}(t) = \frac{P(t)}{V_P^2(T)} \mathbf{v}_p(t)$$

(1-3)

$$\mathbf{i}_{reactive}(t) = \mathbf{i}_{l}(t) - \mathbf{i}_{active}(t)$$

(1-4)

where  $v_p(t)$  and  $i_l(t)$  are the reference voltage and load current vectors, respectively.  $i_{active}(t)$  and  $i_{reactive}(t)$  are the active and reactive instantaneous components of the load current.  $V_p(t)$  is the rms value of  $v_p(t)$ .

The compensating current is composed by the following two terms:

$$\mathbf{i}_c^* = \mathbf{i}_{c1}^* + \mathbf{i}_{c2}^* \tag{1-5}$$

where

- $i_c^*$  is the total reactive compensating current vector;

- $i_{c1}^*$  is the reactive current vector required to balance the currents at the source;

•  $i_{c2}^*$  is the active current vector absorbed by the STATCOM in order to regulate the DC-link voltage to a constant value.

The rest of the variables involved in the algorithm are the following:

- $v_{PCC}$  is the voltage vector at the PCC;

- *i*<sub>l</sub> is the load current vector;

- $v_{DC}$  is the DC-link voltage;

- $v_{DC}^*$  is the DC-link voltage reference;

- $v_c^*$  is the generated control voltage vector for the generation algorithm of the switching signals.

This type of algorithm would only balance the currents measured at the source if the active component of the load is balanced. This is because the STATCOM only provides reactive compensating currents to the grid.

Fig. 1-4. Current controller scheme proposed in [12]

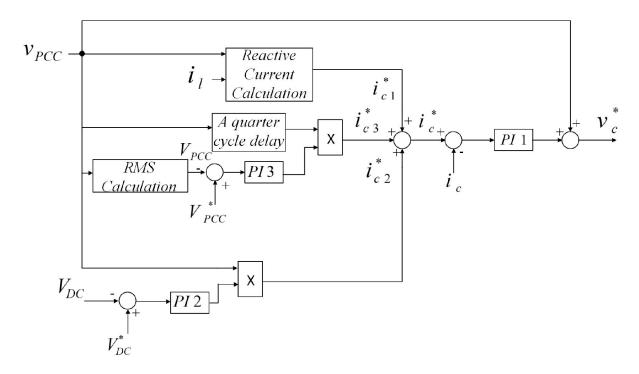

### • Voltage Controller Scheme

The other scheme proposed in [12] is the voltage controller scheme illustrated in Fig. 1-5. The principle of operation consists of having independent control of each phase voltage magnitude. The goal is to have equal magnitudes for  $v_{PCC}$  and  $v_c$ . This is accomplished by [12]:

- a) absorbing reactive current from the grid when the magnitude of  $v_c$  is lower than the magnitude of  $v_{PCC}$ , or;

- b) the STATCOM injects reactive power into the system when  $v_c$  is higher than  $v_{PCC}$ .

The phase-angle shift block is used to generate the necessary phase shift so that the controller absorbs active current to regulate the DC-link voltage [12]. This voltage regulation function at the PCC is not present in the UCSC system but could be designed and implemented in future work.

# • Integrated Controller Scheme

The integrated controller scheme proposed in [12] depicted in Fig. 1-6 performs both functions: current compensation and voltage compensation.

Fig. 1-5. Voltage controller scheme proposed in [12]

Fig. 1-6. Integrated controller scheme proposed in [12]

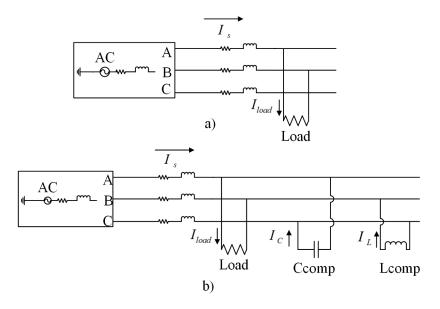

# PWM AC Choppers for Three-Phase Systems with Load Unbalance

The solution presented in [13], is oriented for cases when users are connected only to two phases as depicted in Fig. 1-7 a. Reference [13] mentioned that the issue of unbalanced systems can be solved by applying the Steinmetz Bridge [15] that is illustrated in Fig. 1-7 b from [13]. The bridge consists of capacitors and reactors that balance the source currents.

However, the Steinmetz Bridge has the drawback of requiring tuning the load current changes; that is the compensator elements need to change in order to re-balance the system. This issue can be addressed by having variable compensator capacitor and reactor banks [13]. However, other issues arise with this approach. Transients due to the switching of the compensator elements plus over-voltages and over-currents potentially generated due to the inductors and capacitors [13].

The PWM AC chopper solution illustrated in Fig. 1-8 is proposed in [13] in order to avoid the issues that come with the switching of capacitor and inductor banks. This approach is based on the DC/DC buck converter and the output voltage is dependent of the duty cycle as illustrated in the following equations [13]:

$$I_{a} = \frac{V_{AB}\alpha_{1}^{2}}{\frac{1}{j2\pi fC_{comp}} + j2\pi fL_{out}}$$

(1-6)

$$I_b = \frac{V_{BC}\alpha_1^2}{\frac{1}{j2\pi f L_{comp}}} \tag{1--7}$$

$$\alpha_1 = \sqrt{\frac{I_a \left(\frac{1}{2\pi f C_{comp}} + 2\pi f L_{out}\right)}{V_{AB}}}$$

(1-8)

$$\alpha_2 = \sqrt{\frac{I_b(2\pi f L_{comp})}{BC}} \tag{1-9}$$

Fig. 1-7. a) Unbalanced system schematic [13]. b) Steinmetz Bridge from [13]

Fig. 1-8. AC-choppers solution proposed in [13]

This solution while being cheap and robust as noted in [13], is only applicable f or specific cases with loads connected only to two phases.

The solutions proposed in [8], [12] and [13] approach the unbalanced current issue from different perspectives. Also, these solutions are designed to provide reactive compensating currents; therefore for cases where the active component of the load is unbalanced the application of these solutions is limited.

By finding a solution to the unbalanced load issue, power systems would be more reliable, secure and efficient leading to costs savings for the utilities. Future load growths and interconnection with the main grid of isolated circuits would also become easier to handle for the utilities. Furthermore the generation of energy with higher power quality and lower electricity

prices should attract more customers to a particular area. All this will help utilities to become more competitive [10].

### 1.3 Thesis Objectives

The main objective of this thesis is to develop a solution that would be able to balance the source currents in a power system having unbalanced loads. The solution will be called: Unbalanced Current Static Compensator (UCSC). In order to accomplish this objective, the following enabling objectives should be accomplished:

- an understanding of the theoretical background of the UCSC system;

- a knowledge of the p-q theory as applied to single-phase systems;

- the design of voltage controller for the DC link of the UCSC;

- MATLAB/SIMULINK<sup>TM</sup> simulations of an unbalanced three-phase four-wire system coupled with the UCSC solution;

- an evaluation of the simulation results.

### 1.4 Case Study of a Distribution System with Unbalanced Loading

A case study must be selected in order test the proposed ideas for the unbalanced loading issue. The case study is based on a 34.5 kV unbalanced three-phase four-wire distribution system fed from a power substation.

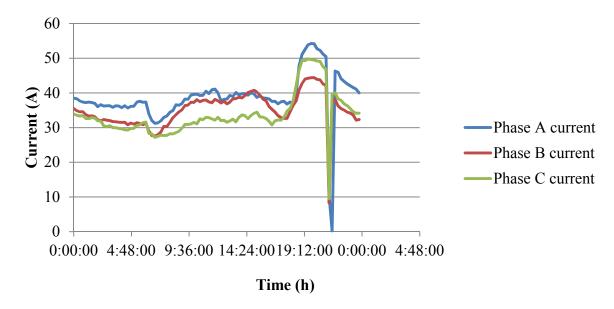

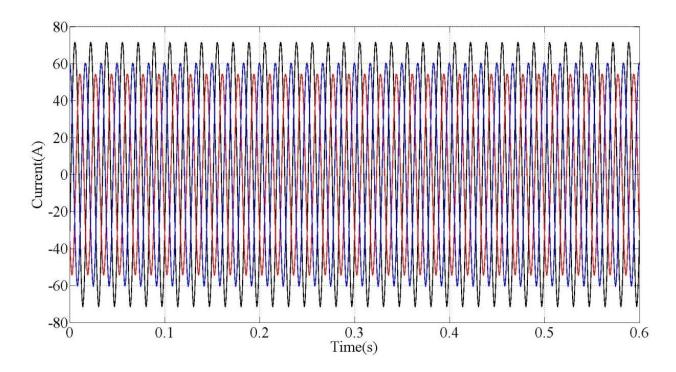

The current unbalance for the case study is based on the current profile depicted in Fig. 1-9. At the 22h:00m:00s, the values of the phase currents are 45.99 A, 36.27 A and 38.33 A for phases *a*,*b* and *c*, respectively.

Fig. 1-9. Current profile of an unbalanced 34.5 kV three-phase distribution feeder

This unbalance leads to a difference of 9.72 A and 7.66 A between phases *a-b* and *a-c*, respectively. This unbalanced condition generates negative- and zero-sequence current magnitudes of 4.43 A and 5.14 A, respectively, that can cause the issues discussed in section 1-1.

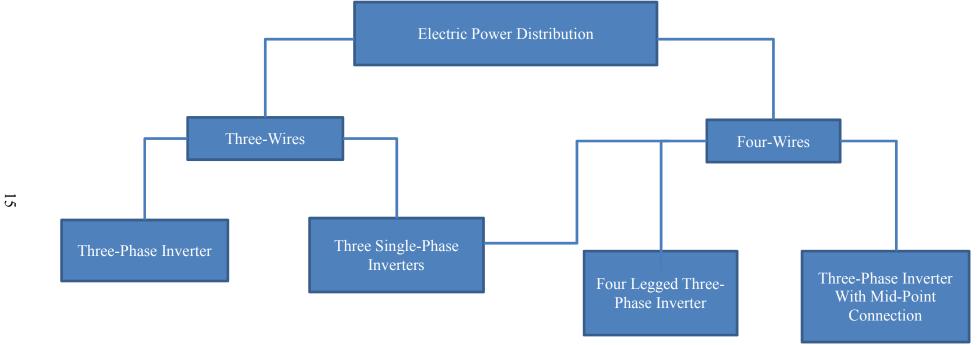

In order to address this unbalance, a topology for the UCSC system must be chosen. During the initial stage of the UCSC project, several topologies were being considered as broadly classified in Fig. 1-10:

- three-phase three-legged converters (refer to Fig. 1-11 and Fig. 1-12;

- three-phase four-legged converter (refer to Fig. 1-13).

- three single-phase H-bridge converters (refer to Fig. 1-14);

The topology of Fig. 1-11 is implemented in the solution proposed by [12] and analyzed in section 1.2. The topologies depicted in Figs. 1-12 and 1-13 are presented in [16] and [17] to be used as the source for unbalanced loads.

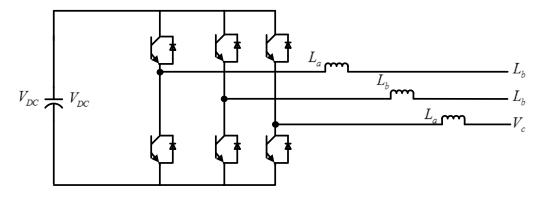

Fig. 1-10. Inverter topologies

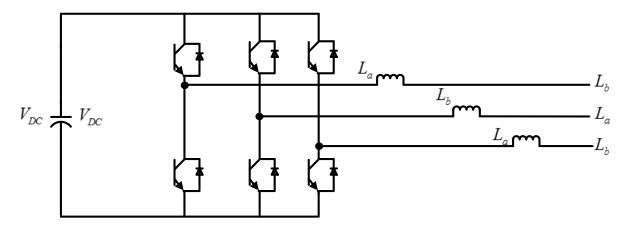

Fig. 1-11. Three-phase three-wire inverter topology

The three-phase three-wire inverter of Fig. 1-11 has six switches and also one capacitor in the DC link. Because the case study is based on a three-phase four-wire system, this type of topology is not suitable for the UCSC project.

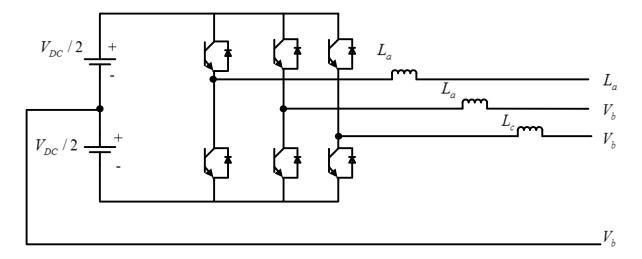

Only the three-phase four-wire with mid-point, the four-leg inverter and the three single-phase inverters topologies are suitable for the UCSC project. The converter of Fig. 1-12 needs to have two capacitors instead of one. The neutral point connection of the topology presented in Fig. 1-12 has the goal of making the three phases independent of each other [18]. This topology has the following drawbacks when supplying unbalanced loads [17], [18]:

- distortion in the symmetrical output voltage for unbalanced loads;

- large capacitors and high DC-link voltage are needed to mitigate the voltage ripple generated by the zero-sequence current that flows across the capacitor;

- small utilization of the DC-link voltage;

- the dependency of the modulation factor of the load current. According to [18], the modulation factor is dependent of the load current. The maximum value is reached when the load is balanced and it's reduced when the load becomes unbalanced [18].

Fig. 1-12. Three-phase four-wire inverter topology

- superposition of a DC component with the output AC voltage;

- power losses due to the zero-sequence current in the DC link.

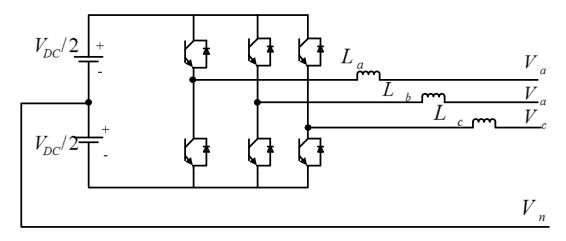

The three-phase four-leg inverter consists of eight switches and one capacitor in the DC link. The advantages of the three-phase four-leg inverter are the following [18], [19]:

- small DC-link capacitor;

- no zero-sequence current across the DC-link capacitor;

- more DC-link voltage utilization in comparison with the three-phase three-legged converter with mid-point connection. This is due to the fact that the maximum line-to-neutral output voltage that can be reached is  $0.577V_{DC}$  in comparison with the  $0.5V_{DC}$  value that can be reached in a three-phase inverter with mid-point connection.

The main drawback for the three-phase four-legged converter is that the control algorithm is more complex than the algorithm required for a conventional three-legged converter [19]. This is one of the reasons that makes the three single-phase H-bridge converters more attractive since the control approach is simpler. Other reasons are the independent control of each phase current

the higher DC-link voltage utilization just like the three-phase four-legged inverter topology. The drawback is that 12 switches are required. Taking all of the above into account, this thesis focuses on the topology composed of three single-phase H-bridge converters as the starting point for the quest for a cost-effective solution for unbalance loading of distribution feeders.

After presenting the unbalanced case and the UCSC topology, the one-line diagram of the case study and its elements are illustrated in Fig.1-14:

- the 34.5 kV power substation;

- the feeder impedances for segment 1 and 2;

- the three-phase unbalanced load;

- the single-phase UCSC-coupling transformers T1, T2 and T3;

- the UCSC system.

Fig. 1-13. Three-phase four-legged inverter topology

Fig. 1-14.One-line diagram for the case study

## 1.5 Thesis Organization

A theoretical background of the system elements will be presented in chapter 2 that starts with an overview of reference frame theory followed by brief descriptions of the components and modes of operation of the H-Bridge. A description of the UCSC and its control algorithm are given in chapter 3.

The model parameters and the analysis of the MATLAB/SIMULINKTM simulations are presented and evaluated in chapter 4. Models of the three-phase four-wire distribution systems and the UCSC control algorithm are presented. These models are built using MATLAB/SIMULINKTM blocks. The conclusions and the recommendations for future work are presented in chapter 5.

# 1.6 Conclusions

The following conclusions can be drawn from chapter 1:

- the diversity of the three- and single-phase loads leads to unbalanced loading of threephase distribution feeders [3];

- steady-state unbalanced operation of three-phase systems results in positivenegative-, and zero-sequence components depending on the system wire configuration [5].

- synchronous generators and induction motors are affected by the negative- and zerosequence currents generated by unbalanced loading;

- the solutions presented in this chapter are limited to cases where only the reactive compensating currents are needed to balance the source currents.

### 1.7 References

- [1] L. M. Faulkenberry and W. Coffer, <u>Electrical Power Distribution and Transmission</u>. Englewood Cliffs, NJ: Prentince Hall, 1996.

- [2] T. Gonen, <u>Electric Power Distribution System Engineering</u>, Second Edition. Boca Raton, FL: CRC Press Taylor & Taylor Group, 2008.

- [3] A. P. S. Meliopoulos, J. Kennedy, C. A. Nucci, A. Borghetti, G. Contaxis, "Power distribution practices in USA and Europe: impact on power quality," *Proceedings. 8th International Conference on Harmonics and Quality of Power Proceedings*, vol. 1, pp. 24–29, October 1998.

- [4] Z. Jinxiang, C. Mo-Yuen; Z. Fan, "Phase balancing using mixed-integer programming [distribution feeders]," *IEEE Transactions on Power Systems*, vol. 13, no. 4, pp. 1487–1492, November, 1998.

- [5] C.B. Jacobina, M.B.deR. Correa, T.M. Oliveiro, A.M.N. Lima, E.R. Cabral da Silva, "Current control of unbalanced electrical systems," *IEEE Transactions on Industrial Electronics*, vol. 48, no. 3, pp. 517–525, June, 2001.

- [6] J. Wang, R. Hamilton, "A review of negative sequence current," 2010 63rd Annual Conference for Protective Relay Engineers, pp. 1–18, April, 2010.

- [7] R.G. Harley, E.B. Makram, E.G. Duran. (1987); "The effects of unbalanced networks on synchronous and asynchronous machine transient stability," *Electric Power System Research*[Online].Available:http://www.sciencedirect.com/science/article/pii/0378779687 900393

- [8] W-J. Lee, T.-Y. Ho, J.-P. Liu, Y.-H. Liu, "Negative sequence current reduction for generator/turbine protection," *Conference record of the 1993 IEEE Industry Applications Society Annual Meeting*, vol. 2, pp. 1428–1433, October, 1993.

- [9] R.H. Salim, R.A. Ramos, N.G. Bretas, "Analysis of the small signal dynamic performance of synchronous generators under unbalanced operating conditions," *IEEE Power and Energy Society General Meeting*, pp. 1–6, July, 2010.

- [10] B. N. Gafford, W.C. Duesterhoeft, C.C. Mosher, "Heating of induction motors on unbalanced voltages," *Transactions of the American Institute of Electrical Engineers Power Apparatus and Systems, Part III*, vol. 78, no. 3, pp. 282–286, April 1959.

- [11] T. A. Short. <u>Electrical Power Dstribution Handbook</u>. Boca Raton, FL: CRC Press Taylor & Taylor Group, 2004.

- [12] Y. Xu, L.M. Tolbert, J.D. Kueck, D.T. Rizy, "Voltage and current unbalance compensation using a static var compensator," *IET Power Electronics*, pp. 977–988, vol. 3, 2010.

- [13] B. Cougo, T. Meynard, "A solution for three-phase system unbalance based on PWM AC Choppers," *32nd Annual Conference on IEEE Industrial Electronics*, (IEC), pp. 1679–1684, November, 2006.

- [14] Y. Xu, L.M. Tolbert, F.Z. Peng, J.N. Chiasson, J. Chen, "Compensation-based non-active power definition," *Power Electronics Letters, IEEE*, vol.1, no. 2, pp. 45–50, June, 2003.

- [15] M. Chindris, A. Cziker, S. Stefanescu, "Symmetrizing Steinmetz circuitry behavior in harmonic polluted networks," *16th International Conference and Exhibition on Electricity Distribution*, vol. 2, pp. 4, 2001.

- [16] H. Mattias, S. Helmut, "Control of a three phase inverter feeding an unbalanced load and operating in parallel with other power sources," *EPE-PEMC*, pp. 1–10, 2002.

- [17] I.Vechiu, O. Curea, H. Camblong, "Transient operation of a four-leg inverter for autonomous applications with unbalanced load," *IEEE Transactions on Power Electronics*, vol. 25, pp. 399–407, February, 2010.

- [18] S. Ei-Barbari, W. Hofmann, "Digital control of a four leg inverter for standalone photovoltaic systems with unbalanced load," *26th Annual Conference of the IEEE Industrial Electronics Society*, IECON, vol. 1, pp. 729–734, 2000.

- [19] R. Zhang, D. Boroyevich, V.H. Prasad, M. Hengchun, F.C. Lee, S. Dubovsky, "A three-phase inverter with a neutral leg with space vector modulation," *Twelfth Annual Applied Power Electronics Conference and Exposition*, APEC, vol. 2, pp. 857–863, vol. 2, February, 1997.

### **CHAPTER 2**

### SYSTEM FUNDAMENTAL CONCEPTS

### 2.1 Background Concepts Related to Power Electronic Converters

An overview of fundamental concepts used in the development and analysis of the proposed UCSC solution should be presented before a detailed description of the case study. Hence, this chapter focuses on the description of the modes of operation and control algorithm for single-phase inverters.

Power electronic converters can be defined as multiport circuits composed of semiconductor switches and are used to interface subsystems that cannot be connected directly because of their different characteristics such as voltage level or type, frequency, phase angle and number of phases. This interface is necessary so that the subsystems are able to exchange electric power between them [1]. Power electronic converters can be classified as follows [1]:

- AC/AC converters interfacing two AC subsystems;

- DC/DC converters interfacing DC subsystems;

- the DC/AC converters where a DC subsystem is interfaced with an AC subsystem.

The DC/AC converter category can be further divided into rectifiers and inverters. The power flows from the AC-side to the DC-side in rectifiers and power flows in the opposite direction (from the DC-side to the AC-side) in inverters [1]. So, the converters are composed of power semiconductor devices (switches) that are controlled (turned on and off) by gating signals that determine the current flow through a circuit branch [1].

Power electronic converters can be further classified depending on the switching method [2]:

- *line frequency (naturally commutated) converters*: the switching process is started by the change of polarity of the AC voltage [1]. The switching frequency on this case has the same value of the line frequency [2].

- Switching (forced commutated) converters: The three main characteristics are [1],[2]

- o the switching frequency is higher than the line frequency;

- o the turn on/off is a controlled process;

- o switches must have gate turn-off capability.

- Resonant and quasi-resonant converters: The switching is performed at zero voltage and/or zero current.

Another aspect used to classify the converters is the DC-side waveforms. If the DC-side current direction is changed in order to control the power flow, then, it is named a voltage-sourced converter (VSC). If the DC-side current remains constant and the DC-side voltage direction is changed to control the power flow, then, it is named a current-sourced converter (CSC) [1]. The VSC is the most suitable option given the fact that one of the goals of the UCSC project is to have independent control of the phase currents. Thus, the rest of the chapter focuses on VSCs that can be further classified as follows [2]:

- Pulse-width-modulated (PWM) inverters: This type of converter is characterized by output AC voltages were the magnitude and frequency are controlled by pulse-width-modulated switches. The input DC voltage remains constant during the converter operation [2].

- *Square-wave inverters*: Instead of using PWM techniques, square-wave converters modify the input DC voltage to control the magnitude of the output AC voltages.

Only the frequency is controlled through the switching devices [2].

• Single-phase inverters with voltage cancellation: This type of converter is used when the input DC voltage is constant and when PWM is not applied. A combination of the PWM and square-wave control techniques is required to control the magnitude and the frequency of the output AC voltage [2].

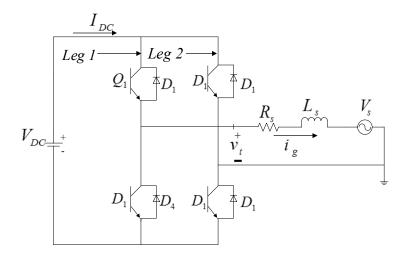

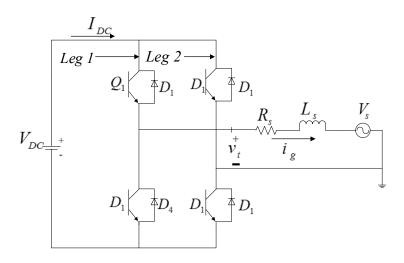

The converters can be also classified as single- or three-phase converters and two of the most common topologies are half H-bridge or full H-bridge [1]. Section 2.2 addresses the full H-bridge single-phase converter which will be referred to as H-bridge converter hereinafter. The schematic of the H-bridge converter is given in Fig. 2-1.

### 2.2 H-Bridge: Rectifier and Inverter Operations

One of the characteristics of the UCSC system is that it is capable of absorbing and injecting active and reactive powers into a three-phase system. This means that the converters of the UCSC system should be able to operate as rectifiers and also as inverters. Based on Fig. 2-1, the converter operates as a rectifier when  $i_g$  (in blue) and  $v_t$  (in red) have opposite signs and as an inverter when the signs are equal [2].

### PWM Algorithm

The rectifier/inverter operation is controlled by the switching signals of the semiconductor switches. One of the methods to generate the switching signals is the PWM switching scheme commonly called "sine-triangle" PWM technique [2]. The PWM scheme generates the switching signals by comparing a sinusoidal signal that has the desired frequency

fundamental  $f_1$  with a triangular signal whose frequency is the switching frequency  $f_{sw}$  of the converter, also called the carrier frequency.

Fig. 2-1. Single-phase H-bridge converter

Fig. 2-2. Filtered single-phase H-bridge output waveforms [2]

The sinusoidal signal (control signal) and the triangular signal are related by two modulation ratios: the amplitude modulation ratio  $(m_a)$  and the frequency modulation ratio  $(m_f)$  where  $m_a$  and  $m_f$  can be defined as follows [2]:

$$m_a = \frac{\hat{V}_{sin}}{\hat{V}_{tri}} \tag{2-1}$$

$$m_f = \frac{f_{sw}}{f_1}. (2-2)$$

where

- $\hat{V}_{sin}$  is the peak magnitude of the sinusoidal control signal;

- $\hat{V}_{tri}$  is the peak magnitude of the triangular waveform signal;

The following guidelines for  $m_a$  and  $m_f$  values should be taken into consideration for the design of a converter system [2]:

- $m_a$  should be less or equal than 1 in order for the amplitude of the fundamental-frequency component to vary linearly with  $m_a$ . Values of  $m_a$  above 1 end up in distorted output voltages that are undesirable in applications such as uninterruptible power supplies [2].

- In order to avoid subharmonics, the value of  $m_f$  should be an integer. An odd integer is preferred in most cases except when working with single-phase converters controlled by PWM unipolar voltage switching scheme [2].

The reduced harmonic content is an important reason to choose the unipolar PWM voltage switching scheme over the bipolar PWM voltage switching scheme [2]. Other characteristics of the unipolar PWM switching scheme are the following [2]:

- The output voltages of legs 1 and 2 are controlled independently. The sinusoidal control signal  $(v_{sin})$ , is compared to the triangular signal  $(v_{tri})$  to control leg 1. In order to control leg 2,  $-v_{sin}$  is compared with  $v_{tri}$  in order to generate the switching signals.

- Contrary to the case of the bipolar PWM switching scheme where the output voltage varies between the positive and negative values of  $V_{DC}$ , the output voltage for unipolar PWM changes between  $V_{DC}$  and zero or between zero and  $-V_{DC}$  as illustrated in Fig. 2-3.

Another important topic that must be studied in order to understand the operation of the UCSC system is the current control scheme that is addressed in section 2.3.

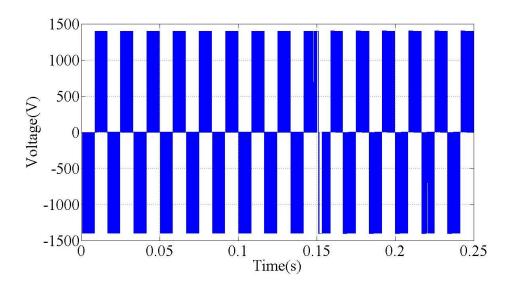

Fig. 2-3. Unipolar PWM voltage switching scheme

### 2.3 Current Control of a H-Bridge

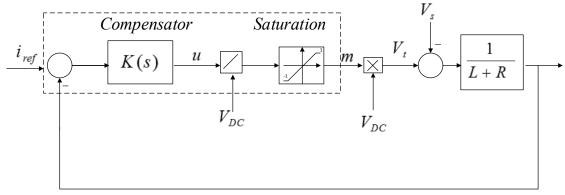

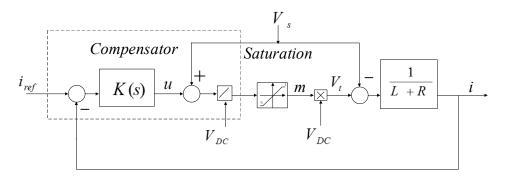

Section 2.2 presented an overview of the single-phase H-bridge converter operating concepts whose understanding is important in order to implement the current control techniques covered in this section. A typical current controller for a single-phase H-bridge converter is illustrated in Fig. 2-4. According to [1], a proportional-integral (PI) compensator can be used in the algorithm if:

- $i_{ref}$  signal is step type;

- $V_S$  is a DC voltage.

The compensator block from Fig. 2-4 can be expressed as follows:

$$K(s) = k_p + \frac{k_i}{s} \tag{2-3}$$

with (2-3) and the diagram of Fig. 2-4, the closed loop gain of the system can be defined as follows [1]:

$$G = \frac{k_p}{L} \left( \frac{s + \frac{k_i}{k_p}}{s + \frac{R}{L}} \right). \tag{2-4}$$

Fig. 2-4. Closed-loop current control diagram

The gains of the PI compensator are defined by [1]:

$$\frac{k_i}{k_p} = \frac{R}{L} \tag{2-5}$$

$$\frac{k_p}{L} = \frac{1}{\tau_i} \tag{2-6}$$

where R and L resistor and inductor interfacing the inverter with the grid, and  $k_i$ ,  $k_p$ ,  $\tau_i$  are the integral, integral gain, proportional gain and the time constant of the system. In most applications the value range for  $\tau_i$  is between 0.5-5.0 ms [1].

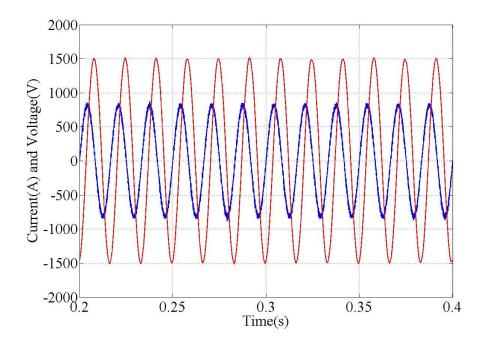

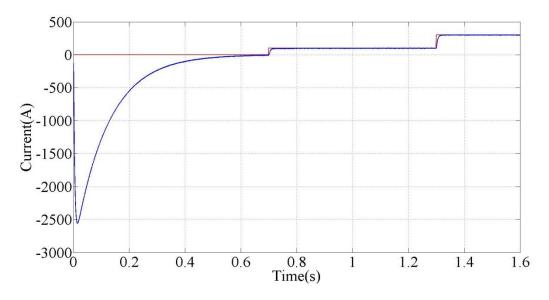

A MATLAB/SIMULINK<sup>TM</sup> simulation is presented in order to illustrate the concept of a single-phase H-bridge current controller. The parameters for the simulation are shown in Table 2-1 [1]. The MATLAB/SIMULINK<sup>TM</sup> H-bridge model and control block are illustrated in Fig. 2-5 and 2-6, respectively. The main issue that can be observed on the system response of Fig. 2-7 is that the system experiences an undershoot response due to initial conditions

Table 2-1. Current controller example parameters [1]

| Parameter       | Value |

|-----------------|-------|

| Resistance (mΩ) | 5     |

| Inductance (μH) | 690   |

| $V_{DC}$ (V)    | 1200  |

| $V_s$ (V)       | 400   |

| $f_{sw}$ (Hz)   | 1620  |

This is due to fact that the system starts from a zero-state and the value of  $V_t$  is equal to 0 and while  $V_s$  is negative. This leads to a negative value of i until it gets regulated to 0 by the controller [1].

Fig. 2-5. MATLAB/SIMULINK<sup>TM</sup> H-bridge model.

Fig. 2-6. MATLAB/SIMULINK  $^{\text{TM}}$  control algorithm block diagram.

Fig. 2-7. Output current i (blue) and reference current  $i_{ref}$  (red) waveforms

The maximum reached value due to the undershot is 2566 A. This condition should be avoided; otherwise, the H-bridge must be designed in such a way that I can withstand the large amount of current generated during the system start up process. The system response settling time is of 0.7 s approximately. When the current goes from 0 A to 100 A at 0.75 s, the system response is over-damped because it does not oscillate to reach the reference signal. The same behavior is observed when the second step is introduced at 1.3 s. The approximate settling time for both cases is of 0.011 s (0.66 cycles) and 0.014 s (0.84 cycles), respectively. The system response can be improved if a feed forward compensation [1] is applied to the control loop as is shown in Fig. 2-8 and the improved response of the system is depicted in Fig. 2-9.

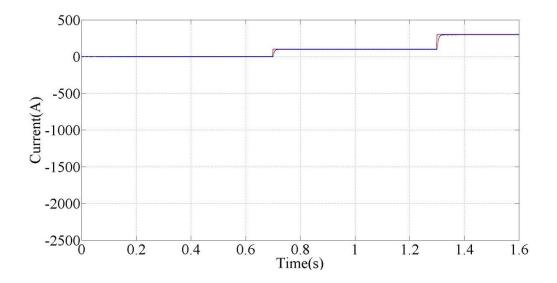

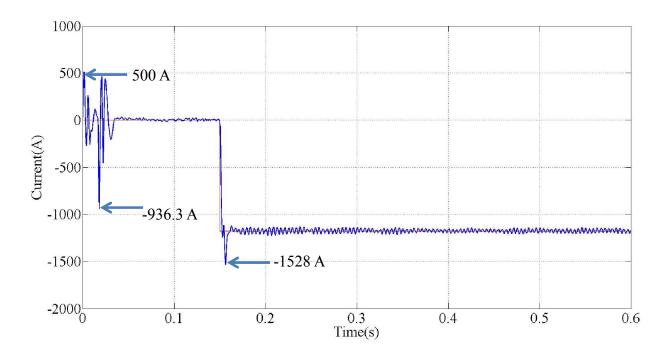

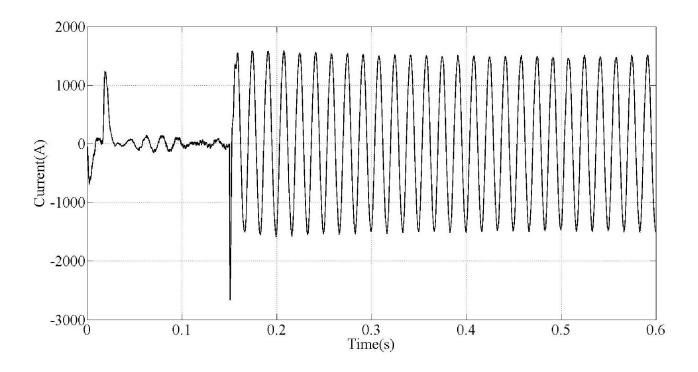

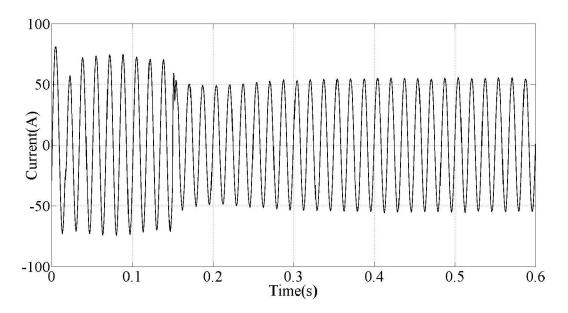

The results depicted on Fig. 2-9 illustrate the improvement of the system response after applying a feed forward compensation technique to the original controller. The undershoot response of the system observed in Fig. 2-7 is mitigated and the settling time is greatly improved as shown in Fig. 2-9. The next section presents the fundamental concepts of reference frame theory that is normally used in three-phase systems.

Fig. 2-8. Closed-loop current control diagram with feed forward compensation

Fig. 2-9. Output current i (blue) and reference current  $i_{ref}$  (red) waveforms with feed forward compensation

### 2.4 Reference Frame Theory

A current controller with a PI compensator can follow a reference with a small or no steady-state error as long as the reference signals are constant or slowly varying [1]; otherwise a very high switching frequency would be required. Because the UCSC system is a solution for three-phase four-wire systems, the reference command in the *abc* frame will not be a constant or

slow varying value and the controller output will have errors in magnitude and phase [1]. This issue can be solved if the *abc* variables are transformed to the synchronous reference frame by applying Park's transformation [3], [4].

The Park's transformation refers stator variables such as currents, flux linkages and voltages of a synchronous machine to a frame reference fixed on its synchronous-rotating rotor so the variation of the inductance values as function of the position of the rotor can be eliminated [4]. This reference frame is the so-called synchronous-rotating reference frame [4].

Even though Park's transformation was envisioned to work in the study of AC machines, it can also be implemented in other constant-parameter power-system components [4]. The Park's transformation equation can be expressed as follows [4]:

$$[\mathbf{f}_{\text{qd0s}}] = [\mathbf{K}_{\text{s}}][\mathbf{f}_{\text{abcs}}]. \tag{2-7}$$

where and f could be current, voltage, flux linkage or electric charge, and [K<sub>s</sub>] is given by:

$$[K_s] = \frac{2}{3} \begin{bmatrix} \cos \theta & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \\ \sin \theta & \sin(\theta - \frac{2\pi}{3}) & \sin(\theta + \frac{2\pi}{3}) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix}$$

(2-8)

with its inverse  $[K_s]^{-1}$  matrix is given by:

$$[K_{s}]^{-1} = \begin{bmatrix} \cos \theta & \sin \theta & 1\\ \cos(\theta - \frac{2\pi}{3}) & \sin(\theta - \frac{2\pi}{3}) & 1\\ \cos(\theta + \frac{2\pi}{3}) & \sin(\theta + \frac{2\pi}{3}) & 1 \end{bmatrix}$$

(2-9)

where  $\theta = \omega_s t + \theta_0$  with  $\omega_s t$  is the grid angular speed, t time and  $\theta_0$  the initial angle [4].

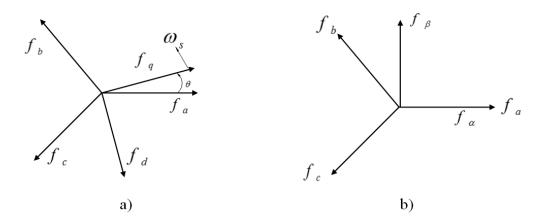

The relationship between the *abc* variables and the d-q axes is illustrated in Fig. 2-10a [4]. Another important transformation of variables used to design current controllers of converter systems is the Clarke's transformation, also known as the  $\alpha - \beta - 0$  transformation. This transformation in matrix form is given by [5]:

$$\begin{bmatrix} \mathbf{f}_{\alpha\beta0} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} f_a \\ f_b \\ f_c \end{bmatrix}$$

(2-10)

where the variables in the *abc* frame are transformed or referred to the  $\alpha - \beta$  stationary axes as illustrated in Fig. 2-10b.

This transformation is derived from the Park's transformation by making  $\theta = 0$  in (2-8) (i.e.,  $\omega_s = 0$ ). The so-called stationary reference frame was used by Akagi *et al.* [6], [7] to generate the p-q theory as stated in [8] in order to design controllers for active power filters.

Fig. 2-10. a) Representation of the *abc* and the d-q variables. b) Representation of the *abc* and the  $\alpha-\beta$  variables

However, as stated in [9], working on the d-q synchronous-rotating reference frame gives more accurate results. The transformation of variables is an important mathematical technique that will be used to design the control algorithm of the UCSC system that will be presented in the following chapter.

### 2.5 Conclusions

An overview of power electronic concepts was presented in this chapter in order to provide the necessary background information to design the UCSC system. It was learned that depending on the flow of power, AC to DC side or DC- to AC side, power electronic converters can be classified into rectifiers and inverters, respectively. The type of converters that was chosen for the UCSC topology is the single-phase H-bridge VSC, which can operate as a rectifier and as an inverter. The reason for choosing the VSC is that it provides the capability of having independent control of the phase currents.

The control of an H-bridge was illustrated with a MATLAB/SIMULINK<sup>TM</sup> simulation and it was concluded that PI controllers work well with constant or slow variable signals. The concepts of the reference frame theory, Park's and Clarke's transformation was presented in order to address the control H-bridges in AC systems. Chapter 3 will focus on presenting the development of the UCSC system topology and control algorithm.

### 2.6 References

- [1] A. Yazdani, R. Iravani, <u>Voltage-Sourced Converters in Power Systems</u>. Hoboken, NJ: John Wiley & Sons, Inc., 2010.

- [2] N. Mohan, T. M. Undeland, W. P. Robbins, <u>Power Electronics Converters, Applications and Design</u>, third edition. Hoboken, NJ: John Wiley & Sons, Inc., 2003.

- [3] R.H. Park, "Two-Reaction theory of synchronous machines—generalized method of analysis—Part I," *AIEE Transactions*, vol. 48, pp. 716–727, July 1929.

- [4] P.C. Krause, O. Wasynczuk, S.D. Sudhoff, <u>Analysis of Electric Machinery and Drive Systems</u>, Third Edition. Somerset, NJ: Wiley, 2013.

- [5] W.C Duesterhoeft, M. W. Schulz, E. Clarke, "Determination of instantaneous currents and voltages by means of alpha, beta, and zero components," *Transactions of the American Institute of Electrical Engineers*, vol. 70, no. 2, pp. 1248–1255, July 1951.

- [6] H. Akagi, Y. Kanazawa, A. Nabae, "Generalized theory of the instantaneous reactive power in three-phase circuits," in *Proceedings of International Power Electronics Conference*, JIEE IPEC, pp. 1375–1386, Japan, 1983.

- [7] H. Akagi, Y. Kanazawa, A. Nabae, "Instantaneous reactive power compensators comprising switching devices without energy storage components." *IEEE Transactions on Industry Applications*, "vol. IA-20, no. 3, pp. 625–630, March, 1984.

- [8] S. L. Czarnecki, "Instantaneous reactive power p-q theory and power properties of three-phase systems," *IEEE Transactions on Power Delivery*, vol. 21, no. 1, pp.362–367, January, 2006.

- [9] M.G. Molina, P.E. Mercado, "Control design and simulation of DSTATCOM with energy storage for power quality improvements," *Transmission & Distribution Conference and Exposition: Latin America*, 2006, TDC '06. IEEE/PES, pp.1–7, August, 2006.

### **CHAPTER 3**

# UNBALANCED CURRENT STATIC COMPENSATOR: COMPONENTS AND CONTROL ALGORITHM

### 3.1 Introduction

The main objective of the UCSC system is to control the flow of currents in a three-phase four-wire distribution feeder at a selected point of common coupling (PCC) in such a way that the currents injected from the power substation are balanced in magnitude and in phase with their associated voltages. This objective is accomplished by having three single-phase H-Bridge converters that will control the flow of current for each phase independently.

The main components of the case study are described in the first part of the chapter and the control is given in the second part of the chapter. Appendix A.1 illustrates the MATLAB/SIMULINK<sup>TM</sup> models used for the single-phase  $\alpha - \beta/d - q$  transformation.

### 3.2 UCSC System Description

The case study of distribution system unbalanced loading was presented on section 1.3. As previously mentioned, the UCSC system is connected to a 34.5 kV three-phase four-wire distribution system. For ease of reference, Fig. 1-11 is here repeated as Fig. 3-1. The main components in Fig. 3-1 are the following:

### *a) Power substation* - The rated values are:

- Line-to-line rms voltage = 34.5 kV;

- Rated power = 6 MVA;

- Frequency = 60 Hz.

Fig. 3-1.One-line diagram for the UCSC case study

- b) Feeder impedances The impedances for segments 1 and 2 are calculated based on the characteristics of a 266,800 AWG aluminum cable from Table A.5 of [1]. These characteristics are the following:

- $r_a = 0.385 \Omega/mile$ ;

- $x_a = 0.465 \Omega/mile$ ;

- segment 1 distance = 0.621371 miles (1 km);

- segment 2 distance = 31.1 miles (50 km);

- pole configuration as per Fig. 3-2.

The positive-sequence impedance of segment 1 is calculated as follows [1]:

$$dp = (Dab \times Dbc \times Dca)^{1/3}$$

(3-1)

$$dp = \sqrt[3]{(46inches \times 86inches \times 132inches)} \times \frac{0.0833 \text{ ft}}{1 \text{ inch}}$$

(3-2)

$$dp = 6.71 \text{ ft}$$

(3-3)

$$X_{dp} = 0.05292 \log_{10} dp \ \Omega/1000 \text{ ft}$$

(3-4)

$$X_{dp} = 0.044 \,\Omega/1000 \text{ft}$$

(3-5)

Fig. 3-2. Pole configuration for segments 1 and 2 of the considered three-phase system [2]

$$Z_{segment1} = r_{ap} + j \left( x_a + x_{dp} \right) \Omega / 1000 ft$$

(3-6)

$$Z_{seament1} = 0.24 + j0.14 \Omega.$$

(3-7)

The same procedure is applied for the calculation of segment 2. The result is the following:

$$Z_{seament2} = 11.96 + j7.19 \Omega.$$

(3-8)

- c) System loads The system loads are aggregated and represented by of parallel resistors and inductors whose values are given in chapter 4.

- d) UCSC Coupling transformers The step-up distribution transformers have voltage ratings of 0.48 19.9 kV and the power capacity for the case study will be based on three single-phase 1 MVA transformers. The ratings were selected based on the current profile of Fig. 1-3 from section 1.3. Information about transformers that can be used for the UCSC system can be obtained from [3] and [4].

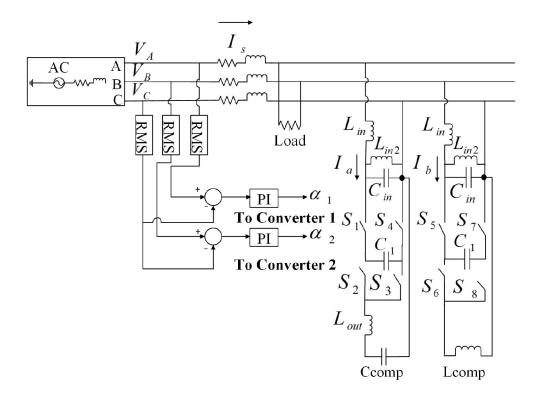

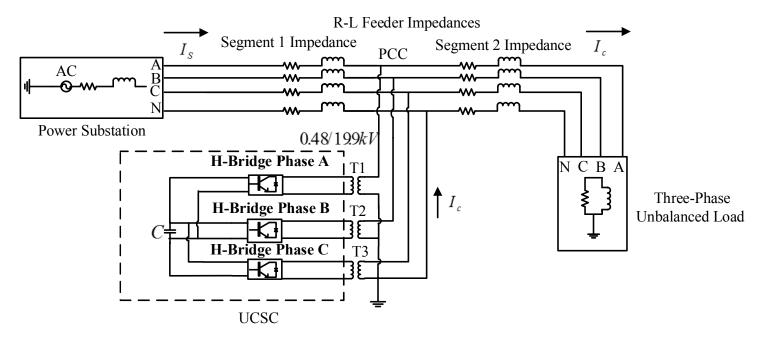

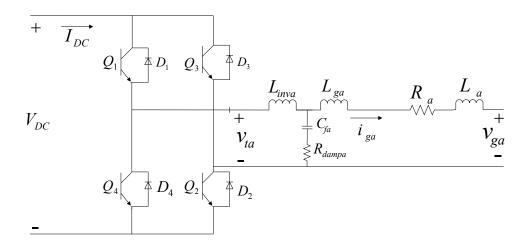

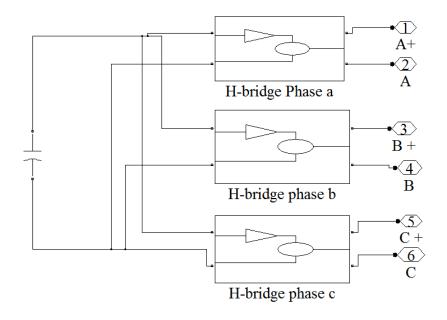

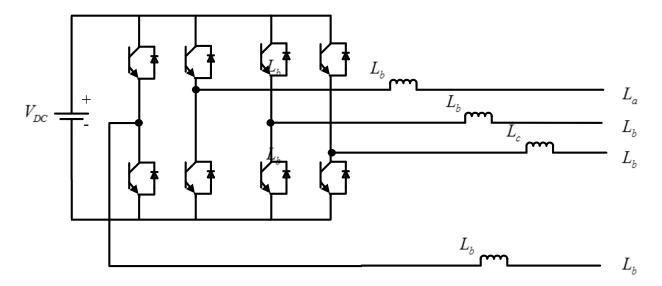

- e) UCSC system The main components which are depicted on Fig. 3-3 are:

- energy storage capacitor in the DC link;

- three single-phase H-Bridge converters;

- three LCL output filters.

### DC-Link Energy-Storage Capacitor

The capacitance is calculated using the following equation from [4]:

$$C_{DC} = \frac{I_2}{4\sqrt{2}(\Delta V_{dc}\%)V_{DC}f_{sw}}$$

(3-9)

where

- $\Delta V_{DC}$ % is the desired percentage DC-link voltage ripple;

- V<sub>DC</sub> is the rated DC-link voltage;

- I<sub>2</sub> is the peak AC-side current;

- f<sub>sw</sub> is the switching frequency.

The parameters to calculate the energy storage capacitor are illustrated in Table 3-1 and the criteria to select the DC-link voltage level and the switching frequency are the following:

- to avoid PWM over-modulation the DC-link voltage must satisfy  $V_{DC} \ge 2V_t$ ; where  $V_t$  is the terminal AC voltage depicted in Fig. 3-3. Over-modulation can increase the harmonics content in the output voltage [5], [6];

- the switching frequency  $f_{sw}$  should be less than 6 kHz to avoid high switching losses, or above 20 kHz to be outside the audible range [6];

- the modulation ratio  $mf = \left(\frac{f_{sw}}{f_1}\right)$  should be an even integer if possible [6].

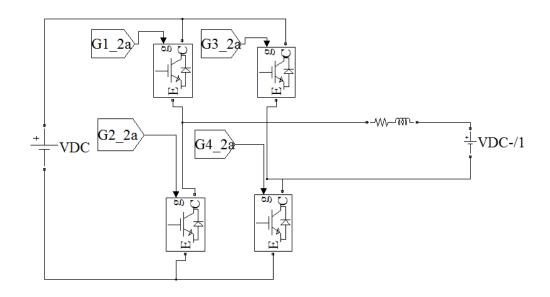

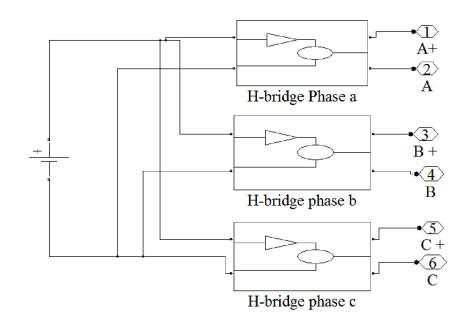

### Single-Phase H-Bridge Converters

The topology for each of the single-phase H-Bridge converters is illustrated in Fig. 3-4. Based on the specifications from Table 3-1, the semiconductor switching devices must have a maximum current capability of 2083 A or more for continuous current, with a DC voltage rating of 1400 V or more. Another important factor that must be taken into consideration when selecting the switching devices is the inrush current. According to [8], the inrush current in a

distribution system is not easy to determine due to the diversity of the loads but an estimation of 4 times the full load current  $(I_g)$  is a good approximation.

Fig. 3-3. Unbalanced current static compensator system

Table 3-1. UCSC system parameters

| Parameter                                 | Value |

|-------------------------------------------|-------|

| DC-link voltage level V <sub>DC</sub> (V) | 1400  |

| DC-link voltage ripple ΔV <sub>DC</sub> % | 1     |

| Switching frequency $f_{sw}$ (Hz)         | 5400  |

| UCSC voltage $V_t$ (V rms)                | 480   |

| Peak grid side current $I_2$ (A)          | 2945  |

| Rated Current Magnitude $I_g$ (A rms)     | 2083  |

| Energy storage capacitor $C_{DC}$ (mF)    | 4.90  |

The IGBT devices (CM2400HC-34N) from MITSUBISHI ELECTRIC<sup>®</sup> [9] are one of the options currently available to build the H-Bridge converters. The main parameters of the IGBT switches are illustrated in Table 3-2 [8]. A switch position will be realized by connecting 4 modules in parallel.

Fig. 3-4. UCSC single-phase H-Bridge converter topology schematic

Table 3-2. IGBT's parameters

| Parameter                                         | Value |

|---------------------------------------------------|-------|

| Collector Emitter Voltage V <sub>ce</sub> (V)     | 1700  |

| Collector Current I <sub>c</sub> (A)              | 2400  |

| Peak Collector Current I <sub>c</sub> (pulse) (A) | 4800  |

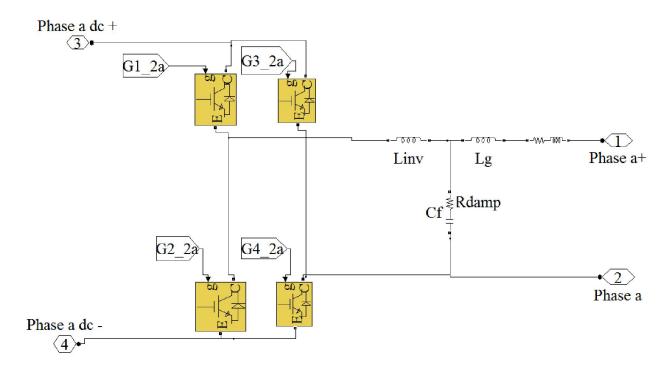

### LCL Output Filters

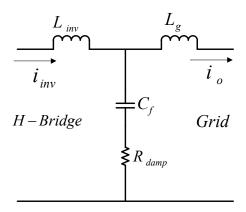

LCL filters were designed to improve the total harmonic distortion (THD) at the outputs of the H-Bridge converters. A schematic of one LCL filter is depicted in Fig. 3-5 where  $L_{inv}$ ,  $L_g$ , represent the inverter-side inductance, grid-side inductance and the filter's capacitance, respectively. The considerations for the design of the filter are [10], [11]:

• The value for the capacitor is restricted by a decrease of the power factor of no more than 5%. In this case a 2% value was chosen as suggested in [11]. The following equation gives the value of  $C_f$ .

$$C_f = 2\% \times \frac{S}{3 \times 2\pi f_1 V_{lg}^2}$$

(3-10)

where

- o S is the VSC rated power in kVA

- o  $f_1$  is the grid frequency

- o  $V_{lg}$  is the line to ground voltage in kV.

Fig. 3-5. LCL filter schematic

• The equation for selecting the value of the inverter-side inductance is:

$$\Delta i = \frac{V_{DC}}{8L_{inv}f_{sw}} \le 20\%I_n \tag{3-11}$$

where

- $\circ$   $\Delta i$  is the ripple current;

- o  $I_n$  is the rated current;

- o  $f_{sw}$  is the switching frequency.

- The grid-side inductance is related to the inverter-side inductance as follows [10]:

$$L_g = rL_{inv} (3-12)$$

where the constant r is calculated using the following:

$$\frac{i_o(h_s)}{i_{inv}(h_s)} = \frac{1}{\left|1 + r\left(1 - L_{inv}C_f(2\pi f_{sw})^2\right) \times 2\%\right|}$$

(3-13)

where  $i_o(h_s)$  and  $i_{inv}(h_s)$  are the output and inverter-ripple currents, respectively.

• The resonant frequency should comply with the following condition:

$$10f_1 \le f_{res} \le \frac{1}{2} f_{sw} \tag{3-14}$$

The value of the damping resistor (R<sub>damp</sub>) in series with the filter capacitor, can be calculated as follows [10]:

$$R_{damp} = \frac{1}{3 \times \omega_{res} \times C_f} \tag{3-15}$$

$$\omega_{res} = \sqrt{\frac{L_{inv} + L_g}{L_{inv} \times L_g \times C_f}}.$$

(3-16)

The calculated parameters values are given in Table 3-3. The table includes the values for the inductors, capacitors and resistors for each phase LCL filter.

Table 3-3. LCL filter parameters

| Parameter                     | Value             |

|-------------------------------|-------------------|

| $L_{inv}$ ( $\mu$ H)          | 73.33             |

| $L_g$ ( $\mu$ H)              | 40.65             |

| $C_f$ (mF)                    | 0.144 (12.5 kVAR) |

| $R_{damp}\left(\Omega\right)$ | 0.15              |

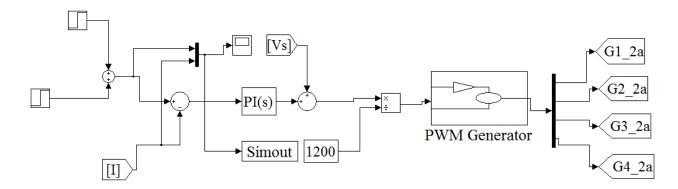

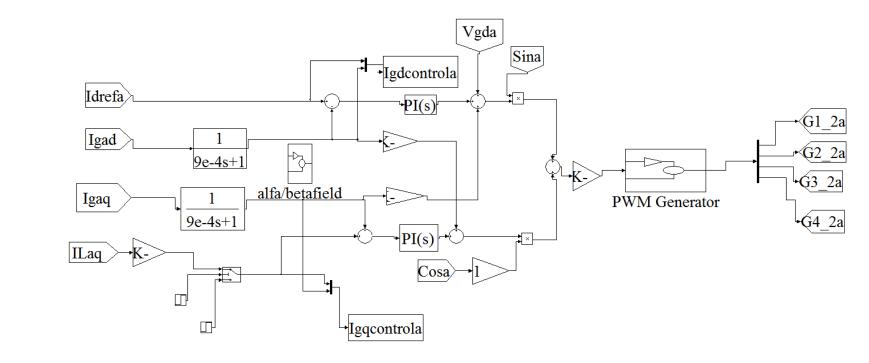

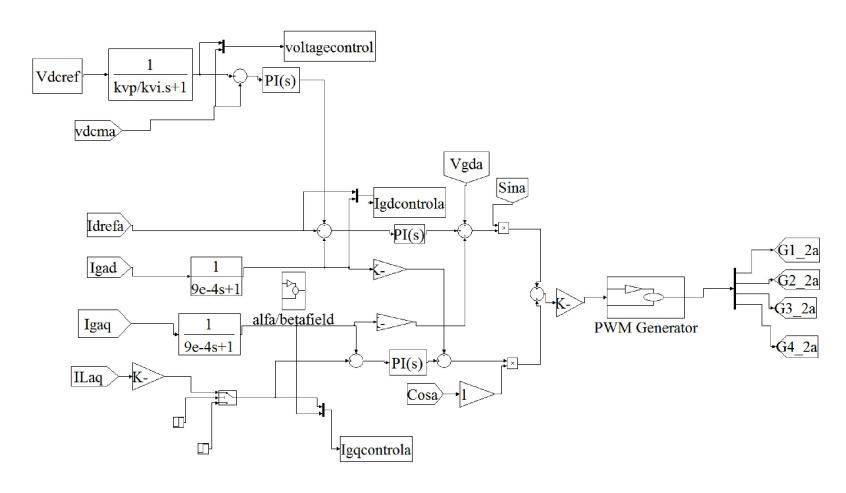

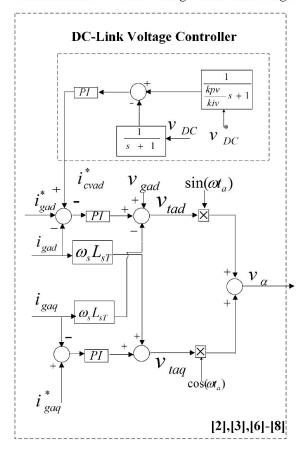

### 3.3 UCSC Control Algorithm

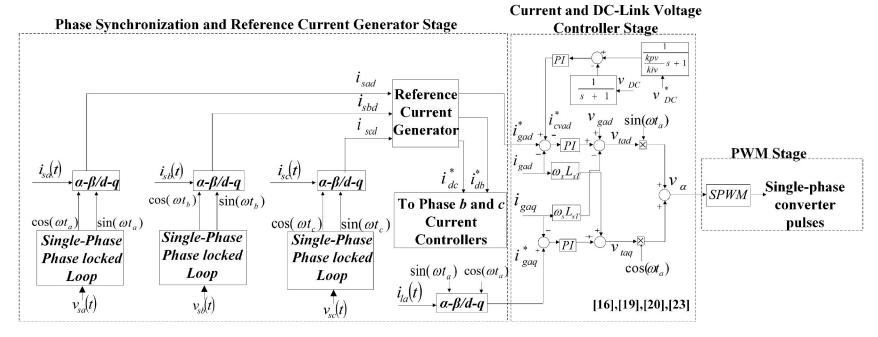

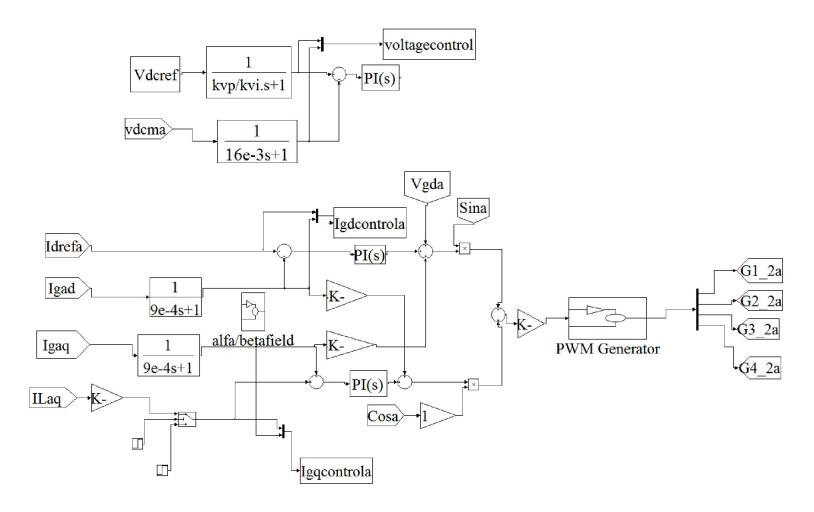

An overview of current controllers for single-phase H-Bridge converters, the reference frame theory, Park's and Clarke's transformation was presented in section 2.3 [12]-[15]. All of these concepts are used in the development of the UCSC control algorithm shown in Fig. 3-6.

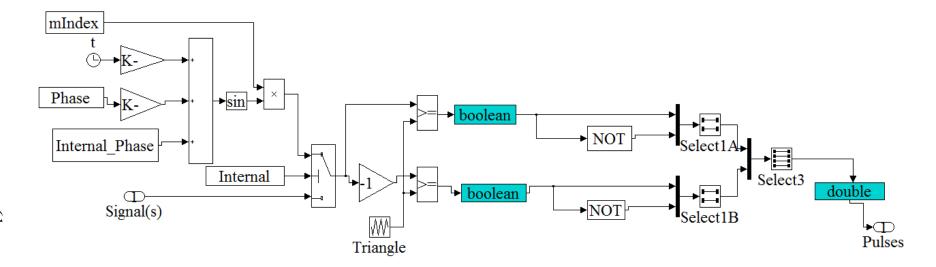

The algorithm is divided into three main stages:

- a) phase synchronization and reference current generator stage;

- b) current and DC-link voltage controller stage;

- c) PWM stage.

### a) Phase Synchronization and Reference Current Generator Stage

This stage has two objectives:

- to obtain the phase-angle from each phase voltage at the PCC.

- to generate the reference current inputs for each of the three single-phase H-Bridge converters current controllers;

Fig. 3-6. Multi-stage UCSC control algorithm block diagram

### Phase Synchronization

The phase synchronization process extracts the phase-angle from each phase voltage at the PCC through the single-phase phase-locked loop blocks that are depicted in Fig. 3-6. The phase-angle is used as the input signal for the  $\alpha - \beta / d - q$  and  $d - q / \alpha - \beta$  transformation blocks. By doing this, the output voltage generated by each single-phase H-Bridge converter of the UCSC system is in-phase with the corresponding grid voltage at the PCC.

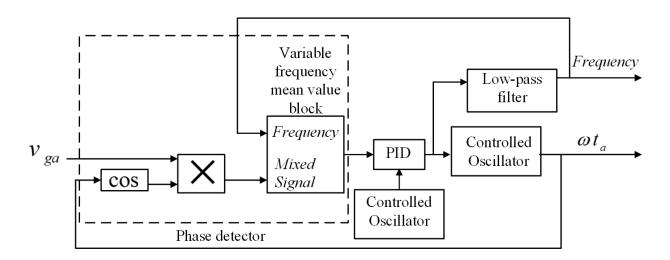

A typical single-phase phase-locked loop algorithm has three components and the algorithm used in the UCSC system is depicted in Fig. 3-7 [17], [18]. The phase-locked loop components are the following [17], [18]:

a phase detector that combines the input signal with the internal oscillator signal that

serves as the input for the variable frequency mean value block. The variable

frequency mean value block generates the DC component of the mixed signal that is

used as the input for the compensator block;

Fig. 3-7. Phase-locked control algorithm block [18]

- a compensator that can be a proportional-integral-derivative controller that generates the necessary inputs for the controlled oscillator and the low pass filter to keep the error signal or phase difference to 0;

- a controlled oscillator that generates the feedback signal for the phase detector.

### Reference Current Generation

As shown in Fig. 3-6, before the current inputs are fed into the reference current generator block, the phase currents must be transformed from the abc reference frame to the d-q reference frame.

As stated in [19], the transformation from the abc frame to the d-q frame is typical of three-phase systems. Because the UCSC control algorithm has been designed with three independent current controllers, one for each phase, the guidelines presented in [19] to perform the reference frame transformation from abc axes to the d-q axes must be followed.

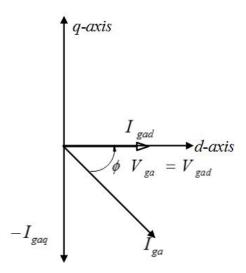

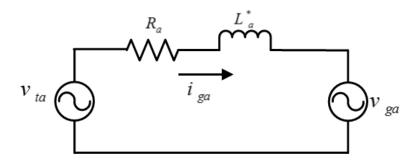

The "change-of-variable" transformation process starts by moving from the  $\alpha - \beta$  axes to the d-q axes for each phase. For phase a, the H-Bridge converter output current,  $i_{ga}$ , from Fig. 3-8, is the  $\alpha$  component and  $i_{ga}$  delayed by a quarter cycle (i.e., 90°) is the  $\beta$  component. The same concept can be applied to phases b and c [20], [21].

When the two orthogonal components have been defined, the  $\alpha - \beta/d - q$  transformation equations can be performed by applying the following equations [14]:

$$\begin{bmatrix} f_d \\ f_q \\ f_0 \end{bmatrix} = \begin{bmatrix} \sin(\theta) & -\cos(\theta) & 0 \\ \cos(\theta) & \sin(\theta) & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} f_\alpha \\ f_\beta \\ f_0 \end{bmatrix}$$

(3-17)

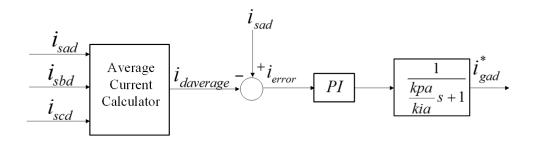

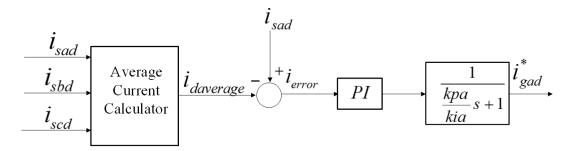

Once the phase currents are transformed from the  $\alpha - \beta$  axes to the d - q axes, the  $I_d$  currents for each phase enter the reference current generator block illustrated in Fig. 3-9 where the subscript "s" stands for source, "a", "b" and "c" for the grid phases and d for the direct axis.

Fig. 3-8. Phase *a* H-Bridge converter

Fig. 3-9. Phase a reference current generator block