## University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2014

# Fabrication of Single Nanowire Device using Electron Beam Lithography

Thach Pham University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the Nanoscience and Nanotechnology Commons, and the Nanotechnology Fabrication Commons

#### Recommended Citation

Pham, Thach, "Fabrication of Single Nanowire Device using Electron Beam Lithography" (2014). *Theses and Dissertations*. 2258. http://scholarworks.uark.edu/etd/2258

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

## Fabrication of Single Nanowire Device using Electron Beam Lithography

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

By

Thach Pham

University of Arkansas

Bachelor of Science in Electrical Engineering, 2011

May 2014 University of Arkansas

| This thesis is approved for recommendation to the Graduate Council. |                                   |  |  |  |  |

|---------------------------------------------------------------------|-----------------------------------|--|--|--|--|

|                                                                     |                                   |  |  |  |  |

|                                                                     |                                   |  |  |  |  |

|                                                                     |                                   |  |  |  |  |

| Dr. Shui-Qing (Fisher) Yu                                           |                                   |  |  |  |  |

| Thesis Director                                                     |                                   |  |  |  |  |

|                                                                     |                                   |  |  |  |  |

| Dr. Hameed Naseem                                                   | Dr. Vasundara Venkatraman Varadan |  |  |  |  |

| Committee Member                                                    | Committee Member                  |  |  |  |  |

#### Abstract

One dimensional nanostructure materials such as nanowires have drawn many interests among the scientific community for a wide range of applications such as field-effect transistors [1], [2], inverters[3], light-emitting diode [1], lasers [4], nanosensors [5], [6], and photodetectors [7]... Comparing with the characterization of nanowire arrays, characterizing a single nanowire will definitely provide a better understanding on new nanowire properties due to simplified behaviors of devices. Although promising theories could be drawn from those results, fabrication of test structure for single nanowire measurements cannot be easily processed using standard microfabrication techniques. Therefore, electron beam lithography integrated with photolithography technique has been used to manipulate the connection; which provides I-V characteristics, of single horizontal nanowire with a specific device. Single Si nanowire characterization could be extended to various materials for further studies.

In addition to single horizontal nanowire device, single vertical nanowire structure has been fabricated. Electron beam lithography technique is mainly used to pattern well-defined nanostructures where single ZnO nanowire is grown. Optical measurement, photoluminescence, is conducted to verify ZnO nanowires.

This thesis also emphasizes on fabrication process to pattern various structures such as lines, rings, and circles with different sizes from 1um to sub 100nm... They could be potential candidate to create nanodisk antenna (rings), fishnet structure (lines), and base to grown single nanowire (circle).

#### Acknowledgments

I would like to express my deep gratitude and my sincere thanks to my advisor, Dr. Shui-Qing (Fisher) Yu, who always supports and guides me patiently during my research time. He gave me good opportunity to study and work in fabrication area where I could be the best of me. I would like to thank Dr. Vasuran Varadan and Dr. Hammed Naseem to be part of my master committee members.

I am also grateful to my colleague, Liang Huang, for providing me useful suggestions and solutions for fabrication process. He is also a good friend and supporter. I thank Dr. Mourad Benamara from Nano Institute for teaching me to take quality SEM pictures.

Special thanks to Seyed Ghetmiri for the help in measuring photoluminescence, Matthew Young for the help in growing Si nanowires and depositing insulator layer SiO<sub>2</sub>, Yusuke Hirono for the help in studying surface roughness using AFM, and Yiyin Zhou for the help in cleaning mask.

I would like to thank my family who always support and colleagues and friends who make my time living in Fayetteville enjoyable. Special thanks to Dongsheng Fang for all the conversations he inspired me.

## Dedication

Students of University of Arkansas who have strong interest in fabrication process of single nanowire device could use this thesis as a reference.

## Table of Contents

## Abstract

## Acknowledgment

## Dedication

## List of Figures

## List of Tables

| СНАРТ  | ER 1: INTRODUCTION                                    | 1  |

|--------|-------------------------------------------------------|----|

| 1.1    | History of nanotechnology                             | 1  |

| 1.2    | From nanostructures to one-dimensional nanostructures | 1  |

| 1.3    | Thesis Outline                                        | 2  |

| СНАРТ  | ER 2: THEORY OF ELECTRON BEAM LITHOGRAPHY AND METAL   |    |

| SEMIC  | ONDUCTOR CONTACT                                      | 4  |

| 2.1 E  | lectron beam lithography                              | 4  |

| 2.1    | .1 Introduction                                       | 4  |

|        | .2 Principle of EBL                                   |    |

|        | .3 System overview                                    |    |

|        | .4 EOS                                                |    |

|        | .5 Stage driving system                               |    |

|        | .6 User interface                                     |    |

|        | letal semiconductor contacts                          |    |

|        | .1 Schottky contact                                   |    |

|        | .2 Ohmic contact                                      |    |

| CHAPT  | ER 3: FABRICATION OF METALLIC NANOSTRUCTURES          | 20 |

| 3.1 In | troduction                                            | 20 |

| 3.2 Fa | abrication process                                    | 20 |

| 3.2    | .1 Traveler preparation                               | 23 |

|        | .2 Structure design                                   |    |

| 3.2    | .3 Substrate preparation                              | 27 |

|        | .4 Electron beam lithography writing                  |    |

|        | .5 Metal deposition & Lift off                        |    |

| 3.3 S  | EM pictures of metallic nanostructures                | 46 |

## CHAPTER 4: FABRICATION AND CHARACTERIZATION OF HORIZONTAL SINGLE Si

| NANOWIRES DEVICE                                                         | 56  |

|--------------------------------------------------------------------------|-----|

| 4.1 Introduction                                                         | 56  |

| 4.2 Fabrication process of horizontal single Si nanowires device         | 57  |

| 4.2.1 Processing flow                                                    | 59  |

| 4.2.2 Mask design                                                        |     |

| 4.2.3 Platform preparation                                               |     |

| 4.2.4 Nanowires deposition & localization                                |     |

| 4.2.5 Bridge design                                                      |     |

| 4.2.6 EBL alignment & writing                                            | 75  |

| 4.2.7 Metal deposition & lift off                                        | 82  |

| 4.3 SEM pictures of single horizontal Si nanowires device                | 83  |

| 4.4 Current-voltage measurement of single horizontal Si nanowires device | 87  |

| 4.4.1 Measurement setup                                                  | 87  |

| 4.4.2 Measurement results and discussions                                | 88  |

| CHAPTER 5: FABRICATION AND CHARACTERIZATION OF VERTICAL SIN              |     |

| NANOWIRES STRUCTURE                                                      | 94  |

| 5.1 Introduction                                                         | 94  |

| 5.2 Fabrication process of vertical single nanowires structure           | 94  |

| 5.2.1 Processing flow                                                    | 96  |

| 5.2.2 Platform preparation                                               |     |

| 5.2.3 ZnO nanowires growth                                               | 103 |

| 5.2.4 Resist strip                                                       | 103 |

| 5.3 SEM pictures of single ZnO nanowire                                  | 104 |

| 5.4 Photoluminescence measurement of single ZnO nanowire                 | 106 |

| CHAPTER 6: CONCLUSION                                                    | 109 |

| Pafarancas                                                               | 111 |

## List of Figures

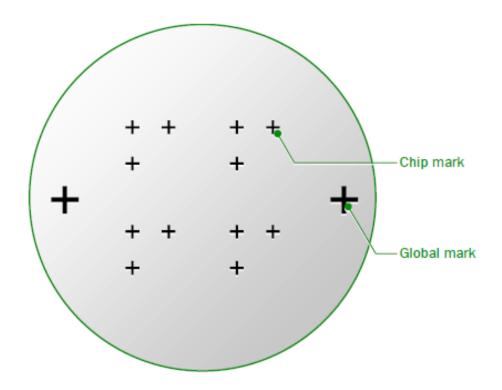

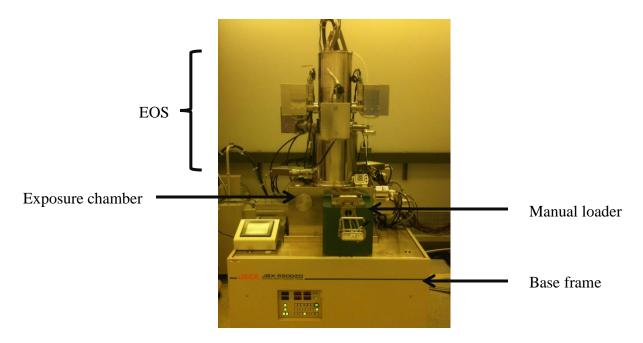

| Figure 2.1 EBL JEOL 5500ZD system (HiDEC cleanroom, University of Arkansas)             |

|-----------------------------------------------------------------------------------------|

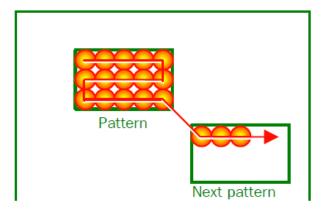

| Figure 2.2 Vector scanning method                                                       |

| Figure 2.3 Step and repeat method                                                       |

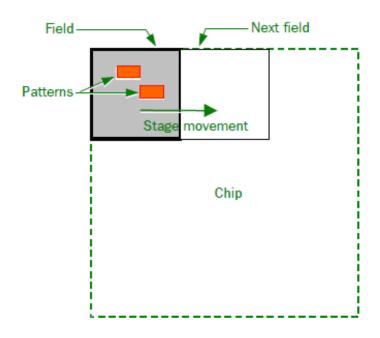

| Figure 2.4 Global marks (PQ) and chip marks                                             |

| Figure 2.5 EBL main console                                                             |

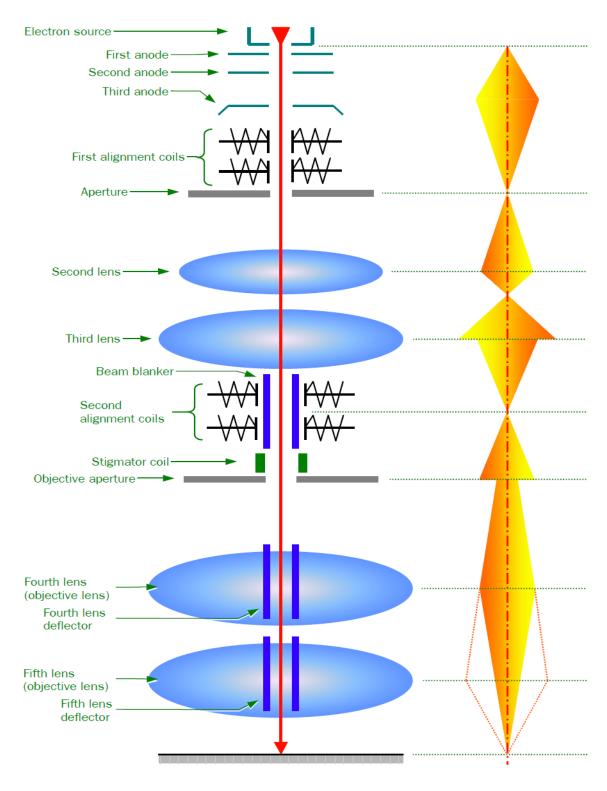

| Figure 2.6 Electrons optics system                                                      |

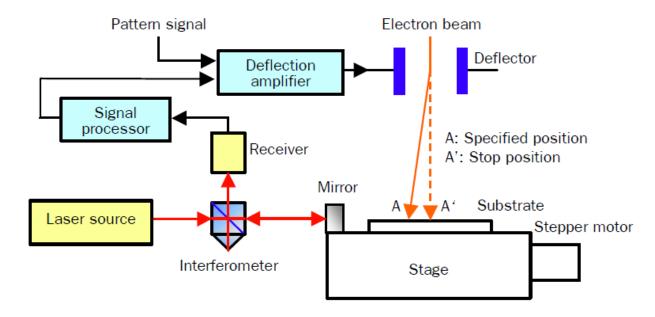

| Figure 2.7 Moving stage system                                                          |

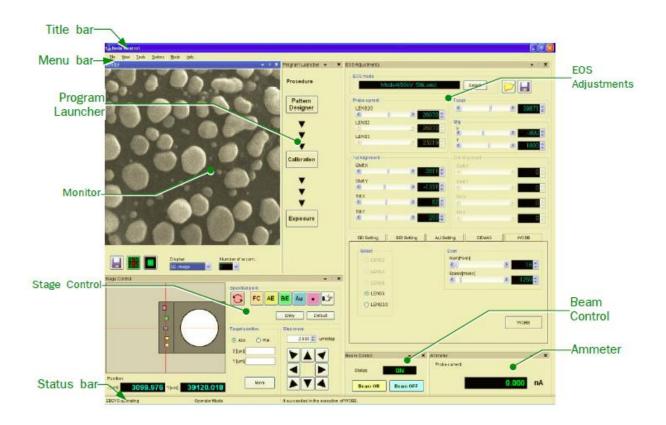

| Figure 2.8 Main interface                                                               |

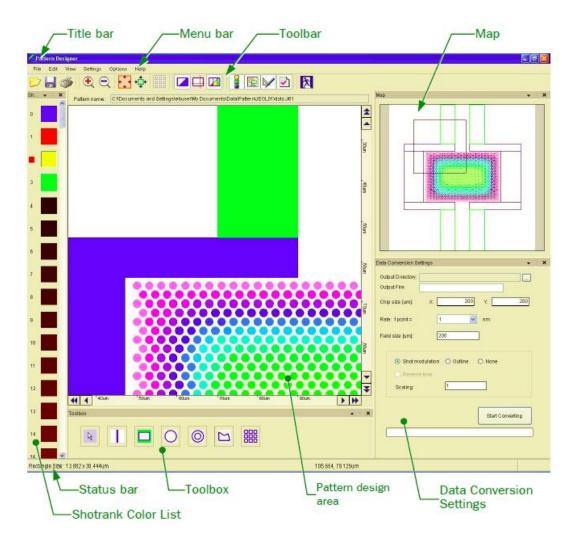

| Figure 2.9 Pattern designer interface14                                                 |

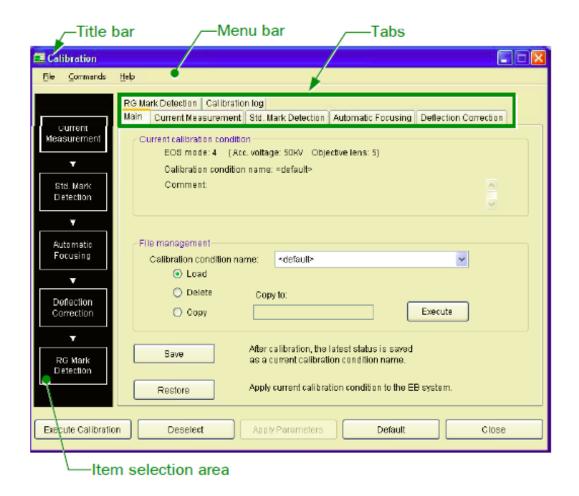

| Figure 2.10 Calibration interface                                                       |

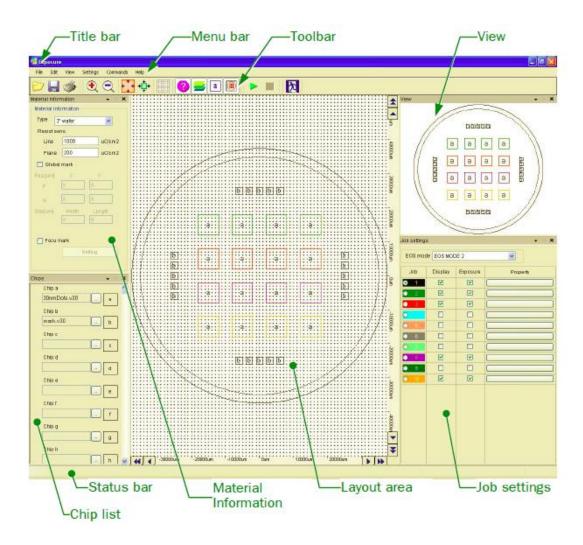

| Figure 2.11 Exposure interface                                                          |

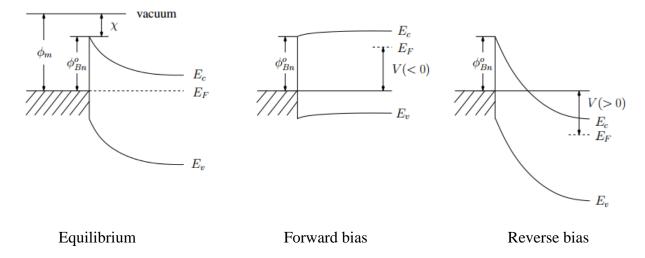

| Figure 2.12 Band diagram of ideal metal n-type semiconductor contact under equilibrium, |

| forward bias, and reverse bias condition                                                |

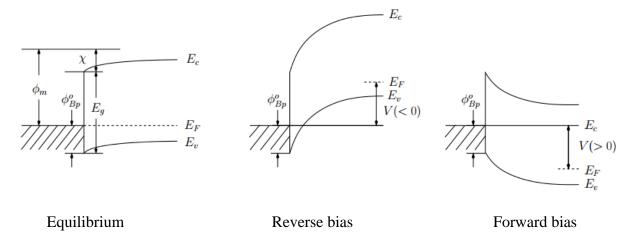

| Figure 2.13 Band diagram of ideal metal p-type semiconductor contact under equilibrium, |

| forward bias, and reverse bias condition                                                |

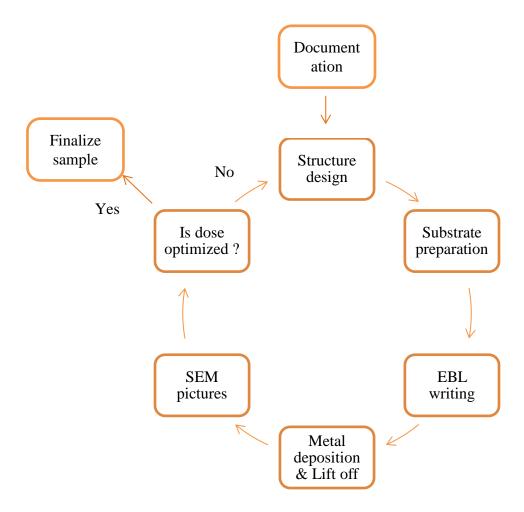

| Figure 3.1 Process flow of metallic nanostructures fabrication                          |

| Figure 3.2 (a) CAD design 5x5 arrays of different doses24                               |

| Figure 3.2 (b) Zoom in CAD design 5x5 arrays of different doses                         |

| Figure 3.3 (a) SEM pictures of metalized 5x5 arrays design                              |

| Figure 3.3 (b) Zoom in SEM picture of metalized single array design                     |

| Figure 3.4 CAD design single array covering 1mm <sup>2</sup> area                       |

| Figure 3.5 (a) Convert dwg file into dxf file in Auto CAD                               |

| Figure 3.5 (b) Convert dxf file into gdsii file in LinkCAD.        | 26 |

|--------------------------------------------------------------------|----|

| Figure 3.5 (c) Convert gdsii file into v30 file in Pattern Design. | 26 |

| Figure 3.6 Nanospec                                                | 28 |

| Figure 3.7 Dektak                                                  | 28 |

| Figure 3.8 (a) Front side of 4" cassette                           | 30 |

| Figure 3.8 (b) Back side of 4" cassette                            | 30 |

| Figure 3.9 (a) Front side of 2" cassette                           | 30 |

| Figure 3.9 (b) Back side of 2" cassette                            | 30 |

| Figure 3.10 (a) Front side of piece cassette                       | 31 |

| Figure 3.10 (b) Back side of piece cassette                        | 31 |

| Figure 3.11 (a) Back side of loaded piece cassette                 | 32 |

| Figure 3.11 (b) Front side of loaded piece cassette                | 32 |

| Figure 3.12 Flow of basic adjustment                               | 33 |

| Figure 3.13 Beam current vs. beam diameter                         | 34 |

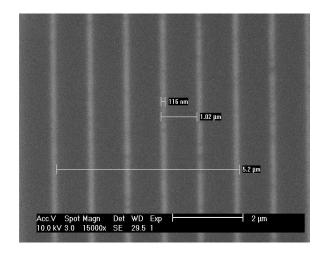

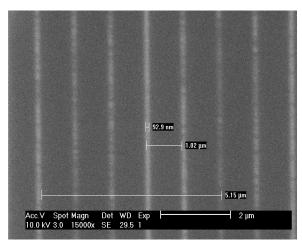

| Figure 3.14 (a) Line width of 116nm, pitch size of 1um             | 37 |

| Figure 3.14 (b) Line width of 93nm, pitch size of 1um              | 37 |

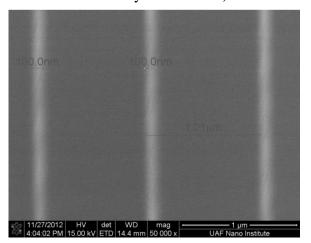

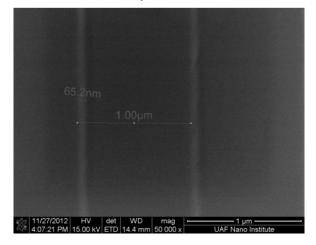

| Figure 3.15 (a) Line width of 100nm, pitch size of 1um             | 37 |

| Figure 3.15 (b) Line width of 65nm, pitch size of 1um              | 37 |

| Figure 3.16 Thermal evaporator Edward 306T                         | 41 |

| Figure 3.17 (a) SEM picture of metalized line with high roughness  | 43 |

| Figure 3.17 (b) SEM picture of metalized line with high roughness  | 43 |

| Figure 3.18 (a) AFM surface geometry of multiple lines             | 43 |

| Figure 3.18 (b) AFM surface geometry of single line                | 43 |

|                                                                    |    |

| Figure 3.19 (a) AFM data, metal thickness of multiple lines                  | 44 |

|------------------------------------------------------------------------------|----|

| Figure 3.19 (b) AFM data, metal thickness of single line                     | 44 |

| Figure 3.20 Thick layer of metal prevents PG remover to attack e-beam resist | 45 |

| Figure 3.21 (a) SEM picture of ring structure where lift off fails           | 45 |

| Figure 3.21 (b) Zoom in SEM picture of ring structure where lift off fails   | 45 |

| Figure 3.22 Reduce metal layer for rings structure                           | 46 |

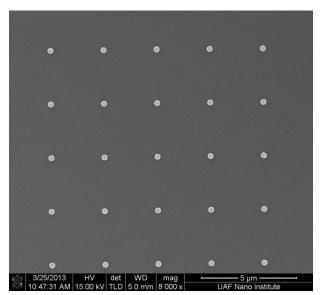

| Figure 3.23 (a) SEM picture of circles having diameter of 1um                | 46 |

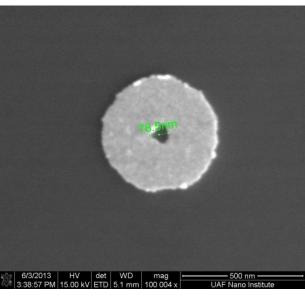

| Figure 3.23 (b) Zoom in SEM picture of 1um circle structure                  | 46 |

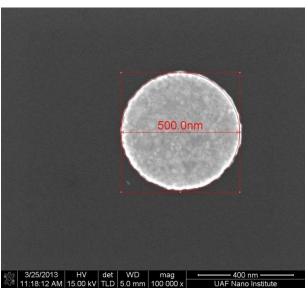

| Figure 3.24 (a) SEM picture of circles having diameter of 500nm              | 47 |

| Figure 3.24 (b) Zoom in SEM picture of 500nm circle structure                | 47 |

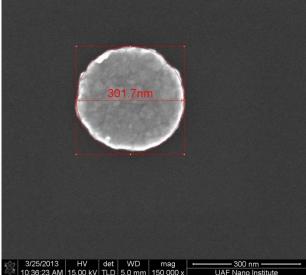

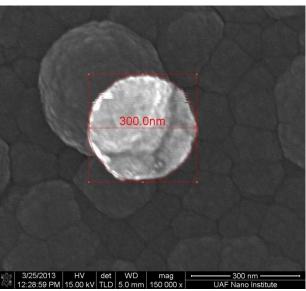

| Figure 3.25 (a) SEM picture of circles having diameter of 300nm              | 47 |

| Figure 3.25 (b) Zoom in SEM picture of 300nm circle structure                | 47 |

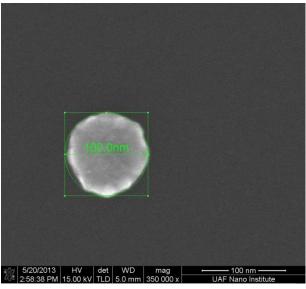

| Figure 3.26 (a) SEM picture of circles having diameter of 100nm              | 48 |

| Figure 3.26 (b) Zoom in SEM picture of 100nm circle structure                | 48 |

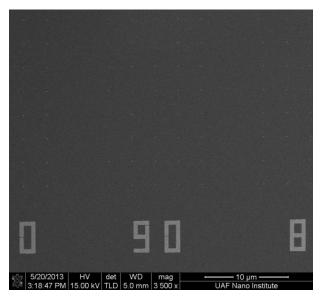

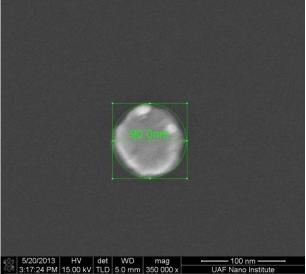

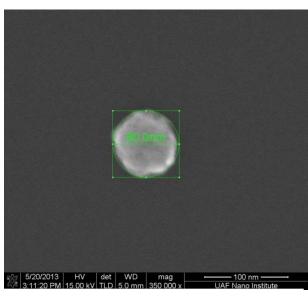

| Figure 3.27 (a) SEM picture of circles having diameter of 90nm               | 48 |

| Figure 3.27 (b) Zoom in SEM picture of 90nm circle structure                 | 48 |

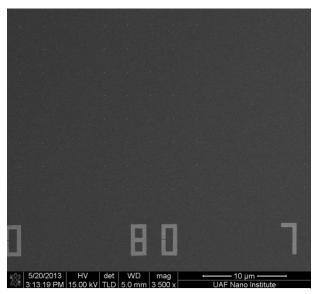

| Figure 3.28 (a) SEM picture of circles having diameter of 80nm               | 49 |

| Figure 3.28 (b) Zoom in SEM picture of 80nm circle structure                 | 49 |

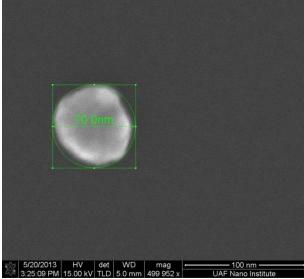

| Figure 3.29 (a) SEM picture of circles having diameter of 300nm              | 49 |

| Figure 3.29 (b) Zoom in SEM picture of 300nm circle structure                | 49 |

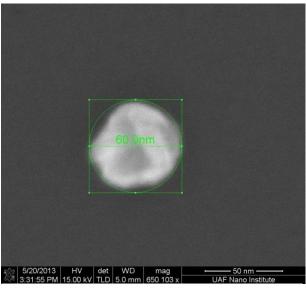

| Figure 3.30 (a) SEM picture of circles having diameter of 60nm               | 50 |

| Figure 3.30 (b) Zoom in SEM picture of 60nm circle structure                 | 50 |

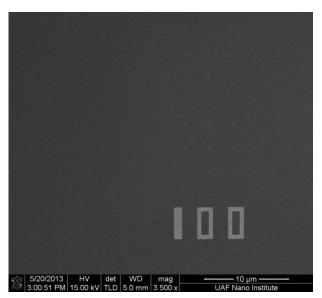

| Figure 3.31 (a) SEM picture of testing layout on a-Si substrate              | 50 |

| Figure 3.31 (b) Zoom in SEM picture of 1um circle structure on a-Si substrate   | 50 |

|---------------------------------------------------------------------------------|----|

| Figure 3.32 (a) Zoom in SEM picture of 500nm circle structure on a-Si substrate | 51 |

| Figure 3.32 (b) Zoom in SEM picture of 300nm circle structure on a-Si substrate | 51 |

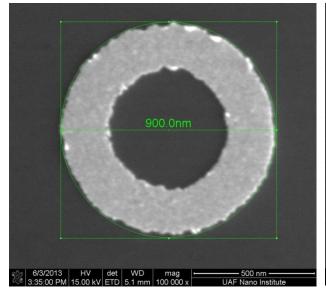

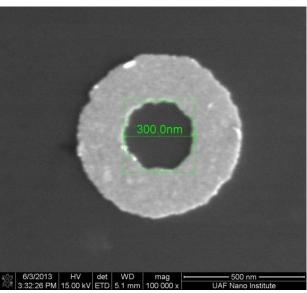

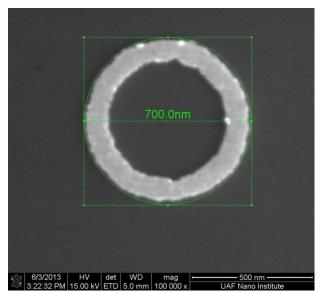

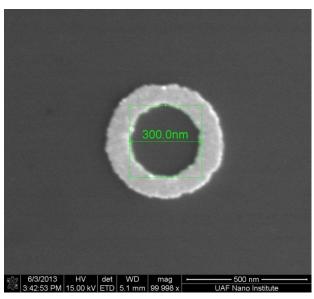

| Figure 3.33 (a) Zoom in SEM picture of ring structure, outer diameter 900nm     | 51 |

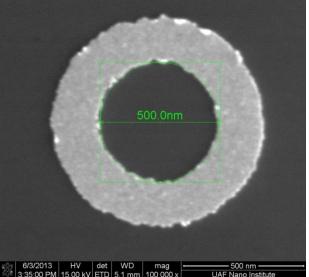

| Figure 3.33 (b) Zoom in SEM picture of ring structure, inner diameter 500nm     | 51 |

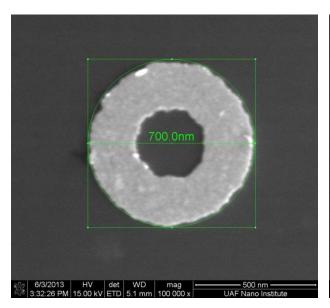

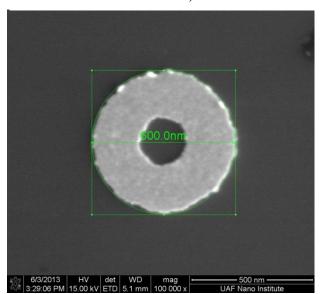

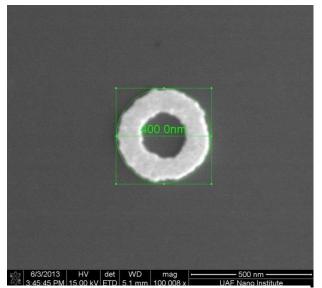

| Figure 3.34 (a) Zoom in SEM picture of ring structure, outer diameter 700nm     | 52 |

| Figure 3.34 (b) Zoom in SEM picture of ring structure, inner diameter 300nm     | 52 |

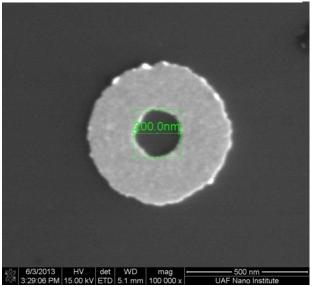

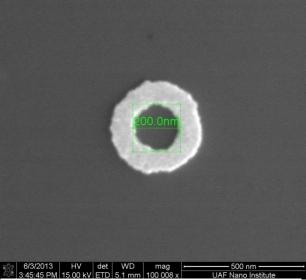

| Figure 3.35 (a) Zoom in SEM picture of ring structure, outer diameter 600nm     | 52 |

| Figure 3.35 (b) Zoom in SEM picture of ring structure, inner diameter 200nm     | 52 |

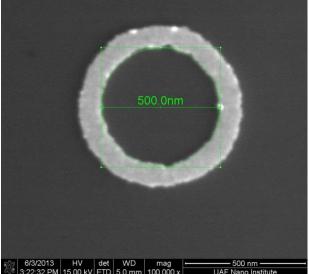

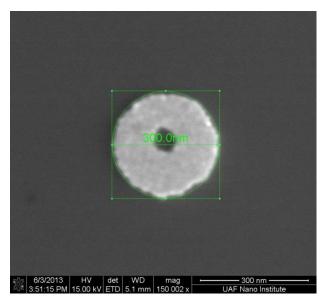

| Figure 3.36 (a) Zoom in SEM picture of ring structure, outer diameter 500nm     | 53 |

| Figure 3.36 (b) Zoom in SEM picture of ring structure, inner diameter 78nm      | 53 |

| Figure 3.37 (a) Zoom in SEM picture of ring structure, outer diameter 700nm     | 53 |

| Figure 3.37 (b) Zoom in SEM picture of ring structure, inner diameter 500nm     | 53 |

| Figure 3.38 (a) Zoom in SEM picture of ring structure, outer diameter 500nm     | 54 |

| Figure 3.38 (b) Zoom in SEM picture of ring structure, inner diameter 300nm     | 54 |

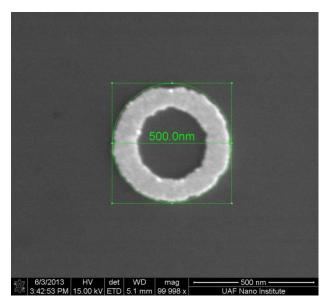

| Figure 3.39 (a) Zoom in SEM picture of ring structure, outer diameter 400nm     | 54 |

| Figure 3.39 (b) Zoom in SEM picture of ring structure, inner diameter 200nm     | 54 |

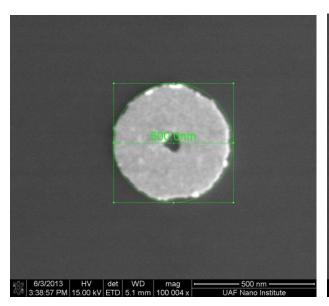

| Figure 3.40 (a) Zoom in SEM picture of ring structure, outer diameter 300nm     | 55 |

| Figure 3.40 (b) Zoom in SEM picture of ring structure, inner diameter 69nm      | 55 |

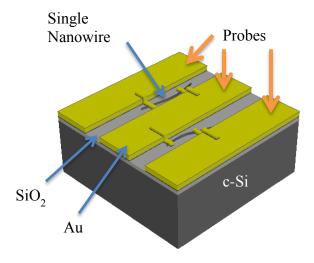

| Figure 4.1 3D module of single horizontal nanowires device                      | 56 |

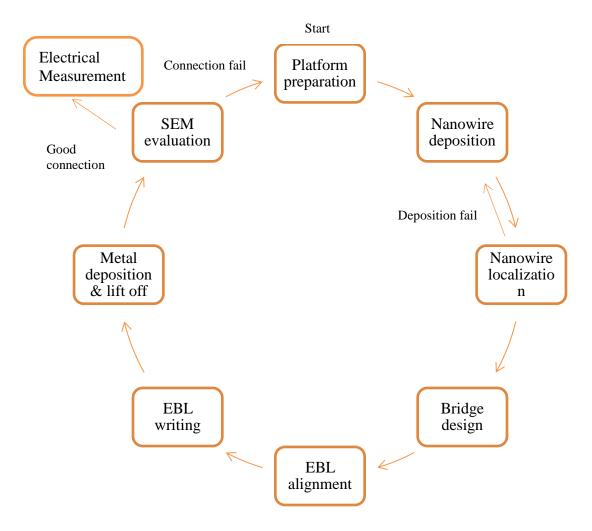

| Figure 4.2 Flow of main fabrication processes                                   | 57 |

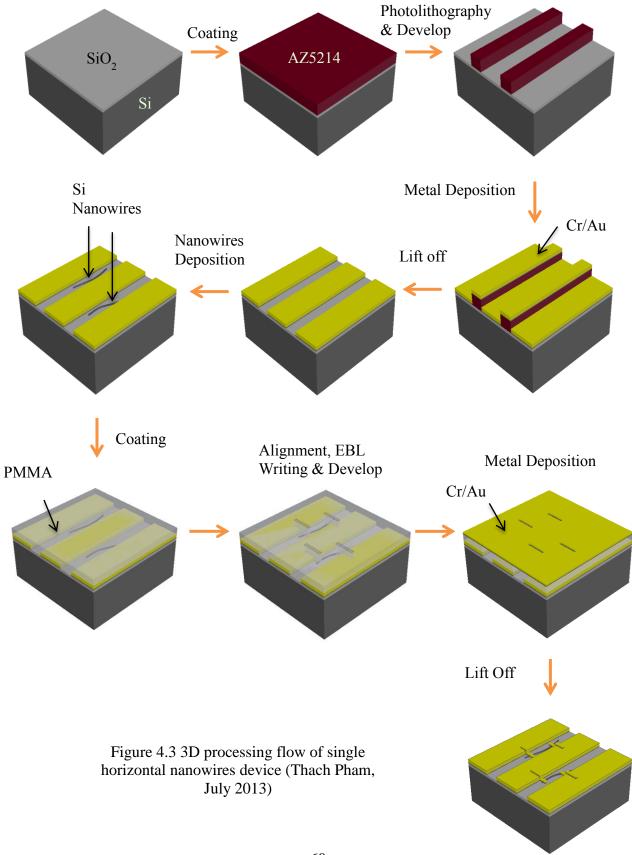

| Figure 4.3 3D processing flow of single horizontal nanowires device             | 60 |

| Figure 4.4 (a) An array of metalized platform                                   | 61 |

| Figure 4.4 (b) Single metalized platform                                   | 61 |

|----------------------------------------------------------------------------|----|

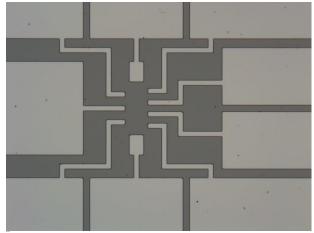

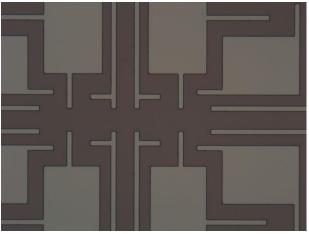

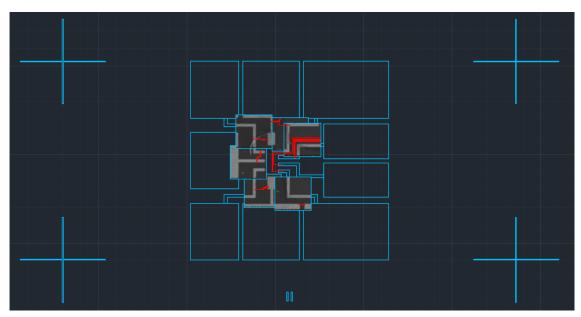

| Figure 4.5 (a) CAD file of 1 <sup>st</sup> design                          | 63 |

| Figure 4.5 (b) Zoom in of single platform in CAD                           | 63 |

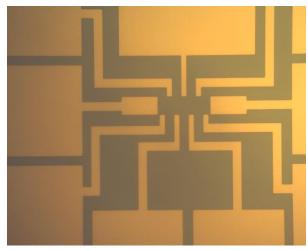

| Figure 4.6 (a) CAD file of 2 <sup>nd</sup> design                          | 64 |

| Figure 4.6 (b) Zoom in of single platform in CAD                           | 64 |

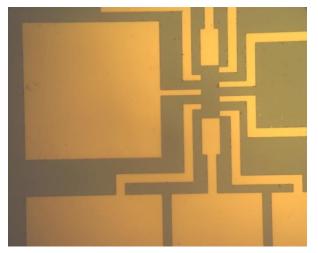

| Figure 4.7 (a) 1 <sup>st</sup> design structure after develop              | 66 |

| Figure 4.7 (b) 2 <sup>nd</sup> design structure after develop              | 66 |

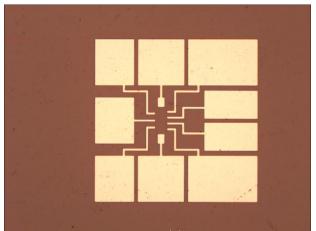

| Figure 4.8 (a) 1 <sup>st</sup> design structure after lift off             | 67 |

| Figure 4.8 (b) 2 <sup>nd</sup> design structure after lift off             | 67 |

| Figure 4.9 (a) Mask before cleaning                                        | 69 |

| Figure 4.9 (b) Mask after cleaning                                         | 69 |

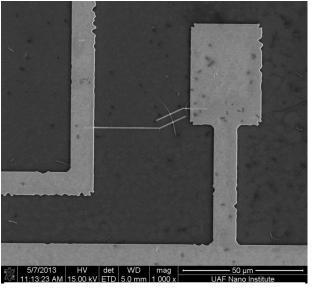

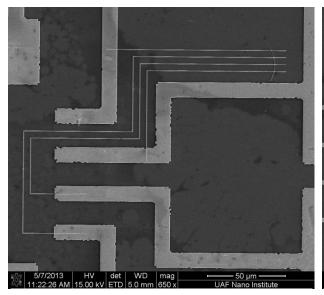

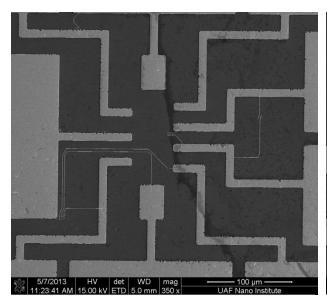

| Figure 4.10 (a) Good nanowires position on 1 <sup>st</sup> design platform | 71 |

| Figure 4.10 (b) Good nanowires position on 2nd design                      | 71 |

| Figure 4.11 (a) Bridge design in CAD platform                              | 74 |

| Figure 4.11 (b) Zoom in bridge design in CAD                               | 74 |

| Figure 4.12 Final plot of bridge design                                    | 75 |

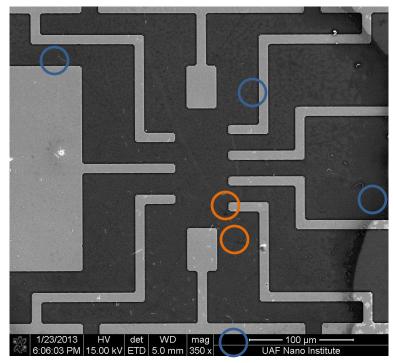

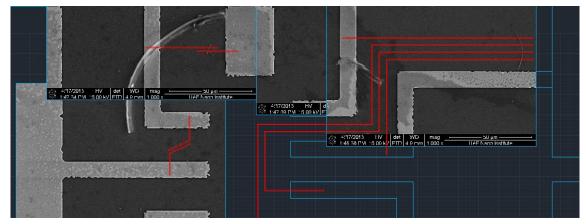

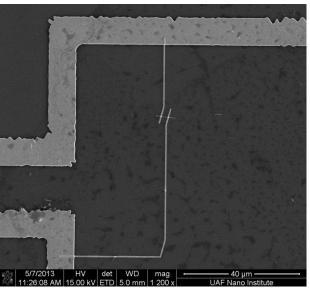

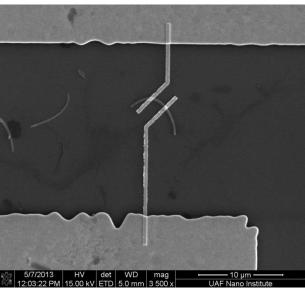

| Figure 4.13 Map layout of platform 11                                      | 83 |

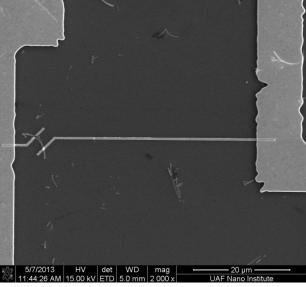

| Figure 4.14 Two connections structure, platform 11                         | 83 |

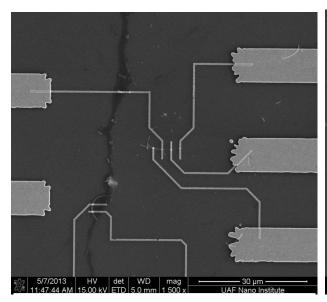

| Figure 4.15 (a) Four connections structure, platform 11                    | 83 |

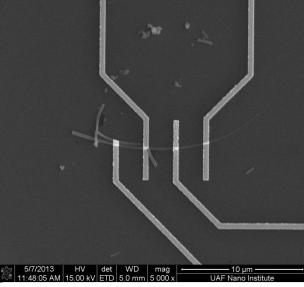

| Figure 4.15 (b) Zoom in four connections structure, platform 11            | 83 |

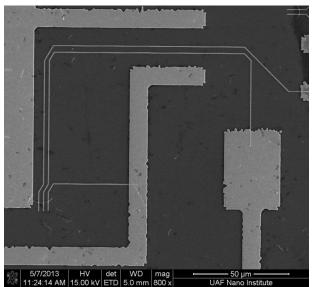

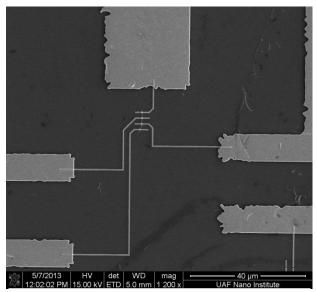

| Fig 4.16 Map layout of platform 13                                         | 84 |

| Fig 4.17 Two connections structure, platform 13                            | 84 |

| Fig 4.18 (a) Four connections structure, platform 13                       | 84 |

| Fig 4.18 (b) Zoom in four connections structure, platform 13                                                                      | 84           |

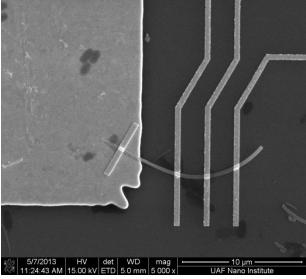

|-----------------------------------------------------------------------------------------------------------------------------------|--------------|

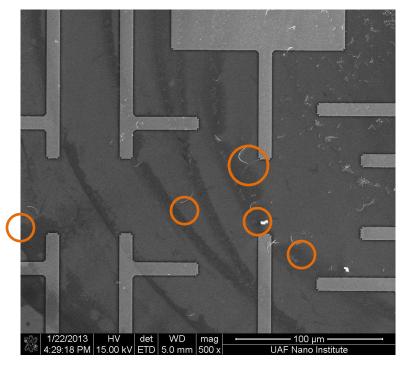

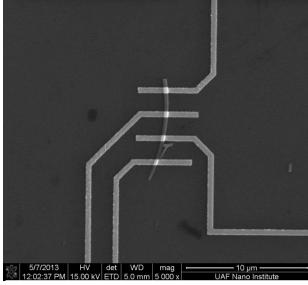

| Fig 4.19 Map layout of platform 32                                                                                                | 85           |

| Fig 4.20 Two connections structure, platform 32                                                                                   | 85           |

| Fig 4.21 (a) Four connections structure, platform 32                                                                              | 85           |

| Fig 4.21 (b) Zoom in four connections structure, platform 32                                                                      | 85           |

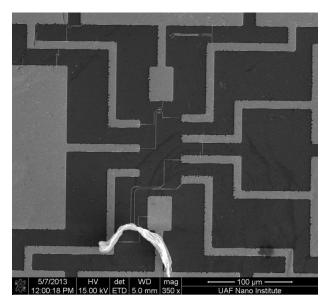

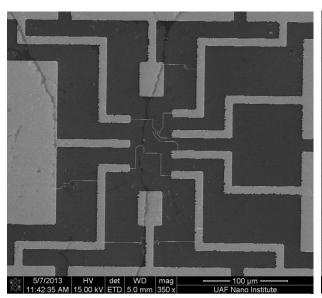

| Fig 4.22 Map layout of platform 41                                                                                                | 86           |

| Fig 4.23 Two connections structure, platform 41                                                                                   | 86           |

| Fig 4.24 (a) Four connections structure, platform 41                                                                              | 86           |

| Fig 4.24 (b) Zoom in four connections structure, platform 41                                                                      | 86           |

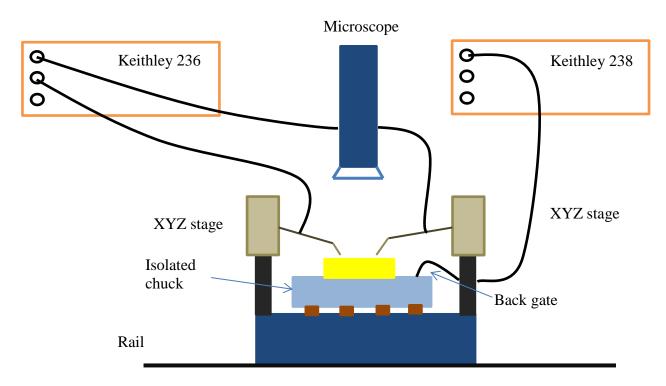

| Fig 4.25 The instruments setup for I-V measurement                                                                                | 87           |

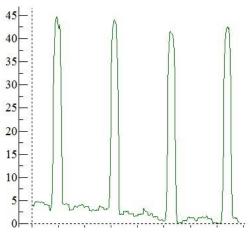

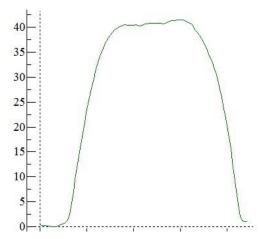

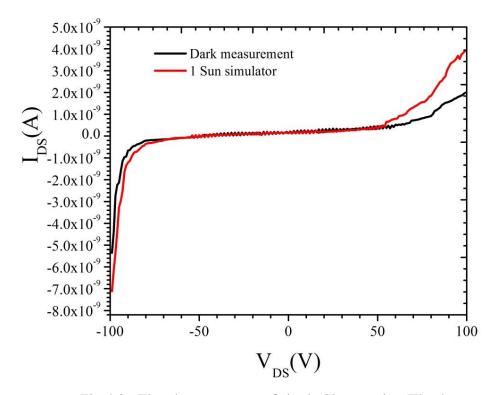

| Fig 4.26 The photoresponse of single Si nanowire                                                                                  | 88           |

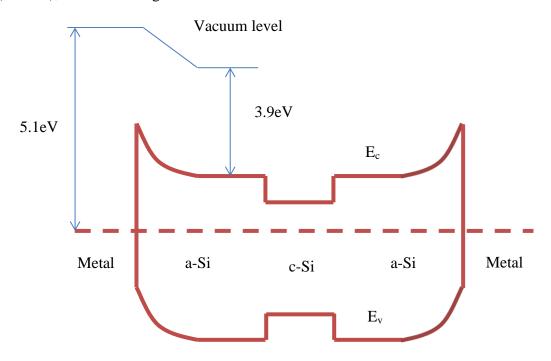

| Fig 4.27 Band gap diagram at two terminals                                                                                        | 89           |

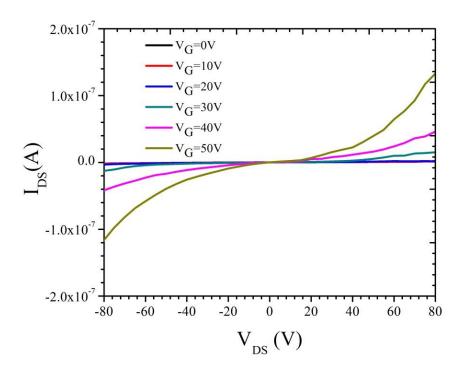

| Fig 4.28 $I_D$ - $V_{DS}$ characteristic curves as a function of $V_G$ of 0V, 10V, 20V, 20V, 30V, 30V, 30V, 30V, 30V, 30V, 30V, 3 | 0V, 40V, and |

| 50V                                                                                                                               | 91           |

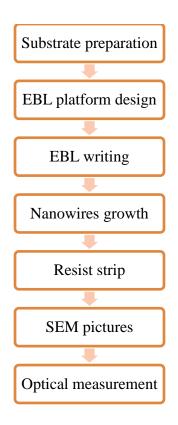

| Fig 5.1 Flow of critical fabrication processes                                                                                    | 95           |

| Fig 5.2 3D processing flow of single vertical nanowire structure                                                                  | 97           |

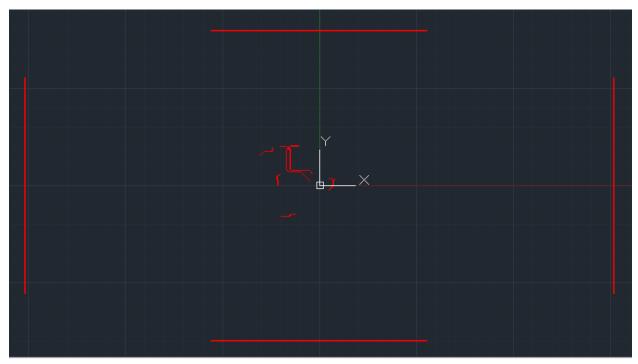

| Fig 5.3 Map layout of 1 <sup>st</sup> design                                                                                      | 101          |

| Fig 5.4 Map layout of 2 <sup>nd</sup> design                                                                                      | 102          |

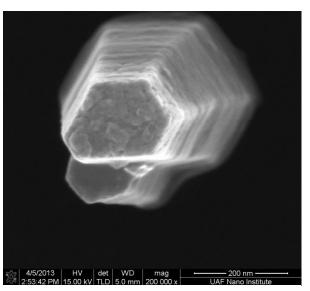

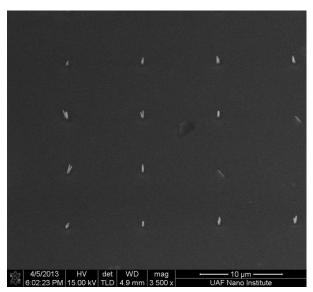

| Fig 5.5 Field of ZnO nanowires, top view                                                                                          | 104          |

| Fig 5.6 Two ZnO nanowires grown on same base                                                                                      | 104          |

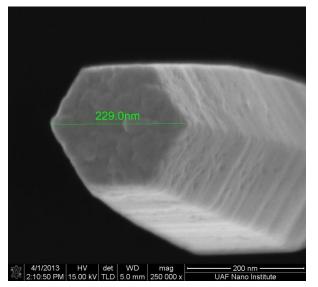

| Fig 5.7 Single ZnO nanowire with top diameter of 229nm, top view                                                                  | 104          |

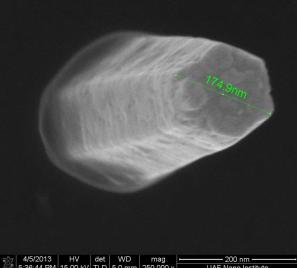

| Fig 5.8 Single ZnO nanowire with top diameter of 175nm, top view                                                                  | 104          |

| Fig 5.9 Field of ZnO nanowires after resist removal, 45° tilted                                                                   | 105          |

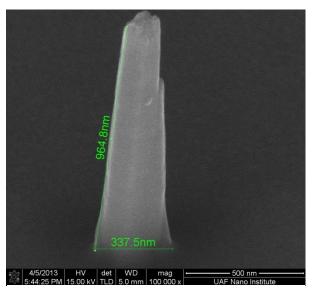

| Fig 5.10 Single ZnO nanowire with 965nm length after resist removal, 45° tilted | 105 |  |

|---------------------------------------------------------------------------------|-----|--|

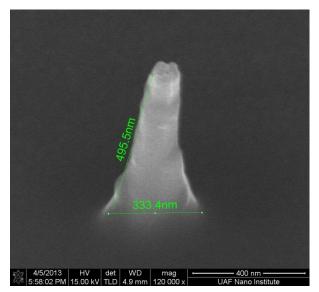

| Fig 5.11 Single ZnO nanowire with 495nm length after resist removal, 45° tilted | 105 |  |

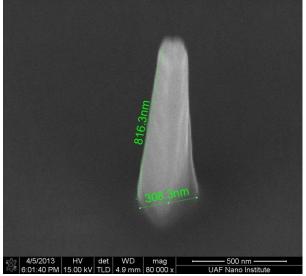

| Fig 5.12 Single ZnO nanowire with 816nm length after resist removal, 45° tilted | 105 |  |

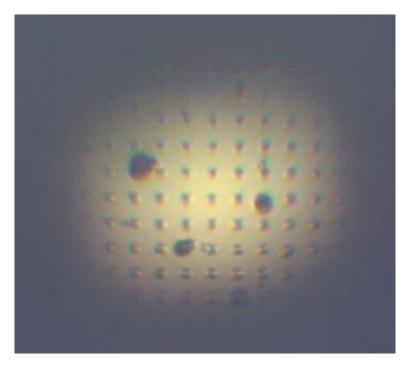

| Fig 5.13 Camera picture of single ZnO nanowires                                 | 106 |  |

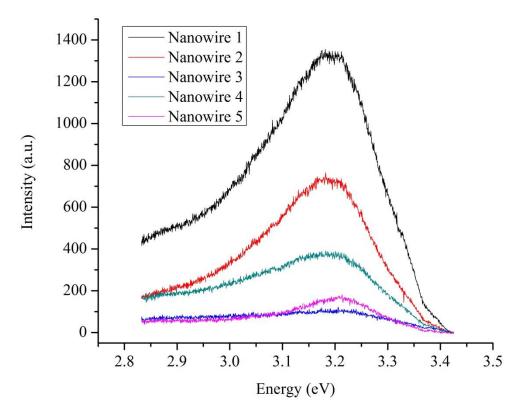

| Fig 5.14 Photo-response of single ZnO nanowire sample at room temperature       | 107 |  |

## List of Tables

| Table 2.1 Electron-optical system (EOS) and system configuration                              | 7  |

|-----------------------------------------------------------------------------------------------|----|

| Table 3.1 Relevant fabrication tools & machines                                               | 22 |

| Table 3.2 Traveler vs. SOP                                                                    | 23 |

| Table 3.3 Resist thickness of PMMA and ZEP 520A                                               | 28 |

| Table 3.4 Recipe summary to fabricate rings and circles                                       | 38 |

| Table 4.1 Fabrication tools and machines                                                      | 58 |

| Table 4.2 List of nanowire types, metal contacts, and the I-V behaviors                       | 93 |

| Table 5.1 Equipment and tools reserved for fabrication process of single vertical nanowires . | 95 |

**CHAPTER 1: INTRODUCTION**

1.1 History of nanotechnology

Although Michael Faraday discovered gold nano-particles in 1857, the first concept of

nanoscience and nanotechnology was presented a hundred years later by Richard Feynman, a

Nobel laureate. Feynman claimed that "There's plenty of room at bottom" [8] where he

discussed the possibility of manipulating materials at atoms scale. Since then, human beings

have rapidly developed and operated tools that have the abilities to detect, scan, and fabricate

materials down to the nanoscale level. As a result, a new form of carbon C60 or fullerenes,

carbon nanotubes (CNT), and quantum dots were discovered in 1985, 1991, and 1993

respectively [9]. In addition, many studies on synthesis materials, fabrication technique, and

materials properties have been widely conducted and reached considerable achievements. This

opened the era of nanotechnology with promising applications in various fields including bio-

medical, electronics, renewable energy, and military defense.

1.2 From nanostructures to one-dimensional nanostructures

Nanostructures are not a new concept. The prefix "Nano" which is derived from Greek

means dwarf [10]. In fact, the concept of "nano" is not limited to only its original definition, but

transforms in parallel with the extraordinary development of human knowledge. Nanostructures,

a particular term with prefix nano, associates with a series of structures having at least one of its

dimensions less than 100nm. One of significant difference that differentiates from one type of

nanostructures to the others is its physical structures. The first classification suggested by Gleiter

in 1995 and later modified by Skorokhod in 2000 divided nanostructures into zero-dimensional

1

(0D), one-dimensional (1D), two-dimensional (2D), and three-dimensional (3D) nanostructures [11].

One-dimensional nanostructures such as wires, rods, and tubes can be defined as a group of materials having one dimension surface constrained from 0.1nm to 100nm. Since the late 1980s, 1D nanostructures have attracted much attention because they show enormous potential to be great study models for nano-scopic physics (e.g. electrical / thermal transport, mechanical properties) and better candidates for fabrication at the nanoscale level (e.g. interconnects and functional units in fabricating electronic, optoelectronic and electromechanical devices) [12]. At the moment, 1D nanostructures can be fabricated by using nanolithography techniques such as Electron Beam Lithography (EBL), Focused Ion Beam (FIB), and X-Ray or extreme UV lithography for academic research purposes [12].

#### Why Single Nanowire?

Nanowires exhibit significantly different thermal, electrical, mechanical and optical properties from their bulk materials thanks to their unique density of electronic states [13]. Thus, mastering the properties of nanowires will lead to promising applications in nanowire field effect transistors, optoelectronics devices, and sensors. Fabricating and characterizing single nanowires is necessary in order to lead to a better understanding of new nanowire material properties because the behaviors of devices are simpler to predict and observe.

#### 1.3 Thesis Outline

The work presented in this thesis will focus on fabricating single horizontal nanowire device using the Electron Beam Lithography (EBL) technique followed by electrical characterizations. Fabrication of single vertical nanowire structures is also another important part

of this thesis. EBL is used to patterns nanostructures where single vertical nanowire is grown. Before that, one step crucial to preparation is the fabrication of well-defined structures such as rings, circles, and lines followed by metallization and lift off to evaluate the final recipes.

The thesis is mainly composed of six chapters. The first chapter provides the introduction to the thesis. Chapter two gives a theoretical overview on electron beam lithography technique based on the JEOL 5500ZD system and metal semiconductor contact. Chapter three covers step by step of processing works to pattern nanostructures such as holes, rings, and lines. While fabrication and electrical characterization of single horizontal nanowire device will be summarized in chapter 4, single vertical nanowire structures' fabrication and optical measurements will be discussed in chapter 5. In the end is chapter 6 which concludes the thesis.

CHAPTER 2: THEORY OF ELECTRON BEAM LITHOGRAPHY AND METAL SEMICONDUCTOR CONTACT

#### 2.1 Electron beam lithography

#### 2.1.1 Introduction

Electron beam lithography (EBL) is a direct writing lithographic technique that uses an electron beam to write patterns. Compared with conventional photolithography, there are two advantages in a semiconductor fabrication field. The first trait is the capability to generate pattern without applying photo mask. This saves the fabrication cost of photo mask and offers the freedom to write patterns without relying on a hard layout. The second trait is higher patterning resolution. EBL provides nano-scaled patterning which cannot be realized by conventional photolithography because of diffraction limit.

The following section will mainly focus on concept and writing principle of EBL based on JEOL 5500ZD system, as shown in figure 2.1.

Figure 2.1 EBL JEOL 5500ZD system (Thach Pham, June 2012, HiDEC cleanroom, University of Arkansas)

#### 2.1.2 Principle of EBL

#### (a) Formation of beam spot

The source of the electron beam comes from thermal field emission type cathode, i.e. ZrO/W is the emitter [14]. The generated electron beam passes through an electronic optical lenses system that is composed of four main stages where the beam is focused and calibrated before reaching a work piece. The user is able to fully control the beam spot size and its movement.

#### (b) Patterns generation

A sample coated with e-beam resist is placed on the work piece of the EBL system. The resist can be either positive or negative. The patterns are formed by integrating deflected electron beam with movement of the stage which controls the structure of patterns.

#### (c) Resist sensitivity

The resist sensitivity or exposure dose (C/cm<sup>2</sup>) is defined as the amount of required energy to fully penetrate an e-beam resist layer, which is determined by the resist sensitivity and can be expressed as:

$$Q = \frac{I * T}{S}$$

Where I (A) is the generated beam current from the emitter, S ( $cm^2$ ) is the pattern writing area, and T (s) is the pattern writing time [14].

Equation 2.1 can be applied to determine resist sensitivity in either case of positive or negative e-beam resist.

#### (d) Scanning method

The electron beam lithography system applies vector scanning method which allows the beam to scan only on a writing area defined by the user.

Figure 2.2 Vector scanning method [14]

As mentioned above, there are two key movements that control the carving of patterns on e-beam sensitive resist. In the first step where the stage is immobile during the scanning process, the beam is deflected to scan only in a specific region, called as "field", as shown in figure 2.2. The field can be divided up to 200,000x200,000 points. The distance between two consecutive points is called as "scanning step". When the beam finishes scanning the first field, the stage moves by a distance equal to the field size in order to continue writing on the second field, as shown in figure 2.3. The process of scanning one field after another one and moving between consecutive fields until all the patterns are successfully transferred on the entire chip is defined as the step and repeat method. [14]

Figure 2.3 Step and repeat method [14]

By modifying different hardware configuration such as objective lens and acceleration voltage, field size, scan step, writing quality, as well as writing speed could be optimized.

Table 2.1 Electron-optical system (EOS) and system configuration

| EOS<br>mode | ACC (kV) | Obj.<br>Lens | Max. Field (um) | Min. Scan Step<br>(nm) | Writing result | Writing<br>Speed |

|-------------|----------|--------------|-----------------|------------------------|----------------|------------------|

| 1           | 25       | 4            | 2000            | 10                     | Rough          | High             |

| 2           | 50       | 4            | 1000            | 5                      | <b>V</b>       | <b>^</b>         |

| 3           | 25       | 5            | 200             | 1                      | <b>V</b>       | <b>^</b>         |

| 4           | 50       | 5            | 100             | 0.5                    | High           | Low              |

#### (e) Global marks and chip marks

Global marks and chip marks are special patterns functioning as alignment signals which provide directional information of the substrate to the user, as shown in figure 2.4. The shape of the marks could vary according to a user's purpose. The common shape for both global marks and chip marks that EBL JEOL 5500ZD system is able to detect is a cross.

In general, at least two global marks and three chip marks are required. Two global marks provide expansion/contraction parameters, rotation and shift of the substrate based on which the system will make corrections. In the case of chip marks, the distortion parameter within the writing field is sent to the system to perform calibration. [14]

Figure 2.4 Global marks (PQ) and chip marks [14]

#### 2.1.3 System overview

The EBL JEOL 5500ZD system configuration is composed mainly of five components: the main console, control rack, high voltage tank, water chiller, and operation console.

#### (a) Main console

The main console consists of the electron-optical system (EOS), exposure chamber, manual loader, and base frame, as shown in figure 2.5.

Figure 2.5 EBL main console (Thach Pham, June 2012, HiDEC cleanroom, University of Arkansas)

#### (b) Operation console

The operation console is the interface between user and equipment. A user can perform 3 main tasks which are pattern design, calibration, and exposure

#### (c) Control rack

The control rack includes rack A, rack B, and PS box. Rack A controls the lenses and deflectors of EOS, rack B controls the work stage, input and output signals, and PS box controls power.

#### (d) High voltage tank

The high voltage tank generates the accelerating voltage.

#### (e) Water chiller

The water chiller keeps the temperature of all equipment stable.

#### 2.1.4 EOS

Figure 2.6 shows the composition of EOS inside EBL system. Two main parts, the electron source column and a column, form the electron optical system [14].

- The electron source column consists of two parts:

- o Electron source: ZrO/W emitter

- Alignment coils include two stages deflection coil to correct the axis of incoming electron beam from the electron source. In figure, the tilt correction deflects the beam in such way that the beam is focus at a point located on the aperture (crossover point) while the horizontal tilt deflects the beam to be focus at a point located on the center of 2<sup>nd</sup> lens.

#### • The column consists of:

- Intermediate lenses (2<sup>nd</sup> and 3<sup>rd</sup> lenses) reduce the dispersion of beam after passing the crossover point. They also serve as tuning tool for beam current or beam size.

- Objective lenses (4<sup>th</sup> and 5<sup>th</sup> lenses) are two main lenses determining the working condition of e-beam writing such as writing quality, writing time, field size, ...

- A stigmator coil is used as correction tool to tweak the beam spot shape from an ellipse to a perfect circle.

- Beam blanker can either block the beam by deflecting it out of the objective aperture or let the beam pass through.

- Deflectors (4<sup>th</sup> and 5<sup>th</sup> deflectors) represent the scanning range of the beam. They

are prime factors along with acceleration voltage to configure the working

condition of EBL machine.

Figure 2.6 Electrons optics system [14]

#### 2.1.5 Stage driving system

The stage driving system applies the laser beam control (LBC) method to accurately control the position of e-beam as shown in figure 2.7.

The stage moves from one field to another using the step and repeat method. However, there will be an error when the stage moves. The stage is assumed to be located at an arbitrary position called the current location which differs from the specified location defined by the user. The discrepancy between these two locations is the error which can be detected by laser interferometer with a resolution of 0.62nm. The error is sent to a system of signal processor as feedback which helps the system to calibrate the beam. [14]

Figure 2.7 Moving stage system [14]

#### 2.1.6 User interface

(a) Main interface: This is the main interface where user performs most of the crucial adjustments such as ammeter, focus, contrast, EOS mode, beam control, and stage movement. In addition, three others main graphic user

interfaces (GUIs) are integrated with the man interface: pattern designer, calibration, and exposure, as shown in figure 2.8.

Figure 2.8 Main interface [14]

(b) Pattern designer interface: This is the only GUI in the EBL system allowing user to create pattern file and convert designed pattern to \*.v30 file, as shown in figure 2.9. The pattern designer limits the diversity of patterns into certain basic shapes such as lines, circles, rectangles, and rings. The need for manually entered coordinates of each object makes this GUI less competitive with third party design program such as Auto CAD.

Figure 2.9 Pattern designer interfaces [14]

(c) Calibration interface: In contrast with the pattern designer interface, the calibration GUI is an irreplaceable tool of EBL system as shown in figure 2.10. This offers not only elemental calibration functions such as beam deflection amplitude and deflection distortion but also magnificent alignment capability between two layers with a high level of accuracy.

Figure 2.10 Calibration interfaces [14]

(d) Exposure interface: The exposure interface function is to create a layout map where the user defines writing areas to match with the sample position as shown in figure 2.11. In addition, this tool includes exposure dose with shot rank table (discuss in chapter 3).

Figure 2.11 Exposure interfaces [14]

#### 2.2 Metal semiconductor contacts

The two-terminal current voltage measurement is one of basic electrical characterization to determine the resistance of a silicon based nanowire. The most critical element in such measurements is having the control over the contact generated when a metal is brought into contact with a semiconductor. In practical, there are two types of metal semiconductor contact: Shottky contact and Ohmic contact.

In the following section, brief theory of two metal semiconductor contacts will be introduced.

#### 2.2.1 Schottky contact

In this subsection, energy band diagrams become the main tool to analyze and explain phenomena that occurs inside the junction.

Figure 2.12 Band diagram of ideal metal n-type semiconductor contact under equilibrium,

forward bias, and reverse bias condition. [15]

Figure 2.13 Band diagram of ideal metal p-type semiconductor contact under equilibrium,

forward bias, and reverse bias condition. [15]

Metals and semiconductors have their own Fermi level with distinctive positions with respect to vacuum level. The vacuum level is defined as a level where all existing electrons are free and isolated. All electrons in metal have negative energy compared with those hanging in

vacuum level. Hence, the required energy to free an average electron located in Fermi level of metal is named as work function. The work function of each metal is different. [15]

The same concept of work function is applied in the case of semiconductors. However, there are no electrons in the Fermi level of a semiconductor and Fermi level depends on doping type. Thus, the concept of work function is replaced by electron affinity. The electron affinity is defined as an amount of energy to liberate an electron located at the bottom of conduction which is irrelevant with doping type. The electron affinity deviates from materials to materials. [15]

When the electric contact is made between metal and semiconductor, a potential barrier will form and prevent the majority of charge carriers (electrons and holes) to cross from one side to another and vice versa assuming that there is no applied voltage. At that stage, the Fermi levels of metal and semiconductor must be realigned under thermal equilibrium condition. The potential barrier height is equal to the initial offset between Fermi levels of two materials in contact. [15]

In the case of an n-type semiconductor, the barrier height can be expressed as:

$$\phi_{Bn} = \phi_m - \chi$$

In the case of a p-type semiconductor, the barrier height can be expressed as:

$$\phi_{Bp} = E_g - (\phi_m - \chi)$$

Where  $E_g$  is the band gap of the semiconductor.

There are two effects when voltage is applied to metal semiconductor layer: reverse bias conditions and forward bias condition. They change upon doping type of semiconductor.

When a positive voltage is applied to an n-type semiconductor, the energy level of Schottky barrier is increased, as shown in figure 2.12. This increment further blocks the electron current from metal to semiconductor although there is still a minority of electrons that can

overcome the energy barrier and define reverse bias current. This reverse bias current is independent with applied voltage. We call this phenomenon the reverse bias condition. In contrast, when a negative voltage is applied to an n-type semiconductor, the energy level of Schottky barrier is decreased. The reduction in potential barrier allows more electrons to flow from semiconductor to metal. The dominant electron flow forms the forward bias current which increases exponentially with applied voltage. This phenomenon is defined as forward bias condition. [15]

In case of a p-type semiconductor, the Schottky barrier is under reverse bias condition when negative voltage is applied and under forward bias condition when positive voltage is applied as shown in figure 2.13. [15]

#### 2.2.2 Ohmic contact

A significant trait to recognize Ohmic contact is its linear I-V curve. The first method to achieve Ohmic contact is to choose metal type which has the work function to be equal or equivalent with the one form semiconductor side. Thus the potential barrier height can be negligible and current flow back and forward between metal and semiconductor is enhanced. Another method is to heavily dope semiconductor material because of the dependency of energy barrier width toward semiconductor doping level. With high levels of doping, the barrier width is severely reduced in both case of p-type or n-type semiconductor. Hence, the current can easily tunnel through the barrier from metal to semiconductor when positive voltage is applied on the heavily doped n-type semiconductor side. When a negative voltage is applied, electrons not only overcome the barrier but also tunnel through it from semiconductor to metal. [15]

#### CHAPTER 3: FABRICATION OF METALLIC NANOSTRUCTURES

#### 3.1 Introduction

Metallic nanostructures play as vital part for the fabrication of innovative nanodevices (electronic, optical, sensory, plasmonic ...). Numerous scientists recently point out the strong relationship between chemical and physical properties with structural properties of nanostrutures. Thus, one way to tuning nanodevices' functionalities is to engineer geometric parameters of metallic nanostructures such as gratings, circles, rings ... This chapter presents the efforts of fabricating several interested metallic nanostructures using Electron Beam Lithography system JEOL 5500ZD as the main tool to archive nanometric resolution.

#### 3.2 Fabrication process

The fabrication process of metallic nanostructures should go through dose calibration step since there are no EBL recipes built up from the beginning. As shown in figure 3.1, this calibration step starts with traveler preparation, structure design with multiple layers of doses, substrate preparation, EBL writing, metal deposition and lift off. Scanning electron microscopy (SEM) pictures will be taken in the end to examine the optimized exposure dose according to that structure's parameters. This particular part could be repeated several times until the level of accuracy of metalized patterns 'parameters meet user's requirements. After completing dose calibration, optimized dose will be applied on the real sample which shares the same fabrication processes listed above with the calibration step except the new structure design containing only the optimized dose. During the whole fabrication process of metallic nanostructures, others calibrations have been made such as electron beam resist spinning thickness, metal deposition thickness, and lift off process.

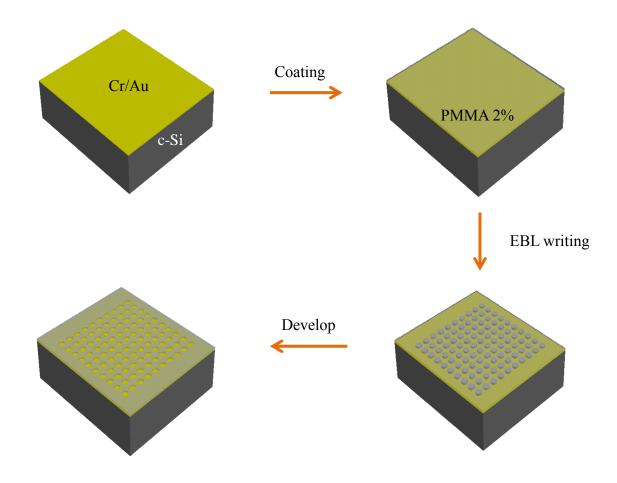

Figure 3.1 Process flow of metallic nanostructures fabrication (Thach Pham, July 2013)

Three particular structures having been studied and fabricated are lines, circles, and rings. Fabrication goals:

- Lines: study ZEP 520A and calibrate line width to 100nm.

- Circles: achieve sub 100nm diameter on c-Si and try fabrication process on different substrates.

- Rings: control inner and outer diameter in such way that |r1-r2| = 100nm and 200nm.

Serving for different potential applications, gratings, circles, and rings are initially fabricated on crystallized silicon substrate while fabrication on glass substrate will be conducted in future.

Besides, two different e-beam resist has been used during calibration process: poly methyl methacrylate (PMMA) and ZEP 520A. PMMA is heavily used in fabrication process of circles and rings while ZEP 520A is used only for the study of line fabrication.

Following table 3.1 shows a list of equipment used in general fabrication process of metallic nanostructures and time estimation for each step:

Table 3.1 Relevant fabrication tools & machines

| Process               | Related equipment              | Time cost                    |  |

|-----------------------|--------------------------------|------------------------------|--|

| Traveler preparation  | Microsoft office               |                              |  |

| Structure design      | • Auto CAD 2012                | 1 hour / pattern design      |  |

|                       | • Link CAD 7                   |                              |  |

| Substrate preparation | Solvent bench                  | 1 hour / 4 samples           |  |

|                       | • Spinner                      |                              |  |

|                       | Hot plate                      |                              |  |

| EBL writing           | EBL system JEOL 5500ZD         | 2-3 hours / sample           |  |

|                       | Develop bench                  |                              |  |

|                       | <ul> <li>Microscope</li> </ul> |                              |  |

| Metal deposition      | Thermal evaporator AUTO        | 3-4 hours / multiple samples |  |

|                       | 306T                           |                              |  |

| Lift off              | Wet bench                      | 2 days                       |  |

|                       | Ultra sonic bath               |                              |  |

|                       | <ul> <li>Microscope</li> </ul> |                              |  |

| SEM pictures          | • FEI NOVA 200                 | 2 hours / sample             |  |

In summary, it will take 4 days to complete one round either for control sample or final sample.

### 3.2.1 Traveler preparation

Documentation of each fabrication processes becomes indispensable step not only in industry but also in academic research. Those important documents, travelers, which record critical processing parameters are initially generated based on a general model provided by researchers. Then, after finishing one loop of process, traveleres will be revised and updated until fabrication recipes of that process is optimized. For each particular device, there will be a separated set of traveler.

The discrepancies between traveler and standard operating procedure (SOP) are shown in table 3.2.

Table 3.2 Traveler vs. SOP

| Traveler                              | SOP                                      |  |  |

|---------------------------------------|------------------------------------------|--|--|

| Devices based                         | Equipment based                          |  |  |

| One time use                          | Multiple time use                        |  |  |

| Record critical processing parameters | Contain detailed machine 's instructions |  |  |

# 3.2.2 Structure design

Structure design is another important preparation step in the fabrication of metallic nanostructures since electron beam lithography is direct writing which does not require a photo mask but a digital plot. The plot, containing the design of nanostructures, could be drawn either from built in program of EBL system called "pattern design" or from third party program such as Auto CAD, a powerful and compatible design tool. Most of design works in my thesis are based on Auto CAD 2012, student version, since it offers drawing flexibility, less time consuming, as well as huge number of exposure dose (EBL "pattern design" only allows 15 layers for each design).

There are always two types of pattern design for each metallic nanostructure in this step:

- Calibration process pattern design

- Final process pattern design

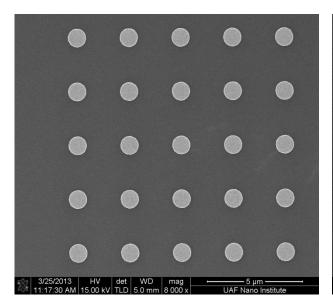

- (a) Calibration process pattern design:

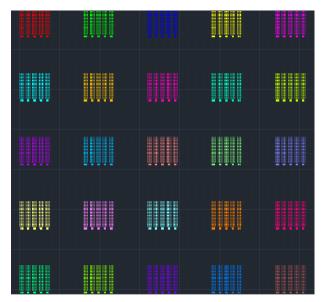

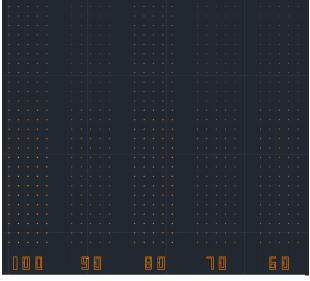

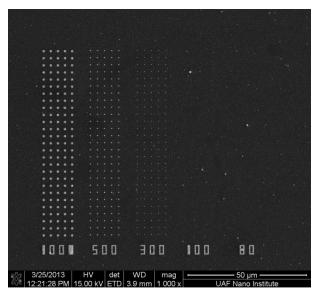

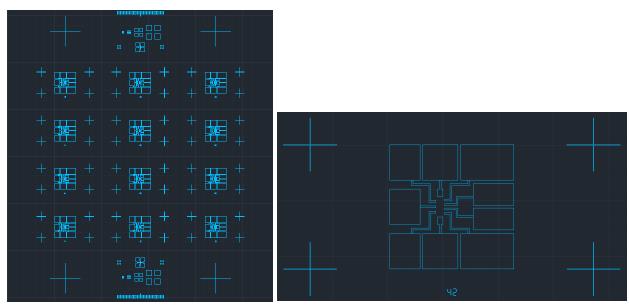

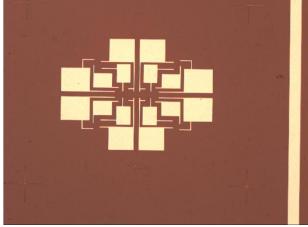

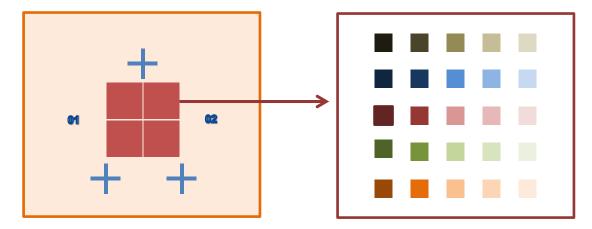

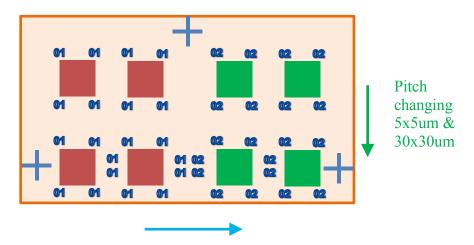

A set of five by five arrays representing 25 distinct exposure doses will be generated to cover 1mm<sup>2</sup> writing area, as shown in figure 3.2a and figure 3.3a. Each similar array contains different structure size ranging from 60nm to 1um and specific dimension marks underneath of those structures, as shown in figure 3.2b and figure 3.3b. In addition, three to five PQ marks, cross marks of 3um width and 300um long are also unevenly distributed at left, right, top and bottom of defined writing area. This enables user to recognize the pattern under microscope after developing, to evaluate lift off process, as well as to comfortably orientate testing sample with SEM camera. Moreover, user has option to modify pitch size in such way that fits to the 1mm<sup>2</sup> writing area.

Figure 3.2 (a) CAD design 5x5 arrays of different doses (Thach Pham, December 2012, Auto CAD 2012)

Figure 3.2 (b) Zoom in CAD design 5x5 arrays of different doses (Thach Pham, December 2012, Auto CAD 2012)

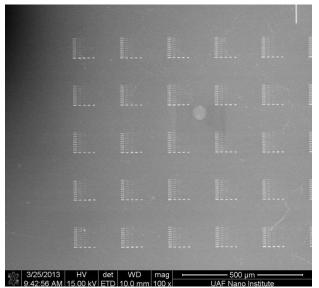

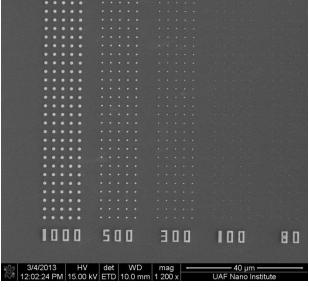

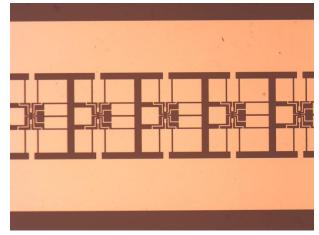

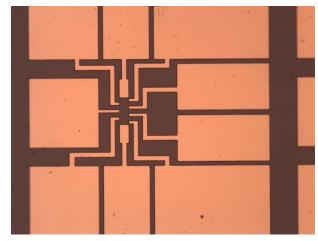

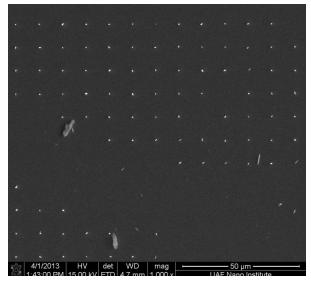

Figure 3.3 (a) SEM pictures of metalized 5x5 arrays design (Thach Pham, March 2013, University of Arkansas)

Figure 3.3 (b) Zoom in SEM picture of metalized single array design (Thach Pham, March 2013, University of Arkansas)

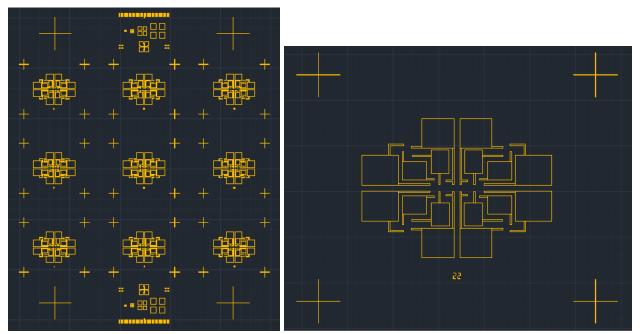

# (b) Final process pattern design

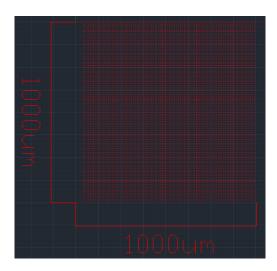

A large array of structure is formed covering 1mm<sup>2</sup> area instead of 5x5 arrays, as shown in figure 3.4. Exposure dose is optimized from control sample and pitch size is also modified. PQ marks stay the same as those in control sample.

Figure 3.4 CAD design single array covering 1mm<sup>2</sup> area (Thach Pham, December 2012, Auto CAD 2012)

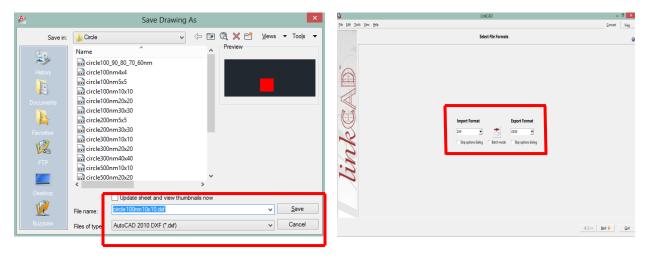

Although pattern design does not resemble in two processes listed above, it still goes through similar converting process to be translated into input file of EBL JEOL 5500ZD, v30 file as shown in figure 3.5.

- In Auto CAD 2012, save as \*.dwg file into \*.dxf file.

- In LinkCAD 7, convert \*.dxf file into \*.gdsii file.

- In Pattern design (EBL system interface), convert \*.gdsii file into \*.v30 file.

Figure 3.5 (a) Convert dwg file into dxf file in Auto CAD (Thach Pham, July 2013)

Figure 3.5 (b) Convert dxf file into gdsii file in LinkCAD (Thach Pham, July 2013)

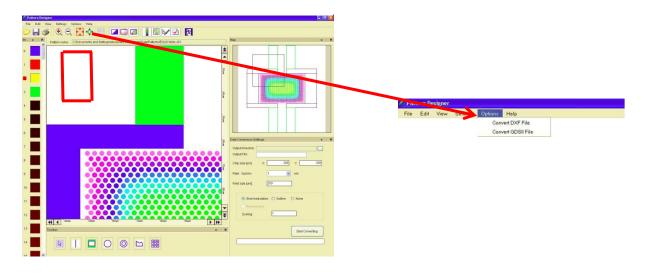

Figure 3.5 (c) Convert gdsii file into v30 file in Pattern Design [14]

### 3.2.3 Substrate preparation

In this section, we discuss about required steps to prepare sample before e-beam lithography writing. 1cmx1cm piece c-Si sample goes through cleaning process and coating process.

### (a) Cleaning step:

- Clean piece c-Si sample using acetone, methanol, and isopropyl alcohol (IPA)

respectively and followed by DI water cleaning. Do not let the surface of sample dry out.

- Dry sample using N<sub>2</sub> gun.

- Dehydrate sample at 90° C for 5 minutes and let it cool down.

- Check with microscope.

Since c-Si piece sample is diced from high qualify 5" Si wafer, there is no need to apply standard cleaning procedure e.g. RCA cleaning.

#### (b) Resist coating step:

- Cover spinning plate with blue tape to protect the back of sample and vacuum chuck.

- Spin coat poly methyl methacrylate (PMMA) 495K 2% at 3000 rpm. This gives approximately 60nm of resist thickness.

- Bake coated sample at 180°C for 2 minutes and let it cool down.

Resist thickness of PMMA 495K (2% and 4%) and ZEP 520A (diluted 1:1, 1:2, 1:4 ratio) is carefully calibrated using both Nanospec (optical measurement) and Dektak profilometer (physical contact) in High Density Electronics Cener (HiDEC)'s cleanroom. Experiment data are collected and presented in table 3.3. The working principle of nanospec (figure 3.6) is

conducting measurement of reflected light to determine film thickness based on interference effects. Thus, it requires a solid and reliable refractive index value of the coating resist which could be accessed in datasheet provided by chemical company. In the other hand, dektak profilometer (figure 3.7) applies surface contact measurement technique where a tip is dragged across the scratched surface of coated control sample.

Table 3.3 Resist thickness of PMMA and ZEP 520A

| E-beam resist | Spin speed | Resist thickness |

|---------------|------------|------------------|

| PMMA 495K 2%  | 3000 rpm   | 50-60nm          |

| PMMA 495K 4%  | 3000 rpm   | 200nm            |

| ZEP 520A 1:1  | 3000 rpm   | 174nm            |

| ZEP 520A 1:2  | 3000 rpm   | 114nm            |

| ZEP 520A 1:4  | 3000 rpm   | 50nm             |

Figure 3.6 Nanospec (Thach Pham, July 2013, University of Arkansas)

Figure 3.7 Dektak profilometer (Thach Pham, July 2013, University of Arkansas)

### 3.2.4 Electron beam lithography writing

If chapter 2 provides working principle of electron beam lithography JEOL 5500ZD, this section will explore in details important processes and techniques to successfully "write" patterns having final dimensions matching to those in design step.

## (a) Sample loading:

- Load sample into cassette.

- Load cassette into chamber 2.

- Pump down chamber 2 until VG2 reaches 4E-3 Pa.

- Open valve connecting 2 chambers and load cassette into chamber 1.

- Pump down system until VG2 reaches 1E-5 Pa and gun valve pops out.

## **Positioning sample in cassette:**

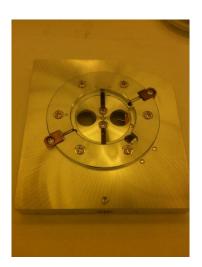

For each EBL exposure, only one sample could be loaded. Coated with e-beam resist, the sample is placed in an appropriate cassette corresponding to sample size. Currently, EBL JEOL 5500ZD supports three main types of cassette: 4" cassette (hold 4" wafer), 2" cassette (hold 2" wafer), and piece cassette (from 1cm x 1cm to 1"x1") as shown in figure 3.8, figure 3.9, and figure 3.10 respectively.

Figure 3.8 (a) Front side of 4" cassette (Thach Pham, January 2013, University of Arkansas)

Figure 3.8 (b) Back side of 4" cassette (Thach Pham, January 2013, University of Arkansas)

Figure 3.9 (a) Front side of 2" cassette (Thach Pham, January 2013, University of Arkansas)

Figure 3.9 (b) Back side of 2" cassette (Thach Pham, January 2013, University of Arkansas)

Figure 3.10 (a) Front side of piece cassette (Thach Pham, January 2013, University of Arkansas)

Figure 3.10 (b) Back side of piece cassette (Thach Pham, January 2013, University of Arkansas)

In order to save writing time and materials cost, piece cassette turns out to be the best choice for calibration process of metallic nanostructures fabrication.

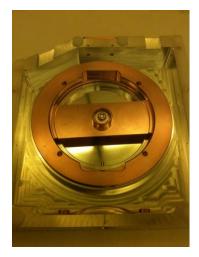

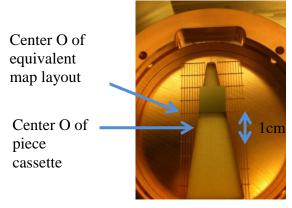

The sample could be positioned anywhere along the triangle region as long as user records that position. In case of 1cm x 1cm sample size, because of the sample size and the mismatch between software and sample position (will be discussed in exposure part) it is recommended to place sample in such way that its center is 1cm above from the one of piece cassette, as shown in figure 3.11.

Figure 3.11 (a) Back side of loaded piece cassette, (Thach Pham, January 2013, University of Arkansas)

Figure 3.11 (b) Front side of loaded piece cassette (Thach Pham, January 2013, University of Arkansas)

### (b) Calibration

Calibration process in EBL could be either simple or complicated depending on the user's purpose. This section only mentions basic calibration process as shown in figure 3.12 for regular exposure while section on nanowire device will explain advanced techniques in alignment calibration.

Changing accelerating voltage Selecting EOS mode Selecting calibration Only when changing the state conditions Selecting objective aperture Rough adjustment of beam current Positioning objective aperture Fine adjustment of beam current Adjusting focus and astigmatism Performing calibration

Figure 3.12 Flow of basic adjustment (Thach Pham, July 2013)

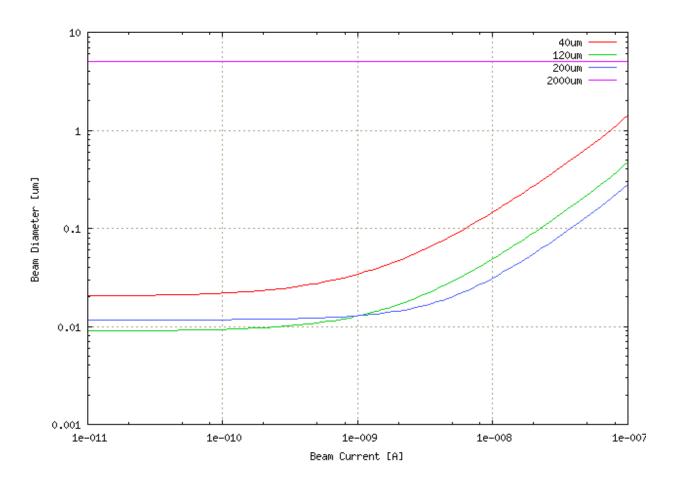

The default setting starts with EOS mode 2 where acceleration voltage is set at 50KV. 4<sup>th</sup> lens and 2<sup>nd</sup> aperture are also set as default. Although standard beam current starts with 1nA, it could be tuned to smaller beam current which provides smaller beam spot. Figure 3.13 summarizes the relation between current and spot size. Red, green, blue and purple curves represent aperture 1, 2, 3, and 4 respectively. At 1nA 2<sup>nd</sup> aperture, the beam size is approximately 15nm.

Figure 3.13 Beam current vs. beam diameter [14]

For some particular nanostructures (e.g. line width less than 60nm or circle diameter less than 100nm), EOS mode 4 is preferred since it provides a smaller working range of e-beam spot size. Another factor to be considered when switching between EOS modes is time cost because writing time and beam current are inversely proportional.

# (c) Exposure

- Open exposure table and import \*.v30 files.

- Choose layout type: piece cassette.

- Select exposure dose.

- Place chips on layout in correct position.

- Edit job property:

o Scan step 1

• Calibration condition file must match with user's calibration file

Cycle: each chip

Calibration mode: deflection

• Save layout file.

Select exposure.

• When exposure is done, record writing time and stop the beam.

• Move the stage back to its original position before unload sample.

Mismatch of sample position with exposure layout software (piece cassette)

As show in figure 3.11b, the center of piece cassette is marked by a unique dot of the triangle. However, 0 in the exposure software (piece cassette layout) does not represent the center of piece cassette. It is located at 10mm above from the origin 0. Consequently, user must record the coordinates of sample position to avoid any misplacing problem.

Exposure dose plan

JEOL 5500ZD has a very unique dose system. User has to input base dose (line and plane dose) from which he/she is able to expand from a single base dose to multiple doses, named as shot rank table. The number of exposure doses depends on the total number of layers that pattern design carries within. The new dose is calculated as the sum of initial dose and input percentage of that initial dose. It could be either positive percentage or negative one. For instance, base dose is 500 uC/cm<sup>2</sup> and percentage input for 1<sup>st</sup> layer is 10. The 1<sup>st</sup> dose will be 550 uC/cm<sup>2</sup> or 1.1 time of 500 uC/cm<sup>2</sup>. If the input is -10, the 1<sup>st</sup> dose will be 450 uC/cm<sup>2</sup>. The resolution for choosing 500 uC/cm<sup>2</sup> as the initial dose is 5 uC/cm<sup>2</sup>. User has the freedom to input a different number for initial dose. Recommended value for starter is 800 uC/cm<sup>2</sup>.

(d) Develop

• Unload the sample from the cassette

• Prepare 3 separate beakers:

o Developer IPA:MIBK 3:1

o IPA

DI water

• Develop sample in IPA:MIBK 3:1 for 60 seconds.

• Dip sample in IPA beaker for another 30 seconds

• Rinse with DI water and dry out using N<sub>2</sub> gun

• Evaluate sample pattern under microscope

The develop time is mainly decided based on exposure dose. For each type of resist, there is an optimized dose for a certain parameter of structures. A great amount of time has been spent going back and forth between exposure dose and develop time. The strategy is to keep one variable constant and let the other changes. For instance, develop time is kept at 60s and exposure doses are varied from 400 uC/cm² to 1200 uC/cm² to fabricate circle of 100nm diameter; e-beam resist is PMMA 495K 2%. After taking SEM pictures, the quasi optimized exposure dose will be found otherwise the process is repeated with a modification of develop time. Recommended starting develop time is 60s.

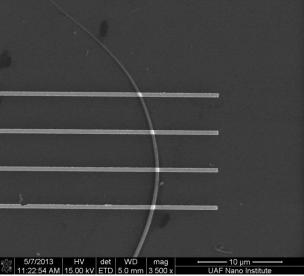

### ZEP 520A study

For the case of ZEP 520A, developer IPA:MIBK 3:1 is replaced by n-amyl acetate. The develop time of ZEP 520A are influenced by developer's temperature [16]. At colder develop temperature, higher resolution will be archived. However, this process is temporary delayed due to time consuming (need brand new dose plan) and less significance comparing with other fabrication process such as rings and circles. Line structure is used for this type of experiment where line width from 116nm to 65nm has been achieved, as shown in figure 3.14.

Figure 3.14 (a) Line width of 116nm, pitch size of 1um (Thach Pham, November 2012, University of Arkansas)

Figure 3.15 (a) Line width of 100nm, pitch size of 1um (Thach Pham, November 2012, University of Arkansas)

Figure 3.14 (b) Line width of 93nm, pitch size of 1um (Thach Pham, November 2012, University of Arkansas)

Figure 3.15 (b) Line width of 65nm, pitch size of 1um (Thach Pham, November 2012, University of Arkansas)

# Recipe summary for circle and rings structures

The fabrication of metallic lines is not in a solid state because of discontinuity of ZEP 520A study. As a result, lines recipe using ZEP 520A won't be summarized in this table where only mature recipes are listed in table 3.4.

Table 3.4 Recipe summary to fabricate rings and circles

| Pattern          | Substrate    | Film                                           | Dose (uC/cm <sup>2</sup> ) | Develop                                  | Reference     |

|------------------|--------------|------------------------------------------------|----------------------------|------------------------------------------|---------------|

| description      |              | description                                    | / Current (nA)             | information                              | sample number |

| Circle<br>1000nm | a-Si on c-Si | 200nm<br>thick, 4%<br>495K<br>PMMA,<br>3000rpm | 860 /-1                    | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_03192013_1  |

| Circle<br>500nm  | a-Si on c-Si | 200nm<br>thick, 4%<br>495K<br>PMMA,<br>3000rpm | 735 /-1                    | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_03192013_1  |

| Circle<br>300nm  | a-Si on c-Si | 200nm<br>thick, 4%<br>495K<br>PMMA,<br>3000rpm | 735 /-1                    | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_03192013_1  |

| Circle<br>1000nm | c-Si         | 60nm thick,<br>2% 495K<br>PMMA,<br>3000rpm     | 860 /-0.5                  | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_03122013_1  |

| Circle<br>500nm  | c-Si         | 60nm thick,<br>2% 495K<br>PMMA,<br>3000rpm     | 800 /-0.5                  | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_03122013_1  |

| Circle           | c-Si         | 60nm thick,                                    | 710 /-0.5                  | 3:1 IPA:                                 | T_03122013_1  |

| 300nm                           |      | 2% 495K<br>PMMA,<br>3000rpm                |           | MIBK 60sec,<br>IPA rinse 15s             |              |

|---------------------------------|------|--------------------------------------------|-----------|------------------------------------------|--------------|

| Circle<br>200nm                 | c-Si | 60nm thick,<br>2% 495K<br>PMMA,<br>3000rpm | 710 /-0.5 | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_05302013_1 |

| Circle<br>100nm                 | c-Si | 60nm thick,<br>2% 495K<br>PMMA,<br>3000rpm | 620 /-0.5 | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_05142013_1 |

| Circle<br>90nm                  | c-Si | 60nm thick,<br>2% 495K<br>PMMA,<br>3000rpm | 640 /-0.5 | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_05142013_1 |

| Circle<br>80nm                  | c-Si | 60nm thick,<br>2% 495K<br>PMMA,<br>3000rpm | 630 /-0.5 | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_05142013_1 |

| Circle<br>70nm                  | c-Si | 60nm thick,<br>2% 495K<br>PMMA,<br>3000rpm | 670 /-0.5 | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_05142013_1 |

| Circle<br>60nm                  | c-Si | 60nm thick,<br>2% 495K<br>PMMA,<br>3000rpm | 760 /-0.5 | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_05142013_1 |

| Ring d1=<br>500nm d2 =<br>900nm | c-Si | 60nm thick,<br>2% 495K<br>PMMA,<br>3000rpm | 510 /-0.5 | 3:1 IPA:<br>MIBK 60sec,<br>IPA rinse 15s | T_05302013_1 |

| Ring d1=                        | c-Si | 60nm thick,                                | 510 /-0.5 | 3:1 IPA:                                 | T_05302013_1 |

| 300nm d2 =  |      | 2% 495K     |           | MIDIZ (Occ.                             |              |

|-------------|------|-------------|-----------|-----------------------------------------|--------------|

|             |      |             |           | MIBK 60sec,                             |              |

| 700nm       |      | PMMA,       |           | IPA rinse 15s                           |              |

|             |      | 3000rpm     |           |                                         |              |

|             |      |             |           |                                         |              |

| Ring d1=    | c-Si | 60nm thick, | 510 /-0.5 | 3:1 IPA:                                | T_05302013_1 |

| 200nm d2 =  |      | 2% 495K     |           | MIBK 60sec,                             |              |

| 600nm       |      | PMMA,       |           | IPA rinse 15s                           |              |

| 0001111     |      | 3000rpm     |           |                                         |              |

|             |      | Зооогри     |           |                                         |              |

| Ding d1_    | c-Si | 60mm thials | 510 /-0.5 | 3:1 IPA:                                | Т 05202012 1 |

| Ring d1=    | C-S1 | 60nm thick, | 3107-0.3  |                                         | T_05302013_1 |

| 100nm d2 =  |      | 2% 495K     |           | MIBK 60sec,                             |              |

| 500nm       |      | PMMA,       |           | IPA rinse 15s                           |              |

|             |      | 3000rpm     |           |                                         |              |

|             |      |             |           |                                         |              |

| Ring d1=    | c-Si | 60nm thick, | 510 /-0.5 | 3:1 IPA:                                | T_05302013_1 |

| 500nm d2 =  |      | 2% 495K     |           | MIBK 60sec,                             |              |

| 700nm       |      | PMMA,       |           | IPA rinse 15s                           |              |

|             |      | 3000rpm     |           |                                         |              |

|             |      |             |           |                                         |              |

| Ring d1=    | c-Si | 60nm thick, | 510 /-0.5 | 3:1 IPA:                                | T_05302013_1 |

| 300 nm d2 = | CBI  | 2% 495K     | 3107 0.3  | MIBK 60sec,                             | 1_03302013_1 |

|             |      |             |           | IPA rinse 15s                           |              |

| 500nm       |      | PMMA,       |           | IPA filise 138                          |              |

|             |      | 3000rpm     |           |                                         |              |

|             | ~.   |             |           |                                         |              |

| Ring d1=    | c-Si | 60nm thick, | 510 /-0.5 | 3:1 IPA:                                | T_05302013_1 |

| 200nm d2 =  |      | 2% 495K     |           | MIBK 60sec,                             |              |

| 400nm       |      | PMMA,       |           | IPA rinse 15s                           |              |

|             |      | 3000rpm     |           |                                         |              |

|             |      |             |           |                                         |              |

| Ring d1=    | c-Si | 60nm thick, | 515 /-0.5 | 3:1 IPA:                                | T_05302013_1 |

| 100nm d2 =  |      | 2% 495K     |           | MIBK 60sec,                             | _            |

| 300nm (not  |      | PMMA,       |           | IPA rinse 15s                           |              |

| optimized)  |      | 3000rpm     |           | 111111111111111111111111111111111111111 |              |

| opunizeu)   |      | Jooorpin    |           |                                         |              |

|             |      |             |           |                                         |              |

### 3.2.5 Metal deposition & Lift off

One of main purpose metalizing exposed patterns is to evaluate the recipe used for the entire fabrication process. Edwards AUTO 306T thermal evaporator (figure 3.16) is mainly used to archive this goal. Follow the metal deposition process is lift off which dissolves the unexposed e-beam resist and simultaneously removes the metal layer sitting on top of those areas. In the end, only exposed areas are metalized and the sample is ready for taking SEM pictures.

## (a) Metal deposition:

- Load one/multiple sample on sample holder disc with kapton tape

- Place/replace Cr rod and fill new Au pallets on boat

- Pump down chamber for 2-3 hours until it reaches approximately 8E-6 mTorr

- Start depositing metal at rate of 1-2 A/s to obtain 5nm Cr and 30 nm Au

Figure 3.16 Thermal evaporator Edward 306T (Thach Pham, July 2013, University of Arkansas)

### (b) Lift off:

- Prepare beaker/beakers containing remover PG, a dedicated solvent stripper for PMMA

- Heat up to 70°C

- Place one sample for each beaker

- Wait 30 minutes

- Bubble sample surface in order to remove most of unnecessary metalized parts.

- Replace new solvent, cover beakers and monitor samples for a least 2 days. Fill up solvent again if it evaporates.

- Bubble sample surface and leave beakers in ultrasonic bath for 5 minutes

- Rinse samples with IPA to stop the reaction of remover PG

- Rinse samples with DI water and dry out using N<sub>2</sub> gun

- Examine sample under microscope. Look for PQ marks

This lift off process has been carefully calibrated for many times and reaches a solid state at the moment. Besides, remover PG could also be replaced by acetone for some applications.

# Metal thickness and roughness study

The metal thickness and the film quality (roughness) are two priority concerns in this step. Many users have totally ignored thickness measurement step after depositing metal layers and always believe in machine tool. As consequence, high resolution SEM picture and atomic force microscopy (AFM) are used to conduct the study of metal thickness and roughness.

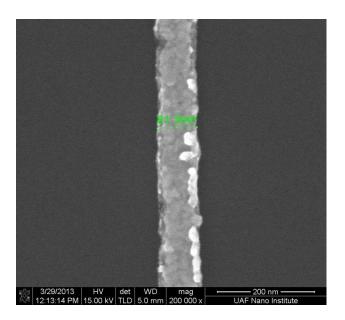

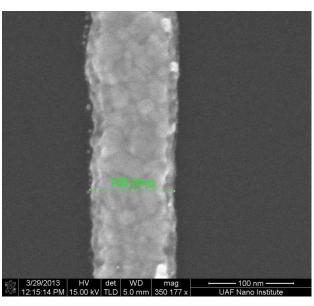

Figure 3.17 (a) SEM picture of metalized line with high roughness (Thach Pham, March 2013, University of Arkansas)

Figure 3.17 (b) SEM picture of metalized line with high roughness (Thach Pham, March 2013, University of Arkansas)

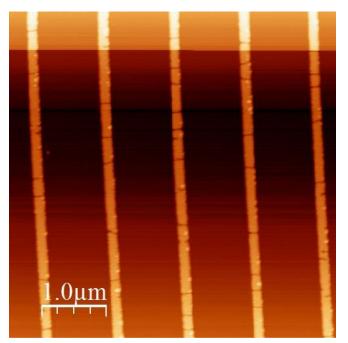

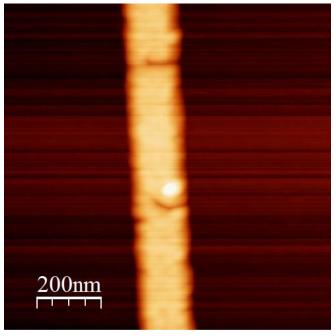

Figure 3.18 (a) AFM surface geometry of multiple lines (Thach Pham, March 2013, University of Arkansas)

Figure 3.18 (b) AFM surface geometry of single line (Thach Pham, March 2013, University of Arkansas)

Figure 3.19 (a) AFM data, metal thickness of multiple lines (Thach Pham, March 2013, University of Arkansas)

Figure 3.19 (b) AFM data, metal thickness of single line (Thach Pham, March 2013, University of Arkansas)

From figure 3.17, figure 3.18, and figure 3.19 a thicker layer of Cr/Au has been deposited (approximately 40nm instead of 30nm) and possesses high roughness. The temporary solution for the metal deposition using thermal evaporator is to lower the deposition rate from 1-2 A/s to 1-2 A/5s or much slower. However, this will raise the temperature inside the chamber. Thus, e-beam resist will melt down and make lift off process much harder. A better solution is to use electron beam evaporator to deposit metal layer since it works in atomic scale.

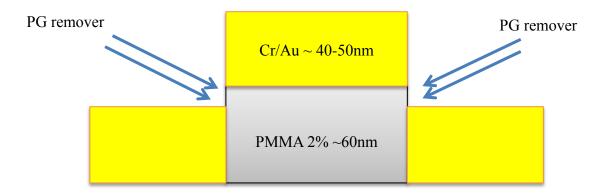

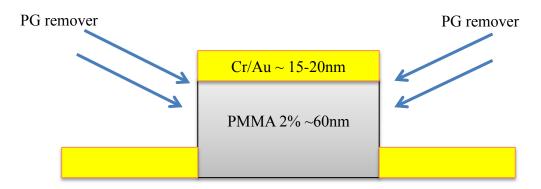

## Lift off problem: rings structure

As shown in figure 3.21, most of metallic rings could not be lift off using 5nm Cr / 30nm Au. Possible reason is that e-beam resist is thin while deposited metal layer might too thick to lift off. From AFM thickness measurement results, depositing 5nm Cr / 30nm Au yields approximately 40-55nm of metal layer, which approaches resist thickness. In addition, heat generated during the metalized process could melt resist's top surface and edges. Consequently, developer barely reaches to open area of e-beam resist and metal layer attaching to the resist remains on unwanted sites, as shown in figure 3.20.

Figure 3.20 Thick layer of metal prevents PG remover to attack e-beam resist (Thach Pham, July 2013)

Figure 3.21 (a) SEM picture of ring structure where lift off fails (Thach Pham, May 2013, University of Arkansas)

Figure 3.21 (b) Zoom in SEM picture of ring structure where lift off fails (Thach Pham, May 2013, University of Arkansas)

One reasonable solution is to either increase resist thickness or reduce metal layer. Since dose plan's status is in solid phase using PMMA 2%, Cr and Au layer has been reduced to 2nm Cr/10-15nm Au. As a result, lift off is a success.

Figure 3.22 Reduce metal layer for rings structure (Thach Pham, July 2013)

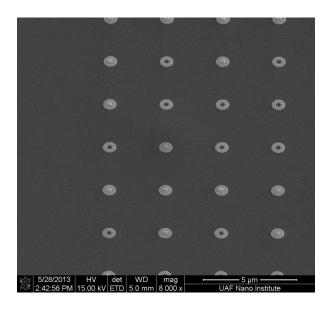

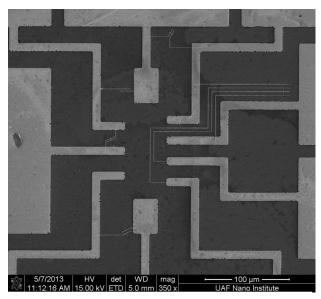

# 3.3 SEM pictures of metallic nanostructures

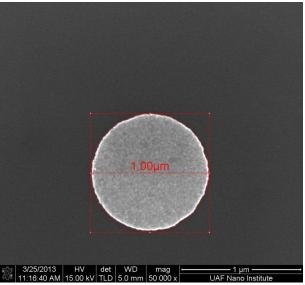

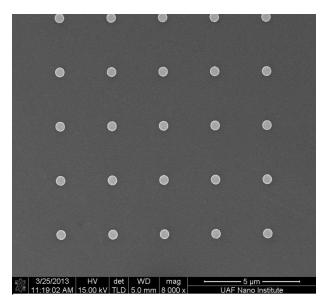

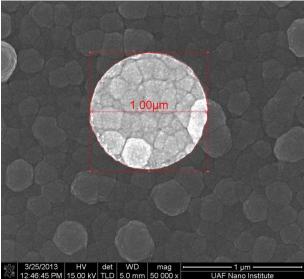

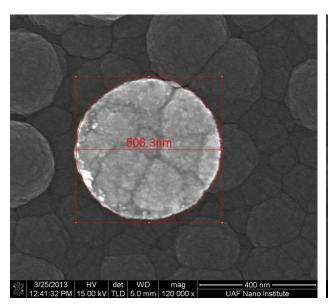

In brief, a considerable amount of nanostructures having various geometrical dimensions from 1um to 60nm has been successfully fabricated using e-beam lithography system although fabrication processes encounter several technical problems. Lines width goes down to 90nm (ZEP 520A); circles diameter reaches 1um, 500nm, 300nm, 100nm, 90nm, 80nm, 70nmn, 60nm (PMMA); rings' inner diameter goes down to 70nm while outer diameter goes down to 300nm.

Figure 3.23 (a) SEM picture of circles having diameter of 1um (Thach Pham, March 2013, University of Arkansas)

Figure 3.23 (b) Zoom in SEM picture of 1um circle structure (Thach Pham, March 2013, University of Arkansas)

Figure 3.24 (a) SEM picture of circles having diameter of 500nm (Thach Pham, March 2013, University of Arkansas)

Figure 3.24 (b) Zoom in SEM picture of 500nm circle structure (Thach Pham, March 2013, University of Arkansas)

Figure 3.25 (a) SEM picture of circles having diameter of 300nm (Thach Pham, March 2013, University of Arkansas)

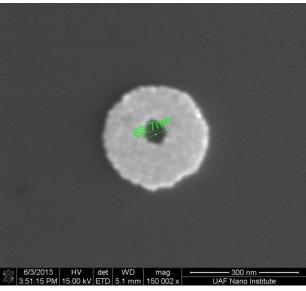

Figure 3.25 (b) Zoom in SEM picture of 300nm circle structure (Thach Pham, March 2013, University of Arkansas)