# Copyright © 2006 IEEE. Reprinted from IEEE Asia Pacific Conference on Circuits and Systems (2006 : Singapore)

This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of the University of Adelaide's products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to pubs-permissions@ieee.org.

By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

# Fourth-Order Discrete-Time Variable Centre Frequency Bandpass Sigma-Delta Modulator

Y. Zhu, S.F. Al-Sarawi, C. C. Lim, and M.J. Liebelt

Abstract—A design for a variable centre frequency bandpass Sigma-Delta modulator is presented. The modulator is based on a tunable discrete-time resonator using only one control parameter. The noise transfer function of the modulator is controlled by a 4-bit digital signal, which provides nine different centre frequencies distributed between 0.1-0.4 normalized frequencies. The measurement results show a stable modulator at all centre frequencies.

Index Terms—ADC, BPSDM, SNR, NTF.

## I. INTRODUCTION

Analog-to-digital converters (ADC) play important roles in digital HF receivers. The received signal is directly digitized at RF, then downconverted utilizing digital downconversion techniques, and further processed by either hardware or software DSP engines, such as software defined radio systems. Bandpass Sigma-Delta modulator (BPSDM) ADCs are able to achieve good performance using comparatively simple circuitries for digitizing passband signals. The main idea is to use a loop filter to shape the quantization noise power out of the band of interest; hence a better signal-to-noise ratio (SNR) is obtained. In contrast, conventional ADCs lower the entire quantization noise floor at the cost of a large number of comparators and digital correction logic. However for a BPSDM, once the noise transfer function (NTF) is decided, the centre frequency, where the RF or IF signal is located, is then fixed without changing the sampling frequency, and therefore prevents the application of a BPSDM for a multiple frequency channel HF receiver system. This issue results in the motivation of developing a BPSDM with variable centre frequencies (VCF).

Early work on VCF BPSDMs using continuous-time (CT) loop filters have been reported [1][2]. However, a CT SDM is a combined z and s-domain system, which makes it difficult to control the NTF when tuning the centre frequency; hence the modulator order and noise shaping efficiency are limited. Another approach is to use a discrete-time (DT) loop filter based on a tunable resonator expressed in the z-domain as

$$R(z) = \frac{Y(z)}{X(z)} = -\frac{az+1}{z^2 + 2az+1},$$

(1)

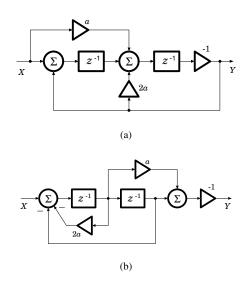

where *a* is the only tuning parameter between -1 and 1, resulting in the corresponding resonance frequency changing from DC to half of the sampling frequency. The resonator can be realized in two different topologies as shown in Fig. 1, based on unit delay elements. This VCF BPSDM algorithm was first presented in [3], then a similar approach was reported in [4] and recently implemented in [5] using double sampling techniques. The purpose of this paper is to present a new NTF synthesis method with controlled out-of-band-gain (OOBG), and the switched-capacitor circuit realization.

Fig. 1. Topologies of the tunable resonator of (1).

#### II. NTF SYNTHESIS

The VCF BPSDM design procedure starts by firstly synthesizing a stable fourth-order NTF, and then realizing the NTF using the variable frequency resonator R(z) [3]. A fourth-order NTF with OOBG = 1.5 and Butterworth type zeros and poles is synthesized using Schreier's MATLAB toolbox [6] as

$$NTF(z) = \frac{(z^2 + 1)^2}{z^4 + 1.255z^2 + 0.4414}.$$

(2)

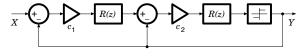

The next step is to map (2) to a fourth-order BPSDM topology using the resonator R(z), as shown in Fig. 2. The

gain parameters  $c_1$  and  $c_2$  provide two degrees of freedom to realize the desired NTF. Using the linear model of the quantizer, the NTF of the fourth-order BPSDM can be derived as

$$NIF(z) = \frac{(z^2 - 2az + 1)^2}{(z^2 + 2az + 1)^2 + c.c.(az + 1)^2 - c.(az + 1)(z^2 + 2az + 1)}$$

(3)

$$(2 + 2u_{2} + i) + c_{1}c_{2}(u_{2} + i) + c_{2}(u_{2} + i)(u_{1} + 2u_{2} + i)$$

Fig. 2. Architecture of the  $4^{th}$ -order VCF BPSDM using the resonator of (1).

Since the OOBG at DC and 0.5 (normalized frequency) is independent of the tuning parameter a, it is convenient to set a = 0 to calculate the parameters  $c_1$  and  $c_2$ , while still satisfying Lee's stability rule of thumb [7]. The NTF with a =0 is given by

$$NTF(z) = \frac{(z^2 + 1)^2}{z^4 + (2 - c_2)z^2 + 1 + c_1c_2 - c_2}.$$

(4)

Comparing (4) to (2) and solving for  $c_1$  and  $c_2$  yields

$$[c_1, c_2] = [0.2792, 0.775].$$

(5)

Substituting the coefficients  $c_1$  and  $c_2$  into (3) results in the final NTF of the fourth-order VCF BPSDM as NTF(z) =

$$\frac{(z^2 - 2az + 1)^2}{(z^2 + 2az + 1)^2 + 0.2164(az + 1)^2 - 0.775(az + 1)(z^2 + 2az + 1)}$$

(6)

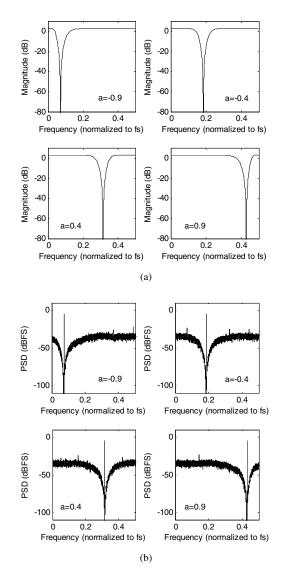

The calculated frequency response of (6) and simulated VCF BPSDM spectrums with different values of a are shown in Fig. 3. Since the OOBG is controlled at less then 2, Lee's stability rule of thumb [7] is always satisfied, therefore as expected the modulator remains stable throughout the tuning range of a from -0.95 to 0.95, corresponding to the normalized centre frequency changing from 0.05 to 0.45.

#### III. CIRCUIT DESIGN AND MEASUREMENT

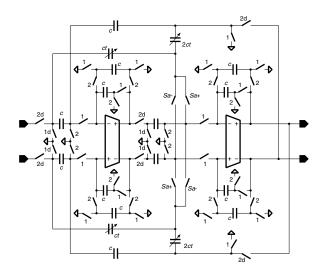

The resonator architecture shown in Fig. 1(a) can be implemented using fully differential switched-capacitor circuitry as illustrated in Fig. 4. Longo's unit delay structure [8] is used to realize the resonator. A two-phase clock and its delayed version, labeled as "1", "2" and "1d", "2d" in the schematic diagram, control the unit delay and feedback paths. NMOS switches are applied at the junctions, which are connected to the virtual ground. CMOS switches are used for the rest on the signal paths. The delayed clock scheme makes the CMOS switches operate slightly later than the NMOS ones, in order to reduce the clock noise injection effect [6]. This is because the summing junctions at the amplifier input

Fig. 3. (a) Calculated NTF frequency responses, and (b) Simulated power spectrum densities (PSDs) of the 4<sup>th</sup>-order VCF BPSDM, normalized to the sampling frequency  $f_s$ .

nodes are disconnected by the NMOS switches, when the CMOS switches start operating with large clock noise injection. The feedback paths are controlled by switches Sa+ and Sa-, corresponding to positive and negative values of the tuning parameter a, respectively.

Fig. 4. Switched-capacitor circuitry realization of the resonator shown in Fig. 2.

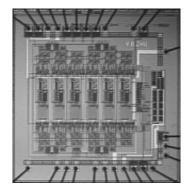

The fourth-order VCF BPSDM layout, implemented in a  $1.5 \,\mu\text{m}$  standard CMOS process, is shown in Fig. 5. Two extra amplifiers are used for subtraction of the feedback signals from the input before the input signals are fed into the resonators. The value of *a*, *c*<sub>1</sub> and *c*<sub>2</sub> are realized using ratios of capacitances. The whole chip contains six cascaded unity delay cells, a single-bit quantizer, switch and capacitor arrays, and a non-overlapped clock generator. The centre frequency is tuned by a 4-bit control word that provides total 9 different centre frequencies, distributed between 0.1 and 0.4 normalized frequencies.

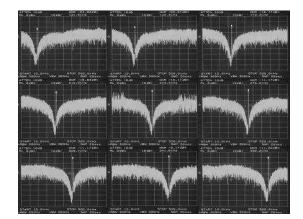

The fabricated chip operates at 1 MHz sampling frequency, and drains 40 mA current from  $\pm 2.5$  V voltage supplies. The measured output spectrums at the nine different centre frequencies are show in Fig. 6. The correct quantization noise shaping validates the algorithm and design methodology. The SNR is 61 dB, calculated from the output spectrum at the centre frequency of 400 kHz, and an oversampling ratio of 64.

Fig. 5. Microscope image of the modulator.

Fig. 6. Measured PSD of the 4<sup>th</sup>-order VCF BPSDM at 9 different centre frequencies (10dB/div).

## IV. CONCLUSIONS

The design of a fourth-order VCF BPSDM is described in this paper. The modulator is based on a tunable resonator controlled by a single parameter, which is feasible for circuit realization. The prototype chip implemented in a 1.5  $\mu$ m CMOS process presented a stable modulator at the nine different centre frequencies. By using the proposed algorithm, design methodology, and a more advanced fabrication process, a much faster bandpass modulator operating at 100 MHz for a monolithic multi-channel HF digital receiver is indeed achievable.

#### REFERENCES

- Raghavan, G., Joseph, J., Walden, R., and Posey, W., 'A bandpass sigma delta modulator with 92 dB SNR and center frequency continuously programmable from 0 to 70 MHz', *IEEE ISSCC*, 1997, pp.214-215

- [2] Shoaei, O., and Snelgrove, W., 'Design and implementation of a tunable 40 MHz-70 MHz Gm-C bandpass sigma-delta modulator', *IEEE Trans. Circuits Syst. II*, 1997 44, pp.521-530

- [3] Zhu, Y. Al-Sarawi, S., Liebelt, M., 'Variable centre frequency bandpass sigma-delta modulator', SPIE International Symposium on Smart Sturctures, Devices, and Systems, Melbourne, Australia 2002, 4935, pp. 197-204

- [4] Cardelli, L., Fanucci, L., Kempe, V., Mannozzi, F., and Strle, D, 'Tunable bandpass sigma delta modulator using one input parameter', *Electron. Lett.*, 2003, **39**, (2), pp. 187-189

- [5] Kuo, C, Chen, C., Lin, H., and Liu, S., 'A tunable bandpass DS modulator using double sampling', *IEEE ISCAS*, May 2005, pp.368-371

- [6] Schreier, R., 'The detla-signa toolbox for MATLAB', [Online], Available: http://www.mathworks.com/support/controlssv5.shtml

- [7] Norsworthy, S. R., Schreier, R., and Temes, G. C., 'Delta-sigma data converters: Theory, design, and simulation', IEEE Press, 1997, New York

- [8] Longo, L., and Horng, B. R., 'A 15b 30 kHz bandpass sigma-delta modulator', *IEEE ISSCC*, Feb 1993, pp. 226-227

**First Author.** Yingbo Zhu received the B.S. degree from the Physics department, USTC in China, where his research was focused on porous silicon for Opto-electronics devices.

In 1994, he was with Philips Semiconductor Manufacturing Corp of Shanghai as an integration engineer in charge of power MOSFET processes. From 2000 to 2005, he worked in CHiPTec research center at the University of Adelaide, Australia, as a Ph.D student. His research interests include integrated wireless frontend IC and Sigma-Delta modulators.

Currently he is with CHiPTec as a post-doctoral, working on a 60 GHz radio frontend project, and low power wireless receivers, ADCs for phased-array and MIMO applications.

Email: yzhu@eleceng.adelaide.edu.au