## Asynchronous Control Circuit Design and Hazard Generation: Inertial Delay and Pure Delay Models

by

### Nozar Tabrizi

B.S.E.E (Sharif University of Technology) 1980 M.S.E.E (Sharif University of Technology) 1988

A thesis submitted for the degree of

### **Doctor of Philosophy**

in the Centre for High Performance Integrated

Technologies and Systems

(CHiPTec)

Department of Electrical and Electronic Engineering

The University of Adelaide

June 1997

### **Table of Contents**

| 1 | Motiv | vation f | For Asynchronous Circuits1                                         |

|---|-------|----------|--------------------------------------------------------------------|

|   | 1.1   | Introd   | uction 1                                                           |

|   |       | 1.1.1    | Clock skew                                                         |

|   |       | 1.1.2    | Power consumption5                                                 |

|   |       | 1.1.3    | Variable computation time 6                                        |

|   |       | 1.1.4    | Modularity and upgradiblity8                                       |

|   | 1.2   | Organ    | ization10                                                          |

| 2 |       |          | traints and Design Techniques of Asynchronous Control              |

|   |       |          |                                                                    |

|   | 2.1   | Introd   | uction                                                             |

|   |       | 2.1.1    | Huffman classical method                                           |

|   |       | 2.1.2    | Speed independent circuits                                         |

|   |       | 2.1.3    | Delay insensitive circuits                                         |

|   | 2.2   | State b  | pased techniques                                                   |

|   |       | 2.2.1    | Classical Huffman method                                           |

|   |       | 2.2.2    | One-hot coding                                                     |

|   |       | 2.2.3    | Timing requirements in the Huffman methodology                     |

|   |       | 2.2.4    | Friedman and Menon's methods to design multiple input change       |

|   |       |          | asynchronous circuits23                                            |

|   | 2.3   | Burst    | mode or self clocked circuits                                      |

|   |       | 2.3.1    | Burst mode circuits using controlled excitation and edge triggered |

|   |       |          | flip-flops26                                                       |

|   |       | 2.3.2    | Locally clocked asynchronous state machines                        |

|   |       | 2.3.3    | Q-Modules                                                          |

|   |       | 2.3.4    | 3D Asynchronous circuits                                           |

|   | 2.4   | Muller   | 's speed independent circuit theory                                |

|   |       | 2.4.1    | Introduction                                                       |

|   |     | 2.4.2  | Two res     | stricted types of speed independent circuits    | 39             |

|---|-----|--------|-------------|-------------------------------------------------|----------------|

|   |     | 2.4.3  | A flow      | table based speed independent circuit realiz    | ation 40       |

|   |     | 2.4.4  | High le     | vel graph specifications for asynchronous cir   | rcuits 43      |

|   |     | 2.4.5  | Signal t    | ransition graphs                                | 44             |

|   |     | 2.4.6  | Change      | diagrams                                        | 47             |

|   |     | 2.4.7  | STG ba      | sed implementations                             | 49             |

|   | 2.5 | Concl  | usion       |                                                 | 50             |

|   |     |        |             |                                                 |                |

| 3 | Two | Level  | Logic In    | aplementation of Asynchronous Circuits          | s from STGs    |

|   |     |        |             | Delay Model and the Well-Behaved                |                |

|   |     |        |             | ***************************************         |                |

|   |     |        |             |                                                 |                |

|   | 3.1 | Introd | uction      |                                                 | 51             |

|   | 3.2 | Basic  | notions a   | nd definitions                                  | 54             |

|   | 3.3 | Well-b | oehaved e   | nvironment                                      | 56             |

|   | 3.4 | Inhere | nt function | on hazards                                      | 58             |

|   | 3.5 | Multip | ole input o | change high to low dynamic hazards              | 58             |

|   |     | 3.5.1  | Introduc    | etion                                           | 58             |

|   |     | 3.5.2  | Dynami      | c hazards                                       | 59             |

|   |     |        | 3.5.2.1     | Dynamic function hazards (Type 1)               | 61             |

|   |     |        | 3.5.2.2     | Dynamic logic hazards caused by static log      | ic 1-hazards   |

|   |     |        |             | (Type 2)                                        | 63             |

|   |     |        | 3.5.2.3     | Real dynamic hazards (Type 3)                   | 64             |

|   |     | 3.5.3  | Delay b     | ound for critical interconnection lines         | 71             |

|   |     |        | 3.5.3.1     | Critical wire delay restriction and virtual iso | ochronic forks |

|   |     |        |             |                                                 | 72             |

|   |     | 3.5.4  | Dynami      | c hazards in multi-level logic                  | 74             |

|   |     | 3.5.5  | Example     | e                                               | 74             |

|   | 3.6 | Multip | ole input c | change low to high dynamic logic hazards        | 75             |

|   | 3.7 | Static | logic haza  | ards                                            | 79             |

|   | 3.8 | Delay  | hazards u   | ander the well-behaved environment assump       | tion 80        |

|   | 3.9 | Conclu | asion       |                                                 | 81             |

| 4 | Dela | ay Hazards in STG Based Two Level Logic Asynchronous Circuits 83   |

|---|------|--------------------------------------------------------------------|

|   | 4.1  | Introduction                                                       |

|   | 4.2  | A classification of delay hazards                                  |

|   | 4.3  | Static 0-delay hazards                                             |

|   | 4.4  | Static 1-delay hazards90                                           |

|   | 4.5  | High to low dynamic delay hazards99                                |

|   | 4.6  | Conclusion103                                                      |

| 5 | Haz  | ards in Complex Gate Based VLSI Circuits104                        |

|   | 5.1  | Introduction                                                       |

|   | 5.2  | Different types of forks 105                                       |

|   |      | 5.2.1 Isochronic forks                                             |

|   |      | 5.2.2 Delay insensitive forks                                      |

|   |      | 5.2.3 Asymmetric isochronic forks                                  |

|   | 5.3  | Relocation of problematic inverters                                |

|   | 5.4  | Safe cells                                                         |

|   | 5.5  | Delay hazards analysis and verification123                         |

|   |      | 5.5.1 Static delay hazards                                         |

|   |      | 5.5.2 Dynamic delay hazards                                        |

|   | 5.6  | Logic hazards in complex logic gates                               |

|   | 5.7  | Conclusion                                                         |

| 5 | A 7  | Tabular Method for Guard Strengthening, Symmetrization and         |

|   | Oper | rator Reduction for Martin's Asynchronous Design Methodology139    |

|   | 6.1  | Introduction                                                       |

|   | 6.2  | Overview of Martin's methodology for asynchronous logic design 140 |

|   | 6.3  | Circuit realization                                                |

|   | 6.4  | Tabular method                                                     |

|   |      | 6.4.1 Deriving new descriptions: STG and STD                       |

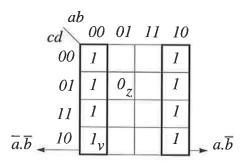

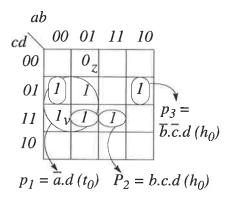

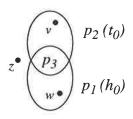

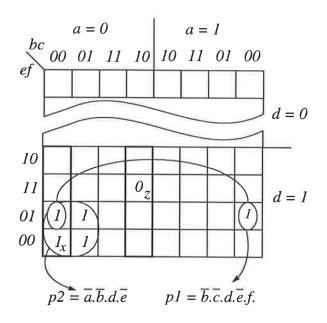

|   |      | 6.4.2 K-Map generation                                             |

|   |      |                                                                    |

|        |        | 6.4.3 Operator extraction                          |

|--------|--------|----------------------------------------------------|

|        | 6.5    | Examples                                           |

|        | 6.6    | Conclusion                                         |

| 7      | Concl  | usion and Further Work154                          |

| Biblio | graphy |                                                    |

| Appen  | ndix A | Parallel Transitions and Distributive Lattices 168 |

|        | A.1    | Introduction                                       |

|        | A.2    | Basic notions and definitions                      |

|        | A.3    | Transition cubes and Poset theory169               |

|        | A.4    | Example                                            |

## **List of Figures**

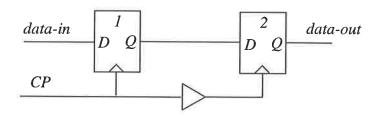

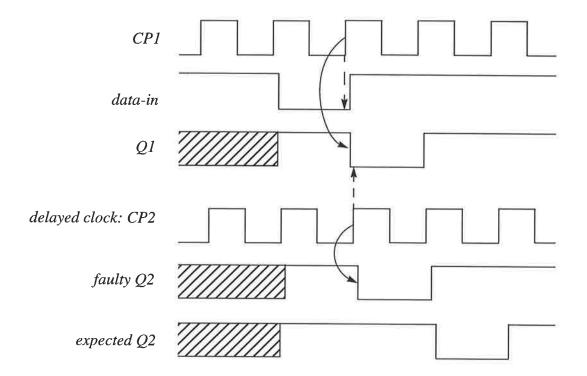

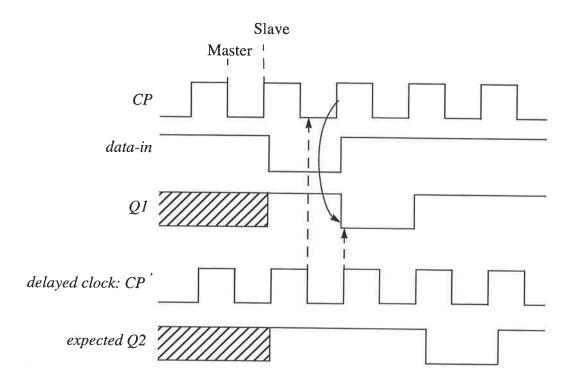

| 1.1  | A shift register suffering from clock skew.                                            | 2   |

|------|----------------------------------------------------------------------------------------|-----|

| 1.2  | Malfunction caused by clock skew                                                       | 3   |

| 1.3  | Faulty triggering avoided using edge triggered master slave flip-flops.                | 4   |

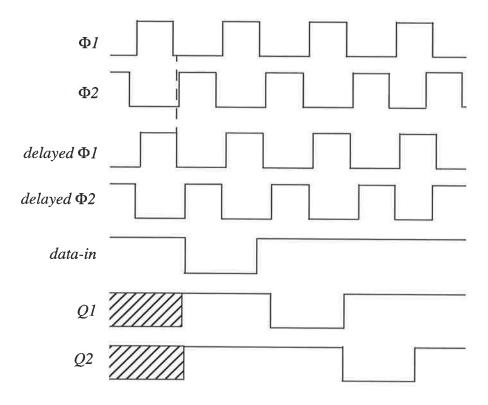

| 1.4  | Faulty triggering avoided using two phase non-overlapping clock.                       | 5   |

| 1.5  | A pipeline structure to demonstrate a better throughput for asynchronous system        | ns. |

|      | The control unit has not been shown here.                                              | 7   |

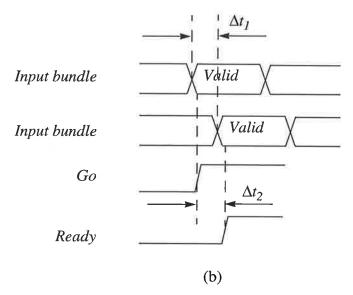

| 1.6  | Bundled data model with two wire handshake, (a) modelling delay in a                   |     |

|      | processing element, and (b) timing diagram.                                            | 8   |

|      |                                                                                        |     |

| 2.1  | (a) Huffman model for asynchronous circuit, (b) the sequential counterpart             | 16  |

| 2.2  | Flow table design                                                                      | 17  |

| 2.3  | An asynchronous circuit behaviour partially modelled by a flow table                   | 18  |

| 2.4  | Critical race as a result of multiple state variable change.                           | 19  |

| 2.5  | Direct implementation of a partial flow table using one-hot coding                     | 21  |

| 2.6  | Multiple input change: second interpretation.                                          | 23  |

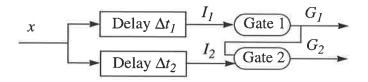

| 2.7  | Circuit M' is driven by both primary and delayed inputs.                               | 25  |

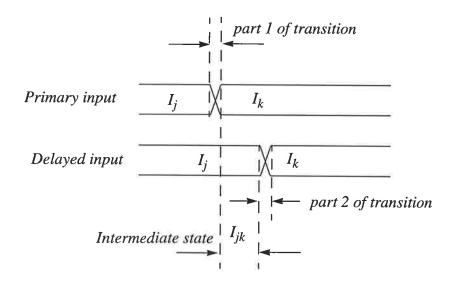

| 2.8  | The timing of the Input transition $I_J \rightarrow I_K$ for the circuit in Figure 2.7 | 25  |

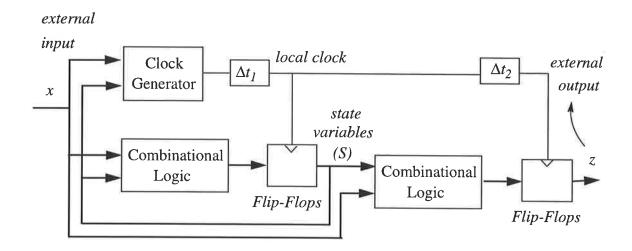

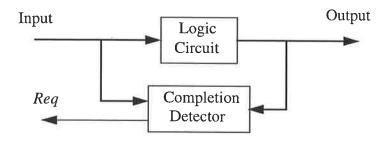

| 2.9  | A general block diagram of burst mode circuits introduced by Chuang and Das.           | 27  |

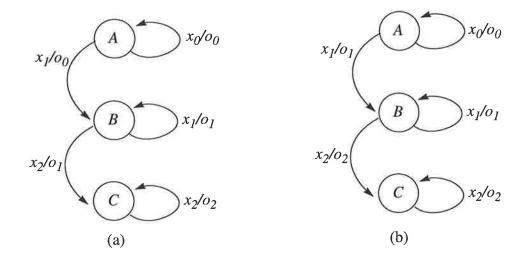

| 2.10 | (a) Moore type and (b) Mealy type asynchronous state graph                             | 28  |

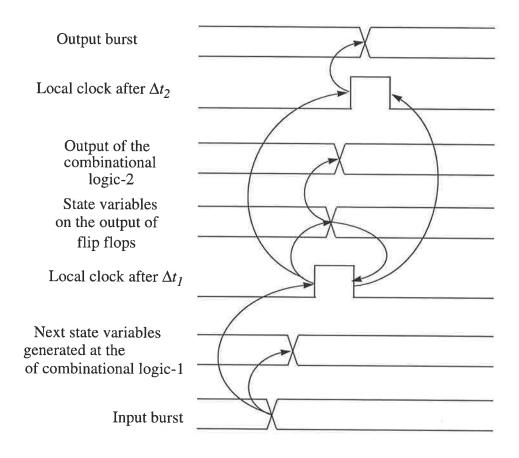

| 2.11 | A general timing diagram corresponding to Figure 2.9.                                  | 29  |

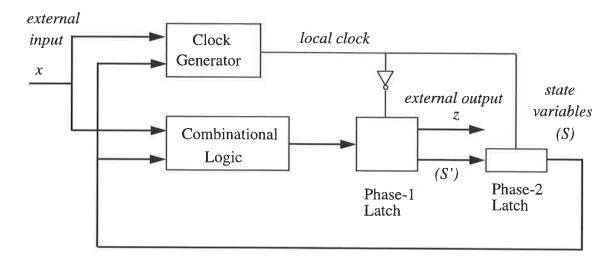

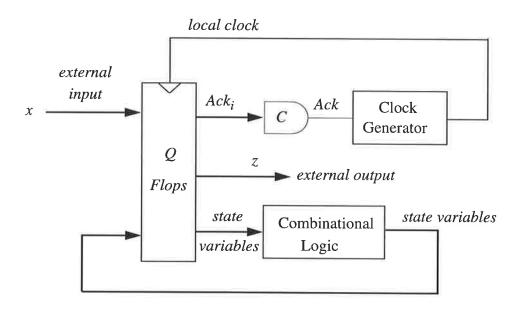

| 2.12 | The general model of locally clocked asynchronous state machines                       | 30  |

| 2.13 | A general timing diagram for locally clocked asynchronous state machines               | 31  |

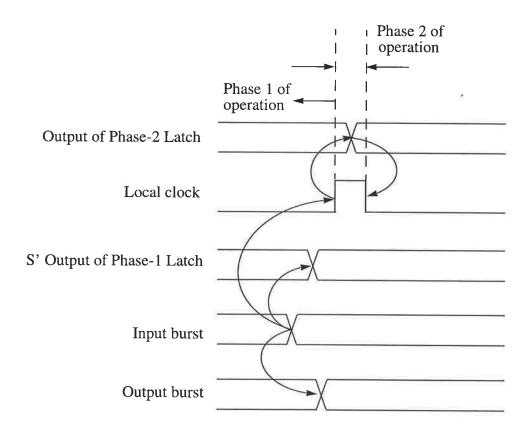

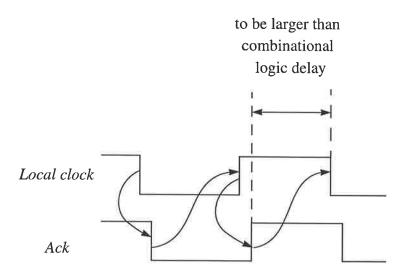

| 2.14 | A general block diagram of a Q-module.                                                 | 32  |

| 2.15 | Semi-delay insensitive timing diagram of control signals in a Q-module: there is       | 3   |

|      | only one timing constraint                                                             | 34  |

| 2.16 | Multiple input change: parallel transitions.                                           | 35  |

| 2.17 | A restricted order for output signal transitions which is difficult to model in flow   | 7   |

|      | table based techniques.                                                                | 37  |

| 2.18 | (a) An autonomous circuit and (b) its state transition diagram.                        | 38  |

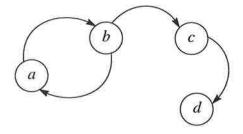

| 2.19 | A symbolic state transition diagram. The equivalent states are {a,b}, {c} and {d}   |

|------|-------------------------------------------------------------------------------------|

|      |                                                                                     |

| 2.20 | A general block diagram of Armstrong et al.'s design method41                       |

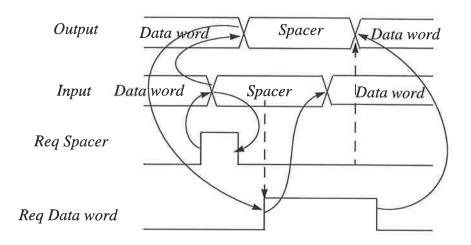

| 2.21 | Timing diagram for the data-spacer method                                           |

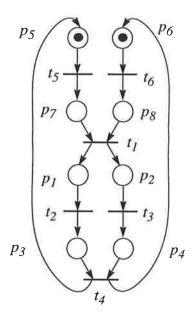

| 2.22 | A Petri net modelling the behaviour of the Muller-C element                         |

| 2.23 | (a) A state machine Petri net, (b) the corresponding STG                            |

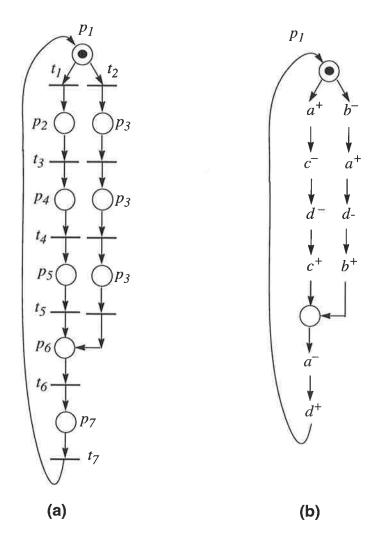

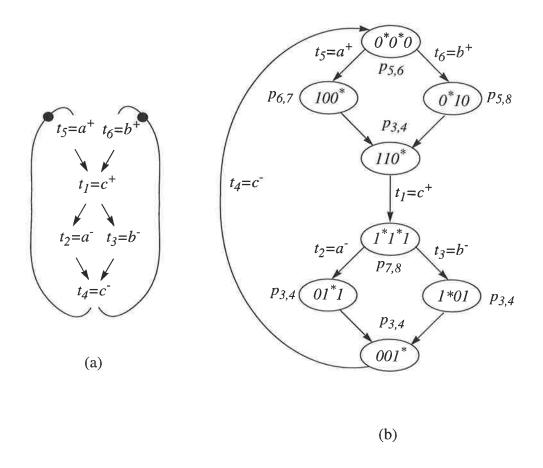

| 2.24 | (a) The STG corresponding to the Petri net in Figure 2.22 with proper               |

|      | interpretation for the transitions, and (b) the resulting STD46                     |

| 2.25 | (a) A change diagram, and (b) the corresponding STD48                               |

|      |                                                                                     |

| 3.1  | Parallelized STGs allow output signal to fire concurrently with input transitions   |

|      | even under well-behaved environment assumption 57                                   |

| 3.2  | High to low dynamic hazard caused by one $h_0$ -type p-term 60                      |

| 3.3  | A transition cube (the whole map) with on-set vertices not covered by one cube.62   |

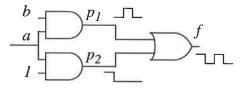

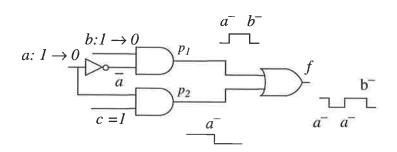

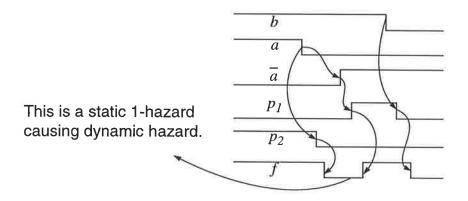

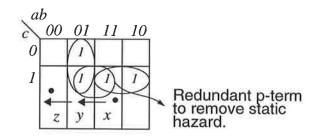

| 3.4  | Dynamic hazard caused by static hazard                                              |

| 3.5  | TCP or prime implicants, either can be used to avoid static hazards                 |

| 3.6  | High to low real dynamic logic hazard generation in unrestricted delay model 65     |

| 3.7  | Graphical representation demonstrating $t_0$ and $h_0$ p-terms participating in a   |

|      | possible 1-0 dynamic hazard                                                         |

| 3.8  | An example demonstrating how an overlapping $h_0$ p-term is disabled when the $t_0$ |

|      | p-term is disabled                                                                  |

| 3.9  | Dynamic hazard in the absence of wire delay in SOP circuits                         |

| 3.10 | Dynamic hazard caused by static hazard assuming SI model                            |

| 3.11 | Timing diagram showing dynamic hazard caused by static hazard                       |

| 3.12 | K-Map showing the role of static hazard in causing dynamic hazard70                 |

| 3.13 | Static hazard and hence dynamic hazard is now removed under the inertial delay      |

|      | model71                                                                             |

| 3.14 | Inertial delay model does not prevent low to high dynamic hazards71                 |

| 3.15 | Dynamic hazard in the presence of wire delay                                        |

| 3.16 | Multi-level combinational circuit which is still 1-0 dynamic hazard free under                  |

|------|-------------------------------------------------------------------------------------------------|

|      | inertial gate delay model74                                                                     |

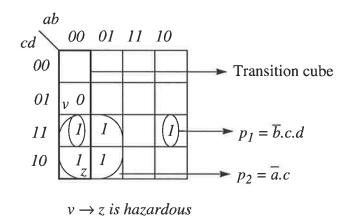

|      | A STG resulting in a possible dynamic hazard on $x = ad + ax + dx$ for $a^- \parallel d^-$ . 75 |

| 3.18 | A transition cube (the whole map) with on-set vertices not covered by one cube                  |

|      | to demonstrate a 0-1 dynamic function hazard                                                    |

| 3.19 | An example demonstrating how an overlapping $h_0$ p-term is disabled when the $t_0$             |

|      | p-term is disabled                                                                              |

| 3.20 | An example demonstrating how an overlapping $h_0$ p-term is disabled when the $t_0$             |

|      | p-term is disabled                                                                              |

| 3.21 | A 0-1 dynamic hazard                                                                            |

| 3.22 | A STG and the resulting two level logic implementation for node $b$ to show                     |

|      | hazard generation due to non-atomic state model                                                 |

|      |                                                                                                 |

| 4.1  | 1-0 dynamic or static 1- (delay) hazard                                                         |

| 4.2  | (a) A partial STG and (b) a typical two level implementation demonstrating delay                |

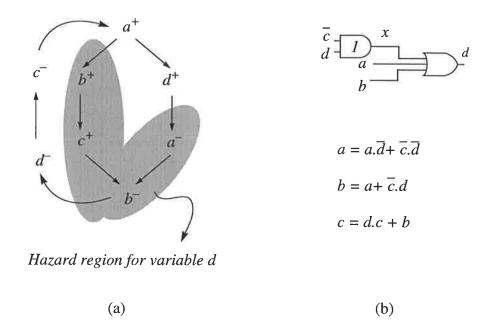

|      | static 0-hazard generation under fork skew assumption                                           |

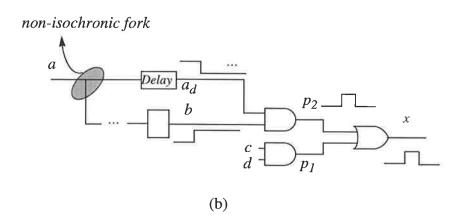

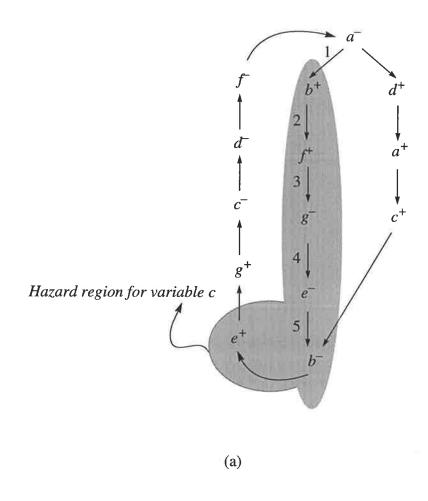

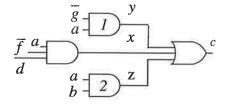

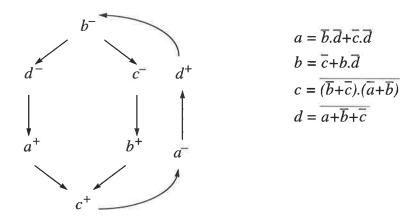

| 4.3  | A STG, the hazard region for node c, and the logic equations of all variables 93                |

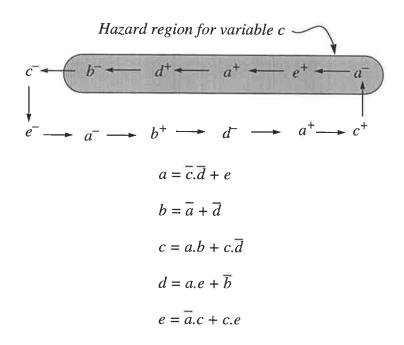

| 4.4  | (a) The STG and hazard region for variable a, and (b) an implementation for node                |

|      | a and the logic equations in Example 4.2. 94                                                    |

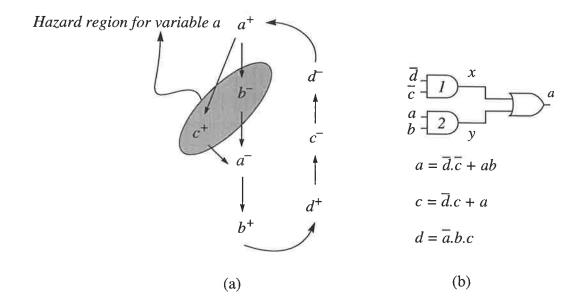

| 4.5  | (a) The STG and hazard region for variable d, and (b) an implementation for node                |

|      | d, and the logic equations in Example 4.3.                                                      |

| 4.6  | (a) The STG and hazard region, and (b) the logic equation and an implementation                 |

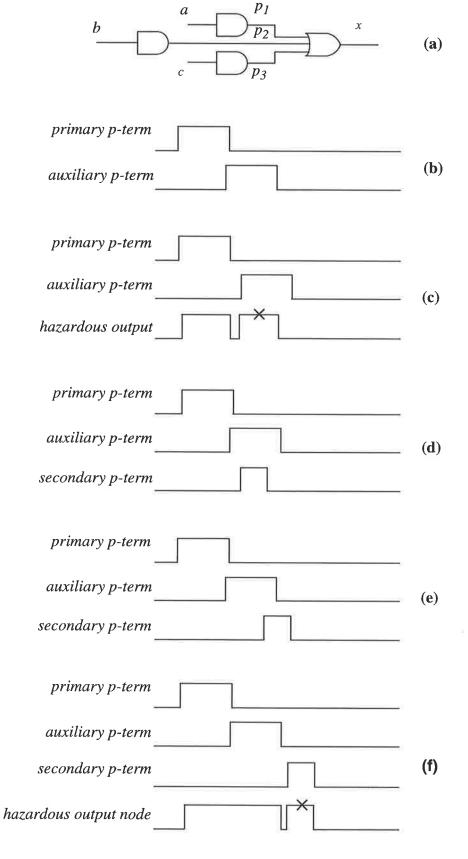

|      | for variable $c$ in Example 4.4                                                                 |

| 4.7  | A STG and the hazard region (the shaded area) for node $b$ (see Example 4.5) 98                 |

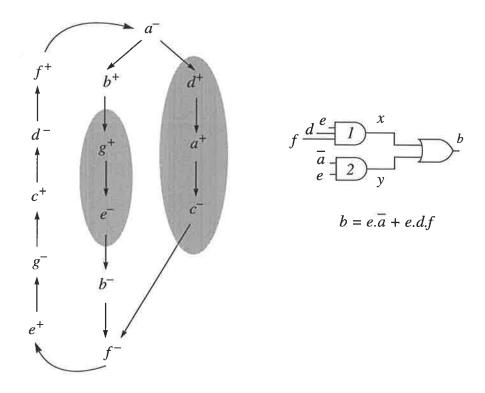

| 4.8  | (a) a typical SOP circuit, (b) - (f) dIfferent delay behaviour of different p-terms in          |

|      | SOPs                                                                                            |

| 4.9  | (a) Two hazard regions for node $c$ , (b) a simple gate implementation for node $c$ ,           |

|      |                                                                                                 |

|      |                                                                                                 |

| 5.1  | Two AND-OR-NOT complex gates realized with (a) real, (b) ideal transistors. 105                 |

|      | A fork with different branch delays                                                             |

|      |                                                                                                 |

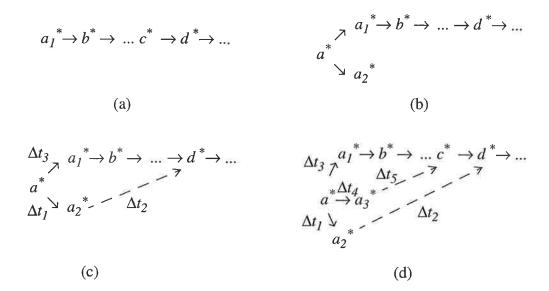

| 5.3  | A set of parallel transitions replacing $x$ when signal $x$ is propagated through a $n$           |

|------|---------------------------------------------------------------------------------------------------|

|      | branch fork                                                                                       |

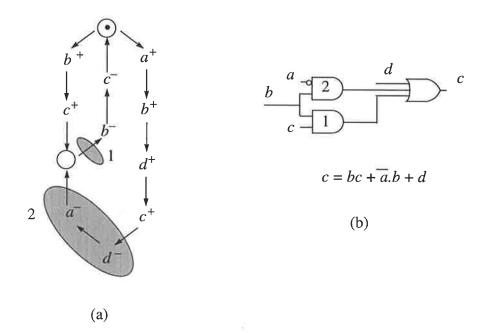

| 5.4  | (a) A STG, (b) the extended STG with a two branch fork for literal a, (c) the same                |

|      | extended STG with the implicit transition $a_2^* \rightarrow d^*$ , (d) a three branch version of |

|      | (c)                                                                                               |

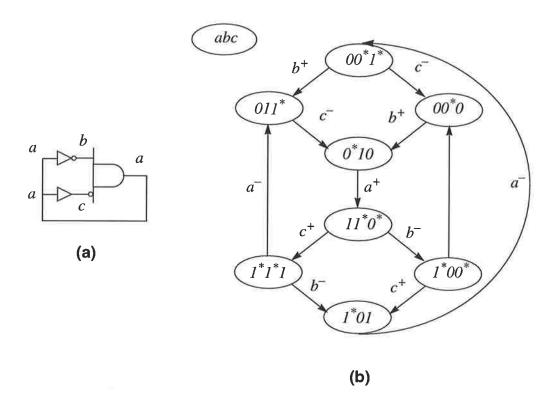

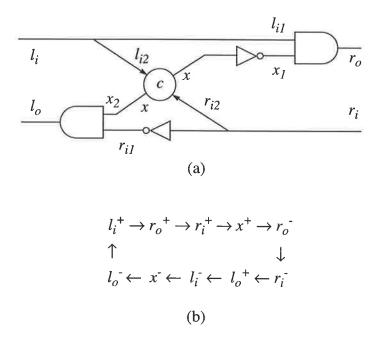

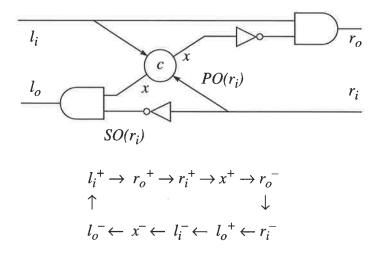

| 5.5  | L/R element: (a) logic circuit, and (b) STG                                                       |

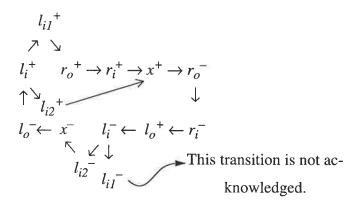

| 5.6  | Both branches $x_1$ and $x_2$ of the isochronic fork $x$ in Figure 5.5 are acknowledged           |

|      | on both transitions                                                                               |

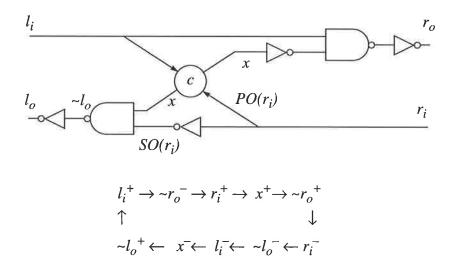

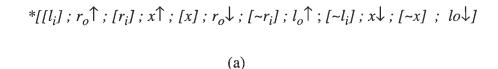

| 5.7  | $STG_{li}$ : the two branch fork $l_i$ is an asymmetric isochronic fork. (See the logic           |

|      | circuit in Figure 5.5)111                                                                         |

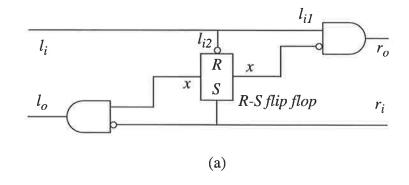

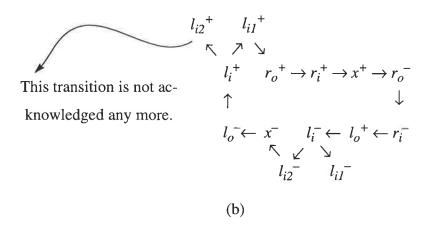

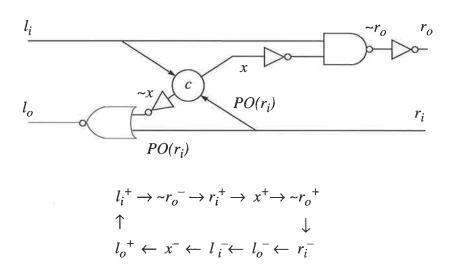

| 5.8  | (a) L/R element implemented with a R-S flip-flop, (b) extended STG for fork                       |

|      | <i>l<sub>i</sub></i> 112                                                                          |

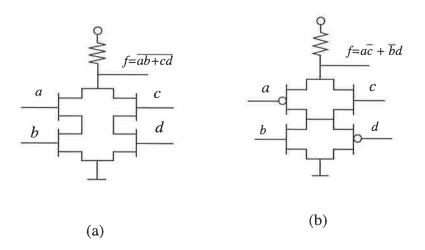

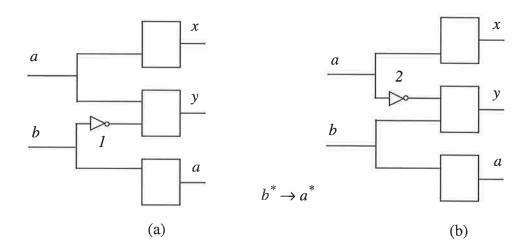

| 5.9  | Using De-Morgan's law a problematic inverter (1) is moved to a asymmetric fork                    |

|      | (2)                                                                                               |

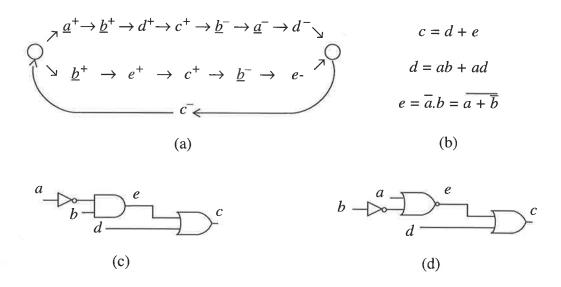

| 5.10 |                                                                                                   |

|      | Law, (a) STG, (b) logic equations, (c) and (d) two possible 2-level                               |

|      | implementations                                                                                   |

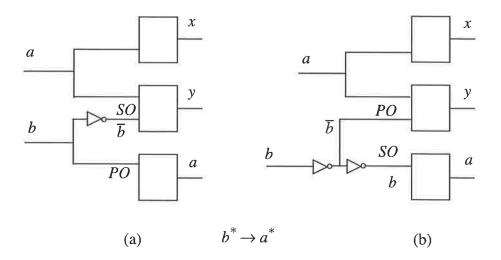

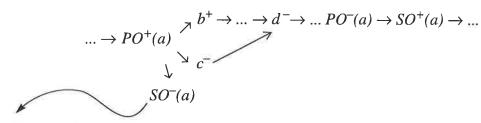

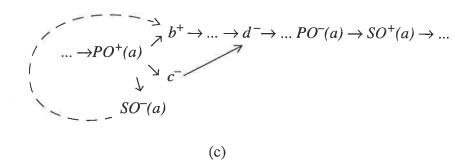

| 5.11 | A hazardous fork on $SO(a)$                                                                       |

| 5.12 | Using double inversion the required order, that is b* and then a*, is guaranteed                  |

|      |                                                                                                   |

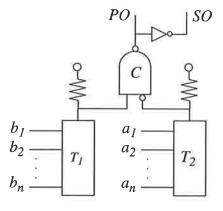

| 5.13 | The basic structure of a safe cell                                                                |

| 5.14 | (a) A partial STG, (b) the corresponding extended STG, and (c) the same STG                       |

|      | with two safe node $b$ and $c$                                                                    |

| 5.15 | A second arrangement for the extended STG in Figure 5.14. Now only one node,                      |

|      | d, needs to be safe                                                                               |

| 5.16 | (a) A partial STG, (b) the corresponding extended STG, (c) the same STG with a                    |

|      | safe node <i>b</i>                                                                                |

| 5.17 | A STG and one corresponding group of logic equations                                              |

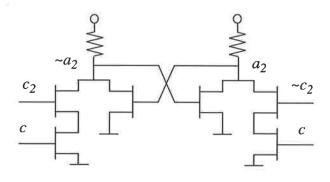

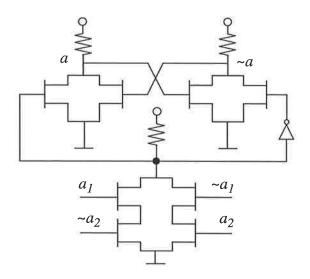

| 5.18 | A modelling node, $a_2$ , implemented as two cross coupled complex gates 121                      |

| 5.19 |                                                                                                   |

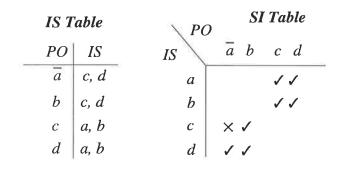

| 5.20 | IS and SI Tables. 122                                                                      |

|------|--------------------------------------------------------------------------------------------|

| 5.21 | Four possible signal transitions and the corresponding literal transition graphs.127       |

| 5.22 | L/R element: logic circuit and STG                                                         |

| 5.23 | Complete STG and SOP-NOT implementation of L/R element                                     |

| 5.24 | Complete STG and modified implementation of L/R element                                    |

| 5.25 | (a) Literal transition 1-2 from Figure 5.21, (b) and (c) two possible positions for        |

|      | the third transition, $PO(x)^+$                                                            |

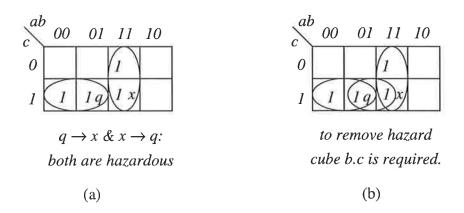

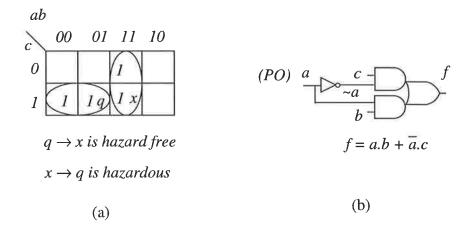

| 5.26 | In simple gate based SOPs (a) both transitions $q \to x \& x \to q$ are hazardous, (b)     |

|      | a redundant cube b.c is introduced to remove the hazard.                                   |

|      |                                                                                            |

| 5.27 | (a) The immunity of complex gates against single input change static hazards, (b)          |

|      | a typical logic diagram                                                                    |

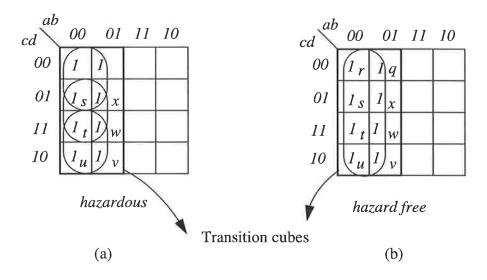

| 5.28 | (a) Hazardous and (b) hazard free multiple input (static 1-hazard) in simple gate          |

|      | based SOPs                                                                                 |

| 5.29 | Hazardous and hazard free multiple input change (static 1-hazard) in complex               |

|      | gate based SOPs                                                                            |

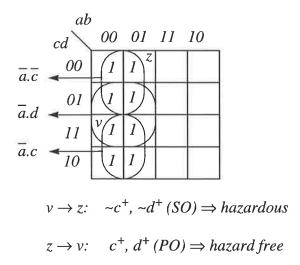

| 5.30 | Multiple input low to high dynamic hazards in simple gate based SOPs 137                   |

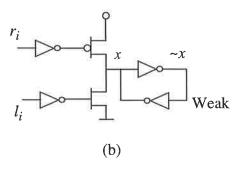

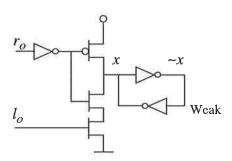

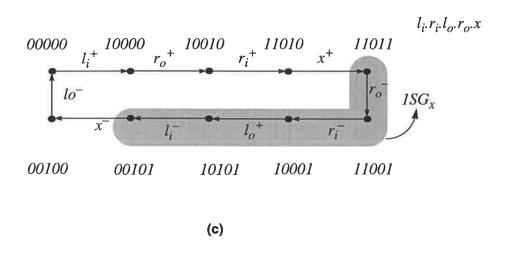

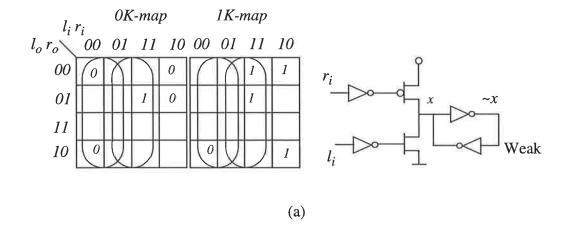

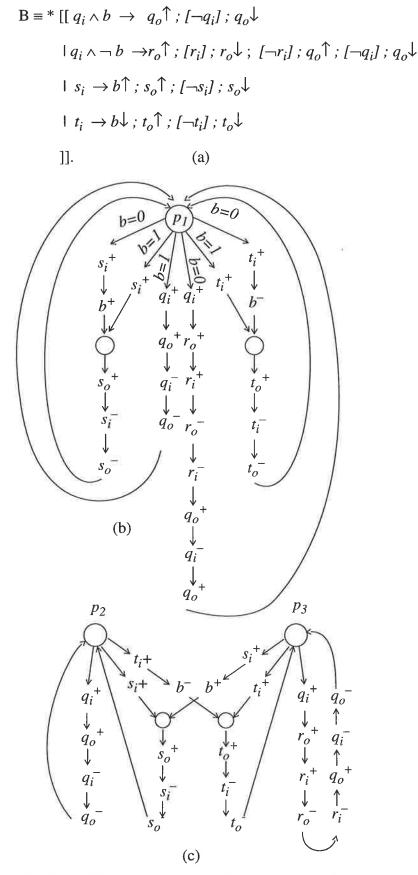

| 6.1  | (a) The output of the handshake expansion of the L/R element. Variable $x$ has             |

|      | been introduced to provide the circuit with enough memory, (b) an                          |

|      | implementation for variable x (see Example 6.1)141                                         |

| 6.2  | A complex gate implementation for the state holding logic operator $x = r_0 + x \cdot l_0$ |

|      |                                                                                            |

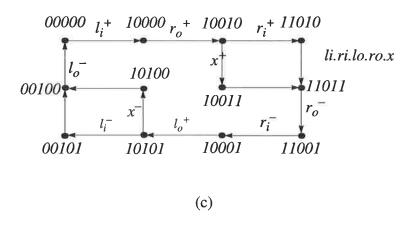

| 5.3  | (a) Output sequence, (b) STG and (c) STD for Example 6.1                                   |

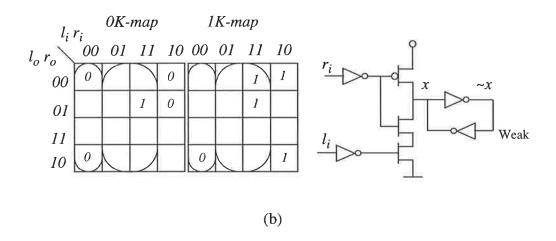

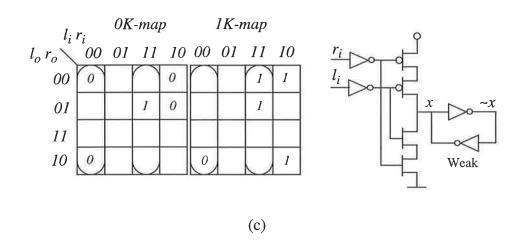

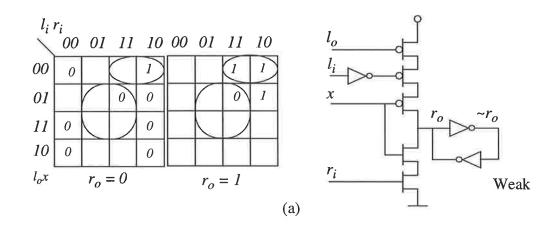

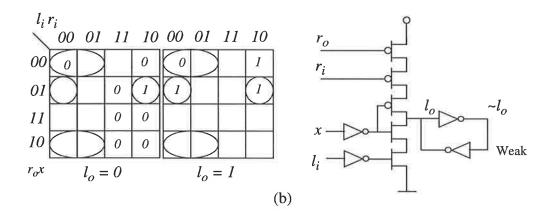

| 5.4  | K-Maps and logic circuits realising state holding node $x$ , assuming shared use (a),      |

|      | disjoint use (b) and not full use (c) of don't cares in Example 6.1                        |

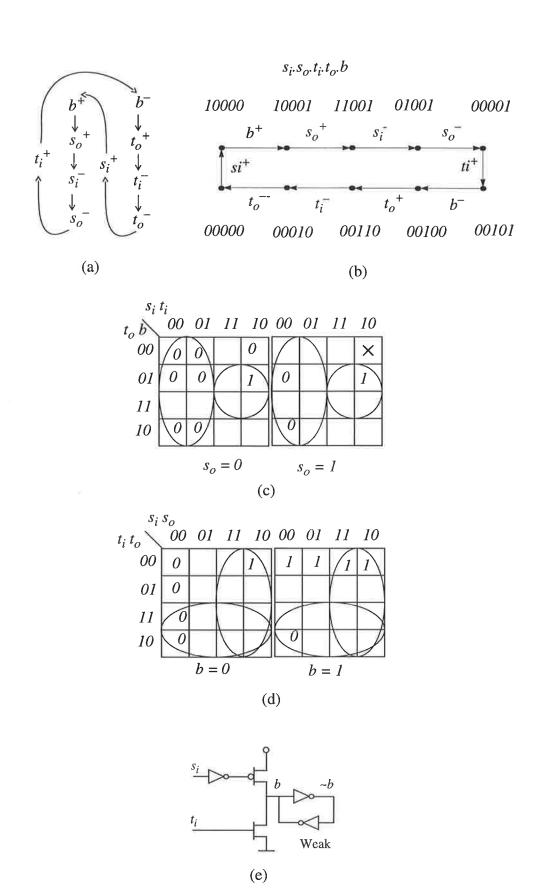

| 5.5  | Output sequence (a), STG (b), and STD (c) for Example 6.2                                  |

| 5.6  | K-map pairs and corresponding circuit realizations for Example 6.2                         |

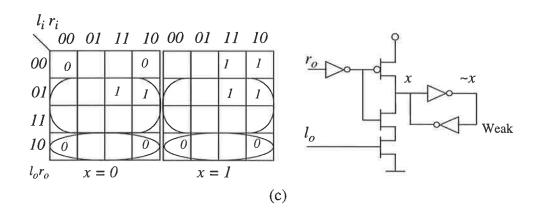

| 5.7  | (a) Compiled program, (b) the corresponding STG, and (c) the reshaped STG for              |

|      | Example 6.3                                                                                |

| 6.8         | (a) Partial STG, (b) the corresponding STD, (d) K-maps and (e) circuit diagram    |  |

|-------------|-----------------------------------------------------------------------------------|--|

|             | (an RS-Flip-Flop) for variable $b$ (c), and K-maps for variable so (c) in Example |  |

|             | 6.3                                                                               |  |

|             |                                                                                   |  |

| <b>A.</b> 1 | Transition cube is $a = 1$ for transition $1010$ (s) to $1101$ (x)                |  |

| A.2         | Hasse diagram for the transition cube shown in Figure A.1                         |  |

#### **Abstract**

The distribution of global clock signals in increasingly complex digital integrated circuits is considered to be a limiting factor in the near future. Clock skew, high power clock drivers, area penalty for global clock routing and a safety margin for clock period are the major factors giving rise to this limit. As an attempt to cope with this shortcoming, asynchronous methodologies have been considered a reasonable successor for the traditional synchronous technique by many researchers since the mid 1980's. However, the remedy, as a general rule, carries its own drawbacks. The major problem in asynchronous design techniques is the generation of possible spurious signal transitions which can easily cause a faulty state change and hence a permanent malfunction in the whole system. There are two usual methods to avoid these problematic signal transitions or *hazards*.

- Delays which may be inserted to balance delays in different signal paths (that is hazard prevention), or to absorb<sup>1</sup> spurious transitions (that is hazard diminishing).

Both approaches suffer from some overhead in terms of area and performance.

- 2. Introducing redundancy is another common technique for preventing hazards. This covers a vast area of research work from introducing redundant states as an attempt to eliminate races in the classical Huffman methodology, to some recent research work of gate level implementation of speed independent circuits.

One major objective in this Ph.D thesis is to relax the hazard problem through a third avenue, that is considering a realistic delay model. Although some researchers have assumed the inertial delay model in their work, this delay model has not been extensively investigated to uncover its effect on the existence of hazards.

We investigate two level logic synthesis of asynchronous circuits from STGs under the *inertial gate delay model* and the well behaved environment. We show that *multiple input high to low dynamic logic hazards* are ruled out under the inertial gate delay model in two level SOP logic circuits. Multiple input low to high dynamic hazards are then studied under the same conditions and it is shown that this type of hazard is unlikely to occur under the inertial gate delay model unless a liberal delay flexibility is required between the first level AND gates of SOPs.

<sup>1.</sup> Only inertial delay can be used for this purpose.

In the next stage of our work we assume the isochronic fork model for interconnection networks and first show that delay hazards are considerably reduced in two level SOP circuits under the pure bounded delay model. The gate delay model is then restricted to inertial and it is shown that delay hazards are further reduced and limited to virtually one type only.

The second major goal in this thesis is focused on design methodologies and hazard free implementations based on redundant logic where the inertial delay model does not help to avoid hazards.

- 1. Delay hazards are analysed in complex gate based implementations which may only be caused by inverters at some inputs under the isochronic fork assumption. We introduce *safe cells*, based on which well-formed STGs can be implemented free of delay hazards with no unrealistic assumptions about physical gates. Although this technique still compromises redundancy for the sake of preventing hazards, we show that it may achieve a significant area gain in comparison with the two-phase RS-implementation method [32] which is one of the few true speed independent implementation techniques that we are aware of.

- 2. Martin's asynchronous design technique [49] is a robust speed independent design methodology. In this thesis we introduce a tabular method to perform the last two of the four phases of Martin's compilation process for asynchronous circuit design. The method is then demonstrated with three examples, illustrating that our systematic method is very straightforward, flexible and convenient to apply, and hence it lends itself to automatic compilation.

In summary the contribution of this thesis is as follows:

We showed that two classes of hazards are ruled out or become considerably less likely to occur under the inertial delay model and the isochronic fork assumption. The significance of these achievements is that the logic designer is relieved of the removing of a major class of hazards.

We introduced safe cells to prevent delay hazards normally caused by inverters at some inputs of complex AND-OR-NOT gates under the unbounded gate delay model. We developed a theorem identifying some sufficient conditions to implement a node with a safe cell. We concluded that safe cells are not dual rail code based and hence can be mixed

with normal AND-OR-NOT gates. The significance of this theory is that the design becomes independent of the delay across inverters which has incorrectly been assumed negligible in some design techniques. This goal is achieved at some area overhead, depending on the number of safe cells used in the circuit.

We developed a tabular method to compile the output of the handshaking expansion stage of Martin's asynchronous design methodology into combinatorial / state holding logic operators in a complementary technology such as CMOS. We showed that this method is a flexible and straightforward alternative for the original method.

### **Statement of Originality**

I declare that this thesis contains no material which has been accepted for the award of any other degree or diploma in any university. To the best of my knowledge and belief, this thesis contains no material previously published or written by any other person, except where the due reference is given in the text of the thesis.

I consent to this thesis being made available for photocopying or loan.

SIGNED:

DATE: 30/6/97

Acknowledgement

I would like to express my gratitude to Professor Kamran Eshraghian my supervi-

sor for his valuable guidance and encouragement during my Ph.D program.

My supervisor Mr. Michael Liebelt deserves special praise for his valuable time and

much helpful advice on this research. Mike was always available to discuss during various

stages of my research. His constructive reviews, comments and suggestions were always

a great support for the progress of the research.

I should thank all academic and administrative staff and also postgraduate students

specially in CHiPTec (the former GaAs) centre in our department who provided me with

such a pleasant environment allowing me to always have enjoyable time during my study

at the University of Adelaide.

I also thank my father, sister and my family. I appreciate their continual support and

encouragement.

I should thank the Ministry of Culture and Higher Education of the Islamic Republic

of Iran for providing me a scholarship and an opportunity for studying in Adelaide.

I also thank the Department of Electrical and Electronic Engineering, the University

of Adelaide for kindly paying my tuition fee for the past two and half years.

Nozar Tabrizi

June 1997

Adelaide

XV

### List of the author's recent publications

- 1. Nozar Tabrizi, Kamran Eshraghian, Michael J. Liebelt, "A 256 x 4 Bit Three Phase GaAs D-RAM.", in Proceedings of the 13th Australian Microelectronics Conference, (Micro'95), pp 306-311, Adelaide, Australia, July 1995.

- Nozar Tabrizi, Michael J. Liebelt, Kamran Eshraghian, "A Tabular Method for Guard Strengthening, Symmetrization and Operator Reduction for Martin's Asynchronous Design Methodology", accepted for publication in the IEEE Transactions on Computers, February 1997.

- 4. Nozar Tabrizi, Michael J. Liebelt, Kamran Eshraghian, "Dynamic Hazards and Speed Independent Delay Model", in Proceedings of the Second International Symposium on Advanced Research in Asynchronous Circuits and Systems, (Async'96), pp 94-103, Aizu, Japan, March 1996.

- 5. Nozar Tabrizi, Michael J. Liebelt, Kamran Eshraghian, "Delay Hazards in Complex Gate Based Speed Independent VLSI Circuits", in proceedings of the Sixth Great Lakes Symposium on VLSI (GLS-VLSI'96), pp 266-271, Iowa, USA, March 1996.

- 6. Nozar Tabrizi, Michael J. Liebelt, Kamran Eshraghian, "Delay Hazards in Two Level Asynchronous VLSI Circuits Synthesised from Signal Transition Graphs", accepted for presentation at the 14th Australian Microelectronics Conference, (Micro'97), Melbourne, Australia.

To the memory of my mother

## Chapter 1

## Motivation for Asynchronous Circuits

#### 1.1 Introduction

Fabrication process dependent and hence unknown parasitic delays inherent in logic gates and manifested as different types of hazards (that is spurious signal transitions), have always been a restricting factor in logic design. In the mature synchronous logic design methodology these parasitic transitions are *hidden* through the use of a global clock signal. However, considering the fast growing technology of integrated circuit fabrication in terms of both chip area and transistor size (and hence transistor count), this signal itself is now becoming a restricting factor: clock skew, high power clock drivers, area penalty for global clock routing and more interesting, a safety margin (in terms of a pessimistically long clock period to guarantee the correct operation under the worst case data, voltage, temperature and process parameters) are the side effects entailing extra design efforts. Al-

though the asynchronous design methodology due to Huffman [32] was proposed in the mid 1950's, the resurgence in asynchronous logic design emerged in the mid 1980's to:

- relax clock distribution problems including clock skew,

high power clock drivers and area penalty for global clock routing,

- reduce power consumption (by eliminating clock drivers and unnecessary signal transitions) and

- provide a better management for chip complexity resulting from the modularity inherent in asynchronous circuits.

In this design methodology, however, the above mentioned spurious signal transitions are manifested as *implementation deviations from specification*, which may not easily be ignored any more and hence are still a major concern in asynchronous logic design.

The following are some of the major benefits in more detail cited for asynchronous circuits:

#### 1.1.1 Clock skew

Considering the clock drivers with limited derive capability and their highly capacitive loads, the clock signal is naturally delayed as it is distributed across the chip. This delay, known as *clock skew*, can easily cause circuit malfunction as demonstrated in Example 1.1.

**Example 1.1:** Consider the shift register shown in Figure 1.1 implemented with edge triggered flip-flops.

Figure 1.1: A shift register suffering from clock skew.

Due to the extra delay caused by the clock driver and the interconnection wires, the active edge of the clock signal is likely to be *seen* by flip-flop 2 after this edge has affected flip-flop 1, violating the hold time requirement of the second flip-flop. The result is incorrect triggering of flip-flop 2 as depicted in Figure 1.2.

Figure 1.2: Malfunction caused by clock skew.

Notice that the data transferred from flip-flop 1 to flip-flop 2 does *not* undergo such a delay to counteract the clock skew, as the former is a *local* signal as opposed to the clock signal which is *global*.

#### Remedy to clock skew side effects

Normal level triggered flip-flops do not help at all, as clock skew can make the slave of flip-flop-1 and master of flip-flop-2 become transparent simultaneously resulting in a similar malfunction to that described above.

There are two solutions to solve this problem:

#### 1- Edge triggered master-slave flip-flops

As the name implies these flip-flops are not level sensitive any more. Figure 1.3 shows how these flip-flops avoid malfunction caused by clock skew.

Figure 1.3: Faulty triggering avoided using edge triggered master slave flip-flops.

Let negative and positive edges of the clock signal trigger master and slave stages, respectively, of all flip fops in the chip. Notice how faulty triggering is avoided now: When the second stage samples its input through its master stage (that is the negative transition of the clock signal), the slave of the preceding stage is expected to trigger (and hence to change the input data of the second stage) half a period later, under conditions of no clock skew. Therefore, clock skew will not cause any malfunction as long as it does not exceed half the clock period, which may be chosen sufficiently long to guarantee safe operation. However edge triggered flip-flops are too complex to be normally considered for use in VLSI implementations.

The usual technique to cope with clock skew in VLSI implementations is the two phase clocking scheme [92]. Recall that the problem with level triggered master slave flip flops is caused by too small a gap between the time slots enabling slave and master stages, resulting in simultaneous transparency of slave stage n and master stage n+1. This problem can be solved if the gap is made controllable and hence sufficiently wide, that is a two phase non-overlapping clocking strategy as shown in Figure 1.4.

Figure 1.4: Faulty triggering avoided using two phase nonoverlapping clock.

Notice how the overlapping de-active region following  $\Phi I$ , that is the *dead time*, guarantees that a master stage and the preceding slave stage will not become transparent simultaneously. In other words as long as the clock skew does not exceed the dead time the operation of the flip-flop may be considered safe. However, the dead time is under the designer's control, so, safe operation can be guaranteed by choosing a sufficiently long dead time, no matter how long the clock skew is. The dead time itself is the obvious price to achieve this safety. The point is that as clock frequency and chip size increase, resulting in an increase in clock skew, the inefficiency caused by the clock skew, (that is the ratio of the dead time to the clock period) is increased as well. That is why clock skew is considered a major limiting factor as chip size and clock frequency are increased.

#### 1.1.2 Power consumption

Considering the market demand for portable electronic products and environmental concerns, low power consumption is becoming a major issue in electronic circuit design. Asynchronous circuits seem promising in this aspect as well. This advantage stems again from the global clock signal being totally eliminated in this methodology. Recall that in

synchronous circuits the global (two-phase) clock signal has to be distributed across the chip and regularly trigger all synchronous memory elements, while many of these elements do not undergo any change in every clock signal transition. The net effect is that a considerable amount of power is wasted during every clock cycle. As an example the second-generation Alpha super scaler micro processor from Digital Semiconductor [22] dissipates 50 Watts from a 3.3V supply at 300 MHz. Notice that an asynchronous circuit is free of such a high frequency signal transition and its direct consequence, high dynamic power dissipation, in the current CMOS technology. More precisely, there is no signal transition other than required by the specification in an asynchronous circuit. So it makes sense to presume that an asynchronous circuit operates at the minimum possible dynamic power dissipation for a given implementation technology.

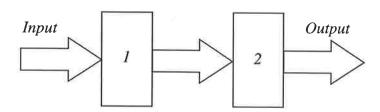

#### 1.1.3 Variable computation time

Some asynchronous systems take advantage of data paths with true completion signals or *self-timed* logic [73] for each computational module<sup>1</sup>. This grants the unique privilege to each module to notify its environment as soon as the result of the computation becomes available. The overall effect may be a better performance for asynchronous systems as shown in the following idealized example.

Consider a *n*-stage pipeline with only one single data item. In the synchronous version the data word has to spend one clock cycle in every stage no matter how long the real process time is. However in a self-timed asynchronous version the data word will leave every stage as soon as the corresponding process terminates. The situation becomes more complex with non-empty pipe lines. Consider the two stage pipeline shown in Figure 1.5.

If the pipeline is synchronous the clock period has to be chosen as  $Max[(tm_1), (tm_2)]$ , with some safety margin, where  $tm_1 = Max$  (computation time-1) and  $tm_2 = Max$  (computation time-2) represent the worst case propagation delay time of the computational modules 1 and 2, respectively. Input data, voltage, temperature and process parameters are the parameters that determine worst case operation time. This of course is too pessimistic (but the most convenient method) to determine the clock period, as not all fabricated chips will operate at the maximum permissible temperature, nor under the worst case process pa-

<sup>1.</sup> This of course incurs some area and performance penalty, as the data path has to have some redundancy. The common technique to realize self-timed data path is *Differential Cascade Voltage Switch Logic*, *DCVSL* [31].

Figure 1.5: A pipeline structure to demonstrate a better throughput for asynchronous systems. The control unit has not been shown here.

rameters. Furthermore, not all clock cycles have to be wide enough to accommodate the worst case computation. Considering this worst case performance the latency and throughput of the synchronous pipeline is determined as  $2 \times Max$   $(tm_1, tm_2)$  and  $\frac{1}{Max(tm_1,tm_2)}$  respectively.

Now consider the asynchronous alternative with a full pipeline where the processed data in stage one does not have to wait for some pre-specified period of time to start the second round of processing in stage two. That is the output of stage one will proceed to stage two as soon as it becomes available provided that the following stage is ready as well to receive data. This clearly reduces the latency and increases the throughput of the pipeline. Assuming an average of half of the maximum delay time for the modules, the average latency and throughput can ideally be improved by a factor of two.

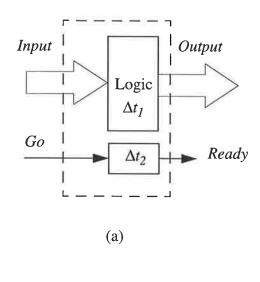

It is interesting to note that speed is adapted to the current operating circumstances of asynchronous circuits and hence is improved even in the absence of true completion signals for data paths. In such cases the delay of computational units are simulated by a fixed delay element with some safety margin as shown in Figure 1.6.

This technique which is to satisfy the timing constraints in the bundled data model in Micropipelines [75], although it lacks the data dependency flexibility introduced by true completion signal generation, still offers an adaptive operation speed, as both the data path and the corresponding delay element are under the same environmental conditions, that is process parameters and temperature. Therefore, the resulting design need not suffer from an extra safety margin to take the worst case process parameter and temperature into consideration. This is in contrast to synchronous circuits where the fixed period of the clock signal has to be sufficiently long to cope safely with the worst case process parameters and temperature.

Figure 1.6: Bundled data model with two wire handshake, (a) modelling delay in a processing element, and (b) timing diagram.

#### 1.1.4 Modularity and upgradiblity

Asynchronous systems are known to be modular, as a module in such a system may be replaced with an upgraded version with no concerns about the environment of that module. This, however, is not the case with synchronous systems. Consider replacing a register in such a system, where some timing characteristics like *set up time* and *hold time* of the replacing module must be taken into consideration and verified against the environment requirements before such a replacement is performed legitimately.

In synchronous systems there would be no point in replacing a slow Adder, for ex-

ample, with a faster one if the bottleneck is known to be somewhere else, say, the multiplier of the system. Self-timed asynchronous systems, however, are more susceptible to an easy upgrading. In the above example since the computation time of all modules are data dependent and hence variable, a fast Adder might result in a better performance, as under some specific conditions the bottleneck may happen to be determined by the Adder itself.

This flexibility of asynchronous systems is manifested as the ease of technology migration as well. A robust asynchronous design works under several different technologies during the life time of the product.

Despite these interesting characteristics, asynchronous circuits still suffer from some drawbacks:

- 1- Asynchronous circuits are more difficult to design. This is primarily due to taking care of the transient response of gates which can easily result in faulty operation in asynchronous circuits. While in synchronous circuits the transient response is hidden by sufficiently wide clock pulses, every asynchronous design technique assumes one type of restriction or another which limits one or more of:

- 1.1- the operation environment, such as single input change at a time in the classical Huffman methodology, or the non-subset requirement for two input bursts enabled in the same state, in the 3D burst mode asynchronous design methodology (see Chapter 2),

- 1.2- the implementation flexibility, such as satisfying the isochronicity of forks in the implementation of speed independent circuits (see Chapter 5).

- 2- The verification of asynchronous circuits is more difficult than synchronous circuits [21][59][6][43], as the design procedure is more complex than that required for synchronous circuits. Furthermore, the verification requirements, time and memory, typically grow exponentially as the complexity of the circuit increases.

- 3- Asynchronous circuits suffer from much more difficult testability as well [42][5]. This is primarily due to the larger number and greater distribution of memory elements in asynchronous circuits. The redundancies introduced in asynchronous circuits such as redundancies to remove hazards, are another

source of complexity in testability of asynchronous circuits. Furthermore, incorrectly estimated transient response of asynchronous circuits may result in permanent non-functionality. More specifically a manufactured chip with a different implemented delay from the specification may not work properly at all, due to a glitch causing an incorrect state change. While in its synchronous counterpart this miscalculation in delays may easily be resolved by decreasing the clock frequency.

4- It is not yet clear whether an asynchronous methodology may result in a net speed gain, due to the overhead incurred by the specific handshaking protocol employed in the methodology, in spite of the partial performance gain due to average case instead of worst case operation discussed above.

#### 1.2 Organization

This thesis is organised as follows:

In Chapter 2 some asynchronous design techniques are reviewed, with an emphasis on the specific delay model in each methodology. We first review state based techniques in Section 2.3 starting with the classical Huffman method and then continue with the first generation extensions to that, namely: one-hot coding, Friedman and Menon's technique, self clocked circuits, Q-modules and 3D asynchronous circuits.

Burst mode or self-clocked circuits are discussed in Section 2.3, which are considered as the second generation extensions to the Huffamn methodology.

In Section 2.4 event based circuits are studied. We start with Muller's theory of speed independent circuits based on Lattice theory, and proceed with a flow table based speed independent design which presents a redundancy based implementation technique to identify end of operation similar to the idea later utilized in self-timed data paths. This technique has been reviewed in this section, only because of its unbounded delay model assumption for logic gates, although it is a flow table based technique. Graph based specifications for Muller's theory (that is signal transition graphs (STGs) and change diagrams (CDs)) are then discussed which are considered as a bridge between the Lattice theory and the theory of Petri nets. This chapter is ended with reviewing some restrictions utilized in some extensions to the original STG based design techniques. A more detailed review of some of these design techniques will be presented in later chapters in order to provide a

deeper background for our work.

This chapter includes some discussions and comparisons between several sources. A good example is the two different interpretations for the notion of multiple transitions which has been covered in Section 2.2.

In Chapter 3, based on the work in [59], we investigate two level logic synthesis of asynchronous circuits from STGs under the *inertial gate delay model* in addition to the above constraints on the environment We show that multiple input high to low dynamic logic hazards are ruled out under the inertial gate delay model in two level SOP logic circuits. We then weaken the zero wire delay restriction and find an upper bound for the delay along critical interconnection wires and hence propose a *virtual isochronic fork* model for interconnection networks. Multiple input low to high dynamic hazards are then studied in two level logic implementations and it is shown that this type of hazard is unlikely to occur under the inertial gate delay model unless a liberal delay flexibility is required between the first level AND gates of SOPs. Static hazards, on the other hand, are shown to not be relaxed under the inertial delay model.

Delay hazards are investigated in two level logic and it is shown that even the well-behaved environment assumption does not necessarily lead to delay hazard free implementations, no matter whether the pure or the inertial delay model is considered. We show that this type of hazard has been overlooked in the design of the STG compiler, SIS [74].

In Chapter 4 we assume the isochronic fork model for interconnection networks and show that delay hazards are considerably reduced in two level SOP circuits under the bounded pure delay model. The gate delay model is then restricted to inertial and it is shown that delay hazards are further reduced and limited to virtually one type only.

In Chapter 5 hazards are analysed in single level logic family under the general pure delay model. We first discuss different types of interconnection forks. Then delay hazards are analysed which may only be caused by inverters at some inputs under the isochronic fork assumption. We introduce *safe cells*, based on which well-formed STGs [59] can be implemented free of delay hazards with no unrealistic assumptions about physical gates. Although this technique still compromises chip area for the sake of preventing hazards, we show that it may achieve a significant area gain in comparison with the two-phase RS-implementation method [33] which is one of the few true speed independent implementation techniques that we are aware of so far. Delay hazards are then analysed in complex

gate based circuits under some gate delay restrictions and hence theorems are developed to identify a subclass of delay hazards. We lastly show how logic hazards are relaxed in this logic class. Notice that these achievements apply to the pure and hence to the inertial delay model as well.

In Chapter 6 we introduce a tabular method to perform the last two of the four phases of Martin's compilation process for asynchronous circuit design. The method is then demonstrated with three examples, illustrating that our systematic method is very straightforward, flexible and convenient to apply, and hence it lends itself to automatic compilation. The technique is independent of the particular delay assumption considered in the design process.

Chapter 7 is the conclusion.

## Chapter 2

# Delay Constraints and Design Techniques of Asynchronous Control Circuits

#### 2.1 Introduction

In this chapter we will consider different delay restrictions in some representative asynchronous design methodologies, as we review and assess the methodologies themselves. These are relevant observations as a major part of the work presented in this thesis is based on some specific delay assumptions.

Asynchronous control circuits are usually classified according to the particular delay model assumed in their synthesis:

#### 2.1.1 Huffman classical method

The Huffman classical method and its extensions like [44][45][46] falling into the first category, assume the bounded but unrestricted gate-wire delay model. It is bounded in the sense that the environment has to know an upper bound on all stray delays (and delay elements if any) to determine the earliest instant of time to apply the next input vector (fundamental mode operation), otherwise the new input may arrive too early disturbing the circuit prematurely and causing a malfunction. As a result, if the value of a delay in a synthesised circuit is increased due to a variation in the process parameters or temperature the timing constraints on the environment must be revised accordingly. A group of these so called delay hazards in two and one level logic circuits are the topic of Chapters 5 and 6, respectively, in this thesis.

This model is also unrestricted in that sense that

1- there is no restriction in the relative values on the gate-wire delays assumed in the circuit. That is in the real chip a gate with an upper delay bound of 100 pico-seconds does not have to operate faster than another gate which has been specified by an upper delay bound of 150 pico seconds. Exceptions to these are some deliberately inserted delay elements to satisfy a particular inequality to guarantee the correct operation.

2- all stray delays can assume either type of models, inertial or pure, or even an inertial followed by a pure, except for delay elements deliberately introduced to absorb spurious transitions (spikes), which have to be of course of inertial type.

#### 2.1.2 Speed independent circuits

The unbounded gate but skew free wire delay (Speed Independent) model was introduced by Muller [57]. In his methodology the bounded delay restriction is lifted from the gate model at the cost of another delay restriction on interconnection wires: the output signal of a gate must be absorbed at all fanout terminals with a negligible skew. This theory also requires an atomic model for all gates, which may not be easily achieved with today's technologies. Notice that both skew free and atomic delay model requirements have been shown to be only sufficient in [50] and [14], respectively, for correct operation.

In some extensions to Muller speed independent theory such as [2] Armstrong not only uses simple logic gates, but a bounded wire delay model as well, of course at the expense of some redundancy and hence area/performance overhead. Similar to Huffman

methods, this technique is flow table based as well, which again differs from Muller's.

#### 2.1.3 Delay insensitive circuits

The most robust asynchronous design technique should obviously assume unbounded gate and unbounded wire delay model, resulting in the so called *delay insensitive* circuits. Although simple gate based delay insensitive circuits have been proven to be very limited [48] there are some delay insensitive synthesis techniques which are based on some specially designed modules with some internal timing assumptions [20] [58], or a one sided delay restriction on a single element [70].

Asynchronous circuit behaviour on the other hand may be classified as state based and event based as well: In the first category starting with Huffman's work and continuing with some extensions [65][66] an intermediate but abstract notion of *state* is explicitly introduced to link the specified inputs to the required outputs, so that at each instant of operation the outputs are determined by the current state and possibly the current inputs. In the event based methodology, however, the logic value of outputs are determined directly by the previous input/output vectors and the current input transitions, that is there is no intermediate layer of state as is the case with the Huffman methodology. As will be discussed in this chapter an interesting difference between these two methodologies is that in the Huffman methodology the initial design usually starts with more states than are really sufficient, that is the initial description is shrunk as the design proceeds, while in the event based methodologies the initial description not only is shrunk, but also is sometimes expanded to solve the CSC problem, described in this chapter.<sup>1</sup>

In this chapter we present a concise but descriptive perspective of some developments in asynchronous design techniques. We start with the Huffman methodology which is more suitable to model choice, and is later developed by Unger [83], and then proceed to its extensions. Then event based techniques will be addressed which are more amenable to model concurrency.

Transition tables in the Huffman methodology may also be expanded by newly introduced state variables to remove races, but not to increase the memory of the network, that is to solve the CSC problem.

#### 2.2 State based techniques

#### 2.2.1 Classical Huffman method

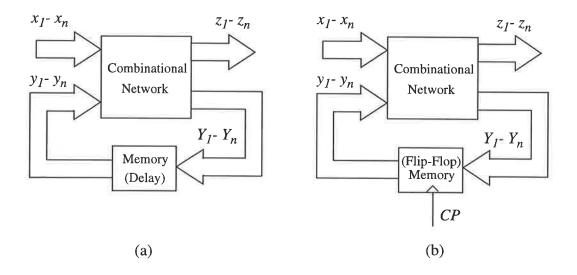

The classical asynchronous design methodology due to Huffman [32] has a close similarity with its synchronous counterpart as shown in Figure 2.1.

Figure 2.1: (a) Huffman model for asynchronous circuit, (b) the sequential counterpart.

In this figure  $x_i$ ,  $z_i$ ,  $Y_i$ , and  $y_i$  represent external input variables, external output variables, excitation variables and state variables, respectively. The principle idea behind both of these techniques is that the outputs of the combinational logic, that is z and Y, depend on (in addition to possibly the current external inputs, in Mealy circuits) some history of the previously applied inputs.

In an asynchronous circuit, starting with a stable state, that is a state in which  $y_i = Y_i$  for all i, upon the arrival of a new input vector, the combinational logic is exposed to the new x vector but the previous y vector due to the delay elements which serve as a short term memory, generating  $Y(x, y_{old})$ . Now if it happens that  $Y(x, y_{old}) = Y(x, Y(x, y_{old}))$  then the whole network has in fact reached a new stable state<sup>2</sup>.

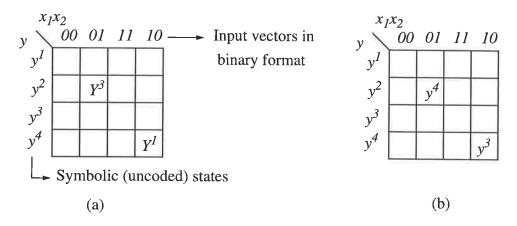

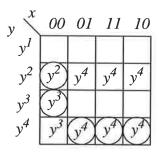

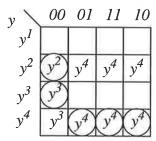

The high level description language in the classical Huffman methodology is a Flow Table (FT) which presents a more qualitative operation principle of the circuit. A FT is in

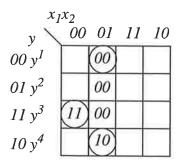

fact a *semi-symbolic Karnaugh map* for the combinational part of the circuit in Figure 2.1-a, where all possible input vectors are laid out horizontally and the *symbolic* internal states are laid out vertically. Each state variable vector  $y^i$  represents a *state* for the circuit. A state concatenated with an input vector is called a *total state*. For example the FT in Figure 2.2-a specifies that for the total state  $y.x = y^2-01$  and  $y^4-10$  the corresponding excitation output of the combinational circuit (that is the excitation variable vectors) would be  $Y^3$  and  $Y^1$ , respectively.

Figure 2.2: Flow table design.

Due to the delay nature of the memory elements which specifies  $y(t) = Y(t + \Delta t)$ , it is more descriptive to replace Y with y in this K-map, resulting in the FT shown in Figure 2.2-b.

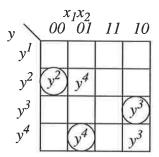

Therefore, starting with a stable state, a FT shows the corresponding next state for every input change. In Figure 2.3 staring with the total stable state  $y^2$ -00, upon the input change of 00 to 01 the circuit changes its state from  $y^2$  to  $y^4$  and eventually settles in the stable total state  $y^4$ -01. Stable states are encircled.

Referring to Figure 2.3 consider the notion of *state*: in order to generate the required output the circuit should first reach the appropriate state. So, the notion of state seems an intermediate stage between external inputs and outputs. The same interpretation is true in Figure 2.1 where the output vector z is a function of both x and y.

<sup>2.</sup> This type of operation is called *normal* mode, as one stable state is reached through only one unstable state. Generally speaking a circuit may pass trough more than one unstable state to stabilise, resulting in a considerable speed penalty.

Figure 2.3: An asynchronous circuit behaviour partially modelled by a flow table.

When the circuit is ready to accept a new input (in the case of the Huffman methodology this happens when the circuit is in a stable state) the environment may have some *choice* of which particular input to apply to the asynchronous circuit.

Notice how *choice* is readily modelled by a flow table. In each stable state all possible choices are tabulated in different columns of the corresponding row.

The first step in the design procedure is to construct a flow table based on the verbal description of the problem. This is rather a non-routine procedure. Different designers may come up with different flow tables with different numbers of states, as it is generally not trivial to intuitively identify equivalent states to close up the flow table at early stages. This problem, however, is greatly relaxed by a mechanical technique for flow tables reduction [68] which normally follows the flow table construction in the standard design procedure. The resulting table has the minimum possible number of states, although it usually has to be expanded again to resolve the critical race problem as described below.

The next step is state assignment, in which unique binary vectors are assigned to each internal state in the simplified flow table just created in the previous stage. Numerical internal states usually introduce the *critical race* problem, in which the correct change of internal state (as a result of an input change) depends on the relative delays of different gates. Much work has been done to avoid critical races, while keeping a particular cost minimum [26][72] [45][80][81].

As an example starting with the total stable state of 1100 in Figure 2.4 the input change to 01 requires both the state variables to change from high to low. However, the circuit will not settle in the correct stable state (that is 0001) if  $y_1$  completes its transition before  $y_2$  fires.

Figure 2.4: Critical race as a result of multiple state variable change.

This problem may always happen if there is a chance for multiple state variable change, revealing the critical role of this stage. An insufficient number of state variables and also inappropriate state coding (even with right number of state variables) may cause circuit malfunction, while a liberal use of state variables results in an inefficient circuit. Furthermore, introducing a (long) sequence of unstable states to make the circuit immune against critical races (that is *multiple transition time encoding*) entails as many passages through the combinational logic as the number of unstable states in the passage, resulting in a considerable degradation of performance, although the idea is straightforward. *Single Transition time* state encoding, on the other hand, entails only one state variable transition in each state change. Therefore, this coding technique not only avoids critical races but entails rippling through the combinational logic unit only once, most likely resulting in the best possible performance.

The final step in the classical Huffman asynchronous circuit design is hazard detection and removal. A hazard is a possible spurious signal transition on the output of a logic gate, which may have different sources. We will discuss this topic in later chapters in more detail.

Efficient computer aided design tools [93] have been developed to automatically perform the different stages of the Huffman design methodology.

#### 2.2.2 One-hot coding

The one-hot coding technique due to Hollaar [29] is another flow table based technique to design asynchronous circuits. Recall that state coding is one of the critical stages in the Huffman methodology, which determines the overall structure of the prospective circuit. An appropriate state coding can remove all critical races with the minimum pos-

sible logic.

The one-hot coding technique totally bypasses the state coding (state variable assignment) stage by using as many state variables as the number of states in the flow table, so that each state is uniquely identified by one state variable asserted to logic high and the rest of the state variables to logic low. This implies one state flip-flop for each state or row of the flow table which of course incurs an exponentially increasing amount of redundancy comparing with encoded states as in Huffman methodology. The major achievement in this state coding technique is that every two adjacent states differ in exactly two bits avoiding any races with a little care as discussed below.

It is concluded in [29] that every excitation variable may be represented as  $Y_n = \overline{R}.y_n + S$ , where  $y_n$  is the corresponding state variable, and  $S \& \overline{R}$ , called transition term and hold term in [28], are two logic functions independent of  $y_n$ . This equation shows that every state variable which represents one state in the one-hot coding can be implemented as a RS-FF with some extra logic. Therefore, unlike the case with the traditional Huffman methodology, one-hot coding approach does not only require state variable assignment, but also has a straight forward implementation as demonstrated here:

Rule 1: A state flip-flop, s, is set if and only if the current state is an immediate predecessor state of s and then a proper input is applied to the circuit specified by the flow table. That is the set input is a two level AND-OR logic function with as many AND gates as the number of immediate predecessors of state s.

Rule one specifies the logic for input S, that is the transition term of the state variable. The logic for input R is determined by Rule 2:

Rule 2: A state flip-flop is reset if and only if starting with that state a state changing input is applied to the circuit according to the flow table. So the reset input needs an OR gate with as many inputs as the number of immediate successor states.

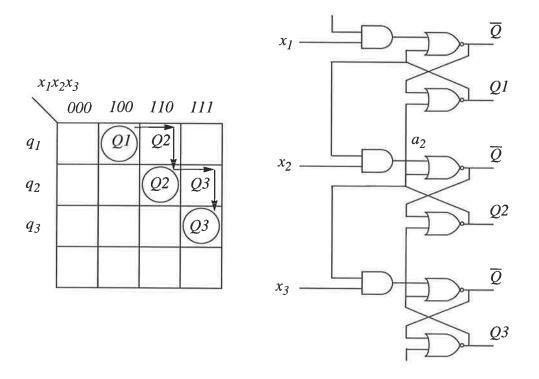

Consider a flow table and the corresponding one-hot implementation shown in Figure 2.5.

Starting with the total state  $Q_1$ -100, suppose that  $x_2$  goes up. This transition is followed by the following sequential transitions:  $x_2^+ \to a_2^+ \to \overline{Q}_2^- \to Q_2^+ \to Q_1^- \to \overline{Q}_1^+$ . This unique order of the transitions which is independent of any relative delays of the gates and or wires guarantees a race free transitions, as the flip flops 1 and 2 may not be

Figure 2.5: Direct implementation of a partial flow table using one-hot coding.

reset both at the same time.

The above technique may not be applicable any more if two states,  $Q_1$  and  $Q_2$ , are immediately reachable from each other, that is  $Q_1 \rightarrow Q_2$  and  $Q_2 \rightarrow Q_1$ . According to the above algorithm, since Q2 is an immediate successor of Q1, Q1 tends to set Q2. Likewise since Q1 is an immediate successor of Q2, Q1 tends to also reset Q2. This holds Q2 in an unstable situation with both outputs at logic high, preventing Q1 from being reset and hence resulting in a deadlock.

This problem is solved by introducing some redundancy to the circuit by either inserting an intermediate state in the flow table, (to make one of the states a non-immediate predecessor of the other one) or adding a product term to de-activate the R input of Q2 and hence let Q2 be pulled down freely.

In addition to structural and race free implementation, Hollaar further shows that his methodology relaxes the fundamental mode restriction so that now two consecutive input vectors in many cases may be applied closer to each other than is required by the traditional Huffman methodology. Notice, however, the main restriction of the bounded delay

model still exists.

#### 2.2.3 Timing requirements in the Huffman methodology

Generally speaking two successive input vectors may differ in exactly one bit, (that is single input change) or multiple bits. The second case has two different interpretation in the literature:

1- All signal transitions occur during some pre-specified maximum (and normally short) time interval. So if the multiple input change  $x_1$   $x_2$   $x_3$ :  $001 \rightarrow 101 \rightarrow 111$  (or  $001 \rightarrow 011 \rightarrow 111$ ) occurs within  $\delta_2$ , the circuit will consider the transitions on  $x_1$   $x_2$  as *simultaneous*, and hence will recognise the three input bit patterns, that is 001, 101 and 111 (or 001, 011 and 111) as *two* successive input vectors, that is 001 and 111. Otherwise they may be considered as *three* consecutive input vectors, that is 001, 101 and 111 (or 001, 111 and 111) as discussed later in this section.

2- The second interpretation of multiple input change is that no matter how close to each other and in whatever order the transitions happen, the circuit reacts to this multiple input change or *input burst* only after all transitions have fired. The primary implication of this interpretation is that starting with a stable state no allowed input burst may be a subset of another legitimate input burst, other wise the circuit would face a non-deterministic situation if the subset transitions occur first.

The usual trend in the classical Huffman methodology is the first interpretation mentioned above, which virtually restricts this method to *single input change*, as simultaneous transitions are not very likely to occur. On the other hand, the new input vector in this methodology can only be applied after all delay elements have reached a steady state, that is every delay element (either explicit or implicit) has identical input and output logic levels. This inherent critical time interval,  $\delta_I$ , categorises this methodology as *bounded* gatewire delay model based<sup>3</sup>, as the environment has to know an *upper bound* for the different delays in the circuit in order to be able to determine a right instant of time to apply the new input vector and avoid too early inputs which may even result in faulty state change. In summary two input vectors are considered *consecutive* if they are at least  $\delta_I$  time units apart. This mode of operation is called *fundamental* [54]. The second critical time interval in this methodology is  $\delta_2$  ( $\delta_I > \delta_2$ ) which identifies simultaneous transitions as being sep-

<sup>3.</sup> as opposed to the unbounded gate delay model to be discussed in this chapter.

arated at most  $\delta_2$  time units apart. Unfortunately, if an input transition satisfies none of these timing constraints, then the circuit reaction is not normally clear [83], unless some provisions like what are discussed in [82] are made.

In the next two sections three techniques are reviewed to relax the problem associated with the first interpretation for multiple transitions, that is to make  $\delta_2$  as large as required. As expected they impose some restrictions on the delay amount of the delay elements used in the design to achieve the goal. However, requiring the input transitions to become complete in some pre-specified time is itself a restriction as well, no matter how long it is. Prolonging,  $\delta_2$ , on the other hand has a direct consequence of slowing the circuit down as now the circuit has to wait for a longer time interval to distinguish between consecutive and simultaneous input transitions.

The second (and more intuitive) interpretation for multiple input change is that all specified transitions can fire in any order and with any spacing. Notice that the flow table is already able to demonstrate this type of parallelism as shown in the partial flow table in Figure 2.6, for the parallel transition  $y^4:11 \rightarrow 00$ . This topic will be discussed in more detail later in this chapter.

Figure 2.6: Multiple input change: second interpretation.

# 2.2.4 Friedman and Menon's methods to design multiple input change asynchronous circuits

Friedman and Menon have proposed three fundamental mode asynchronous design methods in [25] assuming simultaneous input changes. Considering the *simultaneous* interpretation, all input bursts are naturally supposed to complete within some pre-specified time interval, otherwise they might be recognised as two or more consecutive input vectors as described above.

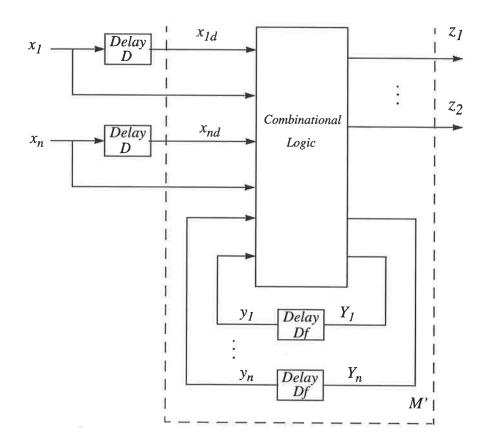

In the first method the intended asynchronous circuit, M, is decomposed into a special type decoder called source box and another asynchronous circuit, M', the inputs to which are one-hot codes only, that is each input vector to M' has exactly one bit at logic high, except for the spacer input (to be discussed shortly) which is all-zeros. For example a three input M' has at most four legitimate input vectors: 000 (spacer), 001, 010 and 100. The code conversion from binary (applied by the environment) to one-hot code is performed by the source box which of course incurs some redundancy and hence area overhead. The point is that, under fundamental mode assumption, circuit M' now does not undergo a multiple input change any more if all two consecutive input vectors to M' are separated by a spacer. This will prevent M' from faulty change of state if all transitions in the input burst are completed in some pre-specified time. Consider the multiple transition  $000 \rightarrow 111$  which may be seen by M as  $000 \rightarrow 001 \rightarrow 011 \rightarrow 111$  and finally translated to  $0001 \rightarrow 0000 \rightarrow 1000$  by the source box (before being applied to M') provided that the whole transition is completed within the pre-specified time, d, which can be chosen by the designer, and through a single delay element, D, in the source box [25]. Notice that although M may see the above simultaneous input change as three (ambiguous) transitions  $000 \rightarrow 001$ , then  $001 \rightarrow 011$  and then  $011 \rightarrow 111$ , this is always translated to only two consecutive single input changes eventually, as seen by M' no matter how many transitions the original multiple input change contains. This in fact means that the time interval  $\delta_2$  (in Huffman method) has now become under the control of the circuit designer.

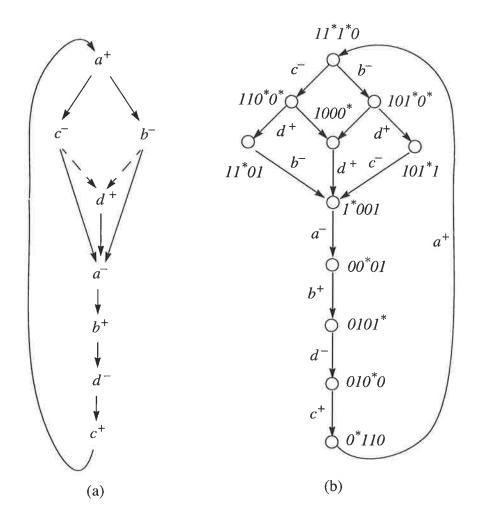

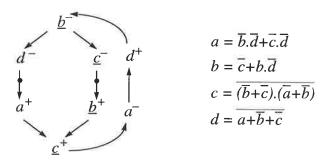

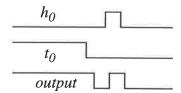

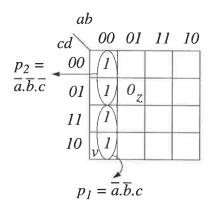

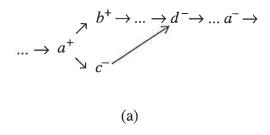

All other classical problems pertaining to critical races and hazards need to be handled as usual. Furthermore, M' is to be so designed that neither the internal state nor the output may change as the spacer replaces a one-hot code.