# **High Quality Micromachined Inductors** for Integrated Communication Systems

A Dissertation Submitted to the Faculty of Sciences of the University of Neuchâtel, in Fulfillment of the Requirements for the Degree of "Docteur ès Sciences"

by

Patrick Carazzetti

Dipl. Ing. Materials Science, EPFL

Institute of Microtechnology University of Neuchâtel Rue Jaquet-Droz 1, CH-2002 Neuchâtel Switzerland

### IMPRIMATUR POUR LA THESE

### High Quality Micromachined Inductors for Integrated Communication Systems

### Patrick CARAZZETTI

## UNIVERSITE DE NEUCHATEL FACULTE DES SCIENCES

La Faculté des sciences de l'Université de Neuchâtel, sur le rapport des membres du jury

MM. N. de Rooij (directeur de thèse), P.-A. Farine, A. Ionescu (EPF Lausanne) et M.-A. Dubois (CSEM, Neuchâtel)

autorise l'impression de la présente thèse.

Neuchâtel, le 4 juillet 2006

Le doyen:

J.-P. Derendinger

To my mother, Loredana and my father, Roberto

### **ABSTRACT**

Low power consumption is certainly one of the most stringent requirements to be met by new generation wireless communication systems. The quality factor (Q-factor) displayed by the numerous passive components of RF front-end transceivers plays a fundamental role on the overall power consumption of the portable electronic devices. Inductors, either in discrete or integrated form, are essential passive components of every RF front-end. They perform critical functions in radio-frequency integrated circuits (RFIC's), such as low noise amplifiers (LNA's), voltage controlled oscillators (VCO's), impedance matching networks, passive filters and baluns. A high Q-factor is of utmost importance since it contributes to reduce phase noise in oscillators, power consumption in amplifiers and insertion loss in filters. Generally, the Q-factor exhibited by on-chip inductors fabricated in standard IC technologies is drastically limited by RF power dissipation through the semiconducting silicon substrate and by the increase of the metal resistance as a consequence of the skin and proximity effects.

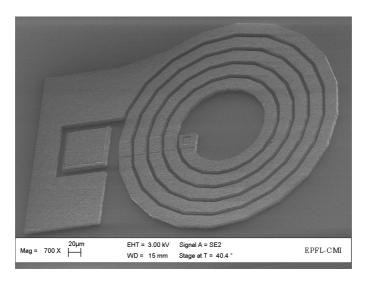

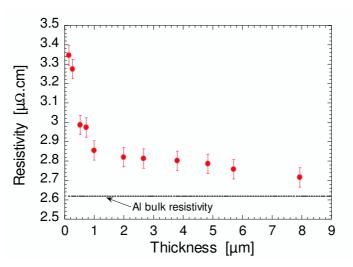

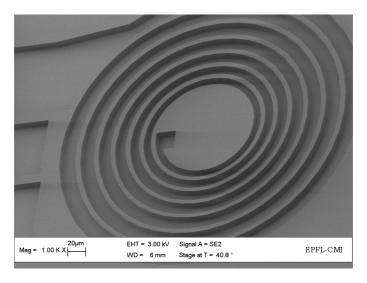

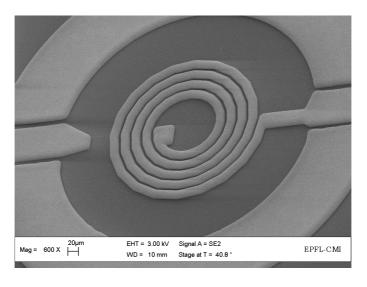

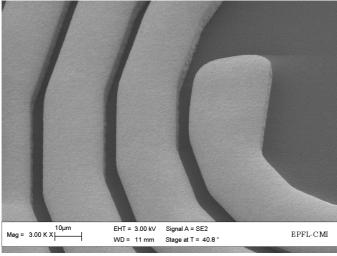

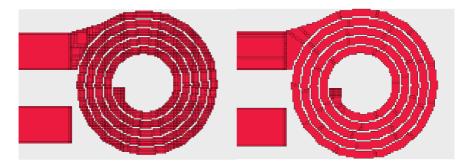

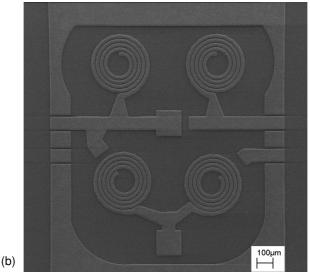

The work reported in this thesis addresses the fabrication and characterization of high-performance miniaturized planar inductors fabricated with innovative and low-thermal budget micromachining processes. Skin and proximity effects in the metal tracks have been addressed by providing highly conducting thick layers of sputter deposited Al or electroplated Ag, and by designing circular and hollow spirals, respectively. On the other hand, energy dissipation in the substrate has been mitigated by using low-loss substrates, such as high-resistivity Si (HRS) or Pyrex.

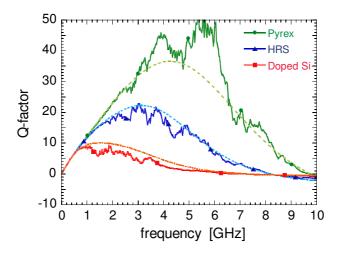

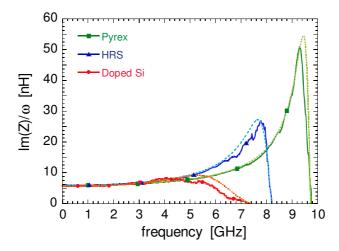

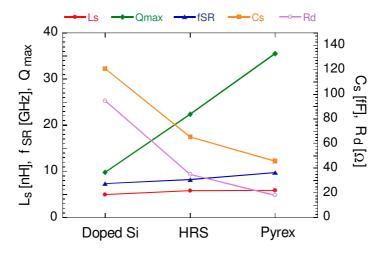

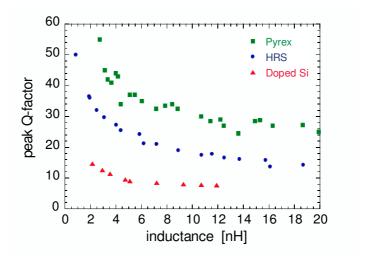

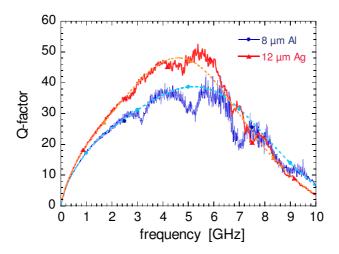

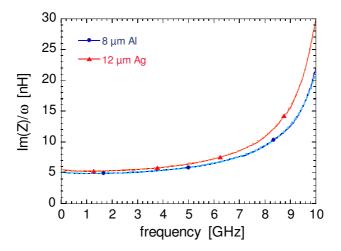

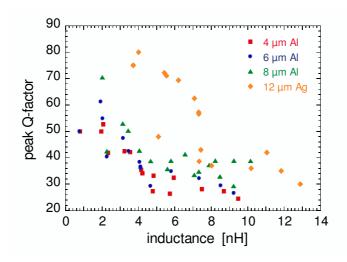

An empirical study of inductor performances has been carried out in order to shed light on the role played by the type of substrate, spiral conductivity and layout parameters. Inductors fabricated on Pyrex achieve better performances, in terms of Q-factor and self-resonance, than their counterparts implemented on HRS. Particularly, peak-Q values exhibit an improvement up to 40%, with a concomitant increase of  $f_{SR}$  by about 1-2 GHz. A Q-factor of 50 at 4.5 GHz and a self-resonance above 10 GHz have been exhibited by a 5 nH inductor implemented on Pyrex with a 12  $\mu$ m-thick Ag spiral; while, a peak-Q of 38 has been obtained from an inductor with identical layout fabricated with a 8  $\mu$ m-thick Al spiral.

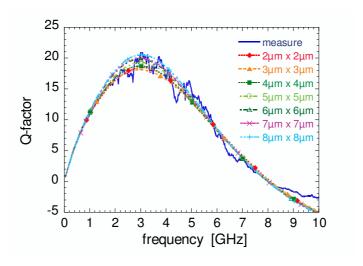

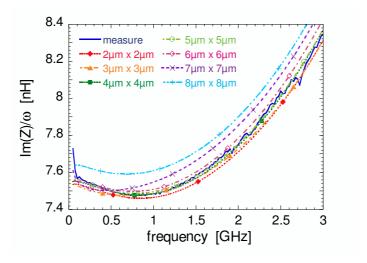

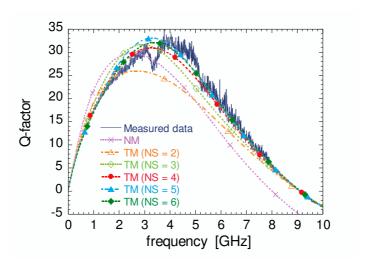

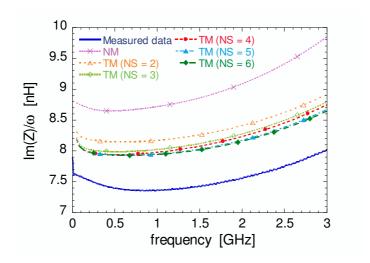

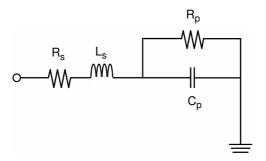

Measured data of inductors have been accurately matched using an equivalent compact model based on frequency-independent elements. Accurate matching of measured performances have also been provided by full-wave EM simulations.

In general, the measured performances challenge those exhibited by state-of-the-art micromachined inductors with similar inductance values. Moreover, the proposed planar geometry is more robust compared to reported developments of suspended or out-of-plane assembled architectures and consequently can withstand violent mechanical shocks and vibrations and also simplifies the packaging procedure of the final device.

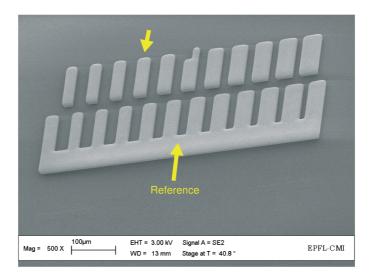

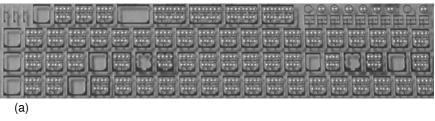

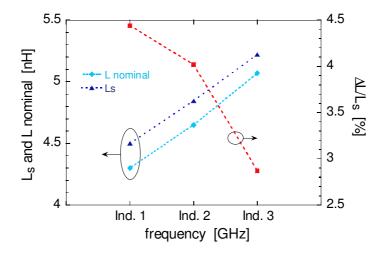

A library of 500 inductors ranging from 0.5 to 20 nH has been established. With the insight gained from the various trends issued from the analysis of experimental data, a set of design rules aiming at the improvement of the performances from a layout point of view has been delineated. In addition, the study of inductor performances as a function of the layout parameters has made possible to design inductors tailored for a given inductance value. The RF characterization of these optimized inductors has pointed out inductance values falling within 5% of their predicted value.

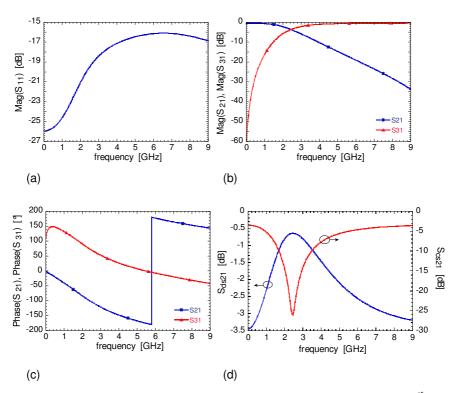

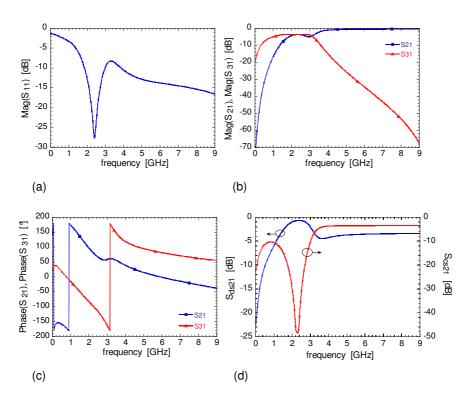

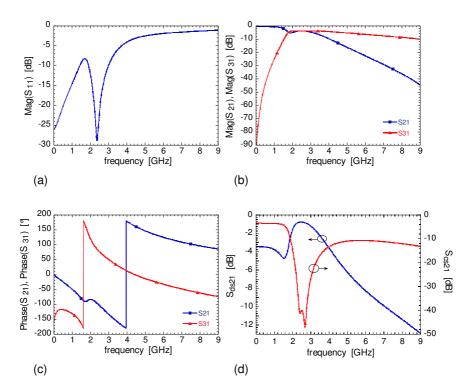

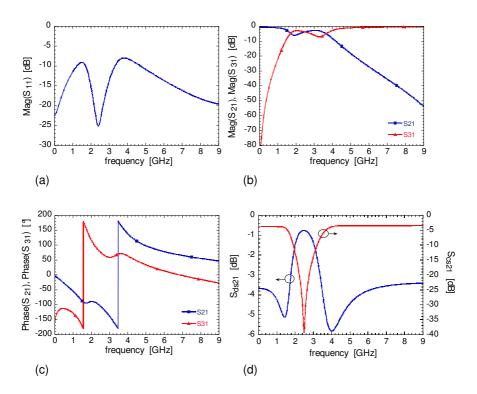

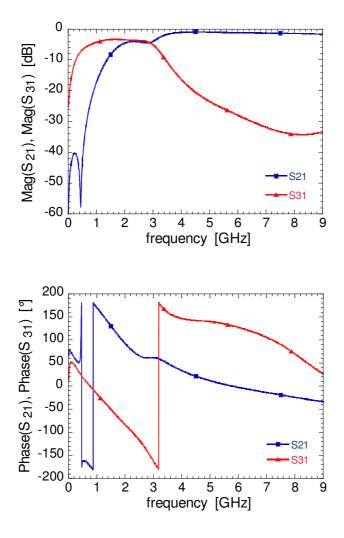

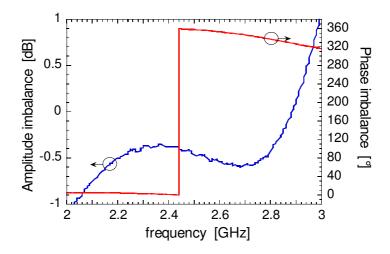

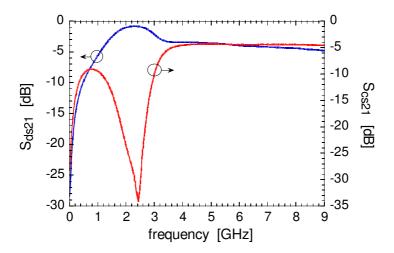

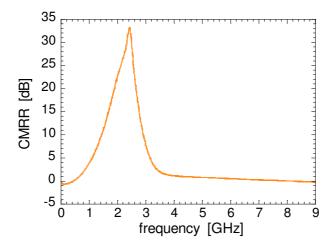

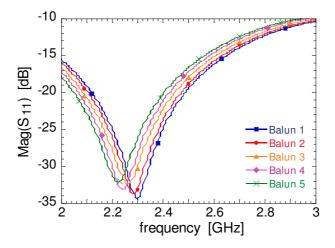

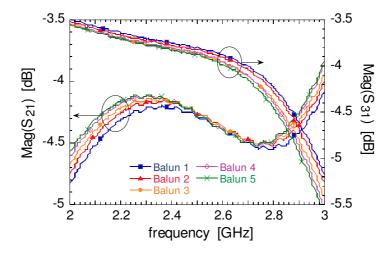

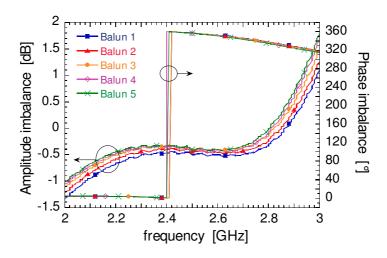

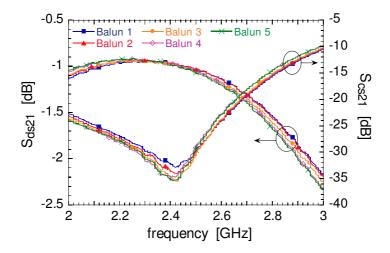

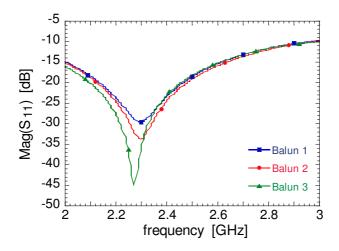

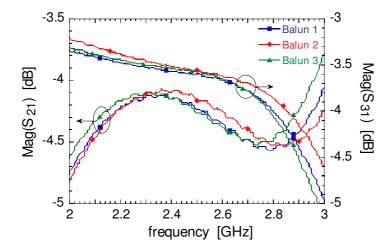

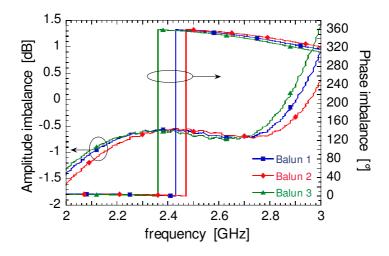

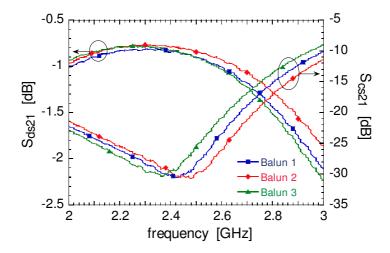

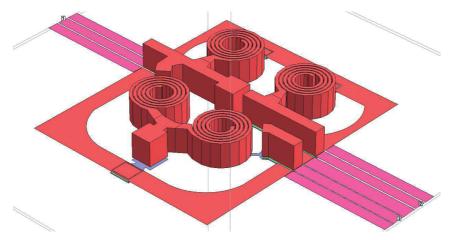

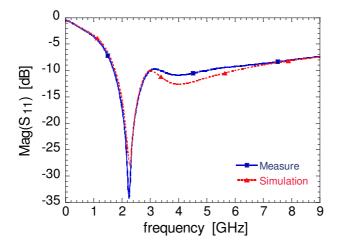

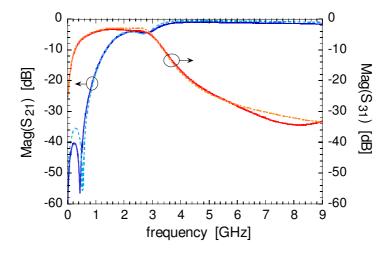

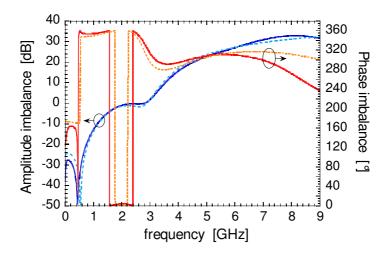

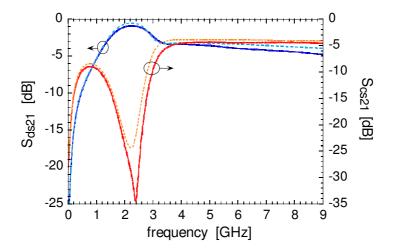

As a further step of the research, lumped-element baluns have been fabricated by co-integrating optimized inductors with MIM capacitors so as to form low-pass and high-pass filter sections. The proposed baluns are designed for operating in a 50  $\Omega$ -single-ended/100  $\Omega$ -balanced environment and target the ISM frequency band (2400-2480 MHz). Typical values of amplitude imbalance obtained within the frequency band of interest are 0.45-0.55 dB and the corresponding phase imbalance is less than 2°. The reflection loss at the single-ended port,  $S_{11}$  is generally better than -20 dB. The single-to-differential insertion loss,  $S_{ds21}$  ranges from -0.8 to -1.0 dB. In general, these performances are comparable to published results concerning micromachined baluns of similar type.

In conclusion, the promising performances obtained from the proposed inductors and baluns make these devices well-suited building-blocks for implementing low-power wireless communication systems.

### TABLE OF CONTENTS

| Abstract                                           | i   |

|----------------------------------------------------|-----|

| Table of Contents                                  | iii |

| Chapter 1 Introduction                             | 1   |

| 1. 1 Aim of the research                           | 3   |

| 1. 2 Organization of the thesis                    | 4   |

| 1. 3 References                                    |     |

| Chapter 2 State-of-the-Art of RF Inductors         | 9   |

| 2. 1 Inductor Q-factor                             | 10  |

| 2. 2 Dissipation mechanisms                        |     |

| 2. 2. 1 Metal losses                               | 11  |

| 2. 2. 1. 1 Skin effect                             | 12  |

| 2. 2. 1. 2 Proximity effect                        | 18  |

| 2. 2. 2 Substrate losses                           | 19  |

| 2. 3 Literature review                             | 21  |

| 2. 4 References                                    | 28  |

| Chapter 3 Technology                               | 37  |

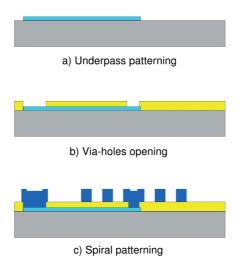

| 3. 1 Aluminum inductors                            | 39  |

| 3. 1. 1 Sputter deposition                         | 39  |

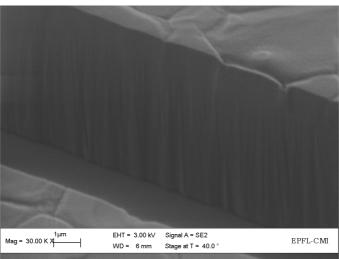

| 3. 1. 2 Dry-etching                                | 39  |

| 3. 1. 3 Fabrication process                        | 43  |

| 3. 1. 4 Characterization of sputtered Al films     | 47  |

| 3. 2 Silver inductors                              | 50  |

| 3. 2. 1 Electroplating                             | 50  |

| 3. 2. 2 Fabrication process                        | 52  |

| 3. 2. 3 Characterization of electroplated Ag films | 56  |

| 3. 3 Surface micromachined inductors                     | 57        |

|----------------------------------------------------------|-----------|

| 3. 3. 1 Hydrofluoric acid (HF) vapor phase etching (VPE) | 57        |

| 3. 3. 2 Fabrication process                              | 58        |

| 3. 4 Summary                                             | 63        |

| 3. 5 References                                          | 65        |

| Chapter 4 RF Characterization of Inductors               | 67        |

| 4. 1 RF measurement                                      | 68        |

| 4. 2 Modeling                                            | 68        |

| 4. 3 Results and discussion                              | 73        |

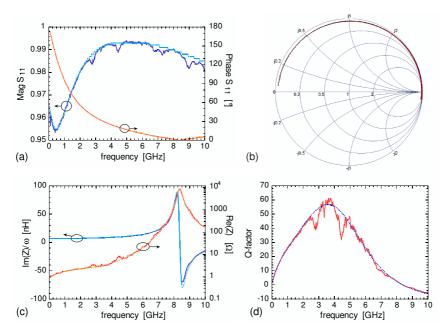

| 4. 3. 1 Equivalent mode                                  | 173       |

| 4. 3. 2 Substrate type                                   |           |

| 4. 3. 3 Spiral conductivity                              | 78        |

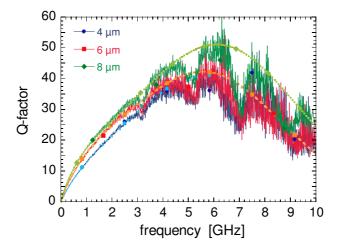

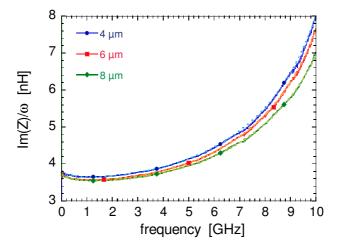

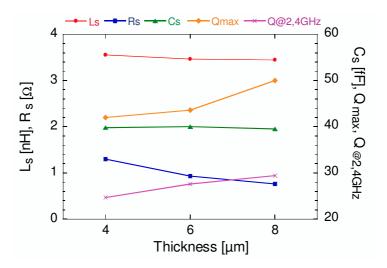

| 4. 3. 3. 1 Spiral thickness                              | <i>78</i> |

| 4. 3. 3. 2 Al versus Ag metallization                    | 80        |

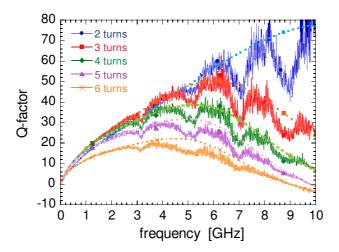

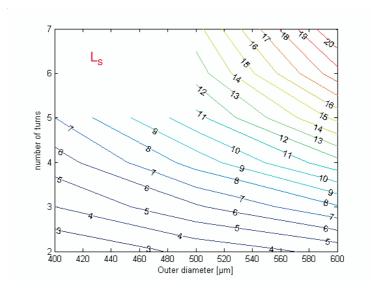

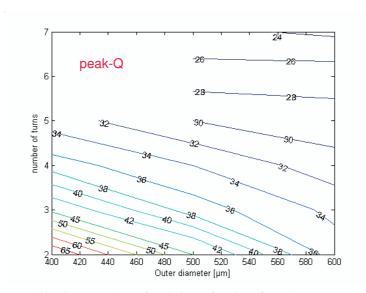

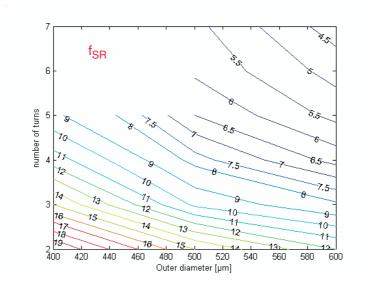

| 4. 3. 4 Layout parameters                                | 83        |

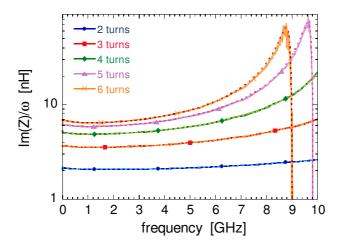

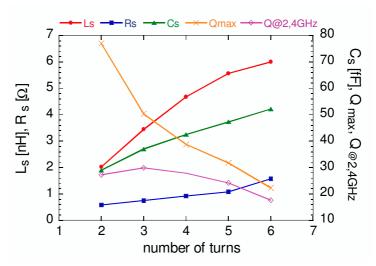

| 4. 3. 4. 1 Number of turns                               |           |

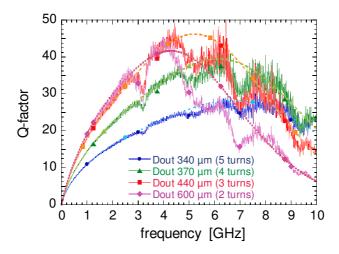

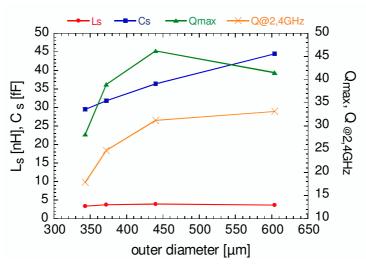

| 4. 3. 4. 2 Outer diameter                                |           |

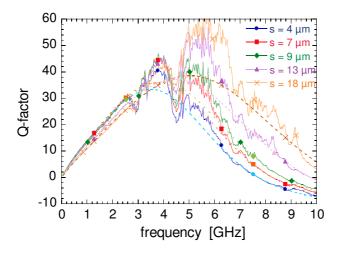

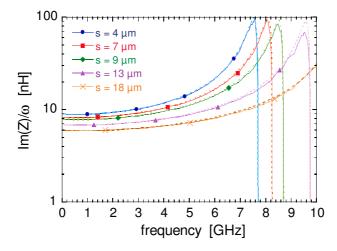

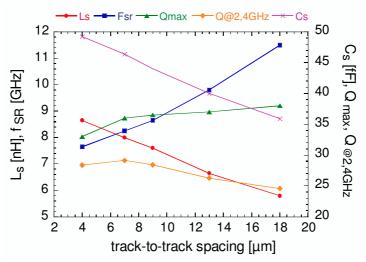

| 4. 3. 4. 3 Track-to-track spacing                        | 87        |

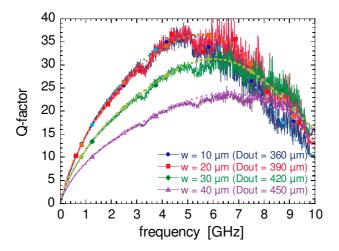

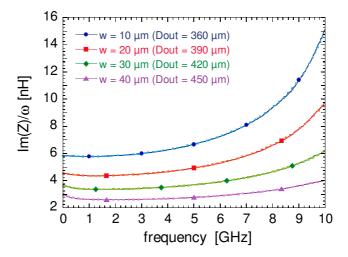

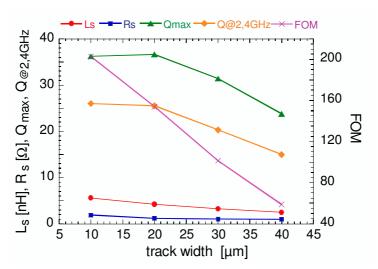

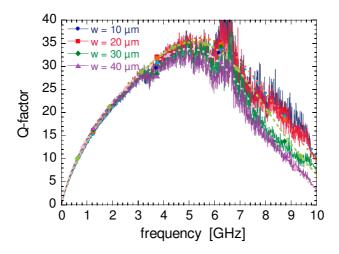

| 4. 3. 4. 4 Track-width                                   | 89        |

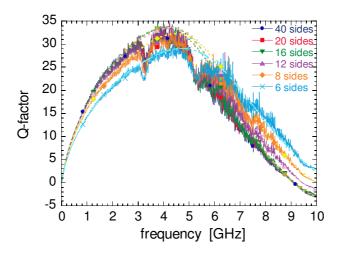

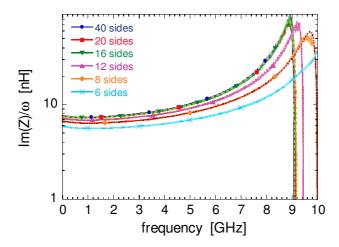

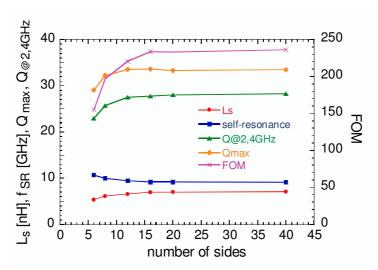

| 4. 3. 4. 5 Coil shape                                    | 92        |

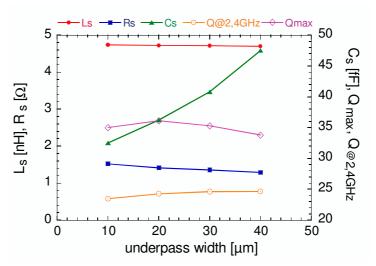

| 4. 3. 4. 6 Spiral-to-underpass capacitance               | 95        |

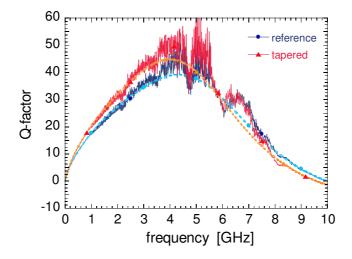

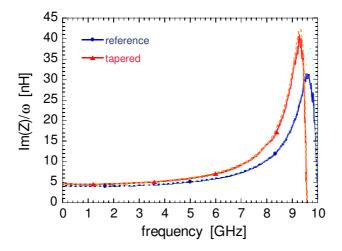

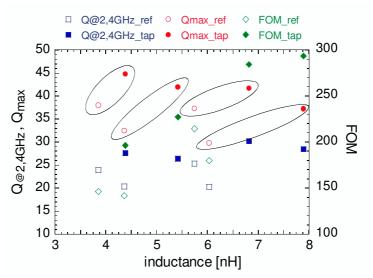

| 4. 3. 5 Tapered inductor                                 | 97        |

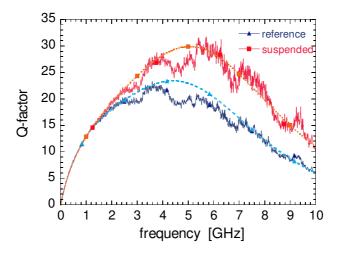

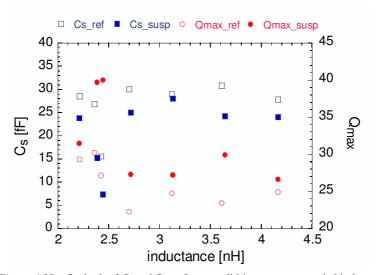

| 4. 3. 6 Suspended inductor                               | 100       |

| 4. 4 Performance outlook                                 | 102       |

| 4. 5 Design rules                                        | 104       |

| 4. 6 References                                          | 105       |

| Chapter 5 EM Simulation of Inductors                     | 107       |

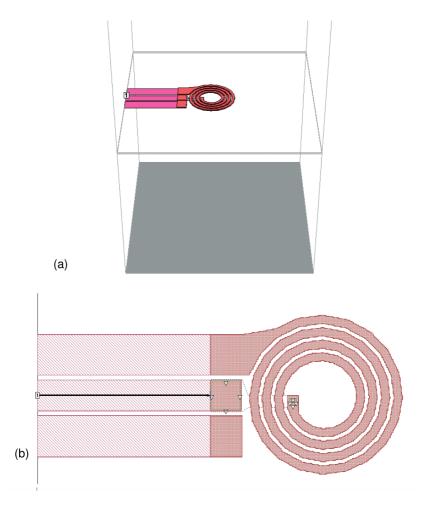

| 5. 1 Edition of a Sonnet project                         | 108       |

| 5.2 Simulation results                                   | 113       |

| 113 |

|-----|

| 117 |

| 120 |

| 122 |

| 124 |

| 126 |

| 127 |

| 128 |

| 130 |

| 134 |

| 144 |

| 146 |

| 146 |

| 150 |

| 156 |

| 159 |

| 162 |

| 166 |

| 168 |

| 171 |

| 175 |

| 177 |

| 179 |

| 181 |

|     |

### CHAPTER 1

### INTRODUCTION

IRELESS communications systems, such as cellular phones, pagers, and global positioning systems (GPS) are familiar and successful examples of the enormous growth experienced by the consumer market over the last ten years. The success of today's handsets is strongly related to the cost, battery lifetime, functionality and weight. The increasing demand for ever more sophisticated products has spurred the manufacturers to develop new solutions for increasing integration and miniaturization of the front-end transceivers, in order to reduce power consumption, increase functionality, reduce size and cost.

Today a situation has been reached where the presence of a multitude of rather cumbersome off-chip passive components, such as inductors, baluns, capacitors, varactor diodes, surface acoustic wave (SAW) and ceramic filters, represents a bottleneck against further miniaturization of radio-frequency (RF) transceivers [1]. In fact, these passive components are currently implemented on the PCB in discrete form. They are not directly integrated onto the IC's because the standard microelectronics technologies do not enable the fabrication of the well-controlled, high-Q elements required by RF applications. This problem is particularly acute in the case of inductors. Inductors are extensively used in RF front-end circuits. They play a key role many applications, such as voltage controlled oscillators (VCOs),

low-noise amplifiers (LNAs), LC filters and impedance matching networks. However, inductors integrated in today's typical silicon processes cannot meet the high performance specification required for RF IC's. For this reason, their off-chip counterpart are still widely used in applications where a high Q-factor is needed. An additional huge drawback of using discrete components is that their assembling in a complete system represents a significant part of the total cost of the final product.

A solution for increasing the level of integration and miniaturization would be the fabrication of circuit blocks and passive elements on the same substrate using a single technology. In recent years, silicon-based technologies have found a wide range of applications in the GHz-range and consequently have emerged as a cost-effective choice for RF front-end circuits [2, 3].

Since the late 70's, single crystal Si has become increasingly available for the rapidly growing IC's industry. This has favoured the advent of micromachining technologies developed for microelectromechanical systems (MEMS) [4] and has made possible the fabrication of miniaturized mechanical structures, devices and systems. A few of the advantages inherent to the MEMS technology include cost reduction through batch fabrication, high level of device reproducibility through advanced lithography and etching techniques, and access to the third dimension, including the ability to create free-standing structures. In addition, by using materials such as silicon and fabrication techniques compatible with IC's technology, MEMS components can be monolithically integrated with electronics. Compared with other more mature MEMS technology fields [4], RF MEMS (or MEMS for radio-frequency applications) is relatively new, but has already generated a great interest [5]. RF MEMS technology is currently under development in a large number of laboratories around the world. Important advantages that this technology can offer are the potential to build a multitude of miniaturized components such as switches, phase shifters, tunable capacitors, inductors, bulk acoustic wave (BAW) resonators and micromechanical resonators [6, 7]. To date, however, only BAW resonators have become a high-volume product. These devices are based on a thin film of piezoelectric aluminum nitride (AlN) vibrating in a thickness resonance mode and exhibit very large Q-factors [8, 9]. Miniature BAW resonators are mostly used for implementing duplexers, receive (RX) and transmit (TX) filters of cell phones [10, 11]. The integration of BAW devices with RF IC's can be realized either using a system-in-package (SiP) procedure [11], or with a monolithic approach enabled by the similar thermal budget involved in the fabrication process of RF IC's and BAW filters [12].

From a more general point of view, the advent of the BAW technology has made possible to get rid of the bulky ceramic front-end filters, SAW filters and the lossy LC tanks.

In conclusion, by combining standard IC's with MEMS technology, a complete communication system could be reduced to a multi-chip module made of an RF IC, a digital IC and a chip bearing all the high-Q components. Such system-on-a-chip (SoC) approach could be foreseen as a first step toward a cheap, miniaturized, and low-power consumption platform dedicated to the present and next-generation wireless communication systems.

### 1. 1 Aim of the research

The work presented in this thesis is foreseen as a first step toward the realization of a miniaturized multichip module obtained by co-integrating BAW filters with either micromachined inductors, or with more complex circuits such as lumped-element baluns.

In the first case, monolithic inductors could be used for tuning the resonance frequency of single resonators and extend the passband of the filter without recurring to off-chip inductors [13, 14].

Whereas, in the second case, micromachined baluns would be cascaded to differential BAW filters so as to fulfill different functions in a RF front-end transceiver depending on its configuration. Examples of applications that can be envisioned are the use of a balun between the single-ended output of the antenna and the first bandpass filter in the Rx path, or the use of a balun between the single-ended output of the LNA and the following filter. From this perspective, micromachined baluns could be used for replacing integrated or surface mount LTCC baluns.

The first goal of the research is the fabrication of high-Q inductors by means of micromachining processes. High-frequency dissipation mechanisms that traditionally limit the performance of integrated inductors are addressed by providing thick conductor layers and by using low-loss substrates, such as high-resistivity Si or Pyrex. As a further step, inductors tailored for a given inductance value are used for implementing balun circuits.

### 1. 2 Organization of the thesis

The first part of Chapter 2 gives an overview of the energy dissipation mechanisms that manifest whenever an inductor is operated at RF frequencies. These dissipation mechanisms, namely metal losses and substrate losses, ultimately degrade the achievable performances of RF inductors in terms of Q-factor and self-resonant frequency. It is shown how the high-frequency losses in metal tracks, that manifest themselves as skin and proximity effect, can be successfully addressed by a proper choice of the conductor thickness (for a given operating frequency) and by an appropriate design. The second part of the chapter outlines various well-established or currently investigated methods available for circuit designers in order to mitigate or even overcome the various forms of power dissipation. Furthermore, the state-of-the-art of RF inductors, based on the most promising published performances, is delineated in the last part of the chapter and will constitute a reference for comparing the performance obtained by the inductors fabricated in this work.

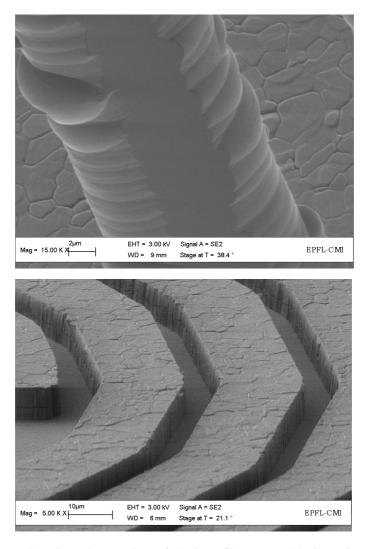

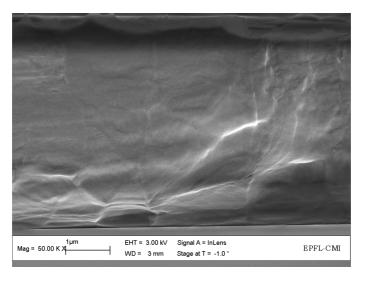

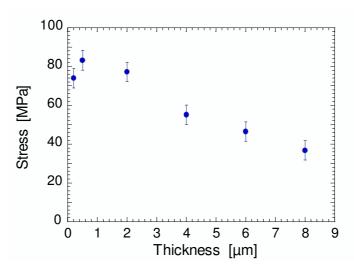

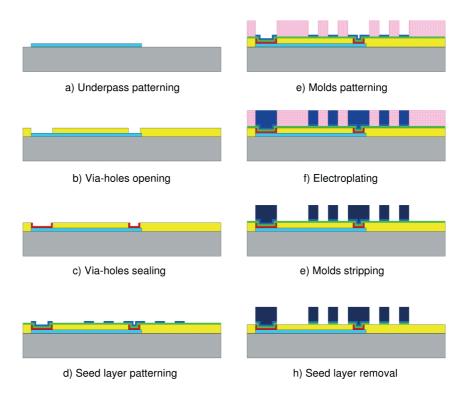

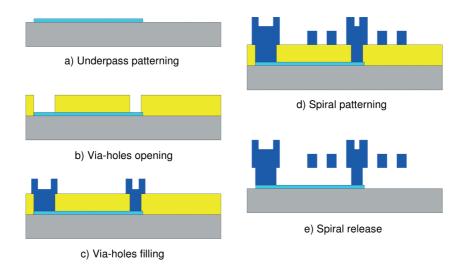

Chapter 3 presents the development of three simple and low-thermal budget micromachining processes enabling the fabrication of high-Q monolithic planar spiral inductors. The essential features of the first process are the use of thick sputter deposited aluminum films patterned by a highly anisotropic dry-etching process. Al films with different thickness have been characterized in terms of electrical conductivity and residual stress in order to assess their reliability.

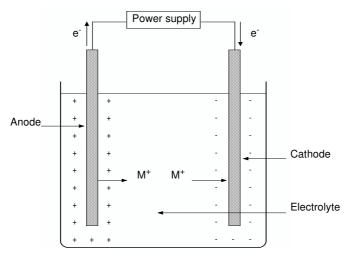

The second process based on Ag electroplating into thick polymer molds has been investigated since electroplating traditionally enables the fabrication of very thick metal films. This characteristic is especially well-suited when a drastic reduction of the DC resistance is desired. Ag has been preferred over Cu due to its higher bulk conductivity.

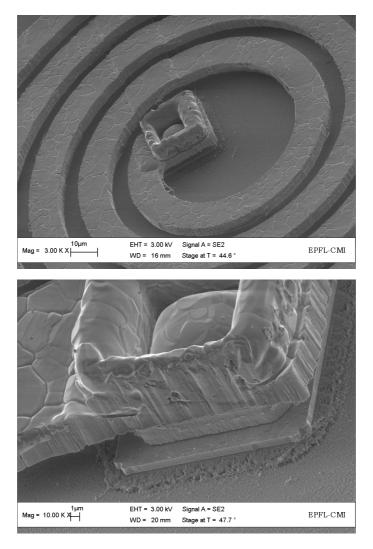

A third processing route involving a post-processing step of surface micromachining by means of HF vapor phase etching has been developed for the fabrication of suspended aluminum structures. The attractiveness of HF vapor phase etching resides in the suppression of stiction phenomena of the released structures. Although the robustness inherent to a monolithic planar structure is partially sacrificed, the main advantage of a suspended architecture is a reduction of the parasitic capacitive coupling to the substrate. Therefore, this process potentially opens a new perspective toward the fabrication of post-CMOS

compatible inductors, even tough direct integration of micromachined inductors on CMOS substrates is not the primary concern of this thesis.

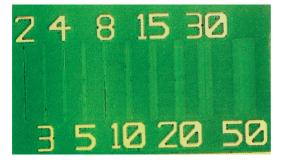

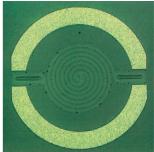

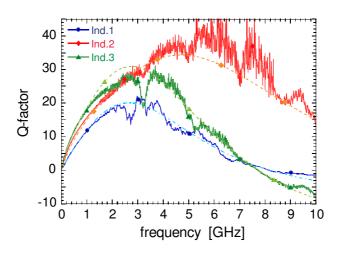

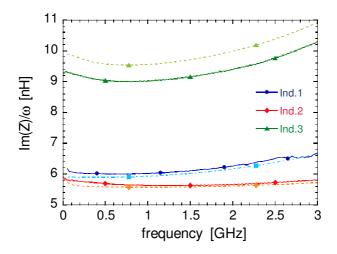

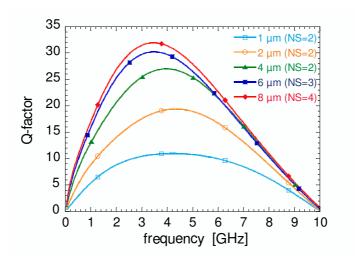

Chapter 4 focuses on the RF characterization of inductors fabricated using the processing routes described in Chapter 3. Particularly, numerous inductors have been designed for covering the inductance range going from 0.5 to 20 nH. An empirical study of inductor performances has been conducted as a function of the substrate type, spiral conductivity, layout parameters and spiral geometry. This study has been motivated by the need to establish accurate design rules enabling the fabrication of optimized inductors tailored for a given inductance value. Such optimized inductors will constitute the building-blocks for more complex circuits such as lumped-element baluns.

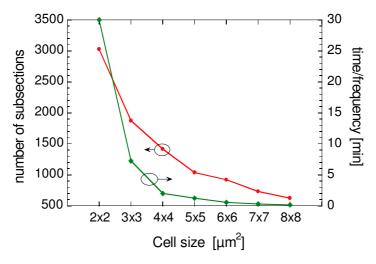

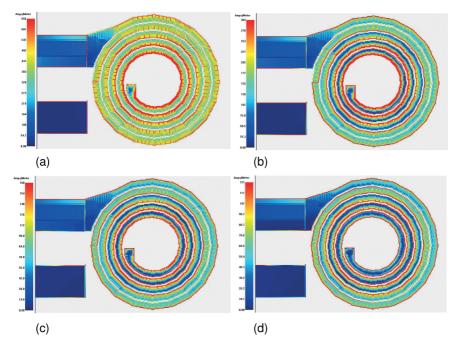

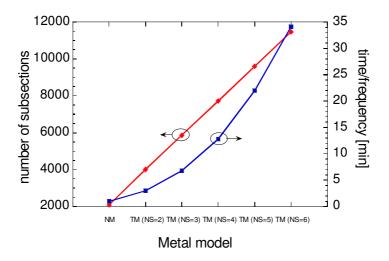

Chapter 5 deals with electromagnetic (EM) simulation of inductors. Since in general simulation is a rather time-consuming procedure, the aim of the presented work is primarily dedicated to the development of necessary knowledge enabling to get fast an accurate matching of measured data. The establishment of a set of optimum simulation conditions will thus help for an efficient simulation procedure of more complex and memory-demanding circuits, such as lumped-element baluns. Furthermore, EM simulation represents a very useful tool for providing physical insight on the role played by the material properties on the achievable performance and for taking into account parasitic coupling phenomena that cannot be easily modeled with circuit simulators.

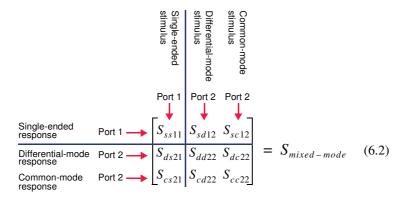

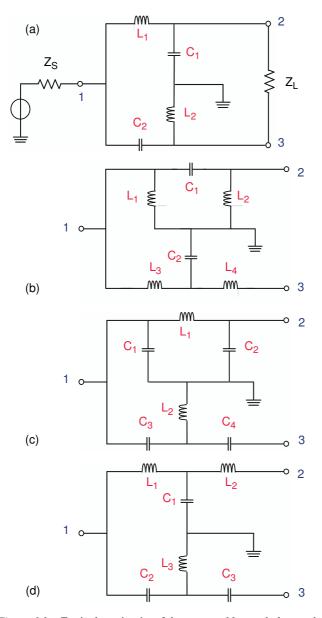

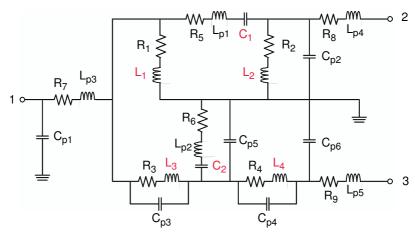

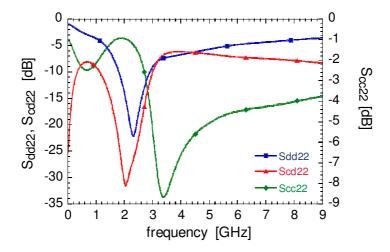

Chapter 6 presents the essential issues of design, fabrication and characterization of lumped-element baluns obtained by co-integrating optimized inductors with metal-insulator-metal (MIM) capacitors so as to form low-pass and high-pass filter sections. The proposed baluns target the ISM frequency band (2400-2480 MHz) and are designed for operating in a 50  $\Omega$ -single-ended/100  $\Omega$ -balanced environment. The formalism of mixed-mode S-parameters is introduced and exploited since it enables a rigorous characterization of the behavior of a balanced device. The measured performances will be compared to those exhibited by reported similar types of micromachined baluns and also by commonly used baluns implemented with LTCC technology. The last part of the chapter deals with EM simulation of baluns.

Concluding remarks and perspectives are summarized in Chapter 7.

### 1.3 References

- [1] C. T. Nguyen, L. P. B. Katehi, and G. M. Rebeiz, "Micromachined devices for wireless communications," *Proc. IEEE*, vol. 86, pp. 1756-1768, 1998.

- [2] J. Sevenhans, F. Op't Eynde, and P. Reusens, "The silicon radio decade," *IEEE Trans. Microwave Theory Tech.*, vol. 50, pp. 235-244, 2002.

- [3] A. A. Abidi, "RF CMOS comes of age," *IEEE J. Solid-State Circuits*, vol. 39, pp. 549-561, 2004.

- [4] K. Petersen, "A new age for MEMS," presented at The 13<sup>th</sup> Conf. Solid-State Sensors, Actuators and Microsystems Transducers'05, Seoul, Korea, 2005.

- [5] J. J. Yao, "RF MEMS from a device perspective," *J. Micromech. Microeng.*, vol. 10, pp. 9-38, 2000.

- [6] K. Grenier, B. P. Barber, V. Lubecke, M. Zierdt, H. Safar, P. Pons, and P. L. Gammel, "Integrated RF MEMS for single chip radio," presented at The 11<sup>th</sup> Int. Conf. Solid-State Sensors, Actuators and Microsystems, Transducers '01 Eurosensors XV, Munich, Germany, 2001.

- [7] H. A. C. Tilmans, W. de Raedt, and E. Beyne, "MEMS for wireless communications: 'from RF-MEMS components to RF-MEMS-SiP'," *J. Micromech. Microeng.*, vol. 13, pp. 139-163, 2003.

- [8] K. M. Lakin, "Thin film resonators and filters," presented at Proc. IEEE Ultrasonics Symposium, Lake Tahoe, NV, 1999.

- [9] M.-A. Dubois and P. Muralt, "Properties of aluminum nitride thin films for piezoelectric transducers and microwave filter applications," *Applied Physics Lett.*, vol. 74, pp. 3032-3034, 1999.

- [10] R. Ruby, P. Bradley, J. Larson III, Y. Oshmyansky, and D. Figueredo, "Ultraminiature high-Q filters and duplexers using FBAR technology," presented at IEEE Int. Solid-State Circuits Conf. (ISSCC'01), San Francisco, CA, 2001.

- [11] R. Aigner, "MEMS in RF-filter applications: thin film bulk-acoustic-wave technology," presented at The 13<sup>th</sup> Int. Conf. Solid-State Sensors, Actuators and Microsystems Transducers'05, Seoul, Korea, 2005.

- [12] M.-A. Dubois, J.-F. Carpentier, P. Vincent, C. Billard, G. Parat, C. Muller, P. Ancey, and P. Conti, "Monolithic above-IC resonator technology for integrated architectures in mobile and wireless communication," *IEEE J. Solid-State Circuits*, vol. 41, pp. 7-16, 2006.

- [13] J.-S. Kim, K.-W. Kim, M.-G. Gu, J.-G. Yook, and H.-K. Park, "Performance of polygonal-shaped TFBARs and on-wafer tuning inductors," presented at IEEE MTT-S Int. Microwave Symp., Philadelphia, PA, 2003.

[14] J.-S. Kim, Y.-D. Kim, M.-G. Gu, and J.-G. Yook, "New modeling of TFBAR and on-wafer inductor effects on the TFBAR ladder filter performance," presented at IEEE MTT-S Int. Microwave Symp., Fort Worth, TX, 2004.

### CHAPTER 2

# STATE-OF-THE-ART OF RF INDUCTORS

SINCE RF inductors implemented in standard silicon processes suffer from poor Q-factors, as a consequence of physical phenomena that convert electromagnetic energy into heat, RF IC's requiring better quality factors, still rely on off-chip discrete inductors. Over the past two decades, intensive research efforts have been made aiming at the improvement of the performance of on-chip spiral inductors in terms of Q-factor and self-resonant frequency. The large amount of published studies witnesses the fact that the implementation of high-Q inductors largely remains an empirical affair because the inductor performances are strongly related to the operating frequency and to the properties of the materials involved in the specific fabrication processes. Material properties include the conductivity of metals layers and substrate, and the permittivity and loss tangent of dielectrics. In addition, the layout parameters and the inductor footprint also play an important role on the achievable performance.

The first part of the chapter gives the definition of the inductor Q-factor. The second part addresses the two main classes of power dissipation mechanisms, namely metal losses and substrate losses, that degrade the performance of on-chip

RF inductors. A literature review discussing various techniques available for mitigating or even suppressing the loss mechanisms is presented in the last part of the chapter. Here, the most promising performances currently establishing the state-of-the-art of RF inductors are summarized.

### 2. 1 Inductor Q-factor

Inductors with high Q values are necessary for designing RF circuits with low insertion loss, low noise, high gain and good frequency selectivity [1]. The Q-factor of an inductor is an index of the stored electromagnetic energy versus dissipated energy [2]:

$$Q = 2\pi \cdot \frac{energy \ stored \ in \ the \ inductor}{energy \ lost \ in \ one \ oscillation \ cycle}$$

(2.1)

The above definition does not specify what stores or dissipates the energy. However, for an inductor, only the energy stored in the magnetic field is of interest. Any energy stored in electric fields due to parasitic capacitances is thus counterproductive and will degrade the achievable Q-factor. Therefore, the energy stored in the inductor is equal to the difference between the peak of magnetic and electric energies:

$$Q = 2\pi \cdot \frac{|W_m| - |W_e|}{P_{diss}} \tag{2.2}$$

where  $W_m$  and  $W_e$  are the peaks of magnetic and electric energy stored in the inductor, and  $P_{diss}$  is the power dissipated. From (2.2) the self-resonant frequency, or  $f_{SR}$ , of the inductor corresponds to the frequency where the peaks of magnetic and electric energy are equal. Consequently, Q drops to zero at  $f_{SR}$  and the impedance of the inductor turns capacitive if the operation frequency exceeds  $f_{SR}$ . The self-resonant frequency is the upper bound for an inductor to be functional, its value is determined by the parasitic capacitances resulting from the coupling to the substrate and between metal traces.

The traditional approach for obtaining Q from RF measurements involves the computation of :

$$Q = \frac{Im(Z)}{Re(Z)} \cong \frac{|X_L|}{R_s} = \frac{\omega L_s}{R_s}$$

(2.3)

where Z is the input impedance of the inductor derived from the measured scattering parameters. At low frequency, the quality factor is well described by the ratio  $\omega L_s/R_s$ ; however, as the frequency increases, Q starts to deviate from  $\omega L_s/R_s$  due to substrate effects, which account for various forms of energy dissipation. Furthermore, as the frequency continues to increase, the self-resonance effect becomes increasingly important due to the increase in the peak of electric energy stored in the capacitor formed between the spiral and the substrate. The self-resonant frequency corresponds to the point where Im(Z) is zero. Despite (2.3) has the drawback to deliver a Q of zero at  $f_{SR}$ , this definition is meaningful when the inductor is operated well below its self-resonance.

### 2. 2 Dissipation mechanisms

#### 2. 2. 1 Metal losses

The resistance of a spiral inductor is frequency-dependent due to magnetically induced eddy currents in the metal traces, that manifest themselves as *skin* and *proximity* effects [3, 4]. Skin effect losses arise from the magnetic field due to the self-inductance of a metal trace, which pushes moving charges away from the field lines and concentrate those charges to a confined portion at the outer skin of the conductor. Moreover, due to the close proximity between conductor segments in a spiral inductor, the current in each segment can induce eddy currents in other segments causing a non-uniform current flow across the trace width. The consequence of skin and proximity effects is addictive and cannot easily be distinguished. However, the net result produced by these effects is an effective reduction of the cross-sectional area of the conductor. This, in turn increases the high-frequency resistance of the metal traces and lowers the achievable Q-factor.

#### 2. 2. 1. 1 Skin effect

The current density in a conductor is uniform in DC mode since its entire cross-sectional area is available for the transport of charge carriers. The DC resistance of a conductor with rectangular cross sectional area is given by:

$$R_{DC} = \frac{\rho \cdot l}{w \cdot t} \tag{2.4}$$

where  $\rho$  is the metal resistivity, l, w and t represent the dimensions of the conductor, i.e., the length, width and thickness, respectively. However, as the frequency increases, the concomitant increased magnetic field at the core of the conductor presents an impedance to the charge carriers, thus decreasing the current density at the core of the conductor and increasing the current density around its perimeter [5]. The current density reaches its maximum value (100%) at the conductor surface and decays in amplitude exponentially with the distance from the surface. The depth into the conductor at which the current density has decreased to 1/e (or 37%) of its surface value is known as the skin depth,  $\delta$ , and is expressed by :

$$\delta = \sqrt{\frac{\rho}{\pi \cdot \mathbf{u} \cdot f}} \tag{2.5}$$

where  $\rho$  is the metal resistivity  $[\Omega \cdot m]$ ,  $\mu = \mu_0 \cdot \mu_r$  is the permeability of the medium [H/m], and f is the frequency [Hz]. The skin effect is negligible only if the depth of penetration at a certain frequency is much greater than the conductor thickness.

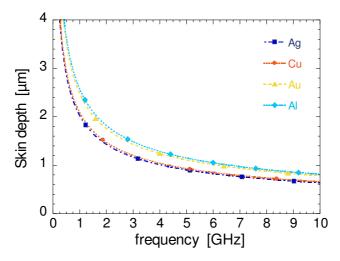

Table 2.1 lists the values of bulk resistivity and skin depth at 2.4 GHz calculated for the most common electrodes available in microtechnology processes, i.e., silver, copper, gold and aluminum. Figure 2.1 illustrates the exponential decay of the skin depth as a function of frequency. For example, the skin depth of aluminum is  $1.66 \, \mu m$  at  $2.4 \, GHz$  and decreases to  $0.81 \, \mu m$  at  $10 \, GHz$ .

| COMMON COMPONION II MEMBER IN MICKOTECHNOLOGI |                                |                    |  |  |

|-----------------------------------------------|--------------------------------|--------------------|--|--|

| Metal                                         | Resistivity [ $\mu\Omega$ ·cm] | δ@ 2.4 GHz<br>[μm] |  |  |

| Silver (Ag)                                   | 1.62                           | 1.31               |  |  |

| Copper (Cu)                                   | 1.72                           | 1.35               |  |  |

| Gold (Au)                                     | 2.44                           | 1.6                |  |  |

| Aluminum (Al)                                 | 2.62                           | 1.66               |  |  |

Table 2.1 : Bulk Resistivity and Skin-Depth,  $\delta$  Calculated at 2.4 GHz for the Most Common Conductors Available in Microtechnology.

Figure 2.1: Exponential behavior of the skin depth,  $\delta$  as a function of frequency.

The exponential attenuation of the current density J [A/m<sup>2</sup>] as a function of distance x away from the surface of a conductor is given by :

$$J = J_0 \cdot e^{-x/\delta} \tag{2.6}$$

The current I [A] is obtained by integrating J over the conductor cross-sectional area. Since J only varies in the x direction, I can be calculated as:

$$I = J \cdot dA = \int_{0}^{t} J_{0} \cdot e^{-x/\delta} \cdot w \cdot dx = J_{0} \cdot w \cdot \delta \cdot (1 - e^{-t/\delta})$$

(2.7)

where t is the physical thickness and w is the width of the conductor. From the above expression, an effective thickness,  $t_{eff}$  can be defined as follows:

$$t_{eff} = \delta \cdot (1 - e^{-t/\delta}) \tag{2.8}$$

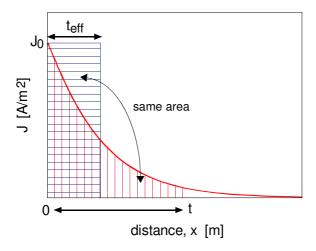

The effective thickness, as illustrated in Figure 2.2, represents an amount defining a fictive thickness for which the current intensity is equal to 100% of its surface value.

Figure 2.2: Effective thickness,  $t_{eff}$  of a conductor with a physical thickness t under the skin effect.

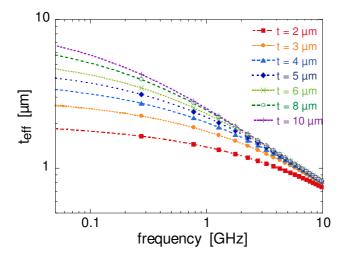

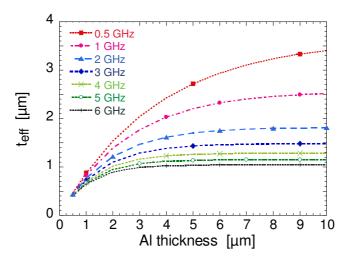

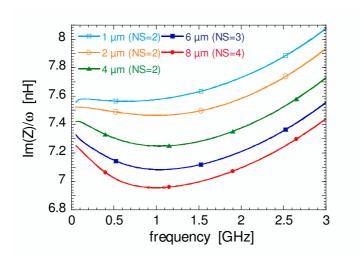

Figure 2.3 displays the calculated  $t_{eff}$  as a function of frequency plotted for several values of physical thicknesses, t of aluminum films.

Figure 2.3: Effective thickness,  $t_{e\!f\!f}$  as a function of frequency for several values of physical thickness, t of Al layers.

From (2.5) and (2.8), an expression taking into account the skin depth effect on the high-frequency resistance is written as follows:

$$R = \frac{\rho \cdot l}{w \cdot t_{eff}} = \frac{\rho \cdot l}{w \cdot \delta \cdot (1 - e^{-t/\delta})}$$

(2.9)

The above relationship has been used for evaluating the frequency-dependent resistance of an inductor as a function of the spiral thickness. The bulk resistivity of Al reported in Table 2.1 is taken for the calculation. The layout parameters defining the total length of the coil, l are the following: outer diameter,  $D_{out} = 500$   $\mu$ m, track width, w = 20  $\mu$ m, turn-to-turn spacing, s = 6  $\mu$ m, number of turns, n = 4. Thus, the coil length is approximated by summing the length of four concentric rings. The first ring has a radius,  $R_I$  given by  $0.5 \cdot (D_{out} - w)$ , the radius of the second

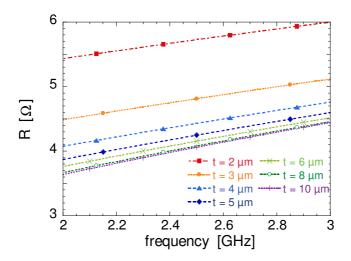

ring is  $R_2 = 0.5 \cdot (D_{out} - 2 \cdot w - 2 \cdot s)$ , and so forth. Figure 2.4 shows the calculated resistance as a function of frequency for various inductors with spiral thickness ranging from 2 up to 10  $\mu$ m.

Figure 2.4: Resistance as a function of frequency for various inductors with identical layout but with different spiral thickness.

A 16% decrease of resistance is obtained at 2.4 GHz when increasing the coil thickness from 2 to 3  $\mu$ m. Further metal thickening still shows a significant benefit, though more and more reduced, up to 8  $\mu$ m; whereas, a coil thickness exceeding 8  $\mu$ m does not lead to any appreciable decrease in resistance. The lower limit reached by the metal resistance is a consequence of the saturation of the conductor cross section that effectively sustains the flow of charges.

Figure 2.5 emphasizes the saturation of the effective thickness of aluminum films as a function of frequency. Considering the frequency range between 2 and 3 GHz, an appreciable increase of the effective thickness can be achieved using films up to 8  $\mu m$ . The increased effective thickness results in a reduced resistance and hence in a higher Q-factor.

However, the increase of Q-factor cannot be sustained indefinitely, especially at high frequency, due to the fact that the series resistance will reach a critical value as a result of the saturation of the effective metal thickness.

Figure 2.5: Effective thickness,  $t_{eff}$  of aluminum films as a function of the physical film thickness, t plotted at different frequencies.

The above developments based on a fictive aluminum spiral inductor targeting the 2.4 GHz operating frequency, have pointed out that there is a strong interest to provide metal films with thickness up to 8  $\mu m$ . In fact, despite the skin effect, a significant reduction of series resistance can be expected for such thick metal films. An aluminum film of 8  $\mu m$  corresponds to approximately 5 skin depths at 2.4 GHz.

### 2. 2. 1. 2 Proximity effect

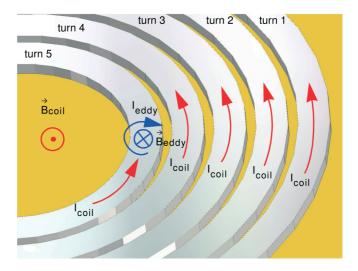

A portion of a multiturn spiral inductor is depicted in Figure 2.6 illustrating the mechanism responsible for the proximity effect [3, 6]. The multiturn inductor carries a current,  $I_{coil}$ , and generates an associated magnetic field,  $B_{coil}$ , that has maximum intensity at the center of the spiral. Here, the magnetic field is oriented in the direction coming out from the page. Due to the time-varying nature of the current circulating in the coil, the magnetic field also varies with time. As the magnetic field lines of adjacent turns penetrate a trace normal to its surface, according to Faraday's and Lenz's laws [7], an electric field is magnetically induced on these inner turns producing circular eddy currents,  $I_{eddy}$ , which flow in the direction where their magnetic flux is opposite to the applied magnetic field. So the opposing magnetic field,  $B_{eddy}$ , due to eddy currents is established and has a direction flowing into the page. This effect is highlighted in turn 5. The magnitude of the induced electric field,  $I_{eddy}$ , is proportional to the derivative of B(t) with respect to time, suggesting that this effect becomes very significant at GHz-frequencies.

The eddy currents in the metal traces cause a non uniform current flow in the inner turns of the spiral. Particularly, on the inner side of the innermost turns, the coil current,  $I_{coil}$  and eddy currents,  $I_{eddy}$  flow in the same direction, so the current density is larger than average. At the outer side, the currents flow in opposite direction, hence the current density is smaller than average.

This phenomenon causes a current constriction, or current crowding, that increases the effective resistance above the value that would exist for a uniform flow throughout the entire trace width. This problem is particularly acute when the spiral inductor is filled with turns up to the center, since in this case a large part of the magnetic field goes through these inner turns.

Although the problem of current crowding is well-known, little information is available in the literature for quantifying its effect on the high-frequency resistance without recurring to numerical simulations [4].

Figure 2.6: Proximity effect in the metal traces of a spiral inductor due to eddy currents. The magnetic field,  $B_{coil}$  generated by the current,  $I_{coil}$  flowing in the multi-turn spiral, passes perpendicularly through the traces, setting up eddy currents loops,  $I_{eddy}$  that constrict the current flow toward the inner trace edges.

#### 2. 2. 2 Substrate losses

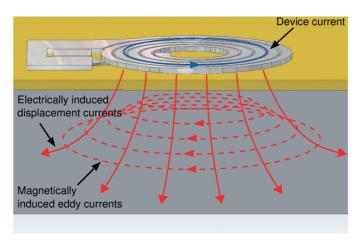

Integrated passive components often reside on top of a conductive silicon substrate. The conductive nature of Si is a major source of power loss and operating frequency limitation. Loss into the volume of the substrate ultimately results in the conversion of electromagnetic energy into heat [8]. To provide more physical insight into this problem, three loss mechanisms can be distinguished. First of all, electric energy is coupled to the substrate through displacement currents due to turn-to-substrate capacitances (see Figure 2.7). These displacement currents flow through the substrate to nearby grounds, that can be located either at the surface or at the backside of the wafer, or both. These electrically induced currents flow vertically or laterally, but always perpendicular to the device segments. In the case of a highly doped Si substrate, electrically induced currents are a dissipation mechanism that dominates over dipole losses. On the other hand,

for insulating substrates, the loss tangent of the material may be the dominant substrate loss mechanism.

Second, if the substrate is sufficiently conductive, magnetically induced currents, or bulk eddy currents, flow into the substrate as a consequence of the time-varying magnetic field penetrating the substrate. Faraday's law implies that this magnetic field induces time-varying solenoidal electric fields, that flow parallel to the spiral segments. The direction of the bulk eddy currents is such that they oppose to the original change in magnetic field, that is in a direction opposite to the current in the inductor. For this reason these currents are also called "image currents".

The inductance value is affected by the substrate eddy currents. Since these currents flow in a direction that is opposed to the coil current, the magnitude of the magnetic field will be reduced and hence the inductance generated by the device will be decreased.

Last, all other loss mechanisms can be grouped into radiation. However, these electromagnetically induced losses occur at much higher frequencies, where the physical dimension of the device approaches the wavelength at the frequency of propagation in the medium of interest, e.g. air or silicon.

Figure 2.7: Schematic representation of substrate currents: displacement currents due to turn-to-substrate capacitances (solid lines), and magnetically induced eddy currents (dashed lines) flowing in a direction opposite to the current in the inductor.

In standard CMOS technologies, the heaviest losses result from eddy currents induced in the low resistivity substrate (typically 0.01-10  $\Omega$ -cm), that often dominate and mask the effects of losses in the metal traces and displacement currents, and finally limit the Q-factor to values around 5. Moreover, for values of silicon resistivity lower than 0.1  $\Omega$ -cm, eddy currents cause their associated magnetic field to weaken the primary field of the spiral. This in turn decreases the inductance value of the device [6]. Inductors built in bipolar processes (or bipolar-derived BiCMOS) often exhibit larger Q values (5 to 10) due to relatively higher substrate resistivity (e.g., 10-30  $\Omega$ -cm), which reduce eddy currents to negligible values, but may still suffer from significant losses due to displacement currents [9].

### 2. 3 Literature review

In 1990, Nguyen and Mayer were the first to show that inductors could be used in silicon IC [10]. A 9.7 nH inductor was reported with a measured maximum Q-factor of 3 at 0.9 GHz. In 1996 Ashby *et al.* [11] demonstrated inductors with peak-Q of 12 at 3.3 GHz for an inductance of 2.9 nH. Since then, a great deal of work was focused at increasing the quality factor of on-chip spiral inductors, by mitigating dissipation mechanisms associated to the semiconducting substrate, or decreasing the metal trace resistance, respectively.

Figure 2.8 outlines the different technologies investigated and developed for these purposes. The most promising published performances, which currently establish the state-of-the-art of RF inductors, are summarized at the end of the chapter. For clarity, the reported performance are separated into two broad groups. The first one lists the performance of monolithic planar inductors fabricated without recurring to any step of surface or bulk micromachining (Table 2.2). Whereas, the second group lists the performances achieved by inductors whose fabrication processes involve post-processing steps of either surface or bulk micromachining (Table 2.3).

### Q-factor enhancement reducing metal losses reducing substrate losses - thick electroplated metal layers - patterned ground shields (PGS) Cu, Au, Ag - low-K dielectric layers - stacking or shunting of several metal - substrate impedance modification : layers in different levels (CMOS) porous silicon (PS), proton implant - design of hollow and circular spirals - high-resistivity Si (HRS), or insulating - design of tapered spirals substrates: Pyrex, quartz, alumina - substrate removal beneath the inductor by surface or bulk micromachining - creation of 3-D out-of-plane structures

Figure 2.8: Schematic classification of the different technologies proposed for decreasing the metal trace resistance, or mitigate substrate losses, respectively.

- differential excitation

Increasing the metal conductivity is the most efficient way currently known to increase the Q-factor in the frequency region below the maximum Q-factor. From this perspective, several methods have been investigated in order to increase the metal thickness, such as shunting several metal layers in different levels through interconnect via-holes [12, 13]. Another solution is to replace aluminum traditionally used in IC processes, with thick electroplated copper [14, 15] or gold metallizations [16, 17] in a post-processing step.

Alternatively, stacking several spirals in series through multilevel interconnects, so as to assimilate a solenoidal structure, has been reported as an effective method to maximize the inductance per unit area and, hence, improve the Q-factor [18-22].

The magnitude of the time-varying magnetic field generated by a planar inductor is strongest in the center of the spiral and thus produces eddy currents of greatest strength in the volume of conductors near the center of the device. As a consequence, the inner turns contribute in a large extent to the total increase of high-frequency resistance. At the same time, these inner turns play a minor role on

the total inductance of the device due to their small diameter. For these reasons, Craninckx and Steyaert [6, 23] suggested to remove the inner turns so as to create a "hollow" spiral. Another approach to mitigate eddy currents in the metal tracks consists in decreasing the width of the inner turns to effectively move these turns closer to the outer edge. This approach results in what is generally referred as a tapered inductor [24-26].

However, the reduction of the substrate related losses remains the major hurdle for enabling high-performance silicon-based inductors. For overcoming substrate losses, several approaches have been proposed. The insertion of a patterned conductive ground shield (PGS), made either of metal or polysilicon, between the inductor and the silicon substrate attenuates the induced magnetic field, and consequently reduce the eddy currents flowing beneath the device [2, 27-29]. The slots patterned in the shield are made narrow enough to preclude the vertical electric field from penetrating down to the underlying silicon. Moreover, the patterned slots act as an open circuit impeding the circular path of the eddy currents. However, the improvement of Q-factor enabled by using a patterned conductive shield comes at the expense of a reduced  $f_{SR}$ . In fact, since the field lines terminate closer to the device, the parasitic capacitance is increased. Nevertheless, the PGS has been demonstrated to be especially useful when attempting to realize an inductor on very low-resistivity substrates, i.e.,  $\rho < 0.1$   $\Omega$ -cm [2].

Another approach to reduce the fields that couple to the substrate is to insert a low-loss low-K dielectric layer between the device and the lossy silicon substrate. Several low-K dielectrics have been investigated such as benzocyclobutene (BCB) [30-32], SU-8<sup>TM</sup> [31], Polyimide [17, 33, 34], Silk<sup>TM</sup> [35, 36]. Cu electroplated inductors with a metal thickness of 6  $\mu$ m using 6  $\mu$ m of BCB ( $\epsilon_r$  = 2.65) to isolate the device from the silicon substrate ( $\rho_{Si}$  = 20  $\Omega$ ·cm) have shown a peak Q-factor of 23 at 1.7 GHz for a corresponding inductance of 3.2 nH [30].

A more attractive and cost-effective solution for on-chip inductors is to realize them above the passivation using thin-film post-processing techniques, in a wafer-level-packaging approach [32]. Inductors employing BCB have been fabricated in a multi-chip module (MCM) on glass substrate exhibiting Q-factor > 100 [37].

Increasing the substrate resistance is another effective means for reducing substrate losses. The use of high-resistivity silicon (HRS) [38-43], sapphire [39, 44, 45], quartz [38, 39], glass [46], GaAs [17, 38], or alumina ( $Al_2O_3$ ) [47], have been used by many researchers to demonstrate high-Q planar inductors (Q > 15). As an example, Benaissa *et al.* [41] have reported a 4.5 nH inductor fabricated on

HRS ( $\rho_{Si} > 1 \text{ k}\Omega\cdot\text{cm}$ ) achieving a peak Q-factor of 17.5 at 3.5 GHz. This corresponds to an almost three-fold improvement compared to the same inductor fabricated on low-resistivity Si ( $\rho_{Si} < 5 \Omega\cdot\text{cm}$ ). Recently published work has also demonstrated the fabrication of high-performance inductors on plastic substrate achieving a peak-Q > 30 for 3 nH [48].

Furthermore, a localized increase of the silicon substrate resistivity can be achieved by means of the formation of porous silicon (PS) [49-52], or with proton bombardment [53-59]. PS formed by anodization of silicon is emerging as an attractive material for RF applications because of its resistivity in the order of  $10^6$   $\Omega$ -cm [60] and its compatibility with very large-scale integrated (VLSI) technology. Kim et al. have reported a 5.7 nH spiral inductor exhibiting a peak-Q of 29 at 7 GHz built on a socket of 200  $\mu$ m of porous silicon formed in a Si substrate with initial resistivity of 0.007  $\Omega$ -cm. On the other hand, the high resistivity achieved after proton bombardment (typically  $10^5$ - $10^6$   $\Omega$ -cm) on wafers of initial resistivity of about 10  $\Omega$ -cm is a consequence of free carriers removal by proton-created charge trappings [61].

advent of micromachining technologies developed microelectromechanical systems (MEMS), innovative processes based on surface or bulk micromachining have been investigated in order to get rid of substrate parasitics. By using selective etching techniques, the silicon substrate can be removed in a post-processing step from underneath the inductor, either by etching from the top [62-68], or from the backside of the wafer [25, 69, 70]. This effectively suppresses induced currents and parasitic capacitance, and consequently shifts the self-resonance frequency toward higher values, thus extending the operating frequency range of the inductor. Alternatively, without altering the substrate itself, it is possible to separate the spiral inductor from the underlying substrate by creating an air gap using sacrificial molds of photoresist [71-73] or sacrificial metallic layers [74, 75]. This results in what is generally referred to as a levitated architecture. Air gaps of 50-60 µm separating the planar inductor from the substrate have been demonstrated. Very promising performance of levitated inductors have been reported by Yoon et al. [75], they demonstrated a peak Q-factor of 35 at 5 GHz for a 5 nH inductor fabricated on glass substrate.

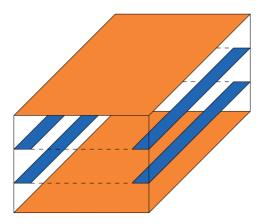

Unlike the conventional planar spiral inductor, where the magnetic and electric fields penetrate the silicon substrate perpendicularly, the magnetic and electric fields of the solenoidal inductor are generated parallel to the substrate. As a consequence, substrate losses can be significantly reduced. Based on these considerations, three-dimensional (3-D) structures, such as solenoid inductors

have been fabricated using high aspect ratio molds [76-84]. Toroidal structures have also been proposed since they better confine the magnetic flux mostly parallel to the substrate with only fringing fields penetrating the substrate [85, 86].

In recent years, more advanced techniques have been developed aiming at the out-of-plane self-assembly of 3-D architectures. Basically, the portion of the structure to be assembled is first released from the substrate by the removal of a sacrificial layer, subsequently the assembly process takes place causing the structure to be lifted away from the surface. The assembly mechanism can be driven by stress-engineered metal films [87-89], surface tension [90], or by the torque generated by an applied magnetic field [91, 92].

A common feature of all these micromachining techniques is the substantial elimination of the resistive losses related to the substrate. However, this also requires extra non-standard processing steps and raises serious reliability issues such as packaging yield and long-term mechanical stability. Fragility to shocks and encapsulation issues are serious bottlenecks that currently hinder the application of micromachined inductors in RFIC's and MMIC's.

The Q enhancement of planar inductors can also be achieved by using differential excitation techniques [93-97]. In the differential excitation, the voltages or currents, of two input or output signals are 180° out of phase, but with the same magnitude. The differential excitation has become an important operation mode in high-performance mixed-signal circuits because it has the advantage of better immunity to environmental noise and offer common-mode rejection. Commonly used IC's that employ these inductors are differential VCOs, double balanced mixers and differential amplifiers. Spiral inductors excited differentially play an important role in these circuits. The Q-factor of such inductors is enhanced and is maintained over a broader bandwidth, compared to single-ended configuration, because of smaller substrate loss.

TABLE 2.2: STATE-OF-THE-ART PERFORMANCES OF MONOLITHIC RF PLANAR INDUCTORS.

| Authors/year/affiliation/<br>reference                              | Technology                                                                             | Substrate                      | Q <sub>max</sub><br>@ f <sub>max</sub><br>[GHz] | L [nH]          |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------|-----------------|

| Choi et al., 2004, KAIST,<br>Korea [14]                             | Thick Cu electroplating (5 to 22 µm) on 7 µm of oxide                                  | silicon<br>(1-30 Ω·cm)         | 55 @ 3.3                                        | 4.5             |

| Burghartz et al., 2004,<br>DIMES, Delft [15]                        | Local thickening of top Al level (1 $\mu$ m) with Cu electroplating (3.4 $\mu$ m)      | silicon<br>(5 Ω·cm)            | 13.2 @ 1                                        | 10              |

| Yim et al., 2002, Uni of Florida, Gainesville [28]                  | Spiral inductors (3 µm Al) on poly-<br>Si patterned ground shield (PGS)                | silicon<br>(20 Ω·cm)           | 13.8 @ 2.5                                      | 4.8             |

| Pieters et al., 2001,<br>IMEC, Leuven [37]                          | Multichip module approach : Cu spiral (3 $\mu$ m) embedded in BCB (10 $\mu$ m)         | glass                          | 115 @ 8                                         | 2               |

| Carchon et al., 2004,<br>IMEC, Leuven [32]                          | Wafer-level-packaging (WLP)<br>approach : Cu spiral (10 μm)<br>embedded in BCB (16 μm) | silicon<br>(20 Ω·cm)           | 38 @ 4.7                                        | 1               |

| Huo et al., 2002, Uni of<br>Science and Technol.,<br>Hong Kong [30] | Cu electroplated inductors (6 µm) on low-K BCB (6 µm)                                  | silicon<br>(20 Ω·cm)           | 23 @ 1.7<br>20 @ 1                              | 3.2<br>5.2      |

| Jeon et al., 2003, Purdue<br>Uni, West Lafayette [31]               | Spiral inductors (3.6 μm Au) on SU-8 (6 μm)                                            | HRS                            | 17 @ 8                                          | 3.2             |

| Zu et al., 1996, Rutgers<br>Uni, Piscataway [33]                    | Staggered double metal-layered inductor (Al 2.5 $\mu$ m) on polyimide (5 $\mu$ m)      | HRS<br>(2 kΩ·cm)               | 30 @ 1                                          | 4               |

| Park et al., 1998, ETRI,<br>Korea [40]                              | Spiral inductor (2 µm Al)                                                              | HRS<br>(2 kΩ·cm)               | 11.5 @ 3                                        | 13              |

| Burghartz et al., 1998,<br>IBM, New York [39]                       | Spiral inductor (Cu)                                                                   | quartz                         | 20 @ 0.75                                       | 80              |

| Dekker et al., 1997,<br>Philips, Eindhoven [46]                     | Spiral inductor (3.5 μm Al) transferred on glass                                       | glass                          | 38.9 @ 4.<br>19 @ 1.5                           | 2.6<br>23.9     |

| Wu et al., 1999, National<br>Central Uni, Taiwan [47]               | Spiral inductor (6 µm Au)                                                              | Al <sub>2</sub> O <sub>3</sub> | 36 @ 4                                          | 2.7             |

| Nam et al., 1997, KAIST,<br>Korea [50]                              | Spiral inductor (2.3 μm Au) on oxidized porous Si (25 μm)                              | silicon<br>(5-7 Ω·cm)          | 13.3 @ 4.6                                      | 6.3             |

| Kim et al., 2001, UCLA [51]                                         | Spiral inductor (4 μm Al) on<br>unoxidized porous Si (50-200 μm)                       | silicon<br>(0.007 Ω·cm)        | 29 @ 7                                          | 5.7             |

| Yang et al., 2003, TSMC,<br>Taiwan [53]                             | Spiral inductor (3 µm Cu) on<br>substrate post-processed with<br>proton bombardment    | silicon<br>(10 Ω·cm)           | 20.7 @ 6.8<br>20.6 @ 6.6<br>18.5 @ 4.1          | 1.1<br>2<br>3.5 |

TABLE 2.3: SATE-OF-THE-ART PERFORMANCES OF MICROMACHINED RF INDUCTORS.

| Authors/year/                                    | Technology                                                                               | Substrate   | Q <sub>max</sub>            | L [nH]     |

|--------------------------------------------------|------------------------------------------------------------------------------------------|-------------|-----------------------------|------------|

| affiliation/reference                            |                                                                                          |             | @ f <sub>max</sub><br>[GHz] |            |

| Yoon et al., 1999,                               | Surface micromachined suspended                                                          | glass       | 57 @ 10                     | 1.75       |

| KAIST, Korea [75]                                | inductors: Ni sacrificial molds (50 µm)                                                  |             | 35 @ 5                      | 5          |

|                                                  | and Cu electroplating (15 µm)                                                            |             | 38 @ 1.8                    | 14         |

| Yoon et al., 2002,                               | Surface micromachined suspended                                                          | silicon     | 70 @ 6                      | 1.38       |

| KAIST, Korea [71]                                | inductors: photoresist sacrificial molds (50 $\mu$ m) and Cu electroplating (10 $\mu$ m) | (1-30 Ω·cm) | 38 @ 2.3<br>32 @ 2.1        | 2.6<br>4.1 |

| Lakdawala et al., 2002,                          | Surface micromachined suspended                                                          | silicon     | 12 @ 7.5                    | 3.2        |

| Carnegie Mellon,<br>Pittsburg [66]               | inductors : air gap (30 µm) created by isotropic RIE etching of Si                       |             | 10.5 @ 5.7                  | 4.15       |

| Jiang et al., 2000,                              | Surface micromachined suspended                                                          | silicon     | 23 @ 7.5                    | 2          |

| Cornell Uni, Ithaca [64]                         | inductors: air gap created by HF                                                         |             | 36 @ 5                      | 2.7        |

|                                                  | etching of SiO <sub>2</sub> (30 µm),                                                     |             |                             |            |

|                                                  | encapsulation of poly-Si structures by<br>Cu electroless                                 |             |                             |            |

| Wang et al., 2004,                               | Surface micromachined suspended                                                          | glass       | 37 @ 1.5                    | 4.2        |

| JiaoTong Uni, Shanghai                           | inductors: photoresist sacrificial molds                                                 |             |                             |            |

| [72]                                             | (60 μm) and Cu electroplating (5 μm)                                                     |             |                             |            |

| Park et al., 1999,                               | Surface micromachined suspended                                                          | silicon     | 16 @ 0.1                    | 16         |

| Georgia Tech, Atlanta                            | inductors: polyimide sacrificial molds                                                   | (3-7 Ω·cm)  |                             |            |

| [63]                                             | (60 $\mu$ m) removed by plasma O <sub>2</sub> and Cu electroplating (15 $\mu$ m)         |             |                             |            |

| Lamán Willagas at al                             |                                                                                          | silicon     | 17 @ 1.5                    | 35         |

| Lopéz-Villegas et al.,<br>2003, Uni of Barcelona | Bulk micromachined suspended inductors: KOH etching of Si from the                       | silicon     | 17 @ 1.5                    | 33         |

| [25]                                             | wafer backside                                                                           |             |                             |            |

| Yoon et al., 1998,                               | Solenoid inductor using photoresist                                                      | glass       | 19 @ 5.5                    | 2.5        |

| KAIST, Korea [76]                                | sacrificial molds and Cu electroplating                                                  |             | 14.5 @ 2.8                  | 5.2        |

|                                                  |                                                                                          |             | 12.5 @ 2.3                  | 10         |

| Chua et al., 1998,                               | 3-D coils self-assembled by stress                                                       | silicon     | 85 @ 1                      | 7.8        |

| PARC, Palo Alto [88]                             | engineered sputtered MoCr alloy                                                          |             | 70@1                        | 9.2        |

| Yoon et al., 2005,                               | Solenoid inductor using a back-bone                                                      | glass       | 84 @ 2.6                    | 1.17       |

| Georgia Tech, Atlanta                            | of SU-8 covered by Cu electroplating                                                     | =           |                             |            |

| [83]                                             |                                                                                          |             |                             |            |

| Lu et al., 2004, Uni of                          | Solenoid inductor using SU-8                                                             | Pyrex       | 72.8 @ 9.7                  | 2.15       |

| Texas, Dallas [81]                               | sacrificial molds and Cu electroplating                                                  |             | 43 @ 2                      | 28         |

| Young et al., 1997, Uni                          | Cu electroplated traces (5 µm) around                                                    | silicon     | 30 @ 1                      | 4.8        |

| of California, Berkeley                          | an Al <sub>2</sub> O <sub>3</sub> core                                                   | (10 Ω·cm)   |                             |            |

| [84]                                             |                                                                                          |             |                             |            |

# 2. 4 References

- [1] C. T. Nguyen, L. P. B. Katehi, and G. M. Rebeiz, "Micromachined devices for wireless communications," *Proc. IEEE*, vol. 86, pp. 1756-1768, 1998.

- [2] C. P. Yue and S. S. Wong, "On-chip spiral inductors with patterned ground shields for Si-based RF IC's," *IEEE J. Solid-State Circuits*, vol. 33, pp. 743-752, 1998.

- [3] W. B. Kuhn and N. M. Ibrahim, "Analysis of current crowding effects in multiturn spiral inductors," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 31-38, 2001.

- [4] A. M. Niknejad and R. G. Meyer, "Analysis of Eddy-current losses over conductive substrates with applications to monolithic inductors and transformers," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 166-176, 2001.

- [5] C. Bowick, *RF Circuit Design*. Indianapolis, IN: Newnes, 1982.

- [6] J. Craninckx and M. Steyaert, "A 1.8-GHz low-phase-noise CMOS VCO using optimized hollow spiral inductors," *IEEE J. Solid-State Circuits*, vol. 32, pp. 736-744, 1997.

- [7] A. Hudson and R. Nelson, *University Physics*, 2<sup>nd</sup> ed. New York, NY: Saunders College Publishing, 1990.

- [8] A. M. Niknejad and R. G. Meyer, *Design, Simulation and Applications of Inductors and Transformers for RF ICs.* Norwell, MA: Kluwer Academic Publishers, 2000.

- [9] J. N. Burghartz, D. C. Edelstein, M. Soyuer, H. A. Ainspan, and K. A. Jenkins, "RF circuit design aspects of spiral inductors on silicon," *IEEE J. Solid-State Circuits*, vol. 33, pp. 2028-2034, 1998.

- [10] N. M. Nguyen and R. G. Meyer, "Si IC-compatible inductors and LC passive filters," *IEEE J. Solid-State Circuits*, vol. 25, pp. 1028-1031, 1990.

- [11] K. B. Ashby, I. A. Koullias, W. C. Finley, J. J. Bastek, and S. Moinian, "High Q inductors for wireless applications in a complementary silicon bipolar process," *IEEE J. Solid-State Circuits*, vol. 31, pp. 4-9, 1996.

- [12] J. N. Burghartz, M. Soyuer, and K. A. Jenkins, "Microwave inductors and capacitors in standard multilevel inteconnect silicon technology," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 100-104, 1996.

- [13] J. N. Burghartz, M. Soyuer, and K. A. Jenkins, "Integrated RF and microwave components in BiCMOS technology," *IEEE Trans. Electron Devices*, vol. 43, pp. 1559-1570, 1996.

- [14] Y.-S. Choi and J.-B. Yoon, "Experimental analysis of the effect of metal thickness on the quality factor in integrated spiral inductors for RF ICs," *IEEE Electron Device Letters*, vol. 25, pp. 76-79, 2004.

- [15] J. N. Burghartz, B. Rejaei, and H. Schellevis, "Saddle add-on metallization for RF-IC technology," *IEEE Trans. Electron Devices*, vol. 51, pp. 460-466, 2004.

- [16] K. Kamogawa, K. Nishikawa, I. Toyoda, T. Tokumitsu, and M. Tanaka, "A novel High-Q and wide-frequency-range inductor using Si 3-D MMIC technology," *IEEE Microwave Guided Wave Letters*, vol. 9, pp. 16-18, 1999.

- [17] I. J. Bahl, "High-performance inductors," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 654-664, 2001.

- [18] J. N. Burghartz, K. A. Jenkins, and M. Soyuer, "Multilevel-spiral inductors using VLSI interconnect technology," *IEEE Electron Device Letters*, vol. 17, pp. 428-430, 1996.

- [19] A. Zolfaghari, A. Chan, and B. Razavi, "Stacked inductors and transformers in CMOS technology," *IEEE J. Solid-State Circuits*, vol. 36, pp. 620-628, 2001.

- [20] C.-C. Tang, C.-H. Wu, and S.-I. Liu, "Miniature 3-D inductors in standard CMOS process," *IEEE J. Solid-State Circuits*, vol. 37, pp. 471-480, 2002.

- [21] G. Lihui, Y. Mingbin, C. Zhen, H. Han, and Z. Yi, "High Q multilayer spiral inductor on silicon chip for 5~6 GHz," *IEEE Electron Device Letters*, vol. 23, pp. 470-472, 2002.

- [22] H.-Y. Tsui and J. Lau, "Experimental results and die area efficient self-shielded on-chip vertical solenoid inductors for multi-GHz CMOS RFIC," presented at IEEE Radio Frequency Integrated Circuits Symp. (RFIC'03), Philadelphia, PA, 2003.

- [23] J. Craninckx and M. Steyaert, "A fully integrated CMOS DCS-1800 frequency synthesizer," *IEEE J. Solid-State Circuits*, vol. 33, pp. 2054-2065, 1998.

- [24] I. J. Bahl, "Improved quality factor spiral inductors on GaAs substrates," *IEEE Microwave Guided Wave Letters*, vol. 9, pp. 398-400, 1999.

- [25] J. M. López-Villegas, J. Samitier, C. Cané, P. Losantos, and J. Bausells, "Improvement of the quality factor of RF integrated inductors by layout optimization," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 76-83, 2000.

- [26] Y.-S. Lin and H.-M. Hsu, "High-performance micromachined tapered spiral inductors with resonant frequency of 17 GHz," *Microwave and Optical Technology Letters*, vol. 35, pp. 56-60, 2002.

- [27] H. P. Tan, J. G. Ma, K. S. Yeo, and M. A. Do, "High-Q Si-based inductor shielded with double-layer polysilicon for RF applications," *Microwave and Optical Technology Letters*, vol. 24, pp. 366-367, 2000.

- [28] S.-M. Yim, T. Chen, and K. K. O, "The effects of a ground shield on the characteristics and performance of spiral inductors," *IEEE J. Solid-State Circuits*, vol. 37, pp. 237-244, 2002.

- [29] A. Scuderi, T. Biondi, E. Ragonese, and G. Palmisano, "A scalable model for silicon spiral inductors," presented at IEEE MTT-S Int. Microwave Symp., Philadelphia, PA, 2003.

- [30] X. Huo, K. J. Chen, and P. Chan, "Silicon-based high-Q inductors incorporating electroplated copper and low-K BCB dielectric," *IEEE Electron Device Letters*, vol. 23, pp. 520-522, 2002.

- [31] J.-H. Jeon, E. J. Inigo, M. T. Reiha, T.-Y. Choi, Y. Lee, S. Mohammadi, and L. P. B. Katehi, "The effect of low-K dielectrics on RFIC inductors," presented at The 33<sup>rd</sup> European Microwave Conf., Munich, Germany, 2003.

- [32] G. J. Carchon, W. de Raedt, and E. Beyne, "Wafer-level packaging technology for High-Q on-chip inductors and transmission lines," *IEEE Trans. Microwave Theory Tech.*, vol. 52, pp. 1244-1251, 2004.

- [33] L. Zu, Y. Lu, R. C. Frye, M. Y. Lau, S.-C. Chen, D. P. Kossives, J. Lin, and K. L. Tai, "High Q-factor inductors integrated on MCM Si substrates," *IEEE Trans. Components, Packaging, and Manufacturing Technology B*, vol. 19, pp. 635-643, 1996.

- [34] G. Ternent, S. Ferguson, Z. Borsosfoldi, K. Elgaid, T. Lohdi, D. Edgar, C. D. W. Wilkinson, and I. G. Thayne, "Coplanar waveguide transmission lines and high Q inductors on CMOS grade silicon using photoresist and polyimide," *Electronics Letters*, vol. 35, pp. 1957-1958, 1999.

- [35] S. Jenei, S. Decoutere, K. Maex, and B. Nauwelaers, "Add-on Cu/Silk<sup>TM</sup> module for high Q inductors," *IEEE Electron Device Letters*, vol. 23, pp. 173-175, 2002.

- [36] W. D. van Noort, C. Detcheverry, A. B. M. Jansman, G. Verheijden, P. Bancken, R. Daamen, V. Nguyen, and R. J. Havens, "RF-performance of thick damascene Cu interconnect on silicon," presented at IEEE MTT-S Int. Microwave Symp., Fort Worth, TX, 2004.

- [37] P. Pieters, K. Vaesen, S. Brebels, S. F. Mahmoud, W. de Raedt, E. Beyne, and R. P. Mertens, "Accurate modeling of high-Q spiral inductors in thin-film multilayer technology for wireless telecommunication applications," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 589-599, 2001.

- [38] A. C. Reyes, S. M. El-Ghazaly, S. J. Dorn, M. Dydyk, D. K. Schroder, and H. Patterson, "Coplanar waveguides and microwave inductors on silicon substrate," *IEEE Trans. Microwave Theory Tech.*, vol. 43, pp. 2016-2022, 1995.

- [39] J. N. Burghartz, D. C. Edelstein, K. A. Jenkins, C. Jahnes, C. Uzoh, E. J. O'Sullivan, K. K. Chan, M. Soyuer, P. Roper, and S. Cordes, "Monolithic spiral inductors fabricated using a VLSI Cu-damascene interconnect technology and low-loss substrates," presented at Int. Electron Devices Meeting (IEDM'96), San Francisco, CA, 1996.

- [40] M. Park, S. Lee, C. S. Kim, H. K. Yu, and K. S. Nam, "The detailed analysis of high Q CMOS-compatible microwave spiral inductors in silicon technology," *IEEE Trans. Electron Devices*, vol. 45, pp. 1953-1959, 1998.

- [41] K. Benaissa, J.-Y. Yang, D. Crenshaw, B. Williams, S. Sridhar, J. Ai, G. Boselli, S. Zhao, S. Tang, S. Ashburn, P. Madhani, T. Blythe, N. Mahalingam, and H. Shichijo, "RF CMOS on high-resistivity substrates for system-on-chip applications," *IEEE Trans. Electron Devices*, vol. 50, pp. 567-576, 2003.

- [42] M. Spirito, F. M. de Paola, L. K. Nanver, E. Valletta, B. Rong, B. Rejaei, L. C. N. de Vreede, and J. N. Burghartz, "Surface-passivated high-resistivity silicon as a true microwave substrate," *IEEE Trans. Microwave Theory Tech.*, vol. 53, pp. 2340-2347, 2005.

- [43] D. Lederer and J.-P. Raskin, "New substrate passivation method dedicated to HR SOI wafer fabrication with increased substrate resistivity," *IEEE Electron Device Letters*, vol. 26, pp. 805-807, 2005.

- [44] R. A. Johnson, C. E. Chang, P. M. Asbeck, M. E. Wood, G. A. Garcia, and I. Lagnado, "Comparison of microwave inductors fabricated on silicon-on-sapphire and bulk silicon," *IEEE Microwave Guided Wave Letters*, vol. 6, pp. 323-325, 1996.

- [45] D. Kelly and F. Wright, "Improvements to performance of spiral inductors on insulators," presented at IEEE MTT-S Int. Microwave Symp., Seattle, WA, 2002.

- [46] R. Dekker, P. Baltus, M. van Deurzen, W. van der Einden, H. Maas, and A. Wagemans, "An ultra low-power RF bipolar technology on glass," presented at Int. Electron Devices Meeting (IEDM'97), Washington, DC, 1997.

- [47] H.-H. Wu and Y.-J. Chan, "High-Q inductors and low-loss bandpass filters on Al<sub>2</sub>O<sub>3</sub> substrates by thin-film technology," *Microwave and Optical Technology Letters*, vol. 20, pp. 322-326, 1999.

- [48] L. H. Guo, Q. X. Zhang, G. Q. Lo, N. Balasubramanian, and D.-L. Kwong, "High-performance inductors on plastic substrate," *IEEE Electron Device Letters*, vol. 26, pp. 619-621, 2005.

- [49] L. T. Canham, M. R. Houlton, W. Y. Leong, C. Pickering, and J. M. Keen, "Atmospheric impregnation of porous silicon at room temperature," *J. Appl. Physics*, vol. 70, pp. 422-431, 1991.

- [50] C.-M. Nam and Y.-S. Kwon, "High-performance planar inductor on thick oxidized porous silicon (OPS) substrate," *IEEE Microwave Guided Wave Letters*, vol. 7, pp. 236-238, 1997.

- [51] H. S. Kim, D. Zheng, A. J. Becker, and Y.-H. Xie, "Spiral inductors on Si p/p<sup>+</sup> substrates with resonant frequency of 20 GHz," *IEEE Electron Device Letters*, vol. 22, pp. 275-277, 2001.

- [52] K. Chong, X. Zhang, K.-N. Tu, D. Huang, M.-C. Chang, and Y.-H. Xie, "Three-dimensional substrate impedance engineering based on p<sup>-</sup>/p<sup>+</sup> Si substrate for mixed-signal system-on-chip (SoC)," *IEEE Trans. Electron Devices*, vol. 52, pp. 2440-2446, 2005.

- [53] M. T. Yang, T. J. Yeh, W. C. Lin, H. M. Hsu, P. Ho, Y. J. Wang, Y. T. Chia, and D. Tang, "Characterization and model of high quality factor and broadband integrated inductor on Si-substrate," presented at IEEE MTT-S Int. Microwave Symp., Philadelphia, PA, 2003.

- [54] A. Chin, "RF passive devices on Si with excellent performance close to ideal devices designed by electro-magnetic simulation," presented at Int. Electron Devices Meeting (IEDM'03), Washington, DC, 2003.

- [55] T.-S. Chen, C.-Y. Lee, and C.-H. Kao, "An efficient noise isolation technique for SOC application," *IEEE Trans. Electron Devices*, vol. 51, pp. 255-260, 2004.

- [56] C. Liao, C.-W. Liu, and Y.-M. Hsu, "Observation of explosive spectral behaviors in proton-enhanced high-Q inductors and their explanations," *IEEE Trans. Electron Devices*, vol. 50, pp. 758-763, 2003.

- [57] K. T. Chan, A. Chin, S. P. McAlister, C. Y. Chang, C. Tseng, V. Liang, J. K. Chen, S. C. Chien, D. S. Duh, and W. J. Lin, "Low RF loss and noise of

- transmission lines on Si substrates using an improved ion implantation process," presented at IEEE MTT-S Int. Microwave Symp., Philadelphia, PA, 2003.

- [58] C.-Y. Lee, T.-S. Chen, J. D.-S. Deng, and C.-H. Kao, "A simple systematic spiral inductor design with perfected Q improvement for CMOS RFIC application," *IEEE Trans. Microwave Theory Tech.*, vol. 53, pp. 523-528, 2005.

- [59] C. Liao and J.-S. Hsu, "An effective single-trap-level model for the proton-induced semi-insulating substrates," *IEEE Trans. Microwave Theory Tech.*, vol. 53, pp. 83-88, 2006.

- [60] H.-S. Kim, Y.-H. Xie, M. de Vincentis, T. Itoh, and K. A. Jenkins, "Unoxidized porous Si as an isolation material for mixed-signal integrated circuit applications," *J. Appl. Physics*, vol. 93, pp. 4226-4231, 2003.

- [61] L. S. Lee, C. Liao, C.-L. Lee, T.-H. Huang, D. Tang, T. S. Duh, and T.-T. Yang, "Isolation on Si wafers by MeV proton bombardment for RF integrated circuits," *IEEE Trans. Electron Devices*, vol. 48, pp. 928-934, 2001.

- [62] Y. Sun, H. van Zeijl, J. L. Tauritz, and R. G. F. Baets, "Suspended membrane inductors and capacitors for application in silicon MMIC's," presented at Proc. IEEE Microwave and Millimeter-Wave Monolithic Circuits Symp., 1996.

- [63] J. Y. Park and M. G. Allen, "Packaging-compatible high Q microinductors and microfilters for wireless applications," *IEEE Trans. Advanced Packaging*, vol. 22, pp. 207-213, 1999.

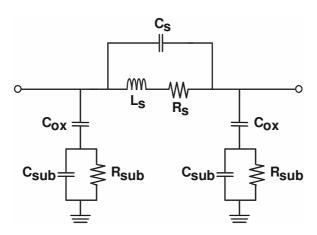

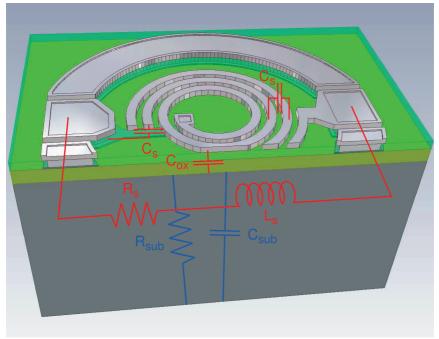

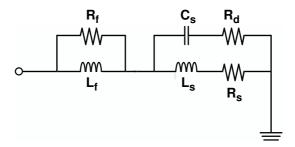

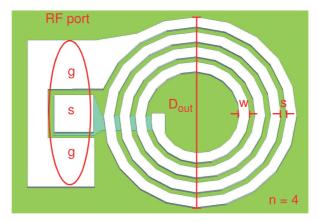

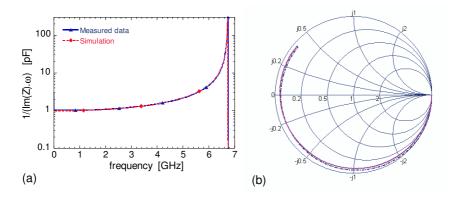

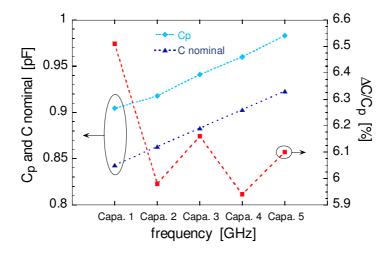

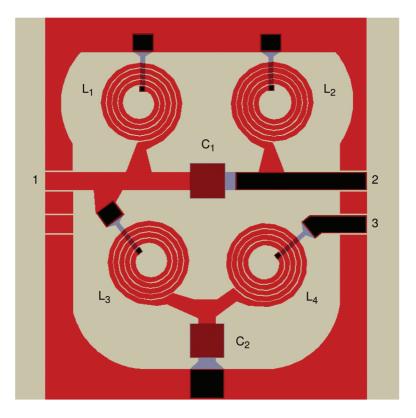

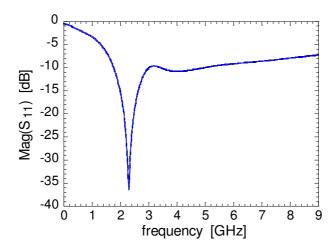

- [64] H. Jiang, Y. Wang, J.-L. A. Yeh, and N. C. Tien, "Fabrication of high-performance on-chip suspended spiral inductors by micromachining and electroless copper plating," presented at IEEE MTT-S Int. Microwave Symp., Boston, MA, 2000.