### UNIVERSIDADE DE LISBOA Faculdade de Ciências Departamento de Informática

# COMPILING THE $\pi\text{-}CALCULUS$ INTO A MULTITHREADED TYPED ASSEMBLY LANGUAGE

**Tiago Soares Cogumbreiro Garcia**

MESTRADO EM INFORMÁTICA

2009

UNIVERSIDADE DE LISBOA Faculdade de Ciências Departamento de Informática

# COMPILING THE $\pi$ -CALCULUS INTO A MULTITHREADED TYPED ASSEMBLY LANGUAGE

**Tiago Soares Cogumbreiro Garcia**

### DISSERTAÇÃO

Projecto orientado pelo Prof. Doutor Francisco Martins

MESTRADO EM INFORMÁTICA

2009

### Agradecimentos

Agradeço ao meu orientador, Francisco Martins, pelo seu apoio, paciência, rigor e minúcia. Ensinou-me a ter força para "não morrer na praia", a ter perseverança para superar últimos 10% do trabalho sem descurar no primor. A qualidade científica que imprime no seu trabalho foi fundamental para o desenvolvimento desta tese.

Agradeço também ao Vasco Vasconcelos por me ensinar a olhar pela primeira vez algo que o sei de cor. Também por me relembrar da máxima: "premature optimisation is the root of all evil". O seu contributo é também marcante no produto final que apresento.

Aproveito para agradecer a ambos pela oportunidade de participar numa visão que me permitiu trabalhar as fundações do meu conhecimento na licenciatura, desenvolver um trabalho mais teórico no mestrado e que me abriu portas para um doutoramento promissor. É uma honra trabalhar convosco.

#### Resumo

Restrições físicas e eléctricas limitam o aumento da velocidade do relógio dos processadores, pelo que não se espera que o poder computacional por unidade de processamento aumente muito num futuro próximo. Em vez disso, os fabricantes estão a aumentar o número de unidades de processamento (*cores*) por processador para continuarem a criar produtos com aumentos de performance. A indústria fez grandes investimentos em projectos como o RAMP e BEE2 que permitem a emulação de arquitecturas multi-core, mostrando interesse em suportar as fundações para a investigação de *software* que se destina a essas arquitecturas.

Para tirar vantagem de arquitecturas multi-core, tem de se dominar tanto a programação concorrente como a paralela. Com a grande disponibilidade de sistemas paralelos que vai desde sistemas embebidos até a super computadores, acreditamos que os programadores têm de fazer uma mudança de paradigma passando da programação sequencial para a programação paralela e produzir *software* adaptado, de raiz, a plataformas multi-core.

O *multithreading* é uma escolha bem conhecida e usada pela indústria para desenvolver sistemas explicitamente paralelos. Os *locks* são um mecanismo utilizado para sincronizar programas *multithreaded* de uma forma altamente eficiente. Porém, é comum surgirem problemas relacionados com concorrência como deter um *lock* tempo demais, não compreender quando se usam *locks* leitores/escritores ou escolher um mecanismo de sincronização desadequado. Estes problemas podem ser mitigados com recurso a abstracções de concorrência.

Os tipos e as regras de tipos são formas simples e eficazes de garantir segurança. Os tipos não são só usados por sistemas de tipos para garantir que programas não têm erros de execução, mas servem também como especificações (verificáveis de uma forma automática). A informação dada pelos tipos é expressiva o suficiente para representar propriedades operacionais importantes, como segurança de memória. Os compiladores que *preservam tipos* perduram a informação dada pelos tipos por todos os passos de compilação, permitindo uma compilação mais segura e que preserva a semântica (representada pelos tipos).

Propomos um compilador que endereça os problemas que levantámos até agora:

• uma linguagem fonte com abstracções para concorrência e para o paralelismo;

- um compilador que se destine a uma arquitectura multi-core;

- uma tradução que preserve a informação dada pelos tipos.

Em relação à linguagem fonte, os cálculos de processos evidenciam-se como um bom modelo de programação para a computação concorrente. O cálculo  $\pi$ , em particular, tem uma semântica bem compreendida, consiste num conjunto pequeno de operadores em que a comunicação é o passo fundamental de computação. Os cálculos de processos oferecem esquemas de compilação natural que expõe o paralelismo ao nível dos *threads*. Por estas razões, escolhemos o cálculo  $\pi$  simplesmente tipificado como linguagem fonte.

Vasconcelos e Martins propõem o MIL como uma linguagem *assembly* tipificada para arquitecturas *multithreaded*, um modelo que assenta numa máquina abstracta multi-core com memória principal partilhada. Esta linguagem fortemente tipificada oferece as seguintes propriedades de segurança: de memória, de controlo de fluxo e de liberdade de *race conditions*. O MIL contradiz a ideia que considera a associação entre a memória e *locks* uma convenção, ao torná-la explícita na linguagem. O sistema de tipos faz cumprir uma política de utilização de *lock* que inclui: proibir apanhar um *lock* em posse (fechado), proibir libertar um *lock* que não está em posse e faz com que os *threads* não se esqueçam de libertar todos os *locks* no final da sua execução.

Propomos uma tradução que preserva os tipos do cálculo  $\pi$  para o MIL. O cálculo  $\pi$ é uma álgebra de processos para descrever *mobilidade*: uma rede de processos interligados computa comunicando ligações (ou referências a outros processos). No cálculo  $\pi$ , a comunicação reconfigura dinamicamente a rede, fazendo com que os processos passem a estar visíveis a diferentes nós quando o sistema evolui. Ao traduzirmos o cálculo  $\pi$ em MIL, partimos de uma linguagem onde os processos comunicam através de passagem de mensagens e chegamos a uma linguagem onde *threads* comunicam por memória partilhada.

O processo de compilação não é directo nem trivial: certas abstracções, como canais, não têm uma representação complementar no MIL. Para ajudar a tradução, desenvolvemos, na linguagem de destino, uma biblioteca de tampões não limitados e polimórficos que são usados como canais. Estes tampões não limitados são monitores de Hoare, daí introduzirem uma forma de sincronização aos *threads* que estejam a aceder o tampão, e que encapsulam a manipulação directa de *locks*. A disciplina de *locks* do MIL permite representar explicitamente a noção da transferência ininterrupta da região crítica dos monitores—vai do *thread* que assinala a condição, e que termina, para o *thread* que está à espera nessa mesma condição, e que é activado. Os tampões não limitados são uma boa forma de representar canais, o que por sua vez simplifica a tradução, já que enviar uma mensagem corresponde a colocar um elemento no tampão, e que receber uma mensagem equivale a retirar um elemento do tampão. Impomos uma ordem FIFO no tampão, para assegurarmos que as mensagens enviadas têm a oportunidade de serem alguma vez recebidas. A função de tradução que definimos é uma especificação formal do compilador. A tradução do cálculo  $\pi$  para MIL comporta a tradução de tipos, de valores e de processos. Os compiladores que preservam os tipos dão garantias em termos de segurança (os programas gerados não vão correr mal) e também em termos de correcção parcial (as propriedades semânticas dadas pelos tipos perduram no programa gerado). O nosso resultado principal é, portanto, uma tradução que preserva os tipos: o compilador gera programas MIL correctos ao nível dos tipos para processos  $\pi$  fechados e bem tipificados. Outra preocupação da nossa função de tradução é que o programa gerado tente manter o nível de concorrência do programa fonte, o que inclui a criação dinâmica de *threads* e a sincronização entre *threads*.

As contribuições deste trabalho são:

- Um algoritmo de compilação que preserva os tipos, mostrando a flexibilidade do MIL num ambiente tipificado e *race-free*.

- Exemplos de programação e estruturas de dados feitos em MIL. Mostramos a implementação de tampões polimórficos não limitados sob a forma de monitores, de variáveis de condição genéricas (primitivas dos monitores) e de filas polimórficas. Também descrevemos como codificar monitores na linguagem MIL.

- Ferramentas. Criámos um protótipo para o compilador de π para MIL, o que consiste em: o analisador sintáctico, o analisador semântico (estático) e o gerador de código. Refinámos o protótipo do MIL: adicionámos suporte para tipos universais e existenciais, *locks* de leitores/escritores, locks lineares e tuplos locais. Criámos uma *applet* Java que mostra de uma forma rápida e intuitiva o nosso trabalho sem ser necessário qualquer instalação (desde que o navegador *web* suporte *applets* de Java): podemos gerar código MIL a partir de código π, alterar o código MIL gerado e executá-lo. Os nossos protótipos estão disponíveis *on-line*, em http://gloss.di.fc.ul.pt/mil/: a *applet* Java, o código fonte e exemplos π e MIL.

**Palavras-chave:** cálculo  $\pi$ , multithreading, compilação certificada, compilação conservadora de tipos, compilação orientada a tipos, monitores

#### Abstract

Physical and electrical constrains are compelling manufactures to augment the number of cores in each die to continue delivering performance gains. To take advantage of the emerging multicore architectures, we need to master parallel and concurrent programming. We encourage empowering languages with adequate concurrency primitives: finegrained for low-level languages and coarse grained for high-level languages. This way, compilers can reuse fined-grained primitives to encode multiple coarse-grained primitives.

Work in type-directed compilers (*e.g.*, the Typed Intermediate Language for the ML language) showed that using a strongly typed intermediate language increases not only safety but also efficiency. Typed assembly languages (TAL) draw the benefits from having type information from end-to-end, originating type-preserving compilers. Vasconcelos and Martins proposed the Multithreaded Intermediate Language (MIL) as a typed assembly language for multithreaded architectures, featuring an abstract multicore machine with shared memory that is equipped with locks.

We propose a type-preserving translation from a simply typed  $\pi$ -calculus into MIL. Process calculi provide natural compilation schemes that expose thread-level parallelism, present in the target architecture. By translating the  $\pi$ -calculus into MIL, we depart from a language where processes communicate through message-passing and arrive in a language where threads communicate through shared memory.

Our contributions consist of

- a translation function that generates MIL from the  $\pi$ -calculus;

- the translation is type-preserving;

- using an unbounded buffer monitor to encode channels;

- detailed examples in MIL (handling concurrency primitives and control-flow);

- implementations in MIL of condition variables, of polymorphic queues, and of an unbounded buffer;

- a generic encoding of monitors in MIL.

**Keywords:** the  $\pi$ -calculus, multithreading, certified compiler, type-preserving compilation, type-directed compilation, monitors

### Contents

| 1                                       | Introduction 1                        |                            |   |  |  |  |  |  |  |  |  |

|-----------------------------------------|---------------------------------------|----------------------------|---|--|--|--|--|--|--|--|--|

|                                         | 1.1                                   | Motivation                 | 1 |  |  |  |  |  |  |  |  |

|                                         | 1.2                                   | Contributions              | 3 |  |  |  |  |  |  |  |  |

|                                         | 1.3                                   | Outline                    | 4 |  |  |  |  |  |  |  |  |

| 2                                       | $\pi$ -Calculus                       | 7                          |   |  |  |  |  |  |  |  |  |

|                                         | 2.1                                   | Syntax                     | 8 |  |  |  |  |  |  |  |  |

|                                         | 2.2                                   | Operational Semantics      | 0 |  |  |  |  |  |  |  |  |

| 3 A Multithreaded Intermediate Language |                                       |                            |   |  |  |  |  |  |  |  |  |

|                                         | 3.1                                   | Syntax                     | 3 |  |  |  |  |  |  |  |  |

|                                         | 3.2                                   | Operational Semantics      | 5 |  |  |  |  |  |  |  |  |

|                                         | 3.3                                   | Type Discipline         28 | 8 |  |  |  |  |  |  |  |  |

|                                         | 3.4                                   | MIL programming examples   | 6 |  |  |  |  |  |  |  |  |

|                                         | 3.5                                   | Types against races        | 0 |  |  |  |  |  |  |  |  |

| 4                                       | An Unbounded Buffer Monitor in MIL 43 |                            |   |  |  |  |  |  |  |  |  |

|                                         | 4.1                                   | The monitor                | 7 |  |  |  |  |  |  |  |  |

|                                         | 4.2                                   | Wait and Signal            | 2 |  |  |  |  |  |  |  |  |

|                                         | 4.3                                   | Polymorphic Queues         | 3 |  |  |  |  |  |  |  |  |

|                                         | 4.4                                   | Discussion                 | 9 |  |  |  |  |  |  |  |  |

| 5                                       | Con                                   | piling $\pi$ into MIL 6    | 1 |  |  |  |  |  |  |  |  |

|                                         | 5.1                                   | The translation function   | 1 |  |  |  |  |  |  |  |  |

|                                         | 5.2                                   | Results                    | 9 |  |  |  |  |  |  |  |  |

| 6                                       | Con                                   | clusion 9.                 | 3 |  |  |  |  |  |  |  |  |

| A                                       | Example of code generation 9          |                            |   |  |  |  |  |  |  |  |  |

| Bi                                      | Bibliography 101                      |                            |   |  |  |  |  |  |  |  |  |

## **List of Figures**

| 2.1  | The echo server interaction from the server's point of view                              | 7  |  |  |  |  |

|------|------------------------------------------------------------------------------------------|----|--|--|--|--|

| 2.2  | Process syntax.                                                                          | 8  |  |  |  |  |

| 2.3  | Type syntax                                                                              | 10 |  |  |  |  |

| 2.4  | Structural congruence rules.                                                             | 13 |  |  |  |  |

| 2.5  | Reaction rules.                                                                          | 14 |  |  |  |  |

| 2.6  | Typing rules for the $\pi$ -calculus                                                     | 17 |  |  |  |  |

| 3.1  | The MIL architecture.                                                                    | 22 |  |  |  |  |

| 3.2  | The lock discipline.                                                                     |    |  |  |  |  |

| 3.3  | Instructions                                                                             | 24 |  |  |  |  |

| 3.4  | Abstract machine                                                                         | 24 |  |  |  |  |

| 3.5  | Operational semantics (thread pool)                                                      | 25 |  |  |  |  |

| 3.6  | Operational semantics (locks).                                                           | 26 |  |  |  |  |

| 3.7  | Operational semantics (memory)                                                           | 27 |  |  |  |  |

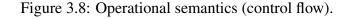

| 3.8  | Operational semantics (control flow)                                                     | 28 |  |  |  |  |

| 3.9  | Types                                                                                    | 29 |  |  |  |  |

| 3.10 |                                                                                          |    |  |  |  |  |

|      | typing rules for types $\Psi \vdash \tau$ .                                              | 30 |  |  |  |  |

| 3.11 | Typing rules for instructions (thread pool and locks) $\Psi; \Gamma; \Lambda \vdash I$   |    |  |  |  |  |

| 3.12 | Typing rules for instructions (memory and control flow) $\Psi; \Gamma; \Lambda \vdash I$ | 32 |  |  |  |  |

| 3.13 | Typing rules for machine states.                                                         | 36 |  |  |  |  |

| 4.1  | An Hoare-style unbounded buffer monitor.                                                 | 44 |  |  |  |  |

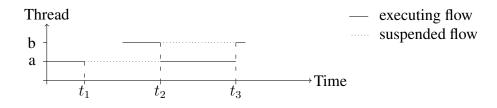

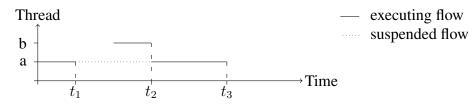

| 4.2  | Execution view of two threads accessing the same monitor                                 |    |  |  |  |  |

| 4.3  | Execution view of two threads accessing the same monitor, following the                  |    |  |  |  |  |

|      | signal and exit regime                                                                   | 45 |  |  |  |  |

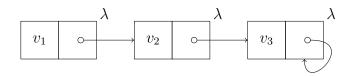

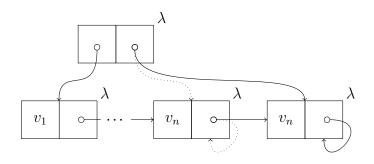

| 4.4  | Three nodes connected linearly. Each node, guarded by the same lock $\lambda$ ,          |    |  |  |  |  |

|      | holds a value $v_i$                                                                      | 54 |  |  |  |  |

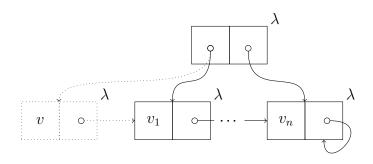

| 4.5  | One node connected to another node                                                       | 55 |  |  |  |  |

| 4.6  | A linked-list with one node and one sentinel                                             |    |  |  |  |  |

| 4.7  | Enqueuing the <i>n</i> -th value to a linked-list                                        | 57 |  |  |  |  |

| 4.8  | Dequeuing the first node of a linked-list.                                               | 59 |  |  |  |  |

### Chapter 1

### Introduction

#### **1.1 Motivation**

Physical and electrical constrains are limiting the increase of processor's clock speed in such a way that the computing power of each processing unit is not expected to increase much more in a near future. Instead, manufactures are augmenting the number of processing units in each processor (multicore processors) to continue delivering performance gains. The industry is making big investments in projects, such as RAMP [39] and BEE2 [3], that enable the emulation of multicore architectures, showing interest in supporting the foundations for software research that targets these architectures.

To take advantage of multicore architectures, programmers must master parallel and concurrent programming [33]. With the advent of major availability of parallel facilities (from embedded systems, to super-computers), programmers must do a paradigm shift from sequential to parallel programming and produce, from scratch, software adapted for multicore platforms.

Multithreading is one of industry's most accepted answer to write explicitly parallel systems. Locks stand forth as a fundamental mechanism for writing highly-efficient multithreaded code [8]. Holding locks for too much time, misusing readers/writers locks, and choosing the wrong synchronisation mechanisms are all frequent arising problems encountered while developing multithreaded systems. Such problems can be mitigated with the appropriate high-level concurrency abstractions. We need to empower low-level languages with fine-grained concurrency primitives in a way that compilers for high-level concurrent languages can take advantage of both efficiently and safely.

Types and type systems are a simple and effective way to ensure safety [9, 36]. Types are not only used by type systems to free programs from executing errors, but serve as specification (verifiable in an automatic manner) that captures important operational properties, such as memory safety. TIL, a type-directed optimising compiler for ML, showed that using a strongly typed intermediate language could help optimisation [44]. Also, the typechecker for TIL helped in making the development of the compiler faster and safer,

since programming errors would be caught early on.

TIL, however, only preserved types through approximately 80% of the compilation process. Loosing type information in the last 20% seems to just move the problem one (translation) step further. TIL was still translating to an untyped language in the end! This thought stemmed the development of Typed Assembly Languages (TAL) [31] and Proof-Carrying Code (PCC) [32], two techniques that introduce *compiler certification*, a formal method that verifies the semantics of the generated code. *Type-preserving* compilers save type information throughout every compilation stage, enabling both safer compilation and better conservation of semantics — the ones captured by types.

We propose a compiler that addresses the issues raised so far.

- the source language must offer concurrency and parallel abstractions;

- the compiler must target a multicore architecture;

- the translation must preserve type information.

Regarding the source language, process calculi arise as an expressive programming model for concurrent and parallel computing. The  $\pi$ -calculus [28], in particular, has wellunderstood semantics, consists of a small set of primitives and operators, and its fundamental step of computation is communication. Process calculi provide natural compilation schemes that expose thread-level parallelism [25]. We choose the simply typed  $\pi$ -calculus as our source language [5, 21, 28].

The Multithreaded Intermediate Language (MIL) [47] is a multithreaded typed assembly language for multicore architectures that have shared (main) memory. This strongly typed language gives the following safety properties: memory safety, control-flow safety, race-freedom safety, and deadlock-freedom safety [48]. MIL contradicts the statement that "the association between locks and data is established mostly by convention" [43] by making this association explicit in the language. The type system enforces a policy on the lock usage that forbids locking an owned locked and unlocking an open lock, and makes sure that threads do not forget to unlock owned locks.

Another possible choice for the target language of a compiler of a concurrent language is the work from Feng and Shao [12], following the lines of program verification and PCC. They propose a logic "type" system for static verification of concurrent assembly programs, with support for unbounded dynamic thread creation and termination. Their idea is to reflect specifications, defined as high-level logic, at the assembly level. Type systems embed a limited array of security properties as part of its soundness proof. By using types and typing rules you gain succinct but limited safety properties, the proof of the program is generated automatically in the form of types. Frameworks like CAP [49, 50] give more flexibility with the cost of making the proof explicit. We choose the former approach since the source language is already less expressive than MIL in terms of types. In terms of a type-preserving compilation, there is no advantage in choosing an even more expressive system like the latter.

There are various works in type-preserving compilation. We highlight the seminal work from Morrisett *et al.* [31] that presents a five stage type-preserving compilation, from System F [17] into a (sequential) typed assembly language. Their work shows the various steps necessary to transform a high-level language into the chosen TAL, whilst maintaining type information. Their TAL features high-level abstractions like tuples, polymorphism, and existential packages.

In the context of process calculi compilation, Turner proposes an abstract machine encoded in the  $\pi$ -calculus for running Pict [38] that is then translated into C [45]. The abstract machine does not take types into consideration. C is not expressive enough to retain the type information of the source language (a polymorphic version of the  $\pi$ -calculus). Also, the generated code is sequential and therefore does not take into account multicore architectures.

In the same line of development as Turner's abstract machine, Lopes *et al.* [25] proposed a multithreaded language (TTyCO) and an abstract machine for TyCO [46], an asynchronous process calculus. TTyCO is an intermediate untyped language, featuring threads and message-queues. This intermediate language lays at a higher-level than MIL. In a sense, we implement the higher-level features of TTyCO that lack in MIL using the unbounded buffer monitor. TTyCO gives no safety-properties. Since the target language is untyped, no type-preserving results can be obtained. Our work continues the work done in TTyCO by targeting a multithreaded typed assembly language through a type-preserving compilation.

### **1.2** Contributions

The present work proposes a type-preserving translation from the  $\pi$ -calculus into MIL. The  $\pi$ -calculus is a process algebra for describing *mobility*: a network of interconnected processes compute by communicating references to processes (links) among them [28]. We choose a simple, simply typed version of the  $\pi$ -calculus [5, 21, 28].

MIL is an assembly language targeted at an abstract multicore machine equipped with a shared main memory. By translating the  $\pi$ -calculus into MIL, we depart from a language where processes communicate through message-passing and arrive in a language where threads communicate through shared memory. The source and target languages as well as their respective underlying models differ substantially. The former is declarative, computation takes place as processes communicate, and synchronisation is made through message-passing. The latter is imperative, the system evolves by evaluating instructions, and synchronisation is made through shared memory.

Translation is not direct. Mapping  $\pi$ -processes into threads follows naturally, *e.g.* we

translate two processes running in parallel into two concurrent threads, but there is no correspondence of channels in MIL. A by-product of our work is an unbounded buffer monitor, a variant of Hoare's bounded buffer monitor [20], entirely written in MIL, that is used by our compiler to encode channels. The monitor provides a (polymorphic) FIFO-ordered buffer that mediates the asynchronous communication between producers and consumers.

As a proof of concept, we develop a program in Java that implements the presented  $\pi$ -calculus type system (in the form of a typechecker) and the  $\pi$ -to-MIL translation function (in the form of a compiler). The MIL interpreter (and typechecker), the  $\pi$ -to-MIL compiler, the examples presented in this work, and the code for the unbounded buffer monitor are all available on-line [26].

The summary of our contributions is:

- a translation function that maps terms of the  $\pi$ -calculus into MIL terms;

- **type-preserving compilation** the main result is that the translation of typable (closed)  $\pi$ -programs generates well-typed MIL programs;

- **detailed examples** we document lock acquisition and control-flow manipulation in MIL through a series of examples;

- a generic encoding of monitors in MIL we precise code and data constituents of monitors as well as give meaning to entering and exiting a monitor procedure;

- **condition variables** we show a MIL implementation of condition variables that features a representation of suspended threads in the form of continuations;

- polymorphic queues we present a polymorphic implementation of queues;

- polymorphic unbounded buffer monitor we show an implementation of a monitor in MIL that represents an unbounded buffer, shielding the client code (the  $\pi$ -calculus compiler in particular) from the hazardous task of direct lock manipulation;

- MIL interpreter we updated the MIL tools (the typechecker and the interpreter);

- $\pi$ -to-MIL compiler we devised a prototype that includes a typechecker for the source language and the  $\pi$ -to-MIL compiler.

### **1.3** Outline

The current chapter introduces our work. In the closing chapter we summarise our results and outline directions for further investigation. Chapters 2 and 3 describe the source language ( $\pi$ -calculus) and the target language (MIL), respectively, and establish the foundations for our contribution, which is presented in Chapters 4 and 5.

More specifically, in Chapter 2, we present a polyadic, simply typed, and asynchronous  $\pi$ -calculus, by formalising its syntax and semantics. We omit the summation and the matching operators from the calculus. The replication operator is restricted to input processes only. Our goal is to expose the source language of our compiler.

Chapter 3 gives a thorough description of MIL, the target language of the translation, covering both syntax and semantics. We devote one section to exemplify lock acquisition and transfer of control flow, two fundamental programming patterns that we apply extensively in the run-time and in the generated code. The last section of the chapter presents the two main results of MIL: that "well-typed machines do not get stuck" and that well-typed machines do not have races.

Chapter 4 details the supporting code used by the translation, including polymorphic queues, condition variables, and the encoding of Hoare-style monitor in MIL. We employ these generic elements in the implementation of an unbounded (polymorphic) buffer monitor, used to encode  $\pi$ -channels in MIL. This chapter encloses our contribution in MIL programming, yielding three libraries: queues, condition variables, and unbounded buffer monitors.

Chapter 5 formalises the translation from the  $\pi$ -calculus into MIL. The unbounded buffer monitor presented in Chapter 4 simplifies the translation, since sending and receiving messages from a channel may be viewed as appending and removing elements from a buffer. We show the outcome of applying the translation function to a  $\pi$ -process. This section includes a detailed proof of the main result of our work: a type-preserving compilation, asserting that type-correct  $\pi$ -programs compile into type-correct MIL programs.

### Chapter 2

### **The** $\pi$ **-Calculus**

The  $\pi$ -calculus, developed by Robin Milner, Joachim Parrow, and David Walker [28], is a process algebra for describing *mobility*, in which processes "move" in a virtual space. The underlying model is a network of interconnected processes that interact by communicating connection links (channels). Since connection links can be retransmitted, the  $\pi$ -calculus is able to express dynamic reconfigurations of the network, where resources become accessible to different parties as the system evolves.

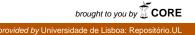

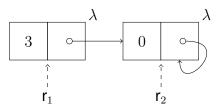

As a motivation example, consider process *echo server* that bounces every message received through a channel back to the sender process (the client). Figure 2.1 depicts such an interplay with emphasis on the server. The server is accessible via link *echo*. Before interaction the server maintains two placeholders to be filled upon data arrival: a message msg that is illustrated by a dashed box in the figure (left) and a *reply* link represented by a circle enclosing a cross. After interaction the server uses the *reply* channel, represented in Figure 2.1 (right) by a filled circle, to bounce the received value msg back to the client, portrayed in the figure by a box holding two symbols ( $\bullet \diamond$ ). The arrows from msg to reply and from reply to the client show the data-flow of the echoed message.

In this chapter we describe the source language of our compiler: the  $\pi$ -calculus. We begin by depicting the syntax of processes and of types on Section 2.1. Next, we cover the operational semantics of the  $\pi$ -calculus and its type system.

Figure 2.1: The echo server interaction from the server's point of view.

|       |   | Values  |         |                                       | Processes        |

|-------|---|---------|---------|---------------------------------------|------------------|

| v ::= | x | name    | P,Q ::= | 0                                     | inactive         |

|       | n | integer |         | $\overline{x}\langle \vec{v} \rangle$ | output           |

|       |   |         |         | $x(\vec{y}).P$                        | input            |

|       |   |         |         | $!x(\vec{y}).P$                       | replicated input |

|       |   |         |         | $P \mid Q$                            | parallel         |

|       |   |         |         | $(\nux\colon\hat{[\vec{T}]})P$        | restriction      |

The syntax of T is defined in Figure 2.3.

Figure 2.2: Process syntax.

### 2.1 Syntax

The adopted  $\pi$ -calculus syntax is based on [27] with extensions presented in [42]: asynchronous [5, 21], meaning that sending a message does not block; polyadic, corresponding to the transmission of sequences of values; and simply typed with constants (integers).

**Processes.** The syntax, depicted in Figure 2.2, is divided into two categories: *values* ranged over by v that represent names and integers; and *processes* ranged over by  $P, Q, \ldots$  that compose the network of processes. A name, ranged over by  $x, y, \ldots$ , is either a link or a placeholder for values. The value n is a meta-variable over integers that corresponds to any possible integer. A vector above a symbol abbreviates a possibly empty sequence of these symbols. For example  $\vec{x}$  stands for the sequence of names  $x_1 \ldots x_n$  with  $n \ge 0$ .

Processes consist of the nil process 0, corresponding to the inactive process; the output process  $\overline{x}\langle \vec{v} \rangle$  that sends data  $\vec{v}$  through a channel x; the input process  $x(\vec{y}).P$  that binds a received sequence of values to names  $\vec{y}$  in the scope of process P via a channel x; the replicated input process  $!x(\vec{y}).P$  that represents an infinite number of input processes running in parallel; the parallel composition of processes  $P \mid Q$  that represents two processes running in parallel; and the restriction process  $(\nu x : \hat{T}])P$  that creates a new channel definition local to process P.

The following example is a possible implementation of the echo server depicted in Figure 2.1.

$$!echo(msg, reply).\overline{reply}\langle msg\rangle$$

(2.1)

The process is ready to receive a message msg and a reply channel via channel *echo*. Upon arrival, the message is bounced back to the server again through the reply link.

**Definition 2.1.1.** Process *P* is a *sub-term* of process *Q* iff

• Q is P,

- or Q is  $P' \mid Q'$  and P is a sub-term of P',

- or Q is  $P' \mid Q'$  and P is a sub-term of Q',

- or Q is  $x(\vec{y}).P'$  and P is a sub-term of P',

- or Q is  $!x(\vec{y}).P'$  and P is a sub-term of P',

- or Q is  $(\nu x: \hat{T}] P'$  and P is a sub-term of P'.

**Types.** In the  $\pi$ -calculus a name can assume a range of values during execution. For example, a name can represent a number 1 or some channel. A type defines the set of values a name accepts [9]. By saying that the name is of type integer, we suppose that the given name can only represent integers during every step of execution. We call a language *typed*, when names can be given types, the opposite of untyped languages.

*Type systems* keep track of types of names and are used to detect execution errors in programs. We quote the definition from Benjamin Pierce [35]:

A type system is a tractable syntactic method for proving the absence of certain program behaviours by classifying phrases according to the kinds of values they compute.

We distinguish two forms of executing errors: *trapped errors* that cause computation to stop immediately and *untrapped errors* that go unnoticed for a certain period of time. For instance, if a machine halts computation when an integer value is used as a channel, then this misuse is a trapped error. A form of an untrapped error is when a machine dwells into an inconsistent state, but does not halt, which could happen upon sending a sequence of three values through a channel that expects a sequence of two values. *Safe languages* are free from untrapped errors, the class of errors harder to track. Languages may enforce safety by performing run-time or compile-time (static) checks. Typed languages usually employ both forms of safety checks. We call *typechecking* to the process that performs the static checks on a typed language. The *typechecker* is the algorithm responsible for typechecking the language.

Which errors should a type system detect? Let *forbidden errors* be the class of possible errors caught by type systems. Forbidden errors should include all untrapped errors and some trapped errors. Type systems therefore target safe languages and additionally catch some trapped errors. We designate programs free from forbidden errors *well-behaved*. A language where all of the (legal) programs are well-behaved is called *strongly checked*.

There are numerous advantages for having types and type systems. For example, a code generator has additional hints for knowing how much memory a value needs. Execution efficiency can be improved, because we can replace run-time checks by static

T ::= int integer type  $| \hat{T} |$  channel type

Figure 2.3: Type syntax.

checks. Small-scale development is hastened by the feedback of the typechecker, reducing the number of debugging sessions. Type information is essential for development tools, including refactoring tools, code analysis, code verification, and integrated development environments. From the knowledge of dependencies between modules given by types, compilers can perform partial compilation that reduces the overall compilationtime. Language features captured by types are usually orthogonal, thus tend to reduce the complexity of programming languages.

The  $\pi$ -calculus version we choose is *monomorphic*, strongly checked, and typed. Monomorphism means that every program fragment (*e.g.*, a value) can only have one type, as opposed to polymorphism, in which a program fragment can have many types. We assign type int to integers. The channel type  $\hat{T}$  describes a link that may communicate a sequence of values each of which assigned to type  $T_i$ , respectively.

For example, type ^[int, ^[int]] captures the semantics of channel *echo* from Process 2.1 and corresponds to a channel type with two parameters, the first an integer type and the second a channel type that communicates integers.

#### 2.2 **Operational Semantics**

The semantics of the  $\pi$ -calculus expresses formally the behaviour of processes. With a rigorous semantics we can identify if two processes have the same structural behaviour, observe how a process evolves as it interacts, and analyse how links move from one process to another.

We begin with name binding. Two constructors bind names.

**Definition 2.2.1** (Binding). In  $(\nu x: \tilde{T}] P$  the displayed occurrence of x is a *binding* with *scope* P. In  $x(\vec{y}).P$  each occurrence of  $y_i$  is a binding with scope P. An occurrence of a name is *bound* if it is, or lies within the scope of, a binding occurrence of the name. An occurrence of a name in a process is *free* if it is not bound. A process with only bound names is said to be *closed*.

The bound name function can be inductively defined as:

Definition 2.2.2 (The bound name function).

$$bn(\mathbf{0}) = \emptyset$$

$$bn(\overline{x}\langle \vec{v} \rangle) = \emptyset$$

$$bn(x(\vec{y}).P) = \{\vec{y}\} \cup bn(P)$$

$$bn(!x(\vec{y}).P) = bn(x(\vec{y}).P)$$

$$bn(P \mid Q) = bn(P) \cup bn(Q)$$

$$bn((\nu x: \hat{T}])P) = \{x\} \cup bn(P)$$

Contrarily to bound names, free names are globally defined. The free name function can be defined as:

**Definition 2.2.3** (The free names function).

$$fn(\mathbf{0}) = \emptyset$$

$$fn(\overline{x}\langle \vec{v} \rangle) = \{x\} \cup fn(\vec{v})$$

$$fn(x(\vec{y}).P) = \{x\} \cup fn(P) \setminus \{\vec{y}\}$$

$$fn(!x(\vec{y}).P) = fn(x(\vec{y}).P)$$

$$fn(P \mid Q) = fn(P) \cup fn(Q)$$

$$fn((\nu x: \hat{T}]) P) = fn(P) \setminus \{x\}$$

$$fn(v_1 \dots v_n) = fn(v_1) \cup \dots \cup fn(v_n)$$

$$fn(x) = \{x\}$$

$$fn(n) = \emptyset$$

For example, in process

$$!echo(msg, reply).reply\langle msg \rangle$$

name echo is free and names msg and reply are bound.

Notice a name may occur both free and bound in the same expression. In the following example name x appears bound and free:

$$x(y).y(x).\mathbf{0}$$

The first displayed occurrence of name x is free, in the outer input process; the second displayed occurrence of x is bound. In the scope of process 0 the use of name x targets the parameter of link y and not the free name.

**Definition 2.2.4.** A *substitution* is a function that is the identity except on a finite set, defined from values to names. A formula  $v\sigma$  represents the application of substitution  $\sigma$  to value v, where:

$$\mathbf{n}\sigma \stackrel{\text{def}}{=} \mathbf{n} \qquad \qquad x\sigma \stackrel{\text{def}}{=} \sigma(x)$$

As for processes, say  $P\sigma$ , the substitution replaces each free occurrence of name x in process P by  $x\sigma$ . We define the application of a substitution to processes (see the *name convention* below) as:

$$\begin{aligned} \mathbf{0}\sigma \stackrel{\text{def}}{=} \mathbf{0} \\ (\overline{x}\langle \vec{v} \rangle)\sigma \stackrel{\text{def}}{=} \overline{x\sigma} \langle \vec{v}\sigma \rangle \\ (x(\vec{y}).P)\sigma \stackrel{\text{def}}{=} (x\sigma)(\vec{y}).P\sigma \\ (!x(\vec{y}).P)\sigma \stackrel{\text{def}}{=} !((x(\vec{y}).P)\sigma) \\ (P \mid Q)\sigma \stackrel{\text{def}}{=} (P\sigma) \mid (Q\sigma) \\ ((\nu x: \hat{T}]) P)\sigma \stackrel{\text{def}}{=} (\nu x: \hat{T}]) P\sigma \end{aligned}$$

We write  $\{\vec{v}/\vec{x}\}$  for the substitution  $\sigma$  such that  $x_i\sigma = v_i$  and  $y\sigma = y$  for  $y \notin \vec{x}$ .

For example, substituting z for x in process  $\overline{x}\langle 2 \rangle | x(y).0$  yields the following result, where  $\sigma = \{z/x\}$ :

$$(\overline{x}\langle 2 \rangle \mid x(y).\mathbf{0})\sigma$$

= $(\overline{x}\langle 2 \rangle)\sigma \mid (x(y).\mathbf{0})\sigma$

= $\overline{x\sigma}\langle 2\sigma \rangle \mid (x\sigma)(y).\mathbf{0}\sigma$

= $\overline{\sigma(x)}\langle 2 \rangle \mid (\sigma(x))(y).\mathbf{0}$

= $\overline{z}\langle 2 \rangle \mid z(y).\mathbf{0}$

**Definition 2.2.5** (Change of bound names). A *change of bound names* in process P is the replacement of a sub-term of P in the form  $x(\vec{y}).Q$  by  $x(\vec{z}).Q\{\vec{z}/\vec{y}\}$  or in the form  $(\nu y: \hat{\vec{T}}) Q$  by  $(\nu z: \hat{\vec{T}}) Q\{z/y\}$ , where z and  $\vec{z}$  are not bound nor free in Q.

A *congruence relation* is an equivalence relation<sup>1</sup> that satisfies some algebraic properties. Furthermore, if  $\equiv$  is a congruence relation on processes, then

- if  $P \equiv Q$ , then  $x(\vec{y}).P \equiv x(\vec{y}).P$ ;

- if  $P \equiv Q$ , then  $!x(\vec{y}).P \equiv !x(\vec{y}).P$ ;

- if  $P \equiv Q$ , then  $P \mid R \equiv Q \mid R$ ;

- if  $P \equiv Q$ , then  $(\nu x: \hat{T}] P \equiv (\nu x: \hat{T}] Q;$

Process P is  $\alpha$ -congruent with process Q, notation  $P \equiv_{\alpha} Q$ , if Q results from P by successive changes of bound names. For example,

$$echo(msg, reply).reply\langle msg \rangle \equiv_{\alpha} echo(x, y).\overline{y}\langle x \rangle$$

<sup>&</sup>lt;sup>1</sup>Equivalence relations are reflexive, symmetric, and transitive.

- (S1) If  $P \equiv_{\alpha} Q$ , then  $P \equiv Q$ .

- (S2) The Abelian monoid laws for parallel: commutative  $P \mid Q \equiv Q \mid P$ , associative  $(P \mid Q) \mid R \equiv P \mid (Q \mid R)$ , and having the inactive process as its neutral element  $P \mid \mathbf{0} \equiv P$ .

- (S3)  $!x(\vec{y}).P \equiv x(\vec{y}).P \mid !x(\vec{y}).P$

- (S4) The scope extension laws:

$$(\nu x: \hat{\vec{T}}) \mathbf{0} \equiv \mathbf{0}$$

$$(\nu x: \hat{\vec{T}}) (P \mid Q) \equiv P \mid (\nu x: \hat{\vec{T}}) Q, \text{ if } x \notin \text{fn}(P)$$

$$(\nu x: \hat{\vec{T}}) (\nu y: \hat{\vec{S}}) P \equiv (\nu y: \hat{\vec{S}}) (\nu x: \hat{\vec{T}}) P$$

#### Figure 2.4: Structural congruence rules.

**Name convention.** For any given mathematical context (*e.g.*, definition, proof), terms are up to  $\alpha$ -congruence and assume a convention (Barendregt's variable convention [2]), in which all bound names are chosen to be different from the free names and from each other.

For example, process

$$x(y).y(x).\mathbf{0}$$

breaks the convention, since the displayed occurrence x is both bound and free. The following  $\alpha$ -congruent term assumes the name convention:

$$x(y).y(z).\mathbf{0}$$

**Structural Congruence.** The syntax differentiates processes that intuitively represent the same behaviour. For example, process  $P \mid Q$  and process  $Q \mid P$  are syntactically different, although our intuition about processes running in parallel is that the syntactic order of these processes is irrelevant. Process  $(\nu x: \hat{}[]) \overline{y} \langle x \rangle$  and process  $(\nu z: \hat{}[]) \overline{y} \langle z \rangle$ are also syntactically different, but both represent an output channel sending a private channel, regardless of the different choice of names.

The *structural congruence* relation,  $\equiv$ , is the smallest congruence relation on processes closed under rules given in Figure 2.4 that capture the intuition about the behaviour of processes. The structural congruence relation divides processes into equivalence classes of terms, simplifying operational semantics rule (*cf.* Figure 2.5). Rule S1 brings the change of bound names into structural congruence; Rule S2 represents the standard commutative monoid laws regarding parallel composition, having 0 as its neutral element; Rule S3 allows replication to fold and unfold. Rule S4 allows for scope

$$\frac{\overline{x(\vec{y}).P \mid \overline{x}\langle \vec{v} \rangle \to P\{\vec{v}/\vec{a}\}} \text{ React}}{P \to P'} \\

\frac{P \to P'}{P \mid Q \to P' \mid Q} \text{ Par } \frac{P \to P'}{(\nu \, x \colon \hat{[\vec{T}]}) P \to (\nu \, x \colon \hat{[\vec{T}]}) P'} \text{ Res}} \\

\frac{Q \equiv P \quad P \to P' \quad P' \equiv Q'}{Q \to Q'} \text{ Struct}}$$

Figure 2.5: Reaction rules.

extension. Notice that restriction order is of no importance, because terms assume the name convention.

**Reduction.** The reduction relation  $\rightarrow$  defined over processes establishes how a computational step transforms a process, as defined in Figure 2.5. The formula  $P \rightarrow Q$  means that process P can interact and evolve (reduce) to process Q. We interpret rules (*e.g.*, Figure 2.5) in form

$$\frac{A \quad B}{C}$$

as A and B imply C. For instance, Rule REACT is an axiom, whereas for Rule PAR we say that if P reduces to P' then  $P \mid Q$  reduces to  $P' \mid Q$ .

Rule REACT is the gist of the reduction rules, representing the communication along a channel. An output process,  $\overline{x}\langle \vec{v} \rangle$ , can interact with an input process,  $x(\vec{y}).P$ , since they share link x. Reduction sends output message  $\vec{v}$  along channel x, resulting in process  $P\{\vec{v}/\vec{y}\}$ .

Rule PAR expresses that reduction can appear as the left-hand side of a parallel composition. Rule REs governs reduction inside the restriction operator. With structural congruence, Rule STRUCT, we are able to rearrange processes so that they can react. Structural congruence and process reduction also bring non-determinism to the  $\pi$ -calculus, since we can arrange different processes to react differently.

Consider a copy of the echo server (Process 2.1) running concurrently with a client that sends number 10, as well as a channel for printing integers in the screen, say *printInt*. The order in which these processes are composed in parallel is relevant for reduction. The input must appear as the left-hand side and the output as the right-hand side, thus we rearrange the terms applying rule S2.

$$echo\langle 10, printInt \rangle | echo(msg, reply).reply\langle msg \rangle$$

$$\equiv echo(msg, reply).\overline{reply}\langle msg \rangle | \overline{echo}\langle 10, printInt \rangle$$

$$\Rightarrow \overline{printInt}\langle 10 \rangle$$

S2

REACT

By placing the process above in parallel with Process 2.1, interactions occur inside the parallel composition (Rule PAR):

$$echo(msg, reply).\overline{reply}\langle msg \rangle \mid \overline{echo}\langle 10, printInt \rangle$$

$$\mid !echo(msg, reply).\overline{reply}\langle msg \rangle \qquad \qquad \mathsf{Par}, \mathsf{React}$$

$$\rightarrow \overline{printInt}\langle 10 \rangle \mid !echo(msg, reply).\overline{reply}\langle msg \rangle$$

With structural congruence and Rule STRUCT, we discard the copy of the echo server, thereby simplifying the term.

$$\begin{split} & echo(msg, reply).\overline{reply}\langle msg \rangle \mid \overline{echo}\langle 10, printInt \rangle \\ & \mid !echo(msg, reply).\overline{reply}\langle msg \rangle \\ & \equiv \overline{echo}\langle 10, printInt \rangle \mid !echo(msg, reply).\overline{reply}\langle msg \rangle \qquad \text{Struct, Par, React} \\ & \rightarrow \overline{printInt}\langle 10 \rangle \mid !echo(msg, reply).\overline{reply}\langle msg \rangle \end{split}$$

Suppose we have a client that sends number 20 along with a private channel to a copy of the echo server.

$$\begin{aligned} & echo(msg, reply).\overline{reply}\langle msg \rangle \mid (\nu x) (\overline{echo}\langle 20, x \rangle \mid x(y).P) \\ & \equiv (\nu x) (echo(msg, reply).\overline{reply}\langle msg \rangle \mid \overline{echo}\langle 20, x \rangle \mid x(y).P) \\ & \rightarrow (\nu x) (\overline{x}\langle 20 \rangle \mid x(y).P) \\ & \rightarrow P\{20/y\} \end{aligned}$$

Res, React

By extending the scope of x to the server, we let interaction evolve inside the restriction and the parallel operators. The server bounces the number 20 back to client x(y). P with Rules RES and REACT. The scope of x is local to the client before reaction, since the scope extension performed on the first step does not make the channel accessible to the server — there are no occurrences of x in the server. After the first reduction, however, the name "moves" to the server. This new scope availability is called *scope extrusion*. The virtual movement from the client to the server is a kind of process mobility. A contrasting form of process mobility is physical mobility, where processes move in a physical space, rather than in a virtual space, for example a mobile phone moving in different cell sites.

Regard how two clients communicate with a copy of the echo server.

$$echo(msg, reply).\overline{reply}\langle msg \rangle \mid \overline{echo}\langle 10, r \rangle \mid \overline{echo}\langle 20, s \rangle$$

By letting reduction develop as is, the client sending channel r communicates with the server.

$$echo(msg, reply).\overline{reply}\langle msg \rangle \mid \overline{echo}\langle 10, r \rangle \mid \overline{echo}\langle 20, s \rangle \quad \text{Par, React}$$

$$\rightarrow \overline{r}\langle 10 \rangle \mid \overline{echo}\langle 20, s \rangle$$

But, if we reorder terms with structural congruence, we observe that the client sending number 20 and channel s can also interact with the server.

$$echo(msg, reply).\overline{reply}\langle msg \rangle \mid \overline{echo}\langle 10, r \rangle \mid \overline{echo}\langle 20, s \rangle$$

$$\equiv echo(msg, reply).\overline{reply}\langle msg \rangle \mid \overline{echo}\langle 20, s \rangle \mid \overline{echo}\langle 10, r \rangle \quad \text{Struct, Par, React}$$

$$\rightarrow \overline{s}\langle 20 \rangle \mid \overline{echo}\langle 10, r \rangle$$

This example highlights the non-deterministic nature of the  $\pi$ -calculus. The same process can yield different computational outcomes.

**Type system.** Before we explain the type system of the  $\pi$ -calculus, we introduce some common grounds.

**Definition 2.2.6** (Type environment). The *type assignment*, notation x: T, assigns a type to a name, where x is the name of the assignment, and T is type of the assignment.

A type environment, or typing, ranged over by  $\Gamma$ , is an ordered list of type assignments in the form of  $\emptyset, x_1: T_1, \ldots, x_n: T_n$ , with  $x_1 \ldots x_n$  distinct. The notation for the empty type environment is  $\emptyset$ . Extending a type environment  $\Gamma$  with type assignment x: T, with name x not mentioned in typing  $\Gamma$ , is of form  $\Gamma, x: T$ . The collection of names  $x_1 \ldots x_n$ declared in  $\Gamma$  is indicated by dom( $\Gamma$ ).

For example,

$\emptyset$ , echo: [int, [int]], msg: int, reply: [int]

is a type environment with three assignments: a channel echo that transmits an integer and a channels of integers, a name msg of type integer, and a channel reply that communicates integers.

*Type judgements* are of form  $\Gamma \vdash v$ : *T* for values and of form  $\Gamma \vdash P$  for processes. The former asserts that a value *v* has type *T*. The latter form asserts that process *P* respects the type assignments in  $\Gamma$ . A typing environment  $\Gamma$  stands as the left-hand side of both forms of judgement and declares the free names of the assertion.

A type system is a collection of axioms and inference rules. Figure 2.6 presents a standard type system for the  $\pi$ -calculus. Type judgements can be either *valid* or *invalid*. A valid type judgement is one that can be proved with an axiom or inference rule from a given type system. We call the proof of the validity of a type judgement a *typing derivation*. A judgement is invalid if there is no valid judgement to prove that assertion. For instance,  $\Gamma \vdash 3$ : int is a valid type judgement, yet  $\Gamma \nvDash 3$ :  $^{[int]}$  is an invalid type judgement. Notice the notation  $\nvDash$  for invalid type judgements. A value v is well-typed in  $\Gamma$ , for some  $\Gamma$ , if there is T such that  $\Gamma \vdash v$ : T. Similarly, given a typing  $\Gamma$ , a process P is well-typed under that type environment if  $\Gamma \vdash P$ .

For typing the  $\pi$ -calculus we are concerned with communication, in particular checking the usage of names. Typing values concerns integers and names. The axiom Tv-BASE

$$\begin{array}{c} \overline{\Gamma \vdash \mathrm{n:\,int}} \ \mathrm{Tv}\text{-}\mathrm{Base} & \overline{\Gamma, x \colon T \vdash x \colon T} \ \mathrm{Tv}\text{-}\mathrm{Name} \\ \\ \overline{\Gamma \vdash \mathbf{0}} \ \mathrm{Tv}\text{-}\mathrm{Nil} & \frac{\Gamma \vdash x \colon \widehat{\Gamma}] \quad \forall v_i \in \vec{v} \colon \Gamma \vdash v_i \colon T_i}{\Gamma \vdash \overline{x} \langle \vec{v} \rangle} \ \mathrm{Tv}\text{-}\mathrm{Out} \\ \\ \\ \frac{\Gamma \vdash x \colon \widehat{\Gamma}[T_1, \dots, T_n] \quad \Gamma, y_1 \colon T_1, \dots, y_n \colon T_n \vdash P}{\Gamma \vdash x(\vec{y}).P} \ \mathrm{Tv}\text{-}\mathrm{In} \\ \\ \\ \frac{\Gamma \vdash x(\vec{y}).P}{\Gamma \vdash !x(\vec{y}).P} \ \mathrm{Tv}\text{-}\mathrm{Rep} & \frac{\Gamma \vdash P \quad \Gamma \vdash Q}{\Gamma \vdash P \mid Q} \ \mathrm{Tv}\text{-}\mathrm{Par} \quad \frac{\Gamma, x \colon \widehat{\Gamma}[\vec{T}] \vdash P}{\Gamma \vdash (\nu \, x \colon \widehat{\Gamma}[T]) \, P} \ \mathrm{Tv}\text{-}\mathrm{Res} \end{array}$$

Figure 2.6: Typing rules for the  $\pi$ -calculus

states that integers are well-typed and assigned to type int. With rule TV-NAME the type assigned to a name is the one found (declared) in the type environment.

As for typing processes, the inactive process 0 is well-typed, axiom TV-NIL. With Rule TV-OUT, a name (of link type) is used as an output process with the arguments of the expected type. Like all composite processes, the typing of the input process  $x(\vec{y}).P$  (with rule TV-IN) depends upon the validity of its constituents, namely P. The continuation Pis therefore checked under a typing extended with parameters  $\vec{y}$  (each  $y_i$  is assigned to its respective type  $T_i$ ). To check a replicated process  $!x(\vec{y}).P$  with Rule TV-REP it is enough to verify if one of its copies is valid. The validity of the parallel process, checked with Rule TV-PAR, depends upon the validity of its parts. For typing restriction ( $\nu x : \hat{T}]$ ) P(rule TV-RES) we check the continuation P under a typing augmented with binding x.

We show that environment  $\emptyset$ , *echo*: [int, [int]] is enough to typify the echo server Process 2.1. Using rule TV-REP we derive

$$\frac{\overline{\emptyset, echo: \hat{[int, \hat{[int]}]} \vdash echo: \hat{[int, \hat{[int]}]}}{(1)} }{\Psi, echo: \hat{[int, \hat{[int]}]} \vdash echo(msg, reply).\overline{reply}\langle msg\rangle} }_{\text{Tv-In}} Tv-In} \\ \frac{\overline{\emptyset, echo: \hat{[int, \hat{[int]}]} \vdash echo(msg, reply)}}{\overline{\emptyset, echo: \hat{[int, \hat{[int]}]} \vdash !echo(msg, reply)}.\overline{reply}\langle msg\rangle}} Tv-Rep}$$

To type the echo server it is enough to type a copy of the server, Rule TV-REP. The derivation proceeds by applying rule TV-IN. The sequent for typing name *echo* with rule TV-NAME is direct. We are left with sequent (1) that also holds, where typing  $\Gamma \stackrel{\text{def}}{=} \emptyset$ , *echo*:  $\hat{[int, \hat{[int]}]}$ , *msg*: int, *reply*:  $\hat{[int]}$

$$\frac{\overline{\Gamma \vdash reply: \widehat{}[\mathsf{int}]} \operatorname{Tv-Name}}{\Gamma \vdash \overline{reply} \langle msg \rangle} \frac{\overline{\Gamma \vdash msg: \mathsf{int}}}{\operatorname{Tv-Out}} \operatorname{Tv-Out}$$

Therefore, Process 2.1 is well-typed under typing  $\emptyset$ , *echo*: [int, [int]].

#### **Lemma 2.2.7.** *If* $\Gamma \vdash P$ *, then* fn(P) $\subseteq$ dom( $\Gamma$ ).

*Proof.* The proof follows by induction in the structure of *P*.

- Case P is 0. By definition of fn,  $fn(0) = \emptyset$ . Hence,  $fn(0) \subseteq dom(\Gamma)$ .

- Case P is x̄⟨v̄⟩. By definition of fn, fn(x̄⟨v̄⟩) = {x} ∪ fn(v̄). By hypothesis Γ ⊢ x̄⟨v̄⟩, thus (by rule Tv-OUT) Γ ⊢ x : ^[T̄] and ∀v<sub>i</sub> ∈ v̄.Γ ⊢ v<sub>i</sub> : T<sub>i</sub>. By rule Tv-NAME, if Γ ⊢ x : ^[T̄], then x ∈ dom(Γ). By definition of ftv, ∀v<sub>i</sub> ∈ v̄.Γ ⊢ v<sub>i</sub> : T<sub>i</sub> if v<sub>i</sub> is a base value, then it is not in the free names of fn(v̄) if it is a name, by rule Tv-NAME, then v<sub>i</sub> ∈ dom(Γ). Hence, {x} ∪ fn(v̄) ⊆ dom(Γ).

- Case P is x(ÿ).Q. By definition of fn, fn(x(ÿ).Q) = {x} ∪ fn(Q) \ {ÿ}. By rule Tv-IN, we have that Γ ⊢ x : ^[T] and Γ, ÿ : T ⊢ Q. Since we have Γ ⊢ x : ^[T], then by rule Tv-NAME x ∈ dom(Γ). Since we have Γ, ÿ : T ⊢ Q, then, by the induction hypothesis, we have that fn(Q) ⊆ dom(Γ, ÿ : T). By applying the set theory and the definition of dom, we have:

$$\begin{aligned} &\operatorname{fn}(Q) \subseteq \operatorname{dom}(\Gamma, \vec{y} : \vec{T}) \\ &= \operatorname{fn}(Q) \subseteq \operatorname{dom}(\Gamma) \cup \operatorname{dom}(\vec{y} : \vec{T}) \\ &= \operatorname{fn}(Q) \subseteq \operatorname{dom}(\Gamma) \cup \{\vec{y}\} \\ &= \operatorname{fn}(Q) \setminus \{\vec{y}\} \subseteq \operatorname{dom}(\Gamma) \end{aligned}$$

We have that  $x \in \text{dom}(\Gamma)$ , hence

$$fn(Q) \setminus \{\vec{y}\} \subseteq dom(\Gamma)$$

$$= \{x\} \cup fn(Q) \setminus \{\vec{y}\} \subseteq dom(\Gamma)$$

$$= fn(x(\vec{y}).Q) \subseteq dom(\Gamma)$$

- Case P is !x(ÿ).Q. By rule TV-REP, we have that Γ ⊢ x(ÿ).Q. Then, by the induction hypothesis, we have that fn(x(ÿ).Q) ⊆ dom(Γ). Since fn(!x(ÿ).Q) = fn(x(ÿ).Q), then fn(!x(ÿ).Q) ⊆ dom(Γ) holds.

- Case P is Q<sub>1</sub> | Q<sub>2</sub>. By rule Tv-PAR, we have that Γ ⊢ Q<sub>1</sub> and Γ ⊢ Q<sub>2</sub>. Hence, by the induction hypothesis, we have that fn(Q<sub>1</sub>) ⊆ dom(Γ) and fn(Q<sub>2</sub>) ⊆ dom(Γ). By applying the set theory, we have

$$\operatorname{fn}(Q_1) \subseteq \operatorname{dom}(\Gamma) = \operatorname{fn}(Q_1) \cup \operatorname{fn}(Q_2) \subseteq \operatorname{dom}(\Gamma) \cup \operatorname{fn}(Q_2)$$

But  $\operatorname{fn}(Q_2) \subseteq \operatorname{dom}(\Gamma)$ , hence  $\operatorname{dom}(\Gamma) \cup \operatorname{fn}(Q_2) = \operatorname{dom}(\Gamma)$ . By definition of fn, we have  $\operatorname{fn}(Q_1 \mid Q_2) = \operatorname{fn}(Q_1) \cup \operatorname{fn}(Q_2)$ . Hence  $\operatorname{fn}(Q_1 \mid Q_2) \subseteq \operatorname{dom}(\Gamma)$ .

Case P is (ν x: T) Q. By hypothesis we have that Γ ⊢ (ν x: T) Q, then, by rule Tv-RES Γ, x : T ⊢ Q. Hence, by the induction hypothesis, fn(Q) ⊆ dom(Γ, x : T). We apply the definition of function dom and the set theory:

$$\begin{aligned} &\operatorname{fn}(Q) \subseteq \operatorname{dom}(\Gamma, x : T) \\ &= \operatorname{fn}(Q) \subseteq \operatorname{dom}(\Gamma) \cup \operatorname{dom}(\emptyset, x : T) \\ &= \operatorname{fn}(Q) \subseteq \operatorname{dom}(\Gamma) \cup \{x\} \\ &= \operatorname{fn}(Q) \setminus \{x\} \subseteq \operatorname{dom}(\Gamma) \end{aligned}$$

By definition of fn, we have that  $fn((\nu x: T) Q) = fn(Q) \setminus \{x\}$ . Thus,

$\operatorname{fn}((\nu x \colon T) Q) \subseteq \operatorname{dom}(\Gamma)$

**Corollary 2.2.8.** *If*  $\emptyset \vdash P$ *, then*  $fn(P) = \emptyset$ *.*

## **Chapter 3**

# A Multithreaded Intermediate Language

Vasconcelos and Martins introduced a multithreaded typed assembly language (MIL), its operational semantics, and a type system that ensures that well-typed programs are free from race conditions [47]. The type system proposed for MIL closely follows the tradition of typed assembly languages [29–31], extended with support for threads and locks, following Flanagan and Abadi [14]. With respect to this last work, however, MIL is positioned at a much lower abstraction level, and faces different challenges inherent to non-lexically scoped languages. Lock primitives have been discussed in the context of concurrent object calculi [13], JVM [15, 16, 22, 23], C [18], C-- [40], but not in the context of typed assembly (or intermediate) languages. In a typed setting, where programs are guaranteed not to suffer from race conditions, MIL

- Syntactically decouples the lock and unlock operations from what one usually finds unified in a single syntactic construct in high-level languages: Birrel's *lock-do-end* construct [4], used under different names (*sync*, *synchronized-in*, *lock-in*) in a number of other works, including the Java programming language [6, 7, 13–16, 18];

- Allows for lock acquisition/release in schemes other than the nested discipline imposed by the *lock-do-end* construct;

- Allows forking threads that hold locks.

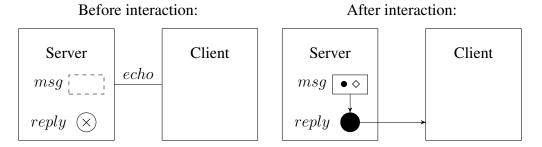

MIL is an assembly language targeted at an abstract multi-processor equipped with a shared main memory. Each processor consists of a series of registers and of a local memory for instructions and for local data. The main memory is divided into a heap and a run pool. The heap stores tuples and code blocks. A code block declares the registers types it expects, the required held locks, and an instruction sequence. The run pool contains suspended threads waiting for a free processor. Figure 3.1 summarises the MIL architecture.

Figure 3.1: The MIL architecture.

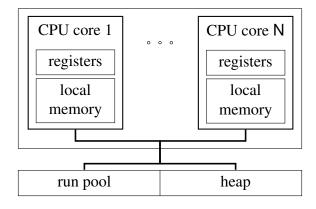

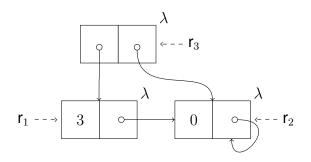

Figure 3.2: The lock discipline.

**Lock discipline.** We provide two distinct access privileges to tuples shared by multiple processors: read-only and read-write, the latter mediated by locks. A standard *test-and-set-lock* instruction is used to obtain a lock, thus allowing a thread to enter a *critical region*. Processors read and write from the shared heap via conventional load and store instructions. The policy for the usage of locks (enforced by the type system) is depicted in Figure 3.2 (cf. Theorem 3.5.3), where  $\lambda$  denotes a *singleton lock type* and  $\Lambda$  the set of locks held by the processor (the processor's *permission*). Specifically, the lock discipline enforces that:

- (1) before lock creation,  $\lambda$  is not a known lock;

- (2) before test-and-set-lock, the thread does not hold the lock;

- (3) before accessing the heap, the thread holds the lock;

- (4) unlocking only in possession of the lock;

- (5) thread termination only without held locks.

### 3.1 Syntax

The syntax of our language is generated by the grammar in Figures 3.3, 3.4, and 3.9. We rely on a set of *heap labels* ranged over by l, a set of *type variables* ranged over by  $\alpha$  and  $\beta$ , and a disjoint set of *singleton lock types* ranged over by  $\lambda$  and  $\rho$ .

Most of the machine instructions, presented in Figure 3.3, are standard in assembly languages. Instructions are organised in sequences, ending in jump or in done. Instruction jump v transfers the control flow to the code block pointed by value v. Instruction done frees the processor to execute another thread waiting in the thread pool. Our threads are cooperative, meaning that each thread must explicitly release the processor (using the done instruction).

Memory tuples are created locally, directly at processor's registers using the **new** instruction. To share memory, tuples are transferred to the heap using the **share** instruction, according to a chosen access policy: read-only or read-write (in which case it must be guarded by a lock). A system implementing MIL must use some scheme of local memory to store local tuples.

The *abstract machine*, generated by the grammar in Figure 3.4, is parametric on the number N of available processors and on the number R of registers per processor. An abstract machine can be in two possible states: halted or running. A running machine comprises a heap, a thread pool, and an array of processors of fixed length N. Heaps are maps from labels into *heap values* that may be tuples or code blocks. *Shared tuples* are

| registers       | $r ::= \mathbf{r}_1 \mid \ldots \mid \mathbf{r}_{R}$                                                                               |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|

| integer values  | $n ::= \ldots \mid -1 \mid 0 \mid 1 \mid \ldots$                                                                                   |

| values          | $v  ::=  r  \mid  n  \mid  l  \mid  \operatorname{pack} \tau, v \operatorname{as} \tau  \mid  v[\tau]  \mid  \langle \bar{\iota} $ |

| authority       | $a ::=$ read-only $\mid$ guarded by $\lambda$                                                                                      |

| instructions    | $\iota$ ::=                                                                                                                        |

| control flow    | $r:=v \mid r:=r+v \mid 	ext{ if } r=v 	ext{ jump } v \mid$                                                                         |

| memory          | $r:=\operatorname{\mathbf{new}} n \ \mid \ r:=v[n] \ \mid \ r[n]:=v \ \mid$                                                        |

|                 | share $r a$                                                                                                                        |

| unpack          | $\omega, r := unpack \; v \; \mid$                                                                                                 |

| lock            | $\lambda,r:=newLock \mid$                                                                                                          |

|                 | $r := testSetLock \ v \ \mid \ unlock \ v \ \mid$                                                                                  |

| fork            | fork v                                                                                                                             |

| inst. sequences | $I ::= \iota; I \mid jump v \mid done$                                                                                             |

The syntax of  $\tau$ ,  $\lambda$ , and  $\omega$  is defined in Figure 3.9.

Figure 3.3: Instructions.

| permissions      | $\Lambda ::= \lambda_1, \dots, \lambda_n$                                                           |

|------------------|-----------------------------------------------------------------------------------------------------|

| access mode      | $\pi$ ::= ro   $\lambda$                                                                            |

| register files   | $R ::= \{\mathbf{r}_1 \colon v_1, \dots, \mathbf{r}_{R} \colon v_{R}\}$                             |

| processor        | $p ::= \langle R; \Lambda; I \rangle$                                                               |

| processors array | $P ::= \{1: p_1, \ldots, N: p_N\}$                                                                  |

| thread pool      | $T ::= \{ \langle l_1[\vec{\tau}_1], R_1 \rangle, \dots, \langle l_n[\vec{\tau}_n], R_n \rangle \}$ |

| heap values      | $h ::= \langle v_1 \dots v_n \rangle^{\pi} \mid \tau\{I\}$                                          |

| heaps            | $H ::= \{l_1 \colon h_1, \ldots, l_n \colon h_n\}$                                                  |

| states           | $S ::= \langle H; T; P \rangle \mid halt$                                                           |

Figure 3.4: Abstract machine.

$$\frac{\forall i.P(i) = \langle .;.; \text{done} \rangle}{\langle .;\emptyset;P \rangle \to \text{halt}}$$

(R-HALT)

$$\frac{P(i) = \langle \_;\_; \mathsf{done} \rangle \qquad H(l) = \forall [\vec{\omega}].(\_\mathsf{requires } \Lambda)\{I\}}{\langle H; T \uplus \{\langle l[\vec{\tau}], R \rangle\}; P \rangle \rightarrow \langle H; T; P\{i: \langle R; \Lambda; I\{\vec{\tau}/\vec{\omega}\}\rangle\}\rangle}$$

(R-schedule)

$$\frac{P(i) = \langle R; \Lambda \uplus \Lambda'; (\text{fork } v; I) \rangle \quad \hat{R}(v) = l[\vec{\tau}] \quad H(l) = \forall [\_].(\_\text{requires } \Lambda) \{\_\}}{\langle H; T; P \rangle \rightarrow \langle H; T \cup \{ \langle l[\vec{\tau}], R \rangle\}; P\{i: \langle R; \Lambda'; I \rangle\} \rangle}$$

(R-FORK)

Figure 3.5: Operational semantics (thread pool).

vectors of mutable values protected by some lock  $\lambda$ , or else of constant values (identified by tag rO). Code blocks comprise a signature and a body. The signature of a code block describes the type of the registers and the locks that must be held by the processor when jumping to the code block. The body is a sequence of instructions to be executed by a processor.

A thread pool is a multiset of pairs, each of which contains the address (*i.e.*, a label) of a code block and a register file. Each processor is composed of a register file, a set of locks (the locks held by the thread running at the processor), and a sequence of instructions (the remaining ones for execution). The processor array of the abstract machine contains N processors.

#### **3.2 Operational Semantics**

The operational semantics is presented in Figures 3.5 to 3.8. The run pool is managed by the rules in Figure 3.5. Rule R-HALT stops the machine when it finds an empty thread pool and all processors idle, changing the machine state to halt. Otherwise, if there is an idle processor and at least one thread waiting in the pool, then rule R-SCHEDULE assigns a thread to the idle processor. Rule R-FORK places a new thread in the pool; the permissions of the thread are split in two: required by the forked code, and the remaining ones. The thread keeps the latter set.

Operational semantics concerning locks are depicted in Figure 3.6. The instruction newLock creates an open lock  $\rho$  whose scope is the rest of the code block, allocates the respective value  $\langle 0 \rangle^{\rho}$  in the heap, and points register r to that (lock) tuple. A lock is an uni-dimensional tuple holding a *lock value* (an integer), because the machine provides for tuple allocation only; lock  $\rho$  is used for type safety purposes, just like all other singleton types. Value  $\langle 0 \rangle^{\rho}$  represents an open lock, whereas value  $\langle 1 \rangle^{\rho}$  represents a closed lock.

The test-and-set instruction, present in many machines designed for multithreading,

$$\frac{P(i) = \langle R; \Lambda; (\lambda, r := \mathsf{newLock}; I) \rangle \quad l \notin \operatorname{dom}(H) \quad \rho \operatorname{fresh}}{\langle H; T; P \rangle \to \langle H\{l: \langle 0 \rangle^{\rho}\}; T; P\{i: \langle R\{r: l\}; \Lambda; I[\rho/\lambda] \rangle\} \rangle}$$

(R-NEWLOCK)

$$\frac{P(i) = \langle R; \Lambda; (r := \mathsf{testSetLock} \, v; I) \rangle \quad \hat{R}(v) = l \quad H(l) = \langle 0 \rangle^{\lambda}}{\langle H; T; P \rangle \to \langle H\{l: \langle 1 \rangle^{\lambda}\}; T; P\{i: \langle R\{r: 0\}; \Lambda \uplus \{\lambda\}; I \rangle\} \rangle}$$

(R-TSL 0)

$$\frac{P(i) = \langle R; \Lambda; (r := \mathsf{testSetLock} v; I) \rangle \quad H(\hat{R}(v)) = \langle 1 \rangle^{\lambda}}{\langle H; T; P \rangle \to \langle H; T; P\{i: \langle R\{r:1\}; \Lambda; I \rangle\} \rangle}$$

(R-TSL 1)

$$\frac{P(i) = \langle R; \Lambda \uplus \{\lambda\}; (\text{unlock } v; I) \rangle \quad \hat{R}(v) = l \quad H(l) = \langle -\rangle^{\lambda}}{\langle H; T; P \rangle \to \langle H\{l; \langle 0 \rangle^{\lambda}\}; T; P\{i; \langle R; \Lambda; I \rangle\} \rangle}$$

(R-UNLOCK)

Figure 3.6: Operational semantics (locks).

is an atomic operation that loads the contents of a bit into a register and then turns that bit on, *i.e.*, sets the bit to 1. Some architectures, like IBM's z/Architecture, serialise the execution of all the processors upon handling a test-and-set (*e.g.*, by blocking the bus) to ensure the atomicity of the operation.

In MIL, we have the *test-and-set-lock* instruction (testSetLock). The sole difference between test-and-set and test-and-set-lock is the semantics given to the target of the instruction, a bit in the case of the former, a tuple holding an integer in the latter case. A real-world implementation of MIL can represent the testSetLock by the test-and-set instruction, and the uni-dimensional tuple by a bit. The testSetLock, also atomic, stores the enclosed value in the left-hand register and turns the lock pointed by the right-hand side register into  $\langle 1 \rangle^{\lambda}$ . Applying the instruction testSetLock to a lock in the unlocked state  $\langle 0 \rangle^{\lambda}$  changes the lock into the locked state  $\langle 1 \rangle^{\lambda}$ , loads value 0 to register r, and adds lock  $\lambda$  to the permissions of the processor (Rule R-TSL0). Applying the instruction testSetLock to a closed lock, state  $\langle 1 \rangle^{\lambda}$ , just places a 1 in register r(Rule R-TSL1). Locks are waved using instruction unlock, as long as the thread holds the lock (Rule R-UNLOCK).

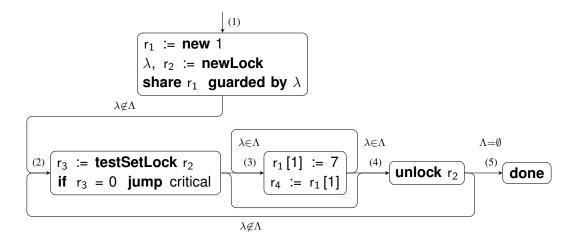

An example of creating and then acquiring a lock follows, storing (a reference of) lock  $\lambda$  in register  $r_1$ .

#### $\lambda$ , r<sub>1</sub> := newLock

Remember the instruction newLock allocates the lock directly in the heap in the unlocked state; register  $r_1$  holds a reference to the enclosed value. Next we try to acquire the open lock  $\langle 0 \rangle^{\lambda}$  present in register  $r_1$ : the value 0 contained in lock is loaded to register  $r_2$ .

#### $r_2 := testSetLock r_1$

Then we test the value in register  $r_2$ , jumping to code block criticalRegion if the lock was acquired; otherwise it jumps to code block tryAgain.

$$\frac{P(i) = \langle R; \Lambda; (r := \mathsf{new} \; n; I) \rangle \quad |\vec{0}| = n}{\langle H; T; P \rangle \to \langle H; T; P\{i: \langle R\{r: \langle \vec{0} \rangle\}; \Lambda; I \rangle\} \rangle}$$

(R-NEW)

$$\begin{array}{l} P(i) = \langle R; \Lambda; (\text{share } r \; a; I) \rangle & R(r) = \langle \vec{v} \rangle \\ \hline \frac{l \notin \operatorname{dom}(H) & \pi \text{ is } \lambda \text{ when } a = \text{guarded by } \lambda \text{ else ro}}{\langle H; T; P \rangle \rightarrow \langle H\{l: \langle \vec{v} \rangle^{\pi}\}; T; P\{i: \langle R\{r: l\}; \Lambda; I \rangle\} \rangle} \end{array}$$

(R-SHARE)

$$\frac{P(i) = \langle R; \Lambda; (r := v[n]; I) \rangle \quad H(\hat{R}(v)) = \langle v_1 .. v_n .. v_{n+m} \rangle^{\pi} \quad \pi \in \{ \mathsf{ro} \} \cup \Lambda}{\langle H; T; P \rangle \rightarrow \langle H; T; P\{i: \langle R\{r: v_n\}; \Lambda; I \rangle \} \rangle}$$

(R-LOADH)

$$\frac{P(i) = \langle R; \Lambda; (r := r'[n]; I) \rangle \quad R(r') = \langle v_1 .. v_n .. v_{n+m} \rangle}{\langle H; T; P \rangle \to \langle H; T; P\{i: \langle R\{r: v_n\}; \Lambda; I \rangle\} \rangle}$$

(R-LOADL)

$$\frac{P(i) = \langle R; \Lambda; (r[n] := v; I) \rangle \quad \hat{R}(v) \neq \langle_{-} \rangle \quad R(r) = l \quad H(l) = \langle v_1 .. v_n .. v_{n+m} \rangle^{\lambda} \quad \lambda \in \Lambda}{\langle H; T; P \rangle \rightarrow \langle H\{l: \langle v_1 .. \hat{R}(v) .. v_{n+m} \rangle^{\lambda}\}; T; P\{i: \langle R; \Lambda; I \rangle\} \rangle} \\ (\mathbf{R}\text{-STOREH}) \\