# DYNAMIC THERMAL MANAGEMENT FOR MICROPROCESSORS THROUGH TASK SCHEDULING

by

## Xiuyi Zhou

B.S. in Computer Science, Nanjing University, China, 2002M.S. in Computer Science, Nanjing University, China, 2005

Submitted to the Graduate Faculty of Swanson School of Engineering in partial fulfillment of the requirements for the degree of PhD in Electrical Engineering

University of Pittsburgh

2011

## UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Xiuyi Zhou

It was presented on September 28, 2010

and approved by

Jun Yang, Ph.D., Associate Professor, Electrical and Computer Engineering Department

Alex Jones, Ph.D., Associate Professor, Electrical and Computer Engineering Department

Steven Levitan, Ph.D., Professor, Electrical and Computer Engineering Department

Guangyong Li, Ph.D., Assistant Professor, Electrical and Computer Engineering

Department

Rami Melhem, Ph.D., Professor, Computer Science Department

Dissertation Director: Jun Yang, Ph.D., Associate Professor, Electrical and Computer Engineering Department Copyright  $\bigodot$  by Xiuyi Zhou2011

## DYNAMIC THERMAL MANAGEMENT FOR MICROPROCESSORS THROUGH TASK SCHEDULING

Xiuyi Zhou, Ph.D.

University of Pittsburgh, 2011

With continuous IC(Integrated Circuit) technology size scaling, more and more transistors are integrated in a tiny area of the processor. Microprocessors experience unprecedented high power and high temperatures on chip, which can easily violate the thermal constraint. High temperature on the chip, if not controlled, can damage or even burn the chip. There are also emerging technologies which can exacerbate the thermal condition on modern processors. For example, 3D stacking is an IC technology that stacks several die layers together, in order to shorten the communication path between the dies to improve the chip performance. This technology unfortunately increases the power density per unit volumn, and the heat from each layer needs to dissipate vertically through the same heat sink. Another example is chip multi-processor. A chip multi-processor(CMP) integrates two or more independent actual processors (called "cores"), onto a single integrated circuit die. As IC technology nodes continually scale down to 45nm and below, there is significant within-die process variation(PV) in the current and near-future CMPs. Process variation makes the cores in the chip differ in their maximum operable frequency, and the amount of leakage power they consume. This can result in the immense spatial variation of the temperatures of the cores on the same chip, which means the temperatures of some cores can be much higher than other cores.

One of the most commonly used methods to constrain a CPU from overheating is hardware dynamic thermal management(HW DTM), due to the high cost and inefficiency of current mechanical cooling techniques. Dynamic voltage/frequency scaling(DVFS) is such a broad-spectrum dynamic thermal management technique that can be applied to all types of processors, so we adopt DVFS as the HW DTM method in this thesis to simplify problem discussion. DVFS lowers the CPU power consumption by reducing CPU frequency or voltage when temperature overshoots, which constrains the temperature at the price of performance loss, in terms of reduced CPU throughput, or longer execution time of the programs. This thesis mainly addresses this problem, with the goal of eliminating unnecessary hardware-level DVFS and improving chip performance.

The methodology of the experiments in this thesis are based on the accurate estimation of power and temperature on the processor. The CPU power usage of different benchmarks are estimated by reading the performance counters on a real P4 chip, and measuring the activities of different CPU functional units. The jobs are then categorized into powerintensive(hot) ones and power non-intensive(cool) ones. Many combinations of the jobs with mixed power(thermal) characteristics are used to evaluate the effectiveness of the algorithms we propose. When the experiments are conducted on a single-core processor, a compact dynamic thermal model embedded in Linux kernel is used to calculate the CPU temperature. When the experiments are conducted on the CMP with 3D stacked dies, or the CMP affected by significant process variation, a thermal simulation tool well recognized in academia is used.

The contribution of the thesis is that it proposes new software-level task scheduling algorithms to avoid unnecessary hardware-level DVFS. New task scheduling algorithms are proposed not only for the single-core processor, but also for the CMP with 3D stacked dies, and the CMP under process variation. Compared with the state-of-the-art algorithms proposed by other researchers, the new algorithms we propose all show significant performance improvement.

To improve the performance of the single-core processors, which is harmed by the thermal overshoots and the HW DTMs, we propose a heuristic algorithm named ThreshHot, which judiciously schedules hot jobs before cool jobs, to make the future temperature lower. Furthermore, it always makes the temperature stay as close to the threshold as possible while not overshooting.

In the CMPs with 3D stacked dies, three heuristics are proposed and combined as one algorithm. First, the vertically stacked cores are treated as a core stack. The power of jobs is balanced among the core stacks instead of the individual cores. Second, the hot jobs are moved close to the heat sink to expedite heat dissipation. Third, when the thermal emergencies happen, the most power-intensive job in a core stack is penalized in order to lower the temperature quickly.

When CMPs are under significant process variation, each core on the CMP has distinct maximum frequency and leakage power. Maximizing the overall CPU throughput on all the cores is in conflict with satisfying on-chip thermal constraints imposed on each core. A maximum bipartite matching algorithm is used to solve this dilemma, to exploit the maximum performance of the chip.

### TABLE OF CONTENTS

| ACKNOWLEDGEMENTS xvi |     |                                                               |    |

|----------------------|-----|---------------------------------------------------------------|----|

| 1.0                  | IN  | TRODUCTION                                                    | 1  |

|                      | 1.1 | THERMAL ISSUES IN CURRENT AND FUTURE PROCESSORS               | 1  |

|                      |     | 1.1.1 Thermal problem in a single-core processor              | 1  |

|                      |     | 1.1.2 Thermal issues in 3D stacked CMP                        | 2  |

|                      |     | 1.1.3 Thermal issues in the CMP impacted by process variation | 2  |

|                      |     | 1.1.4 Performance losses caused by HW DTM                     | 3  |

|                      |     | 1.1.5 DVFS details                                            | 4  |

|                      | 1.2 | MOTIVATION AND PROBLEM STATEMENT                              | 5  |

|                      | 1.3 | THESIS OVERVIEW                                               | 5  |

|                      |     | 1.3.1 ThreshHot - approaching threshold as close as possible  | 5  |

|                      |     | 1.3.2 Power balancing tailored to 3D thermal conditions       | 6  |

|                      |     | 1.3.3 MBM - maximum bipartite matching on CMP-PV              | 7  |

|                      | 1.4 | CONTRIBUTIONS                                                 | 8  |

|                      | 1.5 | ROADMAP                                                       | 8  |

| 2.0                  | OB  | TAINING POWER AND TEMPERATURE                                 | 9  |

|                      | 2.1 | Temperature Obtaining and Computation                         | 9  |

|                      |     | 2.1.1 Thermal sensor readings are insufficient.               | 9  |

|                      |     | 2.1.2 Temperature model                                       | 10 |

|                      |     | 2.1.3 Temperature calculation speedup.                        | 11 |

|            | 2.2 | Computing the powers                                                                                      | 12 |

|------------|-----|-----------------------------------------------------------------------------------------------------------|----|

|            |     | 2.2.1 Power estimation                                                                                    | 12 |

|            |     | 2.2.2 Power prediction                                                                                    | 13 |

|            | 2.3 | Workflow summary                                                                                          | 13 |

|            | 2.4 | The accuracy of temperature calculation                                                                   | 15 |

| 3.0        | RE  | ELATED WORK                                                                                               | 16 |

|            | 3.1 | Prior work in a single core processor                                                                     | 16 |

|            | 3.2 | Prior work in CMP built with stacked dies                                                                 | 18 |

|            | 3.3 | Prior work in CMP with process variation                                                                  | 19 |

| <b>4.0</b> | PR  | <b>ROPOSED TASK SCHEDULING SOLUTIONS</b>                                                                  | 21 |

|            | 4.1 | THRESHHOT         2                                                                                       | 21 |

|            |     | 4.1.1 Thermal scheduling algorithms                                                                       | 21 |

|            |     | 4.1.1.1 The principle                                                                                     | 22 |

|            |     | 4.1.1.2 In practice                                                                                       | 25 |

|            |     | 4.1.2 Linux kernel implementation                                                                         | 26 |

|            |     | 4.1.2.1 The skeleton of the Linux scheduler $\ldots \ldots \ldots \ldots \ldots \ldots 2$                 | 26 |

|            |     | 4.1.2.2 Our modification $\ldots \ldots 2$ | 26 |

|            |     | 4.1.3 Anatomy and comparison of different scheduling algorithms 2                                         | 28 |

|            |     | $4.1.3.1 \text{ Random scheduler } \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 3$             | 31 |

|            |     | $4.1.3.2 Priority scheduler \dots 3$                                                                      | 31 |

|            |     | 4.1.3.3 Mintemp <sup>+</sup> scheduler $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 3$        | 32 |

|            |     | 4.1.3.4 Threshot scheduler                                                                                | 32 |

|            |     | 4.1.4 Experimental evaluation                                                                             | 33 |

|            |     | 4.1.4.1 Benchmark classification                                                                          | 34 |

|            |     | 4.1.4.2 Thermal scheduling results                                                                        | 35 |

|            |     | 4.1.4.3 DTM reductions                                                                                    | 37 |

|            |     | 4.1.4.4 Performance improvements                                                                          | 11 |

|            |     | 4.1.4.5 Overhead                                                                                          | 13 |

|     |       | 4.1.4.6 Impact of varied intervals on ThreshHot                                                                                                        | 3 |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|     |       | 4.1.4.7 Impact of power misprediction    44                                                                                                            | 4 |

|     |       | 4.1.4.8 Scalability                                                                                                                                    | 6 |

| 4.2 | BALA  | NCING BY STACK IN 3D CMP 49                                                                                                                            | 9 |

|     | 4.2.1 | Motivation and rationale                                                                                                                               | 0 |

|     |       | 4.2.1.1 A representative floorplan                                                                                                                     | 0 |

|     |       | 4.2.1.2 Vertically adjacent layers have strong thermal correlations 5                                                                                  | 1 |

|     |       | 4.2.1.3 The die layers further from the heat sink are usually hotter 53                                                                                | 3 |

|     | 4.2.2 | Scheduling algorithms                                                                                                                                  | 4 |

|     |       | 4.2.2.1 The baseline                                                                                                                                   | 5 |

|     |       | $4.2.2.2 \text{ Random (Baseline+)} \dots \dots$ | 6 |

|     |       | 4.2.2.3 Round-Robin                                                                                                                                    | 6 |

|     |       | 4.2.2.4 Temperature balancing by core                                                                                                                  | 7 |

|     |       | 1.2.2.5 Temperature balancing by stack                                                                                                                 | 7 |

|     | 4.2.3 | Experimental methodology                                                                                                                               | 3 |

|     |       | 4.2.3.1 Floorplan setup                                                                                                                                | 3 |

|     |       | $4.2.3.2 Simulation tool and power trace collection \dots \dots \dots \dots \dots 64$                                                                  | 4 |

|     |       | 4.2.3.3 Benchmark classification                                                                                                                       | 4 |

|     |       | 4.2.3.4 DVFS implementation and context switching overhead 65                                                                                          | 5 |

|     | 4.2.4 | Results and analysis                                                                                                                                   | 7 |

|     |       | 4.2.4.1 Homogeneous floorplan                                                                                                                          | 7 |

|     |       | 4.2.4.2 Heterogeneous floorplan                                                                                                                        | 2 |

| 4.3 | MAX   | MUM BIPARTITE MATCHING IN CMP WITH PROCESS VARIA-                                                                                                      |   |

|     | TION  |                                                                                                                                                        | 4 |

|     | 4.3.1 | Motivation                                                                                                                                             | 5 |

|     | 4.3.2 | MBM algorithm   78                                                                                                                                     | 8 |

|     | 4.3.3 | Preparation of input to MBM 80                                                                                                                         | 0 |

|     |       | 4.3.3.1 Predicting future temperatures                                                                                                                 | 1 |

| 4.3.3.2 Frequency prediction                                                           | 84  |

|----------------------------------------------------------------------------------------|-----|

| 4.3.3.3 An evaluation of temperature and frequency estimation error .                  | 87  |

| 4.3.3.4 IPS prediction                                                                 | 88  |

| 4.3.3.5 Algorithms used in comparisons                                                 | 90  |

| 4.3.4 Experimental setup                                                               | 90  |

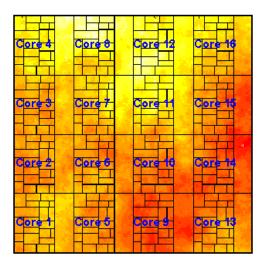

| 4.3.4.1 Floorplan                                                                      | 90  |

| 4.3.4.2 PV modeling                                                                    | 91  |

| 4.3.4.3 Simulation tools and benchmarks                                                | 94  |

| 4.3.4.4 Overhead                                                                       | 95  |

| 4.3.5 Results                                                                          | 97  |

| 4.3.5.1 DVFS and throughput                                                            | 97  |

| 4.3.5.2 Detailed throughput for different workloads                                    | 98  |

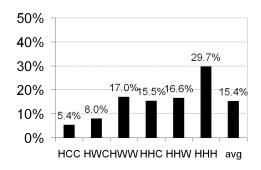

| 4.3.5.3 Thermal environment                                                            | 101 |

| 4.3.5.4 Varied interval length                                                         | 101 |

| 4.3.5.5 Overhead                                                                       | 102 |

| 4.3.5.6 Energy consumption per instruction                                             | 104 |

| 5.0 CONCLUDING REMARKS                                                                 | 105 |

| 5.1 SUMMARY OF RESULTS                                                                 | 106 |

| 5.2 FUTURE WORK                                                                        | 108 |

| 5.2.1 Implementation of our algorithms onto real chips                                 | 108 |

| 5.2.2 Self adaptive scheduling algorithms                                              | 108 |

| 5.2.3 Online computation of thermal coefficients                                       | 109 |

| 5.2.4 More accurate prediction of power consumption of jobs $\ldots$ $\ldots$ $\ldots$ | 109 |

| 5.2.5 New optimization objectives                                                      | 110 |

| BIBLIOGRAPHY                                                                           | 111 |

### LIST OF TABLES

| 1 | Classifications of program thermal intensity.                             | 35 |

|---|---------------------------------------------------------------------------|----|

| 2 | Workload combinations consisting of relatively hot (H), warm (W) and cool |    |

|   | (C) jobs                                                                  | 36 |

| 3 | The combination of benchmarks in simulation                               | 66 |

| 4 | IPC characteristics of benchmarks in SPEC06                               | 95 |

| 5 | The combination of benchmarks when the number of jobs is 8                | 96 |

## LIST OF FIGURES

| 1  | Average error rates for last power value predictor.                                                                                                                                                                                                                                                                                                                                                                                | 14 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Thermal-aware task scheduling methodologies.                                                                                                                                                                                                                                                                                                                                                                                       | 14 |

| 3  | The impact of scheduling a hot and cool program in different orders                                                                                                                                                                                                                                                                                                                                                                | 24 |

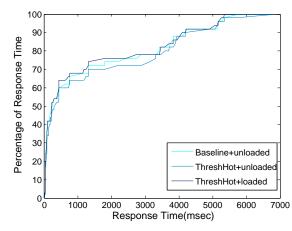

| 4  | Variation in latencies for VNCplay in our thermal-aware scheduler                                                                                                                                                                                                                                                                                                                                                                  | 28 |

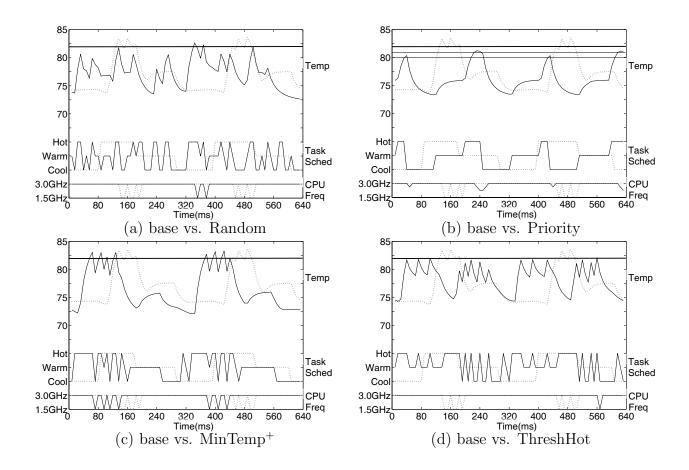

| 5  | A close-up of the execution traces for four different algorithms. Each graph<br>compares the default Linux scheduler (dashed line) with one algorithm (solid<br>line). In all graphs, the top portion shows the temperature variation with<br>time. The middle portion shows the job switching sequence and the bottom<br>portion shows whether a frequency scaling, a reduction from 3GHz to 1.5GHz<br>(downward arrow), occurred | 30 |

| 6  | Thermal profiles of the IntReg for all 22 SPEC2K (left) and media, net, and                                                                                                                                                                                                                                                                                                                                                        |    |

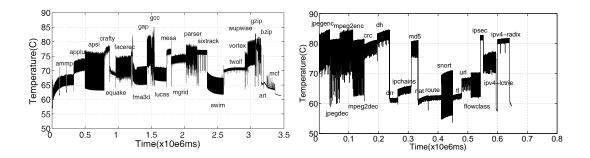

|    | packetbench (right).                                                                                                                                                                                                                                                                                                                                                                                                               | 35 |

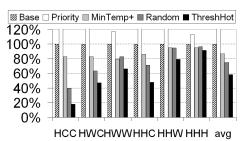

| 7  | Number of thermal emergency triggers, normalized to the baseline scheduler                                                                                                                                                                                                                                                                                                                                                         |    |

|    | (Linux default).                                                                                                                                                                                                                                                                                                                                                                                                                   | 37 |

| 8  | Percentage of execution time under DTM in the baseline scheduler                                                                                                                                                                                                                                                                                                                                                                   | 38 |

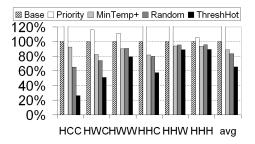

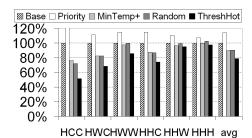

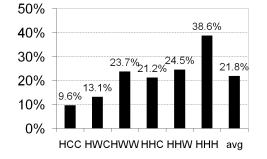

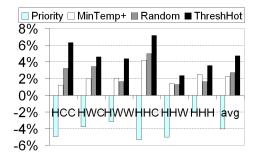

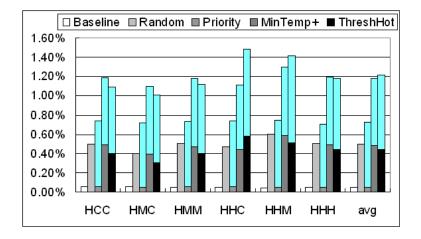

| 9  | The percentage of the execution time reduction from the baseline                                                                                                                                                                                                                                                                                                                                                                   | 39 |

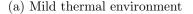

| 10 | Drastic performance changes to individual jobs by MinTempPlus scheduler (mild thermal environment).                                                                                                                                                                                                                                                                                                                                | 42 |

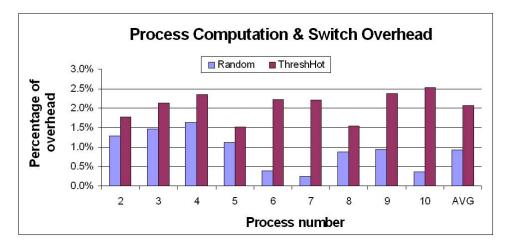

| 11 | Details of the time overhead(represented in percentage in y-axis) incurred by     |    |

|----|-----------------------------------------------------------------------------------|----|

|    | the temperature computation and task switching(upper area marks the over-         |    |

|    | head of temperature prediction), normalized to the execution time in Baseline     |    |

|    | in the medium thermal environment                                                 | 44 |

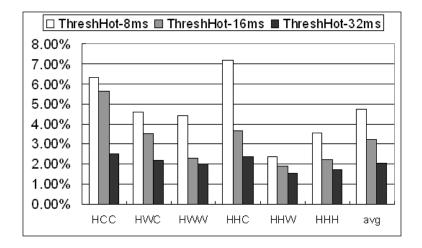

| 12 | The relative performance improvement by ThreshHot over Baseline, under            |    |

|    | different scheduling intervals                                                    | 45 |

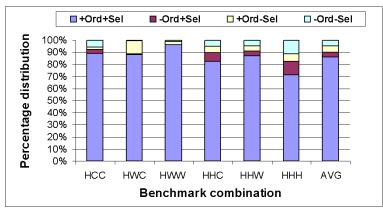

| 13 | The distribution of last value prediction results                                 | 46 |

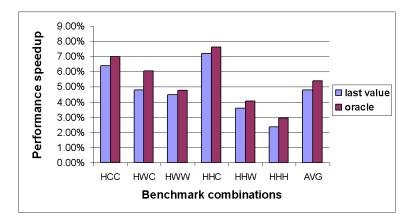

| 14 | The offline performance comparison of last_value power predictor and oracle       |    |

|    | power predictor                                                                   | 47 |

| 15 | The overhead from context switch and temperature computation(x-axis shows         |    |

|    | the number of processes)                                                          | 49 |

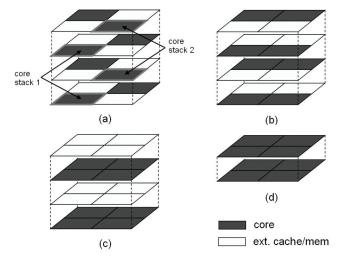

| 16 | 3D chip multiprocessor floorplan options                                          | 50 |

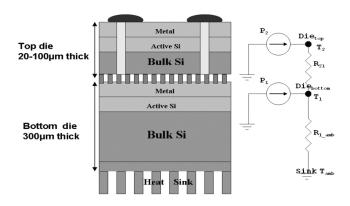

| 17 | A face-to-back 3D die stacking structure as an example, and the corresponding     |    |

|    | thermal model                                                                     | 51 |

| 18 | Thermal correlation between adjacent dies.                                        | 53 |

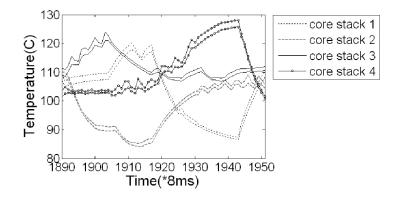

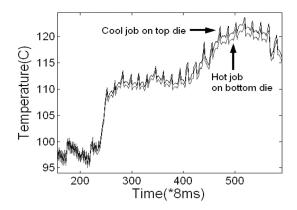

| 19 | Demonstration of the top die being hotter than the bottom die                     | 55 |

| 20 | The temperature balancing-by-stack algorithm.                                     | 60 |

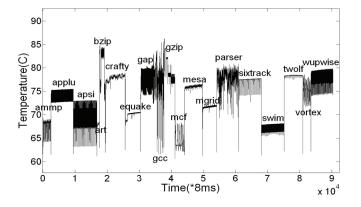

| 21 | Temperatures of the benchmark in SPEC2000                                         | 65 |

| 22 | A zoom-in of temperature variation over time under different scheduling algo-     |    |

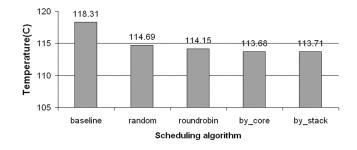

|    | rithms                                                                            | 69 |

| 23 | Peak temperatures of different scheduling algorithms.                             | 69 |

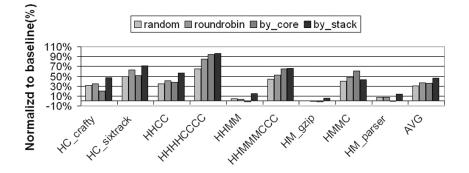

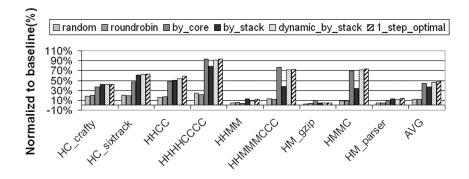

| 24 | Thermal emergency time reductions in homogeneous floorplans                       | 70 |

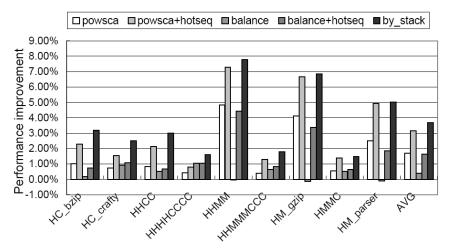

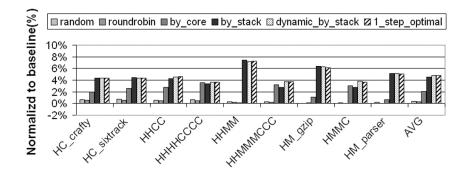

| 25 | Performance improvements for homogeneous floorplans                               | 71 |

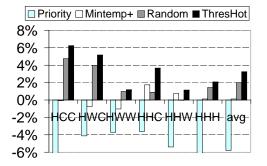

| 26 | The individual and combined effects of three heuristics. The results are relative |    |

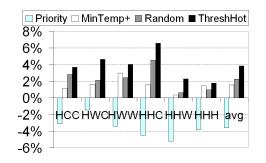

|    | to that of the Random scheduler                                                   | 72 |

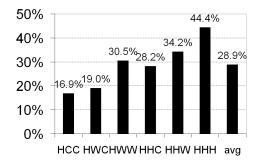

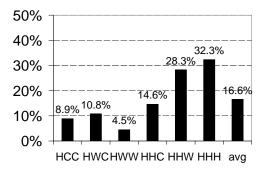

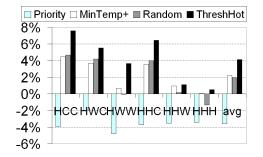

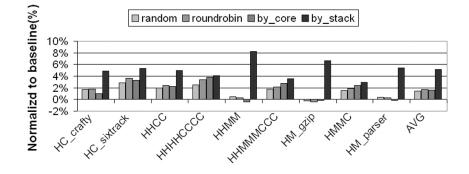

| 27 | Thermal emergency time reductions in heterogeneous floorplans                     | 74 |

| 28 | Performance improvements for heterogeneous floorplan.                             | 75 |

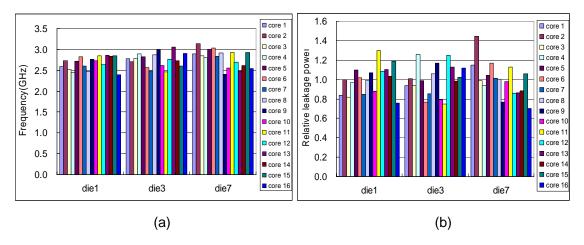

| 29 | (a)The variation of the frequencies of the cores on sample die 1, 3 and 7 among<br>the 20 sample dies. (b) The variation of the leakage power of the cores on<br>sample die 1, 3 and 7 at the temperature of 100C. | 76 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

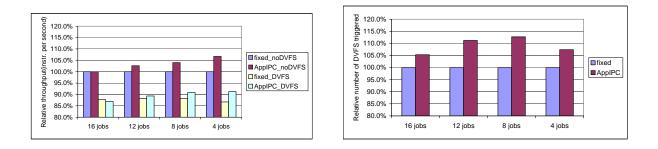

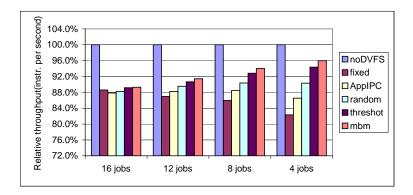

| 30 | The relative throughput attained(left) and the relative DVFS triggered(right) by running varied number of jobs when the interval is 8ms and the thermal environment is hot.                                        | 78 |

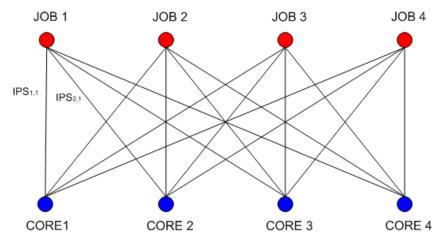

| 31 | $K_{4,4}$ complete bipartite graph, symbolizing the possibilities of mapping jobs                                                                                                                                  |    |

|    | onto cores                                                                                                                                                                                                         | 79 |

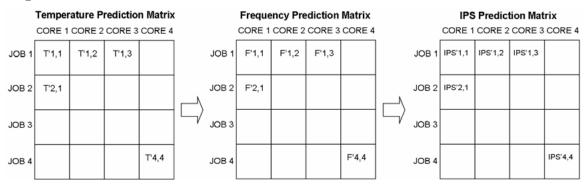

| 32 | The matrices generated for throughput prediction.                                                                                                                                                                  | 81 |

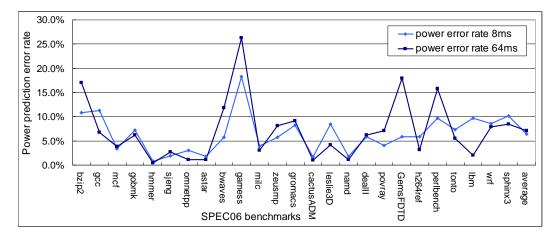

| 33 | The error rate of power prediction by using last-value prediction method                                                                                                                                           | 83 |

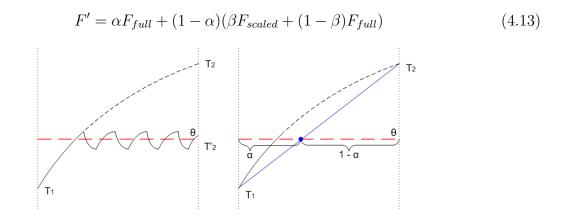

| 34 | The impact of DVFS on the temperature and the linear interpolation of the temperature                                                                                                                              | 85 |

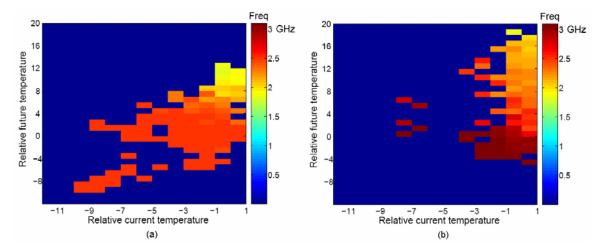

| 35 | The relationship among current temperature, predicted future temperature, and future frequency((a)die 3, core 7, $2.48$ GHz;(b)die 3, core 13, $3.06$ GHz.)                                                        | 86 |

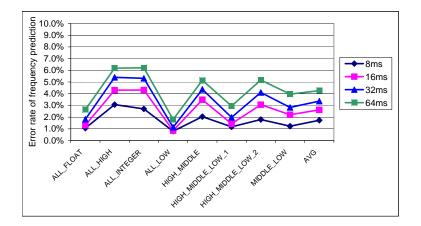

| 36 | The relative error rate of future frequency prediction under varied scheduling intervals when the number of jobs is 8 and the thermal environment is hot.                                                          | 88 |

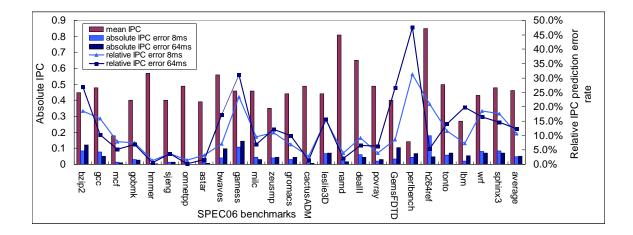

| 37 | The absolute and relative error of IPC prediction by using last-value prediction method                                                                                                                            | 89 |

| 38 | The comparison between the future throughput achieved by using oracle IPC knowledge and the future throughput achieved by using last-value IPC in MBM.                                                             | 89 |

| 39 | The simulated floorplan of CMP-PV.                                                                                                                                                                                 | 92 |

| 40 | A 16-core CMP with process variation. The colormap under the floorplan<br>shows the within-die variation of the threshold voltage.                                                                                 | 92 |

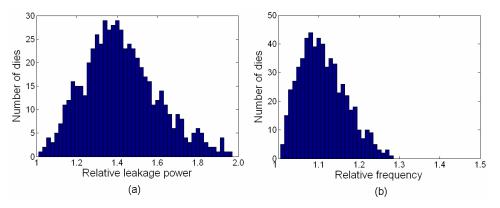

| 41 | Histograms of the ratio between (a) the average leakage power of the cores and<br>the power of the least leaky core (b) and between the average frequency of the                                                   | 0  |

|    | cores and the frequency of the slowest core in the die                                                                                                                                                             | 94 |

| 42 | The relative throughput achieved by running varied number of jobs when the     |     |

|----|--------------------------------------------------------------------------------|-----|

|    | interval is 8ms and the thermal environment is hot                             | 99  |

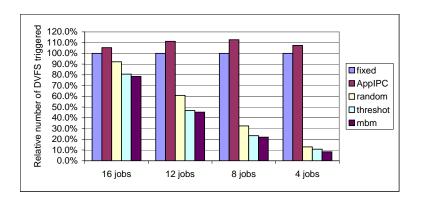

| 43 | The relative DVFS triggered by running varied number of jobs when the in-      |     |

|    | terval is 8ms and the thermal environment is hot                               | 99  |

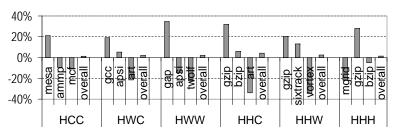

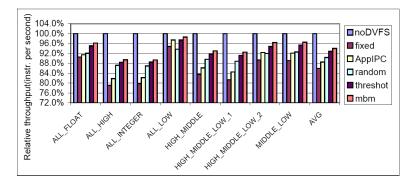

| 44 | The relative throughput achieved by different workloads when the number of     |     |

|    | jobs is 8, the interval is 8ms, and the thermal environment is hot             | 100 |

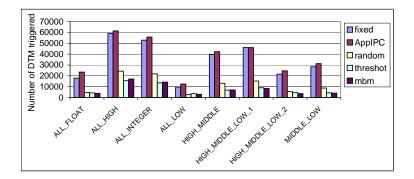

| 45 | The number of DVFS triggered by different workloads when the number of         |     |

|    | jobs is 8, the interval is 8ms, and the thermal environment is hot             | 100 |

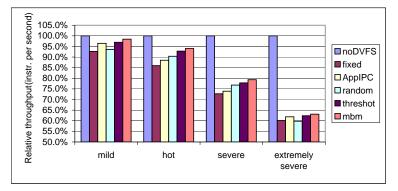

| 46 | The relative throughput under different thermal environments when the inter-   |     |

|    | val is 8ms and the number of jobs is 8                                         | 101 |

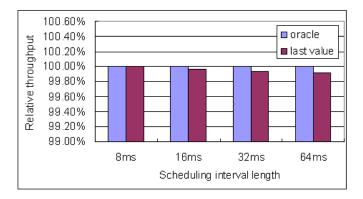

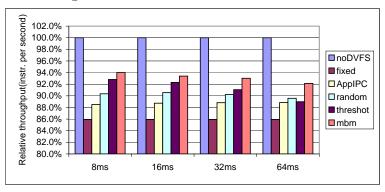

| 47 | The relative throughput achieved by varying scheduling interval length when    |     |

|    | the number of jobs is 8 and the thermal environment is hot                     | 102 |

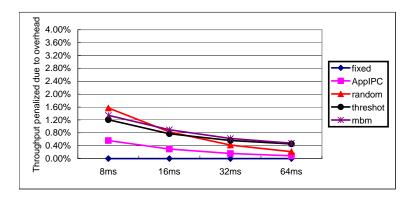

| 48 | The relative throughput penalized due to all sorts of overhead under different |     |

|    | scheduling intervals when the number of jobs is 8 and the thermal environment  |     |

|    | is hot                                                                         | 103 |

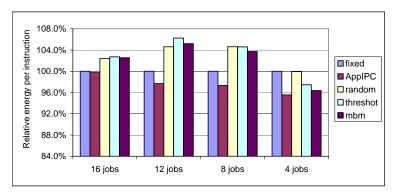

| 49 | The relative energy per instruction(EPI) by running varied number of jobs      |     |

|    | when the interval is 8ms and the thermal environment is hot                    | 104 |

#### ACKNOWLEDGEMENTS

I would like to show my gratitude to my academic advisor Jun Yang for her continuing support and professional guidance in so many years, and for giving me the opportunity to learn how to do research. I also thank Professor Youtao Zhang in the Department of Computer Science, for the engaging brainstorming sessions that he and Dr. Yang presided. I am professionally indebted to both of them.

I thank Lin Li for being a reliable and skillful colleague to work with. I also feel lucky and happy to work with Yi Xu, Bo Zhao, Ping Zhou, Lei Jiang, Yu Du, Weijia Li, and many others. You have made for a wonderful company throughout my years in Pittsburgh.

Finally, I am heartily thankful to all the professors whose classes I have attended and enjoyed(Steven Levitan, J. T. Cain, Rami Melhem), the dissertation committee members for having contributed to the validation of my work, Alex Jones, Guangyong Li, and the staff in the department and at the Graduate School for making it all possible.

#### 1.0 INTRODUCTION

#### 1.1 THERMAL ISSUES IN CURRENT AND FUTURE PROCESSORS

As technology for microprocessors enters the nanometer era, power density has become one of the major constraints to achievable processor performance. High temperatures jeopardize the reliability of the chip and significantly impact its performance. The immense spatial and temporal variation of chip temperature also creates great challenges to cooling and packaging technology which, for the sake of cost-effectiveness [87], are designed for typical, not worstcase, thermal condition. This entails dynamic thermal managements (DTM) to regulate chip temperature at runtime.

#### 1.1.1 Thermal problem in a single-core processor

With high computational power and high power density, some modern single-core processors, such as Intel Pentium 4 and AMD K6, require heat spreader, heat sink and even cooling fans for faster heat dissipation to the ambient air. Moreover, Pentium 4 processor has two on-chip thermal sensors to monitor the temperatures directly. If the temperature is over some predefined threshold, internal hardware mechanisms are triggered to slow the CPU or even completely power off the CPU [87]. These indicate that the thermal problem has existed for a long time in single-core processors.

#### 1.1.2 Thermal issues in 3D stacked CMP

For the promising 3D integration technology, the situation of thermal issues is even more serious. 3D integration technology is a technology that reduces wiring both within and across disparate dies, as wiring has become a major latency, area and power overhead in modern microprocessors. Studies have shown that wires can consume more than 30% of the power within a 2D CMP(chip multiprocessor) [7]. 3D technology provides vertical stacking of two or more dies with a dense, high-speed interface, reducing the wire length by a factor of the square root of the number of layers used [39]. This significant reduction leads to improved performance and lower power dissipation for the interconnection network. 3D integration technology becomes a promising candidate in constructing future CMP.

One key challenge in 3D die stacking is the heat generation from the internal active layers, because the power density per unit volume increases drastically in 3D. This exacerbates existing hotspots and can create new hotspots within the chip, especially when active logic circuits are vertically aligned. For example, the peak temperature can increase by  $17\sim20^{\circ}$ C in a two-layer 3D implementation for an Alpha-like processor, compared to a 2D design [36, 57]. Other studies on logic-logic stacking 3D floorplans [1,7,58] also show similar thermal constraint.

#### 1.1.3 Thermal issues in the CMP impacted by process variation

There is a long-existing problem of process variation(PV) in integrated circuit production. In definition, process variation is the divergence of certain transistor parameters from their nominal values. With the technology size scaling down to 45 nm and below, process variation poses greater challenges for design of future high-performance micro-processors [8], including CMP. Specifically, it makes the cores in a CMP differ significantly in two key parameters: the leakage power each core consumes and the maximum frequency each core can support. These two parameters directly lead to uneven power and thermal distribution across the whole CMP. Without careful planning, an excessive amount of heat can be generated in one specific area of the CMP, which typically is related to the cores with the highest frequency and leakage, while some other area related to the cores with lower frequency and leakage may remain relatively cool.

#### 1.1.4 Performance losses caused by HW DTM

One of the most commonly used methods to constrain a CPU from overheating is hardware dynamic thermal management (HW DTM), due to the high cost and inefficiency of current mechanical cooling techniques. One example of HW DTM techniques is clock gating. While the CPU is overheated, hardware actions such as clock gating are triggered. Portions of the circuit are disabled so that their flip-flops do not change states. There is no dynamic energy consumption and only leakage current exists. Though global clock gating is a well known power saving technique, it is also used as an effective dynamic thermal management technique. By using this, the temperature of the CPU can be lowered. Other useful HW DTM techniques include but are not limited to dynamic frequency scaling (DFS), dynamic voltage scaling(DVS), issue queue toggling and dynamic voltage/frequency scaling(DVFS). This dissertation mainly alleviates the impact of DVFS on a processor, because DVFS is widely used in high-performance processors for energy saving and temperature constraining. Intel's SpeedStep [85] and AMD's PowerNow! [86] are some industrial implementations using these techniques. Note that we use on-demand clock modulation (ODCM) in the experiment of thermal management on single-core processor, due to the limitation of the Pentium 4 processor. On-demand clock modulation is a unique technique in Intel processor series, which is generally global clock gating(AKA stop-clock). The impact of using ODCM is very similar to DFS.

Currently on real machines with real work loads, HW DTM does not happen frequently, because the current on-chip hardware thermal sensors can not respond quickly. For example, the readings of the sensors on Pentium 4 can only change every second, unable to react to the very fast thermal fluctuation of the die temperature happening in milliseconds. However, the software thermal sensor proposed by Wu et al. [74] can respond very quickly. If such thermal sensors are used in the processors in future, HW DTM can react to CPU temperature changes fast enough to prevent any thermal overruns. Therefore, in future HW DTMs could be very frequent.

The common side effect brought by HW DTM such as DVFS is the performance loss. When a thermal emergency happens, DVFS is triggered to make the CPU execute fewer cycles in one time unit. Thus, CPU runs at lower speed and the job on the CPU requires longer time to finish. The way to avoid such side effect is basically to avoid the triggering of DVFS. One heavily researched direction is to smartly schedule tasks onto the CPU to prevent the thermal emergencies from happening.

#### 1.1.5 DVFS details

Dynamic voltage scaling [84] is a power management technique, where the voltage used in a component is increased or decreased, depending upon circumstances. Dynamic frequency scaling [83](also known as CPU throttling) is a technique where a processor is run at a less-than-maximum frequency in order to conserve power.

The switching power dissipated by a chip using static CMOS gates is  $CV^2f$ , where C is the capacitance being switched per clock cycle, V is voltage, and f is the switching frequency, so this part of the power consumption decreases quadratically with voltage and linearly with frequency. There is also a static leakage current, which has become more and more important as feature sizes become smaller (below 90 nanometres) and threshold voltage becomes lower.

Dynamic voltage scaling is generally done in conjunction with dynamic frequency scaling, at least in CPUs. The speed at which a digital circuit can switch states - that is, to go from "low" to "high" (VDD) or vice versa - is proportional to the voltage differential in that circuit. Reducing the voltage means that circuits switch slower, reducing the maximum frequency at which that circuit can run. This, in turn, reduces the rate at which program instructions that can be issued. It may increase run time for program segments that are sufficiently CPU-bound.

#### 1.2 MOTIVATION AND PROBLEM STATEMENT

The motivation of our work starts from the fact that the future temperature of the processor depends on the current temperature of the processor and the power required for the job running on it. Removing a power-intensive job from the hot processor and replacing it with a low-power job can avoid a potential thermal emergency from happening. On the other hand, when the processor is cool, running a power-intensive job will be thermally safe. This indicates that scheduling tasks in a smart way can avoid DVFS penalties and save performance loss brought on by thermal issues. We explore such opportunities in three different scenarios: a single-core processor; CMP using 3D stacking technology(CMP-3D); and CMP with process variation to maximize throughput(CMP-PV). In each scenario, the common questions are: how are the jobs scheduled to avoid unnecessary thermal emergencies? To what extent can DVFS penalties be lowered and performance loss be saved? In the following section, more details are introduced with regard to the different scenarios.

#### 1.3 THESIS OVERVIEW

As introduced above, we explore such opportunities in three different scenarios: a singlecore processor; CMP using 3D stacking technology(CMP-3D); and variation-aware CMP. According different thermal conditions in each scenario, we design specific algorithms or heuristics for task-scheduling policies.

#### 1.3.1 ThreshHot - approaching threshold as close as possible

For single-core CPU, the idea of most of the existing work [14, 17, 56, 27, 42, 44] is to leverage the distinction between hot and cool jobs, and swap them at appropriate times to control the CPU temperature. We have observed that it is not necessarily best to schedule alternately between hot and cool jobs because cool jobs are precious cooling resources and they should be used judiciously. Moreover, a job treated as cool in the past may not be necessarily regarded as cool when it is swapped in. This is because future temperature depends on the power of the job and the current temperature as well. The scheduler must determine correctly the temperature slopes for each candidate job to make an informed selection.

We develop a heuristic scheduling algorithm to alleviate the thermal pressure of a processor. Our algorithm achieves this by observing that when the temperature is always below the thermal threshold, executing a hot job before a cool job results in a lower final temperature than execution in a reversed order. Our algorithm outperforms other scheduling algorithms such as one that changes the priority ranks of the hot and the cool jobs [42]. To know which job will be hot or cool for the hotspot, we develop a highly efficient *on-line* temperature estimator, leveraging the performance counter based power estimation [37, 38, 42], compact thermal modeling [61], and a fast temperature solver [26]. We implemented all these for a Pentium 4 processor.

#### 1.3.2 Power balancing tailored to 3D thermal conditions

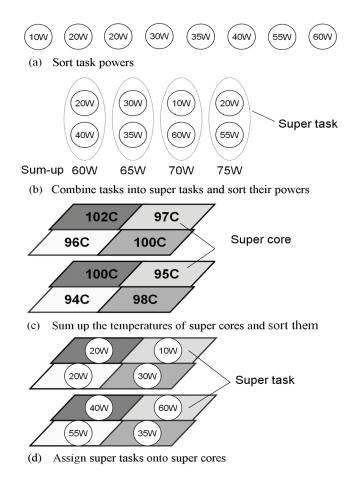

To alleviate the exacerbated thermal situation in 3D stacked dies, we propose a heuristic OSlevel technique that performs thermal-aware task scheduling on a 3D CMP. Unlike previous thermal-aware OS task schedulers for single core or 2D CMP, our scheduler for 3D chips must take into account the thermal conduction in the vertical direction. Early studies have shown that vertically adjacent dies have strong thermal correlations [2,75]. For example, a core in one layer could become hot because of a high power task running in the same vertical column but at a different layer. Based on these observations, our proposed scheduler always considers the aggregated power of cores that are vertically aligned. Secondly, we observed the core far away from the heat sink is always hotter than the neighboring one closer to the sink, whatever jobs are assigned to these cores. So we suggest more power-intensive jobs are always put closer to the heat sink. Finally, when a core is overheated, we choose to engage DTM on a vertically aligned core that generates the most power. Such an approach can greatly reduce the total power in one column and quickly cool down the overheated core.

#### 1.3.3 MBM - maximum bipartite matching on CMP-PV

As IC technology nodes continually scale down to 45nm and below, there is significant within-die process variation in the current and near-future CMPs. Process variation(PV) is the divergence of fabrication process parameters from their nominal values. It makes the cores in the chip differ in their maximum operable frequency, and the amount of leakage power they consume. The techniques for tolerating CMP-PV do exist. For example in Intel's Montecito [20], each core has its own clock and  $V_{dd}$ , and is called as a voltage and frequency island(VFI). Each VFI contains a clock divider to create its own local clock signal from the output of the shared PLL(phase locked loop). As in AMD's quad-core Opteron [67], asynchronous queues provide interfacing between different clock domains, with the buffers between the cores and their routers implemented as dual-clock FIFOs. To take advantage of the frequency variation of the cores caused by process variation in CMPs, R. Teodorescu et al. [68] proposed an algorithm named VarF & AppIPC to map higher-IPC(Instructions Per Cycle) cores to faster cores in order to obtain higher overall throughput. The reason behind this approach is that low-IPC applications are often memory-bound and usually benefit less from high-frequency cores than high-IPC applications do.

Our motivation is to demontrate that VarF & AppIPC might not be able to achieve as high throughput as it intends to do, considering the contraint that the CMP must run under a certain thermal limit. In fact, mapping the high-IPC job onto a fast core may exacerbate the thermal condition in that particular core. If DVFS is triggered frequently, the local throughput will be hurt.

The major contribution of this part is that we propose here a task migration algorithm that still tries to maximize throughput but takes both thermal and PV issues into account. The algorithm not only considers the frequency and leakage power information on each core, but also considers the power characteristics of running jobs (tasks). With that information, the algorithm predicts the throughput of each core-job binding, and uses the Maximum Bipartite Matching algorithm (abbreviated as MBM in this thesis) to get the optimal mapping.

#### 1.4 CONTRIBUTIONS

In summary, the contributions of this thesis are as follows:

- In a single-core, a heuristic algorithm named ThreshHot judiciously schedules hot jobs before cool jobs, to make the future temperature lower. Furthermore, it always makes the temperature as close to the threshold as possible while not overshooting.

- In 3D stacked processors, three heuristics are proposed. First, vertically stacked cores are treated as a core stack. The power of jobs is balanced among the core stacks instead of individual cores. Second, hot jobs are moved close to the heat sink to expedite heat dissipation. Third, when thermal emergencies happen, the most power-intensive job in a core stack is penalized in order to lower the temperature quickly.

- In the CMPs affected by significant process variation issues, maximizing the throughput is in conflict with on-chip thermal constraints. A maximum bipartite matching algorithm is used to solve this dilemma, and the implementation details are discussed.

All the algorithms proposed try to avoid thermal emergencies and the subsequent hardware DVFS. As a result, the chip performance is maintained.

#### 1.5 ROADMAP

The rest of the thesis is organized as follows. Chapter 2 presents an introduction of power obtaining and temperature prediction. Chapter 3 introduces prior work in three scenarios we investigate. The proposed scheduling policies are explained in Chapter 4. Chapter 5 concludes and describes the future work.

#### 2.0 OBTAINING POWER AND TEMPERATURE

All of our thermal-aware scheduling algorithms in this dissertation need information about the peak temperature of the processor. Also, the power consumed for the executed jobs needs to be obtained. In this chapter, we explain how these values can be obtained or estimated at runtime.

#### 2.1 TEMPERATURE OBTAINING AND COMPUTATION

#### 2.1.1 Thermal sensor readings are insufficient.

It seems that the OS could leverage existing on-chip thermal sensors for temperature readings. Unfortunately, this is insufficient because, in addition to the current temperature, our algorithm also needs to predict the temperature in the *next* time interval. Further, for a job not currently in execution it is difficult to determine, from its temperature history, what its temperature might be in the future. For example, suppose a job was swapped out last time at  $65^{\circ}$ C, and currently the sensor reading is  $60^{\circ}$ C. The temperature for this job in the next time interval may be either higher or lower than  $60^{\circ}$ C. This is because the future temperature depends on several factors: the current temperature, the power consumption of this job in the next time interval, and the length of the next interval.

#### 2.1.2 Temperature model.

Consider the simplified thermal model for a processor treated as a single node. The duality between heat transfer and electrical phenomena [41] has provided a convenient basis for modeling the chip temperature using a *dynamic compact thermal model* [61]:

$$\frac{1}{R}T + C\frac{dT}{dt} = P,$$

(2.1)

where T is the temperature relative to the ambient air. R and C are effective vertical thermal "resistor and capacitor" for the entire chip. Note that when  $\frac{dT}{dt} = 0$ , the chip reaches its steady temperature RP which depends on the average power of a job. The time to reach the steady temperature is determined by the RC constant  $(R \times C)$  of the thermal circuit. However, when the chip is switching among different jobs prior to the steady temperature, it is always in a transient stage (i.e.  $\frac{dT}{dt} \neq 0$ ).

Formally,  $T_{next} = F(P, T_{current}, \Delta t)$  where P is the average power in the next interval,  $\Delta t$  is the interval length, and function F is characterized by:

$$\mathbf{G}T + \mathbf{C}\frac{dT}{dt} = P , \qquad (2.2)$$

which is the matrix form of Equation (2.1) with **G** being the matrix of the thermal conductances. Both T and P are now vectors. Therefore, to obtain the temperatures in the next time interval for a candidate job interval, the scheduler must solve Equation (2.2) from  $T_{current}$  (which can be read from sensors), P of the job (which can be projected from its past power consumption), and  $\Delta t$  (which is a fixed value). The sensor readings alone cannot lead to a quantitative comparison with the thermal management threshold.

#### 2.1.3 Temperature calculation speedup.

Equation(2.2) may seem like a lot of computation for the scheduler to solve at runtime. Fortunately, previous work has shown that the complexity of Equation (2.2) can be greatly reduced if the time interval  $\Delta t$  is kept constant [26]. This is the case in our scheduler. Here we discuss the concept briefly.

The linear system in equation (2.2) has a complete solution as:

$$T(t) = e^{\mathbf{C}^{-1}\mathbf{G}t}T(0) + \int_0^t e^{\mathbf{C}^{-1}\mathbf{G}(t-\tau)}\mathbf{C}^{-1}P(\tau)d\tau$$

(2.3)

For a fixed length scheduling interval  $\Delta t$ , we take the average power during the interval so that P(t) can be factored out. (2.3) is now:

$$T(\Delta t) = \mathbf{A}T(0) + \mathbf{B}P \tag{2.4}$$

where  $\mathbf{A} = e^{\mathbf{C}^{-1}\mathbf{G}\Delta t}$ , and  $\mathbf{B} = \int_0^{\Delta t} e^{\mathbf{C}^{-1}\mathbf{G}(t-\tau)}\mathbf{C}^{-1}d\tau$ . Both  $\mathbf{A}$  and  $\mathbf{B}$  are constant matrices with a constant  $\Delta t$ . Since the linear system (2.4) is time-invariant, it holds for every interval  $\Delta t$ . Therefore:

$$T(n\Delta t) = \mathbf{A}T((n-1)\Delta t) + \mathbf{B}P(n-1), \quad \text{or simply}$$

$$T(n) = \mathbf{A}T(n-1) + \mathbf{B}P(n-1)$$

(2.5)

As we can see, once **A** and **B** are pre-calculated and stored, the temperature at any step n can be found through a linear combination of the temperature and power at step n-1. When used online, T(n-1) is the current temperature, P(n-1) is the power dissipated by a job in the next scheduling interval, and T(n) is the temperature at the end of the next interval. Computing the T(n) now is very inexpensive. For example, a P4 thermal model has 82 nodes in total and computing the  $82 \times 1$  temperature vector at runtime takes only ~16.45 $\mu s$ . For CMP-3D or CMP-PV, where the core numbers are much larger, the computation overhead of temperatures can be distributed to all the cores, assuming the lateral heat dissipation among cores can be ignored [80]. Next, we will discuss how to obtain the power values P(n-1) online.

#### 2.2 COMPUTING THE POWERS

#### 2.2.1 Power estimation

Recent research has proposed to incorporate on-chip power sensors for power and thermal control [49]. With on-chip power sensors, the OS can obtain the runtime power consumption of critical components easily and quickly. Though such technology is not readily available, some other alternatives have been proposed before and were demonstrated to be very fast and effective. We adopt the method that uses the performance counters to monitor runtime power consumption [5, 37, 38]. Counters provided by high-performance processors such as the Pentium and UltraSPARC can be queried at runtime to derive the activities of each functional unit (FU). When combined with FUs' per access power, their dynamic power and the total chip power can be obtained. However, earlier work either did not consider the *leakage power* or used a constant as a proxy, since leakage is dependent on temperature which was difficult to obtain at runtime. When the processor runs at a high temperature, its leakage can contribute significantly to the total power [34]. Since we also calculate the temperature online, we consider the leakage as an integral part in our power estimation. In the scenarios of single-core processor and CMP-3D we adopted a model developed in [29, 45] using PTM(Predictive Technology Model)  $0.13\mu$  technology parameters [90], matching the processor technology size(Pentium 4 Northwood) in our experiment. We determined the necessary device constants through SPICE simulation. In the scenario of CMP-PV, the corewise leakage variation is exposed by the effective leakage parameter,  $p_{eff}$  [32]. PTM 32nm technology node is used in SPICE simulation to find  $p_{eff}$  in each individual core. In practice, such core-wise leakage variation parameters can be provided by the chip manufacturers during post-manufacturing.

#### 2.2.2 Power prediction

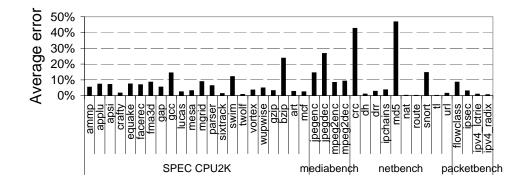

The last issue we need to resolve is the prediction of power consumption of a job in the *next* scheduling interval, as required by Equation (2.5). Here, we face a tradeoff between complexity and accuracy, for a high quality predictor would typically require large memory to store the history information and significant computation time for processing this information. Table-based schemes are likely not appropriate for our framework, for the kernel has a strict limit on the memory space for storing the control information of each job. For example, a good hash table based power predictor that we considered exceeded the kernel space limit, and a small fully associative table predictor could slow down the program by  $\sim 6\%$ . Therefore, we settled for the simple but cost-effective and fast *last-value-based* predictor which always uses the last power values to predict those in the next interval. Its error rates for our experimented benchmarks, including 22 SPEC2K, 4 mediabench, 10 netbench, and 4 packetbench, are shown in Figure 1. As we can see, on most programs it has less than 10% error rate. High misprediction rates are seen in *bzip*, *jpegenc*, *jpegdec*, *crc*, and *md5*. Our experiments with those programs (in Section 4.1.4) did not show significant disadvantages in most cases, indicating that (at least in those cases) mispredictions did not lead to much mis-scheduling. For example, if a job will have the  $i^{th}$  highest temperature among all candidates, and even if the power is mispredicted, its predicted temperature will still remain in the  $i^{th}$  position, then power misprediction does not change the scheduling decision. This is observed clearly in crc and md5, which tend to alternate between two different power levels. Hence, the last-value predictor always missed the right value, but the error does not lead to big temperature changes, and therefore, did not impact the scheduling decision.

#### 2.3 WORKFLOW SUMMARY

To summarize, at the end of each scheduling interval, the OS probes the performance counters from the processor. Those counters record the activities of the current job during the past

Figure 1: Average error rates for last power value predictor.

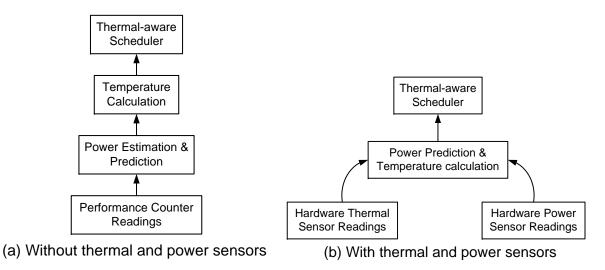

interval. They are then converted into the power consumption to the granularity of functional units. Power prediction is performed at this time. The past power values are then fed into a full-chip thermal model for computing the current temperature at the current scheduling interval. For all candidate jobs, their future temperatures are also calculated at this time using their predicted power values. All those future temperatures are sent to the scheduler for next job selection. The flow is depicted in Figure 2(a).

Figure 2: Thermal-aware task scheduling methodologies.

Alternatively, if the processor has available thermal and power sensors, the OS can directly read information from the sensors to compute the future temperatures, as illustrated in Figure 2(b). However, this would entail *many* sensors as the future temperature calculation needs fine-grained power and temperature information. If the sensors are very few, probing the counters is still necessary but the sensor readings can be used for online self-calibration to lessen the error due to thermal and power model abstraction.

#### 2.4 THE ACCURACY OF TEMPERATURE CALCULATION

W. Wu et al. in [74] developed such a software thermal sensor (STS) in a Linux system with a Pentium 4 Northwood core, using the same methodology as shown in Figure 2(a). Their power and thermal models were calibrated and validated against on-chip sensor readings, thermal images of the Northwood heat spreader, and the thermometer measurements on the package. The thermal profiles they obtained through a continuous execution of some SPEC2K benchmarks for hours show that the computed temperatures on the heat spreader using STS are very close to the thermometer readings on the heat spreader. The reason for the discrepancy between the on-die sensor readings and the computed temperatures of 24 function units is that the sampling interval of the on-die sensor on P4 Northwood is fixed at one second, while the STS can compute temperatures every eight milliseconds. Intel admits the sensors are slow. Therefore, the on-die sensor can miss lots of thermal details. However, W. Wu et al. in [74] show two achievements of STS at least. One is that there is a similarity between the thermal changes from on-die sensor readings and the computed ones. The other is that the errors due to modeling and abstraction do not propagate. Finally, to make sure the temperatures of the function units are accurate, they also calibrated them with the results obtained from the micro-architecture level thermal simulation tool - HotSpot developed by Skadron et al. [62].

#### 3.0 RELATED WORK

Other researchers have done some work in the three thermal scenarios we deal with. However, for each case, our work has improved upon their work or has significant differences from theirs. Here we list the prior work and compare those projects with ours.

#### 3.1 PRIOR WORK IN A SINGLE CORE PROCESSOR

First we introduce the related work on single-core processors. Some recent work has developed temperature control techniques for *real-time* workloads [3,4,69,71]. The main approach is to dynamically adjust the CPU speed to minimize the peak temperature of the CPU, subject to the constraint that all jobs finish by their deadlines. Similar approaches can be used to minimize the energy consumption for real-time systems as well [55,77]. In contrast, our objective is to maximize the performance by scheduling the workloads to keep the temperature below a given threshold. Note that the threshold can be the manufacturer-defined temperature threshold<sup>1</sup> for the physical chip, or an OS-defined threshold for a system to stay within a thermal envelope. Hence, we always attempt to run workloads with full speed as long as the temperature stays below the given threshold.

Thermal management through workload scheduling has been studied in various scenarios. In CMPs, the "Heat-and-Run" technique performs thread assignment and migration

<sup>&</sup>lt;sup>1</sup>This threshold is a safe operating temperature beyond which the chip might be damaged due to overheating, and DTMs must take place.

to balance the chip temperature at runtime [56]. In another work [17], a suite of DTM techniques, job migration policies, and control granularity are jointly investigated to achieve the maximum chip throughput. Also recently, a simple periodic thread swapping between two cores to balance the chip temperature was studied on a dual-core processor [14]. All these approaches exploit a simple interleaving between hot and cool jobs when it comes to scheduling. Our objective is to find the best thread for a core when it becomes hot, and this thread may not be the coolest available thread. For example, when there is both a medium hot and a cool thread, our scheduler will pick a medium hot thread as long as it will not trigger DTM. In this thesis, we demonstrate this philosophy using a scheduling heuristic on a single-core processor, and leave its extensions to CMPs as future work.

In the single-core domain, the "HybDTM" [42] controls temperature by limiting the execution of the hot job once it enters an alarm region. This is achieved by lowering the priority of the hot job so that the OS allocates it with fewer time slices to reduce the processor temperature. The same principle can be seen in [6] where the energy dissipation rate is evened among hot and cool jobs by assigning different CPU time to them. Our technique does not modify the time allocated to hot and cool jobs, as this would affect the fairness policy of the system. Instead, we attempt to rearrange their execution order within each OS epoch to lower the overall temperature. This allows us to control the temperature while preserving priorities among different jobs.

Thermal control through workload management has also been studied at the system level. In [52], a temperature-aware workload placement heuristic was studied for data centers to minimize the cost of cooling. The "Mercury and Freon" [30] framework uses software to estimate temperatures for a server cluster and manages its component temperatures through a thermal-aware load balancer. The "ThermoStat" [13] tool employs a detailed 3D computational fluid dynamics model for a rack-mounted server system. This tool can guide the design of better dynamic thermal management techniques for server racks. Our work targets at CPU temperature control, which can be complementary to system level thermal management schemes.

#### 3.2 PRIOR WORK IN CMP BUILT WITH STACKED DIES

There have been many works recently investigating the performance potential and the challenges in 3D CMP designs. Mysore et al. [54] proposed to stack on top of a normal processor a profiling die that can identify memory leakage, perform diagnosis etc. to save the area and power on the main die. Black et al. [7] studied the performance advantages and thermal challenges for stacking a large DRAM and SRAM cache on a processor, as well as implementing a processor in two layers. Xie et al. [75] reported that the peak temperature in a 3D chip of 2 layers and one die per layer can be as high as 125°C. More importantly, there is only a difference of a couple of degrees, in the worst case, between the hotspots in the top die and the bottom die. This indicates a strong thermal correlation among adjacent layers in a 3D processor. To ensure better heat dissipation in a 3D chip, Puttaswamy et al. proposed a "Thermal Herding" design [58] at the micro-architecture level which lowers the power of the chip by splitting individual function unit blocks across multiple layers, and places the most frequently switched part, or activity, closest to the heat sink. Alternatively, adding thermal vias can also alleviate the thermal conditions within a 3D chip. Goplen et al. [24] studied that proper placement of thermal vias in 3D IC design can obtain a maximum of 47.1% reduction in temperature. In the multicore domain, Loh et al. [48] introduced different approaches for implementing single-core and multicore 3D processors. Particularly, they pointed out that stacking separate cores (in multicore design) can significantly reuse the existing 2D designs, and the interface between the cores needs no more than a few thousand connections.

Compared to the previous work, this thesis focuses mainly on software approaches to thermal management in 3D CMP. There have been proposals on OS-assisted thermal management for single core chips. The HybDTM [42] technique controls temperature by limiting the execution of a hot job once it enters an alarm zone. This is achieved by lowering the priority of the hot job so that the OS allocates fewer timeslices to it and gives cool jobs relatively more timeslices to execute. An ideal simulation study was performed in [44] to show the benefits of interleaving hot and cool job executions. However, neither performance study nor task switching overhead was considered. In the 2D multicore domain, the "Heat-and-Run" scheduler [56] assumes that there is always an idle and cool core present in a CMP such that an overheated core can migrate its thread to the cool core. However, in our technique, all cores are assumed to be busy and have temperatures above an idle core's temperature. Choi et al. [14] compared and implemented three different task schedulers, heat-balancing, deferred execution, and threading with cool-loops, to leverage temporal and spatial heat slacks among application threads. The proposed mechanisms are implemented in the PowerPC5. Chong et al. [66] proposed a 3D MPSoC thermal optimization algorithm that conducts task assignment, scheduling, and voltage scaling for a set of real-time workloads. The goal was to slow down the workloads as long as the deadlines are met. This is quite different from our approach which focuses on best performance and low thermal profile.

#### 3.3 PRIOR WORK IN CMP WITH PROCESS VARIATION

Borkar et al. [8] point out that process variation could be one major challenge in near-future chip production and examples of PV modeling can be seen in [10, 59]. In these papers, the PV effects, both random and systematic, within-die and die-to-die variations are modeled. The impact of PV on the performance and leakage power of logic and SRAM structures is evaluated. Our thermal-aware task scheduling algorithm is based on their work and especially relies on the modeling tool provided by Sarangi et al. [59].

Brooks et al. [11] define and investigate the major components of any hardware dynamic thermal management scheme. Skadron et al. [62] provide a compact thermal model and a fast simulation tool for evaluating the impact of dynamic thermal management. For software-level thermal management by task migration, there are exemplar ideas proposed in [22, 14, 44, 42].

More recently, there have been papers that take power/thermal management along with PV into consideration. Kursun et al. [43] use thermal imaging technique to sense the process

variation of the CMP. Their methodology is to treat the CMP with PV as a "black-box", while our work models PV from the ground up. Moreover, they only consider leakage variation and don't model the possible frequency differences of the cores. Wang et al. [70] accommodate process variation information by using a coefficient matrix, and apply optimal control theory to keep the power and temperature within constraints. The difference between their work and ours is that they haven't considered the potential opportunities brought by task migration. Teodorescu et al. [68] and Herbert et al. [32] model the frequency and leakage discrepancies on CMP from ground up. Teodorescu et al. [68] attempt to maximize the throughput by heuristically mapping the CPU-intensive jobs onto the faster cores and mapping memory-intensive jobs onto the slower cores. Such a fixed mapping may generate sub-optimal results when the faster cores trigger DVFS during thermal emergencies. By setting local and total power constraints, they expand their  $VarF \mathscr{C}AppIPC$  algorithm and use linear programming to maximize the performance. Their linear programming algorithm will change back to  $VarF \mathscr{C}AppIPC$  when the CMP is under thermal constraints, because the sum of the temperatures of the cores is not necessarily below a limit. Each core only needs to satisfy its own thermal constraint. Herbert et al. [32] design a DVFS scheme that adapts to each core's own frequency and leakage settings. Their goal is to minimize the energy per instruction and maintain the throughput of the CMP. The difference of the idea in [68, 32]from ours is that they both bind high-IPC jobs onto faster cores to take advantage of the high frequency. We demonstrate this is not an optimal solution with the thermal constraints considered, and propose a new algorithm.

## 4.0 PROPOSED TASK SCHEDULING SOLUTIONS

Here we discuss about our detailed task scheduling policies on three different thermal scenarios. In each section, we first introduce our idea; then we present specific algorithms or heuristics, which implement the idea. Finally, the results are shown at the end of each section.

# 4.1 THRESHHOT

When a modern single-core processor heats up due to high power, a dynamic thermal management technique curbs the overshooting of die temperature. However, the CPU suffers from performance loss. In the following, we design a heuristic task scheduling method to prevent the temperature from trespassing into this thermal threshold. In this way, the triggering of DTM can be reduced and performance loss can be avoided.

### 4.1.1 Thermal scheduling algorithms

When the processor underlying the OS is overheated and forced to slow down, nearly all vital measures will be degraded: throughput and utilization will be reduced, response time will increase, jobs are more likely to miss deadlines, etc. Thus, independent of the characteristics and focus of a given system, processor overheating will negatively affect its performance.

When incorporating new features, such as thermal awareness, into a scheduler, it is desirable to make them as transparent to the user as possible; in particular, to keep the existing scheduler structure and properties. For this reason, we focus our work on a batch system for which the main objectives are the minimum turnaround time, maximum throughput, and CPU utilization. For batch jobs, the OS periodically interrupts the job execution to maintain its statistics and determines if a different job should be swapped in and, if so, which one. We amend the decision of which job should be selected next with thermal-awareness while keeping all other features intact. Therefore, in every scheduling interval, the OS needs to select the best job anticipating that such a selection would lead to the overall least amount of thermal violations.

4.1.1.1 The principle To keep the temperature below the threshold, a naïve, greedy algorithm tries to control the temperature by keeping the *current* chip temperature as low as possible, by executing at each step the coolest available job. As a result, the jobs are scheduled in the order of increasing temperature, from coolest to hottest. As it turns out, however, the greedy schedule actually increases the chances of exceeding the temperature threshold in the long run. To see this, consider a simple case where at some schedule interval t only two jobs x and y are available, with power consumption  $P_x$  and  $P_y$  respectively, where  $P_x < P_y$  (so x is cooler than y). We will show that if we execute these jobs in order xy (x before y, that is the greedy schedule) then the temperature at the end of t+1 is higher than for the order yx (y before x).

Consider the simplified thermal model for a processor treated as a single node. The duality between heat transfer and electrical phenomena [41] has provided a convenient basis for modeling the chip temperature using a *dynamic compact thermal model* [61]:

$$\frac{1}{R}T + C\frac{dT}{dt} = P, (4.1)$$

where T is the temperature relative to the ambient air. R and C are the effective vertical thermal resistor and capacitor of the entire chip. Note that when  $\frac{dT}{dt} = 0$ , the chip reaches

its steady temperature RP which depends on the average power of a job. The time to reach the steady temperature is determined by the RC constant  $(R \times C)$  of the thermal circuit. However, when the chip is switching among different jobs prior to the steady temperature, it is always in a transient stage (i.e.  $\frac{dT}{dt} \neq 0$ ). Discretizing the time scale into small time steps  $\Delta t$  and denoting by  $T_i$  the temperature at time  $i\Delta t$ , Equation (4.1) can be approximated by

$$\frac{1}{R}T_i + C\frac{T_i - T_{i-1}}{\Delta t} = P$$

(4.2)

Rearranging the terms, we have  $T_i = \alpha T_{i-1} + \beta P$ , where  $\alpha = \frac{RC}{\Delta t + RC}$  and  $\beta = \frac{R\Delta t}{\Delta t + RC}$  are constants dependent on  $\Delta t$  and, clearly,  $\alpha < 1$ . If each scheduling interval is divided into n steps of length  $\Delta t$  the temperature at the end of this interval can be expressed as:

$$T_n = \alpha^n T_0 + (\alpha^{n-1} + \alpha^{n-2} + \dots + 1)\beta P$$

(4.3)

For schedule xy, the temperature after completing y (2n steps) will be

$$T_{2n}^{xy} = \alpha^{2n} T_0 + (\alpha^{n-1} + \alpha^{n-2} + \dots + 1)\beta(\alpha^n P_x + P_y)$$

(4.4)

For schedule yx, this final temperature will be

$$T_{2n}^{yx} = \alpha^{2n} T_0 + (\alpha^{n-1} + \alpha^{n-2} + \dots + 1)\beta(\alpha^n P_y + P_x)$$

(4.5)

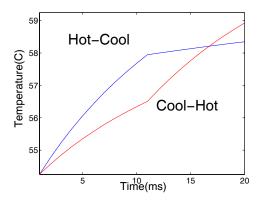

It is now easy to see that  $P_x < P_y$  implies  $T_{2n}^{yx} < T_{2n}^{xy}$ . That is, scheduling the hotter job first results in a lower final temperature. Figure 3 gives an intuitive illustration of the impact on temperature with different scheduling order. The graph shows temperature variation for the IntReg unit with two different power inputs, representing two different jobs. They are scheduled in two different orders as just described. The graph was obtained using a full-chip thermal model (rather than a single node as a whole) solved by the fourth order Runge-Kutta method. As we can see, running the hotter job first results in lower final temperature. If the chip's thermal threshold is in between the difference of the two ending temperatures, the greedy schedule would cause a thermal violation.