## APPLICATION OF BAYESIAN NETWORKS TO COVERAGE DIRECTED TEST GENERATION FOR THE VERIFICATION OF DIGITAL HARDWARE DESIGNS

by

Jeffery S. Vance

BS kp'Computer Engineering, University of Pittsburgh, 2006

Submitted to the Graduate Faculty of

the Swanson School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science

University of Pittsburgh

2010

### UNIVERSITY OF PITTSBURGH

### SWANSON SCHOOL OF ENGINEERING

This thesis was presented

by

Jeffery S. Vance

It was defended on

December 9, 2009

and approved by

Steven P. Levitan, Ph.D., Professor

Allen C. Cheng, Ph.D., Assistant Professor

Jun Yang, Ph.D., Associate Professor

Thesis Advisor: Steven P. Levitan, Ph.D., Professor

Copyright © by Jeffery S. Vance

2010

# APPLICATION OF BAYESIAN NETWORKS TO COVERAGE DIRECTED TEST GENERATION FOR THE VERIFICATION OF DIGITAL HARDWARE DESIGNS

Jeffery S. Vance, M.S.

University of Pittsburgh, 2010

Functional verification is generally regarded as the most critical phase in the successful development of digital integrated circuits. The increasing complexity and size of chip designs make it more challenging to find bugs and meet test coverage goals in time for market demands. These challenges have led to more automated methods of simulation with constrained random test generation and coverage analysis. Recent goals in industry have focused on improving the process further by applying *Coverage Directed Test Generation* (CDG) to automate the feedback from coverage analysis to test input generation.

Previous research has presented Bayesian networks as a way to achieve CDG. Bayesian networks provide a means of capturing behaviors of a design under verification and making predictions to help guide test input generation to reach coverage goals more quickly. Previous research has shown methods for defining a Bayesian network for a design domain and generating input parameters for dynamic simulation.

This thesis demonstrates that existing commercial verification tools can be combined with a Bayesian inference engine as a feasible solution for creating a fully automated CDG environment. This solution is demonstrated using methods from previous research for applying Bayesian networks to verification. The CDG framework was implemented by combining the Questa verification platform with the Bayesian inference engine SMILE (Structural Modeling, Inference, and Learning Engine) in a single simulation environment. SystemVerilog testbenches and custom software were created to automatically find coverage holes, predict test input parameters, and dynamically change these parameters to complete verification with a fewer number of test cases. The CDG framework was demonstrated by performing verification on both a combinational logic design and a sequential logic design. The results show that Bayesian networks can be successfully used to improve the efficiency and quality of the verification process.

# TABLE OF CONTENTS

| 1.0 |     | INTRO                            | DUCTION1                              |  |

|-----|-----|----------------------------------|---------------------------------------|--|

|     | 1.1 | M                                | OTIVATION2                            |  |

|     | 1.2 | PR                               | OBLEM STATEMENT                       |  |

|     |     | 1.2.1                            | The Problem                           |  |

|     |     | 1.2.2                            | The Solution                          |  |

|     | 1.3 | οι                               | JTLINE OF THESIS                      |  |

| 2.0 |     | OVERVIEW OF VERIFICATION METHODS |                                       |  |

|     | 2.1 | VE                               | CRIFICATION OF HDL DESIGNS            |  |

|     | 2.2 | FU                               | NCTIONAL VERIFICATION9                |  |

|     |     | 2.2.1                            | Basic Verification Methodology10      |  |

|     |     | 2.2.2                            | Constrained Random Input Generation11 |  |

|     |     | 2.2.3                            | Functional Coverage12                 |  |

|     | 2.3 | CC                               | OVERAGE DIRECTED TEST GENERATION      |  |

|     |     | 2.3.1                            | Closing Coverage with CDG14           |  |

|     |     | 2.3.2                            | Generating Unplanned Scenarios15      |  |

| 3.0 |     | OVERV                            | /IEW OF BAYESIAN NETWORKS 16          |  |

|     | 3.1 | BA                               | SIC BAYESIAN NETWORK CONCEPTS 16      |  |

|     |     | 3.1.1                            | Example Bayesian Network 17           |  |

|     |     | 3.1.2                                  | Joint Probability Calculations and Inference                  | . 18 |

|-----|-----|----------------------------------------|---------------------------------------------------------------|------|

|     |     | 3.1.3                                  | Inference with Example Bayesian Network                       | . 19 |

|     |     | 3.1.4                                  | Learning Network Parameters                                   | . 21 |

|     | 3.2 | AI                                     | PPLYING BAYESIAN NETWORKS TO VERIFICATION                     | . 23 |

|     |     | 3.2.1                                  | A Framework for CDG                                           | . 23 |

|     |     | 3.2.2                                  | Reaching Unobserved Events                                    | . 25 |

|     |     | 3.2.3                                  | Applying Bayesian Networks                                    | . 26 |

|     |     | 3.2.4                                  | Choosing Domain Variables for the Network                     | . 28 |

| 4.0 |     | IMPLE                                  | MENTATION OF CDG SOLUTION                                     | . 32 |

|     | 4.1 | FU                                     | UNCTIONAL VERIFICATION TOOLS AND TESTBENCH                    | . 32 |

|     | 4.2 | BA                                     | YESIAN NETWORK TOOLS                                          | . 35 |

| 5.0 |     | BAYES                                  | IAN NETWORK FOR A COMBINATIONAL LOGIC DESIGN                  | . 39 |

|     | 5.1 | 0                                      | VERVIEW OF THE WALLACE TREE MULTIPLIER                        | . 40 |

|     | 5.2 | A SIMPLE BAYESIAN NETWORK              |                                                               |      |

|     |     | 5.2.1                                  | Inference with Simple Network                                 | . 42 |

|     | 5.3 | CDG APPLIED TO WALLACE TREE MULTIPLIER |                                                               | . 46 |

|     |     | 5.3.1                                  | Experiment 1: Generate all Outputs                            | . 46 |

|     |     | 5.3.2                                  | Experiment 2: Generate all Outputs with Relearning Parameters | . 49 |

|     |     | 5.3.3                                  | Experiment 3: Generating Result Sequences                     | . 50 |

|     |     | 5.3.4                                  | Experiment 4: Network with Input Properties                   | . 55 |

|     |     | 5.3.5                                  | Experiment 5: Reaching Internal States                        | . 58 |

| 6.0 |     | BAYES                                  | IAN NETOWORK FOR A SEQUENTIAL LOGIC DESIGN                    | . 63 |

|     | 6.1 | BA                                     | YESIAN NETWORK FOR A VENDING MACHINE                          | . 63 |

| 7.0    | CON    | CLUSIONS AND FUTURE WORK                      | 71 |

|--------|--------|-----------------------------------------------|----|

| APPEND | OIX A. | TESTBENCH CODE FOR WALLACE TREE MULTIPLIER    | 74 |

| APPEND | OIX B. | CODE FOR MULTIPLIER BAYESIAN INFERENCE 1      | 01 |

| APPEND | OIX C. | CODE FOR VENDING MACHINE TESTBENCH 1          | 05 |

| APPEND | OIX D. | CODE FOR VENDING MACHINE BAYESIAN INFERENCE 1 | 21 |

| APPEND | OIX E. | EXAMPLE LOG FILES 1                           | 28 |

| BIBLIO | GRAP   | HY1                                           | 31 |

# LIST OF TABLES

| Table 5-1: Simulation Results for Generating all Outputs                           | 48 |

|------------------------------------------------------------------------------------|----|

| Table 5-2: Simulation Results for Generating all Outputs with Relearning           | 50 |

| Table 5-3: Simulation Results for Generating all Output Sequences                  | 52 |

| Table 5-4: Simulation Results using Input Properties to Generate all Results Twice | 57 |

| Table 6-1: Results of Vending Machine Coverage                                     | 70 |

# LIST OF FIGURES

| Figure 2-1. Basic Testbench Structure                                 | 11 |

|-----------------------------------------------------------------------|----|

| Figure 2-2. Typical Process for Coverage Driven Verification          | 13 |

| Figure 3-1. Example Bayesian Network (Based on [2, 11])               | 17 |

| Figure 3-2. Example Bayesian Network with Inference                   | 20 |

| Figure 3-3. Basic Model for Applying Bayesian Networks                | 21 |

| Figure 3-4: Automated CDG using a Bayesian Network                    | 24 |

| Figure 3-5. Example Bayesian Network for Verification (Based on [5])  | 27 |

| Figure 3-6. Example Data Set Generation from Testbench (Based on [1]) | 29 |

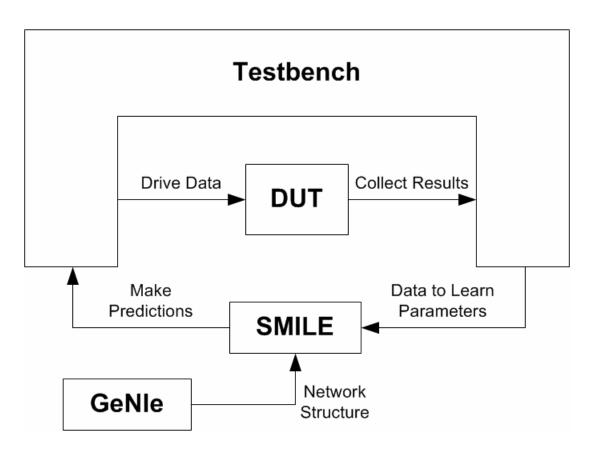

| Figure 4-1: Testbench Structure for CDG Solution                      | 33 |

| Figure 4-2: CDG Solution with GeNIe and SMILE                         | 35 |

| Figure 5-1: 4-bit Wallace Tree Multiplier (based on [18])             | 41 |

| Figure 5-2: Basic 3-Node Bayesian Network                             | 42 |

| Figure 5-3: Inference with Basic Bayesian Network                     | 43 |

| Figure 5-4: Inference Results with More Predictions                   | 45 |

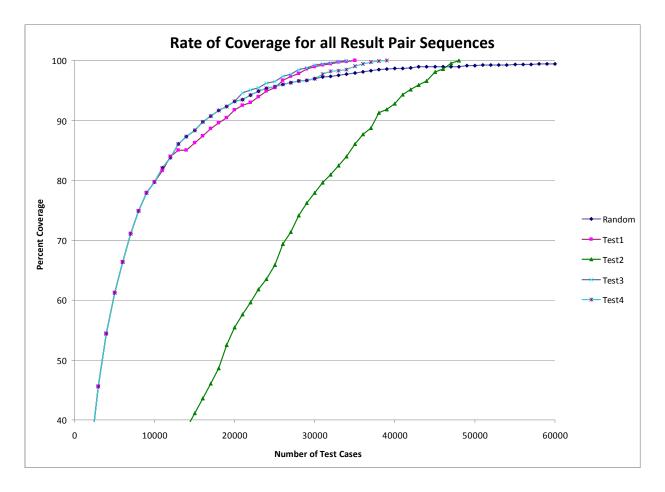

| Figure 5-5: Trend of Coverage for Generating Sequences                | 53 |

| Figure 5-6: Bayesian Network using Test Directives                    | 56 |

| Figure 5-7: A More Complex Bayesian Network for the Multiplier        | 58 |

| Figure 5-8: Inference to Determine Internal States                | 60 |

|-------------------------------------------------------------------|----|

| Figure 5-9: Inference with Additional Evidence for Internal State | 61 |

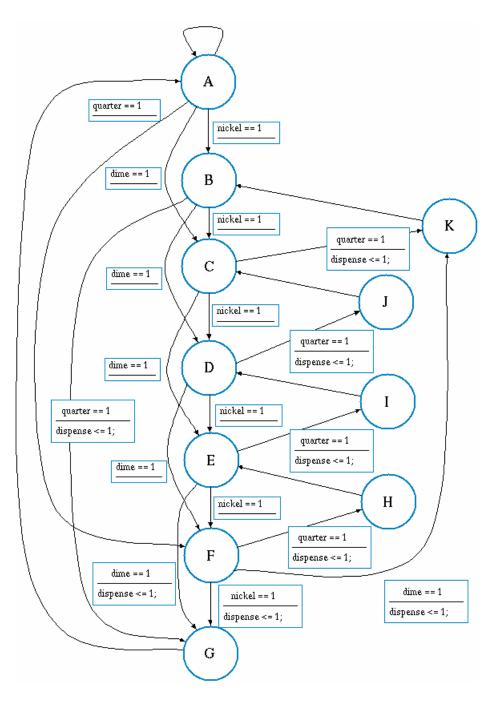

| Figure 6-1: State Machine for a Vending Machine                   | 64 |

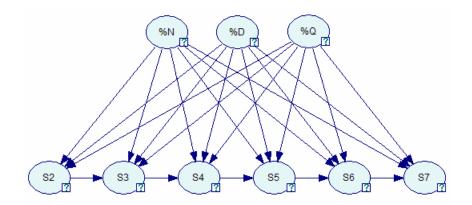

| Figure 6-2: Bayesian Network for a Vending Machine                | 66 |

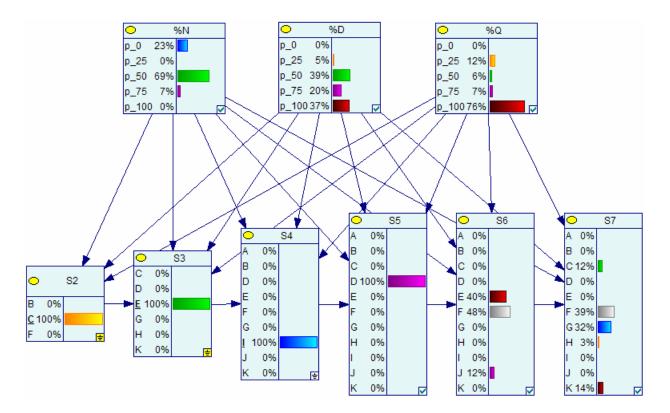

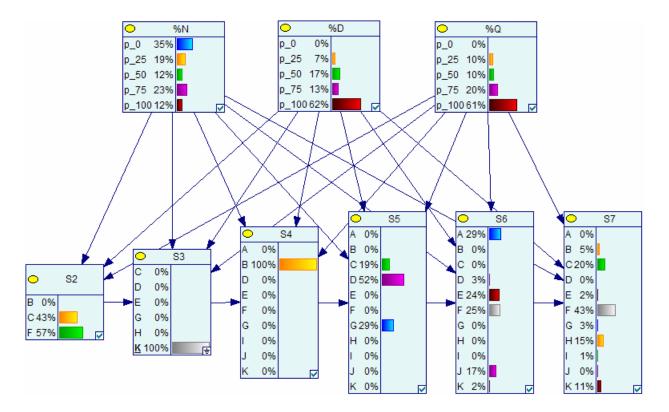

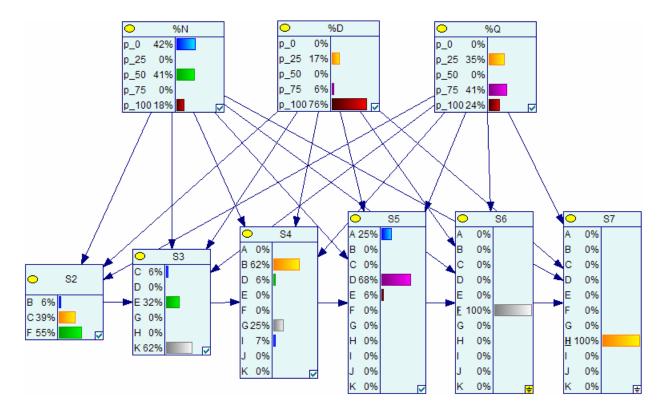

| Figure 6-3: Inference to Reach State I on Step 4                  | 67 |

| Figure 6-4: Inference to Reach State K on Step 3                  | 68 |

| Figure 6-5: Inference to Reach State H on Step 7                  | 69 |

#### **1.0 INTRODUCTION**

Advances in technology continuously require improved performance and features of integrated circuit designs. Chip designs such as microprocessors, specialized System-on-a-Chip (SOC) designs, and Field Programmable Gate Arrays (FPGAs) continue to grow more complex while being adopted in broader types of applications. As the complexity and size of chip designs grow, verifying the correctness of these designs becomes more challenging for design teams. While verification engineers must meet the new challenges of finding bugs, time-to-market demands require the verification process to be completed quickly. In recent industry practice, the verification phase is commonly the longest phase in hardware design cycles and is the most critical to completing a product in time to meet market demands.

In order to meet the increasing challenges of hardware verification, tools and methodologies have been developed to improve verification flows. These solutions succeed in removing much of the manual labor traditionally involved in verifying hardware designs. Tasks such as writing test cases, running tests, and collecting and evaluating results are now typically automated to a high degree. However, verification continues to be one of the primary challenges in hardware design due to new areas of manual effort that are required.

#### **1.1 MOTIVATION**

One of the primary motivations for improving the efficiency and quality of verification cycles is from a business perspective. The highly competitive nature of technology industries puts pressure on companies to release products quickly. Time-to-market is critical to the success of a product since competitive products released earlier to market typically draw the most revenue. Since verification is usually the bottleneck in time-to-market, businesses directly profit from speeding up the verification process.

Ensuring high quality of verification is also important to businesses since the consequences of failing to find bugs can be very costly. Bugs not found until the design is manufactured in silicon are often expensive to fix since it requires repeating much of the development cycle. The consequences of releasing a product with a bug to consumers has been shown to be worse since the company must bear the costs of fixing and replacing defect products as well as endure a potential loss in reputation.

Another motivation in improving verification flows is to provide higher assurance of quality in products for critical systems. Integrated circuits are used in many critical applications such as medical devices, control systems for aviation and automotive industries, and protection systems in nuclear power plants. Regulatory agencies impose strict criteria for engineers to demonstrate the correctness of designs for these products. Improving the verification process allows these companies to more easily meet these criteria while assuring the quality of their designs for critical systems.

2

#### **1.2 PROBLEM STATEMENT**

Many methods for improving the verification flow of hardware designs have been focused on simulation based functional verification. Hardware designs are implemented in a hardware description language and verification engineers create testbenches to simulate the designs at the code level. Recent methods in industry have automated much of this process by using constrained random test input generation, automated checking of data, and coverage monitoring to determine when verification is complete. Using random test inputs allows many design requirements to be verified very quickly with minimal manual effort since no specific test cases are written. Random tests have the additional benefit of possibly generating test scenarios that were not initially thought of.

#### 1.2.1 The Problem

Despite the many improvements in recent functional verification techniques, increasing complexities in designs still make this task a difficult challenge. While much of the manual labor in writing test cases and checking results is removed, there is still often a lot of manual effort required to complete the verification. This is because applying random test inputs alone will not usually produce all the test cases needed to verify the design. The verification team must evaluate the coverage results of the testbench and determine which scenarios remain to be verified. The team can then either write directed tests for the remaining cases, or modify the testbench in attempt to steer the random input generation into the untested scenarios. The manual effort in either solution creates a new bottleneck in the verification cycle that can considerably impact completion schedules for large designs.

Research has been done in *Coverage Directed Test Generation* (CDG) to provide solutions to closing the manual feedback loop from coverage analysis to test input generation. One of these solutions is *dynamic coverage-controlled stimulus generation* [21]. This method attempts to apply machine learning to observe how coverage goals are impacted by changes in input stimulus and dynamically bias input generation parameters to hit the remaining verification scenarios.

S. Fine and A. Ziv (IBM Research Laboratory) have successfully applied Bayesian networks as a method of achieving CDG with dynamic coverage-controlled stimulus generation [5]. In their research, a methodology was developed for creating Bayesian networks to model the relationships between coverage goals, test input parameters, and internal states of a design under verification. It has been shown that this technique can successfully generate test directives from observed coverage holes to guide the verification to completion more quickly [1, 5, 6, 7].

Although previous research has shown success in establishing methods for CDG based verification, there are few solutions for applying these methods in industry using existing verification platforms. Most CDG solutions have been demonstrated with proprietary solutions used by some companies internally for research and development. Despite the continuously enhanced features of commercial verification tools provided by Electronic Design Automation (EDA) vendors, there is currently little guidance for engineers to implement fully automated CDG solutions [16].

#### 1.2.2 The Solution

This thesis demonstrates a feasible solution for creating a fully automated CDG verification environment with existing verification tools and a Bayesian inference engine. This solution allows verification to meet coverage goals without any manual feedback for coverage closure. This solution was demonstrated using the Questa verification tool from Mentor Graphics [17] combined with the inference engine SMILE (Structural Modeling, Inference, and Learning Engine) [13]. The CDG environment was implemented with both SystemVerilog testbenches and custom C++ programs. Testbenches were designed to detect coverage holes at simulation runtime and dynamically update test input parameters according to inference results. Custom C++ programs made use of SMILE to perform inference calculations on a Bayesian network and generate predictions for new test directives. Bayesian network structures were created using GeNIe (Graphical Network Interface) which is a graphical front-end tool that uses the SMILE engine [13].

The CDG framework was demonstrated by performing verification of two example designs: a combinational logic design and a sequential logic design. A 4-bit Wallace Tree multiplier was used to demonstrate the CDG solution for combinational logic. The following experiments were performed to demonstrate the solution for combination logic:

- **Experiment 1:** Generate all possible results of the multiplier using a Bayesian network with parameters based on previous knowledge for generating all results.

- **Experiment 2:** Generate all possible results of the multiplier using a Bayesian network of initialized parameters with no previous knowledge for how to generate results.

- Experiment 3: Generate all possible 2-result sequences for the multiplier using a Bayesian network with no previous knowledge of generating results.

- **Experiment 4:** Perform verification using a Bayesian network based on input properties and random distribution settings instead of input values.

• **Experiment 5:** Perform inference using a more complex Bayesian network to reach interesting internal states such as certain full adder carry bits being set.

The CDG solution for sequential logic was demonstrated by targeting a state machine for a vending machine. An experiment was performed using a Bayesian network to track paths through the state machine based on random test input parameters. This demonstrated how Bayesian network inference can be used to reach certain paths through the state machine more often.

Results from the experiments were compared to true random tests to show improved rate of test coverage. Details of Bayesian network inference results were also shown to allow for higher quality tests to be generated. Although the example designs used are very simple compared to the typical complex designs that warrant CDG, the use of both combinational logic and sequential logic targets demonstrate how these techniques can be applied to large variety of more complex digital designs. It is also shown that the computational complexity of Bayesian networks scales efficiently for large models, therefore allowing this technique to be feasable for complex designs.

Research has been done on other methods for achieving CDG besides using Bayesian networks. One method is Model-based CDG in which an abstract model of the design under verification is used to anticipate how much coverage will likely be reached during the construction of new tests [22]. Another approach has been to use constraint extraction as a method of creating new random input constraints from previous simulation data [23]. Research has also been done on applying inductive learning techniques to generate generic rules for closing coverage based on previous simulations [24]. One of the benefits of using Bayesian

networks for CDG is that there exists a large selection of Bayesian inference tools and a large knowledge base of Bayesian techniques due to their application to many types of problems outside of verification.

#### **1.3 OUTLINE OF THESIS**

The outline of this thesis is as follows: Chapter 2 gives an overview of verification methods for integrated circuit designs including the motivations for coverage directed generation. Chapter 3 gives an overview of Bayesian networks and how they are generally applied to various applications. This is followed by a summary of previous research that demonstrates how Bayesian network can be applied to verification of digital hardware. Chapter 4 gives a detailed description of the CDG framework implementation including testbench, Bayesian network creation, and custom software for inference calculations. Chapter 5 demonstrates the application of the CDG framework to a 4-bit Wallace Tree multiplier. Chapter 6 presents a solution for applying the CDG framework to a vending machine state machine design. Finally, conclusions for the experiments performed are discussed along with several ways the CDG solution could be improved in future work.

#### 2.0 OVERVIEW OF VERIFICATION METHODS

This chapter gives an overview of standard verification methods used in industry for digital integrated circuit designs. The challenges of functional verification are presented to demonstrate the motivation for *Coverage Directed Test Generation* (CDG). The concepts of constrained random testing and coverage analysis are discussed as well as standard testbench techniques and an overview of a basic CDG solution.

#### 2.1 VERIFICATION OF HDL DESIGNS

Technologies and methods for verifying the correctness of integrated circuits have evolved to address the increasingly large and complex chip designs being made. The majority of verification efforts occur in simulation or analysis of designs implemented in a hardware description language (HDL) such as VHDL or Verilog. This allows bugs to be discovered early in the design process, before the physical circuit layout is designed and before fabrication of the actual hardware occurs. Recent studies have shown that the majority of bugs found in integrated circuits are due to functional design errors and incorrect specifications [20]. These types of errors are introduced during HDL implementation phases.

Performing verification of HDL implementations also allows for a much more thorough verification than what can be achieved by performing tests on the final hardware. HDL design errors that go undiscovered can result in fabrication of a final product with an unknown functional bug. Such a bug may only occur under extremely rare conditions and therefore is unlikely to be discovered in basic chip-level testing. Most of today's integrated circuit designs have a state space so large that it is not possible to exhaustively test all functions under all plausible scenarios on the final chip that is manufactured. Verification is therefore accomplished on the HDL code, usually by breaking large designs into smaller functional units that are easier to manage.

One of the primary methods currently used for design verification is functional verification. Functional verification deals with simulating the HDL implementation with a series of tests in order to verify the functional requirements of the design are met. Functional verification is the primary focus of this paper and is discussed in more detail in the following section. Other methods for verifying designs include formal verification, which is done by performing an analysis of the design and applying mathematical proofs that a certain property holds true for all possible inputs. Because formal verification has many complexities, it can only be applied in certain circumstances and is therefore not always an alternative to functional verification [21].

#### 2.2 FUNCTIONAL VERIFICATION

Functional verification uses dynamic simulation to verify the functional requirements of the design under test (DUT) are met. Electronic Design Automation vendors supply tools to the industry that allow designs in an HDL to be simulated, showing the effects of input signals, internal design states, and outputs over time. The challenge to verification engineers is to

develop testbenches that simulate all the scenarios necessary to verify the functional requirements are met as well target special scenarios that may be critical to functionality or more likely to have problems.

In previous practice, it was common for testbenches to be implemented in the same hardware description language as the design (i.e., VHDL, Verilog). In more recent practice, the need for automating functional verification has led to the use of Hardware Verification Languages (HVLs) such as e [9] and SystemVerilog [19]. These languages combine aspects of traditional software programming languages with HDL capabilities. This combination allows for more powerful testbenches that can interface with a DUT while performing advanced software functions. Along with these languages, methodologies such as the Open Verification Methodology (OVM) [14] and e Reuse Methodology (eRM) [4] have been developed to provide reusable solutions and promote industry standard practices to verification engineers. The experiments conducted in this study were implemented using SystemVerilog with OVM.

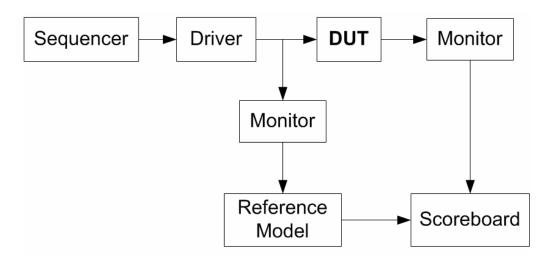

#### 2.2.1 Basic Verification Methodology

Most methodologies that have been developed for hardware verification use the basic testbench model shown in Figure 2-1. The design under test is interfaced with various testbench components that specialize on certain tasks. A sequencer is responsible for generating sequences of test inputs, usually at a high level of abstraction so it is easy to form test cases. This allows test inputs to be defined in terms of high level constructs such as packets or instructions, removing the complexities of bit-level input test cases. The driver is then responsible for translating the generated sequences into a transaction that is inputted directly to the DUT. The driver adheres to all protocols and handshaking required by the DUT input specifications [21]. A testbench will use monitors on both the inputs and outputs of the DUT to passively monitor transactions and collect data for checking. Monitors will usually only check that the DUT protocols are followed correctly and pass on actual data to other components for data checking. Input data is typically passed to a reference model to predict the expected output of the DUT. The DUT outputs are typically passed to a scoreboard which checks that the outputted data matches the predictions of the reference model. This general approach to verification has become standard in industry, with varying degrees of complexity and customization to suit verification environment needs [10]. The testbenches created for the experiments in this paper use this model.

Figure 2-1<Basic Testbench Structure

#### 2.2.2 Constrained Random Input Generation

Traditionally, engineers would write directed tests to complete the verification of a design, with each test targeting a specific requirement. The complexity of designs today make this impractical since the amount of manual labor required to write the sufficient number of test cases is unrealistic for business. Constrained random input generation has mostly replaced this practice since it removes much of the manual labor required. With relatively minimal manual effort, a random input generator can cover a vast amount of the design state space, verifying many functional requirements. Random inputs provide an additional advantage of potentially creating test scenarios that weren't considered in the verification plan. Therefore the thoroughness of the final verification may actually be better than what was planned and may make up for a weakness in the verification plan [10].

For most complex designs, it is statistically improbable and sometimes impossible to generate all the necessary scenarios randomly. This is particularly difficult for special corner cases that can only occur under rare circumstances. One of the challenges to using constrained random inputs is determining when to wait and hope the required scenarios are generated, and when to stop. Usually after stopping, one must either write directed tests to cover the remaining test scenarios, or modify the random input generators with different constraints in order to help guide the inputs into the necessary test cases. With either approach, a considerable amount of manual effort may be required if the design is complex. This is because it may not be easily apparent to an engineer what inputs are necessary to drive a design into a complex scenario of internal states.

#### 2.2.3 Functional Coverage

The use of constrained random input generation presents the challenge of determining when verification is complete. Coverage monitoring is a method of defining goals in the testbench and tracking how many of these goals have been reached. Functional coverage defines these goals to track specific functions and scenarios that need to be exercised according to the verification plan.

After running simulations, a coverage report can be generated and analyzed by an engineer to identify the coverage holes (untested scenarios). Most HVLs include constructs for defining coverage metrics in the testbench code and EDA simulation tools implement the necessary tasks of tracking and reporting coverage results. The verification engineer therefore only needs to be concerned with defining the coverage goals in the testbench code and interpreting the results from the simulation tools.

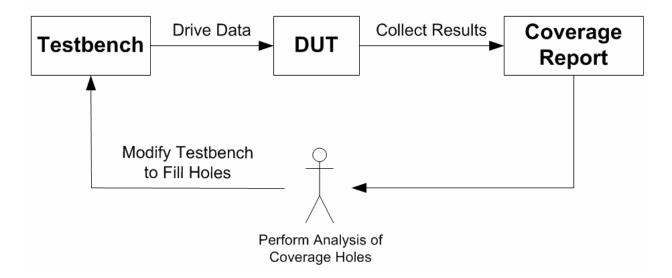

### 2.3 COVERAGE DIRECTED TEST GENERATION

Several challenges to functional verification were discussed in Section 2.1. These challenges involve how to handle the manual effort required to analyze coverage reports, perform analysis of coverage scenarios left untested, and determine how to modify the testbench to reach 100% coverage of the verification plan. For complex designs, a significant amount of manual labor may be involved in each of these tasks. Figure 2-2 shows a simplified model of this process.

Figure 2-2<Typical Process for Coverage Driven Verification

#### 2.3.1 Closing Coverage with CDG

Sometimes the solution for complete coverage is using directed tests for the missing scenarios, however this may require manual effort in both identifying the necessary inputs and creating a customized environment for verifying the scenario. It has been shown in industry that directed tests should be avoided when possible since the specialized environments for directed tests are usually not reusable. The goal of recent verification methodologies has been to move away from this practice and capitalize on reuse of verification components across design phases and projects [10].

The goal of coverage directed test generation (CDG) is to replace the manual feedback stage shown in Figure 2-2 with automated coverage analysis. This would allow software to programmatically find coverage holes, make predictions on how to reach the untested scenarios, and modify the testbench accordingly. This can be done by having adjustable parameters on the constraints for random input generation. These adjustable parameters can be modified at simulation runtime to make more desired types of inputs more likely to be generated, while reducing the chance of generating undesired inputs.

There are two benefits that can be achieved by applying CDG. The first is that unobserved scenarios can be generated more quickly and allow the verification process to complete sooner. The second benefit is that certain scenarios can be more easily tested multiple times with different input parameters. In many designs, different combinations of inputs exist that may lead to the same test scenario. Although the coverage goal may be met by only exercising one of these input combinations, there is value in exercising the other input combinations as well since there may be a hidden bug that only occurs for certain inputs [5].

#### 2.3.2 Generating Unplanned Scenarios

It is important to consider two seemingly conflicting goals when applying CDG to verification: the goal to reach 100% coverage quickly and the goal to test unplanned scenarios. At best, CDG may allow for complete coverage to be met very quickly. If coverage is closed too quickly, one of the primary values of using random inputs may be lost, which is the potential of generating test scenarios that weren't conceived in the verification plan. This is one of the primary motivations to keep random testing in a CDG solution. One could create a CDG implementation in which sets of directed tests are automatically generated to deterministically drive the scenarios that are needed for coverage. While this may allow verification to be completed, it will not test any unplanned scenarios. The high complexity of many designs increases the chance of a bug slipping through the verification process due to engineers neglecting to consider certain scenarios in the verification plan. Allowing unplanned test scenarios to be generated helps address this issue and provides a more thorough verification of the design.

The need to generate unplanned scenarios impacts how random input constraints are managed in the CDG process. At one extreme, the constraints may be too loose and coverage cannot be closed efficiently or at all. At the other extreme, the constraints may be too tight and result in essentially the same thing as inputting directed tests. The best solution may often be in finding a balance between these extremes so that complete coverage can be met in a reasonable time, while still allowing the benefits of random tests.

15

#### 3.0 OVERVIEW OF BAYESIAN NETWORKS

This chapter presents an overview of Bayesian networks. The basic principles of Bayesian networks are demonstrated using examples for modeling a domain to by analyzed. The methods for performing inference in order to generate predictions from known evidence are shown. This is followed by examples of applying these methods to functional verification for digital hardware. The basic framework for including Bayesian networks in *Coverage Directed Test Generation* (CDG) is demonstrated with details of how to model the domain and generate predictions appropriate for constrained random testing.

#### 3.1 BASIC BAYESIAN NETWORK CONCEPTS

Bayesian networks are acyclic graphs that model the direct dependence and conditional probabilities between variables in a domain. These models can be used to calculate the probabilities of certain events likely to occur. All the variables being analyzed are represented as nodes in the graph, each with a set of possible mutually exclusive states. Directed arcs are drawn between variables to show a direct dependencies between the variables. Each node in the graph also includes a conditional probability table. A *conditional probability* is the probability of an event given existing knowledge (or evidence) of the state of a related variable. The common notations for the probability of event A given the known evidence of event B is P(A | B). This

probability is also sometimes referred to as *likelihood* since it serves as a measure of how likely the event A has occurred. The conditional probability table for a node in the network lists the probability of each state for each of the possible combinations of state of the parent nodes. Such a table is also called a *joint probability table* since it provides probabilities for every scenario of parent node values [12].

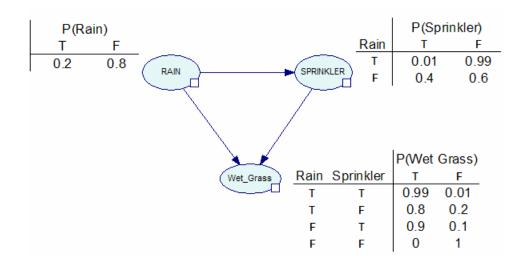

#### 3.1.1 Example Bayesian Network

Figure 3-1 shows an example of a basic Bayesian network modeling the variables likely to cause grass to be wet [2, 11]. In this model, the two variables that may cause wet grass are if it rained and if the sprinkler system had turned on. Each node in the graph represents the state of the variable (true or false), while the arcs show the direct dependencies between these variables. The grass being wet directly depends on whether it rained or the sprinkler system was running. Additionally, the sprinkler system will usually be turned off on days it rains, so the presence of rain directly influences sprinkler state.

Figure 3-1<Example Bayesian Network (Based on [2, 11])

Each node in the network contains a conditional probability table with the likelihood of each state to occur given the states of parent nodes. The probability of rain occurring, P(Rain), is defined to be 20% on a given day. The sprinkler node is directly dependent on the rain node and therefore the probability distribution table provides different values depending on the presence of rain. If the occurrence of rain is true, there is a 99% probability that the sprinkler system was turned off, vs. a 40% chance of the sprinkler running on a day it doesn't rain. The node for wet grass contains a larger probability distribution table since it depends on both of the other two nodes. A probability of the grass being wet is specified for each of the different combinations of the other node states.

#### 3.1.2 Joint Probability Calculations and Inference

The combination of information stored in each of the conditional probability tables along with the network structure can be used to calculate the joint probability distribution of the entire domain (the individual probabilities of all variable states). This is given by the following equation, referred to as the chain rule for Bayesian networks [11]. With the probability of each variable  $A_i$  given its parents  $pa(A_i)$ , the joint probability distribution for a universe of variables Uis given by the following:

$$P(U) = \prod_{i} P(A_i \mid pa(A_i))$$

This equation shows that the joint probability for all variables in a domain can be calculated as the products of individual conditional probabilities throughout the structure of the network. This allows Bayesian networks to scale efficiently to very large models with relatively low computational complexity. The joint probability of all variables can also be calculated with evidence of known states specified. This is done using Bayes' rule which shows how to calculate the likelihood of a variable A given evidence e:

$$P(A \mid e) = \frac{P(e \mid A) \bullet P(A)}{P(e)}$$

Bayes' rule also allows for the belief in this likelihood to be updated as more information is added to the network. In this context, the term P(A) is usually considered a prior probability of A(previous belief of likelihood) and P(A/e) is considered the *posterior* probability of A given the known evidence [12]. This provides a way for Bayesian networks to perform statistical inference and predict the most likely states of variables given certain evidence.

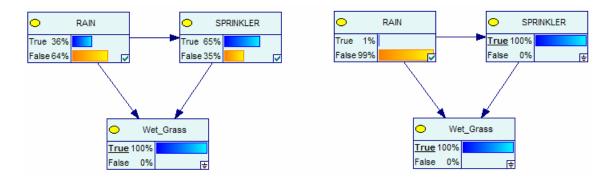

#### 3.1.3 Inference with Example Bayesian Network

The example in Section 3.1.1 demonstrated a basic Bayesian network for showing various events that may lead to grass being wet. Inference can be performed to determine the most likely cause of the wet grass. Figure 3-2 shows two versions of inference with the observed evidence that the grass is wet. With the new evidence specified, the network can update the new probability distribution of the states given the new information. The example on the left shows that there is a 65% chance the sprinkler system was running given the observation of wet grass.

Figure 3-2<Example Bayesian Network with Inference

The second example in Figure 3-2 shows additional evidence being applied to the sprinkler node, indicating the observation that the sprinkler system was in fact on. Updating the network beliefs shows a 99% probability that it did not rain. This type of result is common in Bayesian networks and is referred to as "explaining away" a state. In a model where a state may be caused by two other nodes, the added knowledge that one node was the cause greatly reduces the chance of the other node also being a cause [15]. In this case, the observation that the sprinkler system was on greatly reduces the probability that it had rained.

In the example of Figure 3-2, the inference results gave a full probability table for each of the parent nodes. Another useful calculation is the *Most Probable Explanation* (MPE), which determines the most likely state of each of the nodes and the probability of that network configuration occurring [12]. This is similar to calculating a full probability table of each node and identifying the states with the highest probability. The primary difference is the algorithms used for MPE can be calculated much faster and ensure the estimates for each of the variables agree on the common explanation. For example, a network configuration could have two variables with highest probability estimates for states that are less likely to occur together. The MPE calculation would then likely not estimate a configuration with both of these states.

Therefore MPE calculations may often be more appropriate for analysis than calculating the maximum of each individual probability table.

#### 3.1.4 Learning Network Parameters

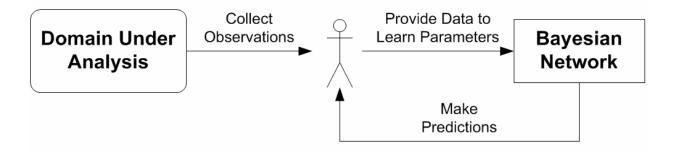

Bayesian networks are used for a variety of applications where statistical conclusions need to be made from previous observations of data. The values in the probability distribution tables can be learned from historical data using the *Expectation Maximization* (EM) algorithm. This algorithm can determine the most likely network parameters when working with complete and incomplete sets of data [12]. Figure 3-3 shows a common process for applying Bayesian networks to any domain under analysis. A person must collect observations from the domain, use this data to learn network parameters, and then query the network for probabilities of states to make predictions. As more observations are made, sets of data can be repeatedly used to relearn network parameters, gradually increasing the accuracy of the model.

Figure 3-3<Basic Model for Applying Bayesian Networks

A classic example of applying Bayesian networks is to diagnose an illness given certain symptoms. Doctors can track the history of symptoms that have been observed for patients over large periods of time, then use this information to generate a Bayesian network with potential diseases as parent nodes and the symptoms as children. Since each disease may result in different combinations of symptoms with different probabilities of each occurring, the network can combine all the data to quickly diagnose a new patient along with a probability of this diagnosis being correct. Similar to the wet grass example, this is done by setting the evidence of observed symptoms on the children and applying Bayes' rule to generate posterior probabilities of the parent nodes.

When generating Bayesian network parameters from historical data, it is important to realize that Bayesian networks can only provide probability calculations for states that have been observed. For diagnosing patients, if a doctor never observed a certain combination of symptoms occurring together, the network would be unable to predict a diagnosis. Bayesian networks can therefore be used for keeping a concise summary of past observations and making predictions based on how frequent certain observations were made.

It is also useful to consider the value of Bayesian networks over other methods of tracking trends. One could conceivably perform some of the same analysis Bayesian networks provide using simple tables of historical data. For diagnosing an illness in which one has a headache, one could simply parse through all the previous cases in which headaches were found and count which illness was the most commonly occurring cause. However this approach requires maintaining historical data in huge tables that do not scale well to large domains. If the analysis were to include 100 possible symptoms, the required table of data would have to be at least  $2^{100}$  entries. This is clearly too large to be manageable for most studies and is a realistic scenario for some applications.

22

#### 3.2 APPLYING BAYESIAN NETWORKS TO VERIFICATION

The goal in applying Bayesian networks to functional verification of chip designs is to reach a fully automated framework for CDG. The manual effort normally required in coverage driven verification (Figure 2-2) can be replaced by a Bayesian network to track previous behaviors and generate predictions to reach certain coverage goals.

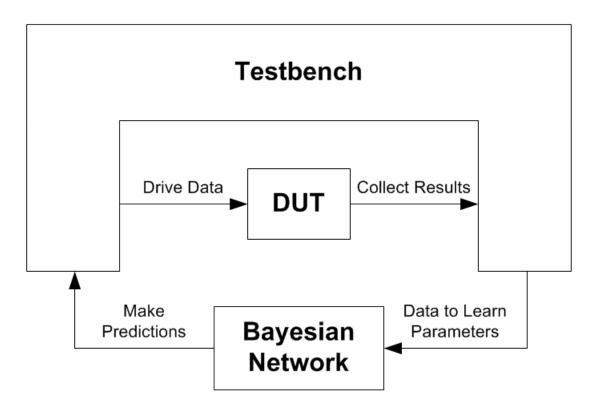

#### 3.2.1 A Framework for CDG

Figure 3-4 shows the CDG framework model with all manual effort removed from the process. The testbench collects the outputs from the design under test and provides data to the Bayesian network to learn the network parameters. The network uses this information to make MPE calculations and provide this data to the testbench. The testbench tracks the status of the coverage goals from the coverage reporting tools at simulation runtime. The testbench then determines how to modify input generation parameters to reach the coverage holes based on the MPE predictions of the Bayesian network.

Figure 3-4: Automated CDG using a Bayesian Network

In this CDG model, the testbench and Bayesian network each mutually depend on the other for information. The normal process of applying Bayesian networks (Figure 3-3) involves manually making observations from a domain and training the network with this data to be a more accurate model. Without this information, the network cannot make any predictions. The testbench fulfills this dependency by continuously providing observations of outputs and internal states from the DUT. The longer the test environment runs in simulation, the more accurate the Bayesian network will become.

The testbench depends on the Bayesian network for predictions on how to reach certain test cases. However, the network can only provide predictions on how to reach events that have already been observed. In the event that that network cannot provide a prediction, the testbench must either continue running with true random (unbiased) test inputs or "guess" the constrained random generation parameters. In either case, the hope is eventually the testbench will exercise the desired event, at which point the Bayesian network has the data needed to update the probability distribution tables. The Bayesian network is then able to make predictions for how to repeat the event in the future.

#### 3.2.2 Reaching Unobserved Events

Since the network cannot make predictions for unobserved states, it is primarily useful for generating predictions to reach an unobserved combination or sequence of states for which each individual event was previously observed. To clarify this concept, this paper will distinguish between the terms *event* and *state*. In this context, a *state* refers to a single more basic observed coverage goal of a design under test, such as a certain output or internal signal value. This could be the output of a multiply instruction, an internal carry bit being set, or the presence of a load instruction in a certain stage of a pipelined processor. The term *event* will be used to refer to a scenario made up of a combination or sequence of states.

A verification plan may include many complex coverage events that are made up of sequences or combinations of more basic states that are individually easier to observe. For example, if generating instructions for a pipelined processor, many add and branch instructions may have been observed, but never in consecutive stages of the pipeline. The Bayesian network can guide the testbench to more likely reach this event since it can make individual predictions for generating both types of instructions. Many of these types of events are also called *cross coverage* goals since they refer to certain combinations of more basic coverage goals occurring together [10].

25

The Bayesian network is also useful for learning how to recreate a certain scenario of interest. An obscure bug might be found in a design for which it is difficult to pinpoint exactly what conditions led to the error. The network can help repeat such a scenario and provide information to determine the combination of states that led to the bug being discovered.

### 3.2.3 Applying Bayesian Networks

Bayesian networks have been successfully applied to hardware verification in recent research (see [1, 5, 6, 7]). Basic methods have been presented for defining the network and generating queries to make predictions for a specific DUT. The most basic method is to manually construct the Bayesian network based on the domain knowledge of the design under test.

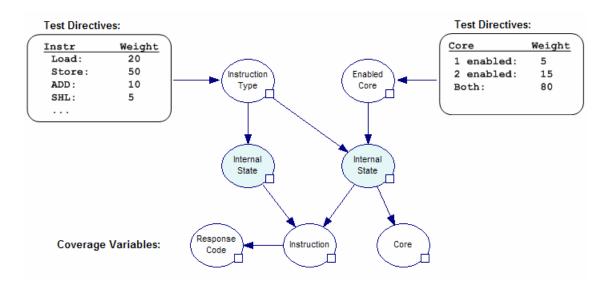

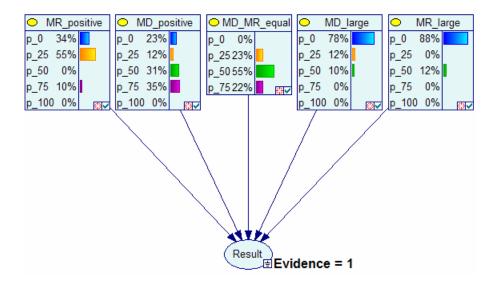

Figure 3-5 shows an example Bayesian network for a multi-core processor (see [5]). The parent nodes of the network are chosen to be the input parameters of the constrained random input generators. In this example, the input parameters are the weights to randomly generate a given CPU instruction (i.e., read, write), and the weights to determine which CPU core is active (or both). The other end of the network contains the coverage variables being tracked in the verification process. These may be used to track coverage goals such as verifying whether every type of command is tested with either core enabled and ensuring every possible response is generated.

Figure 3-5<Example Bayesian Network for Verification (Based on [5])

The internal nodes of the network represent internal states of the design under test. The arcs of the network capture the direct dependencies, starting with how the test input directives influence the internal states and how the internal states influence the outputs and coverage variables. This model also uses hidden nodes (indicated with shaded color) to model internal states that are not observed during simulation. The hidden nodes allow complex internal states that may influence coverage variables, but are not directly observable. They also serve to reduce the complexity of the Bayesian network. Once the Bayesian network is defined, data sets can be generated from simulation runs to capture each of the variable states for different test directives. The *Expectation Maximization* (EM) learning algorithm, as described in Section 3.1.4, can then be used to update the probability distribution tables of the network based on the observed test data. At this point, the network can be queried to make predictions for test inputs [5].

Using the Bayesian network in Figure 3-5 to make predictions can be done by setting evidence to the coverage variables for the state that is desired. For example, to determine how to most likely generate a load command with a certain response code and core 1 enabled, the

Instruction node would be set with evidence "load", the Core node set to "1 enabled", and the Response Code node set to evidence of the desired response code. Inference can then be performed by applying Bayes' rule as described in Section 3.1.2. The likelihood of the parent node states will then be updated given the specified evidence of the coverage variables. The resulting probability estimations on the inputs will directly indicate the best test generator directives to use. The testbench can then be automatically updated to use the test directives with the highest probability for reaching the desired coverage goal. Bayesian inference engines such as SMILE [13] implement the necessary constructs and algorithms for defining a Bayesian network and performing all of these actions.

## **3.2.4** Choosing Domain Variables for the Network

One of the challenges to applying Bayesian networks in the way described in the previous section is the requirement of applying expert knowledge to build the network structure. Although the effort of building the probability distribution tables is reduced through the EM learning algorithm, one must take care to manually build the network structure, choosing which directives, coverage variables, and internal states should be used. Previous research (see [7]) has shown that using too many input directives and coverage variables will lead to a network that is too complex to be useful. The EM learning algorithm will not work if the model is too large. Even if the model is small enough to allow learning, larger models require much larger data sets to have accuracy. Otherwise, the network may make predictions based on a few randomly coincident states that have no real correlation. Therefore the best structure usually requires an expert to determine a few input directives that have most influence toward reaching a smaller subset of coverage goals.

Another decision one must make when building the network is how to model the input parameters in the network. The more traditional way of using Bayesian networks is to use the values of the inputs as the input variables. In the case of processor instructions, the node would have a state for each instruction, tracking how often a load or store instruction occurred. For applying Bayesian networks to verification, previous research has instead used the weights of the test generation parameters rather than the actual values of the inputs. In this case, the input nodes for the processor might be the weighted percent probability of generating a load instruction [1].

Figure 3-6 shows an example of creating a simulation data set to be used for learning parameters of a Bayesian network (based on [1]). The two inputs to the data set are the settings of the test directives and the observed coverage event for each test case. The input directives are captured as the probability weight used on each test input. For example, the first three test cases used directives that the instruction had a 20% chance of being a load, a 50% chance that the instruction is store, and a 30% chance of Core 1 being enabled.

|                 | Test Dire                                   | ctives:        | Test Directiv                           | /es:               | Coverage R  | eport:                                     |      |

|-----------------|---------------------------------------------|----------------|-----------------------------------------|--------------------|-------------|--------------------------------------------|------|

|                 | Instr<br>Load:<br>Store<br>ADD:<br>SHL:<br> |                | Core<br>1 enabled<br>2 enabled<br>Both: |                    | Instr = sto | d, Core1 = (<br>re, Core1 =<br>re, Core1 = | on,  |

| Testbench Simul | lation Log:<br>P(Instr = store)             | P(Instr = Add) | P(Instr = SHL)                          | P(Core1 = enabled) | INSTR       |                                            | CORE |

|                 |                                             |                |                                         |                    | + +         |                                            |      |

| 0.2             | 0.5                                         | 0.1            | 0.05                                    | 0.3                | add         | overlow                                    | both |

| 0.2             | 0.5                                         | 0.1            | 0.05                                    | 0.3                | store       | OK                                         | 2    |

| 0.2             | 0.5                                         | 0.1            | 0.05                                    | 0.3                | load        | OK                                         | both |

| 0.5             | 0.1                                         | 0              | 0.4                                     | 0.5                | load        | OK                                         | both |

| 0.5             | 0.1                                         | 0              | 0.4                                     | 0.5                | store       | INV                                        | both |

| 0.5             | 0.1                                         | 0              | 0.4                                     | 0.5                | load        | ОК                                         | 1    |

|                 |                                             |                |                                         |                    |             |                                            |      |

Figure 3-6<Example Data Set Generation from Testbench (Based on [1])

The primary motivation for using test directives as opposed to actual input values is driven by the goals of constrained random test generation for verification. As discussed in Section 2.3.2, constrained random tests aim at providing rich data sets to reach complex scenarios (combinations of internal design states), including scenarios that were unplanned. If random test generation is constrained too tightly, the verification process may be hindered. If actual input values are used as Bayesian network nodes, there is a possibility the network will make predictions that prevent rich data sets from being generated. For the processor example, this might result in an abundance of load instructions. This result may reach the desired coverage goal quickly, however the test generator would then be overly constrained and unable to generate other instructions mixed with the load instructions, therefore reducing the chance of reaching more interesting scenarios that need to be verified [1].

An interesting aspect of using the probability distribution settings as network input states instead of the actual input values is that the Bayesian network does not maintain any knowledge of the actual generated inputs. It only tracks the input generation settings and the resulting coverage events that occurred. Therefore the inputs to the Bayesian network are considered *soft evidence* since they do not always correlate to the same observed inputs [1]. The same input directives will produce slightly different results over time, which is desired for constrained random testing. While the alternative of using actual input values in the network can be useful for generating tests, the result will be predictions that are more deterministic. This method would be similar to automatically generating directed tests. If the network is queried to generate a load instruction, it will simply give the settings that will most likely generate the instruction deterministically *every* time. Using soft evidence will instead result in predictions that are likely to generate a load instruction *most* of the time.

This chapter has presented an overview of Bayesian networks and how they can be applied to functional verification to reach a fully automated CDG test environment. The next chapter will describe the implementation of the CDG framework, including the use of existing verification tools, Bayesian network creation, testbench implementation, and custom programs to perform inference. This is followed by a series of tests in Chapter 5 to demonstrate the use of the CDG solution.

### 4.0 IMPLEMENTATION OF CDG SOLUTION

This Chapter describes the implementation details of a completely automated solution for *Coverage Directed Test Generation* (CDG) using commercially available tools and industry standards for verification. The functional verification tools will be described as well as testbench implementation and verification methodologies applied. This is followed by a description of the Bayesian inference tools used for constructing the Bayesian networks and performing inference at simulation runtime for generating test input parameters.

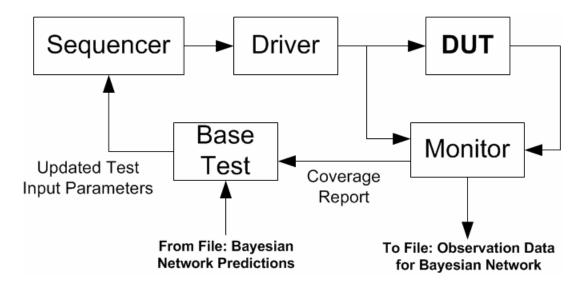

# 4.1 FUNCTIONAL VERIFICATION TOOLS AND TESTBENCH

The Questa verification platform was used for dynamic simulation of a design under test (DUT) and execution of testbenches for verifying the design [17]. Testbenches were implemented using the SystemVerilog verification language [19] along with the Open Verification Methodology (OVM) [14]. This allowed for a complex verification environment to be created relatively quickly with reusable components. The use of current industry standards for testbench design also help demonstrate how the solution can be adopted for other designs.

A different testbench was created for each of the example DUTs used for experiments, discussed further in Chapters 5 and 6. In all cases, the testbenches used the structure of Figure 4-1. This is similar to the generic testbench structure previously shown in Figure 2-1 except without a reference model and scoreboard for checking results. This was done since the purpose of these experiments was to demonstrate the relationships between test input generation and coverage closure. In all experiments, the designs were simple enough to assure no bugs existed with the initial basic tests that were performed. Therefore there was no need to actually check the outputs of the designs for correctness during the experiments. However in a real verification scenario, these components are essential to finding bugs in a DUT.

Figure 4-1: Testbench Structure for CDG Solution

The testbench used a sequencer with control variables for test generation parameters. These control variables were changed at runtime by the base test being executed to change the probability distribution for generating inputs. Initially, all control variables were set to equal values to allow a flat probability distribution for input generation. Doing this resulted in purely random (unconstrained) input generation with an equal chance for all inputs occurring. During simulation time, the base test component would periodically check the coverage report from the monitor to determine which cover points have not been reached. The base test would then change the input generation parameters of the sequencer according to the values predicted by the Bayesian network to more likely reach the needed state. Bayesian network predictions were written to a log file on a periodic basis as more data was learned from the simulation. An example log file is shown in Appendix C, which shows a list of Most Probable Explanation (MPE) calculations for each of the possible outputs of a 4-bit multiplier. When determining which inputs are needed to drive the DUT, the testbench would look up the MPE in the log file, indexed by the result that is needed.

It should be noted that this implementation requires the Bayesian network to generate MPE calculations for *all* anticipated coverage states in advance on a routine basis. A more efficient solution can likely be achieved by having the Bayesian network generate only a single MPE calculation on demand, as needed by the testbench at runtime. This will be discussed more in Chapter 7 as part of the conclusions and future work.

The monitor of the testbench also logged in a file the outputs (and some internal values) of the DUT along with the corresponding input parameters that led to those outputs. This log consisted of a tab delimited listing with each column corresponding to one of nodes of the Bayesian network. The resulting data sets were used by the Bayesian inference engine to learn network parameters. During simulation runtime the testbench would continue to add results to the log, providing a continuously growing data set. This allowed the Bayesian network to relearn network parameters periodically, each time becoming a more accurate model of the domain.

34

# 4.2 BAYESIAN NETWORK TOOLS

The tools used for implementing Bayesian networks and performing inference consisted of the inference engine SMILE (Structural Modeling, Inference, and Learning Engine) and the graphical front-end tool GeNIe (Graphical Network Interface) [13]. Both tools are developed by the Decision Systems Laboratory at the University of Pittsburgh and have over ten years of development and field testing. Figure 4-2 shows the general structure of the CDG solution and how GeNIe and SMILE were integrated into the verification environment.

Figure 4-2: CDG Solution with GeNIe and SMILE

GeNIe was used as a graphical editor to manually create the structure of the Bayesian networks. This included the node names, names of states for each node, and arcs for showing direct dependencies between nodes. GeNIe also allows one to manually define probability distribution tables, set evidence to nodes, perform inference, and analyze results through graphs. The tool can also parse logs of data and apply the Expectation Maximization (EM) algorithm for learning network parameters. Therefore GeNIe was also used for doing some basic stand-alone inference calculations as initial experiments and examples (shown in Chapters 5 and 6). Networks built in GeNIe were saved to files which could be opened during simulation runtime of the testbench.

The inference engine SMILE is used by GeNIe for network definition and inference calculations. This engine is also available as a C++ Application Programming Interface (API), allowing custom programs to be created for building Bayesian networks and performing specific inference calculations. The CDG solution used custom C++ programs with the SMILE API to perform the following operations:

- Open the Bayesian network file previously created in GeNIe

- Open testbench log files and learn network parameters from the data by applying the Expectation Maximization (EM) learning algorithm.

- Set evidence to coverage variable nodes for anticipated coverage states.

- Perform Most Probable Explanation (MPE) calculations for test input parameters given specified evidence.

- Generate a log file of all MPE calculations for each anticipated coverage goal. This log file was used by the testbench to determine how to change test input parameters.

- Save the Bayesian network with updated parameters back to a file.

When creating the Bayesian networks in GeNIe, the network parameters (probability distribution tables) were not specified. This ensured that the initial state of the networks at the beginning of testbench execution had no previous knowledge of the domain other than network structure. Therefore, no predictions could be generated by the inference engine at the start of simulation ensuring all predictions were based on newly observed events. In the event the testbench required predicted test inputs from the Bayesian network that were not available, the testbench would simply continue using flat distribution settings (unconstrained random inputs).

An important consideration when applying GeNIe and SMILE to the CDG solution was how to represent data. These tools require discrete data (as opposed to continuous data) for many operations. Discrete data in these tools are interpreted as strings, with each string corresponding to a different discrete state. For example, a 2-state node in the network could simply have the states "True" and "False", or a 3-state node could have values "small", "medium", and "large". Integer or floating point values are interpreted as continuous data by the inference tools and require discretization. For this reason, all values logged from the testbench were recorded as strings, with each string corresponding exactly to state names used when drawing the Bayesian network in GeNIe.

The SMILE API includes functionality to automatically parse tab delimited data files and correlate the columns and values to network parameters for learning. Testbench logs used headings for each column corresponding exactly to the string used when naming nodes in GeNIe. This ensured that when the network was opened for learning parameters, SMILE would correctly correlate the columns of testbench data to each node of the network, with all logged string values corresponding directly to a node state. To ensure numeric data was interpreted as strings, letter prefixes were added to the numbers for logging. For example, a positive 8 was logged as "p\_8"

and a negative 8 as "n\_8". In some cases binary values were used in the form of "b\_00110". Defining all these strings in the Bayesian network ahead of time and using the same convention for testbench logs ensured SMILE could correctly correlate all data from the testbench to Bayesian network parameters.

This chapter presented a detailed description of the CDG solution using Questa for dynamic simulation and SMILE for Bayesian inference calculations. Chapters 5 describes several experiments that were performed to see how well the CDG solution works for a basic combinational logic design. This is followed by experiments for applying the CDG solution to a sequential logic design in Chapter 6.

# 5.0 BAYESIAN NETWORK FOR A COMBINATIONAL LOGIC DESIGN

This chapter presents a series of experiments that were performed by applying the solution for Coverage Directed Test Generation (CDG) described in Chapter 4 to a basic combinational logic design. Section 5.1 describes a 4-bit Wallace Tree multiplier that was used as an example design under test (DUT). Section 5.2 describes the Bayesian network used along with basic examples of inference being performed to generate test input parameters. Section 5.3 gives descriptions of four experiments and the results of applying CDG to the multiplier. The experiments performed were the following:

- **Experiment 1:** Verify the Bayesian network correctly learned network parameters by generating all possible results randomly and then using the network to predict inputs to recreate the previously observed results.

- Experiment 2: Verify the Bayesian network can correctly relearn network parameters at simulation runtime by starting simulation with unlearned parameters and periodically relearning from new testbench outputs.

- Experiment 3: Generate all possible 2-result sequences for the multiplier using a Bayesian network with no previous knowledge of generating results.

- **Experiment 4:** Perform verification using a Bayesian network based on input properties and random distribution settings instead of input values.

• **Experiment 5:** Perform inference using a more complex Bayesian network to reach interesting internal states such as certain full adder carry bits being set.

All simulations were performed on a computer with an Intel Xeon E5345, 2.33 GHz processor. In most cases the state space of coverage goals was small enough that simulations only required 1 to 2 minutes to complete the coverage goal, with exception to experiment 3 which used more challenging coverage goal and took as long as 20 minutes to complete.

# 5.1 OVERVIEW OF THE WALLACE TREE MULTIPLIER

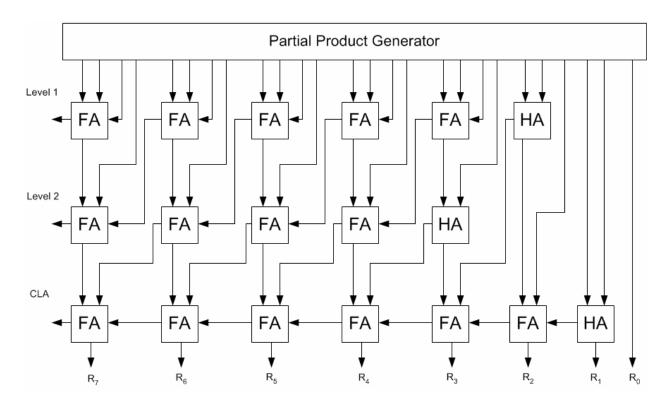

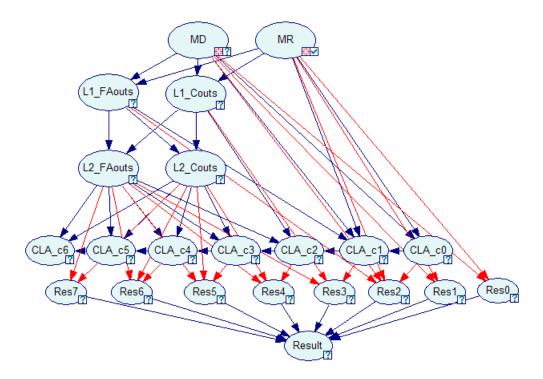

A Wallace Tree multiplier was chosen as an initial example DUT since it is a well known logic design with practical applications while being relatively easy to understand [8]. The Wallace-Tree design also allows for interesting coverage goals to be defined since there are many internal states. Figure 5-1 shows the architecture of a 4-bit Wallace Tree multiplier. Two signed 4-bit numbers are multiplied to produce a signed 8-bit result.

The Wallace Tree inputs are all the partial products of the multiplicand and multiplier. The partial products are formed by performing a logic AND between all pairs of bit positions between the multiplier and multiplicand. For a 4-bit multiplier, these partial products are then added through three levels of full adders (FA) and half adders (HA), as shown in Figure 5-1. The final stage of adders forms a carry-look-ahead adder, producing the final 8 bits of the result. Each FA and HA has an output and a carry out. Verification coverage goals were defined to exercise all possible results from the multiplier, as well as some special scenarios for generating all 2-pair sequences of results and all level 1 FA carry outs being 1.

Figure 5-1: 4-bit Wallace Tree Multiplier (based on [18])

## 5.2 A SIMPLE BAYESIAN NETWORK

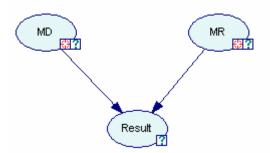

The simplest Bayesian network that can be used for the Wallace Tree is shown in Figure 5-2. This network has only three nodes: the value of the multiplier (MR), the value of the multiplicand (MD), and the result. In this scenario, the coverage goal is simplified to observing all possible results of the multiplier. At this high a level of observation, it is easy to see all direct data dependencies are accounted for since only the multiplier and multiplicand determine the result of the multiplier.

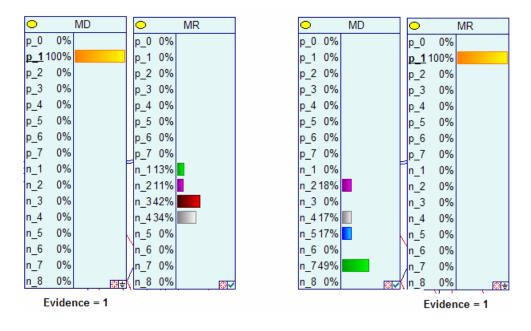

Figure 5-2: Basic 3-Node Bayesian Network

The MD and MR nodes each have 16 states corresponding to the multiplier input values -8 through 7. The result node has 256 states to model all possible 8-bit values, however many of these are impossible states since the only outputs can be the multiplication of two numbers between -8 and 7. Of the 256 states, only 60 are valid results that can be generated from the multiplier.

#### **5.2.1** Inference with Simple Network

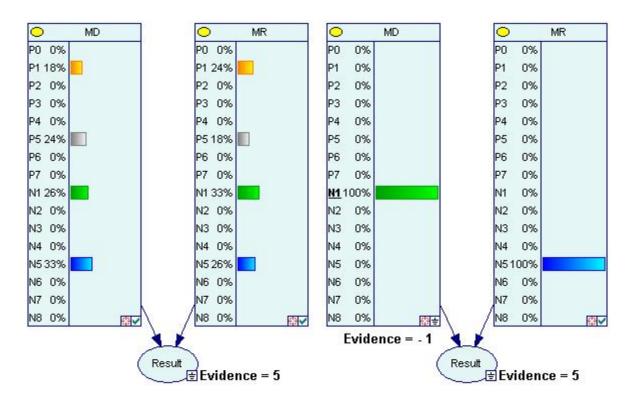

The Bayesian network for the Wallace Tree was first defined manually using GeNIe (Graphical Network Interface), which is a graphical front-end and inference tool for working with Bayesian networks [13]. A testbench was created in SystemVerilog to test a Wallace Tree multiplier implemented in Verilog. The testbench generated a series of random inputs to the DUT and collected all results and internal states of interest. This data was then used by GeNIe which applied the EM algorithm for learning network parameters. The initial scenario used 1000 test cases to ensure a large abundance of data covering all possible input scenarios.

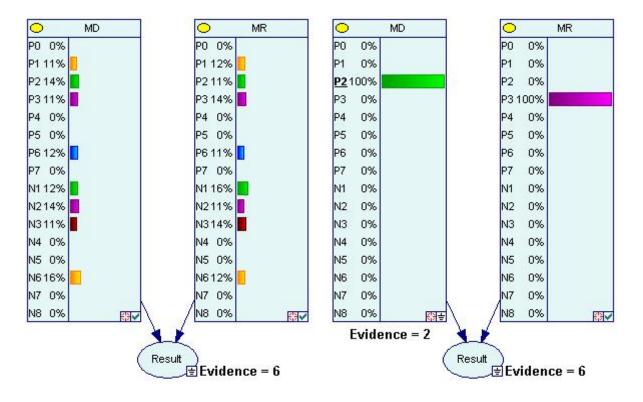

After the parameters of the Bayesian network were learned, inference was performed by querying the network for different coverage goals. Figure 5-3 shows two instances of the

network with MD and MR nodes expanded to show bar graphs of the possible states. In both cases, the network was queried for which test inputs will most likely produce a result of five.

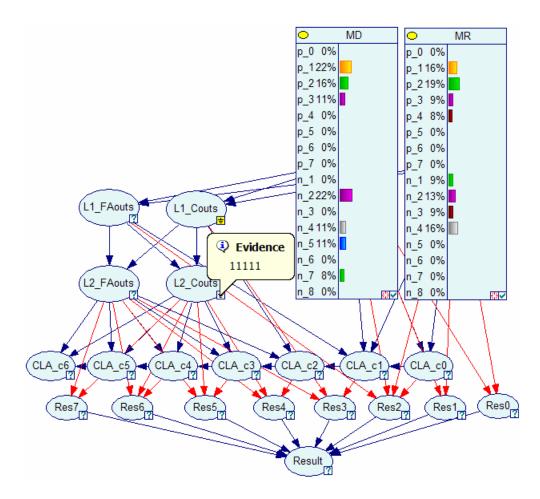

Figure 5-3: Inference with Basic Bayesian Network

The Bayesian network was queried by setting the desired output as evidence on the result node. The belief values were then updated by GeNIe to predict the most likely inputs that will lead to that result. The first example in the left of Figure 5-3 shows the network successfully determined that certain combinations of 1, 5, -1, and -5 on each input will likely produce a 5. With the goal of producing this test scenario, one can then use this information to change the testbench input generation parameters accordingly. In this case, the parameters can be modified so there is about 25% chance of producing positive and negative 1's and 5's, while other values have no chance of being generated. While the first results will quickly lead to the desired test output of a 5, it may not occur immediately since the network may multiply two 1's or two 5's. There is no information about what combination of inputs will produce the desired output. Because the different ways of producing a 5 occurred with similar frequencies in the test data, the network distributed the certainty of producing this result across all the possible inputs that can lead to that result.

The second result in Figure 5-3 shows the result of setting additional evidence on the MD node to -1. Updating the beliefs, the network then determines the only possible way to produce a 5 with MD of -1 is with an MR of -5. This is an example of the network using a conditional dependency relationship to "explain away" the state of the other node, as previously described in Section 3.0.

Figure 5-4 shows another scenario with a coverage goal of producing a result of six. The network successfully determined the eight possible inputs on each node that most likely produce that value. However, since there are many more ways to produce a 6 than a 5, the certainty of producing that result is smaller. The inputs that occurred most often in the test data were given a slightly higher probability. One might update the testbench with 10% - 14% chance of generating those inputs and many undesired test cases may be generated before producing a 6. Similar to the previous test case, the second result shows applying an evidence of 2 to MD resulted in 100% certainty that an MR value of 3 would produce a 6.

Figure 5-4: Inference Results with More Predictions

As discussed in Section 3.1.3, this network used actual input values rather then the test directives that generate these values, resulting in predictions that were deterministic. Querying the network for the inputs that would lead to a 5 would produce a Most Probable Explanation (MPE) result that would produce a -1 and a -5, guarantying a 5 would be generated every time with these settings. In this context, the Bayesian network is essentially generating a directed test to produce a desired result.

# 5.3 CDG APPLIED TO WALLACE TREE MULTIPLIER