# COLLISION RESOLUTION IN ISO 18000-6C PASSIVE RFID COMMUNICATION

by

# Yuan Sun

B.S. in Electrical Engineering, Southeast University, China, 2004M.S. in Electrical Engineering, Southeast University, China, 2007

Submitted to the Graduate Faculty of Swanson School of Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy

University of Pittsburgh

2009

# UNIVERSITY OF PITTSBURGH

This dissertation was presented

by

Yuan Sun

It was defended on

September 4th, 2009

and approved by

Ching-Chung Li, Professor, Electrical and Computer Engineering Dept.

J.T.Cain, Professor Emeritus, Electrical and Computer Engineering Dept.

Joseph Kabara, Assistant Professor, Information Science Dept.

Ronald G. Hoelzeman, Professor, Electrical and Computer Engineering Dept.

Zhi-Hong Mao, Assistant Professor, Electrical and Computer Engineering Dept.

Dissertation Director: Marlin H.Mickle, Professor, Electrical and Computer Engineering Dept.

Copyright © by Yuan Sun

2009

# **COLLISION RESOLUTION IN ISO 18000-6C PASSIVE RFID COMMUNICATION**

Yuan Sun, PhD

University of Pittsburgh, 2009

According to the ISO 18000-6C passive RFID standard, the tags rely on limited energy harvested from the reader carrier wave rather than an internal power supply to perform logic functions and backscatter signals. The reader receives the tag's backscattered response, and then decodes the tag signal in order to access the tag information. However, in a tag intensive environment, when multiple tags receive the reader Query command and respond simultaneously, the reader may receive multiple responses giving what is termed a collision signal. Because the collision signal violates the encoding as specified in the standard, the reader is not able to decode it using its built-in circuitry that is designed for non-colliding tag responses. Therefore, the reader fails to complete the inventory for tags in the field in this case, which degrades the overall performance of the passive RFID system requiring retries.

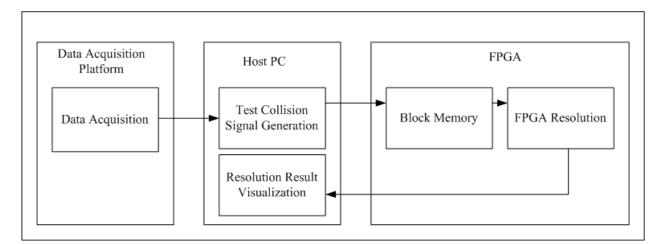

This research focuses on resolving the two-tag collision signal with extensions to more tags. A preliminary tag data acquisition system has been developed along with an ISO 18000-6C conformance test platform, which consists of an FPGA-based software defined reader. The collision signal is obtained from the data acquisition system and processed by the FPGA in real time. Two types of collision resolving algorithms based on phase and amplitude characteristics of the collision signal are developed and simulated using LabVIEW on a host PC and then

realized with a National Instruments FPGA development board NI5640R. These two algorithms deal with the two-tag collision situation with and without a distinct phase shift individually, and they can be unified. As an extension to multiple tag collision resolution, an advanced statistical signal processing method using Independent Component Analysis (ICA) is researched for the three-tag collision situation. The ICA simulation is performed using LabVIEW on the host PC, and then implemented on the target FPGA development board. Performance analysis and comparison are presented to prove the efficiency and timing conformance of the proposed methods to the standard. Finally, the collision signals acquired from moving tags are resolved using the amplitude mapping method to prove the method compatibility on dynamic tags.

# TABLE OF CONTENTS

| PRI | EFAC | CE    |                                                       | XVI |

|-----|------|-------|-------------------------------------------------------|-----|

| 1.0 |      | INTR  | ODUCTION                                              | 1   |

|     | 1.1  | F     | BACKGROUND OF THE PROBLEM                             | 4   |

|     |      | 1.1.1 | The Link Timing of ISO 18000-6C Standard              | 4   |

|     |      | 1.1.2 | The Anti-Collision Mechanism in ISO 18000-6C standard | 6   |

|     |      | 1.1.3 | ISO 18000-6C Tag Baseband Encoding                    | 7   |

|     | 1.2  | S     | TATEMENT OF THE PROBLEM                               | 9   |

|     |      | 1.2.1 | Overview                                              | 9   |

|     |      | 1.2.2 | Dissertation Work                                     | 12  |

| 2.0 |      | DATA  | ACQUISITION PLATFORM                                  | 15  |

|     | 2.1  | F     | PLATFORM ARCHITECTURE                                 | 17  |

|     |      | 2.1.1 | Platform Hardware                                     | 17  |

|     |      | 2.1.2 | Platform Software                                     | 18  |

|     | 2.2  | S     | TANDARD REALIZATION AND DATA ACQUISITION              | 20  |

|     |      | 2.2.1 | Standard Realization                                  | 20  |

|     |      | 2.2.2 | Data Acquisition with the Platform                    | 25  |

| 3.0 |      | TAG   | COLLISION SIGNAL CHARACTERISTICS ANALYSIS             | 29  |

|            | 3.1                                           | TAG COLLISION SIGNAL CHARACTERISTICS               |

|------------|-----------------------------------------------|----------------------------------------------------|

|            | 3.2                                           | DATA PREPROCESSING                                 |

| 4.0        |                                               | <b>RESOLUTION METHOD I: DIRECT EDGE LOCATING40</b> |

|            | 4.1                                           | TAG RESPONSE FRAME ARCHITECTURE42                  |

|            | 4.2                                           | ALGORITHM DESCRIPTION4                             |

|            | 4.3                                           | ALGORITHM SIMULATION40                             |

|            | 4.4                                           | ALGORITHM IMPLEMENTATION50                         |

| 5.0        |                                               | <b>RESOLUTION METHOD II: AMPLITUDE MAPPING62</b>   |

|            | 5.1                                           | ALGORITHM DESCRIPTION                              |

|            | 5.2                                           | ALGORITHM SIMULATION67                             |

|            | 5.3                                           | ALGORITHM IMPLEMENTATION71                         |

|            | 5.4                                           | SOLUTION UNIFICATION70                             |

|            |                                               |                                                    |

| 6.0        |                                               | TAG DYNAMICS80                                     |

| 6.0        | 6.1                                           | TAG DYNAMICS                                       |

| 6.0<br>7.0 | 6.1                                           |                                                    |

|            | 6.1<br>7.1                                    | MOVING TAG COLLISION SIGNAL ANALYSIS85             |

|            |                                               | MOVING TAG COLLISION SIGNAL ANALYSIS               |

|            | 7.1                                           | MOVING TAG COLLISION SIGNAL ANALYSIS               |

|            | 7.1<br>7.2                                    | MOVING TAG COLLISION SIGNAL ANALYSIS               |

|            | 7.1<br>7.2                                    | MOVING TAG COLLISION SIGNAL ANALYSIS               |

|            | 7.1<br>7.2                                    | MOVING TAG COLLISION SIGNAL ANALYSIS               |

|            | <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | MOVING TAG COLLISION SIGNAL ANALYSIS               |

| 8.0   | DATA WHITENING |  |

|-------|----------------|--|

| 9.0   | CONCLUSION     |  |

| 10.0  | FUTURE WORKS   |  |

| APPEN | NDIX A         |  |

| BIBLI | OGRAPHY        |  |

# LIST OF TABLES

| Table 1. Tag Turn-around Time at Typical BLF      | 5  |

|---------------------------------------------------|----|

| Table 2. Possible Voltage Levels in Collision     |    |

| Table 3. Tag Response Statistics (Manufacturer 1) |    |

| Table 4. Tag Response Statistics (Manufacturer 2) |    |

| Table 5. Direct Edge Locating Algorithm           | 46 |

| Table 6. FPGA Resources Utilization               | 60 |

| Table 7. Amplitude Mapping Algorithm              |    |

| Table 8. Pseudo code for Mapping Process          | 67 |

| Table 9. FPGA Resources Utilization               | 74 |

| Table 10. FastICA algorithm                       | 97 |

| Table 11. FPGA Resources Utilization              |    |

| Table 12. FPGA Resources Utilization              |    |

# LIST OF FIGURES

| Figure 1. Passive RFID Collision Situations                 | 2  |

|-------------------------------------------------------------|----|

| Figure 2. Tag States Transition                             | 4  |

| Figure 3. The Three Step Handshake                          | 6  |

| Figure 4. Query Command and Tag Response Formation          | 7  |

| Figure 5. FM0 Baseband Basis Function                       | 8  |

| Figure 6. Miller Baseband Basis Function                    | 8  |

| Figure 7. Generalized Tag Baseband Formation                | 9  |

| Figure 8. Selective Tag Access with Collision Resolution    | 11 |

| Figure 9. Simultaneous Tag Access with Collision Resolution | 11 |

| Figure 10. Collision Resolution Timing Strategy             | 12 |

| Figure 11. Platform Hardware Architecture                   | 18 |

| Figure 12. Platform Software Architecture                   | 20 |

| Figure 13. ASK Modulation Block                             | 21 |

| Figure 14. FIR Filter Magnitude and Phase Response          | 22 |

| Figure 15. Signal Smoothing with 8-order FIR Filter         | 22 |

| Figure 16. Decode Module Architecture                       | 24 |

| Figure 17. Handshake Processing Unit24                                              |

|-------------------------------------------------------------------------------------|

| Figure 18. Acquired Inventory Round25                                               |

| Figure 19. Test Control Panel27                                                     |

| Figure 20. Waveform Analysis Module28                                               |

| Figure 21. Tag Positioning (Vertical Direction)30                                   |

| Figure 22. Tag Positioning (Horizontal Direction)30                                 |

| Figure 23. Acquired Collision Signal31                                              |

| Figure 24. Linear Additive Model of Tag Responses                                   |

| Figure 25. RF Front End Connection with Circulator33                                |

| Figure 26. Accumulated Phase Shift35                                                |

| Figure 27. Tag Phase shift vs. BLF (Manufacturer 1 and Manufacturer 2)              |

| Figure 28. Tag Phase shift Percentage in Symbol duration vs. BLF (Manufacturer 1)37 |

| Figure 29. Tag Phase shift Percentage in Symbol duration vs. BLF (Manufacturer 2)37 |

| Figure 30. the effect of a 10-order median filter38                                 |

| Figure 31. Median Filter order vs. Processed Signal SNR                             |

| Figure 32. Superposition of Two Formation-0 Symbols41                               |

| Figure 33. Superposition of Two Formation-1 Symbols41                               |

| Figure 34. Superposition of Formation-0 Symbol and Formation-1 Symbol42             |

| Figure 35. Tag Response Frame Architecture42                                        |

| Figure 36. Tag Response Preamble in FM044                                           |

| Figure 37. Tag Response Preamble in Miller Subcarrier44                             |

| Figure 38. Ending Location of Preambles in Collision45                              |

| Figure 39. Implementation of the Algorithm using FSM47                              |

| Figure 40. State Transition of the FSM                                |

|-----------------------------------------------------------------------|

| Figure 41. The Running Mean Calculation49                             |

| Figure 42. The Differentiation of Collision signal50                  |

| Figure 43. Collision Signal Edge Detection (LabVIEW Code Segment)51   |

| Figure 44. The Differentiation of Collision signal51                  |

| Figure 45. Two Tag Responses53                                        |

| Figure 46. Collision Signal and its Differentiation54                 |

| Figure 47. Searching Range Overlap55                                  |

| Figure 48. Miss Arbitration                                           |

| Figure 49. Verification Flow of Algorithm Implementation57            |

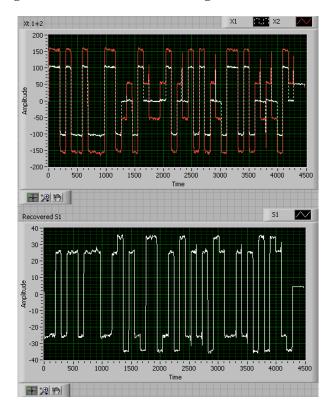

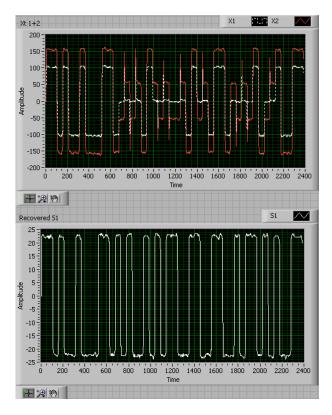

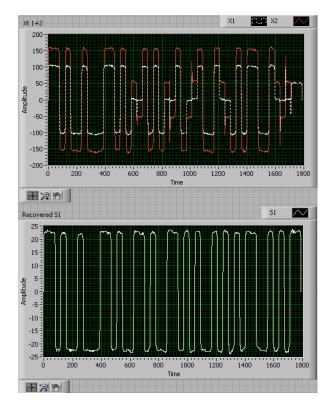

| Figure 50. Resolution Result When BLF=64 kHz58                        |

| Figure 51. Resolution Result When BLF=128 kHz58                       |

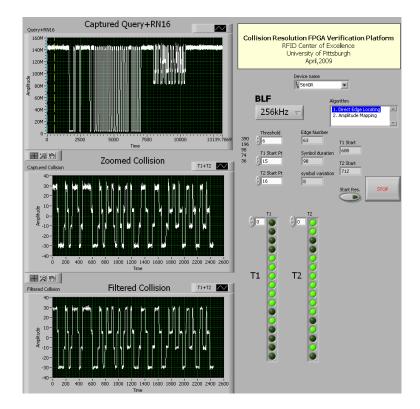

| Figure 52. Resolution Result When BLF=256 kHz59                       |

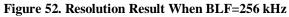

| Figure 53. Resolution Result When BLF=341 kHz59                       |

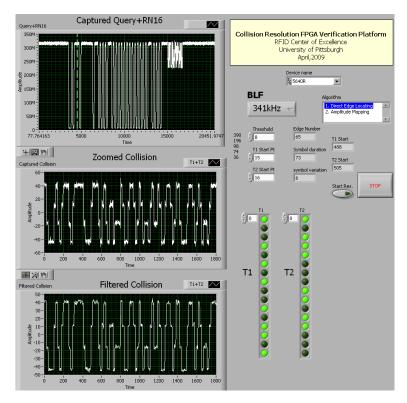

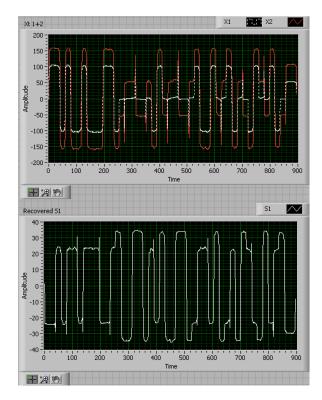

| Figure 54. Resolution Result When BLF=682 kHz60                       |

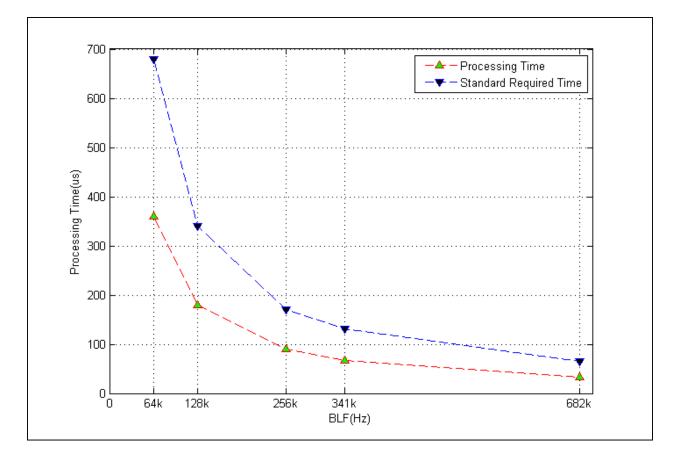

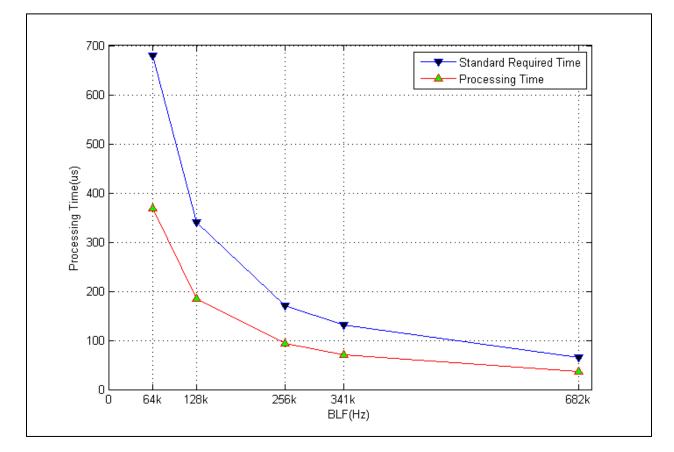

| Figure 55. Processing Time vs. Standard Required Time61               |

| Figure 56. Edge Ambiguity63                                           |

| Figure 57. Collision Patterns                                         |

| Figure 58. Example Superposition of Tag Responses without Phase shift |

| Figure 59. Implementation of the Algorithm using FSM68                |

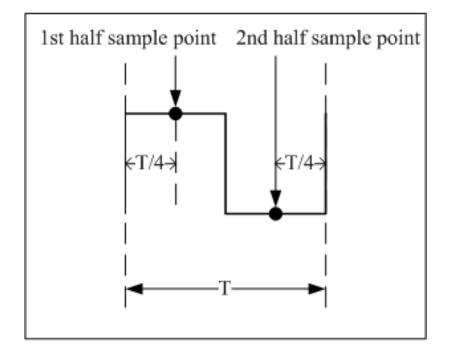

| Figure 60. Symbol Sampling Point68                                    |

| Figure 61. State Transition of FSM69                                  |

| Figure 62. Two Tag Responses70                                        |

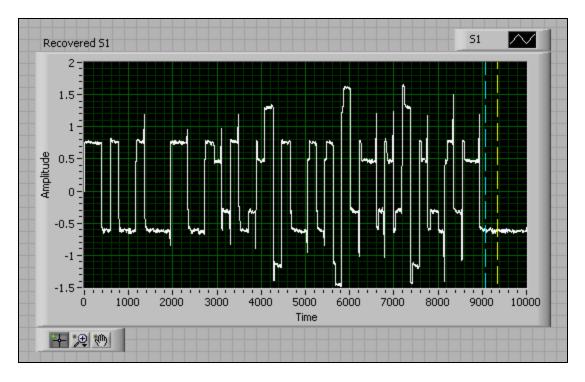

| Figure 63. Collision and Resolved data (Simulation)71       |

|-------------------------------------------------------------|

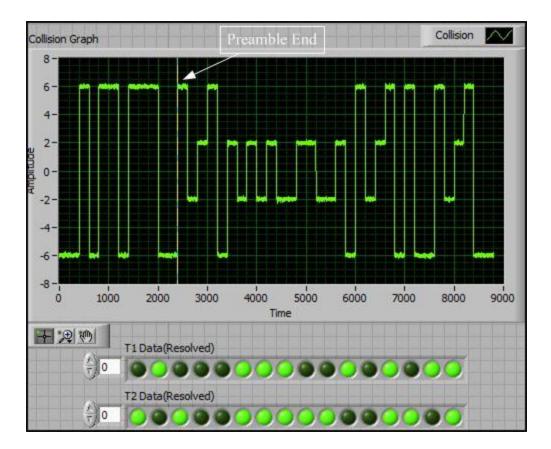

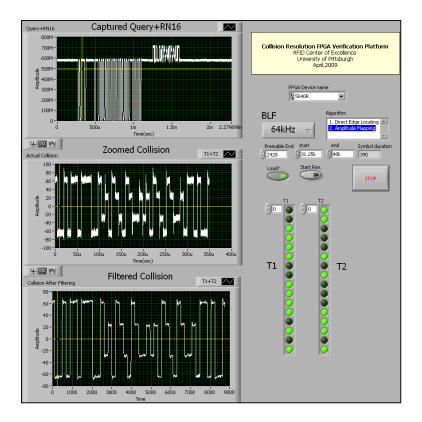

| Figure 64. Collision and Resolved data (BLF=64 kHz)72       |

| Figure 65. Collision and Resolved data (BLF=128 kHz)72      |

| Figure 66. Collision and Resolved data (BLF=256 kHz)73      |

| Figure 67. Collision and Resolved data (BLF=341 kHz)73      |

| Figure 68. Collision and Resolved data (BLF=682 kHz)74      |

| Figure 69. Processing Time vs. Standard Required Time75     |

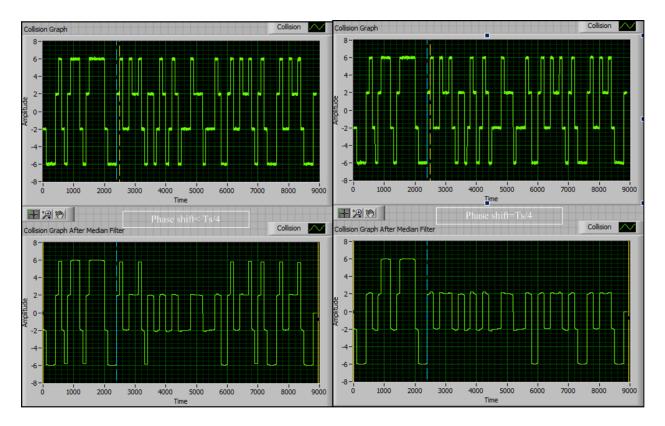

| Figure 70. The Effect of Median Filter77                    |

| Figure 71. Algorithm Comparison78                           |

| Figure 72. Effect of the Limitation of Phase Shift79        |

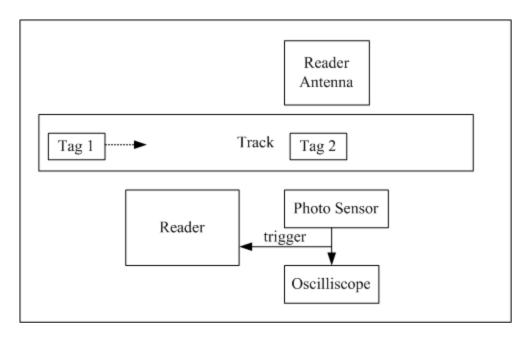

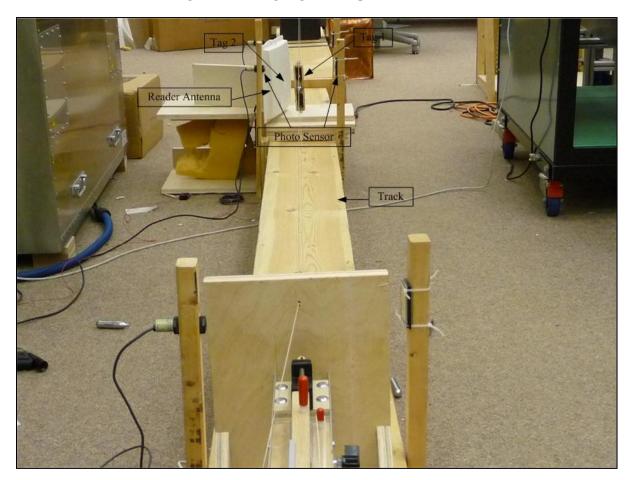

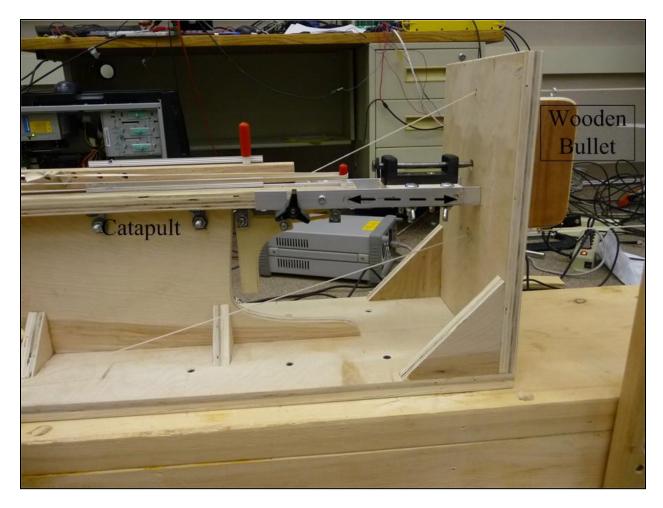

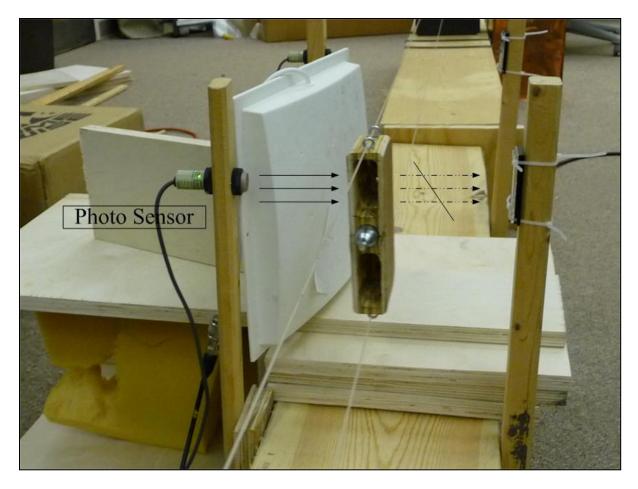

| Figure 73. Moving Tag Data Acquisition Platform81           |

| Figure 74 Maring Tag Data Acquisition Distance (Disture)    |

| Figure 74. Moving Tag Data Acquisition Platform (Picture)81 |

| Figure 74. Moving Tag Data Acquisition Platform (Picture)   |

|                                                             |

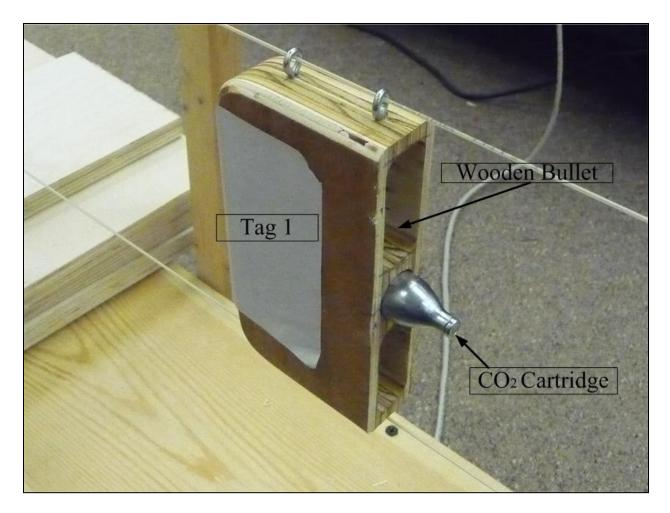

| Figure 75. Wooden Bullet82                                  |

| Figure 75. Wooden Bullet                                    |

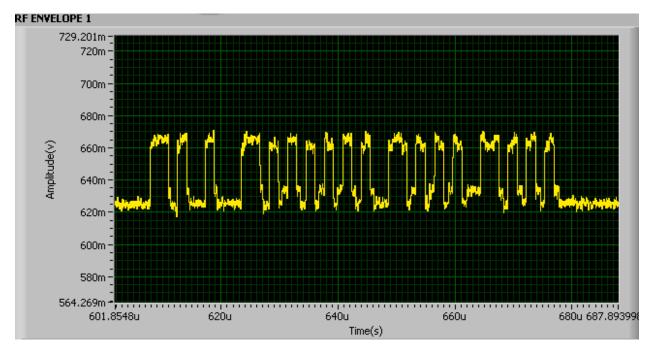

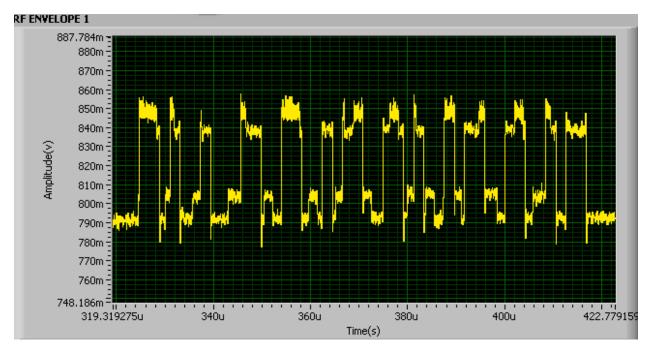

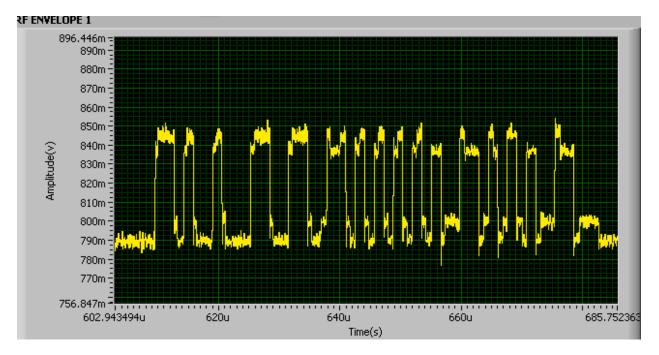

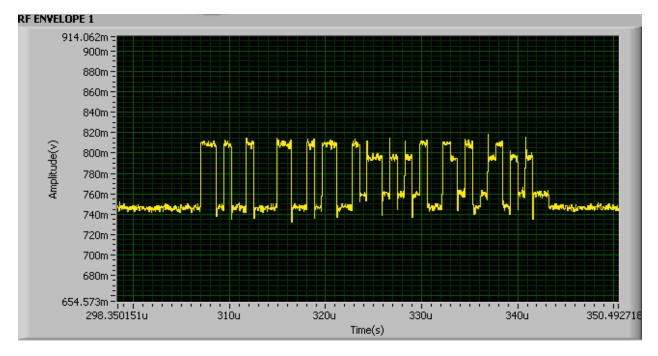

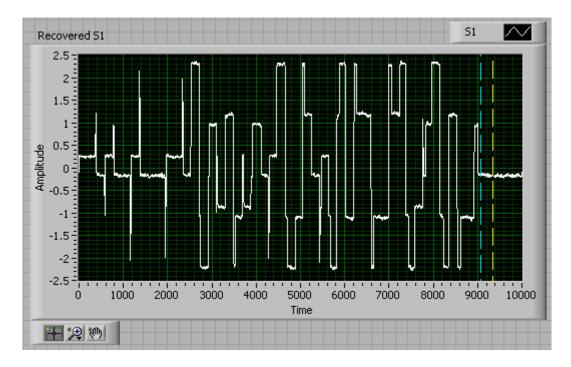

| Figure 86. 2-tag Collision Signal (Speed=25miles/hour, BLF=64 kHz)                   | 38             |

|--------------------------------------------------------------------------------------|----------------|

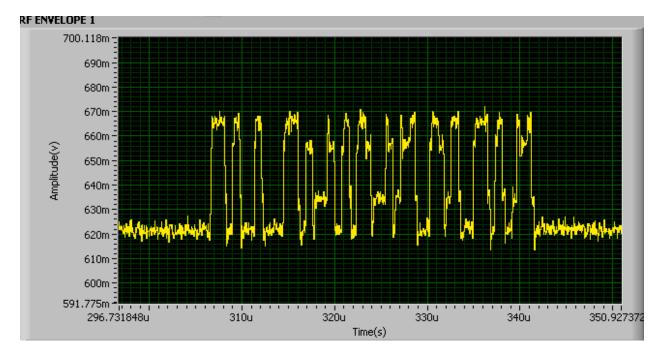

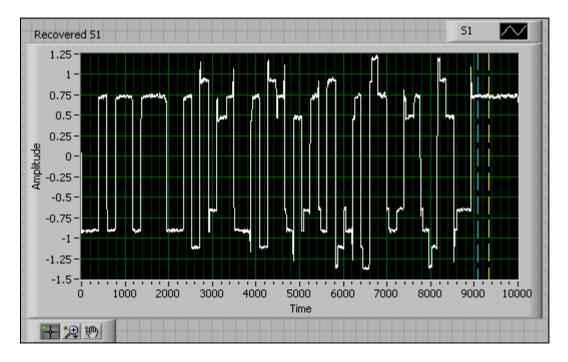

| Figure 87. 2-tag Collision Signal (Speed=25miles/hour, BLF=128 kHz)                  | <u> 39</u>     |

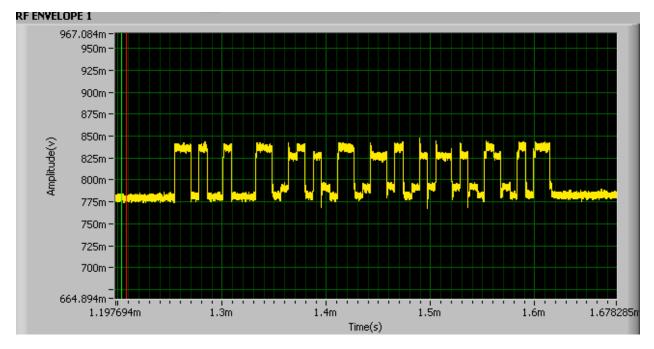

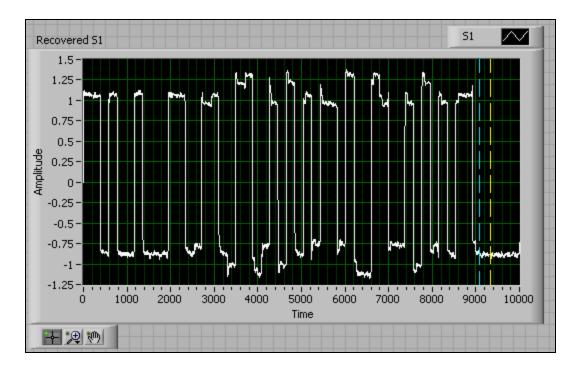

| Figure 88. 2-tag Collision Signal (Speed=25miles/hour, BLF=256 kHz)                  | <b>39</b>      |

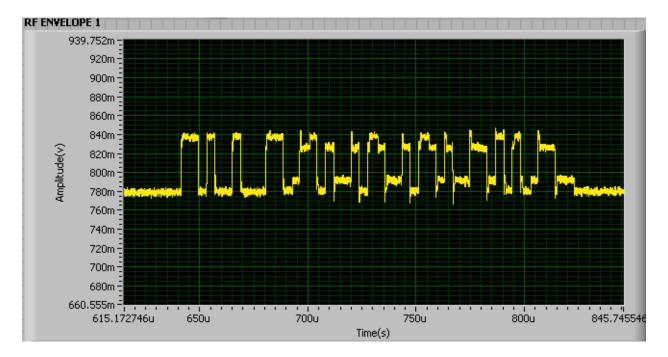

| Figure 89. 2-tag Collision Signal (Speed=25miles/hour, BLF=341 kHz)                  | <del>)</del> 0 |

| Figure 90. 2-tag Collision Signal (Speed=25miles/hour, BLF=682 kHz)                  | <del>)</del> 0 |

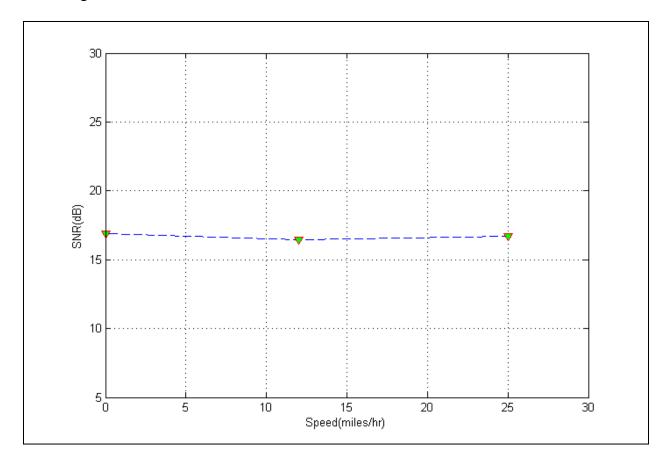

| Figure 91. Average Signal-to-Noise Ratio Comparison                                  | <b>91</b>      |

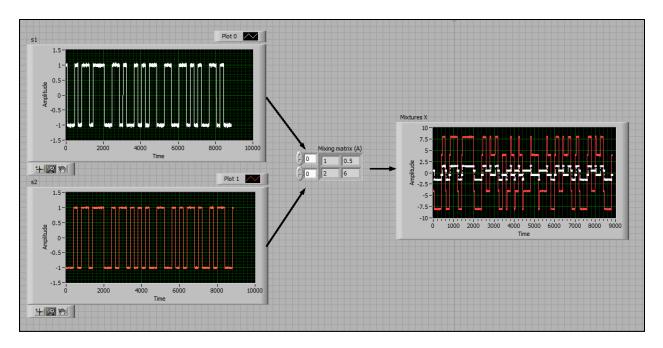

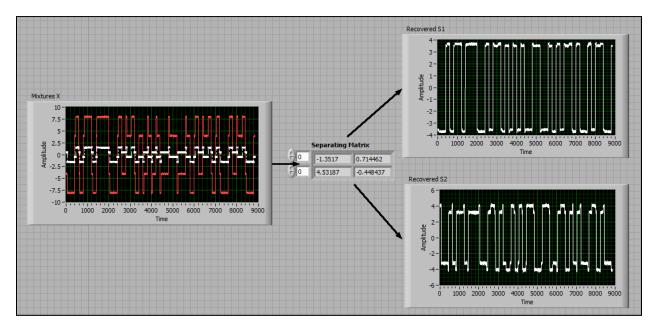

| Figure 92. Simulated Tag Signal Mixing                                               | <del>)</del> 9 |

| Figure 93. Resolution Result                                                         | <del>)</del> 9 |

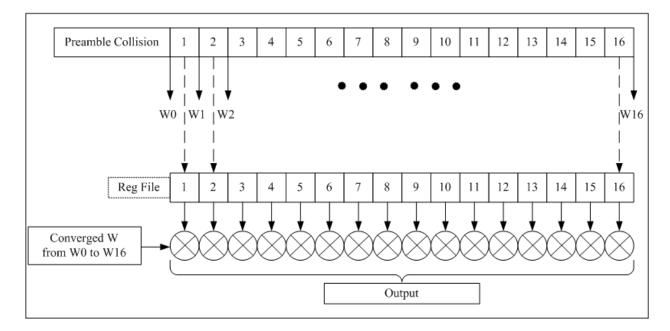

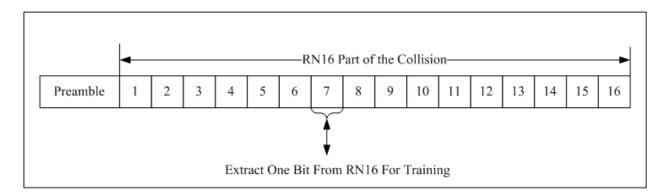

| Figure 94. Combination of Batch Training and Online Training10                       | )1             |

| Figure 95. Perform ICA on Portions of the Entire signal10                            | 02             |

| Figure 96. Collision Signal down Sampling10                                          | 03             |

| Figure 97. 2-Tag Collision Signal Acquisition Setup for ICA10                        | )5             |

| Figure 98. Tag and Antenna Positioning10                                             | 05             |

| Figure 99. 2-tag Collision Resolution Result using FastICA in FPGA (BLF=64 kHz)10    | )6             |

| Figure 100. 2-tag Collision Resolution Result using FastICA in FPGA (BLF=128 kHz)10  | )6             |

| Figure 101. 2-tag Collision Resolution Result using FastICA in FPGA (BLF=256 kHz)10  | <b>)7</b>      |

| Figure 102. 2-tag Collision Resolution Result using FastICA in FPGA (BLF=341 kHz)10  | <b>)7</b>      |

| Figure 103. 2-tag Collision Resolution Result using FastICA in FPGA (BLF=682 kHz)10  | )8             |

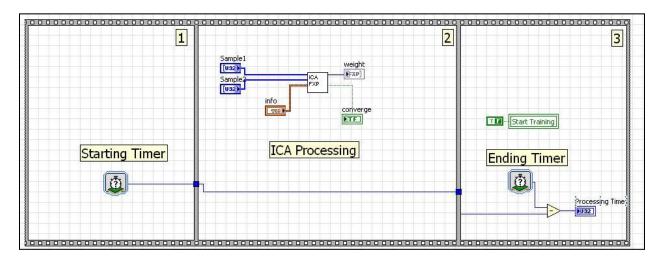

| Figure 104. Processing Time Recording (LabVIEW FPGA code Segment)10                  | )8             |

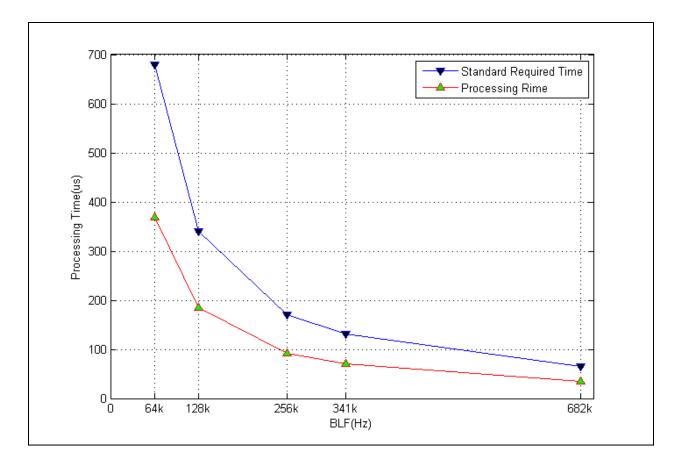

| Figure 105. 2-tag Collision Resolution Processing Time vs. Standard Specification    | 10             |

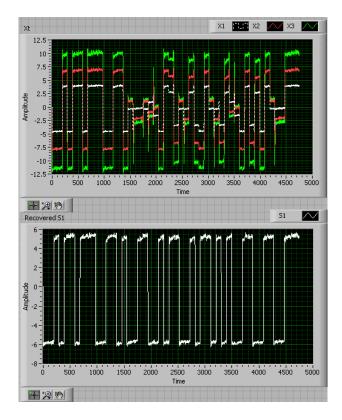

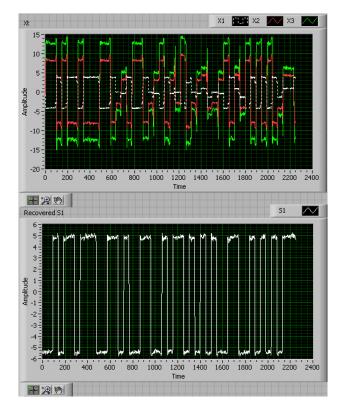

| Figure 106. 3-tag Collision Resolution Result using FastICA in FPGA (BLF=64 kHz)12   | 11             |

| Figure 107. 3-tag Collision Resolution Result using FastICA in FPGA (BLF=128 kHz)12  | 11             |

| Figure 108. 3-tag Collision Resolution Result using FastICA in FPGA (BLF=256 kHz) 12 | 12             |

| Figure 109. 3-tag Collision Resolution Result using FastICA in FPGA (BLF=341 kHz)112 |

|--------------------------------------------------------------------------------------|

| Figure 110. 3-tag Collision Resolution Result using FastICA in FPGA (BLF=682 kHz)113 |

| Figure 111. 3-tag Collision Resolution Processing Time vs. Standard Specification114 |

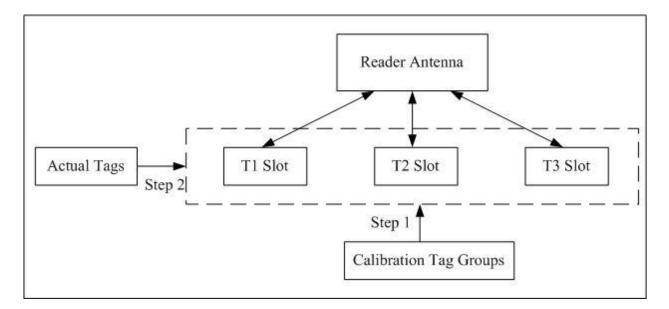

| Figure 112. Calibration for Universal Whitening Matrix117                            |

| Figure 113. Artificial Mixing Matrix117                                              |

| Figure 114. Estimation of the Universal Whitening Matrix117                          |

| Figure 115. Resolution Result Based on Universal Whitening Matrix (Group 1)118       |

| Figure 116. Covariance Matrix of the Whitened Collision Signal (Group 1)118          |

| Figure 117. Resolution Result Based on Universal Whitening Matrix (Group 2)119       |

| Figure 118. Covariance Matrix of the Whitened Collision Signal (Group 2)119          |

| Figure 119. Resolution Result Based on Universal Whitening Matrix (Group 3)120       |

| Figure 120. Covariance Matrix of the Whitened Collision Signal (Group 3)120          |

| Figure 121. Resolution Result Based on Universal Whitening Matrix (Group 4)121       |

| Figure 122. Covariance Matrix of the Whitened Collision Signal (Group 4)121          |

| Figure 123. Resolution Result Based on Universal Whitening Matrix (Group 5)122       |

| Figure 124. Covariance Matrix of the Whitened Collision Signal (Group 5)122          |

| Figure 125. Resolution Result Based on Universal Whitening Matrix (Group 6)123       |

| Figure 126. Covariance Matrix of the Whitened Collision Signal (Group 6)123          |

| Figure 127. Resolution Result Based on Universal Whitening Matrix (Group 7)124       |

| Figure 128. Covariance Matrix of the Whitened Collision Signal (Group 7)124          |

| Figure 129. Resolution Result Based on Universal Whitening Matrix (Group 8)125       |

| Figure 130. Covariance Matrix of the Whitened Collision Signal (Group 8)125          |

## PREFACE

My first experience with electrical components was twenty three years ago, when I was at the age of four. My father, a senior electrical engineer, was testing a television set and that moment is what started my interest in electrical engineering. I would like to thank my father, Xiaoming Sun, for all of the generous mentoring and guidance he has provided since my childhood. On the eve of starting my American dream, three years ago, I experienced the passing away of my beloved mother, Weihua Huang. This wonderful woman gave me all of her love, hope and blessings. I built my first perceptions of the USA from this great woman. Serving as a successful manager in China Mobile for over a decade, she visited this country for several times. I will never forget her last words, "Son, go to America, to witness and study the most advanced technology in the world."

Today, on the eve of obtaining my Ph.D., I am deeply indebted to my advisor, Dr. Marlin H.Mickle. During my most confusing periods of time, Dr.Mickle's lucid explanations and patient guidance always provided me with enlightment. He would always say "Get things done, Get things done efficiently, Get things done simply" and this is something that has served me well and I've learned to live by during my time at the RFID Center of Excellence.

I would also like to thank Dr. Zhi-Hong Mao, Dr. J.T. Cain, Dr. Ronald G. Hoelzeman, Dr. Joseph Kabara and Dr. C. C. Li for serving on my committee and providing me with helpful suggestions. I am also greatly appreciative to Dr. Peter J.Hawrylak for his detailed, technical guidance. Without the help of these advisors, I would not have been able to accomplish this work in such a short time.

I would also like to thank the dear friends that I've made during my studies here at Pitt. First I would like to thank Samuel Dickerson for greatly helping me improve my English skills during the past two years, providing me with insightful interchanges about research, and for being a good friend. I would also like to extend my thanks to Dr.Ajay Ogirala and Michael Rothfuss for all the help along the way of my Ph.D.

#### **1.0 INTRODUCTION**

Because passive RFID systems make use of the electromagnetic spectrum, they are relatively easy to jam using energy at the right frequency when they are in a dense tag environment. Although this would only be an inconvenience for consumers in non timing-critical situations (e.g. in stores with longer waits at the checkout), it could be disastrous in other environments, such as hospital emergency centers and in the military in a field of operation.

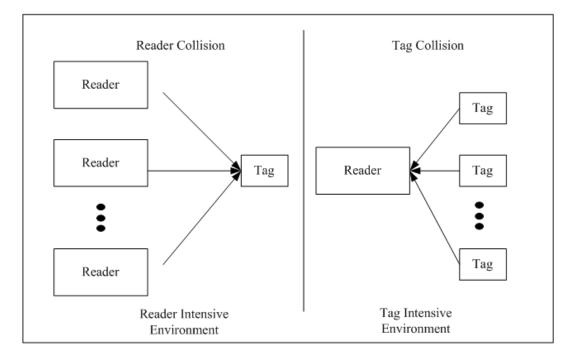

The collisions in passive RFID communications lie in two major categories: the reader collision and the tag collision (as shown in Figure 1). Reader collision occurs in a reader intensive environment when the signals from two or more readers overlap in time and frequency. In such a situation, the tag is unable to respond to simultaneous queries; Tag collision occurs in a tag intensive environment when multiple tags are present in the transmitting field of the reader. In such a situation, tags may respond to the reader query command simultaneously causing the reader to fail to decode the received signal, which is the result of collision.

The scope of this dissertation is to resolve the tag collisions in order to improve the reading efficiency of ISO 18000-6C RFID systems [1]. To address the tag collision problem, multiple anti-collision protocols enabling the passive RFID tags to take turns in transmitting to a reader have been developed. Generally, there are two types of anti-collision protocols in common use based on time division multiple access (TDMA): One is the dynamic framed slotted Aloha, the other is a Binary Tree scheme [2]. The ISO 18000-6C RFID systems make use of the

dynamic framed slotted Aloha. However, the dynamic framed slotted Aloha is a probabilistic method that can decrease the probability of collision occurrences significantly, but collisions cannot be completely avoided. Therefore, in the worst case when two or more tags in an inventory round select the same time slot to respond (e.g. when the reader enforces all tags to respond), the reader may receive an unrecognizable (un-decodable) mixture of signals. Accordingly, the reader read rates will be degraded due to this collision situation in the communication process. Therefore, it is intuitive to increase the system read rate more from purely collision avoidance by recovering the original tag signals from the collision at the reader side. The philosophy of this method is to resolve the collision after it occurs rather than to avoid its occurrence. It is also possible to combine the use of an anti-collision mechanism and the resolution of the collision signal in order to increase the efficiency of the reader-tag communication.

**Figure 1. Passive RFID Collision Situations**

In addition, the ISO 18000-6C passive RFID tags rely on limited energy harvested from the interrogator carrier wave rather than an internal power supply to perform logic functions and backscatter signals. Although this feature makes passive RFID tags easy and inexpensive to deploy and maintain compared to active tags, the passive tags are subject to more critical communication timing constraints; a reader which fully conforms to the standard must realize the tag inventory round including a real time three-step handshake in order to make the tag transit into the data access states, which allows for tag memory access. The effective turn-around time between each of the three steps lies in the range of from 31.25µs in the worst case when the tag back link frequency (BLF) reaches 640kHz to 0.5ms in the best case when BLF is as low as 40kHz, which implies that the interrogator or the test platform conforming to the ISO 18000-6C standard shall complete the signal decode and command assembly work in real time during each step of the handshake. If the reader fails to achieve this requirement, the tags will lose power and transit back to the initial state waiting for a new effective inventory round.

The timing limitation implies that the reader must resolve the tag collision in real time. If at least one of the tag responses can be resolved from the collision and decoded in the specified real time, one inventory round including the three step handshake can be performed. Furthermore, if more than one tag response can be resolved from the collision, inventory rounds potentially can be performed in parallel which leads to a dramatic increase in system read rates.

### **1.1 BACKGROUND OF THE PROBLEM**

### 1.1.1 The Link Timing of ISO 18000-6C Standard

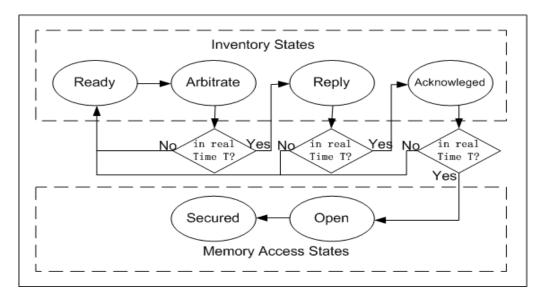

The ISO 18000-6C standard specifies two categories of tag states: the inventory states and the memory access states as shown in Figure 2. In order to access the memory content in the tag, a reader shall complete an inventory round to make the tag pass all the inventory states until entering the memory access states. The challenge lies in the fact that each step of the inventory round must be completed in a soft real time T (i.e. the Turn-around time between the reader command and the following tag response), which requires the reader to complete the decoding for the tag response and then sends out the next command within this turnaround time. If any transition step in the inventory round fails to complete in T, the tag will transit back to the Ready state (the initial state after power up). Table 1 lists the required turn-around time for typical tag BLF.

**Figure 2. Tag States Transition**

| BLF    | Minimum | Maximum  |

|--------|---------|----------|

| 64kHz  | 46.90µs | 312.50µs |

| 128kHz | 23.45µs | 156.25µs |

| 256kHz | 11.73µs | 78.125µs |

| 320kHz | 9.38µs  | 62.50µs  |

| 640kHz | 4.69µs  | 31.25µs  |

Table 1. Tag Turn-around Time at Typical BLF

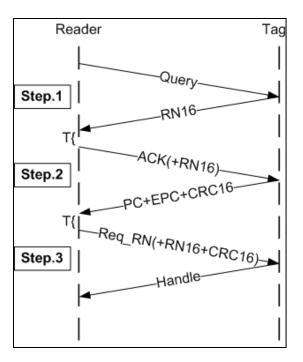

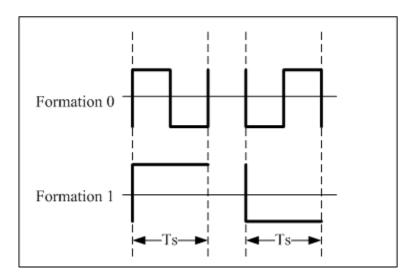

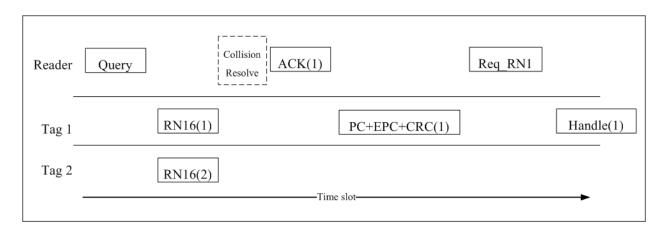

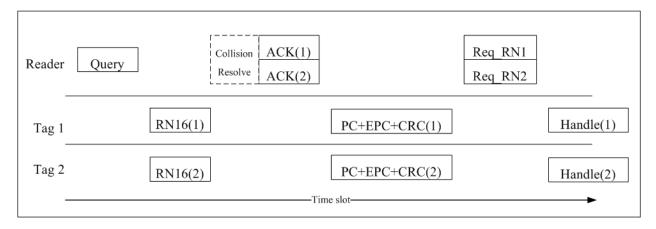

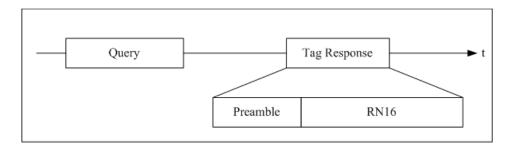

Corresponding to each state in the inventory round, there exists a three-step handshake as shown in Figure 3. At the first step (Step.1) of the handshake, the reader assembles and sends out a Query command; the tag chooses a random time slot to backscatter its 16-bit random number (RN16) after receiving a Query command, and then transits from the Arbitrate state to the Reply state. In the following step (Step.2), the reader decodes the tag backscattered random number and attaches it to the command header of an acknowledge command, ACK, and then sends out the ACK command within the turn-around time T. The tag receives this ACK command and responds with its ID (the tag PC and EPC number) protected by a 16-bit CRC code. The tag then transits into the Acknowledged state. At the last step (Step.3), the interrogator receives the tag response and sends out a Req\_RN command within the same turn-around time, T, in Step 2 to notify the tag entering into the memory access state (Open or Secure state). The tag receives this Req\_RN command and backscatters a Handle (a special code).

Figure 3. The Three Step Handshake

### 1.1.2 The Anti-Collision Mechanism in ISO 18000-6C standard

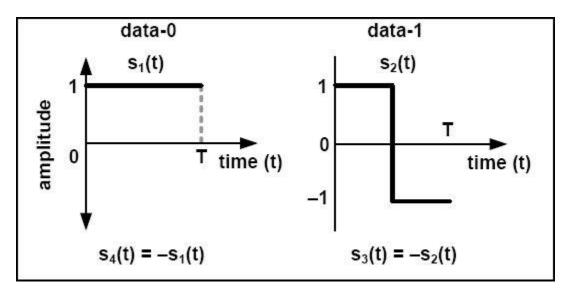

To start an inventory round for the tags in the field, the reader needs to send a Query command as the first step in the inventory round. The formation of the Query command and the tag corresponding response are shown in Figure 4. The anti-collision dynamic framed slotted Aloha algorithm is realized by specifying a value ranging from 0-15 to the 4-bit Q field in the Query command. Upon receiving the Query command, the matching tags pick a random number in the range of  $[0, 2^{Q}-1]$  to load into its slot counter. If a tag, in response to the Query command, loads its slot counter with zero, it responds with a 16-bit random number (RN16). The tag collision occurs when multiple tags in the reader field load their slot counter with zero and, thus, respond to the Query command simultaneously. A form of collision control can be realized by

specifying a large value for Q, in the extreme case when Q equals 16 the probability for an N tag collision is  $(1/65536)^{N-1}$ .

| <i>Query</i> command                            |         |                       |                                          |                                       |                                         |                                      |              |      |       |

|-------------------------------------------------|---------|-----------------------|------------------------------------------|---------------------------------------|-----------------------------------------|--------------------------------------|--------------|------|-------|

|                                                 | Command | DR                    | М                                        | TRext                                 | Sel                                     | Session                              | Target       | Q    | CRC-5 |

| # of bits                                       | 4       | 1                     | 2                                        | 1                                     | 2                                       | 2                                    | 1            | 4    | 5     |

| description                                     | 1000    | 0: DR=8<br>1: DR=64/3 | 00: M=1<br>01: M=2<br>10: M=4<br>11: M=8 | 0: No pilot tone<br>1: Use pilot tone | 00: All<br>01: All<br>10: ~SL<br>11: SL | 00: S0<br>01: S1<br>10: S2<br>11: S3 | 0: A<br>1: B | 0–15 |       |

| Tag reply to a <i>Query</i> command<br>Response |         |                       |                                          |                                       |                                         |                                      |              |      |       |

| # of bits 16                                    |         |                       |                                          |                                       |                                         |                                      |              |      |       |

| description RN16                                |         |                       |                                          |                                       |                                         |                                      |              |      |       |

#### Figure 4. Query Command and Tag Response Formation

## 1.1.3 ISO 18000-6C Tag Baseband Encoding

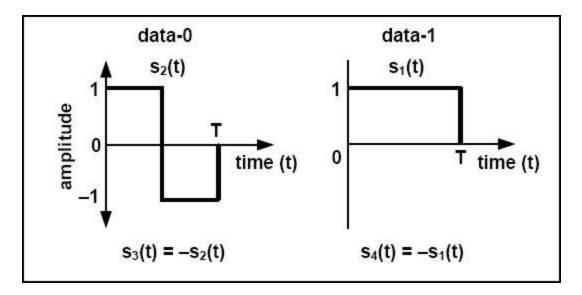

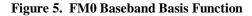

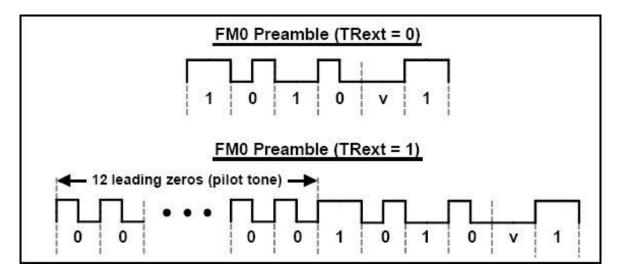

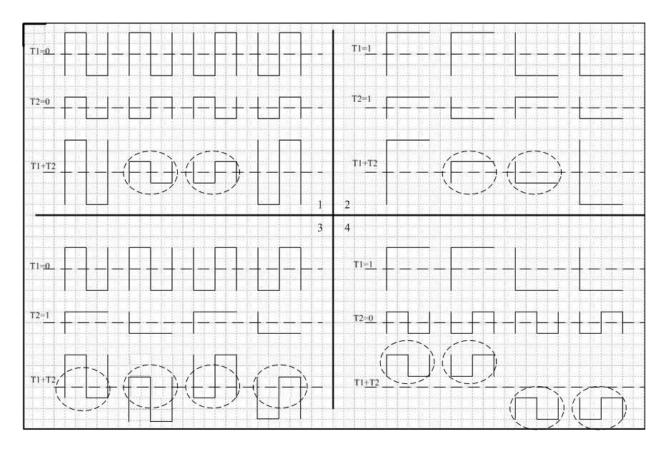

According to the ISO 18000-6C standard [1], Tags shall encode the backscattered data as either FM0 baseband or Miller modulation of a subcarrier at the data rate (BLF). The reader commands the encoding choice, and both FM0 and Miller are bi-phase space encoding.

Figure 5 shows the basis functions of FM0. FM0 inverts the baseband phase at each symbol boundary; a data-0 has an additional mid-symbol phase inversion.

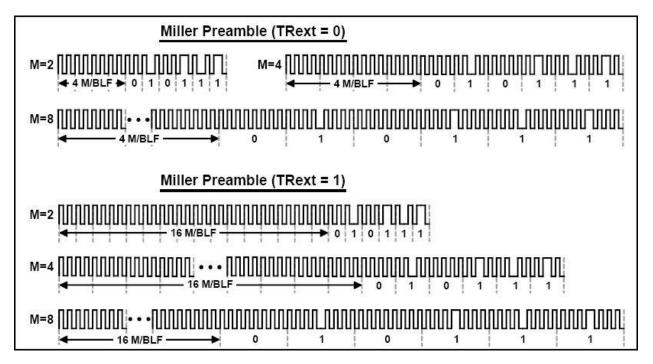

Figure 6 shows the basis function of Miller encoding. Baseband Miller inverts its phase between two data 0's in sequence. Baseband Miller also places a phase inversion in the middle of a data 1 symbol. When employing Miller encoding, the tag modulates a square wave shaped subcarrier by the Miller baseband. The Miller sequence contains exactly two, four or eight subcarrier cycles per bit [1].

Figure 6. Miller Baseband Basis Function

Generally, the symbol of both FM0 and Miller can be categorized into formations as shown in Figure 7. Formation 0 features a edge transition in the middle of the symbol, while there is no edge transition in Formation 1 symbol.

Figure 7. Generalized Tag Baseband Formation

# **1.2 STATEMENT OF THE PROBLEM**

#### 1.2.1 Overview

The focus of this research is to resolve the two tag collision situation with extension to three or more collision tags. The collision can be simulated by letting the reader set the Q in the Query command to a value of zero. The two tags will then both load 0 into their slot counter and respond with their 16-bit random numbers simultaneously. The two tag responses are supposed

to be linearly superimposed as will be discussed. The reader receives baseband collision signals after RF and IF down conversions and are thus the superposition of the two symbol formations of either FM0 or Miller encoding as discussed in last section. Due to the attenuation of different propagation paths and the fact that the Phase Locked Loop (PLL) in the reader receiver circuitry can only lock to one of the tag backscatter carrier waves, or the reader transmitting carrier wave depending on the relative strength of them. The downconverted two tag responses are normally different in magnitude. In addition, due to the capacitor variation in the tag chips (silicon), a phase shift (delay) may exist between the two responses even when the two tags are from the same manufacturer. (Detailed analysis of the two tag collision baseband signal violates the standard specified FM0 or Miller encoding, which causes the functional failure in the reader decode circuitry.

Without any collision resolution, the reader can only decode tags responding in different time slots, while two tags can share a common time slot provided their separate response can be recovered and extracted from the collision signal. For two tags in the field on a reader where Q = 4, the probability of two tag responses colliding is  $(1/16) \times (1/16)$ . The probability of three tags colliding is  $(1/16) \times (1/16) \times (1/16)$ , which reduces the collision probability significantly. Therefore, successful resolution of the two tag collision can significantly improve system data access efficiency. For example, the reader can selectively access one tag in a two tag collision situation as shown in Figure 8. As another example, with the reader collision resolution mechanism, the reader can simultaneously complete two independent inventory rounds for two tags as illustrated in Figure 9.

Figure 8. Selective Tag Access with Collision Resolution

#### Figure 9. Simultaneous Tag Access with Collision Resolution

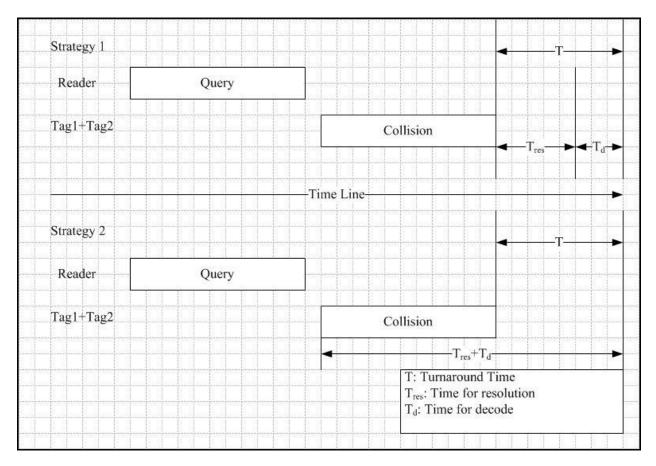

As discussed in the previous section, the standard mandates a real-time turnaround time specification. The collision resolution needs to be completed before the time out occurs. Therefore, two strategies can be considered for the timing of the collision resolution as shown in Figure 10. The first strategy starts the resolution after the complete acquisition of collision, while the second one performs an on-line resolution one symbol after the other. The time available for collision resolution in the first strategy is less than the standard specified turnaround time because after the resolution, the reader needs time to decode the recovered tag response after it is finished. In comparison, the time available for the resolution equals the turnaround time plus the tag signal duration, and the reader can simultaneously decode the recovered symbols one by one.

Figure 10. Collision Resolution Timing Strategy

# 1.2.2 Dissertation Work

This is a research to solve the tag collision resolution problem for ISO 18000-6C passive RFID communication systems.

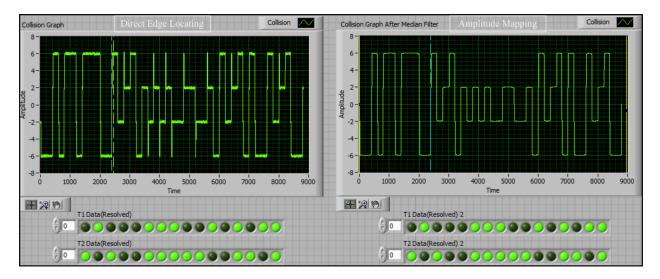

Two straightforward online resolution methods are adapted to the two tag collision problem. The first method is the direct edge locating of the collision signal. The second one is the amplitude mapping to resolve a two-tag collision. The direct edge locating method will focus on resolving the two-tag collision with significant phase shift (larger than 15% of the symbol duration), while the amplitude mapping method will focus on resolving the collision with very

short or without phase shift. The two resolution methods can be unified by pre-processing the tag collision with a median filter in real time. As a part of the research, simulations are performed on a host PC as preliminary work to verify the functionality of the algorithms. The proposed algorithms are then optimized and implemented in one Xilinx Virtex-II Pro XC2VP30 FPGA on the NI5640R software defined transceiver board to verify their ability to resolve a two-tag collision within the real time limitation as specified in ISO 18000-6C standard.

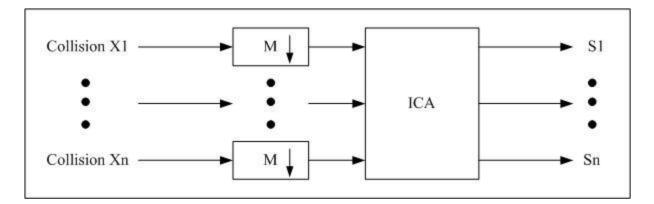

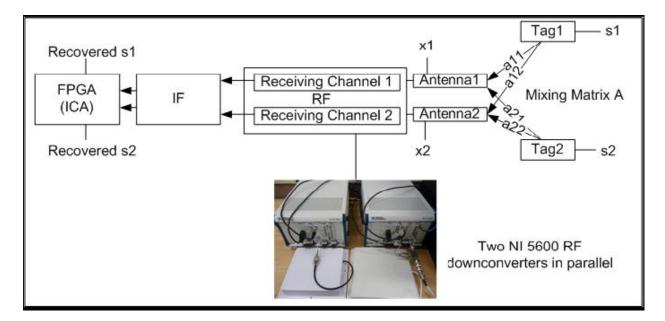

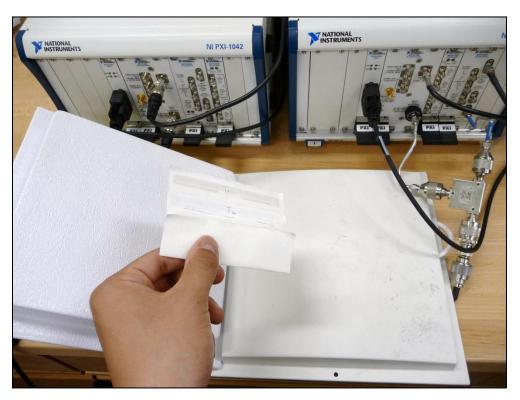

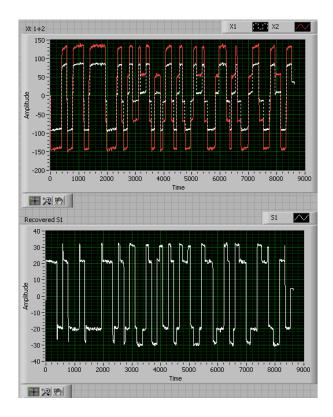

To extend the resolution to multiple tag (greater than two) collisions, a statistic signal processing method using Independent Component Analysis (ICA) is used. The ICA method resolves two or more tag collisions without the limitation of the direct edge locating and amplitude mapping at the expense of increased hardware for additional receiving channels and higher computation load. To decrease the computation load of ICA in order to achieve the required processing speed, the ICA algorithm is optimized by working on the down sampled collision signal without losing recovery accuracy.

Finally, the collision signal acquired from moving tags with speeds up to 40 miles/hour will be resolved by the amplitude mapping method using the FPGA to prove the compatibility of the research's application on dynamic tags. All of the above methods work on commercial off the shelf passive RFID tags.

In Summary, the dissertation work includes:

- Developing a conformance test platform and a data acquisition platform ISO 18000-6C

Passive RFID systems

- Study and Analysis of 2-tag and 3-tag collision signal acquired from both the stationary tags and moving tags

- Host PC Simulation and FPGA implementation of a 2-tag collision resolution algorithm based on both the amplitude and phase shift characteristics of signals

- Host PC simulation and FPGA implementation of ICA for multiple tag collision resolution

### 2.0 DATA ACQUISITION PLATFORM

Supported by the RFID Center of Excellence at the University of Pittsburgh, an ISO 18000-6C RFID tag conformance test platform has been developed as a preliminary to the research for this dissertation. This platform works by sending the user specified reader command to the tags under test as the test stimulus, analyzing the acquired tag backscatter, and then checking the tag response baseband waveform against the standard. This platform can thus serve as a data acquisition platform to obtain the tag response signal and the collision signal, which are the source signals in interest in this research.

When selecting the hardware device for this platform, general purpose microprocessors and available commercial readers are both considered as candidates for ISO 18000-6C realization. General purpose microprocessors could be utilized to perform the communication, but they usually take multiple cycles to finish one instruction, and the total number of machine language instructions varies with the efficiency of user programming algorithms and the compilers. Therefore, they are difficult to time accurately and sometimes inefficient in communication timing control and, thus, not the best device to be selected. Available commercial readers are alternative platforms, however their architectures are fixed after manufacture and most of those devices require users to familiarize themselves with the vendor specified command format in order to manipulate the reader which burdens the user and degrades the RFID data access efficiency. In addition, there is no evidence that the commercial readers can provide convenient forward compatibility while the passive tags advance in technology. Upgrading those readers to support the new features of tags is usually the major R&D cost if a hardware modification is required. Unlike microprocessors, FPGAs are easier to make timing accurate in their Hardware Description Language (HDL) programming nature. Compared to the fixed structure of commercial interrogators, a reconfigurable platform can be easily customized to perform in-depth functions. Therefore, in light of the defects of the possible solutions, it is intuitive to utilize the re-programmability of an FPGA baseband processor to build a flexible interrogator for ISO 18000-6C passive RFID tags.

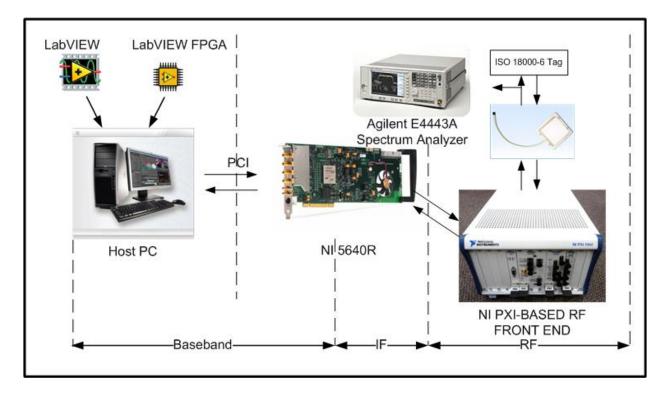

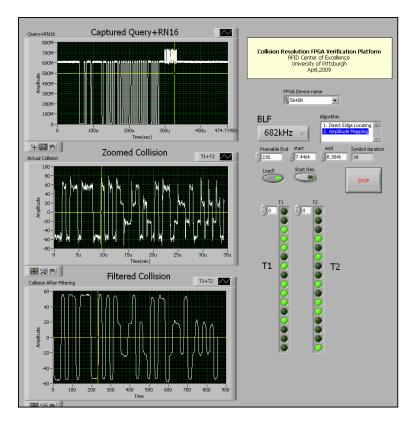

To these ends, an FPGA based software defined radio architecture is employed to implement the ISO 18000-6C standard for the data conformance test platform. It features: 1) a real-time FPGA baseband, 2) a software controllable IF and RF front-end, and 3) a host PC based GUI control panel. The development tool set includes National Instrument (NI) LabVIEW 8.5 (for software programming and test front panel control), and LabVIEW FPGA module 8.5 (for FPGA baseband hardware programming). LabVIEW is distinctly suited for FPGA programming because it clearly represents parallelism and data flow. With the LabVIEW FPGA Module, custom measurement and control hardware requiring high-speed hardware reliability and tight determinism can be simulated and synthesized without low-level hardware description languages or board-level design. The LabVIEW compiler automatically translates the LabVIEW graphic code into low-level HDL code.

### 2.1 PLATFORM ARCHITECTURE

The reconfigurable software defined radio test platform consists of two major parts:

- 1. The hardware, which includes the signal baseband, the intermediate frequency and the RF front end.

- 2. The software running on a PC controls the hardware and analyzes the backscattered signal.

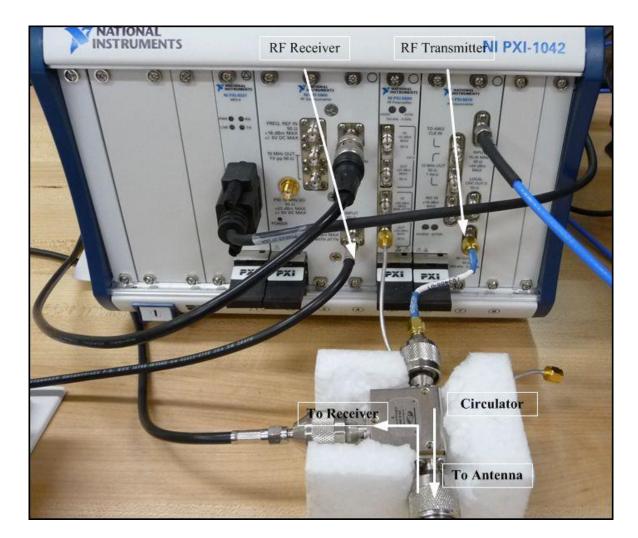

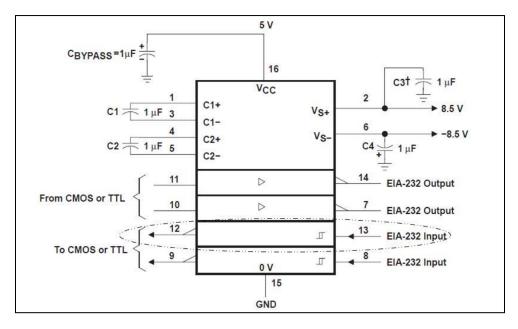

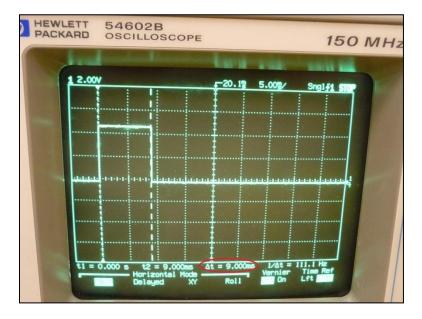

## 2.1.1 Platform Hardware

The architecture of the platform hardware connection is shown in Figure 11. The 2-way signal flow includes the transmitter side and the receiver side. On the transmitter side, the software on the host PC selects and sends out the user specified command to the FPGA-based baseband. The baseband assembles the received binary command using PIE encoding according to the standard and then passes the data into the intermediate frequency band (IF). The IF stage consists of a DA9857 14-bit quadrature digital upconverter and a DA6654 14-bit downconverter. With the built-in Numerical Controlled Oscillator (NCO), the IF upconverter modulates the baseband data in DSB-ASK at the IF center frequency of 25MHz. The signal baseband (Xilinx Virtex-II Pro XC2VP30 FPGA) and the IF stage are together in the NI PCI-5640R Software-Defined Radio transceiver board. The 25MHz IF ASK signal is sent into the RF front end tuned to 915MHz for RF stage modulation. The RF front end consists of an NI 5610 RF upconverter and the NI5600 RF downconverter, which are connected by the NI PXI bus. On the receiver side, the tag backscattered signal passes through the 2-stage ASK demodulation in the RF and IF bands, and then enters into the baseband. An Agilent E4443A real time spectrum analyzer is employed as an auxiliary monitor of the RF communication process in the air interface. The FPGA decodes the signal using FM0 or Miller encoding and sends the received signal as well as the decoded binary data back to the host PC for software offline analysis.

Figure 11. Platform Hardware Architecture

# 2.1.2 Platform Software

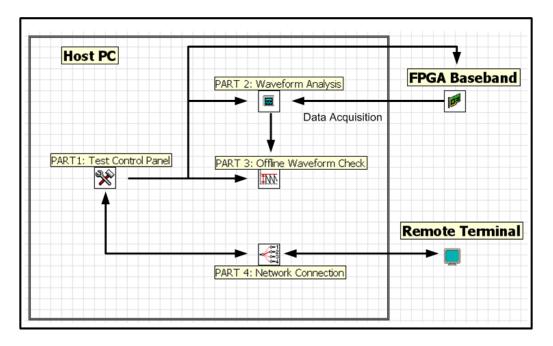

The platform software running on the host PC handles four major functions:

1. The test control panel: Using this panel, the user can select the command to send and set the command parameters. A set of the physical layer (PHY) features such as modulation depth, the length of Tari value, RTcal, and TRcal can be controlled by inputting values in corresponding text fields on the front panel. In addition, the IF and RF stage hardware are both configured by

specifying the expected center frequency, the output power level, and the sampling length/accuracy.

2. The signal analysis: The host PC software receives the demodulated baseband I/Q signals, and displays the RF envelope, the I vs. Q waveform, the constellation diagram, and also calculates the spectrum.

3. The offline conformance check: The received RF envelope and calculated spectrum can be stored by the user optionally for offline conformance checking in a separate offline analysis module. The pulse width of the data stream and the integration of power in the specified bandwidth are checked against the standard.

4. The interface for remote control: By using the LabVIEW supported remote panel interface, the host PC can be accessed by remote machines through Ethernet/Internet connection in a Client-Server relationship. This allows a remote terminal to send a command to the local host PC, which connects to the baseband and RF front end to perform the data acquisition and conformance test.

Figure 12 illustrates the software workflow of the host PC software.

19

Figure 12. Platform Software Architecture

# 2.2 STANDARD REALIZATION AND DATA ACQUISITION

#### 2.2.1 Standard Realization

The FPGA baseband realizes the logic function of an ISO 18000-6C conforming reader. The FPGA baseband consists of four parts to realize the ISO 18000-6C standard: the ASK modulator, the real-time DSP unit, the signal decode module for both the FM0 and the Miller encoding signal, and the processing unit for the previously mentioned three step real time handshake.

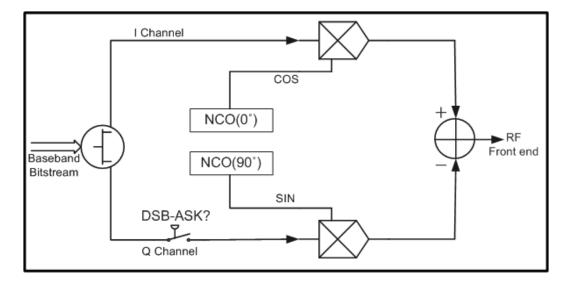

On the transmitter side, the FPGA assembles the reader commands. It receives the binary command from the host PC control panel, and then modulates the data stream using ASK after performing the encoding. The modulation of the ASK signal is shown in Figure 13. The encoded data are sent into two separate quadrature channels – I and Q in the IF stage. The ASK

modulation is realized by setting the magnitude multiplier in each channel as 1 when the incoming data bit is "1" in binary, and setting the multiplier to zero when the data bit is "0". The DSB-ASK and SSB-ASK modulation manner can be selected by controlling the strobe of the Q channel.

Figure 13. ASK Modulation Block

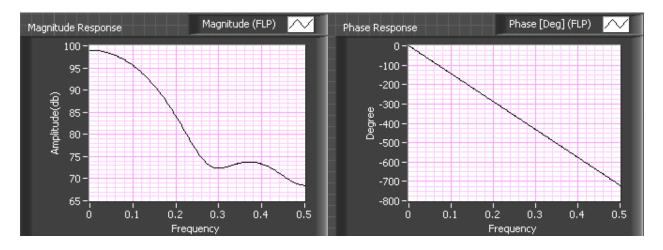

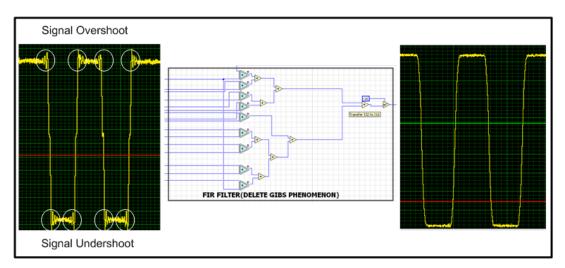

However, the square wave shaped command bit stream generated by the FPGA contains a theoretically unlimited bandwidth. If it is passed into the IF upconverter without bandwidth limiting, the so called Gibbs phenomenon[7] occurs, resulting in significant over/under shoot at the data edges which degrades the output signal. The over/under shoots of the output command usually exceed the maximum tolerance specified in the ISO 18000-6C standard and make the outputting command signal invalid for the tag in test. Therefore, real-time DSP work is necessary for guarantying the quality of generated interrogator signals. To eliminate the Gibbs phenomenon, a low pass filter is placed between the FPGA baseband and the IF stage in order to limit the bandwidth of the outputting baseband signals below the cut off frequency of the interpolation filter in IF upconverter. With the LabVIEW built-in Digital Filter Design (DFD)

toolkit, the tap coefficients for an 8-order Bessel FIR low pass filter are generated and the magnitude/phase responses are displayed in Figure 14.

Figure 14. FIR Filter Magnitude and Phase Response

As shown, the bandwidth of the baseband signal is limited to 30% of the sampling frequency, which is 10% below the cut-off frequency of the interpretation filter in the IF stage. The coefficients are selected to be symmetric to the center tap in order to ensure a linear phase response. Figure 15 shows the realization of the filter in the LabVIEW FPGA Module and its corresponding effect. Comparing the baseband outputs, it can be seen that the under/over shoots in command signals are significantly quenched after the smoothing.

Figure 15. Signal Smoothing with 8-order FIR Filter

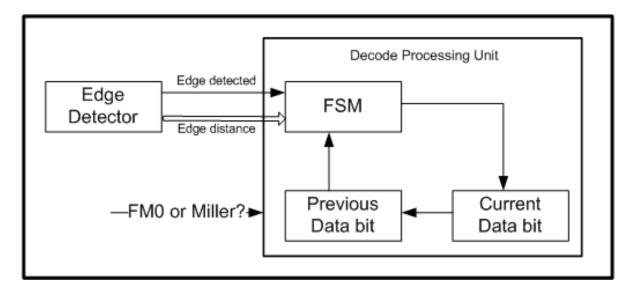

On the receiver side, the FPGA baseband receives the IF demodulated tag backscattered signals, and recovers the binary information in this FM0 or Miller encoded bit stream using a decode module. In the decode process, the clock recovery method is critical to accuracy. In light of the fact that the FM0 and Miller encoding are both self-clocking bi-phase code, the decoding can be based on edge detection and pulse width measuring. Figure 16 shows the architecture of the decode module. In the decode module, the edge detector scans the data series, and sends out a notification signal as well as the distance between current and previous edges (i.e. the pulse widths) to the decode processor. The decode processor includes a 2-state Finite State Machine (FSM), which arbitrates the corresponding logic value for the data bit based on the inputs from the edge detector and the previous data bit.

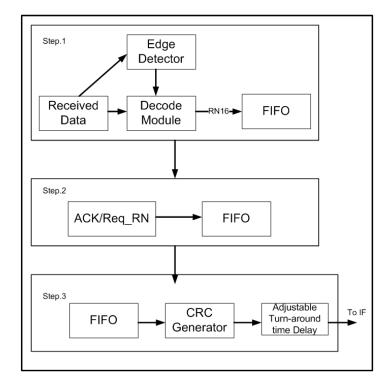

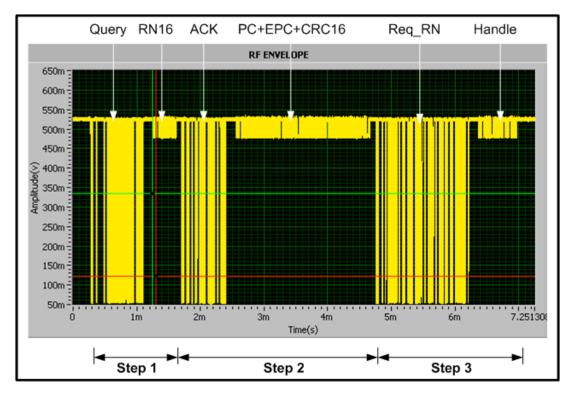

The infrastructure of the handshake processing unit is shown in Figure 17. In Step 1 of the three step handshake, the decode module notifies the decode module every time it detects an edge in the tag response. The decode module decodes the incoming tag response and sends out a handshake signal to the processing unit once the decode finishes for the tag backscattered random number. In Step 2, the decoded 16-bit binary random number is stored in the block memory in the FPGA and passed into an FIFO for command assembly. The ACK command header is sent into the same FIFO, and by doing this, the random number gets attached to the header. The FIFO is connected to an optional delay module which allows for a turn-around time adjustment. In Step 3, the assembly of the Req\_RN command follows the same procedure as in Step 2 except that the FIFO is also connected to a CRC16 generator for the CRC attachment. Handshake signals are also sent after the command assembly finishes in each step to notify the ASK modulator to modulate the assembled command for transmission. Figure 18 shows the acquired sampling of the three step handshake.

The synthesis result of the platform provided by Xilinx XST shows that the design utilizes 86% of the total slices, 73% of the Block RAMs and 403 user I/Os among the total 556 I/O blocks of the Virtex-II Pro XC2VP30 FPGA. Consequently, the design takes reasonable advantage of the device resources.

Figure 16. Decode Module Architecture

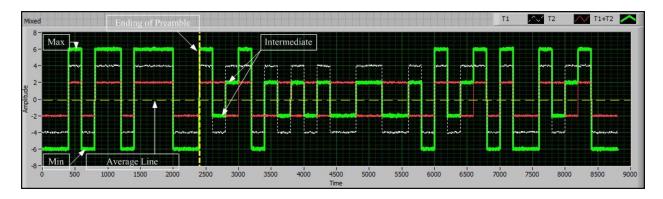

**Figure 18. Acquired Inventory Round**

## 2.2.2 Data Acquisition with the Platform

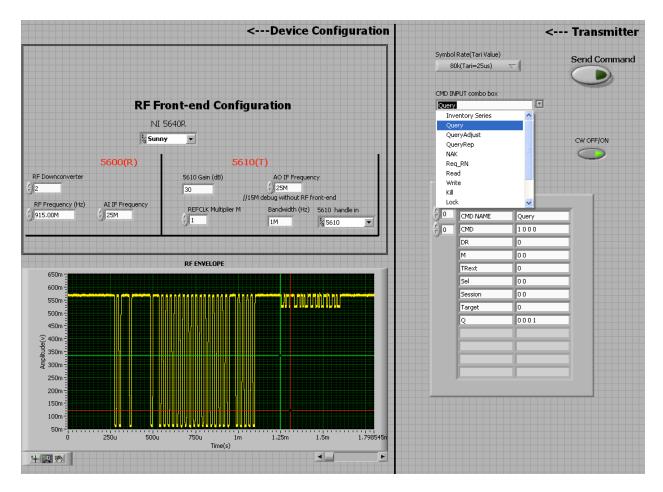

As introduced in Section 2.1.1, the test stimulus reader command as well as hardware details can be configured by the LabVIEW Graphic User Interface (GUI) test control panel, and the acquired tag response can be displayed by the signal analysis module.

In the test control panel, the user gets full control of the communication PHY and Media Access Control (MAC) configuration. The output power level and the center frequency of the RF front-end can be changed and reset by inputting the expected value in the corresponding number fields. In addition, the center frequency of the IF stage and the ASK modulation depth can also be configured. The command parameters specified by the standard such as Tari value, TRcal, and RTcal can be input by the user. In addition, the accuracy and length of the FPGA acquisition can be customized. The acquisition sampling rate varies from 2MHz to 25MHz (by default), which allows for a measurement resolution up to 0.04µs (25MHz sampling rate) in distance between adjacent sampling points. The user can easily select the command type to send, and the corresponding pre-stored default command parameters are loaded into an editable combo box automatically. The command parameter in the command combo box can be changed if necessary to send out a customized command. Figure 19 shows the test control panel. As shown, the RF front-end and the IF stage are tuned at 915MHz and 25MHz, separately; The Tari value is set as 25µs, the modulation depth is 90% and the sampling frequency is 25MHz; A Query command has been selected from the command menu, and its Q field is changed from "0000" to "0001". After clicking the "Send" button, the corresponding RF envelope of the reader command and tag response are captured by the platform hardware and displayed in the virtual oscilloscope. As shown, all the other ISO 18000-6C commands can be selected by the user from the combo box.

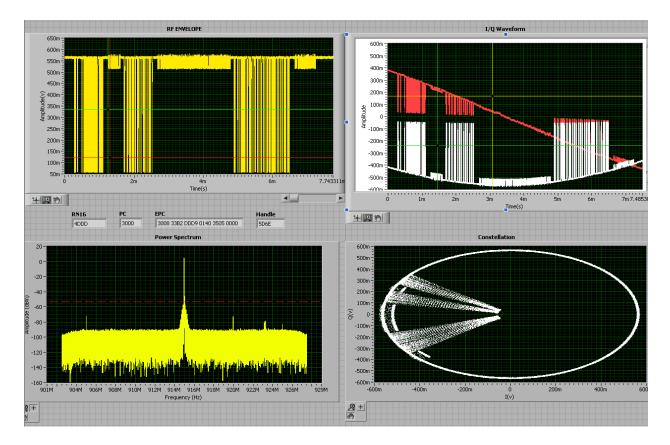

The waveform analysis module accepts the captured RF envelope and calculates the spectrum. The I vs. Q waveform as well as the constellation diagram are also generated from the acquired sampling data. The decoded message of the tag response is simultaneously displayed. Figure 20 shows an excerpt of the front panel of the waveform analysis module. Accompanying the RF envelope of the three step handshake are the decoded binary message for the RN16 after Query command, the PC+EPC+CRC after the ACK command and the Handle+CRC16 after the Req\_RN command.

**Figure 19. Test Control Panel**

Figure 20. Waveform Analysis Module

### 3.0 TAG COLLISION SIGNAL CHARACTERISTICS ANALYSIS

### 3.1 TAG COLLISION SIGNAL CHARACTERISTICS

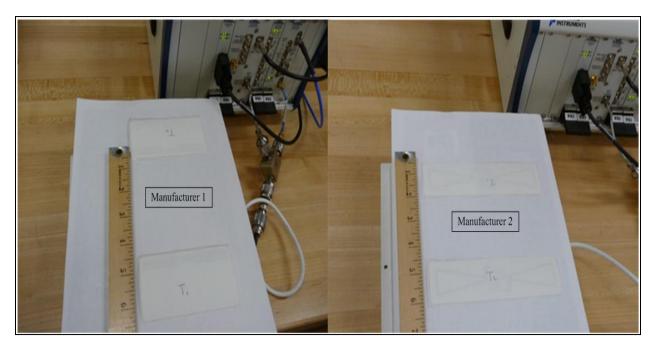

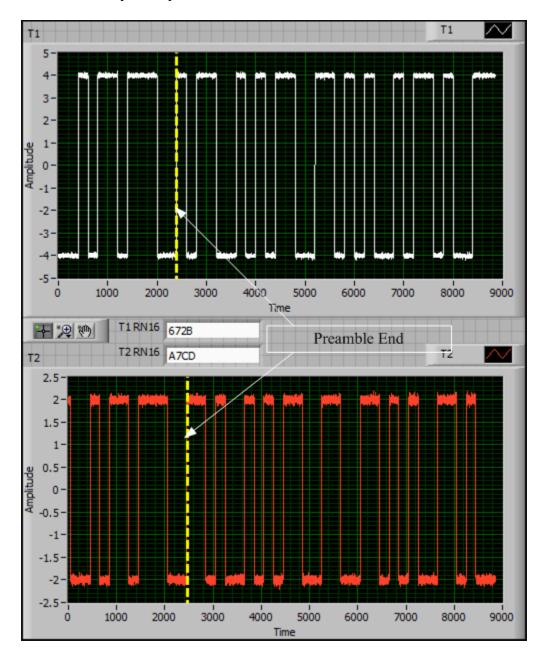

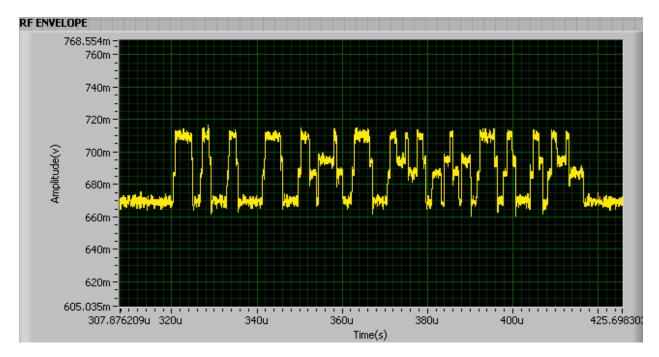

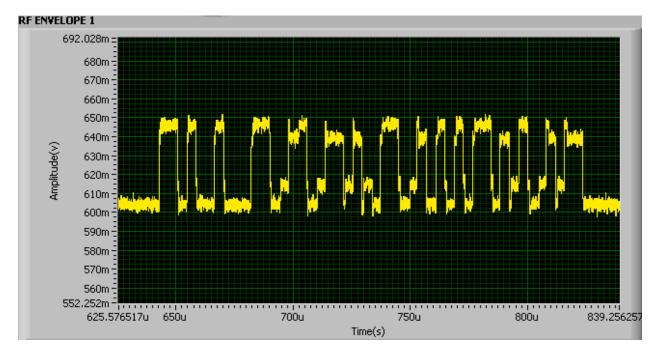

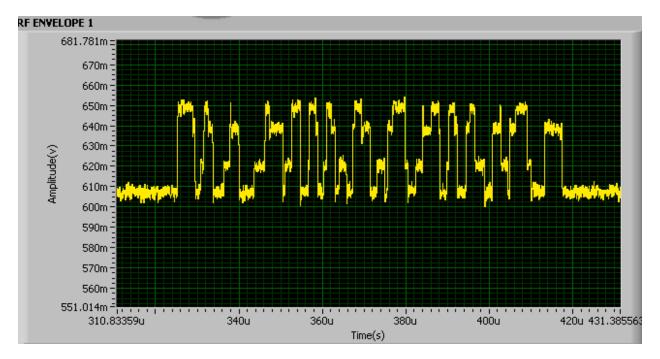

Because this research focuses on the resolution of two-tag collisions, the collision signal is generated from two tags from the same manufacturer in the transmitting field of the data acquisition platform as introduced in Section 2.0. By configuring the command parameter, the platform sends out a Query command with its Q equaling zero, and thus forces the two tags in the field to transmit their 16-bit random numbers simultaneously. By doing so, the two-tag collision situation is simulated. The RF carrier wave frequency for the air interface is set at 915MHz, and the IF frequency is set at 15MHz. At the receiver side, the collision signal is acquired by the platform, and then downconverted to the baseband signal, which is sent into the FPGA.

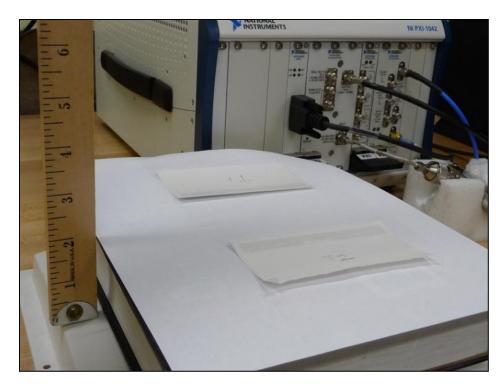

During the collision signal acquisition, in the vertical direction, the two tags, T1 and T2, are placed two inches from the center of the reader antenna as shown in Figure 21, while they are symmetric to the center and spaced by five inches from their individual antenna centers in horizontal direction. As shown in Figure 22, collision signal of tags from two different manufacturers are generated and captured. From the LabVIEW signal analysis module on the host PC, an acquired collision signal is visualized as shown in Figure 23.

Figure 21. Tag Positioning (Vertical Direction)

Figure 22. Tag Positioning (Horizontal Direction)

Figure 23. Acquired Collision Signal

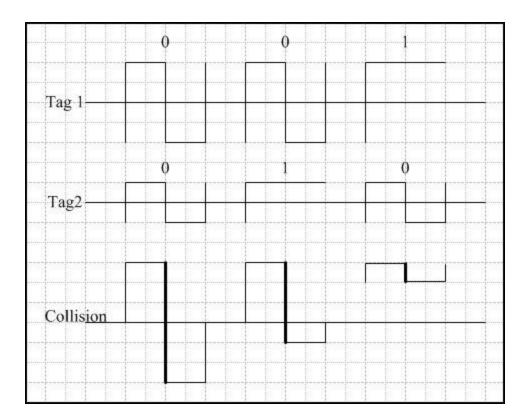

Based on observation, the features of the collision signal can be summarized as follows:

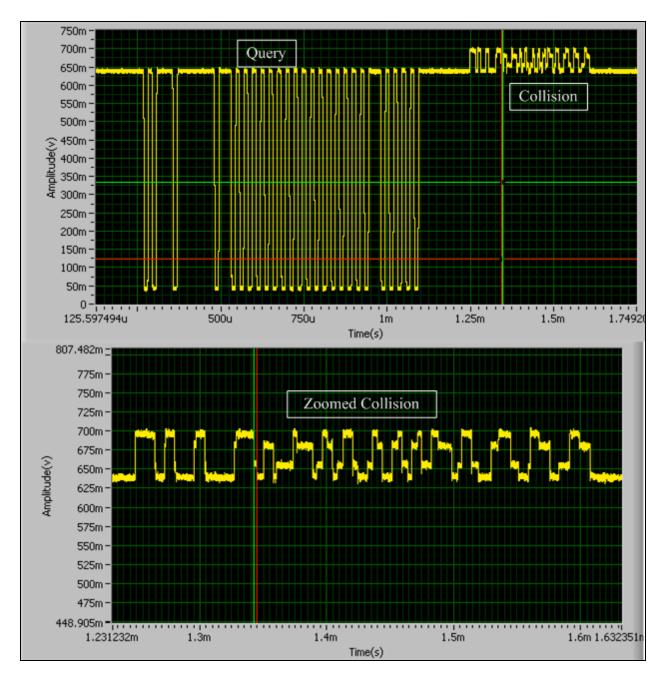

1. The collision signal is the result of the linear superposition of tag responses, and the superposition follows a linear additive model as depicted in Figure 24.

Figure 24. Linear Additive Model of Tag Responses

2. The received two tag responses are possibly different in magnitude. If the received two tag responses have the same magnitude, only three possible voltage levels can be generated when they are linearly superposed. Whereas, if they are different in magnitude, according to permutation, four possible voltage level can be obtained from their linear superposition. The assumption is summarized in Table 2, in the left sub table, the response of Tag 1 and Tag 2 are with the same magnitude of [A-, A+], while in the right sub table, Tag 1 is with a magnitude of [A-, A+], and Tag 2 is with a magnitude [B-, B+] (A≠B). This assumption is proven by locating the four different voltage levels in the observed collision signal. The different received tag responses are caused by two major facts. The first one is that the two tag responses propagate to the receiver through different paths, they thus suffer from different path attenuation. The second fact is that the RF transmitting channel and the receiving channel of the data acquisition platform are combined by a circulator connected to one patch antenna as shown in Figure 25. Because the transmitting power of the reader carrier wave is significantly larger than the power of the received tag response, the PLL in the RF receiving circuitry locks onto the phase of the transmitting carrier wave. In addition, due to the capacitor variation in each tag, the

tags carrier waves may be different in phase. Therefore, the received two tag responses suffer from different attenuation factors caused by carrier wave asynchronization with the receiver's local oscillator (LO).

| Tag1 |           |           | Tag1 |           |           |

|------|-----------|-----------|------|-----------|-----------|

| Tag2 | A+        | A-        | Tag2 | A+        | A-        |

|      |           |           |      |           |           |

| A+   | (A+)+(A+) | 0         | B+   | (A+)+(B+) | (A-)+(B+) |

|      |           |           |      |           |           |

| A-   | 0         | (A-)+(A-) | B-   | (A+)+(B-) | (A-)+(B-) |

Table 2. Possible Voltage Levels in Collision

Figure 25. RF Front End Connection with Circulator

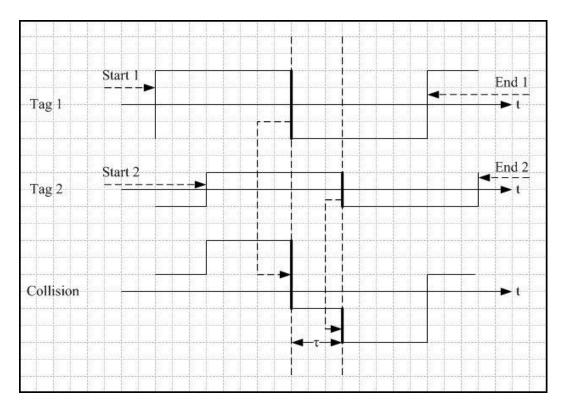

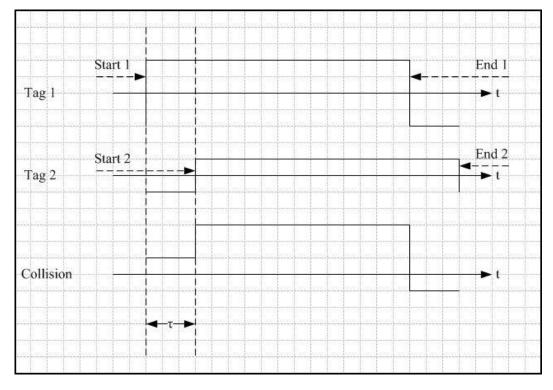

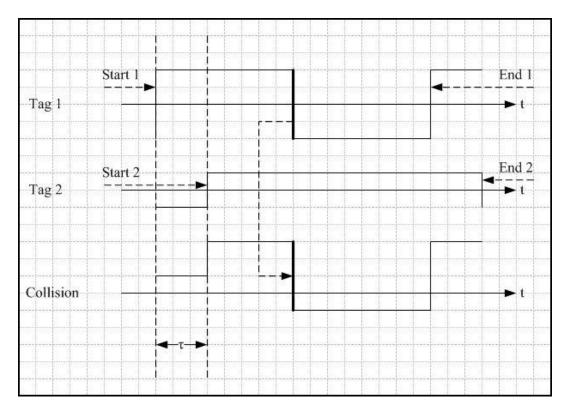

- 3. The two tag responses are added together with a phase shift (delay). The reason for this phase shift is due to two reasons. Due to the physical variations of the capacitors for forming the backscatter signal in each tag, the two tags respond to the reader with different speeds after receiving the Query command. In addition, the signal from each tag propagates through different paths, which are different in distance. The phase shift caused by the propagation path difference equals the quotient of path length difference divided by the speed of light. Because the range of passive RFID communication cannot exceed 10m normally, it is thus minimal and can be neglected in analysis. In summary, the observed phase shift in the collision signal is assumed to be due to the difference in the tag circuitry response speed.

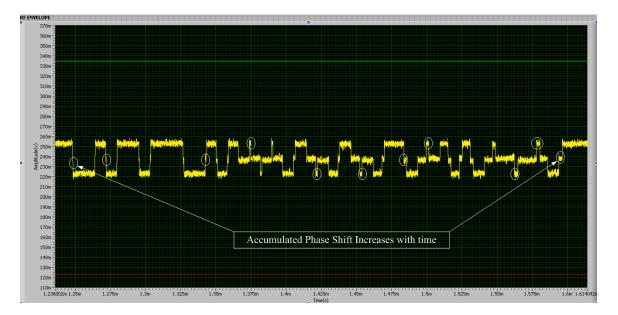

- 4. The phase shift is not fixed during the backscatter, and it accumulates with time. Referring to the Standard, the reason of the accumulated phase shift is due to the tag response frequency deviation (BLF deviation) tolerance. As an example, this phenomenon can be observed in the zoomed tag response in Figure 26. The phase shift at the ending bit of the responses (in this case it is 2.486µs corresponding to the last white circle in Figure 26) is much larger than the initial phase shift (125ns, which implies at the beginning two tags almost respond to the reader simultaneously).

Figure 26. Accumulated Phase Shift

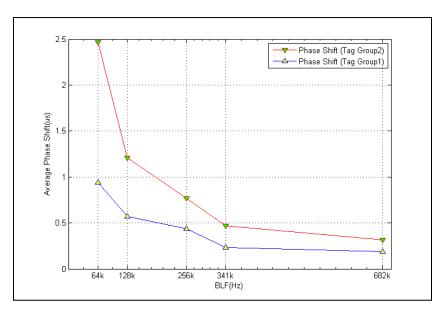

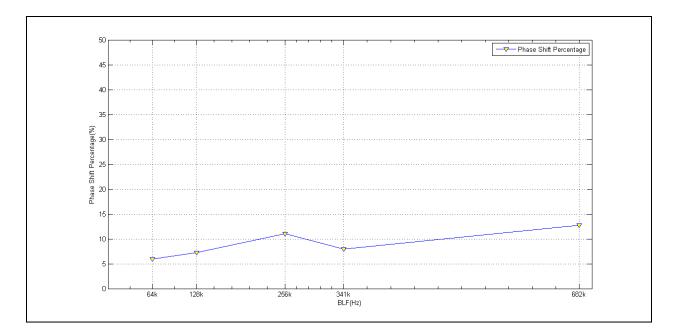

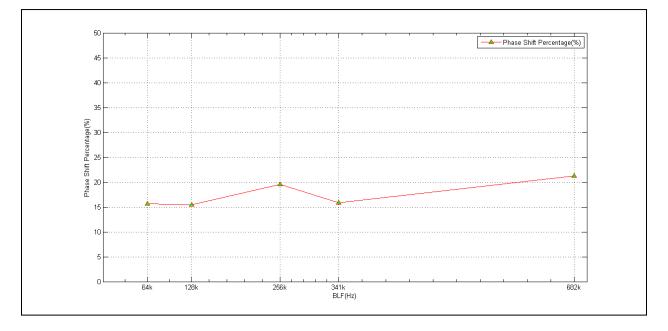

5. The average phase shift is inversely proportional to the tag BLF, and cannot exceed 25% of the symbol duration. This conclusion is obtained by commanding the tags to respond at typical BLF and measuring the length of phase shift as shown in Table 3 and Table 4. The unit of the phase shift in the tables is micro seconds. The data acquisition precision is 0.04µs (25MHz). Table 3 lists the measurement results of the phase shift among seven different tags from manufacturer 1. Table 4 lists the measurement results of the phase shift among seven different tags from manufacturer 2. For each measurement, the tags are placed together with two in a group. Figure 27 shows and compares the average phase shift of tags from each manufacturer at typical BLFs. As shown, the tags from Manufacturer 1 (blue line), and thus the edge locating method is more suitable to resolve the collision of the former. Reciprocally, the amplitude method is more suitable for the latter as will be discussed in Section 4.0 and Section 5.0. Figure 28 and Figure 29 show the percentage of average phase shift in the symbol duration for tags from each manufacturer separately. As

shown, the largest average phase shift takes 21.30% (<25%) of the symbol duration, when the BLF is 682 kHz and manufacturer number 2's tag is selected.

In summary of the features of the collision signal, four voltage levels and a phase shift (observed as short edge transition) exist in the received collision baseband, which is not fixed.

| BLF  | 0     | 1     | 2     | 3     | 4     | 5     | 6     | Avg   | Percentage(over Ts) | Multiple of<br>Precision |

|------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|--------------------------|

| 64k  | 0.341 | 1.334 | 1.163 | 0.536 | 0.592 | 2.44  | 0.191 | 0.942 | 6%                  | 24                       |

| 128k | 0.758 | 1.313 | 0.352 | 0.127 | 0.174 | 0.691 | 0.565 | 0.569 | 7.29%               | 15                       |

| 256k | 0.508 | 0.527 | 0.428 | 0.222 | 0.271 | 0.739 | 0.345 | 0.434 | 11.10%              | 11                       |

| 341k | 0.282 | 0.319 | 0.114 | 0.182 | 0.081 | 0.426 | 0.239 | 0.235 | 8%                  | 6                        |

| 682k | 0.052 | 0.128 | 0.256 | 0.223 | 0.178 | 0.296 | 0.183 | 0.188 | 12.80%              | 4                        |

Table 3. Tag Response Statistics (Manufacturer 1)

Table 4. Tag Response Statistics (Manufacturer 2)

| BLF  | 0     | 1     | 2     | 3     | 4     | 5     | 6     | Avg   | Percentage(over Ts) | Multiple of<br>Precision |

|------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|--------------------------|

| 64k  | 4.072 | 1.023 | 3.69  | 1.444 | 2.679 | 2.9   | 1.436 | 2.463 | 15.70%              | 61                       |

| 128k | 1.303 | 0.72  | 1.409 | 1.328 | 0.959 | 1.429 | 1.3   | 1.207 | 15.50%              | 30                       |

| 256k | 0.389 | 1.105 | 0.558 | 0.5   | 0.888 | 1.127 | 0.795 | 0.766 | 19.60%              | 20                       |

| 341k | 0.704 | 0.461 | 0.265 | 0.54  | 0.476 | 0.338 | 0.491 | 0.468 | 15.90%              | 12                       |

| 682k | 0.417 | 0.264 | 0.376 | 0.183 | 0.377 | 0.408 | 0.169 | 0.313 | 21.30%              | 7                        |

Figure 27. Tag Phase shift vs. BLF (Manufacturer 1 and Manufacturer 2)

Figure 28. Tag Phase shift Percentage in Symbol duration vs. BLF (Manufacturer 1)

Figure 29. Tag Phase shift Percentage in Symbol duration vs. BLF (Manufacturer 2)

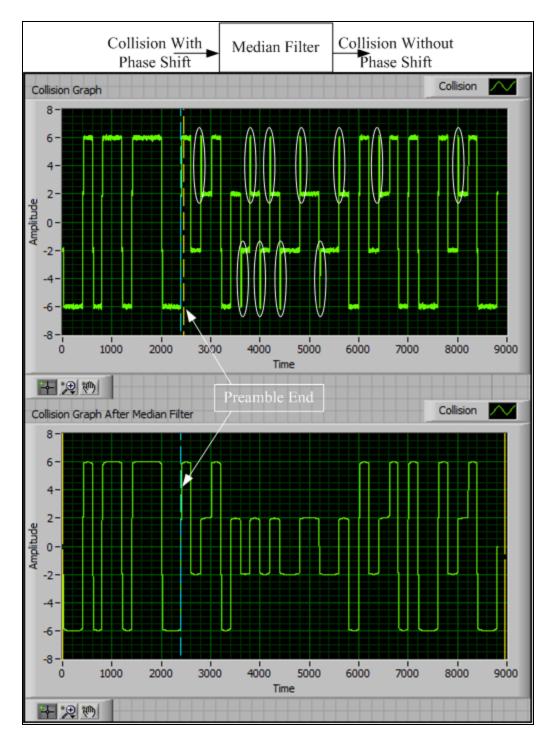

## 3.2 DATA PREPROCESSING

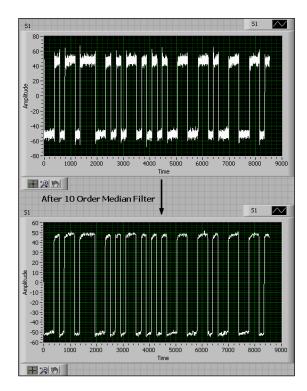

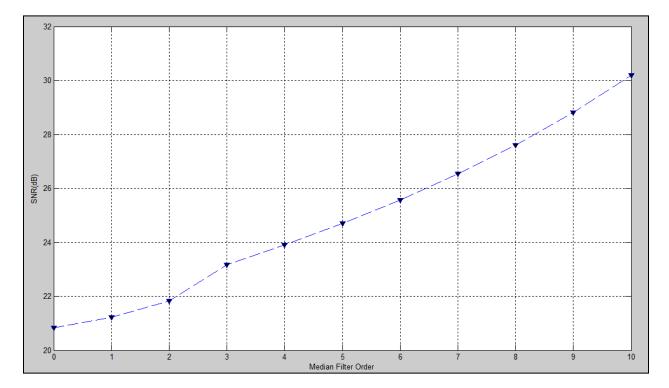

Before the actual collision resolution, a certain amount of data preprocessing is usually necessary to suppress the noise in the acquired collision signal, which is due to the imperfect RF receiving channel characteristics. Unlike the reader, which transmits commands with fixed baseband frequency, the tags BLF can vary in a wide range (normally from 64 kHz to 640 kHz). Therefore, improving the quality of the received baseband signal requires adapting tap coefficients for different typical BLFs if using traditional digital filters in baseband such as FIR and IIR filters. As an alternative to avoid the complicacy of designing FIR/IIR filters, a fixed point median filter using bubble sorting is realized in the FPGA baseband to preprocess the incoming collision signals. As shown in Figure 30, the SNR of the received tag response is significantly improved using a 10 order median filter.

Figure 30. the effect of a 10-order median filter

A trade off can also be made between the complexity of the median filter and its effect as shown in Figure 31. Normally, a median filter with 4 orders, which guarantees a 3dB SNR improvement over original signal, is enough for the application.

Figure 31. Median Filter order vs. Processed Signal SNR

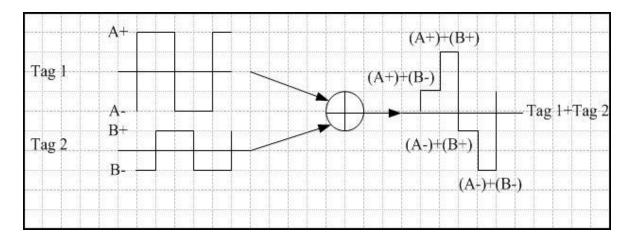

### 4.0 **RESOLUTION METHOD I: DIRECT EDGE LOCATING**

Because a collision results in the linear superposition of each tag's response, the formation of each tag's response is invariant. In addition, because each tag's response potentially arrives at the receiver side at different instants because they normally propagates through different paths (i.e. the phase shift observed in the collision), the edge transition in each tag's response is kept and not overlapped with each other (spaced by the phase shift). Figure 32 illustrates the superposition of two formation-0 symbols, and the two edge transitions are maintained in the collision. As discussed in Section 3.1, the phase shift value is not fixed and can be accumulated over the collision duration due to the tag BLF deviation. Figure 33 illustrates the superposition of two formation-1 symbols. There is no edge transition in the collision because of the absence of edge transition in each individual tag response. Figure 34 illustrates the superposition of one formation-0 symbol and one formation-1 symbol, only one edge transition can be observed in the collision. Therefore, although superimposed, the two tag responses can still be treated as being independent. It is possible to recover the information of each tag by locating the edge transition in each symbol duration from the start of each tag's response. This is based on the exact locating of each tag's start in the collision, which will be discussed in next section.

Figure 32. Superposition of Two Formation-0 Symbols

Figure 33. Superposition of Two Formation-1 Symbols

Figure 34. Superposition of Formation-0 Symbol and Formation-1 Symbol

## 4.1 TAG RESPONSE FRAME ARCHITECTURE

According to the ISO 18000-6C standard, when the tag responds to the reader, it shall precede its data with a preamble. Figure 35 shows the tag response frame architecture after a Query command.

Figure 35. Tag Response Frame Architecture

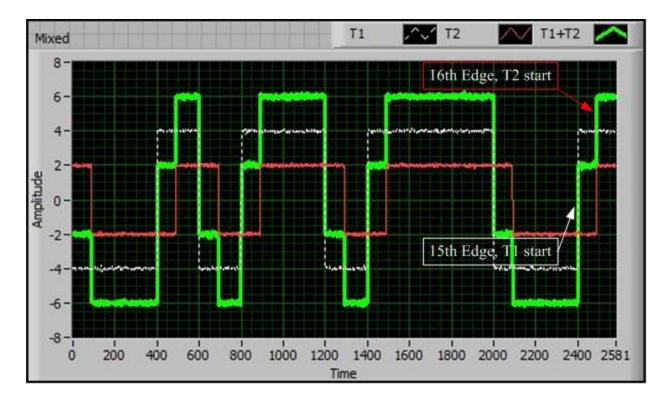

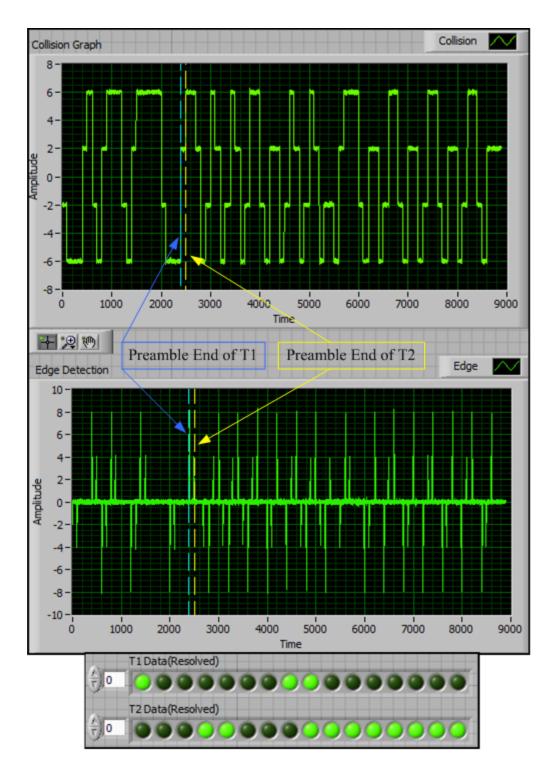

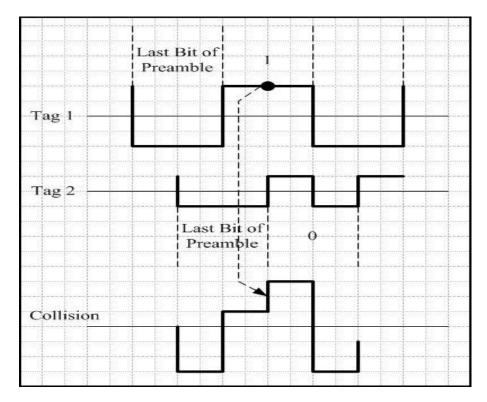

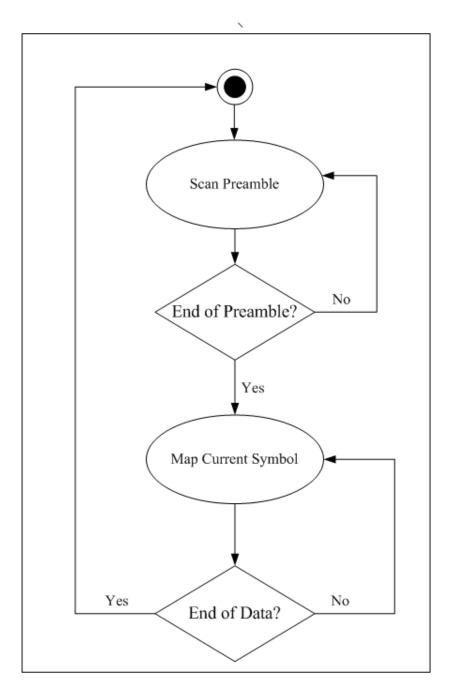

Figure 36 shows the preamble of the tag response when FM0 encoding is employed. In Figure 37 the preamble of the tag response when Miller encoding is employed. The parameter TRext decides whether a 12-zero pilot tone is used in the preamble. While two tags respond to the reader's Query command with their individual RN16, the two RN16 numbers shall be preceded by the same preamble. This information can be utilized to locate the starting edge of each tag's RN16. Because once the formation of the preamble is fixed, the ending of the preamble (i.e. the start of the RN16) can be located by counting to the edge number in the preamble from the start of the preamble. For example, in the FM0 encoding preamble as shown in Figure 36, suppose no pilot tone is used (TRext=0), there are eight edges in the preamble. The ending of the preamble can thus be located by counting eight edges from the start edge of the preamble. In the collision signal, because the two tag responses are linearly superimposed with a phase shift, the ending of each preamble can be located by counting to the edge number in the preamble from the start of each preamble in the collision. Suppose the preamble contains N edges, the ending of the individual tag response are at the position of the (2N-1)<sup>th</sup> and the 2N<sup>th</sup> edge in the collision signal. Figure 38 shows an example of a collision signal consisting of two tag preambles in FM0 without a pilot tone. Because each tag's preamble has eight edges, the ending of the tag 1 and tag 2 responses are at the 15<sup>th</sup> edge and 16<sup>th</sup> edge in the collision signal. The ending location for Miller encoding is similar.

Figure 36. Tag Response Preamble in FM0

Figure 37. Tag Response Preamble in Miller Subcarrier

Figure 38. Ending Location of Preambles in Collision

#### 4.2 ALGORITHM DESCRIPTION

After locating the end of the preamble (i.e. the starting of the RN16 in the tag responses), each bit in the RN16 of individual tag corresponding to one symbol duration can be recovered. The direct edge locating algorithm for two-tag RN16 collision resolution is listed in Table 5. This algorithm checks the collision signal one sample point at a time, and thus it is an online algorithm.

#### Table 5. Direct Edge Locating Algorithm

- Locating the preamble ending edge of tag 1 and tag 2 separately in the collision signal, denoted as St1 and St2.

- ii. Start from St1, check the existence of edge transition at time instant St1+ $k \times T_s$  (k= 1, 3, 5, ..., 31), which corresponds to the middle of each symbol in tag 1's RN16 ( where  $T_s$  is the symbol duration). If an edge transition is found at the specified position, the corresponding data bit in the RN16 is in formation 0. Otherwise, it is in formation 1.

- iii. Start from St2, check the existence of edge transition at time instant  $St1+k\times T_s$  (k=1, 3, 5, ..., 31), which corresponds to the middle of each symbol in tag 2's RN16 (where  $T_s$  is the symbol duration). If an edge transition is found at the specified position, the corresponding data bit in the RN16 is in formation 0. Otherwise, it is in formation 1.

## 4.3 ALGORITHM SIMULATION

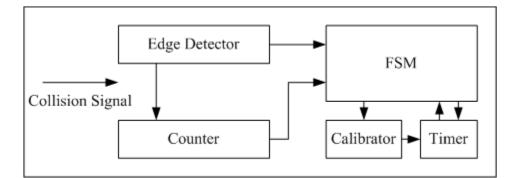

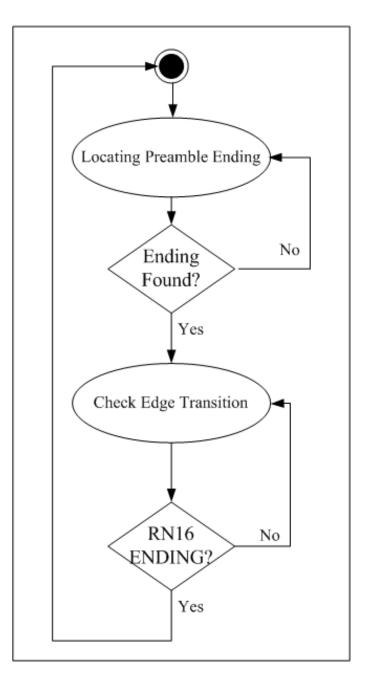

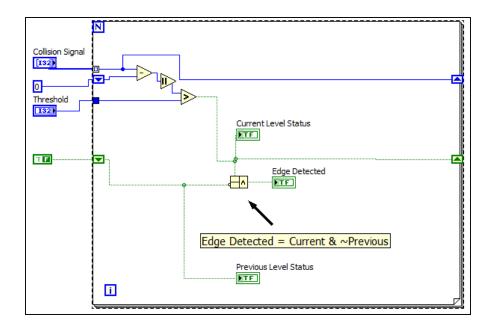

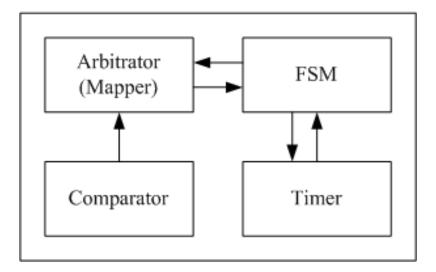

The direct edge locating algorithm is simulated using LabVIEW on the Host PC. It is implemented by using a finite state machine (FSM) as shown in Figure 39. The edge detector detects each edge transition in the collision signal, and sends out handshake signals to the

counter and the FSM once an edge is found. The counter records the number of the edges detected. A timer counts the elapsed time since the start of the RN16, and notifies the FSM once it reaches the middle of a symbol as specified in Table 5. Because of the tag response BLF deviation, the exact location of the symbol middle edge transition deviates around the theoretic symbol center at  $St+k\times T_s(k=1, 3, 5, ..., 31)$ . Therefore, if using the fixed starting point St and increasing it by the fixed symbol duration to locate the edge transitions, the probability of error increases accordingly as the time reaches later symbols in the collision. To increase the robust property of the algorithm, a calibrator is employed to align the timer and FSM to the exact starting point of the incoming symbol after successfully resolving the previous collision symbol. Figure 40 shows the state transition of the FSM control logic.

Figure 39. Implementation of the Algorithm using FSM

Figure 40. State Transition of the FSM

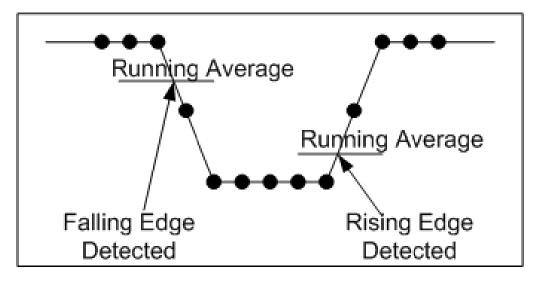

The edge detector is implemented in two ways. The first method is based on calculating the running mean of the input signal. Figure 41 shows the work flow of the edge detection using the running mean of the signal samples. The edge detector keeps recording the running mean of the magnitude of the latest 5 signal sample points, and updates the average of the positive peak and the negative peak online. If the previous signal point is below the average while the current signal point is above the average, a rising edge is detected; the falling edges are found in a similar manner.

Figure 41. The Running Mean Calculation

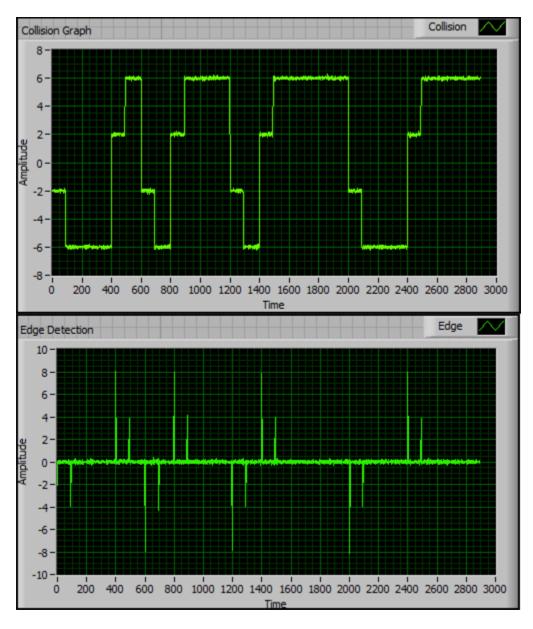

The second method is to calculate the differentiation of the input signal. Because the edge is a singular point in the signal, the corresponding differentiation appears as a spike. The differentiation is calculated using Eq.4.1. In simulation, the edge transition time of the tag response normally takes no more than two sampling periods ( $0.08\mu$ s), the  $d_t$  is set as 1. Therefore, the differentiation actually equals the difference of the two adjacent sampling points in the signal. Figure 42 shows the preamble part of an FM0 collision and its corresponding differentiation. However, in reality it is possible that the edge transitions in the tag response can take more than one sampling periods. In this case, Eq.4.1 outputs a pulse rather than an impulse if  $d_t$  is still set to 1. To guarantee the algorithm's compatibility with the less steep edge transition scenario without dynamically changing the unpredictable  $d_t$ , the algorithm detects only the rising edge of the differentiation output as shown in the LabVIEW code segment in Figure 43.

Differentiation =

$$\frac{y(t) - y(t - dt)}{dt}$$

(Eq. 4.1)

Figure 42. The Differentiation of Collision signal

Figure 43. Collision Signal Edge Detection (LabVIEW Code Segment)

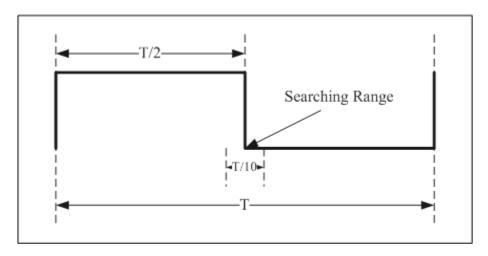

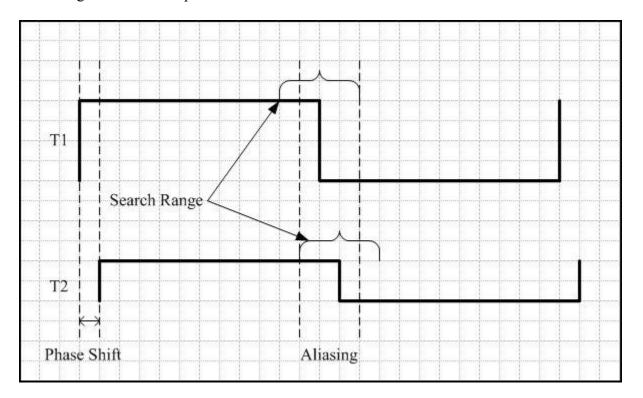

Because the variation of symbol duration exists in the practical tag response, the middle symbol edge transition can appear in a range around the supposed  $St+k\times T_s$  (k=1, 3, 5, ..., 31) positions rather than exactly at the middle of each symbol. Therefore, the FSM searches a range around the middle of each symbol for the edge transition rather than at the exact middle position. The search range is of a length of 5% of the symbol duration centered at the middle of each symbol. Figure 44 shows the searching range.

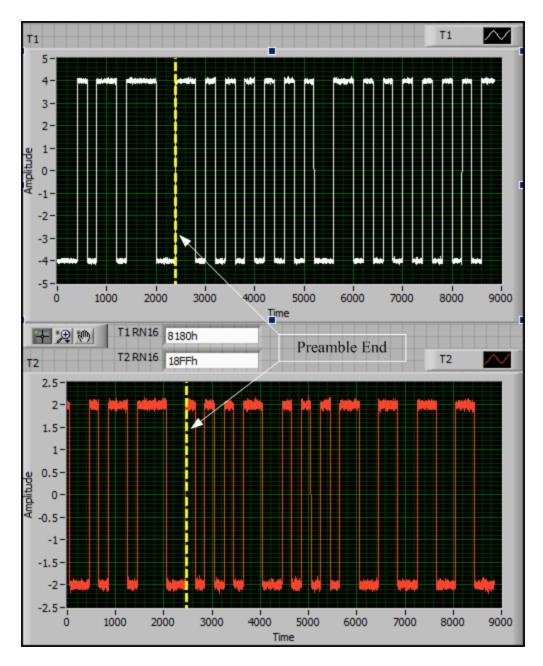

Figure 44. The Differentiation of Collision signal

In the simulation, the symbol duration is set as 400 sample points, and the search range is thus 40 data points centered at the middle of each symbol. Two RN16 (8180h and 18FFh) encoded with FM0 are inputted to simulate the two tag responses separately. A Gaussian white noise with 5% of the signal strength is added to each tag response to simulate the channel noise. Figure 45 shows the two tag responses with noise. Figure 46 shows the collision signal and its corresponding differentiation showing the edges. The LEDs in Figure 46 show the recovered data from the collision, the LED turned on corresponds to the formation-1 symbol while the LED turned off corresponds to the formation-0 symbol. As a comparison, the recovered data are exactly the inputted RN16s.

Figure 45. Two Tag Responses

Figure 46. Collision Signal and its Differentiation

There are two limitations of the algorithm:

As the BLF of tag increases, the phase delay decreases as shown in Section 3, which requires more accuracy of the hardware timer to locate the searching range for each symbol. It is also possible that the searching range of the current symbol for each tag may overlap (as shown in Figure 47), which requires the shrinking of the searching range. This limitation can be removed by using the amplitude mapping which is designed for tags with minimal phase shift as will be discussed in Section 5.0.

Figure 47. Searching Range Overlap

2. The phase shift cannot exceed 50% of the symbol duration, otherwise the symbol beginning of the leading tag will interfere with the middle of the lagging tag. This is illustrated in Figure 48. In Figure 48, the phase shift is exactly 50%, and the formation 1 symbol in Tag 1 is arbitrated as formation 0 due to the edge transition appeared in the

search range in the collision, which is actually is beginning edge of Tag 2's RN16. This limitation can be overcome by adjusting software parameters for the case in which the phase shift becomes larger than 50% of the symbol duration provided that it is not exactly 50%. However, based on the measurement of the practical phase shift at typical tag BLFs as shown in Figure 28 and Figure 29 of Section 3.0, the phase shift cannot exceed 25% of the symbol duration.

Figure 48. Miss Arbitration

## 4.4 ALGORITHM IMPLEMENTATION

When simulated in LabVIEW on the host PC, the direct edge locating algorithm is developed as an online function for convenient FPGA transplant: The program reads in the collision signal and performs point-by-point processing on it. LabVIEW provides its FPGA compilation environment in its LabVIEW FPGA module, which allows for direct translation of LabVIEW code into lowlevel HDL code. The floating-point numbers used in the host PC LabVIEW need to be transferred to fixed point numbers in LabVIEW FPGA module.

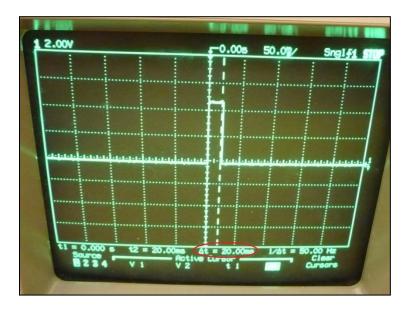

Because most of the computation involved in the algorithm is Boolean for the arbitration logic and countering for timers, the NI5640R FPGA baseband used in the data acquisition platform featuring a Xilinx Virtex-II Pro XC2VP30 FPGA is capable. The implementation verification flow is shown in Figure 49. Two individual tag responses of typical BLF are acquired by the data acquisition platform and mixed to generate the collision signal as the test bench on Host PC. The typical BLFs are 64 kHz, 128 kHz, 256 kHz, 341 kHz and 682 kHz. The test bench signal is then streamed into the FPGA, and stored in the FPGA block memory for play back. The resolution result generated by the FPGA is streamed back to the host PC for visualization and comparison with the original tag responses. The FPGA also generates a time stamp once it finishes the resolution, which shows the processing time.

Figure 49. Verification Flow of Algorithm Implementation

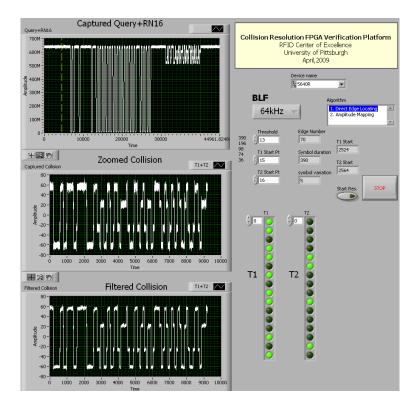

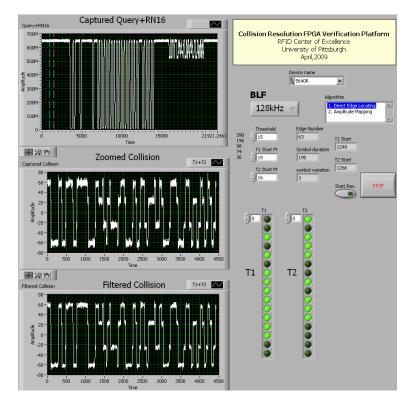

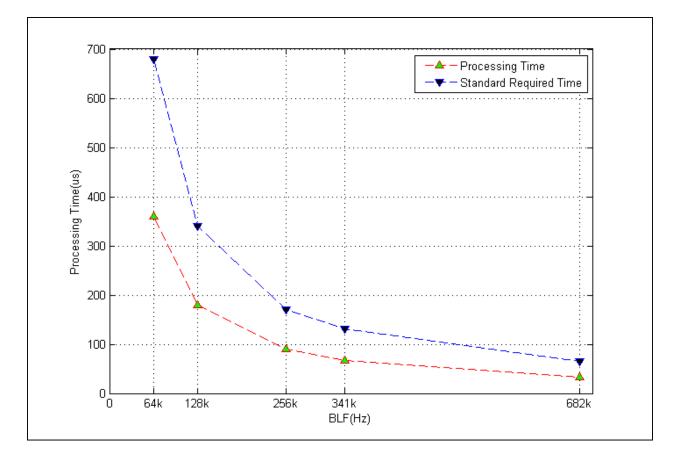

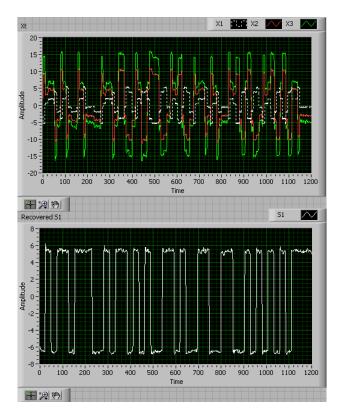

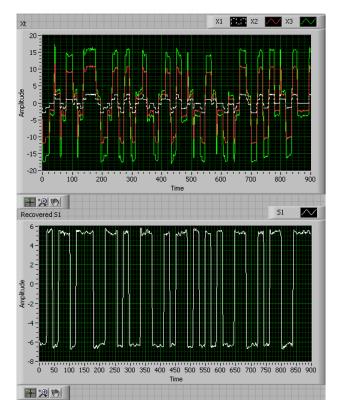

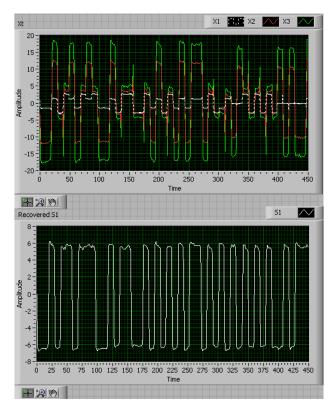

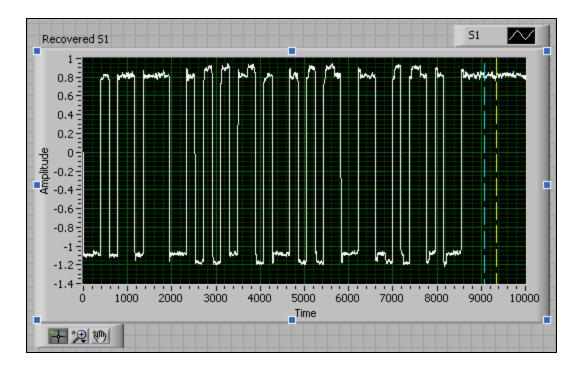

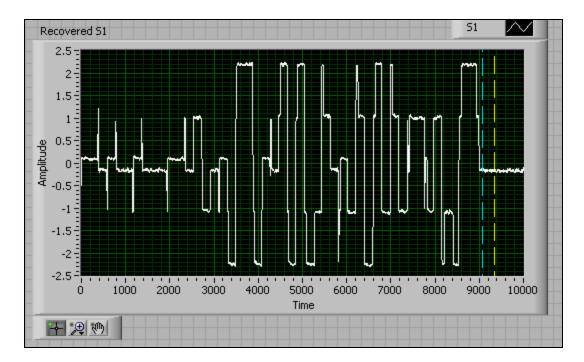

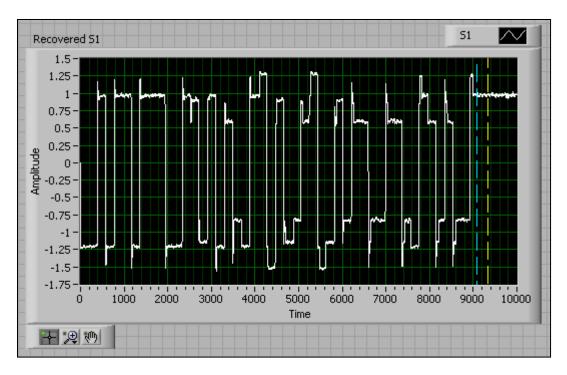

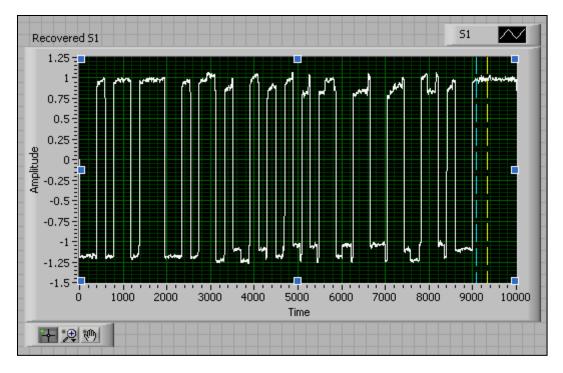

Figure 50, Figure 51, Figure 52, Figure 53, Figure 54 show the resolution results on actual tag collision signal at each typical tag BLF.

Figure 53. Resolution Result When BLF=341 kHz

Figure 54. Resolution Result When BLF=682 kHz

The FPGA resource utilization reported by Xilinx XST FPGA compiler is listed in Table

6. As shown, the design only utilizes 20% of the total FPGA logic slices.

| Compilation Summary                                                                                                                                                                                                                                                                              |                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|