# DESIGN & IMPLEMENTATION OF A REAL-TIME, SPEAKER-INDEPENDENT, CONTINUOUS SPEECH RECOGNITION SYSTEM WITH VLIW DIGITAL SIGNAL PROCESSOR ARCHITECTURE

by

# Wai-Ting Ng

B.S. in Engineering, University of Pittsburgh, 2004

Submitted to the Graduate Faculty of

School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science

University of Pittsburgh

# UNIVERSITY OF PITTSBURGH SCHOOL OF ENGINEERING

This thesis was presented

by

Wai-Ting Ng

It was defended on

July 21, 2006

and approved by

Alex K. Jones, PhD, Assistant Professor

Steve P. Levitan, PhD, Professor

Committee Chair: Raymond R. Hoare, PhD, Assistant Professor

Copyright © by Wai-Ting Ng 2006

# DESIGN & IMPLEMENTATION OF A REAL-TIME, SPEAKER INDEPENDENT, CONTINUOUS SPEECH RECOGNITION SYSTEM USING A VLIW DIGITAL SIGNAL PROCESSOR ARCHITECTURE

Wai-Ting Ng

University of Pittsburgh, 2006

This thesis explores the feasibility of mapping a real-time, continuous speech recognition system onto a multi-core Digital Signal Processor architecture. While a pure hardware solution is capable of implementing the entire recognition process in real-time, the design process can be lengthy and inflexible to changes. However, a low-end embedded processor such as ARM7 is insufficient to execute in real-time. As a result, a more flexible and powerful DSP solution w ith Texas Instrum ents' C 6713 m ulti-core DSP is used to exploit the instruction level parallelism within the speech recognition process. By exploiting the parallelism using 7 optimization techniques, the performance of the recognition process can be real-time on a 300 MHz DSP for a 1000 word vocabulary.

At its core, continuous speech recognition is essentially a matching problem. The recognition process can be divided into four major phases: Feature Extraction, Acoustic Modeling, Phone Modeling and Word Modeling. Each phase is analyzed in detail to identify performance issues. In short, the major issues are its massive computations and large memory bandwidth. After applying various optimizations, the overall computational performance has improved from about 15 times slower than real-time to 1.6 times faster than real-time with the hardware. Through utilization of Direct Memory Access and larger cache memory, the memory bandwidth problem can be solved. The conclusion is that a multi-core DSP running at 300 MHz would be sufficient to implement a 1000 word Command & Control type application using the optimization techniques described in this thesis.

# TABLE OF CONTENTS

| 1.0 | IN  | rodu  | UCTION                                      | 1    |

|-----|-----|-------|---------------------------------------------|------|

|     | 1.1 | THE   | PROBLEM                                     | 2    |

|     | 1.2 | THE   | SOLUTION                                    | 3    |

|     | 1.3 | CON   | TRIBUTIONS & ORGANIZATION OF THE THESIS     | 5    |

|     |     | 1.3.1 | Organization of the Thesis                  | 5    |

| 2.0 | LIT | ERAT  | URE REVIEW                                  | 8    |

|     | 2.1 | SPHI  | INX 3                                       | 9    |

|     | 2.2 | DIGI  | TAL SIGNAL PROCESSORS                       | . 10 |

|     |     | 2.2.1 | Very-Long-Instruction-Word Architecture     | . 11 |

|     |     | 2.2.2 | Memory Architecture                         | . 11 |

|     |     | 2.2.3 | Direct Memory Access                        | . 12 |

|     | 2.3 | DEV   | ELOPMENT PLATFORM SPECIFICATIONS            | . 12 |

|     |     | 2.3.1 | Texas Instruments C6713 DSP                 | . 13 |

|     |     | 2.3.2 | Memory System                               | . 15 |

|     | 2.4 | OPT   | IMIZATIONS OVERVIEW                         | . 16 |

|     |     | 2.4.1 | Variable Registering                        | . 16 |

|     |     | 2.4.2 | Constant Propagation                        | . 16 |

|     |     | 2.4.3 | Data Dependency                             | . 17 |

|     |     | 2.4.4 | Loop Carried Dependency and Memory Aliasing | . 17 |

|     |     | 2.4.5 | Software Pipeline                           | . 20 |

|     |     | 2     | .4.5.1 Instruction Latency                  | . 23 |

|     |      | 2.4.6 | Loop   | Unrolling To Balance Resources          | . 24 |

|-----|------|-------|--------|-----------------------------------------|------|

|     |      | 2.4.7 | Packe  | d Data Memory Access                    | . 26 |

| 3.0 | ov   | ERVIE | W OF   | AUTOMATIC SPEECH RECOGNITION AND SYSTEM |      |

| DE  | SIGN | SPEC  | IFICA  | TIONS                                   | . 28 |

|     | 3.1  | FOR   | MAL I  | DEFINITION                              | . 29 |

|     | 3.2  | BLO   | CK LE  | VEL OVERVIEW                            | . 30 |

|     | 3.3  | Perfo | rmanc  | e Characteristics                       | . 33 |

|     | 3.4  | TIMI  | NG R   | EQUIREMENT                              | . 35 |

|     | 3.5  | PERI  | FORM   | ANCE MEASUREMENTS                       | . 36 |

|     |      | 3.5.1 | Regis  | ter Utilization                         | . 38 |

| 4.0 | FE   | ATURE | E EXT  | RACTION                                 | . 40 |

|     | 4.1  | PRE-  | EMPE   | IASIS                                   | . 41 |

|     | 4.2  | WIN   | DOWI   | NG                                      | . 44 |

|     | 4.3  | POW   | ER SP  | ECTRUM                                  | . 48 |

|     | 4.4  | MEL   | SPEC   | ΓRUM                                    | . 52 |

|     | 4.5  | MEL   | CEPS   | ΓRUM                                    | . 55 |

|     | 4.6  | DYN   | AMIC   | FEATURE: DELTA, DOUBLE DELTA            | . 56 |

|     | 4.7  | PERI  | FORM   | ANCE SUMMARY                            | . 57 |

| 5.0 | AC   | OUSTI | С МО   | DELING PERFORMANCE                      | . 59 |

|     | 5.1  | IMPI  | LEME   | NTATIONS OF GAUSSIAN EVALUATION         | . 62 |

|     |      | 5.1.1 | Indivi | dual Component Approach                 | . 63 |

|     |      | 5     | .1.1.1 | Algorithm Characteristics               | . 66 |

|     |      | 5     | .1.1.2 | Baseline Performance                    | . 67 |

|     |      | 5     | .1.1.3 | Optimization: Variable Registering      | . 69 |

|     |      | 5     | .1.1.4 | Optimization: Constant Propagation      | . 69 |

|     |      | 5     | .1.1.5 | Optimization: Software Pipeline         | . 70 |

|     |      | 5.1.1.6 Optimization: Removing Memory Aliasing                      | 72  |

|-----|------|---------------------------------------------------------------------|-----|

|     |      | 5.1.1.7 Optimization: Loop Unrolling by 3x                          | 73  |

|     |      | 5.1.1.8 Optimization: Packed Data Memory Access                     | 76  |

|     |      | 5.1.1.9 Optimization: Loop Unrolling by 2x                          | 76  |

|     |      | 5.1.1.10 Individual Component Approach Performance Summary          | 79  |

|     |      | 5.1.2 Individual Dimension Approach                                 | 80  |

|     |      | 5.1.2.1 Optimization: Software Pipeline                             | 82  |

|     |      | 5.1.2.2 Removing Memory Aliasing                                    | 83  |

|     |      | 5.1.2.3 Optimizations: Packed Data Memory Load and Loop Unrolling B | y   |

|     |      | 2x                                                                  | 85  |

|     |      | 5.1.2.4 Optimization: Loop Unrolling by 4x, 6x And Summary          | 88  |

|     | 5.2  | MEMORY BANDWIDTH ISSUE                                              | 89  |

|     |      | 5.2.1 The Problem                                                   | 89  |

|     |      | 5.2.2 The Solution                                                  | 90  |

| 6.0 | PH   | ONE AND WORD MODELING                                               | 91  |

|     | 6.1  | PHONE MODELING THEORY                                               | 94  |

|     | 6.2  | PHONEMES EVALUATION                                                 | 95  |

|     | 6.3  | WORD ORGANIZATION                                                   | 98  |

|     | 6.4  | IMPLEMENTATION AND RESULT                                           | 99  |

| 7.0 | co   | NCLUSION                                                            | 102 |

|     | 7.1  | MAJOR CONTRIBUTIONS                                                 | 103 |

|     | 7.2  | FUTURE WORK                                                         | 105 |

| API | PENI | DIX SOURCE CODE                                                     | 106 |

| RIR | LIO  | CRAPHY                                                              | 155 |

# LIST OF TABLES

| Table 2.1: Memory systems and configurations summary                         | 5 |

|------------------------------------------------------------------------------|---|

| Table 4.1: Performance summary for Pre-Emphasis                              | Ļ |

| Table 4.2: Performance summary for Windowing                                 | } |

| Table 4.3: Performance summary for Power Spectrum (FFT)                      | 2 |

| Table 4.4: Performance summary for Mel Spectrum54                            | ļ |

| Table 4.5: Performance summary for Mel Cepstrum56                            | ĺ |

| Table 4.6: Performance summary for Dynamic Feature                           | 7 |

| Table 4.7: Optimization summary for FE                                       | } |

| Table 4.8: Performance summary for FE                                        | } |

| Table 5.1: Calculation statistic in AM for various speech corpuses           | 2 |

| Table 5.2: A list of important characteristics of the Gaussian Evaluation 67 | 7 |

| Table 5.3: Summary of different optimization results79                       | ) |

| Table 5.4: Summary of resource utilizations with different optimizations79   | ) |

| Table 5.5: Performance Summary for the Individual Dimension Approach         | } |

| Table 5.6: Resource Utilization Summary89                                    | ) |

| Table 6.1: Example of words in phonetic representation                       | 2 |

| Table 6.2: HMM Characteristics and Performance                               | L |

| Table 7.1: Summary of results of all processing blocks                       | 3 |

# LIST OF FIGURES

| Figure 2.1: A simplified block diagram of the C6713 DSK showing the key components         | . 13 |

|--------------------------------------------------------------------------------------------|------|

| Figure 2.2: Illustrates the operation(s) support by different functional unit              | . 13 |

| Figure 2.3: A architectural diagram showing the functional units and registers arrangement | 14   |

| Figure 2.4: An example of data dependency                                                  | . 17 |

| Figure 2.5: A code sample illustrating loop carried dependency                             | . 18 |

| Figure 2.6: Sample source code                                                             | . 18 |

| Figure 2.7: Generated assembly from source code in Figure 2.6                              | . 19 |

| Figure 2.8: Example of a software pipelined loop                                           | . 20 |

| Figure 2.9: A feedback table generated with the source code showing in Figure 2.6          | . 21 |

| Figure 2.10: Example of delay slot and functional unit latency of some C67x instructions   | . 24 |

| Figure 2.11: Modified source code with restrict type qualifier                             | . 25 |

| Figure 2.12: Feedback table with modified source code                                      | . 26 |

| Figure 2.13: Modified code with new function to assert data are double-word-aligned        | . 27 |

| Figure 2.14: Assembly showing two LDWs combined into one double load LDDW                  | . 27 |

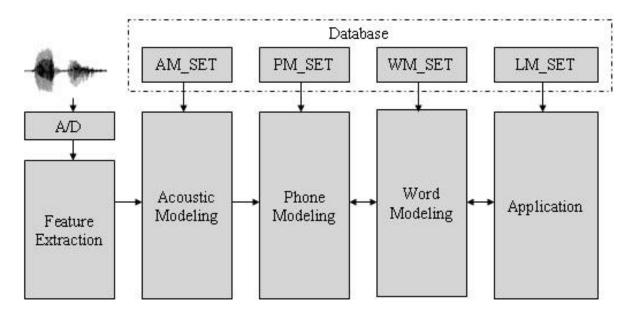

| Figure 3.1: Basic ASR system in block levels                                               | . 28 |

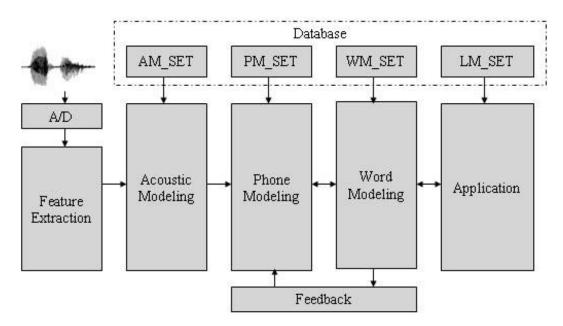

| Figure 3.2: Block diagram for ASR with Feedback                                            | . 32 |

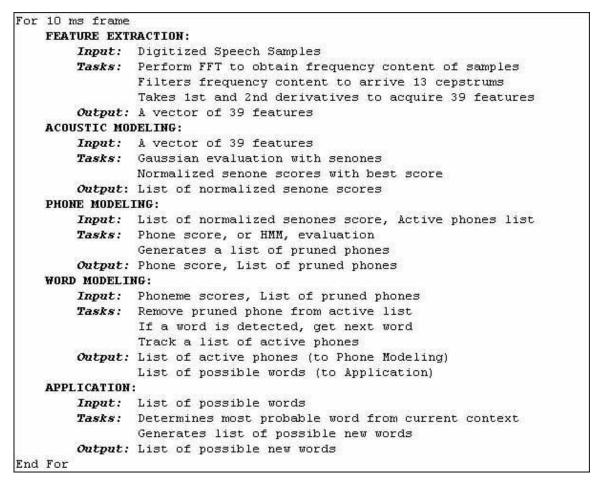

| Figure 3.3: Block level pseudo-code for data flow                                          | . 32 |

| Figure 3.4: An example of a compiler generated register utilization table                  | . 38 |

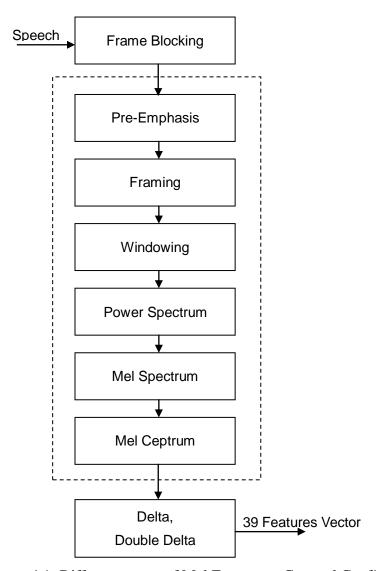

| Figure 4.1: Different stages of Mel Frequency Cepstral Coefficients                        | , 41 |

| Figure 4.2: Implementation code for pre-emphasis                                           | . 42 |

| Figure 4.3: Optimized assembly showing pipelined instruction                               | . 43 |

| Figure 4.4: Optimized result showing in the software pipeline table            | 43 |

|--------------------------------------------------------------------------------|----|

| Figure 4.5: Sphinx version source code for Windowing function                  | 45 |

| Figure 4.6: Optimized source code for Windowing function                       | 46 |

| Figure 4.7: Optimized assembly for Windowing function                          | 46 |

| Figure 4.8: Software pipeline feedback table for Windowing function            | 47 |

| Figure 4.9: Pre-FFT stage source code for Power Spectrum function              | 49 |

| Figure 4.10: Generates twiddle-factors source code from TI                     | 49 |

| Figure 4.11: Pre-calculate the sin and cosine values during initialization     | 50 |

| Figure 4.12: Source code for Square Magnitude                                  | 51 |

| Figure 4.13: Software pipeline feedback after applying different optimizations | 51 |

| Figure 4.14: Source code for Mel Spectrum                                      | 53 |

| Figure 4.15: Software pipeline feedback table for Mel Spectrum                 | 54 |

| Figure 4.16: Source code for Mel Cepstrum                                      | 55 |

| Figure 5.1: Source code for Individual Component Approach                      | 64 |

| Figure 5.2: Data Flow Diagram for the Gaussian Evaluation core                 | 65 |

| Figure 5.3: Generated assembly with no optimizations                           | 68 |

| Figure 5.4: Software pipeline feedback table                                   | 71 |

| Figure 5.5: Generated assembly with the Loop Dependency Bound identifier       | 72 |

| Figure 5.6: Source code for the core Gaussian evaluation                       | 73 |

| Figure 5.7: Modified source code with the pragma instruction                   | 74 |

| Figure 5.8: Feedback result after performing loop unrolling                    | 75 |

| Figure 5.9: Modified source code with loop unrolling factor of 2               | 77 |

| Figure 5.10: The result of unrolling the loop by 2                             | 78 |

| Figure 5.11: Source code with the Individual Dimension Approach                | 81 |

| Figure 5.12: Software pipeline result with the individual dimension approach   | 83 |

| Figure 5.13: Assembly code showing the Loop Carried Dependency Path            | 83 |

| Figure 5.14: Modified source code with the use of restrict keyword               | <b>. 8</b> 4 |

|----------------------------------------------------------------------------------|--------------|

| Figure 5.15: Feedback result after removing memory aliasing                      | . 85         |

| Figure 5.16: Modified source code with double-word load and loop unrolling of 2x | . 86         |

| Figure 5.17: Performance after applying double-word load and loop unrolling      | . 87         |

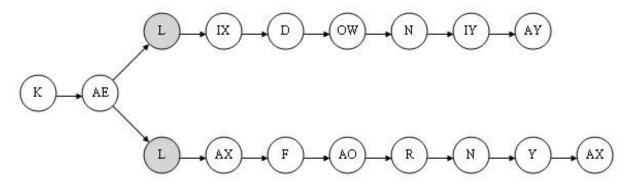

| Figure 6.1: An example of word decomposed into multiple phones                   | . 91         |

| Figure 6.2: An example of a subtree with two words.                              | . 93         |

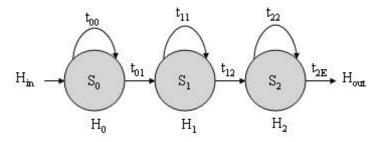

| Figure 6.3: A simple 3-state HMM                                                 | . 94         |

| Figure 6.4: Source code for the core part of the HMM evaluation function         | . 99         |

#### 1.0 INTRODUCTION

Voice communication is one of the most primary and fundamental interactions between human beings in everyday life. The technological curiosity to build a machine that understands humans and the desire to simplify daily life through automation have driven the speech research community for the past few decades. Speech recognition began as people tried to allow computers to recognize isolated words. As progress has been made though the years, researchers have shifted focus to continuous speech recognition. With the increased understanding of human speech, significant improvements have been made within different areas of Automatic Speech Recognition (ASR). Recent advancements in computer hardware has enabled more practical software-based speech recognition applications to emerge. Commercial software running on desktop computers is slowly becoming more mature and usable. Most cellular phones are equipped with a simple recognition process that recognizes names and digits fairly accurately. However, speech-enabled applications have not yet been integrated into our daily life due to the fact that the efficiency level of embedded speech recognition applications is still low. In order to incorporate more speech-enabled applications into human life and to automate daily tasks, recognition processes must run on a portable device, and these processes must also be able to recognize continuous speech with high accuracy in real-time.

#### 1.1 THE PROBLEM

Simply stated, the problem of continuous Automatic Speech Recognition is that the process is computationally intensive. Many approaches have been taken to solve this problem but none have yet tried to map the entire recognition process on a multi-core DSP.

Speech recognition started with the attempt to decode isolated words. As time progressed, research focus has shifted to continuous speech. With years of research effort, the start-of-the-art recognition systems are capable of recognizing continuous speech with acceptable accuracy. Furthermore, recognition systems that are built for Command and Control type applications have achieved accuracy greater than 90% [2]. However, most of these recognition systems are designed to run on a computer system with a high-clock-rate General Purpose Processor (GPP) and a large amount of memory bandwidth available.

The difficulties of recognizing continuous speech can be summarized into the following areas: large variable nature of speech signal, difference in speakers, dictionary size and environment distortions. Through years of study, researchers have obtained a better understanding of speech signals. Statistical models trained by people for thousands of hours are used to compensate for different speakers. Environment distortions can be minimized using various signal processing techniques. Among these difficulties, dictionary size has the most important effect on the system performance.

At its core, speech recognition is a matching problem between observed signals and a set of pre-defined words, or word library. The larger set of the pre-defined words implies that more computations are required. More importantly, the time available to complete all computations remains the same regardless of the dictionary size. State-of-the-art systems are mostly software based that are designed to run on computer platforms with the General Purpose Processor architecture. One limitation of using these GPP architectures is the lack of multiple processing units to take advantage of the instruction parallelism within the

recognition process. Furthermore, speech recognition process requires massive amounts of memory bandwidth between the processing unit and memory. The cache architectures that are designed to provide quick access to recently accessed data can take advantage of the locality for parts of the recognition process where data accesses are more sequential. However, some parts of the process inherit a highly irregular memory access pattern where cache would be less useful. For the GPP systems, these limitations are usually compensated by the high clock rate processor and the large amount of cache memory available.

These software-based systems produce relatively good results as long as a high-clock-rate processor is available. However, such a machine might not always be available or even desired for certain applications. For example, mobile phones and PDAs are platforms where hardware resources are limited. Various approaches have been taken to scale down the number of computations. Using a smaller sized dictionary reduces the number of computations but also reduces the usability of the application. Another approach is to reduce the bit precision of the calculation.

#### 1.2 THE SOLUTION

The process of ASR is generally divided into multiple stages. The first stage typically involves extracting useful information from the voice signal. The next few stages take the extracted information and perform word matching at different levels. The differences in functional characteristics and requirements of each stage creates an uneven amount of processing cycle consumption. One study [1] has shown that the Acoustic Modeling stage can potentially consume up to 95% of the entire process. As a result, more effort is spent investigating and optimizing areas that consume the majority of processing time.

A close examination reveals that speech algorithms inherit substantial instruction-level parallelism (ILP) at various stages of the process. It has been shown that custom designed hardware with a deep pipeline is capable of implementing a 1000 word Command and Control based application in real-time [1]. However, custom designed hardware lacks the flexibility for changes due to the evolutionary process of speech recognition. Also, the design cycle of such custom architecture is rather lengthy. This thesis investigates a more flexible software approach with a multi-core Digital Signal Processor (DSP) architecture. This thesis utilizes the Texas Instruments TMS320C6713 DSP Starter Kit as a demonstration that real-time Automatic Speech Recognition is possible an embedded DSP processor.

DSP technology has improved significantly in recent years. Advanced architecture such as Very Long Instruction Word (VLIW) enables a single DSP to execute multiple instructions simultaneously. The VLIW architecture is designed specially for computationally intensive applications such as speech recognition. Furthermore, these DSPs are usually equipped with highly efficient and flexible cache architecture along with multiple channel Direct Memory Access (DMA). With careful design and optimization, the cache system and DMA can be used together to solve the memory bandwidth issue.

This research focuses on the exploitation of the parallelism within speech recognition for multi-core DSP and predicts the resources requirement for real-time. The result has shown that by taking advantage of the multiple execution units and by using various compiler optimizations, a single DSP running at 300 MHz with at least 3MB of on-chip memory would be sufficient to implement a 1000 word Command and Control based application running in real-time. This research will expand the applicability of speech recognition from high clock rate general purpose computers to low-power, portable devices such as cellular phones and PDAs.

#### 1.3 CONTRIBUTIONS & ORGANIZATION OF THE THESIS

The major contributions of this thesis are:

- Redesigned and mapped a real-time, speaker independent, command and control based speech recognition system onto a multi-core DSP architecture. Also examined and optimized each stage of the recognition process including Feature Extraction, Acoustic Modeling, Phone & Word Modeling.

- Optimized Feature Extraction using various optimization techniques including Memory Aliasing, Software Pipeline, Loop Unrolling and Packed Data Memory Access.

- Investigated Acoustic Modeling in two different approaches, Component Approach and Dimension Approach.

- Optimized the Component Approach using various optimization techniques.

- Optimized the Dimension Approach using various optimization techniques.

- Resolved the memory bandwidth problem in Acoustic Modeling by eliminating the delay effect of accessing external memory using DMA and Cache Buffering technique.

- Examined and implemented Phone & Word Modeling and determined that they are computationally simple but require a large memory bandwidth.

#### 1.3.1 Organization of the Thesis

The remainder of this thesis is organized as follows: Chapter 2 reviews recent works pertaining to Automatic Speech Recognition. Different approaches including pure software and dedicated custom hardware architecture had been taken to implement speech recognition. The characteristics and performances of these different approaches will be presented and discussed briefly.

Chapter 3 provides an overview of the Automatic Speech Recognition process. In addition, the system design specifications and requirements will be presented. The specifications of the DSP including the VLIW architecture, the memory system and the DMA will be described in detail along with the real-time requirements. Finally, the basic performance measurements are presented. These measurements will be used to determine how well an algorithm is optimized.

With all the pieces in place, Chapter 4 begins to focus on the detail implementation and optimization of the first stage of the ASR process, Feature Extraction. This section will provide the background theory of Feature Extraction along with its operations performed. The implementation will then be presented. After applying various optimizations, the performance result improved 332% from 231,577 cycles to 69,684 cycles. Furthermore, the implementation is functionally verified against the Sphinx 3 system using the data samples extracted from Sphinx 3.

Chapter 5 focuses on the next phase, Acoustic Modeling. This chapter will discuss the background theory, performance issues and different implementations and the performance result. As shown in [1], AM is the most computational intensive phase of the entire recognition process. As a result, two different approaches, Component Approach and Dimension Approach, are implemented. Each approach is optimized with numerous different optimization techniques to obtain the best performance possible with the given DSP architecture. After comparing the optimal performances, the Dimension approach has the best performance of 0.75 million cycles, an improvement of 4500% from 33.8 million cycles without any optimization. Another performance problem for AM is that it requires a large amount of data that must be stored in the external memory. However, accessing the external memory requires significant amounts of cycle delay. One solution is to use Direct Memory Access as the detail will be presented in (section.5.2) All implementations are functionally verified against the original Sphinx 3 system using the same input samples from Sphinx 3.

Finally, Charter 6 discusses both Phone Modeling and Word Modeling. PM and WM are relatively insignificant from the computation perspective. However, a memory bandwidth problem similar to AM exists and the same solution used for AM is not applicable in this case. The best solution is that a traditional cache system large enough for all required data for PM and WM is sufficient. Similar to the previous sections, the theory, functions and implementations of Phone Modeling will be provided in detail.

In conclusion, all performance results from different phases will be summarized. Each phase is implemented and functionally verified against Sphinx 3. Although the integration of all phases of the 1000 w ord com m and and control application doesn't execute in real-time on the 225 MHz DSP. However, it a multi-core DSP running at 300 MHz would be sufficient for real-time implementation.

#### 2.0 LITERATURE REVIEW

Speech recognition has been a popular research topic for the past several decades. Various methods of implementation have been applied to solve the problem of Automatic Speech Recognition. These implementations range from pure software designed to run on GPP to dedicated custom hardware architectures.

With the recent advancement of computer hardware, more promising software-based solutions have been developed not only in the research community, but also in the commercial market. Carnegie Mellon University's SPH IN X [3] and University of Cobrado's SONIC [11] are two examples of successful research systems. For the commercial systems, IB M 's ViaVoice [12] and Nuance' Dragon Naturally Speaking [13] are two popular recognition software. However, all these software-based systems are designed to run on computer systems with high clock rate GPP. They also require a large memory footprint for data storage.

Various works have been done in the research community to characterize speech recognition system and to investigate the implementation of speech recognition in embedded applications. Agaram, et al [15] characterized the speech recognition process in 2001. Aside from the characterization, their research group also performed an extensive analysis on the effect of various cache sizes. The investigated result shows that speech recognition processes substantially exercise the memory system and exhibit a low level of Instruction Level Parallelism. They then proposed various methods to improve the throughput of the system. As a result, they were able to increase the instruction per cycle (IPC) from 0.64 to 3.55.

Binus, et al [10] profiled and characterized Sphinx 3 system in the block levels and their results indicate that the majority of computations in speech recognition is spent in Acoustic Modeling.

Hagen, et al [16] characterized the speech recognition process in hand-held mobile devices. Their work evaluated the performance of the SONIC [11] recognition system from the University of Colorado on a PDA-like architecture. Their work focused on optimizing the code using a strategic set of compiler optimizations. The result shows that real-time recognition is close to being possible with a 500 MHz processor with moderate levels of ILP and cache resources.

The results of the above work conclude that speech recognition is extremely computational intensive where special attention should be paid to Acoustic Modeling. Significant amounts of memory bandwidth is required and recognition algorithms exhibits moderate level of ILP.

#### **2.1 SPHINX 3**

A software-based speech recognition system developed by Carnegie Mellon University called Sphinx [3] is used as the basis for this research. Specifically, version 3 of Sphinx is used. Sphinx 3 is a speaker independent, continuous speech, software recognition system. Sphinx 3 had shown that it is capable of archiving 10x more than real-time in a broadcasting news transcription system [7]. Ten times real-time is considered a fairly solid result due to the fact that the system was implemented in 1999 and the word library used contains 64,000 words.

In Sphinx 3, all words are decomposed into sub-word units, called *phonemes*. Specifically in Sphinx 3, all phonemes are decomposed into sub-phoneme units called

senones [8]. More information about the modeling of phoneme and senone will be presented in later sections. The word library used for this research is based on the DARPA's Resource Management (RM1) corpus [6], which contains 1000 words used in command and control type tasks. All algorithms used in this research are either partially or fully derived from Sphinx 3.

#### 2.2 DIGITAL SIGNAL PROCESSORS

Digital Signal Processors (DSPs) are special-purpose microprocessors designed with specialized architectures very suitable for different type of signal processing applications. The flexibility though reprogramming and the power efficiency provided by the DSP made it very suitable for most embedded applications. Compared to most general purpose processors (GPP), DSPs offer the instruction sets that typically reduce the number of instructions needed to perform the same operations. For example, most signal processing algorithms perform multiple-and-add (MAC) operations. Typically, a MAC takes a few cycles to complete in GPP but only takes one cycle to execute in VLIW DSP. The ability to execute multiple instructions is enabled by the advanced Very Long Instruction Word (VLIW) architecture. At the same time, the use of VLIW architecture increases the memory bandwidth. For parts of the recognition process where all required data fit on the on-chip memory, no significant performance decrease will be imposed from the memory access latency. However, if external memory is needed, the performance will decrease considerably due to the long latency of external memory accesses. If external memory is necessary, it is possible to reduce the latency effect through careful use of the on-chip memory along with Direct Memory Access, or DMA.

#### 2.2.1 Very-Long-Instruction-Word Architecture

Most state-of-the-art DSPs are designed based on the VLIW architectures [9]. VLIW architectures are developed with the purpose to exploit and to increase the instruction-level parallelism (ILP) in programs. These processors contain multiple functional units that are capable of executing multiple instructions simultaneously. The instruction sets of these VLIW architectures are usually simpler than GPP instructions. In order to take advantage of these architectures, enough ILP is necessary. State-of-the-art compilers can exploit ILP through code scheduling techniques such as Software Pipelining [28] and generate codes that group together independent instructions that can run in parallel. A Very-Long-Instruction Word, that contains multiple independent instructions, can then be fetched from the instruction cache together and dispatched to the different functional units in parallel. The DSP used for this functional research has eight units: two floating-point multipliers, two floating-point/fixed-point ALUs and four fixed-point ALUs.

#### 2.2.2 Memory Architecture

Most state-of-the-art DSPs are equipped with two level cache architecture along with a large sized on-chip fast memory, typically SRAM. More often, the second level cache is configurable to either as another cache or on-chip SRAM. For example, the targeted DSP used for this research has 192 Kbytes of on-chip SRAM along with a 2-level cache system. The capacity of the Level 1 (L1) cache is 4 Kbytes organized into 2 direct mapped, or 2-way associative, caches. The capacity of the Level 2 (L2) cache is 64 Kbytes. Furthermore, the Level 2 cache can be configured to be all on-chip SRAM, part SRAM and part cache, or all cache.

Typically a cache hit in L1 cache does not impose any latency while a cache miss in L1 will result in a few cycles delay if the data is resided in L2 cache. If the data is not in L2, then more cycles are needed to access the data from the external memory.

#### 2.2.3 Direct Memory Access

DMA is a mechanism used to transfer data between peripherals and memory or between different memory sections without the interference of the processor. In other words, data movement and data processing can be executed in parallel. With this capability and the configured L2 cache as all on-chip SRAM, the latency effect of external memory access can be completely eliminated. This can be accomplished by configuring L2 as a double buffer so while the processor is using the data of one buffer; the other buffer be being filled with new data by the DMA. One last requirement is that the two buffers are located in separate memory banks so simultaneous accesses by the processor and DMA are possible.

### 2.3 DEVELOPMENT PLATFORM SPECIFICATIONS

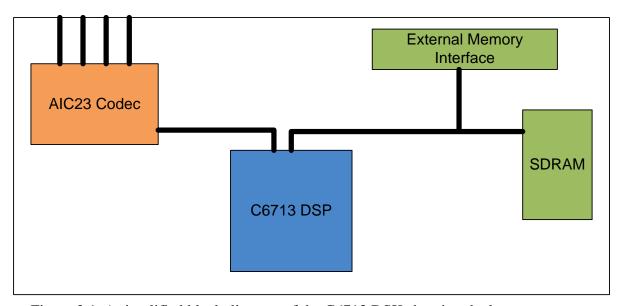

The development platform used in this research is the TMS320C6713 DSP Starter Kit (DSK) from Texas Instruments. The DSK features a TMS320C6713 DSP running at 225 MHz. Other important peripherals available with this DSK are a 24-bit stereo codec, a 32-bit External Memory Interface (EMIF) and 16 Mbytes of external SDRAM. A basic block diagram taken from the TI TMS320C6713 DSK technical reference [27] is shown in Figure 2.1.

Figure 2.1: A simplified block diagram of the C6713 DSK showing the key components

#### 2.3.1 Texas Instruments C6713 DSP

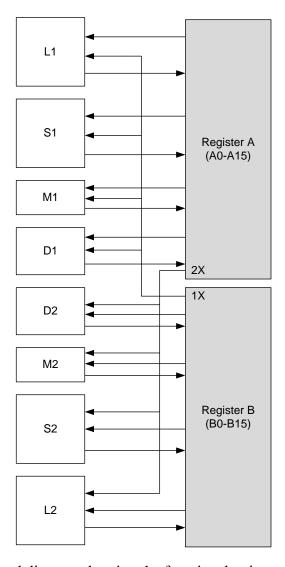

The C6713 DSP is the high performance floating-point DSP from Texas Instruments. It has 32 32-bit registers and is capable of loading either a 32-bit single word or a 64-bit double word per cycle. The DSP is designed based on an advanced VLIW architecture with eight functional units: 2 fixed-point ALUs (.D units), 4 floating-point/fixed-point ALUs (.L and .S units) and 2 floating-point multipliers (.M units). Figure 2.2 lists the type of operation(s) dedicated to each type of the functional units.

| Functional<br>Unit | L                                  | s                               | М        | D                        |

|--------------------|------------------------------------|---------------------------------|----------|--------------------------|

| Operations         | Logical<br>Addition<br>Subtraction | Shift<br>Branch<br>Add/Subtract | Multiply | Load<br>Store<br>Add/Sub |

Figure 2.2: Illustrates the operation(s) support by different functional unit

Eight functional units enable 8 independent instructions to be executed in parallel. These functional units are divided into two separate clusters where each cluster has 4 units each. The 32 registers are organized into 2 register files, each has 16 registers. Each cluster has its own register file, and each functional unit has its own access port to its corresponding register file. To pass data from one cluster to the other, a cross path (.X) must be used. A detailed architectural diagram [27] is shown in Figure 2.3 illustrating the functional units' arrangement.

Figure 2.3: A architectural diagram showing the functional units and registers arrangement

#### 2.3.2 Memory System

Three memory systems are available on the TMS320C6713 DSK, cache system, on-chip SRAM and external SDRAM. The C6713 DSP utilizes a two-level cache memory system. Level 1 (L1) is a two-way set-associative cache with the total capacity of 4 KB. The capacity of the level 2 (L2) cache is 64 KB, which can be configured to be all cache, all SRAM, or part cache and part SRAM. In addition to the 2 levels cache, 192 KB of on-chip SRAM is also available for both data and programming storage. If more memory space is needed, there are 16 MB of Synchronous DRAM available through the external memory interface. Table 2.1 summarizes the memory systems available and the configurations used for this research:

Table 2.1: Memory systems and configurations summary

| Memory      | Туре                              | Line Size<br>(Bytes) | Capacity<br>(KB) | Read Hit<br>Penalty<br>(Cycles) | Read Miss Action | Read Miss<br>Penalty<br>(Cycles) |

|-------------|-----------------------------------|----------------------|------------------|---------------------------------|------------------|----------------------------------|

| L1P         | Direct mapped cache               | 64                   | 4                | 1                               | L2 Request       | 5                                |

| L1D         | 2-Way Set<br>Associative<br>Cache | 32                   | 4                | 1                               | L2 Request       | 4                                |

| L2          | SRAM                              | -                    | 64               | 4                               | EMIF Request     | Vary                             |

| On-<br>Chip | SRAM                              | 17                   | 192              | 4                               | <b>#</b>         | -                                |

| External    | SDRAM                             |                      | 16 MB            | vary                            | 2                | 2                                |

In addition to the memory type and the capacity, Table 2.1 also summarized other characteristics. Line Size is the number of bytes allocated from the next level memory when a read miss occurs. Read Hit Penalty is the number of cycles for the processor to access the data if the data exists in that particular memory section. Read Miss Action is the process that

occurs when the data requested is not available. Finally, Read Miss Penalty is the number of stall cycles when a miss occurs. Note that for this research, L2 is configured as all SRAM.

#### 2.4 OPTIMIZATIONS OVERVIEW

The overall performance of a speech recognition system depends mostly on the efficiency of the algorithms and the mapping of the algorithm onto the available hardware. There are numerous compiler optimization techniques available to help improve the performance of the algorithm. This section will describe the different optimization techniques available and how they are applied.

#### 2.4.1 Variable Registering

Variable Registering is one of the basic optimization techniques. Instead of reading and writing data from memory outside of the processor for every instruction, registers are used to temporarily store data until the data is no longer needed. This optimization reduces the number of memory accesses significantly and resulting major performance improvement.

#### 2.4.2 Constant Propagation

Constant Propagation is an optimization that replaces local copies of the global variable with the actual value. This technique increases the code size slightly but also improves the code performance.

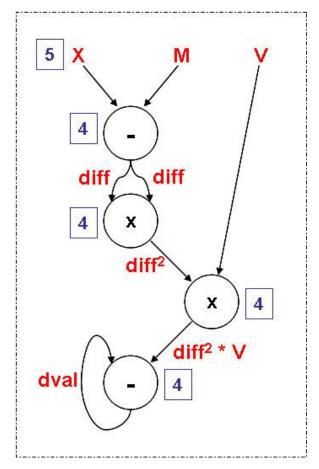

#### 2.4.3 Data Dependency

Data dependency occurs when the next instruction cannot be executed because it requires the result from the previous instruction. An example is illustrated in Figure 2.4.

```

diff = f - m[i];

lrd[i] -= diff = diff = v[i];

```

Figure 2.4: An example of data dependency

As illustrated, the second calculation cannot be executed until *diff* is computed by the previous instruction. If the software code is executed sequentially, data dependency would not be an issue. However, almost all modern processors are capable of executing multiple instructions in parallel in order to improve performance. As a result, data dependency can post a significant performance limitation on parallel executed code.

#### 2.4.4 Loop Carried Dependency and Memory Aliasing

Loop carried dependency occurs when the next iteration of the loop cannot start until the previous iteration is completed. This is an issue that only exists in software code executed in parallel. An example is shown in Figure 2.5.

```

Void test (float *ary, float *window, Int len)

{

Int i;

for (i = 0; i < len; i++)

ary[i] = ary[i] * window[i];

}

return;

}</pre>

```

Figure 2.5: A code sample illustrating loop carried dependency

It is not immediately obvious why multiple iterations cannot be executed in parallel since each iteration involves only one element from the each of the *ary* and the *window* array and the result of the multiplication is stored back to the *ary* array. From the compiler prospective, it has no idea if any part of the *ary* and *window* arrays are overlapped in the memory, or *memory aliasing*. If some parts of the two arrays are overlapped, then executing this code in parallel would produce incorrect results.

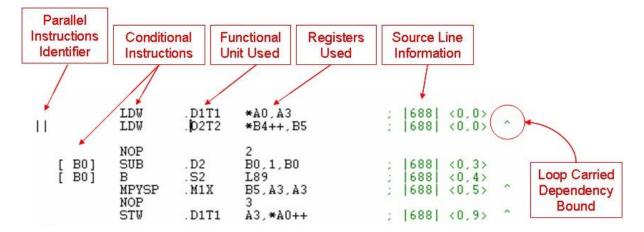

One way to identify loop carried dependency is to use a dependency graph if the source code is available. A simpler way to find the dependency is by using the compiler generated assembly. Figure 2.6 displays a sample code and Figure 2.7 shows the generated assembly from the sample code.

```

Void fe_multiply_window(float *ary, float *window, Int len)

{

Int i;

if (len > 1){

for (i = 0; i < len; i++)

ary[i] *= window[i];

}

return;

}</pre>

```

Figure 2.6: Sample source code

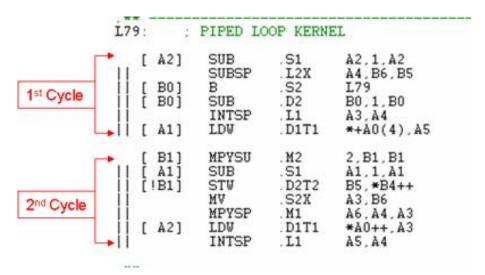

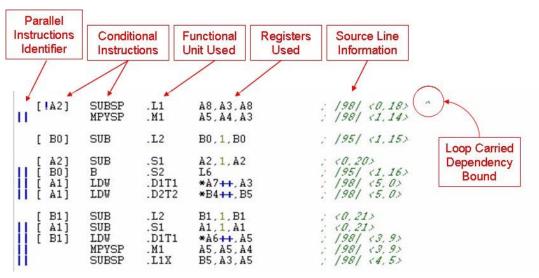

Figure 2.7: Generated assembly from source code in Figure 2.6

Instructions with dependency are indicated by (^) symbol as shown in Figure 2.7. Clearly, the problem exists between the LDW (load word) and the STW (store word) instructions. Figure 2.6 shows that the core calculation requires two loads, a multiply and a store. Within the scope of the local function, the compiler cannot assume that pointers *ary* and *window* do not overlap. The compiler cannot execute another load instruction for the next iteration until the store instruction from the previous iteration is completed.

Assuming that the two input pointers do not overlap in memory, the dependency can be removed by explicitly informing the compiler that there is no aliasing using the *restrict* keyword [25]. The *restrict* keyword is a type qualifier that represents a guarantee by the programmer that within the scope of the pointer declaration the object pointed to can only be access by that pointer. It is applied to the variable in the function declaration as shown in the following code sample: void function\_name (int \* restrict variable). For more information on *restrict* type qualifier, please refer to [25].

#### 2.4.5 Software Pipeline

Software Pipelining [28] significantly improves code performance by executing multiple iterations of the loop in parallel. This is enabled by the advanced VLIW architecture. Figure 2.8 illustrates a software pipelined loop. A, B, C, D and E are five independent stages of a loop.

| Phases   |   |   | n   | oop Iteratio | L    |      |   | Cycle |  |  |  |  |

|----------|---|---|-----|--------------|------|------|---|-------|--|--|--|--|

|          | 6 |   |     |              |      |      | A | 1     |  |  |  |  |

| Prologue |   |   |     |              |      | A    | В | 2     |  |  |  |  |

|          | d |   |     |              | A    | В    | С | 3     |  |  |  |  |

|          | - |   |     | A            | В    | С    | D | 4     |  |  |  |  |

| Kernel   | 1 |   | A   | В            | С    | D    | E | 5     |  |  |  |  |

|          |   | A | В   | С            | D    | E    |   | 6     |  |  |  |  |

|          | A | В | С   | D            | E    |      |   | 7     |  |  |  |  |

|          | В | С | D   | E            | - 25 |      |   | 8     |  |  |  |  |

| Epilogue | С | D | E   |              |      |      |   | 9     |  |  |  |  |

|          | D | E | × : |              | - 8  | - Vi |   | 10    |  |  |  |  |

|          | E |   |     |              | 6    |      |   | 11    |  |  |  |  |

Figure 2.8: Example of a software pipelined loop

In Figure 2.8, cycle 5 to 7 are known as the kernel. All five stages of instructions from five different iterations are executed in parallel. Cycles 1 to 4 are known as the prologue, which set up the software pipeline. Cycles 8 to 11 are known as the epilogue, which finishes the pipeline. Since all five stages are executed in parallel during the kernel, the iteration interval (ii) is only one cycle. Software Pipelining has the most advantage when the kernel can continue to execute with a minimum iteration interval and all functional units are fully utilized.

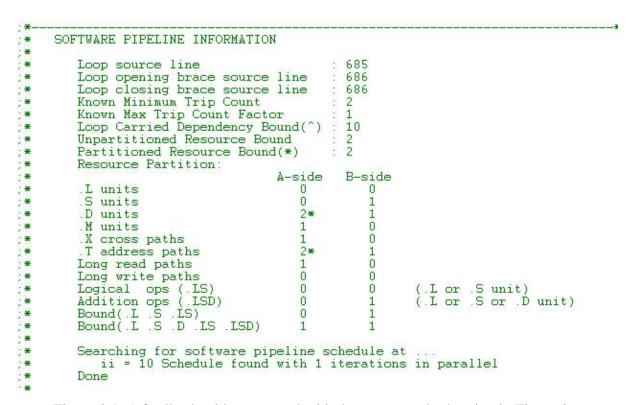

Before applying any optimization techniques to improve the code performance, problems must first be identified. A very useful way to identify performance issues, is by using the software pipeline feedback table. This feedback information is generated along with the assembly by the compiler. An example of a feedback table generated using the source code showing in Figure 2.6 is shown in Figure 2.9.

Figure 2.9: A feedback table generated with the source code showing in Figure 2.6

It is very important to understand the information from the feedback table showing in Figure 2.9 as many performance issues can be identified using this information.

- Loop source line: The line number of loop declaration in the source code.

- Loop opening brace source line: The line num ber for the loop opening brace, "\f".

- Loop closing brace source line: The line number for the loop closing brace, "?".

- *Known Minimum Trip Count:* The minimum number of loop iterations determined by the compiler.

- Known Max Trip Count Factor: The number of times the loop can be unrolled as determined by the compiler. This factor must be evenly divided into the Known Minimum Trip Count.

- Loop Carried Dependency Bound (^): The number of cycles needed to execute one iteration of the loop if a loop carried dependency existed. This line can be used to identify any loop carried dependency.

- *Unpartitioned Resource Bound:* The maximum number of times that any particular resource is being used for one iteration. This figure is determined by the compiler before instructions are partitioned to two resource clusters.

- Partitioned Resource Bound (\*): The maximum number of times that any particular resource is being used for one iteration after instructions are partitioned by the compiler to the two resource clusters. The resource that is used most is indicated by (\*) on the A-and B- side resource listing. This information can also be used to identify any uneven partitioning between two resource clusters.

- .L units: Floating-point arithmetic execution units. Two units total are available, one on side-A and one on side-B. The number under each side indicates the number of times this unit is used for one iteration. For exam ple, a "1" under side-A for .L units means that this floating-point unit on side-A is used by one instruction only for one iteration.

- .S units: Fixed-point arithmetic execution units. There are total of two, one on side-A and one of side-B. The number under each side indicates the number of times this unit is used for one iteration.

- .D units: Address calculation units. There are total of two, one on side-A and one of side-B. The number under each side indicates the number of times this unit is used for one iteration.

- .M units: Floating-point multiplier units. There are total of two, one on side-A and one of side-B. The number under each side indicates the number of times this unit is used for one iteration.

- .X cross path: Cross path used for transfer data from one side of the register file to the other side for execution. There are two paths total. One path between side-A execution units and side-B register file and the other path between side-B execution units and side-A register file.

- .T address path: Address path used to pass the calculated address from .D units to its associated register file.

- ii = xx: Iteration interval. This is the number of cycles needed for one loop iteration determined by the compiler. From the example in Figure 2.9, 10 cycles are required for one loop iteration because a loop carried dependency exists.

- *x iterations in parallel:* This indicates the number of iterations executed in parallel.

- **2.4.5.1 Instruction Latency** Instruction latency is an important factor that affects the performance of the code. Although an instruction can be issued to a functional unit every cycle, the result usually is not available until a few cycles later, this is the instruction latency. The number of cycles required after the execution and before the result is ready is called the delay slot. Different instructions have varied amounts of delay slots. Figure 2.10 shows the delay slot and the functional latency for some common C67x instructions. To minimize the effects of long instruction latency, optimization techniques like Loop Unrolling and Software Pipelining are used. For a full list of C67x instructions delay slot and functional latency, please refer to [24].

| Instruction | Delay Slot | Functional Unit<br>Latency | Description                                    |

|-------------|------------|----------------------------|------------------------------------------------|

| ADD         | 0          | 1                          | Signed or Unsigned Fixed-Point Addition        |

| LDW         | 4          | 1                          | Load 32-bit word from memory                   |

| MPY         | 1          | <u>1</u>                   | Signed or Unsigned Fixed-Point Multiplication  |

| ADDSP       | 3          | 1                          | Single Precision Floating-Point Addition       |

| LDDW        | 4          | 1                          | Load 64-bit word from memory                   |

| MPYSP       | 4          | 1                          | Single Precision Floating-Point Multiplication |

| MPYDP       | 9          | 4                          | Double Precision Floating-Point Multiplication |

Figure 2.10: Example of delay slot and functional unit latency of some C67x instructions

#### 2.4.6 Loop Unrolling To Balance Resources

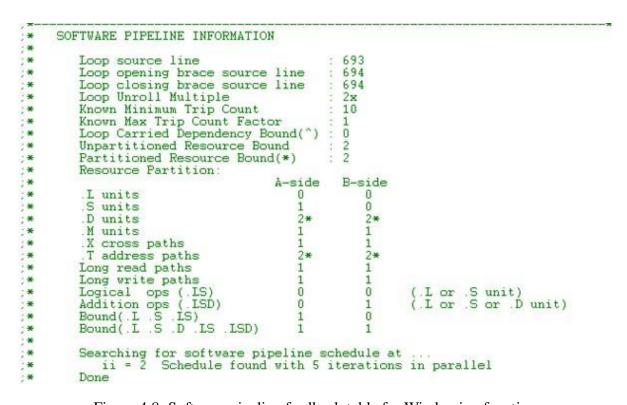

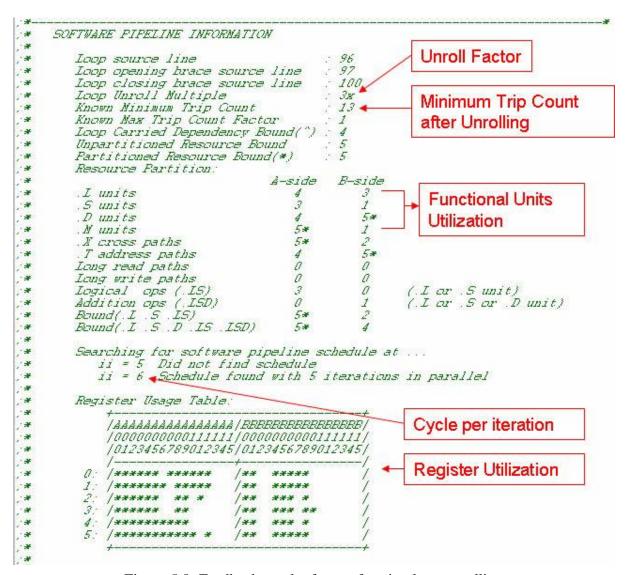

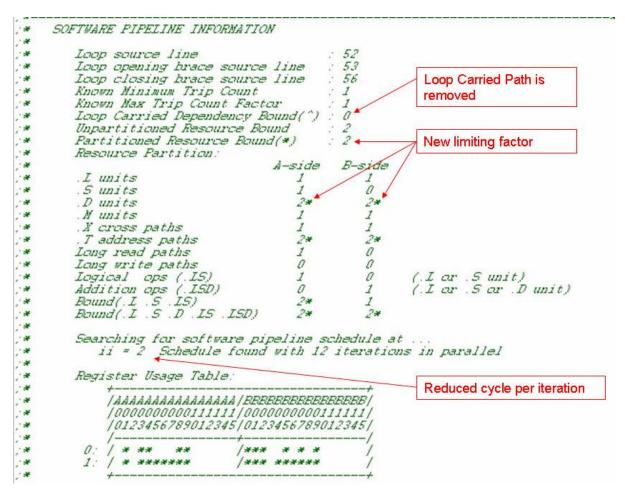

The DSP architecture and the number of functional units available limit the performance of a software pipelined loop. The C6713 DSP used in this research has eight functional units divided into two separate channels. Each channel has four units, one type of functional unit each, with two cross path between the channels. The number of functional units available is known as the resource constraint. An example would be a loop with too many load and store operations but too few multiplications. The two-channel architecture also presents aproblem of resource partitioning. For example, if a loop contains three load/store operations, the two channels will not be balanced since one channel would have two operations while the other channel only has one.

The software pipeline feedback table is a good tool to identify any unbalanced utilization of resources. The line Partitioned Resource Bound (\*) from Figure 2.9 shows that there are unbalanced resources between the two channels. The reason is that the loop has an odd number of instructions, two loads and one store that would use both the .D and .T functional units.

To balance the resources for this loop, loop unrolling can be considered. Notice that to perform loop unrolling, the loop count must be a multiple of the unrolling factor. For example, to unroll the loop by a factor of 2 correctly without doing extra calculations, the loop count must also be even. Similarly, to unroll a loop by a factor of 3, the loop count must be a multiple of 3. In Figure 2.6, the compiler does not know the *len* value from the local view of the function so the compiler does not perform loop unrolling. A *MUST\_ITERATE (MIN LOOP COUNT, MAX LOOP COUNT, UNROLL FACTOR)* pragma can be used to pass the minimum loop count, maximum loop count (optional) and the unrolling factor information to the compiler. With the information explicitly stated, the compiler can perform loop unrolling for our example loop. Figure 2.11 shows the modified source code and Figure 2.12 shows the newly generated feedback table.

```

Void fe_multiply_window(float * restrict ary, float * restrict window, Int len)

{

Int i;

// JN: since len is fe->frame_size, can assume even number for now 410

#pragma MUST_ITERATE(20, ,2);

for (i = 0; i < len; i++)

ary[i] *= window[i];

return;

}</pre>

```

Figure 2.11: Modified source code with restrict type qualifier

```

*

SOFTWARE PIPELINE INFORMATION

×

Loop source line

689

*

Loop opening brace source line

690

*

Loop closing brace source line

690

Loop Unroll Multiple

2x

*

10

Known Minimum Trip Count

Known Max Trip Count Factor

*

Loop Carried Dependency Bound(

0

×

Unpartitioned Resource Bound

3

3

×

Partitioned Resource Bound(*)

Resource Partition:

*

B-side

A-side

*

.L units

0

0

.S units

0

×

.D units

3*

3*

*

1

1

.M units

.X cross paths

*

T address paths

3*

3*

*

Long read paths

1

1

0

0

Long write paths

(.L or .S unit)

(.L or .S or .D unit)

*

ops (.LS)

ops (.LSD)

0

0

Logical

0

*

Addition ops (

1

Bound(.L .S .LS)

Bound ( . L

*

.S .D .LS .LSD)

```

Figure 2.12: Feedback table with modified source code

Looking at the new feedback information, the loop now is unrolled by a factor of 2x (Loop Unroll Multiple). Also, both A-side and B-side channels have the same amount of instructions scheduled.

## 2.4.7 Packed Data Memory Access

This optimization technique can also help balancing resources for certain situations. The C6713 DSP is capable of loading a single 32-bit word or a 64-bit double word per cycle. An example of the situation where this optimization is suitable would be the example loop shown in Figure 2.6. The loop contains two loads, one multiply and one store. Without unrolling the loop, there will be unbalanced usage on the D function units. Packed data optimization reduces the number of load instruction from two to one. Notice that in order to apply this optimization technique, the data in the memory must be continuous and double-word-aligned.

Double-word-aligned means the lower 3 bits of the address are zero. To explicitly instruct the compiler that data are double-word-aligned, a function is used to assert that data are double-word-aligned. Figure 2.13 shows the modified code from the previous example and Figure 2.14 shows the newly generated assembly with two 32-bit loads is now combined to one 64-bit load.

```

#define WORD_ALIGNED(x) (_nassert(((int)(x) & 0x7) == 0))

Void fe_multiply_window(float * restrict ary, float * restrict window, Int len)

{

Int i;

WORD_ALIGNED (ary);

WORD_ALIGNED (window);

// JN: since len is fe->frame_size, can assume even number for now 410

#pragma MUST_ITERATE(20, ,2);

for (i = 0; i < len; i++)

ary[i] *= window[i];

return;

}</pre>

```

Figure 2.13: Modified code with new function to assert data are double-word-aligned

```

190: ; PIPED LOOP KERNEL

[ B0] B .S1 L90 ; |694| <2,4>

|| LDDW .D1T1 *++A3,A1:A0 ; |694| <4,0>

```

Figure 2.14: Assembly showing two LDWs combined into one double load LDDW

# 3.0 OVERVIEW OF AUTOMATIC SPEECH RECOGNITION AND SYSTEM DESIGN SPECIFICATIONS

Automatic Speech Recognition (ASR) is essentially a matching problem. The goal is to find the best match between a set of existing words and an observed speech. Continuous speech recognition extends the matching from single word to a series of words. Figure 3.1 shows the basics of an ASR system in block levels:

Figure 3.1: Basic ASR system in block levels

The speech signal is first sampled by an analog-to-digital converter. The digital representation of the speech is then processed by the Feature Extraction (FE) block. In FE,

characteristics of the speech are extracted to form a vector of 39 features. Each feature corresponds to the characteristics of a different frequency band. A new feature vector is generated every 10 millisecond interval, which is the basic requirement for real-time speech processing. The next three blocks, Acoustic Modeling (AM), Phone Modeling (PM) and Word Modeling (WM) combine to perform word matching at different levels. The feature vector is matched against each word available from the word library. The Word Modeling block keeps track of words that have the probabilities higher than a certain threshold and eliminates words that have probabilities below that threshold. Once a word is recognized by the WM block, it will be passed onto the Application block. Usually the duration of a spoken word requires multiple 10 ms frames. As a result, several frames are needed before a word can be recognized. This is the basic idea of word recognition in ASR. Continuous speech recognition is archived at the Application block. As words are observed by the WM block, a model of inter-words probability from the LM\_SET of the Database can be used to determine how these recognized words are related, hence, forming a continuous speech. This task is done by the Application block.

#### 3.1 FORMAL DEFINITION

The goal of ASR is to transcribe speech into words and sentences. From a statistical point of view, the goal is that given an acoustic observation  $X = X_{I - ...} X_n$ , find the corresponding word sequence  $W = W_{I - ...} W_n$  that maximizes the posterior probability P(W/X). This expression implies finding the probability of every word within the given word library. For large sized word library, it is very impractical. Instead, B ayes' rule can be applied to decompose the posterior probability, P(W/X), into two components:

$$P(W/X) = \frac{PX/WPW}{PX}$$

Eq. 3.1

P(W|X) is the probability of the word sequence W given the observed sequence X. P(X|W) is the probability of the observed sequence X given the word sequence X. P(W) is the probability of the word sequence X. P(X) is the probability of the observed sequence. Equation 3.1 can be further simplified by removing P(X) because the probability of the observed sequence is random for every case. Furthermore, the purpose of speech recognition is to find the best match between the observed sequence and the word library. Hence, the modified equation looks like the following:

$$\max P(W|X) = \max P(X|W)P(W)$$

Eq. 3.2

Equation 3.2 indicates that finding the best match is to maximize the product of P(X/W) and P(W). The probability of each word, P(W), is generated by comparing the relative occurrence frequency against other words in the dictionary. For example, the word "the" has a much higher probability of occurrence than other words like "coefficients" or "G aussian". P(W) is used by the Word Modeling block and is pre-generated and stored in the WM\_SET of the Database. P(X/W) is determined by the Acoustic Modeling and the Phone Modeling blocks.

## 3.2 BLOCK LEVEL OVERVIEW

This section provides a functional overview for each processing block in Figure 3.1. From Figure 3.1, speech is first sampled then propagated from the FE block through AM, PM, WM and Application blocks. This system model is simple and straightforward since data flow

sequentially and all words are evaluated against the sampled speech. However, evaluating all words is sometime impossible to achieve in real-time for certain applications. All words needed to be evaluated due to the assumptions that any word is possible to be the starting word of a sentence, and any word can transit into another word. However, in reality, the probability of certain words being the starting word is very small relative to other words. For exam ple, the word "he" has a higher probability of being the start of a sentence than the word "only". Hence, the number of computations can be reduced by only evaluating those probable, or "active", words at any given frame. Tracking these active words is the responsibility of the Application block.

For a word library that only contains a few words, it may be possible to recognize each word as a whole. However, for a large word library that contains similar words, it is no longer possible to recognize each word as a whole. In order to distinguish similar words; all words are further divided into multiple sub-word units called *phonemes*. With this new word definition, ASR can be viewed as phoneme recognition instead of word recognition. While the Application block is responsible for word tracking, WM block is responsible for phoneme tracking. Similar to word tracking, phoneme tracking is necessary because not all phonemes can be the starting part of a word and not all phonemes are allowed to be followed by any phonemes. Only those active phonemes are evaluated by the Phone Modeling block at any given frame. The list of active phonemes passed from WM to PM is referred as Feedback. The system model with Feedback is more complex as extensive data management is required. However, from the computational stand point, Feedback helps improve the overall system performance by reducing the required number of evaluations. A modified block diagram with Feedback is shown in Figure 3.2. Pseudo-code of the data flow with Feedback is also provided in Figure 3.3.

Figure 3.2: Block diagram for ASR with Feedback

Figure 3.3: Block level pseudo-code for data flow

The pseudo-code in Figure 3.3 shows the inputs, outputs along with all the tasks performed for each of the processing block.

The Database divides the word library into four datasets, one for each processing block as shown in Figure 3.2. Each dataset contains the necessary information needed for each block to complete its tasks. For example, the AM dataset stores the means and covariants needed for Gaussian evaluations.

## 3.3 Performance Characteristics

The differences in functionality have created different performance characteristics and memory bandwidth requirements for each processing block. The performance of these speech recognition processes had been characterized and profiled in [10]. It shows that FE takes up less than 1% of the overall computation cycles while AM takes up about 55%-95% and PM combined with WM consumes about 5%-45%. The actually percentages depend mainly on the size of the word library used. The larger the dictionary size, the more the performance of AM becomes significant over the other blocks.

The most computation intensive function in Feature Extraction is the Fast Fourier Transform (FFT), which converts the data samples from the time scale to the frequency scale. Utilizing the hand optimized signal processing library [26] available along with the DSP, the amount of computational cycles required to perform FFT is reduced to almost negligible relative to other parts of the recognition process, which corresponds to [10]. Also, all data required with FE can be stored within the on-chip SRAM which eliminates the performance effect that will be caused by accessing to the external memory.

The main function of Acoustic Modeling is to take the sample characteristics and match them against its own library. Part of this process is the Gaussian evaluation. Each of these evaluations includes two multiplications and two subtractions. The size of the dictionary dictates the number of Gaussian evaluations required. For the 1000 word dictionary used in this research, approximately 604,000 evaluations are performed every 10 milliseconds, which translates into 1.2 million multiplications and subtractions each. In Sphinx 3, all of these computations are evaluated in float point precision. Other research [1] had shown that reducing the bit precision does not impose significant decrease in system performance; however, the number of computations does not change.

While it is a challenge to perform such massive amounts computations with a limited amount of computing cycles, the bigger problem is feeding these computations with the required data. Each Gaussian evaluation takes three inputs and produces one output. Depending on the method of implementation, the required number of input data can be varied. However, regardless of the implementations, a minimum of two inputs are necessary. With each input data stored with 4 bytes each regardless of fixed-point or floating-point, approximately 4.83 Megabytes of data bandwidth is needed for every 10 ms. This amount of data is larger than most of the cache available on any system. As a result, these data will be stored in the external memory.

The primary function of Phone Modeling is to evaluate all of the active phonemes within a 10 ms frame. Phonemes are made active based on the previous frame of data by the Word Modeling block. In Sphinx 3 and for this research, each phoneme is modeled as a 3 states Hidden Markov Model (HMM). More information about HMM will be discussed in (section.6.0) Computational wise, each HMM evaluation consists of 9 additions and 3 comparisons. All operations are done in integer form. From the study of [1], at most approximately 4000 phonemes can be active at any given frame for the 1000 words dictionary, which are significantly fewer computations compared to AM. On the other hand, the amount

of data required per HMM evaluation is more than Gaussian evaluation. A total of 15 integers are needed for each HMM evaluation. Further, unlike AM where data are accessed in a regular manner, data required for PM are from multiple different locations and these locations are more random and irregular. This type of irregular memory access pattern presents a different type of challenge than AM.

The final stage considered in this research is Word Modeling. WM keeps track of all phonemes, removing unpromising ones and adding new ones to the active list. Since the operation of WM is tightly coupled with PM, they will be analyzed together from this point and on.

Summarizing these performance characteristics, it should be clear that AM should be the main focus since AM requires the most processing power and the largest memory bandwidth.

# 3.4 TIMING REQUIREMENT

The standard technique used for speech processing is based on frame processing. Sphinx 3 processes speech data at 10 millisecond intervals. In order to be real-time, all computations must be completed within the 10 ms interval. The number of computation cycles available, however, depends on the speed of the processor. For example, if the processor is operating at 100 MHz, that means all calculations must be done in 1 million cycles, 1/100 of a second. For this research, the DSP operates at 225 MHz. As a result, the cycle budget available for this research to satisfy the real-time requirement is 2,250,000 cycles.

#### 3.5 PERFORMANCE MEASUREMENTS

As presented in the (section 3.3), different processing blocks have different computational and memory requirements. Feature Extraction is the least computational intensive relative to other parts of the recognition process. Also the memory footprint is small enough to be stored entirely in the on-chip SRAM. However, in embedded environment where a high speed processor isn't available, FE remains a performance bottleneck. As a result, FE must also be optimized using several compiler optimizations. The optimized performance of FE improved 332% from 231,000 cycles to 69,000 cycles, which is 3.07% of the real-time budget.

Acoustic Modeling is the most computational intensive and requires the largest memory bandwidth in the entire recognition process. For these reasons, most efforts are spent trying to optimize AM. AM implementation presents two separate problems: a large number of computations and massive memory bandwidth. AM performs 1.2 million multiplications and subtractions each. For a fair comparison with Sphinx 3, all operations are performed in floating-point precision. With eight functional units available where two of them are float-point multipliers and two are floating-point ALUs, it seems possible to execute a single Gaussian evaluation per cycle. However, data dependency and functional unit latency prevent the achievement of such performance. Data dependency exists due to the fact that not all 4 operations are independent. In other word, the output of one operation is the input for the other operations. Further, although all functional units are capable of executing most instructions in a single cycle, but there exists some latency before the result is available. This latency is due to the deep pipeline architecture of these functional units.

Although it is impossible to archive one cycle per Gaussian evaluation with the available DSP architecture, it is possible to get close to it. Two different implementations methods were analyzed in this research where each of them is optimized through software pipeline and various compiler techniques. The best performance obtained is 1.25 cycle per Gaussian

evaluation resulting an approximately 754,000 total cycles. This result is obtained based on the assumption that all data are available to the processor without any latency. In reality, this is impossible since the L1 cache size is too small. The DSP and cache architecture used in this research impose a 4 cycles delay whenever L1 misses and L2 hits, regardless of L2 being on-chip SRAM or cache. Further, if L2 misses and external memory is accessed, over 100 cycles of delay is possible. To eliminate this memory latency effect, the L2 cache is configured to be used as all on-chip SRAM where it is divided into two different buffers. While one buffer is being accessed by the processor, the other buffer can be filled with new data using DMA. This method will completely eliminate the effect of external memory latency. Since the line size of the L1 cache is 8 32-bits words, the actual performance would now be the total number of data required divided by 8 and multiples by 4 cycles. With 603,000 total evaluations and 3 pieces of float-point data each, total of 1.81 million float-point data is needed. Dividing by 8 and multiplying by 4 resulting 905,000 cycles. With the processor running at 225 MHz, a 10 ms frame would have 2.25 million real-time cycle budget. After optimizing AM, the overall cycle performance would be 1,659,000 (computation + memory latency, 754,000 + 905,000), which is about 73.7% of the real-time cycle budget.

Finally, for PM and WM, all computations are integer based with no data dependency. The only problem is that PM and WM also require a fairly large memory bandwidth and the access pattern is more irregular. Due to the irregularity, DMA would not be as useful in this case since data are coming from different locations of the memory rather than accessed as a block in sequential fashion. The only solution would be to have all the required data to be stored in the on-chip SRAM. However, since PM and WM do not present any computational issues, they are only implemented for the completeness of the project.

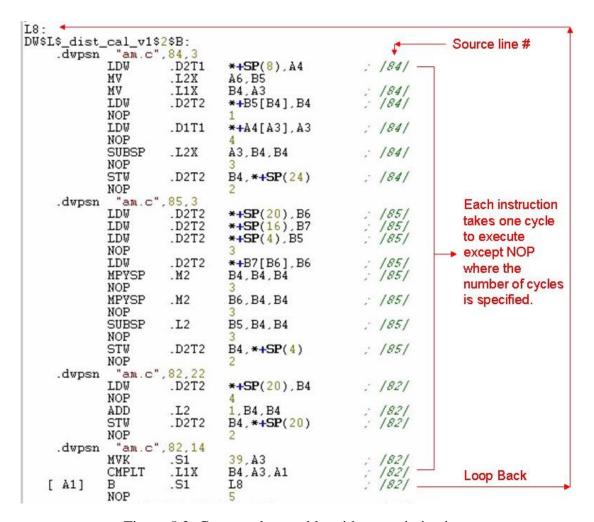

# 3.5.1 Register Utilization

Registers are temporary stores within the processor. Their purpose is to allow the processor to have quick access to often used variables. Certain complex algorithms require storing more temporary variables than the number of registers available. Whenever the processor runs out of register, external memory is accessed. In other word, the number of registers available limits the performance of execution of an algorithm. The registers also play an important role on the efficiency of a software pipeline code since the number of registers along with the number of execution units available limits how many iterations of a loop can be execute in parallel. An example of a register utilization table generated by the compiler is shown in Figure 3.4.

Figure 3.4: An example of a compiler generated register utilization table

As mentioned before, C6713 DSP has 32 registers that are divided into 2 register files, each has 16 registers. The example showing in Figure 3.4 indicates that each loop takes 3 cycles to execute (ii = 3). As a result, the Register Usage Table shows 3 cycles of usage, 0-2. Each (\*) indicates that register is used in that particular cycle. For example, registers A00, A01,

A03-A09 are used in cycle 0. Register utilization is used as a measurement to determine how well an algorithm is optimized. In other word, a 100% utilization of registers for every cycle is best while more unused register means more possible optimizations can be applied.

# 4.0 FEATURE EXTRACTION

This section discusses the theory, implementation and optimizations used for Feature Extraction (FE). Although FE takes up less than 1% of the overall cycle budget on systems with high speed processors, FE can become a significant performance issue in embedded environments. As a result, FE must also be optimized using various compiler optimization techniques. The optimized performance of FE improved 332% from 231,000 cycles to 69,000 cycles, which is 3.07% of the real-time budget.

Feature extraction, often referred to as the front-end processing, generates a set of 39-dimension features representing the important characteristics of the digitized speech samples. This is accomplished by dividing the input speech samples into blocks and derives a smoothed spectral estimate from each divided block. The typical spacing of each block is 10 milliseconds, resulting 100 frames per second. To obtain the required spectral estimates, numerous processes have been developed [17]. However, the most standard method, Mel-Frequency Cepstral Coefficients (MFCC) [18], is used by Sphinx 3. MFCC is a representation of a windowed signal derived from the FFT of that signal. The process of MFCC is divided into six stages as shown in Figure 4.1 and is described in detail in the following sections.

Figure 4.1: Different stages of Mel Frequency Cepstral Coefficients

# 4.1 PRE-EMPHASIS

In the spectrum of a human speech signal, the energy of the signal decreases as the signal frequency increases. The pre-emphasis process is applied to the input speech samples by using a first order FIR filter to increase the signal energy inversely proportional to its signal's frequency. This will equalize the power across all frequencies. The computation performed in Sphinx is show in Equation 4.1.

$$y[n] = x[n] - x[n-1]$$

, where  $0.9 < = < = 1$

In this research, is set to be 0.97, same as Sphinx. This operation is performed on every speech sample.

Pre-emphasis is implemented as a for-loop when each loop iteration performs a multiplication and an addition. The source code is shown in Figure 4.2.

Figure 4.2: Implementation code for pre-emphasis

Since all iterations are independent of each other, there is no data dependency issue. Further, *restrict* keyword is used to guarantee that *in* and *out* are non-overlapping arrays. However, Loop unrolling, Packed Data Load and other techniques are not applicable due to the fact that the loop count can be varied depending on the sampling rate. Finally, this loop is further optimized with software pipeline. The optimized assembly is shown in Figure 4.3.