# AUTONOMOUSLY RECONFIGURABLE ARTIFICIAL NEURAL NETWORK ON A CHIP

## by

## Zhanpeng Jin

M.S., Northwestern Polytechnical University, 2006

B.S., Northwestern Polytechnical University, 2003

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

## **Doctor of Philosophy**

University of Pittsburgh 2010

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Zhanpeng Jin

It was defended on

June 25, 2010

and approved by

Allen C. Cheng, Assistant Professor, Electrical and Computer Engineering

Steven P. Levitan, John A. Jurenko Professor, Electrical and Computer Engineering

Zhi-Hong Mao, Assistant Professor, Electrical and Computer Engineering

Marlin H. Mickle, Nickolas A. DeCecco Professor, Electrical and Computer Engineering

Shi-Kuo Chang, Professor, Computer Science

Wenyan Jia, Research Assistant Professor, Neurological Surgery

Dissertation Director: Allen C. Cheng, Assistant Professor, Electrical and Computer

Engineering

Copyright © by Zhanpeng  $\,$  Jin  $\,$  2010

## AUTONOMOUSLY RECONFIGURABLE ARTIFICIAL NEURAL NETWORK ON A CHIP

Zhanpeng Jin, PhD

University of Pittsburgh, 2010

Artificial neural network (ANN), an established bio-inspired computing paradigm, has proved very effective in a variety of real-world problems and particularly useful for various emerging biomedical applications using specialized ANN hardware. Unfortunately, these ANN-based systems are increasingly vulnerable to both transient and permanent faults due to unrelenting advances in CMOS technology scaling, which sometimes can be catastrophic. The considerable resource and energy consumption and the lack of dynamic adaptability make conventional fault-tolerant techniques unsuitable for future portable medical solutions.

Inspired by the self-healing and self-recovery mechanisms of human nervous system, this research seeks to address reliability issues of ANN-based hardware by proposing an Autonomously Reconfigurable Artificial Neural Network (ARANN) architectural framework. Leveraging the homogeneous structural characteristics of neural networks, ARANN is capable of adapting its structures and operations, both algorithmically and microarchitecturally, to react to unexpected neuron failures. Specifically, we propose three key techniques — Distributed ANN, Decoupled Virtual-to-Physical Neuron Mapping, and Dual-Layer Synchronization — to achieve cost-effective structural adaptation and ensure accurate system recovery. Moreover, an ARANN-enabled self-optimizing workflow is presented to adaptively explore a "Pareto-optimal" neural network structure for a given application, on the fly.

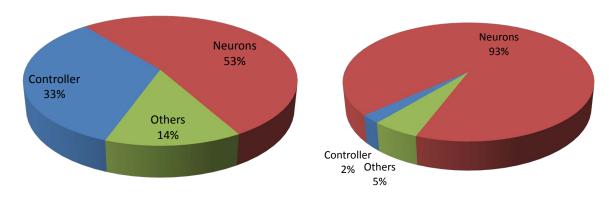

Implemented and demonstrated on a Virtex-5 FPGA, ARANN can cover and adapt 93% chip area (neurons) with less than 1% chip overhead and O(n) reconfiguration latency. A detailed performance analysis has been completed based on various recovery scenarios.

## TABLE OF CONTENTS

| 1.0 | IN'           | TRODUCTION                                                            | 1  |

|-----|---------------|-----------------------------------------------------------------------|----|

|     | 1.1           | Research Motivation and Problem Statement                             | 1  |

|     | 1.2           | Scope of Thesis                                                       | 4  |

|     |               | 1.2.1 Research Hypothesis and Aims                                    | 4  |

|     |               | 1.2.2 Addressing ANN's Recovery Issue                                 | 5  |

|     |               | 1.2.3 Addressing ANN's Optimization Issue                             | 8  |

|     |               | 1.2.4 Addressing ANN's Adaptation Cost Issue                          | 12 |

|     | 1.3           | Contributions                                                         | 13 |

|     | 1.4           | Thesis Outlines and Organizations                                     | 16 |

| 2.0 | RE            | LATED WORK                                                            | 17 |

|     | 2.1           | Hardware Implementations of Artificial Neural Networks                | 17 |

|     | 2.2           | Implementation Strategies and Examples of Neural Networks on FPGAs    | 21 |

|     | 2.3           | Fault-Tolerant Artificial Neural Networks                             | 26 |

|     | 2.4           | Reconfigurable Artificial Neural Networks                             | 30 |

| 3.0 | $\mathbf{AR}$ | CTIFICIAL NEURAL NETWORK                                              | 35 |

|     | 3.1           | Neural Network Theory and Multilayer Perceptron                       | 36 |

|     | 3.2           | Back-Propagation Training Algorithm                                   | 40 |

|     | 3.3           | Limb Endpoint Locomotion Prediction — An ANN Biomedical Case Study .  | 43 |

|     |               | 3.3.1 Motivation and Background                                       | 43 |

|     |               | 3.3.2 Proposed ANN-based Model                                        | 45 |

|     |               | 3.3.3 ANN Structure Exploration                                       | 47 |

|     |               | 3.3.4 End-Point Locomotion Prediction Performance of ANN-Based Model. | 47 |

|            |               | 3.3.5 Remaining Questions                                      | 50         |

|------------|---------------|----------------------------------------------------------------|------------|

| 4.0        | $\mathbf{AU}$ | TONOMOUSLY RECONFIGURABLE ARTIFICIAL NEURAL NET                | <b>'</b> _ |

|            | W             | ORK ARCHITECTURE                                               | 54         |

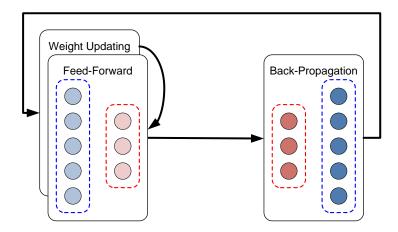

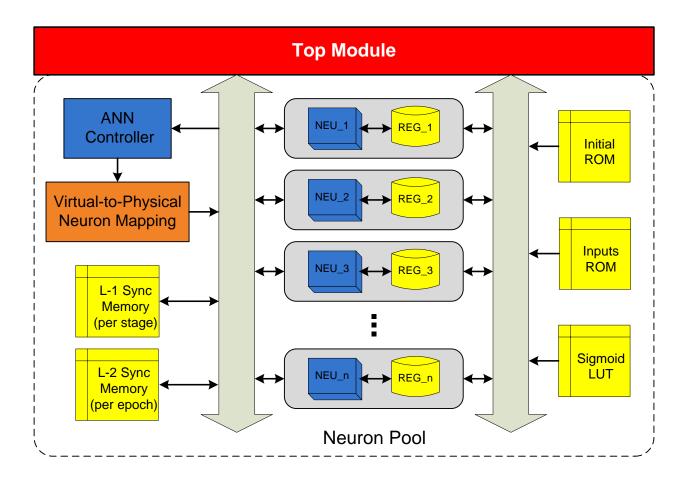

|            | 4.1           | System Overview                                                | 55         |

|            | 4.2           | Biologically Inspired Approaches                               | 60         |

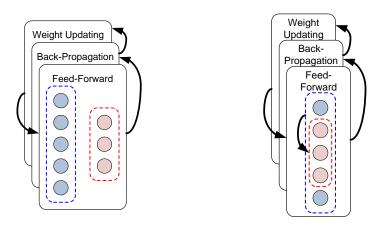

|            | 4.3           | Self-Healing Artificial Neural Network                         | 64         |

|            |               | 4.3.1 Distributed Neural Network Architecture                  | 67         |

|            |               | 4.3.2 Decoupled Virtual-to-Physical Neuron Mapping             | 71         |

|            |               | 4.3.3 Dual-Layer Memory Synchronization Mechanism              | 76         |

|            | 4.4           | Self-Optimizing Artificial Neural Network                      | 82         |

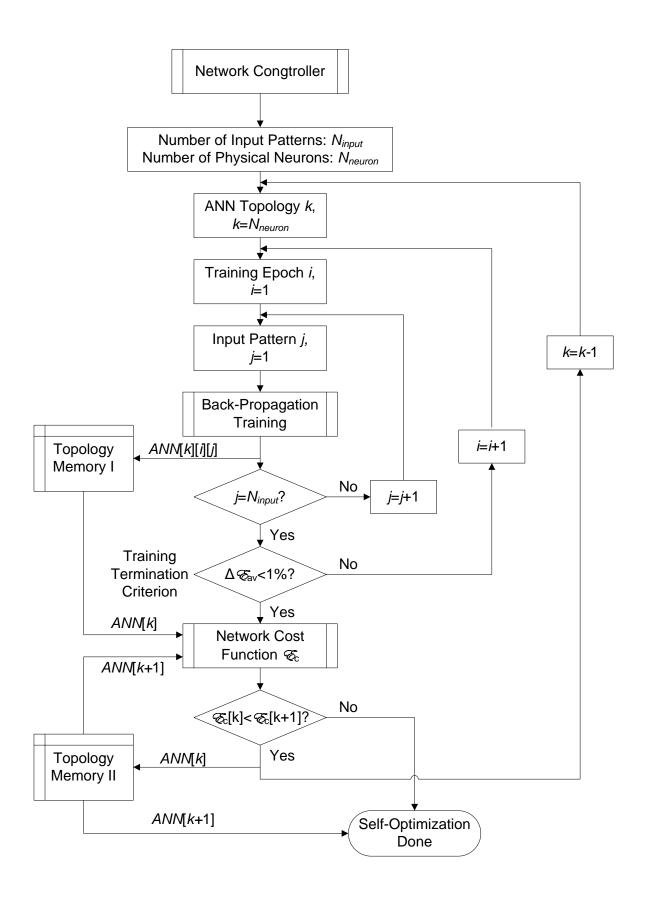

|            |               | 4.4.1 Structural Optimization of Artificial Neural Networks    | 84         |

|            |               | 4.4.2 Neural Pruning                                           | 88         |

|            |               | 4.4.3 ARANN-based Self Optimization                            | 90         |

|            |               | 4.4.4 Power/Thermal-Aware Design Optimization                  | 95         |

|            | 4.5           | Virtual-to-Physical Neuron Mapping                             | 97         |

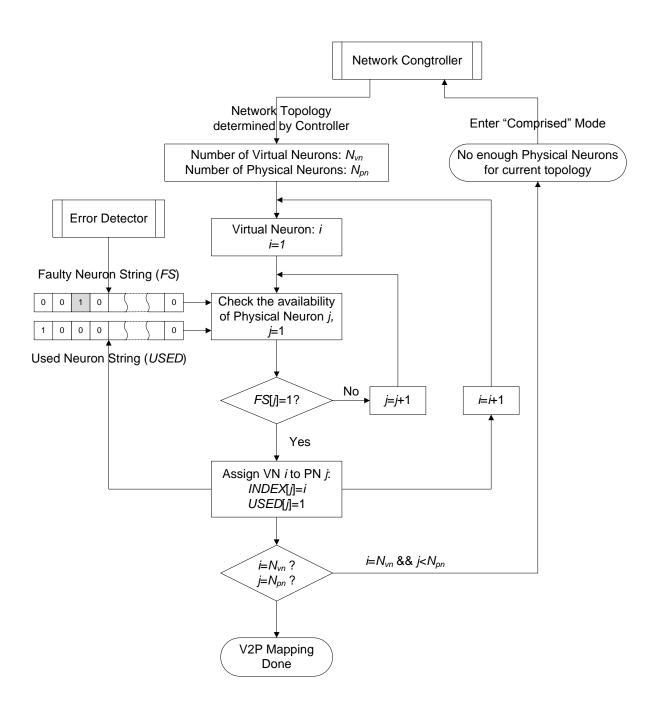

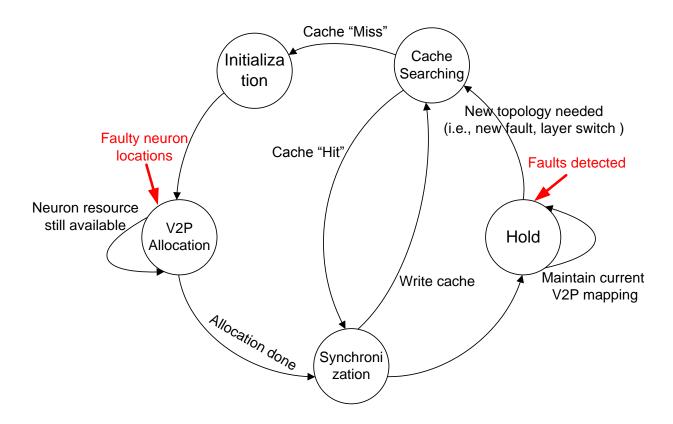

|            |               | 4.5.1 Adaptive Physical Neuron Allocation                      | 99         |

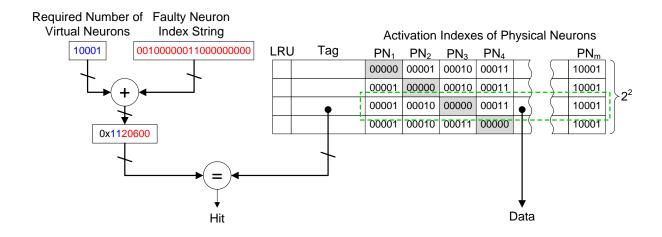

|            |               | 4.5.2 Cache-Accelerated Adaptive Physical Neuron Allocation    | 103        |

|            |               | 4.5.3 Virtual-to-Physical Neuron Mapping Memory                | 105        |

|            |               | 4.5.4 Mask-Based Virtual-to-Physical Neuron Mapping Memory     | 107        |

|            |               | 4.5.5 Comparisons and Considerations of V2P Mapping Schemes $$ | 120        |

| <b>5.0</b> | $\mathbf{AR}$ | ANN IMPLEMENTATION CHALLENGES AND SOLUTIONS .                  | 124        |

|            | 5.1           | Arithmetic Representation                                      | 124        |

|            |               | 5.1.1 Floating-Point Format                                    | 126        |

|            |               | 5.1.2 Fiexd-Point Format                                       | 126        |

|            |               | 5.1.3 Comparisons Between FLP and FXP Formats                  | 129        |

|            | 5.2           | Compact Multi-Purpose Neurons                                  | 130        |

|            |               | 5.2.1 Two Input 16-Bit SIMD Dynamic Adders/Subtracters         | 130        |

|            |               | 5.2.2 16-Bit Two's Complement Multiplication                   | 131        |

|            |               | 5.2.3 Squared Errors                                           | 132        |

|            |               | 5.2.4 Subtract-and-Multiply Operations                         | 135        |

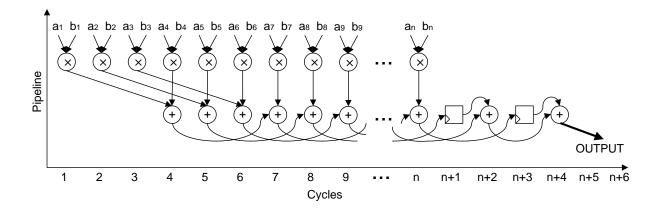

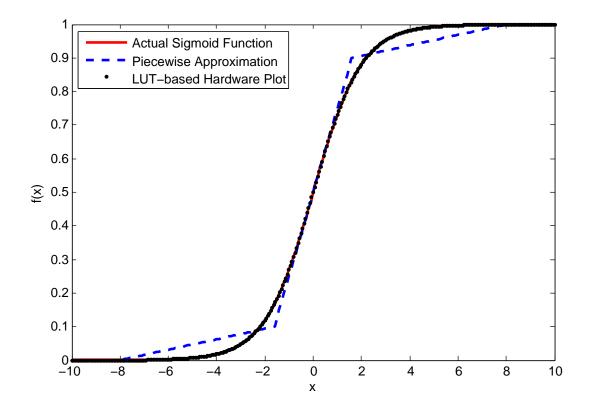

|     |      | 5.2.5 Multiply-Accumulate (MAC) Operations            | 135 |

|-----|------|-------------------------------------------------------|-----|

|     | 5.3  | Implementation Strategies of Activation Functions     | 138 |

|     |      | 5.3.1 LUT-Based Approach                              | 139 |

|     |      | 5.3.2 BRAM-Based Approach                             | 139 |

|     |      | 5.3.3 Piecewise Linear Approximation Approach         | 140 |

|     |      | 5.3.4 Performance Comparisons of Activation Functions | 141 |

|     | 5.4  | Bidirectional Time-Multiplexed ANN                    | 142 |

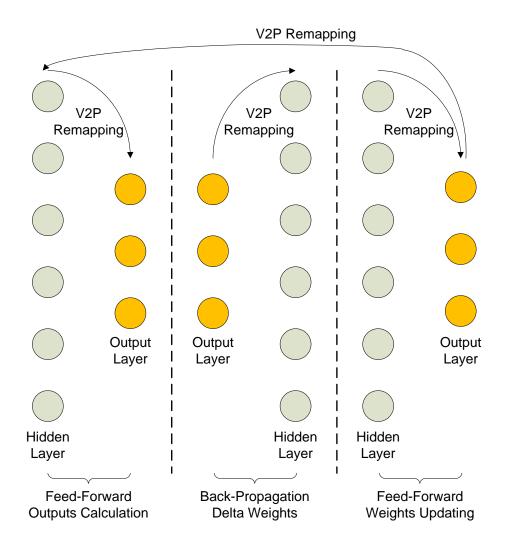

|     |      | 5.4.1 Time-Multiplexed Implementations                | 144 |

|     |      | 5.4.2 Design Framework                                | 147 |

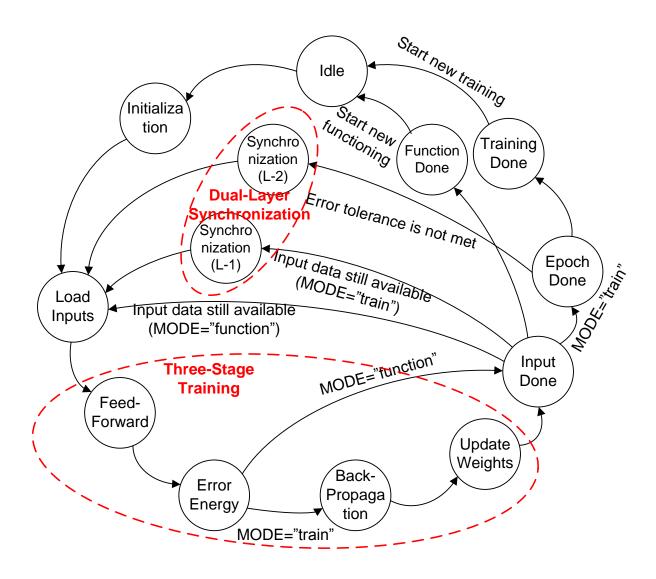

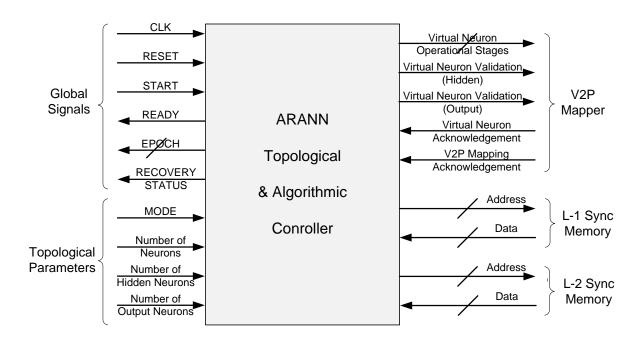

|     |      | 5.4.2.1 ANN Controller                                | 148 |

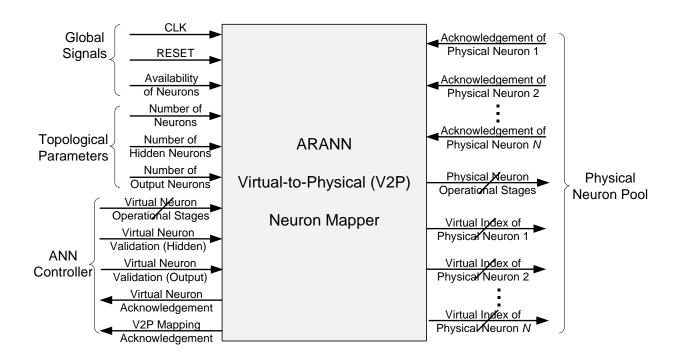

|     |      | 5.4.2.2 Virtual-to-Physical Neuron Mapper             | 152 |

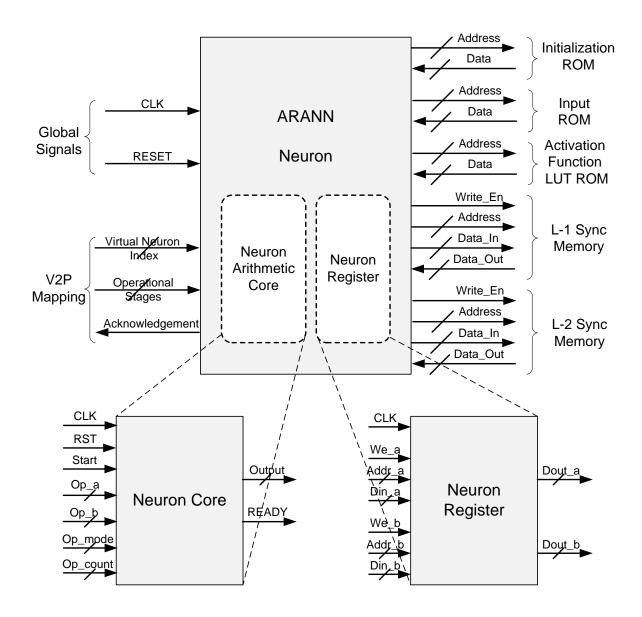

|     |      | 5.4.2.3 Neuron Units                                  | 156 |

|     |      | 5.4.2.4 Memory Units                                  | 158 |

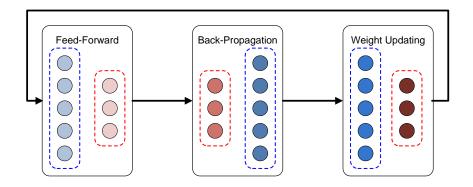

|     |      | 5.4.3 Three-Stage Learning Process                    | 158 |

| 6.0 | RE   | SULTS AND ANALYSIS                                    | 163 |

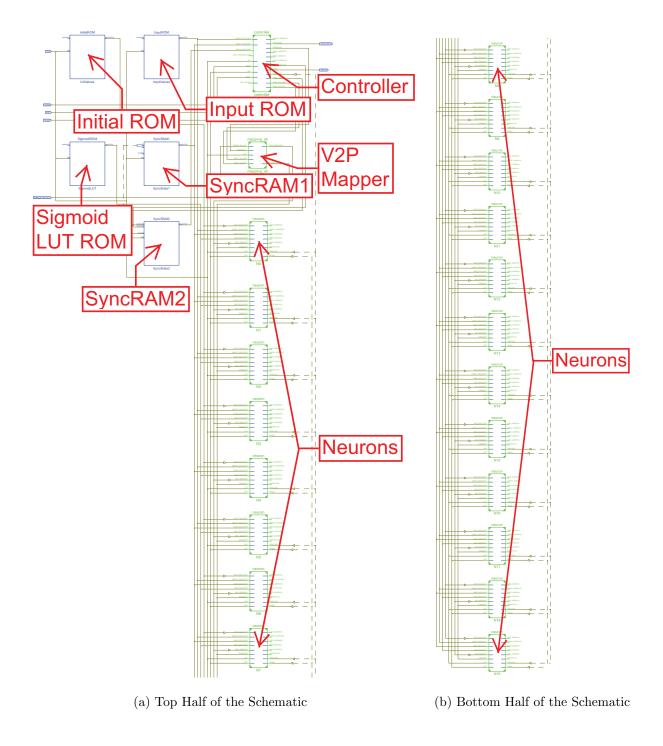

|     | 6.1  | Implementation of ARANN                               | 163 |

|     | 6.2  | Training Performance of ARANN                         | 169 |

|     | 6.3  | Self-Healing Process of ARANN                         | 176 |

|     | 6.4  | Self-Optimizing Process of ARANN                      | 189 |

| 7.0 | CO   | NCLUSIONS                                             | 196 |

|     | 7.1  | Thesis Summary                                        | 196 |

|     | 7.2  | Research Aims and Solutions                           | 198 |

|     |      | 7.2.1 Self-Healing ANN Solution                       | 199 |

|     |      | 7.2.2 Self-Optimization ANN Solution                  | 200 |

|     |      | 7.2.3 Low-Cost System Adaptation                      | 201 |

|     | 7.3  | Future Work                                           | 202 |

| DIE | T TC | OCDADUV                                               | 205 |

## LIST OF TABLES

| 1 | Examples of Neural Network Hardwares                                     | 19  |

|---|--------------------------------------------------------------------------|-----|

| 2 | Comparison of Performance and Power Consumption among Software, FPGA,    |     |

|   | and ASIC Implementations of An ANN System                                | 23  |

| 3 | Fitting Performance among 2 ANN-based and 2 Statistical Regression-based |     |

|   | Prediction Schemes                                                       | 50  |

| 4 | Comparison of Reconfigurable Neuron Implementations                      | 98  |

| 5 | Comparisons of V2P Neuron Mapping Design Strategies                      | 121 |

| 6 | Applicability of V2P Neuron Mapping Design Strategies                    | 123 |

| 7 | Rounding Rules for 32-bit Multiplication Results                         | 133 |

| 8 | Comparison of Synthesis Results for LUT-based, PWL Approximation, and    |     |

|   | Block RAM-based Approaches                                               | 142 |

| 9 | Synthesis Results of ARANN Components                                    | 166 |

## LIST OF FIGURES

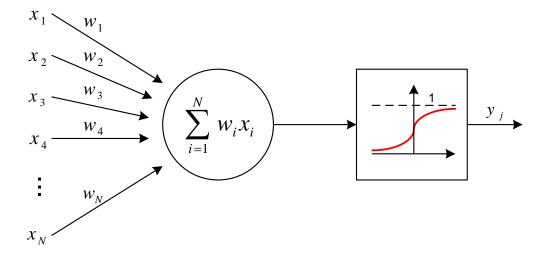

| 1  | An Artificial Neuron Based on McCulloch-Pitts Model                         | 37  |

|----|-----------------------------------------------------------------------------|-----|

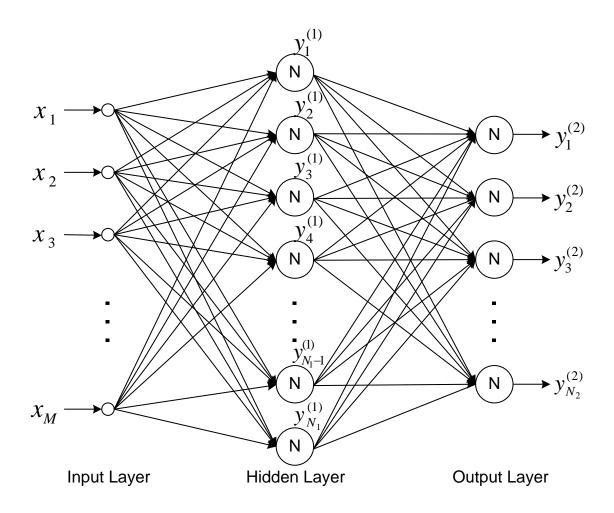

| 2  | Multilayer Feed-Forward Neural Network                                      | 39  |

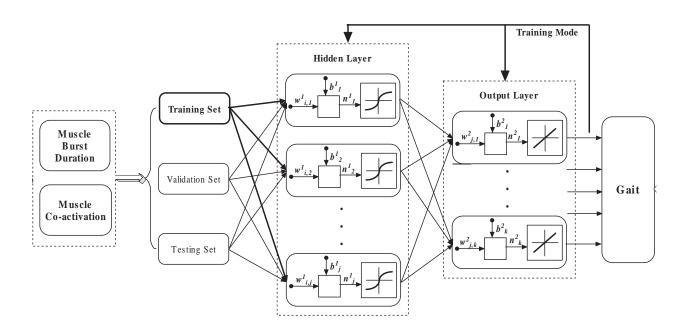

| 3  | Workflow of The Proposed ANN-Based Technique                                | 46  |

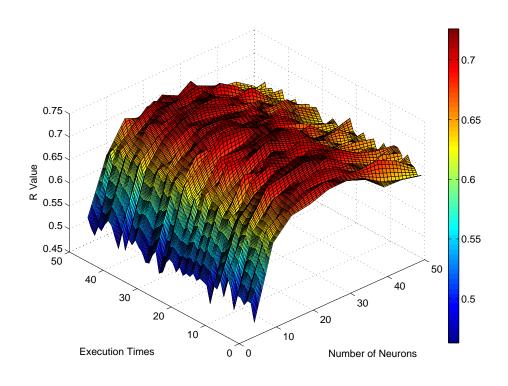

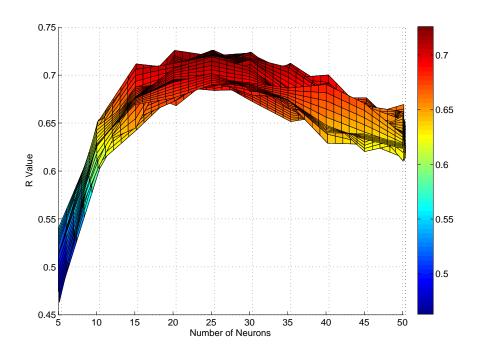

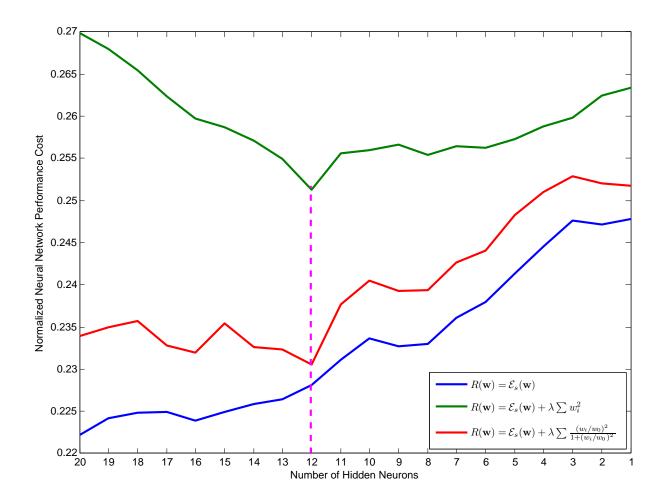

| 4  | The Accuracy of ANN as A Function of The Number of Hidden Neurons           | 48  |

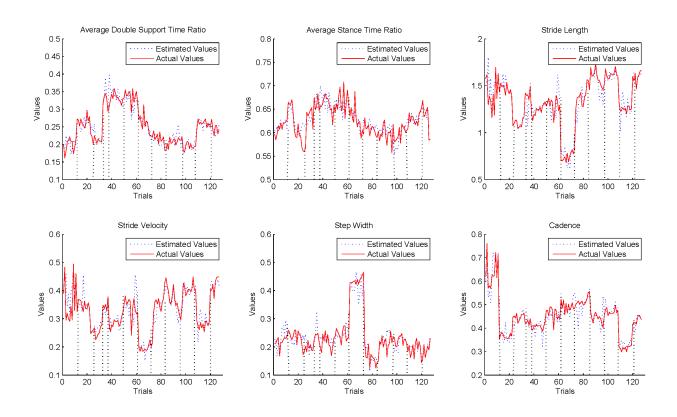

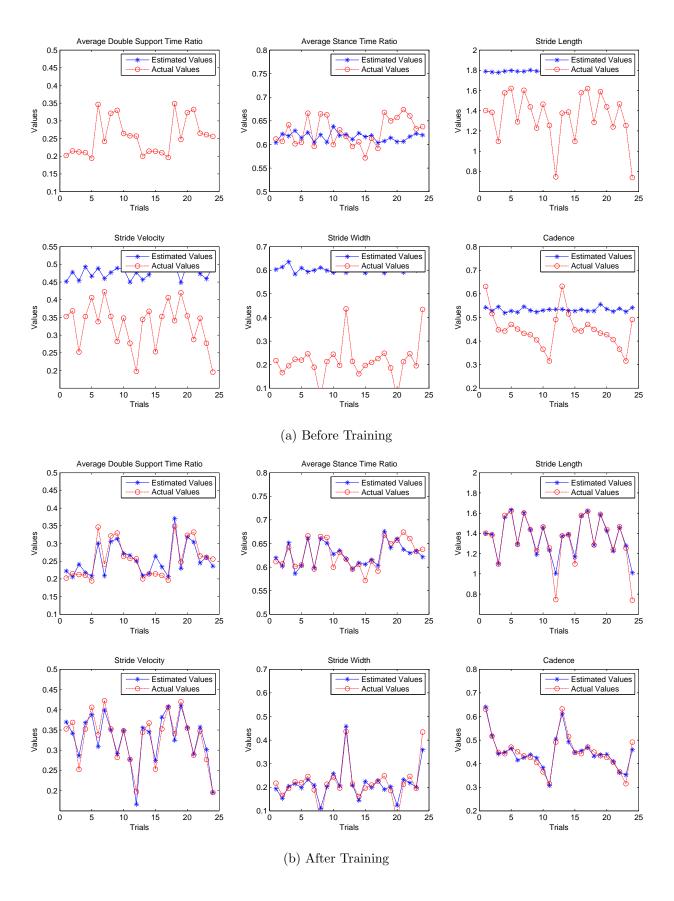

| 5  | End-Point Locomotion Prediction Performance of ANN-based Model              | 51  |

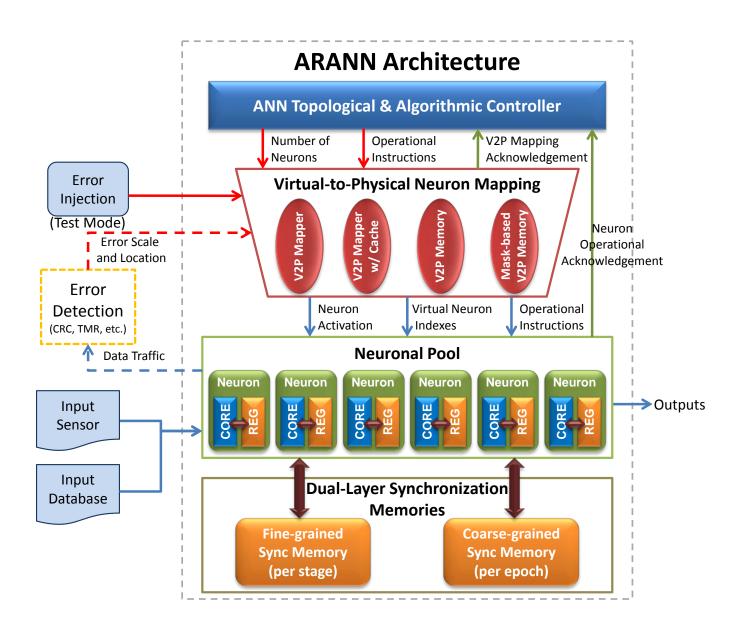

| 6  | System Diagram of the ARANN                                                 | 58  |

| 7  | Schematic Illustrations of the Damage to Neurons and Synapses               | 61  |

| 8  | Schematic Illustrations of the Synaptic Plasticity and Neurogenesis         | 63  |

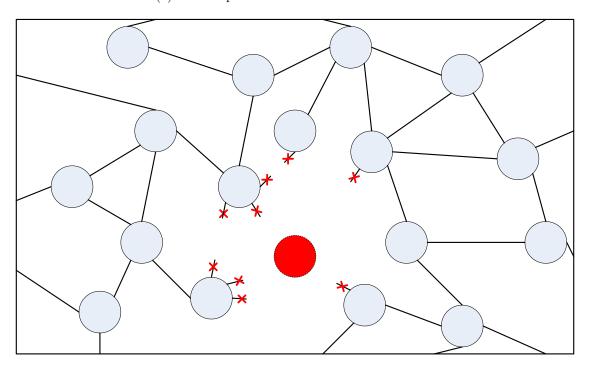

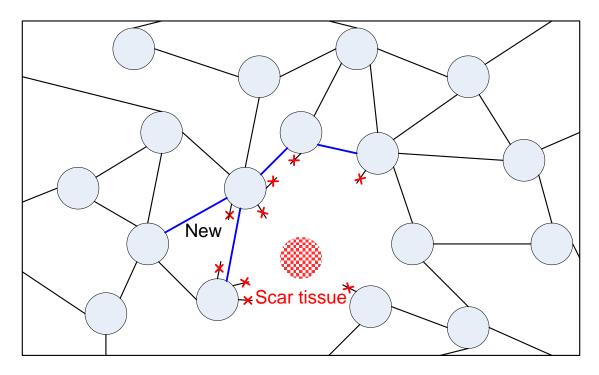

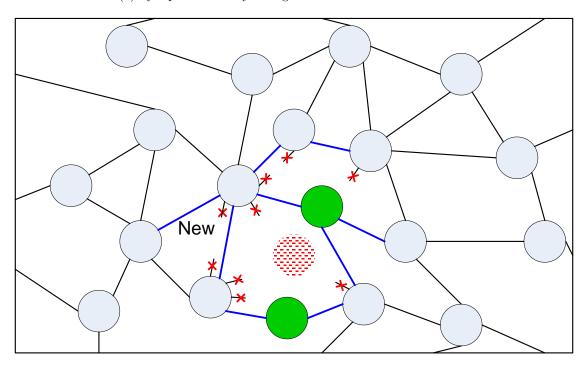

| 9  | Illustration Diagrams of The Neural Plasticity in ARANN                     | 66  |

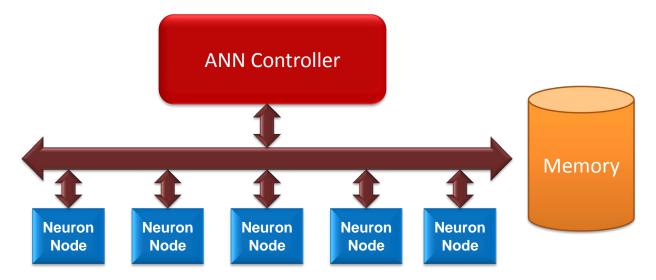

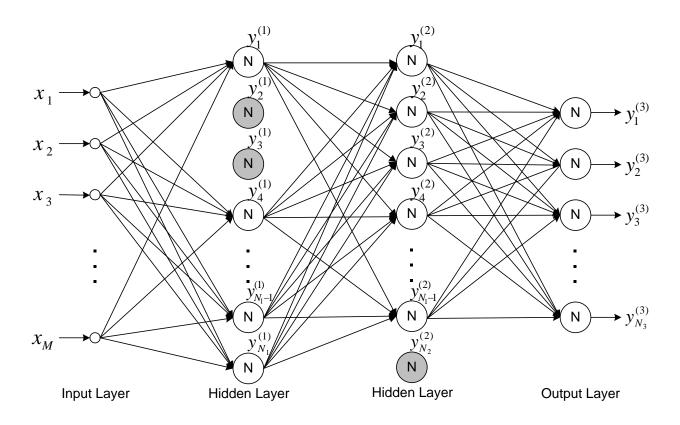

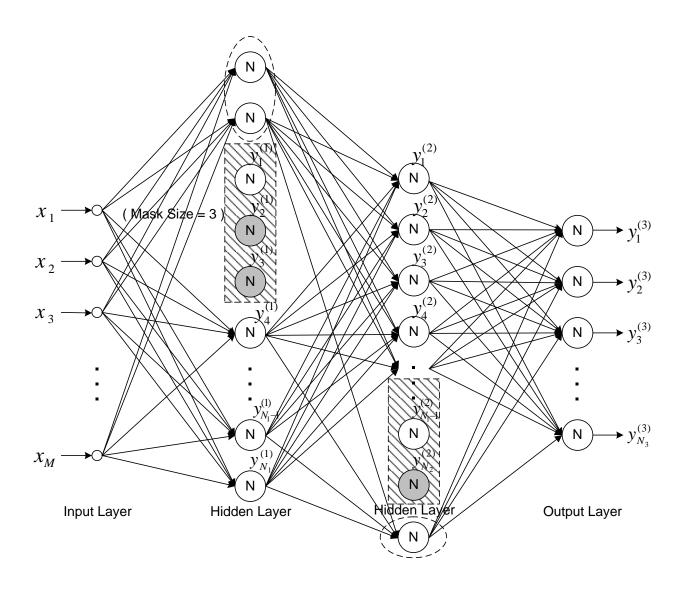

| 10 | System Architecture Diagrams of the Artificial Neural Network               | 69  |

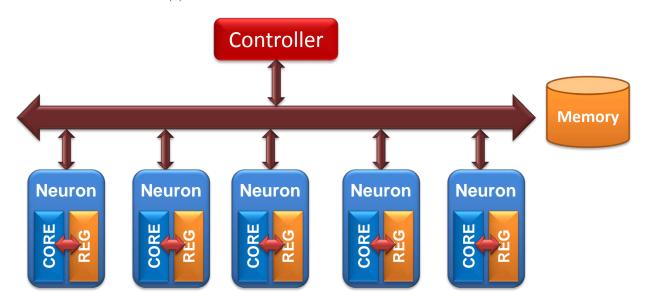

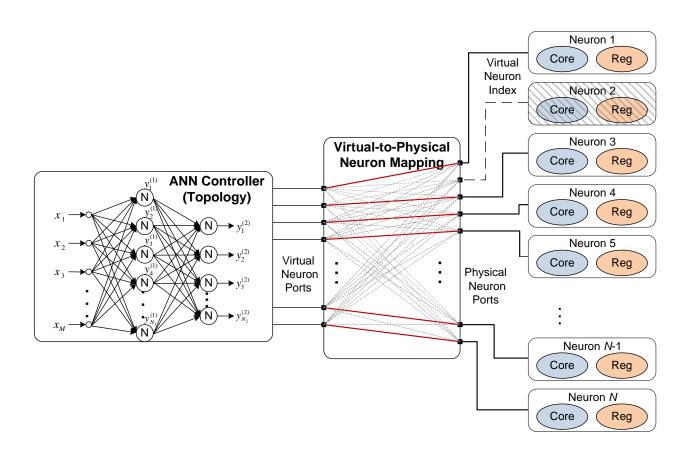

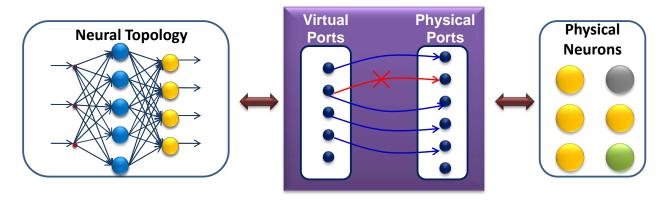

| 11 | Architectural Diagram of Virtual-to-Physical Neuron Mapping Mechanism       | 73  |

| 12 | Case Illustrations of Virtual-to-Physical (V2P) Neuron Mapping Mechanism .  | 75  |

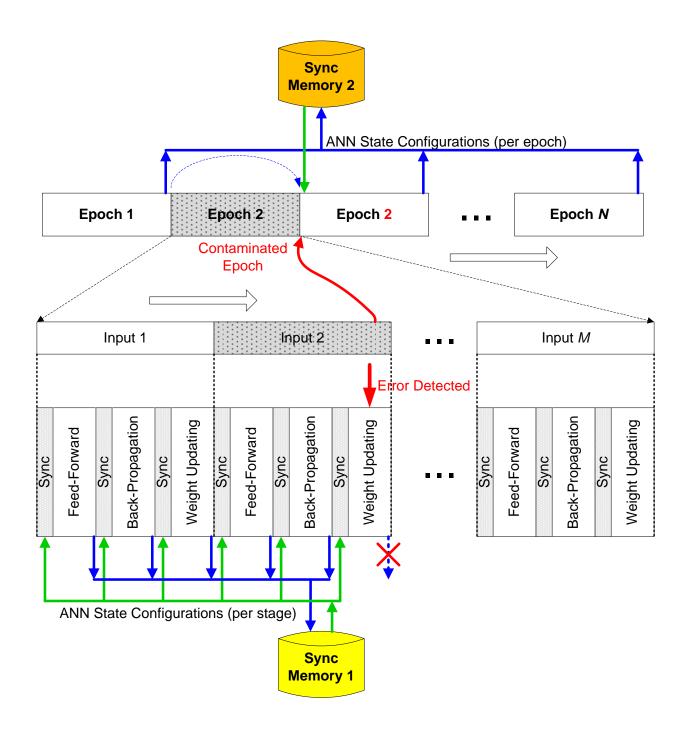

| 13 | Architectural Diagram of Dual-Layer Memory Synchronization Mechanism        | 80  |

| 14 | Illustration Diagram of Error Reaction Based on Dual-Layer Memory Synchro-  |     |

|    | nization Mechanism                                                          | 81  |

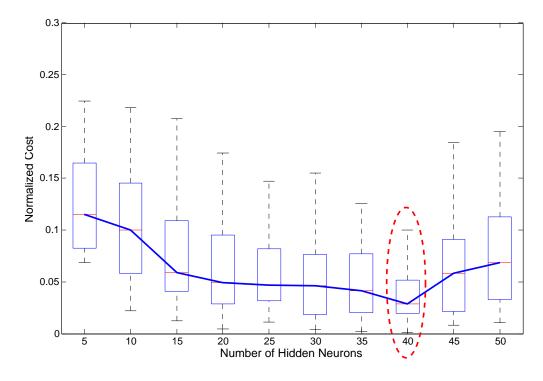

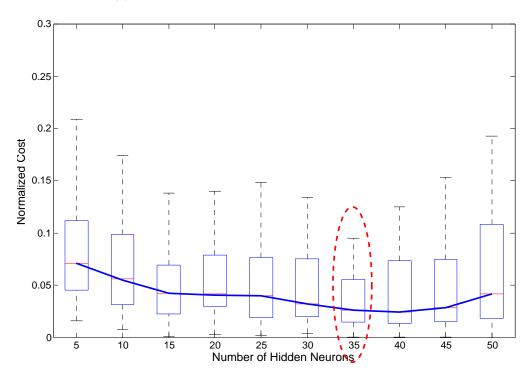

| 15 | The Normalized Cost over Different Numbers of Hidden Neurons                | 91  |

| 16 | Adaptive Self-Optimization Workflow of ARANN                                | 93  |

| 17 | Adaptive Physical Neuron Allocation Workflow                                | 100 |

| 18 | Stage Transitions and V2P Remappings during Neural Network Training Process | 102 |

| 19 | Architectural Diagram of Physically-Tagged Cache for Physical Neuron Allo-  |     |

|    | cation                                                                      | 104 |

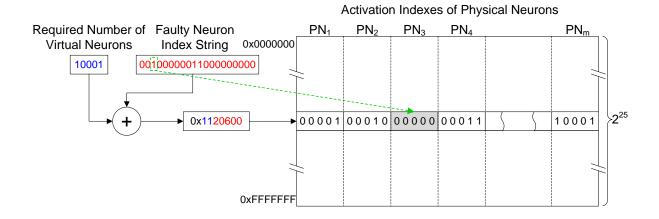

| 20 | Architectural Diagram of Virtual-to-Physical Neuron Mapping Memory          | 106 |

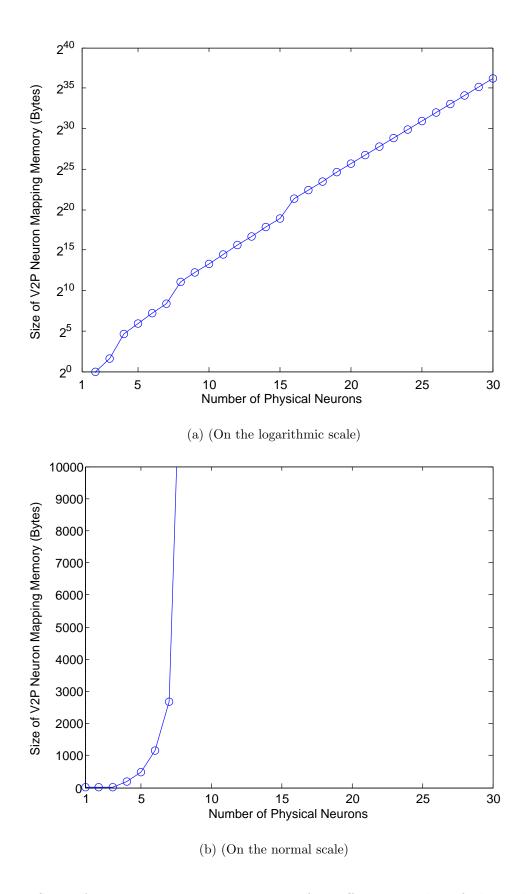

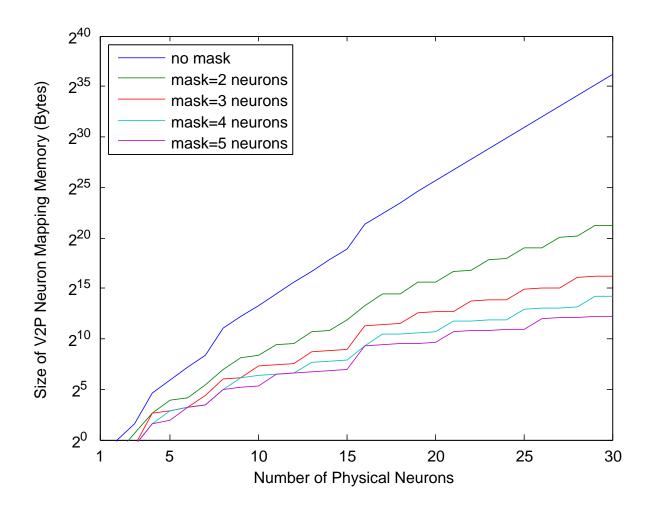

| 21 | Sizes of V2P Neuron Mapping Memory for Different Number of Physical Neuron   | s108 |

|----|------------------------------------------------------------------------------|------|

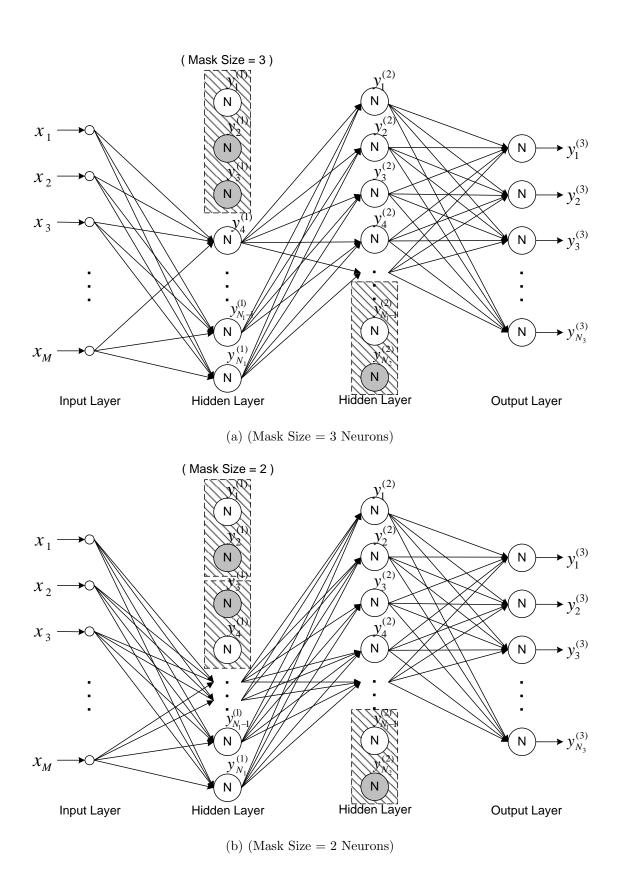

| 22 | Reconfigured ANN Interconnection Topology By Isolating the Faulty Neurons    | 109  |

| 23 | Mask-Based Reconfigured ANN Structural Topology                              | 112  |

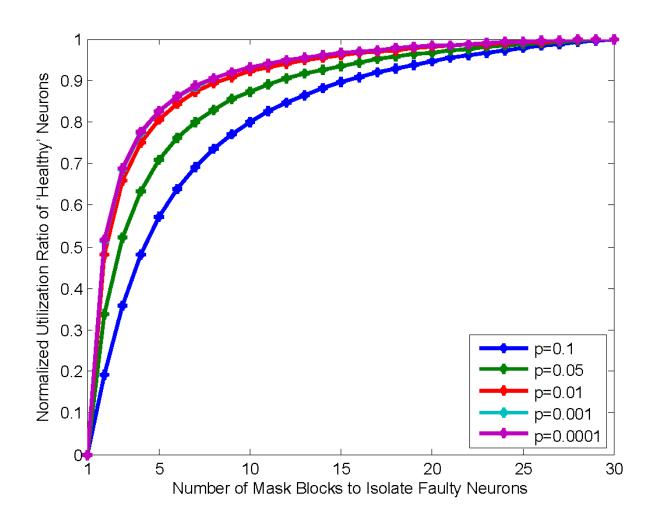

| 24 | Normalized Utilization Ratio of 'Healthy' Neurons with Different Probability |      |

|    | (p) of Hard Faults                                                           | 113  |

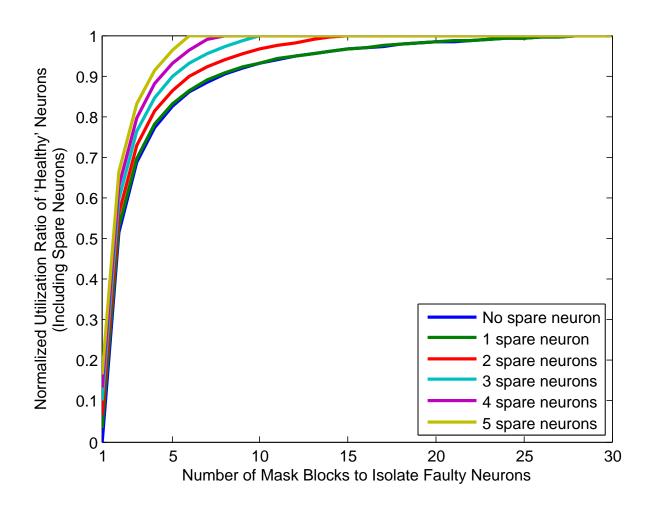

| 25 | Reconfigured ANN Interconnection Topology with Backup Neurons                | 115  |

| 26 | Normalized Utilization Ratio of 'Healthy' Neurons with Different Number of   |      |

|    | Backup Neurons                                                               | 117  |

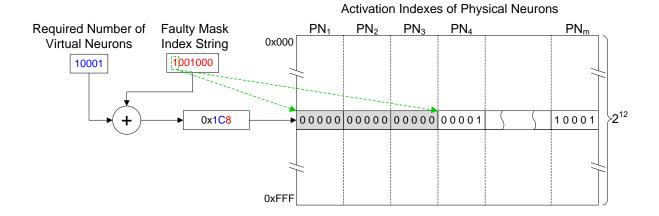

| 27 | Architectural Diagram of Mask-Based Virtual-to-Physical Neuron Mapping       |      |

|    | Memory                                                                       | 118  |

| 28 | Sizes of V2P Neuron Mapping Memory for Different Physical Neuron Numbers     |      |

|    | and Mask Sizes                                                               | 119  |

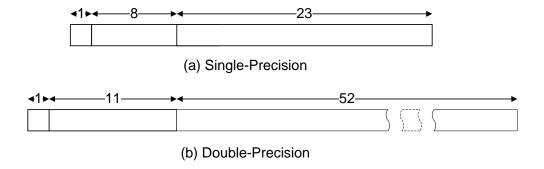

| 29 | IEEE Floating-Point Numbers                                                  | 127  |

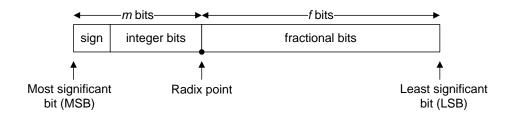

| 30 | Format of A Fixed-Point Number                                               | 127  |

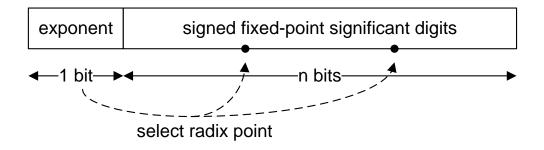

| 31 | Format of A Dual FXP Number                                                  | 129  |

| 32 | Two 16-bit SIMD Dynamic Adder/Subtractor                                     | 130  |

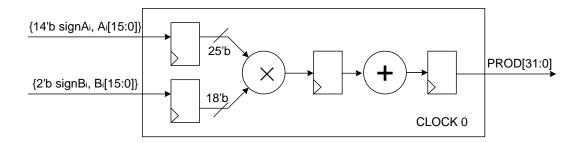

| 33 | 16-bit Two's Complement Multiplier                                           | 132  |

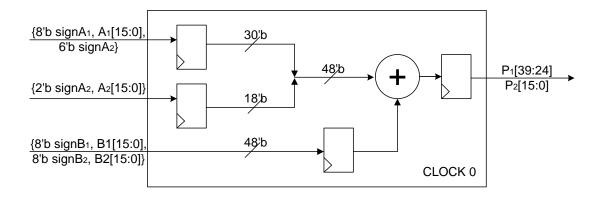

| 34 | Sum of Squared Errors Based on DSP48E                                        | 133  |

| 35 | DSP48E-Based Subtract-and-Multiply Operation: (A-B) x B                      | 134  |

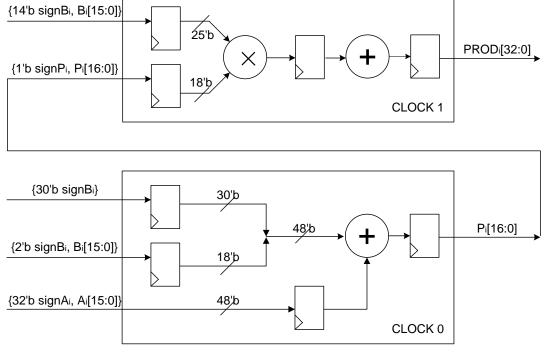

| 36 | DSP48E-Based Subtract-and-Multiply Operation: A x (1-B)                      | 135  |

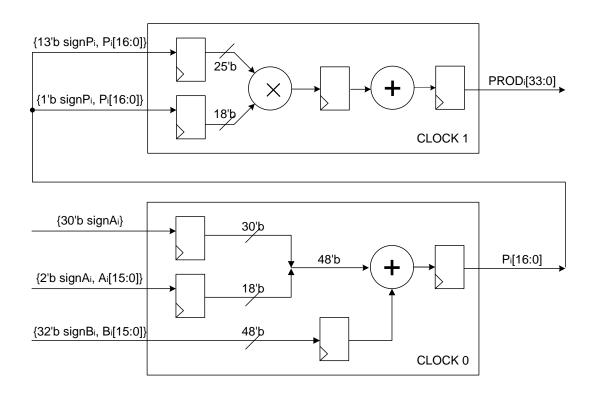

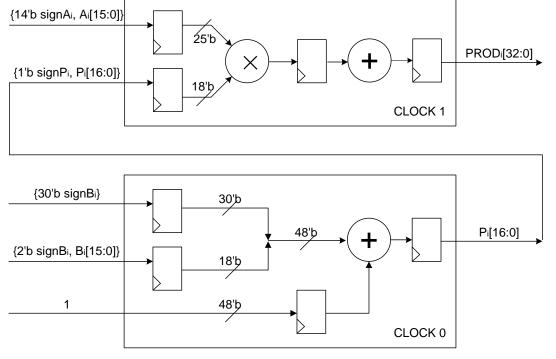

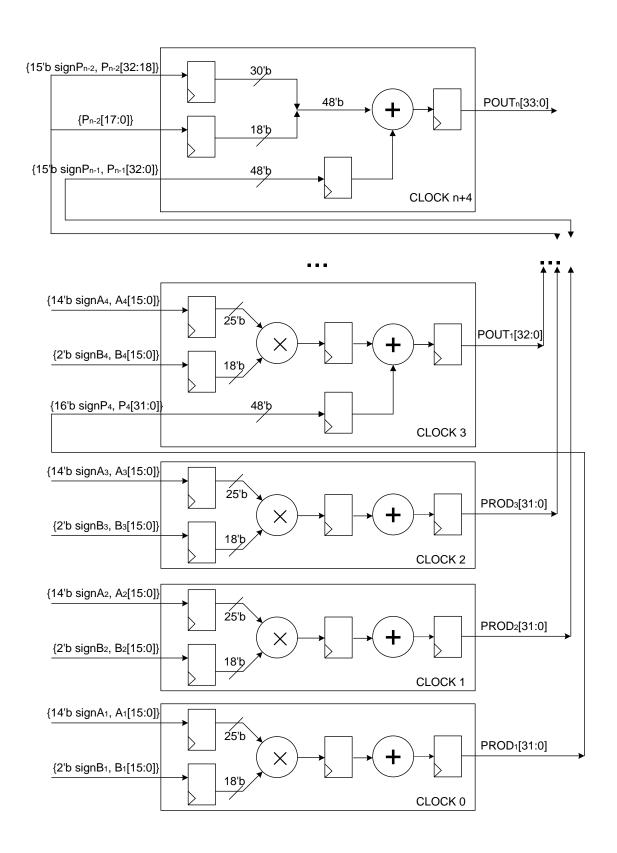

| 37 | DSP48E-Based Multiply-Accumulation                                           | 136  |

| 38 | Operation Data Flow and Pipeline Scheduling of Multiply-Accumulation         | 137  |

| 39 | Comparison of Acutal Log-Sigmoid Function, Piecewise Linear Approximation    |      |

|    | and BRAM-Based Hardware Implementation                                       | 141  |

| 40 | Design Options for Three-Stage MLP Neural Networks                           | 146  |

| 41 | Architecture Diagram of The Implemented Multilayer Perceptron (MLP) Neu-     |      |

|    | ral Network                                                                  | 147  |

| 42 | Finite State Diagram of The Implemented Multilayer Perceptron (MLP) Neu-     |      |

|    | ral Network                                                                  | 149  |

| 43 | Block Diagram of the ANN Topological & Algorithmic Controller                | 151  |

| 44 | Finite State Diagram of The Virtual-to-Physical Neuron Mapping Block          | 154 |

|----|-------------------------------------------------------------------------------|-----|

| 45 | Block Diagram of the Virtual-to-Physical Neuron Mapper                        | 155 |

| 46 | Block Diagram of the Physical Neuron Unit in ARANN                            | 157 |

| 47 | Register Organization for Each Neuron                                         | 159 |

| 48 | Schematic Diagram of the Implemented ARANN (20 Neurons)                       | 165 |

| 49 | Footprint Percentages of Major Components in Centralized and Distributed      |     |

|    | ANN Design Examples                                                           | 166 |

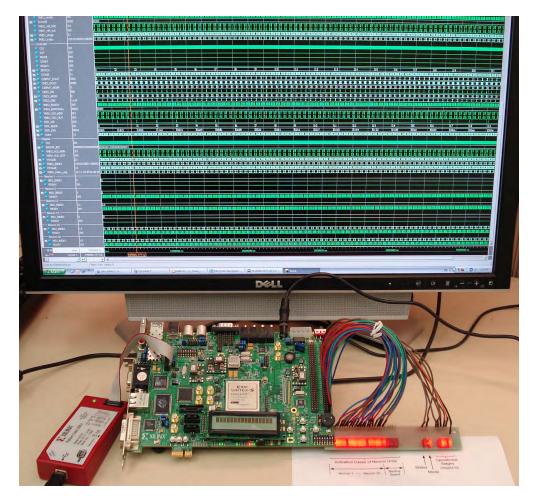

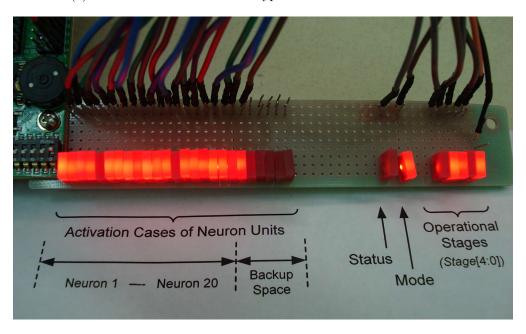

| 50 | The FPGA Prototype of the Proposed ARANN System                               | 168 |

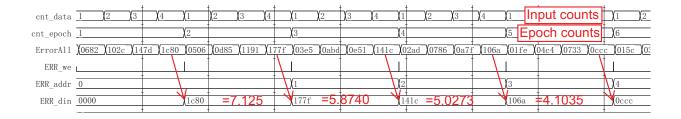

| 51 | Waveform Segment of Training Process in Post-Synthesis Simulation             | 171 |

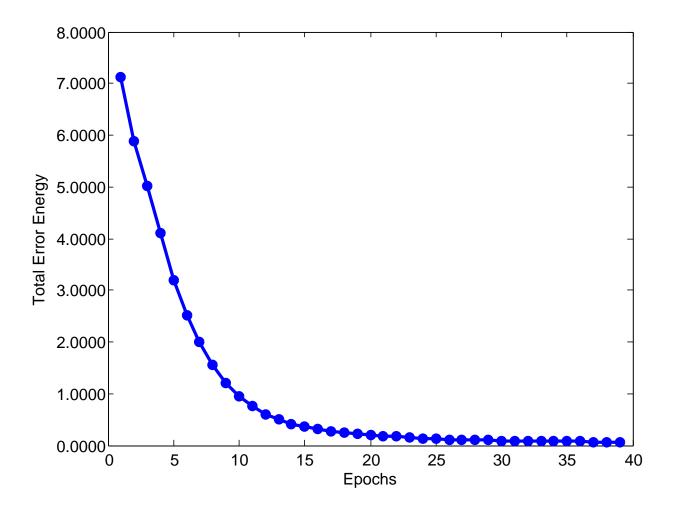

| 52 | Convergence of Total Error Energy During the Training Process                 | 172 |

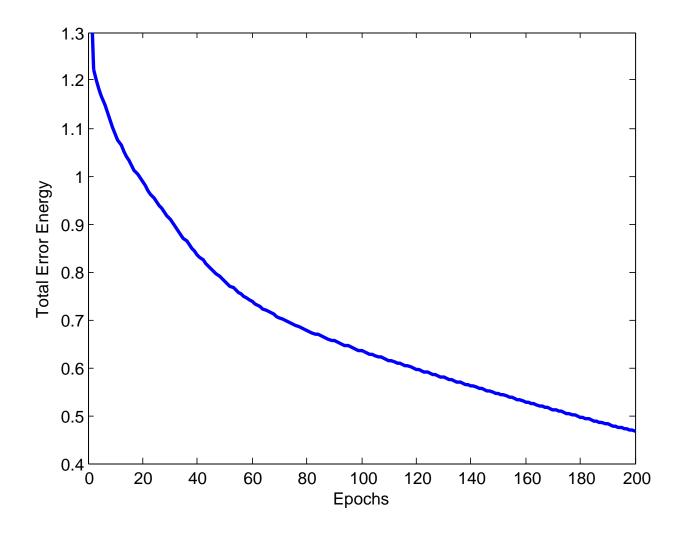

| 53 | Training Error Convergence of the Endpoint Locomotion Prediction Case         | 174 |

| 54 | Prediction Performance of ARANN for Endpoint Locomotion Prediction Case       | 175 |

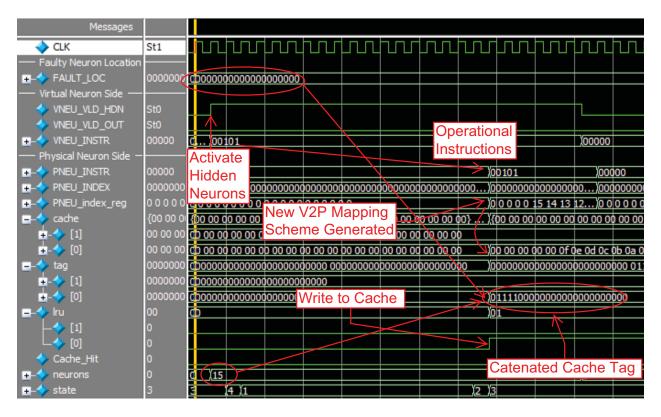

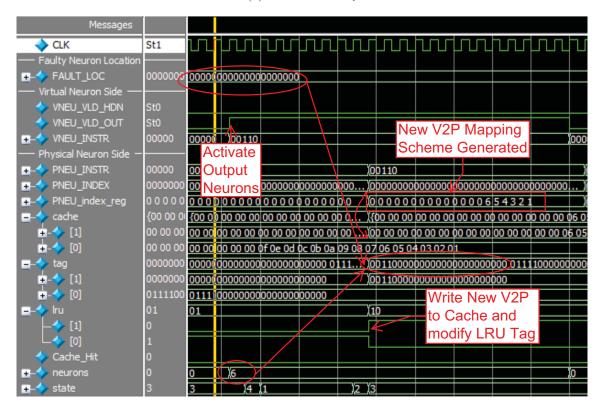

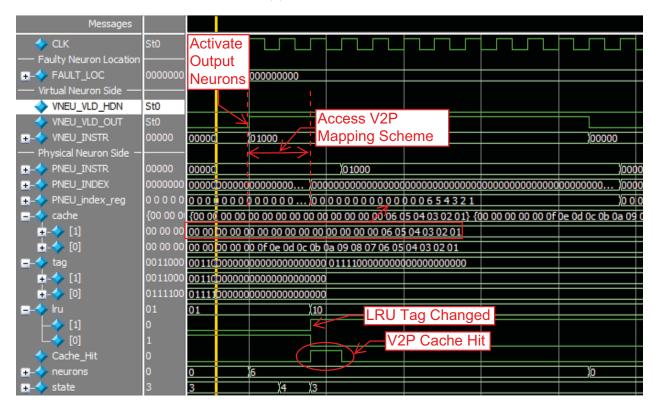

| 55 | Adaptations of V2P Mapping Scheme for Hidden & Output Layers (Cache Miss)     | 178 |

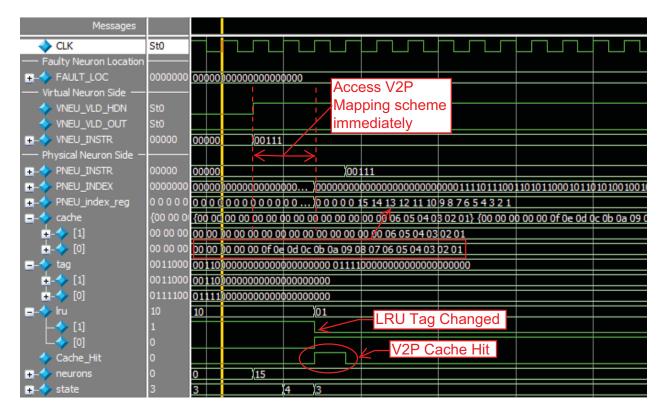

| 56 | Adaptations of V2P Mapping Scheme for Hidden & Output Layers (Cache Hit)      | 180 |

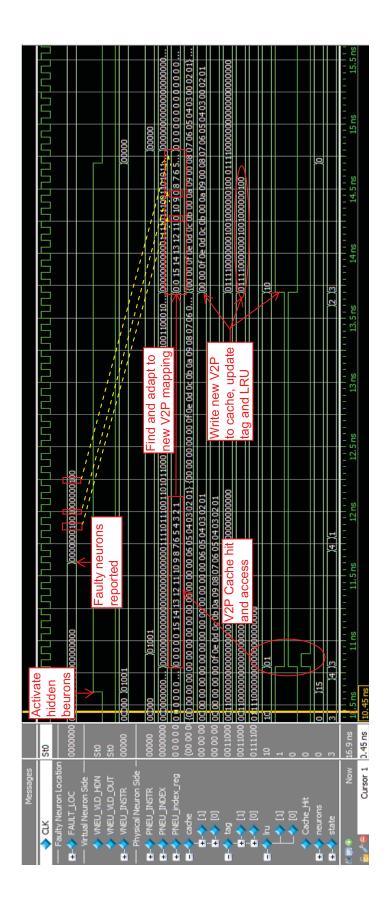

| 57 | Adaptation of V2P Mapping Scheme in case of Faulty Neurons Detected           | 181 |

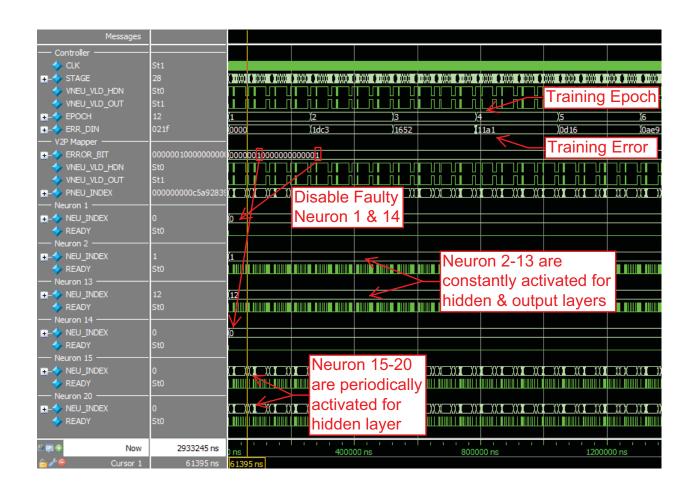

| 58 | Training Process and Neuron Allocation of ARANN with Faulty Neurons           | 183 |

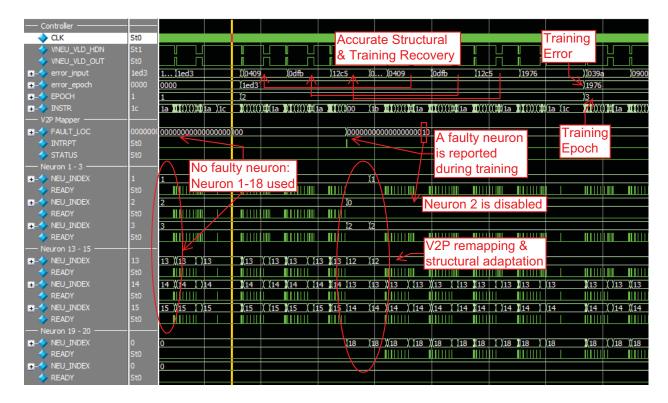

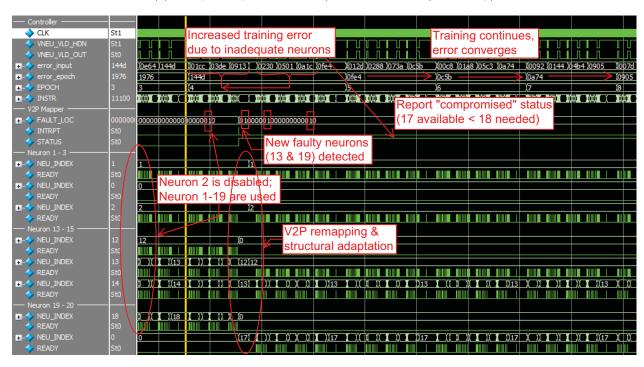

| 59 | Recovery of Training Process In Case of Fault-Triggered Structural Adaptation | 185 |

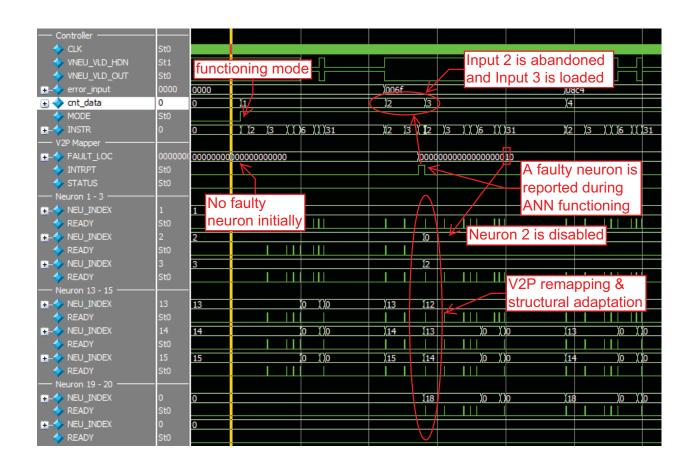

| 60 | ANN Functioning Process and Neuron Allocation of ARANN with Faulty Neu-       |     |

|    | rons                                                                          | 187 |

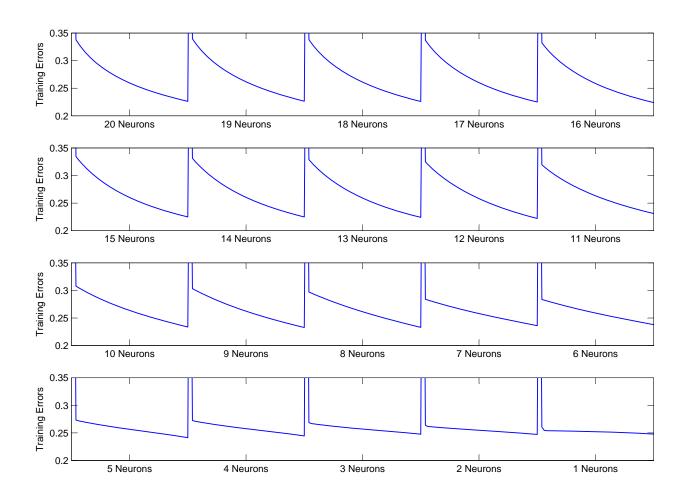

| 61 | Self-Optimizing Training Process of ARANN (20 $\rightarrow$ 1 neuron)         | 191 |

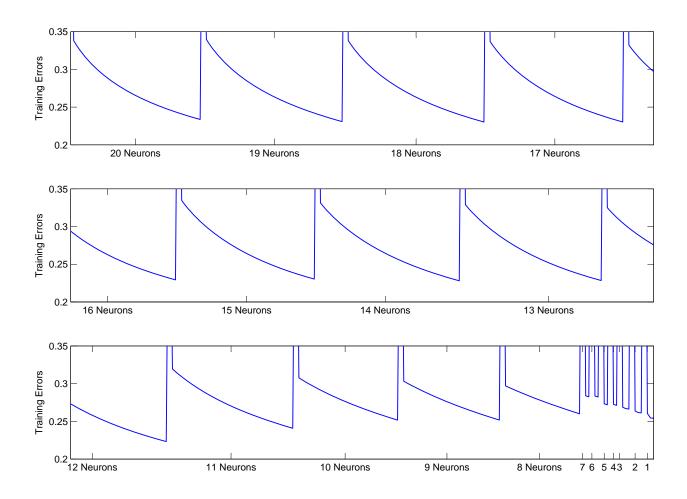

| 62 | Self-Optimizing Training Process of ARANN (20 $\rightarrow$ 1 neuron)         | 192 |

| 63 | Hybrid Performance and Overhead Evaluation in ARANN Self-Optimizations        | 193 |

#### ACKNOWLEDGEMENTS

This dissertation is intended to record and present one of my major research efforts during the Ph.D. study at the University of Pittsburgh. Fortunately, it has successfully finished after many months and years of hard work. However, it is the faculty, friends, and family members who have helped me to complete this dissertation. I would like to express my gratitude to these individuals for their support and assistance. Although I hope to list all people who offered their valuable help and suggestion to me and contributed to the extraordinary experiences I have been fortunate to enjoy over the past three years, I would inevitably leave out deserving colleagues, friends, and relatives and thus I am eager to show my sincerest respect and appreciation to all of "anonymous heroes" firstly.

The first person I would like to appreciate is my thesis advisor, Dr. Allen C. Cheng, for his constant guidance, encouragement, assistance, and support. Dr. Cheng not only put a lot of serious efforts into guiding my research but also spent tremendous time to proofread and correct all my works. Without him, the accomplishment of this dissertation would otherwise have remained only a dream. I have been fortunate enough to work with Dr. Cheng and have learned a lot from him. I've been deeply impressed by his admirable academic ambition, broad scientific view, remarkable enthusiasm, and exceptional intelligence full of new ideas. It is unimaginable how hard to mentor a foreign student and help him grow to be both a critical thinker and a qualified researcher. He spent countless nights in editing my manuscripts and confirming every aspect of research results to be tiniest level of detail. I can still remember the scenario when I received the revision of my first paper draft from Dr. Cheng. Every page is full of red markers with the modifications and comments from a single word to the whole section. Thanks to the extensive training offered by Dr. Cheng, I was excited to see less and less "red markers" shown in my paper drafts. More importantly, he constantly gave me

valuable suggestions and kept me abreast with the state of the art electronic and computer techniques which greatly benefit my research. Furthermore, he has also taught me many important lessons in life which will always guide me throughout my career.

Thanks to Dr. Steven P. Levitan, Dr. Zhi-Hong Mao, Dr. Marlin H. Mickle, Dr. Shi-Kuo Chang, and Dr. Wenyan Jia for serving on my doctoral dissertation committee.

Dr. Levitan is one of the most engaging, humorous, and friendly professors I've ever met. His incredible sense of humor and jokes made the taxing classes much more joyful and refreshing. I really enjoy the courses with him and appreciate his extensive expertise in VLSI and EDA areas. On the other side, Dr. Levitan is also among the most critical and strict faculty members in the pursuit of scientific excellence. The challenging questions he raised and inspirable comments were invaluable help to me while working on my dissertation.

Holding the joint Ph.D. degree from two big-name schools — MIT and Harvard, Dr. Mao is well known for his solid background in mathematics, control systems, computation intelligence, and neuroengineering. Dr. Mao is very approachable and warms to students readily. He has gained great reputation from students for his excellent teaching. He has guided me as a friend through his wisdom and valuable experience. I am really thankful for the generous time and promptness he offered in giving me suggestions and solutions to overcome research obstacles. I also thank him for being open and sharing with me his wonderful experience and perspectives on the academic careers.

As one of the most prestigious faculty members in our department, I am sincerely impressed by Dr. Mickle's unremitting devotion to research and teaching. Over the past half century, he has observed and actively engaged into the incomparable development of electronic and computer techniques. Now, he continues to share his wealth of experiences to all his students. In his computer architecture class, Dr. Mickle always has the wisdom and experience to simplify situations and things that seem so complicated to me.

Thanks to Dr. Chang and Dr. Jia, the external committee members, for their providing me significant comments and suggestions from other perspectives and helped me sharp my thinking. I could not work out this thesis without their dedicated help, guidance and support.

I would like to thank the Department of Electrical and Computer Engineering for the tremendous graduate education I have received in the past three years and especially those administrative staff for their kind help and dedicated support. Several individuals deserve special mention for their long valuable help during my studies in ECE. I thank William McGahey and Jim Lyle for their long, timely technical assistance with lab infrastructure. I owe a special debt to Theresa Costanzo and Sandy Weisberg for their kind understanding and patience to help me solve various problems and personal matters.

I've been especially fortunate to know and work with Yuwen Sun, Shimeng Huang, Joseph Oresko, Heather Duschl, Kingsley Adeoye, Jun Cheng, and Timothy Sestrich in the ACT Lab. I really enjoy the wonderful time with all these good friends, either in research or in pleasure. They are the constant source of my inspiration. Their intelligent ideas and technical skills have inspired and boosted lots of my work.

I would like to gratefully and sincerely thank Michael and Bronwynn McAdams, Bill and Phyllis Sutton (my beloved grandpa and grandma in America), Carol McAdams, and all members in Sutton's family and McAdams's family. It is your strong faith in the faithful God, admirable love, friendly help, and selfless support that help me survive in another country and feel like living at another home with many cordial family members. I am so grateful for your accompany and all you did in the past three years.

My family has been a tremendous source of love, encouragement, and inspiration. I thank my parents, Yuejie Jin and Suxia Guo, for their faithful love and persistent supports allowing me to continue my earnest pursuit in sciences. Their kind indulgence has kept me working towards my ambitious goals through my entire life. Also, I wish to express my earnest gratitude to my mother in law, Ms. Hongxu Zhao. She provided me with unending understanding, encouragement and immeasurable support on my studies, and endured the suffering of missing her daughter alone.

Finally, and most importantly, I would like to express my deepest appreciation to my wife Jie Yin. Your unwavering love, great support, helpful encouragement, quiet patience, kind indulgence, and significant sacrifice were undoubtedly the bedrock upon which I can continue my academic pursuit in Pittsburgh in the past three years. I am very thankful for your faithfully staying besides me during the most difficult and confusing time of my life. Without you, I can't believe this work could be finished as fast and well. I love you so much!

#### 1.0 INTRODUCTION

#### 1.1 RESEARCH MOTIVATION AND PROBLEM STATEMENT

Throughout the history of digital electronics, the technology has improved exponentially over time. The performance of devices is roughly doubling every 18 months because transistor size and cost of chips have shrunk at an impressive pace. Unrelenting advances in the transistor density of integrated circuits have resulted in a large number of engineered systems with diversified functional characteristics to meet various demands of the human life, ranging from micro-embedded devices, implantable medical devices, smart sensors, to critical infrastructure. Correspondingly, the complexity of system-level design for these increasingly evolved engineered systems is further compounded when interdisciplinary requirements are included, for example, massive integration and interconnection between components and subsystems, feedback and redundancy. The increasingly shrinking electronic technology and the compound complexity in these systems have resulted in substantial increases in both the number of hard errors [78], mainly due to variation, material defects, and physical failure, as well as the number of soft errors [259], primarily due to alpha particles from normal radiation decay, from cosmic rays striking the chip, or simply from random noise. Although these complex systems are designed to guarantee robust operation to the events that have been anticipated and accounted for in the design blueprint, unfortunately, most engineered systems still operate under great risk of uncertainty. To ensure the appropriate operation of complex systems under highly unreliable circumstances, a new paradigm for design, analysis and synthesis of engineered systems is needed. It is therefore imperative that system designers build robust fault-tolerance into computational circuits, and that these designs have the ability to detect and recover the damages causing the system to process improperly or even disabled.

Recently, the concept of autonomous reconfigurability has emerged and evolved to be a promising mechanism for ensuring appropriate operational levels during and after unexpected natural or man-made events that could impact critical engineered systems in unforeseen ways or to take advantage of unexpected opportunities. Autonomous reconfigurability refers to a system's ability to change its structure and operations or both in response to an unforeseen event in order to meet its objectives. This concept can be realized and advanced using the powerful state-of-the-art computational platforms and techniques, including a collection of hardware devices, software, networks, and ubiquitous computation, which can provide the capability for embedding reconfigurability into complex engineered systems. Thus, as one fundamental infrastructure, a flexible hardware substrate is required to support the idea of "reconfigurability", providing considerable space and performance for very large-scale integration of heterogeneous, multi-functional circuitries and enough flexibility for allowing the adaptation mechanism to modify the system. Specifically, the hardware substrate must provide a mechanism to accommodate redundant system components or design elements, to evaluate and change different possible topologies/connections dynamically, to be easily accessed internally and externally at any point in time, and to allow a sufficiently wide search space.

Artificial neural network (ANN), an established bio-inspired computing paradigm, mimics its biological counterpart in the human brain to provide self-adaptive flexibility and powerful learning ability. Such neural networks usually involve a highly structured network of simple processing elements (neurons), which can exhibit complex global behaviors, determined by the synaptic connections between processing elements and specific element parameters. The true power of neural networks lies in their abilities to represent both linear and non-linear relationships and to learn these relationships directly from the data being modeled. Given its considerable capability in recognizing complex patterns, ANN has proved very effective in a variety of real-world problems [230] and has been particularly investigated for emerging biomedical applications [15, 65, 121, 170]. For instance, many successful applications of neural networks on biomedical problems have been extensively reported and demonstrated, including electrocardiography (ECG) [47, 120, 119, 134, 135, 208, 261], electromyography (EMG) [29, 33, 88, 106, 210, 292], electroencephalography (EEG) [56, 140, 171, 175, 265, 267],

medical speech [132, 243, 309] and image processing [149, 167, 182, 234], etc. Accordingly, many dedicated ANN-based devices and systems have been developed using off-the-shelf hardware to facilitate the healthcare and clinical treatment. As people become more active in monitoring their own health conditions and the remarkable development of telemedicine and pervasive healthcare techniques in recent years, ultra-portable and ultra-reliable ANN-based medical systems have become of great interest to the whole society.

Specifically, for the portable goal, it may not be optimal to design a highly redundant system providing exhaustive coverage on any system failure. Emerging smart biomedical devices will be either worn by people or implanted into human body, thus they are expected to play significant roles in non-stop routine monitoring and directing some medical response mechanisms, such as implanted pacemakers and defibrillator [28, 155, 235, 236, 296, 297], wearable functional electrical stimulation (FES) devices [76, 77, 282, 283, 299], or prosthetic limbs [9, 192, 160, 263]. It is manifest that how severe problems can be caused, sometimes people would die from this, if the devices can not work properly due to unexpected faults. Meanwhile, it is also unacceptable that the systems have been out of order for a long time and the patients have to wait for the repair or replacement of the broken devices, not to mention that sometimes it would be really difficult to replace a device without invasive surgery.

Like other electronic systems, ANN-based systems are also increasingly vulnerable to both transient and permanent faults [157] which sometimes can be catastrophic, especially for medical applications. Conventional fault-tolerant techniques applicable to ANN-based systems include spatial redundancy, temporal redundancy, and coding [227]. Those techniques, such as Error Correction Coding (ECC) [41, 53, 83], Dual Modular Redundancy (DMR) [82, 278] or Triple Modular Redundancy (TMR) [215, 244, 257, 260], usually consume considerable system resources and energy, which can be prohibitive to meet the strict requirements of next-generation portable or implantable medical applications. Moreover, their lack of dynamic adaptability makes their protection effective only against faults that can be conceived at the design stage.

Inspired by the precise, systematic, sophisticated, supremely intelligent, and essentially AR-based automatic recovery mechanisms of the mammalian Central Nervous System (CNS) to react to unexpected injuries or diseases, we would like to explore the possibility to mimic

CNS's faulty reaction strategies and to develop a cyber-enabled artificial neural network environment with self-healing and self-optimizing capabilities. This dissertation proposes a novel *Autonomously Reconfigurable Artificial Neural Network (ARANN)* architectural framework. Leveraging the inherently homogeneous structural characteristics of neural networks, ARANN is capable of adapting ANN's structures and behaviors, both algorithmically and microarchitecturally, to react to unexpected faults at any neuron.

In this study, we will examine and investigate various techniques to help build a novel flexible and reliable artificial neural network platform, which is particularly suitable for nextgeneration mission-critical applications requiring high degree of reliability and portability.

#### 1.2 SCOPE OF THESIS

#### 1.2.1 Research Hypothesis and Aims

It is well demonstrated that the reliability issues of future highly integrated electronic systems have become increasingly severe. While there are steadily increasing demands on the reliable, fault-tolerant devices to improve the quality of people's lives, particularly in the biomedical domain to facilitate the medical treatment and prevention of individuals. In this study, we will focus on a particular important computing technique widely used in biomedical applications — artificial neural network — and investigate the possibility of building reliable and fault-tolerant ANN-based systems from a biologically inspired perspective. Orthogonal with conventional electronic reliability design techniques, we would like to explore an alternative way to augment the fault-tolerance and resilience of ANN-based hardware systems, leveraging the inherently homogeneous structural characteristics of neural networks. The research hypothesis of this study is that:

"Reliable and fault-tolerant ANN-based next-generation biomedical platforms can be realized by incorporating appropriate bio-inspired autonomous reconfigurability."

To test this hypothesis and demonstrate the feasibility of maintaining appropriate levels of operation and performance of ANN-based systems by autonomously reconfiguring its

structures and adapting its operations, in case of expected faults occurring at any computation nodes (neurons), we have several specific research aims shown as follows.

- 1. To enable ANN-based system to make appropriate structural adaptations in response to unexpected failures of computational neuron nodes.

- 2. To make ANN-based system determine a well balanced (Pareto-optimal) structure in an online and autonomous manner, when functioning accuracy, generalization capability and power consumption are all of great concern to designers and users.

- 3. To reduce the latency and overhead of structural adaptation and realize cost-effective system reconfiguration.

- 4. To demonstrate the efficacy and efficiency of the proposed autonomously reconfigurable artificial neural network architectural framework on a real hardware platform, aiming at a targeted application.

#### 1.2.2 Addressing ANN's Recovery Issue

Inspired by the precise, systematic, sophisticated and supremely intelligent automatic recovery mechanism of the mammalian Central Nervous System (CNS) to react to unexpected injuries or diseases, we would like to explore the possibility to mimic CNS's faulty reaction strategies and to develop a cyber-enabled artificial neural network environment with self-healing capabilities. Artificial neural network is essentially a highly scalable and parameter non-sensitive architecture, which means the overall system performance is determined by a large set of homogeneous neuron units and their associated synaptic connections, thus the change of a specific synaptic connection or the adding/removing a specific neuron unit will not cause tremendous effects on the whole ANN system. The inherent characteristics of neural networks make the principles of Autonomously Reconfigurability perfectly applicable to the ANN systems and help ANN systems meet the extremely stringent requirements on reliable operations. Given the fact that most previous reliability-aware studies usually enhance the fault tolerance capability of state-of-the-art hardware systems based on either space- or time-redundancy techniques, in this study, we hope to address the reliability issues of emerging ANN-based hardware from another perspective.

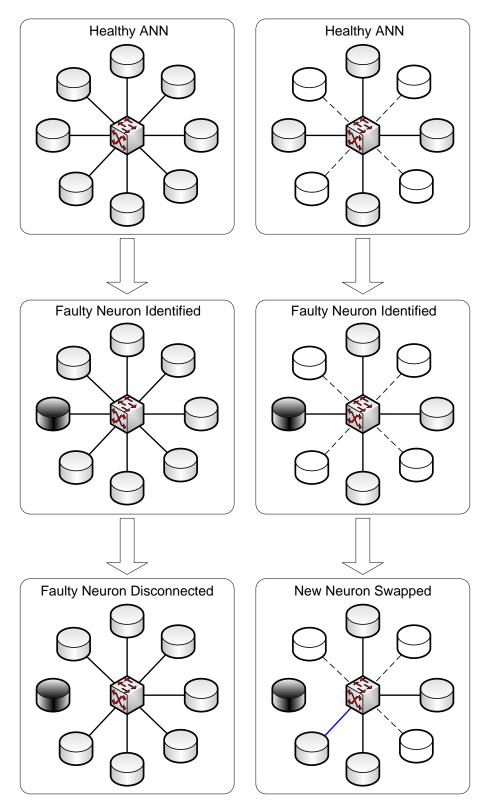

In principle, the ultimate goal is to achieve a reliable solution and at least maintain appropriate operational capabilities by making ANN system capable of adapting its structure or operations in response to an unforeseen event. This strategic target essentially involves an optimal trade-off among system performance, reliability requirements, and associated costs. Instead of preparing a lot of identical backup hardware components to fill in the vacant positions in case some components are physically damaged, our proposed system would be capable of dynamically determining an optimal structure and connections of each individual neuron unit for the ANN system, as well as adaptively finding and incorporating available neuron resources to maintain the best achievable performance of the affected ANN system. Specifically, in a similar way as CNS's recovery process in case of a acquired brain injury, the proposed self-healing ARANN architecture can immediately adapt the system structure to disconnect the damaged neuron unit from the main network, if any error has been reported by the fault detector, and then involve new neuron units into the network to maintain the desired performance if any available neuron units are found. Otherwise, if no further neuron resources are available, the ARANN will continue its normal operation in a compromised mode caused by the slightly fewer neuron nodes contained by the current ANN system. One of the most profound benefits of the proposed ARANN is the opportunity to help ANN system react to any unexpected harmful events in an autonomous, on-line, and efficient manner without halting system execution and introducing considerable redundancy.

To better utilize the massively parallel processing nature of neural networks and facilitate their structural adaptation, we propose a *Distributed Artificial Neural Network (DANN)* architecture. Unlike prevailing Centralized ANN implementation, which usually features a "master-slave" system consisting of a highly-centralized, heavy-weight controller and a group of rather simple computational nodes (neurons), DANN is mainly made up of a lightweight topological & algorithmic controller and a mass of highly independent, autonomic, smart neuron units. Alleviating the computational burden from one central controller to a number of homogeneous neuron nodes, DANN can significantly improve the system performance by maximizing the degree of neuron-level parallelism. Also, DANN greatly reduces the data and control dependency between the central controller and all neurons, which provides a more flexible architectural infrastructure for the ANN structural adaptation.

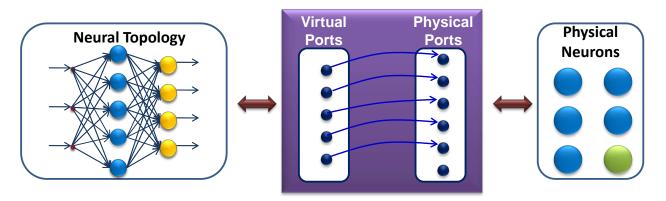

Given the loosely coupled computations and communications enabled by DANN, we present a novel Decoupled Virtual-to-Physical (V2P) Neuron Mapping strategy to implement a cost-efficient system adaptation scheme. Specifically, we propose a "neuron virtualization" by abstracting away the direct connections between ANN controller and all physical neuron units, and inserting a flexible V2P neuron mapping block to determine appropriate connections between virtual and physical neuron ports, according to the desired number of virtual neurons specified by the algorithm and the availability of individual physical neurons implemented on the hardware. With such a decoupling scheme, the real spatio-temporal connections of "physical neurons" is transparent to the controller that handles "virtual neurons". A detected faulty neuron can be timely removed from the neural network by changing the corresponding V2P mapping scheme to swap the faulty neuron with a spare neuron. The proposed Decoupled V2P Neuron Mapping has successfully addressed the reconfigurability and adaptability issues of conventional neural network implementations. It provides a convenient way to achieve the resource-efficient neuron reuse. More importantly, it indicates the possibility of increasing ANN's reliability by automatically reconfiguring and revising its structure in case one or more physical neurons are damaged.

Furthermore, the standard ANN learning process involves a large amount of training epochs, training patterns, and training stages (i.e., feed-forward calculation, back-propagation, and weight updating) and is also highly data dependent, since the magnitudes of synaptic weight changes highly reply on the calculated performance errors, which is iteratively determined by the synaptic weights updated in the training procedure of either previous input pattern or most recent epoch. Considering the severe influence of a faulty neuron on the whole neural network due to the inevitable time delays among the occurrence, detection, notification, and treatment of faulty neurons, a more accurate system recovery scheme besides the systematic reconfiguration is highly demanded to guarantee both the successful recovery of ANN systems in both physical structures and functioning accuracy. In the ARANN architectural framework, we ensure a smooth, accurate and consistent recovery, no matter when an unexpected fault is detected, by proposing the *Dual-Layer Memory Synchronization* mechanism, which includes a fine-grained memory and a coarse-grained memory maintaining and synchronizing relevant ANN state information on a stage or epoch basis respectively.

#### 1.2.3 Addressing ANN's Optimization Issue

Artificial Neural Networks (ANNs), since its earliest emergence about half a century ago, have been extensively studied and broadly used in a wide variety of applications, such as biomedicine [65, 170], industrial control [172, 201, 269], finance [139, 255, 307], engineering [43, 142], and computer science [89, 252]. Along with the remarkable efforts researchers have made to discover more effective ANN algorithms for some as of yet unsolved problems, another important research question of great concern is how to find and determine the best structure and configuration for a given ANN algorithm. Usually, for a standard fully-connected multi-layer perceptron neural network, the most critical parameters include the number of hidden layers and the number of neurons in each layer. It has been widely investigated and demonstrated that, with any of a wide variety of continuous nonlinear activation functions, one hidden layer with an arbitrarily large number of neurons suffices for the "universal approximation" property discussed by Hornik [112, 113, 114] and Bishop [19] respectively. In this case, the number of neurons in the only hidden layer becomes the only significant parameter that determines MLP's behavior and performance. Unfortunately, there has not been any theory yet to precisely determine the right (optimal) number of hidden neurons used by MLP for a specific problem. Although researchers have proposed many criteria or algorithms to help ANN users explore an optimal structure, such as the Akaike's Information Criterion (AIC) [5], Network Information Criterion [195], and the exploration of best number of hidden neurons [80, 173, 291], it is still in early stage to widely apply all these algorithms onto real problems due to either their extremely complex algorithmic computations or application-dependent characteristics. Until now, most of previous studies using neural networks have still highly relied on the science of experience or extensive experimental trials. Therefore, a practical issue of using ANNs is how to determine a optimal ANN structure, particularly the number of hidden neurons in the network. In general, the neural network may not learn the presented problem well if it is too small. On the other side, an over-sized network may lead to over-fitting and poor generalization performance [98]. Thus, as we presented before, it is highly desired that the ANN systems can find appropriate network architecture automatically under the guidance of certain algorithms.

To solve real-world problems using ANNs, it usually requires the use of highly structured networks of a rather large size. A rule of thumb for obtaining good generalization capability is to use the smallest system that will fit the data [233]. Because a neural network with minimum size is less likely to learn the idiosyncrasies or noise in the training data, and may thus generalize better to new data [103]. Since there has not been any theory capable of directly determining the best size of neural networks, we should search and find an optimal network structure by comparing various potential candidates according to a certain evaluation criterion. One effective and efficient approach is so-called network pruning. It starts with a rather large MLP with sufficient neuron units for the given application, and train the initial system using a common learning algorithm until an acceptable training accuracy achieved. After that, some inactive neurons will be gradually removed or certain synaptic weights will be eliminated in a selective and orderly fashion. This key idea is to iteratively evaluate the trade-off between the training accuracy and the structural complexity of ANN systems and then select the optimal structure providing reasonable accuracy with the least design complexity.

Although such type of optimization strategies has been extensively investigated and used in software implementations of neural networks, there has not been any neural hardware capable of dynamically optimizing its structure and providing efficient solutions for different applications, because most neural hardware were developed for certain applications only and they are reluctant to evolve into a more efficient shape. However, for emerging wearable biomedical devices and future pervasive healthcare, a highly integrated, multi-functional, ultra low-power, ultra-portable, extraordinary reliable hardware platform is mandatory. As one of the most important and promising techniques, ANN-based hardware is also expected to fit different applications in a more power-efficient manner. One possible solution to achieve this goal is to make ANN adaptable and reconfigurable and thus determine the system structure according to specific requirements and design trade-offs between performance measure and complexity overhead. Leveraging the reconfigurable and adaptable architectural infrastructure provided by ARANN, we incorporated the concept of neural network pruning into ARANN and proposed a Self-Optimizing Artificial Neural Network (SOANN), making use of ARANN's incomparable capabilities of connecting and disconnecting any physical neuron

unit to/from the main network on the fly. Instead of determining an "optimal" neural network structure for one certain application by the off-line analysis, the ARANN architecture will be able to evaluate the system cost involving both performance measure and complexity overhead, and then adaptively explore the most optimal network structure with the appropriate performance tradeoff. In summary, the proposed ARANN-based self-optimization approach is capable of helping users further shape the structure of neural networks and remove unnecessary (or "redundant") neurons which have little or no influence on the overall network performance.

Another major motivation to develop a flexible neural network platform with the capability of adapting and optimizing its structure in an autonomous manner is the increasing demands on the more diversified neural network systems. It is well known that ANNs have had very broad applications in biomedical domain. Most of previous studies usually involve extensively off-line analysis of experimental data and then propose a "supposedly" optimal neural network model for that particular problem. This may be the case for a very concentrated study with relatively few variables or parameters involved. However, as the rapid development of biomedical sciences, more sophisticated clinical techniques have been invented to provide more accurate diagnostic solutions and address certain highly intricate medical conditions. It is well known that the human body is one of the most complex elements in the universe and thus any medical condition can not be purely caused by one or a few clinical parameters. Therefore, such type of emerging comprehensive diagnostic systems usually involves the exhaustive analysis on a variety of biomedical parameters. For instance, Hudson and Cohen [49, 122] proposed a hybrid system in which biomedical signal data (e.g., ECG, EEG, and other clinical parameters) can be incorporated for developing higher-order medical decision systems and demonstrated increased sensitivity, specificity, and accuracy. Usakli et al. [287] also presented the possibility of involving both electroencephalogram (EEG) and electrooculogram (EOG) for the development of future Human-Computer Interface (HCI) or Brain-Computer Interface (BCI). In these cases, although a fixed neural network structure may be able to provide reasonable accuracy for modeling one certain bio-signal as studied in many previous work, it is highly desired that a reconfigurable neural network platform can be developed and adapted to meet different needs and characteristics of various biomedical parameters in an on-line manner. For example, one research scenario is to develop a hybrid healthcare assistive system, where ANN-based platform can be dynamically adapted and autonomously optimized for different usages, such as using parameter A to detect condition I, using parameter B to detect condition II, or using parameters A and B to monitor condition III, etc. In addition, a self-optimizing neural network can provide more flexibility to find an optimal model for a certain problem. The exploration of an optimal biomedical model is extremely challenging and sometimes even unfeasible, because many biomedical parameters are closely correlated and interacted, and thus it is really difficult to accurately identify the set of "influential" parameters. One possible solution is to tentatively investigate potential involved variables and adaptively find the most optimal model based on the identified variables. For example, Cecotti and Gräser [31] proposed to use neural network pruning strategy to reduce the number of electrodes and to select the best electrodes in relation to the subject particularities for a P300 Brain-Computer Interface application. It is shown that, even the involved biomedical parameters can not be accurately determined without adaptive evaluations, not to mention the optimal structure of neural networks used to model their behaviors. A reconfigurable neural network platform with the on-line self-optimizing capability will provide promising performance benefits for next-generation sophisticated biomedical solutions and significantly reduce the off-line optimization analysis efforts.

As electronic circuits' speeds and circuit densities continuously increase, circuit board power density increases as well and thermal management becomes an increasingly significant part of system design [25]. During the development of a large-scale circuit board, thus the thermal design aspects have proved crucial to its reliable operation. Reducing thermally induced stress and preventing local overheating remain major concerns when optimizing the capabilities of modern system chips [24]. However, such thermal-efficient approaches will usually bring considerable loss of performance, which is also critical to the increasingly computation-intensive applications. Therefore, seeking an effective way to balance the requirements on the high computational performance and the reliable operations with efficient power management has been of great interest to the academia. The employment of reconfigurability design concept can bring extra benefits in further addressing the reliability issues during the system execution. Given the flexible adaptability provided by ARANN, we

propose to further augment system's reliable operation and prevent the system from overheating without loss of performance by providing more modular design options that can be conveniently loaded and swapped into the main system. These design options may offer different performance/power tradeoffs and many other controllable diversified characteristics. With the support of the proposed Virtual-to-Physical Neuron Mapping, such swaps between characteristics-specific modules can be accomplished within a little while. Once the system has been cooled down by switching to power-efficient design modules, the high-performance system components can be now reloaded into the system again. In this way, the complex system can achieve an optimal balanced tradeoff between the intensive performance demands and the robust reliability requirements.

#### 1.2.4 Addressing ANN's Adaptation Cost Issue

As we mentioned before, given the desired number of neuron units (determined by the ANN Controller) and the locations of potentially damaged neurons (designated by the Error Detector), the Virtual-to-Physical (V2P) Neuron Mapper will establish connections between the virtual neuron ports and corresponding physical neuron units. There are generally two cases associated with such V2P mapping process. The first case is that the available (physical) neuron units in hardware are more than the desired (virtual) neurons specified by the ANN Controller, thus like those faulty neurons, some neuron units will not be enabled and used in the current ANN structure. The other case is that the available physical neuron units are not enough to meet the needs of the ANN Controller any more, probably due to gradually increased damage on hardware. In this case, the V2P Mapper will exhaustively search those still "healthy" neuron units and involve all of them in the current ANN structure. Also, the V2P Mapper will return the number of currently involved physical neuron units and a feedback signal back to the ANN Controller to tell users that the system is now running in a "Compromised" mode and the level of damage on hardware.

It is shown that the V2P Neuron Mapper is one of the most critical components within this Autonomously Reconfigurable Artificial Neural Network (ARANN) architecture and also the major element which introduces extra time and space overhead to the ANN system.

Considering the possibility that the electronic reliability issues will become increasingly severe and the exponentially growing needs of more versatile, easily configured ANN hardware, it is highly desired to design and implement a fast, flexible, accurate, and resource-efficient V2P mapping block which can be integrated into our ARANN architecture. In this thesis, we explore several different V2P mapping design solutions from various perspectives and then analyze their specific characteristics (i.e., performance, implementation efficiency, and potential overhead) and applicabilities to pursue the lowest time and space overhead associated with the demonstrated autonomous reconfiguration capability. We propose four V2P design strategies: 1) Adaptive Physical Neuron Allocation ("V2P Mapper"), 2) Cache-Accelerated Adaptive Physical Neuron Allocation ("V2P Mapper w/ Cache"), 3) Virtual-to-Physical Neuron Mapping Memory ("V2P Memory"), and 4) Mask-Based Virtual-to-Physical Neuron Mapping Memory ("Mask-based V2P Memory").

According to thorough comparison of results, it is clearly shown that there isn't a perfect design choice and all these four design strategies have distinct characteristics in design complexity, resource requirement, time overhead, and applicability to various scales of problems and thus have their own advantages and limitations. Since in this thesis we only investigated and implemented a small-scale ANN system for a relatively simple biomedical application (see section 3.3) and we also assume a relatively low defective probability for our ANN system, thus the *Cache-Accelerated V2P Mapper* seems to be a good design choice and has been used in all of our experiments thereafter.

#### 1.3 CONTRIBUTIONS

Computer systems may fail in any number of ways, thus some certain levels of fault-tolerance are extremely necessary, and particularly critical for emerging biomedical portable/implantable systems due to their difficult system rebuilding and physically invasive procedures. Artificial neural network (ANN) has proved to be effective in a variety of biomedical applications and many ANN-based medical solutions today have been demonstrated using off-the-shelf hardware. Due to unrelenting advances in technology scaling and large scale integration, these

systems are increasingly vulnerable to both transient and permanent faults which sometimes can be catastrophic, especially for medical applications. Conventional fault-tolerant techniques applicable to ANN-based systems usually consume considerable system resources and energy, which can be prohibitive to meet the strict requirements of next-generation ultraportable or implantable medical applications. Moreover, their lack of dynamic adaptability makes their protection effective only against faults that can be conceived at the design stage.

Inspired by the precise, systematic, sophisticated, supremely intelligent, and essentially autonomous reconfiguration-based automatic recovery mechanisms of the mammalian Central Nervous System (CNS) to react to unexpected injuries or diseases, we would like to explore the possibility to mimic CNS's faulty reaction strategies and to develop a cyberenabled artificial neural network environment with self-healing and self-optimizing capabilities. This dissertation proposes a novel Autonomously Reconfigurable Artificial Neural Network (ARANN) architectural framework. Leveraging the inherently homogeneous structural characteristics of neural networks, ARANN is capable of adapting ANN's structures and behaviors, both algorithmically and microarchitecturally, to react to unexpected faults at any neuron. More specifically, in a similar way as CNS's recovery process in case of a acquired brain injury, the proposed self-healing ARANN architecture can immediately adapt the system structure to disconnect the damaged neuron unit from the main network, if any error has been reported by the fault detector, and then involve new neuron units into the network to maintain the desired performance if any available neuron units are found. Otherwise, if no further neuron resources are available, the ARANN will continue its normal operation in a compromised mode caused by the slightly fewer neuron nodes contained by the current ANN system. Given the incomparable capabilities of connecting and disconnecting any physical neuron unit to/from the main network on the fly, ARANN will be able to evaluate the system cost involving both performance measure and complexity overhead, and then adaptively explore the most optimal network structure with appropriate design tradeoff.

The contributions of this dissertation research are threefold:

• First, we propose a novel biologically-inspired Autonomously Reconfigurable Artificial Neural Network (ARANN) architectural framework, capable of adapting ANN's struc-

ture and operations, both algorithmically and microarchitecturally, to react to unexpected faults occurring at any neuron. We demonstrate the effective and efficient self-healing and self-optimizing system adaptation methodologies on the ARANN, leveraging several architectural innovations which include the *Distributed ANN* architecture, the neuron virtualization technique with a *Decoupled Virtual-to-Physical Neuron Mapping*, and a *Dual-Layer Memory Synchronization* mechanism to ensure a smooth, accurate and consistent recovery of the highly structured neural network systems.

- Secondly, to further reduce the added time latency and resource overhead associated with ARANN's dynamic structural reconfiguration, we present and investigate four possible design solutions for the most critical component in the ARANN — Virtual-to-Physical Neuron Mapping. A thorough analysis and comparison have been performed on all of them to explicitly demonstrate their specific applicabilities.

- Thirdly, we verify the proposed ARANN using a real biomedical case study that presents an ANN-based model for limb endpoint locomotion prediction. And we also prototype the proposed ARANN on the state-of-the-art FPGA platform. Because of the demonstrated scalability and properties, the proposed ARANN architectural framework will be scalable to different scales of neural networks and can be deployed on either a single integrated circuit chip or a multiple processing elements environment, such as multi-FPGAs, multicore chips or chip-multiprocessors (CMPs).

In summary, the proposed ARANN architectural framework provides designers (particularly future biomedical system designers) with a new genre of highly integrated, multifunctional, ultra low-power, ultra-portable, extraordinary reliable neural network platform that can achieve self-healing and self-optimization through autonomous structural reconfiguration. The ARANN system either can be completely recovered or can be adapted into a "compromised" mode with a certain degree of performance tradeoff. Both two solutions can be achieved timely and will not stop the system execution at all. Actually, the most profound benefit of the proposed ARANN is the opportunity to help ANN system react to any unexpected harmful events in an autonomous, on-line, and efficient manner without halting system execution and introducing considerable redundancy.

#### 1.4 THESIS OUTLINES AND ORGANIZATIONS

The reminder of this thesis is organized as follows:

Chapter 2 gives an overview of artificial neural network techniques, reviews all previous efforts on the hardware implementation of artificial neural networks, and discusses prior reconfigurable neural network design practices that are closely related to our study.

Chapter 3 provides a methodological overview on artificial neural networks and particularly examines the Multilayer Perceptron (MLP) including its architectural properties, interconnections, and back-propagation training algorithms. We also present a case study on the effective use of ANN in emerging biomedical applications — an ANN-based model for limb end-point locomotion predictions.

Chapter 4 presents the proposed Autonomously Reconfigurable Artificial Neural Network methodology framework. We describe the major architectural innovations and hardware infrastructure that support the ARANN, and demonstrate the effective and efficient self-healing and self-optimizing system adaptation methodologies on the ARANN.

Chapter 5 discusses the design issues and challenges when implementing a Multilayer Perceptron (MLP) neural network on the FPGA, given the relatively limited resources available. Specifically, we discuss the issues with regard to arithmetic representations, multi-purpose smart neurons, activation function implementation strategies, as well as the hierarchically bidirectional neuron/synapse-reused ANN implementations. The realization details are all demonstrated in this chapter.

Chapter 6 shows the experimental results and gives detailed analysis on the performance benefits and overheads of the proposed ARANN architectural framework. For comparison purpose, a case study on the aforementioned biomedical application of ANNs is also demonstrated; the performance results based on the proposed reconfigurable platform are compared with the data generated from MATLAB simulation.

Chapter 7 offers conclusions and future directions of this thesis research. This thesis involves several topics, and consequently, the work in this thesis could be continued and extended in a variety of directions, such as utilizing the platform-level reconfigurability or deploying ARANN onto multi-chip environment for more complicated applications.

#### 2.0 RELATED WORK

This chapter describes prior and concurrent research related to this dissertation study. These relevant studies are presented under different categories based on the nature of the work. Along with detailed description and comparative analysis, what is also provided are insights explaining what the proposed ARANN is different from all prior work and why it is advantageous over those work.

# 2.1 HARDWARE IMPLEMENTATIONS OF ARTIFICIAL NEURAL NETWORKS

General-purpose computers are traditionally based on the von-Neumann architecture, which is essentially sequential. Artificial neural networks, on the other hand, significantly benefit from their massively parallel processing nature. In the past several decades, the performance of conventional von-Neumann processors has continued to increase dramatically and the up-to-date computing systems have been able to meet various increasing computational requirements. Thus, when the extraordinary processing performance is not particularly desired, most researchers or designers who widely explore ANN-based solutions to solve real problems, usually rely on the software implementation on a PC or workstation without any special hardware components or devices. A tremendous amount of work has been done in developing simulation environments for artificial neural networks on sequential machines [81, 196]. However, the software simulation cannot provide real-time learning and response when the emulated ANNs contain a large number of neurons and synapses, even on the fastest sequential machines. The inherently parallel nature of ANNs demands a more par-

allelized computational architecture capable of processing synaptically connected neurons simultaneously using multiple simple processing elements (PEs).

The idea of building the neural network on hardware platform is definitely not new and can date back to more than one decade ago. Some emerging specialized applications have motivated the use of application-specific neural network hardware. For example, a variety of low-cost consumer devices dedicated for certain applications (e.g., speech recognition) and analog neuromorphic devices (e.g., silicon retinas) have been introduced and developed to meet people's various demands on ANN-based solutions [163]. The development of digital neuro-hardware is driven by the desire to speed-up the simulation of ANNs and to achieve a better performance-to-cost ratio than general-purpose systems [251]. It has been demonstrated that the hardware implementations of artificial neural networks are able to take full advantage of their inherent parallelism and thus can achieve much better performance by orders of magnitude compared to their counterparts simulated in software.

In general, neural network hardware designers have followed two distinct approaches. One is to build a general, but probably expensive, system that can be re-programmed for many kinds of tasks, such as Adaptive Solutions' CNAPS (Connected Network of Adaptive Processors) [97], Siemens' SYNAPSE (Synthesis of Neural Algorithms on a Parallel Systolic Engine) [232], as well as the NESPINN (Neurocomputer for Spiking Neural Networks) [130]. Another approach is to build low-cost, application-specific chips that can handle computationally intensive and regular tasks effectively and efficiently for certain applications, such as IBM's ZISC [169]. Several overviews on available neural network hardwares and systems have been presented and published by Dias et al. [60], Moerland and Fiesler [188], and Lindsey [168], as illustrated in Table 1.

Many researchers initiated efforts to integrate neural networks of large sizes on a single chip [85, 231, 288], which can execute complex operations of neural networks at a higher speed and a lower per-unit cost compared to software implementations. As the dramatic development of integrated circuit technology, the main implementations of neural networks have been evolving and expanding from the original LSI circuits to the latest SoCs, 3D chips, FPGAs and digital/analog/mixed-signal VLSIs. In what follows, I will give a brief overview on the prior efforts on ANN hardware implementations and neural computing systems.

Table 1: Examples of Neural Network Hardwares

| System                            | Architecture                 | Learn            | Precision      | Neurons | Synapses       | Speed                 |

|-----------------------------------|------------------------------|------------------|----------------|---------|----------------|-----------------------|

| Analog Implementations            |                              |                  |                |         |                |                       |

| Intel<br>ETANN                    | $\mathrm{FF}\ \mathrm{ML}^a$ | No               | $6b \times 6b$ | 64      | 10280          | 2 GCPS                |

| Synaptics Silicon Retina          | Neuromorphic                 | No               | N/A            | 48×48   | Resistive net  | N/A                   |

|                                   |                              | Digital          | Implementat    | tions   |                |                       |

| Philips<br>Lneuro-1               | FF ML                        | No               | 1-16b          | 16 PE   | 64             | $26 \text{ MCPS}^b$   |

| Hitachi<br>WSI                    | Wafer, SIMD                  | $\mathrm{BP}^a$  | $9b\times8b$   | 144     | N/A            | $300 \text{ MCUPS}^c$ |

| Siemens<br>MA-16                  | Matrix ops                   | No               | 16b            | 16 PE   | 16×16          | 400 MCPS              |

| IBM<br>ZISC036                    | RBF                          | $\mathrm{ROI}^a$ | 8b             | 36      | $64 \times 36$ | $250~\mathrm{kpat/s}$ |

| SAND/1                            | FF ML, RBF,<br>Kohonen       | No               | 13b            | 8       | Off chip       | 32 MCPS               |

| Hybrid Implementations            |                              |                  |                |         |                |                       |

| AT&T<br>ANNA                      | FF ML                        | No               | $3b\times6b$   | 16-256  | 4096           | 2.1 GCPS              |

| Mesa Research<br>Neuralclassifier | FF ML                        | No               | 6b×5b          | 6       | 426            | 21 GCPS               |

| Ricoh<br>RN-200                   | FF ML                        | BP               | N/A            | 16      | 256            | 3.0 GCPS              |

<sup>&</sup>lt;sup>a</sup> FF ML — Feedforward Multilayer networks; BP — Backpropagation; ROI — Region of Influence

$<sup>^</sup>b$  The average speed performance of the retrieve (or feed-forward) process of a neural network model is measured in *million connections per second (MCPS)*

<sup>&</sup>lt;sup>c</sup> The average speed performance of the learning process of a neural network model is measured in *million* connection updates per second (MCUPS)

Blayo and Hurat [20] presented a Wafer Scale Integration (WSI) neural network dedicated to pattern recognition on associative memory. The presented device consists of implementing the N-neuron Hopfield Network as a systolic square array made up of  $N^2$  cells.

Graf and Henderson [86] designed an analog CMOS neural net with a programmable architecture containing 32k connections with analog signals inside the network and digital signals for all others. The deployed network consists of building blocks that can be joined to form various network architectures and thus can be programmed to implement single-layer networks or multi-layer networks. The chip was fabricated in a  $0.9\mu m$  CMOS technology and executed the feed-forward computations within 100ns.

Satyanarayana et al. [249] presented the design and implementation of a neural network with programmable topology and programmable weights, built using analog CMOS VLSI technology. They proposed a new "distributed neuron-synapse" circuit block and a array of switches in the interconnections between synapses and neurons to change the network topology. Thus the proposed hardware neural network was able to alter the topology while solving a program, switch off unused synapses, increase the resolution by providing some redundant synapses, and correct offsets commonly observed in analog circuits.

Cox and Blanz [50, 51] firstly moved the neural network implementations to Field-Programmable Gate Array hardware domain. They presented the implementation of GAN-GLION, a fully interconnected, digital, feed forward connectionist classifier with one hidden layer capable of 4.48 billion interconnections per second. The entire architecture was built using Xilinx XC3090 and XC3042 Logic Cell Arrays (LCAs), which contain 320 CLBs and 144 CLBs respectively and together compute the scaled weighted sum of their fourteen inputs passed through the activation function in the PROM.

Due to the limited computational capability of FPGA devices at that time, Botros and Abdul-Aziz [22, 23] then expanded the hardware implementation of a fully digital MLP using FPGAs to a even bigger scale, where each node (neuron) in the network was implemented with two Xilinx XC3042 FPGAs and a 1K×8b EPROM. This three-layer network (5–4–2) was trained off-line on a PC and the final values of weights were obtained at the end of training session. All internal multiplications and sigmoid activation functions were realized in a look-up table fashion by programming the CLBs and the EPROM.

So far, we have already known a lot of pioneers in the hardware implementations of neural network. However, sometimes the specific hardware has been heavily influenced by the need to address a diverse range of applications and varying demands require a variety of solutions. In order to give a comprehensive evaluation on aforementioned popular implementations from a comparison perspective, Morgan *et al.* [191] analyzed various implementation technologies (FGPAs, VLSI and WSI) in terms of HyperNet system cost, complexity and performance. The HyperNet was a probabilistic hypercube-based artificial neural network proposed by Gurney [91]. Among all three designs using FPGA (Xilinx 4025), VLSI (0.7 $\mu$ m CMOS chip of 180mm<sup>2</sup>), and WSI (0.7 $\mu$ m chip of 12.5cm diameter), Morgan *et al.* demonstrated FPGA's promising performance advantage over software implementation at a low cost, as well as the higher performance offered by VLSI and WSI but with high initial development costs.

## 2.2 IMPLEMENTATION STRATEGIES AND EXAMPLES OF NEURAL NETWORKS ON FPGAS

An artificial neural network (ANN) is essentially a parallel and distributed network of simple nonlinear processing units interconnected in a layered topology [312]. Parallelism, modularity, and dynamic adaptation are three most noticeable and important computational characteristics associated with ANNs. Fortunately, the inherent regularity, homogeneity and reconfigurability of FPGAs makes it a perfect candidate platform to implement ANNs, since it is able to quickly reconfigure itself to adapt any changes in the internal parameters and overall behaviors of an ANN. However, FPGA realization of ANNs with a large number of neurons is still a very challenging task because ANNs are computationally intensive algorithms and it is extremely expensive to exhaustively implement every computational module (adders, multipliers, sum of squares, sum of products, etc.) in each neuron unit. Zhu and Sutton [312] provided a brief survey of existing ANN implementations on FPGAs and reexamined all design issues that are important for such type of implementations. Similar issues were also reported by Hu et al. [118] and Muthuramalingam et al. [197], including data representation, inner-products computation, implementation of activation functions,

storage and update of weights, nature of learning algorithms, serial/parallel design choices and physical design constraints.