# DESIGN AUTOMATION FOR LOW POWER RFID TAGS

by

## Swapna R. Dontharaju

M.S. Computer Science and Engineering, Pennsylvania State University, 2004

> Submitted to the Graduate Faculty of School of Engineering in partial fulfillment of the requirements for the degree of

## Doctor of Philosophy

University of Pittsburgh

2007

## UNIVERSITY OF PITTSBURGH SCHOOL OF ENGINEERING

This dissertation was presented

by

Swapna R. Dontharaju

It was defended on

July 19, 2007

and approved by

Dr. Alex K. Jones, Assistant Professor, Electrical and Computer Engineering Department Dr. Marlin H. Mickle, Professor, Electrical and Computer Engineering Department Dr. James T. Cain, Professor, Electrical and Computer Engineering Department Dr. Ronald Hoelzeman, Associate Professor, Electrical and Computer Engineering Department

Dr. Bryan Norman, Associate Professor, Industrial Engineering Department

Dissertation Director: Dr. Alex K. Jones, Assistant Professor, Electrical and Computer

Engineering Department

Copyright © by Swapna R. Dontharaju

2007

#### DESIGN AUTOMATION FOR LOW POWER RFID TAGS

Swapna R. Dontharaju, PhD

University of Pittsburgh, 2007

Radio Frequency Identification (RFID) tags are small, wireless devices capable of automated item identification, used in a variety of applications including supply chain management, asset management, automatic toll collection (EZ Pass), etc. However, the design of these types of custom systems using the traditional methods can take months for a hardware engineer to develop and debug. In this dissertation, an automated, low-power flow for the design of RFID tags has been developed, implemented and validated. This dissertation presents the RFID Compiler, which permits high-level design entry using a simple description of the desired primitives and their behavior in ANSI-C. The compiler has different back-ends capable of targeting microprocessor-based or custom hardware-based tags. For the hardwarebased tag, the back-end automatically converts the user supplied behavior in C to low power synthesizable VHDL optimized for RFID applications. The compiler also integrates a fast, high-level power macromodeling flow, which can be used to generate power estimates within 15% accuracy of industry CAD tools and to optimize the primitives and / or the behaviors, compared to conventional practices. Using the RFID Compiler, the user can develop the entire design in a matter of days or weeks. The compiler has been used to implement standards such as ANSI, ISO 18000-7, 18000-6C and 18185-7. The automatically generated tag designs were validated by targeting microprocessors such as the AD Chips EISC and FPGAs such as Xilinx Spartan 3. The corresponding ASIC implementation is comparable to the conventionally designed commercial tags in terms of the energy and area. Thus, the RFID Compiler permits the design of power efficient, custom RFID tags by a wider audience with a dramatically reduced design cycle.

### TABLE OF CONTENTS

| PR  | PREFACE |                                                           |    |

|-----|---------|-----------------------------------------------------------|----|

| 1.0 | IN'     | TRODUCTION                                                | 1  |

| 2.0 | CO      | NTRIBUTIONS                                               | 7  |

|     | 2.1     | Problem Statement                                         | 7  |

|     | 2.2     | Contributions                                             | 8  |

|     |         | 2.2.1 RFID Compiler for the Microprocessor-based Tag      | 8  |

|     |         | 2.2.2 Hardware RFID Compiler with VHDL Behavior           | 8  |

|     |         | 2.2.3 Hardware RFID Compiler with C Behavior              | 8  |

|     |         | 2.2.3.1 EPC C1 Generation 2 Hardware RFID Compiler        | 9  |

|     |         | 2.2.4 Techniques For Optimizing The Tag Power Consumption | 9  |

| 3.0 | BA      | CKGROUND                                                  | 10 |

|     | 3.1     | Introduction to RFID Systems                              | 10 |

|     |         | 3.1.1 RFID Architecture                                   | 11 |

|     |         | 3.1.2 RFID Tag Characteristics                            | 11 |

|     |         | 3.1.2.1 Communication                                     | 12 |

|     |         | 3.1.2.2 Computation                                       | 13 |

|     |         | 3.1.2.3 Security                                          | 13 |

|     |         | 3.1.3 RFID Applications                                   | 14 |

|     |         | 3.1.4 RFID Standards                                      | 15 |

|     | 3.2     | Hardware Design Methodologies                             | 16 |

|     |         | 3.2.1 Design Flows For ASICs and FPGAs                    | 18 |

|     | 3.3     | Related Work                                              | 20 |

|            |     | 3.3.1 Commercial Systems                                                | 20          |

|------------|-----|-------------------------------------------------------------------------|-------------|

|            |     | 3.3.2 Customizable Systems                                              | 22          |

|            | 3.4 | RFID Prototyping Environment                                            | 24          |

| <b>4.0</b> | RF  | ID SPECIFICATION METHODOLOGY AND COMPILATION FLO                        | <b>W</b> 26 |

|            | 4.1 | Description of The Primitives                                           | 27          |

|            |     | 4.1.1 ISO 18000 Part 7                                                  | 27          |

|            |     | 4.1.2 ANSI NCITS 256-2001                                               | 28          |

|            | 4.2 | Macros Specification                                                    | 29          |

|            | 4.3 | Template for Behavior                                                   | 32          |

|            | 4.4 | Microprocessor-Based Controller                                         | 34          |

|            | 4.5 | The Prototype Microprocessor System                                     | 36          |

|            | 4.6 | Results                                                                 | 41          |

| 5.0        | HA  | RDWARE RFID COMPILER WITH VHDL BEHAVIOR                                 | 43          |

|            | 5.1 | VHDL Behavior-Based Front-end                                           | 44          |

|            | 5.2 | Hardware Controller-Based Back-end                                      | 44          |

|            | 5.3 | Implementation of Primitives                                            | 46          |

|            |     | 5.3.1 FPGA-Based Implementation                                         | 46          |

|            |     | 5.3.2 ASIC Implementation                                               | 52          |

| 6.0        | HA  | RDWARE RFID COMPILER WITH C BEHAVIOR                                    | 56          |

|            | 6.1 | C Behavior-Based Front-end                                              | 57          |

|            | 6.2 | Back-end Integrated with SuperCISC Compiler                             | 57          |

|            | 6.3 | Implementation of Primitives                                            | 64          |

|            |     | 6.3.1 Comparison With Hardware RFID Compiler With VHDL Behavior         | 64          |

|            |     | 6.3.2 Comparison With The ISO 18185 RFID Standard                       | 66          |

|            | 6.4 | The ISO 18000 Part 6C Standard                                          | 70          |

|            |     | 6.4.1 Description of ISO 18000 Part 6C Standard Interrogator Commands . | 70          |

|            |     | 6.4.2 Tag States and Slot Counter                                       | 71          |

|            |     | 6.4.3 Tag Memory                                                        | 72          |

|            |     | 6.4.4 Security Features                                                 | 72          |

|            | 6.5 | Implementing ISO 18000 Part 6C                                          | 75          |

|     |      | 6.5.1 Extensions to The Hardware RFID Compiler For ISO 18000-6C    | 79  |

|-----|------|--------------------------------------------------------------------|-----|

|     |      | 6.5.2 Comparison with ISO 18000 Part 7                             | 81  |

|     |      | 6.5.3 Custom Hardware-based Tag                                    | 81  |

|     | 6.6  | Compiler Optimizations                                             | 84  |

|     | 6.7  | Results                                                            | 86  |

| 7.0 | ТЕ   | CHNIQUES FOR OPTIMIZING THE TAG POWER CONSUMP-                     |     |

|     | TI   | ON                                                                 | 90  |

|     | 7.1  | Power Macromodeling                                                | 91  |

|     |      | 7.1.1 Motivation                                                   | 91  |

|     |      | 7.1.2 Power Macromodeling Framework                                | 92  |

|     |      | 7.1.2.1 Library of Power Profiles                                  | 95  |

|     |      | 7.1.2.2 SystemC Simulator Construction                             | 96  |

|     |      | 7.1.2.3 Power Estimation                                           | 99  |

|     |      | 7.1.2.4 Results                                                    | 103 |

|     |      | 7.1.3 Evaluation of Alternate Protocol Designs: Example            | 105 |

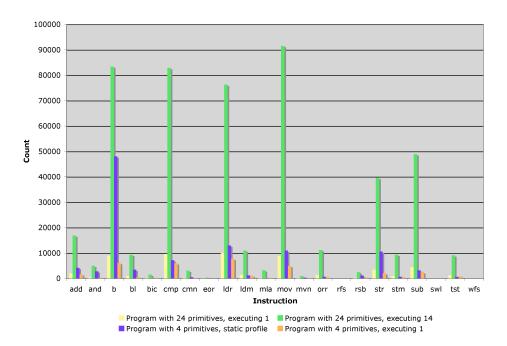

|     | 7.2  | Study of Application Specific Instruction Sets For Microprocessors | 105 |

|     |      | 7.2.1 Power and Area study of ISA subset of EISC CPU               | 106 |

| 8.0 | CC   | NCLUSIONS                                                          | 110 |

|     | 8.1  | Contributions                                                      | 111 |

|     |      | 8.1.1 RFID Compiler for the Microprocessor-based Tag               | 111 |

|     |      | 8.1.2 Hardware RFID Compiler with VHDL Behavior                    | 111 |

|     |      | 8.1.3 Hardware RFID Compiler with C Behavior                       | 112 |

|     |      | 8.1.3.1 EPC C1 Generation 2 Hardware RFID Compiler                 | 113 |

|     |      | 8.1.4 Techniques For Optimizing The Tag Power Consumption          | 113 |

|     | 8.2  | Future Research                                                    | 116 |

| BIE | BLIC | OGRAPHY                                                            | 117 |

### LIST OF TABLES

| 1  | Area and performance result for implementing the primitive logic on a Cool-                                     |    |

|----|-----------------------------------------------------------------------------------------------------------------|----|

|    | runner II XC2C512                                                                                               | 49 |

| 2  | Area for implementing the primitive logic on an Actel Fusion AFS090                                             | 49 |

| 3  | Power and energy results for implementing the primitive logic on a Coolrunner                                   |    |

|    | II XC2C512                                                                                                      | 53 |

| 4  | Area for implementing the primitive logic on a $0.16\mu\mathrm{m}$ ASIC. ASIC area is in                        |    |

|    | $100\mu m^2$                                                                                                    | 54 |

| 5  | Area and Dynamic Power for implementing the primitive logic on a $0.16\mu\mathrm{m}$                            |    |

|    | ASIC. ASIC area is in $100\mu m^2$ . Dynamic Power is in mW. Quiescent Power                                    |    |

|    | $<0.4\mu$ W                                                                                                     | 64 |

| 6  | Area and Dynamic Power for implementing the ISO 18185 primitive logic on a                                      |    |

|    | $0.16\mu\mathrm{m}$ ASIC. ASIC area is in $100\mu m^2$ . Dynamic Power is in mW. Quiescent                      |    |

|    | Power $<0.4\mu$ W                                                                                               | 69 |

| 7  | ISO Part 6C Command Codes                                                                                       | 71 |

| 8  | LFSR Sequence For The Seed '111'.                                                                               | 81 |

| 9  | Power and energy results for implementing $Query$ , $Collection$ and 10 ISO Part 7                              |    |

|    | primitives (inclusive of <i>Collection</i> ) as a 0.16 $\mu$ m ASIC. ASIC area is in 100 $\mu$ m <sup>2</sup> . |    |

|    | Dynamic power is in mW. Quiescent Power $< 0.4 \mu$ W                                                           | 83 |

| 10 | Area for implementing the original compiler-generated Part 6C primitive logic                                   |    |

|    | on a 0.16 $\mu$ m ASIC. ASIC area is in 100 $\mu$ m <sup>2</sup>                                                | 84 |

| 11 | Area for implementing the fully optimized Part 6C Inventory primitive logic                                     |    |

|    | on a 0.16 $\mu$ m ASIC. ASIC area is in $100\mu m^2$ .                                                          | 88 |

| 12 | Dynamic power for implementing the fully optimized Part 6C Inventory prim-              |     |

|----|-----------------------------------------------------------------------------------------|-----|

|    | itive logic on a 0.16 $\mu$ m ASIC. Dynamic power is in mW. Quiescent Power             |     |

|    | $<0.4\mu W.$                                                                            | 88  |

| 13 | Resource utilization for implementing the Part 6C Inventory primitive logic on          |     |

|    | a Spartan 3 FPGA.                                                                       | 89  |

| 14 | Area and Dynamic power for implementing the fully optimized Part 6C Access              |     |

|    | primitive logic on a 0.16 $\mu$ m ASIC. ASIC area is in $100\mu m^2$ . Dynamic power is |     |

|    | in mW. Quiescent Power $< 0.4 \mu$ W                                                    | 89  |

| 15 | Power Macromodeling vs. Traditional Method For Commands From ISO                        |     |

|    | 18000-6C                                                                                | 104 |

| 16 | Power Macromodeling vs. Traditional Method For Commands From ISO                        |     |

|    | 18000-7                                                                                 | 104 |

| 17 | The impact of modifying a standard can be studied using the Power Macro-                |     |

|    | modeling Flow. Results shown are for reducing the number of states in the Part          |     |

|    | 6C standard state machine to six. On average, power is reduced by 10.97%.               |     |

|    | Similarly, many different modifications can be modeled.                                 | 104 |

| 18 | Power study for reducing EISC ISA.                                                      | 107 |

### LIST OF FIGURES

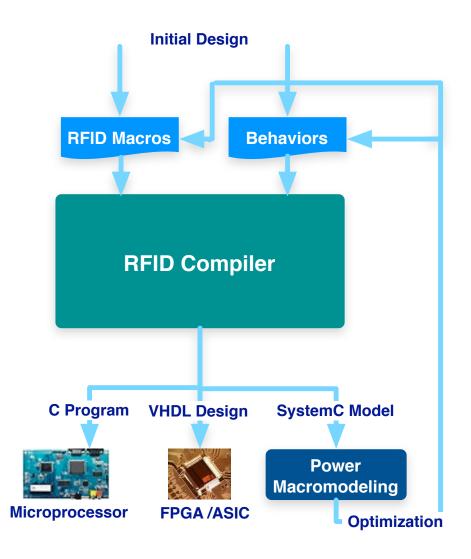

| 1  | RFID Specification Methodology and Compilation Flow                      | 3  |

|----|--------------------------------------------------------------------------|----|

| 2  | Comparison of RFID tag design philosophies                               | 5  |

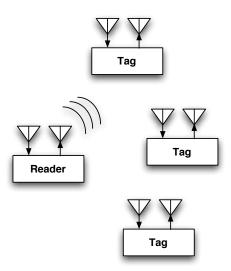

| 3  | Common RFID Tags                                                         | 11 |

| 4  | RFID Reader                                                              | 12 |

| 5  | The Main Components of an RFID System                                    | 13 |

| 6  | Organization of a Simple Bus-oriented Microprocessor                     | 17 |

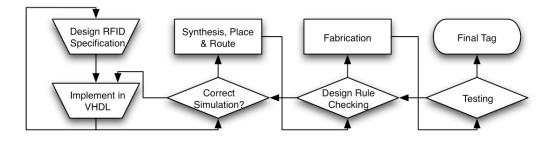

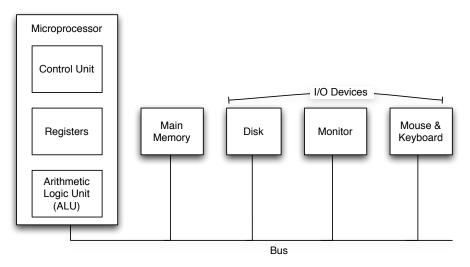

| 7  | Design Flow For Reconfigurable Hardware                                  | 19 |

| 8  | Some RFID Products From Savi [1]                                         | 21 |

| 9  | Rule-based RFID tag system. Source: [2]                                  | 22 |

| 10 | Example ECA rule for an employee access control application. Source: [2] | 23 |

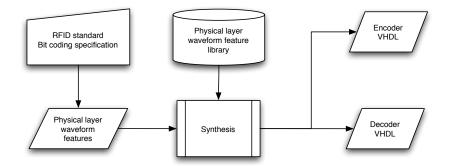

| 11 | The generation flow for an RFID data encoder and decoder. Source: [3]    | 24 |

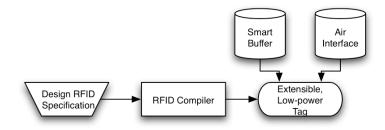

| 12 | Extensible, low-power RFID tag                                           | 25 |

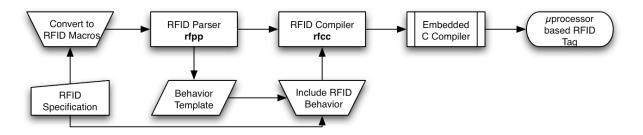

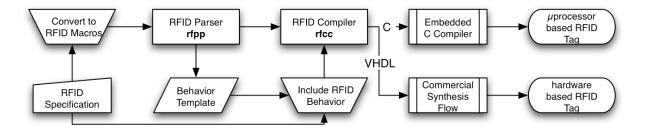

| 13 | RFID Specification Methodology and Compilation Flow                      | 26 |

| 14 | Collection Command and Response Format (ISO 18000-7)                     | 28 |

| 15 | Get Tag Status Primitive and Response Format (ANSI)                      | 28 |

| 16 | Macros specification (ISO 18000-7).                                      | 30 |

| 17 | Macros specification (ANSI-256)                                          | 31 |

| 18 | RFID Specification Grammar.                                              | 31 |

| 19 | Pseudo-code for Template Generation                                      | 32 |

| 20 | Template Generated for Behavior of <i>Collection</i> Command             | 33 |

| 21 | Behavior of <i>Collection</i> Command After User Input.                  | 33 |

| 22 | Pseudo-code for Tag Program Generation.                                  | 35 |

| 23 | Outline of Compiler-generated Tag Program                                        | 37 |

|----|----------------------------------------------------------------------------------|----|

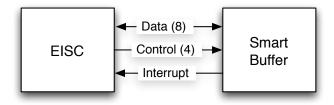

| 24 | Interface Between the EISC processor and the <i>Smart Buffer</i>                 | 38 |

| 25 | Interrupt Service Routine to Read the Incoming Command from the Smart            |    |

|    | Buffer                                                                           | 39 |

| 26 | Routine to Send the Response to the Smart Buffer                                 | 40 |

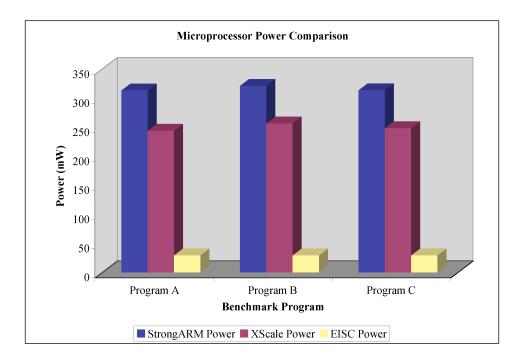

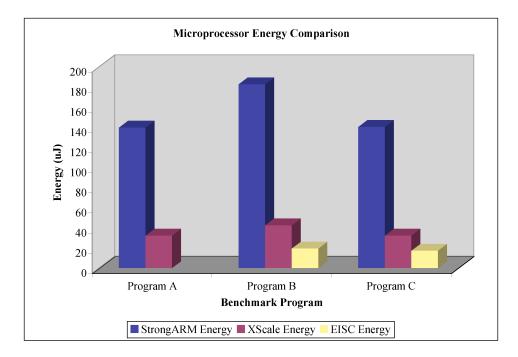

| 27 | Power consumption results for microprocessor-based RFID tags                     | 42 |

| 28 | Energy results for microprocessor-based RFID tags during response generation.    | 42 |

| 29 | Hardware RFID Compiler with VHDL Behavior                                        | 43 |

| 30 | Template Generated for Behavior of <i>Collection</i> Command                     | 45 |

| 31 | Behavior of <i>Collection</i> Command After User Input                           | 45 |

| 32 | Outline of Automatic VHDL Design Generation Using VHDL AST                       | 47 |

| 33 | Commands from ISO 18000 Part 7.                                                  | 48 |

| 34 | Commands from ANSI NCITS 256-2001.                                               | 48 |

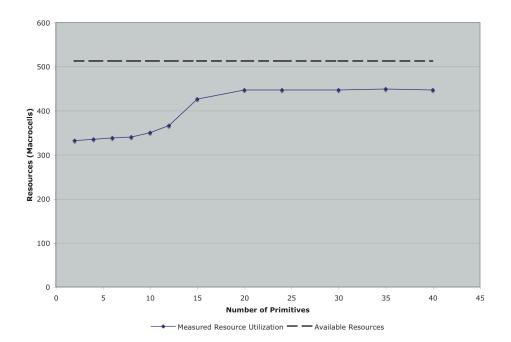

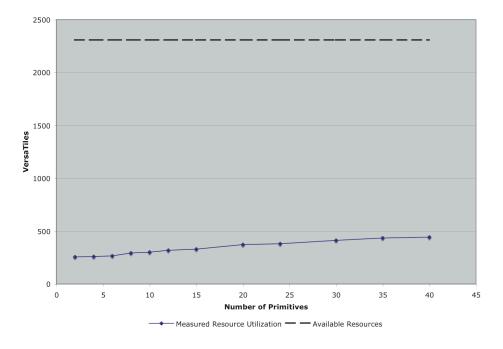

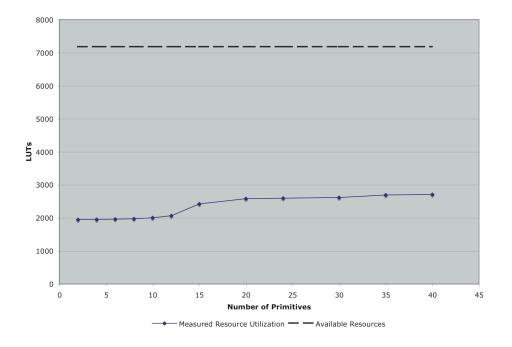

| 35 | Resource utilization of user defined logic for FPGA-based prototype systems.     | 50 |

| 36 | Resource utilization of user defined primitive logic and smart buffer on a Spar- |    |

|    | tan 3 prototype system.                                                          | 51 |

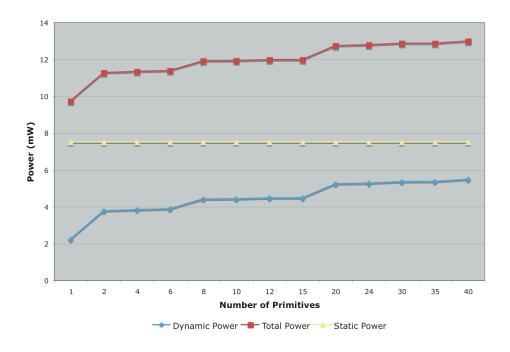

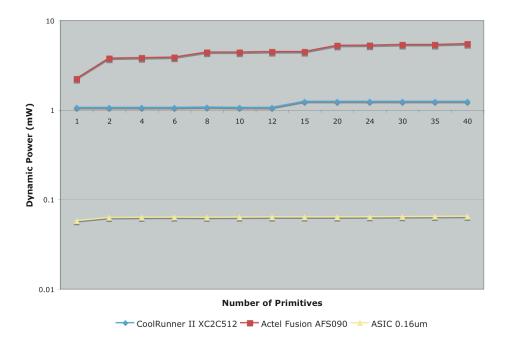

| 37 | Power consumption for implementing the primitive logic on Actel Fusion           | 53 |

| 38 | Power consumption comparison for implementing the primitive logic on a Cool-     |    |

|    | runner II XC2C512, an Actel Fusion AFS090, and 0.16 $\mu$ m ASIC                 | 55 |

| 39 | Hardware RFID Compiler with C Behavior                                           | 57 |

| 40 | Behavior of <i>Collection</i> Command Marked for Hardware Creation               | 58 |

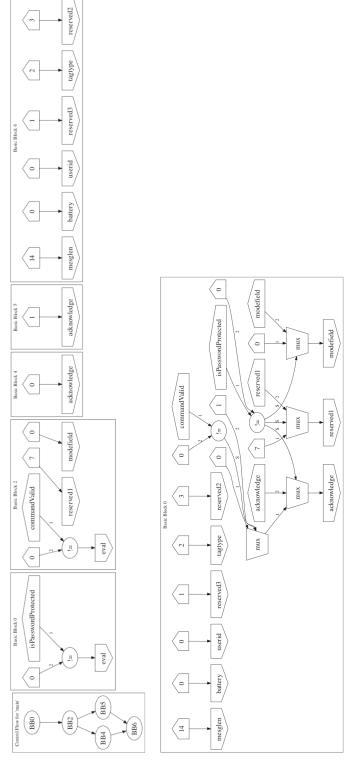

| 41 | Synthesis process for the <i>Collection</i> (icol) command                       | 60 |

| 42 | VHDL Design for the <i>Collection</i> (icol) command                             | 61 |

| 43 | SuperCISC Function That Prints Details of Each Entity.                           | 62 |

| 44 | RFID Compiler Function That Adds Components to the RFID Tag VHDL AST.            | 63 |

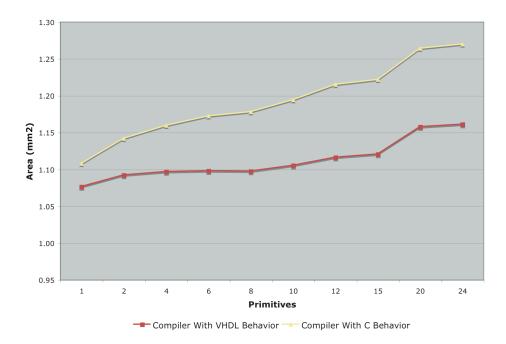

| 45 | Area Comparison of the Two Hardware RFID Compilers.                              | 65 |

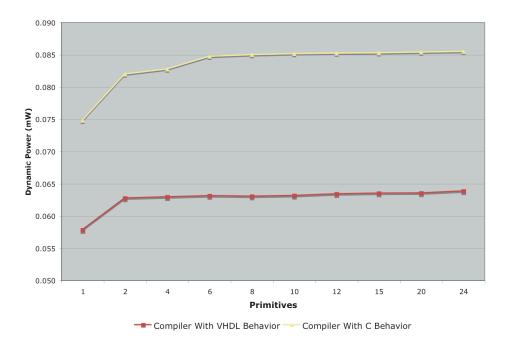

| 46 | Power Comparison of the Two Hardware RFID Compilers.                             | 65 |

| 47 | Example command/response formats from ISO 18185 Part 1                           | 67 |

| 48 | Macros specification for <i>Sleep All But</i> command from ISO 18185 Part 1      | 68 |

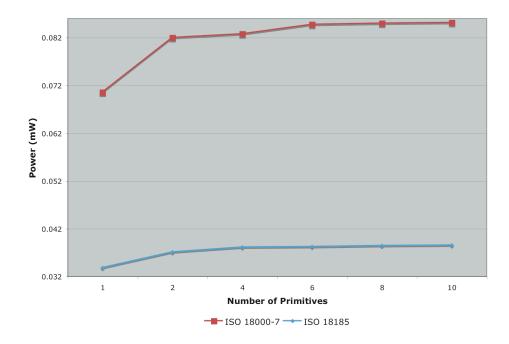

| 49 | Power consumption comparison for implementing the ISO 18000-7 and ISO                         |     |

|----|-----------------------------------------------------------------------------------------------|-----|

|    | 18185 primitive logic on a $0.16\mu m$ ASIC.                                                  | 69  |

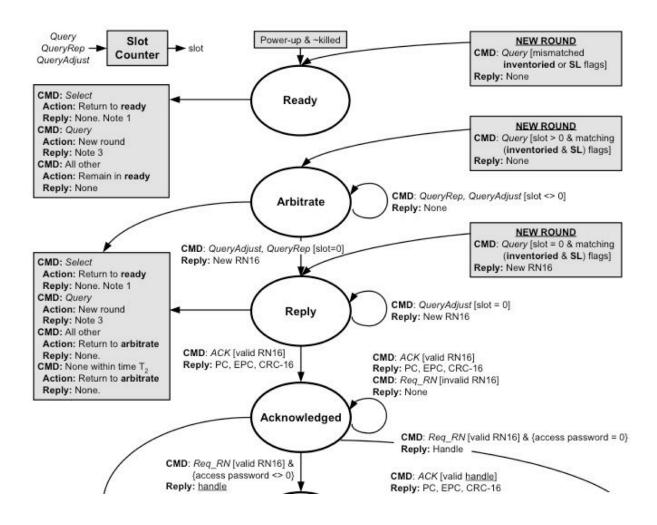

| 50 | Partial state diagram of ISO Part 6C tag from the EPCGlobal Class 1 Gener-                    |     |

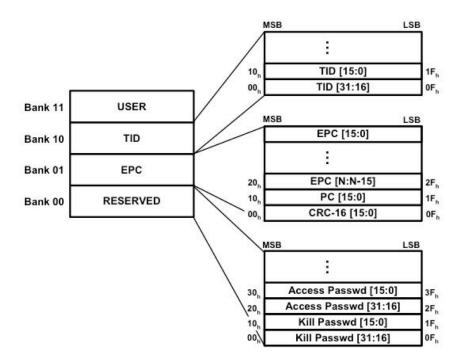

|    | ation 2 document [4]                                                                          | 73  |

| 51 | Logical Memory Map of ISO Part 6C Tag [4]                                                     | 74  |

| 52 | Query command and response format from ISO Part 6C.                                           | 75  |

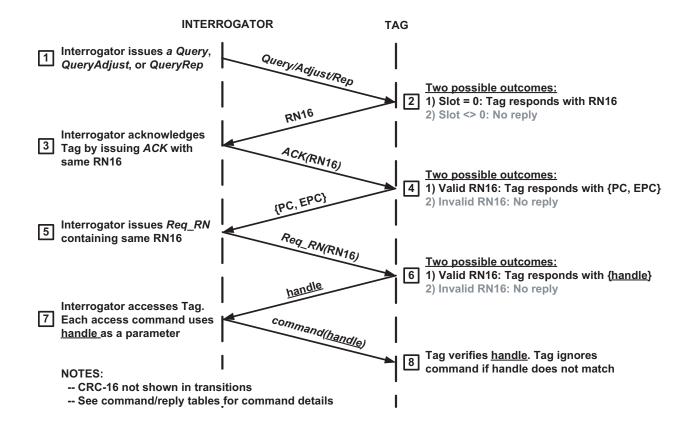

| 53 | Communications required as part of the 18000 Part 6C $Query\ {\rm command}\ [4].$ .           | 76  |

| 54 | Macros specification file for commands required as part of the 18000 Part $6\mathrm{C}$       |     |

|    | Query command.                                                                                | 77  |

| 55 | Template generated for <i>Query</i> command                                                   | 77  |

| 56 | Tag behavior for <i>Query</i> command                                                         | 78  |

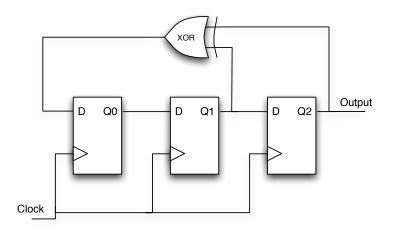

| 57 | A 3-bit Fibonacci LFSR.                                                                       | 80  |

| 58 | VHDL for 16-bit LFSR                                                                          | 82  |

| 59 | Outline of Precision Pass That Updates Sizes of CDFG Nodes                                    | 85  |

| 60 | Example precision file                                                                        | 86  |

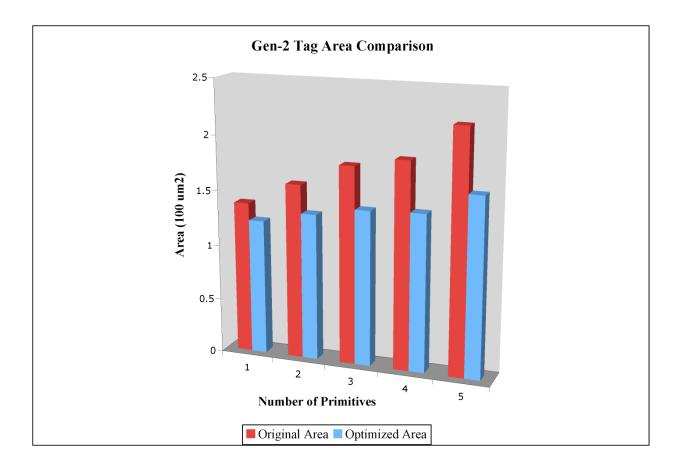

| 61 | Area for implementing the Part 6C primitive logic on a $0.16\mu\mathrm{m}$ ASIC with and      |     |

|    | without optimizations                                                                         | 87  |

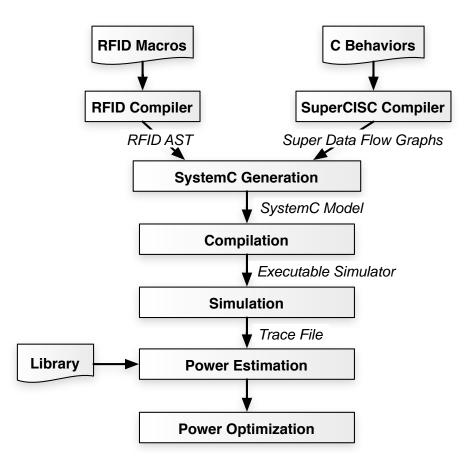

| 62 | RFID high-level specification methodology and compilation flow                                | 91  |

| 63 | Power macromodeling flow. Prior to VHDL code generation in Figure 62, this                    |     |

|    | flow generates a SystemC model to allow power analysis. The user changes the                  |     |

|    | specification until an acceptable power result is achieved, and then Figure 62                |     |

|    | resumes at VHDL generation                                                                    | 94  |

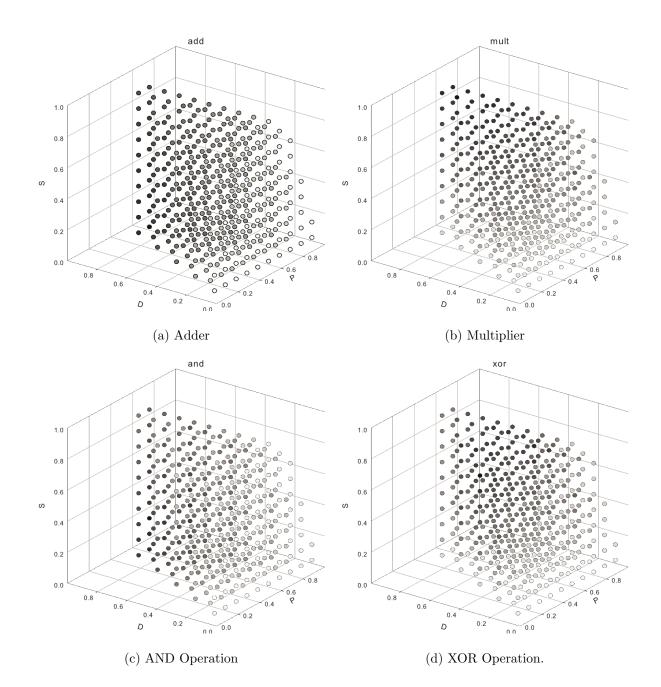

| 64 | 4-D plots of $p$ , $d$ , and $s$ versus power for functional units synthesized as $0.16\mu m$ |     |

|    | OKI ASICs. Power is indicated as a color between black and white where                        |     |

|    | solid black represents the least power consumed by the device and solid white                 |     |

|    | indicates the most power consumed by the device. Measurements are taken at                    |     |

|    | 0.1 intervals in each dimension $p, d, and s. \ldots \ldots \ldots \ldots \ldots \ldots$      | 97  |

| 65 | Outline for SystemC simulator generation                                                      | 98  |

| 66 | Outline for SystemC module generation                                                         | 98  |

| 67 | Outline for trace instruction generation                                                      | 100 |

| 68 | Outline for simulator framework generation                                      | 101 |

|----|---------------------------------------------------------------------------------|-----|

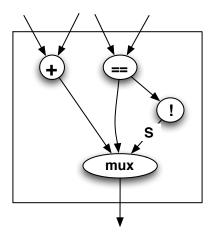

| 69 | An example module. Energy of the module is based on the energy of each of       |     |

|    | the individual functional units addition, equivalence, multiplexer, and logical |     |

|    | not                                                                             | 102 |

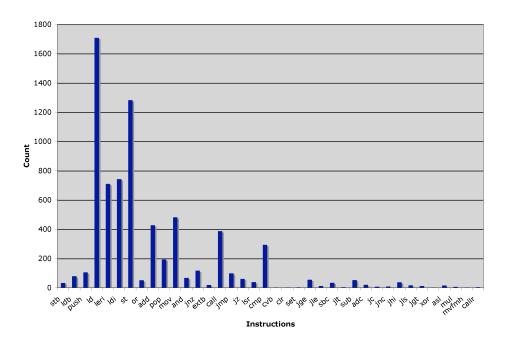

| 70 | ARM instruction profile.                                                        | 106 |

| 71 | EISC instruction profile.                                                       | 107 |

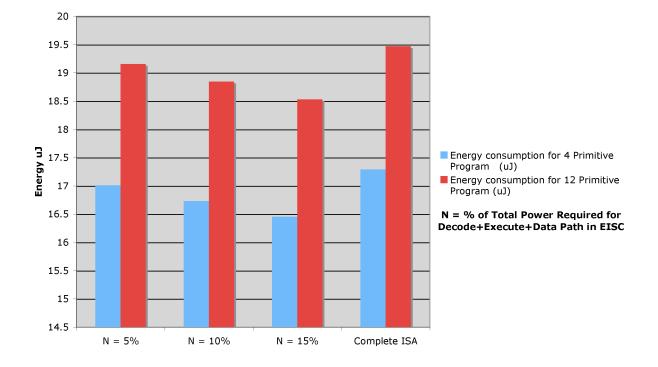

| 72 | Energy consumption of RFID C program generated by the compiler for differ-      |     |

|    | ent values of N.                                                                | 108 |

#### PREFACE

I am highly indebted to my advisor, Dr. Alex K. Jones, who provided me the support to carry out my research and made my stay at the University of Pittsburgh productive and enjoyable. He has always made time to talk to me about both research and career issues. Without his guidance and persistent help, this dissertation would not have been possible. I would like to express my deep gratitude for Professors Marlin Mickle and Tom Cain for providing recommendations and suggestions which were invaluable for my research. I also thank my other committee members, Professors Ron Hoelzeman and Bryan Norman for their guidance.

I would like to thank my student colleagues and friends in the EDA lab, the RFID Center for Excellence and at the University of Pittsburgh who have helped me in many ways. I would like to thank the administration and the staff in the Department of Electrical and Computer Engineering who have made it a great experience to be a part of the Department.

Words alone cannot express the thanks I owe my husband, Muthukumar, my mother, Vidya and my sister, Sudha for their unconditional love, patience, understanding and support. Most of all, I am grateful to my father for being my incessant source of inspiration. I dedicate this dissertation to his memory.

#### 1.0 INTRODUCTION

Radio Frequency Identification (RFID) systems are expanding rapidly with their applications in a wide range of areas. RFID systems consist of Radio Frequency (RF) tags and RF readers or interrogators. These systems are used for a wide range of applications that track, monitor, report and manage items as they move between different physical locations. The tags consist of integrated circuits and an RF antenna. A wide range of extensions such as memory, sensors, encryption, and access control can be added to the tag. The interrogators query the tags for information stored on them, which can include items like identification numbers, user written data, or sensory data. Tags contain a unique tag identification number and potentially additional information of interest to manufacturers, healthcare organizations, military organizations, logistics providers and retailers, or others that need to track the physical location of goods or equipment.

RFID tags generally come in two types, active and passive. Active tags require an internal power source to power the tag for receiving queries and transmitting responses. Passive tags do not contain an internal power source and receive energy from the interrogator query. This energy is used to power the tag to determine and send a response to the query. This energy may not be sufficient for intensive computation, limiting the complexity of response. The range of passive tags is also significantly lower compared to active tags. Active tags, on the other hand, are more costly than passive tags and may also require frequent battery replacement.

RFID applications are numerous and far reaching. The most widely used applications can be categorized as those for supply chain management, security, and the tracking of important objects and personnel. Though standards (ISO/IEC JTC1, ANSI, EPC etc) have been developed for RFID hardware, software and data management, these applications have customized requirements. The RFID tag circuits for these are implemented in custom designed chips. Such chips can only be used in specific applications, and therefore, are often called application specific integrated circuits (ASICs).

The design, development, and fabrication of Application Specific ICs is expensive and time consuming. The design process of ASICs requires considerable knowledge in digital logic design, which is very different from application programming in high-level languages such as C. In addition, it is a long and a tedious process that involves designing, synchronizing and synthesizing the digital design. Currently, this process involves months for a hardware engineer to complete. To reduce the design time, effort and cost significantly, it is necessary to develop design automation tools that allow the designers to reduce the time to move from specifications to hardware implementations.

The cost of fabrication of ASICs is very high. Small companies and RFID application programmers are, from a cost standpoint, prohibited from designing their own ASICs. As a result, the design of RFID systems is being done by large companies with state of the art hardware design and fabrication capabilities. These companies also drive the direction of the evolution of RFID systems and, hence, the standards, as technological capability is the key to the development of standards. With the design automation tool, smaller companies or RFID application programmers will be able to achieve customized RFID tag ICs implementations in less time, in a cost effective manner.

The market for RFID tags is characterized by rapidly evolving applications and rather short market windows. A key concept for coping with such requirements is the retargeting of system components for different and/or modified applications or standards. The modified applications can be implemented quickly using the design automation flow.

Power optimization is critical in RFID systems because the power budget is limited in the case of passive tags and battery drain needs to be limited in the case of active tags as frequent replacement of batteries may not be feasible. Thus, the tags generated by the design automation tool must be extremely power efficient.

In this dissertation, an automated, low-power flow for the design of RFID tags has been developed, implemented and validated. This dissertation presents the RFID Compiler, which was developed at Electronic Design Automation Laboratory at the University of Pittsburgh.

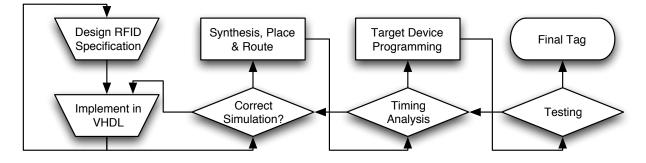

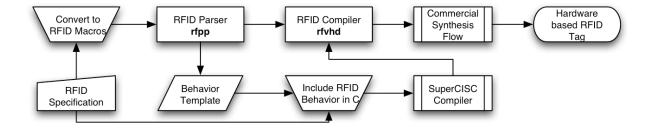

Figure 1: RFID Specification Methodology and Compilation Flow

Figure 1 shows the RFID Compiler flow. The RFID Compiler permits high-level design entry using a simple description of the desired primitives and their behavior in ANSI-C. The compiler has different back-ends capable of targeting microprocessor-based or hardwarebased tag controllers. For the hardware-based tag, the back-end automatically converts the user supplied behavior in C to low power synthesizable VHDL. The compiler also integrates a fast, high-level power macromodeling flow, which can be used to generate accurate power estimates and to optimize the primitives and their behaviors.

Figure 2 presents a comparison of different RFID tag design methodologies. The current state of the art tag development shown in Figure 2(a) requires lengthy design, fabrication, and testing cycles which can take months, with intellectual property (IP) reuse, to years if developing new IP. A customizable RFID tag, as shown in Figure 2(b), can handle variations in standards and requirements as they are developed with a significantly shorter time to market than current flows. A customizable RFID tag can make flexible RFID systems economically viable. This tag is mass produced and tailored to a particular RFID use after fabrication.

In this dissertation, the design flow from the RFID primitives to the power optimized tag controller is presented. Relative to contemporary technology, the design flow developed and implemented in this dissertation:

- allows for a simple specification of the RFID primitives and description of the primitives behavior in C

- allows RFID technology design by a wider audience, not necessarily hardware designers

- generates a low power design

- quickly generates accurate power estimates, which can be used for exploration and optimization of both the standard and the C code for behaviors.

This dissertation presents the algorithms, approaches, and techniques used in the design flow of the RFID Compiler. The main emphasis of the mechanisms used in this research is to shorten the design time while producing an implementation which is power efficient.

Several standards have been implemented with the RFID Compiler. Two System-on-a-Chip implementations for the ISO 18000-7 and ANSI standards were first used to validate

(a) Current RFID tag design flow. All tag components integrated manually. Estimated time: months or years.

(b) Automated RFID tag design flow. Prepackaged extensible silicon device. Estimated time: hours or days.

Figure 2: Comparison of RFID tag design philosophies.

the design flow. First, a C program was automatically generated and compiled for the microprocessor-based system. Second, the microprocessor was replaced with a block of low-power FPGA logic. For, the 18000-6C and 18185-7 standards, VHDL was generated, synthesized for ASICs and compared with the corresponding manual implementations. Power estimates were generated using the power macromodeling flow and were compared with the power estimates from the traditional methods to validate the accuracy and the gain in designer productivity.

#### 2.0 CONTRIBUTIONS

There are two major problems in the current RFID systems. (1) Custom tags, with additional capabilities beyond those specified in existing RFID tag standards, are sometimes required for specific applications. To build such custom systems from scratch is generally cost prohibitive and requires long design times. (2) Power optimization is critical in RFID systems because the power budget is limited for passive RFID systems and battery drain needs to be limited for active RFID systems as frequent replacement of batteries is often not feasible after deployment.

#### 2.1 PROBLEM STATEMENT

The objective of this dissertation is to solve the above problems by presenting a standard design flow for the rapid development of RFID tags with custom capabilities, for a wide variety of applications. To address the problem of rapid design of custom tags the RFID specification methodology and compilation flow will automatically generates RFID tag controller code based on a high-level description of the commands to be implemented. The design methodology is proven by targeting embedded microprocessor-based and hardware-based prototypes.

To address the problem of developing low-power tags, this dissertation integrates power as one of the primary metrics early in the design flow. The compiler automatically generates an application specific simulator for the specified design and accurately estimates the power consumed by the design with a factor of 100 speedup over traditional power estimation methods.

#### 2.2 CONTRIBUTIONS

#### 2.2.1 RFID Compiler for the Microprocessor-based Tag

The RFID compiler allows *RFID primitives* or the transactions employed by the RFID systems to be specified using *RFID macros*, an assembly-like format. These RFID macros are processed to generate a template file to specify the behavior for each primitive or macro. All behavior is specified using ANSI-C allowing the user to create arbitrarily complex behaviors. Finally, the RFID compiler generates a C program as output that is compiled onto the microprocessor with its platform-specific C compiler.

#### 2.2.2 Hardware RFID Compiler with VHDL Behavior

While the embedded processor approach does provide a reasonable power/energy consumption, improvement is still possible. To improve both the power and capacity of the controller, a hardware-based RFID controller is explored. The hardware RFID compiler processes the original RFID macros to generate VHDL template files to specify the behavior. The behavior for each primitive is specified using VHDL and the remaining code segment for packet packing, unpacking, and decoding is automatically generated and output in VHDL rather than in C. Finally, the RFID compiler generates the tag controller VHDL design which is synthesized, mapped, placed, and routed for the target hardware using commercially available tools. ASIC implementation of the primitives will be evaluated to reduce the energy.

#### 2.2.3 Hardware RFID Compiler with C Behavior

Because C is a significantly more universally known programming language than VHDL or Verilog, it is desirable to continue allowing the end-user specify the primitive behaviors for the RFID Tag in C. The extended hardware RFID compiler can read primitive behavioral descriptions in ANSI-C and generate synthesizable VHDL for combinational implementation. These combinational blocks are combined with the automatically generated packet packing, unpacking, and decoding VHDL and synthesized for the reprogrammable hardware target. 2.2.3.1 EPC C1 Generation 2 Hardware RFID Compiler EPCglobal Class-1 Generation-2 UHF (Gen-2) specification, recently standardized as ISO 18000 Part 6C, is becoming widely accepted in the supply chain today and is driving the development of passive tags. The communication primitives of Part 6C are significantly different and more complex than the ISO 18000 Part 7 standard. This is because the standard relies on multiple variables and storage of state at several points during each communication operation. This makes the RFID compiler significantly more general than the original implementation. The Hardware RFID Compiler with C behavior is extended with features to support Part 6C primitives and is optimized for low-power and area.

#### 2.2.4 Techniques For Optimizing The Tag Power Consumption

To enable the design of low-power tags, a power macromodeling flow is implemented, which calculates power at a high level during the RFID compiler design automation process. In this flow, the RFID compiler automatically generates a SystemC-based application specific simulator for the input specification. Through access to a pre-profiled library of blocks in the target fabrication process, the power consumption is estimated within an accuracy of 15% of the conventional ASIC power estimation flows, while being 100 times faster. The estimates can be used for the optimization of the primitive behaviors and in the evaluation of alternate protocol designs.

The remainder of the dissertation is organized as follows: Chapter 3 presents the background for this dissertation and the related work. Chapter 4 describes the stages of the RFID specification methodology and the compilation flow in detail for the microprocessor-based system. Chapter 5 describes the Hardware RFID Compilation flow with the behavior specified in VHDL. Chapter 6 describes the Hardware RFID Compilation flow with the behavior specified in C. Chapter 6.4 describes the EPC C1 Generation 2 Hardware RFID Compilation flow. Chapter 7 describes the techniques for optimizing the tag power consumption implemented in the compiler. Finally, the conclusions are presented in Chapter 8.

#### 3.0 BACKGROUND

A considerable body of literature exists on RFID systems. This chapter provides a brief description of RFID systems, their architecture, the tag characteristics, the prevalent standards and common RFID applications.

The focus of this dissertation is to present a standard design flow for the rapid design of low-power RFID tags with custom capabilities for different applications. The automatically generated tag controller code targets embedded microprocessor-based and hardware-based tags. To provide an understanding of the design process and gain in design times, this chapter covers the relevant aspects of the traditional ASIC design flow. The design flows for the reconfigurable field programmable gate arrays (FPGAs) and embedded microprocessors are also included.

This chapter also includes a section describing the commercial RFID systems and other research programs that build customizable RFID systems. Finally the prototyping environment used in the University of Pittsburgh compilation flow is described.

#### 3.1 INTRODUCTION TO RFID SYSTEMS

RFID technology is an alternative to barcode technology and it enables identification at a distance without a line of sight. Figure 3 shows common devices that employ RFID tags. Figure 4 shows an RFID reader that is used to communicate with the tags. Electronic tagging is superior to barcodes in many ways. It allows writing data into the tag, interaction with sensors, scanning a large number of items simultaneously without human error, etc. It supports a much larger set of unique IDs and additional data such as the manufacturer ID.

Figure 3: Common RFID Tags

RFID is not a new technology. For instance, the principles of RFID were employed by the British in World War II to distinguish allied aircrafts from enemy aircrafts. During the 1960s, work on employee access control was carried out at Los Alamos National Laboratories. For many years this technology has been used in applications as diverse as: animal tracking, automatic toll collection and many forms of ID badge for access control. Recently, RFID has become more mainstream. RFID tags can now be achieved at low manufacturing costs and are being adopted in many new applications.

#### 3.1.1 **RFID** Architecture

An RFID system mainly consists of tags and readers. The reader, also called the interrogator, sends and receives RF data to and from the tag via antennas. The tag, or transponder, is made up of the microchip that stores the data and an antenna. The information collected from the tags is stored in a back-end database. Figure 5 shows the main components of an RFID system.

#### 3.1.2 **RFID** Tag Characteristics

Tags can vary in terms of the frequency at which they communicate, the protocol, how they are powered and how they store data.

Many types of RFID devices exist, but at the highest level, they can be divided into active and passive devices. Active tags require a power source and use energy stored in a

Figure 4: RFID Reader

battery. The active tag's lifetime, and hence the number of operations, is limited by the stored energy. They have ranges of over a hundred feet. They typically cost more than the passive tags and are used to track high value goods like vehicles and pallets.

In the case of passive tags, the reader is responsible for powering and communicating with the tag. The reader transmits a low power radio signal through its antenna to the tag, which in turn receives it through its own antenna to power the integrated circuit. As a result, passive tags transmit information over shorter distances, typically less than 10 feet. Since they cost considerably less, they are used in tracking low cost items. They do not require batteries and have an indefinite operational life.

**3.1.2.1** Communication There are many different versions of RFID systems that operate at different radio frequencies. The choice of frequency is dependent on the requirements of the application. Three primary frequency bands have been allocated for RFID use. The Low Frequency band (125/134KHz), is most commonly used for access control and asset tracking. The High Frequency band (13.56 MHz) is used where medium data rate and read ranges are required. The Ultra High Frequency (850 MHz to 950 MHz and 2.4 GHz to 2.5 GHz) band offers the longest read ranges and highest reading speeds. The techniques in this dissertation can be applied regardless of the frequency employed.

Figure 5: The Main Components of an RFID System

**3.1.2.2 Computation** Most passive tags have simple or no computational capabilities. They may only have a simple memory that can be remotely accessed. They may have a simple design that can perform certain XOR and AND operations. Active tags can be more complex, and could have have a few thousand logical gates to implement logic.

The two basic types of memory available on RFID tags are read-only memories and read-write memories. Read only chips are programmed with unique information stored on them during the chip manufacturing process. The information on read only chips can never be changed. With read write memories, the user can add information to the tag or write over existing information when the tag is within range of the reader.

**3.1.2.3** Security Applications for RFID continue to expand into domains such as electronic passports, electronic payment systems, and electronic container seals. These applications have a risk of unauthorized access to sensitive biometric or financial information through the RFID tag or or tag communication. RFID devices are susceptible to many forms attacks, which may affect the security and privacy of the individual users or the organizations. Some of the main attacks possible are physical attacks against tags, counterfeiting

of tags or readers, eavesdropping messages transmitted in protocols, etc. Some of the attacks that are less malicious are traffic analysis to detect when and how many messages are sent, disrupting messages and denial of service attacks.

However, as RFID devices are intended to be small and relatively simple devices, security protocols and techniques can significantly lag behind the other details such as correctness, read rate, power consumption, etc. This is primarily because strong authentication and encryption algorithms are complex and would significantly increase the cost and power budget of the tag. As such, the state of security in RFID systems is generally weak compared to other mature computational technologies such as Internet servers, shared computing workstations, and even smart-cards. Various security techniques have been proposed in the recent years, including killing tags at the checkout point, physical tag memory separation, rolling codes, hash locks, challenge-response protocols, etc. An exhaustive study of the security attacks of RFID as well as the protection techniques is beyond the scope of this dissertation, but can be found in [5]. Design automation flow discussed in this dissertation could allow the RFID primitives to support novel security techniques.

#### 3.1.3 **RFID** Applications

RFID is expected to provide huge advantages to manufacturers by offering the tools to better plan production and respond more quickly to market demand. The use of RFID tags will permit automatic management of stock and inventories in shops and warehouses. Supermarkets and other retailers across the world are pioneering large-scale item-level deployments of RFID in consumer goods. Some examples are: Wal-Mart in the US, Marks & Spencer and Tesco in the UK and Metro in Germany. By using RFID technology for tracking sales, stock and orders they aim to lower operational costs which in turns impacts the pricing.

The United States Department of Defense has been using active tags to reduce logistics costs and to improve supply chain visibility for more than 15 years. The US government is considering the use of RFID tags in the passports to reduce counterfeiting and to enable automatic identity checking. The European Union is planning to incorporate RFID tags in the European paper currency to make forgeries difficult and to provide tracking of its use. Management of books can be automated by using RFID for libraries. Tags can be inserted in each volume, thus simplifying the work of library staff as well as improving the experience of users. Inventories can be carried out without removing books from the shelves, by automatically detecting missing or misfiled books, or even by using an automatic sorter for the returned volumes. An example is the use RFID tags in the Vatican Library in Rome to identify and manage its extensive book and document collection [6].

Many access control applications also employ RFID tags. The use of RFID cards or badges makes access control simpler for people as they do not have to manipulate their identification card. It can also be used for identifying people or for safety reasons, e.g., when a building must be evacuated. Theft and vandalism are also impeded. Another example of access control is the keyless and passive entry systems in cars. The owner initiates a secure exchange of information between the car's remote unit and the car by the push of a button on the remote, and the door of the car automatically unlocks itself.

RFID technology is very useful in location sensing, item/animal tracking, healthcare, etc. Examples include a location sensing prototype system for locating objects inside buildings [7] and a system for identifying persons and objects inside and outside hospitals [8]. RFID tags and intelligent transponders are widespread for vehicle to roadside communications, road tolling and vehicle access control. Different types of RFID systems are being developed to support all aspects of aviation baggage tracking, sorting and reconciliation [9].

This motivates the need for different RFID customizations and possible interoperability across domains. This can be easily accomplished using the concepts in this dissertation.

#### 3.1.4 RFID Standards

There are number of standards for RFID systems which have either been published or are in the process of being elaborated. The main specifications are: ISO (International Organization for Standardization [10]) standards, EPC (Electronic Product Code [4]) specifications and ANSI (American National Standards Institute [11]).

The key active ISO standard is 18000-7 [10], which is an international standard that defines the air interface for RFID devices used in item management applications. The stan-

dard defines the forward and return link parameters for an active RFID air interface at 433 MHz and the communications protocol used. The ISO 18185 Part 1 standard [12] is an international standard that provides a system for the unique identification and presentation of information about freight container electronic seals. It is used in conjunction with the other parts of ISO 18185 such as, Part 4 that specifies data protection and Part 7 that specifies the physical layer protocol.

The EPC specifications, established by EPCGlobal, distinguish several classes of tags according to their function. Class 1 corresponds to the most simple tags, which have only a unique identifier for the tag by default. Class 2 offers more memory and allows authentication functions to be carried out. Class 3 corresponds to semi-passive tags and finally class 4 corresponds to active tags, which can potentially communicate with each other. Of these, the Class 1 Generation 2 (or "Gen 2") UHF specification is the most widely used [4]. It has been integrated with the ISO standards as the 18000-6C passive standard [13].

The ANSI/NCITS 256-2001 is the American National Standard for RFID devices [11]. It is intended to allow for compatibility and to encourage interoperability of products for the growing RFID market in the United States.

As part of this dissertation, I show the comparison of automated implementations of these standards and in some cases, merge the implementations of different standards such as ISO 18000-7 and ANSI/NCITS 256-2001.

#### 3.2 HARDWARE DESIGN METHODOLOGIES

Historically, digital hardware has been divided into two main groups, general-purpose processor and application specific hardware. A general-purpose processor is a fixed architecture device which implements a pre-defined set of instructions. General-purpose processors can be classified as: microprocessors and digital signal processing (DSP) processors among others. Examples of microprocessors are Intel's Pentium family, Sun's UltraSparc family, Intel's XScale, and IBM's PowerPC for embedded applications, etc. These processors execute programs stored in some internal or external memories by fetching their instructions, examining them and then executing them one after another. An organization of a simple bus-oriented microprocessor is shown in Figure 6. New programs can be loaded into memory as needed. The computation of any algorithm is determined by the software program, not the hardware. Because their instruction sets include very general applications such as arithmetic and logical operators, general-purpose processors can be programmed to perform any conceivable function. The application can be programmed in a high-level language such as C and is compiled for execution on any processor. However, general-purpose processors are slower than dedicated hardware at performing computationally intensive functions. They also consume higher power compared to application specific hardware.

Figure 6: Organization of a Simple Bus-oriented Microprocessor

For application-specific hardware, an engineer designs all of the circuits specifically for an application. These circuits or custom hardware implementations, which are often referred to as application-specific integrated circuits (ASICs), usually lead to better performance than general-purpose processors since they can be optimized for the specific application. However, if a new function is required, then an entirely new ASIC must be created. Another disadvantage of ASICs is the labor-intensive design cycle. It typically takes months or years for hardware engineers to design a new ASIC and have it fabricated and tested. This also translates into a high cost and long time-to-market. In spite of these drawbacks, application specific hardware is widely used whenever performance is of primary importance or product

volume is very high. By optimizing the hardware for a particular task, an ASIC can often achieve computation speeds several orders of magnitude faster than doing the same computation using general-purpose hardware, while also requiring lower power. ASICs shine in extremely high volumes of production of relatively unchanging specification as they provide the best performance and power solution.

In recent years, programmable logic devices have been increasingly gaining interest, when high volume is not possible, but custom hardware is desired. They have some of the advantages of both general-purpose and application-specific hardware. These devices are most commonly commercially available Field Programmable Gate Arrays (FPGAs) or Complex Programmable Logic Devices (CPLDs). While FPGAs are large, have higher performance and consume higher power, CPLDs are small, have lower performance and consume lower power. These devices provide a relatively large number of programmable functional units and programmable interconnections. The functionality of the hardware is determined by how the functional units and interconnections are configured. By changing the configuration, the hardware can be made to perform a completely different function. Different types of applications can be implemented at speeds between application specific hardware and general-purpose processors. In addition, the configuration can be changed relatively quickly from one function to another, giving some of the same flexibility as general-purpose processors. These programmable logic devices consume lower power compared to general-purpose processors and higher power compared to application-specific hardware.

#### 3.2.1 Design Flows For ASICs and FPGAs

The traditional design flow for ASICs is depicted in Figure 2(a). It starts with the development of a hardware definition for the application. This is usually done with a hardware description language (HDL). The two main HDLs in use today are VHDL and Verilog. For HDL coding, a sound knowledge of the digital logic design is required. The functionality of the HDL is then verified in simulation against the initial specification. The HDL description of the design is then synthesized into a netlist consisting of cells and their interconnections. The cells used in the netlist are obtained from a standard cell technology library provided by the ASIC manufacturer, typically analogous to basic logic gates. The library defines the delay models, models for variations of temperature, voltage and manufacturing processes as well as the functionality of each cell. This gate-level netlist is then simulated to verify the functionality of the design. The logic cells are then placed on the layout of the chip as a minimum area arrangement that meets the performance constraints. After placing the logic gates, the interconnections between logic gates are routed according to the specified netlist. Post-layout simulation is performed at this level, mainly to verify that the design meets the specified timing constraints. Pin assignment is then performed to connect the input and output signals of the design to the I/O pins of a chosen frame. Finally, the physical layout of the design is sent off for fabrication.

Figure 7: Design Flow For Reconfigurable Hardware

The traditional design flow for reconfigurable hardware is depicted in Figure 7. To map an application to reconfigurable hardware, the designer must first define the hardware structure for the application using a HDL. After that, the HDL code is verified to make sure that it matches the required functionality, prior to synthesis. The design is then synthesized into a technology-dependent netlist. This netlist is specified in terms of the basic logic block of the device. For example, if the Xilinx Spartan-3 series FPGAs are used, the netlist is specified in terms of Configurable Logic Block (CLB). The incoming netlists and constraints are mapped into the available resources on the target device. Then the design is placed and routed onto the device to meet the timing constraints. The timing of the design is then verified by static timing analysis. The placement and routing processes produce the physical implementation for the design, which is then translated into a bit stream (commonly known as configuration file), which is used to program the target device. This flow is considerably simpler and shorter than the ASIC design flow. Moreover, once the functionally correct and synthesizable VHDL is available, mapping to the target device can be done quickly and efficiently using commercial back-end tools.

The compilation flow developed in this dissertation automatically generates the tag C program or synthesizable tag VHDL design for compiling on to microprocessors or for mapping on to programmable logic devices. This avoids the high initial cost, the lengthy development cycles, and the inherent inflexibility of conventional ASICs. RFID tags with custom capabilities for different applications can be designed and prototyped in a short amount of time. However, if the tag design is to be manufactured on a very large scale, ASIC fabrication can be done after prototyping the tag design using a reconfigurable device.

#### 3.3 RELATED WORK

Several RFID tags are being developed in the industry and in research labs. In this section, some of these tags are highlighted. The available customizable RFID systems are also presented. The differences between these approaches and this dissertation are also discussed.

#### 3.3.1 Commercial Systems

Some of the companies that develop RFID tags are Savi, Intermec, Phillips, Motorola, Hitachi, etc. The tags are designed using a traditional ASIC design flow. The SaviTag ST-602 is a simple, low cost, tag for real-time tracking of containers and their contents within facilities or across geographies. It has a battery life of four years, a range of about 300 feet and memory capacity of 36 bytes (see Figure 8(a)) [14]. The SaviTag ST-654 high performance tag is suited for various applications including tracking of shipping containers, vehicles, and other large assets. It is claimed to have immunity to some effects such as dirt and enclosures,

(a) Savi Tag ST-602

(b) Savi Tag ST-654

Figure 8: Some RFID Products From Savi [1].

and has a range of up to 300 feet, a typical battery life of five years using lithium cells and memory capacity of 128K (see Figure 8(b)). The Savi tags are compatible with the Savi reader products (for example, see Figure 8(c)).

Other custom tags, which are commercially available, are also designed using the standard ASIC design flow. A novel design of a batteryless, self-powered RFID transponder is presented in [15]. Data transmission uses frequency shift keying (FSK) modulation and the circuit is designed such that the output frequencies are implicitly determined, independent of the load of the antenna. The design is fabricated as a 0.8um CMOS circuit. An integrated circuit for a battery-less transponder system for high performance identification systems is described [16]. The operating principle of the system gives a superior performance in reading distance due to separation of the powering and data transmission phases. The design of a read/write tag targeted towards low-cost applications is described in [17]. An ultra small RFID micro-chip storing a unique 128-bits ROM ID code, for use in a reliable authentication through a network-based secure ID management is available [18]. An ultra-small radio-frequency identification chip, called the u-chip, has been developed for use in a wide range of individual recognition applications [19] . The chip is fabricated using 0.18um standard CMOS technology. The RFID enabled micro-chip [20] is small sized and low cost, and is suitable for attachment to paper media and small products, aiding counterfeit prevention and product tracking in market environments. A wireless sensor prototype platform (UbiSensor) presented in [21] combines sensors and RFID resulting in sensing, data processing, network protocol execution, and energy scavenging capabilities. The platform design is driven by energy consumption minimization of given tasks. A commercially available microcontroller, low power RF transceiver, and power generator circuits are used.

#### 3.3.2 Customizable Systems

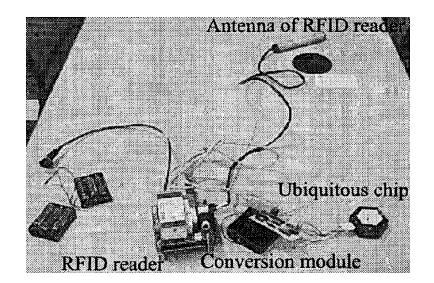

Figure 9: Rule-based RFID tag system. Source: [2].

A rule-based RFID tag system using ubiquitous chips is proposed in [2] to construct flexible and scalable systems. Ubiquitous chips are rule-based I/O control devices, to which several devices such as switches, sensors, LEDs (Light Emitting Diode), etc., can be attached. Ubiquitous chips use ECA rules for event-driven programming. An ECA rule consists of the following three parts: events (E), conditions for executing the actions (C) and the actions to be carried out (A). ECA rules have been used to describe the behaviors of active databases. An active database is a database system that carries out prescribed actions in response to a generated event inside / outside of the database. A simple example of an ECA rule is shown in Figure 10.

- E: A person passes the entrance.

- C: He/She has a license to enter the office.

- A: Open the door.

Figure 10: Example ECA rule for an employee access control application. Source: [2].

Figure 9 shows a prototype of the system proposed in [2]. An RFID reader and RFID tags made by Texas Instruments (TI-K2A-001A) are used. The reader is connected to a ubiquitous chip through a conversion module. The conversion module converts the ID received from the RFID reader into the ubiquitous chip format. The application program is input into the ubiquitous chips using rules to describe behaviors. Using this system, an employee access control application is implemented. The authors then show how this system can be customized using a different set of rules when the application is extended to support a different type of access control. This approach may be useful when applications are simply extended, however, when a completely new application or a new protocol needs to be implemented the tag itself will require customization. Our RFID design automation flow allows full customization of RFID tags.

One of the main components of an RFID system communication is the physical layer protocol employed to encode bits of information. The physical layer features for the bit encoding mechanism vary across various RFID standards. For example, the ISO 18000 Part 7 active tag standard specifies *Manchester encoding* [22] to transmit encoded data RFID interrogators and tags [10] while the ISO 18000 Part 6C standard defines different physical layer features of transactions among readers and tags. *Pulse-Interval Encoding (PIE)* [13] is utilized to encode data transmitted from readers to tags and either *FM0* [23] or *Miller encoding* [24] is utilized to encode the backscattered data from tags back to readers [13]. [3] describes a methodology by which the physical layer decoder and encoder hardware blocks can be automatically generated from a high-level specification of the protocol. This design flow is shown in Figure 11. The user describes the waveform features of the encoding scheme

such as edge transitions, level detection, pulse width detection, etc. from a physical layer specification. The user can then combine one or more wave features to represent bits or groups of bits. The physical layer synthesis tool then automatically generates hardware blocks for encoding and decoding the signal in VHDL. These VHDL descriptions are created from the combination of predefined parameterized hardware libraries and automatically generated hardware blocks for detecting and generating the waveform features in the encoding.

Figure 11: The generation flow for an RFID data encoder and decoder. Source: [3].

# 3.4 RFID PROTOTYPING ENVIRONMENT

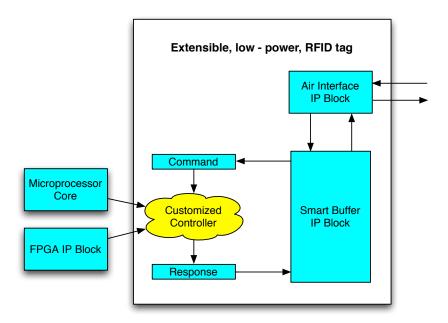

The RFID compiler uses a simple specification of the RFID design to create the RFID tag controller. The complete tag prototype consists of a programmable controller, an air interface, and a power-aware *smart buffer* that sits in between, as shown in Figure 12. The *smart buffer* [25], implemented in an FPGA, contains a small amount of logic to detect whether incoming packets are intended for the tag, thereby allowing the controller to remain powered down to reduce overall system power consumption. The *Air Interface* serves as an interface between the smart buffer and the interrogator, with the necessary receiver and transmitter circuitry to allow the RFID tag to communicate with the RFID interrogator.

Figure 12: Extensible, low-power RFID tag.

# 4.0 RFID SPECIFICATION METHODOLOGY AND COMPILATION FLOW

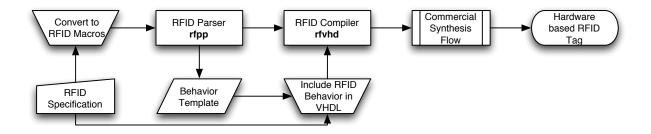

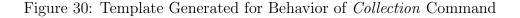

The RFID specification methodology and compilation flow are illustrated in Figure 13. The RFID primitives from the specification of the standards and the proprietary extensions are first converted into a simple assembly-like description or RFID macros. The first stage of the compiler, the RFID Parser (rfpp), reads this and builds it into the compiler. The user then defines the tag behavior in response to each RFID primitive in ANSI-C. To simplify the user interaction, the RFID Parser generates C code templates automatically. The user uses simple ANSI-C constructs to plug in the behavior into the template. The RFID Compiler (rfcc) generates the tag controller C code based on the input RFID macros and the tag behavior. The C code is compiled using an embedded compiler to generate executable binary for the microprocessor of the tag.

Figure 13: RFID Specification Methodology and Compilation Flow

To provide the background for understanding the inputs to the RFID specification methodology and compilation flow, the basic RFID command structures from the ISO 18000 Part 7 and ANSI-256 specifications are described in Section 4.1. The process for converting the basic RFID structures from the standard specification into a form read by the compiler is described in Section 4.2. The process for inserting the RFID tag response behavior described in the standard into the automatically generated behavior template into the form read by the compiler is shown in Section 4.3. Section 4.4 describes the process to generate the final program to be executed on the tag. Section 4.5 describes the prototype microprocessor based system developed, and the experimental results are shown in Section 4.6.

# 4.1 DESCRIPTION OF THE PRIMITIVES

#### 4.1.1 ISO 18000 Part 7

As an illustration of the RFID standards specification, a *primitive*, *Collection* command has been selected from the ISO/IEC 18000-7:2004(E) standard. The format of the fields in the interrogator to tag command format for the *Collection* command primitive and its response are shown in Figure 14. Each RFID primitive has a unique field called the command code or opcode, which serves as the identifier and signals the tag what type of command is being issued. In addition to the opcode, each RFID primitive contains a number of other fields of varying lengths as positions for data present as can be inferred from Figure 14. The command contains a CRC to ensure the command packet is properly formed. The remainder of the packet contains particular fields appropriate to the command. For example, the command type field indicates the presence of Tag ID and Owner ID fields. Broadcast commands do not contain a Tag ID while point to point commands contain a specific Tag ID of the target tag. The Owner ID field, which is programmed in the tag's memory, allows the segregation of different groups of tags within the whole population.

Similarly, the tag response includes the command code, CRC and other data fields. The tag response also includes a tag status field, which consists of nested fields such as acknowledge, tag type, battery, etc.

| n Con                       | nmand           |                                                                                                                                                                               |                                                       |                                                                                                                                        |                                                                                                                   |                                                                                                                                                                                    |                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                     |  |

|-----------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Type                        | Owner           | Id In                                                                                                                                                                         | terrogator ]                                          | ode                                                                                                                                    | Siz                                                                                                               | æ H                                                                                                                                                                                | Res                                                                                                                                                                             | erved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CRC                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                     |  |