# THE VLIW-SUPERCISC COMPILER: EXPLOITING PARALLELISM FROM C-BASED APPLICATIONS

by

Joshua D. Fazekas

B.S. Computer Engineering, University of Pittsburgh, 2006

Submitted to the Graduate Faculty of

the School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science

University of Pittsburgh

2006

## UNIVERSITY OF PITTSBURGH SCHOOL OF ENGINEERING

This thesis was presented

by

Joshua D. Fazekas

It was defended on

April 28th, 2006

and approved by

Alex K. Jones, Assistant Professor, Electrical and Computer Engineering Department

Raymond R. Hoare, Assistant Professor, Electrical and Computer Engineering Department

J.T. Cain, Professor, Electrical and Computer Engineering Department

Thesis Advisor: Alex K. Jones, Assistant Professor, Electrical and Computer Engineering

Department

## THE VLIW-SUPERCISC COMPILER: EXPLOITING PARALLELISM FROM C-BASED APPLICATIONS

Joshua D. Fazekas, M.S.

University of Pittsburgh, 2006

A common approach to decreasing embedded application execution time is creating a homogeneous parallel processor architecture. The parallelism of any such architecture is limited to the number of instructions that can be scheduled in the same cycle. This number of instructions scheduled in a cycle, or instruction-level parallelism (ILP), is limited by the ability to extract parallelism from the application. Other techniques attempt to improve performance with hardware acceleration. Often, segments of highly computational extensive code are extracted and custom hardware is created to replace the software execution. This technique requires many resources and still does not address the segments of code outside of the computationally extensive kernel.

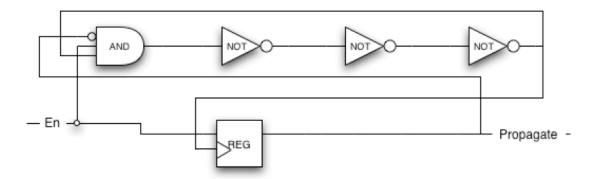

To solve this problem, hardware acceleration for computationally intensive segments of code in addition to accelerating the entire application with very long instruction word, VLIW, techniques is proposed. (1) A compilation flow that targets a 4-wide VLIW processor architecture is presented. This system was used to investigate the available speed-up of VLIW architectures. The architecture was modified to combine the VLIW processor with the capability to execute application specific customized instructions. To create the custom instruction hardware, a control and data flow graph (CDFG) framework was created. The CDFG framework was created to provide a framework for compiler transformations and hardware generation. In order to remove control flow from segments of code selected for hardware generation, (2) the technique of hardware predication was developed. Hardware predication allows *if-then* and *if-then-else* control flow constructs to be transformed into strict data flow through the use of multiplexors. From the transformed CDFGs, (3) a VHDL generation pass was created that translates the compiler data structures into synthesizable VHDL. The resulting architecture contains the VLIW processor and tightly coupled application specific hardware. This architecture was analyzed for performance changes compared to the initial VLIW architecture, and a traditional processor. Lastly, (4) the architecture was analyzed for power and energy savings. A post static timing pass was added to the compilation flow for the insertion of hardware to delay early switching of operations.

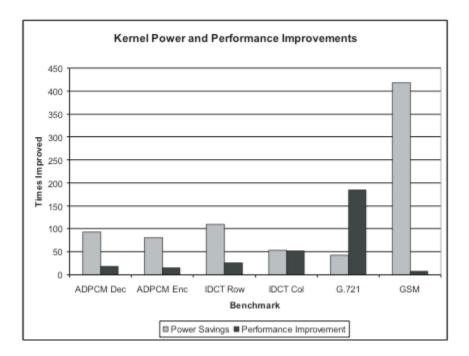

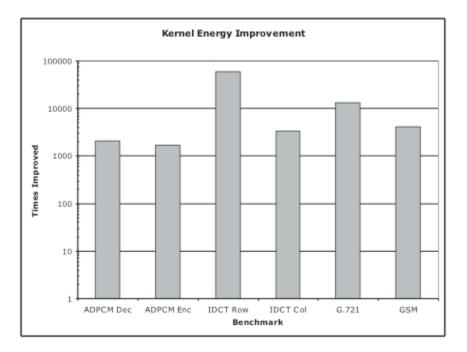

By measuring only the execution of the hardware function and comparing the performance to the equivalent code executed in software, a performance multiplier of up to 322 times is seen when synthesized onto an Altera Stratix II ES2S180F1508C4 FPGA. The average performance increase seen was 63 times faster. For the entire application, the speedup reached nearly 30X and was on average 12X better than a single processor implementation. The power and energy required by the VLIW processor core and the hardware functions for the computational kernels after 160nm OKI standard cell ASIC synthesis show a maximum power savings of 417 times that of execution on the processor with an average of 133 times savings in power consumption. With the increased execution time and the savings in power the energy savings will see a multiplicative effect. The energy improvement is therefore several orders of magnitude for the hardware functions, the savings range from over 1,000X to approximately 60,000X.

## TABLE OF CONTENTS

| 1.0        | INTRODUCTION                                                   | 1  |

|------------|----------------------------------------------------------------|----|

|            | 1.1 Motivation                                                 | 3  |

|            | 1.2 Key Contributions                                          | 4  |

| 2.0        | RELATED WORK                                                   | 6  |

| 3.0        | VERY LONG INSTRUCTION WORD PROCESSORS                          | 10 |

|            | 3.1 A VLIW/SIMD FPGA Processing Architecture                   | 10 |

|            | 3.2 Compiler Flow for a VLIW/SIMD FPGA Processing Architecture | 16 |

|            | 3.3 Results                                                    | 18 |

| <b>4.0</b> | CONTROL AND DATA FLOW GRAPHS                                   | 21 |

|            | 4.1 Control Flow                                               | 21 |

|            | 4.2 Data Flow                                                  | 27 |

|            | 4.2.1 The statement class                                      | 27 |

|            | 4.2.2 The <i>expression</i> class                              | 31 |

|            | 4.2.3 The CDFG node class                                      | 31 |

|            | 4.2.4 A parsing example                                        | 34 |

|            | 4.3 Results                                                    | 35 |

| 5.0        | COMPILATION FOR HARDWARE FUNCTIONS                             | 38 |

|            | 5.1 Profiling                                                  | 41 |

|            | 5.2 Preprocessing Compiler Transformations                     | 41 |

|            | 5.2.1 Definition-Use Analysis                                  | 44 |

|            | 5.2.2 Inlining and Loop Unrolling                              | 46 |

|            | 5.2.3 Code Motion                                              | 49 |

|            | 5.3 Hardware Predication                                                 | 53                   |

|------------|--------------------------------------------------------------------------|----------------------|

|            | 5.4 Results                                                              | 57                   |

| 6.0        | ASPECTS OF HARDWARE GENERATION                                           | 66                   |

|            | 6.1 VHDL Generation                                                      | 66                   |

|            | 6.2 Interfacing Software and Hardware                                    | 70                   |

|            | 6.3 Aspects of Performance Gain                                          | 72                   |

|            | 6.4 Results                                                              | 75                   |

| 7.0        | PERFORMANCE RESULTS                                                      | 79                   |

|            |                                                                          |                      |

| 8.0        | <b>REDUCING POWER AND DELAY ELEMENTS</b>                                 | 84                   |

| 8.0        | <b>REDUCING POWER AND DELAY ELEMENTS</b> 8.1 Power Modeling and Analysis | 84<br>85             |

| 8.0        |                                                                          | -                    |

| 8.0        | 8.1 Power Modeling and Analysis                                          | 85                   |

| 8.0<br>9.0 | <ul> <li>8.1 Power Modeling and Analysis</li></ul>                       | 85<br>89             |

|            | <ul> <li>8.1 Power Modeling and Analysis</li></ul>                       | 85<br>89<br>92       |

|            | <ul> <li>8.1 Power Modeling and Analysis</li></ul>                       | 85<br>89<br>92<br>97 |

### LIST OF TABLES

| 1 | Performance of Instructions (Altera Stratix II FPGA EP2S180F1508C4)        | 12 |

|---|----------------------------------------------------------------------------|----|

| 2 | Performance data of 3 implementations of VLIW instruction decoder on an    |    |

|   | Altera Stratix II                                                          | 15 |

| 3 | The <i>ExecutionObject</i> subclasses.                                     | 29 |

| 4 | The CDFG node data structures                                              | 33 |

| 5 | Hardware function synthesis results.                                       | 78 |

| 6 | Power and energy required by the VLIW processor core and the SuperCISC     |    |

|   | hardware functions for computational kernels after 160nm OKI standard cell |    |

|   | ASIC synthesis.                                                            | 91 |

## LIST OF FIGURES

| 1  | Very Long Instruction Word Architecture.                                          | 11             |

|----|-----------------------------------------------------------------------------------|----------------|

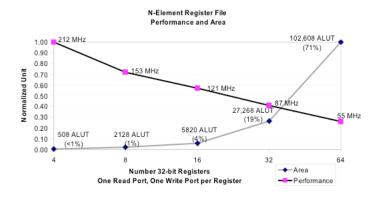

| 2  | N-element Register File Supporting P-Wide VLIW with P Read Ports and P            |                |

|    | Write Ports.                                                                      | 13             |

| 3  | Scalability of a 32-element register file with 2 read and 1 write port per pro-   |                |

|    | cessor for a Stratix II                                                           | 13             |

| 4  | Scalability of an N-element register file having N read and N write ports on an   |                |

|    | Altera Stratix II                                                                 | 14             |

| 5  | Scalability of a 32-bit P-to-1 multiplexer on an Altera Stratix II (EP2S180F1508C | <b>4)</b> . 15 |

| 6  | Compilation Flow Blue blocks represent added functionality                        | 17             |

| 7  | VLIW ROM file format.                                                             | 17             |

| 8  | Cycle-by-Cycle visual representation of an FIR filter generated by Trimaran       | 19             |

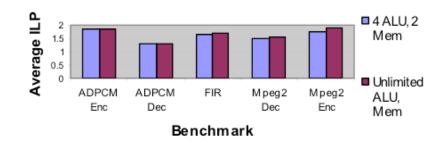

| 9  | Average IPL of Banchmarks.                                                        | 20             |

| 10 | Example showing the commands used to convert from C source to a SUIF2 file        |                |

|    | format.                                                                           | 22             |

| 11 | Example showing the commands used to execute the SUIF control flow graph          |                |

|    | pass                                                                              | 23             |

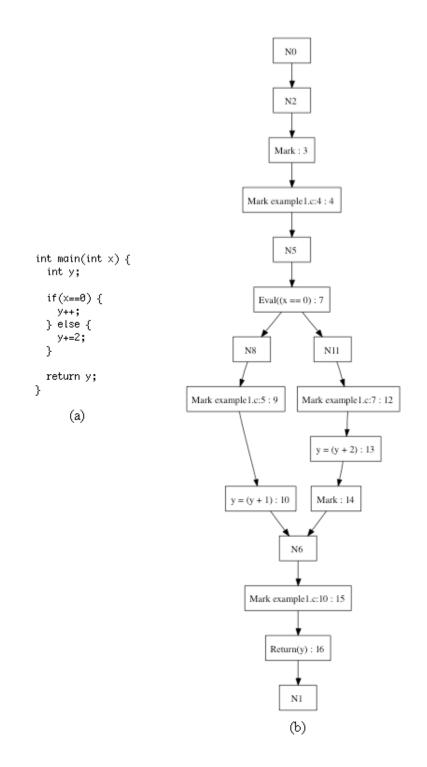

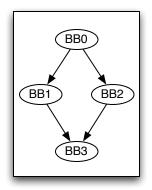

| 12 | C source and generated CFG for a simple example                                   | 24             |

| 13 | CFG of basic blocks for a simple example                                          | 25             |

| 14 | Pseudo-code to call the function to create basic blocks, based on the starting    |                |

|    | nodes for each basic block.                                                       | 26             |

| 15 | Pseudo-code to create the basic blocks, and identify the new starting nodes for   |                |

|    | basic blocks.                                                                     | 28             |

| 16 | Pseudo-code for parsing a SUIF statement class.                                 | 30 |

|----|---------------------------------------------------------------------------------|----|

| 17 | Pseudo-code for parsing a SUIF expression class                                 | 32 |

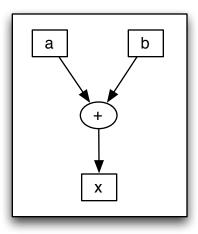

| 18 | Example data flow graph segment for the statement: $x = a + b$                  | 34 |

| 19 | Source code of a simple example to show the CDFG pass                           | 35 |

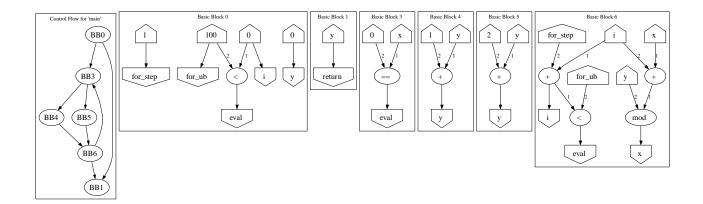

| 20 | Example control and data flow graph for a simple source code                    | 36 |

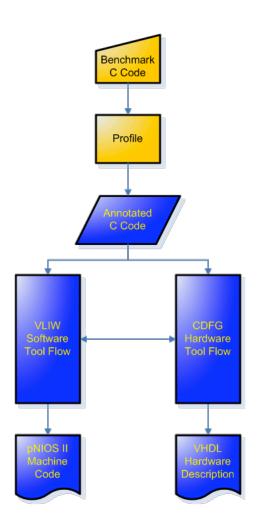

| 21 | The VLIW - SuperCISC Compilation Flow                                           | 39 |

| 22 | The VLIW - SuperCISC Architecture                                               | 40 |

| 23 | Excerpt of the Shark profiling results for the g721 benchmark                   | 42 |

| 24 | Code excerpt of results from Figure 23 after insertion of directives to outline |    |

|    | computational kernels that are candidates for custom hardware implementation.   | 43 |

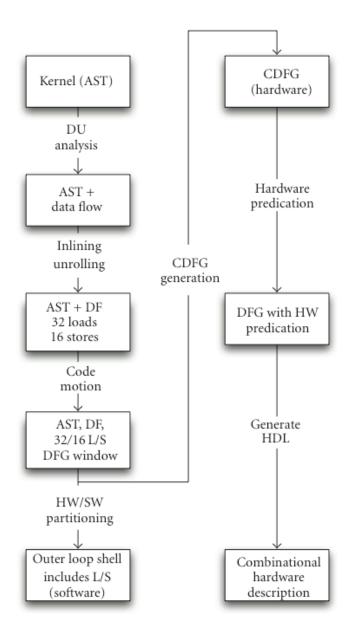

| 25 | Description of the compilation and synthesis flow for portions of the code      |    |

|    | selected for custom hardware acceleration. Items on the left side are part of   |    |

|    | phase 1, which uses standard compiler transformations to prepare the code for   |    |

|    | synthesis. Items on the right side manipulate the code further using hardware   |    |

|    | predication to create a DFG for hardware implementation                         | 45 |

| 26 | Fmult function from G.721 benchmark.                                            | 47 |

| 27 | G.721 code after function inlining.                                             | 48 |

| 28 | Unrolled inner loop of inlined G.721 hardware kernel.                           | 49 |

| 29 | G.721 benchmark after inlining, unrolling, and code motion compiler transfor-   |    |

|    | mations.                                                                        | 50 |

| 30 | G.721 benchmark example of a static array                                       | 52 |

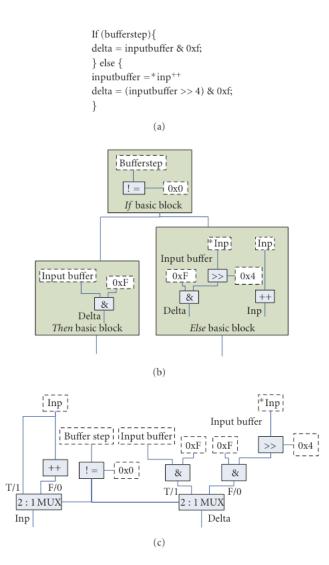

| 31 | Software code, CDFG, and DFG with predicated hardware example for control       |    |

|    | flow in ADPCM encoder.                                                          | 55 |

| 32 | Pseudo-code for parsing a SUIF expression class                                 | 57 |

| 33 | Pseudo-code for the predicating an <i>if-then</i> control flow structure        | 58 |

| 34 | Source Code for the G.721 Benchmark Kernel.                                     | 60 |

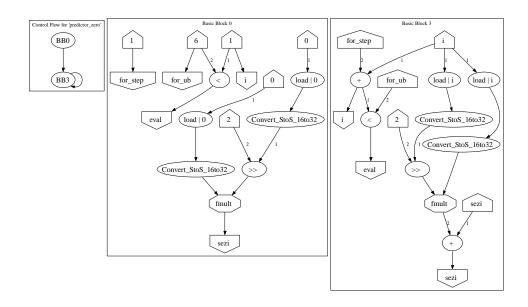

| 35 | CDFG for the <i>predictor_zero</i> Function of the G.721 Benchmark              | 61 |

| 36 | CDFG for the <i>fmult</i> Function of the G.721 Benchmark.                      | 62 |

| 37 | CDFG for the quan Function of the G.721 Benchmark                               | 63 |

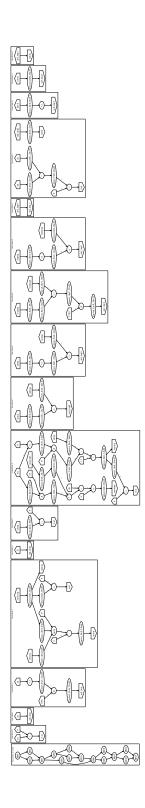

| 38 | CDFG for the Entire G.721 benchmark after Compiler Transformations              | 64 |

| 39 | SuperCISC compilation flow - Blue blocks represent added functionality               | 65 |

|----|--------------------------------------------------------------------------------------|----|

| 40 | Pseudo-code for top level hardware generation.                                       | 67 |

| 41 | Pseudo-code for Entity Declaration Parsing                                           | 68 |

| 42 | Pseudo-code for Architecture Declaration Parsing.                                    | 69 |

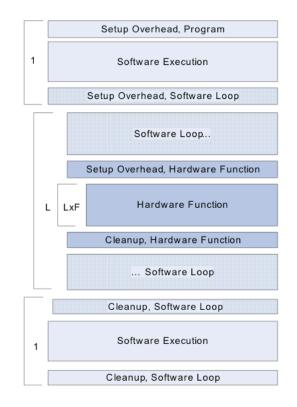

| 43 | Algorithm execution profile including potential overheads. In the VLIW pro-          |    |

|    | cessor with hardware functions, the hardware functions require no hardware           |    |

|    | specific setup overhead.                                                             | 71 |

| 44 | Software code and data flow graph (DFG) showing control flow in ADPCM                |    |

|    | encoder                                                                              | 72 |

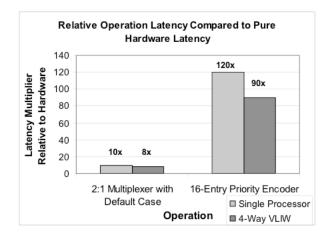

| 45 | Latency for software equivalent of 2:1 multiplexer and 16-entry priority encoder     |    |

|    | relative to hardware implementation                                                  | 73 |

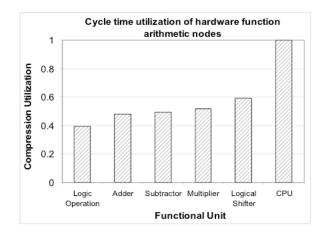

| 46 | Cycle time utilization of hardware function arithmetic nodes as normalized to        |    |

|    | the cycle time of a 167 MHz processor on an Altera EP2S180                           | 75 |

| 47 | Simple Source Code Marked for Hardware Creation.                                     | 76 |

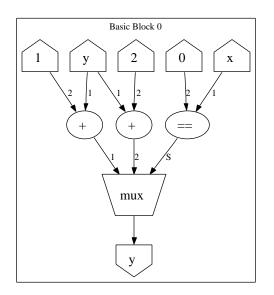

| 48 | CDFG for the Simple Source Code from Figure 47                                       | 76 |

| 49 | Generated VHDL for the Simple Source Code from Figure 47                             | 77 |

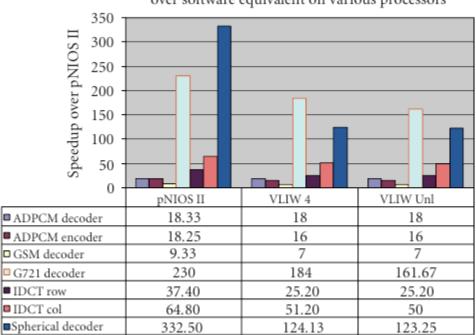

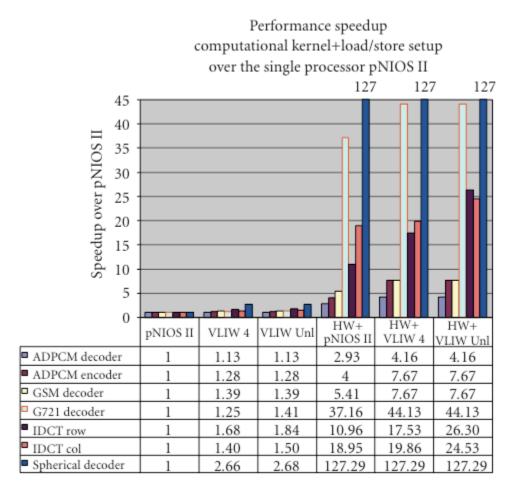

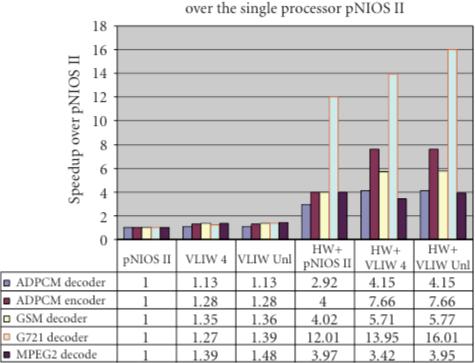

| 50 | Performance improvement from hardware acceleration of computational por-             |    |

|    | tion of the hardware kernel                                                          | 81 |

| 51 | Kernel speedups several architectures when considering required loads and            |    |

|    | stores to maintain the register file.                                                | 82 |

| 52 | Overall performance speedup of the entire application for several architectures      |    |

|    | including overheads associated with function calls.                                  | 83 |

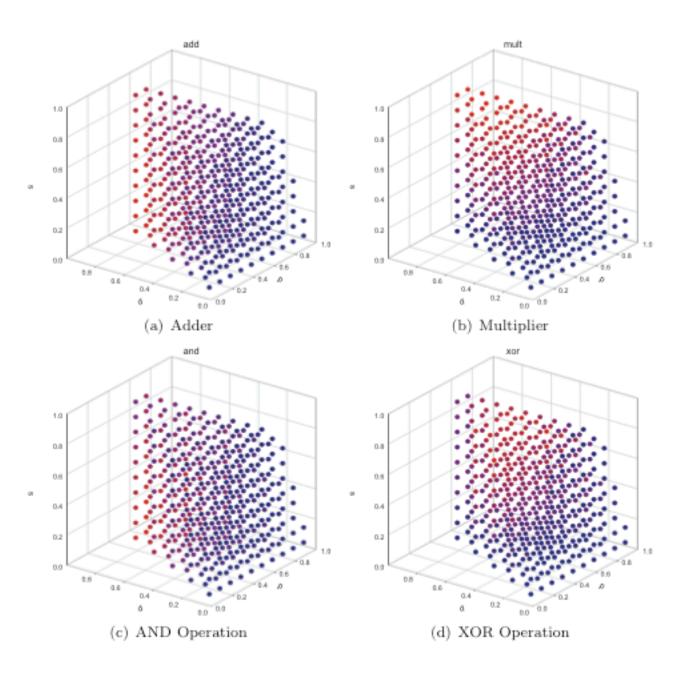

| 53 | 4-D plots of $p$ , $d$ , and $s$ versus power for several ALU operations synthesized |    |

|    | with standard cells for a 160nm OKI ASIC process. Power is indicated as a            |    |

|    | color between red and blue where solid blue represents the least power con-          |    |

|    | sumed by the device and red indicates the most power consumed by the device.         |    |

|    | Measurements taken at 0.1 intervals in each dimension $p, d, and s. \ldots$          | 86 |

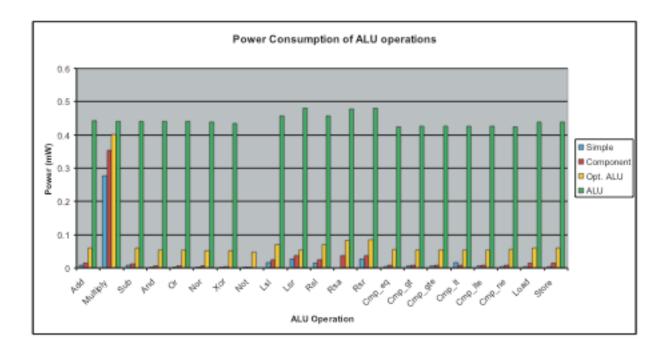

| 54 | Power profile of several different functional unit implementation techniques.        |    |

|    | Results for a standard cell 160nm OKI ASIC process.                                  | 88 |

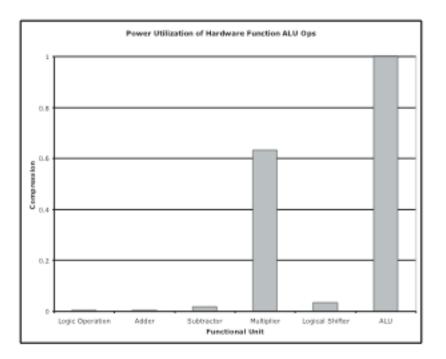

| 55 | Power compression of various classes of ALU operations                               | 90 |

| 56 | Power reduction shown with performance improvement for benchmark suite | 91 |

|----|------------------------------------------------------------------------|----|

| 57 | Energy improvement of SuperCISC over VLIW for benchmark suite          | 92 |

| 58 | Proposed Delay Element.                                                | 93 |

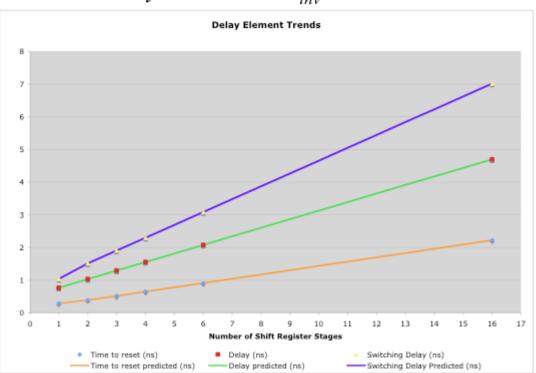

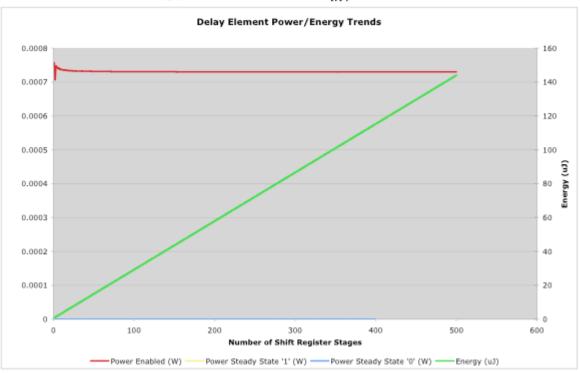

| 59 | Proposed Delay Element's Delay Function.                               | 94 |

| 60 | Proposed Delay Element's Power and Energy Cost.                        | 95 |

#### 1.0 INTRODUCTION

As demand for processing power increases, and fabircation technologies continue to increase transistor density, it is important to develop architectures that can leverage these transistor densities and provide increasingly high performance capability while satisfying progressively stricter power budgets.

Today, most current processor improvements revolve around increasing the size of the processing device. For example, a SIMD, Single Instruction Multiple Data, machine takes a single processing element and replicates the physical device many times. Then, the same instruction is executed on every logic unit. The operations remain independant by scheduling each processing unit to operate on different sets of data. Thus, complex data dependant operations can be completed with relative ease. This technique has been around for a long time and is used almost solely in vector processing calculations. Another technique, MIMD or Multiple Instruction Multiple Data, also takes the same core processing element and replicates the logic units. In this technique each of the instructions can be operated on independently. A MIMD machine behaves essentially like a multiprocessor system on a chip. The difficulty in creating these types of processor lies in the network connecting the logic units, and the ability to schedule instructions that are independent of each other for every processor.

The problem with SIMD and MIMD solutions is that up until now all of the thinking and development for the past forty years has been on software that will execute sequentially. Several large scale projects, such as the Intel Itanium 2 VLIW processor, have failed in the market due to the lack of ability to leverage the hardware resources and the increased cost of the processor. The compiler used to support the Itanium processor was not ready for release when the processor debuted and offered a poor performance increase over standard execution. In addition, software developers were required to release separate binaries to utilize the additional processing hardware. In order to circumvent this problem, another company, Transmeta, created a hardware wrapper that translates standard executable binaries into VLIW instructions on the fly. The concept relies greatly on the ability for the hardware to essentially recompile the code at runtime. The cost of the hardware translation increases the overall system cost, but Transmeta feels it is required to support legacy code.

Both of these projects, and many more attempt to utilize available transistors to increase performance. Another use for these available transistor that is being developed is an attempt to create custom hardware based on specific applications. This is not a new concept, some of the earliest main stream processors like the Intel 8086, for example, contained the ability to send data off the chip to a co-processor. The Intel 8087 was later developed to provide additional processing power. The 8087 added the capability to perform complex math operations operations, and floating-point operations up to fifty times greater than execution on the processor.

The concept of creating architectures with the ability to contain reconfigurable coprocessing units is being heavily researched. In the embedded market, processors are commonly developed for one or two applications. In order to meet timing constraints, some algorithms must be implemented entirely in hardware. The cost of custom hardware is much greater than the cost of executing an application on a processor. To counter this cost, hybrid systems that allow embedded processors to execute application specific hardware are being developed.

The subject of this thesis is a compilation and design automation flow for algorithms written in 'C'. Presented within are an architecture and a design flow that allow for the creation of application-specific hardware accelerated processors. Initially, investigations into the utilization of field programmable gate array, FGPA, resources led to the creation of large very long instruction word, VLIW, processors. After a design flow was created for the VLIW architecture it was found that many of the available resources were still not utilized. In order to increase the resource utilization, application-specific instructions were added to the processors. These custom instructions are mapped into available resources on the target FPGA. A compilation flow was created to automatically generate the hardware needed

for these custom instructions. The architecture was modified to contain a 4-wide VLIW reduced instruction set processor with the ability to execute super complex instructions. The encouraging performance results led to researching the use of standard cell application-specific integrated circuits (ASICs) as a target technology.

#### 1.1 MOTIVATION

Computer architects are always looking at different ways to improve overall processor speed. The current trend is to increase cache size, and add multiple processor cores to a single chip. One of the main reasons for this trend is that the current VLSI fabrication process has made it possible to place billions of transistor on a chip, however, current design tools limit the architects ability to use all of the available gates. In addition, as transistors scale to the tens of nanometers, effects such as clock skew and leakage power are becoming significant hurdles in processor design. Multi-core and large cache architectures allow designers the ability to create a single small design, or reuse an existing design, that contains only a small percentage of the total available gates on the chip. These designs can then be replicated many times on the chip. By treating each of the cores as a separate entities, with separate clock domains, the problem of clock skew becomes much more manageable.

There is no single correct solution to how the additional available resources should be used. Many proposals fail to make the mainstream due to lack to popular support. However, with the increasing size of the embedded computing market and the increasing use of custom processors, the need for high-level synthesis tools is increasing. The approach presented leverages the popular use of FPGA and ASIC targets for speeding up the critical areas of execution. It offers the designer the ability to specify the algorithm on the application level in C/C++ code with the ability to produce a system shown to exceed the performance of a standard VLIW processor.

#### 1.2 KEY CONTRIBUTIONS

To accelerate the sections of code executed in software a VLIW processor was created. The processor was designed to behave like the reduced instruction set Altera NIOS II processor. A single processor system was also developed along side this VLIW processor to benchmark the performance increase. In order to exercise the architectures, a compilation flow for the VLIW processor was developed. The system architect was consulted to extend the NIOS II instruction set for VLIW execution. When tested the VLIW architecture provided less than a 2X increase in performance on average.

In order to create automatically generated hardware functions, an intermediate representation, IR, friendly to the needed compiler transformations was required. A control and data flow graph (CDFG) framework provides both the combinational segments of execution, or data flow, and the control boundaries. The CDFG IR was coded within the SUIF2 compiler. After the front-end of the SUIF2 compiler completes, a built in control-flow pass is executed. From the sequential statements provided by the control flow, data flow graph are created. The IR is currently being used for two other academic projects, in addition to the compiler transformations for hardware generation.

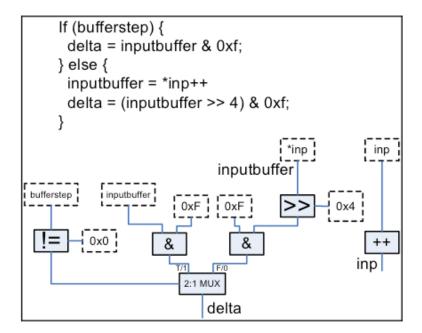

Data flow can be implemented in hardware very efficiently. On the other hand, control flow is suited very well for processor execution. To obtain a highly efficient architecture, the data flow of computational kernels is accelerated in application specific hardware. The looping and control flow structures are executed in the processor. To increase the amount of kernel code executing in hardware, a technique called predication was used to convert control flow to data flow. Hardware predication takes *if-then* and *if-then-else* control flow constructs and transforms them into data flow through the use of multiplexors. Other techniques, such as function inlining, and loop unrolling were also explored to eliminate control flow.

After a large section of data flow has been created for the computational kernel the last step is to translate the IR to a hardware description language. This translation is built into the compiler as a pass. This VHDL generation pass translates the compiler data structures into synthesizable VHDL. The VLIW architecture was modified to execute the generated hardware functions as a custom instruction in the processor. Data between the processor and hardware was shared through the processor's register file. The resulting architecture contains the VLIW processor and tightly coupled application specific hardware. The entire architecture was synthesized and tested for performance. The computationally intensive software kernels, which are typically called by the application many times, show an average increase in performance of 63X. Some benchmark kernels see improvements of over 300X. The entire application execution was also measured. The hardware accelerated VLIW processor showed performance speedups of 12X on average over a single processor implementation. The highest application speedup reached nearly 30 times the execution of the single processor setup.

The power required for processor execution is generally much higher than custom hardware for the same technology. This is contributed to the processor overhead of fetching, decoding, the ability to execute many operations, and write back. The processor was synthesized in a 160nm ASIC process and the benchmark kernels were analyzed for power. The result was compared to the same kernel's power for the generated hardware synthesized in the same 160nm ASIC process. The power requirements were compared, and the required energy was calculated based on the timing information from the ASIC synthesis. For the computational kernels the power improvement of the hardware execution is between just under 50X and over 400X with an average of just over 130X improvement. The energy improvement seen by the hardware execution combines the power efficiency and the decrease latency and therefore is several orders of magnitude lower for the hardware functions. The energy savings range from over 1,000X in the worst case to approximately 60,000X.

Chapter 2 describes the work related to the architecture and compilation design flow. The architecture is described in detail in Chapter 3. The intermediate representation created by the front-end of the compiler is detailed in Chapter 4. Chapter 5 discusses the transformations to the intermediate representation used by the compiler to produce a combinational data flow. Chapter 6 illustrates the conversion of the transformed intermediate code representation into a hardware description. The performance results of the architecture are presented in Chapter 7. Energy and power saving results are presented in Chapter 8. Finally, Chapter 9 describes the conclusion of the work and proposes areas suitable for future work.

#### 2.0 RELATED WORK

Manual hardware acceleration has been applied to countless algorithms and is beyond enumeration here. These systems generally achieve significant speedups over their software counterparts. Behavioral and high-level synthesis techniques attempt to leverage hardware performance from different levels of behavioral algorithmic descriptions. These different representations can be from hardware description languages (HDLs) or software languages such as C, C++, Java, and Matlab.

The HardwareC language is a C-like HDL used by the Olympus synthesis system at Stanford [1]. This system uses high-level synthesis to translate algorithms written in HardwareC into standard cell ASIC netlists. Esterel-C is a system-level synthesis language that combines C with the Esterel language for specifying concurrency, waiting, and pre-emption developed at Cadence Berkeley Laboratories [2]. The SPARK synthesis engine from the UC Irvine translates algorithms written in C into hardware descriptions emphasizing extraction of parallelism in the synthesis flow [3] [4]. The PACT behavioral synthesis tool from Northwestern University translates algorithms written in C into synthesizable hardware descriptions that are optimized for low-power as well as performance [5] [6].

In industry, several tools exist which are based on behavioral synthesis. The Behavioral Compiler from Synopsys translates applications written in SystemC into netlists targeting standard cell ASIC implementations [7] [8]. SystemC is a set of libraries designed to provide HDL-like functionality within the C++ language for system level synthesis [9]. Synopsys cancelled its Behavioral Compiler because customers were unwilling to accept reduced quality of results compared to traditional RTL synthesis [10]. Forte Design Systems has developed the Cynthesizer behavioral synthesis tool that translates hardware independent algorithm descriptions in C and C++ into synthesizable hardware descriptions [11]. Handel-

C is a C-like design language from Celoxica for system level synthesis and hardware software co-design [12]. Accelchip provides the AccelFPGA product, which translates Matlab programs into synthesizable VHDL for synthesis on FPGAs [13]. This technology is based on the MATCH project at Northwestern [14]. Catapult C from Mentor Graphics Corporation translates a subset of untimed C++ directly into hardware [15].

The difference between these projects and the technique presented is that they try to solve the entire behavioral synthesis problem. The presented approach utilizes a 4-wide VLIW processor to execute nonkernel portions of the code (10% of the execution time) and utilizes tightly coupled hardware acceleration using behavioral synthesis of kernel portions of the code (90% of the execution time). The available hardware resources were matched to the impact on the application performance so that the processor core utilizes 10% or less of the hardware resources leaving 90% or more to improve the performance of the kernels.

The synthesis flow presented utilizes a DFG representation that includes hardware predication: a technique to convert control flow based on conditionals into multiplexer units that select from two inputs from this conditional. This technique is similar to assignment decision diagram (ADD) representation [16] [17], a technique to represent functional register transfer level (RTL) circuits as an alternative to control and data flow graphs (CDFGs). ADDs read from a set of primary inputs (generally registers) and compute a set of logic functions. A conditional called an *assignment decision* then selects an appropriate output for storage into internal storage elements. ADDs are most commonly used for automated generation of test patterns for circuit verification [18] [19]. The technique presented is not limited to decisions saved to internal storage, which imply sequential circuits. Rather, the new technique applies hardware predication at several levels within a *combinational* (i.e., DFG) representation.

The support of custominstructions for interface with coprocessor arrays and CPU peripherals has developed into a standard feature of soft-core processors and those which are designed for DSP and multimedia applications. Coprocessor arrays have been studied for their impact on speech coders [20] [21], video encoders [22] [23], and general vector-based signal processing [24] [25] [26].

These coprocessor systems often assume the presence and interface to a general-purpose processor such as a bus. Additionally, processors that support custom instructions for interface to coprocessor arrays are often soft-core and run a significantly slower clock rates than hard-core processors. The VLIW-SuperCISC processor is fully deployed on an FPGA system with detailed post place-and-route performance characterization. Our processor does not have the performance bottleneck associated with a bus interconnect but directly connects the hardware unit to the register file. There is no additional overhead associated with calling a hardware function.

Several projects have experimented with reconfigurable functional units for hardware acceleration. PipeRench [27] [28] [29] [30] [31] and more recently HASTE [32] have explored implementing computational kernels on coarse-grained reconfigurable fabrics for hardware acceleration. PipeRench utilizes a pipeline of subword ALUs that are combined to form 32-bit operations. The limitation of this approach is the requirement of pipelining as more complex operations require multiple stages and, thus, incur latency. In contrast, by using non-clocked hardware functions that represent numerous 32-bit operations. RaPid [33] [34] [35] [36] [37] is a coarse-grain reconfigurable datapath for hardware acceleration. RaPid is a datapath-based approach and also requires pipelining. Matrix [38] is a coarse-grained architecture with an FPGA like interconnect. Most FPGAs offer this coarse-grain support with embedded multipliers/adders. The presented approach, in contrast, reduces the execution latency and, thus, increases the throughput of computational kernels.

Several projects have attempted to combine a reconfigurable functional unit with a processor. The Imagine processor [39] [40] [41] combines a very wide SIMD/VLIWprocessor engine with a host processor. Unfortunately, it is difficult to achieve efficient parallelism through high ILP due to many types of dependencies. The presented processor architecture differs as it uses a flexible combinational hardware flow for kernel acceleration.

The Garp processor [42] [43] [44] combines a custom reconfigurable hardware block with a MIPS processor. In Garp, the hardware unit has a special purpose connection to the processor and direct access to the memory. The Chimaera processor [45] [46] combines a reconfigurable functional unit with a register file with a limited number of read and write ports. The new system differs as it uses a VLIW processor instead of a single processor and the hardware unit connects directly to all registers in the register file for both reading and writing allowing hardware execution with no overhead. These projects also assume that the hardware resource must be reconfigured to execute a hardware-accelerated kernel, which may require significant overhead. In contrast, the new system configures the hardware blocks prior to runtime and uses multiplexers to select between them at runtime. Additionally, the new system is physically implemented in a single FPGA device, while it appears that Garp and Chimaera were studied in simulation only.

In previous work, a 64-way and an 88-way SIMD architecture was created and interconnected the processing elements (i.e., the ALUs) using a hypercube network [47]. This architecture was shown to have a modest degradation in performance as the number of processors scaled from 2 to 88. The instruction broadcasting and the communication routing delay were the only components that degraded the scalability of the architecture. The ALUs were built using embedded ASIC multiply-add circuits and were extended to include user-definable instructions that were implemented in FPGA gates. However, one limitation of a SIMD architecture is the requirement for regular instructions that can be executed in parallel, which is not the case for many signal processing applications. Additionally, explicit communications operations are necessary.

Work by industry researchers [48] shows that coupling a VLIW with a reconfigurable resource offers the robustness of a parallel, general-purpose processor with the accelerating power and flexibility of a reprogrammable systolic grid. For purposes of extrapolation, the cited research assumes the reconfiguration penalty of the grid to be zero and that design automation tools tackle the problem of reconfiguration. The presented system differs because the FPGA resource can be programmed prior to execution, giving us a more realistic reconfiguration penalty of zero. A compiler and automation flow to map kernels onto the reconfigurable device is also provided [49].

#### 3.0 VERY LONG INSTRUCTION WORD PROCESSORS

VLIW (Very Long Instruction Word) processors gained their name from the fact that each instruction word is used to program multiple execution units and therefore requires many bits. By definition, a VLIW processor is able to independently execute on two or more instructions simultaneously. The execution units in VLIW processors have historically been based on the design of a simple processor. These processors are then replicated, typically four to eight times, and placed onto a single chip, essentially creating a multiprocessor system on a chip. In contrast to a traditional superscalar processor in which logic is added to the processor to execute more complex instructions, a VLIW processor uses its multiple execution units to decompose complex instructions and execute the simple instructions in parallel.

Section 3.1 details the design of a VLIW processor's architecture developed by another student, and a mapping on a VLIW processor onto a FPGA (Field Programmable Gate Array). Section 3.2 describes the compiler flow for the VLIW architecture. The results of the VLIW processor can be found in section 3.3.

#### 3.1 A VLIW/SIMD FPGA PROCESSING ARCHITECTURE

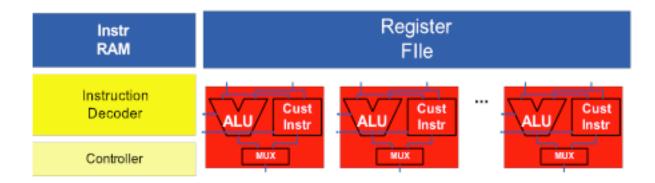

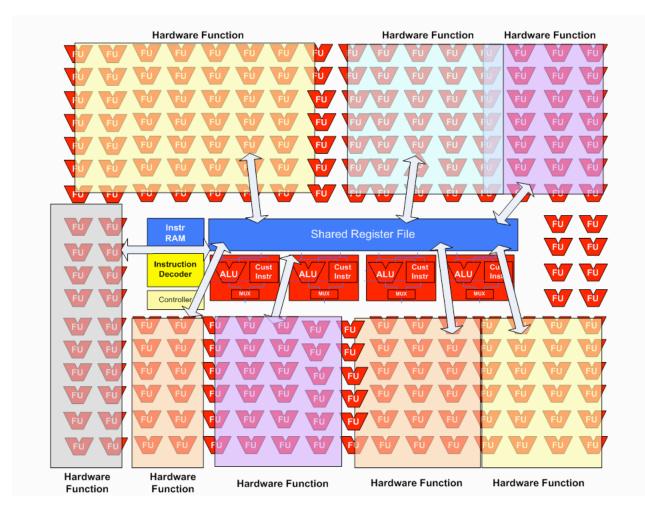

In order to examine the scalability of a VLIW architecture for FPGAs, a VLIW architecture was developed and synthesized. The architecture created is shown in Figure 1, the wider instruction stream and the shared register file scale with the size of the VLIW processor. The ALUs (also called processing elements PEs) are identical to that of a single processor VLIW or a stand-alone processor. Rather than having a single instruction executed each

Figure 1: Very Long Instruction Word Architecture.

clock cycle, a VLIW can execute P operations for a P processor VLIW. In this section, the architecture developed in primary by Dara Kusic is detailed, the scalability of each of its components is described.

The VLIW processor array consists of 32-bit processors with a shared register file. The processors are identical in architecture and fully supportive of the RISC instruction set of the NIOS II soft-core processor. Exploitation of the available width of the VLIW architecture relies on the VLIW compiler to concurrently schedule data-independent sequential operations. The system implements a five-stage instruction cycle consisting of instruction fetch, operand fetch, two execute cycles and a writeback stage.

The processing element supports four types of 2-operand arithmetic operations: add/subtract, multiply, logic operations, and shift. The latency of each operation is listed in Table 1. ALU functionality can be augmented for digital signal processing and multi-media applications by implementing custom instructions through utilization of an expanded opcode and digital signal processing blocks for multiply-accumulate operations.

Processor operations are grouped into L operations (multiply, add/subtract, logical, shift, etc). Within each ALU, each of the L operations executes concurrently using separate function units. A multiplexer then selects between the L 32-bit function unit outputs and feeds the result back into the register file. It was noted that there is a wide range of performance for the individual function units and that the size of L has an impact on the

| ALU Module                  | Clock      | Latency             |

|-----------------------------|------------|---------------------|

| Adder/Subtractor/Comparator | 156.62 MHz | $6.38 \mathrm{~ns}$ |

| 2-Operand Mulitplier        | 108.52 MHz | $9.21 \mathrm{~ns}$ |

| Logical Unit (AND/OR/XOR)   | 108.52 MHz | $2.37 \mathrm{~ns}$ |

| Variable Left/Right Shifter | 216.68 MHz | $4.61 \mathrm{~ns}$ |

| Top ALU (4 Modules Above)   | 102.07 MHz | $9.80 \mathrm{~ns}$ |

Table 1: Performance of Instructions (Altera Stratix II FPGA EP2S180F1508C4)

overall ALU performance. By grouping the function units together, the size of the multiplexer can be reduced down to a 4-to-1 at a loss of only 6 MHz.

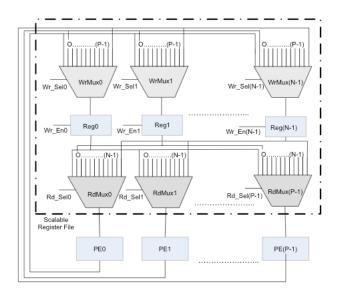

The gains offered by a VLIW supporting a large instruction set come at a price to the performance and area of the design. The number of ports to the shared register file, Figure 2 and instruction decode logic have shown to be the greatest limitations to VLIW scalability.

Multiplexing breadth and width pose the greatest hindrances to clock speed in a VLIW architecture. The effect of multiplexers was studied by charting the performance impact of increasing the number of ports on a shared register file, an expression of increasing VLIW width.

For the *P*-processor VLIW with an *N*-element register file, the multiplexers function as routers, as shown in Figure 2. For write operations, each of the *N* registers requires a 32-bit *P*-to-1 multiplexer as data can come from any processor. For read operations, each of the *P* ports requires a 32-bit *N*-to-1 multiplexer as each processor can read from any of the *N* registers.

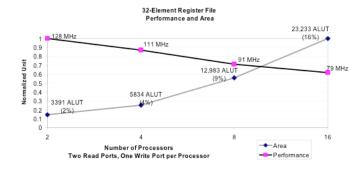

In Figure 3, the number of 32-bit registers is fixed to 32 and the number of processors is scaled. For each processor, two operands need to be read and one written per cycle. Thus, for P processors there are 2 P read ports and P write ports. The register file lost an average of 16 MHz and gained an average of 2x area utilization per processor doubling. At 16 processors, 16% of the FPGA is utilized and the clock frequency is 79 MHz.

Figure 2: N-element Register File Supporting P-Wide VLIW with P Read Ports and P Write Ports.

Figure 3: Scalability of a 32-element register file with 2 read and 1 write port per processor for a Stratix II .

Figure 4: Scalability of an N-element register file having N read and N write ports on an Altera Stratix II.

Figure 4 shows results of scaling both the number of read/write ports and the number of 32-bit registers. In this case, the register file lost an average of 39 MHz and gained an average of 3x area utilization per doubling of the PEs, read/write ports and register file elements. An *ALUT* contains one register and combinational logic; a Stratix II EP2S180 contains 143,520 ALUTs.)

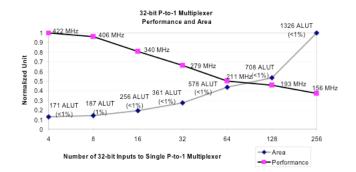

The multiplexer is the most elemental design unit contributing to performance degradation of the register file as the VLIW scales. The next step was to measure the impact of a single 32-bit P-to-1 multiplexer on the Stratix II EP2S180. As the width, P, doubled, the area increased by a factor of 1.4x. The performance took the greatest hit of all the scaling tests, losing an average of 44 MHz per doubling. This can be seen in Figure 5. The performance detriment naturally furthers as the number of P-to-1 multiplexers multiplies to serve as read and write ports to the register file.

The multiplexed data routing system of the register file was replaced by a crossbar architecture resembling a 2-D switched array. The crossbar architecture offered no clear advantage over the multiplexed architecture in terms of either area or performance. The decision was made to retain the multiplexed routing system in favor of its scalability with respect to the VHDL design process.

The second most significant performance bottleneck is the instruction decoder that translates opcodes into control signals. The decoder can be implemented as either combinational

Figure 5: Scalability of a 32-bit P-to-1 multiplexer on an Altera Stratix II (EP2S180F1508C4).

logic, as a ROM, or as a RAM. Table 2 shows the resulting area and performance for an Altera NIOS II decoder that was created. This section was accepted for publication, for further review see [50].

Table 2: Performance data of 3 implementations of VLIW instruction decoder on an Altera

Stratix II

| Decoder Type                   | ALUTS | %Area | Clock      | Latency             |

|--------------------------------|-------|-------|------------|---------------------|

| Decoder - ROM                  | 174   | < 1   | 344.23 MHz | 2.90  ns            |

| Decoder - RAM (11-bit address) | 6630  | 4     | 124.16 MHz | 8.05  ns            |

| Decoder - Combination Logic    | 1,192 | < 1   | 108.85 MHz | $9.19 \mathrm{~ns}$ |

## 3.2 COMPILER FLOW FOR A VLIW/SIMD FPGA PROCESSING ARCHITECTURE

To execute software code on the architecture described in section 3.1, a compilation flow was developed. The input to the flow is C code. The code is read into the compiler and scheduled into instructions that can be performed in parallel. The final result is machine code that can be executed on the VLIW FPGA processor.

Trimaran [51] is an open source VLIW compiler based on the IMPACT [52] front-end and the ELCOR [53] back-end. Trimaran uses a machine description language that allows the used to specify changes in the target architecture. The ELCOR back-end was developed to target the Hewlett-Packard HPL-PD family of processors. Third-party back-ends exist to target other architectures. Triceps [54] is a Trimaran back-end to target the StrongARM processor, and Tritanium [55] is available to target the Intel Itanium series of processors.

Trimaran was selected as a framework for the VLIW FPGA compiler. Trimaran was chosen because it is an open source, extensible VLIW compiler. It contains separate frontend and back-end code and code that translates the intermediate representation, IR, between the two. Trimaran was also chosen because the projects mentioned above serve as examples of how to modify the code generation for different processor targets.

The complete compilation flow can be seen in Figure 6 below. Only the Trimaran backend was modified, the front-end, IMPACT, remained unchanged. The back-end was changed to target the VLIW NIOS II processor from the IMPACT IR. Much of the existing Trimaran code was reused to accelerate development time. An assembler to translate the assembly code into a ROM file was primarily written by Ahmed Muaydh. The assembler generates very long instruction words, and therefore must add idle operations for processors when no instruction is scheduled in the assembly. Figure 7 shows an example of four instructions and their instruction word.

The NIOS II back-end is closely coupled to code from the ELCOR back-end. Only changes that were required for the VLIW NIOS II machine were made. The back-end is responsible for instruction scheduling, register allocation, and code generation. The ELCOR back-end was capable of scheduling several instruction that were not supported by the RISC

Figure 6: Compilation Flow Blue blocks represent added functionality.

| add.0 r7, r5, r6  |                     |          |          |  |  |

|-------------------|---------------------|----------|----------|--|--|

| sub.1 r10, r8, r9 |                     |          |          |  |  |

|                   | slli.2 r12, r11, #5 |          |          |  |  |

|                   | ldw.3 r14, 24(r13)  |          |          |  |  |

| 0x314f883a        | 4a15c83             | 5818917a | 6b800617 |  |  |

Figure 7: VLIW ROM file format.

NIOS II architecture. In this case, these instructions were decomposed into multiple NIOS II instructions. To adjust the scheduling instructions that were decomposed were given a higher instruction latency in the Trimaran machine description. Another change was the removal of support for predication. The VLIW NIOS II architecture does not support predication thus the ability to use this hardware feature was removed. Another example of the changes to ELCOR was the adaption of a floating-point module from the Triceps project to allow floating-point execution to be modified into a fixed-point implementation.

In Figure 7 there is an example of generated assembly code. Each Nios II instruction has been appended with an ID number corresponding to the processing element it has been scheduled on. In the example, these four instructions have been scheduled for the same cycle because they occur in order, from the lowest ID to the highest ID. The assembler translates each instruction to its binary format from the NIOS II specification. The instructions scheduled for the same cycle are then concatenated and combined with the FPGA ROM format to produce a file that can be read into the FPGA.

#### 3.3 RESULTS

The Trimaran compiler was used to investigate the Instruction Level Parallelism (ILP) of several benchmarks. The compiler generates scheduled VLIW assembly code. From the assembly code, the frequency how many of the processing elements in the VLIW processor are being used every cycle can be inspected. Trimaran is able to output the IPL from the source code.

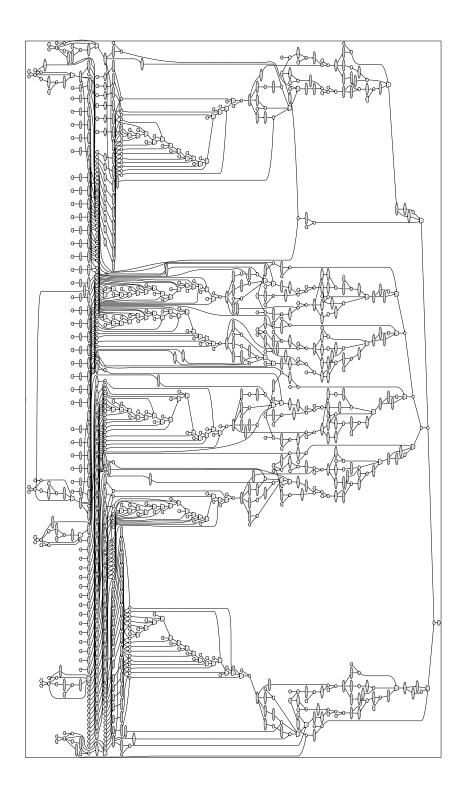

Figure 8 is an example of a cycle-by-cycle view within Trimaran. A yellow block indicates the start of a basic block; a segment of code that contains only sequential execution from start to finish, or in other words, contains no looping or branching. Within each basic block, a row represents a clock cycle. Each of the blocks to the right side of the clock cycle indicate instructions that are scheduled for execution in that clock cycle. For example, in clock cycle 0 of basic block 4, there are eight instructions scheduled for execution. In the next cycle, there are only three instructions, and in the third cycle zero instructions are scheduled.

Figure 8: Cycle-by-Cycle visual representation of an FIR filter generated by Trimaran.

Trimaran was designed to target different Hewlett-Packard processors, and thus gives the user the ability to change many of the target processor's features. Trimaran uses a machine description to allow the user to specify register file sizes, number of functional units, individual instruction latency, and more. Changes to these parameters in the machine description allowed the tradeoffs in section 3.1 to be evaluated.

The benchmarks, ADPCM encoder and decoder, MPEG2 encoder and decoder, and an FIR filter were chosen to be examined to detect their ILP by Trimaran. The ADPCM benchmark was choose because of its control oriented execution, the MPEG2 benchmark was chosen because of its data oriented execution, and the FIR filter was chosen as a combination of both control and data flow.

ILP results for two different types of processors were generated. The first architecture was a 4 processing element VLIW with 2 memory ports. The results were compared to an architecture with 100 processing elements and memory ports. The results, seen in Figure 9, show that the average ILP for both architectures is less then 2. Therefore, VLIW architectures with many processing elements will have a low overall utilization, leaving most of the processing elements idle.

Upon examining the cycle-by-cycle output, Figure 8, it can be seen that there are cycles where many processing elements are idle. Both architectures that were studied were given a 2 cycle access time to main memory. In cycle 2 of Figure 8, all of the processors are idle. This

Figure 9: Average IPL of Banchmarks.

is because of a memory overhead. In the following cycle, 3, there is only a single processing element being used. Typically, this means that the instruction that is executing in cycle 3 had a data dependance from one of the instructions in cycle 1. These Data dependancies are one of the chief restrictions of ILP, but there are also several other factors that can limit it.

The scaling tradeoffs presented in Section 3.1 and the ILP limitations presented above indicate that replicating processing elements in a VLIW architecture has very strict limitations. The average ILP of the benchmarks profiled was 2. Therefore, even though the capability of placing up to 64 processing elements in the VLIW architecture within the target Altera Stratix II FPGA is available, many of the resources would never be used. The above results were accepted for publication [50] and provided the initial groundwork for the research described in the following chapters.

#### 4.0 CONTROL AND DATA FLOW GRAPHS

This chapter provides details of control flow graph, CFG, creation, data flow graph, DFG, creation, and control and data flow graph, CDFG, creation. A control flow package is included as part of the SUIF2 [56] compiler framework's package. Section 4.1 describes the use of the existing control flow package and the extensions added for the purpose of CDFG creation. Section 4.2 describes the SUIF extension that was written to create DFGs. The final goal was to produce a CDFG framework that provides a interface to explore automatic hardware generation. The results of the CDFG generation are found in section 4.3 below. This work is based on the creation of similar graphs used for hardware synthesis; details can be found in [1].

#### 4.1 CONTROL FLOW

The SUIF2 compiler framework was created to support collaborative research in optimizing and parallelizing compilers. Initially, the project included the ability to convert C and C++ files into and out of the SUIF file format, and the ability to do some simple code transformations. Since it was first released many academic and industry projects have created extensions to the framework, which SUIF defines as passes. Since the initial release, the SUIF group has released an add-on package that includes a dead code solver, a data flow solver, and a control flow graph builder.

To build a control flow graph using the extra SUIF package is trivial once the package has been installed. First, the source code is converted into the SUIF2 format. Means for the conversion are provided by the compiler. Figure 10 shows the commands required for [examples]\$

[examples]\$scc -.spd example1.c

[examples]\$porky -defaults example1.spd example1.porky

[examples]\$suif1to2 -o example1.suif example1.porky

Warning duplicate cached types PointerType

[examples]\$

Figure 10: Example showing the commands used to convert from C source to a SUIF2 file format.

converting a C source file into the SUIF2 format. This method uses the SUIF1 front-end and converts the SUIF1 AST into SUIF2 format.

The scc command in Figure 10 calls the SUIF1 front-end and creates a SUIF1 AST from the C source. According to the man page, the porky command is "to be used right after the front end, to turn some non-standard SUIF that the front end produces into standard SUIF. It also does some things, like constant folding and removing empty symbol tables, to make the code as simple as possible without losing information." The final command, suif1to2, converts a SUIF1 AST to a SUIF2 AST.

The SUIF1 front-end is used because the SUIF2 front-end is closed source and is copyright The Portland Group Inc. and Edison Design Group Inc. The PGI front-end does not preserve compiler directives, such as #pragma, during the conversion to the SUIF2 AST. Later in section 5.1 these compiler directives will be used.

Figure 11 shows an example of the commands used to create a control flow graph. The first step is to execute the SUIF2 framework binary, suifdriver. Next, the control flow pass is loaded into memory, followed by the SUIF source file. The control flow pass can now be run. The pass will annotate each SUIF source code line with a unique ID number to identify its location in the control flow graph. The pass will also annotate the top level procedure structure with a list of all of the control graph nodes and a list of successors. Each control flow graph node data structure contains a list of its parents, a list of its successors, and a pointer to the SUIF data structure containing the translated source code.

```

[examples]$

[examples]$suifdriver -e "

import suif_cfgraph;

load example1.suif;

print_suif_cfgraph_to_dot;

" > example1.dot

[examples]$dot -Tps -o example1.ps example1.dot

[examples]$

```

Figure 11: Example showing the commands used to execute the SUIF control flow graph pass.

The control flow graph pass includes two output options, a human readable text format, and a dot format graph which can be parsed with the unix tool dot to create a visual representation of the graph. During the execution of the control flow graph pass in Figure 11, the output was piped to a file. This file contains the dot text representation of the control flow graph. The dot command was used to create a postscript file containing the visual representation of the graph.

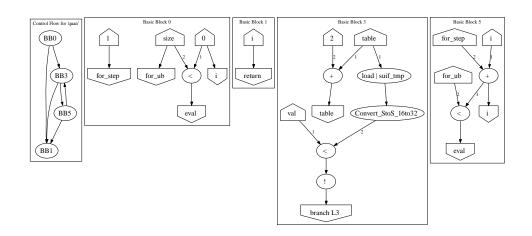

Figure 12(a) shows a simple C source code. The C source has been converted into the SUIF2 format and the control flow graph pass was executed on it. Figure 12(b) shows the corresponding control flow graph, that has been generated using the dot tool.

Control flow graphs that are produced from the SUIF pass are modified into a format that allows for easy control and data flow graph creation. Each block in Figure 12(b) represents a control flow graph node. The CDFG representation has to clearly define the differences in control flow and data flow. To do this, basic blocks are created. A basic block is a term used to define a block of code that contains only one control flow input, and only one control flow output. Therefore, the interior of a basic block is strict data flow.

Figure 14 shows the pseudo-code used to convert the CFG blocks into basic blocks. In the function, a list of all nodes that are identified as the beginning of a basic block is kept. The function initializes the list to contain the top node in the graph. A loop completes after there are no more nodes in the list. This loop calls the function, *create\_basic\_blocks\_helper*,

Figure 12: C source and generated CFG for a simple example.

Figure 13: CFG of basic blocks for a simple example.

which checks nodes to see if they should be added to this basic block or the list of starting nodes. The helper function can be seen in Figure 15.

The basic block object is created in *create\_basic\_blocks\_helper*. Figure 15 details the creation of the basic block and how nodes are added to it. After the block is created the algorithm checks to see if it is at the end of the graph. If the node has only one control flow input and only one control flow output it is added to the basic block and the algorithm continues on the successor. If the node has two or more outputs, it belongs to the current basic block, and all of its outputs are added to the starting node list. If the node has two or more predecessors, there is a control flow break before the node. In this case, the node is not added to the basic block. The node with multiple inputs is then added to the starting nodes list if it has not previously been added. This function returns after there is a break in the control flow and nodes are added to the starting nodes list.

Figure 13 depicts the control flow graph of the example code from Figure 12(a). Here, the *if-then-else* statement creates a control flow branch from basic block 0. The path along basic block 1 represents the *if* condition. The path through basic block 2 represents the *then* condition. The two paths converge in basic block 3, after all of the statements in both cases are completed.

```

//list of nodes that are the first node of a basic block

list startNodes

create_basic_blocks(the_graph) {

//give each basic block a UID

int uid = 0;

//get the first node in the graph

firstNode = the_graph->get_node_iterator()

//add the first node to the list of start nodes

startNodes.add(firstNode);

while(startNodes is not empty) {

//get the first node in the list

node = startNodes.first();

//call the function to create the basic block

create_basic_blocks_helper(the_graph, node, uid);

//remove the node from the list

startNodes.remove(node);

i++;

}

}

```

Figure 14: Pseudo-code to call the function to create basic blocks, based on the starting nodes for each basic block.

## 4.2 DATA FLOW

After the control flow has been completed, the basic blocks that were created contain only data flow. Each basic block contains a list of ordered sequential statements which corresponds to the source code. In order to create a data flow graph for each basic block, the statements are parsed. Each executable SUIF statement is translated into multiple data flow graph nodes. At this point, the CDFG AST is completed and is independent of the SUIF2 AST.

In order to parse the statements an understanding of the SUIF data structures must be attained. In the SUIF AST any object that executes is called an *ExecutionObject*. Each node from the original control flow graph that SUIF creates, as seen in Figure 12(b), contains a pointer to an *ExecutionObject*. The *ExecutionObject* class is an abstract class with two subclasses, *Statement* and *Expression*. Both of these classes are also abstract and contain many subclasses. Each control flow graph node's *ExecutionObject* corresponds to a *Statement* class because each node contains an executable line of source code. Table 3 lists the subclasses of the *ExecutionObject* class.

#### 4.2.1 The *statement* class

The data flow pass parses the statements based on their individual fields. Figure 16 shows a segment of the algorithm used to parse the *statement* class. First the algorithm must identify which type of statement it is parsing. Each statement is parsed in a different manner, based on its data structures. The *StoreVariableStatement* example from the figure contains a pointer to a variable symbol, the symbol is translated into a  $cdfg_node_var$  object. The statement also contains an expression. The result of the expression is stored into the variable. This is represented in the DFG by a line from the  $cdfg_node_var$  to the node created from the expression object.

```

create_basic_blocks_helper(the_graph, node, uid) {

//create the basic block

new bb(uid);

while(true) {

//Get the successors and predecessors

out = the_graph->get_successors(node);

in = the_graph->get_predecessors(node);

if (there are successors)

//move to the first one

out.increment();

} else {

//if there are no sucessors, at end of the basic block

break;

}

if (there are predecessors)

//move to the first one

in.increment();

}

if(there are no more successors AND

there are no more predecessors) {

//this is a node with only one input and output

bb->add_node(node);

//get the predecessor and loop

out.reset();

node = out.get();

} else {

//check to see if there is more then one successors

if(there are more successors) {

//add the node to the basic block. Node has multiple outputs and belongs to this bb

bb->add_node(node);

out.reset();

if (the successors have not been added as startNodes)

//get the successors and add them

while(there are more successors) {

node = out.get();

startNodes.add(node);

out.increment();

}

}

}

if(there are more predecessors) {

//Node has multiple inputs and doesn't belong to this bb

if(the node has not been added as startNodes) {

startNodes.add(node);

}

}

//all possible paths are covered and

break;

}

}

}

```

Figure 15: Pseudo-code to create the basic blocks, and identify the new starting nodes for basic blocks.

| Statement                               |                                      |                          |

|-----------------------------------------|--------------------------------------|--------------------------|

| 200000000000000000000000000000000000000 | Compound statements                  |                          |

|                                         |                                      | StatementList            |

|                                         |                                      | ScopeStatement           |

|                                         | High Level Control Flow Statements   | Scopestatement           |

|                                         | lingh Lever control I low Statements | IfStatement              |

|                                         |                                      | WhileStatement           |

|                                         |                                      | DoWhileStatement         |

|                                         |                                      | ForStatement             |

|                                         | Simple Control Flow Statements       | ForStatement             |

|                                         | Simple Control Flow Statements       | BranchStatement          |

|                                         |                                      |                          |

|                                         |                                      | MultiWayBranchStatement  |

|                                         |                                      | JumpStatement            |

|                                         |                                      | JumpIndirectStatement    |

|                                         |                                      | ReturnStatement          |

|                                         |                                      | LabelLocationStatement   |

|                                         | Computational statements             |                          |

|                                         |                                      | StoreStatement           |

|                                         |                                      | StoreVariableStatement   |

|                                         |                                      | CallStatement            |

|                                         |                                      | EvalStatement            |

|                                         | VarArgs                              |                          |

|                                         | Pseudo-Statements                    |                          |

|                                         |                                      | MarkStatement            |

| Expression                              |                                      |                          |

|                                         | Constant                             |                          |

|                                         | BinaryExpression                     |                          |

|                                         | UnaryExpression                      |                          |

|                                         | SelectExpression                     |                          |

|                                         | Load Expressions                     |                          |

|                                         | 1                                    | SymbolAddressExpression  |

|                                         |                                      | LoadExpression           |

|                                         |                                      | LoadVariableExpression   |

|                                         |                                      | LoadValueBlockExpression |

|                                         | Data Structure Access Functions      |                          |

|                                         |                                      | ArrayReferenceExpression |

|                                         |                                      | MultiDimArrayExpression  |

|                                         |                                      | FieldAccessExpression    |

|                                         |                                      | rieiuAccessiixpression   |

| Table 3: | The | ExecutionObject | subclasses. |

|----------|-----|-----------------|-------------|

|----------|-----|-----------------|-------------|

```

void parse_statements(execution_object eo){

//Find the statement type

if (is_kind_of<BranchStatement>(eo)) {

. . .

} else if (is_kind_of<CallStatement>(eo)) {

. . .

}

. . .

else if (is_kind_of<StoreVariableStatement>(eo)) {

//Convert to the type

StoreVariableStatement *stmt = to<StoreVariableStatement>(eo);

//Get the variable that is stored to

VariableSymbol *var = stmt->get_destination();

String varString = var->get_name();

//check to see if the variable has been used

int i = _uidmap->get_id(varString.c_str());

if(i == -1) {

//the variable has not been used, initialize the version tracker

i = 0;

_uidmap->set(varString.c_str(),0);

} else {

//increment the version tracker

_uidmap->set(varString.c_str(),i++);

}

//keep the id to later check if the same var is being read and written

_varid = i;

//store statements should always create new nodes

cdfg_node_var *op = new cdfg_node_var(i, varString.c_str());

//parse the right hand side of the statement

cdfg_base *cb = parse_expressions(stmt->get_value());

}

. . .

else {

assert(false);

}

}

```

Figure 16: Pseudo-code for parsing a SUIF statement class.

# 4.2.2 The *expression* class

Each *statement* class typically has at least one embedded expression class. Expression classes can also have embedded expressions. The *expression* class is parsed in much the same way as the *statement* class. The expression parser is called first from the statement parser, and then it may be called recursively. Figure 17 shows a selection from the expression parsing algorithm. Like the statement parser, once the type of expression is determined CDFG nodes are created and linked to each other based on the expression's data structure.

The *BinaryExpression* class contains an operation and two source operands, which are *expression* classes. A  $cdfg_node_binary$  class is created and the type is set to the *BinaryExpression* classe's type. Next, the first source operand is sent to the expression parser. The expression parser will return a pointer to a CDFG node. This returned value will be stored as the first operand to the binary expression. The process is repeated with the second source expression.

## 4.2.3 The CDFG node class

The control and data flow pass creates CDFG node data structures to translate the SUIF objects into a data flow graph. The CDFG node data structures were created to be object oriented. The class structure for each of the nodes can be seen in Table 4. The root abstract class,  $cdfg_base$ , contains a unique id integer for each node, and a string value. The base node also contains methods that each child class must declare, such as a print method, and a node type identifier.

A *cdfg\_node\_input* is created when an expression is parsed and the variable has not yet been defined. The *cdfg\_node\_const* declares a special type of input node, a constant value. A constant input in created when the SUIF expression *Constant* is parsed.

When a variable node is defined, see Figure 16 for the *Store VariableStatement* example, a  $cdfg\_node\_var$  is created. Variable nodes are often removed from the data flow graph because temporary variables between operation nodes are not required for data flow. The option to keep variable nodes in the graph has been added to show a correlation between the source

```

void parse_expressions(expression expr){

if (is_kind_of<ArrayReferenceExpression>(expr)) {

. . .

} else if (is_kind_of<BinaryExpression>(expr)) {

//Convert to the type

BinaryExpression *ex = to<BinaryExpression>(expr);

//Find the binary type

LString lstr = ex->get_opcode();

String str = String(lstr);

char *op_char = new char[20];

type binary_type;

if (lstr == k_add) {

op_char = " + ";

binary_type = add_type;

} else if (lstr == k_multiply) {

op_char = " * ";

binary_type = multiply_type;

} else if (lstr == k_subtract) {

op_char = " - ";

binary_type = subtract_type;

} else if (lstr == k_divide) {

op_char = " / ";

binary_type = divide_type;

}

. . .

else {

assert(false);

}

//Find the precision and sign

DataType *dtype = ex->get_result_type();

bool sign;

int precision;

get_info(dtype, &sign, &precision);

//Create the node

cdfg_node_binary *op = new cdfg_node_binary(_idmap->get_new_id(op_char), op_char, sign);

//Parse the first source

cdfg_base *cb = create_op_expr(ex->get_source1());

op->set_first(cb);

//Parse the second source

cb = create_op_expr(ex->get_source2(), cnode);

op->set_second(cb);

return op;

}

. . .

else {

assert(false);

}

}

```

Figure 17: Pseudo-code for parsing a SUIF expression class.

| cdfg_base |                 |                 |                  |               |

|-----------|-----------------|-----------------|------------------|---------------|

|           | cdfg_node_input |                 |                  |               |

|           |                 | cdfg_node_const |                  |               |

|           | cdfg_node_var   |                 |                  |               |

|           |                 | cdfg_node_call  |                  |               |

|           |                 | cdfg_node_unary |                  |               |

|           |                 |                 | cdfg_node_binary |               |

|           |                 |                 |                  | cdfg_node_mux |

Table 4: The CDFG node data structures.

code and the CDFGs. At the time of the parsing, each variable node contains a list of control flow nodes that contains that nodes uses. In a post processing pass, the variable nodes that are defined within the basic block and used outside of the basic block are marked as output nodes. Detecting uses is done by using the SUIF2 reaching definitions package and an upwards use solver that was developed to determine the liveness of any variable. Variable nodes are represented as boxes in the visual representation.

Operations in the SUIF structure are defined as either the UnaryExpression class or the BinaryExpression class. The type of expression is extracted either a cdfg\_node\_unary or cdfg\_node\_binary node is created. The unary node class is an extension of the variable class that contains only one input node. Similarly, the binary node is an extension of the unary node class that contains exactly two input nodes. These operation nodes are represented in circles in the visual graph.

The *cdfg\_node\_mux* class is not used during CDFG creation. The mux node is an extension of the binary class and has three inputs, a true value, a false value, and a binary selector. This node is used later, during a graph transformation. The mux node is represented as an inverted trapezoid in the dot representation.