# A VECTORIZED PROCESSING ALGORITHM FOR CONTINUOUS SPEECH RECOGNITION AND ASSOCIATED FPGA-BASED ARCHITECTURE

by

Jeffrey William Schuster

B.S., University of Pittsburgh, 2004

Submitted to the Graduate Faculty of

School of Engineering in partial fulfillment

of the requirements for the degree of

Master of Science

University of Pittsburgh

2006

#### UNIVERSITY OF PITTSBURGH

### SCHOOL OF ENGINEERING

This thesis was presented

by

Jeffrey William Schuster

It was defended on

March 29, 2006

and approved by

Raymond Hoare, Ph.D., Assistant Professor, Department of Electrical and Computer Engineering

Steven Levitan, Ph.D., John A. Jurenko Professor, Department of Electrical and Computer Engineering

Alex K. Jones, Ph.D., Assistant Professor, Department of Electrical and Computer Engineering

Thesis Advisor: Raymond R. Hoare, Ph.D., Assistant Professor, Department of Electrical and Computer Engineering

## A VECTORIZED PROCESSING ALGORITHM FOR CONTINUOUS SPEECH RECOGNITION AND ASSOCIATED FPGA-BASED ARCHITECTURE

Jeffrey William Schuster, M.S.

University of Pittsburgh, 2006

This work analyzes Continuous Automatic Speech Recognition (CSR) and in contrast to prior work, it shows that the CSR algorithms can be specified in a highly parallel form. Through use of the MATLAB software package, the parallelism is exploited to create a compact, vectorized algorithm that is able to execute the CSR task. After an in-depth analysis of the SPHINX 3 Large Vocabulary Continuous Speech Recognition (LVCSR) engine the major functional units were redesigned in the MATLAB environment, taking special effort to flatten the algorithms and restructure the data to allow for matrix-based computations. Performing this conversion resulted in reducing the original 14,000 lines of C++ code into less then 200 lines of highly-vectorized operations, substantially increasing the potential Instruction Line Parallelism of the system.

Using this vector model as a baseline, a custom hardware system was then created that is capable of performing the speech recognition task in real-time on a Xilinx Virtex-4 FPGA device. Through the creation independent hardware engines for each stage of the speech recognition process, the throughput of each is maximized by customizing the logic to the specific task. Further, a unique architecture was designed that allows for the creation of a static data path throughout the hardware, effectively removing the need for complex bus arbitration in the system. By making using of shared memory resources and applying a token passing scheme to the system, both the data movement within the design as well as the amount of active data are continually minimized during run-time. These results provide a novel method for perform speech recognition in both hardware and software, helping to further the development of systems capable of recognizing human speech.

©2006 - Jeffrey W. Schuster

## TABLE OF CONTENTS

| 1.0 | INTR          | ODUC  | ГІОЛ                                | 1  |

|-----|---------------|-------|-------------------------------------|----|

| 2.0 | PREVIOUS WORK |       |                                     | 7  |

|     | 2.1           | MA.   | JOR RESEARCH TOPICS                 | 7  |

|     |               | 2.1.1 | Signal Processing                   | 7  |

|     |               | 2.1.2 | Discrete Vs. Continuous Models      | 8  |

|     |               | 2.1.3 | Gaussian Selection                  | 10 |

|     |               | 2.1.4 | Feature Selection                   | 11 |

|     |               | 2.1.5 | Token Passing                       | 12 |

|     | 2.2           | CON   | MMERCIAL SOFTWARE SYSTEMS           | 13 |

|     |               | 2.2.1 | IBM's Via Voice                     | 14 |

|     |               | 2.2.2 | BBN's Byblos                        | 14 |

|     |               | 2.2.3 | SRI's DECIPHER                      | 15 |

|     |               | 2.2.4 | CMU's SPHINX                        | 16 |

|     | 2.3           | CUS   | STOM HARDWARE ARCHITECTURES         |    |

|     |               | 2.3.1 | Sensory Inc                         | 19 |

|     |               | 2.3.2 | University of Birmingham            | 19 |

|     |               | 2.3.3 | University of California at Berkley | 20 |

|     | 2.4           | VEC   | CTOR PROCESSING ARCHITECTURES       |    |

|     |               | 2.4.1 | VLIW Processors                     | 22 |

|     |               | 2.4.2 | SIMD Processors                     |    |

|     |               | 2.4.3 | Sony, Toshiba, IBM CELL Processor   |    |

|     |               | 2.4.4 | Stretch Inc. S5000 Chip Family      | 27 |

| 3.0 | SYST          | EM AR | RCHITECTURE                         |    |

|     | 3.1                              | SYS                          | STEM OVERVIEW                                          | 29 |

|-----|----------------------------------|------------------------------|--------------------------------------------------------|----|

|     | 3.2                              | PRE                          | ELIMINARY ANALYSIS                                     |    |

|     | 3.3                              | SYS                          | TEM LEVEL HARDWARE                                     |    |

|     |                                  | 3.3.1                        | System controller                                      | 35 |

|     |                                  | 3.3.2                        | Central Data Structure                                 |    |

|     | 3.4                              | TES                          | T / DEVELOPMENT ENVIRONMENT                            |    |

| 4.0 | ACOU                             | USTIC I                      | MODELING                                               |    |

|     | 4.1                              | GAU                          | USSIAN PROBABILITY EVALUATIONS                         |    |

|     |                                  | 4.1.1                        | One-Dimensional Gaussian Probability Density Functions | 40 |

|     |                                  | 4.1.2                        | D-Dimensional Gaussian Probability Density Functions   | 44 |

|     | 4.2                              | DES                          | SCRIPTION OF CALCULATIONS                              | 47 |

|     | 4.3                              | MA                           | TRIX MATLAB REPRESENTATION                             | 50 |

|     | 4.4                              | HAI                          | RDWARE ARCHITECTURE                                    | 55 |

|     |                                  | 4.4.1                        | Gaussian Distance Pipelined Processor                  | 56 |

|     |                                  | 4.4.2                        | Log-Add LUT                                            | 58 |

|     |                                  | 4.4.3                        | Find MAX / Normalizer                                  | 61 |

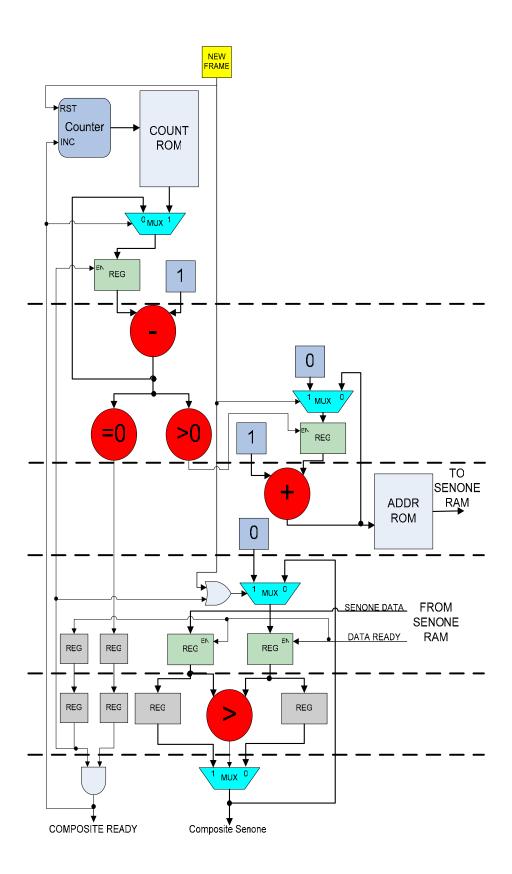

|     |                                  | 4.4.4                        | Composite Senone Evaluator                             | 63 |

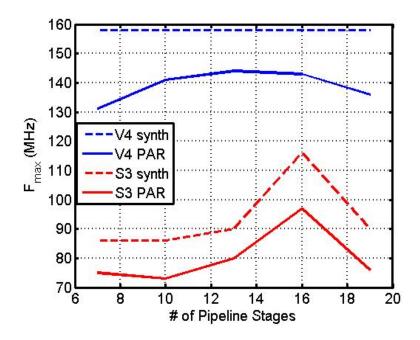

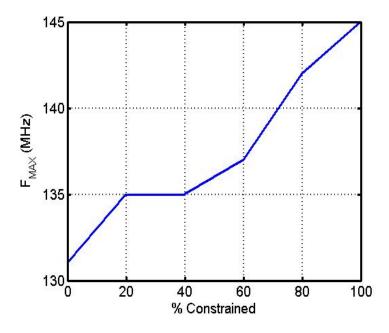

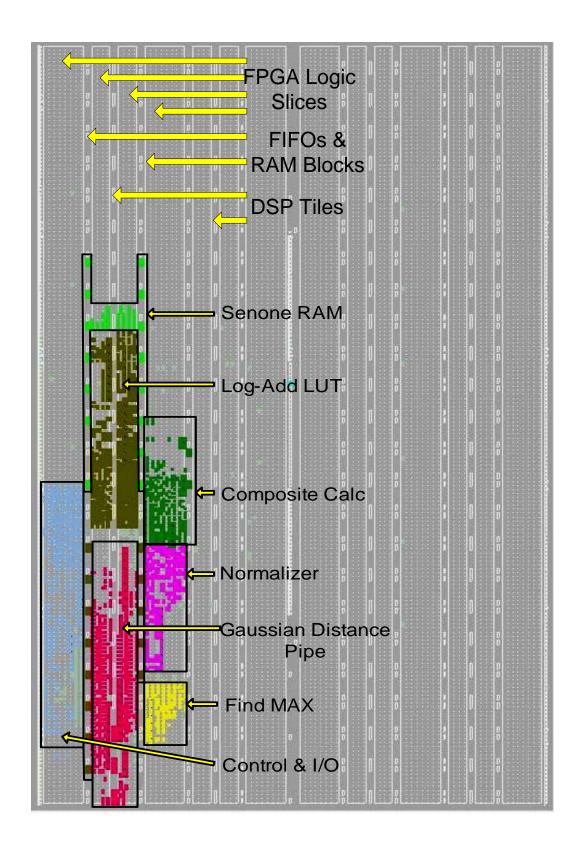

|     | 4.5 HARDWARE PERFORMANCE RESULTS |                              |                                                        |    |

| 5.0 | PHONEME EVALUATION               |                              |                                                        | 71 |

|     | 5.1                              | HID                          | DEN MARKOV MODELING                                    | 71 |

|     |                                  | 5.1.1                        | Mathematics                                            | 72 |

|     |                                  | 5.1.2                        | HMM Topologies                                         | 73 |

|     |                                  | 5.1.3                        | Viterbi Searching                                      | 76 |

|     | 5.2                              | DEC                          | CSRIPTION OF CALCULATIONS                              | 78 |

|     | 5.3                              | MATRIX MATLAB REPRESENTATION |                                                        | 82 |

|     | 5.4                              | HAI                          | RDWARE ARCHITECTURE                                    | 85 |

|     |                                  | 5.4.1                        | HMM Control Logic                                      | 86 |

|     |                                  | 5.4.2                        | HMM Pipeline                                           |    |

|     |                                  | 5.4.3                        | HMM Pruner                                             | 91 |

|     | 5.5                              | HAI                          | RDWARE PERFORMANCE RESULTS                             | 92 |

| 6.0 | WOR                              | D MOD                        | DELING                                                 | 97 |

|                                    | 6.1     | TREE SEARCHING                              | 97  |

|------------------------------------|---------|---------------------------------------------|-----|

|                                    | 6.2     | MATRIX MATLAB REPRESENTATION                |     |

|                                    | 6.3     | HARDWARE ARCHITECTURE                       |     |

|                                    |         | 6.3.1 Token Deactivator                     | 103 |

|                                    |         | 6.3.2 Token Activator                       | 104 |

|                                    | 6.4     | HARDWARE PERFORMANCE RESULTS                | 108 |

| 7.0                                | PERFC   | DRMANCE PROFILES                            | 113 |

|                                    | 7.1     | LITERATURE PERFORMANCE REVIEW               | 113 |

|                                    | 7.2     | MATRIX MATLAB PERFORMACE PROFILE            |     |

|                                    | 7.3     | HARWARE PROFILE SUMMARY                     | 121 |

| 8.0                                | CONC    | LUSIONS, CONTRIBUTIONS, & FUTURE DIRECTIONS |     |

|                                    | 8.1     | CONCLUSIONS                                 | 125 |

|                                    | 8.2     | CONTRIBUTIONS                               | 125 |

|                                    | 8.3     | FUTURE DIRECTIONS                           | 127 |

| APPENDIX A: VECTORIZED MATLAB CODE |         | 131                                         |     |

|                                    | A.1     | RM1_top_level.m                             | 131 |

|                                    | A.2     | data_loader.m                               | 133 |

|                                    | A.3     | acoustic_modeler_comp_senones.m             | 135 |

|                                    | A.4     | logs3_add_look_up_float.m                   | 136 |

|                                    | A.5     | HMM_eval_no_comps.m                         | 136 |

|                                    | A.6     | word_model.m                                | 138 |

| APP                                | ENDIX B | : VHDL CODE                                 | 141 |

|                                    | B.1     | AM_calc.vhd                                 | 141 |

|                                    | B.2     | gaus_calc_top_v2.vhd                        |     |

|                                    | B.3     | composite_senone_calc.vhd                   |     |

|                                    | B.4     | find_max.vhd                                | 176 |

|                                    | B.5     | gaus_dist_full_pipe_V2_FINAL.vhd            | 180 |

|                                    | B.6     | log_add_calc_V1_FINAL.vhd                   | 192 |

|                                    | B.7     | normalizer.vhd                              | 203 |

|                                    | B.8     | hmm_top_struct.vhd                          | 209 |

|                                    | B.9     | hmm_pipe_w_mdef.vhd                         | 229 |

| B.10         | hmm_calc_vNEW.vhd         | 241 |

|--------------|---------------------------|-----|

| B.11         | mdef_rom_struct.vhd       | 251 |

| B.12         | ph_ptr_ram_NEW_struct.vhd |     |

| B.13         | new_pruner.vhd            |     |

| BIBLIOGRAPHY |                           |     |

## LIST OF TABLES

| Table 1. Number of Compute Cycles for 3 Different Speech Corpuses                    |         |

|--------------------------------------------------------------------------------------|---------|

| Table 2. Number of Calculations Necessary for Various Dictionaries                   |         |

| Table 3. Parallelism in Acoustic Modeling                                            | 53      |

| Table 4. Summary of Synthesis and Place-and-Route Results for Virtex-4 SX35          | 71      |

| Table 5. Summary of Synthesis Results for HMM Pipeline using both Precision Synthese | sis and |

| Synopsys Synplify                                                                    |         |

| Table 6. Summary of Place-and-Route Results for PE                                   |         |

| Table 7. Summary of Word Model Synthesis Results                                     | 112     |

| Table 8. Summary of Software Performance Results                                     | 115     |

| Table 9. Summary of Hardware Performance Results                                     | 124     |

## LIST OF FIGURES

| Figure 1. Continuous vs. Discrete Gaussian PDFs                                     | 9  |

|-------------------------------------------------------------------------------------|----|

| Figure 2. A Simple Tree Structure                                                   | 13 |

| Figure 3. Sample HMM Topology                                                       | 17 |

| Figure 4. Diagram of Decoder Architecture                                           | 22 |

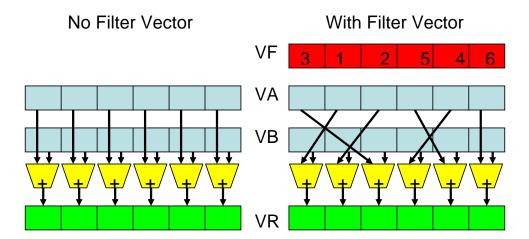

| Figure 5. SIMD Processing With and Without Filter Vector                            | 25 |

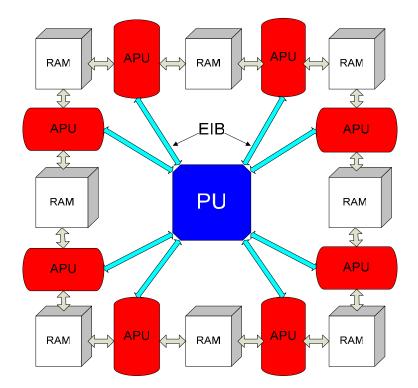

| Figure 6. Block Diagram of Cell Architecture                                        | 27 |

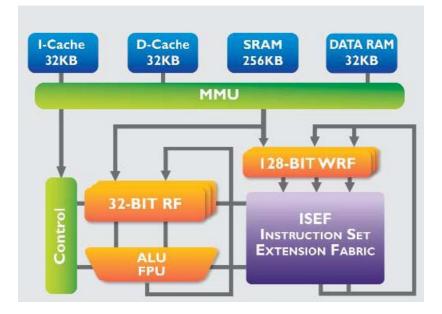

| Figure 7. Stretch Inc. S5000 Processor Engine                                       | 29 |

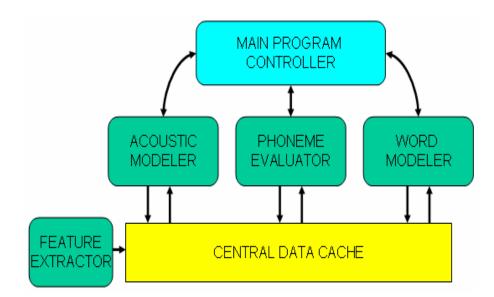

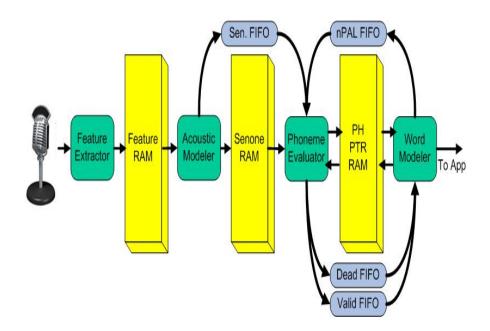

| Figure 8. Block Diagram of Software-Based ASR System                                | 31 |

| Figure 9. Block Diagram of the Speech Silicon Hardware-Base ASR System              | 33 |

| Figure 10. FSM for System Controller                                                | 37 |

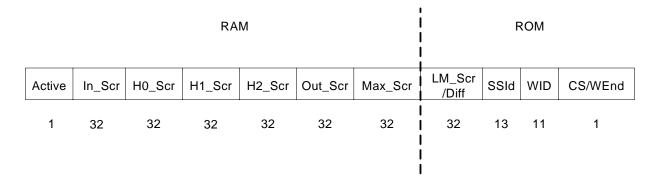

| Figure 11. Organization of Fields in Database                                       | 38 |

| Figure 12. Sample Set of Gaussian Distributions for Multiple $\sigma^2$ Values      | 42 |

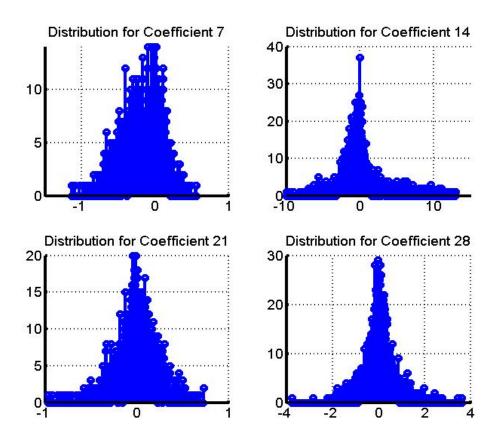

| Figure 13. Distribution of 2,100 Cepstral Inputs for 4 Different Coefficients       | 44 |

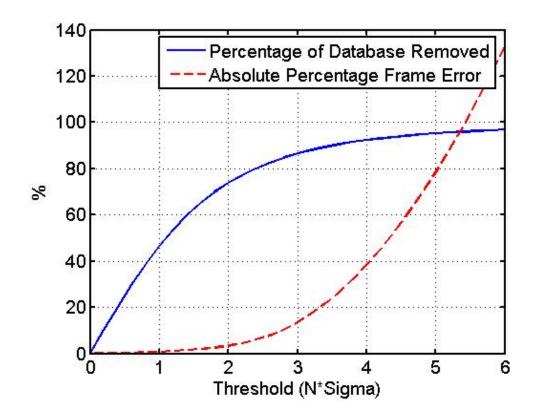

| Figure 14. Percentage Error Vs. Percentage of Database Removed for Varying n Values | 45 |

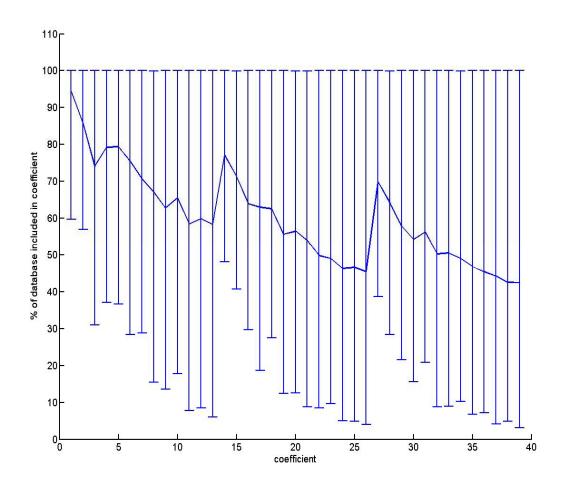

| Figure 15. Percentage Contribution of Each Dimension of a Multivariate Gaussian PDF | 47 |

| Figure 16. Initialization Code for AM                                               | 54 |

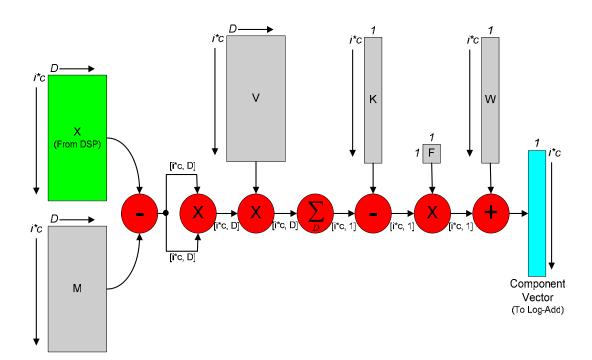

| Figure 17. Calculation of Component Scores                                          | 54 |

| Figure 18. Block Diagram of Vectorized Gaussian PDF Calculation                     | 55 |

| Figure 19. Code for Vectorized Calculation of Log-Summation                         | 56 |

| Figure 20. Code Necessary to Calculate Senone Scores                                | 57 |

| Figure 21. Code for Composite Senone Calculation                                    | 58 |

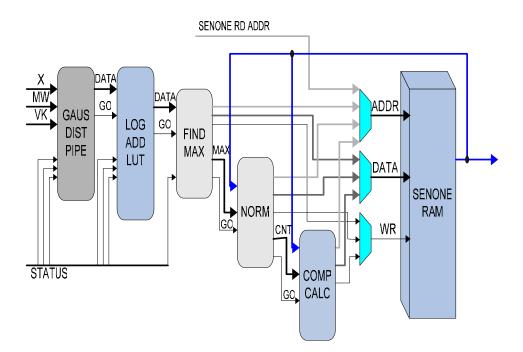

| Figure 22. Block Diagram for Acoustic Modeling Co-Processor                         | 59 |

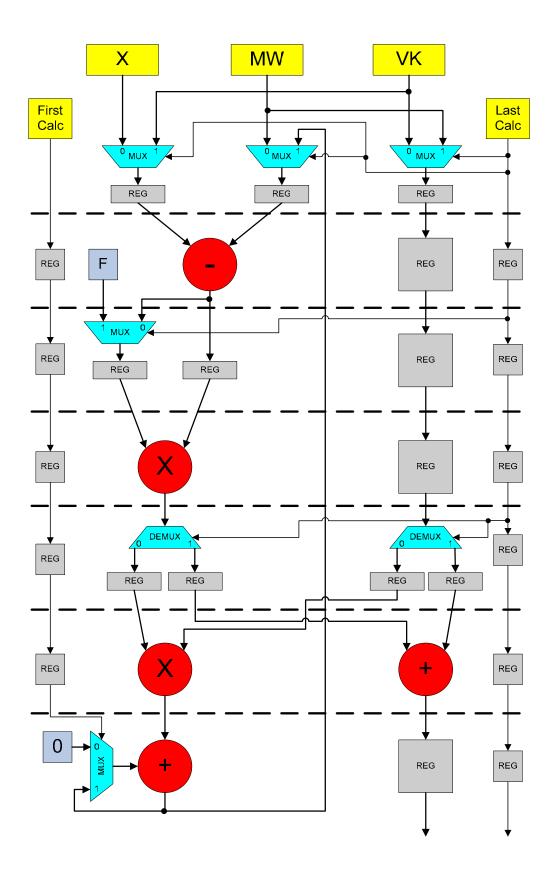

| Figure 23. Data Flow Graph for Gaussian Distance Pipe                               | 60 |

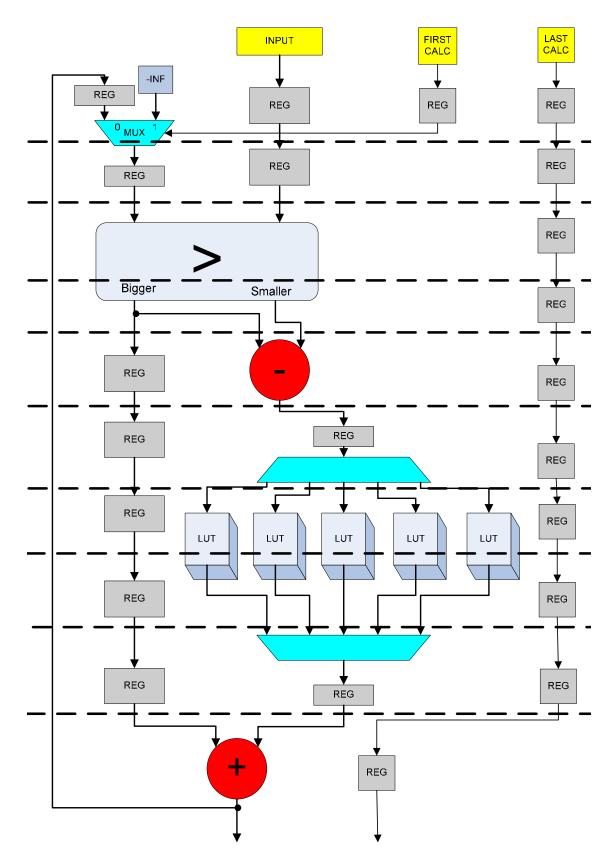

| Figure 24. Data-Flow Graph for Log-Add LUT                                          | 63 |

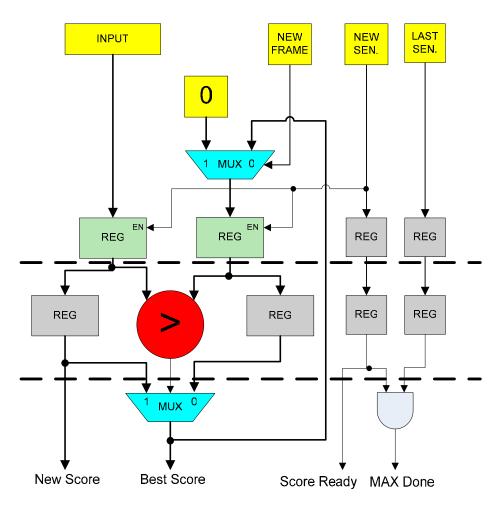

| Figure 25. Data-Flow Graph for Find Max Unit                                        | 65 |

| Figure 26. Data Flow Graph for Composite Senone Calculation                         | 68 |

| Figure 27. Analysis of $f_{max}\xspace$ vs. Pipeline Stages for Virtex-4 SX and Spartan-3 FPGAs | 70  |

|-------------------------------------------------------------------------------------------------|-----|

| Figure 28. Speed Improvement vs. Percentage of Design Constrained for Gaussian Distance         |     |

| Pipe                                                                                            | 72  |

| Figure 29. Post Place-and-Route Layout for AM Pipeline on a Virtex-4 SX35 FPGA                  | 73  |

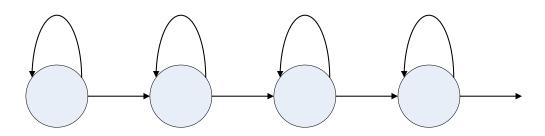

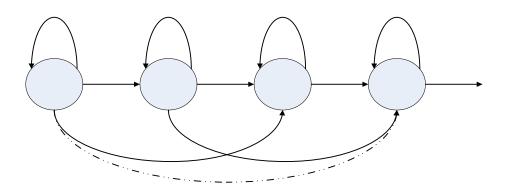

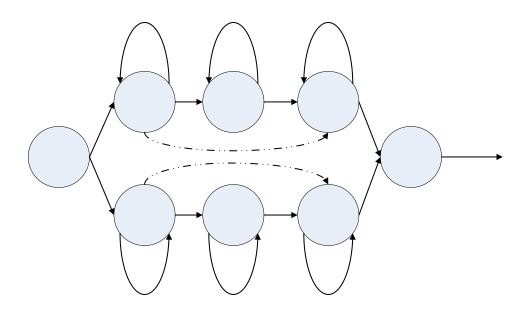

| Figure 30. Linear HMM Topology                                                                  | 77  |

| Figure 31. Comparison of Bakis and Left-to-Right Topology HMMs                                  | 77  |

| Figure 32. Sample Alternative Paths HMM Topology                                                | 78  |

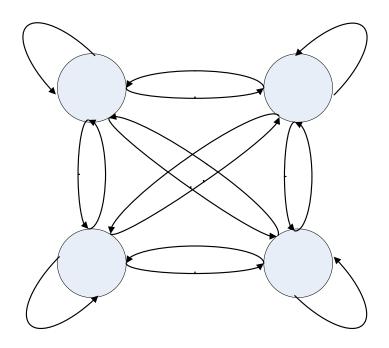

| Figure 33. Sample Ergodic HMM Topology                                                          | 79  |

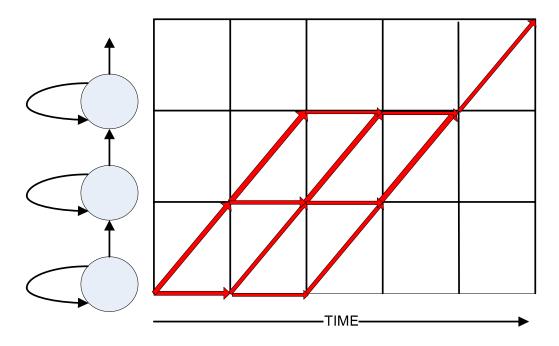

| Figure 34. Sample HMM Trellis                                                                   | 80  |

| Figure 35. HMM Trellis with Viterbi Algorithm                                                   | 81  |

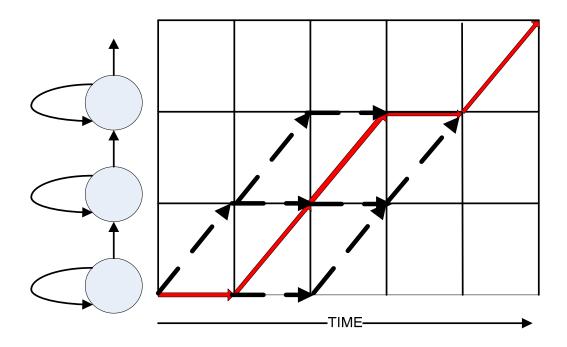

| Figure 36. Data-Flow Diagram for Memory Access for HMM Calculation                              | 83  |

| Figure 37. HMM Topology with Labeled Values                                                     | 84  |

| Figure 38. Code for PE initialization                                                           | 86  |

| Figure 39. Code for Data Allocation in PE                                                       | 87  |

| Figure 40. Code for HMM Calculation and Data Storage                                            | 87  |

| Figure 41. Code for HMM Pruning                                                                 | 88  |

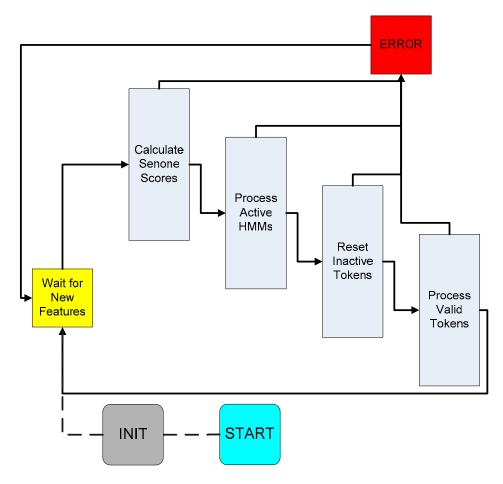

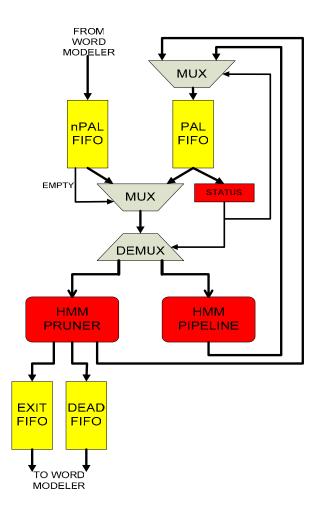

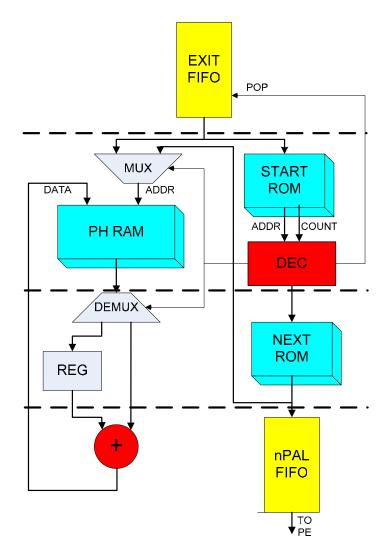

| Figure 42. Control for Phoneme Evaluator                                                        | 90  |

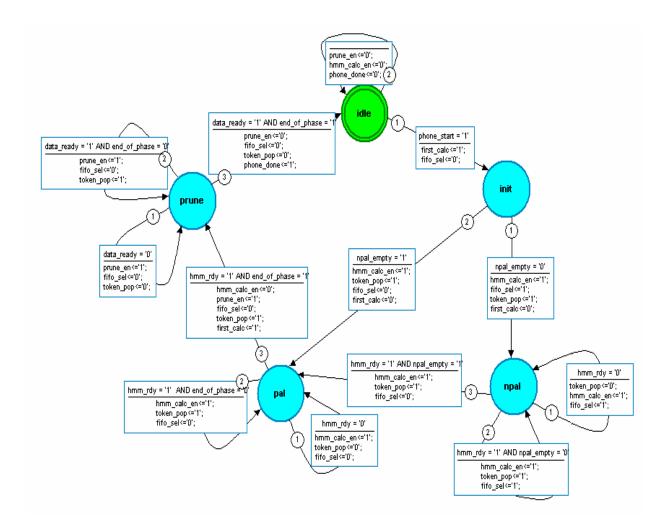

| Figure 43. Finite State Machine for PE Control                                                  | 91  |

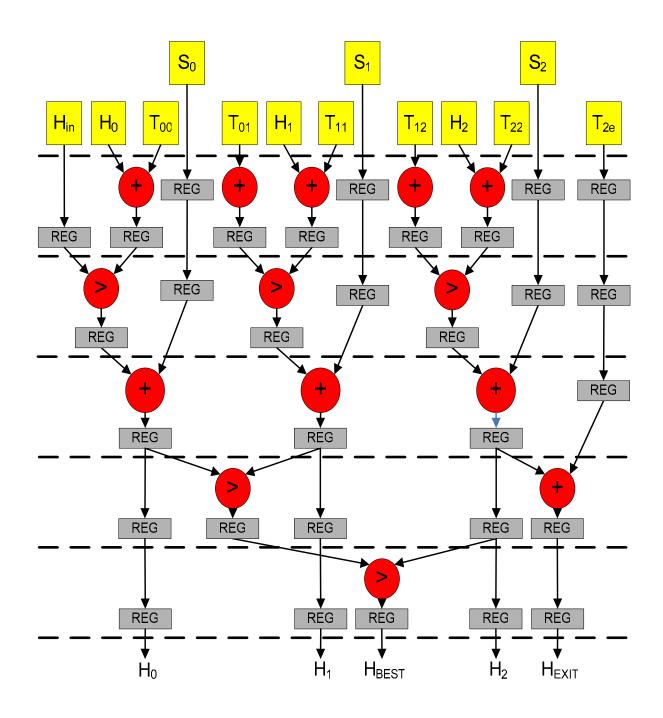

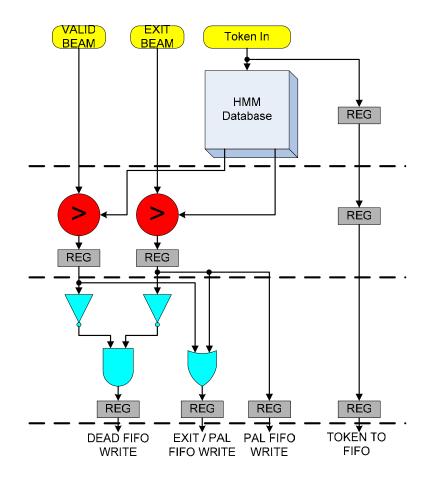

| Figure 44. Data-Flow Graph for HMM Pipeline                                                     | 93  |

| Figure 45. Data-Flow Graph for HMM Pruner                                                       | 95  |

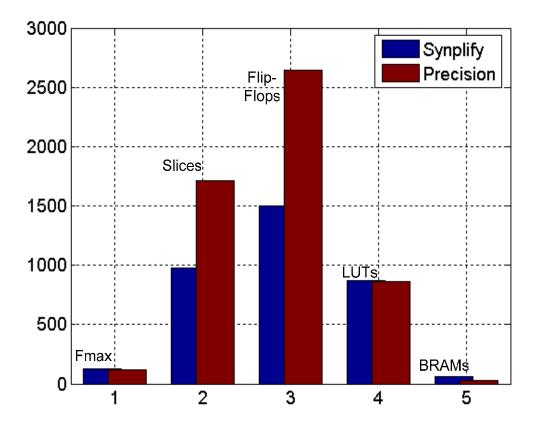

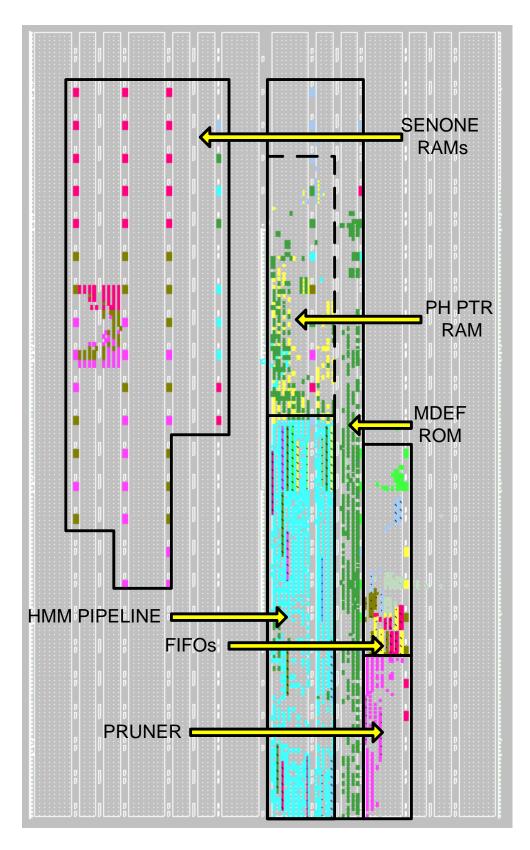

| Figure 46. Precision Synthesis Vs. Synopsys Synplify                                            | 96  |

| Figure 47. Final Layout for PE                                                                  | 99  |

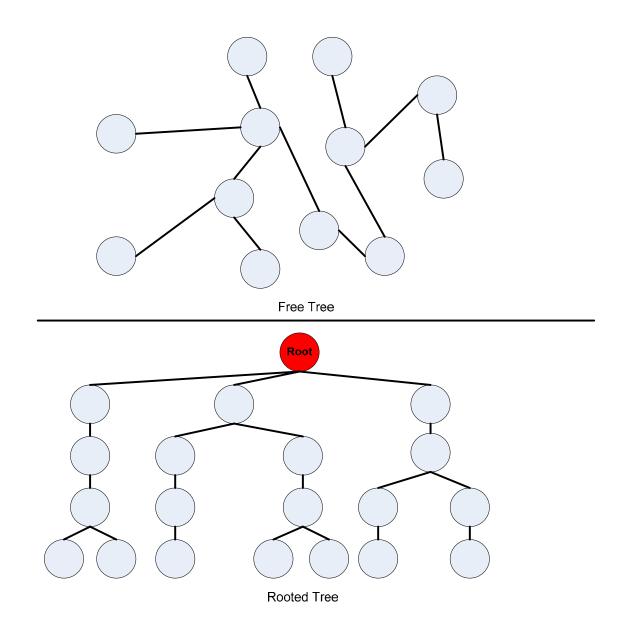

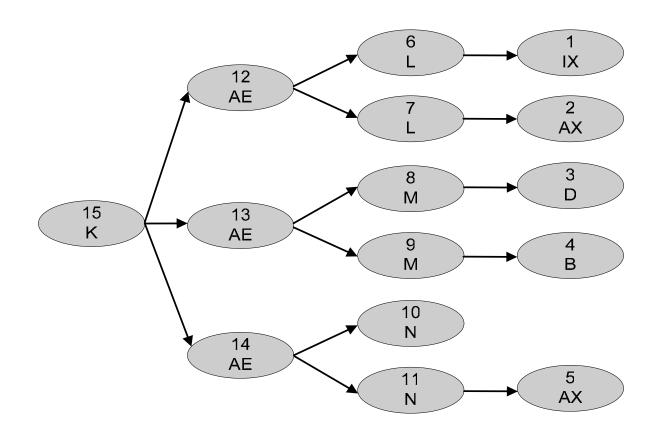

| Figure 48. Sample Tree Topologies                                                               | 102 |

| Figure 49. Code for Token Deactivation and Frame Initialization                                 | 104 |

| Figure 50. Code for Obtaining Link-List Information                                             | 105 |

| Figure 51. Code for Obtaining Leaf-Node Propagation Information                                 | 105 |

| Figure 52. Code for Main WM Loop                                                                | 106 |

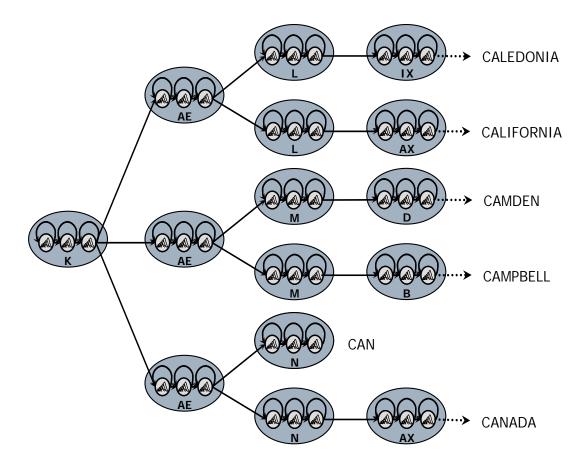

| Figure 53. Sample Word Tree                                                                     | 108 |

| Figure 54. Sample Search Space Node Mapping                                                     | 109 |

| Figure 55. Data Flow Graph for Token Activator                                                  | 111 |

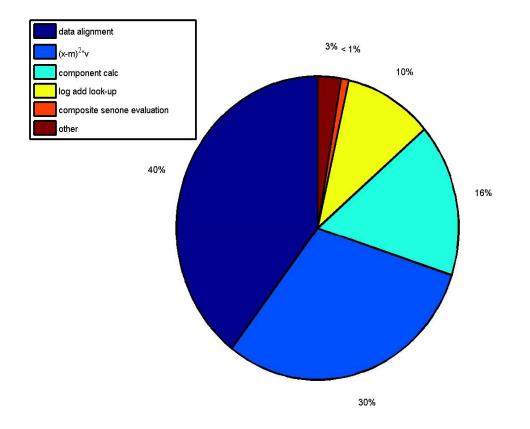

| Figure 56. Performance analysis of MATLAB Model for Acoustic Modeling                           | 117 |

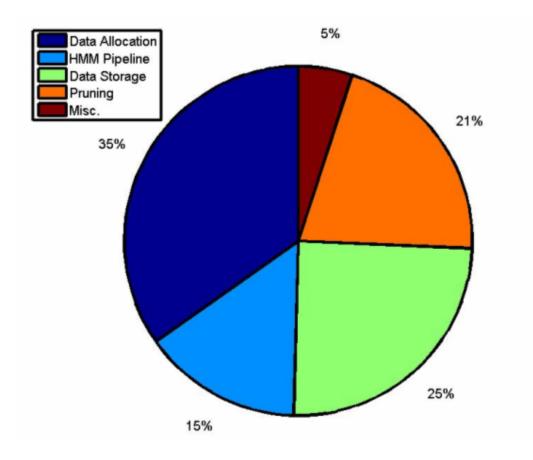

| Figure 57. | Results of Code Profile for PE      | 119 |

|------------|-------------------------------------|-----|

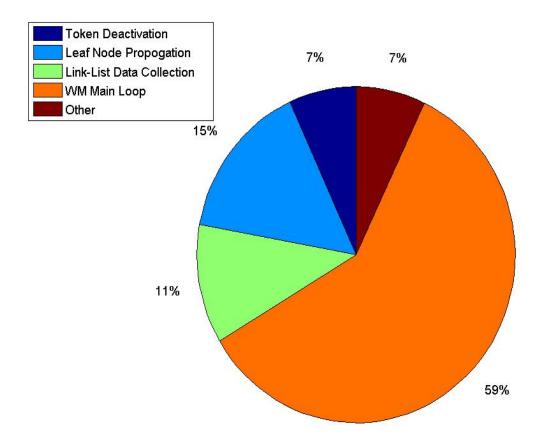

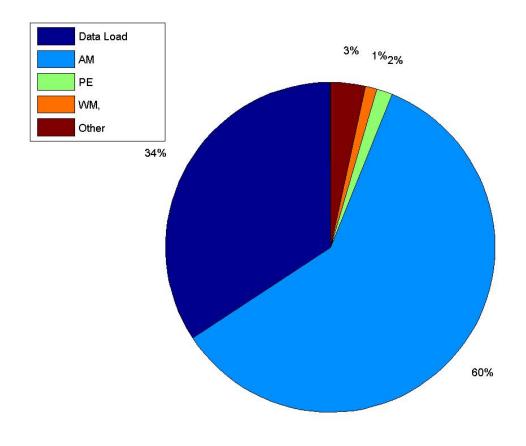

| Figure 58. | Code Profile for WM                 | 120 |

| Figure 59. | Code Profile for Entire MATLAB Code | 121 |

#### PREFACE

I would like to pay special thanks to all of the people who helped me along this journey. To all my lab mates past and present, especially Dara, Shenchih, & Eliott, for providing both the intellectual and moral support to continue pursuing my education. To the members of my research team, Kshitij and Johnny, for correcting me when I was wrong and for all the long nights spent in debate. To all of my professors for the knowledge they passed on, the questions they answered, and most importantly the questions they posed that forced me to reach further and learn more. A special thanks goes to Dr. Hoare, Dr. Jones, and Dr. Levitan for appearing on my committee and helping me fine tune the end result of many years of hard work. Dr. Hoare, who gave me the opportunity that not even I thought I deserved, my deepest thanks to you for the chance to expand my horizons and the chance to begin developing into the engineer I hope to be. I would also like to thank my friends and family for their support and encouragement through all of the highs and lows of the past few years. Finally, a world of thanks to my mother and father for their unwavering belief in my ability to achieve anything and for giving me the attitude and poise to attempt it.

### **1.0 INTRODUCTION**

As speech recognition technology was being developed in the 80's and 90's researchers examined numerous techniques for reducing the computational complexity of the process, attempting to reach middle-ground between speed and accuracy. One the one side of the argument were isolated word systems that could only operate on a single word at a time but accurate on medium to large scale dictionaries. In the opposing camp were systems focused on the recognition of conversational speech, allowing the user to interact with the device as they would a person but severely limiting the size of the dictionary as well as the potential accuracy. Many of the first systems to attempt speech recognition used discrete models in which isolated words were able to be deciphered as opposed to conversational speech. By removing any crossword articulation effects, and limiting the number of recognizable words to those necessary for a specific task, the accuracy of a system could be increased substantially without dramatically affecting the computational load. Using discrete models does however require the user to speak to the machine in isolated words which sounds very different from conversational speech. This difference can take some time for a person to adjust to and it most situations is highly undesirable.

In contrast to discrete speech systems, other groups worked with single-user, systems, able to handle more conversational speech, but only from one user. These systems require that the user train the system to understand them, leading to the need for numerous systems in a single building, each dedicated to one person's voice. Using speaker-dependent systems also requires the storage of large amounts of data, since each speaker needs their own specific model, which can become a very costly process in systems where multiple speakers are using large-scale dictionaries. Additionally, these types of systems have no certainty that they can recognize words outside of the set they were trained on. A simple example of a speaker-dependent system

1

can be seen in current mobile phone technology where by recording a voice command, that command can be repeated at a later time to create an action. Unfortunately, these systems are semi-accurate, and can be cumbersome if multiple recognitions are necessary to complete a task.

With the rise of high performance computing, new techniques have been developed that take a more broad approach to the problem, attempting to exploit computational ability for the sake of multiple user, continuous speech recognition. Most of these systems rely on complex software- based algorithms to analyze incoming speech requiring state-of-the-art processors and large amounts of memory. In these speaker-independent systems, large numbers of probability evaluations are performed to determine the most likely sequence of sounds heard, which in turn can be correlated to the most likely sequence of words heard by the system. In order to achieve acceptable recognition rates extensive off-line training must occur to ensure that the models being used by the system are both general enough to cover a large base of different speakers and yet unique enough to accurately represent the different sounds in a given speech corpus. Even with modern computers these methods still suffer serious computational overhead, taking between 0.6X real-time on a 1.7GHz Athalon Processor to upwards of 10X real-time when running on a 450MHz Pentium III style device, to analyze a full English speech corpus. This results in systems that perform transcription oriented tasks quite well but fall short of user expectations when continuous real-time recognition is required [1, 7, 8, 9].

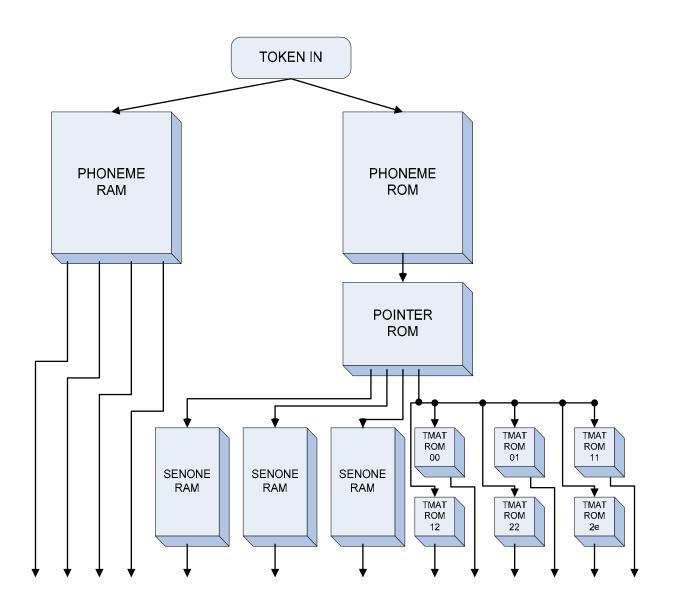

The current generation of ASR technologies can be broken down into three basic functional units: a Feature Extraction unit, an Acoustic Modeler, and a Language Modeler [2, 6, 18]. Acoustic modeling is consistently the most computationally intensive of the three phases, taking up anywhere from 30% to 95% of the computation time [1, 3, 4]. Acoustic modeling can be broken down into two major components, the actual Acoustic Modeler and the Phoneme Evaluator. The Acoustic Modeler is responsible for comparing the incoming data to a predefined set of Gaussian Probabilities via the evaluation of multi-dimensional Gaussian PDFs. These evaluations are computationally intensive and can require upwards of 4.9 million floating point operations per second to completely evaluate the database [5]. To further the problem many of the state-of-the-art recognition systems like BBN's *Byblos*, CMU's *Sphinx*, Cambridge University's *HTK Toolkit*, IBM's *Via Voice*, and SRI's *DECIPHER*, perform statistical pattern matching using Hidden Markov Models (HMMs) during phoneme evaluation, requiring the calculation of hundreds of thousands of state probabilities based on the results obtained by the

Acoustic Modeler [6, 7, 8, 9]. In the Language Modeling phase a high-level tree structure is created to link the phonemes together into words. This tree can become cumbersome and can cause severe pipe-line stalls, resulting in an overall IPC that ranges between 0.37 and 1.2 [5]. Additional details on previous work and processing technologies can be found in Chapter 2 of this document.

The first major contribution of this research examines the calculations being performed in software and exposes the potential for parallelism. It has been shown that systems such as the SPHINX recognition engine have very poor IPC rates, between 0.5 and 0.6 for a 1.7GHz AMD processor, but the equations begin performed imply much larger potentials [5]. This potential parallelism is illustrated through the reorganization of the data to allow for large matrix-based operations in MATLAB. These operations while executing sequentially on a Pentium 4 processor, show the potential for parallelism upwards of 600,000 elements for certain operations. Additionally a token passing scheme is employed, resulting in reductions in the computational workload of the system. The derivation of MATLAB code based on point-wise matrix operations serves to illuminate the potential for parallelism in the speech recognition process and to highlight the portion of the algorithm that stand to benefit most from large parallel operations. Combining the potential increase in parallelism with a method for reducing unnecessary data accesses, answers are provided for both the performance and memory problems associated with ASR leading to the possibility for ASR systems able to perform speaker-independent recognition in real-time.

The second major contribution of this work uses the potential parallelism for the design of pipelined hardware on a 90nm FPGA capable of operating at over 100MHz. Being able to operate with a clock frequency over 100MHz ensures real-time operation based on the amount of calculations necessary for a 1,000 word dictionary given that the job takes less than 1 million cycles. The specific details correlating the 100MHz clock to the ability to recognize speech in real-time are discussed in depth in Chapter 3. Using the matrix-based MATLAB code as a template for the creation of a hardware system the portions of the code that benefited most from parallelism could be specially designed to exploit it. Developing custom hardware blocks for each portion of the speech recognition task allowed for the creation of an architecture that is able to efficiently manage the data in between the blocks as well as efficiently processing it within a given block. Each block in the design was created to allow for the use of a token passing scheme to manage the active data in the system. Through the use of shared RAM arrays to store the active data and FIFOs to manage the active workload of the system, the designed system is able to perform a minimal amount of work at all times while simultaneously maximizing the bandwidth in each cell. Additionally, the Acoustic Modeling hardware block is flexible and its computations can be configured through the data stored in RAM; thus, a variety of Gaussian calculations can be computing using this block.

The following chapter of this work presents an array of previous works in both hardware and software to help characterize the current state-of-the-art. Additionally, the major research areas in speech recognition are discussed to illuminate the corners of the field that are currently of special interest. The chapter will conclude with a brief analysis of some existing processor architectures that while not specifically designed for speech recognition, highlight some unique architectures that serve to illustrate the desired architecture in an ideal speech recognition system.

After a summary of the current research field, Chapter 3 will present the high-level system details for the designed system. First, a summary of the major operations for the speech recognition process is given to lay the foundation for the remainder of the document. A preliminary analysis of the task to be performed is then given to help quantify the complexity of the project and the potential resources required for a functional system. The next section of this chapter describes the system-level hardware needed to interconnect the individual hardware cells. This hardware represents a joint effort between myself and the members of my research group to establish an efficient means for moving data throughout the system and while not pertinent to the contributions of this thesis, is necessary for sake of complete understanding of the final design. Chapter 3 then concludes with a description of the testing and development environments used throughout the project.

Chapter 4 begins the bulk of the contributions of this thesis by presenting the work done on the Acoustic Modeling portion of the speech recognition process. Acoustic Modeling involves the evaluation of thousands of multi-variant Gaussian distributions for each new input to the system and is a mathematically complex operation. After presenting the preliminary mathematics for the process, the development of the MATLAB algorithm is discussed. This discussion will cover the complete code used by MATLAB to perform the Acoustic Modeling algorithm and show how the use of large-scale matrix operations can help to simplify the operations needed for the process. Next, the hardware development will be examined, paying special attention to derivation of the pipeline used for the core of the Acoustic Modeling calculation. In this section, the specific operation of the pipeline will be discussed, and its ability to change functionality based on the input configuration will be examined. Having detailed the hardware necessary for completion of the Acoustic Modeling task, this chapter will conclude with an analysis of both the synthesis and the post place-and-route results for the derived hardware. Additionally, this chapter briefly discusses the ability to use state-of-the-art design tools to help increase the performance of the design without presenting any additional designer effort.

After summarizing the Acoustic Modeling process this document will go on to describe the next major portion of the design, the Phoneme Evaluation block. Phoneme Evaluation is the process of utilizing the data generated by the Acoustic Modeler to evaluate the active set of Hidden Markov Models in the system. Hidden Markov Models, HMMs, are used to represent the individual phonetic units of a given language, and their evaluation presents its own unique set of computational problems. Chapter 5 follows a similar format to Chapter 4 beginning first with an introduction to Hidden Markov Models, followed by a description of the major mathematics From here, the software development will first be described needed for the process. concentrating on the ability to use compact pointer vectors to perform sparse-matrix operations, leading to the ability to remove all loops from the phoneme evaluation process. As in the previous chapter the description of the software development will next lead to the derivation of the custom hardware created to perform phoneme evaluation. During the description of the hardware development special attention will be paid to the large data allocation problem presented by phoneme evaluation and how these conflicts were resolved. Chapter 5 concludes with a summary of the synthesis and place-and-route results for the hardware design and examines the effects of different synthesis tools on the end performance of the designed logic.

In the same style as the previous chapters, Chapter 6 presents the work done for the Word Modeling process. This process involved the evaluation of a large tree structure and the propagation of information throughout it. While the MATLAB code for this block represents a unique contribution to this work and helps to quantify MATLABs ability to perform search based operations, the hardware development is less critical and presented only for the sake of completeness in the document. While the hardware cell for this portion of the design is based on

the derived MATLAB code, it is not unique work nor is it a performance critical portion of the design worth focusing significant attention on. As in Chapters 4 and 5 a summary of the placeand-route results will be given although with not as much detail as in the preceding chapters.

Having examined the development of the hardware and software cells for the speech recognition system, Chapter 7 will spend some time quantifying the performance of the MATLAB code written for this thesis. While profiling of the MATLAB code does not lead directly to a performance profile of the associated C-code, nor does it exemplify the performance boundaries of the hardware device, it does provide a unique insight into the capabilities of the MATLAB computing engine and helps to show how MATLAB can greatly accelerate some operations while impeding others. This chapter is presented solely to help characterize the MATLAB code and the associated programming environment in an effort to show the completeness of the work performed on the software algorithms.

This work concludes with a summary of the major contributions of the research and presents the potential future directions for research in this area. Chapter 8 will discuss the final results of the project and help to summarize the specific contributions that make this work unique and beneficial to the speech recognition community. After discussing the benefits of this specific work, Chapter 8 will conclude with a contemplation of the potential to develop this work into real-world products capable of improving the quality of life of generations to come.

#### 2.0 PREVIOUS WORK

Since the first researchers began to look at the speech recognition problem in the early 70's the amount of data required has always been a limiting factor. The amount of information that humans use to process and understand speech is much greater than what a modern computer can process in real-time, resulting in the need to trade speed for accuracy or visa versa. Exploration of these trade-offs has resulted in some major advancements in both the signal processing used to transform the incoming audio into some useful information, as well as the architectures of the software systems used to process this information in an efficient and meaningful way.

#### 2.1 MAJOR RESEARCH TOPICS

During the past 40 years of ASR research a number of developments have helped to bring the technology to the level that we are currently familiar with. These advances have occurred in a number of different research areas from signal processing to computer system architecture and each new development has helped push the industry forward. The following section will take a look at some of the key developments in the ASR field over the past few decades and illustrate how each of these events played into the current state-of-the-art technology.

#### 2.1.1 Signal Processing

Before any actual speech processing can begin, it is first necessary to convert the incoming audio into some useful information that uniquely represents the sounds heard in a given sample. Modern ASR systems employ a number of standard frequency-domain transforms such as the Fast Fourier Transform (FFT), Discrete Cosine Transform (DCT), and Cepstral Transform to extract information about the features, frequency content, of a sample [10, 12, 14]. As Signal Processing evolved along side high-performance computing in the 80's and early 90's, it was found that using greater numbers of features can noticeably increase word recognition accuracy [11, 12]. Early systems generally relied on low-order Liner Prediction Coefficients (LPCs), usually only the first 10-13, to extract the information regarding the relative frequency content of a speech sample. Most of these systems also relied on a frequency-warping transform, usually a bilinear, to warp the frequency axis and give the frequencies around the human speech band more weight. Eventually it was found that converting LPCs to Cepstral Coefficients and also making use of the first and second derivatives enabled a significant improvement in recognition accuracy [13, 14]. Also aiding in ability to obtain such high recognition rates was the application of a new frequency transform, the Mel-scale transform which is described in detail by [19]. This transform breaks the frequency band into as many as 40 separate regions and quantizes the information in each of the regions separately to allow for maximum frequency resolution in each band. Based on these high word accuracy rates, the use of a 39-dimensional Mel-Frequency Cepstral Coefficient (MFCC) vector to quantize the incoming audio has become the methodology of choice for feature extraction, resulting in the "standard" acoustic front-end as described by [15]. Despite the increase in computation this standard acoustic front-end is used in most state-of-the-art systems including BYBLOS, DECIPHER, and SPHINX 3 due to the substantial increase in recognition that can be obtained [9, 16, 17].

#### 2.1.2 Discrete Vs. Continuous Models

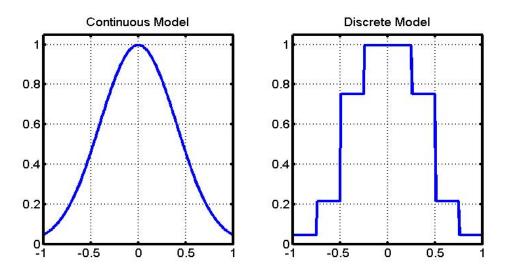

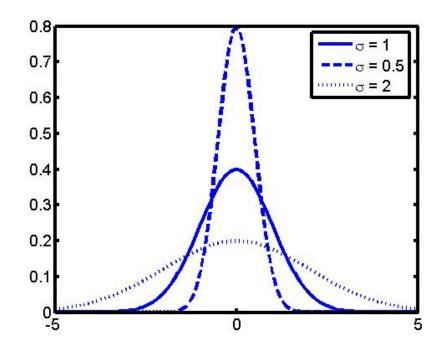

The majority of state-of-the-art speech recognizers rely on the use of Hidden Markov Modeling (HMM) techniques to correlate the data provided by the Feature Extractor to a known database of phonetic units, phonemes [6, 7, 8, 9, 16]. HMMs can be viewed as either continuous or discrete based on the types of data they attempt to model, with the continuous models requiring significantly more calculations than their discrete counterparts. Figure 1 shows the difference between the Gaussian Probability data used to score the HMMs in a discrete versus a continuous system.

Figure 1. Continuous vs. Discrete Gaussian PDFs

In a system using discrete HMMs, each Gaussian is pre-calculated, quantized, and stored in memory such that when the system is in use, no actual calculation is required and the values necessary may simply be looked up. While this does provide a very efficient manner acquiring the result of the Gaussian evaluation it introduces a significant amount of error into the system through the quantization of the Gaussian PDF, and in systems where multiple similar Gaussians are necessary there results quickly become highly confusable. One way to remedy this problem is through reducing the size of the quantization step but this leads to large increases in the

amount of memory required, which in most current systems may be an even larger problem than the one it attempts to solve. In semi-continuous models, a manageable set of parent-Gaussians is chosen to represent the entire desired set, and when a result is needed from the full set, the parent Gaussian is calculated and a weighting factor is applied to make it unique. Because this method actually calculates some Gaussians precisely, it is an inherently more accurate method than using a discrete model, but due to the fact that not all the Gaussians are directly calculated there is still a noticeable loss in precision versus using a continuous model. A Continuous HMM system actually stores the means and variances for each Gaussian in the knowledgebase and fully calculates each probability as it is needed. It has been shown that Continuous Density HMMs can increase the recognition accuracy upwards 6% when compared to Discrete or Semi-Continuous HMMs and in turn the number of likelihood calculations has increased from a few hundred to multiple thousands in most systems today [3, 12, 18, 22]. Coupled with this, it was found that greater the number of mixtures, where each additional mixture contains a unique cluster of Gaussians, that were used to model each state, the better the recognition accuracy [12]. Hence, it is not just the increase in dimensionality of the problem but also the increase in the number of quantities that need evaluation that has caused the computational requirements to drastically increase over the years. Since these calculations take a majority of the computational effort, between 58% and 70% of the total run-time, in-depth research has been focused on minimizing the number of these calculations without sacrificing accuracy [5].

Early ASR systems were limited by the performance of the available microprocessors and consequently relied on discrete HMMs in an effort to reduce the volume of Gaussian probability calculations necessary to evaluate the knowledgebase. Certain combinations of these limited Gaussians make up the states in an HMM and thus by computing the likelihoods over this limited set, recognition can be performed with significantly fewer calculations [6, 18]. An example of this method can be found in the SPHINX 2 system that used only 256 distributions as compared to SPHINX 3's 50k [1, 6, 16, 28]. Although discrete HMMs do provide a substantial amount of computational savings they also introduce large error rates when compared to continuous systems and restrict the system to smaller dictionary sizes, making them an undesirable solution in situations requiring high word accuracy rates on dictionaries over 5,000 words.

#### 2.1.3 Gaussian Selection

Noting the need for continuous HMMs to achieve acceptable recognition rates, a significant amount of research has been done to expose other possible optimizations for the phoneme evaluation problem. One method, Gaussian Selection, has become one of the more widely accepted techniques in ASR. Originally proposed by Boccheiri [20], this method uses a process of Vector Quantization that utilizes, a set of coarse Gaussians to map multiple Gaussians in the full model to one of the vector quantized Gaussians [4, 20, 21]. For every input speech frame, the best matching coarse Gaussians are found and used as pointers to clusters of high-probability Gaussians that need to be evaluated fully. The remainder of the set can then either be approximated or completely ignored [16, 21, 23]. This method has been able to reduce the number of Gaussians that need to be calculated by a factor of up to 16 but can increase the word error rate by as much as 28% [23, 24]. Though this method does significantly reduce the computations necessary, it can also create issues involving branch misprediction and memory access bottlenecks, that can lead to pipeline stalls up to 52% on a Pentium III platform [3, 5, 6]. In the case of the SPHINX 3 system, the sub-vector quantization algorithm is used to reduce the number of Gaussians being analyzed during any single frame by a factor of 12 during the first pass of the search [20, 25]. In this initial pass a short list of Gaussians is returned, determining the candidates from the full model to evaluate on the second pass of the search as potential matches for the current input frame. While this method does provide improvement over a direct analysis of the full model, the system still takes ~1.8X real time on a 1.7GHz AMD Athlon processor, requiring 800MB/sec main memory bandwidth [5].

#### **2.1.4 Feature Selection**

Another school of thought involves Feature Selection, in which specific features are used based on their impact on the likelihood calculations [26]. This method can reduce the amount of computation between 33% and 66% depending on how the features are defined [11, 27]. A basic method of Feature Selection is to only evaluate the low order Cepstral coefficients (c1~c9) and their 1<sup>st</sup> and 2<sup>nd</sup> derivatives while simply ignoring any data generated in the higher-order coefficients (c10~c13). This reduced or 'First 24' evaluation can be very effective for small dictionary tasks but as the amount of variability increases in the system, the effects of the highorder coefficients become more evident.

To account for this problem, work done at the University of Washington and AT&T's Bell Labs used data driven approaches to try and determine which information is most relevant and prune the search accordingly [11, 27]. In the University of Washington's approach, the D-dimensions were broken into 3 groups according to their importance in the calculation. First, a summation of the primary group is performed and compared to a preset threshold. If the summation has not crossed the threshold for a particular component, then that component is still considered a valid candidate and must be further analyzed using the secondary and tertiary sets, checking after each pass to ensure the on-going validity of the component. This system was able to speed up the process by 40% while only increasing the word error rate by 0.2% for the 1400 word TIMIT database [27]. In contrast, Bell Labs performed a full statistical analysis to find the 24 most important dimensions, and then removed the others from any calculation ever. This method has shown a 0.3% increase in word error rate, but provides less overall speed up than the University of Washington's system [11]. Both of these systems highlight a very interesting model for reduction of a static sub-set for use in the likelihood evaluation.

#### 2.1.5 Token Passing

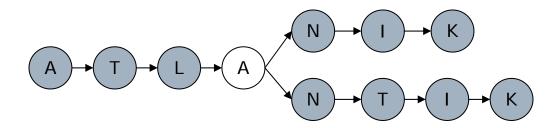

The token passing algorithm as described by Young [66], provides a methodology for controlling the flow of data within an ASR system in an optimal fashion. Rather than trying to optimize the calculations being performed by merging Gaussians or intelligently selecting features to operate on, this algorithm minimizes the total work done by the system by monitoring the active data in the system and only performing the operations necessary to update the active data. By considering each HMM in the system as a unique token and then stringing tokens together to create words, a tree-style architecture is created. This tree is then used to determine which tokens to calculate in the next turn based on the locations of the active tokens in the present turn. In the simple case shown in Figure 2 the un-shaded node (i.e. token) is active indicating that the two nodes connected to the active node need to be calculated next while the others do not.

Figure 2. A Simple Tree Structure

Using the token-passing scheme can result in substantial savings noting that in the simple example above only two of the 11 possible nodes are evaluated yielding an 82% reduction in the work done by the system. In systems with large dictionaries where the tree-structure can exceed 1,000 nodes, the amount of savings can be quite large and allows for a more precise evaluation of the active tokens since fewer total tokens need to be evaluated at a given time. This model has been widely accepted and is currently used with great success in systems from Carnegie Mellon University, the University of California at Berkley, the Helsinki University of Technology, and Tsinghua University in Beijing [6, 17, 29, 30, 31].

#### 2.2 COMERCIAL SOFTWARE SYSTEMS

As the personal computer began to evolve in the late 80's and early 90's many research organizations, both academic and corporate, started pursuing the idea of performing speech recognition on these platforms in attempts to make voice the primary means of data entry. These research efforts focused primarily on software-based algorithms that would be able to be run in conjunction with the computers operating system without causing severe memory access problems or other pipe-line stalls. The following section highlights a few of these research endeavors and provides a summary of their functionality and performance characteristics.

#### 2.2.1 IBM's Via Voice

One of the more successful commercial speech recognition products on the market today is the Via Voice system from IBM, originally designed for the 1996 DARPA HUB-4 evaluations [8]. This system is based on a set of 5.7K HMM states comprised of 170K Gaussians, and was trained using 35 hours of data from the broadcast news (BN) corpus distributed by the LDC for the DARPA evaluations. The feature extraction unit for Via Voice uses a 60-dimensional input vector as opposed to the standard 39-dimensional vector presented in [15] to achieve higher recognition rates in languages other than English, specifically Mandarin Chinese [32]. Via Voice also uses Speaker Adaptive Training (SAT) and Cluster Adaptive Training (CAT) models to increase the speaker variability of the recognition engine. The SAT and CAT models define different classes of speakers in terms of their gender, age, or dialect and when a new speaker begins to use the system the are assigned to one of the pre-defined groups and the phoneme models are adjusted accordingly. By adapting the knowledge base dynamically even the earliest incantations of the Via Voice system were able to achieve recognition rates over 83% for both English and Mandarin Chinese speakers.

#### 2.2.2 BBN's BYBLOS

Another popular commercial system BBN's BYBLOS, was also originally designed for the 1996 DARPA HUB-4 evaluations. This system only makes use of 4K three-state HMMs, but uses 64 Gaussians per state for a total of 768K Gaussians [34]. The earliest versions of BYBLOS had word error rates as high as 30% but as of the 1999 DARPA evaluations the error had been reduced to 15% [9, 33]. A sub-vector quantization algorithm is used during the first pass of the search to help minimize the amount of work done by the system and SAT models are also used to help adapt the system to a particular speaker. The original BYBLOS system ran on the standard 39-dimensional Cepstral vector, but later versions have been updated to accept multiple different sizes of input vectors allowing the end user to further customize the performance of the system. Recent versions of the system have also gotten away from the discrete densities used in the early manifestations and have become more speaker-independent with each new generation. In recent years, the BYBLOS recognition engine has been incorporated into a conference transcription and archive software suite called Rough'n'Ready with a dictionary of over 45K words [35]. This product can not only transcribe speech but can also archive the data it records by speaker, topic, or 'named entity'. The named entity archive method looks for specific words in a conversation, generally the name of a product or business account, and will file the transcription with a header attached to it such that it may be queried from the archive at a later date. The ability of this system to perform topic spotting as well as speaker identification sets this system apart from most other ASR systems on the market, but these abilities come at the cost of a system that runs at 40 times real time.

#### **2.2.3 SRI's DECIPHER**

The research team from SRI international has also been involved in developing speaker independent recognition software since the field first became a popular topic. The first cut of their DECIPHER system came out in 1989 as part of one of the earlier DARPA evaluations. This system uses the standard front-end (39 Mel-scaled Cepstra) and the widely accepted 3-state HMM models [7], but also incorporates a Gaussian Merging-Splitting Algorithm as described in [36]. Use of this algorithm allows for the models to be trained in a very simplistic manner,

providing both a shorter training cycle and a method by which the models can be adapted while the system is in operation. This allows the system to constantly learn new patterns as opposed to being limited to a finite set of speaker-groups as in the SAT and CAT training methodologies. During the 1989 DARPA evaluation the DECIPHER system was able to achieve recognition rates over 75% on a database of 1300 words and by the time the 1997 evaluations took place, the system was able to achieve recognition rates over 80% on a dictionary of 48,000 words. This system also benefits from the use of information from 4 different knowledge sources to derive the final probability of a given word. By combining the results of the evaluation with and without cross-word articulation models, as well as the 5-gram language model and the total number of hypothesis for a given recognition, DECIPHER is able to consistently recognize easily confusable words, and words with strong cross articulation effects [7].

#### 2.2.4 CMU's SPHINX

The SPHINX Large Vocabulary Continuous Speech Recognition (LVCSR) engine, designed by CMU, has for the past 15 years been one of the most successful research projects in the speech recognition industry. During the DARPA evaluations in 1989 the SPHINX-I system was able to recognize continuous speech from a 997 word vocabulary with between 70% - 95% accuracy using discrete HMMs [17]. By the 1992 DARPA, evaluations the SPHINX-II system had been developed using semi-continuous HMMs and applying an A\* search algorithm, as described by [39], to the language model. A\* is leading one-time computation algorithm used in path-finding research and has been shown to effectively minimize the portion of the search space that needs evaluation at a given time. By only focusing on area in the search space that are actually encountered as opposed to evaluating the entire space and then choosing the ideal path, the amount of calculation is reduced. While the performance of this algorithm does degrade as the path length increases is benefits are apparent noting that the SPHINX II system scored higher than any other in the evaluation with recognition rates consistently over 95% on a 5,000 word dictionary, setting the standard for future generations of software base speech recognition systems [28]. The SPHINX-II system was also one of the first systems to switch to the use of Mel-Frequency Cepstral Coefficients (MFCC) for the input feature stream as opposed to the previously accepted bi-linearly transformed LPC Cepstral coefficients.

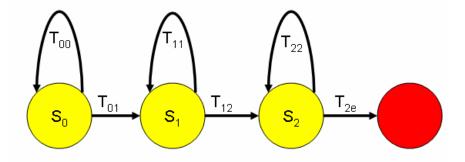

For the 1996 evaluations, the SPHINX-III system was introduced and by using continuous HMMs as well as multi-pass search strategy, was able to achieve greater than 85% for a dictionary of over 51,000 words [37, 38]. Another major improvement in the SPHINX-III system was the ability to choose different HMM topologies to formulate the phoneme models. This ability allows for a system that can be modified according the specific recognition needs of the application without having to redesign the entire knowledgebase. For example, in situations where the users are talking very quickly, co-articulation effects can be very severe and using a three-state topology may not be ideal. In a situation like this where the individual phonetic units may not have a clear beginning, middle, and end, the topology of the HMM can be altered to allow for transitions straight from the beginning to the end states as shown in Figure 3, where the solid lines represent the standard transitions and the dotted lines show the alternative transitions.

Figure 3. Sample HMM Topology

In addition to being one of the most consistently successful projects presented in the DARPA evaluations over the past 15 years, the SPHINX recognition engine has also been one of the more widely researched speech recognition engines with projects from research facilities such as the University of Utah and the University of Texas at Austin dedicated solely to the characterization and performance analysis of the SPHINX recognition engine as the golden model for the design of future ASR systems [5, 6]. Projects such as these as well as the continued research efforts of CMU have resulted multiple revisions and optimizations of the SPHINX-III platform all helping to create an industry benchmark system, able to perform large scale recognition tasks at near real-time speeds with very high levels of recognition accuracy.

The most recent revisions to the SPHINX project have been aimed at moving the code from a C++ design over to a JAVA based system. The SPHINX-4 project is a joint venture between Carnegie Mellon University, SUN Microsystems, and the Mitsubishi Electric Research Laboratory aimed at developing a speech recognition toolkit from which the end user could build their own custom speech recognition system based on the SPHINX recognition engine [40]. SPHINX-4 also benefits from a redesigned decoder architecture, the inclusion of a stand-alone graph construction module, and the application of the Bushderby classification algorithm to the language model. The graph construction module is responsible for creating and managing the trellis created as the tree-structure is evaluated over time. This module controls the transitions out of one tree and into another, and also the removal of branches as their probabilities become undesirable. This structure has been static in previous versions of the SPHINX system so by creation of the graph construction module, a new method for dynamic creation is introduced to the recognition engine, furthering its abilities to adapt to new scenarios and different applications. The Bushderby classification algorithm, described in detail in [41], is a direct extension of the Viterbi algorithm and by incorporating it into the langue model, the system gains the ability to classify mismatched data and adapt the system accordingly. The SPHINX-4 system is not currently finished and resultantly no quantification of the word error rates were available at the time of this paper but based on the success of the previous generations of the SPHINX recognition engine, SPHINX-4 promises to provide a user-friendly, highly customizable speech recognition platform capable of large-vocabulary recognition with impressive accuracy.

#### **2.3 CUSTOM HARDWARE ARCHITECTURES**

In recent years Application Specific Integrated Circuit (ASIC) architectures and embedded system design have become increasingly popular. As these systems become larger and more widely accepted the possibility to implement speech recognition on such devices has become an appealing alternative to the software based solutions currently on the market. Both the governmental and private sectors have spent significant amounts of money over the past decade attempting to determine the feasibility of a single-chip speech recognition engine, all the while fighting a battle between the amount of memory required to perform accurate recognition and the amount of logic required to fabricate such intelligent systems. The consistently improving computational ability of Field Programmable Gate Arrays (FPGAs) has allowed for a number of research institutions to experiment with the potential of these devices to be configured for speech recognition applications.

#### 2.3.1 Sensory Inc.

Sensory Inc. offers a single chip speech recognition microcontrollers based on a simple 8-bit microcontroller, the RSC-4128 [42, 43]. These systems have both onboard memory for storage of speaker-dependent models and off-chip storage for speaker independent models. In speaker independent mode the RSC-4128 is capable of recognizing a set of up to 20 words, while in speaker dependent mode the set size can be increased to 100. The number of possible sets of words in either mode is limited only by the size of the off-chip memory, but if no external memory is available then it is only possible to recognize a set of 10 speaker dependent words. The RSC device is also capable of using either HMM-based model or Neural Network Models depending on the desired user configuration. These devices also have word spotting and continuous listening capabilities, wherein the system will listen for one of a set of key-words and either enables a device based on that word or begin the recognition process from that word forward. While these devices do provide a good solution for small vocabulary speech recognition in real-time, they are limited in terms of their applications since the majority of speech recognition tasks require significantly more than 20 words. Unfortunately, word error rates are not widely published for these devices, but it is not expected that an 8-bit microcontroller is capable of performing with similar quality to a desktop system. This intuition is confirmed by the observation that Sensory's primary audience for their chips are the manufacturers of children's toys whose devices would not be hindered by mediocre recognition rates.

#### 2.3.2 University of Birmingham

The research group from the University of Birmingham in the United Kingdom has also produced promising results in the field of hardware-based speech recognition engines with a system they implemented on a Xilinx Virtex XCV1000 FPGA. While this system is only capable of recognition rates around 56% for the 500-word TIMIT knowledgebase it only occupies 45% of the entire device and is capable of performing at over 75X faster than real-time [46, 47]. A major reason for the reduced accuracy of this system lies in the use of mono-phones as the primary phonetic unit as opposed to bi- or tri-phones as are used in other commercially used systems [7, 37, 44, 46]. This choice was made in an attempt to prove the performance of the architecture while minimizing the amount of external memory required for basic recognition and serves well to highlight the impact that co-articulation effects have on continuous speech recognition. One of the primary goals of this project was to show the effectiveness of using an off-the-shelf FPGA as a dedicated speech co-processor, capable of perform the recognition at speeds much greater than real-time allowing for multiple input streams to be analyzed at once. The second generation of this design took advantage of the less than real time abilities of the preliminary system and was effectively able to process three speech file simultaneously. This new version of the architecture was released in both a mono-phone and a bi / tri-phone version, capable of speeds of 250X less than real-time and 13X less than real-time respectively [48]. Although this work provides a compact and efficient architecture for processing data in hardware based ASR systems, there are still obvious issues with respect the completeness of the knowledgebase and the overall scalability of the design that keep this research from providing a complete solution to the hardware speech recognition problem.

#### 2.3.3 University of California at Berkley

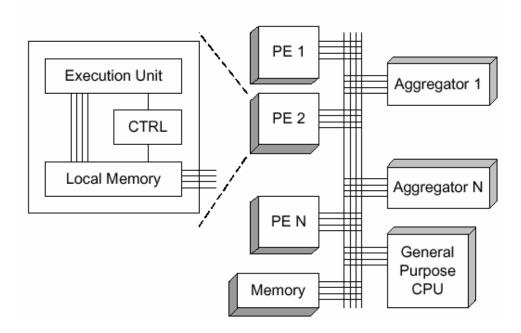

In 2003 the University of California at Berkley completed work on a custom ASIC design for a speaker independent recognition device capable of recognition rates over 80% for dictionaries up to 50 words [44, 45]. This project was aimed at creating a system capable of small vocabulary (< 100 words) focusing on low power considerations for handheld devices. Because of their small

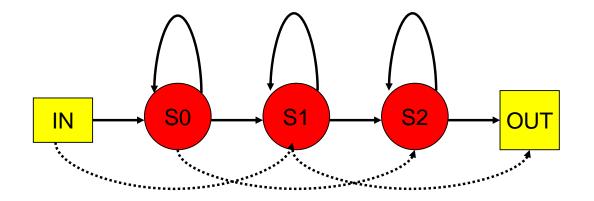

dictionary objective, the design team chose to implement a system based on a large array of identical processing elements connected to one another via aggregator units. The recognition system is based off of the traditional 3-state HMM topology for the phoneme models, and also uses a vector quantization algorithm to reduce the complexity of the Gaussian probability evaluations. As described in section 2.1 of this paper, it is the large amount of data that needs to be processed not the amount of work that needs done on the data that becomes the limiting factor. So by creating a system containing multiple identical blocks in parallel, the throughput can be greatly increased and the cycle count lowered. Using this ideology, the research group determined the number of processing elements, memories, and aggregators that could fit on onechip and worked backwards to determine the total number of nodes possible in the tree and subsequently the number of words allowable in the dictionary. By intelligently analyzing the language model for the given dictionary it was determined that the majority of the HMMs are only used in certain branches of the tree, enabling the HMMs in the knowledgebase to be clustered together into groups of highly associated nodes. By allowing each processing element to act only on HMMs within a given cluster, the routing of the data from one element to the next is greatly simplified and can be directly extracted from the tree-structure derived for a given dictionary. While this does reduce the complexity of the data path, the scheduling of the data on the busses, the intercommunication between aggregator nodes and the global control logic remain fairly complex alluding to potential problems as the design is scaled upwards. To help with this scheduling / synchronization issue, the computations within in a cycle are divided into two phases; first the aggregators and all nodes with no new inputs complete their operation, and secondly the nodes receiving data from other nodes or the aggregator are allowed to execute. To help further stream-line the operation of the system the token passing algorithm was employed to manage the communication and transfer of information between the aggregator nodes. Figure 4 shows the architecture of the designed decoder.

Figure 4. Diagram of Decoder Architecture

For achieving a low power system the design team utilized gated clocks as well as a single-cycle operation flow. This was possible since the system requires relatively slow clock speeds (< 5MHz) to run at real-time. Additionally, voltage scaling was used to further reduce the amount of power used by the system but this can only be applied to systems with moderate supply voltages, since the delay added by this measure become prohibitive as the supply voltage decreases. The Berkley system was able to achieve word accuracy rates as high as 80% for dictionaries under 50 words but was only able to achieve sentence accuracy around 25% [31]. This system provides a highly effective architecture for low power speaker independent recognition, but does not seem to offer the scalability required to adapt the architecture for large dictionary tasks.

#### 2.4 VECTOR PROCESSING ARCHITECTURES

Vector Processors have been a topic of major interest in recent years, with a number of major processor manufacturers beginning research on new vector processing architectures. From the new generation of VLIW and SIMD processors to fully-custom architectures such as the Cell processor from Sony, Toshiba, and IBM, the potential gains from parallel processing have become evident and the number of applications benefiting from this technology is constantly rising. Among the benefactor technologies, speech processing appears to have large potential gains from the use of parallel architectures, noting that the crux of the problem lies in the inability to exploit the inherent parallelism due to the limitations of the current generation of processors.

#### 2.4.1 VLIW Processors

Very Long Instruction Word (VLIW) processors provide a unique architecture for the development of speech recognition systems due to their ability to perform multiple instructions in a single cycle. Observing the latent parallelism in the speech recognition process, the ability to perform loop unrolling becomes obvious, allowing for a direct implementation in a VLIW architecture. As described in [49], the higher the number of instructions able to be implemented in parallel the greater the advantage of VLIW systems over other parallel architectures such as superscalar systems. Further, VLIW systems benefit from the fact that the scheduling of the instructions is performed by the compiler, as opposed to necessitating special hardware to perform this scheduling during run-time as in the superscalar architectures, leading to the need for less overall hardware in the design [50]. In a speech processing system the number of elements that can be operated on in parallel is quite large, hence the advantages of a VLIW become very evident, however this paradigm does saturate at some point due to the fact that the size of the device necessary to perform extremely large sets of data in parallel becomes prohibitively large. Another limiting factor for VLIW implementation lies in the need to perform both floating point and integer operations in large parallel groups. Due to the fact that VLIW systems require separate function units for each issue in the instruction word most traditional implementations reserve certain issues for integer operations and others for floating

point operations. For a speech processing system it is desired to have each issue be capable of executing both floating point and integer operations at different times, but this would require the inclusion of both integer and floating point ALUs, as well as a multiplexor to select between them. This leads to an architecture with double the number of ALUs of a traditional VLIW processor. For example if we derived an 8-wide VLIW with 4 memory read issues, 2 floating point issues, and 2 integer issues, during run-time half of the issues (2 memory and either both floating point or both integer) would be idle resulting in a significant amount of unused resources. This reduction in ability to fully utilize the device would lead to a system that functions more like a 4-wide VLIW than an 8-wide, which is an extremely undesirable result when the name of the game is massive parallelism. Even in heterogeneous systems where all function units are capable of all instructions, the necessity for a shared register file for the processor creates its own limitations. The shared register file does not scale well, resulting in the limitations that while VLIW processor perform well for widths less than 16, as the size of the processor increases the potential benefits start to decrease. In the research presented in [51] by R. Hoare, et al. at the University of Pittsburgh, a modified VLIW system is presented that incorporates dedicated hardware functions that can be executed along side the VLIW instructions to assist in the speed-up of algorithms that are not able to be efficiently implemented in sequential code. This research was able to speed up the GSM speech coding algorithm by 7X and shows a very interesting method for accelerating the operations of traditional VLIW processors. While the notion of dedicated hardware functions working in parallel with VLIW processors solves some of the problems found when trying to implement speech recognition on a VLIW platform. it does not provide a complete solution to the problem.

## 2.4.2 SIMD Processors

Another popular parallel architecture, Single Instruction Multiple Data (SIMD), takes a different approach to increasing Instruction Level Parallelism (ILP) from the VLIW architecture and gives a another perspective on how to implement speech recognition systems. In SIMD architectures, a single instruction is applied to all elements of an input vector, creating a system that can perform the same action on large amounts of data in a single cycle [52]. These systems can perform intra- as well as inter- element operations and also support saturation arithmetic, which is commonly used in video and signal processing algorithms. Some SIMD processors, such as the AltiVec processor are also capable of using a filter vector to rearrange the elements of the input vectors. Figure 5 illustrates the functionality of a SIMD processor with and with out the inclusion of the filter vector.

Figure 5. SIMD Processing With and Without Filter Vector

SIMD architectures fit the speech processing paradigm quite well since the majority of the parallelism observed in a speech recognition system occurs in the form of identical processing of large numbers of elements. Since this architecture only requires the construction of a single integer and a floating point ALU capable of vector ops, the necessary hardware need not share

registers as in the case of the VLIW. While SIMD processors seem to provide some additional benefits over VLIW systems, they are still restricted in the number of parallel elements that can be processed before the size of the hardware become a limiting factor.

A purely SIMD processor would also encounter some difficulties handling the word modeling process in an ASR system. This is largely due to the complexity of the data fetch that would need to occur in order to fill the input vectors with the proper amount of data to take full advantage of the SIMD processors capabilities. During the word modeling phase a tree structure, described briefly in Section 2.1.5, need to be evaluated resulting in the traversal of a large number of link-list style elements. Assuming that all of these lists are contained in unified memory bank, each active token in the system must be read and its corresponding link-list starting address decoded. Then, the addresses must be applied to the memory bank sequentially and the elements in the link-lists fed out of the memory and into the SIMD processors input vector buffer. The amount of overhead required to execute this process would render the full capabilities of the SIMD processor inactive during the time that the memory fetch was occurring, resulting in significant processor stalls. From this observation, it would seem that while the SIMD processor does provide a reasonable platform for the development of speech recognition systems, much like the VLIW processor discussed in Section 2.4.1 it only provides a partial solution to the entire problem, leading to the pursuit of other more ideal architectures.

# 2.4.3 Sony, Toshiba, IBM Cell Processor

During the first quarter of 2005, a joint research venture between Sony, Toshiba, & IBM filed the patent documents on a revolutionary processor architecture code-named Cell. The Cell processor takes a multi-core computing approach to System-on-Chip design, resulting in a network of eight Attached Processing Units (APUs) connected to a master Processing Unit (PU) via the Element Interface Bus (EIB) [53]. Figure 6 illustrates the overall architecture of the Cell processor.

Figure 6. Block Diagram of Cell Architecture

Each Cell processor is capable of 250 GFLOPS and has a 6.4 Gigabit/sec I/O bus to allow for the creation of ad-hoc networks of Cell processors to perform massively distributed processing operations. The master PU is based on the 4.6GHz 64-bit Power PC architecture with each of the APUs operating as a 4x32 (128 bit) SIMD processor with four integer and four floating point units, each capable of 32 billion operations per second. The eight APUs are set-up in a ring with shared memory banks between each APU as well as a common external RAM location attached to the EIB for use by all APUs. One of the truly unique and powerful capabilities of the Cell is the ability to run in stream mode. In stream mode, one of the APUs performs an action on some data and then puts it to a specified location in its shared RAM bank. The data is then immediately read out of the RAM bank by the other APU connected to the shared memory, processed further, and then written to the next shared memory. This process creates a constant flow of data between each APU allowing for highly pipelined processing to be executed, with a level of efficiency order of magnitude larger than any commercially available processor today. Additionally, the Cell is capable of accessing the external memory at well over 10 Gigabytes/sec,

which it highly advantageous in applications that require both extremely large amounts of memory and constant access to the memory, such as speech and other signal processing operations. Use of Cell processors for speech processing applications appears to solve both of the major problems encountered when designing ASR systems; the need for highly parallel processing and the need for extremely high throughput. Further this architecture has the benefits of both SIMD processors and VLIW processors; in that each of the APUs is in fact a SIMD unit, while having eight of them on one chip allows for the multi-functionality of a VLIW processor. Unfortunately it may be years before the research community gets access to the Cell chip on a level that will allow for the development of custom embedded systems based on this revolutionary processor architecture.

# 2.4.4 Stretch Inc. S5000 Chip Family