# POWER MANAGEMENT TECHNIQUES FOR CONSERVING ENERGY IN MULTIPLE SYSTEM COMPONENTS

by

Neven Abou Gazala

B.E., Arab Academy for Science and Technology, 1996M.E., Arab Academy for Science and Technology, 2000M.S., University of Pittsburgh, 2003

Submitted to the Graduate Faculty of the Department of Computer Science in partial fulfillment of the requirements for the degree of

## Doctor of Philosophy

University of Pittsburgh 2008

## UNIVERSITY OF PITTSBURGH DEPARTMENT OF COMPUTER SCIENCE

This dissertation was presented

by

Neven Abou Gazala

It was defended on

February 7th 2008

and approved by

Rami Melhem, Department of Computer Science, University of Pittsburgh Daniel Mossé, Department of Computer Science, University of Pittsburgh Bruce Childers, Department of Computer Science, University of Pittsburgh

Mary Jane Irwin, Department of Computer Science and Engineering, Penn State University

Dissertation Advisors: Rami Melhem, Department of Computer Science, University of Pittsburgh,

Daniel Mossé, Department of Computer Science, University of Pittsburgh

#### ABSTRACT

## POWER MANAGEMENT TECHNIQUES FOR CONSERVING ENERGY IN MULTIPLE SYSTEM COMPONENTS

Neven Abou Gazala, PhD

University of Pittsburgh, 2008

Energy consumption is a limiting constraint for both embedded and high performance systems. CPU-core, caches and memory contribute a large fraction of energy consumption in most computing systems. As a result, reducing the energy consumption in these components can significantly reduce the system's overall energy consumption. However, applying multiple independent power management policies in the system (one for each component) may interfere with each other and in some occasions increase the combined energy consumption.

In my thesis, I present three power management techniques that target more than a single component in a system. The focus is on reducing the total energy consumption in processors, caches and memory combinations. First, I present a memory-aware processor power management using collaboration between the OS and the compiler. The technique objectives are: (1) finish the application execution before its deadline and (2) minimize the combined energy consumption in processor and memory. Second, I present an integrated-DVS technique for processor and on-chip cache power management in multi-voltage domain systems. Integrated-DVS co-ordinates power management decisions across voltage domains rather that being applied in isolation in each domain. Third, I present a Power-Aware Cached DRAM (PA-CDRAM) memory organization for reducing the energy consumption in DRAM memory and off-chip caches. PA-CDRAM exploits the high internal memory bandwidth by bringing the off-chip caches "closer" to the memory, which improves both the overall performance and energy consumption.

The techniques in my dissertation highlight the importance of designing power management schemes that consider multiple components and their interactions (in terms of power and performance) in the system rather than applying multiple isolated power management polices. This study should lay the foundation for further research in the domain of integrated power management, where a single power manager controls many system components.

## TABLE OF CONTENTS

| 1.0        | IN  | <b>INTRODUCTION</b> 1                                            |    |  |

|------------|-----|------------------------------------------------------------------|----|--|

|            | 1.1 | Problem statement                                                | 2  |  |

|            | 1.2 | Contributions                                                    | 3  |  |

|            |     | 1.2.1 Memory-aware processor power management                    | 3  |  |

|            |     | 1.2.2 Integrated DVS policies for CPU and cache power management | 5  |  |

|            |     | 1.2.3 Power-aware Cached DRAM                                    | 5  |  |

|            |     | 1.2.4 Summary of contributions                                   | 6  |  |

|            | 1.3 | Thesis roadmap                                                   | 7  |  |

| 2.0        | BA  | CKGROUND AND RELATED WORK                                        | 8  |  |

|            | 2.1 | CPU power management using DVS                                   | 8  |  |

|            | 2.2 | Cache power management                                           | 10 |  |

|            | 2.3 | Power management in Multiple clock domains chips                 | 11 |  |

|            | 2.4 | DRAM power management                                            | 13 |  |

|            | 2.5 | Embedded DRAM                                                    | 15 |  |

| 3.0        | MO  | DELS                                                             | 16 |  |

|            | 3.1 | Real-time applications                                           | 16 |  |

|            | 3.2 | CPU energy model                                                 | 17 |  |

|            | 3.3 | Cache energy model                                               | 18 |  |

|            | 3.4 | Memory energy model                                              | 18 |  |

| <b>4.0</b> | CO  | MPILER AND OS COLLABORATION FOR CPU AND MEMORY                   |    |  |

|            | PO  | WER MANAGEMENT                                                   | 20 |  |

|            | 4.1 | Compiler and OS collaborative approach                           | 21 |  |

|            | 4.2 | PMP versus PMH placement strategy                                | 23 |  |

|            | 4.3 | Collaborative power management algorithm overview                | 26 |  |

|     | 4.4 | Compiler support for the Collaborative scheme                                                                                                                           |

|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |     | 4.4.1 Timing Extraction                                                                                                                                                 |

|     |     | 4.4.2 Placement of PMHs                                                                                                                                                 |

|     |     | 4.4.2.1 Sequential code                                                                                                                                                 |

|     |     | 4.4.2.2 Branches                                                                                                                                                        |

|     |     | 4.4.2.3 Loops                                                                                                                                                           |

|     |     | 4.4.2.4 Procedure calls                                                                                                                                                 |

|     |     | 4.4.3 PMH computation of $wcr_i$                                                                                                                                        |

|     |     | 4.4.3.1 Static PMH                                                                                                                                                      |

|     |     | 4.4.3.2 Index-controlled PMH                                                                                                                                            |

|     |     | 4.4.4 Example on the PMH placement and execution                                                                                                                        |

|     | 4.5 | OS Support for the Collaborative Scheme                                                                                                                                 |

|     |     | 4.5.1 Dynamic Speed Setting                                                                                                                                             |

|     |     | 4.5.1.1 CPU speed computation                                                                                                                                           |

|     |     | 4.5.1.2 Memory-aware speed setting $\ldots \ldots \ldots \ldots \ldots \ldots 36$                                                                                       |

|     |     | 4.5.2 Setting the PMP-interval                                                                                                                                          |

|     |     | 4.5.3 OS extensions                                                                                                                                                     |

|     | 4.6 | Evaluation                                                                                                                                                              |

|     |     | 4.6.0.1 Impact on energy and performance                                                                                                                                |

|     |     | 4.6.0.2 Run-time Overhead $\ldots \ldots \ldots$        |

|     | 4.7 | Conclusion                                                                                                                                                              |

| 5.0 | INT | TEGRATED DVS POLICIES FOR CPU AND CACHE POWER MAN-                                                                                                                      |

|     | AG  | <b>EMENT</b>                                                                                                                                                            |

|     | 5.1 | Introduction                                                                                                                                                            |

|     | 5.2 | Integrated DVS ( $IDVS$ ) policy $\ldots \ldots \ldots$ |

|     |     | 5.2.1 Motivation $\ldots \ldots \ldots$                 |

|     |     | 5.2.2 Integrated DVS architecture                                                                                                                                       |

|     |     | 5.2.3 MCD inter-domain interactions                                                                                                                                     |

|     | 5.3 | Online IDVS policy                                                                                                                                                      |

|     |     | 5.3.1 Limitation of the online IDVS policies                                                                                                                            |

|     | 5.4 | Machine Learning based IDVS approach                                                                                                                                    |

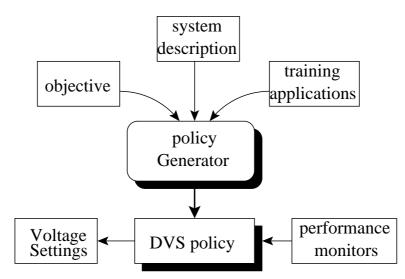

|     |     | 5.4.1 Overview of ML-IDVS approach                                                                                                                                      |

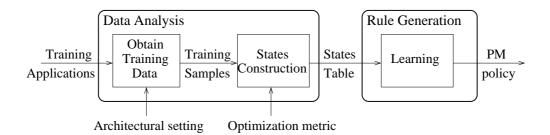

|     |     | 5.4.2 Construction of IDVS Policy                                                                               | 5 |

|-----|-----|-----------------------------------------------------------------------------------------------------------------|---|

|     |     | 5.4.2.1 Stage I: Data analysis $\ldots \ldots 6$ | 5 |

|     |     | 5.4.2.2 Stage II: IDVS policy learning                                                                          | 2 |

|     |     | 5.4.3 Design Issues                                                                                             | 3 |

|     | 5.5 | Evaluation                                                                                                      | 4 |

|     |     | 5.5.1 Experimental setup                                                                                        | 4 |

|     |     | 5.5.2 Evaluation of online-IDVS policy                                                                          | 6 |

|     |     | 5.5.2.1 Impact on performance and energy consumption $\ldots \ldots \ldots 7$                                   | 6 |

|     |     | 5.5.2.2 Varying system configurations                                                                           | 8 |

|     |     | 5.5.3 Evaluation of ML-IDVS approach                                                                            | 0 |

|     |     | 5.5.3.1 Impact on performance and energy consumption $\ldots \ldots \ldots 8$                                   | 1 |

|     |     | 5.5.3.2 Analysis of the training process $\ldots \ldots \ldots \ldots \ldots \ldots $ 8                         | 4 |

|     |     | 5.5.4 Online-IDVS versus ML-IDVS                                                                                | 5 |

|     |     | 5.5.4.1 Energy and delay savings                                                                                | 5 |

|     |     | 5.5.4.2 Discussion $\ldots$ 8                                                                                   | 6 |

|     | 5.6 | Conclusion                                                                                                      | 9 |

| 6.0 | PO  | WER-AWARE CACHED DRAM                                                                                           | 0 |

|     | 6.1 | Cached DRAM                                                                                                     | 1 |

|     | 6.2 | PA-CDRAM                                                                                                        | 2 |

|     |     | 6.2.1 DRAM-core power management                                                                                | 4 |

|     |     | 6.2.2 DRAM-core versus near-memory cache energy trade-off 9                                                     | 5 |

|     | 6.3 | PA-CDRAM implementation                                                                                         | 7 |

|     |     | 6.3.1 PA-CDRAM architecture                                                                                     | 7 |

|     |     | 6.3.2 Near-memory cache controller                                                                              | 8 |

|     |     | 6.3.3 PA-CDRAM operation                                                                                        | 9 |

|     | 6.4 | Energy and delay modeling of PA-CDRAM                                                                           | 2 |

|     | 6.5 | Evaluation of PA-CDRAM                                                                                          | 4 |

|     |     | 6.5.1 Methodology                                                                                               | 5 |

|     |     | 6.5.2 Energy and delay                                                                                          | 7 |

|     |     | 6.5.2.1 Effect on delay                                                                                         | 7 |

|     |     | 6.5.2.2 Effect on energy consumption                                                                            | 8 |

|     |     | 6.5.3 Near-memory versus near-processor caches                                                                  | 0 |

|     |             | 6.5.4  | Cache controller location                                                                                                                    |

|-----|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

|     |             | 6.5.5  | Effect of multiprocess and multithreaded environments                                                                                        |

|     |             | 6.5.6  | Sensitivity to design parameters                                                                                                             |

|     |             |        | 6.5.6.1 Effect of varying the cache size                                                                                                     |

|     |             |        | 6.5.6.2 Effect of varying the CPU frequency                                                                                                  |

|     |             |        | 6.5.6.3 Effect of logic slowdown                                                                                                             |

|     |             |        | 6.5.6.4 Effect of CPU and memory bus bandwidth                                                                                               |

|     | 6.6         | Discu  | ssion $\ldots \ldots \ldots$ |

|     | 6.7         | Concl  | usion $\ldots \ldots 121$    |

| 7.0 | CO          | NCLU   | SIONS AND FUTURE WORK                                                                                                                        |

|     | 7.1         | Concl  | usions $\ldots \ldots 123$   |

|     | 7.2         | Futur  | e Work                                                                                                                                       |

| AP  | PEN         | DIX.   | DERIVATION OF DVS FORMULAS                                                                                                                   |

|     | A.1         | Deriva | ation for Proportional closed-form equation                                                                                                  |

|     |             | A.1.1  | Derivation for Lemma 1                                                                                                                       |

|     |             | A.1.2  | Derivation of Proportional closed-form formula                                                                                               |

|     | A.2         | Deriva | ation for Greedy closed-form equation                                                                                                        |

|     |             | A.2.1  | Derivation for Lemma 2                                                                                                                       |

|     |             | A.2.2  | Derivation of the Greedy closed-form formula                                                                                                 |

| BIB | <b>SLIO</b> | GRAF   | РНҮ133                                                                                                                                       |

### LIST OF TABLES

| 2.1 | Examples on CPU power management schemes                                              | 8   |

|-----|---------------------------------------------------------------------------------------|-----|

| 4.1 | Adverse combinations of code structure for some PMP placement strategies              | 25  |

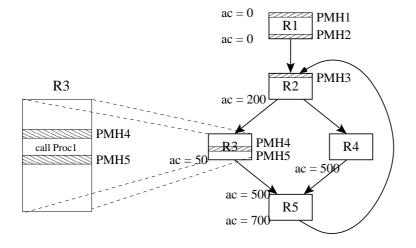

| 4.2 | Profiled <i>wcc</i> for each region in CFG shown in Figure 4.6                        | 33  |

| 4.3 | Other profiled information for CFG shown in Figure 4.6                                | 33  |

| 4.4 | The inserted PMHs details.                                                            | 34  |

| 4.5 | Simplescalar configuration                                                            | 40  |

| 4.6 | The power levels in the Transmeta processors model                                    | 41  |

| 4.7 | The power levels in the Intel XScale processor model.                                 | 41  |

| 4.8 | The number of executed PMPs, PMH and speed changes for the sub-band tuner             | 52  |

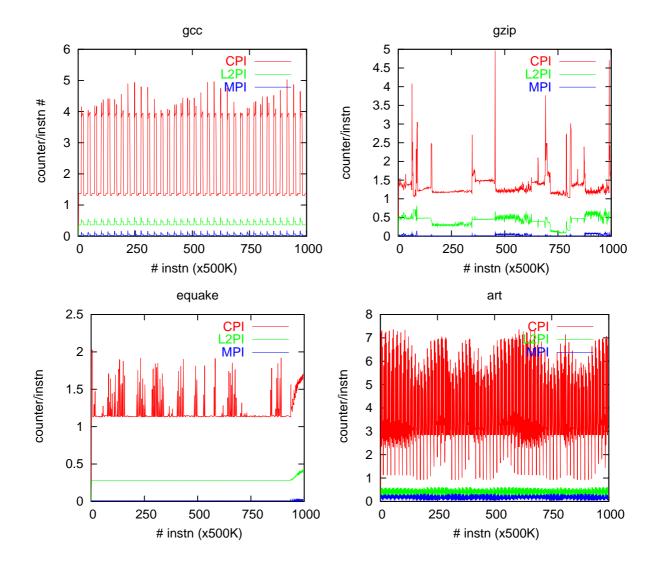

| 5.1 | Percentage of time intervals that experience positive feedback scenarios in some      |     |

|     | MiBench and SPEC2000 benchmarks.                                                      | 60  |

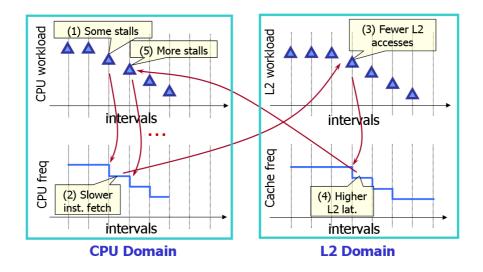

| 5.2 | Rules for adjusting core and L2 cache speeds in local DVS policy and proposed policy. | 62  |

| 5.3 | Eight training samples: CPI (C), L2PI (L) and energy-delay product (ED) at all        |     |

|     | frequency combinations.                                                               | 68  |

| 5.4 | Constructed $ST$ from samples in Table 5.3                                            | 71  |

| 5.5 | Example of a policy to minimize energy-delay product                                  | 73  |

| 5.6 | Simulation configurations                                                             | 75  |

| 5.7 | Variants of our proposed policy: actions of setting the core voltage $(V_c)$ and the  |     |

|     | cache speed $(V_{\$})$ in rules 1 & 5 from Table 5.2                                  | 78  |

| 5.8 | Comparison of online-IDVS and ML-IDVS                                                 | 88  |

| 6.1 | PA-CDRAM cache commands send across the control bus                                   | 100 |

| 6.2 | System configuration                                                                  | 107 |

| 6.3 | Per-access latency and energy break down of L3 and near-memory caches                 | 110 |

| 6.4 | PA-CDRAM energy consumption normalized to the base case when running appli- |

|-----|-----------------------------------------------------------------------------|

|     | cation pairs interleaved                                                    |

### LIST OF FIGURES

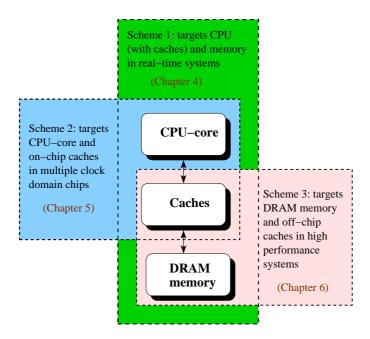

| 1.1  | Proposed power management techniques targeting more than one system component.   | 4  |

|------|----------------------------------------------------------------------------------|----|

| 2.1  | Example of domain partitions in MCD processors [1, 2]                            | 12 |

| 4.1  | (a) Sample CFG. (b) Invocations of PMHs & PMPs for executing the bold path in    |    |

|      | (a)                                                                              | 22 |

| 4.2  | Some PMP placement strategies and their adverse cases of code structure (See Ta- |    |

|      | ble 4.1 for description)                                                         | 24 |

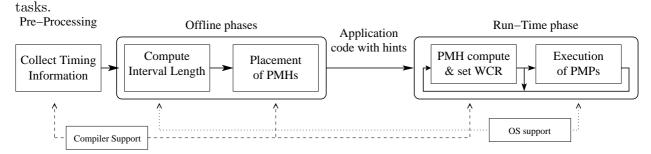

| 4.3  | Phases of the collaborative power management scheme                              | 26 |

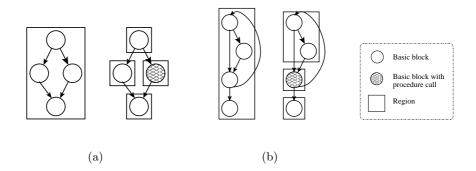

| 4.4  | Examples on region segmentation for (a) branches and (b) loops, with and without |    |

|      | procedure calls.                                                                 | 28 |

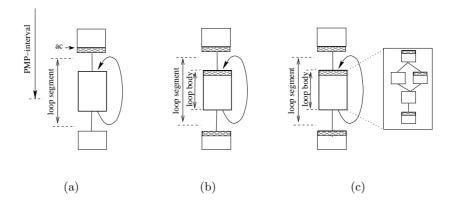

| 4.5  | PMH placement in loops when (a) ac+loop_segment > PMP-interval, (b) loop_body    |    |

|      | $<$ PMP-interval $<$ loop_segment, and (c) loop_body $>$ PMP-interval            | 31 |

| 4.6  | Example of the PMH placement in a simple CFG.                                    | 33 |

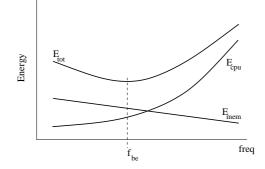

| 4.7  | Lowest total energy consumption at break-even frequency                          | 36 |

| 4.8  | ISR pseudocode for PMPs.                                                         | 39 |

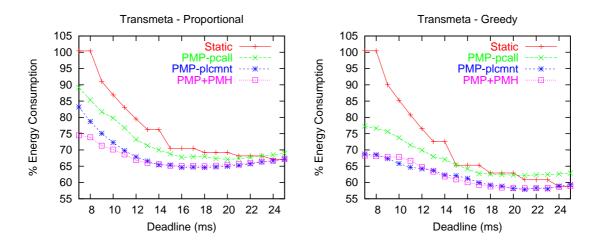

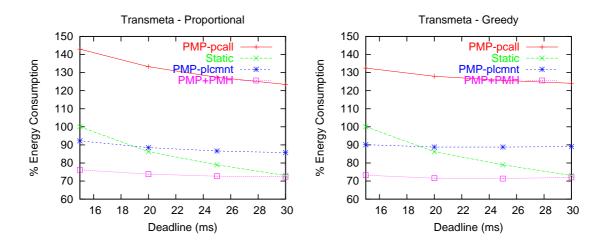

| 4.9  | ATR: Total (CPU+memory) energy consumption normalized to no power manage-        |    |

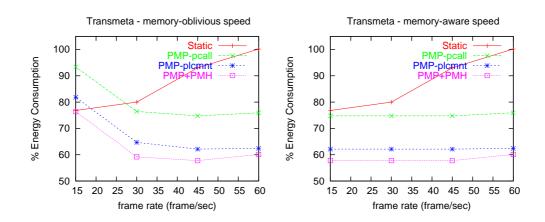

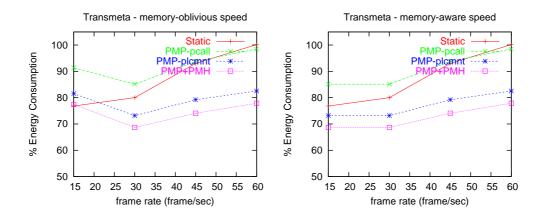

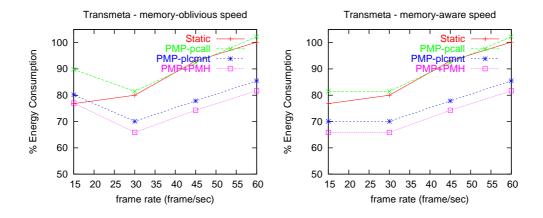

|      | ment on Transmeta Crusoe.                                                        | 43 |

| 4.10 | ATR: Total (CPU+memory) energy consumption normalized to no power manage-        |    |

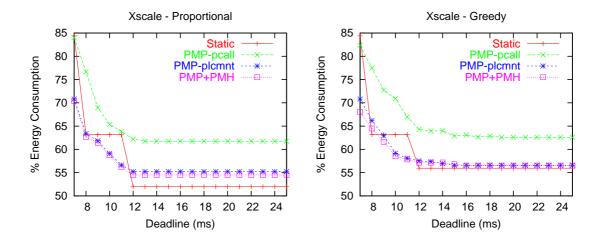

|      | ment on Intel XScale.                                                            | 44 |

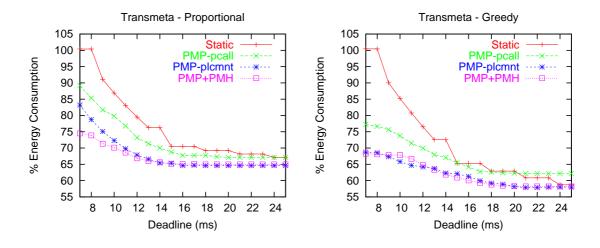

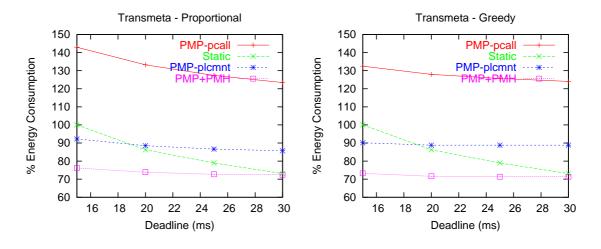

| 4.11 | MPEG2 decoder: Total energy consumption normalized to no power management        |    |

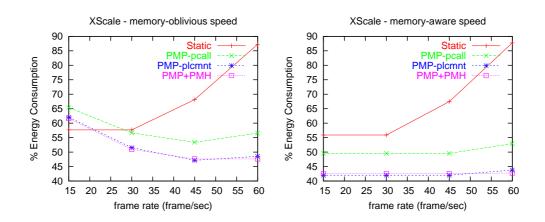

|      | scheme on Transmeta Crusoe                                                       | 47 |

| 4.12 | MPEG2 decoder: Total energy consumption normalized to no power management        |    |

|      | scheme on Intel XScale.                                                          | 48 |

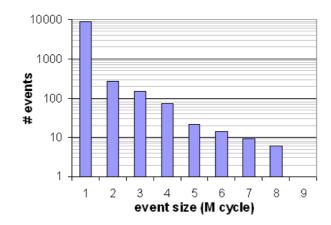

| 4.13 | Size distribution (in million cycles) for the sub-band filter events             | 49 |

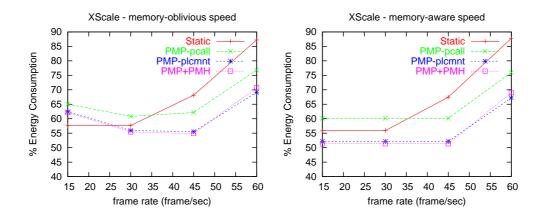

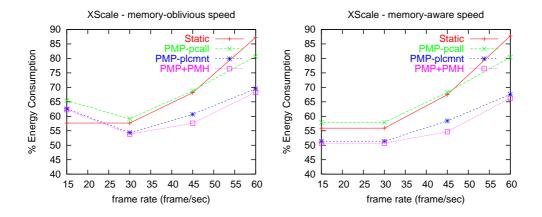

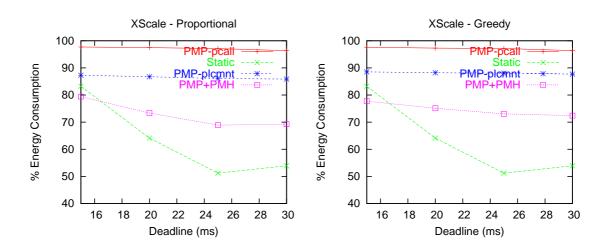

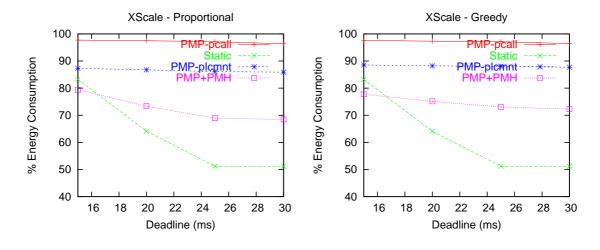

| 4.14 | Sub-band Tuner: Total energy consumption normalized to no power management                    |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | scheme on Transmeta Crusoe                                                                    | 51 |

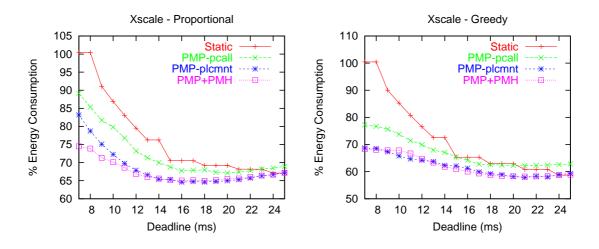

| 4.15 | Sub-band Tuner: Total energy consumption normalized to no power management                    |    |

|      | scheme on Intel XScale model.                                                                 | 52 |

| 5.1  | Variations in application phases throughout execution                                         | 57 |

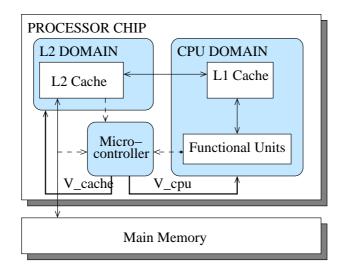

| 5.2  | Example of an MCD processor design with integrated DVS control                                | 59 |

| 5.3  | Example of positive feedback in local power management in each domain                         | 60 |

| 5.4  | Information flow in ML-IDVS                                                                   | 65 |

| 5.5  | Stages for automatic DVS policy generation.                                                   | 66 |

| 5.6  | Acc construction pseudocode                                                                   | 69 |

| 5.7  | ST construction pseudocode to minimize energy-delay product                                   | 70 |

| 5.8  | Energy and delay of Local-DVS and our online-IDVS relative to no-DVS policy in                |    |

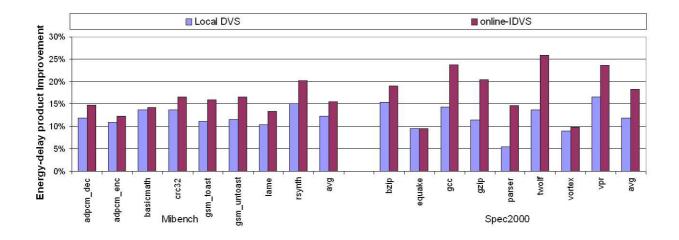

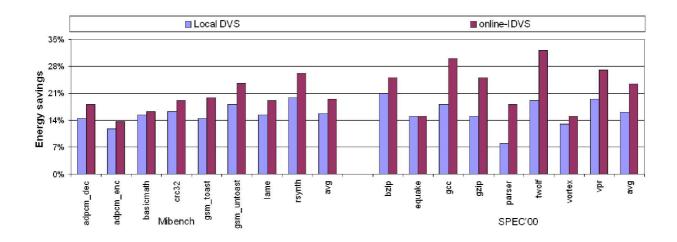

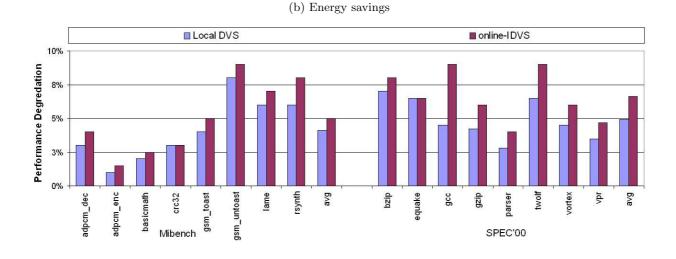

|      | configuration A and two voltage domains processor.                                            | 77 |

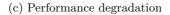

| 5.9  | Average degradation in energy-delay product relative to the local-DVS policy                  | 79 |

| 5.10 | Energy and delay for local-DVS and online-IDVS policy relative to no-DVS policy               |    |

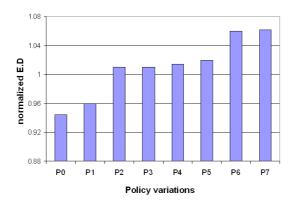

|      | for processors with (a) two domains and (b) six domains. $\ldots \ldots \ldots \ldots \ldots$ | 80 |

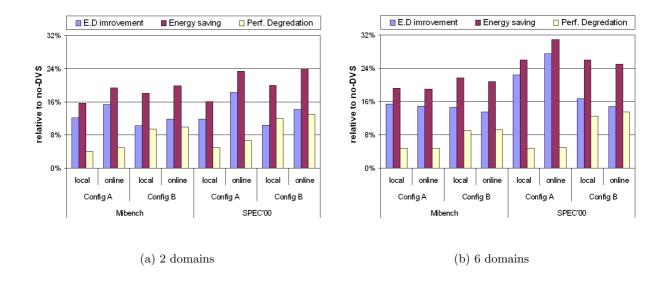

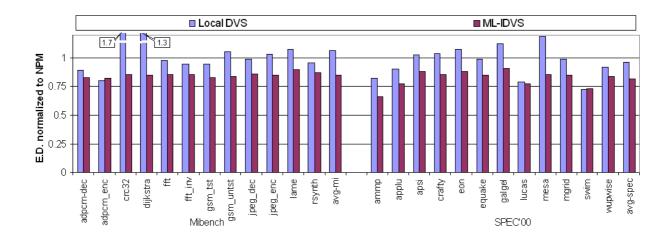

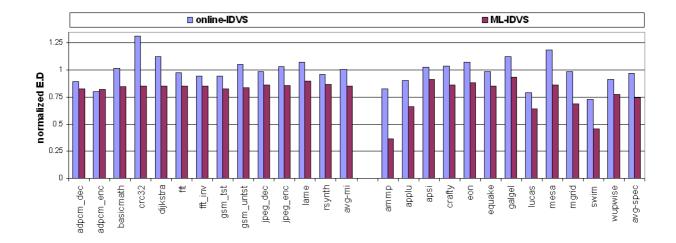

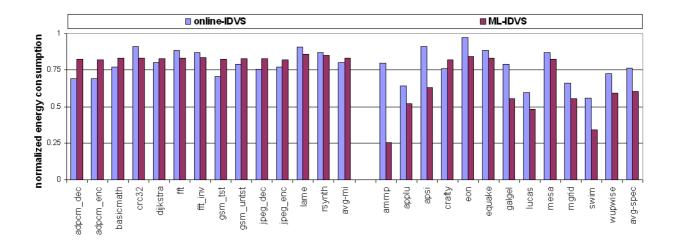

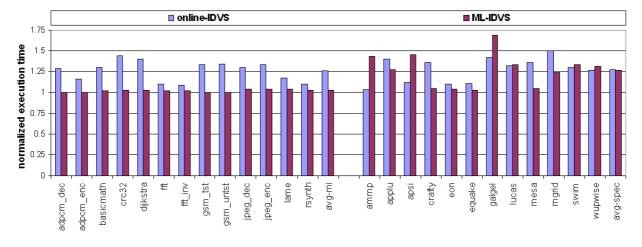

| 5.11 | Energy-delay product for SPEC2000 and MiBench benchmarks when using local-                    |    |

|      | DVS versus ML-IDVS.                                                                           | 82 |

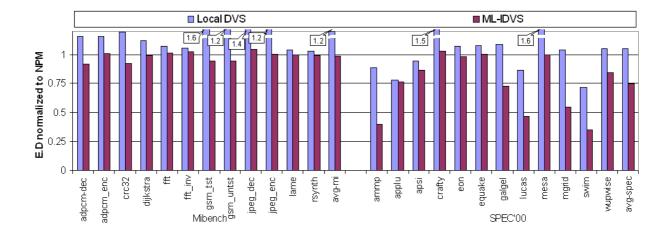

| 5.12 | Energy-delay product when optimizing energy with delay bound                                  | 83 |

| 5.13 | Energy-delay product for policies running on system with configuration Config B in            |    |

|      | Table 5.6.                                                                                    | 83 |

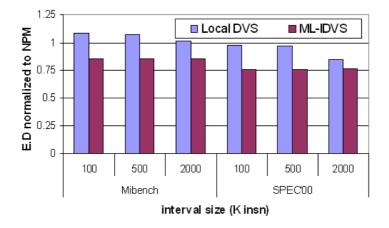

| 5.14 | Average energy-delay product at different DVS control-interval sizes (using Config A).        | 84 |

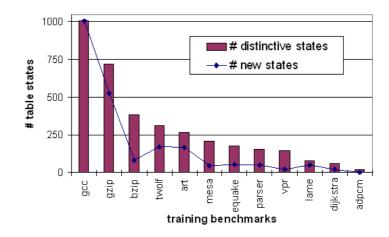

| 5.15 | ST coverage                                                                                   | 85 |

| 5.16 | Online-IDVS versus ML-IDVS normalized to no-DVS                                               | 87 |

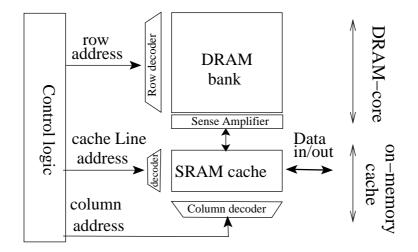

| 6.1  | Functional block diagram of a CDRAM                                                           | 92 |

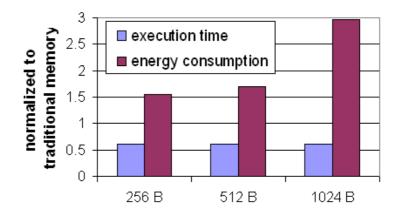

| 6.2  | Average performance and energy consumption for different near-memory cache block              |    |

|      | sizes                                                                                         | 94 |

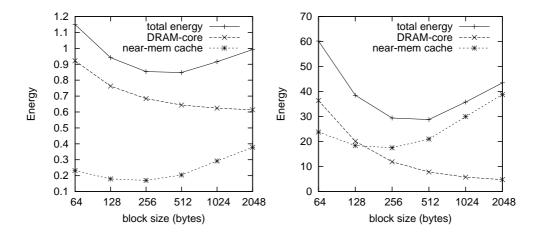

| 6.3  | The effect of different cache block sizes on the memory energy consumption for the            |    |

|      | CPU-intensive $bzip$ (left) and the memory-intensive $mcf$ (right)                            | 96 |

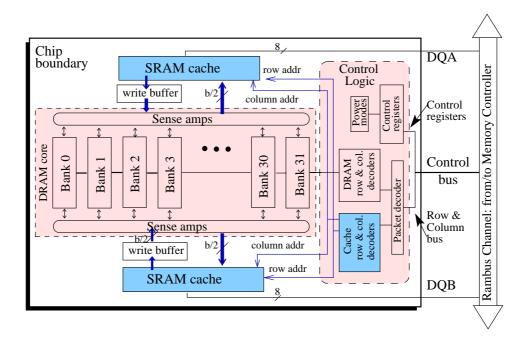

| 6.4  | Functional block diagram of a PA-CDRAM. Dark blocks are the added components                  |    |

|      | to an RDRAM architecture.                                                                     | 98 |

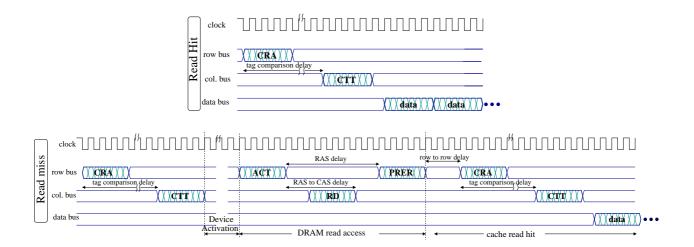

| 6.5  | Timing diagram of the Rambus channel for near-memory cache read hit (upper) and                                                                                                                            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | read miss (lower) transactions                                                                                                                                                                             |

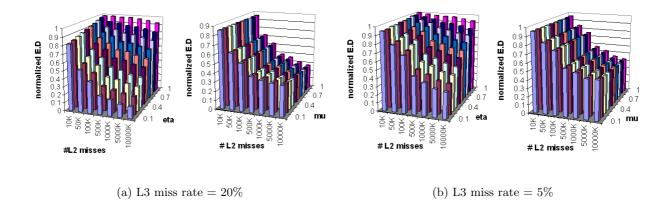

| 6.6  | The effects of varying $\eta$ and $\mu$ on the energy-delay product $\ldots \ldots \ldots$ |

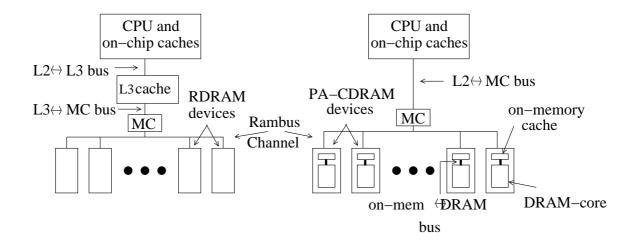

| 6.7  | Memory organizations of the base case (left) and the proposed PA-CDRAM (right). 106                                                                                                                        |

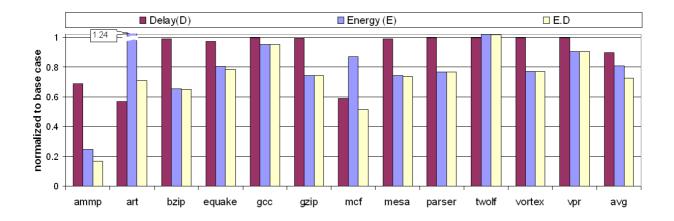

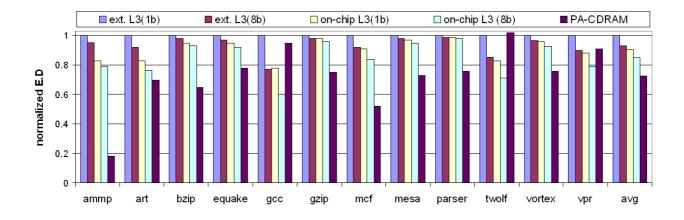

| 6.8  | PA-CDRAM energy-delay break down normalized to the base case                                                                                                                                               |

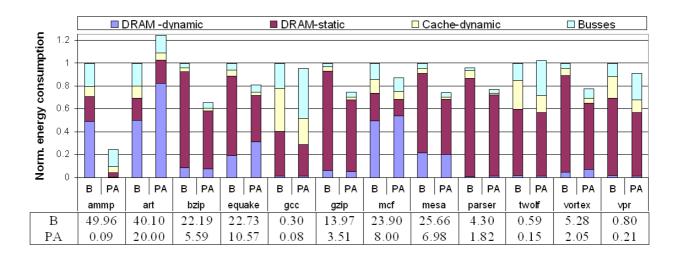

| 6.9  | PA-CDRAM and the base case energy break down and cache miss rates $\ldots$ 109                                                                                                                             |

| 6.10 | Energy-delay product of near memory versus near-processor cache organizations nor-                                                                                                                         |

|      | malized to the base case                                                                                                                                                                                   |

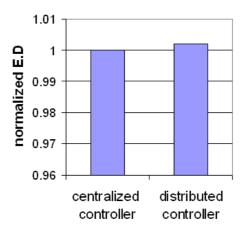

| 6.11 | Energy-delay product of distributed controller normalized to centralized cache con-                                                                                                                        |

|      | troller design                                                                                                                                                                                             |

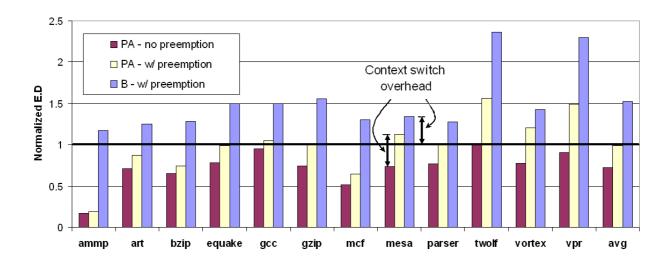

| 6.12 | Energy-delay product with and without pre-emption, normalized to the base case                                                                                                                             |

|      | without preemption                                                                                                                                                                                         |

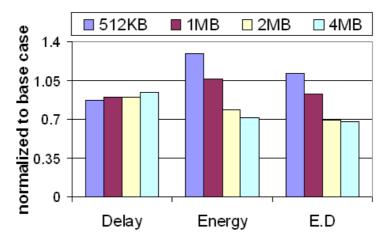

| 6.13 | The effect of varying the cache size on execution time, energy and energy-delay                                                                                                                            |

|      | product normalized to the base case                                                                                                                                                                        |

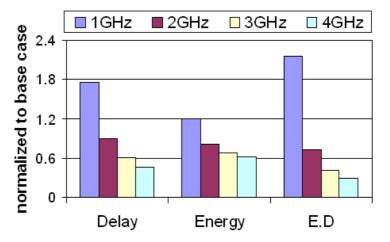

| 6.14 | The effect of varying the CPU frequency for the PA-CDRAM, normalized to the base                                                                                                                           |

|      | case on execution time, energy and energy-delay product                                                                                                                                                    |

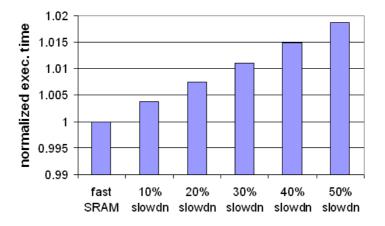

| 6.15 | The effect of the logic slowdown in the near-memory cache on the total execution                                                                                                                           |

|      | time normalized to fast SRAM case                                                                                                                                                                          |

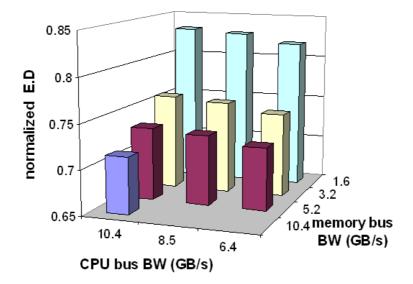

| 6.16 | The effect of different CPU and memory bus bandwidth                                                                                                                                                       |

#### 1.0 INTRODUCTION

Energy consumption is a limiting constraint for both embedded and high performance systems. In embedded systems, the operational lifetime of a device is limited by the rate of energy dissipation from its battery. On the other hand, energy consumption in high-performance systems increases thermal dissipation, which requires more cooling resources, and thus higher system management overhead. Among the major energy consumers in computing systems are the CPU and memory subsystems. In high performance systems such as servers, CPU and memory consume up to 50% [3] and 41% [4], respectively; while in portable devices they consume 26% and 23%, respectively [5].

The continuous demand for more computing power motivates the design of more sophisticated processors. With the increase in system's computing capabilities, power dissipation is expected to rise proportionally in these systems [6]. Moreover, increasing the computing capability would potentially increase workload on the memory system, thus increasing its power dissipation as well. Accordingly, this increase in power dissipation motivates the need for more efficient system-wide power management schemes.

Reducing the energy consumption in computing systems has become a prime design criterionmotivated by the limited lifetime of battery operated systems, and the high electrical and cooling power costs in server farms. Processor and memory subsystems contribute a large fraction of the overall system power dissipation. The fraction of the processor energy compared to the memory energy varies based on the system parameters (memory size, processor core complexity) and on the application behavior (memory versus CPU intensive). As a result, to achieve overall low system energy, choosing an appropriate power management technique should be based on the fraction of the power consumed by each.

Applying power management techniques often involves a trade-off between performance and energy consumption. Thus, a power management scheme should consider this trade-off in addition to existing application and system performance constraints. Application performance constraints can be a result of a limitation in the available time for application execution, as in *real-time systems*. System constraints are the result of performance bottleneck(s) in one or more of the system components (as in memory and I/O subsystems).

A major constraint imposed on computing systems is the increasing speed gap between processor and memory. This speed difference limits the overall system performance. The main contributors to this problem are the large memory access time and the limited transfer bandwidth between the memory and the CPU [7]. Memory architectures aim at decreasing the access time by using faster clocks and increasing the level of concurrency in data accesses. However, the bus transmission speed is becoming a significant bottleneck limiting the memory system performance [8]. Thus, systems —especially with large memory traffic— face the problem of minimizing this speed gap to achieve high performance while consuming less energy.

Independently managing power in one system component while neglecting other component's power may not necessarily achieve lower combined energy consumption for the entire system. For example, slowing down the processor to save its energy increases the execution time and causes memory to retain data for longer periods, thus consuming more memory's energy. Hence, an effective power management scheme should consider multiple system components for optimizing the system's total energy consumption.

#### 1.1 PROBLEM STATEMENT

Power dissipation in CPU, caches and memory accounts for the majority of total power consumption in most computing systems. Components that consume large percentage of the overall system's energy consumption are good targets for power management.

The objective of applying power management policies is to ideally optimize the overall system energy consumption rather than reduce energy consumption of one component. The majority of power management policies proposed in the literature address the energy problem for one system component. While these policies can locally minimize energy consumption for a component, being oblivious to the overall system power may adversely affect other system components by increasing their energy consumption. As a result, the system's overall energy savings is lower. For example, dynamic voltage scaling in processors slowdown execution of a process. Accordingly, this increases energy consumption in the memory system, and the I/O devices associated with a process due to the extension of their active periods. Thus, to achieve higher energy savings for the entire system, the power management technique should take into account the resulting effects on the other components in the system or even target more than one system component simultaneously.

We address the problem of achieving efficient power management in more than one system component simultaneously. The main focus of our study are CPU, caches and main memory energy consumption. We propose three power management techniques with the objective of reducing the combined energy consumption in multiple components with minimal impact on performance.

#### 1.2 CONTRIBUTIONS

In this dissertation, we present three power management techniques. The common feature among the techniques is that they reduce the combined energy consumption of at least two system components. Each of these techniques addresses a particular class of systems.

For systems with dominant processor power consumption, we propose a scheme that primarily targets the CPU energy consumption without consuming excessive memory energy. We approach this problem in the context of real-time systems where timing constrains are critical. For systems with comparable processor and cache energy consumption, we propose a second scheme that manages both the CPU and the on-chip caches simultaneously. This technique is feasible in modern chips with multiple clock and voltage domains, where the clock and voltage of each domain is controlled independently. The third scheme targets the memory and off-chip cache energy consumption while improving the overall system performance. This technique is intended for systems where memory energy dominates the total system energy. Figure 1.1 summarizes the focus and domain of each of the three proposed techniques. A brief overview of each scheme is presented next.

#### 1.2.1 Memory-aware processor power management

Dynamic Voltage Scaling (DVS) is an effective technique for reducing power dissipation in processors. DVS slows down the processor's speed to lower its energy consumption. Because some applications must finish by a certain deadline, the objective of a power management scheme employing this technique is to efficiently use the available slack (time when processor is idle) to reduce

Figure 1.1: Proposed power management techniques targeting more than one system component.

the processor's frequency without violating an application's timing constraints. More slack utilization implies more slowdown and thus more processor energy savings. On the other hand, excessive slowdown in processor speed increases the time where the memory stays active, which increases the system's overall energy. Thus, finding an efficient operating frequency that balances these trade-offs is essential to reduce the system's overall energy.

To maximize the amount of detected slack in the system, we take advantage of dynamic slack, which is the slack resulting from applications running for shorter times than their worst case execution times. This is different than static slack which is known offline (the difference between the worst case execution time and an application's deadline). To detect and utilize dynamic slack, we use the compiler knowledge of the state of execution of an application. The compiler inserts special hints in the application code. These hints are capable of computing–at run-time– the worst case remaining cycles for the application to finish execution at each hint location. At run time, information from the hints is passed to the operating system to periodically schedule the proper speed based on the combined available static and dynamic slacks. To avoid excessive slowdown of the application's execution, and hence increasing the memory's energy, we compute a cut-off frequency below which the processor should not operate. This cutoff frequency represents the break-even point where further slowdown causes the energy savings in the processor to be less than the additional energy consumed in memory. We model the processor and memory energies to compute this cut-off frequency based on processor and memory parameters.

The main contributions of this work are: (1) describe an approach where the OS and compiler collaborate to extract information useful for building more efficient power management policies, and (2) determine the cut-off frequency beyond which the overall system energy increases despite decrease in the CPU energy. More details on this work in presented in Chapter 4.

#### 1.2.2 Integrated DVS policies for CPU and cache power management

When the fractions of power consumed by the processor and memory are comparable, we should target both components simultaneously, focusing on the interplay of power management in both subsystems. In this scheme, we are especially concerned with the processor and the on-chip caches.

In multiple clock and voltage domain chips, we propose an integrated technique for controlling the voltage/frequency of each of the domains. The integrated technique is more efficient than its local counterpart because it considers interactions among domains. In our proposed policies, we focus mainly on the CPU-core and L2 cache domains. We first propose a generic online heuristicbased integrated DVS policy that suits most application classes. We then proposed a machine learning approach that generates DVS policies optimized for each class of applications.

This work shows that integrated DVS policies are more energy efficient than local DVS policies that target different domains in isolation. This efficiency is primarily due to the global knowledge of the workload and power dissipation in different chip domains. That global knowledge allows the policy to make better informed decisions with respect to selecting the best speeds for each domain. More details on this work in presented in Chapter 5.

#### 1.2.3 Power-aware Cached DRAM

Dynamic power management in memory can indirectly influence the processor's energy consumption when applications experience performance degradation due to increased average memory access latency. This increase is a result of extra delay experienced from transitioning the memory to low power states. Longer execution time implies that the processor resources have to be active for longer periods, thus consuming more energy. On the other hand, memory has a huge internal bandwidth compared to its external bus bandwidth. To exploit the wide internal bus, cached DRAM (CDRAM) adds an SRAM cache to the DRAM array on the memory chip. Such a near-memory cache acts as an extra memory hierarchy level, whose fast latency improves the average memory access time and potentially improves system performance. However, proposed CDRAM organizations do not necessarily optimize the system energy due to the extra energy consumed in the near-memory caches.

In our work, we investigate the effect of placing a subset of the total cache capacity closer to the memory rather than closer to the CPU. We are especially interested in overall performance and energy consumption. We optimize the CDRAM organization for energy efficiency. We integrate a moderately sized cache within the chip boundary of a power-aware multi-banked memory. We call this organization power-aware cached DRAM (PA-CDRAM). In addition to improving performance, PA-CDRAM significantly reduces energy consumption in caches and in main memory. This is due to (1) using small caches distributed to the memory chips reduces the cache access energy compared to using a large non-distributed cache, (2) near-memory caches allow the access of relatively large blocks from memory, which is not affordable with near-processor caches, and (3) memory energy consumption is reduced by having longer memory idle periods during which DRAM banks can be powered off. PA-CDRAM improves the original CDRAM by tackling the interplay of the cache and memory organizations to optimize the memory's performance and energy consumption. The contribution of this part of the work is twofold. First, we propose near-memory caches for energy reduction of the overall system. Second, we describe an implementation of PA-CDRAM that integrates a near-memory cache in a Rambus chip (RDRAM). We also describe how our implementation can maintain backward compatibility with existing Rambus memories. More details on this work in presented in Chapter 6.

#### **1.2.4** Summary of contributions

To summarize, the contributions of this dissertation work are:

- We present a collaboration scheme between operating system and compiler for a memory-aware CPU power management technique for real-time systems. This technique is more efficient than a compiler-only and OS-only schemes because it can extracts more information about the system and use it more efficiently.

- We propose a class of integrated DVS techniques for reducing energy consumption in both CPU-

core and L2 caches for multiple clock domains. The integrated DVS technique is more energy efficient than local DVS techniques due to its global knowledge of both power and activity of the target components.

• We devise an architectural optimization for improving the energy consumption in DRAM memory and off-chip caches, called PA-CDRAM, in high performance systems. PA-CDRAM improves both overall performance and energy consumption over traditional memory hierarchy.

#### 1.3 THESIS ROADMAP

The remainder of this dissertation is organized as follows. Chapter 2 reviews background and some related work to power management techniques that target CPU, caches and memory energy consumption. Chapter 3 introduces the main models used throughout this work. Our proposed policy for memory-aware CPU power management is presented in Chapter 4, followed by techniques for integrated CPU and cache power management in Chapter 5. Our technique for improving performance and reducing energy consumption in DRAM memory and off-chip caches is presented in Chapter 6. Chapter 7 summarizes and concludes our thesis.

#### 2.0 BACKGROUND AND RELATED WORK

#### 2.1 CPU POWER MANAGEMENT USING DVS

An efficient power saving technique for processors dynamically changes the CPU supply voltage according to current workload. This technique is called *dynamic voltage scaling (DVS)*. Reducing voltage in CMOS circuits reduces the processor's power consumption quadratically. Because the processor clock frequency is dependent on the supply voltage, reducing the voltage causes a program to run slower. However, this slowdown is linear with the supply voltage. Since, the dynamic energy consumed by an application is the product of the CPU power and time spent running an application, running a program with reduced voltage and frequency leads to significant energy savings.

DVS techniques can be classified into schemes that use information about tasks' deadlines and schemes that maintain an acceptable performance degradation to achieve significant energy savings. Orthogonally, speed scheduling in DVS algorithms can be controlled by either the OS or the compiler/application. Table 2.1 lists some power management techniques based on this classification.

|             | application w/o deadlines            | applications w deadlines                |

|-------------|--------------------------------------|-----------------------------------------|

| OS directed | Childers et al. [9], ECOSystem [10], | Mossé et al. $[13]$ , Gruian $[14]$ ,   |

|             | Vertigo [11, 12]                     | PACE [15], Pillai et al. [16], Aydin et |

|             |                                      | al. [17], Pering et al. [18]            |

| Compiler    | Hsu el al. [19, 20]                  | Azevedo et al. [21], Shin et al. [22],  |

| directed    |                                      | Saputra et al. [23]                     |

Table 2.1: Examples on CPU power management schemes

For systems with no strict time constraints, the operating system periodically collects information about the system and adjusts the speed accordingly. Childers et al. [9], periodically invokes an interrupt service routine that adjusts the speed to maintain a desired performance goal. The OS keeps track of the accumulated application's instruction level parallelism throughout the application execution time. The ECOSystem framework [10] allocates energy budget per resource to limit the battery energy dissipation per period. Flautner et al. [11, 12] classified execution intervals as interactive, periodic producer, and periodic consumer to derive potential deadlines. The derived deadlines guide the speed setting in each scheduling interval.

Power-aware compilation performs specialized code optimizations to assign lower speeds to selected code segments. Hsu el al. [19, 20], identifies program regions where the CPU can be slowed down. The compiler sets the speed in each region based on the expected time the CPU would wait for a memory access. However, this work does not exploit dynamic slack time generated in computation-dominated applications.

Time restrictions in real-time applications mandate the processor to finish the application's execution before its deadline. On the OS level, CPU speeds are set using knowledge about a task execution time profile. Mossé et al. [13] present a number of dynamic speed-setting schemes that reclaim both static and dynamic slack. Gruian [14] determines a voltage schedule that changes the speed within the same task/application based on task's statistical behavior. Similarly, in PACE [15], a task's speed increases as it's execution progresses over time based on probability distribution of its execution times. Pillai et al. [16] presented power management heuristics that modify EDF and RMS scheduling in RT-Linux to incorporate voltage scaling. Aydin et al. [17] determine the optimal static speed for periodic real-time tasks with different power characteristics. Pering et al.[18] presented one of the early DVS implementation on a CPU scheduler to target real-time system.

Compiler controlled DVS techniques in real-time systems analyze an application and insert code offline that controls the CPU speed at run-time. Azevedo et al. [21] insert checkpoints at the start of each branch, loop, function call, and normal segment. Information about the checkpoints along with profile information are used to estimate the remaining cycle count and hence compute a new frequency. Shin et al. [22] augment each basic block in a CFG with its worst case execution cycles along with the remaining worst case cycles till the end of the program. Speed-change code is inserted in selected branches. The branch is selected if the remaining cycles at this branch is smaller than the worst case remaining cycles at a sibling branch. Saputra et al. [23] select the best supply voltage for each loop nest based on the loop's estimated energy. The voltage levels are set at compile time for each region using an integer linear programming DVS strategy. Kim et al. [24] presented a comparison of Shin's and Gruian's algorithms on the same simulation environment. They showed that the performance of these two schemes are quite different depending on the available slack times.

My proposed CPU power management scheme falls in to the class of schemes that target applications with deadlines. OS-directed schemes predict the remaining workload based on overall worst-case and average-case execution time estimates. However, the collaborative scheme estimates the remaining execution time based on knowledge about the current execution instance of an application. This knowledge provides more accurate estimates that can be used in scheduling the CPU speed.

Compared to the aforementioned compiler-directed schemes, the key advantage of the collaborative scheme is the use OS's runtime knowledge in computing the CPU speed while accounting for overheads. In Azevedo et al. [21], run-time overhead of updating data structures and setting the new voltages is relatively high especially on the nodes granularity assumed (almost every basic block). The collaborative scheme uses a much larger granularity than a basic block to schedule the CPU speed with minimal overheads. In Shin et al. [22], profiled timing information and speed change decisions are hard coded in the selected branches. However, part of the dynamic slack is wasted due to the deviation of the actual execution time from the profiled information used to set the speed. In contrast, the collaborative scheme can account for this slack by calculating the speed at run-time. Since Saputra et al. [23] assign lower voltages to loops only, their scheme is best suited for media applications where the loop dominates the execution of an application, while my proposed scheme fits general purpose applications.

#### 2.2 CACHE POWER MANAGEMENT

The current increase in the number of cores per chip requires a similar increase in on-chip cache capacities. Larger caches provide faster access to the data coming from multiple running threads on these cores. As a result, on-chip caches occupy large chip area and consume a large percentage of the total chip power. Efficient cache management and organization improve the cache access latency and power consumption. Examples of techniques that can optimize cache performance and energy are cache partitioning, turning off unused sections in the cache, and tag-array optimizations.

Cache partitioning reduces both the per-access energy and latency due to activating and ac-

cessing small portions of the cache rather than the entire cache. Accessing a portion of the cache involves activation of shorter bit and word lines. Kim et al. examine ways of splitting the cache into smaller units, each of which is called a sub-cache [25]. They selectively activate a target cache upon a memory access. In CMP processors, a cache partitioning manager can allocate cache sizes according to the demands of the running threads [26, 27, 28]. Ravindran et al. use the compiler to analyze applications' cache access characteristics, and accordingly determine the cache partitioning strategy [26]. The compiler inserts hints to control cache lookup and data placement of each partition. Data is accessed from partitions as indicated by a bit-vector associated with each Load/Store instructions.

In conjunction with partitioning, parts of the cache can be set at a lower power state or even turned off. Putting unused cache portions into lower power states is beneficial in reducing the cache's leakage energy with insignificant impact on performance. Patel et al. exploits the spatial/temporal properties of data caches to store high locale data in a separate small memory while turning off the cache lines belonging to this data [29]. Kadayif et al study the relationship between prefetching and the turnoff of cache lines to save leakage energy [30, 31].

Since the cache's tag array is accessed at every cache access, reducing per-access energy in the tag array causes significant decrease in the cache energy consumption. Zhou et. al. propose a cache architecture which eliminates the majority of references of TLB lookups by storing both virtual and physical tags [32]. For I-cache, Petrov et al. proposes a software-directed technique that reduces the number of tag bits lookup for instructions in the most frequently executed loops [33]. Loghi et al. propose reducing the number of tag bits by moving a large number of tag bits to an external register [34].

#### 2.3 POWER MANAGEMENT IN MULTIPLE CLOCK DOMAINS CHIPS

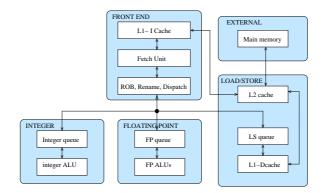

With the increase in number of transistors and reduced feature size, higher chip densities create a problem for clock synchronization among chip computational units. With a single master clock for the entire chip, it is harder to design a clock distribution network that limits clock skew in the different chip components. Several solutions have been proposed to this problem using globallyasynchronous locally synchronous (GALS) designs. In a GALS design, a chip is divided into multiple clock domains (MCD). Each domain operates synchronously with its own clock, and communicates

Figure 2.1: Example of domain partitions in MCD processors [1, 2]

with other domains asynchronously through FIFO queues.

MCD design increases the opportunity for better power management with dynamic voltage and frequency scaling (DVS). Since each domain maintains its own clock and voltage independently of other domains, DVS can be applied in each domain for an extra level of power management (rather than applying DVS at the chip level). Power and energy benefits come from dynamically adjusting an individual domain's clock and voltage according to its activity.

Several power management policies have been proposed to incorporate DVS into MCD chips. For example, an online power management policy that monitors queue occupancy of each domain and adapts the domain voltage accordingly has been proposed [1, 2]. Figure 2.1 shows the domains of the proposed MCD chip. For each domain, the policy computes the change in the average queue length in consecutive intervals. Increasing queue length triggers higher voltage and clock settings for a domain and vice versa. Results show a significant power and energy improvement. In general, policies in the literature focus on each domain in *isolation* without considering possible inter-domain effects when varying clock/voltage.

MCD design has the advantages of alleviating some clock synchronization bottlenecks and reducing the power consumed by the global clock network. Semeraro et al. explored the benefit of voltage scaling in MCD versus globally synchronous designs [35]. They find a potential 20% average improvement in the energy-delay product. Similarly, Iyer at al. analyzed the power and performance benefit of MCD with DVS [36]. They find that DVS provides up to 20% power savings over an MCD core with single voltage.

In industrial semiconductor manufacturing, National Semiconductor in collaboration with ARM

developed PowerWise technology that uses Adaptive Voltage Scaling and threshold scaling to automatically control the voltage of multiple domains on chip [37]. The PowerWise technology can support up to 4 voltage domains [38]. Their current technology also provides power management interface for dual-core processors.

Another technique by Magklis et al. is a profile-based approach that identifies program regions that justify reconfiguration [39]. This approach involves extra overhead of profiling and analyzing phases for each application. Zhu et al presented architectural optimizations for improving power and reducing complexity [40]. However, these policies do not take into account the cascading effect of changing a domain voltage on the other domains.

Wu et al. present a formal solution by modeling each domain as a queuing system [41]. However, they study each domain in isolation and incorporating domain interactions increases the complexity of the queuing model. Varying the DVS power management interval is another way to save energy. Wu et al. adaptively vary the controlling interval to react to changes in workload in each domain [42]. They do not take into account the effect induced by voltage changes in one domain on the other domains.

MCD design can be applied to multicore and simultaneous multithreading processors such [43, 44, 45]. In [43, 44], each core has its own clock network, and the DVS policy independently controls each core's voltage. Lopez et al. studies the trade-off between adapting the L2 cache capacity and speed based on the number of active threads in the core domain [45].

#### 2.4 DRAM POWER MANAGEMENT

Current memory organizations, such as SDRAM and Rambus, allow managing energy consumption by setting the DRAM chips to one of two or more power states [46]. DRAM chips are set at a low power (sleep) state during idle periods and transitioned to a high power state (active) to service memory requests. During a read/write transaction, *all* chip components (row decoder, clock, etc.) are powered up to service requests. Powering down some of these components creates power-saving states. Delay penalties result from transitioning between power states before servicing a memory request. A common technique of scheduling a chip's power state transitions is through a *time-out* policy. A power management algorithm defines a time-out threshold such that, when a memory idle period exceeds this threshold, the chip is transitioned to a lower power state. At the micro-architecture level, the use of special purpose memory like *Streaming Memory*, *Scratch-Pad Memory*, or *Energy-Saver Buffers* can reduce the memory's energy by accessing the most frequent data from these special low power memories [47, 48]. Fan et al. [49, 50] analyzed different memory controller policies and their effect on the DRAM power. They found that immediate shutdown of the memory chips yields better results than sophisticated adaptive techniques. Memory and disk controller policies can apply similar power management strategies [51, 52].

In the OS layer, Lebeck et al. [53] proposed the use of a power aware allocation policy where data is allocated sequentially in each memory bank to increase the bank idle periods. An implementation of the memory power manager in the Linux operating system [54] allocates memory pages to banks grouped based on the allocating process. Li et al. [51] presented a technique that provides performance guarantees on the memory system by periodically adjusting the time-out threshold based on the available slack and the current workload. Cai et al. [52] uses an interval based scheme that adapt the memory page size and the disk time-out threshold based on the system workload.

Other research direction targets compiler techniques for memory power management. Delaluz et al.[55, 56] group the allocation of the requested pages in memory based on application's order of data accesses. Ozturk et al. [57] modify the data access pattern of a performance-oriented scheme to reduce leakage and dynamic energy in the memory hierarchy. Grun et al. [58] clustered variables into memory banks based on their spatial and temporal locality. Kandemir et al. [59] presented a code optimization technique to manage the flow of data to/from a scratchpad memory.

My proposed memory power management scheme compares to schemes implemented in the architecture and the OS levels. While the use of extra on-chip memory (as with energy-saving buffers and streaming memories) reduces the activation of the DRAM chips, the aggressive prefetching creates a memory bus performance bottleneck and increases the bus's energy consumption. These factors were not accounted for in the above related work. In comparison, my scheme uses near-memory caching (within the DRAM chips) to avoid such a bottleneck. With respect to adaptive OS techniques that vary the time-out threshold, they mainly optimize the energy-delay product without providing bounds on the delay experienced during this adaptation (except in [51]). However, we propose to maintain the memory delays within specified bounds. In contrast to [51], we look for adapting more reconfigurable system parameters, such as the cache block size, in conjunction with the time-out threshold.

#### 2.5 EMBEDDED DRAM

Integrating DRAM and logic cells on the same chip is an attractive solution to achieve both high performance (from logic cells) and high memory density (from DRAM cells). This integration avoids the high latency of going off-chip by doing computation (or even caching) at the memory itself. Currently, manufactured chips with embedded DRAM and logic are mainly used in applications like computer graphics, networking, and handheld devices [60]. Based on the fabrication technology (either DRAM-based or logic-based), some degradation to the speed (density) of the logic (DRAM) cells may occur. For example, in early DRAM-based chips, logic cells were reportedly slower by 20% to 35% [60]. However, emerging fabrication technologies aim at overcoming these penalties. For example, NEC's embedded DRAM chips offer DRAM-like density with SRAM-like performance [61], and IBM's third generation embedded DRAM chips support two embedded DRAM families for high density and high performance to serve both purposes with no degradation [62].

#### 3.0 MODELS

#### 3.1 REAL-TIME APPLICATIONS

Real-time applications are characterized by deadlines. A *deadline* is the amount of time available for an application to finish execution. The deadline should be larger than or equal to the application's worst case execution time. Since the execution time for an application may vary in a system with multiple operating frequencies, the execution time is expressed in cycles rather than time units. Thus, the application's duration is represented by its *worst case execution cycles* (WCC). We define an application *worst case execution time* (WCET) as the time spent executing the WCC at the maximum frequency. We consider two types of real-time applications: applications subject to hard deadlines and others subject to soft deadlines. It is *critical* for applications with hard deadlines to meet these deadlines. However, it is *desirable* for an application with a soft deadline to finish execution within the allowed deadlines. That is, in contrast to hard deadlines, it is acceptable for applications with soft deadlines to endure performance degradation in excess of their deadlines in order to achieve higher energy savings.

When running at the maximum frequency, if *deadline* > WCET (i.e., the allotted time exceeds the WCET), the time difference is known as *static slack*. During actual execution, an application runs for its *actual execution time* (ACET), which is smaller than or equal to its WCET. The difference between WCET and ACET is called the *dynamic slack*, which usually comes from data dependencies that cause program instances to execute different paths. Thus, it is safe to represent application duration by its *worst case cycles* (WCC). Similarly, ACC is used to represent the actual number of cycles spent executing an application.

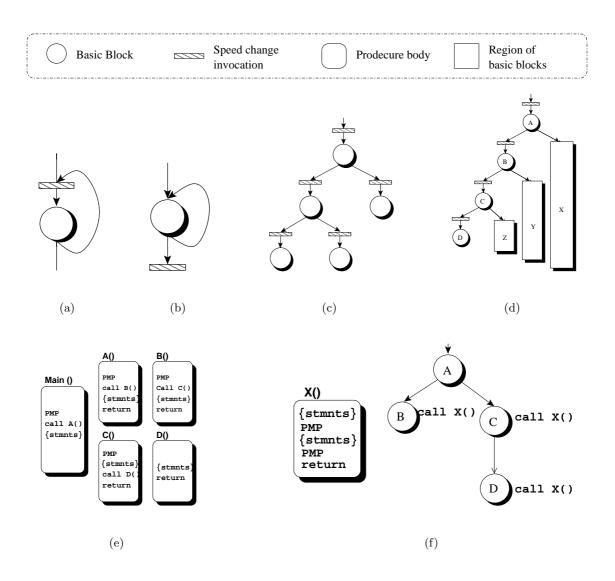

We consider the general form of real-time applications that may consist of sequential code, branches, loops and procedures. A program is represented by a *control flow graph* (CFG). CFGs are used as an intermediate representation in compilers. CFG consists of *basic blocks* (code segment with one entry point, exit point and no jump instructions contained within it).

#### 3.2 CPU ENERGY MODEL

In CMOS circuits, energy dissipated is the sum of three main components: dynamic, static and leakage power. Dynamic energy is a function of the processor's switching activity, operating frequency and voltage. Dynamic power is directly proportional to the square of the input voltage:  $P_{dyn} \alpha CV_{dd}^{\beta} f$ , where C is the switched capacitance,  $V_{dd}$  is the supply voltage, f is the operating frequency and  $\beta$  is a processor dependent constant that is typically greater than or equal to two. Static energy is the energy consumed due to powering up some of the core's structures like the register file and the load/store queue. This energy is consumed independent of any activity in the core. Leakage energy is the energy consumed during processor's idleness as a result of the leakage current flow in the transistors. Leakage energy is a function of both the gate supply and threshold voltages.

Most commercially available processors support Dynamic Voltage Scaling (DVS) capabilities to control the trade-offs between performance and energy consumption. Two examples are the Transmeta Crusoe TM5400 [63] and the Intel XScale [64]. In this work, we consider realistic processors with discrete voltage and frequency levels. We refer to changing the voltage/frequency and speed changes interchangeably.

When computing and changing the CPU speed, two main sources of overhead may be encountered depending on the CPU architecture: (1) computing a new speed, and (2) setting the speed through a voltage transition in the processor's DC-DC regulator (resulting in a processor frequency change) and the clock generator. The speed change overhead takes between  $25\mu$ sec to  $150\mu$ sec and consumes energy in the range of micro Joules (for example  $4\mu$ J in *lparm*) [65, 18]. We assume that the overhead of changing the voltage is constant for all the power level transitions in a given processor, whereas the overhead of computing the speed depends on the CPU operating frequency during each computation.

#### 3.3 CACHE ENERGY MODEL

Access energy and latency for each cache access is a function of the cache configuration. For a given technology, the key parameters for cache configuration are cache size, associativity, and cache block size. Varying these parameters affects the length of the word and bit lines that need to be activated at each cache access. Longer lines causes longer delay and higher power consumption per access. We use the Cacti 3.0 [66] simulator to obtain the access energy and latency for the different configurations of caches used in our work. In Cacti, the per-access energy and latency is divided into portions consumed in the tag-array and the data-array (including sense amplifiers and output latches). In n-way set associative caches, tag and data arrays are accessed concurrently to reduce the total access time. In fully associative caches, the tag array is replaced by a fully associative decoder, after which the data array is accessed. Tag comparison takes place in the decoder. Then, the decoder drives the wordline associated with the cache entry. The serial access of tag and data arrays reduces the cache per-access energy; however, it increases the per-access latency. Using Cacti, we obtain access latencies and energy assuming that the cache is operating at voltage  $V_{dd} = 1.3 \text{ V}$ .

When integrating SRAM cache and DRAM memory on the same chip as discussed in Section 2.4, we add a delay penalty ranging from 10% to 35% for accessing logic cells in the memory chip [60]. We also account for delay penalties for accessing off-chip caches.

#### 3.4 MEMORY ENERGY MODEL

External DRAM memory usually consists of multiple memory chips. A chip contains one or more memory banks. Each chip can be transitioned independently to/from a low power memory state. A chip consists of control logic (for example, row and column decoders) and data array (memory banks). Energy in the DRAM-core is consumed during read/write activity ( $E_{dyn}$ ) and during idle periods ( $E_{static}$ ). The memory's dynamic energy is consumed in address decoding,  $E_{addr\_decode}$ , and data transfer to/from DRAM-core. At each miss in the lowest level cache, the memory controller decodes the row and column addresses then precharges a row in the desired bank containing the requested data. Data access energy is proportional to the number of bytes transferred during read or write transactions. During inactivity (idle periods), the memory's idle energy is a function of the idle time spent at each power state. We assume five DRAM power states: active, standby, nap, sleep, and off [67]. Transition energy,  $E_{trans}$ , is consumed when a chip transitions to/from the active state. Thus, the energy consumed in the DRAM-core  $E_{tot}$  equals:

$$E_{tot} = d \ E_{addr\_decode} + c \ P_{access} \ t_{access} \ + \ \sum_{s} P_s \ t_s \ + \ r \ E_{trans}$$

where d is the number of data requests; c is the number of transferred bytes;  $P_{access}$  is the power dissipated during read/write transactions.  $P_s$  is the power consumed when the DRAM is in the  $s^{th}$ state.  $t_{access}$  and  $t_s$  are the time for transferring a single byte to/from DRAM-core and the time spent in the  $s^{th}$  state, respectively; and r is the number of transitions to and from the active state.  $E_{addr\_decode}$ ,  $P_{access}$ ,  $t_{access}$ ,  $P_s$ , and  $E_{trans}$  are memory specific parameters while d, c,  $t_s$ , and r are factors of the application's memory access pattern and the memory hierarchy configuration.

## 4.0 COMPILER AND OS COLLABORATION FOR CPU AND MEMORY POWER MANAGEMENT

Dynamic Voltage Scaling (DVS) slows down the processor speed to reduce its power consumption. The objective of a power management scheme employing DVS is to efficiently use the available slack (time where the processor is idle) to reduce the processor's speed without violating applications time constraints. Better slack utilization implies a decrease in processor energy consumption but an increase in other system components.

Dynamically changing the speed in real-time applications (tasks) is classified into two categories: *inter-task* and *intra-task* voltage scaling [24]. Inter-task DVS schemes schedule speed changes when a task starts or finishes execution, while intra-task schemes schedule speed changes during task execution. In this chapter, we describe an intra-task DVS scheme, where voltage scheduling points (also called *power management points*, *PMP*) are invoked throughout an application's execution to change the CPU speed.

Considering the general form of a real-time application code, automatically deciding on the proper location to invoke PMPs using intra-task DVS scheduling is not trivial. One problem is how frequently the power manger should change the speed. Ideally, the more voltage scaling invocations, the more fine-grain control the application has for exploiting dynamic slack and reducing energy. However, in practice, the energy and time overhead associated with each speed adjustment can overshadow the DVS energy savings.

To design an efficient intra-task DVS scheme, a PMP should have enough information about the application to select the most energy-efficient speed level. With knowledge about the application execution, a PMP estimates the amount of work remaining to execute versus the time available before a deadline. The proper estimation by PMPs of the remaining workload saves energy by selecting the slowest speed that guarantees meeting the application's deadline.

The contribution of this chapter is threefold. First, we present a novel technique that in-

volves the collaboration between the OS and the compiler to collect both run-time information and path-dependent information. Second, we show the effect of reducing the CPU frequency on increasing the memory energy consumption. We present speed scheduling schemes that compute the proper CPU frequency such that the sum of the CPU energy and the memory energy consumption is minimized. Third, we evaluate our technique on time-sensitive applications running on two commercially available processors with dynamic voltage scaling. We show that our technique can achieve significant energy reduction over no power management, OS-directed and compiler-directed power management techniques.

Next, we present a brief description of the power management approach that deals with these issues. We start with a discussion of the idea behind our OS-compiler collaborative approach in Section 4.1 and highlight its advantages over OS-only or compiler-only approaches in Section 4.2. A brief overview of the technique is presented in Section 4.3. We then describe the different algorithm phases and the role of both compiler and the OS in Section 4.4 and Section 4.5. We present a detailed evaluation on different real-time applications in Section 4.6 followed by a chapter conclusion in Section 4.7.

#### 4.1 COMPILER AND OS COLLABORATIVE APPROACH

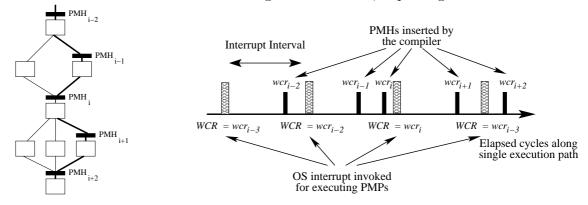

To control the number of speed changes during the execution of an application, we present a collaborative compiler-OS technique [68]. Initially, some timing information is collected about a program's execution behavior. This information is used offline to compute how frequently PMPs are invoked. The number of cycles between executions of two PMPs is called the *PMP-interval*. The length of the PMP-interval controls the number of PMPs executed in an application, and therefore the overhead. Next, the compiler inserts instrumentation code to compute some timing information and make it available to the operating systems. We call such instrumentation: power management hints, *PMH*. PMHs compute the *worst-case remaining* cycles, *wcr<sub>i</sub>*, starting from the *i*<sup>th</sup> PMH location to the end of the application. The value of *wcr<sub>i</sub>* at these locations may vary dynamically based on the executed path for each run. For example, the remaining cycles at a PMH inside a procedure body is dependent on the path from which this procedure is invoked. During run-time, a PMH computes and passes dynamic timing information (i.e., *wcr<sub>i</sub>*) to the OS in a predetermined memory location named  $R_{WCR}$ , which holds the most recent value of the estimated

worst case remaining cycles. Periodically, a timer interrupt invokes the operating system to execute an *interrupt service routine* (ISR) that does the PMP job; that is, the ISR adjusts the processor speed based on the latest worst case remaining cycles, WCR, value and the remaining time to the deadline.