# DYNAMIC BINARY TRANSLATION FOR EMBEDDED SYSTEMS WITH SCRATCHPAD MEMORY

### by

### José Américo Baiocchi Paredes

B.S., Pontificia Universidad Católica del Perú, 2002 M.S., University of Pittsburgh, 2009

Submitted to the Graduate Faculty of the Department of Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh 2011

## UNIVERSITY OF PITTSBURGH DEPARTMENT OF COMPUTER SCIENCE

This dissertation was presented

by

José Américo Baiocchi Paredes

It was defended on

November 11th 2011

and approved by

Bruce R. Childers, Associate Professor, Department of Computer Science

Sangyeun Cho, Associate Professor, Department of Computer Science

Youtao Zhang, Associate Professor, Department of Computer Science

Jack W. Davidson, Professor, University of Virginia

Dissertation Director: Bruce R. Childers, Associate Professor, Department of Computer Science

Copyright © by José Américo Baiocchi Paredes 2011

## DYNAMIC BINARY TRANSLATION FOR EMBEDDED SYSTEMS WITH SCRATCHPAD MEMORY

José Américo Baiocchi Paredes, PhD

University of Pittsburgh, 2011

Embedded software development has recently changed with advances in computing. Rather than fully co-designing software and hardware to perform a relatively simple task, nowadays embedded and mobile devices are designed as a platform where multiple applications can be run, new applications can be added, and existing applications can be updated. In this scenario, traditional constraints in embedded systems design (i.e., performance, memory and energy consumption and real-time guarantees) are more difficult to address. New concerns (e.g., security) have become important and increase software complexity as well.

In general-purpose systems, Dynamic Binary Translation (DBT) has been used to address these issues with services such as Just-In-Time (JIT) compilation, dynamic optimization, virtualization, power management and code security. In embedded systems, however, DBT is not usually employed due to performance, memory and power overhead.

This dissertation presents *StrataX*, a low-overhead DBT framework for embedded systems. *StrataX* addresses the challenges faced by DBT in embedded systems using novel techniques. To reduce DBT overhead, *StrataX* loads code from NAND-Flash storage and translates it into a Scratchpad Memory (SPM), a software-managed on-chip SRAM with limited capacity. SPM has similar access latency as a hardware cache, but consumes less power and area.

StrataX manages SPM as a software instruction cache, and employs victim compression and pinning to reduce retranslation cost and capture frequently executed code in the SPM. To prevent performance loss due to excessive code expansion, StrataX minimizes the amount of code inserted by DBT to maintain control of program execution. When a hardware instruction cache is available, StrataX dynamically partitions translated code among the SPM and main memory. With these techniques, StrataX has low performance overhead relative to native execution for MiBench

programs. Further, it simplifies embedded software and hardware design by operating transparently to applications without any special hardware support. *StrataX* achieves sufficiently low overhead to make it feasible to use DBT in embedded systems to address important design goals and requirements.

#### TABLE OF CONTENTS

| PRE | FAC | E     |                                       | xiv |

|-----|-----|-------|---------------------------------------|-----|

| 1.0 | INT | rod   | UCTION                                | 1   |

|     | 1.1 | СНА   | LLENGES                               | 3   |

|     |     | 1.1.1 | Memory constraints                    | 3   |

|     |     | 1.1.2 | Performance constraints               | 3   |

|     |     | 1.1.3 | Heterogeneous memory resources        | 4   |

|     | 1.2 | RESE  | ARCH OVERVIEW                         | 5   |

|     | 1.3 | RESE  | ARCH SCOPE                            | 6   |

|     | 1.4 | DOC   | UMENT ORGANIZATION                    | 7   |

| 2.0 | BA  | CKGF  | ROUND AND RELATED WORK                | 8   |

|     | 2.1 | BASI  | C CONCEPTS                            | 8   |

|     | 2.2 | DYN   | AMIC BINARY TRANSLATION               | 12  |

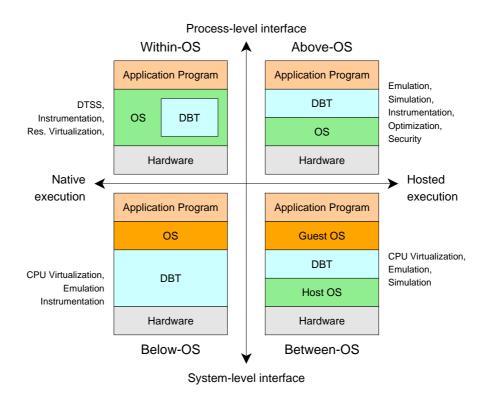

|     |     | 2.2.1 | Types of DBT systems                  | 12  |

|     |     | 2.2.2 | DBT services                          | 13  |

|     |     | 2.2.3 | DBT implementation                    | 17  |

|     |     |       | 2.2.3.1 Fragment Formation            | 17  |

|     |     |       | 2.2.3.2 Overhead Reduction Techniques | 19  |

|     |     |       | 2.2.3.3 Trace Formation               | 20  |

|     |     |       | 2.2.3.4 Fragment Cache Management     | 20  |

|     |     | 2.2.4 | DBT in Embedded Systems               | 23  |

|     | 2.3 | SCRA  | ATCHPAD MEMORY                        | 24  |

|     |     | 2.3.1 | Scratchpad memory allocation          | 25  |

|     |     |       | 2.3.1.1 Static allocation             | 25  |

|     |     |       | 2.3.1.2 Dynamic allocation            | 28  |

|     |     | 2.3.2 | SPM address translation                             | 29 |

|-----|-----|-------|-----------------------------------------------------|----|

|     |     |       | 2.3.2.1 Software caching                            | 29 |

|     |     |       | 2.3.2.2 Hardware-assisted address translation       | 30 |

|     |     | 2.3.3 | SPM sharing                                         | 31 |

|     | 2.4 | FLAS  | SH MEMORY                                           | 32 |

|     |     | 2.4.1 | Code Execution from NAND Flash                      | 32 |

| 3.0 | ST  | RATA  | X FRAMEWORK FOR MEMORY-CONSTRAINED EMBEDDED SYSTEMS | 34 |

|     | 3.1 | TARG  | GET SYSTEM                                          | 34 |

|     | 3.2 | SYST  | EM-ON-CHIP SIMULATOR                                | 36 |

|     |     | 3.2.1 | Dynamic code generation                             | 36 |

|     |     | 3.2.2 | Dynamic memory allocation                           | 37 |

|     |     |       | 3.2.2.1 SPM simulation                              | 38 |

|     |     | 3.2.3 | NAND Flash simulation                               | 38 |

|     | 3.3 | STRA  | ATAX OVERVIEW                                       | 40 |

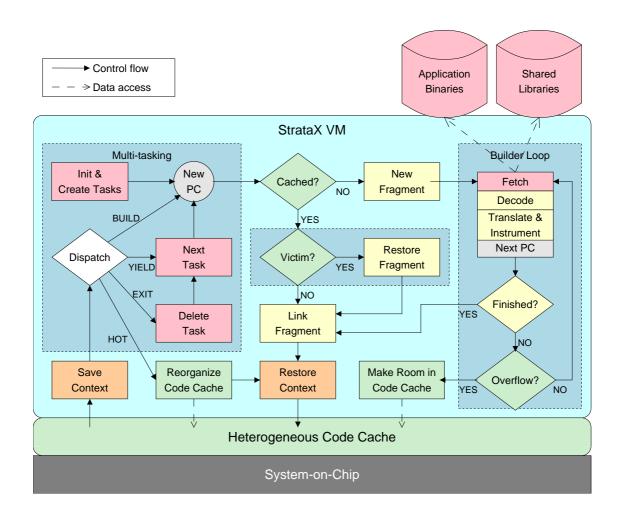

|     |     | 3.3.1 | Operation                                           | 40 |

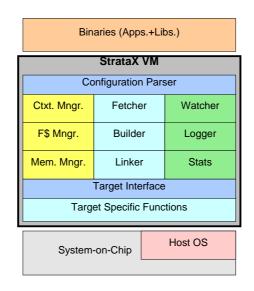

|     |     | 3.3.2 | Architecture                                        | 42 |

|     |     | 3.3.3 | Approaches                                          | 43 |

|     |     |       | 3.3.3.1 Bounded fragment cache                      | 43 |

|     |     |       | 3.3.3.2 Translated code footprint reduction         | 44 |

|     |     |       | 3.3.3.3 Fragment cache management                   | 45 |

|     |     | 3.3.4 | Implementation                                      | 45 |

|     |     |       | 3.3.4.1 Translation                                 | 46 |

|     |     |       | 3.3.4.2 Fragment formation                          | 46 |

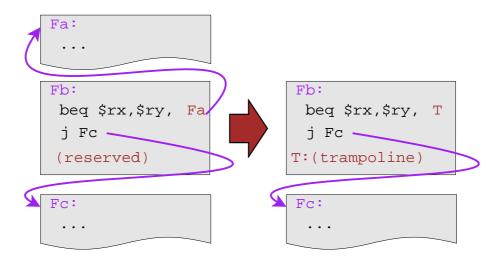

|     |     |       | 3.3.4.3 Trampolines                                 | 48 |

|     |     |       | 3.3.4.4 Fragment cache management                   | 49 |

|     |     |       | 3.3.4.5 Fragment linking and unlinking              | 49 |

|     |     |       | 3.3.4.6 System call handling                        | 50 |

|     | 3.4 | EXPE  | ERIMENTAL METHODOLOGY                               | 51 |

| 4.0 | CO  | DE G  | ENERATION                                           | 54 |

|     | 4.1 | PERF  | FORMANCE OF SMALL FRAGMENT CACHES                   | 54 |

|     | 4.2 | FRAC  | GMENT FORMATION STRATEGY                            | 59 |

|     | 4.2 | CON   | TPOL CODE ECOTPRINT PEDITCTION                      | 61 |

|     |     | 4.3.1 | Translated Code Composition Without Footprint Reduction | 64  |

|-----|-----|-------|---------------------------------------------------------|-----|

|     |     | 4.3.2 | Performance Without Footprint Reduction                 | 67  |

|     |     | 4.3.3 | Reducing Trampoline Size                                | 70  |

|     |     |       | 4.3.3.1 Alternative Trampoline Designs                  | 71  |

|     |     |       | 4.3.3.2 Evaluation                                      | 73  |

|     |     | 4.3.4 | Reducing Indirect CTI Handling Code Size                | 74  |

|     |     |       | 4.3.4.1 Alternative IBTC Lookup Designs                 | 75  |

|     |     |       | 4.3.4.2 Evaluation                                      | 77  |

|     |     | 4.3.5 | Eliminating the Fragment Prologue                       | 78  |

|     |     |       | 4.3.5.1 Self-Modifying Control Transfer                 | 79  |

|     |     |       | 4.3.5.2 Bottom Jump Eliding                             | 80  |

|     |     |       | 4.3.5.3 Evaluation                                      | 81  |

|     |     | 4.3.6 | Translated Code Composition with Footprint Reduction    | 84  |

|     |     | 4.3.7 | Performance With Footprint Reduction                    | 84  |

| 5.0 | FR  | AGMI  | ENT CACHE MANAGEMENT                                    | 88  |

|     | 5.1 | FRAC  | GMENT CACHE LAYOUT                                      | 88  |

|     |     | 5.1.1 | Fragment Cache Layout Alternatives                      | 89  |

|     |     | 5.1.2 | Trampoline Pool Management                              | 90  |

|     |     | 5.1.3 | Evaluation                                              | 91  |

|     | 5.2 | HETI  | EROGENEOUS FRAGMENT CACHE MANAGEMENT                    | 94  |

|     |     | 5.2.1 | Heterogeneous Fragment Cache Allocation                 | 94  |

|     |     | 5.2.2 | Basic Heterogeneous Fragment Cache Management           | 95  |

|     |     |       | 5.2.2.1 Eviction Policies                               | 95  |

|     |     |       | 5.2.2.2 Resizing Heuristic                              | 96  |

|     |     |       | 5.2.2.3 Evaluation                                      | 96  |

|     |     | 5.2.3 | SPM-Aware Translation                                   | 98  |

|     |     |       | 5.2.3.1 Evaluation                                      | 99  |

|     |     | 5.2.4 | Comparison to Homogeneous Fragment Cache                | 100 |

|     | 5.3 | SCRA  | ATCHPAD FRAGMENT CACHE MANAGEMENT                       | 103 |

|     |     | 5.3.1 | Victim Compression                                      | 103 |

|     |     |       | 5.3.1.1 Dynamic SPM Partitioning                        | 104 |

|     |     |       | 5.3.1.2 Compression and Decompression                   | 105 |

|     |            | 5.3.1.3 Evaluation                     |

|-----|------------|----------------------------------------|

|     | 5.3.2      | Fragment Pinning                       |

|     |            | 5.3.2.1 Pinning and Release Strategies |

|     |            | 5.3.2.2 Evaluation                     |

|     | 5.3.3      | Overall Improvement                    |

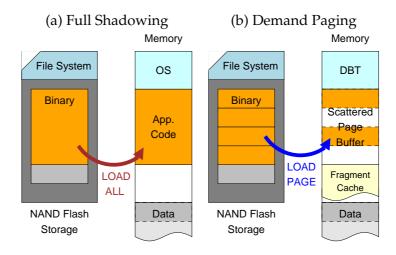

|     | 5.4 DEM    | AND PAGING FOR NAND FLASH              |

|     | 5.4.1      | Scattered Page Buffer                  |

|     |            | 5.4.1.1 Evaluation                     |

|     | 5.4.2      | Unified Code Buffer                    |

|     |            | 5.4.2.1 Evaluation                     |

|     | 5.4.3      | Asynchronous Loading                   |

|     |            | 5.4.3.1 Evaluation                     |

| 6.0 | CONCLU     | JSIONS AND FUTURE WORK                 |

|     | 6.1 SUM    | MARY OF CONTRIBUTIONS                  |

|     | 6.2 FUTU   | JRE WORK                               |

| DID | I IOCD A D | 120                                    |

#### LIST OF TABLES

| 2.1 | SPM allocation approaches                                  |

|-----|------------------------------------------------------------|

| 3.1 | PISA instruction handling examples                         |

| 3.2 | StrataX fragment formation options                         |

| 3.3 | PXA270 SimpleScalar Configuration                          |

| 3.4 | ARM926 SimpleScalar Configuration                          |

| 3.5 | ARM1176 SimpleScalar Configuration                         |

| 4.1 | Number of flushes for 64KB, 32KB, and 16KB fragment caches |

| 4.2 | Evaluated fragment formation strategies                    |

| 5.1 | Final fragment cache size                                  |

| 5.2 | Speedup (slowdown) with victim compression                 |

| 5.3 | Number of flushes without and with fragment pinning        |

| 5.4 | Speedup (slowdown) with fragment pinning                   |

| 5.5 | NAND Flash pages read (512 bytes/page)                     |

| 5.6 | NAND Flash pages read with UCB-75%                         |

#### LIST OF FIGURES

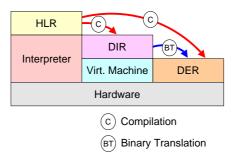

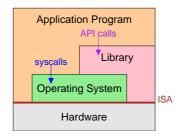

| 2.1  | Program Representation and Execution                                                  | 9  |

|------|---------------------------------------------------------------------------------------|----|

| 2.2  | Abstraction Layers                                                                    | 11 |

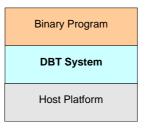

| 2.3  | A DBT system                                                                          | 12 |

| 2.4  | Types of DBT systems                                                                  | 14 |

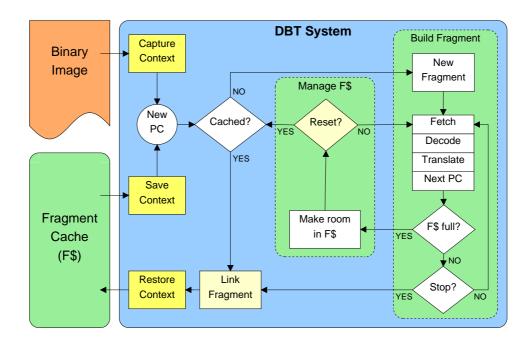

| 2.5  | DBT Overview                                                                          | 18 |

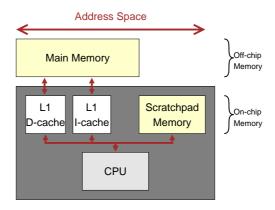

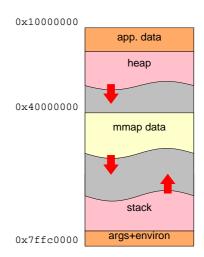

| 2.6  | Processor address space with scratchpad memory                                        | 25 |

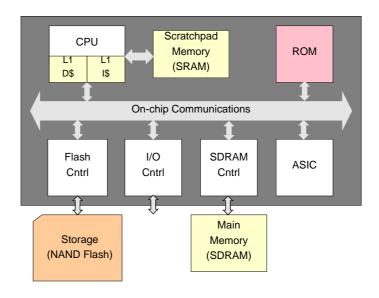

| 3.1  | Example target SoC                                                                    | 35 |

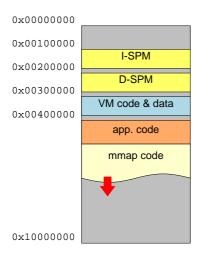

| 3.2  | SimpleScalar address space use                                                        | 37 |

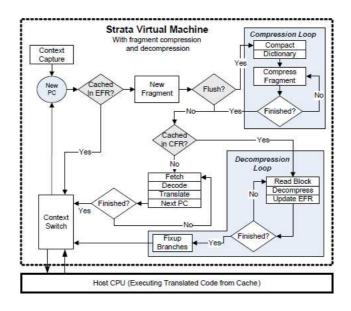

| 3.3  | StrataX Virtual Machine                                                               | 41 |

| 3.4  | StrataX Architecture                                                                  | 42 |

| 3.5  | Fragment unlinking                                                                    | 50 |

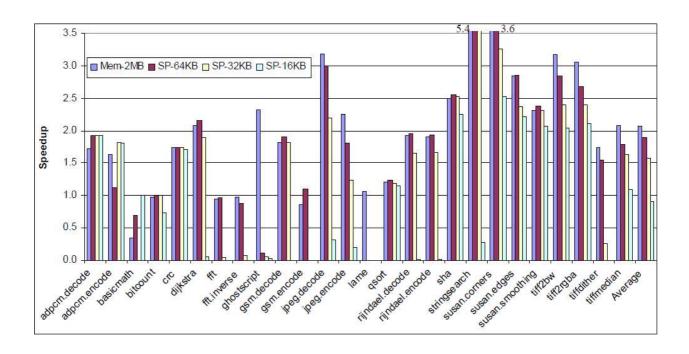

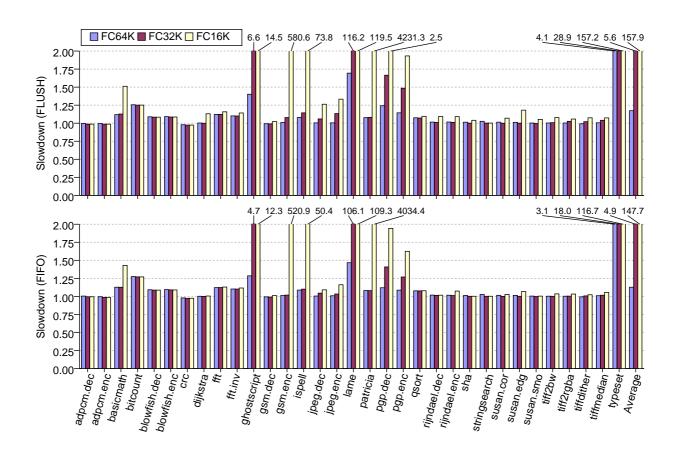

| 4.1  | Speedup relative to native execution for a 2MB fragment cache in SDRAM; and frag-     |    |

|      | ment caches in 64KB, 32KB and 16KB SPM with FLUSH                                     | 55 |

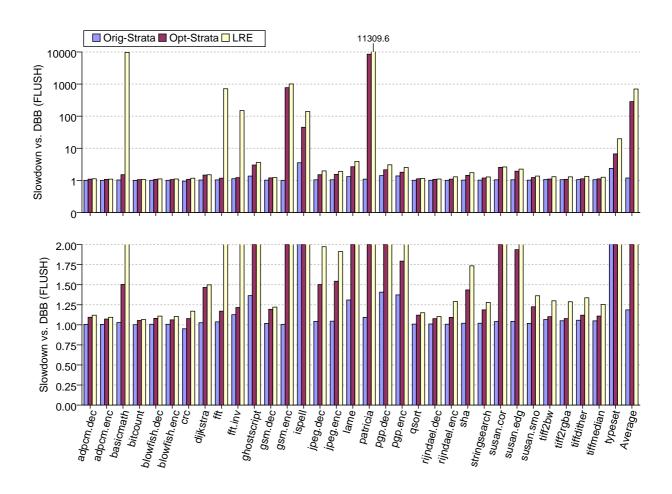

| 4.2  | Slowdown relative to DBB for evaluated fragment formation strategies                  | 61 |

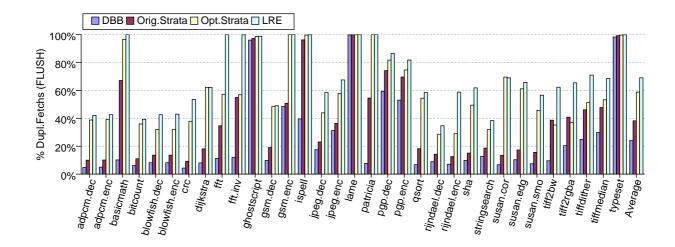

| 4.3  | Percentage of duplicated instruction fetches for different fragment formation strate- |    |

|      | gies                                                                                  | 62 |

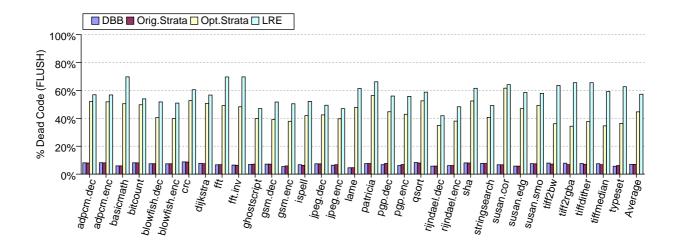

| 4.4  | Percentage of dead translated code for different fragment formation strategies        | 63 |

| 4.5  | Example fragments with instruction categories                                         | 65 |

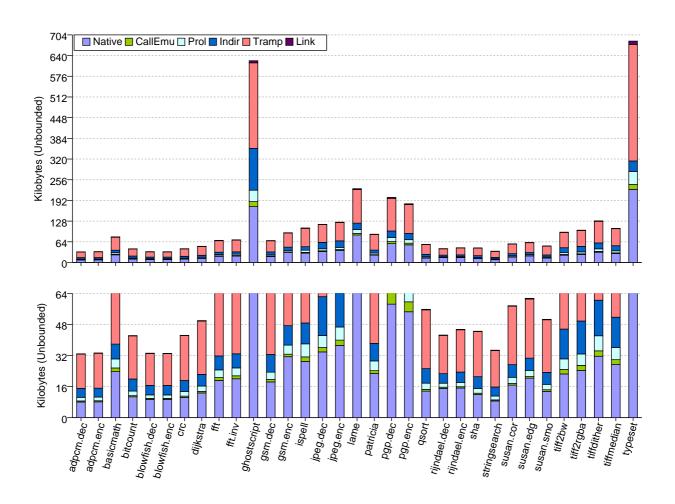

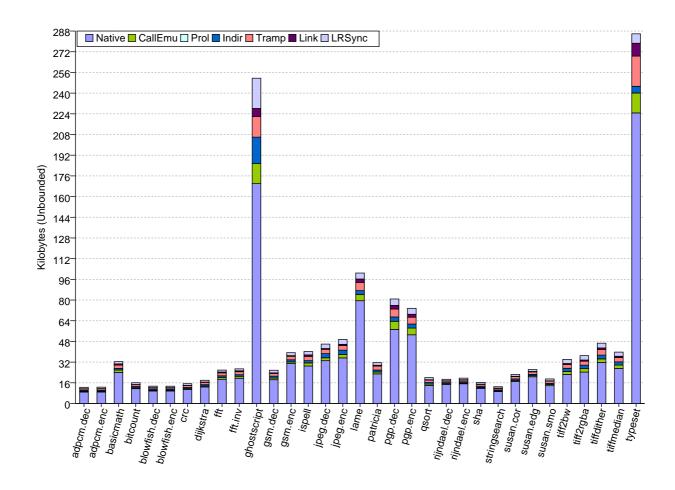

| 4.6  | Initial translated code size for an unbounded fragment cache                          | 66 |

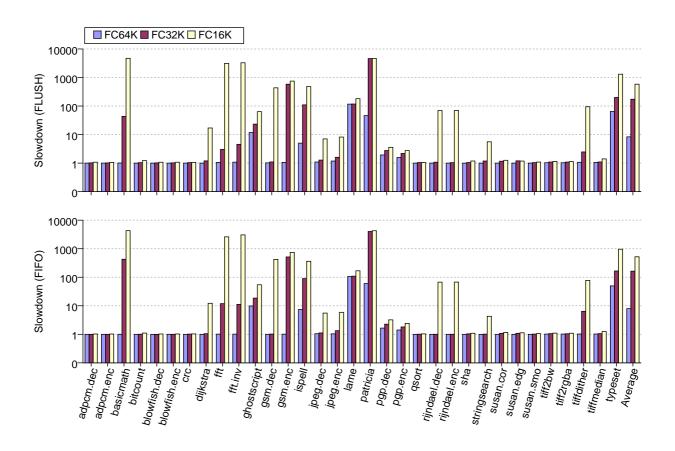

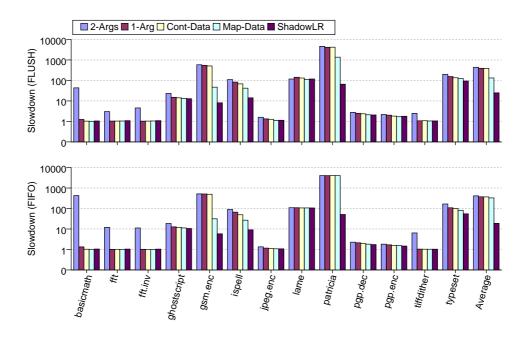

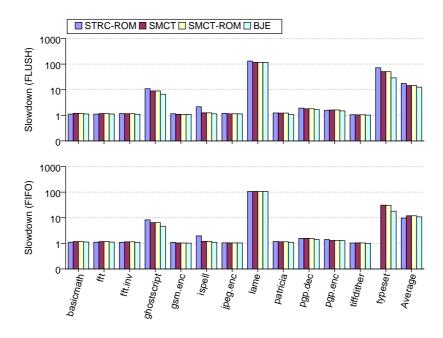

| 4.7  | Slowdown relative to unbounded fragment cache for 64KB, 32KB and 16KB frag-           |    |

|      | ment caches in SPM with FLUSH and FIFO                                                | 68 |

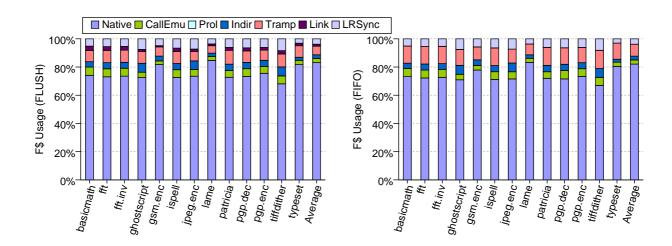

| 4.8  | Initial relative 32KB fragment cache usage                                            | 70 |

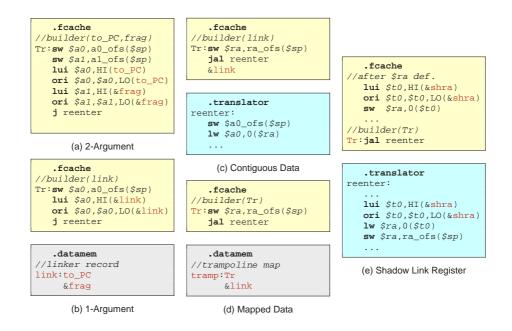

| 4.9  | Trampoline design choices                                                             | 71 |

| 4.10 | Performance of trampoline designs for a 32KB fragment cache                           | 73 |

| 4.11 | Relative 32KB fragment cache usage after Shadow LR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Ŀ        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.12 | Indirect CTI handling with an IBTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )        |

| 4.13 | Performance of IBTC lookup placements for 32KB fragment cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ;        |

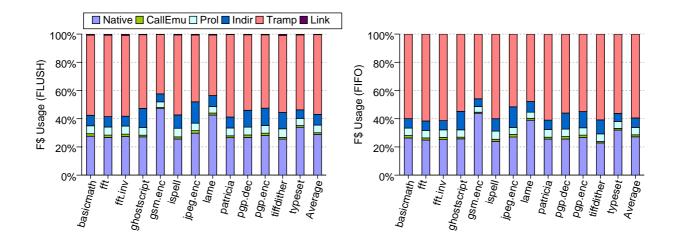

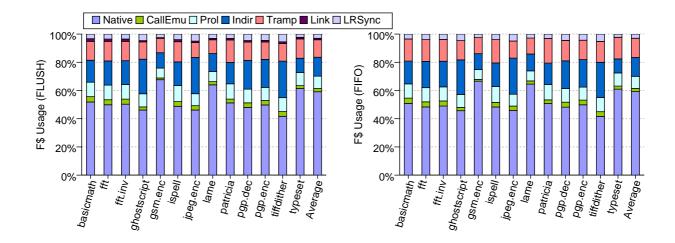

| 4.14 | Relative 32KB F\$ usage after STRC IBTC lookup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )        |

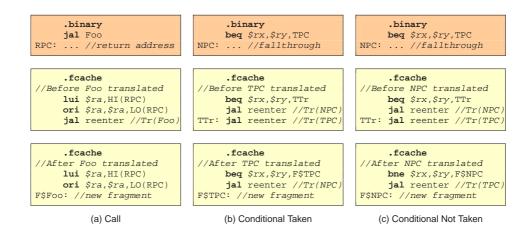

| 4.15 | Control transfer to fragment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | )        |

| 4.16 | Bottom Jump Eliding (BJE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -        |

| 4.17 | Performance with SMCS, SMCS-ROM and BJE for 32KB fragment cache 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u>,</u> |

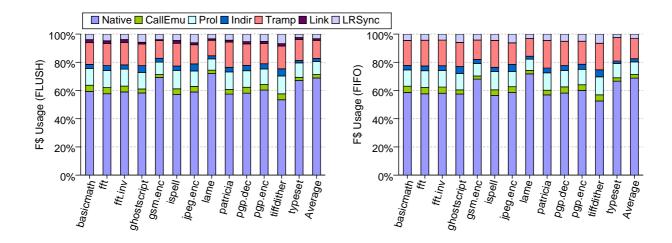

| 4.18 | Relative 32KB F\$ usage after BJE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | }        |

| 4.19 | Final translated code size with footprint reduction for an unbounded fragment cache 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ;        |

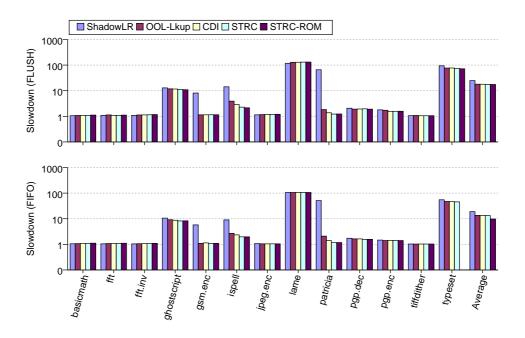

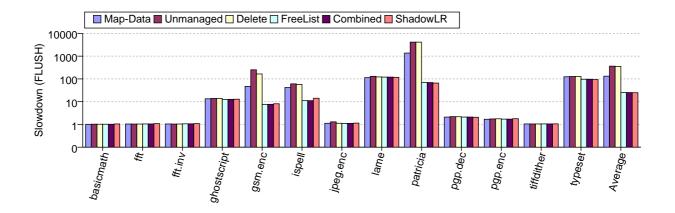

| 4.20 | Final slowdown with control code footprint reduction relative to initial unbounded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|      | fragment cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )        |

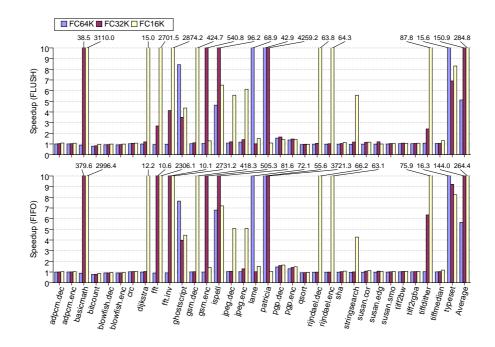

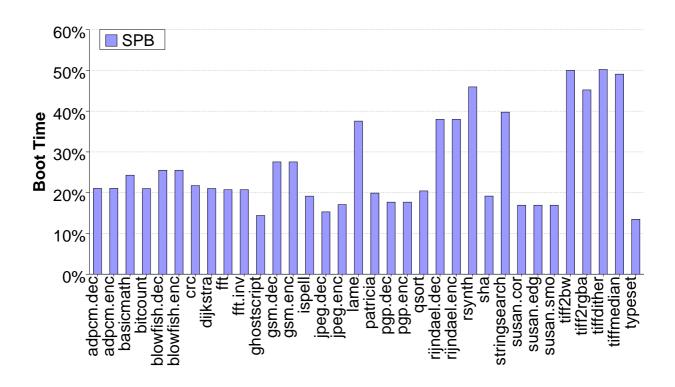

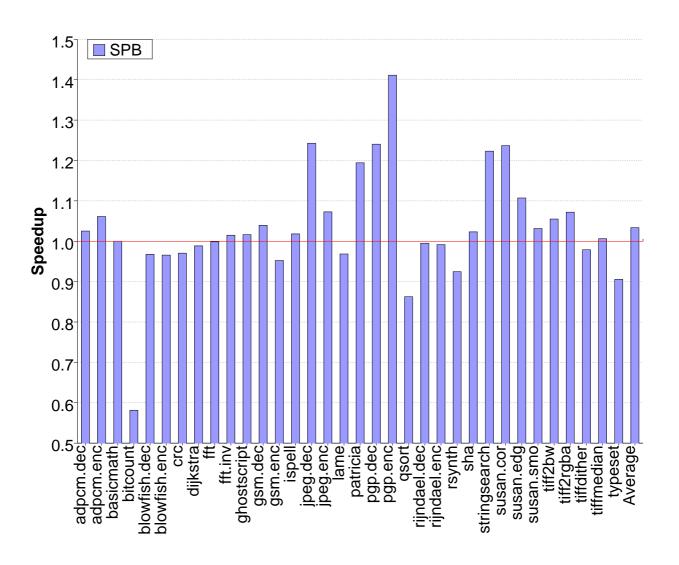

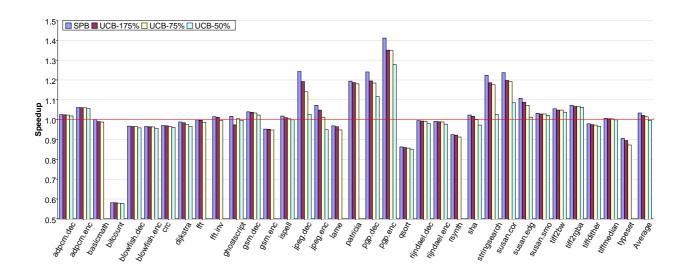

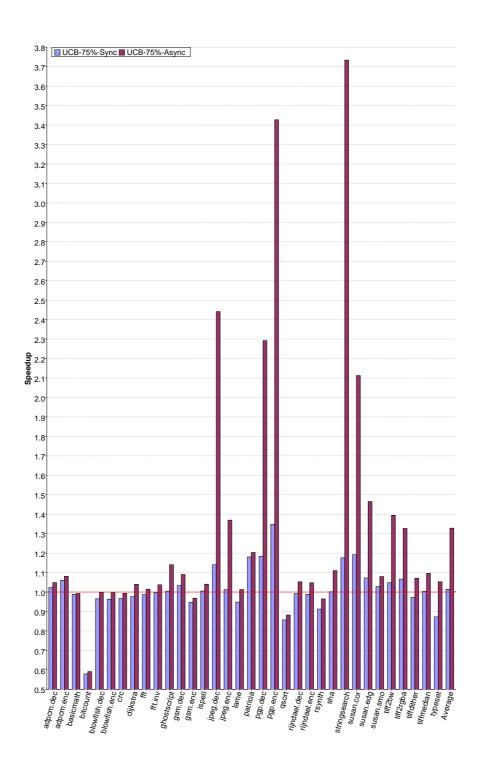

| 4.21 | Speedup with control code footprint reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7        |

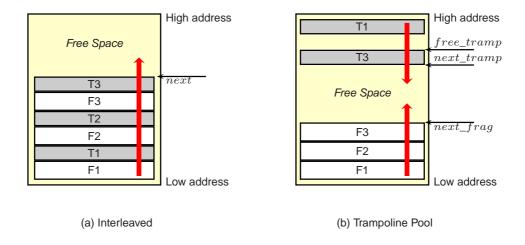

| 5.1  | Trampoline placement alternatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )        |

| 5.2  | Slowdown for 32K fragment cache with trampoline pool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>,</u> |

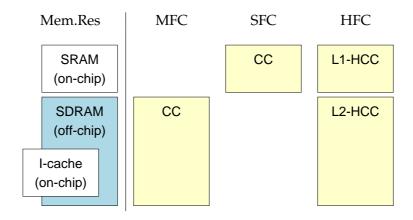

| 5.3  | Fragment Cache Allocation Alternatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ė        |

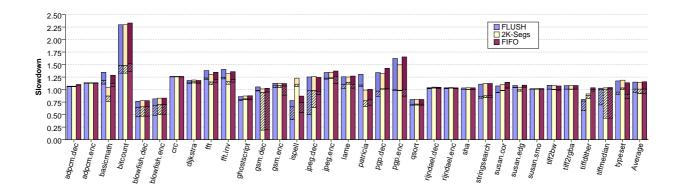

| 5.4  | Slowdown relative to native execution for HFC with FLUSH, Segmented FIFO and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|      | FIFO eviction policies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7        |

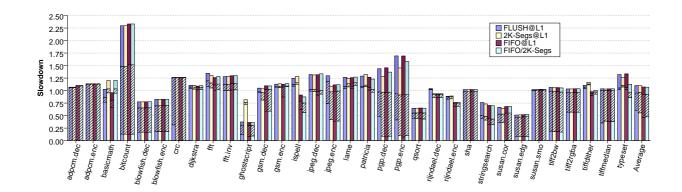

| 5.5  | Slowdown relative to native execution for HFC with SPM-aware policies 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | )        |

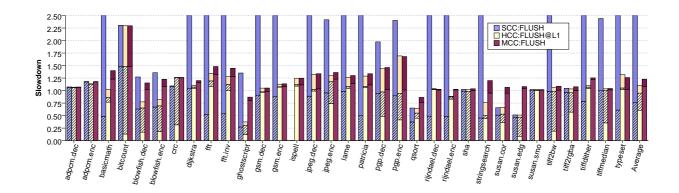

| 5.6  | Slowdown relative to native execution for SFC, HFC and MFC with FLUSH $\dots$ 100 | )        |

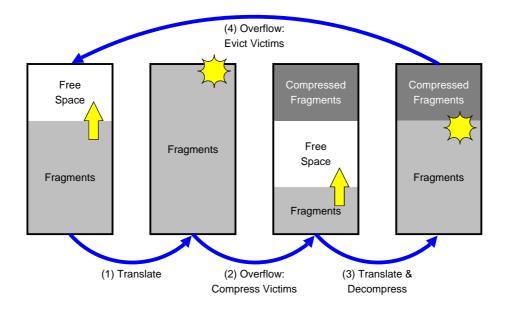

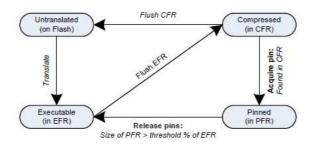

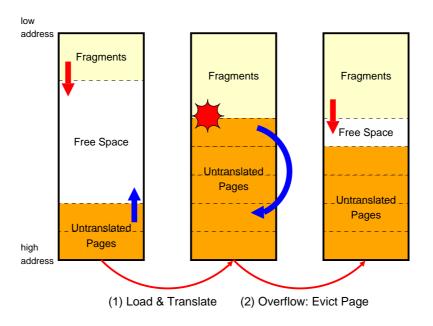

| 5.7  | Victim compression and space reclamation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ;        |