# UNIVERSITE TOULOUSE III – PAUL SABATIER U.F.R Physique Chimie Automatique

# THESE

en vue de l'obtention du

## **DOCTORAT DE L'UNIVERSITE DE TOULOUSE**

Délivré par l'université Toulouse III - Paul Sabatier

Discipline: Informatique

présentée et soutenue

par

Benjamin FONTAN

le 17 janvier 2008

# Titre:

# MÉTHODOLOGIE DE CONCEPTION DE SYSTÈMES TEMPS RÉEL ET DISTRIBUÉS EN CONTEXTE UML/SysML

## Directeur de thèse :

Pierre de SAQUI-SANNES

# **JURY**

| M. Jean-Philippe BABAU     | Rapporteur  |

|----------------------------|-------------|

| Mme Isabelle CHRISMENT     | Examinateur |

| M. Guy JUANOLE             | Président   |

| M. Pierre de SAQUI-SANNES  | Examinateur |

| Mme Françoise SIMONOT-LION | Rapporteur  |

| M. François VERNADAT       | Examinateur |

**AUTEUR: Benjamin FONTAN**

TITRE: MÉTHODOLOGIE DE CONCEPTION DE SYSTEMES TEMPS RÉEL ET DISTRIBUÉS EN

**CONTEXTE UML/SysML**

**DIRECTEUR DE THESE: Pierre de SAQUI-SANNES**

LIEU ET DATE DE SOUTENANCE : TOULOUSE le 17 janvier 2008

#### **RESUME:**

En dépit de ses treize diagrammes, le langage UML (Unified Modeling Language) normalisé par l'OMG (Object Management Group) n'offre aucune facilité particulière pour appréhender convenablement la phase de traitement des exigences qui démarre le cycle de développement d'un système temps réel. La normalisation de SysML et des diagrammes d'exigences ouvre des perspectives qui ne sauraient faire oublier le manque de support méthodologique dont souffrent UML et SysML.

Fort de ce constat, les travaux exposés dans ce mémoire contribuent au développement d'un volet « méthodologie » pour des profils UML temps réel qui couvrent les phases amont (traitement des exigences - analyse - conception) du cycle de développement des systèmes temps réel et distribués en donnant une place prépondérante à la vérification formelle des exigences temporelles. La méthodologie proposée est instanciée sur le profil TURTLE (Timed UML and RT-LOTOS Environment). Les exigences non-fonctionnelles temporelles sont décrites au moyen de diagrammes d'exigences SysML étendus par un langage visuel de type « chronogrammes » (TRDD = Timing Requirement Description Diagram). La formulation d'exigences temporelles sert de point de départ à la génération automatique d'observateurs dédiés à la vérification de ces exigences. Décrites par des méta-modèles UML et des définitions formelles, les contributions présentées dans ce mémoire ont vocation à être utilisées hors du périmètre de TURTLE. L'approche proposée a été appliquée à la vérification de protocoles de communication de groupes sécurisée (projet RNRT-SAFECAST).

#### **MOTS CLES:**

Méthodologie, UML temps réel, SysML, Exigences temporelles, Vérification formelle, Observateurs, Protocoles, Communication de groupe sécurisés

**DISCIPLINE ADMINISTRATIVE: INFORMATIQUE**

LABORATOIRE: LAAS-CNRS 7 Avenue du colonel Roche 31 077 TOULOUSE CEDEX 04

#### REMERCIEMENTS

Les travaux à l'origine de ce mémoire ont été réalisés dans le Département de Mathématiques, Informatique et Automatique de L'ISAE et dans le groupe Outils et Logiciels pour la Communication du LAAS-CNRS. Aussi je voudrais saisir cette opportunité pour remercier MM Darrenougé directeur de l'ENSICA et Fourrure directeur général de l'ISAE (issu du rapprochement de l'ENSICA et SUPAERO). Mes remerciements vont de pair à MM Ghallab et Chatila directeurs successifs du LAAS-CNRS pour m'avoir accueilli dans leur laboratoire. Je tiens également à remercier François Vernadat et Patrick Sénac respectivement responsables du groupe OLC du LAAS-CNRS et du département DMIA de l'ISAE pour m'avoir accueilli et aidé dans mes travaux. Enfin, j'ai une pensée particulière pour J.P Courtiat, ancien responsable du groupe OLC et mon ancien co-directeur de thèse pour m'avoir guidé durant la première année de ma thèse et pour l'attention qu'il a portée ensuite à mes travaux et ce malgré ses obligations diplomatiques.

Je voudrais aussi pouvoir exprimer ici mes plus vifs remerciements à Pierre de Saqui-Sannes qui a bien voulu accepter d'encadrer ce mémoire de Doctorat. Sans sa disponibilité (24 heures sur 24), sa patience, les conseils qu'il m'a prodigués tout au long de ces trois ans, ses mots d'encouragement, ce travail n'aurait pas pu, sans doute, être mené à son terme. Son encadrement « rapproché » restera pour moi un très bon souvenir et m'aura grandement appris.

Je remercie Françoise Simonot-Lion et Jean-Philippe Babau qui ont accepté la charge de rapporteurs. Ils ont aussi accepté d'être membre de mon jury, qu'ils trouvent ici le témoignage de ma reconnaissance. Je remercie également Guy Juanole, Isabelle Chrisment et François Vernadat de m'avoir fait l'honneur d'examiner mes travaux. Leur présence dans leur jury fut pour moi un grand plaisir.

Je remercie chaleureusement Ludovic Apvrille, qui a suivi de près ce travail et sans qui mes travaux n'existeraient pas sous cette forme. Ses observations judicieuses et ses remarques ont été des plus déterminantes dans la conduite de ces travaux et à la forme finale qu'ils ont pris.

Mes remerciements vont également à tous les membres du projet SAFECAST. J'ai une pensée toute particulière pour Sara à qui je souhaite de terminer le plus rapidement possible et dans les meilleures conditions son manuscrit. Je tiens également à remercier Philippe et particulièrement Thierry et Pierre pour m'avoir encadré avec Sara dans ce projet.

J'adresse mes plus sincères remerciements à Michel Diaz, qui a bien voulu répondre à mes sollicitations pour mener à bien ce travail.

Les personnels du DMI par leur gentillesse et leur convivialité dont ils ont su faire montre ont rendu mon séjour très agréable parmi eux. Je tiens à remercier toute l'équipe d'enseignant chercheur du DMI: Laurent, Fabrice, Emmanuel, Jérôme et Tanguy. Par leur grandes compétences et leurs remarquables qualités humaines, ils ont su rendre chaleureuses et fructueuses ces quelques années passées parmi eux. Je garde de très bons souvenirs des nombreuses discussions mathématiques, philosophiques et œnologiques avec Yves pendant lesquelles j'ai su que je ne savais rien (ou du moins pas grand-chose). Je remercie également le personnel administratif du DMI en l'occurrence René et Bernard pour leur efficacité et tous les services rendus.

Je n'oublie pas de remercier également l'ensemble de mes collègues du groupe OLC avec qui j'ai passé des moments agréables. Par leur gentillesse et leur convivialité, ils ont rendu mon séjour très agréable parmi eux. Qu'ils trouvent ici collectivement et individuellement l'expression de toute ma gratitude.

Je ne saurais passer cette occasion sans saluer les doctorants actuels et anciens que j'ai pu côtoyer au cours de ces quelques années. Je salue donc les vieux docteurs et jeunes maitres de conférences: Ernesto (pour moi tu resteras toujours un docteur) et Florestan. Les jeunes docteurs: Francisco, Mathieu, Manu, Hervé, Ahlem et les doctorants Sara, Jérôme, Nicolas, François, Juan, Ali, Amine, Lei et Nourredine, ainsi que la nouvelle génération qui je pense va nous faire rêver: Alexandre, Thomas et Guodong. Enfin en écrivant ces lignes j'ai une certaine nostalgie en pensant à Tarekinho, plus qu'un collègue de bureau ces trois ans de « vie commune » ont été pour moi un vrai plaisir et une thérapie concernant un certain « humour approximatif ». Ces souvenirs resteront gravés dans ma mémoire.

Il me semble opportun d'avoir une pensée pour l'ensemble de mes collègues de l'UPS que j'ai eu le plaisir d'avoir à la fois comme professeurs durant ma scolarité et comme collègues par la suite. Merci de m'avoir donné envie de continuer dans les études et de m'avoir fait confiance pour les enseignements. Je pense particulièrement à Pascal qui m'a permis d'apprécier et de m'impliquer dans mes travaux d'enseignements. Enfin je remercie tous les étudiants (ISAE compris) qui m'ont fait apprécier d'enseigner. Merci à tous d'avoir supporté mes moments d'euphorie et mes changements d'humeur occasionnés par ce travail.

Un grand merci à tous mes amis qui m'ont supporté durant tant d'années: Philippe, Bastien, Fred et Adrien. Merci de m'avoir fait décompresser surtout durant la sacro-sainte période de rédaction, merci d'être toujours là. Je remercie aussi Fanny pour ses talents de cinéaste. J'ai également une pensée particulière pour Anne-Charlotte, Fabrice et bien sûr ma petite filleule Alix qui court déjà après les tortues. Je remercie chaleureusement toute ma famille (et aussi la belle) de m'avoir supporté et épaulé. Merci à mes parents d'avoir cru en moi dans des périodes difficiles, et de m'avoir donné tous les moyens de poursuivre mes études.

Et enfin pour conclure ces remerciements, je ne peux m'empêcher de penser à Gwenaëlle, qui un jour m'a dit de manière naturelle « Tiens je te verrais bien docteur! ». Et bien oui c'est fait, encore merci pour ton soutient qui a été essentiel tout au long de ces huit années. Merci de m'avoir supporté et de m'avoir fait devenir ce que je suis aujourd'hui: je ne sais vraiment pas ce que je serai devenu sans toi. Du fond du cœur, j'aimerais t'adresser mes plus grands remerciements, pour le reste tu sais ce que tu représentes pour moi et c'est donc naturellement à toi que je dédie ce mémoire.

# Table des matières

| Table des matières                                                          | 1  |

|-----------------------------------------------------------------------------|----|

| Index des figures                                                           | 5  |

| Index des tableaux                                                          | 6  |

| Index des définitions                                                       | 7  |

|                                                                             |    |

| Chapitre I. Introduction                                                    | 9  |

| 1. Développer des systèmes temps réel fiables                               | 9  |

| 2. L'émergence d'un consensus : UML                                         | 10 |

| 3. Les réponses apportées par l'ingénierie des exigences                    | 10 |

| 4. Contributions apportées dans ce mémoire                                  | 11 |

| 5. Organisation du mémoire                                                  | 12 |

|                                                                             |    |

| Chapitre II. Contexte et positionnement des travaux                         |    |

| 1. Les systèmes temps réel (STR)                                            |    |

| 1.1. Exigences posées par les STR                                           |    |

| 1.2. Méthodologies de conception de STR                                     |    |

| 1.2.1. Avant UML                                                            |    |

| 1.2.2. Les méthodologies orientées UML                                      |    |

| 1.2.3. Les méthodes formelles dans la conception et la validation des STR   |    |

| 2. Systèmes temps réel et distribués (STRD)                                 |    |

| 2.1. Les exigences temporelles liées à la Qualité de Service des STRD       |    |

| 2.2. Méthodologies de conception de STRD                                    |    |

| 3. TURTLE (Timed UML and RT-LOTOS Environment)                              |    |

| 3.1. Un profil dédié à la vérification de systèmes temps-réel et distribués | 24 |

| 3.1.1. La sémantique TURTLE : le langage RT-LOTOS                           |    |

| 3.1.2. Les diagrammes UML TURTLE                                            | 25 |

| 3.1.3. Un profil outillé                                                    | 29 |

| 3.1.4. Positionnement du profil TURTLE                                      | 30 |

| 3.2. Méthodologie présentée en [APV 06]                                     | 31 |

| 4. Conclusion                                                               | 32 |

|                                                                             |    |

| Chapitre III. Proposition d'une méthodologie                                |    |

| 1. Vue d'ensemble de la méthodologie                                        |    |

| 1.1. Définition informelle                                                  |    |

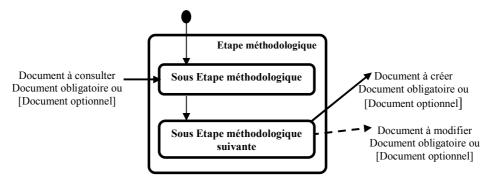

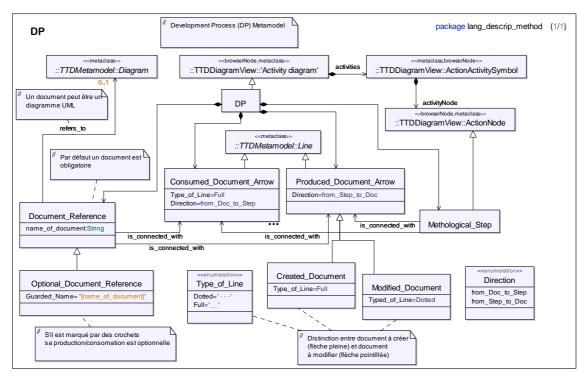

| 1.2. Langage de description d'une méthodologie                              | 35 |

| 1.2.1. Principe                                                             |    |

| 1.2.2. Définition formelle                                                  |    |

| 1.2.3. Méta-modèle                                                          |    |

| 2 Guide de lecture                                                          | 38 |

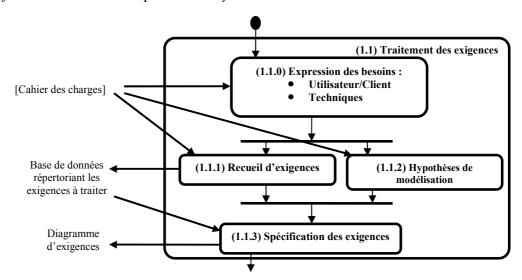

| 3. | Vérificat        | tion formelle d'exigences temporelles de modèles en contexte UML/SysML     | 39  |

|----|------------------|----------------------------------------------------------------------------|-----|

|    |                  | itement des exigences                                                      |     |

|    | 3.1.1.           | Recueil des exigences                                                      | 40  |

|    | 3.1.2.           | Hypothèses de modélisation                                                 | 42  |

|    | 3.1.3.           | Spécification des exigences                                                | 42  |

|    |                  | alyse                                                                      |     |

|    |                  | nception                                                                   |     |

|    |                  | rification formelle des exigences                                          |     |

| 4. | Spécialis        | sation dans le domaine des protocoles                                      | 50  |

|    |                  | règles de traitement des exigences                                         |     |

|    | 4.1.1.           | Exigences liées au type de protocoles envisagés et à la qualité de service |     |

|    | 4.1.2.           | Hypothèses de modélisation                                                 | 51  |

|    | 4.1.3.           | Les règles liées à la phase d'analyse                                      | 53  |

|    |                  | règles liées à la phase de conception                                      |     |

| 5. | Conclusi         | ion                                                                        | 63  |

| ~  |                  |                                                                            |     |

|    |                  | Langage de description d'exigences non-fonctionnelles temporelles          |     |

| 1. |                  | 'art et positionnement de nos travaux                                      |     |

| 2. |                  | on d'un langage de description d'exigences temporelles                     |     |

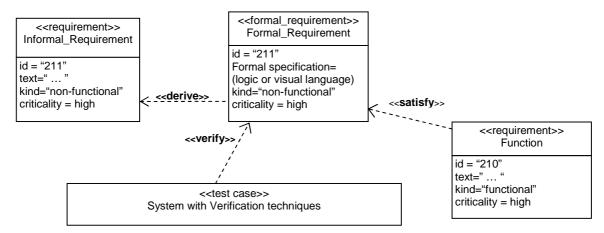

|    | 2.1. For 2.1.1.  | malisation d'exigences temporelles SysML                                   |     |

|    |                  | Exemple de diagramme d'exigences                                           |     |

|    | 2.1.2.<br>2.1.3. | Définitions formelles                                                      |     |

|    |                  | Méta-modèle UML                                                            |     |

|    | 2.2.1.           | ning Requirement Description Diagram (TRDD)                                |     |

|    | 2.2.1.           | Définition formelle                                                        |     |

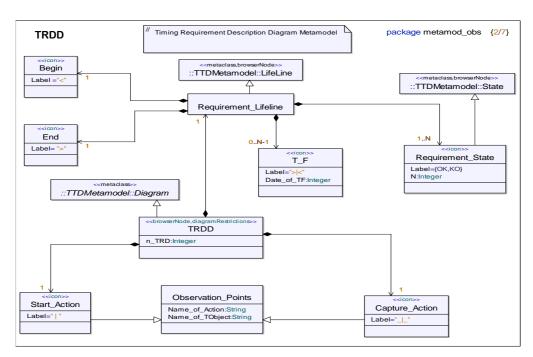

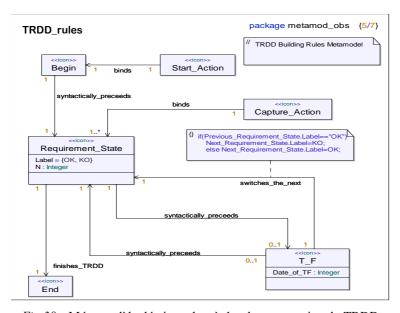

|    | 2.2.2.           | Méta-modèles UML                                                           |     |

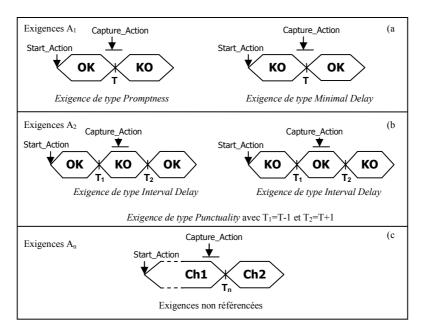

|    | 2.2.3.           | Pouvoir d'expression des TRDD                                              |     |

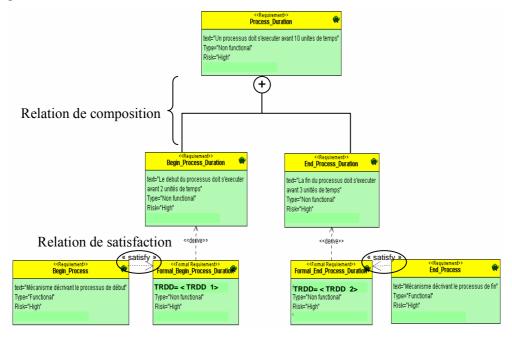

| 3  |                  | ition d'exigences                                                          |     |

| ٦. | 1                | concepts de composition et satisfaction                                    |     |

|    |                  | position d'extension des diagrammes d'exigences                            |     |

|    |                  | inition formelle                                                           |     |

| 4  |                  | ion                                                                        |     |

| ٠. | Concrasi         |                                                                            | 1 / |

| C  | hapitre V.       | Vérification formelle d'exigences temporelles sur le modèle de conception  | 81  |

| 1. |                  | es de vérification des exigences temporelles                               |     |

|    |                  | vérification par contrôle de modèles                                       |     |

|    |                  | ification guidée par les observateurs                                      |     |

|    | 1.2.1.           | Mise en œuvre d'observateurs dans le simulateur Véda                       |     |

|    | 1.2.2.           | Observateurs de machines synchrones                                        |     |

|    | 1.2.3.           | Observateurs pour les systèmes auto-validés                                |     |

|    | 1.2.4.           | Le langage GOAL                                                            |     |

|    | 1.2.5.           | Les observateurs du profil UML OMEGA                                       | 85  |

|    | 1.2.6.           | Méthodes de surcharge                                                      |     |

|    | 1.2.7.           | Diagrammes de contexte et d'observation                                    | 86  |

# Table des matières

| 2. Generat      | ion d'observateurs IURILE a partir d'exigences temporelles                      | 8 / |

|-----------------|---------------------------------------------------------------------------------|-----|

| 2.1. Co         | nstruction d'un observateur TURTLE                                              | 87  |

| 2.1.1.          | Définition d'un observateur TURTLE                                              | 87  |

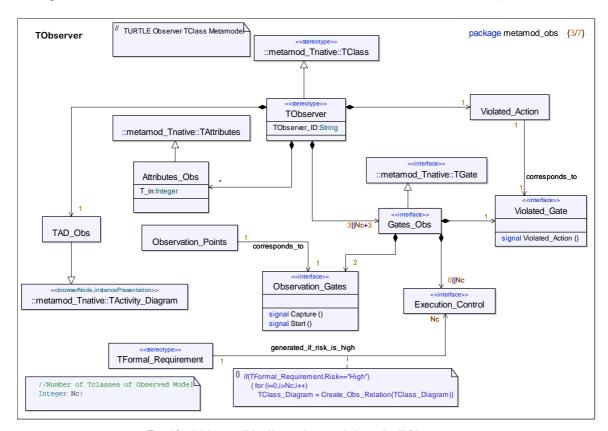

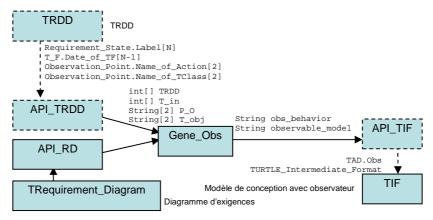

| 2.1.2.          | Méta-modèle UML d'une Tclass observateur                                        | 88  |

| 2.2. Vu         | e d'ensemble                                                                    | 89  |

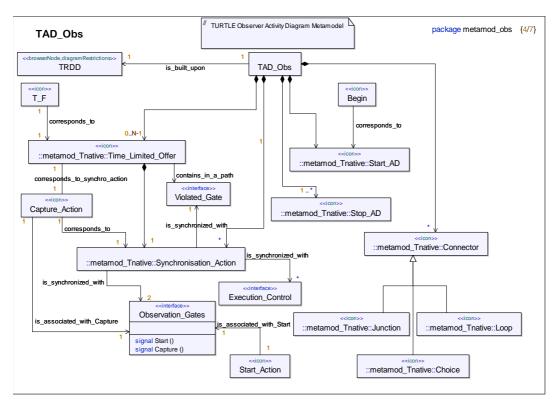

| 2.3. Tra        | aduction d'un TRDD vers le diagramme d'activités de l'observateur               | 90  |

| 2.3.1.          | Tables de traductions                                                           | 90  |

| 2.3.2.          | Méta-modèles UML du diagramme d'activités d'un observateur                      | 91  |

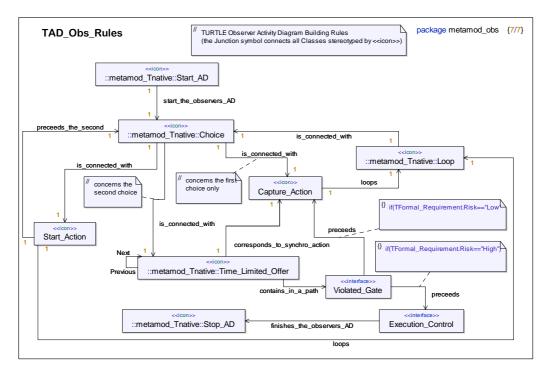

| 2.3.3.          | Algorithmes de construction du comportement de l'observateur                    | 93  |

| 2.3.4.          | Exemples                                                                        | 95  |

| 2.3.5.          | Algorithmes de construction du comportement complet de l'observateur            | 96  |

| 2.4. Int        | égration de l'observateur dans le modèle                                        |     |

| 2.4.1.          | Définition des points d'observations                                            |     |

| 2.4.2.          | Construction du modèle observable : principe                                    |     |

| 2.4.3.          | 1                                                                               |     |

| 2.4.4.          | Algorithme d'insertion d'un observateur dans le système à observer              |     |

|                 | ion sur l'approche de vérification guidée par les observateurs                  |     |

|                 | pothèses                                                                        |     |

|                 | cement des points d'observations                                                |     |

|                 | rs une implantation complète de l'approche                                      |     |

| 4. Conclus      | ion                                                                             | 105 |

| G1 1/ T/I       | A PLACE TO CAST                                                                 | 106 |

|                 | . Application : le projet SAFECAST                                              |     |

| 1. Le proje     | et SAFECAST                                                                     | 106 |

|                 | seau sans fil : le médium PMR                                                   |     |

|                 | vue de travaux sur la modélisation et la vérification de protocoles de sécurité |     |

|                 | urquoi utiliser TURTLE dans le projet SAFECAST ?                                |     |

|                 | es, architecture et services considérés                                         |     |

|                 | igences temporelles d'un protocole de sécurité                                  |     |

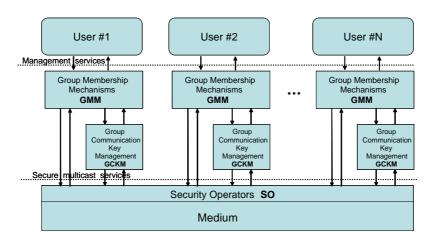

| 2.2. Are 2.2.1. | chitecture génériqueServices de diffusion sécurisée                             |     |

|                 |                                                                                 |     |

|                 | Services de gestion des groupes                                                 |     |

|                 | nitement des exigences                                                          |     |

| 3.1.1.          | Recueil des exigences                                                           |     |

| 3.1.1.          | Hypothèses de modélisation                                                      |     |

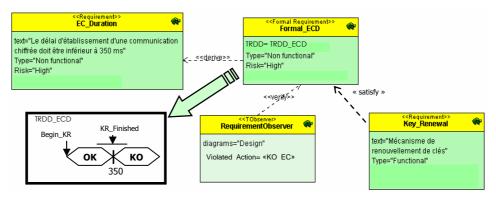

| 3.1.2.          | Spécification d'une exigence temporelle                                         |     |

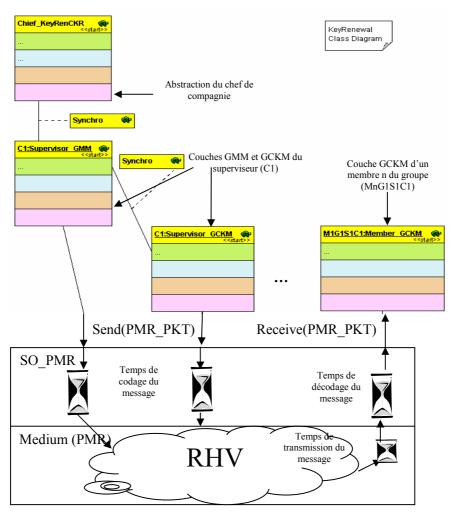

|                 | odèle de conception pour la fonctionnalité Génération et Distribution des clés  | 113 |

|                 | ewal)                                                                           | 114 |

|                 | nstruction des observateurs                                                     |     |

|                 | utions et résultats                                                             |     |

|                 | sion                                                                            |     |

| J. Concrus      | 1011                                                                            | 110 |

| Chapitre VI     | I. Conclusions et perspectives                                                  | 119 |

|                 | es contributions                                                                |     |

|                 |                                                                                 |     |

# Méthodologie de conception de systèmes temps réel et distribués en contexte UML/SysML

| 2. Per  | rspectives                                                               | 121 |

|---------|--------------------------------------------------------------------------|-----|

|         | Enrichir les descriptions d'exigences non-fonctionnelles temporelles     |     |

| 2.2.    | Extension de la méthodologie dans les phases de déploiement et de codage | 122 |

| 2.3.    | Perspectives liées au projet SAFECAST                                    | 123 |

| Référei | 1ces                                                                     | 124 |

| Annexe  | es                                                                       | 131 |

# **Index des figures**

| Fig.1.   | Cycle de vie des systèmes selon la méthode UP                                                                                                                               | 18              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Fig.2.   | Architecture à trois couches inspirée du modèle OSI                                                                                                                         |                 |

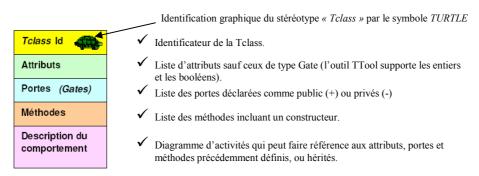

| Fig. 3.  | Structure d'une Tclass.                                                                                                                                                     |                 |

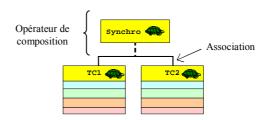

| Fig.4.   | Composition entre deux instances de classes.                                                                                                                                | .26             |

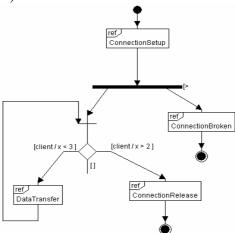

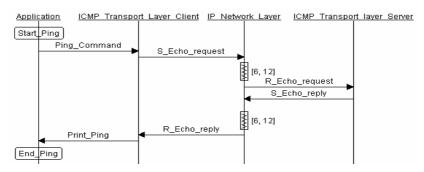

| Fig.5.   | Exemple de diagramme global d'interactions TURTLE                                                                                                                           | . 28            |

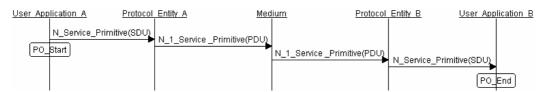

| Fig. 6.  | Exemple de diagramme de séquences                                                                                                                                           | . 29            |

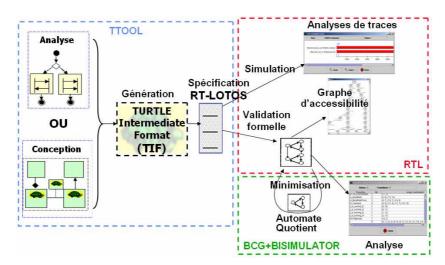

| Fig. 7.  | La chaîne d'outils du profil TÜRTLE                                                                                                                                         | 30              |

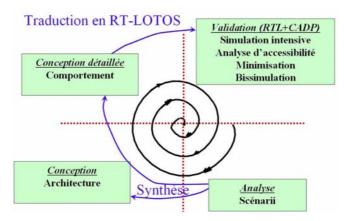

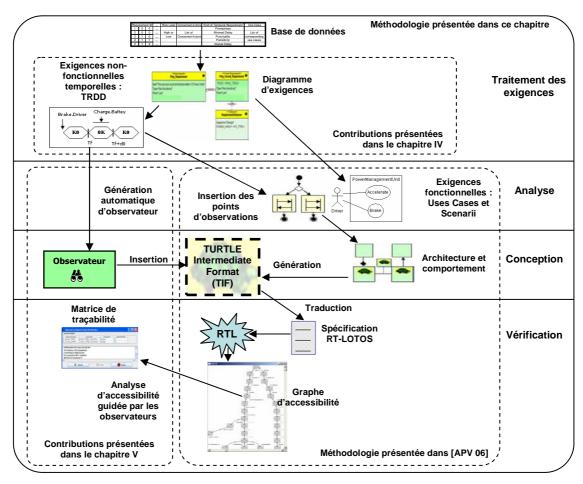

| Fig. 8.  | Méthodologie TURTLE pour la conception de systèmes temps réel                                                                                                               | 32              |

| Fig.9.   | Langage de description de la méthodologie (DP)                                                                                                                              | .36             |

|          | Méta-modèle du DP                                                                                                                                                           | . 37            |

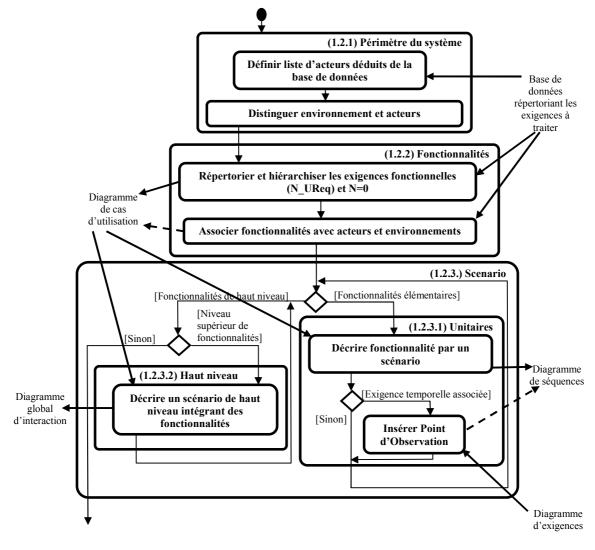

| Fig.11.  | DP de la phase de traitement des exigences                                                                                                                                  | 40              |

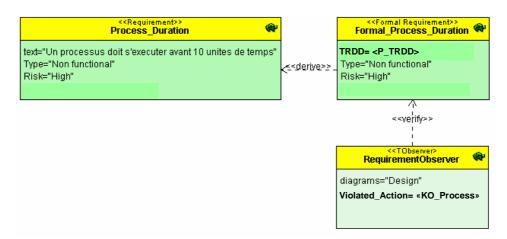

|          | Pattern du diagramme d'exigence incluant une exigence formelle                                                                                                              |                 |

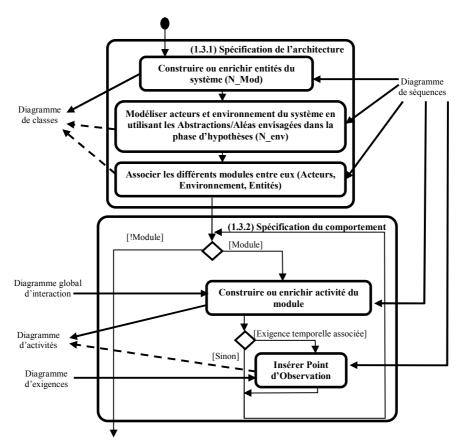

| Fig. 13. | DP de l'étape d'analyse                                                                                                                                                     | 44              |

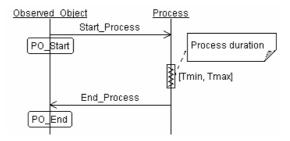

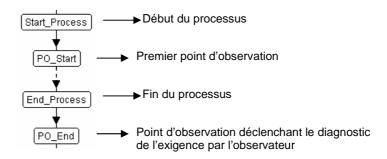

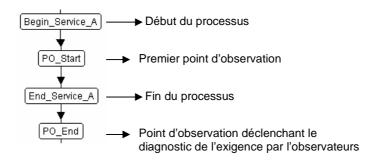

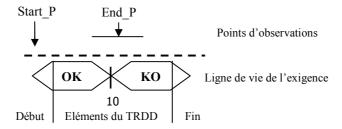

| Fig. 14. | Placement des points d'observation dans un diagramme de séquences TURTLE                                                                                                    | . 45            |

| Fig. 15. | DP de l'étape de conception                                                                                                                                                 | . 46            |

| Fig. 16. | Placement des points d'observations dans la classe observée                                                                                                                 | . 47            |

| Fig.17.  | DP de l'étape de vérification                                                                                                                                               | . 48            |

| Fig. 18. | Matrice de traçabilité de TURTLE pour la vérification d'exigences non-fonctionnelles                                                                                        | . 50            |

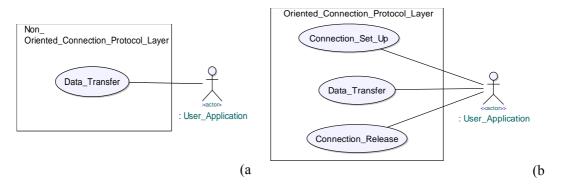

| Fig.19.  | Diagrammes de cas d'utilisation générique pour un protocole en mode connecté et non-                                                                                        | <i>5 1</i>      |

| E:- 20   | connecté                                                                                                                                                                    | -               |

| _        |                                                                                                                                                                             |                 |

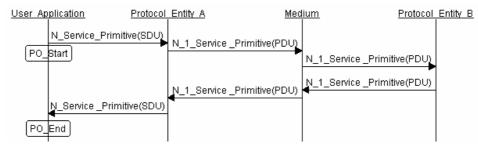

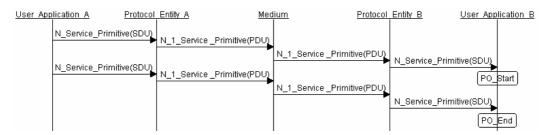

|          | Placement des points d'observation dans un diagramme de séquence TURTLE                                                                                                     |                 |

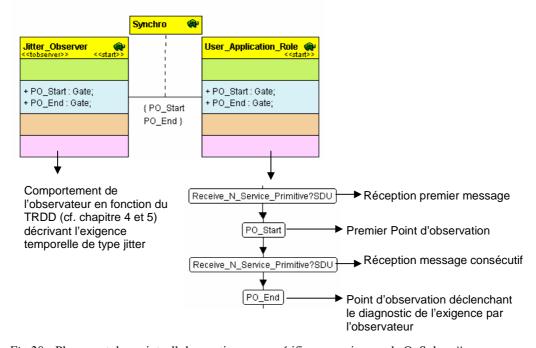

| F lg.22. |                                                                                                                                                                             | 55              |

| Ei~ 22   | « jitter »                                                                                                                                                                  | .55             |

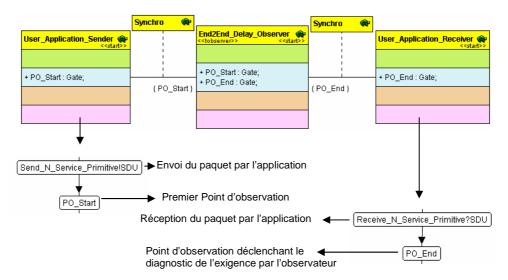

| F lg.∠3. | « end to end delay »                                                                                                                                                        | 56              |

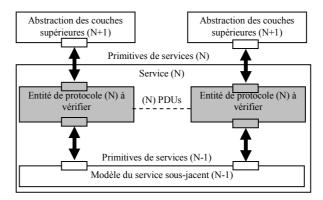

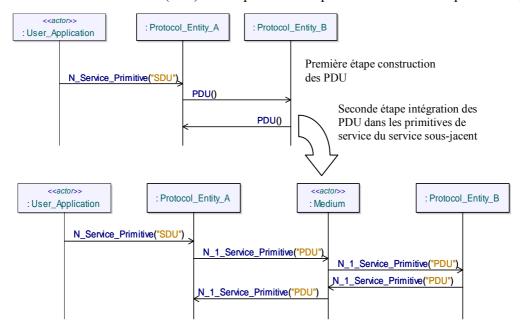

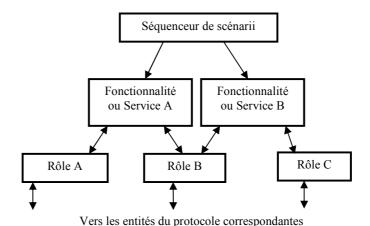

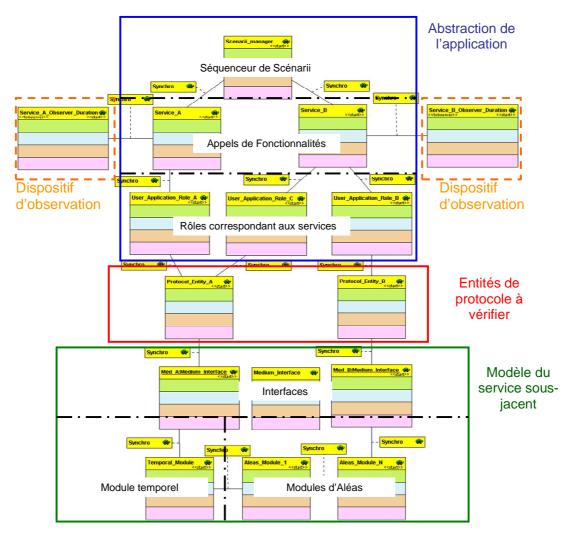

| Eia 24   | Description de l'abstraction des couches supérieures                                                                                                                        |                 |

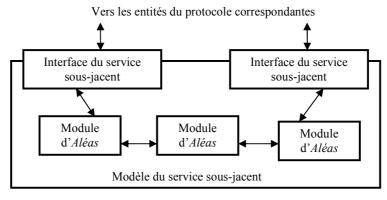

| _        | Description du modèle du service sous-jacent.                                                                                                                               |                 |

| _        | Pattern de diagramme de classes d'un protocole à vérifier.                                                                                                                  | <i>51</i><br>59 |

|          | Placement des points d'observations dans la classe d'appel de fonctionnalité Service A.                                                                                     |                 |

|          | Placement des points d'observations dans la classe d'apper de fonctionnaire service_A.  Placement des points d'observations pour vérifier une exigence de QoS de « jitter » |                 |

|          | Placement des points d'observations pour verrifer une exigence de Qos de « fitter »  Placement des points d'observations dans les classes applications pour vérifier une    | .00             |

| 1 lg.29. |                                                                                                                                                                             | . 61            |

| Fig. 20  |                                                                                                                                                                             | . 61<br>62      |

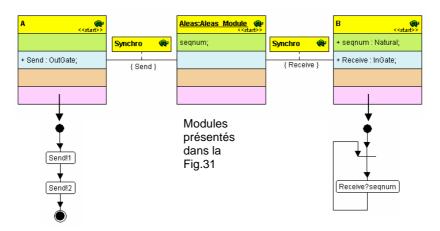

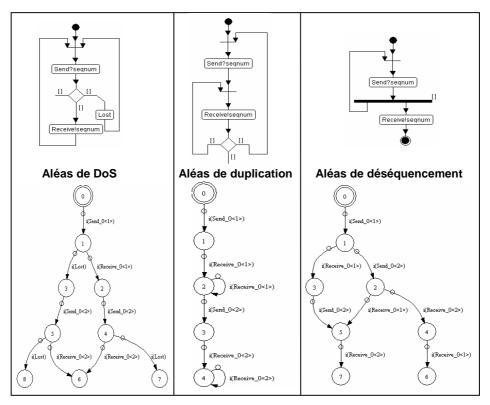

|          | Diagrammes d'activités et graphes d'accessibilité correspondant aux Aléas liés à un                                                                                         | 02              |

| 1 1g.31. | service non-fiable                                                                                                                                                          | 63              |

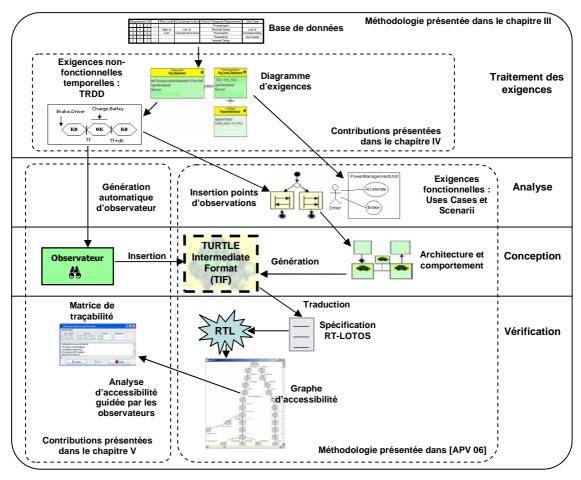

| Fig. 32  | Récapitulatif de la méthodologie et présentation des contributions                                                                                                          |                 |

| _        | Diagramme d'exigences TURTLE                                                                                                                                                | . 04<br>69      |

| _        | Méta-modèle du diagramme d'exigences TURTLE                                                                                                                                 | uə<br>71        |

| ェルミ・ノサ・  | TITOM INCADIO AU MUCIUMMO A CALCUICO I CIVILLI                                                                                                                              | / 1             |

| Fig. 35.       | Diagramme de description d'exigence temporelle de P_TRDD                                             | 72    |

|----------------|------------------------------------------------------------------------------------------------------|-------|

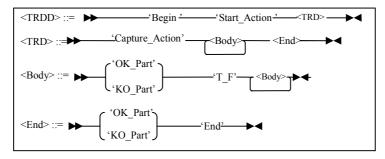

|                | Grammaire pour la construction de description d'exigences temporelles                                |       |

|                | Méta-modèle du TRDD.                                                                                 |       |

| Fig. 38.       | Méta-modèle décrivant les règles de construction du TRDD                                             | 75    |

|                | Exemples de TRDD                                                                                     |       |

| Fig. 40.       | Proposition d'extension des diagrammes d'exigences TURTLE                                            | 78    |

| Fig. 41.       | Méta-modèle d'une classe stéréotypé « TObserver »                                                    | 89    |

| Fig. 42.       | Méta-modèle du diagramme d'activités d'un observateur                                                | . 92  |

|                | Méta-modèle des règles de construction du diagramme d'activités d'un observateur                     |       |

|                | Application des algorithmes 2, 3 et 4 aux exemples de la Fig.39 (chapitre IV page 68)                |       |

| Fig. 45.       | Génération des observateurs                                                                          | 98    |

| Fig. 46.       | Méta-modèle du package TIF incluant des observateurs                                                 | 99    |

| Fig. 47.       | Caractérisation du placement des points d'observations                                               | .103  |

| Fig. 48.       | Vers l'implantation de nos travaux                                                                   | .105  |

| Fig. 49.       | Architecture de modélisation de communications de groupes sécurisées                                 | .111  |

| Fig. 50.       | Diagramme d'exigence EC Duration                                                                     | . 114 |

| Fig. 51.       | Diagramme de classes simplifié du protocole de gestion de clés                                       | .115  |

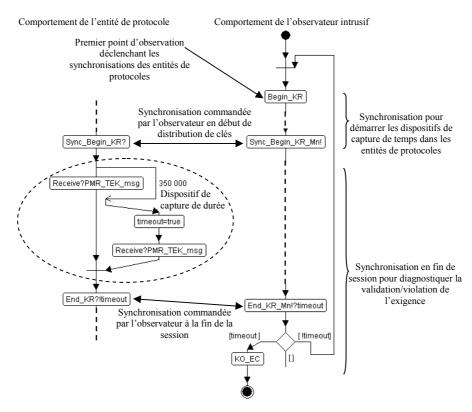

| Fig. 52.       | Diagramme d'activités d'une entité du protocole de gestion de clés et de l'observateur               | .116  |

| Fig. 53.       | Récapitulatif de la méthodologie et présentation des contributions                                   | .120  |

| Fig. 54.       | Caractérisation du dispositif d'observation pour le déploiement                                      | .122  |

| 11             | ndex des tableaux                                                                                    |       |

| <i>Tab.1</i> . | Taxonomie des exigences non-fonctionnelles temporelles inhérentes aux systèmes                       |       |

| T. 1. 2        | temps réel                                                                                           |       |

|                | Sémantique des éléments du diagramme d'activité TURTLE                                               |       |

|                | Guide de lecture du chapitre III.                                                                    | 38    |

| 1 ab. 4.       | Base de données répertoriant les exigences à traiter dans la phase de recueil                        | 4 1   |

| T 1 5          | d'exigences                                                                                          | 41    |

| 1ab.3.         | Base de données répertoriant les exigences enrichies dans la phase de spécification                  | 40    |

| T 1 6          | d'exigences                                                                                          |       |

|                | Langages visuels basés sur la description de scenarii                                                |       |

|                | Langages visuels basés sur les chronogrammes.                                                        | 6     |

|                | Sémantique des éléments du TRDD.                                                                     |       |

| Tab.9.         |                                                                                                      | 73    |

| Tab. 10        | Table de traduction des descriptions d'exigences temporelles TURTLE en diagramme d'activités TURTLE. | 73    |

|                | d'activités TURTLE                                                                                   |       |

|                | d'activités TURTLE                                                                                   |       |

| Tab.11         | d'activités TURTLE                                                                                   | 91    |

|                | d'activités TURTLE                                                                                   | 91    |

# Index

| <i>Tab.13</i> . | Base de données | présentant l'exigence | de délai de renouv | ellement de clés 1 | 113 |

|-----------------|-----------------|-----------------------|--------------------|--------------------|-----|

|                 |                 |                       |                    |                    |     |

# Index des définitions

| Définition 1 : Processus de développement   | 36 |

|---------------------------------------------|----|

| Définition 2 : Diagramme d'exigences        |    |

| Définition 3 : Exigence informelle          | 69 |

| Définition 4 : Exigence temporelle formelle |    |

| Définition 5 : Observateur.                 |    |

| Définition 6 : TRDD                         | 73 |

| Définition 7 : Diagramme d'exigences étendu | 79 |

| Définition 8 : Observateur.                 |    |

# **Chapitre I.** Introduction

# 1. Développer des systèmes temps réel fiables

Le domaine du temps réel touche des applications, très variées dans la vie quotidienne, telles que le guidage ou la navigation (de bateaux, d'avions, de train ou d'automobile), le contrôle de processus industriels, la robotique, les télécommunications (téléphones portables, satellites), les transactions bancaires ou même les loisirs (jeux vidéo). Si certaines défaillances apparaissent dans ce type de systèmes, cela peut conduire à des pannes, des pertes de données ou de temps qui peuvent être catastrophiques pour certaines applications (avions, automobiles, bateaux, trains, centrales nucléaires). A cette criticité en vies humaines s'ajoute également une notion de criticité économique et le besoin de satisfaire le client.

Les domaines des transports et des banques, pour n'en citer que quelques uns, ont déjà une longue tradition de la recherche de la fiabilité, eu égard à la criticité des systèmes qu'ils déploient. Ces domaines sont ceux où les méthodes de développement de systèmes sont les plus rigoureuses (pensons aux organismes de certification en aéronautique qui tendent aussi à être intégrés dans le domaine de l'automobile), faisant parfois appel aux *méthodes formelles* que le reste de l'industrie juge, avec une opinion préconçue, souvent inutilement compliquées et lourdes à mettre en œuvre.

L'intérêt de ces méthodes formelles n'a cessé de croître avec l'essor des systèmes distribués. Des défaillances locales qui n'avaient auparavant aucune conséquence, peuvent maintenant entrainer des pannes plus significatives de par la « connectivité » des systèmes déployés à grande échelle (Internet par exemple) et en interdépendances croissantes. L'on assiste donc à un intérêt grandissant pour les méthodes, langages et techniques permettant d'améliorer rapidement et efficacement la qualité de systèmes répondant aux attentes du client. L'utilité de ces méthodes formelles est avérée en matière de validation de systèmes a priori puisqu'une vérification formelle de modèle permet de confronter un modèle de conception aux exigences à valider pour détecter les erreurs de conception sans attendre la réalisation d'un prototype voire même du système effectif.

# 2. L'émergence d'un consensus : UML

L'Unified Modeling Language (UML) [UML] [BOO 03] est un langage pour documenter et spécifier graphiquement tous les aspects d'un système à logiciel prépondérant. L'ambition des promoteurs d'UML est de fédérer en une seule notation les meilleures caractéristiques des différents langages de modélisation qui utilisent le paradigme objet. En tant que standard de l'OMG (Object Management Group) [OMG], UML jouit d'une popularité sans précédent à la fois dans le monde industriel et académique. UML se veut être un médium, sous forme de modèle graphique, servant à harmoniser les différents acteurs concourant à la réalisation d'un système, et à garantir la cohérence et la qualité de la conception.

UML présente l'avantage de pouvoir se décliner sous forme de « profils » spécialisés en fonction des domaines d'application considérés (pour le temps réel par exemple [OMG 05] [OMG 07]). Ces profils permettent aussi de combler des lacunes d'UML en termes de sémantique pour servir de pivot à des outils de validation (dans notre cas la vérification formelle). Les outils dédiés aux profils « UML temps réel », c'est-à-dire aux personnalisations d'UML destinées à mieux prendre en compte le caractère réactif de ces systèmes mais aussi l'expression d'exigences et de mécanismes temporels, pêchent par le volet méthodologique. La manière d'utiliser le profil est insuffisamment et informellement documentée (manque de modèles génériques par exemple). De surcroit, l'objectif de *traçabilité des exigences* si souvent affiché n'est que partiellement atteint dans la mesure où certaines exigences doivent être décrites hors du modèle UML et reliées de manière ad-hoc et non automatisable à la validation de modèle.

Une qualité importante du langage UML est de se construire autour des fonctions que le système doit offrir (c'est-à-dire les *exigences fonctionnelles*); ce sont les *cas d'utilisations*. Ce concept permet d'avoir un vue opérationnelle du système en termes de mécanismes à concevoir, ce qui convient bien pour décrire des solutions logicielles (architectures, comportement). Mais UML est mal adapté pour décrire le problème à résoudre - l'objet même du cahier des charges - les *exigences non-fonctionnelles* (dans le domaine temporel, par exemple, le temps de sortie des trains d'atterrissage d'un avion). Or ces *exigences non-fonctionnelles* influencent toutes les définitions des mécanismes définis dans des *cas d'utilisations*.

# 3. Les réponses apportées par l'ingénierie des exigences

Pour palier le problème de l'expression des *exigences non-fonctionnelles*, l'ingénierie des exigences [LAM 06] [HUL 04] définit le concept d'objectif et permet de formuler plus précisément les *exigences*, *fonctionnelles* ou *non-fonctionnelles*. L'utilisation des techniques de modélisation orientées « objectifs » [LAM 06] permet d'élaborer le cahier des charges d'un système de manière rigoureuse. En effet, à partir d'un objectif donné, en se posant la question du « pourquoi », on peut identifier des objectifs de haut niveau à satisfaire ; en se posant la question du « comment », on peut identifier l'ensemble des mécanismes qui vont permettre d'atteindre les objectifs en question.

Dans ce contexte, l'OMG a récemment normalisé SysML [SysML] amenant avec lui, entre autres concepts, l'idée de pouvoir formuler des exigences au moyen d'un *diagramme d'exigences*. Ceux-ci concourent à assurer, à des fins documentaires, un suivi de ces exigences dans le cycle de développement du système par la construction d'une *matrice de traçabilité*. Notons néanmoins que

dans les premiers outils disposant de plug-ins SysML (par exemple, TAU G2.3.1 [TAU]), les exigences sont décrites de manière totalement informelle et sans lien automatisé avec les fonctionnalités de validation de modèles.

# 4. Contributions apportées dans ce mémoire

Les travaux présentés dans ce mémoire se concentrent sur les phases amont (traitement des exigences – analyse – conception) du cycle de développement de systèmes temps réel à logiciel prépondérant en donnant une place majeure à la vérification formelle des exigences temporelles.

Les principales contributions de ce mémoire visent donc à :

- Définir un volet « méthodologie » d'utilisation de profils UML/SysML temps réel reposant sur des outils de vérification formelle qui distingue explicitement aspects fonctionnels et non-fonctionnels. La méthodologie présentée dans ce mémoire intègre l'aspect formalisation et vérification pour assurer la traçabilité des exigences non-fonctionnelles temporelles qui sont occultées dans de très nombreuses méthodologies UML (par exemple [BOO 00] [ROQ 04] [DOU 04]). Avant de présenter la méthodologie en question, ce mémoire introduit un langage de description de processus méthodologique qui intègre la notion de production/consommation de biens livrables (en l'occurrence des diagrammes UML et SysML). Notons que la méthodologie proposée s'appuie sur des diagrammes UML et SysML (d'exigences, d'analyse de conception) génériques et réutilisables bien qu'elle ait pour finalité d'être instanciée dans le profil UML TURTLE [APV 04] [APV 06] (Timed UML and RT-LOTOS Environment).

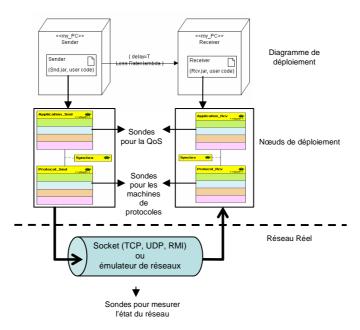

- Spécialiser la méthodologie dans le domaine des protocoles en prenant en compte les exigences liées au concept de *Qualité de Service* (QoS). Pour utiliser le profil TURTLE en conception de protocoles, ce mémoire établit un ensemble de règles de définition d'exigences, mais aussi de construction de diagrammes d'analyse et de conception liés au concept de *qualité de service* dans les protocoles temps réel (en terme de *gigue* et *délai de bout en bout*). Indépendantes de TURTLE, ces règles sont généralisables à d'autres profils UML.

- Enrichir les capacités de modélisation du profil UML TURTLE pour la phase de traitement des exigences. Les diagrammes d'exigences de SysML [SysML] sont étendus pour séparer les exigences informelles des exigences formelles et en particulier des exigences nonfonctionnelles temporelles présentant une occurrence de début et de fin afin de mesurer leur distance temporelle. Ces dernières sont définies non pas par des formules de logique [HUT 04], mais par un langage visuel basé sur la représentation en chronogrammes et appelé diagramme de description d'exigences temporelles (Timing Requirement Description Diagram ou TRDD). Ces contributions sont présentées au travers de définitions formelles et de méta-modèles afin de les rendre réutilisable dans des profils UML/SysML autres que TURTLE.

- Construire un dispositif automatisé permettant de tracer les exigences non-fonctionnelles par vérification guidée par observateurs. Ce dispositif repose sur la génération automatique d'observateurs à partir d'une spécification des exigences temporelles par les diagrammes d'exigences étendus et les TRDD. Cette génération automatisable s'effectue en deux grandes étapes : la construction du comportement de l'observateur (à partir de la spécification de

l'exigence en TRDD) et la construction du modèle observable contenant le modèle du système couplé avec l'observateur. Ce modèle observable est dérivé du modèle TURTLE de conception. Ces contributions sont présentées sous formes d'algorithmes validés expérimentalement et en cours d'implantation dans l'outil TTool [TTOOL] qui supporte le profil TURTLE.

- Caractériser l'insertion d'un observateur dans le modèle à observer. Cet aspect présente un caractère fondamental de la vérification guidée par observateurs. Si ces derniers ne sont pas greffés correctement dans le modèle cela conduit à un mauvais diagnostic de l'observateur. Nous avons donc proposé des patterns de placement « correct » des observateurs caractérisant différentes exigences temporelles que l'on cherche à vérifier dans le modèle (mesurer la durée d'une fonctionnalité ou d'un service, mesurer la gigue au niveau de l'application ou le délai de bout en bout d'un protocole).

- Instancier l'ensemble de nos travaux dans un projet industriel. Le projet RNRT SAFECAST [SFC] dédié à la conception d'un protocole de communication de groupes sécurisée, a permis d'instancier sur un système distribué et temps réel complexe la méthodologie et le traitement d'exigences proposés dans ce mémoire. En complément à la vérification orientée sécurité décrite en [L 4.1], nous avons apporté à EADS (leader du projet) des preuves de satisfaction (ou non) d'exigences temporelles. L'on notera en particulier notre contribution aux livrables du projet ([L 2.5] [L 4.1] [L4.2] [L 4.3] [L 3.4] [L 4.4]).

# 5. Organisation du mémoire

Ce mémoire est structuré de la manière suivante.

Le chapitre II définit le contexte et les champs d'application de nos travaux. Nous introduisons, dans un premier temps, les exigences posées par les systèmes temps réel et dans un second temps les méthodologies associées à la conception de ce type de systèmes. Puis, nous spécialisons la discussion précédente vers les systèmes qui sont à la fois temps réel et distribués. Nous décrivons ensuite le profil UML temps réel TURTLE [APV 04] et les éléments de méthodologie qui avaient été proposés pour ce profil avant que ne démarrent les travaux présentés dans ce mémoire [APV 06]. Enfin, nous dressons un bilan général des différents travaux présentés dans ce chapitre en identifiant les points durs non-traités pour annoncer les chapitres suivants de ce mémoire.

Le chapitre III présente une proposition de méthodologie pour la vérification des exigences temporelles dans un système temps réel et en particulier les protocoles. Nous introduisons, tout d'abord, un langage de description de processus méthodologique utilisé dans la suite du chapitre. Ensuite, nous présentons une méthodologie de conception de systèmes temps réel en contexte UML/SysML, en se dégageant d'outils UML particuliers dans un premier temps puis en se focalisant sur le profil UML TURTLE. Enfin, cette méthodologie est spécialisée pour la conception de protocoles temps réel.

Le chapitre IV est consacré aux diagrammes de la phase de traitement des exigences dans le profil TURTLE. Après avoir présenté un état de l'art des travaux dédiés aux langages de description formelle d'exigences temporelles, nous introduisons les diagrammes utilisés en TURTLE pour spécifier les exigences non-fonctionnelles temporelles. Il s'agit d'une combinaison des diagrammes

#### Chapitre I. Introduction

d'exigences SysML et des diagrammes de description d'exigences temporelles (*Timing Requirement Description Diagram ou* TRDD en abrégé). Enfin, nous proposons des extensions aux diagrammes d'exigences TURTLE pour décrire l'aspect compositionnel des exigences temporelles en introduisant les notions de raffinement et de satisfaction d'exigences fonctionnelles.

Le chapitre V traite du volet « vérification d'exigences non-fonctionnelles temporelles » de TURTLE. Après avoir recensé les différentes méthodes de vérification d'exigences temporelles, nous présentons le processus de vérification d'exigences temporelles guidée par observateurs dans le profil TURTLE. Enfin, nous précisons les hypothèses de fonctionnement de ce processus avant de caractériser le placement des *points d'observations*, élément crucial dans la *vérification guidée par les observateurs*.

Le chapitre VI décrit l'instanciation de nos travaux dans un projet industriel, SAFECAST [SFC], qui soulève une problématique de communication de groupe sécurisée. Après avoir brièvement décrit les objectifs de ce projet, nous positionnons notre contribution à SAFECAST par rapport aux travaux du domaine. Ensuite, nous proposons des canevas d'exigences et d'architecture incluant les différents services du protocole SAFECAST. Puis nous présentons le modèle TURTLE pour la vérification formelle d'une exigence temporelle concernant la durée du service de génération et de distribution des clés, point dur de l'architecture SAFECAST.

Le chapitre VII conclut ce mémoire en dressant un bilan de nos contributions et en ouvrant des perspectives à notre travail.

# Chapitre II. Contexte et positionnement des travaux

Le travail présenté dans ce mémoire est centré sur la vérification d'exigences temporelles et le développement d'une méthodologie qui intègre pleinement ce traitement. Aussi, ce chapitre dresse-til un état de l'art en matière d'exigences et de méthodologies proposées par d'autres auteurs pour les systèmes temps réel centralisés, puis distribués.

Ce chapitre est structuré comme suit. La section 1 recense dans un premier temps les exigences posées par les systèmes temps réel et dans un second temps les méthodologies associées à la conception de ce type de systèmes. La section 2 spécialise la discussion précédente vers les systèmes qui sont à la fois temps réel et distribués. La section 3 présente le profil UML temps réel TURTLE adossé au langage formel RT-LOTOS et expose les éléments de méthodologie publiés jusqu'ici pour ce profil, antérieurement aux (et indépendamment des) contributions présentées dans ce mémoire. Enfin, la section 4 dresse un bilan général des différents travaux présentés dans ce chapitre et identifie les points durs non-traités,.

# 1. Les systèmes temps réel (STR)

# 1.1. Exigences posées par les STR

[HUL 04] distingue deux classes d'exigences dans un système :

- Les exigences fonctionnelles représentent les différentes fonctionnalités que devra satisfaire le système et correspondent à l'aspect opérationnel de ce système. En matière de vérification formelle, on associe généralement ce type d'exigences à des « propriétés générales » telles que l'absence de blocage non désiré (« deadlock »), l'absence de fonctionnement cyclique infini non désiré (« livelock ») ou encore la possibilité de revenir à l'état initial.

- Les exigences non-fonctionnelles correspondent aux critères de qualité attendus du système, par exemple en termes de performances temporelles. A titre d'exemple, pensons aux différentes garanties temporelles (par exemple des délais maximum ou minimum) que doit satisfaire un système temps réel.

Dans le domaine du temps réel, les *exigences non-fonctionnelles temporelles* se répartissent plus précisément en deux catégories [WAH 94]:

- Les exigences où le temps est exprimé de manière qualitative (ou *logique*). On ne considère alors qu'un ordre partiel entre événements (par exemple un ascenseur doit être à l'arrêt pour que la porte s'ouvre).

- Les exigences où le temps est exprimé de manière quantitative. On considère dans ce cas l'ordre des événements mais aussi les distances temporelles entre ces derniers (par exemple la porte d'un ascenseur doit s'ouvrir deux secondes après l'arrêt de la cabine).

Dans le domaine de la vérification formelle d'exigences temporelles quantitatives, il existe deux manières de représenter le temps [ALU 94] :

- En l'exprimant de manière *discrète* en considérant le temps comme une horloge préalablement définie. Le modèle temporel correspondant est donc basé sur une horloge discrète. Cette expression du temps peut s'avérer être un facteur limitant : par exemple, si un système a des constantes de temps variant de 1 à 10000, considérer une horloge discrète de granularité 1 engendre un nombre d'états prohibitif dans le modèle. D'autre part, l'utilisation du temps discret, par la construction d'une horloge discrète, suppose la connaissance exacte de la durée totale d'exécution du système, c'est-à-dire des durées des diverses opérations à réaliser.

- En l'exprimant de manière *continue* en considérant le temps comme une succession d'horloges et de frontières temporelles. Pour cela on construit un modèle plus fin où l'on peut utiliser différentes horloges pour spécifier le comportement temporel du système. Outre la meilleure prise en compte des différentes granularités temporelles du système, cette représentation du temps permet aussi de prendre en compte une *incertitude sur les contraintes temporelles* du système (durée des tâches, des communications).

Ce mémoire se focalise sur les *exigences non-fonctionnelles temporelles* quantitatives où le temps est représenté de manière *continue*. Ces dernières correspondent à des propriétés de *vivacité bornée* [ALU 93] issues de la classe des propriétés de *sûreté*<sup>2</sup> (« *safety* ») liées à la correction partielle du système. Les propriétés de *vivacité bornée* se voient affecter une date butoir pour laquelle la propriété n'est plus satisfaite [ALU 93]; ceci implique donc que le système doit être borné temporellement pour pouvoir être vérifié.

Le Tab.1 présente les exigences non-fonctionnelles correspondant à des propriétés de *vivacité* bornée définies dans [ALU 93]. On note la relation de satisfaction d'une exigence E sur un système S par S \ \delta E.

| Nom de la classe d'exigence          | Définition                                                                                                                                                                                                                                                                                        |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Délai maximum</b> (Promptness)    | E assure qu'un événement devra obligatoirement se produire avant un certain délai $D_{max}$ . $S \models E$ est vrai si cet événement s'est produit avec un délai strictement inférieur au délai maximum $D_{max}$ .                                                                              |

| <b>Délai minimum</b> (Minimal Delay) | E assure qu'un événement ne devra jamais se produire avant un certain délai $D_{min}$ . $S \models E$ est vrai si cet événement s'est produit avec un délai strictement supérieur au délai minimum $D_{min}$ et inférieur à la date butoir où l'exigence n'est plus satisfaite (vivacité bornée). |

| Ponctualité (Punctuality)            | E assure qu'un événement devra obligatoirement se produire à un instant T. S   E est vrai si cet événement se produit à cet instant T.                                                                                                                                                            |

<sup>&</sup>lt;sup>1</sup> Une propriété de vivacité assure qu'un événement sous certaines conditions devra fatalement se produire.

<sup>2</sup> Une propriété de sûreté assure qu'un événement sous certaines conditions ne doit jamais se produire.

| <b>Périodicité</b> (Periodicity)    | E assure qu'un événement devra obligatoirement se                            |  |  |

|-------------------------------------|------------------------------------------------------------------------------|--|--|

|                                     | produire régulièrement à un instant T. S \( \bigs \) E est vrai si cet       |  |  |

|                                     | événement se produit aux instants modulo T.                                  |  |  |

| <b>Délai borné</b> (Interval Delay) | E assure qu'un événement devra obligatoirement se                            |  |  |

|                                     | produire entre/hors un intervalle temporel $]T_{min}; T_{max}[. S \models ]$ |  |  |

|                                     | E est vrai si cet événement se produit entre/hors cet                        |  |  |

|                                     | intervalle temporel $]T_{min}; T_{max}[.$                                    |  |  |

Tab.1. Taxonomie des exigences non-fonctionnelles temporelles inhérentes aux systèmes temps réel

Le choix d'exprimer les exigences dans les bornes strictes (inférieures et/ou supérieures) n'est pas anodin ; il correspond au non-déterminisme temporel de la sémantique du langage TURTLE (cf. chapitre V section 3.1) sur lequel s'instancie la méthodologie présentée au chapitre III de ce mémoire.

# 1.2. Méthodologies de conception de STR

Cette section recense des méthodologies de conception de systèmes temps réel. La section 1.2.1 présente brièvement les méthodologies antérieures à la normalisation d'UML. La section 1.2.2 dresse un panorama des méthodologies dédiées au langage UML. Enfin, la section 1.2.3 recense des méthodologies reposant sur les méthodes formelles.

## 1.2.1. Avant UML

La méthode MERISE [TAR 83] orientée « systèmes d'informations », a rencontré un succès certain dans les années 80. La conception du système d'information repose sur un *cycle d'abstraction* composé d'étapes afin d'aboutir à un système d'information fonctionnel proche de la réalité. La méthode MERISE préconise d'analyser séparément données et traitements dans chaque étapes. Le passage à une autre étape correspond à un point de validation et de décision. Il s'agit donc de valider une à une chacune des étapes en prenant en compte les résultats de l'étape précédente. Une telle démarche est beaucoup trop rigide à cause des nombreux points de validation nécessitant de remonter au système général à la fin de chaque *cycle d'abstraction*. Enfin, si nous mentionnons MERISE de par sa large diffusion et les comparaisons fréquentes avec les méthodologies basées UML, il faut rappeler que cette méthode n'a pas du tout été conçue pour les STR.

Moins rigide que MERISE du point de vue validation, SA-RT (*Structured Analysis - Real Time*) [HAT 87] se répandit vers le début des années 1990 comme l'un des standards de description systèmes temps réel. SA-RT est une méthode graphique de description d'un système temps réel complexe par *analyse fonctionnelle descendante* [HAT 87]. L'analyse chemine du général vers le particulier et le détaillé contrairement à MERISE qui opère des retours successifs au système général. SA-RT s'appuie sur différentes descriptions du système à concevoir : vue statique présentant les transformations de données et vue dynamique présentant les réactions du système face à des stimuli de son environnement. Le temps est représenté dans la vue dynamique de manière logique par des machines à états finis (ce formalisme permettant de décrire la réaction du système face à des stimuli extérieurs au système).

Ni MERISE, ni SA-RT ne prennent en compte le fait qu'un système ou une partie d'un système peut être vue comme un ensemble de modules (notion de *modularité*) éventuellement réutilisables (notion de *portabilité*). D'où l'introduction de méthodes de conception orientée objet qui

intègrent les concepts de *modularité* et *portabilité*. Ces méthodes basées sur des langages de modélisation orienté objet (comme OMT<sup>3</sup> [RUM 91]) ont été utilisées dans l'industrie pour la conception des systèmes temps réel avant la normalisation d'UML. Cependant ces méthodes ne prennent pas en compte explicitement les besoins du client et le fait que ce dernier peut changer d'avis pendant un projet.

En introduisant le concept de développement adaptatif, les méthodes de types AGILE [AGIL] (dont la plus utilisée est la méthode *eXtrem Programming* [KEN 00]) présentent de très bonnes solutions de rapidité dans le développement et de prise en compte de modifications demandées par les clients durant le cycle de développement. L'aspect itératif et incrémental présenté dans les méthodes AGILE est donc pris en compte dans la méthodologie présentée au chapitre III de ce mémoire. Impliquer le client dans le projet favorise la conception d'un système qui réponde à ses attentes. Il faut donc construire un modèle du système autour des *cas d'utilisation* qui correspondent aux besoins et exigences des utilisateurs. L'on parle alors de « bonne pratique » (notion de *best practices*) dans le développement de système.

# 1.2.2. Les méthodologies orientées UML

En intégrant des modèles orientés autour des *cas d'utilisation* et les notions de *modularité* et *portabilité*, les méthodes de type UP (*Unified Process*) [BOO 00] s'imposent très souvent dans des grands projets (méthode *Rational Unified Process* ou RUP). Elles sont construites autour du langage semi-formel UML [UML]. Un processus unifié (UP) est « *itératif et incrémental, centré sur l'architecture, construit à partir des cas d'utilisations et piloté par les risques* » [BOO 00]. Un processus unifié doit être vu comme une trame commune de meilleures pratiques de développement, et non comme une tentative d'élaborer un processus universel.

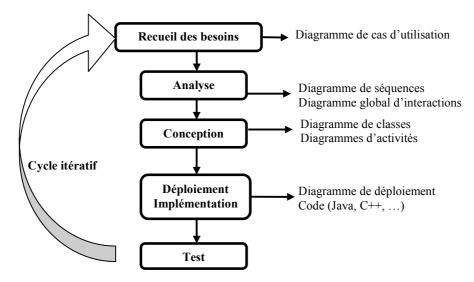

La Fig.1, montre le cycle itératif d'une méthode UP, découpé en 5 activités de développement :

- Le recueil des besoins. Cette activité permet de définir les différents besoins (ou exigences) et de faire la distinction entre besoins fonctionnels qui conduisent à l'élaboration des modèles de cas d'utilisations et les besoins non-fonctionnels qui forment une liste d'exigences à satisfaire. Le modèle de cas d'utilisation présente le système du point de vue de l'utilisateur sous forme de cas d'utilisation et d'acteur. Il est représenté par un diagramme de cas d'utilisations UML.

- L'analyse. L'objectif de cette activité est d'accéder à une compréhension des besoins et des exigences. Ceci correspond à la livraison de spécifications du modèle d'analyse. Ce dernier livre une spécification complète des exigences fonctionnelles (*les cas d'utilisations* appelées très souvent *besoins*) et les structure sous forme de scénarii pour faciliter la compréhension. Le modèle correspondant est décrit en UML par des diagrammes de séquences et des diagrammes globaux d'interaction; il permet d'établir des passerelles avec le modèle de conception.

- La *conception*. Cette activité permet d'acquérir une compréhension approfondie des contraintes liées au langage de programmation, à l'utilisation et à la collaboration des

<sup>&</sup>lt;sup>3</sup> OMT est le langage de modélisation orienté objet qui a été fusionné dans UML (principalement dans les diagrammes de conception).

différents composants du système ainsi qu'au système d'exploitation. Dans cette activité, on détermine les principales interfaces et on les transcrit en *diagrammes de classes* UML. Ceci permet ensuite de coder dans l'activité suivante avec un langage orienté objet de type Java ou C++. Ceci prépare la phase d'implémentation en décomposant le système en sous-systèmes qui correspondent aux différentes classes du système et en définissant le comportement interne de chaque classe par des diagrammes UML, par exemple des *diagrammes d'activités* ou des *machines à états*.

- L'implémentation et déploiement se basent sur la conception pour programmer le système sous forme de classes (codes sources, scripts, binaires ou exécutables). Les objectifs principaux de cette activité concernent la planification de l'intégration des composants pour chaque itération, et la production des classes et des sous-systèmes sous forme de code source. Le modèle de déploiement est décrit en UML par des diagrammes de déploiement.

- Le *test* permet enfin de confronter les résultats de l'implémentation avec des *cas de test* planifiés pour chaque itération à partir du recueil des besoins.

Fig.1. Cycle de vie des systèmes selon la méthode UP

La méthode 2TUP (2 Track Unified Process) [ROQ 04] est une méthode UP qui apporte une réponse aux contraintes de changements continuels imposés aux systèmes d'information. Le terme « 2 Track » signifie littéralement que le processus suit deux chemins. Il s'agit des chemins fonctionnels formulés par le client et d'architecture technique définis par l'équipe de conception. Ce dernier chemin permet la conception d'un prototype dépendant le moins possible des aspects fonctionnels et réutilisable dans d'autres projets. Cette distinction nous parait donc une bonne piste dans la distinction des différentes exigences fonctionnelles (distingués par fonctionnels et techniques) dans le système mais ne permet pas spécifier les exigences non-fonctionnelles contrairement à la méthodologie présentée dans ce mémoire.

ROPES (*Rapid Object-Oriented for Embedded Systems*) [DOU 04] spécialise la méthode UP dans le cadre de la conception de systèmes temps réel. Cette méthode encourage la synthèse

automatique de code pour faciliter la génération rapide de prototypes à partir des modèles spécifiés dans le profil UML SPT [OMG 05] (cf. section 3.1.4) qui spécialise la norme UML dans le domaine des systèmes temps réel. La classification des exigences fonctionnelles (prioritaire, risque, standardisation possible) [DOU 04] présente une bonne solution pour définir de manière complète des exigences fonctionnelles (fonctionnalités). La méthodologie proposée au chapitre III reproduit la même approche en intégrant un élément manquant dans le cycle de développement à savoir la définition des exigences non-fonctionnelles temporelles, élément prépondérant dans le développement de systèmes temps réel.

Enfin, le survol de toutes ces méthodes de conception basées sur le langage semi-formel UML très utilisées dans le milieu industriel nous amène à faire le constat que la validation du système est basée uniquement sur le test du code. Ceci est regrettable car des fautes de conception dues à un défaut de validation *a priori* sont découvertes lors de la première phase d'implémentation. Des solutions peuvent être apportées par l'utilisation de méthodes formelles, permettant de générer un modèle exécutable pour détecter des erreurs de conception *a priori* lors des premières étapes du cycle de développement d'un système temps réel.

# 1.2.3. Les méthodes formelles dans la conception et la validation des STR

Parmi les nombreuses taxonomies applicables aux langages formels de modélisation, nous distinguons dans cette section :

- D'une part, les langages tels que la méthode B [ABR 96], qui relèvent du « correct par construction » dans la mesure où le concepteur démarre par une spécification embryonnaire et fait évoluer son modèle par une série de transformations qui garantissent à chaque étape la préservation des propriétés qui étaient satisfaites à l'étape antérieure. A chaque étape du développement, des obligations de preuve sont imposées. Une obligation de preuve est une propriété qui doit être satisfaite pour que le système construit soit « correct par construction » [ABR 96].

- D'autre part, les langages qui impliquent que le modèle doit être vérifié a posteriori et de manière systématique à la suite de chaque grande étape du le cycle de développement.

L'approche proposée ultérieurement dans ce mémoire repose sur cette seconde catégorie de langages.

S'appuyant également sur la deuxième catégorie de langage, les travaux de [BAB 01] présentent une méthode de développement de systèmes embarqués basée sur le langage SDL [SDL 99] et appelée PROSEUS (Development method for PROtotyping embedded SystEms by using UML and SDL). [BAB 01] fait l'hypothèse que l'analyse des besoins fonctionnels et la conception ont été spécifiées en UML puis traduits en SDL. Afin d'intégrer les contraintes temps réel dans le modèle du système, [BAB 01] propose un typage des signaux échangés entre système et événements qui modélise les contraintes de temps de l'application à développer. Les paramètres des signaux contiennent des caractéristiques temporelles exprimées en logique temps réel [JAH 86] et définies selon le mode de propagation [BAB 98]. L'étude se focalise ensuite sur la phase de définition de l'architecture de l'application, phase fondamentale dans les systèmes temps réel embarqués car les choix effectués au niveau de l'architecture influent directement sur les performances du système [BAB 01]. La définition de l'architecture matérielle et logicielle (qui peut être exprimée par des

diagrammes UML de déploiement et de composant) s'appuie sur des structures types définies en SDL qui représentent les unités de traitement du système, les médiums de communication et l'environnement. A chaque signal, on associe des contraintes temporelles à partir du modèle précédent. Cette approche autorise une modélisation fine des contraintes du système (liées aux unités de traitement du système, aux médiums de communication et à l'environnement). Ceci nous a donné des pistes pour définir les cycles itératifs de la méthodologie présentée dans ce mémoire (cf. chapitre III section 3.1.2 et 4.1.2). Le modèle du système doit être conçu dans un premier temps dans un contexte atemporel. Ensuite, les paramètres temporels sont insérés non pas dans les signaux comme en [BAB 01] mais dans les diagrammes d'activités TURTLE (cf. section 3.1.2.2 de ce chapitre).

S'inscrivant entièrement dans un processus UP, ACCORD|<sub>UML</sub> [ACCOR] est une méthodologie orientée développement de modèles d'applications temps-réel distribuées et embarquées. L'objectif général de la méthodologie est de masquer autant que possible les aspects d'implantation autour d'une approche dirigée par les modèles (patrons de conception, raffinement automatique de modèle, génération de code, validation par construction de modèles...), afin de permettre aux développeurs de se concentrer sur les aspects métier du système (fonctionnalités, contraintes de performance...) [PHA 04]. ACCORD concerne la spécification de systèmes temps réel décomposés par des *objets temps réel* étendus par les concepts suivants [GER 04] : une boîte à lettre pour la réception des requêtes et un contrôleur de concurrence et d'état spécifié par une machine à états arbitrant l'exécution des messages en fonction de l'état et des contraintes de concurrences associées reposant sur la représentation continue du temps. La validation dans la méthode ACCORD concerne trois aspects [PHA 04]: la vérification, la simulation et le test. L'aspect vérification utilise les méthodes formelles par le biais de l'outil AGATA [AGAT] en générant un modèle exécutable pour vérifier que le système décrit par le modèle de conception satisfait bien les exigences définies dans les diagrammes d'exigences. Ces dernières sont dérivées pour être spécifiées formellement soit par des formules de logique soit par des observateurs (une présentation de ces différentes techniques de vérification est proposée dans le chapitre V section 1). Les exigences vérifiées incluent les propriétés de sûreté, vivacité, blocages temporels et comportements non-conformes au cahier des charges reposant sur la description d'un temps logique. La méthode ACCORD|<sub>UML</sub> repose sur le profil UML ACCORD [ACCOR] mais peut être facilement dégagée de celui-ci pour être réutilisée dans d'autres environnements et intégrer l'aspect « validation » (soit la vérification, la simulation et le test) dans toutes les étapes du cycle de conception. Tout comme la méthode ACCORD, nous souhaitons, dans ce mémoire, nous dégager de profils spécifiques pour définir une méthodologie de conception de systèmes temps réel prenant en compte la phase de traitement des exigences (ce qui n'est pas défini dans la méthode ACCORD<sub>UML</sub>). La méthodologie présentée dans ce mémoire couvre donc la phase de spécification des exigences non-fonctionnelles temporelles, à formaliser au demeurant en vue d'une vérification formelle du modèle du système à concevoir.

Incluant le traitement des exigences par l'utilisation de *diagrammes d'exigences* SysML [SysML], MeMVaTEx [MeMV] (Méthode de Modélisation pour la Validation et la Traçabilité des Exigences) propose une méthodologie qui considère les exigences comme des classes conceptuelles définies dans les premières étapes de la modélisation et tracées durant tout le cycle de vie de développement du système. Cette méthode [ALB 07] permet, tout comme la méthodologie présentée dans ce mémoire, de faire la liaison entre les langages UML 2.0 [UML] et SysML [SysML]. MeMVaTEx est basée sur le profil UML MARTE [OMG 07] (cf. section 3.1.4) de modélisation de

systèmes temps réel. MeMVaTEx est orientée développement d'application temps réel dans le domaine de l'automobile. Le cycle de développement s'inspire de celui présenté dans le projet EAST-EEA [EAST]. Les exigences initiales sont données sous forme textuelle puis traduites par des diagrammes d'exigences SysML. Chaque exigence peut être connectée aux autres exigences, greffée à une partie du modèle ou encore représentée par un cas de test. Les exigences sont ensuite construites et tracées durant toutes les phases de développement en utilisant les mécanismes de traçabilité des exigences du méta-modèle SysML (concept de composition, vérification, satisfaction). La traçabilité des exigences est définie par construction de références entre le modèle et les documents externes où sont définies les exigences. Ces documents contiennent le résultat de la validation et vérification des exigences. Une matrice de traçabilité SysML contenant les résultats de validation des exigences peut alors être produite. Cependant l'aspect « formalisation des exigences » n'est pas décrit exhaustivement dans MeMVaTEx [ALB 07]. Nous présupposons donc que cette méthode n'inclut pas encore un processus de description formelle des exigences temporelles. Centrée autour de la vérification formelle d'exigences temporelles, l'approche proposée dans ce mémoire prend au contraire en compte l'aspect « recueil d'exigences » et la manière de formaliser les exigences non-fonctionnelles par une dérivation (cf. chapitre IV). De plus, la méthode MeMVaTEx repose sur le profil UML MARTE [OMG 07] (cf. section 3.1.4) pour le développement d'applications automobiles. La méthodologie présentée dans ce mémoire se veut être plus générale ; elle se dégage d'outils UML spécifiques et s'applique aux systèmes temps réel en général avec une particularisation au domaine des systèmes temps réel et distribués.

# 2. Systèmes temps réel et distribués (STRD)

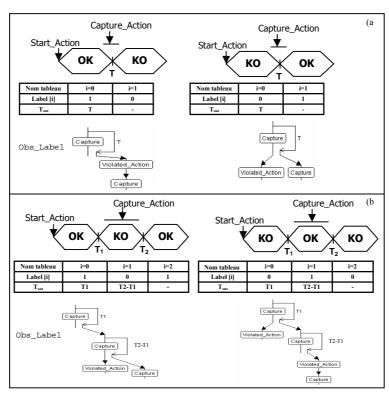

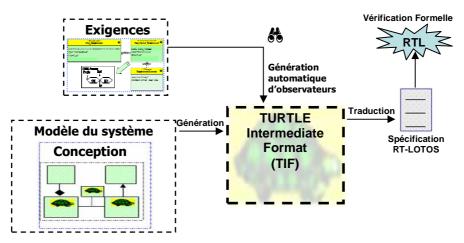

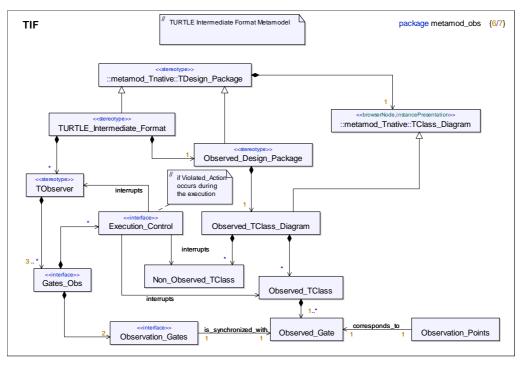

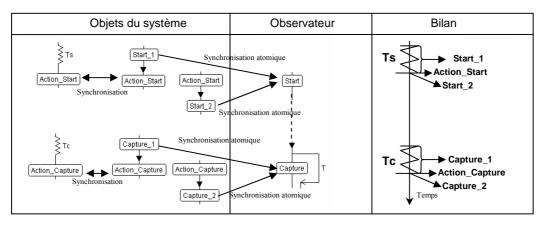

# 2.1. Les exigences temporelles liées à la Qualité de Service des STRD