# Space optical instruments optimisation thanks to CMOS image sensor technology

Olivier Saint-Pé\*a, Michel Tuleta, Robert Davancensa, Franck Larnaudiea, Pierre Magnanb, Philippe Martin-Gonthierb, Franck Corbièreb, Magali Estribeaub

aEADS-ASTRIUM 31 Avenue des Cosmonautes 31402 Toulouse Cedex 4 France bSUPAERO-CIMI 10 Avenue Edouard Belin BP 4032 31055 Toulouse Cedex France

### ABSTRACT

Today, both CCD and CMOS sensors can be envisaged for nearly all visible sensors and instruments designed for space needs. Indeed, detectors built with both technologies allow excellent electro-optics performances to be reached, the selection of the most adequate device being driven by their functional and technological features and limits. The first part of the paper presents electro-optics characterisation results of CMOS Image Sensors (CIS) built with an optimised CMOS process, demonstrating the large improvements of CIS electro-optics performances. The second part reviews the advantages of CMOS technology for space applications, illustrated by examples of CIS developments performed by EADS Astrium and Supaéro/CIMI for current and short term coming space programs.

Keywords: APS, space, CMOS Image Sensor, cameras

## **1. INTRODUCTION**

Today, both CCD and CMOS sensors can be envisaged for nearly all visible sensors and instruments designed for space applications. Indeed, detectors built with both technologies allow excellent electro-optics (EO) performances to be reached (detection efficiency, Modulation Transfer Function (MTF), read-out noise, dark current density....), the selection of the most adequate device type being driven by their functional and technological features and limits. Optical sensor and instrument designers have therefore to consider CCD and CMOS as complementary technologies rather than competing ones, which allows optimal instrumental concepts to be devised. The advantages and drawbacks of the CCD

are well known: this paper puts emphasis on the CMOS detectors to illustrate this complementarity.

The first part of the paper presents EO characterisation results of CMOS Image Sensors (CIS) developed by EADS Astrium and Supaéro/CIMI teams built with an optimised CMOS process, demonstrating the recent improvements of CIS EO performances.

The second part reviews the advantages of CMOS technology for space applications, illustrated by examples of CIS developments performed by EADS Astrium and Supaéro/CIMI for current and short term coming space programs.

## 2. CIS ELECTRO-OPTICS PERFORMANCES IMPROVEMENTS

CIS developed during the infancy of this technology were manufactured using standard mixed signal CMOS processes. They featured good EO performances1, close to the ones achieved by standard front-side illuminated CCDs usually used for space programs developed in the nineties2. Such results allowed design engineers to consider this technology for applications which strongly benefited of CIS functional and technological advantages, such as star trackers and miniature cameras3. Nevertheless, some of these EO performances were not sufficient in order to fulfil high-end applications for demanding applications such as Earth observation. Despite possible performances improvement thanks to specific in pixel electronics designs4, only CMOS technology modifications were able to bring strong improvements for some of the major CIS EO parameters5. Since the end of the 90s, and as the photonics market was strongly growing, several CMOS foundries invested in order to propose optimized CMOS technologies able to offer high performances for large volumes applications (mobiles, digital cameras, computer peripherals, toys....).

\*olivier.saintpe@astrium.eads.net: phone number: 33 5 62 19 67 16

Copyright 2005 Society of Photo-Optical Instrumentation Engineers. This paper was published in "Proceedings of SPIE - Volume 5978 - Sensors, Systems, and Next-Generation Satellites IX " and is made available as an electronic reprint with permission of SPIE. One print or electronic copy may be made for personal use only. Systematic or multiple reproduction, distribution to multiple locations via electronic or other means, duplication of any material in this paper for a fee or for commercial purposes, or modification of the content of the paper are prohibited.

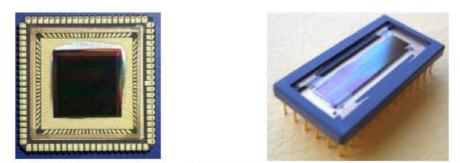

The space community can today benefit of such technological improvements, as recently demonstrated by devices (Fig.1) developed by EADS Astrium and Supaéro/CIMI6 using a 0.35 µm CMOS process optimized for imaging applications.

Fig 1: left: 1024x1024 pixels 2D array with 13 µm pixel pitch; right: 3078 pixels linear array with 6.5 µm pixel pitch: both devices have been manufactured using a 0.35 µm CMOS process optimized for imaging applications

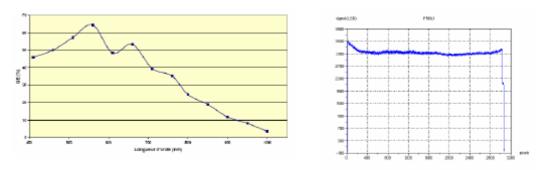

The improvements of the performances achieved for these devices are impressive, as reported in previous papers about 1k x 1k 2D arrays6,7. For the 3k linear array featuring 6.5  $\mu$ m pitch, peak detection efficiency close to 70% has been measured (geometric fill factor close to 100%), as shown by Fig 2-a, with excellent PhotoResponse Non Uniformity (Fig. 2-b). The device has been operated without any performances degradation at least up to 15 Mpixels/s.

Fig. 2: left: peak detection efficiency close to 70 % has been measured using a front-side illuminated monolithic CMOS Image Sensor (3k linear array with 6.5 µm pixel pitch); right: the uniformity of photoresponse of the device is excellent

EO performances of CMOS processes optimised for imaging applications are continuing to increase8. Coupled to CMOS technology scaling, this leads to CIS strong improvements. Today, even consumer high quality reflex9 or digital video10 cameras are increasingly equipped with CIS instead of CCDs. In addition, thanks to a strong R&D activity, alternative ways that could be foreseen for consumer and/or niche imaging markets (such as space, military and medical ones) are explored, some of them being driven by the needs for continuously smaller pixel pitches required for consumer applications (pixel pitch as low as 1.5 µm being now achieved):

- the hybrid approach, which main advantage is to allow independent optimisation for the photodetectors layer and for the read-out circuit layer. In addition, hybridisation approach permits to reach nearly 100% fill factor and gives more rooms for the in-pixel circuitry. Two different ways are today investigated. The first one is close to what is done for IRCMOS, i.e. indium bump flip chip assembly of a monocristalline silicon detection layer on top a CMOS read-out circuit11. The second one is based on the deposition of amorphous silicon thin film on top of the read out circuit12.

- The thinned and back side illuminated approach13, derived from what is developed for CCD, which should allow to improve quantum efficiency/fill factor, particularly for the shortest wavelengths, even for small pixel pitch.

## CIS ADVANTAGES FOR SPACE APPLICATIONS

## 3.1 General overview

The previous paragraph has demonstrated that CIS EO performances allow these detectors to fulfil demanding applications. As mentioned in the introduction, the selection of the detection technology has therefore to be driven by the functional and technological features and limits, which generally become the discriminating point between CMOS and CCD. Whatever the photodetector selected for photons to electrons conversion, all the approaches listed in the previous paragraph stay compatible with the mixed signal core process and would offer several technical advantages with respect to CCD, such as (non exhaustive list):

- Very low power consumption, which could be a driver for solar system exploration or optical instruments on board microsatellites: without any optimisation, the 1k x 1k array presented above feature less than 20 mW power consumption (2 Mpixels/s output rate) to be compared to several hundreds mW for a CCD with equivalent format. The power consumption ratio between CIS and CCD image function would even more increased when including all peripheral electronics

- High frame rate operations, which cannot be offered by CCD, explaining why all recent imagers developed for large frame rates are based on CMOS technology. In addition, it should be noticed that the temporal noise of CIS will not degrade as fast as the one of CCD with increasing read-out rate, as CIS pixel bandwidth is better matched to the sampling frequency

- Read-out flexibility, such as spatial sub-windowing, very fast access to the useful informations, temporal gating, multiple read out in order to reduce temporal noise, provide images deglitching and/or manage a large dynamics, use of rolling or snapshot read-out, in order to avoid artefacts present in CCDs used for space applications such as smearing

- Simple electrical interfaces and integration of peripheral functions (such ADC), in order to decrease power and mass budgets, to reduce instrument integration effort and to improve reliability

- Ability to design photodetectors topologies dedicated to the applications. Contrary to CCDs, which pixel size and topology are constrained by charges transfer need, CIS pixels can match the ultimate requirement for a given application, such as photosensitive size and shape. In addition, very small pixels (less than 2 µm) can be addressed thanks to advanced lithographic design rules and very large photodiodes can be designed too

- Strong antiblooming capability without any impact on the other parameters

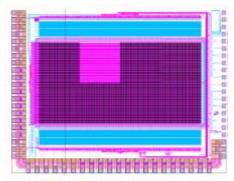

- Better behaviour with respect to radiation environments for both ionising dose effects and displacement damages, even using standard CMOS technologies, thanks to the use of specific design rules14 (figure 3). This advantage is particularly important for intermediate and elliptic orbits around Earth and for missions close to the Sun (Bepi Colombo and Solar Orbiter ESA future missions for instance).

Fig; 3: Test vehicle developed by EADS Astrium and Supaéro/CIMI using a standard 0.35 µm CMOS process. Several pixel types have been implemented on this vehicle with optimised designs in order to improve their behaviour with respect to ionizing dose effects. The device has been tested as fully operationnal at least up to 100 krads.

- Read-out compatibility with other spectral domains. For instance, the same electronics can be used for different spectral channels, from UV to IR

- On-chip analogue and/or digital signal processing integration in order to improve data processing while avoiding expensive and power hungry off-chip processing such as those required when using CCDs

## **3.2** Current or short term coming developments

Based on EADS Astrium large experience in optical instruments and sensors design and considering that our team has now 10 years of experience with CMOS and more than 20 years of experience with CCDs, some lessons have been learnt about the use of CIS for space applications:

- the use of CIS allows performances similar to CCD to be achieved in some applications, while decreasing instrument/sensor cost. Even if it is misleading to consider that the price of a state of the art CIS dedicated to an ambitious space mission will be low, it is true that the price of the complete imaging function would be lower using a specific CIS instead of a CCD for a large number of space applications.

- Thanks to its architectural / technological advantages, CIS can improve some instruments and sensors performances

- CIS allows new instruments designs that were not feasible based on CCDs usually used for space applications

- In some specific cases, CCD cannot easily be replaced by CIS: this is mainly the case when charges transfer is a specific advantage/need for the application

- System architecture global optimisation can be done by the design of a dedicated CIS, which can be considered as an Imaging-ASIC

- Mimic what is done with CCD when designing a system based on CIS will rarely lead to the optimum result

The following examples demonstrate that CIS is now considered as a mature technology by our team and that current developments are based on this technology.

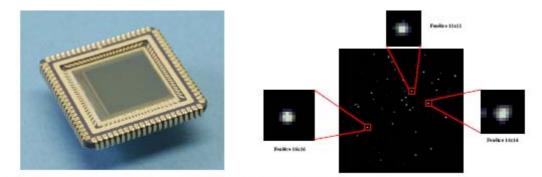

#### 3.2.1 Star trackers and optical terminals

Star trackers were among the first equipments for which CIS were foreseen as featuring strong advantages over CCDs. Figure 4 shows a 2D array developed by EADS Astrium and Supaéro/CIMI for such applications15, including a 750x750 pixels photosensitive area (20 µm pixel pitch), CDS stages and a powerful integrated programmable timing and control function offering several read-out modes: autonomous read-out, adjustable integration time, fast charges damping, multiple read-out and sub-window dynamic mode able to randomly read a large number of windows even if superimposed.

Fig 4: pixels (20 µm pitch) CIS developed for star tracking applications, including a dedicated programmable timing and control function: right: example of application for the sub-window dynamic mode for this CIS

In the nineties, EADS ASTRIUM developed the SILEX (Semi-conductor Inter-satellite Link Experiment) system for the ESA, and gained a strong know-how in optical communications16. First SILEX optical communication was successfully performed in December 2001 between the two optical terminals respectively

mounted onboard geostationary ARTEMIS spacecraft and Low Earth Orbit SPOT4 spacecraft (figure 5-a). The SILEX Terminal Optical Bench is equipped with two CCDs:

- The Acquisition Sensor Detection Unit (ASDU) is a 288 x 384 pixels CCD which allows the spot detection in the terminal Field of View, at the beginning of the Acquisition phase.

- The Tracking Sensor Detection Unit (TSDU) is a 17x17 pixels CCD which allows to track the spot at the center of the terminal Field of View, at high frequency at the end of the Acquisition phase, and during all the Communication phase.

Both CCDs offer a 3Mpixels/s rate, and frames rate are adjusted depending of required SNR, typically respectively to 30Hz and 4kHz. The SILEX system demonstrated in-flight expected performances, but the Assembly, Integration and Test phase of the terminal optical benches was long and meticulous, due to separated Acquisition and Tracking sensors.

Since end of 2003, EADS ASTRIUM develops for the DGA, a new optical terminal to be mounted onto an aircraft to demonstrate the possibility to communicate with the terminal mounted on board ARTEMIS. A 750x750 pixels array with high output rate has been developed in the frame of this project, to realize both the Acquisition and Tracking functions17. Acquisition frame rate is 10Hz and Tracking frame rate can be adjusted until 12kHz depending of required SNR. Figure 5-b shows the combined Acquisition and Tracking Sensor before integration on the Optical Bench. This sensor simplifies dramatically the Assembly, Integration and Test of the terminal Optical Bench and illustrates the possibilities offered by CMOS Imaging Sensors in such complex system as optical communication terminal.

Fig. 5-a: left: SPOT 4 images transmission down to ground via optical link and ARTEMIS relay overcomes intermittent radio electrical visibility from its ground network; Fig. 5-b: right: CIS acquisition and tracking sensor developed by EADS Astrium and Supaéro/CIMI

Through specific studies performed by Astrium for institutional customers (ESA, CNES,...) or on internal funding, CMOS Image Sensor have several times being compared to CCDs for other sensor applications – sensors meaning that the imaging device is integrated in a closed loop able to control an overall process (platform stability, mechanisms pointing...)– generally showing strong advantages for the use of CIS versus CCD.

## **3.2.2 Earth observation**

Earth (or other Solar system objects) observation is an important field within space business. Since the beginning of the 80s, most of the visible sensors dedicated to remote sensing from space are based on CCD detectors. The availability of high performances CIS offers a powerful alternative, not only due to the generic advantages of CIS with respect to CCD. It is for instance well known that the use of CIS will be beneficial for hyperspectral instruments (based on a dispersive spectrometer) as it offers read-out of spectral line of interest, selectable gain and/or dynamic range per spectral line, no smearing artefact, higher read-out rate...

More generally, smearing is often a drawback for 2D CCDs in space (even for frame transfer devices), as it degrades the quality of the useful data, requires specific processing and can strongly reduce the useful dynamics per pixel. Interline architecture would remove this weakness but is not offered by CCD manufacturers working

within the space niche market. Mechanical shutter is an other available approach, but at the expense of higher risk, budget and vibrations. CCDs smearing effects is especially bothersome when: (i) high speed has to be achieved, for instance in whiskbroom observation modes; (ii) large size devices are requested, such as for staring or step and stare observations.

In the framework of a recently started development for an Earth observation instrument located on GEO orbit, EADS Astrium has selected CIS rather than CCD technology in order to manufacture the requested 2 Millions pixels detector flight models. This choice is mainly driven by the absence of smearing and by the larger available charge handling capacity per pixel. The launch of the instrument is planned before end of 2008.

Observation of Earth or Solar system objects is often based on pushbroom technique. Depending on the requested spatial resolution and Signal to Noise Ratio (SNR), the orbit parameters, the platform capabilities, the optics characteristics and the scene radiometric features, the instrument designer can select either a linear array or a Time Delay and Integration (TDI) device. Since 2000, in cooperation with SUPERO/CIMI and CEA/LETI, Astrium has studied for DGA analogue TDI CIS architectures able to fulfil the most demanding High Resolution (HR) requirements for Earth observation, demonstrating the feasibility for such approach. The time delayed summation of the voltage provided by each photodetector from a given TDI column is performed on chip at the periphery of the photosensitive area. Even if such approach adds on chip complexity with respect to TDI CCDs, and taken into account the design/integration complexity of today and future HR focal planes, the use of such devices would lead to simpler focal planes and lower mass/power/envelope budgets.

More recently, EADS-Astrium and SUPAERO/CIMI have studied on chip digital TDI as an alternative to the analogue approach, demonstrating that it will be possible to efficiently emulate TDI by digital ways even for demanding Earth observation missions and confirming that such an architecture can feature a strong interest18, particularly taken into account the expected CMOS digital performances improvements in the coming years.

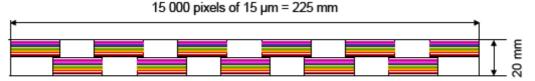

When TDI is not requested for pushbroom systems, CMOS linear array can be selected, featuring several advantages with respect to CCDs while reaching high electro-optics performances (see §2), particularly for multispectral and superspectral observations. Indeed, the architecture flexibility and the low power dissipation of CIS allow to easily manufacture multilinear arrays, that can be butted together in order to build large multispectral focal planes, as proposed by Astrium in the framework of future ESA missions (Fig. 6). If required, other detection material can be hybridized on the CMOS device in order to extend the spectral range of the focal plane19 (for instance from VISNIR up to SWIR using MCT or InGaAs photodiodes array).

Fig. 6: thanks to CIS architecture flexibility and low power dissipation, high performances multispectral CMOS linear arrays can be manufactured. Butting several of them would lead to large superspectral focal planes

Alternatives to pushbroom observations from Low Earth Orbit are also investigated. In the framework of a 2001 CNES study, Astrium has proposed to use the CIS snapshot capabilities in order to build large 2D focal planes featuring electronics shutters and operated in stare or in step and stare modes. This approach is currently investigated20, as it features system advantages, even if some specific parameters have to be optimized. Indeed, and even if a large number of video outputs operated at high pixel rate are used for the pixel information acquisition (minimizing therefore the delay between the end of the integration time and the data read out), the design of the analogue memory node within each pixel has to be optimised in order to maximize its shuttering efficiency (degraded by both non perfect light masking and leakage current sources) while minimizing fill factor degradation.

## 3.2.3 Smart sensors

CIS offer the capability to mix within a single chip detection and signal processing functions. This opens the door for new applications thanks to smart sensors approach, when compared to a more classical way, where pixel/image acquisition and data processing are performed at different places. Some processing can be performed using analogue subfunctions, for instance the calculation of the energetic centroiding in a sub-window21. The

use of deep sub-micron CMOS process would allow to integrate one ADC per pixel22, offering the capability to design local and global data processing via numerical way.

An illustration of CIS smart sensor advantages when compared to CCD is what can be called smart events detectors. This example also demonstrates that system architect have now to master new capabilities offered by CIS in order to achieve the optimal sensor/instrument architecture and design. Events detection means that within a field imaged on the imager photosensitive area, some events have to be detected and localized. In some case, the signal level of the events need also to be measured. Using a CCD, and because of its serial read-out architecture, all the pixels of the frame have to be read out, transferred to a dedicated electronics function and processed in order to determine which pixels contain informations related to the events to be detected (in general, the fraction of hit pixels is very low). The criticality of such a sensor increases with the amount of pixels (large 2D arrays for instance) and with the temporal accuracy specified for the events detection process (few kHz being required in some case). For demanding applications, a design based on CCDs leads to hundreds of fast video outputs coupled to a power hungry analogue and digital electronics, making its implementation very difficult for space applications. Thanks to CIS advantages, elegant architectures can be designed. Indeed, it is possible to integrate for each pixel a comparison function able to detect at high rate if its photodetector has been illuminated or hit by the event to be detected. If this is the case, the in pixels comparators will made available on dedicated busses the addresses of the (few) pixels to be read-out, dramatically reducing the data rate and removing any off-chip data processing dedicated to events detection. Several fields of applications, such as high energy particles detection, photons counting23, flash detection...will benefit of such "events detectors" architecture and operation for short term coming space applications.

#### CONCLUSIONS

The previous paragraphs demonstrated that CIS are now able to fulfil the requirements for many space sensors or instruments and that they offer real advantages with respect to CCDs for some applications. The mastering of CIS capabilities is therefore a necessity for a team willing to manufacture new generation of optical sensors and instruments. New ways are today investigated in order to further improve their EO performances and functional features. CIS should therefore be one of the key element allowing to take up future space imaging systems challenges.

### REFERENCES

1. O. Saint-Pé et al., *High performance monolithic CMOS detectors for space applications*, SPIE Proceedings, Vol. 4540, pages 318-327, 2001

2. TH 7863A data sheet, Thomson Composants Militaires et Spatiaux CCD Products Handbook, 1992/1993

3. C. Cavadore et al., *Active Pixel Image Sensor for space applications*, ESA 2nd Round Table on Micro/Nano – Technologies for Space, 15-17/10/97, WPP-132

4. P. Belliot, Axes d'amélioration des pixels de type APS réalisés en fonderie CMOS standard, APS CNES workshop, 27-28/11/02

5. M. Furumiya et al. *High-sensitivity and no cross-talk pixel technology for embedded image sensor*, IEEE Transaction on Electron Devices, Vol. 48, n°10, 2001

6. O. Saint-Pé et al., *Research-grade CMOS image sensors for demanding space applications*, 5th International Conference on Space Optics (ICSO), 2004

7. O Saint-Pé et al., *Research-grade CMOS image sensors for remote sensing applications*, SPIE Proceedings, Vol. 5570, pages 549-556, 2004

8. JA. Krymski et al, A 2 e- noise 1.3 Mpixel CMOS sensor, SPIE Proceedings, IEEE Workshop on CCD and AIS, pages 1-6, 2003

9. B. Rodricks et al., First principles' imaging performance evaluation of CCD- and CMOS- based digital camera systems, SPIE Proceedings, Vol. 5678, pages 59-74, 2005

10. L. J. Kozlowski et al. A progressive 1920x1080 Imaging SoC for HDTV, ISSCC 2005 proceedings

11. Y. Bai et al., Hybrid CMOS focal plane array with extended UV and NIR response for space applications, SPIE Proceedings, Vol. 5167, pages 83-93, 2003

12. See http://www-leti.cea.fr/commun/events/RA-2004-fr.pdf

13. B. Pain et al., A back-illuminated Megapixel CMOS Imager sensor, IEEE Workshop on CCD and AIS, Nagano, 2005

14. P. Martin-Gonthier et al., Overview of CMOS process and design options for image sensor dedicated to space applications, this proceeding

15. F. Larnaudie et al., *Development of a 750x750 pixels CMOS Imager Sensor for tracking applications*, 5<sup>th</sup> International Conference on Space Optics (ICSO), 2004

16. G. Planche et al. SILEX in orbit performances, 5th International Conference on Space Optics (ICSO), 2004

17. M. Bréart de Boisanger et al., Développement d'un senseur d'acquisition et de poursuite (ATS) pour un terminal de liaison optique, OPTRO 2005 conference, Paris

18. L. J. Kozlowski et al. Progress toward high-performance infrared imaging systems-on-a-chip, SPIE Proceedings, Vol. 4130, pages 245-253, 2000

19. J. A. Mendenhall et al., Flight test results of the Earth Observation-1 Advanced Land Imager, SPIE Proceedings, Vol. 4814, pages 296-305, 2002

20. A. Materne et al., *Development of a CMOS snapshot Active Pixel Sensor for spaceborne Earth observation applications*, first symposium on Disruptive Technologies, 4 to 7th of July 2005, Marseille

21. C. Sun et al, A smart CMOS imager with on-chip high-speed windowed centroiding capability, IEEE Workshop on CCD and AIS, pages 29-32, 1999

22. S. Kleinfelder et al., A 10000 frames/s CMOS digital pixel sensor, IEEE Journal of Solid-State Circuits, Vol 36, n°12, pages 2049-2059, 2001

23. R. A. Kimble et al., A high-speed, event-driven Active Pixel Sensor readout for photon-counting microchannel plate detectors, SPIE Proceedings, Vol. 4854, pages 203-214, 2003