# DESIGNING OF AN OPERATIONAL AMPLIFIER

## FIRDAUS @ NUKHA BINTI TIMYATI

UNIVERSITE TUN HUSSEIN ONN MALAYSIA

|                                     | UNIVERSITI TU                                           | UN HUSSEIN ONN MALAYSIA                                                                                                                  |

|-------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | BORANG PEN                                              | GESAHAN STATUS TESIS <sup>*</sup>                                                                                                        |

| JUDUL:                              | DESIGNING OF AN OPI                                     | ERATIONAL AMPLIFIER                                                                                                                      |

|                                     |                                                         |                                                                                                                                          |

|                                     |                                                         |                                                                                                                                          |

|                                     | SESI PENGA                                              | AJIAN:                                                                                                                                   |

| Saya,                               | FIRDAUS @ NU                                            | UKHA BINTI TIMYATI                                                                                                                       |

|                                     | 1                                                       | (HURUF BESAR)                                                                                                                            |

| mengaku membe<br>syarat-syarat sepe | narkan tesis ( <del>PSM</del> /Sarjana<br>erti berikut: | a/ <del>Doktor-Falsafah</del> )* ini disimpan di Perpustakaan dengan                                                                     |

| <ol><li>Perpustakaar</li></ol>      | n dibenarkan membuat sal<br>nggi.                       | Hussein Onn Malaysia.<br>inan untuk tujuan pengajian sahaja.<br>inan tesis ini sebagai bahan pertukaran antara institusi                 |

| SU                                  | LIT                                                     | (Mengandungi maklumat yang berdarjah keselamatan atau<br>kepentingan Malaysia seperti yang termaktub di dalam<br>AKTA RAHSIA RASMI 1972) |

| TE                                  | RHAD                                                    | (Mengandungi maklumat TERHAD yang telah ditentukan<br>oleh organisasi/badan di mana penyelidikan dijalankan)                             |

| TII 🗸                               | DAK TERHAD                                              |                                                                                                                                          |

| (TANDA                              | FM<br>TANGAN PENULIS)                                   | Disahkan oleh:<br>(TANDATANGAN PENYELIA)                                                                                                 |

| Alamat Tetap :                      |                                                         | -                                                                                                                                        |

| 15 JALAN KENAI                      | NGAN INDAH                                              |                                                                                                                                          |

| TAMAN KENAN                         |                                                         | PROF. MADYA SITI HAWA BINTI RUSLAN                                                                                                       |

| 86400 PARIT RAJ                     | A BATU PAHAT JOHOR                                      | Nama Penyelia                                                                                                                            |

| Tarikh : NOVE                       | MBER 2008                                               | Tarikh : NOVEMBER 2008                                                                                                                   |

CATATAN

\*

Potong yang tidak berkenaan. Jika tesis ini SULIT atau TERHAD, sila lampirkan surat daripada pihak Berkuasa/organisasi berkenaan dengan menyatakan sekali sebab dan tempoh tesis ini Perlu dikelaskan sebagai SULIT atau TERHAD Tesis dimaksudkan sebagai tesis bagi Ijazah Doktor Falsafah dan Sarjana secara penyelidikan, atau disertasi bagi pengajian secara kerja kursus dan penyelidikan, atau Laporan Projek Sarjana Muda (PSM) \*\*

#### DESIGNING OF AN OPERATIONAL AMPLIFIER

## FIRDAUS @ NUKHA BINTI TIMYATI

A project report is submitted in partial fulfillment of the requirements for the award of the Degree of Master in Electrical Engineering

Faculty of Electrical and Electronic Engineering Universiti Tun Hussein Onn Malaysia

NOVEMBER 2008

"I declare that I have read this thesis and in my opinion, it is suitable in terms of scope and quality for the purpose of awarding a Master in Electrical Engineering"

|            | T.L                                   |

|------------|---------------------------------------|

| Signature  | :                                     |

| Supervisor | : ASSOC. PROF. SITI HAWA BINTI RUSLAN |

| Date       | : NOVEMBER 2008                       |

To my darling husband... Md. Nazri Mohidin @ Mohyeddin... you are all things beautiful to me...

To my adorable kids... Mirza Khumaini, Nuqman Nazhan, Firas Nazih and Naqib Nadzif... you are always in my heart and will always be...

To **my beloved father**... *Haji Timyati Alwai*... I really appreciate your upbringing and endless support...

To my only sister... Noor Fahrina Timyati... may you lead a successful life despite your hearing disability...

#### ACKNOWLEDGEMENT

Alhamdulillah, Praise to Allah the almighty which with His bless; the completion of this dissertation is possible.

It is my greatest pleasure to express my gratitude to everyone whom had contributed towards the completion of this dissertation. My special gratefulness firstly goes to my supervisor, **Assoc. Prof. Siti Hawa Binti Ruslan**. Her continuous guidance and knowledge sharing is truly invaluable towards my intellectual and personal development.

There were friends and families that had kindly assisting me along the way of this dissertation. Their books, notes, thoughts, ideas, and support had helped me in finding solutions whenever there was problem.

The seed of kindness will always bloom to the fullest. The seed of knowledge is timeless and precious. Thank you one, thank you all, for the pleasure of appreciation has been done.

$\mathbf{i}\mathbf{v}$

#### ABSTRACT

Natural signals come in analog forms and these signals are bearing valuable information and need to be processed. An operational amplifier is the most versatile and important building blocks in analog circuit design. Therefore this project is dedicated to designing an operational amplifier and analyzing the properties. The performance is measured based on its DC and small-signal analysis. Schematic of the circuit is drawn using Tanner EDA's S-Edit<sup>TM</sup>. Then T-Spice<sup>TM</sup> is utilized to simulate the circuit. Output waveform generated by W-edit is used to obtain the DC curve, the Bode plot for magnitude and Bode plot for phase. Additionally, other types of parameters are used for the same circuit. It is found that Level 1 Parameters suits the operational amplifier being designed and it works well as expected. The design gives a 96dB gain. The layout for the whole circuit is done based on MOSIS layout rules using SCN3M technology.

#### ABSTRAK

Dunia kita dipenuhi oleh pelbagai isyarat analog semulajadi yang membawa maklumat-maklumat tertentu. Namun maklumat ini perlu diproses sebelum digunakan. Salah satu komponen yang paling berguna dan merupakan salah satu blok penting dalam rekabentuk litar analog ialah penguat operasi. Oleh itu, projek ini adalah bertujuan untuk menghasilkan litar penguat operasi dengan mengambilkira pelbagai faktor penting dalam rekabentuk litar. Hasil simulasi litar ini digunakan untuk menentusahkan semua kiraan yang dibuat semasa proses rekabentuk. Prestasi litar diukur berdasarkan analisis DC dan isyarat kecil. Litar skematik dalam projek ini dihasilkan menggunakan S-Edit™ Tanner EDA. Simulasi litar pula menggunakan T-Spice<sup>™</sup>. Gelombang keluaran dilihat melaui W-Edit dan kemudiannya digunakan untuk menentukan kemampuan litar. Sebagai tambahan, penggunaan set parameter yang berlainan turut digunakan untuk simulasi litar yang sama. Hasil kajian mendapati rekabentuk litar ini sesuai menggunakan parameter Level 1 dan dapat beroperasi seperti yang dikehendaki. Litar yang direka menghasilkan gandaan sebanyak 96dB. Bentangan keseluruhan litar juga telah dibuat berdasarkan hukum bentangan dari MOSIS menggunakan teknologi SCN3M.

## CONTENTS

CHAPTER ITEMS

PAGES

| TITLE           | i   |

|-----------------|-----|

| DECLARATION     | ii  |

| DEDICATION      | iii |

| ACKNOWLEDGEMENT | iv  |

| ABSTRACT        | v   |

| ABSTRAK         | vi  |

| CONTENTS        | vii |

| LIST OF TABLES  | xi  |

| LIST OF FIGURES | xii |

|                 |     |

## I INTRODUCTION

| I  | INTRODUCTION |                           | 1 |

|----|--------------|---------------------------|---|

|    | 1.1          | Background of the Problem | 1 |

|    | 1.2          | Statement of the Problem  | 3 |

|    | 1.3          | Expected Findings         | 3 |

|    | 1.4          | Objectives                | 4 |

|    | 1.5          | Importance of the Study   | 4 |

|    | 1.6          | Scope of Project          | 5 |

|    | 1.7          | Thesis Outline            | 5 |

|    |              |                           |   |

| II | LITE         | RATURE REVIEW             |   |

| 2.1 | Literat | ure Review                   | 6  |

|-----|---------|------------------------------|----|

|     | 2.1.1   | Previous Works               | 6  |

| 2.2 | MOSFET  |                              | 8  |

|     | 2.2.1   | MOSFETs Designations         | 9  |

|     | 2.2.2   | MOSFET Drain Characteristics | 10 |

vii

|      | 2.2.3   | MOSFET Circuit Model                   | 11 |

|------|---------|----------------------------------------|----|

| 2.3  | Ampli   | fier Concepts                          | 13 |

|      | 2.3.1   | Common-source Amplifier with           | 14 |

|      |         | Current Source Supply                  |    |

|      | 2.3.2   | Current Sources and Sinks              | 14 |

|      | 2.3.3   | Differential Amplifier                 | 16 |

| 2.4  | Two-S   | tage CMOS Operational Amplifier        | 17 |

|      | Topolo  | ogy                                    |    |

|      | 2.4.1   | DC Analysis of a Two-Stage Amplifier   | 21 |

|      | 2.4.2   | Small-Signal Analysis                  | 25 |

| RES  | EARCH   | METHODOLOGY                            |    |

| 3.1  | The Ty  | wo-Stage Operational Amplifier         | 28 |

|      | 3.1.11  | Determining the Voltage and Currents   | 29 |

|      | 3.1.2 I | Determining the Dimension of           | 30 |

|      | -       | Fransistors                            |    |

|      | 3.1.3 H | Performance of Operational Amplifier   | 31 |

|      | 3.1.4 7 | Tanner EDA Tools                       | 31 |

|      | 3.1.57  | The Level 1 MOSFET Model               | 32 |

|      | F       | Parameters                             |    |

| 3.2  | Analys  | sis of Two-Stage CMOS Operational      | 33 |

|      | Ampli   | fier                                   |    |

|      | 3.2.1 E | DC Analysis of the Two-Stage Amplifier | 33 |

|      | 3.2.2 S | mall-signal Analysis                   | 34 |

| RESU | ILTS AN | ID ANALYSIS                            |    |

| 4.1  | The Ci  | rcuit                                  | 35 |

|      | 4.1.1   | Current Sources/Sinks                  | 36 |

|      | 4.1.2   | Common-Source Amplifier                | 37 |

|      |         |                                        |    |

4.1.3 Transistor Dimensions

III

IV

viii

38

| 4.2 | Compariso      | n of Results                  | 39 |

|-----|----------------|-------------------------------|----|

|     | 4.2.1 DC       | Results                       | 39 |

|     | 4.2.2 AC       | Results                       | 40 |

| 4.3 | Simulation     | Results for Waveform          | 41 |

|     | 4.3.1 The      | DC Characteristics            | 41 |

|     | 4.3.2 The      | Bode Plot for Magnitude       | 42 |

|     |                | Bode Plot for Phase           | 43 |

| 4.4 | Results of I   | Level 2 Model Parameters      | 43 |

|     | 4.4.1 The      | DC Characteristics            | 44 |

|     | 4.4.2 The      | Bode Plot for Magnitude       | 45 |

|     |                | Bode Plot for Phase           | 46 |

| 4.5 | Results of 2   | .0μm Process                  | 47 |

|     | 4.5.1 Level    | 2 MOSFET Parameters           | 47 |

|     | 4.5.1.1        | The DC Characteristics        | 48 |

|     | 4.5.1.2        | 2 The Bode Plot for Magnitude | 49 |

|     | 4.5.1.3        | The Bode Plot for Phase       | 50 |

|     | 4.5.2 Nomin    | al Level 5 MOSFET Parameters  | 50 |

|     | 4.5.2.1        | The DC Characteristics        | 51 |

|     | 4.5.2.2        | The Bode Plot for Magnitude   | 52 |

|     | 4.5.2.3        | The Bode Plot for Phase       | 53 |

| 4.6 | The Transist   | ors Region                    | 54 |

| 4.7 | The Layout     |                               | 55 |

|     | 4.7.1 PMOS     |                               | 56 |

|     | 4.7.2 NMOS     |                               | 57 |

|     | 4.7.2.1        | PMOS and NMOS                 | 57 |

|     | 4.7.3 Resisto  | r                             | 58 |

|     | 4.7.4 Capacit  | ors                           | 59 |

|     | 4.7.5 Active a | and Passive Devices           | 60 |

|     |                |                               |    |

| V | CON | <b>VCLUSIONS</b> |    |

|---|-----|------------------|----|

|   | 5.1 | Discussion       | 62 |

|   | 5.2 | Conclusions      | 64 |

|   | 5.3 | Recommendations  | 65 |

|   | REF | ERENCES          | 66 |

|   | APP | ENDICES          | 69 |

х

## LIST OF TABLES

NO. OF TABLES

## TITLE

PAGES

| 2.1  | Results of operational amplifier in the previous research works.     | 7  |

|------|----------------------------------------------------------------------|----|

| 2.2  | Steady-state equations for n-channel MOSFET.                         | 12 |

| 2.3  | Steady-state equations for p-channel MOSFET.                         | 12 |

| 2.4  | DC MOSFET SPICE parameters.                                          | 13 |

| 4.1  | The output of current source/sink.                                   | 37 |

| 4.2  | The output of current source/sink with common-source                 | 38 |

|      | amplifier.                                                           |    |

| 4.3  | Transistor dimensions.                                               | 39 |

| 4.4  | Voltages at nodes.                                                   | 40 |

| 4.5  | DC results.                                                          | 40 |

| 4.6  | The PMOS Layout and its extraction results                           | 56 |

| 4.7  | The NMOS Layout and its extraction results                           | 57 |

| 4.8  | The results for current mirror, differential pair and current source | 58 |

| 4.9  | The layout and extraction result for a square of resistors           | 59 |

| 4.10 | The layout and extraction for the capacitors                         | 60 |

| 5.1  | The results of this operational amplifier design.                    | 63 |

|      |                                                                      |    |

## LIST OF FIGURES

| NO. OF      | FIGURES TIT                                | TLE                 | PAGES |

|-------------|--------------------------------------------|---------------------|-------|

|             |                                            |                     | 2     |

| 1.1         | Simple sample-and-hold.                    | CEET                | 9     |

| 2.1         | Voltage and current designations for MO    | SFE15.              | 10    |

| 2.2         | (a) I-V curves of a MOSFET.                | t since les monds   | 10    |

|             | (b) Description of I-V plot for MOSFET     | in simpler words.   | 11    |

| 2.3         | Characteristics of an NMOS device.         |                     | 11    |

| 2.4         | Characteristics of a PMOS device.          |                     | 14    |

| 2.5         | Common-source amplifier.                   |                     | 14    |

| 2.6         | Current mirror circuit.                    |                     |       |

| 2.7         | Fully differential amplifier with current  |                     | 17    |

| 2.8         | Block diagram for an integrated operation  | onal amplifier      | 18    |

| 2.9         | Differential input pair with current mirre | or.                 | 18    |

| 2.10        | The two-stage operational amplifier circ   | uit.                | 20    |

| 2.11        | Unity-gain feedback configuration.         |                     | 21    |

| 2.12        | The small-signal equivalent circuit.       |                     | 26    |

| 3.1         | Level 1 MOSFET Model Parameters.           |                     | 32    |

| 4.1         | The circuit.                               |                     | 36    |

| 4.2         | The circuit testing the function of curre  | nt source and sink. | 37    |

| 4.3         | The current source/sink with common        | source amplifier.   | 38    |

| 4.4         | The DC Characteristics curve.              |                     | 41    |

| 4.5         | The Bode plot for magnitude.               |                     | 42    |

| 4.6         | The Bode plot for phase.                   |                     | 43    |

| 4.7         | Level 2 Model Parameters.                  |                     | 44    |

| 4.8         | The DC characteristics based on Level      | 2 Parameters.       | 45    |

| 4.0<br>4.9  | The frequency response based on Leve       | el 2 Parameters.    | 46    |

| 4.9<br>4.10 | The Bode plot for phase based on Lev       | el 2 Parameters.    | 46    |

xii

## **NO. OF FIGURES**

## TITLE

## PAGES

| 4.11 | Level 2 Model Parameters of 2µm process.                       | 48 |

|------|----------------------------------------------------------------|----|

| 4.12 | The DC characteristics from Level 2 model parameters.          | 48 |

| 4.13 | The Bode plot for magnitude based on Level 2 model parameters. | 49 |

| 4.14 | The Bode plot for phase from Level 2 model parameters.         | 50 |

| 4.15 | Level 5 Model Parameters of 2µm process.                       | 51 |

| 4.16 | The DC characteristics of Level 5 model parameters.            | 52 |

| 4.17 | The Bode plot for magnitude based on Level 5 model parameters. | 53 |

| 4.18 | The Bode plot for phase based on Level 5 model parameters.     | 53 |

| 4.19 | The transistors' region for different parameters               | 54 |

| 4.20 | The layout of all devices                                      | 61 |

#### CHAPTER I

#### **INTRODUCTION**

The chapter is dedicated to description of background of the problem with statement of the problem is then clarified. Then, the expected findings, objectives, importance and scope of project are explained. Relevant terms used are revealed in the last part of this chapter.

#### 1.1 Background of the Problem

Digital implementation offers significant benefits. The operation of digital circuits does not require precise values of the signal and this means digital circuits are less sensitive than analogue circuits. Moreover, the emergence of very large-scale integration (VLSI) circuits had enabled the integration of complex digital signal processing (DSP) systems on a single chip. In terms of storage, digital signal can be stored almost indefinitely on various media without any loss (Mitra, 2006). These advantages had made digital implementation much more desirable than its analogue counterpart.

As most natural signals are in analogue form, including the biomedical signals, analogue signals need to be converted into digital form to be processed digitally. Sampling is a crucial step in typical digital signal processing system (Floyd, 2006).

Apparently, development of the integrated circuits in microelectronics industry is the most influential industry in the society. Operational amplifiers are one of the devices that could be designed using metal-oxide semiconductor fieldeffect transistors (MOSFET) in microelectronics analogue circuit design (Howe & Sodini, 1997). Sampling circuits also employ operational amplifier in its building blocks.

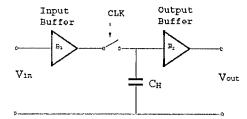

A simple sample-and-hold (S/H) circuit consists of an input buffer, an electronic switch, a storage capacitor and an output buffer as in Figure 1.1. The switch is closed during sample mode enabling  $V_{out}$  to track input voltage. In the hold mode, the switch is opened, isolating the storage capacitor from the input and  $V_{out}$  remains until the next sampling phase. Traditionally, S/H circuits are in voltage-mode whereby input voltage is sampled at discrete-times and held constant until the next sampling instant (Chennam & Fiez, 2004).

Figure 1.1: Simple sample-and-hold (Chennam & Fiez, 2004).

## 1.2 Statement of the Problem

Technology scaling and reduced supply voltages results in increased speed and reduced power consumption. Low power consumption is favourable in complementary metal-oxide semiconductor (CMOS) designs because this could prolong the battery-life. Therefore, this project is focusing in designing an operational amplifier with low voltage supply and low power consumption.

## 1.3 Expected Findings

The project is meant to come up with an operational amplifier to be used in analogue-to-digital converter (ADC) circuit. In this project, integrated circuit design system will be used. Therefore it consists of the schematic of transistor level circuits and their respective simulated output waveforms. Outputs will be obtained through the schematic editor, SPICE simulator and waveform viewer. The performance of the operational amplifier in this project is determined by its direct current (DC) characteristics and frequency response. All the values are first obtained by calculation and then compared with simulation values.

#### 1.4 Objectives

The output of the project is an operational amplifier consists of Metal Oxide Semiconductor (MOS) transistors. Specifically, the project purposes are:

- 1. To design an operational amplifier with power supply of 3.3V.

- 2. To design an operational amplifier that dissipates power in milli-Watts range.

## 1.5 Importance of the Study

This project is a CMOS analogue electronic design of an operational amplifier. It will have a relatively high gain at lower frequencies. An operational amplifier with good DC characteristics will eliminate the need of a voltage offset in the circuit and thus reduce the complexity of the circuit. Low power consumption in operational amplifier is desirable and therefore, this project will concentrate on producing an operational amplifier that consumes less power.

## 1.6 Scope of Project

There are many types of operational amplifier available. The operational amplifier in this design is set to:

- 1. Use power supplies of  $V_{DD}$  = 3.3V and  $V_{SS}$  = -3.3V.

- 2. Dissipate power in milli-Watt range.

- 3. Have the minimum length of  $3\mu m$  for all transistors.

- 4. Drive a typical capacitive load of 7.5pF for operational amplifier.

#### 1.7 Thesis Outline

This thesis started with Chapter I whereby every introduction that briefly describes the project. Then, Chapter II reveals the previous works on operational amplifier and all the theories relevant to design an operating amplifier. The research methodology is included in Chapter III. All the calculation and simulation results of the operational amplifier are in Chapter IV. As the final chapter, Chapter V includes discussion, conclusion, and recommendation.

#### CHAPTER II

#### LITERATURE REVIEW

#### 2.1 Literature Review

In order to facilitate comparison, the results obtained from previous works that had been published are summarized in Table 2.1. The operational amplifier concept is then briefly discussed. This project used MOSFETs, thus, the designation of voltages and currents are clarified first. Then, the drain characteristics of MOSFETs are pointed out. Equations related to the DC analysis of the amplifier are introduced and also equations involved in the small-signal analysis of the operational amplifier.

#### 2.1.1 Previous Works

Operational amplifier design has been developed continuously. The previous works can be concluded as in Table 2.1.

|   | Author                                                                                                      | Year | Power<br>Supply<br>(V) | Architecture                                                          | Low<br>Freqency<br>Gain (dB) | Unity Gain<br>Frequency                                       | Phase<br>Margins                                                | Power<br>Dissipa-        |

|---|-------------------------------------------------------------------------------------------------------------|------|------------------------|-----------------------------------------------------------------------|------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------|--------------------------|

| 1 | Rob van Dongen<br>& Vincent<br>Rikkink                                                                      | 1995 | 1.5V                   | simple two-<br>stage                                                  | 63dB                         | (Hz)<br>1MOhm 150p<br>F = 0.85MHz<br>1kOhm 150p<br>F = 1.1MHz | (degrees)<br>1MOhm 150<br>pF = 47deg<br>1kOhm 150p<br>F = 59deg | <u>tion (W)</u><br>135uW |

| 2 | G.N. Lu & G. Sou                                                                                            | 1998 | 1.3V                   | regulated-<br>cascode                                                 | >68dB                        | 10MHz<br>(transition<br>frequency)                            | 70deg                                                           | 0.28mW                   |

| 3 | Kimmo Lasanen,<br>Elvi Riiisiinen-<br>Ruotsalainen &<br>Juha<br>Kostamovaara                                | 2000 | 1.0V                   | bulk-driven<br>Miller comp.                                           | 83dB                         | 190kHz                                                        | 73deg                                                           | 5uW                      |

| 4 | Jean-Francois<br>Delage &<br>Mohamad Sawan                                                                  | 2001 | 2.7-<br>5.0V           | two-stage                                                             | 91.8dB                       | >13.8MHz                                                      | >51deg                                                          | not<br>available         |

| 5 | Vadim I-Vanov &<br>Shilong Zhang                                                                            | 2002 | 2.5-<br>5.5V           | not available                                                         | >100dB                       | 250MHz                                                        | not available                                                   | not<br>available         |

| 6 | Franz Schlögl &<br>Horst<br>Zimmermann                                                                      | 2005 | 1.2V                   | 4-stage Miller<br>comp.                                               | 128.8dB                      | 693MHz                                                        | 48deg                                                           | 18mW                     |

| 7 | Carsten<br>Bronskowski &<br>Dietmar<br>Schroeder                                                            | 2006 | 3.3V                   | rail-to-rail<br>folded<br>cascode                                     | not<br>available             | 1.1-39MHz                                                     | >55deg                                                          | 140uW-<br>30mW           |

| 3 | Philipp Meier auf<br>der Heide,<br>Carsten<br>Bronskowski,<br>Jakob M.<br>Tomasik &<br>Dietmar<br>Schroeder | 2007 | 3.3V                   | programmable<br>operational<br>amplifier<br>based on rail-<br>to-rail | not<br>available             | 0.3-48MHz<br>(μ power<br>consumption)                         | 68.4deg                                                         | 49uW                     |

Table 2.1: Results of operational amplifier in the previous research works.

Power consumption is one of the critical aspects in operational amplifier design. As power consumption is directly related to the current and voltage supply, it seems that reduced supply voltages means reduced power consumption. The low frequency gain and unity-gain frequency are two other aspects usually discussed. Process integration refers to the well-defined collection of semiconductor processes required to fabricate CMOS integrated circuits. There is a strong connection between circuit design and process integration (Baker, 2005). Since operational amplifiers in this review are all CMOS integrated circuit, variation in process might lead to variation in performance of the operational amplifier.

.

Rob van Dongen and Vincent Rikkink (Dongen & Rikkink, 1995) had developed two-stage architecture for the operational amplifier. The input stage was a transconductance amplifier while the output stage is a common-source amplifier. The combination has poles at higher-frequencies which were at 0.85 MHz and 1.1 MHz. Common-source amplifier was chosen for the output stage because it can operate using as low as 1V of voltage supply since in this configuration, there will be no more than two transistors between the V<sub>DD</sub> and ground.

Likewise, Jean-Francois Delage and Mohamad Sawan (Delage & Mohammad Sawan, 2001) were also proposing an operational amplifier based on two-stage amplifier. However, this operational amplifier was developed by a rail-to-rail input stage and an AB class amplifier at the output. It has minimal phase margin with 35pF of capacitive load. The pole is situated at 13.8 MHz. This means that the amplifier has a higher frequency of unity gain apart from having a higher low-frequency gain than the operational amplifier proposed by Ron van Dongen and Vincent Rikkink.

Similarly for this project, two-stage architecture is proposed for the operational amplifier, as it will meet the desired specification.

#### 2.2 MOSFET

The metal-oxide semiconductor field-effect transistor, MOSFET is a multiterminal microelectronic device. MOSFETs are the dominant transistor type for digital IC's and have important applications in analogue signal processing circuits (Howe & Sodini, 1997).